Page 1

CMOS LSI

Ordering number : EN4305A

52295TH (OT) No. 4305-1/3

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

Dual VCO

LC7444

Overview

The LC7444 consists of two independent VCO (voltage

controlled oscillator) circuits.

These circuits support VCO operation with only the

addition of external resistors that determine the oscillation

range.

Features

• Two independent VCO circuits

• The oscillator frequency range can be set with external

resistors.

• Good linearity in the voltage - frequency conversion

characteristics

• High-impedance oscillator control voltage input

• CMOS clock output

• Fabricated in a CMOS process for lower power

• Oscillator frequency range: 8 to 32 MHz

• Operating supply voltage: 5 V ± 10%

• Package: DIP14

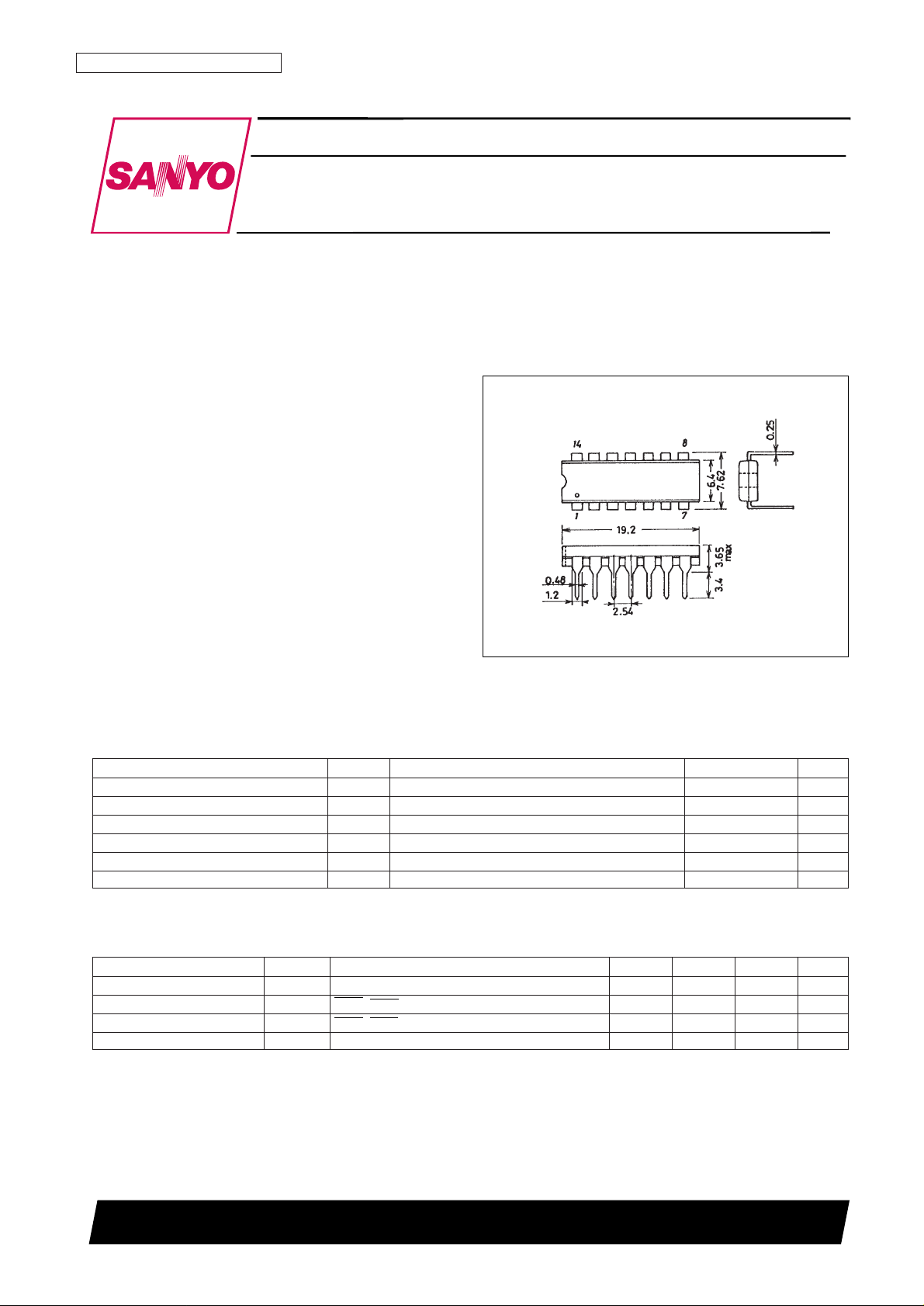

Package Dimensions

unit: mm

3003A-DIP14

Specifications

Absolute Maximum Ratings at Ta = 25 ± 2°C, VSS1 = VSS2 = 0 V, VDD= VDD1, VDD2

Allowable Operating Ranges at Ta = –10 to +70°C, VSS1 = VSS2 = 0 V, VDD= VDD1, VDD2

Parameter Symbol Conditions Ratings Unit

Maximum supply voltage V

DD

max –0.3 to +7.0 V

Maximum input voltage V

IN

max –0.3 to VDD+ 0.3 V

Maximum output voltage V

OUT

max –0.3 to VDD+ 0.3 V

Allowable power dissipation Pd max 300 mW

Operating temperature Topr –10 to +70 °C

Storage temperature Tstg –55 to +125 °C

Parameter Symbol Conditions min typ max Unit

Supply voltage V

DD

4.5 5.0 5.5 V

Input high level voltage V

IH

ENA1, ENA2 0.7 V

DD

V

Input low level voltage V

IL

ENA1, ENA2 0.3 V

DD

V

Oscillator range resistors Rrng R1, R2 6.8 13 kΩ

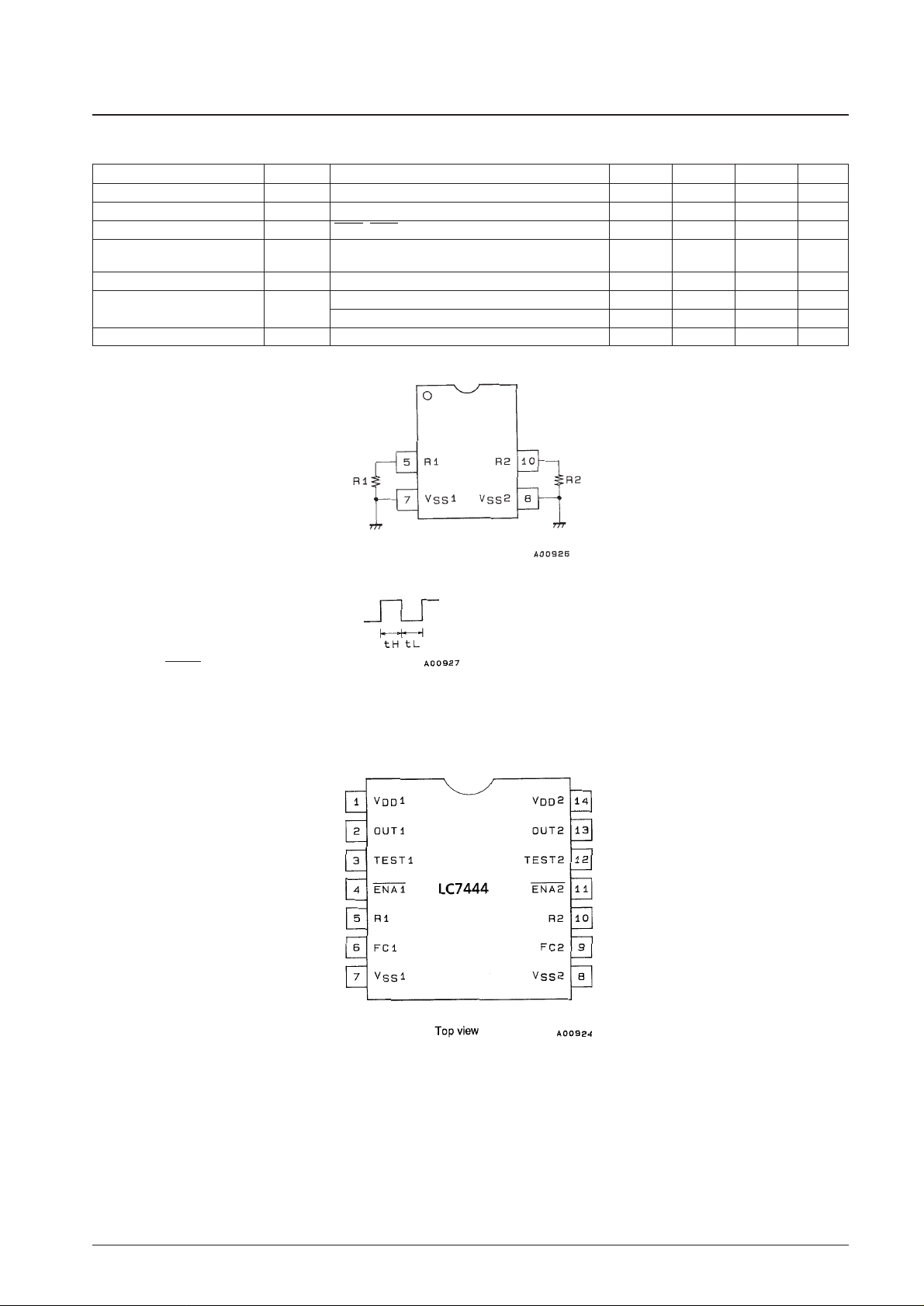

[LC7444]

SANYO: DIP14

Page 2

Electrical Characteristics at Ta = 25 ± 2°C, VDD= 5 V ± 10%, VSS1 = VSS2 = 0 V, VDD= VDD1, VDD2

Note: 1.

2. Duty: Du

Du =

× 100

Pin Assignment

tH

tH + tL

No. 4305-2/3

LC7444

Parameter Symbol Conditions min typ max Unit

Output high level voltage V

OH

OUT1, OUT2: IOH= –1 mA VDD– 0.4 V

Output low level voltage V

OL

OUT1, OUT2: IOL= 1 mA 0.4 V

Quiescent current I

DDS

ENA1, ENA2 = VDD, FC1, FC2 = V

SS

2 mA

Operating current drain I

DD

R1 = R2 = 7.5 kΩ, no output load,

7 mA

oscillator clock = 20 MHz

Input leakage current I

IH

, I

IL

–1 +1 µA

Oscillator clock frequency

fo

R1, R2 = 6.8 kΩ, FC1, FC2 = V

SS

to V

DD

*1

16 32 MHz

operating range

R1, R2 = 13 kΩ, FC1, FC2 = V

SS

to V

DD

*1

8 16 MHz

Duty Du *2 50 %

Page 3

PS No. 4305-3/3

LC7444

Pin Functions

Sample Application

Pin No. Symbol Function

1 V

DD

1 Power supply

2 OUT1 VCO1 clock output

3 TEST1 Test pin. Must be tied low in normal operation.

4 ENA1 VCO1 enable input

5 R1 VCO1 oscillator range resistor

6 FC1 VCO1 control voltage input

7 V

SS

1 Ground

Pin No. Symbol Function

8 V

SS

2 Ground

9 FC2 VCO2 control voltage input

10 R2 VCO2 oscillator range resistor

11 ENA2 VCO2 enable input

12 TEST2 Test pin

13 OUT2 VCO2 clock output

14 V

DD

2 Power supply

This catalog provides information as of May, 1995. Specifications and information herein are subject to change

without notice.

■ No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace

equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of

which may directly or indirectly cause injury, death or property loss.

■ Anyone purchasing any products described or contained herein for an above-mentioned use shall:

➀ Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and

distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all

damages, cost and expenses associated with such use:

➁ Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on

SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees

jointly or severally.

■ Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for

volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied

regarding its use or any infringements of intellectual property rights or other rights of third parties.

Loading...

Loading...