SANYO FW103 Datasheet

FW103

Ordering number : EN5305A

Ultrahigh-Speed Switching Applications

P-Channel Silicon MOSFET

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

O1397TS (KOTO) TA-0255 No.5305-1/3

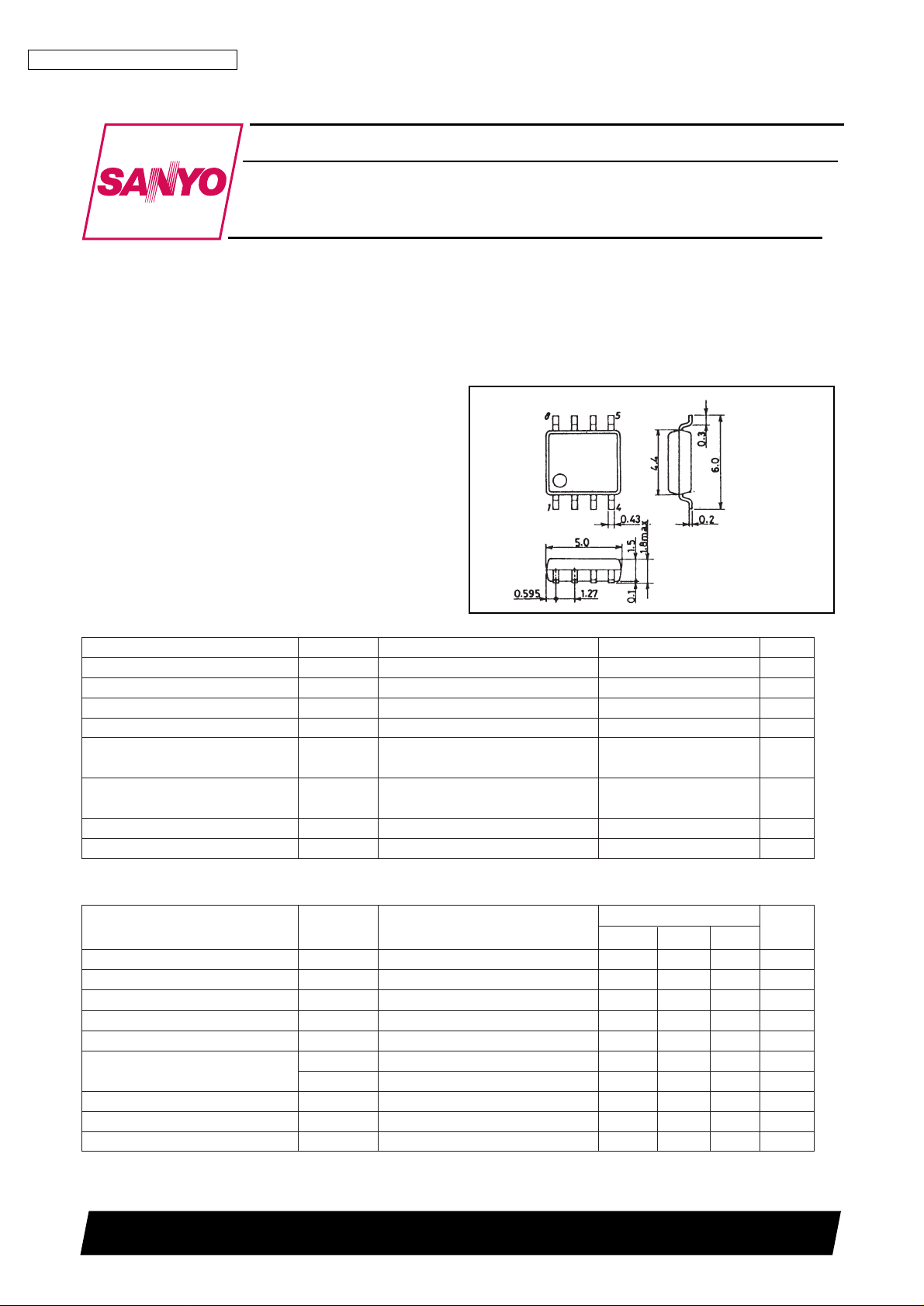

Package Dimensions

unit: mm

2129-SOP8

[FW103]

SANYO : SOP8

1 : Source1

2 : Gate1

3 : Source2

4 : Gate2

5 : Drain2

6 : Drain2

7 : Drain1

8 : Drain1

Specifications

Absolute Maximum Ratings

at Ta=25°C

Parameter Symbol Conditions Ratings Unit

Drain-to-Source Voltage V

DSS

–30 V

Gate-to-Source Voltage V

GSS

±20 V

Drain Current (DC) I

D

–3 A

Drain Current (pulse) I

DP

PW≤10µs, duty cycle≤1% –32 A

Allowable Power Dissipation P

D

Mounted on a ceramic board 1.7 W

(1000mm

2

×0.8mm) 1unit

Total Dissipation P

T

Mounted on a ceramic board 2.0 W

(1000mm

2

×0.8mm)

Channel Temperature Tch 150 °C

Storage temperature Tstg –55 to +150 °C

Electrical Characteristics at Ta=25°C

Parameter Symbol Conditions

Ratings

min typ max

Unit

D-S Breakdown Voltage V

(BR)DSSID

=–1mA, VGS=0 –30 V

Zero-Gate-Voltage Drain Current I

DSS

VDS=–30V, VGS=0 –100 µA

Gate-to-Source Leakage Current I

GSS

VGS=±16V, VDS=0 ±10 µA

Cutoff Voltage V

GS(off)

VDS=–10V, ID=–1mA –1.0 –2.5 V

Forward Transfer Admittance

yfs VDS=–10V, ID=–3A 2 4 S

Static Drain-to-Source R

DS(on)

ID=–3A, VGS=–10V 95 125 mΩ

ON-State Resistance R

DS(on)

ID=–3A, VGS=–4V 150 205 mΩ

Input Capacitance Ciss VDS=–10V, f=1MHz 550 pF

Output Capacitance Coss VDS=–10V, f=1MHz 370 pF

Reverse Transfer Capacitance Crss VDS=–10V, f=1MHz 70 pF

Continued on next page.

Features

• Low ON resistance

• Ultrahigh-speed switching.

• Composite type with two 4V-drive P-channel MOSFETs

facilitating high-density mounting.

• Matched pair capability.

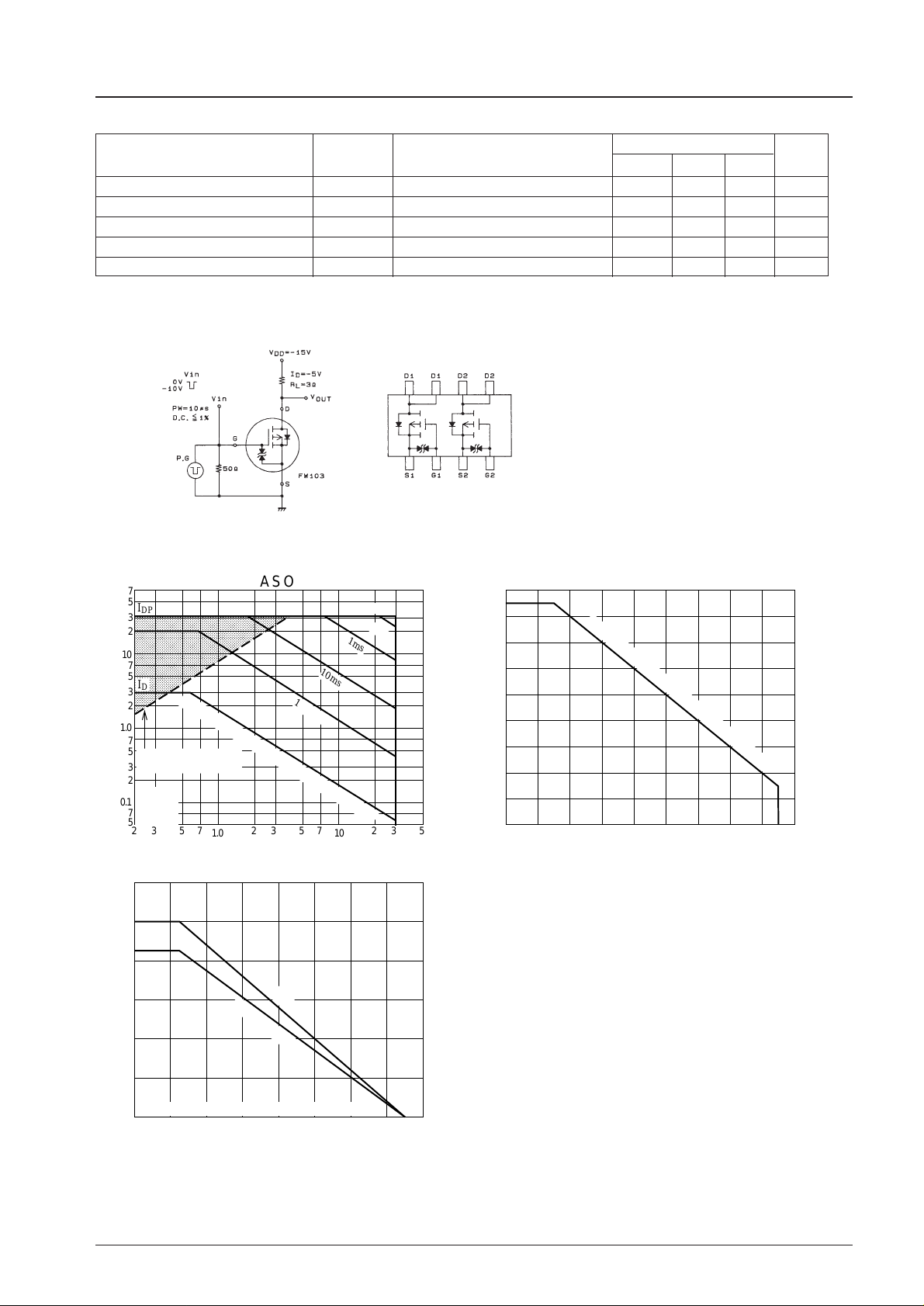

Continued from preceding page.

Parameter Symbol Conditions

Ratings

min typ max

Unit

Turn-ON Delay Time t

d(on)

See specified Test Circuit. 20 ns

Rise Time t

r

″ 110 ns

Turn-OFF Delay Time t

d(off)

″ 330 ns

Fall Time t

f

″ 170 ns

Diode Forward Voltage V

SD

IS=–3A, VGS=0 –1.0 –1.2 V

Switching Time Test Circuit Electrical Connection

(Top view)

FW103

No.5305-2/3

ASO

101.0

2 3 5 7 2 3 5 2 3 57

1.0

0.1

10

7

7

2

5

3

7

2

5

3

7

2

5

3

5

I

DP

I

D

1ms

10ms

100ms

Drain Current

, I

D

– A

1.0

1.2

1.4 1.6 1.8

0.80.6

0.40.20

0

0.6

0.8

1.0

0.4

0.2

1.2

1.4

1.6

1.8

1.7

PD(FET2) – PD(FET1)

Allowable Power Dissipation, P

D

(FET2)

– W

Drain-to-Source Voltage, V

DS

– V

Operation in this area

is limited by RDS(on).

10µs

100µs

Mounted on a ceramic board (1000mm2×0.8mm)

Total dissipation

Per unit dissipation

Mounted on a ceramic board (1000mm

2

×0.8mm)

Mounted on a ceramic board (1000mm

2

×0.8mm)

Allowable Power Dissipation, PD(FET1)

– W

80

100

120 140 160

60

40200

0

0.8

1.2

0.4

1.6

1.7

2.0

2.4

PD – Ta

Allowable Power Dissipation, P

D

– W

Ambient Temperature, Ta – °C

Ta=25°C

1pulse

1unit

Loading...

Loading...