Page 1

FILE NO.

Service Manual

CD

Micro Component System

DC-DA1000 (XE)

Contents

Specifications ...................................................................1

System connections .........................................................1

What to do if .....................................................................1

CD pick-up maintenance..................................................1

Laser beam safety precaution.......................................... 2

Tape adjustments ............................................................2

Tuner adjustments ...........................................................3

Exploded view

(Cabinet & Chassis) ...................................................... 4

Parts list

(Cabinet & Chassis) ...................................................... 5

Exploded view & Parts list (Tape mechanism).............. 8

(CD mechanism) ................. 8

SP: This service manual consists of "DC-DA1000U/XE" (Main unit : 129 647 02) and

"SX-DA1000/XE" (Speaker system : 165 064 02).

IC block diagram & description ........................................9

LCD display description ...................................................14

Wiring connection ............................................................15

Schematic diagram

(FRONT) .......................................................................16

(CD)...............................................................................18

(TUNER) .......................................................................22

(AMPLIFIER )................................................................ 26

Wiring diagram

(FRONT & CD).............................................................. 20

(TUNER) .......................................................................24

(AMPLIFIER)................................................................. 28

(POWER TRANSFORMER & LED) ..............................30

PRODUCT CODE No.

129 648 02

REFERENCE No.

SM5810385

Page 2

SPECIFICATIONS

Tuner

Reception frequency.............. FM : 87.5 ~ 108 MHz

AM : 522 ~ 1611kHz

CD player

Channels................................ 2-channel stereo

Sampling frequency ............... 44.1 kHz

Pick-up................................... Optical 3-beam

semiconductor laser

Laser output........................... 0.6mW(Continuous wave max.)

Wave length........................... 790 nm

Wow and Flutter..................... Below measurable limits

Cassette deck section

Track system ......................... 4-track, 2-channel stereo

Frequency response .............. 80 Hz to 15 kHz

Signal to noise ratio ............... 40 dB

Wow and Flutter..................... 0.15% (WRMS)

Fast forward / Rewind time .... Approx. 110 sec. (C-60)

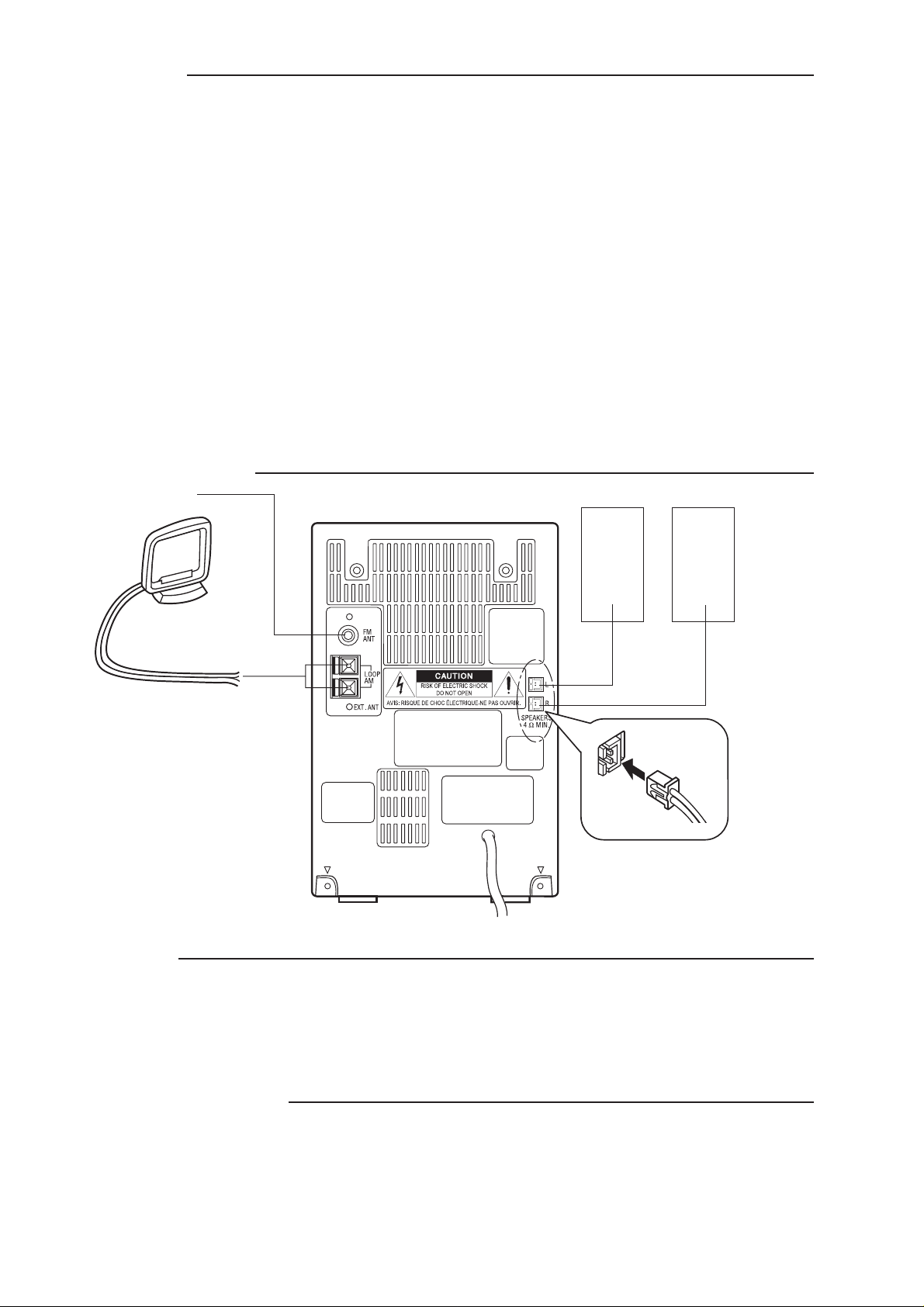

SYSTEM CONNECTIONS

FM aerial

General

Output power ......................... 4 W x 2

(at 4 ohms, 10% distortion)

Outputs .................................. SPEAKERS : 4 ohms

PHONES : 8 - 32 ohms

Power requirements............... AC 230V, 50Hz

Power consumption ............... 18 W

Dimensions (W x H x D) ........ Approx. 141 x 212 x 210 mm

Weight.................................... Approx. 2.2 kg

Speaker system

Type....................................... Full range bass reflex

Unit used................................ 8 cm cone type

Maximum

power-handling capacity ..... 6 Watts (peak)

Nominal impedance ............... 4 ohms

Dimensions (W x H x D) ........ Approx. 141 x 210 x 173mm

Weight.................................... Approx. 1.1 kg (per speaker)

Specifications subject to change without notice.

R ch speakerL ch speaker

AM loop aerial

To an AC outlet

WHAT TO DO IF

If the operation of the unit or display is not normal,

1. Disconnect the mains lead.

2. Wait for at least 30 seconds.

3. Connect the mains lead.

4. Operate the unit.

CD PICK-UP MAINTENANCE

About pick-up (Optical lens) Cleaning

Clean a lens with swab of the cotton which moistened it with alcohol, cleaning paper or cleaning disc appointed.

Specified cleaning disc : LC-1 (Part code : 645 026 1961 ..... manufactured by SANYO.)

Show a clean procedure in the following in reference by swab of cotton.

1. Cotton swab is wrapped with Cleaning paper.

2. Add the isopropyl alcohol.

3. Gently move the tip of cotton swab just like a draw a whirlpool from inside to outside on the surface of lens.

- 1 -

Page 3

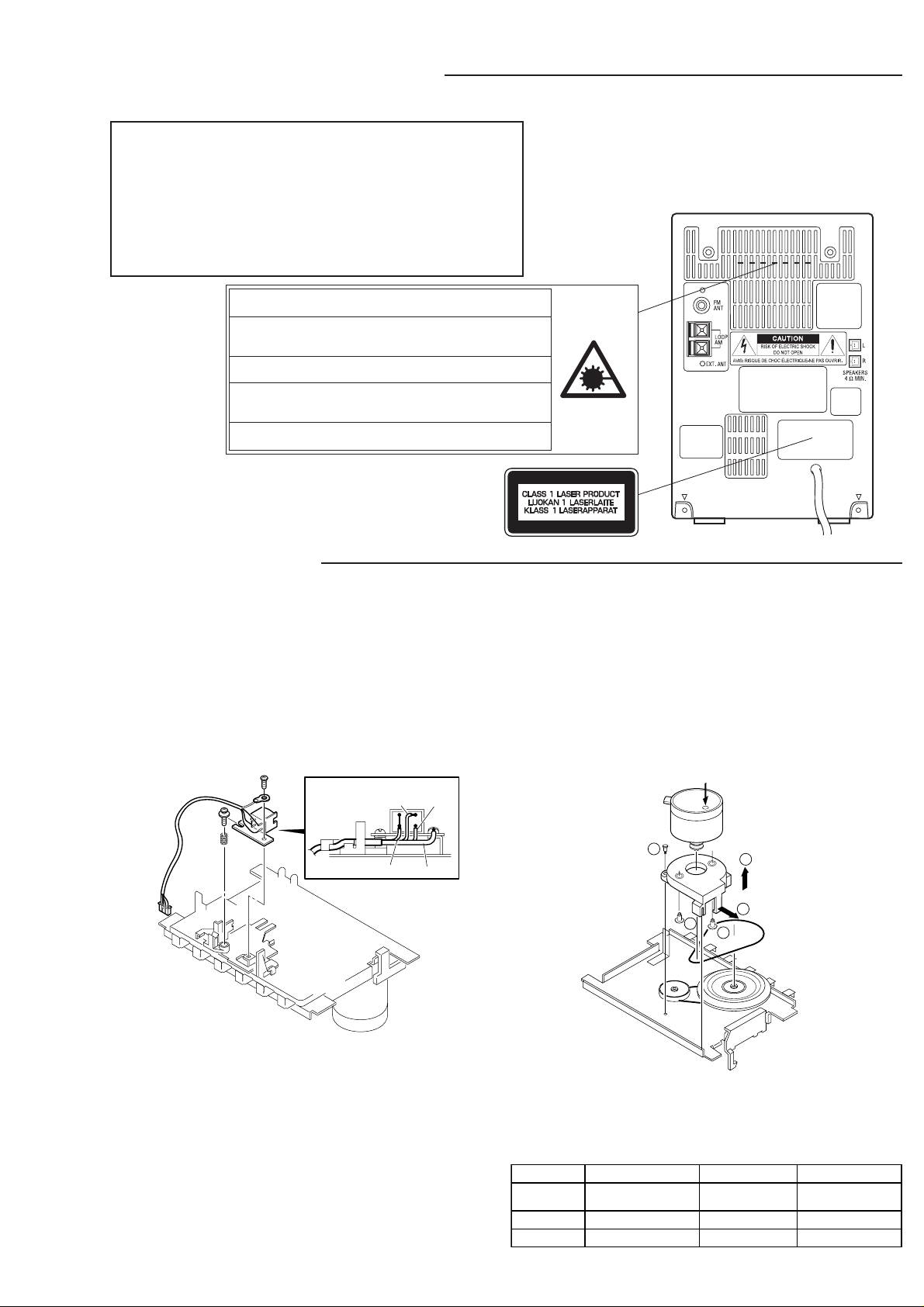

LASER BEAM SAFETY PRECAUTION

• Pick-up that emits a laser beam is used in this CD player section.

CAUTION :

THIS PRODUCT CONTAINS A LOW POWER LASER DEVICE,

TO ENSURE CONTINUED SAFETY DO NOT REMOVE ANY

COVERS OR ATTEMPT TO GAIN ACCESS TO THE INSIDE

OF THE PRODUCT.

REFER ALL SERVICING TO QUALIFIED PERSONNEL.

LASER OUTPUT ..............0.6 mW Max. (CW)

WAVELENGTH .................. 790 nm

CAUTION – INVISIBLE LASER RADIATION WHEN OPEN AND

INTERLOCKS DEFEATED. AVOID EXPOSURE TO BEAM.

ADVARSEL – USYNLIG LASER STRÅLING VED ÅBNING, NÅR

SIKKERHEDSAFBRYDERE ER UDE AF FUNKTION, UNDGÅ UDS ÆTTELSE

FOR STRÅLING.

VARNING – OSYNLIG LASER STRÅLNING NÄR DENNA DEL ÄR ÖPPNAD

OCH SPÄRR ÄR URKOPPLAD. STRÅLEN ÄR FARLIG.

VORSICHT – UNSICHTBARE LASERSTRAHLUNG TRITT AUS, WENN

DECKEL GEÖFFNET UND WENN SICHERHEITSVERRIEGELUNG

ÜBERBRÜCKT IST. NICHT, DEM STRAHL AUSSETZEN.

VARO – AVATTAESSA JA SUOJALUKITUS OHITETTAESSA OLET ALTTIINA

NÄKYMÄTTÖMÄLLE LASERSÄTEILYLLE. ÄLÄ KATSO SÄ

TEESEEN.

TAPE ADJUSTMENTS

a. Replacing the head

1. After replacement, demagnetize the heads by using

a degausser.

2. Be sure to clean the heads before attempting to make

any adjustments.

3. Be sure both channels (1 and 2) are the same level.

(Using a dual-channels oscilloscope).

4. All wiring should be returned to the original position

after work is completed.

R / P HEAD

RED

WHITE

YELLOW EARTH

c. Adjusting motor speed

1. Insert the test tape (MTT-111 or etc. 3,000 Hz).

2. Press the PLAY button.

3. Use a flat-tip screwdriver to turn the SVR to adjust so

that the frequency counter becomes 3,000 Hz.

4. Press the STOP button.

d. Replacing the moto

MOTOR SPEED

ADJUSTMENT

1

4

3

2

4

b. Adjusting head azimuth

1. Load a test tape (VTT-738, etc. :10kHz) for

azimuth adjustment.

2. Press the PLAY button.

3. Use a cross-tip screwdriver to turn the screw for

normal azimuth adjustment so that the left and right

outputs are maximized at the same phase during

normal playback.

4. Press the STOP button.

e. Checking the mechanism torques

• Clean the head, capstan and pinch roller before making

any measurement.

Measurement Take-up torque Back tension Tape tension

Cassette for PLAY : TW-2111A PLAY : TW-2111A Drive-power cassette

measurement F.FWD/REW : TW-2231 TW-2412

PLAY 30 ~ 70gr.cm 1.0 ~ 6.0gr.cm 80 gr or more

F.FWD/REW 55 gr or more - -

- 2 -

Page 4

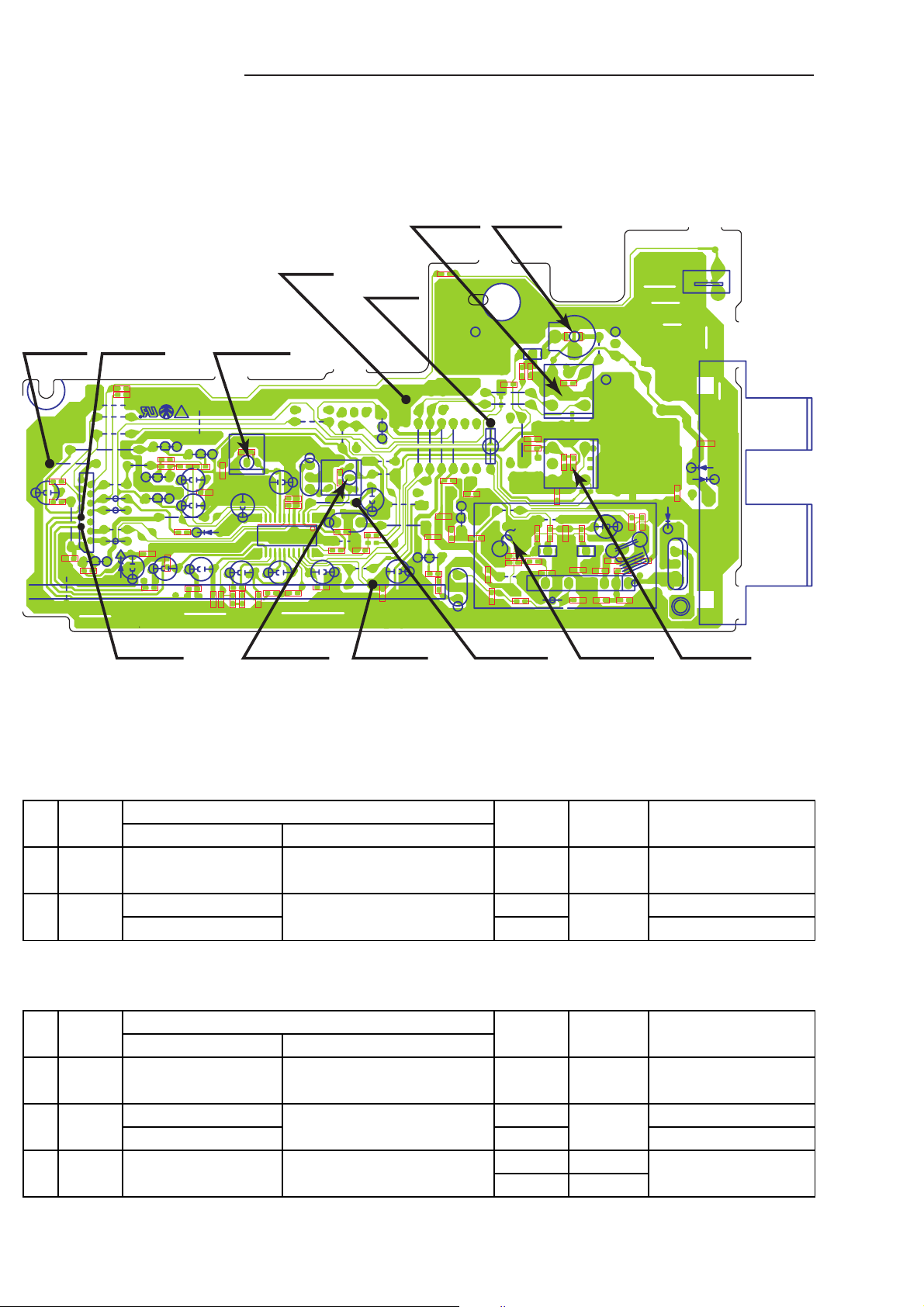

TUNER ADJUSTMENTS

C2001

C2014

C2022

C2011

C2802

R2900

• Use a plastic screw driver for adjustments.

• MODE : ST (Stereo)

• Speaker impedance : 4 ohms

• TUNING

FM : 87.5 - 108MHz

AM : 522 - 1611kHz

L2204

CT211

TP15

J2202

C2218

R2201

R2206

FR_GND

LID_SW

AM OSC

IF

VT

J2212

MONO

MUTE

BAND1

TU_L

BAND2

C2025

TU_R

SD

AMPGND

ST

+B 9V

J2307

J2305

CN202

Q2003

R2210

TP13

C2029

1AD4B10D1712D

C2027

T002 94V-0

J2300

J2301

J2303

J2104

L2005

L2007

J2107

L2006

E

R2129

C2312

D2104

E

Q2111

Q2102

C2311

R2801

Q2110

R2127

C2801

TP14

E

C2207R2128

E

J2210

R2205

C2802

C2802

C2701

R2701

J2304

Q2101

R2104

R2106

C2106

D2101

C2107

T2002

T2002

E

R2105

C2110

C2113

C2111

R2303

R2301

C2114

C2702

C2115

TP12

J2302

BAND1

XF215

C2108

C2103

C2102

IC211

C2119

C2112

C2118

R2302

C2117

T2001

T2001

J2209

J2108

C2120

J2101

R2126

XF212

C2101

R2101

TP11

E

J2102

J2103

C2104

C2209

R2107

J2109

J2306

J2211

C2121

C2122

Q2201

J2204

R2009

Q2001

E

R2007

R2901

J2205

R2010

J2206

C2019

R2008

J2207

R2011

XF211

C2010

E

Q2002

C2003

VT

J2208

TP24TP25

R2117

J2200

J2201

L2002

J2110

C2020

R2006

J2105

D2003

C2017

C2008

C2012

D2102

C2126

R2113

R2119

C2131

J2203

R2003

CT211

R2900

R2900

C2141

J2100

L2204

MW ANT

L2205

C2142

R2131

C2002

C2005

C2009

C2022

C2022

L2001

C2001

C2001

C2024

LW OSC

R2005

C2013

C2014

C2014

J2106

R2014

C2015

L2003

R2004

MW OSC

C2140

R2002

C2021

D2002

R2001

IC201

C2011

C2011

U

L2002 L2205

C2026

D2006

SH201

CN203

S2001

C2902

D2004

D2005

XF210

CN201

1. FM

Step

1

2

2. AM

Step

1

2

3

Adjusting

Circuit

IF(0V)

Adjustment

Cover

Voltage

Adjusting

Circuit

IF

Adjustment

Cover

Voltage

Tracking

Input Output

FM Antenna SG=66dBuV

--- Connect Digital DC voltmeter to 87.5MHz 1.00±0.05V

--- TP11(H), TP12(E). 108.0MHz 5.50±0.50V Check Only

Input Output

--- Connect Digital DC voltmeter to 522kHz 1.00±0.05V

--- TP11(H )and TP12(E). 1611kHz 7.10±0.50V Check Only

Loop Ant

Antenna : 75Ω unbalanced direct, Modulation : 1 kHz

Dev. : ±22.5kHz(MONO), ±22.5kHz(MAIN), ±6.75kHz(PILOT)

RF Level : dBuV EMF

Output Level : about 30mV at TP13, TP14, TP15

Connection

Alignment voltage IC211 Alignment voltage IC211

3-22pin(TP24,25) is 0.0±0.05V 3-22pin is 0.0±0.05V

SG

Frequency

98.0MHz

Adjustment

T2002

L2002

Remark

Anntena : IRE Loop(SG), Moduration : 1kHz 30%

RF Level : dBuV EMF

Output Level : about 30mV at TP13, TP14, TP15

Connection

Connect Sweep generator to test

point TP13(L), TP14(R) and TP15(E).

Connect to VTVM 603kHz L2204

point TP13(L), TP14(R) and TP15(E).

SG

Frequency

450kHz

at 999kHz

Adjustment

T2001

L2205

1404kHz CT211

Remark

MaximumLoop Ant

Maximum

- 3 -

Page 5

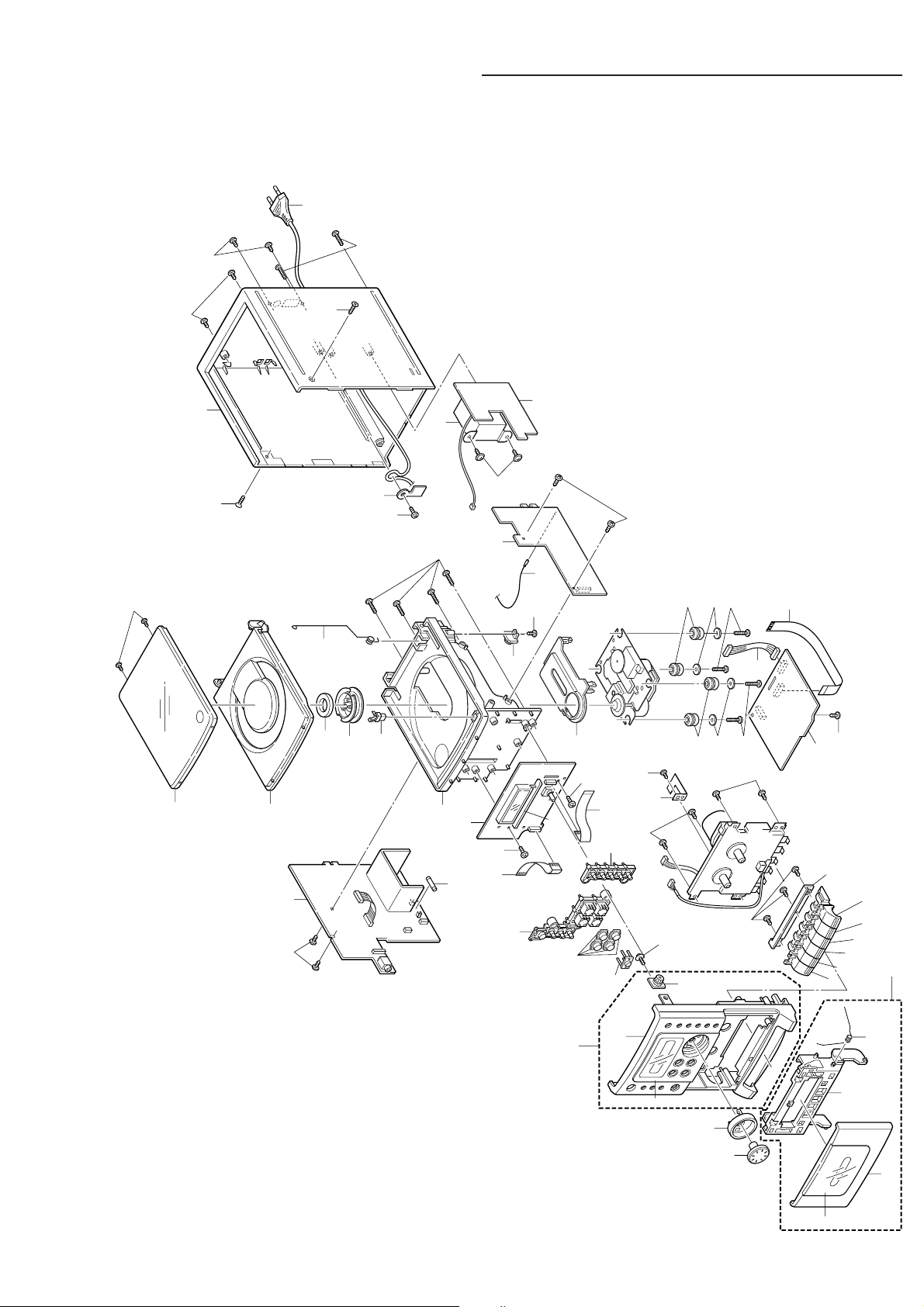

EXPLODED VIEW (CABINET & CHASSIS)

1

3

2

6

7

10

9

8

Y01

Y02

Y03

Y03

Y04

Y05

Y05

Y07

Y08

Y07

Y06

Y08

Y09

Y10

Y11

Y14

Y15

Y16

Y16

Y17

Y18

Y19

Y12

Y13

11

15

14

13

4

5

12

16

17

18

19

24

25

73

27

28

29

32

33

30

31

34

35

26

24

20

21

51

52

55

53

54

56

71

72

74

75

57

76

58

23

22

- 4 -

Page 6

PARTS LIST

PRODUCT SAFETY NOTICE

EACH PRECAUTION IN THIS MANUAL SHOULD BE FOLLOWED DURING SERVICING. COMPONENTS IDENTIFIED WITH THE

!!

IEC SYMBOL

PERFORMANCE CAN BE OF SPECIAL SIGNIFICANCE. WHEN REPLACING A COMPONENT IDENTIFIED BY

REPLACEMENT PARTS DESIGNATED, OR PARTS WITH THE SAME RATINGS OF RESISTANCE, WATTAGE OR VOLTAGE THAT

ARE DESIGNATED IN THE PARTS LIST IN THIS MANUAL. LEAKAGE-CURRENT OR RESISTANCE MEASUREMENTS MUST BE

MADE TO DETERMINE THAT EXPOSED PARTS ARE ACCEPTABLY INSULATED FROM THE SUPPLY CIRCUIT BEFORE

RETURNING THE PRODUCT TO THE CUSTOMER.

CAUTION : Regular type resistors and capacitors are not listed. To know those values, refer to the schematic diagram.

N.S.P : Not available as service parts.

!

IN THE PARTS LIST AND THE SCHEMATIC DIAGRAM DESIGNATED COMPONENTS IN WHICH SAFETY AND

!!

!

, USE ONLY THE

Regular type resistors are less than 1/4 W carbon type and 0 ohm chip resistors.

Regular type capacitors are less than 50 V and less than 1000 µF type of Ceramic type and Electrical type.

PACKING & ACCESSORIES

REF.NO. PART NO. DESCRIPTION

614 326 6396 CARTON CASE

614 325 2818 CUSHION,REAR

614 325 2825 CUSHION,FRONT

614 326 6433 INSTRUCTION MANUAL

614 327 0607 INSTRUCTION SHEET,GREECE

645 005 1227 ASSY,ANTENA,LOOP

or 645 046 8322 ASSY,ANTENA,LOOP

645 057 4559 REMOCON,RB-DA1000

614 325 5741 LID,BATTERY,SERVICE

614 326 5955 ASSY,BOX,SPEAKER(L,R)

CABINET & CHASSIS

REF.NO. PART NO. DESCRIPTION

1 614 325 2665 COVER,DECK

2 614 325 2672 DEC,WINDOW,DECK

3 614 325 2740 LID,CASSETTE

4 614 325 2788 SPRING,DOOR DECK

5 614 325 2603 ASSY,DOOR,DECK

6 614 325 2733 KNOB,VOLUME

7 614 325 2658 CAP,DECORATION

8 614 326 6259 DEC,WINDOW LCD

9 614 326 6334 PANEL,FRONT

10 614 326 6129 ASSY,PANEL,FRONT

11 614 309 7969 ASSY,GEAR,CASSETTE

12 614 326 1971 KNOB,DEC MECHA,REC

13 614 326 2589 KNOB,DEC MECHA,PLAY

14 614 326 2596 KNOB,DEC MECHA,REW

15 614 326 2602 KNOB,DEC MECHA,FFWD

16 614 326 2619 KNOB,DEC MECHA,STOP/EJECT

17 614 326 2626 KNOB,DEC MECHA,PAUSE

18 614 326 2633 MOUNTING,DEC KNOB

19 614 308 0534 SPRING,PLATE,REC

20 614 325 2719 DEC,WINDOW,BUTTON,1 KEY

21 614 325 2634 BUTTON,LEFT,8 KEYS

22 614 325 2702 DEC,WINDOW SENSOR

23 614 325 2627 BUTTON,RIGHT,5 KEYS

24 614 310 3899 SPACER,MECHA,CD+DA11

25 614 307 2072 COVER,PICK-UP

26 614 322 2132 ASSY,GEAR,LID,CD

27 614 325 2764 MOUNTING,CD

28 614 303 0263 LATCH,PUSH,CD DOOR LOCKING

29 614 307 8821 PULLEY

30 614 303 0256 LATCH,MAGNET

31 614 325 2795 SPRING,DOOR CD

32 614 325 2757 LID,CD

33 614 326 8581 DEC,WINDOW,CD

34 614 308 4914 STOPPER

35 614 326 8215 ASSY,CABINET,REAR

REF.NO. PART NO. DESCRIPTION

SPRING DECK REC

Y05 411 021 3503 SCR S-TPG BIN 3X10,

FRONT PWB+MOUNT

Y06 411 021 3503 SCR S-TPG BIN 3X10,

MTG CD+CD PCB

Y07 411 021 1806 SCR S-TPG BIN 2.6X10,

MTGCD+MECHACD

Y08 411 092 0906 WASHER Z 2.6X10X0.5,

MECHA CD+MOUNTING

Y09 411 021 3503 SCR S-TPG BIN 3X10,

MTG CD+TUNER PCB

Y10 411 021 3503 SCR S-TPG BIN 3X10,

MTG CD+ASSY,GEAR

Y11 411 021 4906 SCR S-TPG BIN 3X20,

PANEL+MOUNTING

Y12 411 021 3503 SCR S-TPG BIN 3X10,

MTG CD+AMP PCB

Y13 411 184 0906 SCR S-TPG BIN 2.3X10,

WIN CD+LID CD

Y14 411 020 9100 SCR S-TPG BRZ+FLG 3X12,

REAR+P-TRANS

Y15 411 021 3503 SCR S-TPG BIN 3X10,

REAR+STOPPER

Y16 411 098 7800 SCR S-TPG FLT 3X12,

PANEL+REAR+MOUNTING

Y17 411 021 4500 SCR S-TPG BIN 3X16,PANEL+REAR

Y18 411 021 3503 SCR S-TPG BIN 3X10,

MTG CD+REAR

Y19 411 021 3404 SCR S-TPG BIN 3X10,

C-REAR(ANT TERMINAL)

ELECTRICAL PARTS

REF.NO. PART NO. DESCRIPTION

51 614 326 2770 FLEXIBLE FLAT CABLE,

FRONT TO AMP

or 614 327 0812 FLEXIBLE FLAT CABLE,

FRONT TO AMP

52 614 326 2787 FLEXIBLE FLAT CABLE,

FRONT TO TUNER

or 614 327 0829 FLEXIBLE FLAT CABLE,

FRONT TO TUNER

53 614 314 4779 ASSY,WIRE

or 614 309 8454 ASSY,WIRE

54 614 326 2794 FLEXIBLE FLAT CABLE,CD PICK UP

or 614 327 0836 FLEXIBLE FLAT CABLE,CD PICK UP

55 423 016 7908 FUSE 250V 2.5A

56 614 274 2013 CORD,ID CONNECTOR

57 645 051 8775 TRANS,POWER

58 645 016 9939 CORD,POWER-1.74MK

FIXING PARTS

REF.NO. PART NO. DESCRIPTION

Y01 411 020 8905 SCR S-TPG BRZ+FLG 3X10,GEAR

Y02 411 021 3503 SCR S-TPG BIN 3X10,

F-PANEL+MTG DECK KNOB

Y03 411 021 3503 SCR S-TPG BIN 3X10,

PANEL+DECK MECHA

Y04 411 126 1404 SCR S-TPG BIN 2X4,

FRONT P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

71 614 326 6815 ASSY,PWB,FRONT(Only Initial)

BR601 614 325 3730 HOLDER,LCD

C6200 403 373 7001 NP-ELECT 1U M 50V

or 403 259 0508 NP-ELECT 1U M 50V

CN601 645 059 0474 SOCKET,FPC 14P,FRONT-AMP

CN602 614 016 8464 PLUG,FRONT-LED

- 5 -

Page 7

PARTS LIST

REF.NO. PART NO. DESCRIPTION

CN603 645 059 0481 SOCKET,FPC 15P,FRONT-TU

D6901 407 012 4406 DIODE 1SS133

D6902 407 012 4406 DIODE 1SS133

IC601 409 546 0701 IC LC72338-9B55,MICON

L6900 645 001 4550 INDUCTOR,10U K

L6901 645 002 1459 INDUCTOR,22U K

LCD60 645 057 4542 LCD

LS601 614 309 4180 DEC,SHEET,LCD,DEC_LCD_SHEET

Q6200 405 017 9709 TR 2SC3330-U

or 405 017 9600 TR 2SC3330-T

or 405 011 8609 TR 2SC1740S-S

or 405 011 8500 TR 2SC1740S-R

or 405 143 8706 TR KTC3199-GR

Q6201 405 017 9709 TR 2SC3330-U

or 405 017 9600 TR 2SC3330-T

or 405 011 8609 TR 2SC1740S-S

or 405 011 8500 TR 2SC1740S-R

or 405 143 8706 TR KTC3199-GR

S6001 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6002 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

or 645 006 5958 SWITCH,PUSH 1P-1T

or 645 048 3820 SWITCH,PUSH

S6003 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6004 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6005 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6006 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 220 5471 SWITCH,TACT

or 614 240 1002 SWITCH,TACT

S6007 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6008 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6009 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6010 614 220 5471 SWITCH,TACT

or 614 240 1002 SWITCH,TACT

or 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

S6011 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6012 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6013 645 048 3820 SWITCH,PUSH

or 645 006 5958 SWITCH,PUSH 1P-1T

or 614 240 1002 SWITCH,TACT

or 614 220 5471 SWITCH,TACT

S6500 645 057 4535 SWITCH,ROTARY(ENCODER)

SE601 407 220 6803 PHOTO DIODE SPS-444-1-G1

X6001 645 052 6206 OSC,CRYSTAL 4.5MHZ

LED P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

72 614 325 4751 ASSY,PWB,LED(Only Initial)

D6951 408 049 3707 LED SLP-3G118C51HAB-T1,LED

D6952 408 049 3707 LED SLP-3G118C51HAB-T1,LED

D6953 408 049 3707 LED SLP-3G118C51HAB-T1,LED

D6954 408 049 3707 LED SLP-3G118C51HAB-T1,LED

D6955 408 049 3707 LED SLP-3G118C51HAB-T1,LED

CD P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

73 614 325 4720 ASSY,PWB,CD(Only Initial)

CN111 645 059 0498 SOCKET,FPC 16P

CN113 645 005 8127 PLUG,6P

or 614 310 2472 PLUG,6P

CN122 614 310 2496 PLUG,8P

or 645 005 8134 PLUG,8P

D1401 407 012 4406 DIODE 1SS133

D1402 407 012 4406 DIODE 1SS133

D1403 407 012 4406 DIODE 1SS133

D1404 407 099 5204 ZENER DIODE MTZJ5.1B

D1410 407 098 3300 DIODE RL153-BF-S2

IC101 409 503 5701 IC LA9242M-MPB

IC102 409 539 9704 IC LC78629E

IC103 409 486 8706 IC MM1469XH

L1451 645 001 4550 INDUCTOR,10U K

PR140 645 014 2499 PROTECTOR,0.4A 125V

Q1301 405 008 6809 TR 2SB808-F-SPA

or 405 008 7202 TR 2SB810-E

or 405 008 7301 TR 2SB810-F

Q1401 405 141 3604 TR KTA1273-Y

or 405 009 5207 TR 2SB927-S

or 405 009 5306 TR 2SB927-T

X1451 614 231 2667 RESONATOR

or 645 057 1145 OSC,CERAMIC 16.93MHZ

TUNER P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

74 614 326 6822 ASSY,PWB,TUNER(Only Initial)

CN201 645 038 7715 TERMINAL

or 645 025 4703 TERMINAL,ANTENNA

CN202 645 059 0481 SOCKET,FPC 15P

CN203 614 221 8273 TERMINAL

CT211 645 032 5663 TRIMMER,7PF

D2002 407 157 8109 VARACTOR DI SVC211-B

D2003 407 157 8109 VARACTOR DI SVC211-B

D2004 407 012 4406 DIODE 1SS133

D2005 407 012 4406 DIODE 1SS133

D2006 407 012 4406 DIODE 1SS133

D2101 407 012 4406 DIODE 1SS133

D2102 407 105 1602 VARACTOR DI SVC342M-V

or 407 105 1305 VARACTOR DI SVC342L-V

D2104 407 099 5303 ZENER DIODE MTZJ5.6B

IC201 409 016 0200 IC LA1186N-AUDIO

IC211 409 474 3201 IC LA1844ML

L2001 645 040 2753 INDUCTOR,AIR —

L2002 645 040 2746 COIL,AIR —

L2003 645 002 1534 INDUCTOR,8.2U K

L2005 645 002 1459 INDUCTOR,22U K

L2006 645 002 1459 INDUCTOR,22U K

L2007 645 002 1459 INDUCTOR,22U K

L2204 645 037 2377 TRANS,ANT,796KHZ

L2205 645 040 2739 TRANS,OSC,796KHZ

Q2001 405 151 4301 TR KTC3195-Y

or 405 151 4806 TR KTC3195-O

Q2002 405 151 4301 TR KTC3195-Y

or 405 151 4806 TR KTC3195-O

Q2003 405 017 9600 TR 2SC3330-T

or 405 011 8609 TR 2SC1740S-S

or 405 011 8500 TR 2SC1740S-R

or 405 143 8706 TR KTC3199-GR

or 405 017 9709 TR 2SC3330-U

- 6 -

Page 8

PARTS LIST

REF.NO. PART NO. DESCRIPTION REF.NO. PART NO. DESCRIPTION

Q2101 405 000 0904 TR DTA114YS

or 405 151 5209 TR KRA107M

Q2102 405 143 0007 TR KRC107M

or 405 000 3806 TR DTC114YS

Q2110 405 143 0007 TR KRC107M

or 405 000 3806 TR DTC114YS

Q2111 405 151 4301 TR KTC3195-Y

or 405 151 4806 TR KTC3195-O

Q2201 405 151 5209 TR KRA107M

or 405 000 0904 TR DTA114YS

S2001 645 023 5795 SWITCH,LEVER

SH201 614 256 3052 SHIELD

T2001 645 043 0213 FILTER,450KHZ

T2002 645 040 9981 TRANS,IF 10.7MHZ

or 645 039 9923 TRANS,IF 10.7MHZ

XF210 645 059 0047 FILTER,BP

XF211 645 054 1223 CERAMIC FILTER 10.70MHZ

or 645 010 7665 CERAMIC FILTER 10.70MHZ

or 614 240 2917 FILTER,CERAM

XF212 645 010 7665 CERAMIC FILTER 10.70MHZ

or 614 240 2917 FILTER,CERAM

or 645 054 1223 CERAMIC FILTER 10.70MHZ

XF215 645 059 0054 CERAMIC FILTER 450KHZ

AMPLIFIER P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

75 614 325 4706 ASSY,PWB,AMP(Only Initial)

C4714 403 058 4608 POLYESTER 0.15U J 50V

C4814 403 058 4608 POLYESTER 0.15U J 50V

C4913 403 329 5907 ELECT 3300U M 25V

or 403 350 9301 ELECT 3300U M 25V

C4918 403 377 6307 POLYESTER 1000P J 50V

or 403 056 7502 POLYESTER 1000P J 50V

CN401 645 006 1875 PLUG,2P,SPEAKER

CN402 645 006 1875 PLUG,2P,SPEAKER

CN405 614 310 2755 PLUG,4P

or 645 004 2904 PLUG,4P

CN406 614 310 2458 PLUG,4P

or 645 005 8110 PLUG,4P

CN421 645 011 6384 JACK,PHONE D3.6,HEADPHONE

or 645 055 1017 JACK,PHONE D3.6,HEADPHONE

CN441 614 310 2731 PLUG,2P,POWER

or 645 004 2881 PLUG,2P,POWER

CN490 645 012 2736 SOCKET,DIP 8P

CN491 645 059 0474 SOCKET,FPC 14P

CN492 614 309 8812 ASSY,WIRE

or 614 314 4809 ASSY,WIRE

D4102 407 012 4406 DIODE 1SS133

D4951 407 099 6003 ZENER DIODE MTZJ9.1B

D4953 407 012 4406 DIODE 1SS133

D4961 407 012 4406 DIODE 1SS133

D4962 407 012 4406 DIODE 1SS133

D4963 407 012 4406 DIODE 1SS133

D4980 407 098 3300 DIODE RL153-BF-S2

D4981 407 098 3300 DIODE RL153-BF-S2

D4982 407 098 3300 DIODE RL153-BF-S2

D4983 407 098 3300 DIODE RL153-BF-S2

D4993 407 012 4406 DIODE 1SS133

FCL41 645 006 4760 HOLDER,FUSE

or 645 031 7903 HOLDER,FUSE

FCL42 645 006 4760 HOLDER,FUSE

or 645 031 7903 HOLDER,FUSE

HS401 614 307 9866 HEAT SINK

IC410 409 384 3506 IC BA3314F

IC411 409 390 1107 IC LC75392

IC412 409 295 7402 IC TA8229K

IC446 409 039 9204 IC NJM78L05A

L4780 645 002 1459 INDUCTOR,22U K

L4781 645 002 1459 INDUCTOR,22U K

L4881 645 002 1459 INDUCTOR,22U K

L4902 645 031 5893 TRANS,OSC,85KHZ,O.S.C

LG401 645 006 4432 FIXER

PR495 645 014 2529 PROTECTOR,1.25A 125V

PR496 645 014 2536 PROTECTOR,1.5A 125V

Q4103 405 000 0508 TR DTA114ES

or 405 110 5400 TR KRA102M-A

Q4104 405 000 3103 TR DTC114ES

or 405 109 9204 TR KRC102M-A

Q4106 405 000 3103 TR DTC114ES

or 405 109 9204 TR KRC102M-A

Q4108 405 000 3806 TR DTC114YS

or 405 143 0007 TR KRC107M

Q4109 405 000 3806 TR DTC114YS

or 405 143 0007 TR KRC107M

Q4730 405 006 1806 TR 2SA933S-R

or 405 006 1905 TR 2SA933S-S

or 405 004 5103 TR 2SA608-G-SPA

or 405 004 4601 TR 2SA608-F-SPA

or 405 143 6504 TR KTA1267-GR

Q4740 405 000 3103 TR DTC114ES

or 405 109 9204 TR KRC102M-A

Q4751 405 151 4400 TR KTD1303

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

or 405 033 6805 TR 2SD1468S-S

Q4830 405 143 6504 TR KTA1267-GR

or 405 004 4601 TR 2SA608-F-SPA

or 405 004 5103 TR 2SA608-G-SPA

or 405 006 1806 TR 2SA933S-R

or 405 006 1905 TR 2SA933S-S

Q4840 405 000 3103 TR DTC114ES

or 405 109 9204 TR KRC102M-A

Q4851 405 033 6805 TR 2SD1468S-S

or 405 151 4400 TR KTD1303

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

Q4902 405 011 8500 TR 2SC1740S-R

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8609 TR 2SC1740S-S

or 405 143 8706 TR KTC3199-GR

Q4903 405 143 8706 TR KTC3199-GR

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

Q4904 405 143 8706 TR KTC3199-GR

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

Q4951 405 138 6403 TR KTD2058Y

or 405 095 1602 TR 2SD2061-E

or 405 095 1701 TR 2SD2061-F

Q4992 405 141 3703 TR KTA1271-Y

or 405 008 2405 TR 2SB698-F

or 405 008 2504 TR 2SB698-G

Q4994 405 143 0007 TR KRC107M

or 405 000 3806 TR DTC114YS

Q4995 405 141 3703 TR KTA1271-Y

or 405 008 2405 TR 2SB698-F

or 405 008 2504 TR 2SB698-G

R4752 402 071 1304 FUSIBLE RES 2.2 JA 1/4W

R4852 402 071 1304 FUSIBLE RES 2.2 JA 1/4W

R4941 402 081 0205 FUSIBLE RES 27 JA 1/4W

S4950 645 038 7586 SWITCH,PUSH,R/PSW

SA402 411 021 6405 SCR S-TPG BIN 3X8

- 7 -

Page 9

PARTS LIST

POWER TRANSFORMER P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

76 614 325 4744 ASSY,PWB,PT(Only Initial)

CN450 614 020 1215 SOCKET,2P

CN451 614 017 8203 TERMINAL BOARD

CN452 614 017 8203 TERMINAL BOARD

CN453 614 314 4762 ASSY,WIRE

or 614 309 8447 ASSY,WIRE

L4591 645 041 3087 INDUCTOR,180U

or 645 038 6053 INDUCTOR,181U

EXPLODED VIEW & PARTS LIST(TAPE MECHANISM)

TM01

TM02

TM03

*

TAPE MECHANISM

REF.NO. PART NO. DESCRIPTION

TM01 645 033 8625 E HEAD 6PA

TM02 645 041 3025 R.P HEAD

TM03 645 009 1612 PINCH ROLLER ARM ASSY

TM04 645 009 1766 RF BELT

TM05 645 033 3415 MAIN BELT

TM06 614 312 0629 ASSY,MOTOR,FOR SERVICE

614 309 7976 ASSY,MECHA,TM-DA70TN-SH

* N.S.P : Not supplied as service parts.

TM04

TM05

*

*

*

*

TM06

EXPLODED VIEW & PARTS LIST(CD MECHANISM)

PM09

PM09

PM06

*

PM08

PM08

PM04

PM05

CD MECHANISM

REF.NO. PART NO. DESCRIPTION

PM01 620 021 8436 PLUG 6P

PM02 620 233 0853 ASSY MOTOR

PM03 620 236 3776 COVER,GEAR

PM04 620 230 8753 GEAR MIDDLE

or 620 237 8800 GEAR MIDDLE

PM03

PM05 620 230 8760 GEAR DRIVE

or 620 237 8770 GEAR DRIVE

PM06 620 231 0596 SHAFT SLIDE

PM07 620 233 0860 SWITCH LEAG

PM08 411 104 8401 SCR PAN PCS 2X3

PM09 411 027 5402 SCR S-TPG FLT 2.6X6

PM10 620 236 0836 PWB,MOTOR

614 325 6014 ASSY,MECHA,DA11T3CN-SASH

*

* N.S.P : Not supplied as service parts.

*

*

PM07

PM02

PM01

PM10

- 8 -

Page 10

IC BLOCK DIAGRAM & DESCRIPTION

14

13

12

11

10

1

2

3

4

5

6

7

NF1

IN1

GND

Vcc

IN2

FILTER

ALC

ALC

NC

NC

NC

OUT 1

OUT 2

NF2

150k

150k

+

+

-

-

9

8

IC103 MM1469XH (CD Driver)

28 27 26 25 24 23 22 21 20 19 18 17 16 15

Vcc

Vcc

D.BUFD.BUFD.BUFD.BUF

IC201 LA1186N-AUDIO (FM Front End)

Level shift

T.S .D

Level shift

1234567 891011121314

Level shift

DRIVER MUTE

Level shift

D.BUFD.BUFD.BUFD.BUF

IC211 LA1844ML ( Tuner System)

24 23 22 21 20 19 18 17 16 15 14

ALC

BUFF

LEVEL

DET

FM

IF

AM

OSC

S-CURVE

FM

DET

AM

MIX

AM/FM

IF

BUFF

AM

RF.AMP

AM

IF

AGC

AM

DET

COMP

TUNING

DRIVE

Vref BUFFER

RF MIX REG OSC

1 2 3 4 5 6 7 8 9

RF IN GND IF OUT Vcc

13

2

PILOT

CANCEL

FF

19k

PILOT

DET

P-DET

304kHz

DECODER

ANTI-BIRDIE

VCO

STEREO

SW

FF

38k

FF

19k

REG

1

23456789101112

GND

IC410 BA3314F (Dula Preamplifier with ALC Detector)

VCC

- 9 -

Page 11

IC BLOCK DIAGRAM & DESCRIPTION

IC411 LC75392 (Function & Electric Volume) IC412 TA8229K (Power Amplifier)

LT

L1

(R1)

L2

(R2)

L3

(R3)

L4

(R4)

LT2

LT4

(RT2)

(RT4)

LT3

(R

6,25

T3)

5,26

LTCOM

(RTCOM)

4,27

LT1

(RT1)

7,2

12

11

10

9

8,2

OUT

(RTOUT)

(RVRIN)

3,28

LVRIN

2,29

LVROUT

(RVROUT)

1,30

IN-1

NF1

11

10

-

+

VCC1VCC2

48

Ch-1

6

5

B.S.1

OUT-1

Vref

18

LATCH

DECODER

14

CL

DI

CE

15

16

CONTROL

SHIFT REGISTER

IC446 NJM78L05A (Stabilized Power Supply)

R13

13

DDVSS

V

RIPPLE

TERMINAL

IN-2

NF2

9

12

13

BIAS CIRCUIT

THERMAL CUT-OFF

PROTECTION

-

Ch-2

+

7

3

2

POWER

GND

OUT-2

B.S.2

14 15

17

Q5Q6

PRE

GND1

Q12

PRE

GND2

I

V

3

Q15

Q10

R14

R15

R16

R5

Q11

Q9

R1 R2

Q1 Q2 Q3

R17

R3

R4

Q4

Q14

R11

R12

Q13

R9

R10

Vo

1

Q7Q8

R6

R8

R7

2

GND

- 10 -

Page 12

IC BLOCK DIAGRAM & DESCRIPTION

XIN

TEST2

SI0/PG3

SO0/PG2

SCK0/PG1

PG0

PC3

PC2

PC1

PC0

PB3

PB2

PB1

PB0

PA3

PA2

PA1

PA0

PK3

PK2

INT1/PK1

INT0/PK0

PN3/S32

PN2/S31

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

P10/DAC0

P11/DAC1

P12/DAC2

P13/DAC3

Vdd1

Vdd2

COM1

COM2

COM3

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

S14

S15

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65

PN1/S30

BEEP/PN0/S29

PM3/S28

PM2/S27

PM1/S26

PM0/S25

[Vpp]Vdd

SI1/PF3/S24

SO1/PF2/S23

SCK1/PF1/S22

PF0/S21

SI2/PE3/S20

SO2/PE2/S19

SCK2/PE1/S18

PE0/S17

S16

XOUT

TEST1

E02

E01

VSS

AMIN

FMIN

Vdd

SNS

LCTR

HCTR

HOLD

PH0/ADI0

PH1/ADI1

PH2/ADI2

PH3/ADI3

IC601 IC LC72338-9B55 (Single-Chip PLL + Controller)

XIN

XOUT

FMIN

AMIN

SNS

VDD

VSS

HCTR

LCTR

HOLD

TEST1

TEST2

PA0

PA1

PA2

PA3

PB0

PB1

PB2

PB3

PC0

PC1

PC2

PC3

PG0

SCK0/PG1

SO0/PG2

SI0/PG3

1

REFERENCE DIVIDERDIVIDER

80

74

1 / 16,1 / 17

PROGRAMMABLE DIVIDER

SELECTER

PHASE

DETECTOR

UNLOCK

F/F

COMMON

DRIVER

75

72

73

76

70

71

V-DET

SNSFF

1 / 2

UNIVERSAL

COUNTER

(20bits)

LATCH

LCDA/B

4

LCPA/B

4

SEG

PLA

7

LCD

LATCH

96

PORT

DRIVER

69

79

2

18

17

16

15

14

13

12

11

10

9

8

7

BUS

DRIV.

LATCH

BUS

DRIV.

LATCH

BUS

DRIV.

SIO

512 x 4bits

ROM

8K x 16bits

ADDRESS DECODER

PROGRAM COUNTER

STACK

6

5

4

3

LATCH

BUS

DRIV.

RAM

ALU

ADDRESS

DECODER

BUS

DRIVER

INSTRUCTION

DECODER

JUDGE

DAC

BEEP

LATCH

BUS

DRIV.

LATCH

BUS

DRIV.

LATCH

BUS

DRIV.

LATCH

BUS

DRIV.

LATCH

BUS

DRIV.

LATCH

BUS

DRIV.

MPX

MPX

MPX

MPX

MPX

INTERRUPT

ADC

MPX

LATCH

BUS

DRIV.

77 E01

78

E02

58

COM1

57

COM2

56

COM3

Vdd1

60

59

Vdd2

S1

55

54

S2

53

S3

52

S4

S5

51

S6

50

S7

49

S8

48

S9

47

S10

46

S11

45

44

S12

43

S13

S14

42

41

S15

S16

40

39

S17/PE0

38

S18/PE1/SCK2

S19/PE2/SO2

37

36

S20/PE3/SI2

S21/PF0

35

34

S22/PF1/SCK1

33

S23/PF2/SO1

S24/PF3/SI1

32

30

S25/PM0

29

S26/PM1

28

S27/PM2

27

S28/PM3

26

S29/PN0/BEEP

25

S30/PN1

24

S31/PN2

23

S32/PN3

61

PJ3/DAC3

62

PJ2/DAC2

63

PJ1/DAC1

64

PJ0/DAC0

19

PK3

20

PK2

21

PK1/INT1

22

PK0/INT0

65

PH3/ADI3

66

PH2/ADI2

67

PH1/ADI1

68

PH0/ADI0

- 11 -

Page 13

IC BLOCK DIAGRAM & DESCRIPTION

IC601 IC LC72338-9B55 (Single-Chip PLL + Controller)

PIn name Pin No. I/O I/O Format Functions

Port only for key return signal input.

PA0

PA1

PA2

PA3

PB0

PB1

PB2

PB3

PC0

PC1

PC2

PC3

PG0

PG1/SCK0

PG2/SO0

PG3/SI0

XIN

XOUT1 80

EO1

EO2

VSS

VDD

FMIN

AMIN

HCTR

SNS

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4 3 I/O

78

77

76

31,73

74

75

70

72

I

O

I

O

O

-

I

I

I

I

Pull-down

resistor

input

Unbalance

CMOS

Push-pull

CMOS

posh-pull

The threshold voltage is set to a relatively low value.

When a key matrix is formed by combining PB and PC ports,

maximum three simultaneous key presses can be detected.

All of four pull-down resistor are set by the IOS instruction with

Pn=2, bl and specification of resistor for each pin is impossible.

The input is disabled in clock stop mode.

Port only for key source signal output.

Since the output transistor circuit is an unbalanced CMOS

structure, diodes to prevent short-circuiting due to multiple key

presses are not required.

In clock stop mode, these pins go to the output high-impedance

state and hold this state until an output instruction is executed.

General-purpose output/serial I/O ports. Schmidt type input

the IOS instruction performs switching between general-purpose

I/O ports and serial I/O ports, and between input and output for

general-purpose I/O ports.

• When used as general-purpose I/O ports these pins

can be set for input or output in bit units(bit I/O),

and are set for use as general-purpose I/O ports by

the IOS instruction with Pn=0.

b0=SI/O 0 0 • • • general-purpose port

1 • • • SI/O port

Specification of input or output is made by the IOS instruction

in bit units.

PG • • • Pn=6 0 • • • Input

1 • • • Output

• When used as serial I/O ports these pins are set for

serial I/O port use by the IOS instruction with Pn=0.

The content of serial I/O data buffer is saved or load by the

INR and OUTR instructions.

*Pin setup states when used as serial I/O ports

PG0 • • • general-purpose input or output

PG1 • • • SCK0 output in internal block

SCK0 input in external block

PG2 • • • SO0 output

PG3 • • • SI0 input

In clock stop mode, input is disabled and these pins go to

the high-impedance state.

During the power-on reset, these pins become general-purpose

input ports.

-

4.5MHz crystal oscillator pin.

Charge pump output pin.

These pins go to high-impedance state when the HOLD pin is set

CMOS

low in the hold enable state.

tristate

In ckock stop mode, during the power-on reset and in the PLL

stop state, these pins go to the high-impedance state.

-Power supply pin.

FMVCO (local oscillator) input pin.

This pin is selected by the PLL instruction CW1 (b1=0,b0=don't

care). Capacitor coupling must be used for signalinput. Input is

disabled when the HOLD pin is set low inthe hold enable state.

Input is disable in clock stop mode,during the power-on reset,

and in the PLL stop state.

AMVCo (lcal oscillator) input pin.

This pin is selected and the band set by the PLL instruction

CW1 (b1,b0).

b1 b0 Band

1 0 2 to 40MHz (SW)

1 1 0.5 to 10MHz (MW,NW)

Capacitor coupling must be used for signal input.

Input is disabled when the HOLD pin is set low in the hold enable

state. Input is disabled in clock stop mode, during the power-on

reset, and in the PLL stop state.

Universal counter / general-purpose input port.

The IOS instruction b3 with Pn=3 switches the pin function

between universal counter input and general-purpose input.

• Frequency measurement

The universal counter function is selected by an IOS

instruction with Pn=3 and b2=0. HCTR frequency measure ment mode is set up by a UCS instruction with b3=0 and b2=0,

and counting is started with a UCC instruction after the count

time is selected. The CNTEND flag is set when the count

completes. To operate this circuit as an AC amplifier in this

mode, the input must be capacitor coupled.

• For use as the general-purpose input pin.

The general-porpose input port function is selected by an IOS

instruction with Pn=3 and b2=1. An internal register (address

OEH) input instruction INR(b0) is used to acquire data from

this pin.

Input is disabled in clock stop mede (the input pin will be pulled

down.) During the power-on reset, the universal counter function

is selected.

Voltage sense / general-purpose input pin port.

This circuit is designed for a relatively low input threshold voltage.

• For use as the voltage sense pin

This input pin is is used to determine whether or not a power

failure occurred after recovery from backup (clock stop) mode.

An internal sense F/F is used for this determination. The

sense F/F is tested with a TUL instruction (b2).

• For use as the general-purpose input port

When used as a genaral-purpose input port, the state is

sensed by using a TUL instruction (b3).

Since unlike other input ports, input is not disablle in clock

stop mode and during the power-on reset, special care is

required with respect to through currents.

PIn name Pin No. I/O I/O Format Functions

LCTR

71

I

HOLD

PH0/ADI0

PH1/ADI1

PH2/ADI2

PH3/ADI3

PJ0/DAC0

PJ1/DAC1

PJ2/DAC2

PJ3/DAC3

PK0/INT0

PK1/INT1

PK2

PK3

Vdd1

Vdd2

TEST1

TEST2

COM1

COM2

COM3

S1

|

S16

I

69

68

67

I

66

65

64

63

O

62

61

22

21

I/O

20

19

57

58

79

2

58

57

O

56

55

|

O

40

Universal counter (freqency and period measurement) / generalpurose input port.

This IOS instruction b3 with Pn=3 swithes the pin function

between universal counter input and general-puropse input.

• Frequency measurement

The universal counter function is selected by an IOS

instruction with Pn=3 and b3=0. LCTR frequency measure ment mode is set up by a UCS instruction with b3=0 and b2=1,

and counting is started with a UCC instruction after the count

time is selected. The CNTEND flag is set when the count

completes. To operate this circuit as an AC amplifier in this

mode, the input must be capacitor coupled.

• Period measurement

With the universal counter function selected, a UCS instruction

with b3=1 and b2=0 sets up the period measurement mode

and a UCC instruction starts counting after selecting the

count time. The CNTEND flag is set when the count

completes. In this mode, the signal must be input with DC

coupling to turn off the bias feedback resistor.

• For use as general-purpose input pin use.

The general-purpose input port function is selected by an IOS

instruction with Pn=3 and b3=1. An internal register (address

OEH) input instruction INR(b1) is used to acquire data from

this pin. Input is disabled in clock stop mode. (The input pin

will be pulled down.) During the power-on reset. The universal

counter function(in HCTR frequency measurement mode) is

selected.

PLLcontrol and CLOCK STOP mode control pin.

Setting this pin low in the hold enable state disables input to the

FMIN and AMIN pins and sets the E0 pin to the high-impedance

state. To enter clocl stop mode, set the HOLDEN flag, set this pin

low, and execute a CKSTP instruction. To clear clock stop mode

set this pin high.

General-purpose input ports/ADC input pins.

The IOS instruction with Pn=7 switches the pin function between

genetal-purpose input ports and ADC inputs.

• For use as the general-purpose input port

The IOS instruction with Pn=7 specifies the use as general purpose input port in bit units.

• For use as ADC input pin

The IOS instruction with Pn=7 specifies the use as ADC in bit

units. The IOS instruction with Pn=1 specifies the pin to

convert. The UCC instruction (b2) starts a conversion.

The ADCE flag will be set when the conversion completes.

Note) Executing an input instruction for a port specified for ADI

use will always return low since input is disabled. These

pins must be set up for general-purpose input port usage

before an input instruction is excuted. (In other words, the

port must be set to the general-porpose input function

before the input instruction is executed.)

Input is disabled in clock stop mode. During the power-on reset

these pins go to the general-purpose input port function.

General-purpose output ports/DAC input pin.

The IOS instruction with Pn=9 switches the pin function between

general-purpose output ports and ADC inputs. Since these pins

are open drain circuit, pull-up resistors are required in exrernal

circuit accepting these outputs.

• For use as general-purpose output port

The IOS instruction with Pn=9F specifies general-purrpose

input port use in bit units.

Nch

• For use as DAC

open drain

The IOS instruction Pn=9 is used to switch the port in bit units.

DAC data is loaded into tne DAC (0 to 3) specified with the

DAC instruction, Although PWM waveform is output as soon

as the port is switched, the data prior to that load is output for

up to 114µs (1/8.791kHz) after data is loaded.

The general-purpose output port function is selected after a power

-on reset, and the output go to the transistor off (H output) state.

General-purpose I/O / external interrupt ports

There is no instruction that switches the function between generalpurpose ports and external interrupt ports. These pins function for

input only when the external interrupt enable flag is set.

(Output disables)

• For use as general-purpose I/O port

These pins can be set for input or output in bit units (bit I/O).

The IOS instruction is used to specify input or output in bit

units.

CMOS

• For use as external interrupt pin

push-pull

This function can be used by setting the external interrupt

enable flags (INT0EN and INT1EN) in status register 2.

The corresponding pin is automatically set to the input port.

To enable interrupt operation, the interrupt enable flag (INTEN)

in status register 1 must also be set. The IOS instruction with

Pn=3, b1=INT1, and b0=INT0 is used to select rising or falling

edge detection.

In clock stop mode, input is disabled and these pins go to the highimpedance state. During the power-on reset, these pins go to the

general-purpose input port function.

Pin for external application of 2/3 voltage of LCD drive bias.

Pin for external application of 1/3 voltage of LCD drive bias.

LSI test pin.

These pins must be either left open or connected to ground.

CMOS

LCD driver common output pin.

three

Driver format 1/3 duty, 1/3 bias.

value

This pin is fixed at the low level in CLOCK STOP mode.

output

This pin is fixed at the low level after a power-on reset.

LCD driver common output pin.

CMOS

Driver format 1/3 duty, 1/3 bias.

three

The frame frequency 100MHz.

value

This pin is fixed at the low level in CLOCK STOP mode.

output

This pin is fixed at the low level after a power-on reset.

- 12 -

Page 14

IC BLOCK DIAGRAM & DESCRIPTION

IC601 IC LC72338-9B55 (Single-Chip PLL + Controller)

PIn name Pin No. I/O I/O Format Functions

S17/PE0

S18/PE1/SCK2

S19/PE2/SO2

S20/PE3/SI2

S25/PM0

S26/PM1

S27/PM2

S28/PM3

39

38

I/O

37

36

30

29

I/O

28

27

LCD driver segment output, general-porpose input/output and

serial I/O ports

The IOS instruction is used to switch between the LCD driver

segment output, general-purpose I/O, and serial I/O functions,

and to switch between input and output of the general-purpose

input port function.

• For use as segment output

These pins can be set in bit units.

The IOS instruction with Pn=ODH specifies segment output

use in bit units.

b0=S17/PE0 0 • • • Segment output

b1=S18/PE1 1 • • • PE0 to 3 output

b2=S19/PE2

b3=S20/PE3

• For use as general-purpose input /output port

These pins can be set for input /output in bit units.

(1 bit I/O)

b2=SI/O2 0 • • • Genetal-purpose port

CMOS

1 • • • SI/O port

three

Input /output is specified with the IOS instruction in bit units.

value

PE • • • Pn=4 0 • • • Input

output

1 • • • Output

and

• For serial I/O port

push-pull

The serial I/O port function is specified with the IOS instruction

(Pn=0).

The contents of the serial I/O data buffer can be saved and

loaded with the INR and OUTR instructions.

*Pin setup states when used as a serial I/O port

PE0 • • • General-purpose input /output

PE1 • • • SCK2 output in internal clock mode

SCK2 output in external clock mode

PE2 • • • SO2 output

PE3 • • • SI2 input

In CLOCK STOP mode, if this port is used as a general-purpose

I/O port or as a serial I/O port, the pins go to the input disabled

high-impedance state. If used for segment output, the pins fixed at

the low level. The segment output port function is selected after a

power-on reset.

LCD driver segment output, general-porpose input /output ports.

The IOS instruction is used to switch between the LCD driver

segment output, general-purpose I/O port, and serial I/O to switch

between input and output of the general-purpose input /output

port function.

• For use as segment output

These pins can be set in 4 bits units. The IOS instruction with

CMOS

Pn=OEH specifies segment output use in bit units.

three

b0=S25 to 28/PM0 to 3 0 • • • Segment output

value

1 • • • PM0 to 3

output

• For use as general-purpose input /output port

and

These pins can be set for input /output in bit units.

push-pull

Input /output is specified with the IOS instruction in bit units.

PM • • • Pn=OCH 0 • • • Input

1 • • • Output

In CLOCK STOP mode, if this port is used as a general-purpose

I/O port, the pins go to the input disabled high-impedance state. If

used for segment output, the pins are fixed at the low level. The

segment output port function is selected after a power-on reset.

PIn name Pin No. I/O I/O Format Functions

S21/PF0

S22/PF1/SCK1

S23/PF2/SO1

S24/PF3/SI1

S29/PN0/BEEP

S30/PN1

S31/PN2

S32/PN3

35

34

I/O

33

32

26

25

O

24

23

LCD driver segment output, general-porpose input/output and

serial I/O ports.

The PF0 to 3 inputs are in the Schmidt format.

The IOS instruction is used to switch between the LCD driver

segment output, general-purpose I/O, and serial I/O functions, and

to switch between input and output of the general-purpose input

port function.

• For use as segment output

These pins can be set in 4 bits units. The IOS instruction with

Pn=OEH specifies segment output use in bit units.

b0=S21 to 24/ PF0 to 3 0 • • • Segment output

1 • • • PE0 to 3

• For use as general-purpose input /output port

These pins can be set to input /output in bit units. (1 bit I/O)

CMOS

b1=SI/O 1 0 • • • Genetal-purpose port

three

1 • • • SI/O port

value

Input /output is specified with the IOS instruction in bit units.

output

PF • • • Pn=5 0 • • • Input

and

1 • • • Output

push-pull

• For use as serial I/O port

The serial I/O port function is specified with the IOS instruction

(Pn=0). The contents of the serial I/O data buffer can be saved

and loaded with the INR and OUTR instructions.

*Pin setup states when used as a serial I/O port

PF0 • • • General-purpose input /output

PF1 • • • SCK1 output in internal clock mode

SCK1 output in external clock mode

PF2 • • • SO1 output

PF3 • • • SI1 input

In CLOCK STOP mode, if this port is used as a general-purpose

I/O port or as a serial I/O port, the pins go to the input disabled

high-impedance state. If used for segment output, the pins are

fixed at the low level. The segment output port function is selected

after a power-on reset.

Segment output/general-porpose input port 1/ BEEP tone output

pins. The IOS instruction is used to switch between the segment

output port and the PN0 to 3 functions. The BEEP instruction

switches between the general-purpose output port and BEEP tone

function.

• For use as segment output

These pins can be set in 3 bits units. The IOS instruction with

Pn=OEH specifies segment output use in bit units.

b2=S29 to 32/ PN0 to 3 0 • • • Segment output

1 • • • PN0 to 3

CMOS

• For use as general-purpose output.

three

The general-porpose output port function is selected with the

value

BEEP instruction (b3=0).

output

PN1 to 3 are dedicated general-purpose output function pins.

and

• For use as BEEP output pin

push-pull

The BEEP instruction with b3=1 sets the BEEP output.

The BEEP instruction bit b0,b1 and b2 sets the frequency.

When this is set as the BEEP port, executing an output

instruction will rewrite the inter nal latch data but has no

influence on the output.

These pins go to the output high-impedance state in clock stop

mode. If used for segment output, the pins are fixed at the low level.

These pins go to the output high-impedance state during the

power-on reset and hold that state until an output instruction is

executed.

- 13 -

Page 15

LCD DISPLAY DESCRIPTION

FF

LCD60

28 1

T9

T2

N

FF

T4T6

T3T5

1h

12

T7

PAD NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

2h

345

4h

3h

T8

IC NO.

C1

C2

C3

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

S14

S15

S16

S17

S18

S19

S20

S21

S22

S23

S24

S25

T1

COM1

COM1

--

-7A

7B

ON

6A

6B

OFF

T1

5

T5

4A

4B

4M

3A

3B

3M

T2

T9

T8

2A

2B

2h

1A

1B

1h

SURR

67

COM2

--

COM2

-7F

7G

7C

6F

6G

6C

MHZ

PROG.

T6

4F

4G

4C

3F

3G

3C

T4

T3

4h

2F

2G

2C

1F

1G

1C

SLEEP

1h

A

BF

G

K

CE

D

3h

A

BF

G

CE

D

4h

COM3

--

--

COM3

7E

7D

CH

6E

6D

TR

kHZ

BASS

ST

4E

4D

4K

3E

3D

3K

T7

--

3h

2E

2D

MONO

1E

1D

1K

AM

- 14 -

Page 16

WIRING CONNECTION

CN202

(15P)

TUNER P.W.B

FM

ANT.

CN203

(1P)

CN201

AM LOOP

ANT.

L-CH

SPEAKER

BOX

AMPLIFIER P.W.B

R-CH

SPEAKER

BOX

LED P.W.B

FRONT P.W.B

CN601

(14P)

CN122

(8P)

LCD60

CN111

CD P.W.B

(16P)

CN602

CN113

(6P)

BOARD

TO

BOARD

(2P)

CN603

(15P)

CN421

PHONES

CN491

(14P)

CN490

(8P)

CN406

(4P)

CN405

(4P)

P.T

FU401

T2.5A L 250V

BK RE

CN450

(2P)

CN441

(2P)

BL

BW

CN452 CN451

CN402

(2P)

CN401

(2P)

AC IN

(16P)

CD-R/RW MECHANISM

This is a basic wiring diagram.

(6P)

- 15 -

ORANGE

POWER TRANSFORMER P.W .B

TAPE DECK MECHANISM

RED

BROWN

YELLOW

MOTOR

SWITCH

R/P HEAD

M

Page 17

SCHEMATIC DIAGRAM (FRONT)

TO TUNER SEC.

GND

LID_SW.

AMOSC

AMIF

VT

MONO

TU_MUTE

BAND1

TU_L

BAND2

TU_R

SD

TU_GND

STEREO

TU_+B

CN603

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

+B_8.5V

GND

1

2

75

71

26

10

24

TU_L

23

TU_R

36

TU_GND

37

TU_+B

C6912

0.01

CN602

+B_8.5V

GND

560

R6951

560

R6952

000000

D6954D6955

330

R6953

330

R6954

000000000

D6951

D6952D6953

R6201

2.7K

Q6201

2SC1740

C6200

1/50

C6201

0.01

Q6200

2SC1740

S6500

100K

R6103

R6501

1K

R6502

1K

TO FMOSC

C6104

C6105

123

-2-1

123

C6914

C6913

CD_RST

C6916

JOG

33P

33P

3

4

5

6

8

9

10

11

14

TA_PLAY

17

18

21

23

24

54

R6200

X6001

100P

100P

1000P

10K

R6104

SE601

27

2.2K

4.5MHz

C6915

R6906

C6918

2200P

C6920

C6921

10K

R6105

28

100P

470

100P

100P

10K

R6106

29

R6009

75

22UH

L6901

330P

C6103

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65

VSS

EO2

XOUT

1

XIN

TEST2

2

3

SQOUT

COIN

4

CQCK

5

RWC

6

DSP_RESET

7

BEAT

8

SURR

9

TU_MUTE

10

AUX_MUTE

11

BASS

12

PB1

13

P_CON

14

PA3

15

TAPE_PLAY

16

WRQ

17

DRF

18

JOG2

19

20

JOG1

21

PICK_SW.

22

REMIN

23

BAND2

BAND1

24

A

MUTE

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

C6206

100P

0.01

10K

R6113

C6910

25

30

34

33

32

EO1

TEST1

QLC723389B55M

S23

S24

S25

MONO

29

26

27

28

404142

39

35

AMOSC

IC601

S22

0.01

30

C6922

100P

C6102

VDD

FMOSC

S21

VDD

323334

43

71

330P

C6101

AMIF

LID_SW.

S20

S19

46

45

LCD60

EU-1 US JP

OPEN 0 8.2K

0.01

33K

R6009

C6911

R6109

47K

330P

C6100

DIST

FMIF

AC_SENS

SELECTION

STEREO

SD

S18

SYNC_REC.

R6907

35

373836

505152

494448

47

(TV)

66

65

KY0

KY1

D_CLK

D_OUT

VF_CE

(POWER)

(VDD1)

(VDD2)

COM1

COM2

COM3

S10

S11

S12

S13

S14

S15

S17

S16

47K

39

40

R6108

R6107

S1

S2

S3

S4

S5

S6

S7

S8

S9

10K

R6112

53

C6202

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

C6208

2200P

54

SS EU-2 JP

8.2K

8.2K 8.2K

10K 10K

15K 15K 27K

100P

C6203

1000P

4.7K

4.7K

10K

R6012

100P

C6012

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

100P

C6205

57

56

55

12345678910111213141516171819202122232425262728

10K

47K

R6111

R6011

C6011

58

C6904

10K

100P

8.2K

R6115

47/10

10K

R6010

100P

C6010

100P

C6204

MODEL JPOOTHER

R6115

R6114

47K

1001000/6.3

R6905C6905

0.01

C6903

64

63

62

CLOCK

AUX

D6901

1SS133

C6901

0.01

8.2K

CLOCK

C6900

10/16

D6902

1SS133

S6001

MEMORY

S6002

TIMER/CLOCK

S6003

POWER

S6004

FUNCTION

S6005

TU/BAND

S6006

PRESET/REP.

65

560

R6001

680

R6002

8201.5K 1.2K

R6003R6005 R6004

11

8

9

14

TA_PLAY

L6900

64

25

63

38

62

66

TU_+B

TU_GND

TU_L

TU_R

CD_RST

10

560

R6006

6801.2K 820

R6007R6013 R6008

1.5K2.2K

R6014R6015

3

4

5

17

6

18

21

C6906

100P

S6007

SOUND PRESET

S6008

BASS

S6009

SURR.

S6010

TU DOWN

S6011

TU UP

S6012

CD PLAY

S6013

CD STOP

TU_+B

TU_GND

TU_L

TU_R

CD RESET

SQOUT

COIN

CQCK

WRQ

RWC

DRF

(PICK_SW.)LIMIT

TO AMP SEC.

CN601

14

AUX_MUTE

13

12

11

10

QSOUND

9

8

TAPE_PLAY

7

AC_SNS

6

5

VOL_CLK

4

A_MUTE

3

VOL_DATA

2

SYNC REC.

1

VOL_STB

BEAT

BASS

ST_BY

GND

+5.6V

TO CD SEC.

0.01

C6501

0.01

C6502

This is a basic schematic diagram.

- 17 -- 16 -

Page 18

SCHEMATIC DIAGRAM (CD)

PICK UP

COM

DT11T3CN

GND

LD

LD

VR

SVR

LAND

SHORT

MD

MD

F+

T-

T+

COIL

COIL

FOCUS

TRCKING

F-

SPINDLE MOTOR

M

M

SLED MOTOR

MECHANISM

LIMIT

LIMIT SW

BASE

E

D

A

B

C

GND

68P

68P

C1480

C1467

16M

PCK

R1473

100K

C1485

0.0

0.0

TST11

FSEQ

0.01

22000P

4.8

4.8

REST

CQCK

IC102

LC78629E

(D-MUTE)

CONT1

DVDD

4.8

4.8

4.8

0.0

0.0

0.0

10;K

L1451

4.7K

R1472

4.8

0.0

0.0

TEST1

4.8

68P

C1471

0.0

0.0

CS

4.2M

TEST5

JP-

JP+

TGL

0.0

0.0

0.0

0.0

C1457

10;25

10

330P

C1308

C1341

R1340

R1342

R1344

R1345

R1346

R1347

0.15

R1312

R1303

R1305

0.22

27K

R1310

15K

Q1301

2SB810

3.6

4.2

1000P

82K

82K

82K

82K

150K

150K

150K

2.2K

C1304

3300P

R1311

6.8K

R1304

6.8K

0.033

R1309

C1301

330

100K

47;10

FIN2

2.5

2.5

FIN1

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

TE

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

E

2.5

2.5

JP

TO

FD

R1313

22K

10

11

12

13

14

15

16

R1302

100

R1301

C1335

10;50

4.3

4.9

3.6

1.6

C1302

C1303

0.22

C1305

R1308

C1309

0.047

C1310

VREFVREF

16

COMMON

15

E

14

D

13

A

12

B

11

C

10

F

F

9

GND

8

LD

7

VR

6

MD

5

F+

4

T-

3

T+

2

F-

1

CN111

C1312

1000P

C1313

0.1

3.3K

1.5K

R1502

R1501

SP+

SL+

SP+

6

SP-

SP-

5

SL+

4

SL-

SL-

3

LIMIT

2

GND

1

0.01

C1334

C1333

0.22;50

LDS

4.9

4.9

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

1

RFVCC

2

3

F

4

TB

5

TE-

6

TE

7

8

TESI

SCH

9

TH

TA

TD-

TD

REF

R1315

R1314

22K

LDD

0.2

0.0

3.6

4.2

2.2

2.2

VCC1

LASER

VPPC

REF

REF

REF

BPL

REF

-HIST.COMP

SHOCK:WCOMP

TGHI

TGHI

TGLI

TGLI

THLDI

REF

TOFF2

REF

REF

TOFF

FA

FA-

FD-

2.5

2.5

2.5

2.5

2.5

2.5

2.5

2.5

15K

C1350

0.018

R1317

R1318

68K

1.5K

28 27 26 25 24 23 22 21 20 19 18 17 16 15

-

+

IN

REG

IN

+---

BH1

VCA

VCA

TOADJ

R1320

8.2K

C1332

BAL

BALREF

THLDI

FE

C1315

VC

5V

C1339

0.047

2.5

1.0

TES

0.018

IC103

MUTE

GEN

VDD

PH1

TBC

JP

FE-

2.5

FE

C1340

10;25

2.5

2.5

0.1

C1331

TGLI

THLDI

0.01

C1337

0.01

2.5

2.5

1.0

LF2

BH1

FE1

RF

REF

VCA

REF

STOP

TOSTA

AND

OR

WCOMP

FSC

REF

GEN

FSERCH

SP

AGND

0.0

0.0

VDD

MM1469XH

CN113

R1476

1K

0.01

C1405

THLD

2.2

VR

REF

FSS

2.5

C1338

10;25

C1330

2.5

PH1

VCA

TGL

DEF

FSTA

FOFF

3300P

C1316

IN IN

0.01

C1336

R1453

10;25

2.5

4.9

4.9

0.0

0.0

4.8

0.0

FSS

DRF

CE

OR

2.5

SLOFSLOF

SLEQ

2.5

22;50 6.8K

CL

DAT

CLK

CL

CLK

DAT

LATCH

SLOF

CLK

CE

CL

DAT

PONRST

CV-

CV+

JP-

JP+

DEF

THLD

TBC

FSC

REF

RFS-

REF

RF

RFSM

CV+

CV-

SLOF

HFL

TES

TOFF

REF

TGL

JP+

JP-

SLD

32313029282726252423222120191817

SL-

JP-

SL+

2.5

2.5

2.3

2.3

2.3

2.3

0.0

C1321

R1331

3300P

10K

R1329

R1330

VC

REFI

VCC2

FSS

DRF

REF

GEN

2.5

1K 56K

C1317

D

a

FSTA

FSTA

8CM

12CM

C1318

2.5

Q

R

100P

R1327

56K

DEF

HFL

DRF

0.22;50

1.5K

R1503

VCC

JP

REF

TO

2.9

EFBAL

FOSTA

TOSTA

2FREQ

LASER

8/12CM

SPD

2.5

4.7;50

C1319

FSTA

SLOF

REF

REF

C1320

CE

REF

R1328

S.DVCC

PH4

BH2

GAIN

REF

VHFL

REF

VDRF

VCC

VR+0.3V

REF

S.Q.R

FOCS

REF

STOP

FOADJ

FE1

REF

REF

REF

SPOF

REF

SPI

SPG

SP-

2.2

2.5

2.5

2.5

33K

R1324

R1326 R1325

IC101

DEF

LA9242M

NC

0.0

0.0

TBC

2.5

2.5

FSC

2.5

2.5

DGND

0.0

0.0

SLI

SLC

2.4

2.4

1P

C1322

2.4

1.6

CV+

CV-

SLOF

0.0

4.8

HFL

TES

TOFF

0.0

4.8

TGL

4.8

4.8

JP+

33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48

0.0

0.0

0.0

220K

220K

2.7K

R1337

6.8K

C1329

4.7;50

R1338

330K

R1333 R1334

15K 1K

C1324

R1332

C1451 R1454

0.1 680

C1452

0.1

0.01

C1456

C1455

C1346

33P

C1325

2200P

10K

R1335

R1336

0.1

100K

R1343

330

0.033

12P

18K

C1323

RF

100P

C1481

R1455

R1456

0.0

0.0

DEFI

0.0

0.0

TAI

PDO

0.0

0.0

VVSS

1.5

1.5

ISET

4.8

68K

4.8

VVDD

10K

FR

0.0

0.0

DVSS

EFMO

2.3

2.3

EFMIN

0.0

0.0

TEST2

CLV+

CLV-

0.0

4.8

V/P

HFL

TES

TOFF

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

0.0

4.8

++

D1401 D1402 D1403

1413121110987654321

1SS133 1SS133 1SS133

C1402

C1407

0.022

C1408

100;16

Q1401

8.0

8.4

400mA

KTA1273

C1401

470;6.3

PR140

C1403

5.0

0.01

5.0

8.0

8.2

470;10

C1404

0.01

COIN

CONT2

0.01

C1472

C1468

0.0

0.0

SQOUT

(SLED +)

CONT3

0.0

0.0

100P

C1469

RWC

(SLED -)

CONT4

R1464

0.0

+9V

1K

FSX

WRQ

CONT5

0.0

EMPH

SBCK

C2F

SFSY

DOUT

PW

EFLG

SBSY

XVSS

XOUT

XVDD

MUTER

RVDD

RCHO

RVSS

LVSS

LCHO

LVDD

MUTEL

TEST3

0.0

49505152535455565758596061626364

XIN

NC

TEST4

32313029282726252423222120191817

0.0

C1470

48474645444342414039383736353433

68P

R1462

560

R1463

560

R1475

560

R1465

560

0.0

0.0

X1451

16.93M

4.8

4.8

0.0

4.7

5.1

5.1

2.1

2.1

C1492

47;10

0.0

0.0

2.1

2.1

5.1

5.1

0.0

4.7

0.0

0.0

0.0

0.0

C1475

R1499

C1491

C1493

100

68P

R1498

REST

CQCK

COIN

SQOUT

100

RWC

WRQ

C1495

DRF

C1773

R1771

10;25

1K

C1772C1782

1000P1000P

100K 100K

R1783 R1773

C1783

0.01

10;25

R1781

1K

CD_R

A.GND

CD_L

0.01

0.01

TO FRONT PWB

LIM_SW

DRF

RESET

RWC

CQCK

WRQ

COIN

SQOUT

TU_L

TU_R

TU_GND

TU_+B

CN122

1

TU_GND

2

TU_R

3

TU_L

4

CD_R

5

6

7

8

CD_GND

CD_L

GND

+B

A.GND

R1480

DRF

REST

D1404

MTZJ5.1B

RWC

CQCK

WRQ

COIN

SQOUT

TU_L

TU_R

TU_GND

TU_+B

560

C1415

220P

TU_GND

TU_R

TU_L

CD_R

D1410

RL153

CD_L

TU_+B

PLAY

STOP

This is a basic schematic diagram.

- 19 -- 18 -

Page 19

WIRING DIAGRAM ( CD & FRONT )

C6208

R6005

R6006

C6912

C1404

CD P.W. BOARD FRONT P.W. BOARD

SP+

SP-

SL+

SL-

LIMIT

GND

TU+B

CN113

C1404

C1404

J1428

D1410

J1214

CN122

C1415

TUGND

CD_R

TU_R

TU_L

J1426

J1427

C1403

R1473

A_GND

CD_L

GND

+B

J1212

J1213

R1503

VREF

COMMON

GND

LD

SVR

MD

F+

TT+

F-

J1424

J1425

J1328

J1420

R1502

R1501

E

D

A

B

C

F

J1423

J1327

IC103

C1337

C1335

R1301

C1401

CN111

J1414

J1415

J1417

J1418

J1416

J1413

J1419

R1476

J1412

J1421

J1422

J1326

D1401

J1210

C1301

J1209

J1211

C1405

C1402

D1402