Page 1

This Document can not be used without Samsung’s authorization

Samsung Electronics 7-1

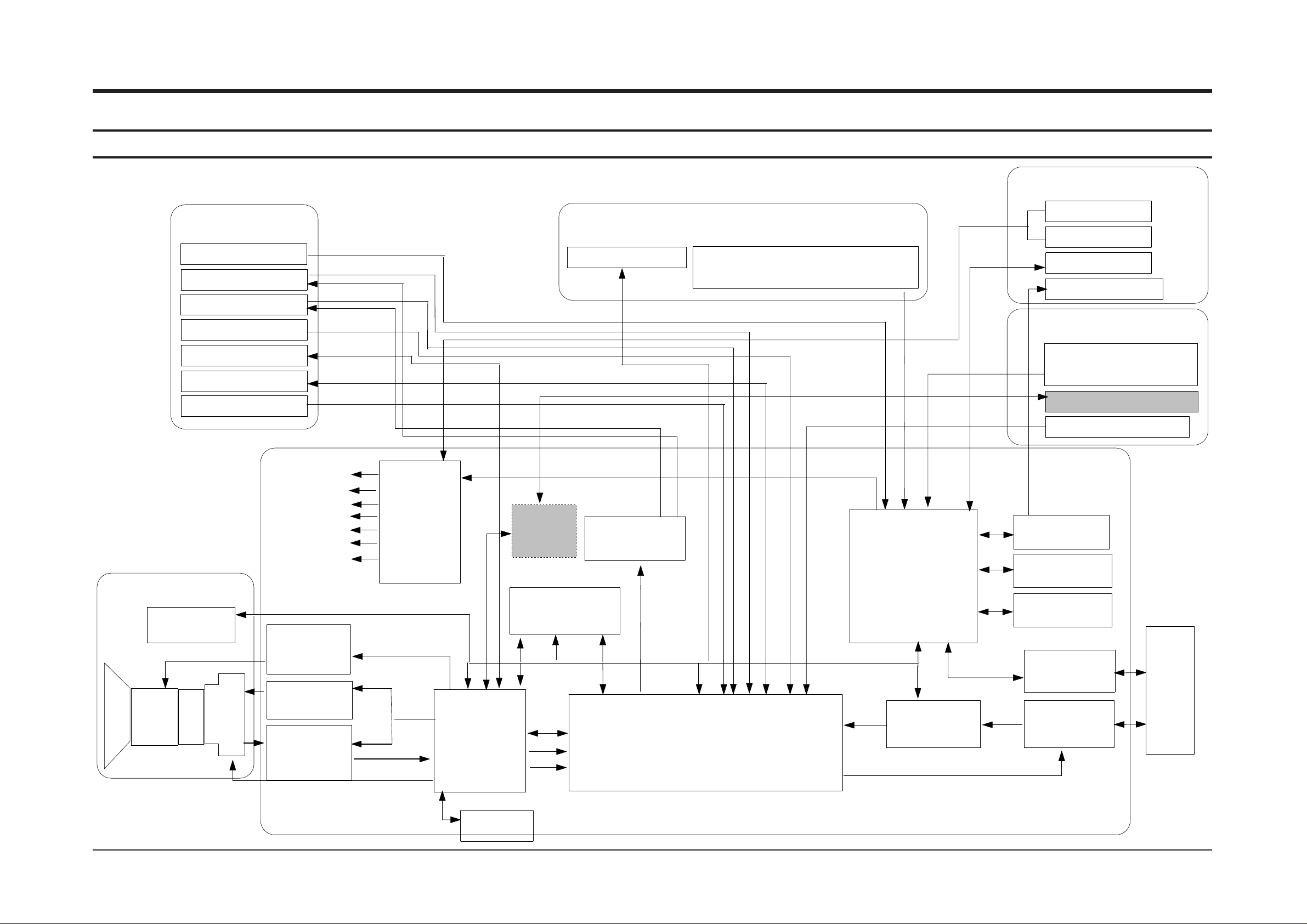

7. Block Diagrams

Camera Lens Ass’y

DSP6

(S5C7376X)

Motor Drive

(LB11993W)

CDS/AGC/A

DC

(TLV990B)

V.Drive

(KS7221D)

Main MICOM

(TMP1962)

Audio I/F

(BU7806)

X20

Lens

1/6"

CCD

O

L

P

F

Iris

Hall sensor

;

PRML

(LC74132W)

PREAMP

(LA70056T)

D

E

C

K

Video I/F

(NJM2538))

Zoom/focus

M. Drive

(UPD16877)

64M

SDRAM

DC/DC

(BD9833)

5V

3.3V

1.8V

BL5V

-15V~-7.5V

Drum VS

Capstan VS

Reset

(XC61FC2512)

RTC

(RS5C372A)

EEPROM

(24C045STP)

Main Ass’y

10Bits

ITU-R

656

27Mhz

54Mhz

Record Data

Envelope

PB CLK

PB DATA

H1,H2

Multi

Card

Slot

Remocon

S-jack

AV-jack

Internal MIC

USB jack

IEEE1394 jack

Front Ass’y

Ext. MIC jack

(BW;0.16"/76K )

Zoom S/W, Photo Key,

Tape Eject key, S.Shutter key

Right Ass’y

M/S Socket[Multi]

Battery

Lithium Battery

DC Jack

Menu Key&Selector,

Function Key

112K PVI LCD

POWER KEY

Rear Ass’y

Left Ass’y

DV_1_Chip

(GLOBALi)

7-1 All Block Diagram

Page 2

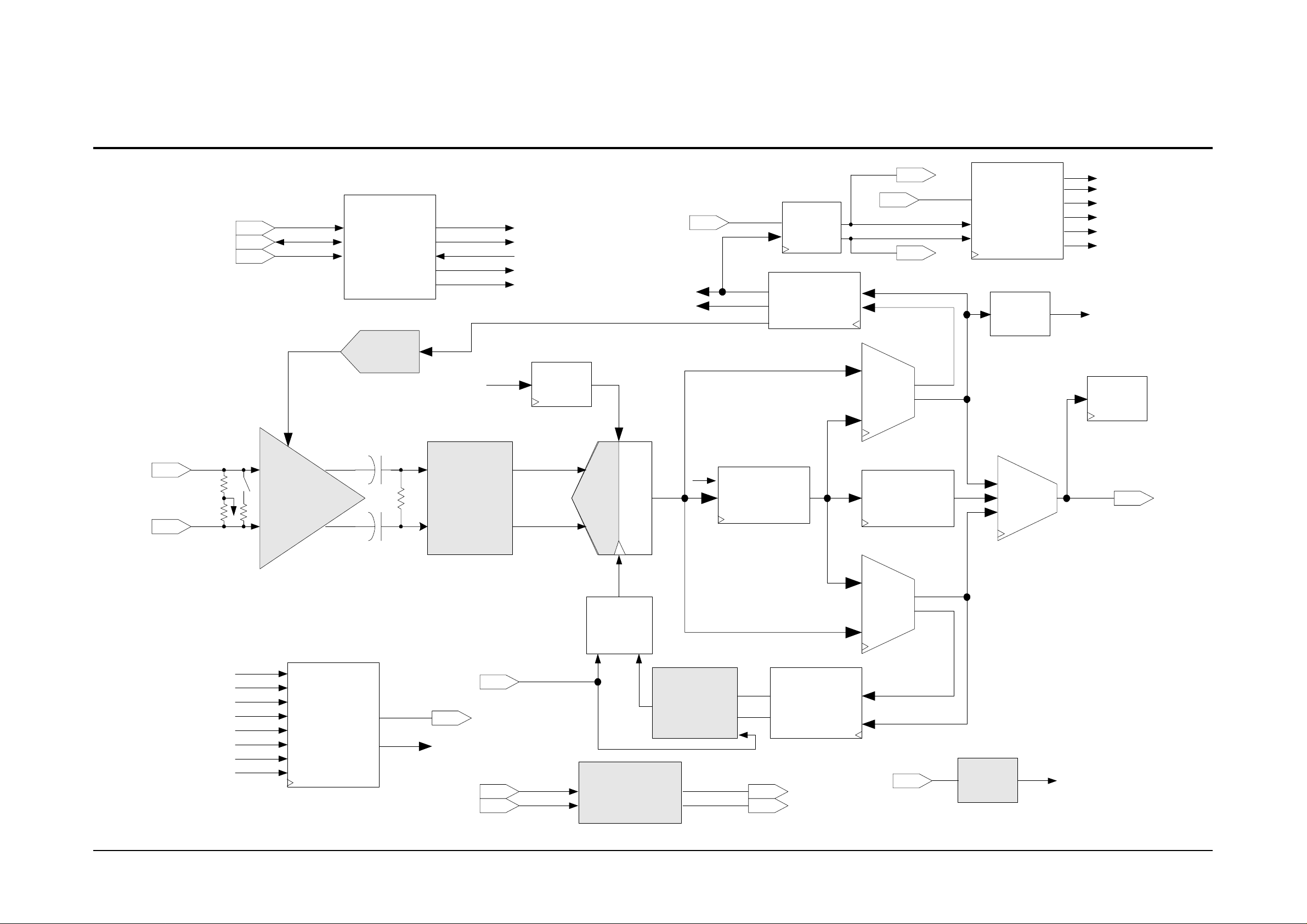

Block Diagrams

7-2 Samsung Electronics

This Document can not be used without Samsung’s authorization

VGA

DIP

DIN

VGX

VGY

CTF

VGX

VGY

CTX

CTY

AF

adrd afrd

cdcd

DD

afrd ddrd

ADC

CTX

CTY

adrd

afrd

adrd

slrd

trsl

adafrd

TRD

pherr adafrd

slrd

phadj

TRA

pherr

phadj

trck

fref

adrd

afrd

adafrd

gcsl

slrd

GCD

gcnewus

slrd

adafrd

gcerr

gcdac

padDIP

padDIN

slgcrd

ddrd

sltrrd

ddrd

padrd

CK

rsck

trckfref

padFREF

CC

DO

padRG

QE

afrd

tb

adrd

gcerr

gcnewus

trerr

adrg

afrg

lowz

updo

UP

reg_sel

padSEN

padSD

padSCK

updi

updo

upw

upr

padSEN

padSD

padSC K

reg_selects

updi

updo

upw

upr

adrd

afrd

adrg

afrg

lowz

trerr

gcerr

gcnewus

padTB

PG

pgrd

pgrg

pgrg pgrd

test

data

SA

updord

padRG

gcnewus

gcnewus

gcerr

gcdac

padXZ

updo

IO_TL

padATOAC

padATIX

padATIY

padATODC

padATIX

padATIY

padATOA Cx/y

padATOD Cx/y

POR

porbVD

VD

porb

padRG

CD

cdcdslrd

cdcd

cdcd

k

XZ

ccgctrk

cctrtrk

ccgcrg

cctrrg

lowz

cciacq

GCDAC

TD

XZ

iorg

gcnewus

DO

padDO

7-2 IC101 Block Diagram

Page 3

Block Diagrams

Samsung Electronics 7-3

This Document can not be used without Samsung’s authorization

SHUFFLE

VIDEO

CODEC

AUDIO

AUXSC

DVC_LINK

IIC

CODEC

(channel)

MODAS

DEMOD

VCO

DAC

4MBits

SDRAM

10.5MBits

SDRAM

1394

PHY

MICOM

Camera

PRML

Audio

AD/DA

Video

Decoder

CLOCK

OSD

2

nd

-DV1CHIP

LCD

AFE

Audioo

DSP

Color

Encoderr

7-3 IC201 Block Diagram

Page 4

Block Diagrams

7-4 Samsung Electronics

This Document can not be used without Samsung’s authorization

CAMERA

PROCESSOR

MPEG4

CODEC

(30FPS@VGA)

JPEG

CODEC

VIDEO BUS

AHB BUS

ARM920T

AHB2VIDEO

BRIDGE

APB BUS

AHB2APB

BRIDGE

USB 2.0 DEV.

UART * 2

AUDIO

CODEC

(G.726)

MS Pro

SD/MMC

Timer * 4

GPIO(32bit)

DNIe

DMA * 4

DVC

DSP

I2C*2

Motor

Control

PWM

2ch

I2S

SPI * 2

OSD

AD 4ch

(200KHz/

10bit)

DRAM

Controller

(for F/W)

NAND

FLASH

CONTROLLER

7-4 ICM01 Block Diagram

Loading...

Loading...