Samsung S5PV210 Hardware Design Manual

S5PV210_HARDWARE DESING GUIDE REV 1.0

Hardware Design

Guide

S5PV210

RISC Microprocessor

FEB 8, 2010

REV 1.0

S5PV210_HARDWARE DESING GUIDE REV 1.0

2

Important Notice

The information in this publication has been carefully

checked and is believed to be entirely accurate at the

time of publication. Samsung assumes no

responsibility, however, for possible errors or

omissions, or for any consequences resulting from the

use of the information contained herein.

Samsung reserves the right to make changes in its

products or product specifications with the intent to

improve function or design at any time and without

notice and is not required to update this

documentation to reflect such changes.

This publication does not convey to a purchaser of

semiconductor devices described herein any license

under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or

guarantee regarding the suitability of its products for

any particular purpose, nor does Samsung assume

any liability arising out of the application or use of any

product or circuit and specifically disclaims any and all

liability, including without limitation any consequential

or incidental damages.

"Typical" parameters can and do vary in different

applications. All operating parameters, including

"Typicals" must be validated for each customer

application by the customer's technical experts.

Samsung products are not designed, intended, or

authorized for use as components in systems

intended for surgical implant into the body, for other

applications intended to support or sustain life, or for

any other application in which the failure of the

Samsung product could create a situation where

personal injury or death may occur.

Should the Buyer purchase or use a Samsung product

for any such unintended or unauthorized application,

the Buyer shall indemnify and hold Samsung and its

officers, employees, subsidiaries, affiliates, and

distributors harmless against all claims, costs,

damages, expenses, and reasonable attorney fees

arising out of, either directly or indirectly, any claim of

personal injury or death that may be associated with

such unintended or unauthorized use, even if such

claim alleges that Samsung was negligent regarding

the design or manufacture of said product

S5PV210_HARDWARE DESING GUIDE REV 1.0

.

S5PV210 RISC Microprocessor

Hardware Design Guide, Revision 1.0

Copyright © 2010 Samsung Electronics Co., Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in

any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior

written consent of Samsung Electronics.

Samsung Electronics Co., Ltd.

San #24 Nongseo-Dong, Giheung-Gu

Yongin-City, Gyeonggi-Do, Korea 446-711

TEL : (82)-(031)-209-4356

FAX : (82)-(031)-209-3262

Home Page: http://www.samsungsemi.com

Printed in the Republic of Korea

S5PV210_HARDWARE DESING GUIDE REV 1.0

4

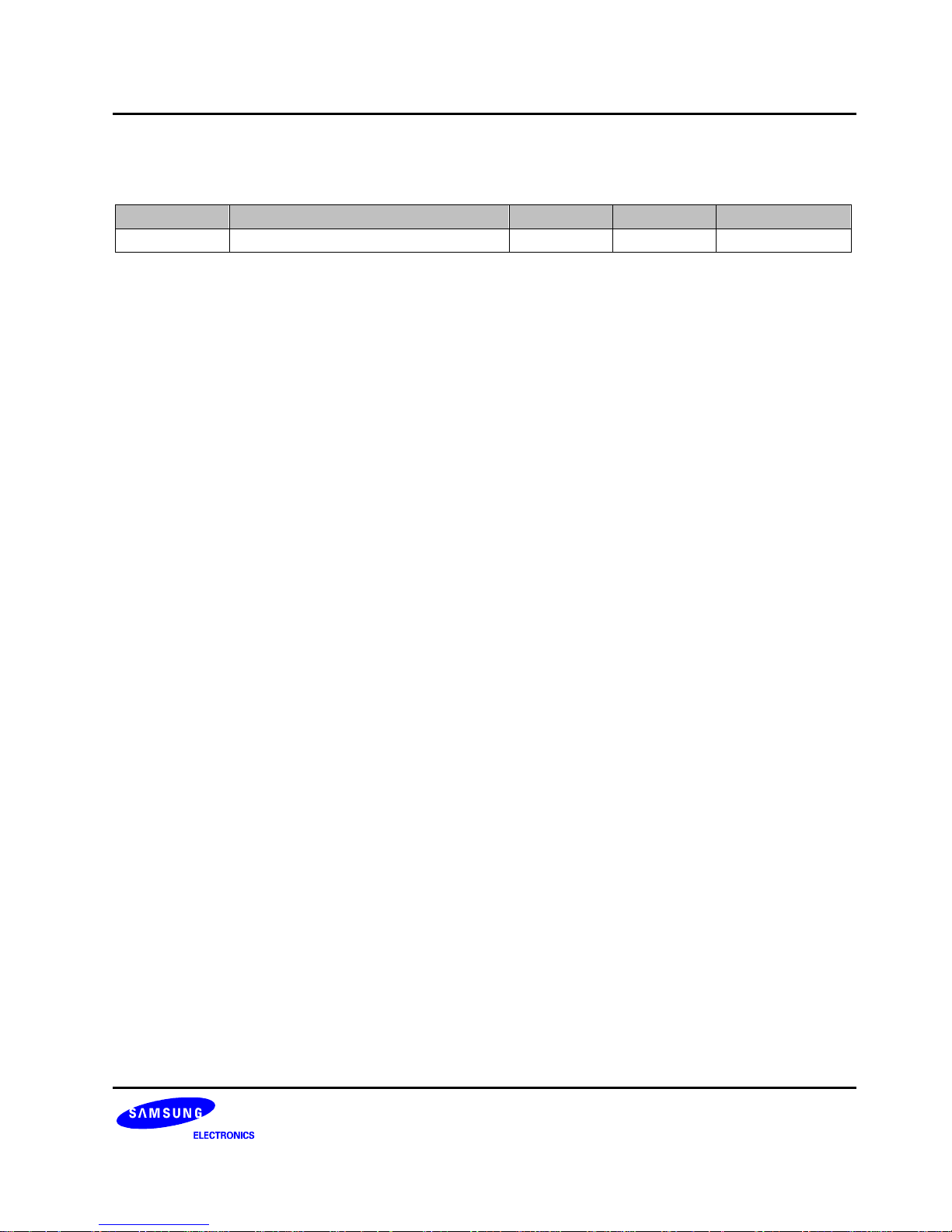

Revision History

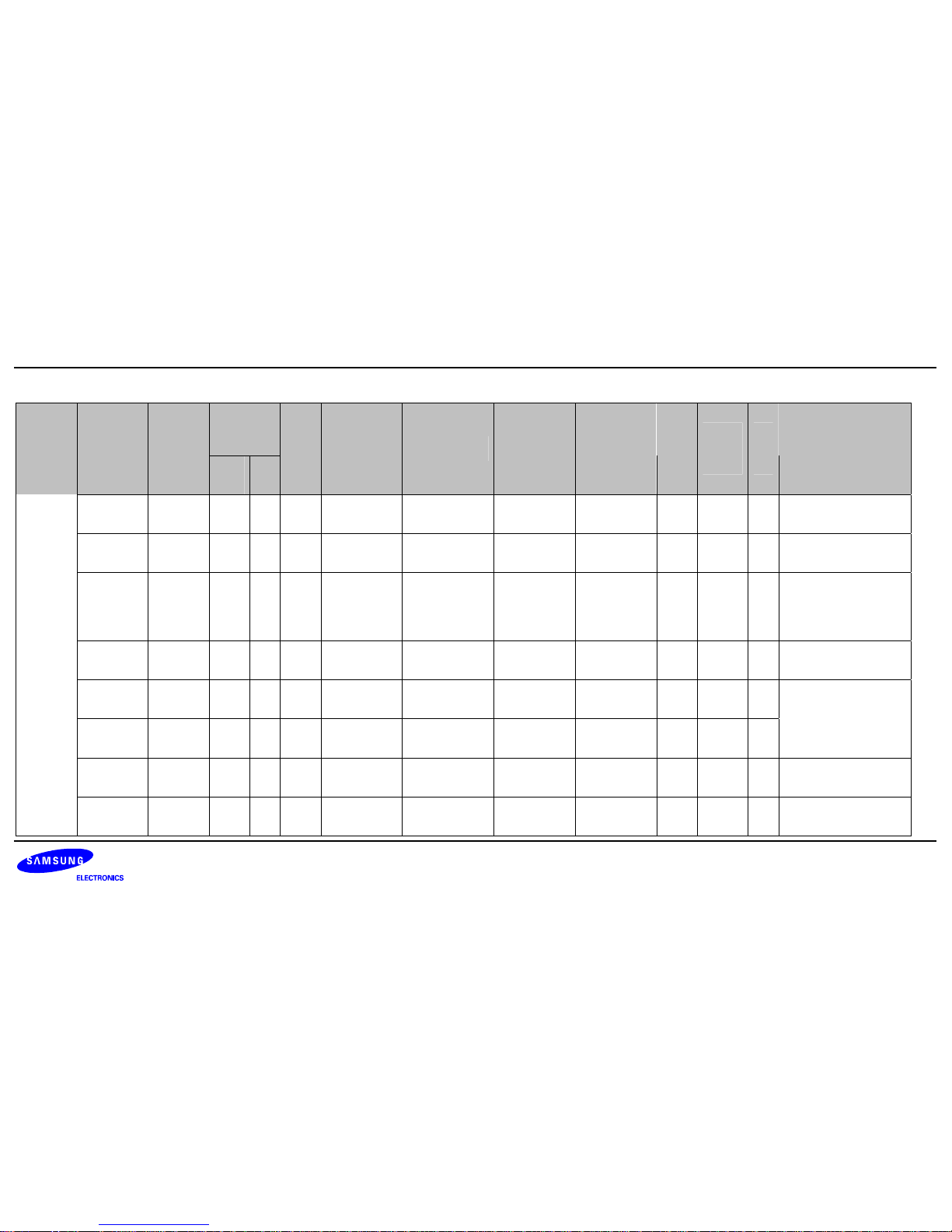

Revision No Description of Change Refer to Author(s) Date

1.0 - First release version Feb 08, 2010

S5PV210_HARDWARE DESING GUIDE REV 1.0

5

Table of Contents

1. OVERVIEW...............................................................................................................................................8

1.1. S5PV210 Pin Information...........................................................................................................................8

2. BALL NUMBER ASSIGNMENT .............................................................................................................63

3. POWER................................................................................................................................................... 71

3.1. Pin Power Domain....................................................................................................................................71

3.2. Recommend Operating Conditions........................................................................................................73

3.3. Circuit design without level shifter........................................................................................................75

3.4. Power On/Off Sequence..........................................................................................................................76

3.5. Pin configuration guide in Sleep mode .................................................................................................78

4. SYSCON.................................................................................................................................................79

4.1. Signal Description....................................................................................................................................79

4.2. Booting Option .........................................................................................................................................81

4.3. Feature of the IROM Boot mode .............................................................................................................82

4.4. Clock..........................................................................................................................................................83

5. MEMORY SUBSYSTEM.........................................................................................................................85

5.1. Signal Description....................................................................................................................................85

5.2. TQ : Temperature Indicator..................................................................................................................... 85

5.3. PCB LAYOUT GUIDELINES FOR MEMORY...........................................................................................85

6. SROM CONTROLLER............................................................................................................................88

6.1. Signal Description....................................................................................................................................88

6.2. SRAM/ROM Interface Examples ............................................................................................................. 89

7. ONENAND CONTROLLER.....................................................................................................................90

7.1. Signal Description....................................................................................................................................90

7.2. Circuit Diagram Example.........................................................................................................................91

8. NAND FLASH CONTROLLER ...............................................................................................................92

8.1. Signal Description....................................................................................................................................92

9. CF CONTROLLER..................................................................................................................................94

9.1. CFCON feature .........................................................................................................................................94

9.2. Signal Description....................................................................................................................................94

9.3. CF 1-slot operation guide........................................................................................................................95

9.4. CF 2-slot operation guide........................................................................................................................96

10. PWM TIMER........................................................................................................................................97

S5PV210_HARDWARE DESING GUIDE REV 1.0

6

10.1. Overview................................................................................................................................................ 97

10.2. Signal Description................................................................................................................................97

11. UART...................................................................................................................................................98

11.1. Signal descriptoin ................................................................................................................................98

12. IIC-BUS INTERFACE ..........................................................................................................................99

12.1. Pin Description .....................................................................................................................................99

12.2. Equation of the pull-up resistor value..............................................................................................100

13. SPI.....................................................................................................................................................101

13.1. Signal Description..............................................................................................................................101

13.2. EXTERNAL Loading Capacitance.....................................................................................................101

13.3. SPI Maximum Speed .......................................................................................................................... 101

14. USB HOST.........................................................................................................................................102

14.1. Singnal Description............................................................................................................................102

14.2. Power Domain..................................................................................................................................... 102

14.3. Circuit Diagram Example...................................................................................................................102

14.4. USB SIGNAL ROUTING......................................................................................................................103

15. USB 2.0 HS OTG...............................................................................................................................105

15.1. Signal Descriptoin..............................................................................................................................105

15.2. Power Domain..................................................................................................................................... 105

16. MODEM INTERFACE........................................................................................................................107

16.1. Signal Description..............................................................................................................................107

16.2. Pin Connection Example ...................................................................................................................107

17. SD/MMC HOST CONTROLLER........................................................................................................109

17.1. Signal Description..............................................................................................................................109

17.2. Muxed Signal usage...........................................................................................................................109

18. TSI .....................................................................................................................................................111

18.1. Signal Description..............................................................................................................................111

18.2. Connection Example..........................................................................................................................111

19. DISPLAY CONTROLLER..................................................................................................................112

19.1. Signal Description..............................................................................................................................112

19.2. VD signal connection.........................................................................................................................113

19.3. VD signal connection at each bpp mode......................................................................................... 114

20. CAMERA INTERFACE......................................................................................................................116

20.1. Signal Description..............................................................................................................................116

20.2. Camera INPUT..................................................................................................................................... 117

S5PV210_HARDWARE DESING GUIDE REV 1.0

7

20.3. Restriction...........................................................................................................................................117

21. MIPI DSI & CSI..................................................................................................................................118

21.1. Signal Description..............................................................................................................................118

21.2. Design Guide.......................................................................................................................................119

22. TV ENCODER....................................................................................................................................120

22.1. Signal Description..............................................................................................................................120

23. HDMI..................................................................................................................................................121

23.1. Overview.............................................................................................................................................. 121

23.2. Signal Description..............................................................................................................................121

23.3. Circuit Diagram Example...................................................................................................................122

23.4. PCB Artwork Guide............................................................................................................................ 124

24. IIS MULTI AUDIO INTERFACE (V5.1)..............................................................................................126

24.1. Signal Description..............................................................................................................................126

24.2. Audio Port ...........................................................................................................................................126

25. IIS BUS CONTROLLER ....................................................................................................................128

25.1. Signal Description..............................................................................................................................128

25.2. External Clock Source .......................................................................................................................128

25.3. Connection Example..........................................................................................................................129

26. AC97 CONTROLLER........................................................................................................................130

26.1. AC97 Signal Description....................................................................................................................130

26.2. Audio Ports .........................................................................................................................................130

26.3. Connection Example..........................................................................................................................130

27. PCM BUS CONTROLLER.................................................................................................................131

27.1. Signal Description..............................................................................................................................131

27.2. External Clock Source .......................................................................................................................132

27.3. Connection Example..........................................................................................................................132

28. SPDIF ................................................................................................................................................134

28.1. Signal Description..............................................................................................................................134

29. ADC&TOUCH SCREEN INTERFACE...............................................................................................135

30. KEYPAD INTERFACE.......................................................................................................................136

S5PV210_HARDWARE DESING GUIDE REV 1.0

8

1. Overview

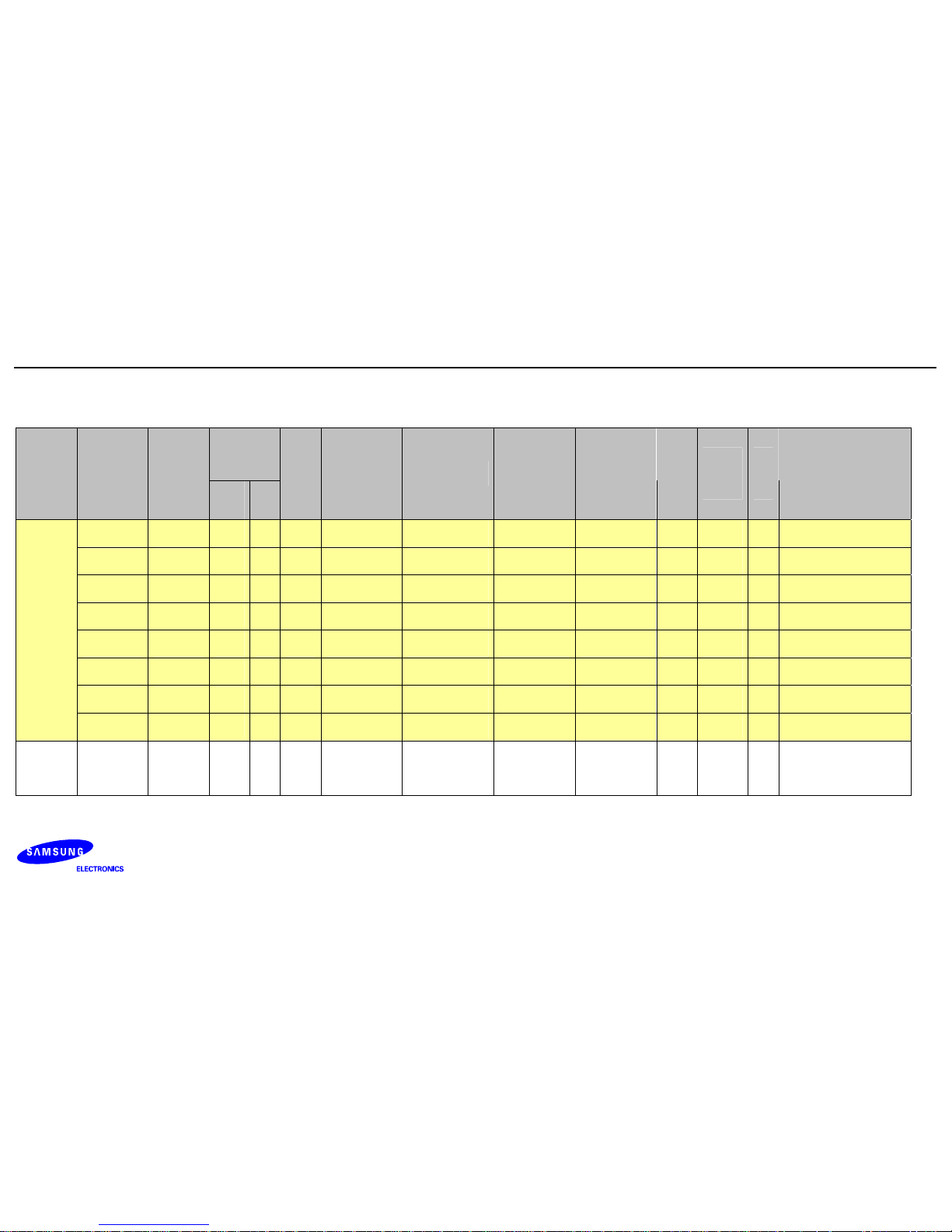

1.1. S5PV210 Pin Information

Definitions

Available Usage(AU)

- G/E/W : GPIO & EINT & Wake up source

- G/E : GPIO & EINT

- G : GPIO

- D : Dedicated signal

- I : Internally connected to MCP and ball out

- I(x) : Internally connected to MCP and No ball out

RET @ Power down

- No_Ret: this signal doesn’t have a retention function in power down mode

- Ret_IO : this signal has a retention function in power down mode and released by setting Enable_GPIO bit

(others[31])

- Ret_IO (sleep) : this signal has a retention function in only sleep mode and released by setting Enable_GPIO bit

(others[31])

- Ret_CF : this signal has a retention function in power down mode and released by setting Enable_CF_IO bit

(others[30])

- Ret_MMC : this signal has a retention function in power down mode and released by setting Enable_ MMC_IO

bit (others[29])

- Ret_UART : this signal has a retention function in power down mode and released by setting

Enable_GPIO_UART_IO bit (others[28]) => Only Uart2, 3

- Ret_Auto : this signal has a retention in power down mode and released automatically after wakeup.

note) Need to more attention when this kinds of signals are used for GPIO,.

Because these signals move to default signal level after wakeup until S/W set to the level.

S5PV210_HARDWARE DESING GUIDE REV 1.0

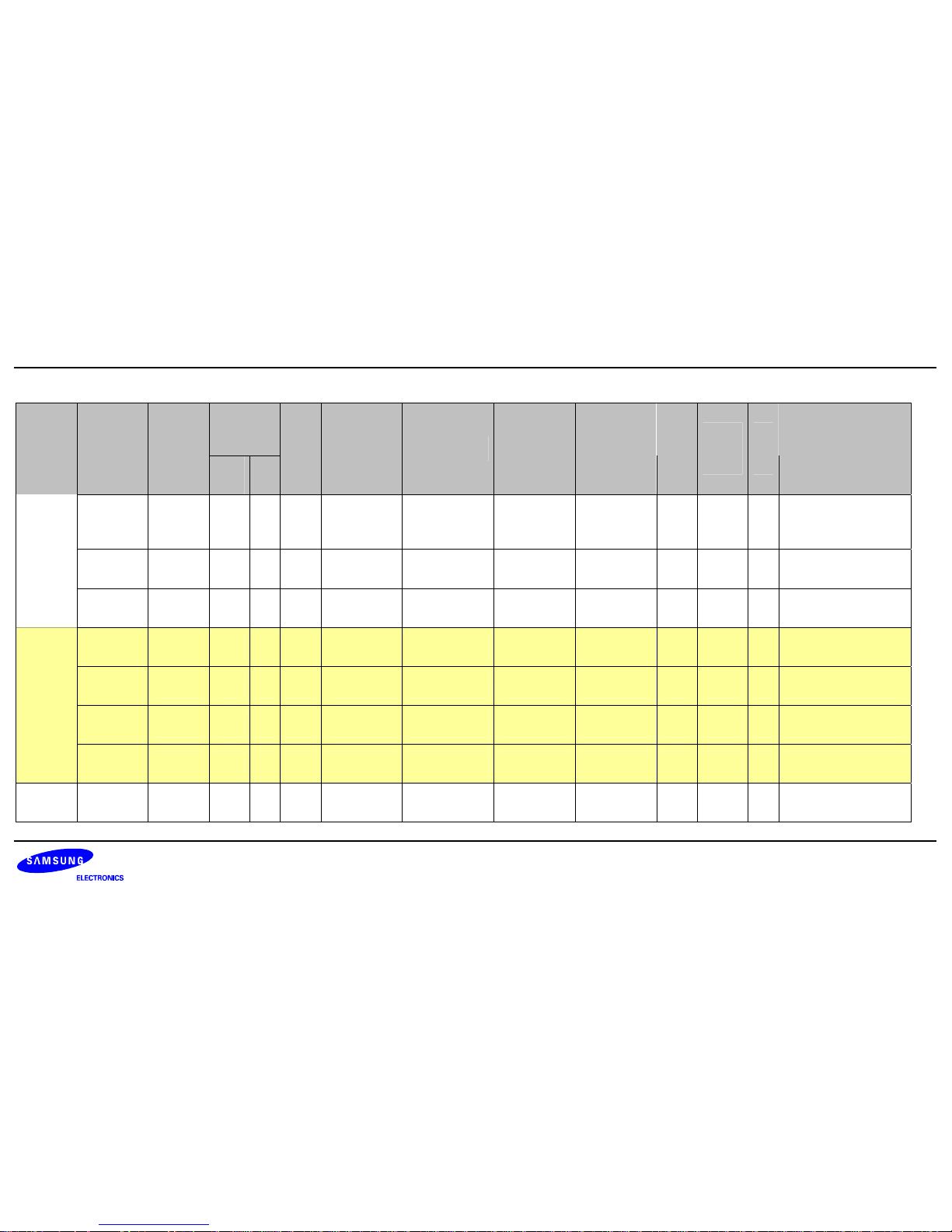

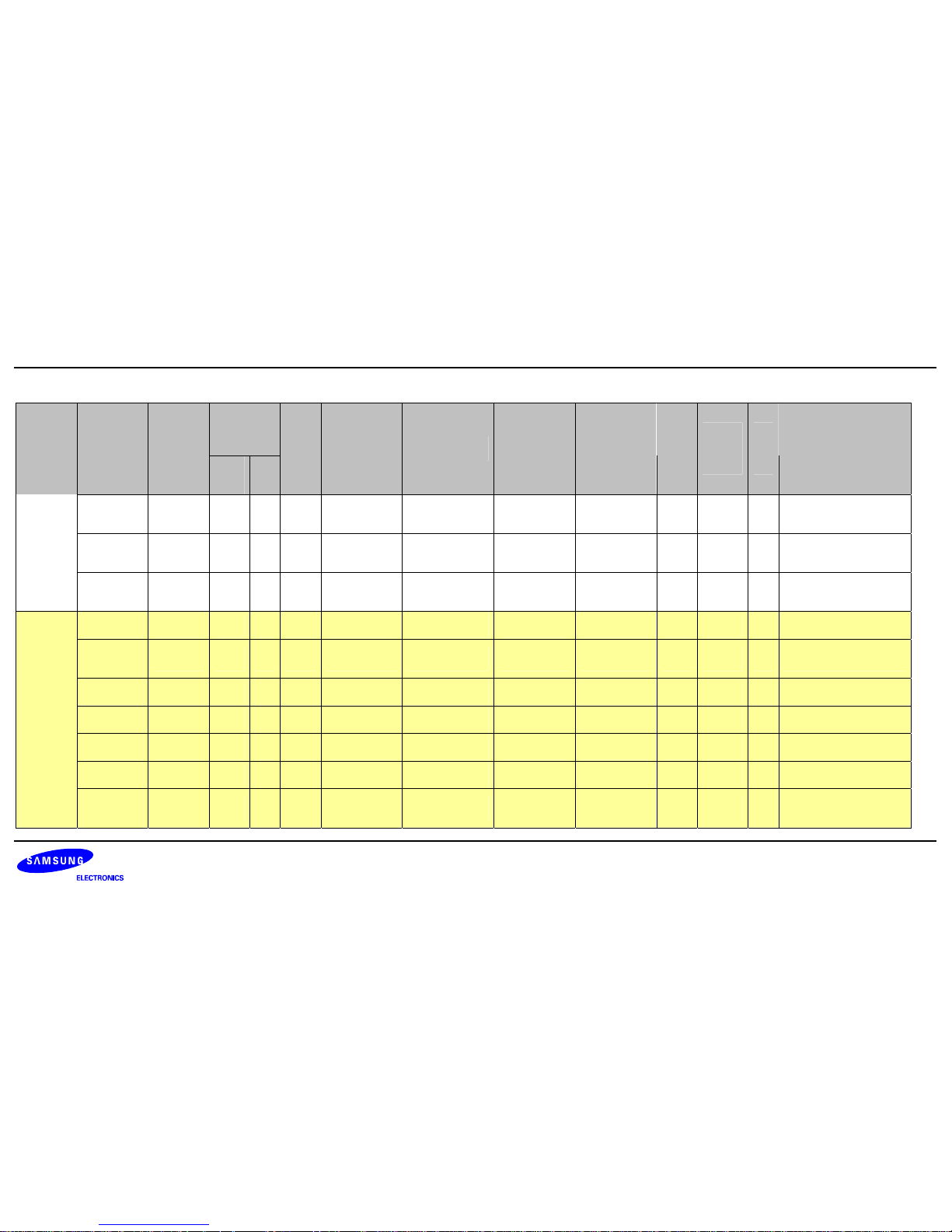

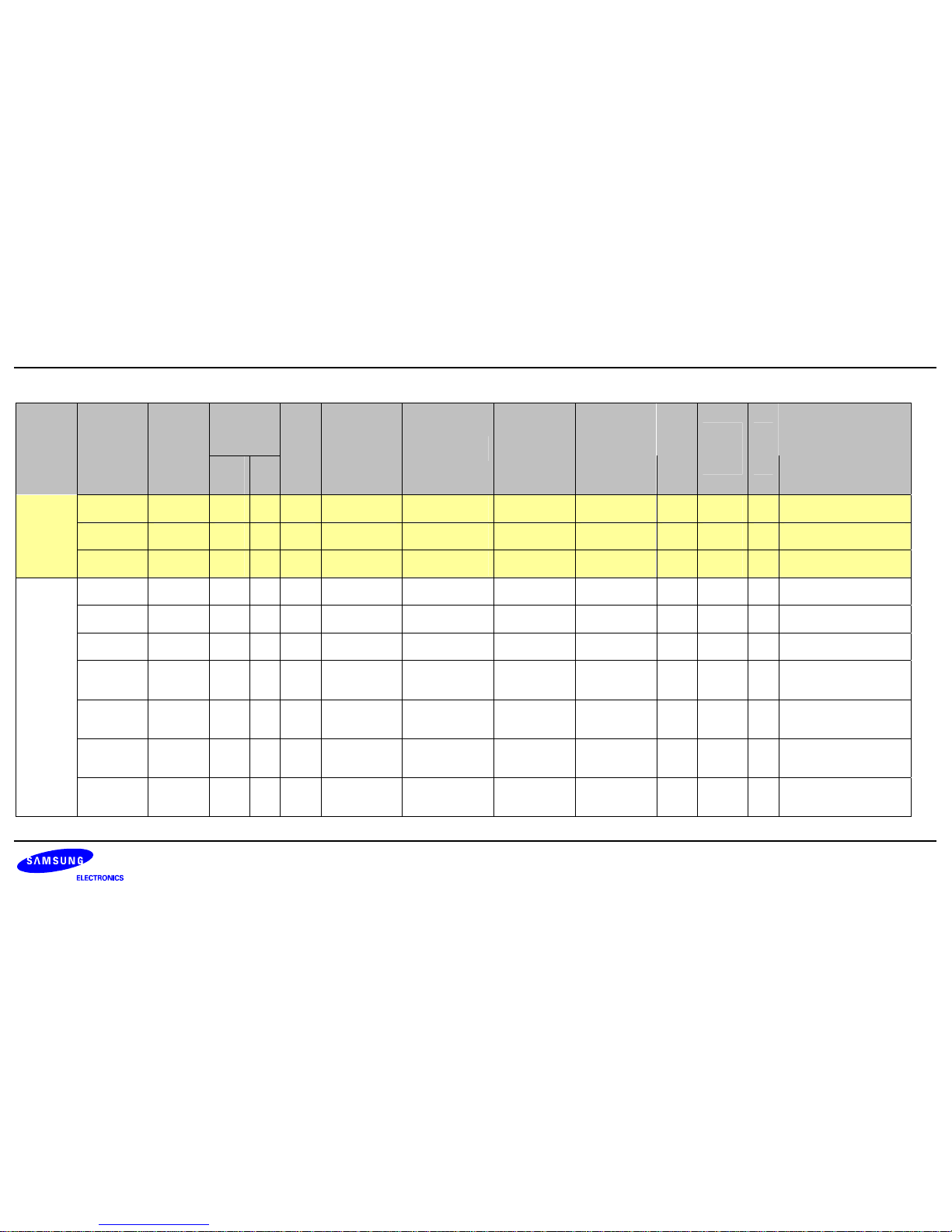

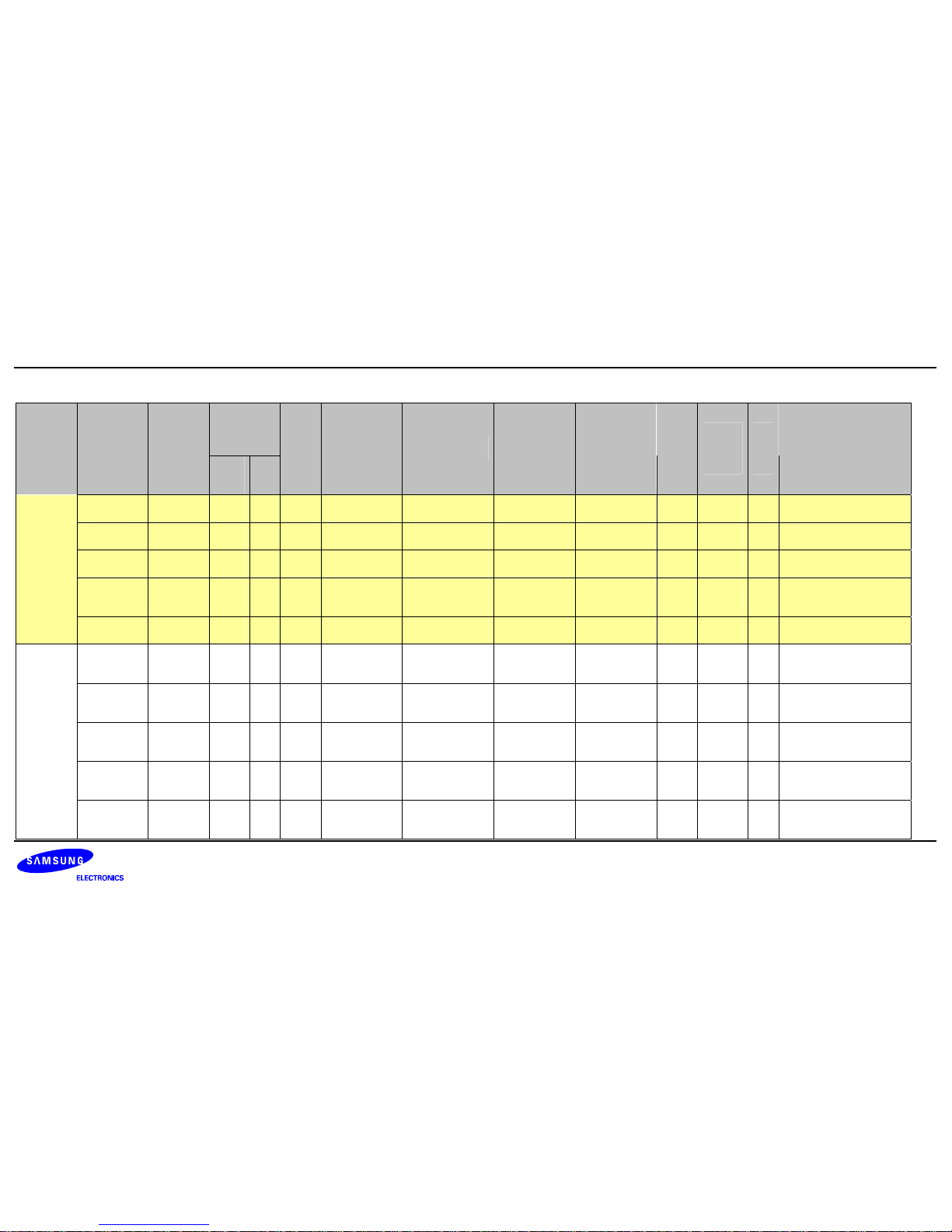

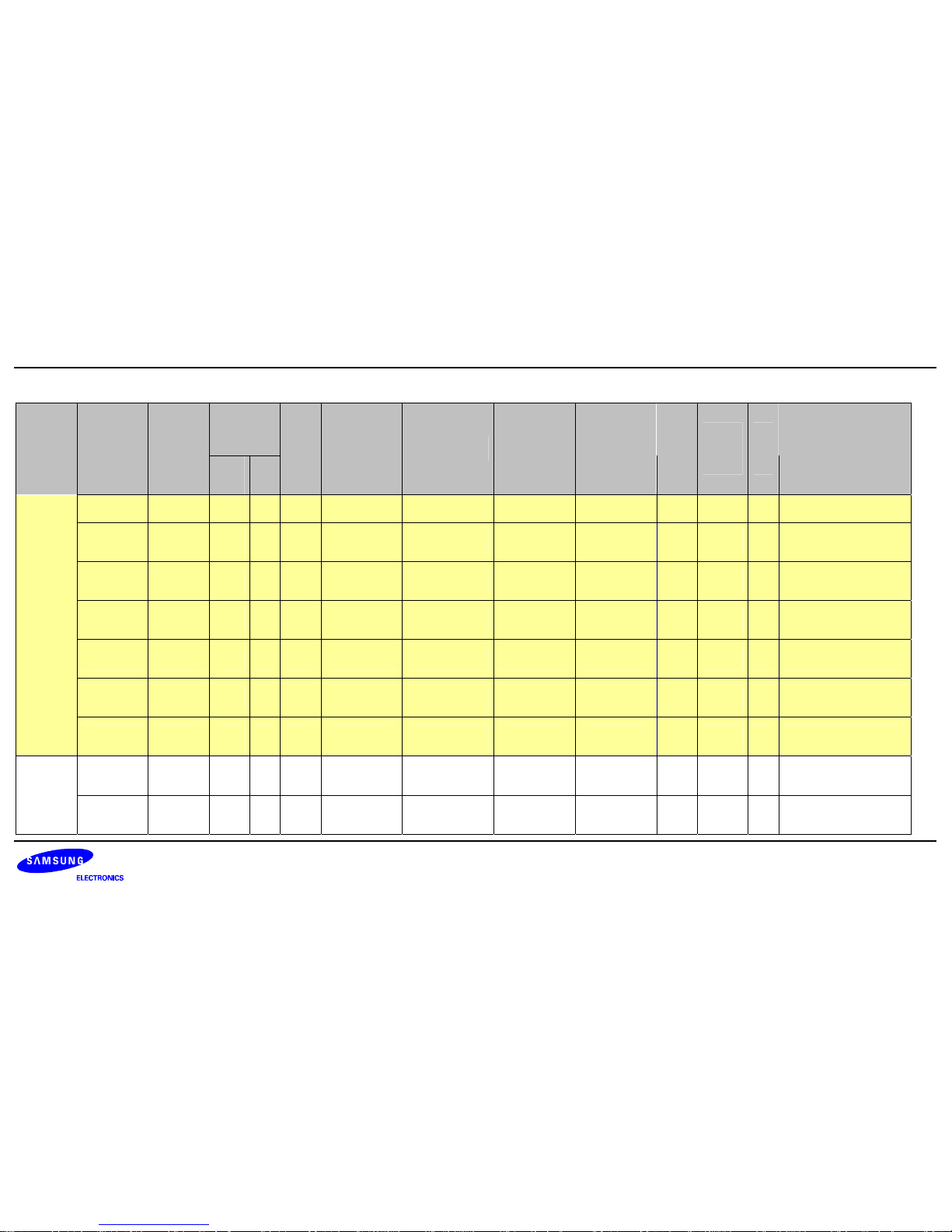

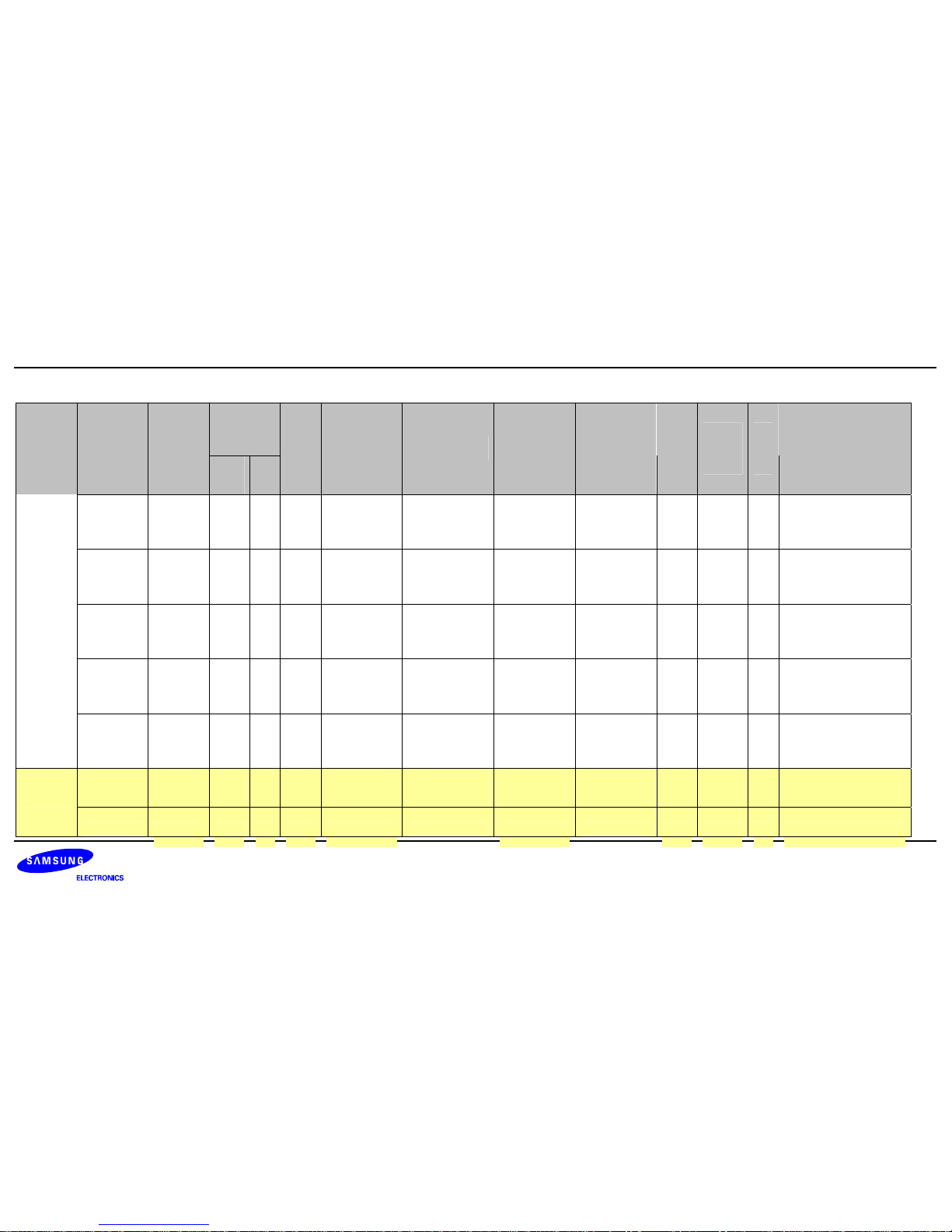

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XuRXD[0] GPA0[0] GPI PD I(L) UART_0_RXD

G/E Ret_IO NC

XuTXD[0] GPA0[1] GPI PD I(L) UART_0_TXD

G/E Ret_IO NC

XuCTSn[0] GPA0[2] GPI PD I(L) UART_0_CTSn

G/E Ret_IO NC

XuRTSn[0] GPA0[3] GPI PD I(L) UART_0_RTSn

G/E Ret_IO NC

XuRXD[1] GPA0[4] GPI PD I(L) UART_1_RXD

G/E Ret_IO NC

XuTXD[1] GPA0[5] GPI PD I(L) UART_1_TXD

G/E Ret_IO NC

XuCTSn[1] GPA0[6] GPI PD I(L) UART_1_CTSn

G/E Ret_IO NC

VDD_EXT0

XuRTSn[1] GPA0[7] GPI PD I(L) UART_1_RTSn

G/E Ret_IO NC

VDD_EXT1

XuRXD[2] GPA1[0] GPI PD I(L) UART_2_RXD

UART_AUDIO_

RXD

G/E

Ret_UA

RT

NC

for RP(Low Power

Audio)debugging

S5PV210_HARDWARE DESING GUIDE REV 1.0

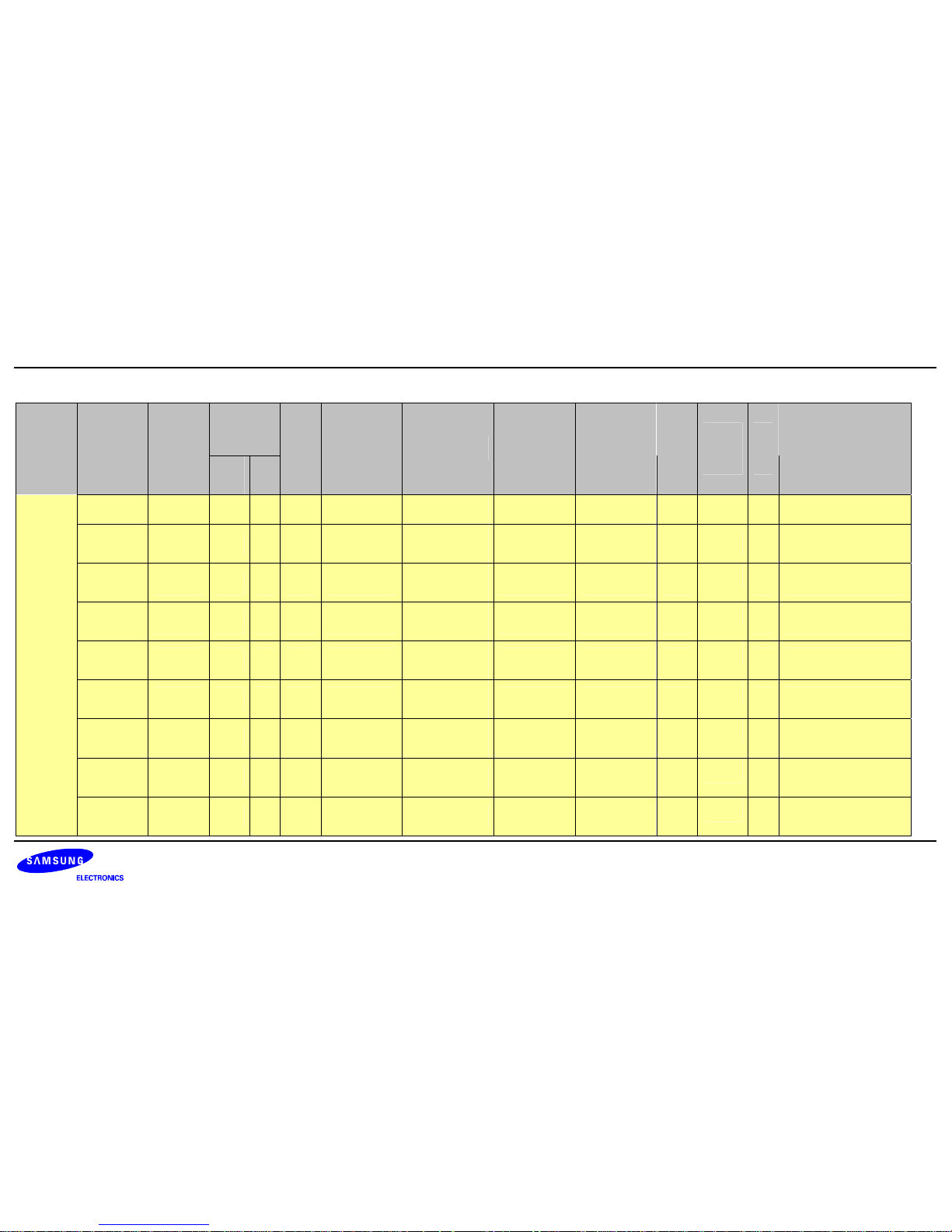

10

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

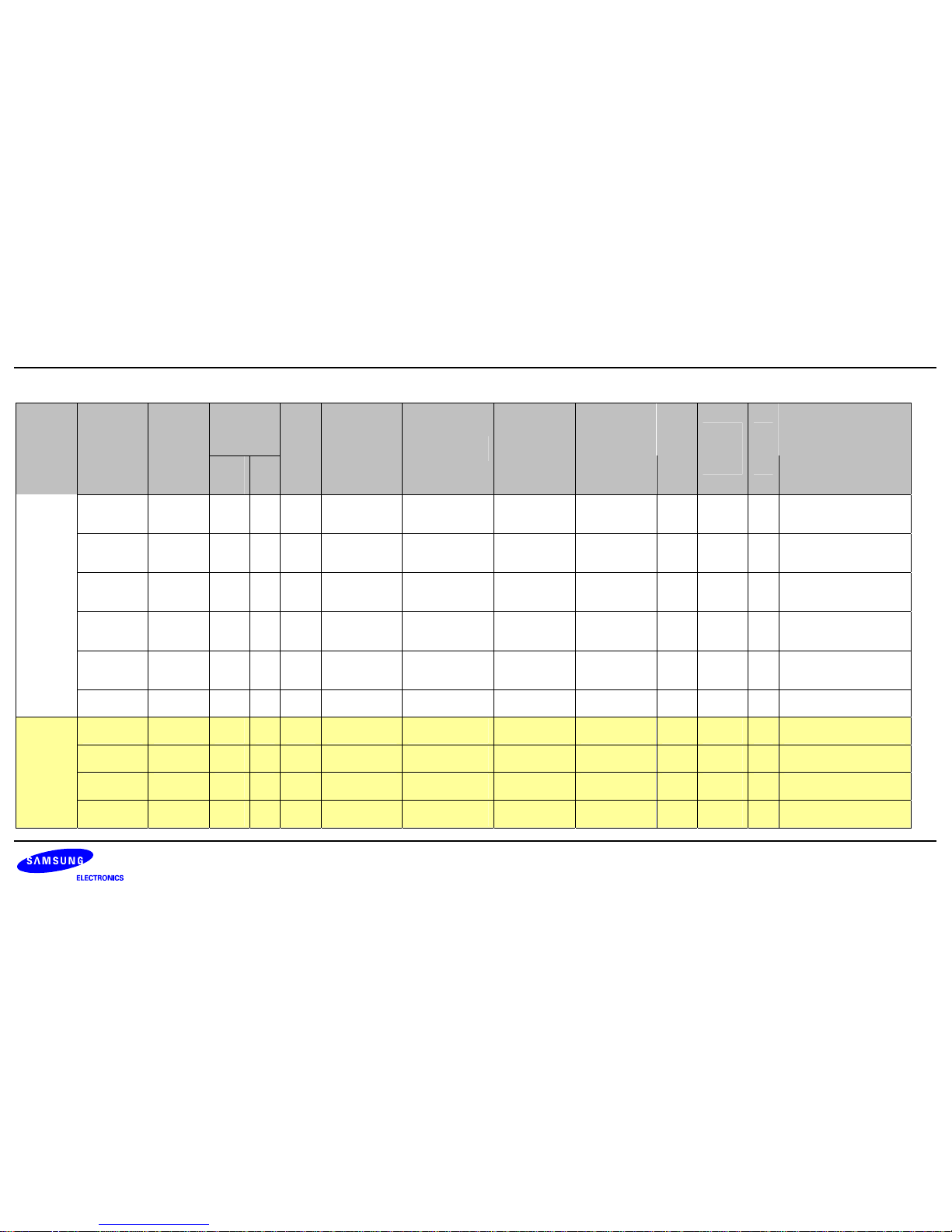

XuTXD[2] GPA1[1] GPI PD I(L) UART_2_TXD

UART_AUDIO_

TXD

G/E

Ret_UA

RT

NC

for RP(Low Power

Audio)debugging

XuRXD[3] GPA1[2] GPI PD I(L) UART_3_RXD UART_2_CTSn

G/E

Ret_UA

RT

NC

XuTXD[3] GPA1[3] GPI PD I(L) UART_3_TXD UART_2_RTSn

G/E

Ret_UA

RT

NC

XspiCLK[0

]

GPB[0] GPI PD I(L) SPI_0_CLK

G/E Ret_IO NC

XspiCSn[0

]

GPB[1] GPI PD I(L) SPI_0_nSS

G/E Ret_IO NC

XspiMISO[

0]

GPB[2] GPI PD I(L) SPI_0_MISO

G/E Ret_IO NC

VDD_EXT0

XspiMOSI[

0]

GPB[3] GPI PD I(L) SPI_0_MOSI

G/E Ret_IO NC

VDD_EXT2

XspiCLK[1

]

GPB[4] GPI PD I(L) SPI_1_CLK

G/E Ret_IO NC

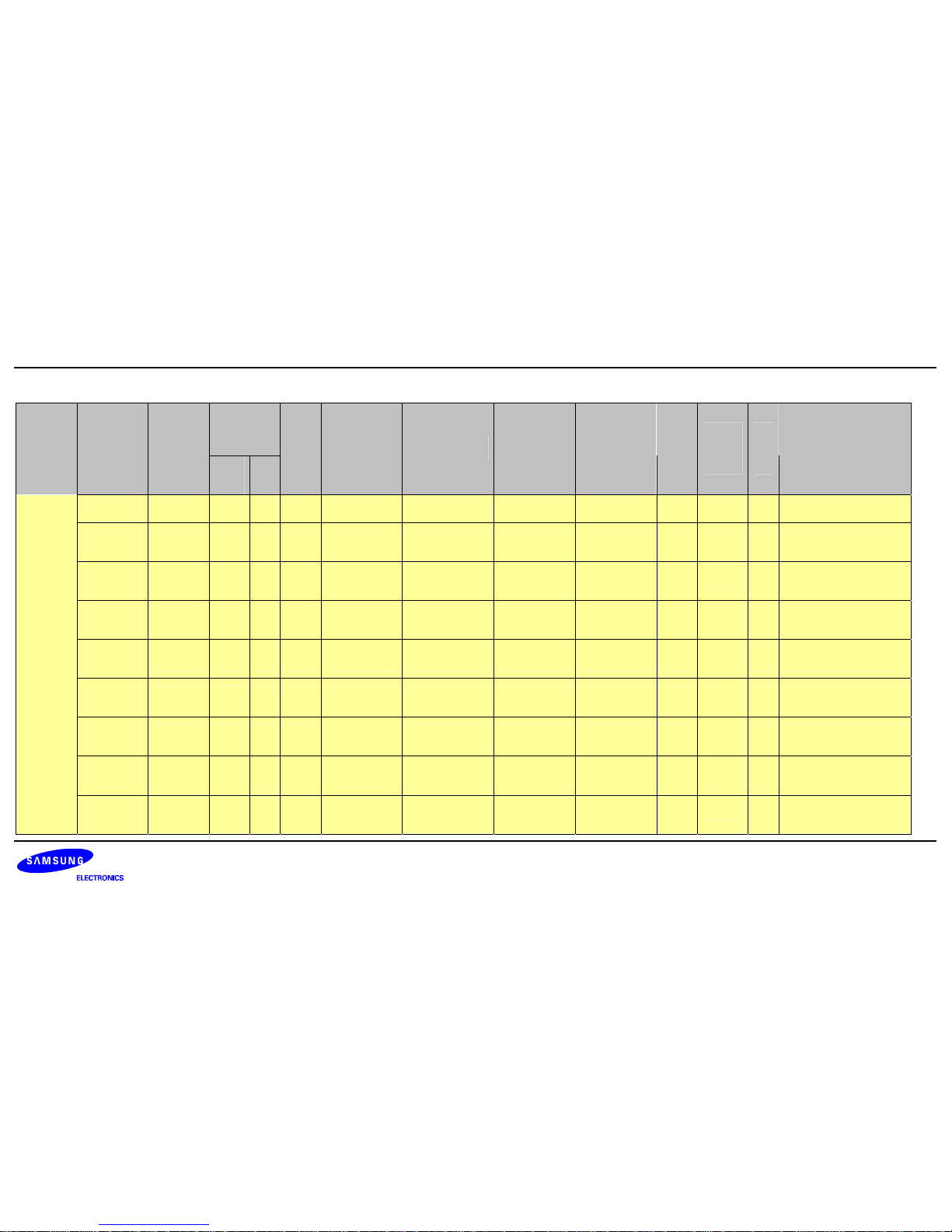

S5PV210_HARDWARE DESING GUIDE REV 1.0

11

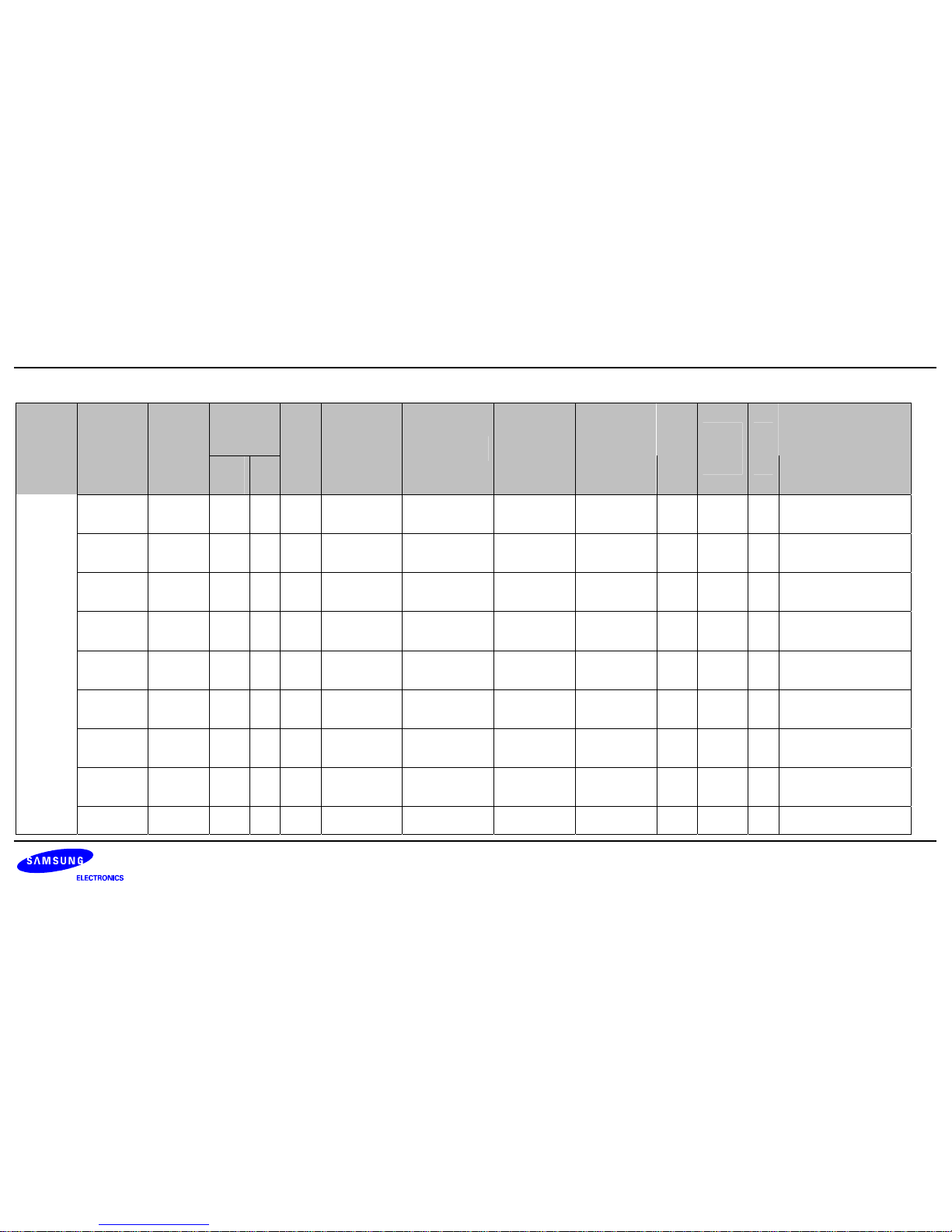

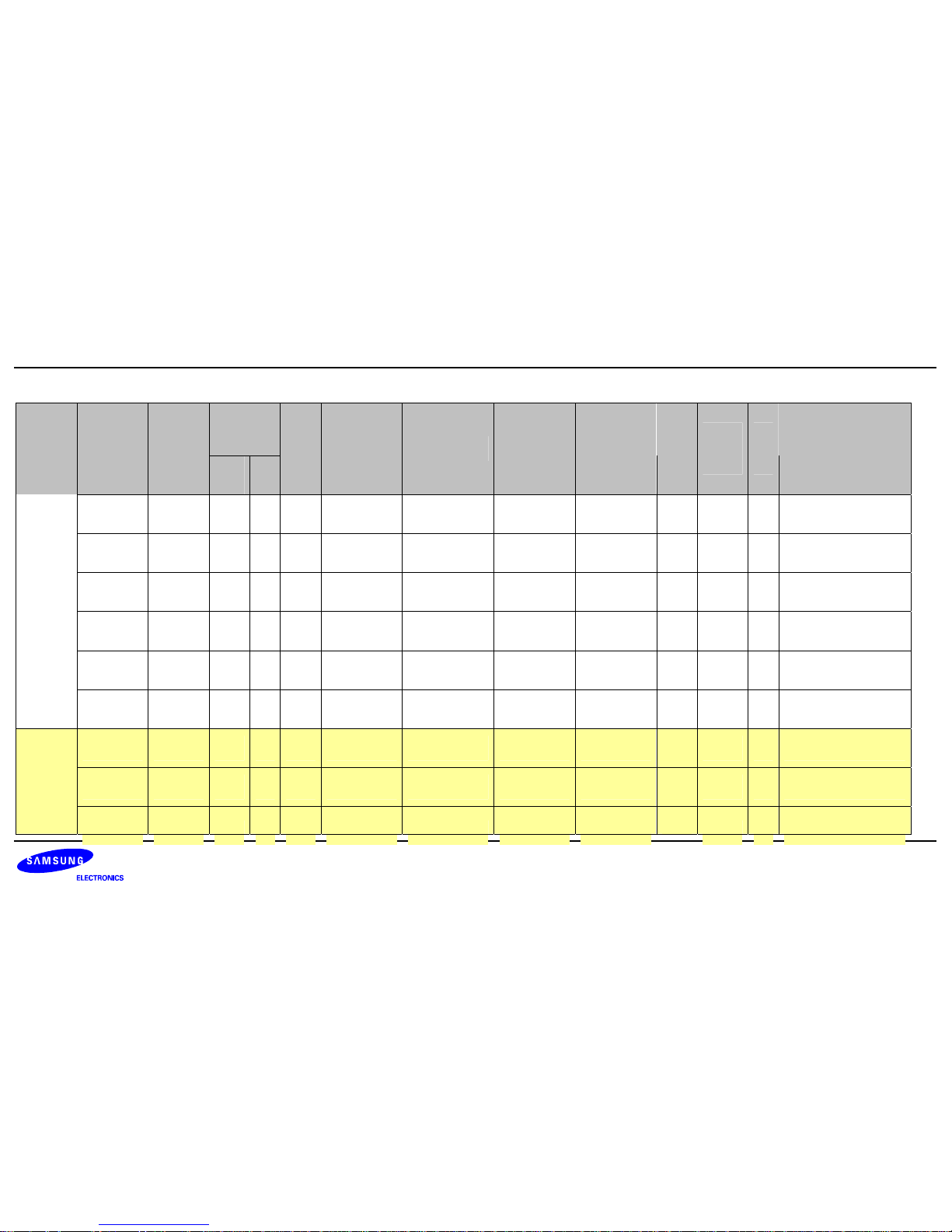

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XspiCSn[1

]

GPB[5] GPI PD I(L) SPI_1_nSS

G/E Ret_IO NC

XspiMISO[

1]

GPB[6] GPI PD I(L) SPI_1_MISO

G/E Ret_IO NC

XspiMOSI[

1]

GPB[7] GPI PD I(L) SPI_1_MOSI

G/E Ret_IO NC

Xi2s1SCLK GPC0[0] GPI PD I(L) I2S_1_SCLK PCM_1_SCLK AC97BITCLK

G/E Ret_IO NC

Xi2s1CDCL

K

GPC0[1] GPI PD I(L) I2S_1_CDCLK PCM_1_EXTCLK AC97RESETn

G/E Ret_IO NC

Xi2s1LRCK GPC0[2] GPI PD I(L) I2S_1_LRCK PCM_1_FSYNC AC97SYNC

G/E Ret_IO NC

Xi2s1SDI GPC0[3] GPI PD I(L) I2S_1_SDI PCM_1_SIN AC97SDI

G/E Ret_IO NC

Xi2s1SDO GPC0[4] GPI PD I(L) I2S_1_SDO PCM_1_SOUT AC97SDO

G/E Ret_IO NC

Xpcm2SCLK GPC1[0] GPI PD I(L) PCM_2_SCLK SPDIF_0_OUT I2S_2_SCLK

G/E Ret_IO NC

VDD_AUD

Xpcm2EXTC

LK

GPC1[1] GPI PD I(L)

PCM_2_EXTCL

K

SPDIF_EXTCLK I2S_2_CDCLK

G/E Ret_IO NC

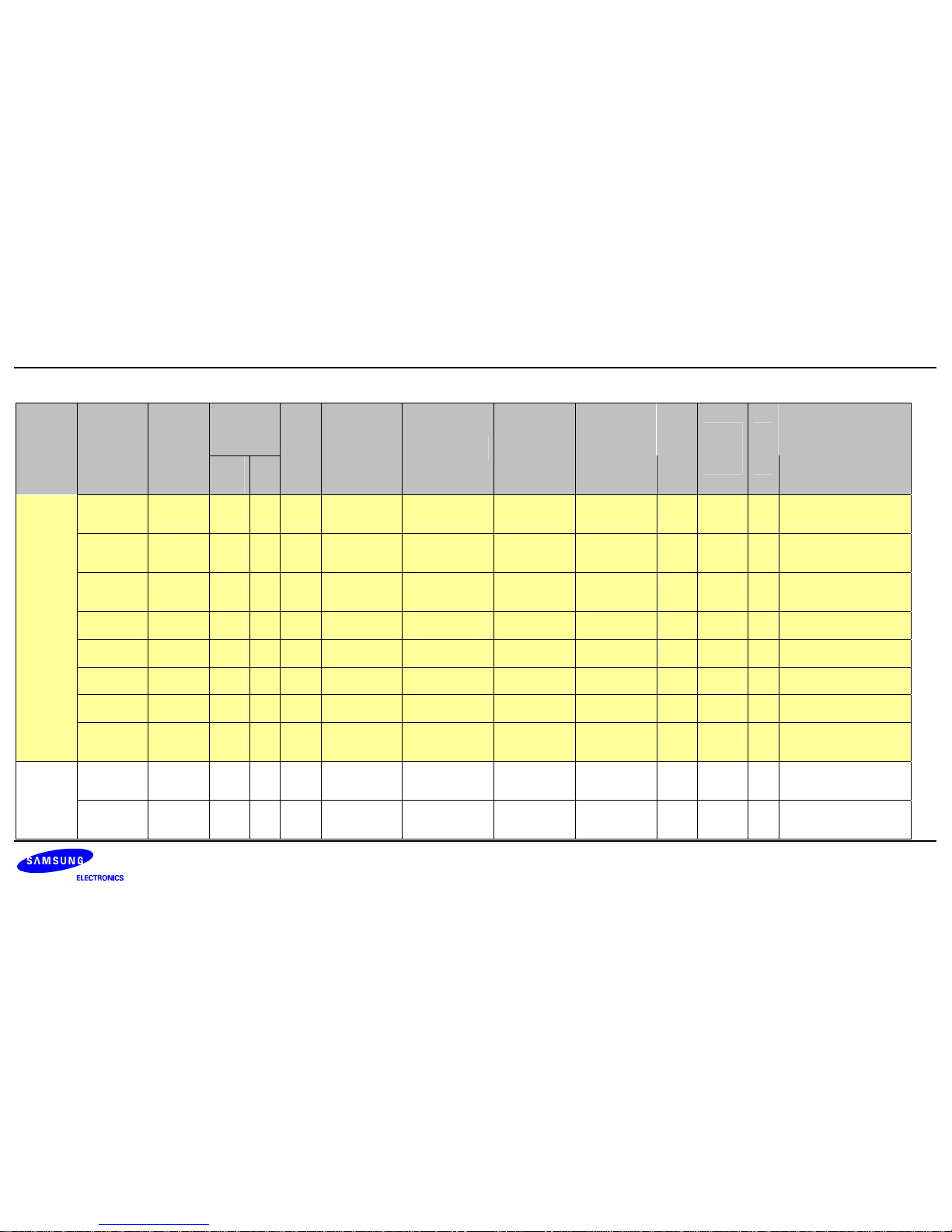

S5PV210_HARDWARE DESING GUIDE REV 1.0

12

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

Xpcm2FSYN

C

GPC1[2] GPI PD I(L) PCM_2_FSYNC LCD_FRM I2S_2_LRCK

G/E Ret_IO NC

Xpcm2SIN GPC1[3] GPI PD I(L) PCM_2_SIN I2S_2_SDI

G/E Ret_IO NC

Xpcm2SOUT GPC1[4] GPI PD I(L) PCM_2_SOUT I2S_2_SDO

G/E Ret_IO NC

XpwmTOUT[

0]

GPD0[0] GPI PD I(L) TOUT_0

G/E Ret_IO NC

XpwmTOUT[

1]

GPD0[1] GPI PD I(L) TOUT_1

G/E Ret_IO NC

XpwmTOUT[

2]

GPD0[2] GPI PD I(L) TOUT_2

G/E Ret_IO NC

XpwmTOUT[

3]

GPD0[3] GPI PD I(L) TOUT_3

PWM_MIE/PWM_M

DNIE

G/E Ret_IO NC MIE PWM control

Xi2c0SDA GPD1[0] GPI PD I(L) I2C0_SDA

G/E Ret_IO NC

VDD_EXT0

Xi2c0SCL GPD1[1] GPI PD I(L) I2C0_SCL

G/E Ret_IO NC

VDD_EXT1

Xi2c1SDA GPD1[2] GPI PD I(L) I2C1_SDA

G/E Ret_IO NC For HDMI

S5PV210_HARDWARE DESING GUIDE REV 1.0

13

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

Xi2c1SCL GPD1[3] GPI PD I(L) I2C1_SCL

G/E Ret_IO NC For HDMI

Xi2c2SDA GPD1[4] GPI PD I(L) I2C2_SDA IEM_SCLK

G/E Ret_IO NC

Xi2c2SCL GPD1[5] GPI PD I(L) I2C2_SCL IEM_SPWI

G/E Ret_IO NC

XciPCLK GPE0[0] GPI PD I(L) CAM_A_PCLK

G/E Ret_IO NC

XciVSYNC GPE0[1] GPI PD I(L) CAM_A_VSYNC

G/E Ret_IO NC

XciHREF GPE0[2] GPI PD I(L) CAM_A_HREF

G/E Ret_IO NC

XciDATA[0

]

GPE0[3] GPI PD I(L)

CAM_A_DATA[

0]

G/E Ret_IO NC

XciDATA[1

]

GPE0[4] GPI PD I(L)

CAM_A_DATA[

1]

G/E Ret_IO NC

XciDATA[2

]

GPE0[5] GPI PD I(L)

CAM_A_DATA[

2]

G/E Ret_IO NC

VDD_CAM

XciDATA[3

]

GPE0[6] GPI PD I(L)

CAM_A_DATA[

3]

G/E Ret_IO NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

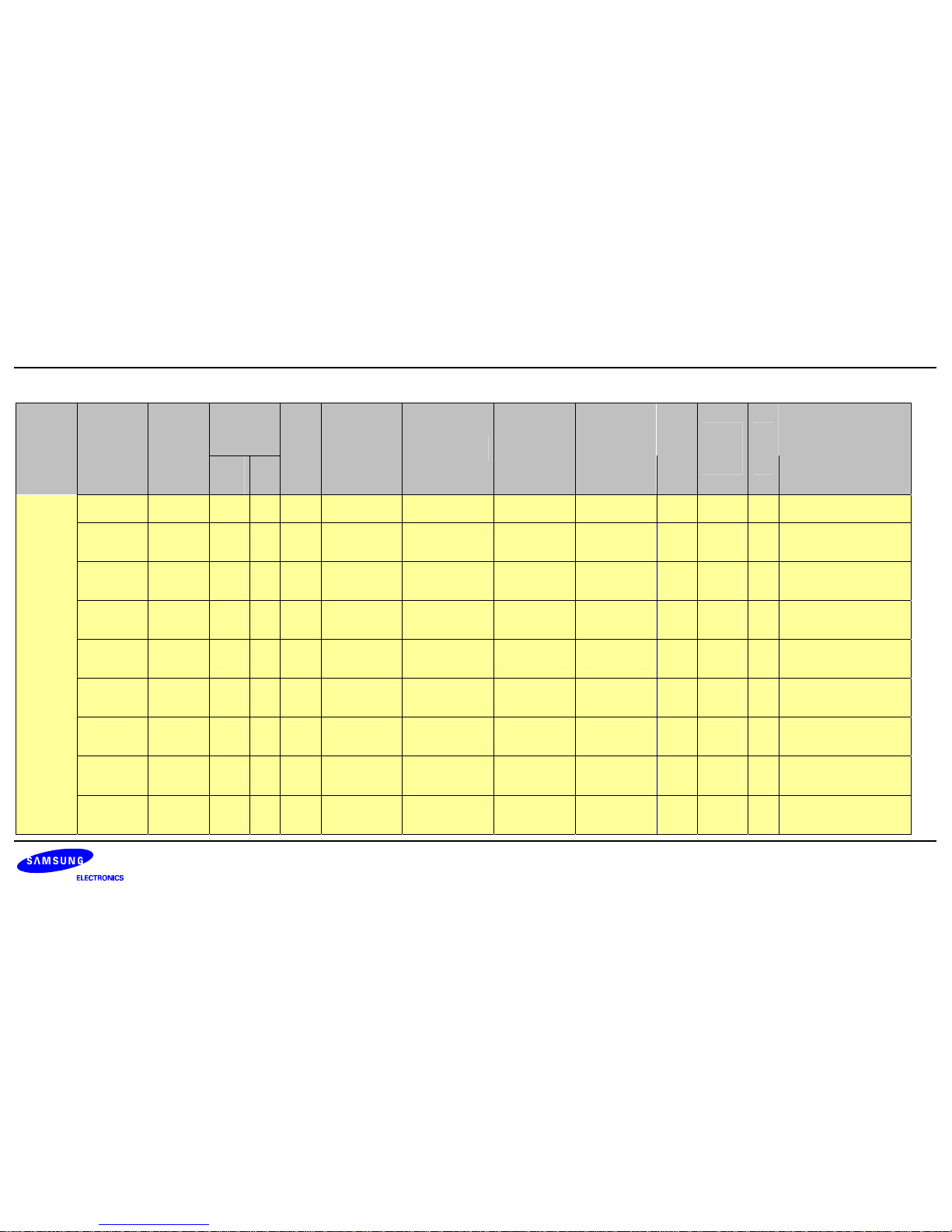

14

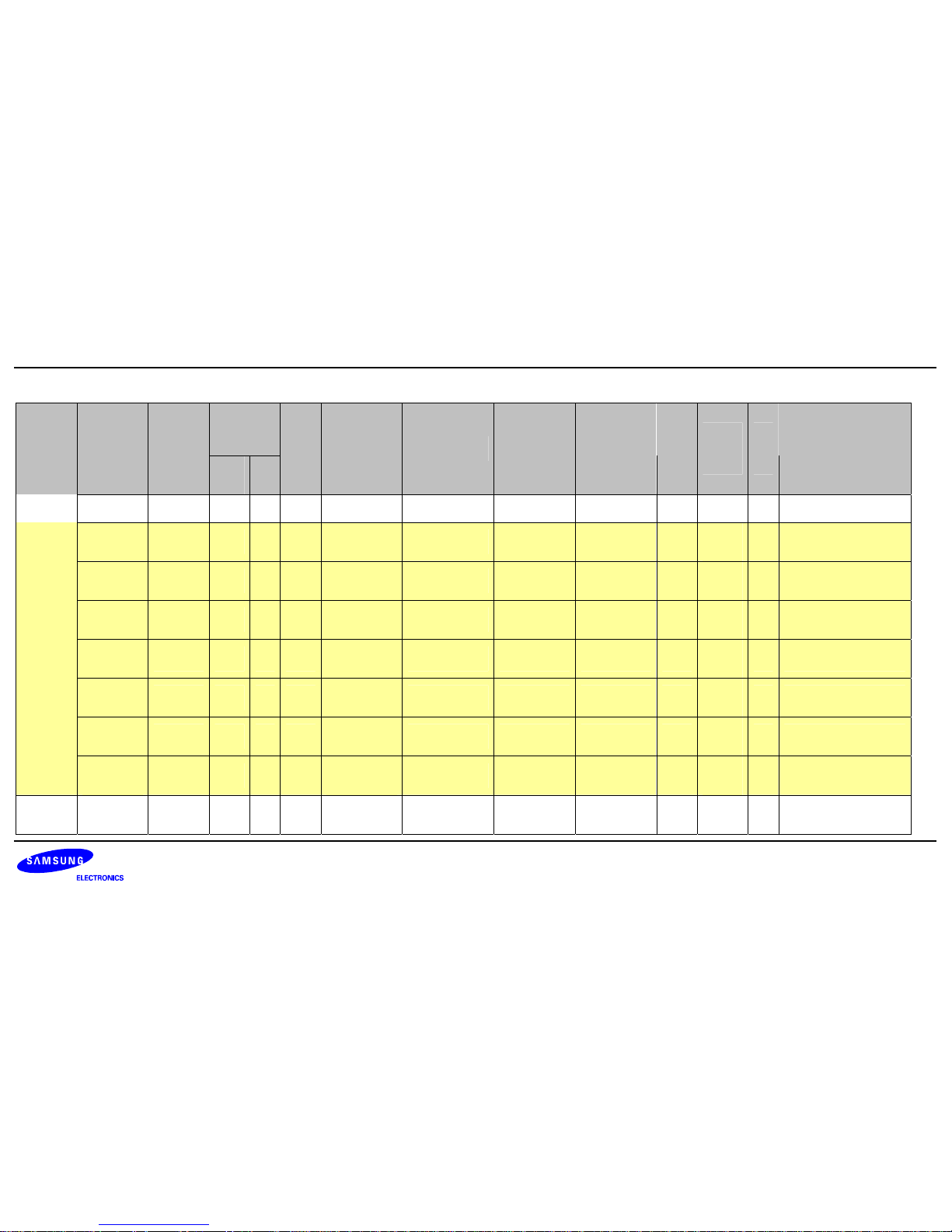

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XciDATA[4

]

GPE0[7] GPI PD I(L)

CAM_A_DATA[

4]

G/E Ret_IO NC

XciDATA[5

]

GPE1[0] GPI PD I(L)

CAM_A_DATA[

5]

G/E Ret_IO NC

XciDATA[6

]

GPE1[1] GPI PD I(L)

CAM_A_DATA[

6]

G/E Ret_IO NC

XciDATA[7

]

GPE1[2] GPI PD I(L)

CAM_A_DATA[

7]

G/E Ret_IO NC

XciCLKenb GPE1[3] GPI PD I(L)

CAM_A_CLKOU

T

G/E Ret_IO NC

XciFIELD GPE1[4] GPI PD I(L) CAM_A_FIELD

G/E Ret_IO NC

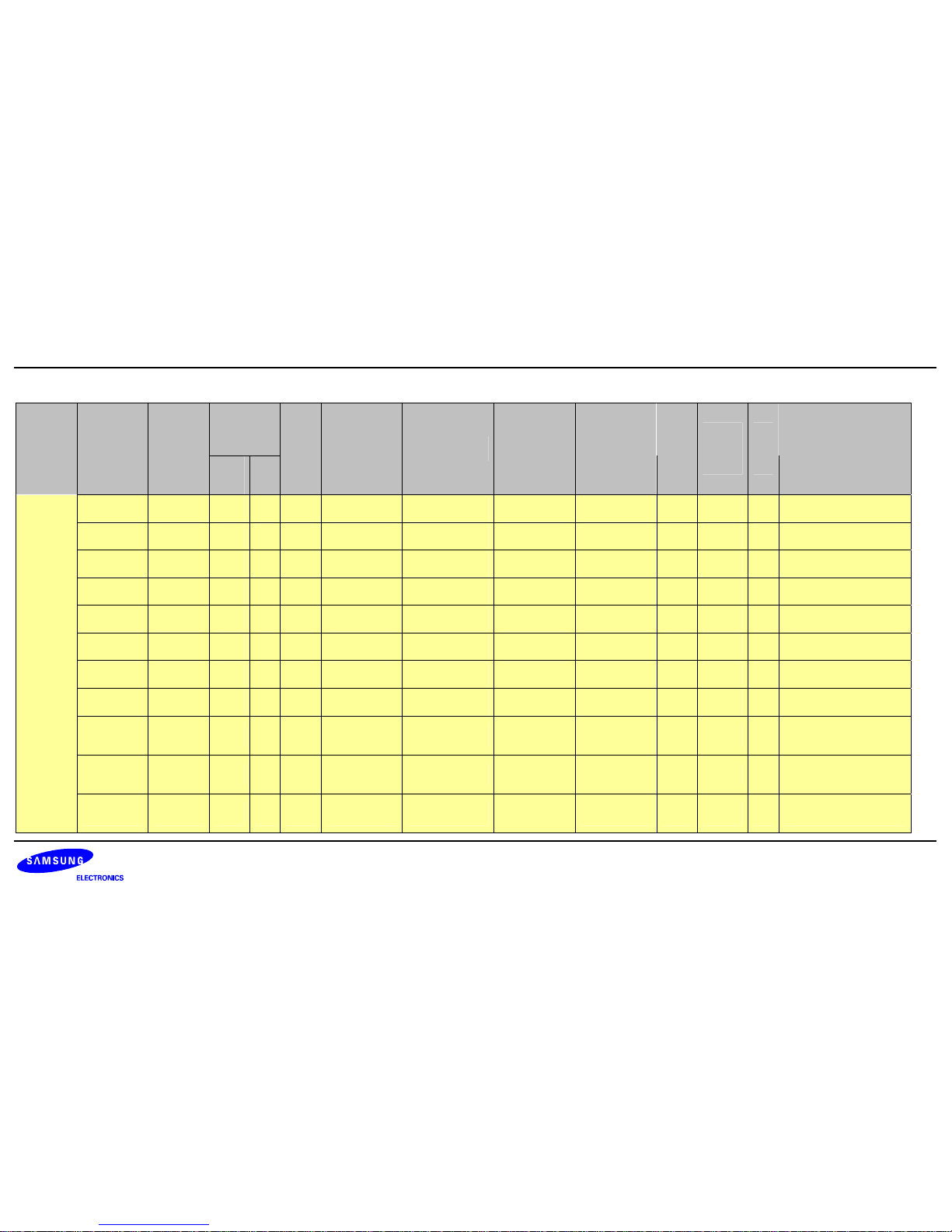

XvHSYNC GPF0[0] GPI PD I(L) LCD_HSYNC SYS_CS0 VEN_HSYNC

G/E Ret_IO NC

XvVSYNC GPF0[1] GPI PD I(L) LCD_VSYNC SYS_CS1 VEN_VSYNC

G/E Ret_IO NC

XvVDEN GPF0[2] GPI PD I(L) LCD_VDEN SYS_RS VEN_HREF

G/E Ret_IO NC

VDD_LCD

XvVCLK GPF0[3] GPI PD I(L) LCD_VCLK SYS_WE V601_CLK

G/E Ret_IO NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

15

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XvVD[0] GPF0[4] GPI PD I(L) LCD_VD[0] SYS_VD[0] VEN_DATA[0]

G/E Ret_IO NC

XvVD[1] GPF0[5] GPI PD I(L) LCD_VD[1] SYS_VD[1] VEN_DATA[1]

G/E Ret_IO NC

XvVD[2] GPF0[6] GPI PD I(L) LCD_VD[2] SYS_VD[2] VEN_DATA[2]

G/E Ret_IO NC

XvVD[3] GPF0[7] GPI PD I(L) LCD_VD[3] SYS_VD[3] VEN_DATA[3]

G/E Ret_IO NC

XvVD[4] GPF1[0] GPI PD I(L) LCD_VD[4] SYS_VD[4] VEN_DATA[4]

G/E Ret_IO NC

XvVD[5] GPF1[1] GPI PD I(L) LCD_VD[5] SYS_VD[5] VEN_DATA[5]

G/E Ret_IO NC

XvVD[6] GPF1[2] GPI PD I(L) LCD_VD[6] SYS_VD[6] VEN_DATA[6]

G/E Ret_IO NC

XvVD[7] GPF1[3] GPI PD I(L) LCD_VD[7] SYS_VD[7] VEN_DATA[7]

G/E Ret_IO NC

XvVD[8] GPF1[4] GPI PD I(L) LCD_VD[8] SYS_VD[8]

V656_DATA[0

]

G/E Ret_IO NC

XvVD[9] GPF1[5] GPI PD I(L) LCD_VD[9] SYS_VD[9]

V656_DATA[1

]

G/E Ret_IO NC

XvVD[10] GPF1[6] GPI PD I(L) LCD_VD[10] SYS_VD[10]

V656_DATA[2

]

G/E Ret_IO NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

16

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XvVD[11] GPF1[7] GPI PD I(L) LCD_VD[11] SYS_VD[11]

V656_DATA[3

]

G/E Ret_IO NC

XvVD[12] GPF2[0] GPI PD I(L) LCD_VD[12] SYS_VD[12]

V656_DATA[4

]

G/E Ret_IO NC

XvVD[13] GPF2[1] GPI PD I(L) LCD_VD[13] SYS_VD[13]

V656_DATA[5

]

G/E Ret_IO NC

XvVD[14] GPF2[2] GPI PD I(L) LCD_VD[14] SYS_VD[14]

V656_DATA[6

]

G/E Ret_IO NC

XvVD[15] GPF2[3] GPI PD I(L) LCD_VD[15] SYS_VD[15]

V656_DATA[7

]

G/E Ret_IO NC

XvVD[16] GPF2[4] GPI PD I(L) LCD_VD[16] SYS_VD[16]

G/E Ret_IO NC

XvVD[17] GPF2[5] GPI PD I(L) LCD_VD[17] SYS_VD[17]

G/E Ret_IO NC

XvVD[18] GPF2[6] GPI PD I(L) LCD_VD[18] SYS_VD[18]

G/E Ret_IO NC

XvVD[19] GPF2[7] GPI PD I(L) LCD_VD[19] SYS_VD[19]

G/E Ret_IO NC

XvVD[20] GPF3[0] GPI PD I(L) LCD_VD[20] SYS_VD[20]

G/E Ret_IO NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

17

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XvVD[21] GPF3[1] GPI PD I(L) LCD_VD[21] SYS_VD[21]

G/E Ret_IO NC

XvVD[22] GPF3[2] GPI PD I(L) LCD_VD[22] SYS_VD[22]

G/E Ret_IO NC

XvVD[23] GPF3[3] GPI PD I(L) LCD_VD[23] SYS_VD[23] V656_CLK

G/E Ret_IO NC

XvVSYNC_L

DI

GPF3[4] GPI PD I(L) VSYNC_LDI VSYNC_LDI VSYNC_LDI

G/E Ret_IO NC

XvSYS_OE GPF3[5] GPI PD I(L) SYS_OE SYS_OE VEN_FIELD

G/E Ret_IO NC

Xmmc0CLK GPG0[0] GPI PD I(L) SD_0_CLK

G/E

Ret_MM

C

NC

Xmmc0CMD GPG0[1] GPI PD I(L) SD_0_CMD

G/E

Ret_MM

C

NC

Xmmc0CDn GPG0[2] GPI PD I(L) SD_0_CDn

G/E

Ret_MM

C

NC

Xmmc0DATA

[0]

GPG0[3] GPI PD I(L)

SD_0_DATA[0

]

VDD_EXT0

Xmmc0DATA

[1]

GPG0[4] GPI PD I(L)

SD_0_DATA[1

]

G/E

Ret_MM

C

NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

18

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

Xmmc0DATA

[2]

GPG0[5] GPI PD I(L)

SD_0_DATA[2

]

G/E

Ret_MM

C

NC

Xmmc0DATA

[3]

GPG0[6] GPI PD I(L)

SD_0_DATA[3

]

G/E

Ret_MM

C

NC

Xmmc1CLK GPG1[0] GPI PD I(L) SD_1_CLK

G/E

Ret_MM

C

NC

Xmmc1CMD GPG1[1] GPI PD I(L) SD_1_CMD

G/E

Ret_MM

C

NC

Xmmc1CDn GPG1[2] GPI PD I(L) SD_1_CDn

G/E

Ret_MM

C

NC

Xmmc1DATA

[0]

GPG1[3] GPI PD I(L)

SD_1_DATA[0

]

SD_0_DATA[4]

G/E

Ret_MM

C

NC

Xmmc1DATA

[1]

GPG1[4] GPI PD I(L)

SD_1_DATA[1

]

SD_0_DATA[5]

G/E

Ret_MM

C

NC

Xmmc1DATA

[2]

GPG1[5] GPI PD I(L)

SD_1_DATA[2

]

SD_0_DATA[6]

G/E

Ret_MM

C

NC

Xmmc1DATA

GPG1[6] GPI PD I(L)

SD_1_DATA[3

SD_0_DATA[7]

G/E

Ret_MM

NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

19

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

[3] ]

C

Xmmc2CLK GPG2[0] GPI PD I(L) SD_2_CLK

G/E

Ret_MM

C

NC

Xmmc2CMD GPG2[1] GPI PD I(L) SD_2_CMD

G/E

Ret_MM

C

NC

Xmmc2CDn GPG2[2] GPI PD I(L) SD_2_CDn

G/E

Ret_MM

C

NC

Xmmc2DATA

[0]

GPG2[3] GPI PD I(L)

SD_2_DATA[0

]

G/E

Ret_MM

C

NC

Xmmc2DATA

[1]

GPG2[4] GPI PD I(L)

SD_2_DATA[1

]

G/E

Ret_MM

C

NC

Xmmc2DATA

[2]

GPG2[5] GPI PD I(L)

SD_2_DATA[2

]

G/E

Ret_MM

C

NC

VDD_EXT1

Xmmc2DATA

[3]

GPG2[6] GPI PD I(L)

SD_2_DATA[3

]

G/E

Ret_MM

C

NC

VDD_EXT2

Xmmc3CLK GPG3[0] GPI PD I(L) SD_3_CLK

G/E

Ret_MM

C

NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

20

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

Xmmc3CMD GPG3[1] GPI PD I(L) SD_3_CMD

G/E

Ret_MM

C

NC

Xmmc3CDn GPG3[2] GPI PD I(L) SD_3_CDn

G/E

Ret_MM

C

NC

Xmmc3DATA

[0]

GPG3[3] GPI PD I(L)

SD_3_DATA[0

]

SD_2_DATA[4]

G/E

Ret_MM

C

NC

Xmmc3DATA

[1]

GPG3[4] GPI PD I(L)

SD_3_DATA[1

]

SD_2_DATA[5]

G/E

Ret_MM

C

NC

Xmmc3DATA

[2]

GPG3[5] GPI PD I(L)

SD_3_DATA[2

]

SD_2_DATA[6]

G/E

Ret_MM

C

NC

Xmmc3DATA

[3]

GPG3[6] GPI PD I(L)

SD_3_DATA[3

]

SD_2_DATA[7]

G/E

Ret_MM

C

NC

XEINT[0] GPH0[0] GPI PD I(L)

G/E/

W

No_Ret NC

Can be used as a

PS_HOLD pin

Wakeup source

VDD_SYS0

XEINT[1] GPH0[1] GPI PD I(L)

G/E/ No_Ret NC wakeup source

S5PV210_HARDWARE DESING GUIDE REV 1.0

21

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

W

XEINT[2] GPH0[2] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[3] GPH0[3] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[4] GPH0[4] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[5] GPH0[5] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[6] GPH0[6] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[7] GPH0[7] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[8] GPH1[0] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

VDD_SYS1

XEINT[9] GPH1[1] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

S5PV210_HARDWARE DESING GUIDE REV 1.0

22

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XEINT[10] GPH1[2] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[11] GPH1[3] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[12] GPH1[4] GPI PD I(L)

HDMI_CEC

G/E/

W

No_Ret NC wakeup source

XEINT[13] GPH1[5] GPI PD I(L)

HDMI_HPD

G/E/

W

No_Ret NC wakeup source

XEINT[14] GPH1[6] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[15] GPH1[7] GPI PD I(L)

G/E/

W

No_Ret NC wakeup source

XEINT[16] GPH2[0] GPI PD I(L) KP_COL[0]

G/E/

W

No_Ret NC wakeup source

XEINT[17] GPH2[1] GPI PD I(L) KP_COL[1]

G/E/

W

No_Ret NC wakeup source

VDD_KEY

XEINT[18] GPH2[2] GPI PD I(L) KP_COL[2]

G/E/ No_Ret NC wakeup source

S5PV210_HARDWARE DESING GUIDE REV 1.0

23

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

W

XEINT[19] GPH2[3] GPI PD I(L) KP_COL[3]

G/E/

W

No_Ret NC wakeup source

XEINT[20] GPH2[4] GPI PD I(L) KP_COL[4]

G/E/

W

No_Ret NC wakeup source

XEINT[21] GPH2[5] GPI PD I(L) KP_COL[5]

G/E/

W

No_Ret NC wakeup source

XEINT[22] GPH2[6] GPI PD I(L) KP_COL[6]

G/E/

W

No_Ret NC wakeup source

XEINT[23] GPH2[7] GPI PD I(L) KP_COL[7]

G/E/

W

No_Ret NC wakeup source

XEINT[24] GPH3[0] GPI PD I(L) KP_ROW[0]

G/E/

W

No_Ret NC wakeup source

XEINT[25] GPH3[1] GPI PD I(L) KP_ROW[1]

G/E/

W

No_Ret NC wakeup source

XEINT[26] GPH3[2] GPI PD I(L) KP_ROW[2]

G/E/

W

No_Ret NC wakeup source

S5PV210_HARDWARE DESING GUIDE REV 1.0

24

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XEINT[27] GPH3[3] GPI PD I(L) KP_ROW[3]

G/E/

W

No_Ret NC wakeup source

XEINT[28] GPH3[4] GPI PD I(L) KP_ROW[4]

G/E/

W

No_Ret NC wakeup source

XEINT[29] GPH3[5] GPI PD I(L) KP_ROW[5]

G/E/

W

No_Ret NC wakeup source

XEINT[30] GPH3[6] GPI PD I(L) KP_ROW[6]

G/E/

W

No_Ret NC wakeup source

XEINT[31] GPH3[7] GPI PD I(L) KP_ROW[7]

G/E/

W

No_Ret NC wakeup source

Xi2s0SCLK GPI[0]

Func

0

PD O(L) I2S_0_SCLK

PCM_0_SCLK

DS

Ret_IO

(sleep)

NC For low power audio

VDD_AUD

Xi2s0CDCL

K

GPI[1]

Func

0

PD O(L) I2S_0_CDCLK

PCM_0_EXTCLK

DS

Ret_IO

(sleep)

NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

25

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

Xi2s0LRCK GPI[2]

Func

0

PD O(L) I2S_0_LRCK

PCM_0_FSYNC

DS

Ret_IO

(sleep)

NC

Cannot be used as GPIO

& EINT

Xi2s0SDI GPI[3]

Func

0

PD I(L) I2S_0_SDI PCM_0_SIN

DS

Ret_IO

(sleep)

NC

Xi2s0SDO[

0]

GPI[4]

Func

0

PD O(L)

I2S_0_SDO[0

]

PCM_0_SOUT

DS

Ret_IO

(sleep)

NC

Xi2s0SDO[

1]

GPI[5]

Func

0

PD O(L)

I2S_0_SDO[1

]

DS

Ret_IO

(sleep)

NC

Xi2s0SDO[

2]

GPI[6]

Func

0

PD O(L)

I2S_0_SDO[2

]

DS

Ret_IO

(sleep)

NC

XmsmADDR[

0]

GPJ0[0] GPI PD I(L) MSM_ADDR[0]

CAM_B_DATA[

0]

CF_ADDR[0]

MIPI_BYTE_C

LK

G/E Ret_CF NC

VDD_MODE

M

XmsmADDR[ GPJ0[1] GPI PD I(L) MSM_ADDR[1]

CAM_B_DATA[

CF_ADDR[1] MIPI_ESC_CL

G/E Ret_CF NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

26

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

1]

1]

K

XmsmADDR[

2]

GPJ0[2] GPI PD I(L) MSM_ADDR[2]

CAM_B_DATA[

2]

CF_ADDR[2] TS_CLK

G/E Ret_CF NC

XmsmADDR[

3]

GPJ0[3] GPI PD I(L) MSM_ADDR[3]

CAM_B_DATA[

3]

CF_IORDY TS_SYNC

G/E

Ret_CF

NC

XmsmADDR[

4]

GPJ0[4] GPI PD I(L) MSM_ADDR[4]

CAM_B_DATA[

4]

CF_INTRQ TS_VAL

G/E

Ret_CF

NC

XmsmADDR[

5]

GPJ0[5] GPI PD I(L) MSM_ADDR[5]

CAM_B_DATA[

5]

CF_DMARQ TS_DATA

G/E

Ret_CF

NC

XmsmADDR[

6]

GPJ0[6] GPI PD I(L) MSM_ADDR[6]

CAM_B_DATA[

6]

CF_DRESETN TS_ERROR

G/E

Ret_CF

NC

XmsmADDR[

7]

GPJ0[7] GPI PD I(L) MSM_ADDR[7]

CAM_B_DATA[

7]

CF_DMACKN MHL_D0

G/E

Ret_CF

NC

XmsmADDR[

8]

GPJ1[0] GPI PD I(L) MSM_ADDR[8]

CAM_B_PCLK

SROM_ADDR[1

6]

MHL_D1

G/E

Ret_CF

NC

XmsmADDR[

9]

GPJ1[1] GPI PD I(L) MSM_ADDR[9]

CAM_B_VSYNC

SROM_ADDR[1

7]

MHL_D2

G/E

Ret_CF

NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

27

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XmsmADDR[

10]

GPJ1[2] GPI PD I(L)

MSM_ADDR[10

]

CAM_B_HREF

SROM_ADDR[1

8]

MHL_D3

G/E

Ret_CF

NC

XmsmADDR[

11]

GPJ1[3] GPI PD I(L)

MSM_ADDR[11

]

CAM_B_FIELD

SROM_ADDR[1

9]

MHL_D4

G/E

Ret_CF

NC

XmsmADDR[

12]

GPJ1[4] GPI PD I(L)

MSM_ADDR[12

]

CAM_B_CLKOU

T

SROM_ADDR[2

0]

MHL_D5

G/E

Ret_CF

NC

XmsmADDR[

13]

GPJ1[5] GPI PD I(L)

MSM_ADDR[13

]

KP_COL[0]

SROM_ADDR[2

1]

MHL_D6

G/E

Ret_CF

NC

XmsmDATA[

0]

GPJ2[0] GPI PD I(L) MSM_DATA[0] KP_COL[1] CF_DATA[0] MHL_D7

G/E

Ret_CF

NC

XmsmDATA[

1]

GPJ2[1] GPI PD I(L) MSM_DATA[1] KP_COL[2] CF_DATA[1] MHL_D8

G/E

Ret_CF

NC

XmsmDATA[

2]

GPJ2[2] GPI PD I(L) MSM_DATA[2] KP_COL[3] CF_DATA[2] MHL_D9

G/E

Ret_CF

NC

XmsmDATA[

3]

GPJ2[3] GPI PD I(L) MSM_DATA[3] KP_COL[4] CF_DATA[3] MHL_D10

G/E

Ret_CF

NC

XmsmDATA[ GPJ2[4] GPI PD I(L) MSM_DATA[4] KP_COL[5] CF_DATA[4] MHL_D11

G/E

Ret_CF

NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

28

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

4]

XmsmDATA[

5]

GPJ2[5] GPI PD I(L) MSM_DATA[5] KP_COL[6] CF_DATA[5] MHL_D12

G/E

Ret_CF

NC

XmsmDATA[

6]

GPJ2[6] GPI PD I(L) MSM_DATA[6] KP_COL[7] CF_DATA[6] MHL_D13

G/E

Ret_CF

NC

XmsmDATA[

7]

GPJ2[7] GPI PD I(L) MSM_DATA[7] KP_ROW[0] CF_DATA[7] MHL_D14

G/E

Ret_CF

NC

XmsmDATA[

8]

GPJ3[0] GPI PD I(L) MSM_DATA[8] KP_ROW[1] CF_DATA[8] MHL_D15

G/E

Ret_CF

NC

XmsmDATA[

9]

GPJ3[1] GPI PD I(L) MSM_DATA[9] KP_ROW[2] CF_DATA[9] MHL_D16

G/E

Ret_CF

NC

XmsmDATA[

10]

GPJ3[2] GPI PD I(L)

MSM_DATA[10

]

KP_ROW[3] CF_DATA[10] MHL_D17

G/E

Ret_CF

NC

XmsmDATA[

11]

GPJ3[3] GPI PD I(L)

MSM_DATA[11

]

KP_ROW[4] CF_DATA[11] MHL_D18

G/E

Ret_CF

NC

XmsmDATA[

12]

GPJ3[4] GPI PD I(L)

MSM_DATA[12

]

KP_ROW[5] CF_DATA[12] MHL_D19

G/E

Ret_CF

NC

S5PV210_HARDWARE DESING GUIDE REV 1.0

29

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

XmsmDATA[

13]

GPJ3[5] GPI PD I(L)

MSM_DATA[13

]

KP_ROW[6] CF_DATA[13] MHL_D20

G/E

Ret_CF

NC

XmsmDATA[

14]

GPJ3[6] GPI PD I(L)

MSM_DATA[14

]

KP_ROW[7] CF_DATA[14] MHL_D21

G/E

Ret_CF

NC

XmsmDATA[

15]

GPJ3[7] GPI PD I(L)

MSM_DATA[15

]

KP_ROW[8] CF_DATA[15] MHL_D22

G/E

Ret_CF

NC

XmsmCSn GPJ4[0] GPI PD I(L) MSM_CSn KP_ROW[9] CF_CSn[0] MHL_D23

G/E

Ret_CF

NC

XmsmWEn GPJ4[1] GPI PD I(L) MSM_WEn KP_ROW[10] CF_CSn[1] MHL_HSYNC

G/E

Ret_CF

NC

XmsmRn GPJ4[2] GPI PD I(L) MSM_Rn KP_ROW[11] CF_IORN MHL_IDCK

G/E

Ret_CF

NC

XmsmIRQn GPJ4[3] GPI PD I(L) MSM_IRQn KP_ROW[12] CF_IOWN MHL_VSYNC

G/E

Ret_CF

NC

XmsmADVN GPJ4[4] GPI PD I(L) MSM_ADVN KP_ROW[13]

SROM_ADDR[2

2]

MHL_DE

G/E

Ret_CF

NC

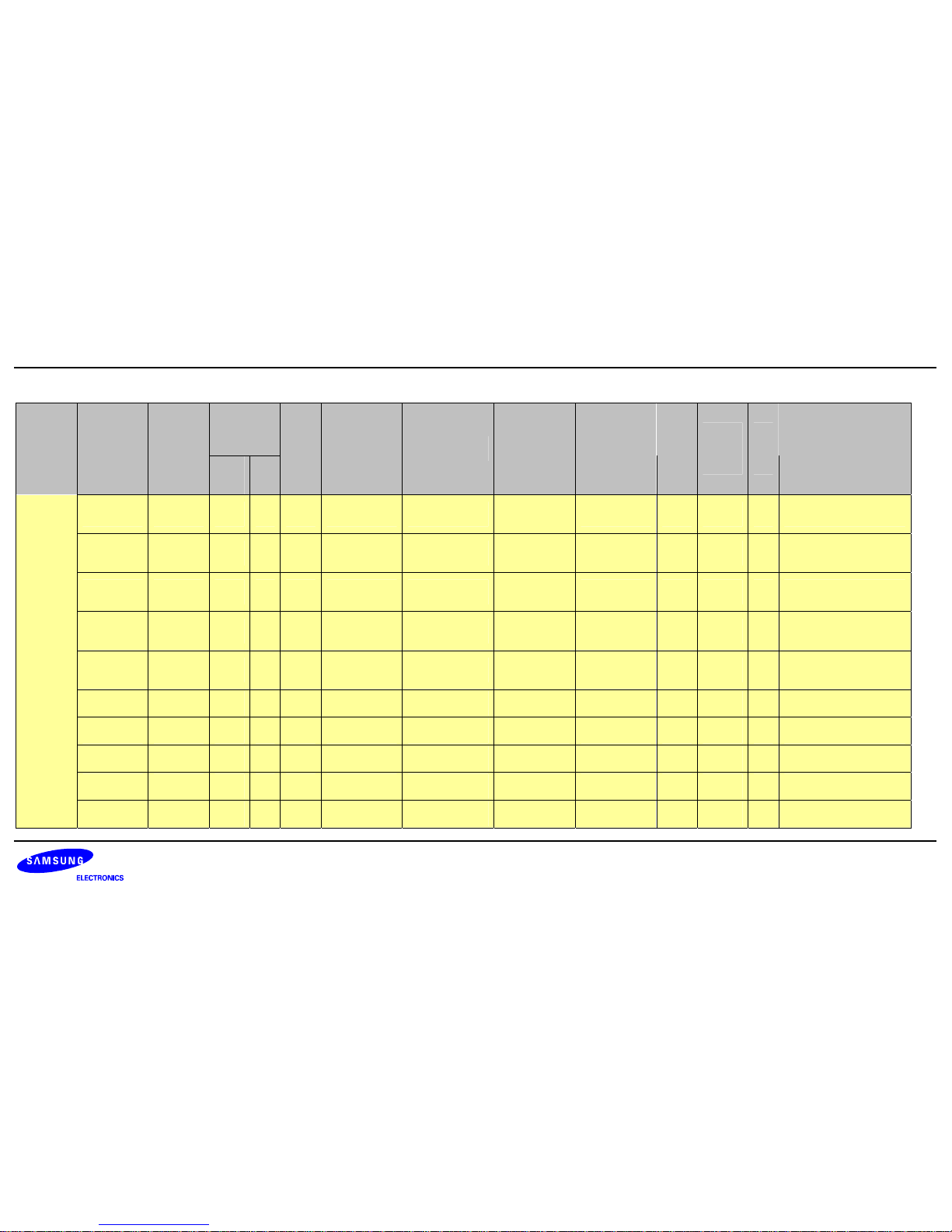

Xm0CSn[0] MP0_1[0]

Func

0

- O(H) SROM_CSn[0]

G

Ret_aut

o

NC

VDD_M0

Xm0CSn[1] MP0_1[1]

Func

0

- O(H) SROM_CSn[1]

G

Ret_aut

o

NC

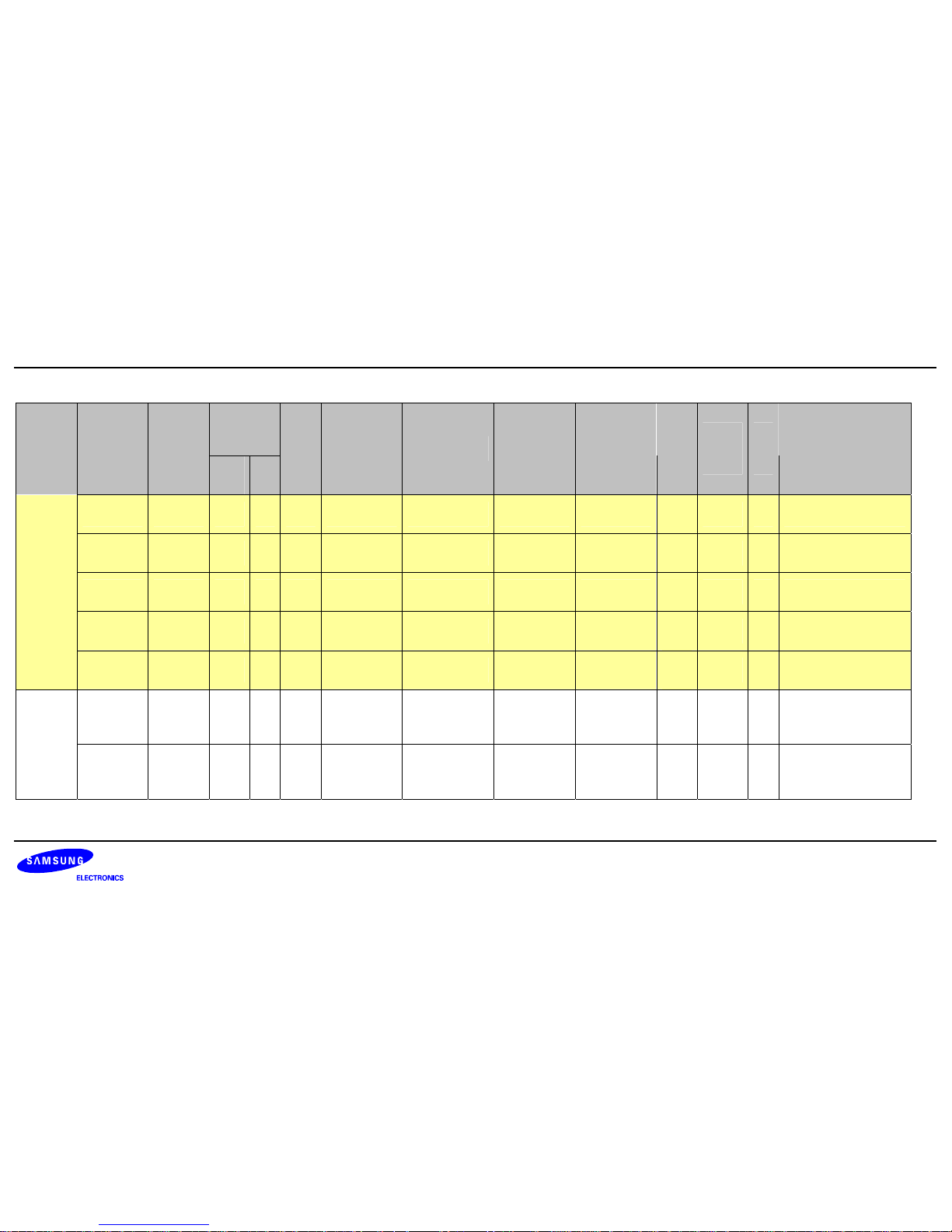

S5PV210_HARDWARE DESING GUIDE REV 1.0

30

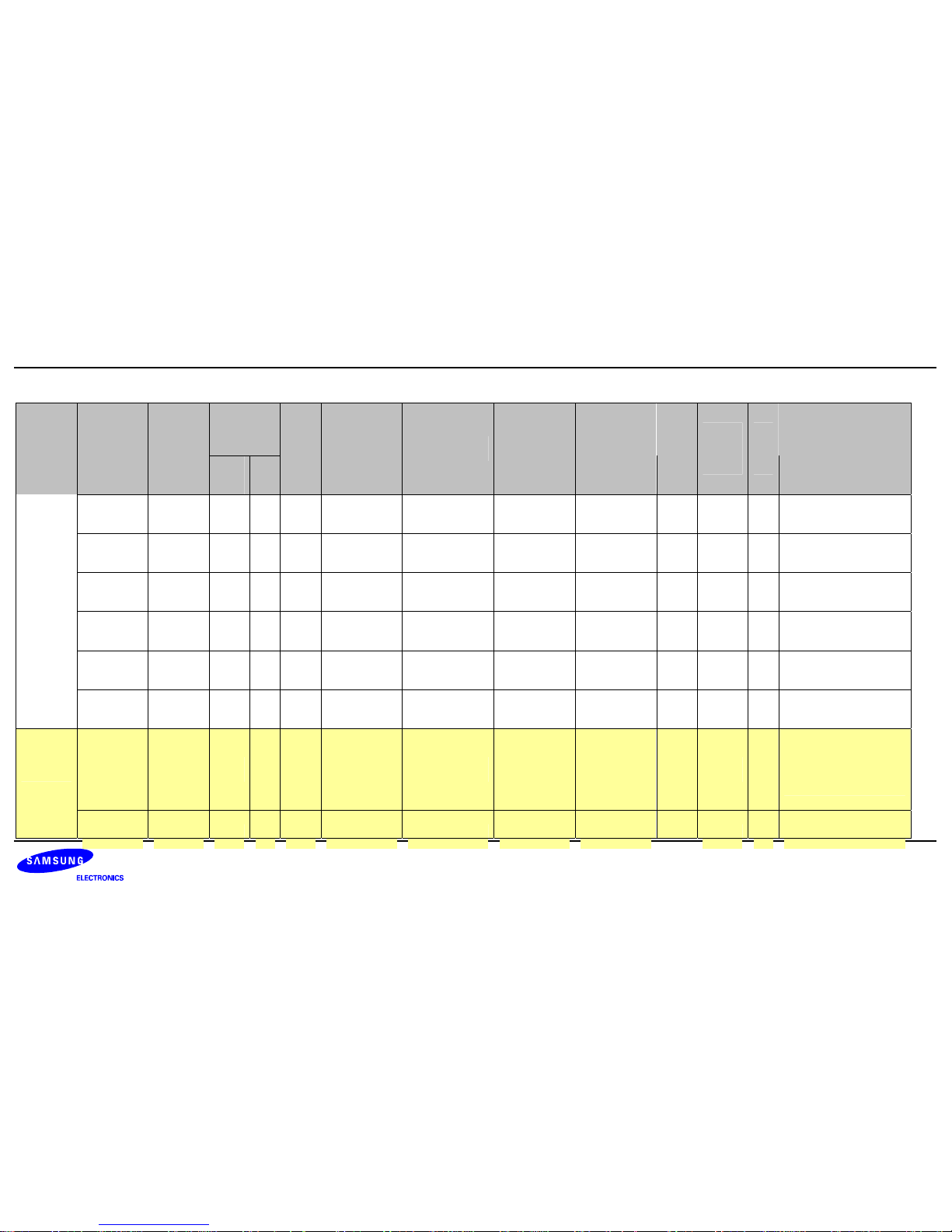

GPIO

Reset

value

IO Power

Domain

Ball Name Port

In/

Out

Pu/

Pd

Rese

t

stat

us

Func-0 Func-1 Func-2 Func-3

AU

RET @

Power

down

Not

Use

d

Circuit guide

Xm0CSn[2] MP0_1[2]

Func

1

- O(H) SROM_CSn[2] NFCSn[0]

G

Ret_aut

o

NC

Xm0CSn[3] MP0_1[3]

Func

1

- O(H) SROM_CSn[3] NFCSn[1]

G

Ret_aut

o

NC

Xm0CSn[4] MP0_1[4]

Func

3

- O(H) SROM_CSn[4] NFCSn[2]

ONANDXL_CSn

[0]

I

Ret_aut

o

-

Should be connected to

CE signal of OneNAND

Externally

Xm0CSn[5] MP0_1[5]

Func

3

- O(H) SROM_CSn[5] NFCSn[3]

ONANDXL_CSn

[1]

G

Ret_aut

o

NC

Xm0OEn MP0_1[6]

Func

0

- O(H) EBI_OEn

I

Ret_aut

o

-

Xm0WEn MP0_1[7]

Func

0

- O(H) EBI_WEn

I

Ret_aut

o

-

Internally connected to

OneNAND

Xm0BEn[0] MP0_2[0]

Func

0

- O(H) EBI_BEn[0]

G

Ret_aut

o

NC

Xm0BEn[1] MP0_2[1]

Func

0

- O(H) EBI_BEn[1]

G

Ret_aut

o

NC

Loading...

Loading...