Samsung S5N8944B Datasheet

S5N8944B

G.Lite

ADSL Transceiver for CO and CPE

Preliminary Information

(Revision 2.1)

June 2000

SAMSUNG ELECTRONICS CONFIDENTIAL PROPRIETARY

Copyright ©2000 Samsung Electronics, Inc. All Rights Reserved

S5N8944B

G.Lite ADSL Transceiver for CO and CPE

Contents

1. Features............................................................................................................................5

2. General Description .........................................................................................................5

3. Logical Symbol Diagram ..................................................................................................6

4. Pin Configuration.............................................................................................................7

5. Pin Description .................................................................................................................8

6. Functional Description................................................................................................... 11

7. I/O Timing Description ...................................................................................................13

8. Electrical Characteristics...............................................................................................17

9. Package Description......................................................................................................20

CONFIDENTIAL

2

Preliminary Information (Rev.2.1 )

S5N8944B

G.Lite ADSL Transceiver for CO and CPE

List of Figures

Figure 1: General Block Diagram...................................................................................... 5

Figure 2: Logical Symbol Diagram of the S5N8944B.........................................................6

Figure 3: Pin Configuration of the S5N8944B....................................................................7

Figure 4: Functional Block Diagram of the S5N8944B..................................................... 12

Figure 5: AFE Data I/F Timing Diagram........................................................................... 13

Figure 6: AFE Control I/F Timing Diagram....................................................................... 13

Figure 7: Motorola Read Cycle Timing Diagram .............................................................. 14

Figure 8: Motorola Write Cycle Timing Diagram .............................................................. 14

Figure 9: Intel Read Cycle Timing Diagram..................................................................... 15

Figure 10: Intel Write Cycle Timing Diagram ................................................................... 15

Figure 11: Non-ATM I/F (Byte Mode) Timing Diagram..................................................... 16

Figure 12: Non-ATM I/F (Envelope Mode) Timing Diagram ............................................. 16

Figure 13: ATM I/F (UTOPIA-2 Transmit) Timing Diagram............................................... 17

Figure 14: ATM I/F (UTOPIA-2 Receive) Timing Diagram................................................ 17

Figure 15: 160-QFP Package Diagram............................................................................ 20

CONFIDENTIAL

3

Preliminary Information (Rev.2.1 )

S5N8944B

G.Lite ADSL Transceiver for CO and CPE

List of Tables

Table 1: Pin Description of the S5N8944B......................................................................... 8

Table 2: Absolute Maximum Ratings............................................................................... 18

Table 3: Recommended Operating Conditions ................................................................ 18

Table 4: Power Dissipation.............................................................................................. 18

Table 5: DC Characteristics ............................................................................................ 19

CONFIDENTIAL

4

Preliminary Information (Rev.2.1 )

G.Lite ADSL Transceiver for CO and CPE

Line

Processor

End

Hybrid

Driver

DSP

S5N8944

S5N8943

1. Features

• Full Compliance with ITU-T G.Lite and G.hs

• FDM based DMT Line Coding

• Data Rate: Up to 3.5 Mbps for Downstream and 600 kbps for Upstream.

• Reach: 5.4 km (18 kft) on 24 AWG and 4 km (13.5kft) on 26 AWG

• Rate Adaptive Modem (steps of 32kbps)

• Reed-Solomon Forward Error Correction with Interleaver

• Frequency and Time Domain Equalizer

• Support Fast Retraining Function

• Support Network Management Function

• Support Power Management Function

• Host Interface (Intel/Motorola) and ATM(UTOPIA-2)/non-ATM Interface

• 0.25µm, 2.5V CMOS Technology

• Operating Temperature: -40 °C to 85 °C

• Package Type: 160-QFP

2. General Description

S5N8944B

The S5N8944B is a complete ATM-based rate adaptive G.Lite ADSL modem solution with

associated F/W and an Analog Front-End (S5N8943). The S5N8944B provides all the digital

functions such as ATM TC, FEC codec with interleaver/de-interleaver, adaptive QAM codec,

FFT/IFFT, equalizers, digital filters and so on.

There are four interfaces for external communications; UTOPIA-2 interface for direct connection

to ATM systems, serial interface for non-ATM applications, 16-bit ADC/DAC interface, and host

interface for general CPUs like Intel or Motorola.

The same chipset can be used at both sides of the link, Central Office and Customer Premises

Equipment. The S5N8944B uses 17.664MHz Xtal oscillator as a master clock for CO side and

17.664MHz VCXO for CPE.

ATM

or

Non-ATM

Digital

Interface

DMT

Analog

Front-

Line

Phone

Host

CONFIDENTIAL

ROM

Figure 1: General Block Diagram

5

Preliminary Information (Rev.2.1 )

G.Lite ADSL Transceiver for CO and CPE

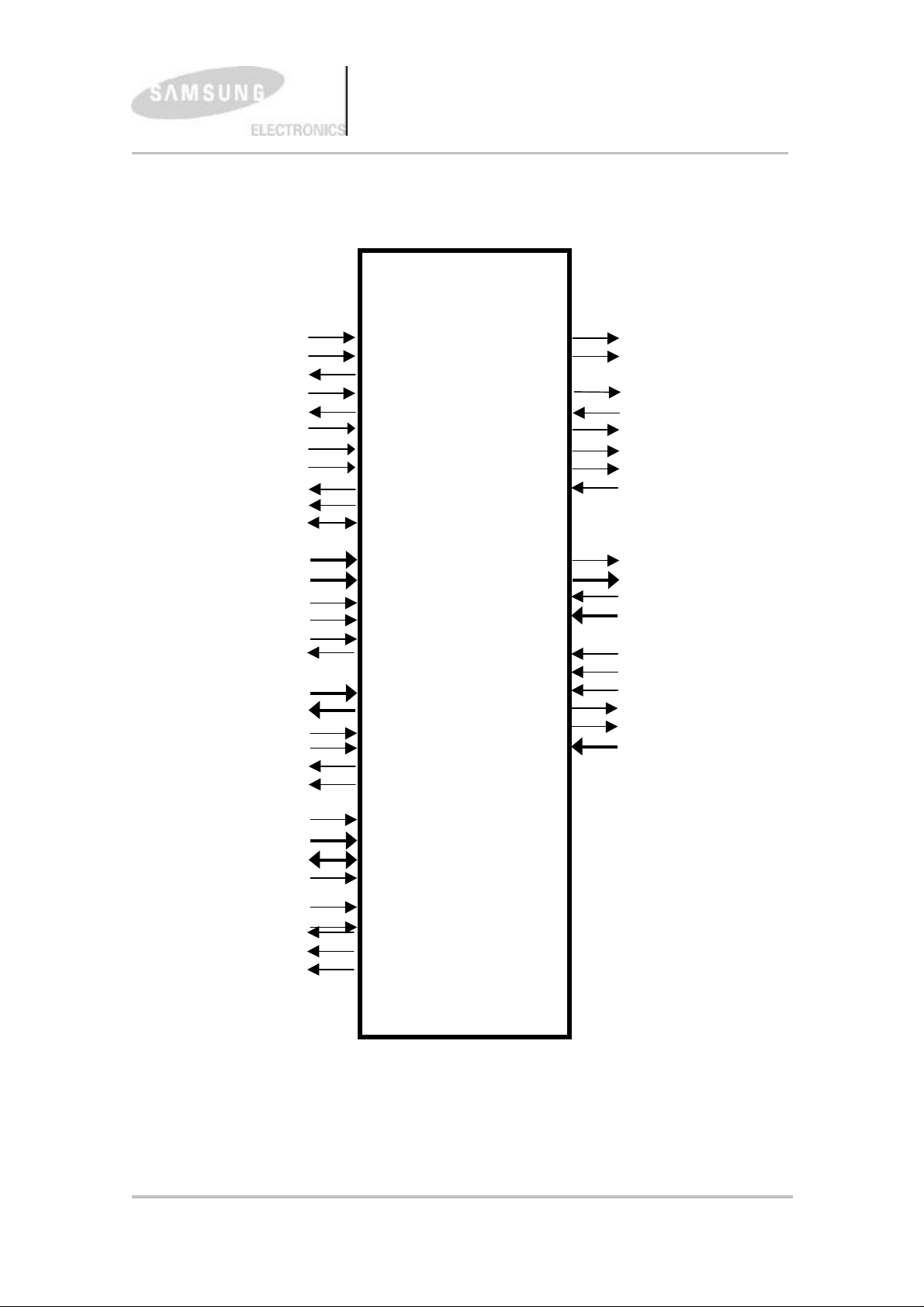

3. Logical Symbol Diagram

S5N8944B

RESET_N LD_TX_PWDN

XTAL_IN LD_RX_PWDN

XTAL_OUT

EXT_CLK AFE_RESET_N

PLL_FLT AFE_SDI

TEST_MODE AFE_SDO

TEST_SCN_EN AFE_SCK

CO_RT AFE_SEN_N

TX_SHOW AFE_BUSY

RX_SHOW

NTR

S5N8944B

TX_ADDR[4:0] DAC_REF

TX_DATA[7:0] DAC_DATA[15:0]

TX_CLK ADC_REF

TX_ENB ADC_DATA[15:0]

TX_SOC

TX_CLAV TL_TMS

TL_TCK

RX_ADDR[4:0] TL_TDI

RX_DATA[7:0] TL_TDO

RX_CLK TL_TINTP

RX_ENB TL_BMODE[1:0]

RX_SOC

RX_CLAV

HS_SEL

HS_ADDR[9:0]

HS_DATA[15:0]

HS_CS_N

HS_RD_N

HS_WR_N

HS_READY

HS_INT

HS_WAKEUP

CONFIDENTIAL

Figure 2: Logical Symbol Diagram of the S5N8944B

6

Preliminary Information (Rev.2.1 )

1

122

80

120

S5N8944B

DAC_DATA_8

DAC_DATA_7

DAC_DATA_6

DAC_DATA_5

DAC_DATA_4

TX_DATA_1

TX_DATA_0

HS_CS_N

TX_DATA_2

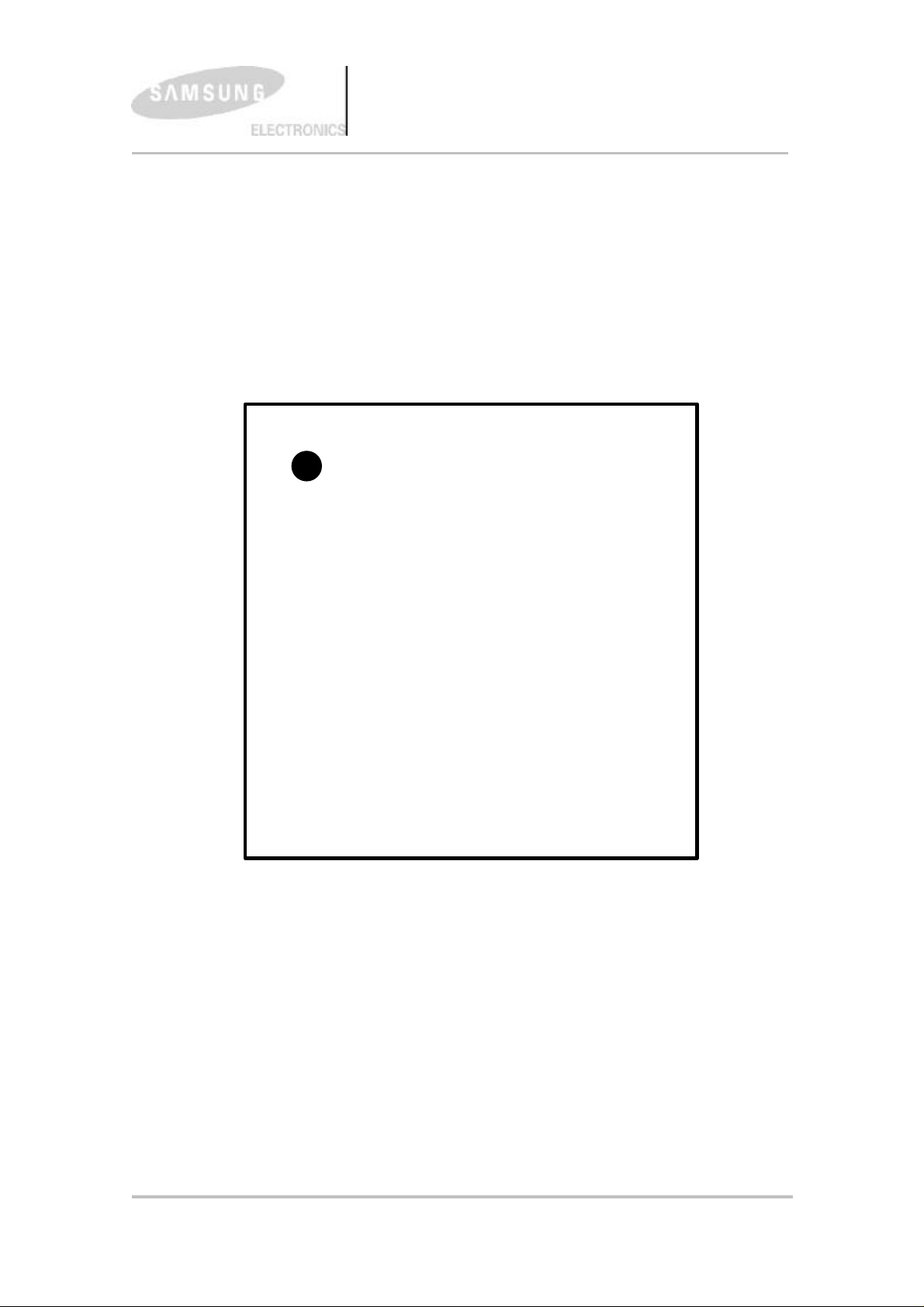

4. Pin Configuration

TL_BMODE_0

TL_BMODE_1

TEST_MODE

RESET_N

PLL_FLT

AGND17

160

159

158

157

AVDD16

155

156

154

HS_SEL

CO_RT

AGND15

AGND16

152

153

AVDD15

VDD14

149

150

151

S5N8944B

G.Lite ADSL Transceiver for CO and CPE

RX_ADDR_4

RX_ADDR_3

RX_ADDR_2

RX_ADDR_1

RX_ADDR_0

RX_DATA_7

RX_DATA_6

RX_DATA_5

RX_DATA_4

RX_DATA_3

RX_DATA_2

RX_DATA_1

RX_DATA_0

XTAL_OUT

XTAL_IN

GND14

147

148

146

145

VDD13

143

144

GND13

142

141

140

139

138

137

136

135

134

133

132

131

VDD12

129

130

RX_CLAV

GND12

128

RX_SOC

RX_CLK

126

127

RX_ENB

NTR

124

125

123

HS_RD_N

HS_WR_N

HS_READY

VDD1

GND1

HS_INT

HS_WAKEUP

HS_DATA_15

HS_DATA_14

HS_DATA_13

HS_DATA_12

HS_DATA_11

HS_DATA_10

GND2

VDD2

HS_DATA_9

HS_DATA_8

HS_DATA_7

HS_DATA_6

HS_DATA_5

HS_DATA_4

HS_DATA_3

HS_DATA_2

GND3

VDD3

HS_DATA_1

HS_DATA_0

HS_ADDR_9

HS_ADDR_8

HS_ADDR_7

HS_ADDR_6

HS_ADDR_5

HS_ADDR_4

GND4

VDD4

HS_ADDR_3

HS_ADDR_2

HS_ADDR_1

HS_ADDR_0

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

TEST_SCN_EN

AFE_SEN_N

AFE_SDI

AFE_SDO

GND5

ADC_REF

AFE_SCK

G.Lite ADSL Transceiver

for

CO and CPE

(160-QFP)

ADC_DATA_0

ADC_DATA_1

ADC_DATA_2

ADC_DATA_3

ADC_DATA_4

ADC_DATA_5

VDD6

GND6

ADC_DATA_6

ADC_DATA_7

ADC_DATA_8

ADC_DATA_9

ADC_DATA_10

ADC_DATA_11

ADC_DATA_12

ADC_DATA_13

ADC_DATA_14

ADC_DATA_15

VDD5

DAC_DATA_0

DAC_REF

EXT_CLK

DAC_DATA_3

DAC_DATA_2

VDD7

GND7

DAC_DATA_1

TX_DATA_3

119

VDD11

118

GND11

117

TX_DATA_4

116

TX_DATA_5

115

TX_DATA_6

114

TX_DATA_7

113

TX_ADDR_0

112

TX_ADDR_1

111

110

TX_ADDR_2

109

TX_ADDR_3

108

TX_ADDR_4

107

TX_CLAV

106

TX_SOC

105

TX_CLK

104

TX_ENB

103

VDD10

102

GND10

101

TL_TINTP

100

TL_TDO

99

TL_TDI

98

TL_TCK

97

TL_TMS

96

VDD9

95

94

GND9

93

RX_SHOW

92

TX_SHOW

91

LD_RX_PWDN

90

LD_TX_PWDN

89

AFE_BUSY

88

AFE_RESET_N

87

DAC_DATA_15

86

DAC_DATA_14

85

GND8

84

VDD8

83

DAC_DATA_13

82

DAC_DATA_12

81

797877767574737271706968676665646362616059585756555453525150494847464544434241

DAC_DATA_11

DAC_DATA_10

CONFIDENTIAL

Figure 3: Pin Configuration of the S5N8944B

Preliminary Information (Rev.2.1 )

7

Loading...

Loading...