Samsung S5F429PX03-LDB0 Datasheet

1/4 INCH CCD IMAGE SENSOR FOR PAL CAMERA S5F429PX03

ORDERING INFORMATION

H-CCD

INTRODUCTION

The S5F429PX03 is an interline transfer CCD area image

sensor developed for PAL 1/4 inch optical format video

cameras, surveillance cameras, object detectors and image

pattern recognizers. High sensitivity is achieved through the

adoption of Ye, Cy, Mg and G complementary color mosaic

filters, on-chip micro lenses and HAD (Hole Accumulated

Diode) photosensors. This chip features a field integration

read out system and an electronic shutter with variable charge

storage time.

FEATURES

• High Sensitivity

• Optical Size 1/4 inch Format

• No Adjust Substrate Bias

• Ye, Cy, Mg, G On-chip Complementary Color Mosaic

Filter

• Low Dark Current

• Horizontal Register 3.3 to 5.0V Drive

• 14pin Ceramic DIP Package

• Field Integration Read Out System

• No DC Bias on Reset Gate

14Pin Cer - DIP

Device Package Operating

S5F429PX03-LDB0 14Pin Cer - DIP

-10 °C − +60 °C

STRUCTURE

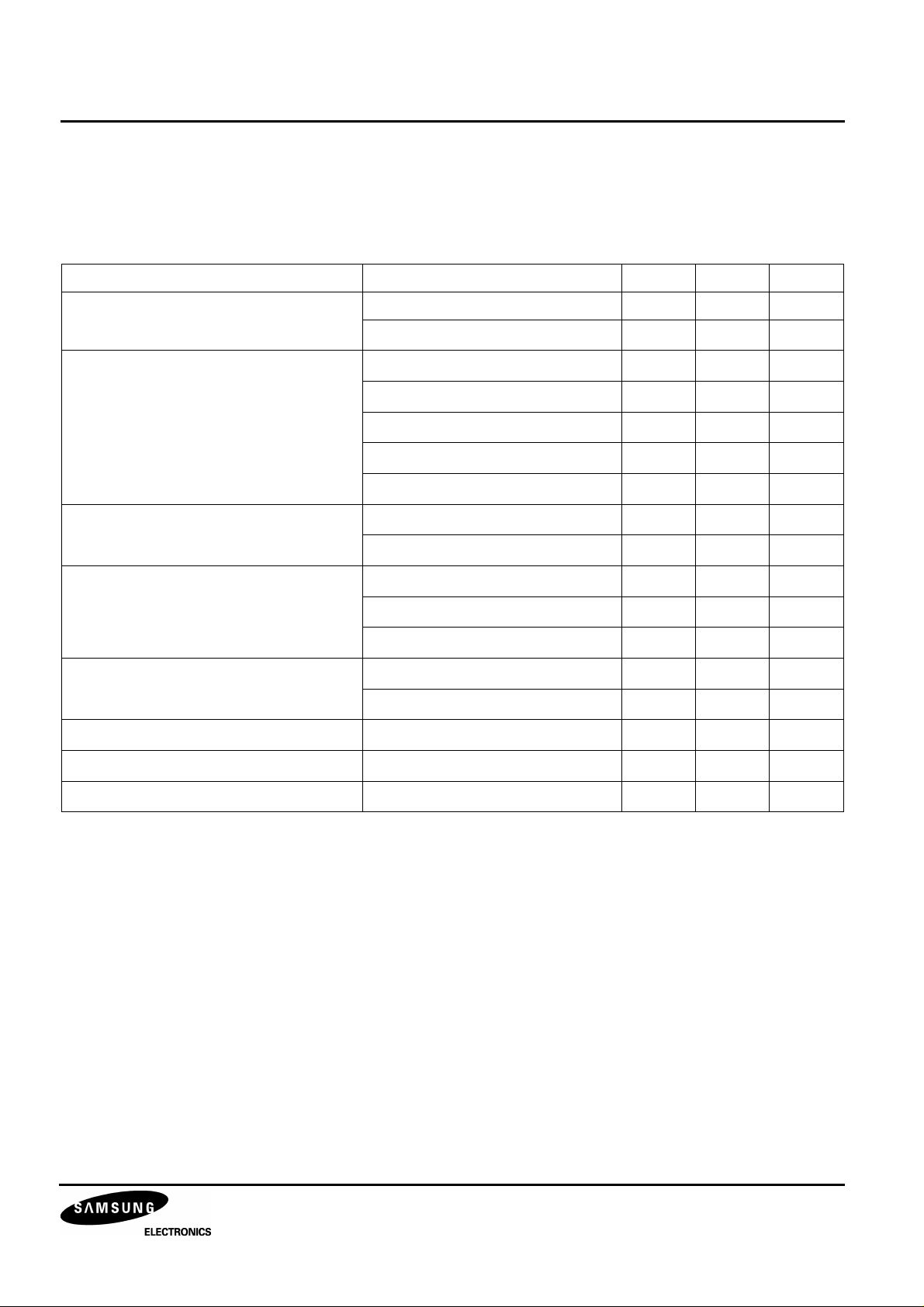

• Number of Total Pixels: 537(H) × 597(V)

• Number of Effective Pixels: 500(H) × 582(V)

• Chip Size: 4.80mm(H) × 4.04mm(V)

• Unit Pixel Size: 7.30 µm(H) × 4.70 µm(V)

• Optical Blacks & Dummies: Refer to Figure Below

Vertical 1 Line (Even Field Only)

16 7 500 30

1 582 14

V-CCD

OUTP UT

Effective

Imagi ng

Area

Du mmy P ixels

Optical Black Pixels

E ffective Pixel s

1

S5F429PX03 1/4 INCH CCD IMAGE SENSOR FOR PAL CAMERA

BLOCK DIAGRAM

(Top View)

7

V

OUT

8 9 10 11 12 13 14

V

DD

6 5 4 3 2 1

GND NC

Vertical Shift Register CCD

Cy Ye

Mg.

Cy

Cy

G

Cy

Mg Mg

GND

Ye

Ye

Mg

Ye Ye

Φ

SUB

Φ

V1

Vertical Shift Register CCD

G

G

Horizontal Shift Register CCD

V

L

Φ

Φ

Cy

Mg

Cy

Cy

Cy

RG

V2

G

Φ

Vertical Shift Register CCD

Ye

G

Ye

Ye

Mg

G

Φ

H1

V3

Vertical Shift Register CCD

Figure 1. Block Diagram

Φ

Φ

V4

H2

PIN DESCRIPTION

Table 1. Pin Description

Pin Symbol Description Pin Symbol Description

1

2

3

4

Φ

Φ

Φ

Φ

V4

V3

V2

V1

Vertical register transfer clock 8

Vertical register transfer clock 9 GND GND

Vertical register transfer clock 10

Vertical register transfer clock 11

5 NC No connection 12

6 GND Ground 13

7

2

V

OUT

Signal output 14

Φ

V

Φ

Φ

Φ

DD

SUB

V

L

RG

H1

H2

Output stage drain bias

Substrate clock

Protection transistor bias

Reset gate clock

Horizontal register transfer clock

Horizontal register transfer clock

1/4 INCH CCD IMAGE SENSOR FOR PAL CAMERA S5F429PX03

ABSOLUTE MAXIMUM RATINGS

(NOTE)

Table 2. Absolute Maximum Ratings

Characteristics Symbols Min. Max. Unit

Substrate voltage SUB - GND -0.3 40 V

VDD, V

Vertical clock input voltage ΦV1, ΦV3, - GND

ΦV2, Φ

ΦV1, ΦV3, - V

ΦV2, Φ

ΦV1, ΦV2, ΦV3, Φ

Horizontal clock input voltage ΦH1, ΦH2 - V

ΦH1, ΦH2 - SUB

Voltage difference between vertical and

horizontal clock input pins

ΦV1, ΦV2, ΦV3, Φ

ΦH1, Φ

ΦH1, ΦH2 - Φ

OUT

V4

V4

H2

- SUB

- GND

L

- VL

L

V4

V4

V4

- SUB

-40 10 V

-0.3 30 V

-0.3 17 V

-0.3 30 V

-0.3 17 V

-40 10 V

-0.3 7 V

-40 7 V

15 V

17 V

-17 17 V

Output clock input voltage ΦRG - GND

ΦRG - SUB

Protection circuit bias voltage

Operating temperature

Storage temperature

NOTE: The device can be destroyed, if the applied voltage or temperature is higher than the absolute maximum rating voltage

or temperature.

VL - SUB

T

OP

T

STG

-0.3 17 V

-40 17 V

-40 10 V

-10 60 °C

-30 80 °C

3

S5F429PX03 1/4 INCH CCD IMAGE SENSOR FOR PAL CAMERA

DC CHARACTERISTICS

Table 3. DC Characteristics

Item Symbol Min. Typ. Max. Unit

Output stage drain bias

Protection circuit bias voltage

Output stage drain current

CLOCK VOLTAGE CONDITIONS

Table 4. Clock Voltage Conditions

Item Symbol Min. Typ. Max. Unit Remark

Read-out clock voltage

Vertical transfer clock voltage V

Horizontal transfer clock voltage V

V

VM1

V

VH1

VL1

HH1

, V

~ V

~ V

, V

V

V

I

VH3

VM4

VL4

HH2

DD

DD

14.55 15.0 15.45 V

L

The lowest vertical clock level

5 mA

14.55 15.0 15.45 V High level

-0.2 0.0 0.2 V Middle

-8.0 -7.5 -7.0 V Low

3.0 5.0 5.25 V High

V

HL1

Charge reset clock voltage V

Substrate clock voltage

V

, V

RGH

V

RGL

ΦSUB

HL2

-0.05 0.0 0.05 V Low

4.75 5.0 5.25 V High

-0.2 0.0 0.2 V Low

21.5 22.5 23.5 V Shutter

4

1/4 INCH CCD IMAGE SENSOR FOR PAL CAMERA S5F429PX03

V

=

V

-0.3V

DRIVE CLOCK WAVEFORM CONDITIONS

Read Out Clock Waveform

100%

90%

V

VH1,VVH3

10%

0%

Vertical Transfer Clock Waveform

tr twh tf

0V

¥Õ

V V H 1

¥Õ

V VH2

V 1

V 2

V V H H

V V L 1

V VL

V V H H V VHH

V

VHL

V

VL

V

VH

V V H H

V V H L

V

VL H

V

V

V

V VL H

V VL 2

V VL L

VVH= (V

VV L = (V V L 3 + VV L 4)/ 2

V¥ÕV= V

¥Õ

V 3

V

V H L

V V HL

V VHH

V V H L

V

VH3

V VL 3

VL L

¥Õ

V 4

VH

VHL

V

V

V VL

VH

V VH H

VHL

V V H 4

V

VH H

V

VH

V VL H

V

VL L

V

VH H

V

VHL

V VL H

V

VL L

V

VH 1

+ V

VH 2

VL 4

)/2

V

VH H

= VVH+ 0.3V

V

VL

VVH L = VV H - 0. 3 V

VH n

- V

VL n (n = 1~4)

V

= V

V L

V L

+ 0.3V

VL H

VL L

5

S5F429PX03 1/4 INCH CCD IMAGE SENSOR FOR PAL CAMERA

V

Horizontal Transfer Clock Waveform Diagram

90%

10%

HL

Reset Gate Clock Waveform Diagram

RG waveform

V

RGLH

V

RGLL

tr twh

twl

Point A

V¥Õ

tf

H

twl

twh tftr

V

RGH

V

¥Õ

RG

V

+ 0.5V

RGL

V

RGL

¥Õ

H1 waveform

10%

V

is the maximum value and V

RGLH

in the diagram about to RG rise

V

RGL

= (V

RGLH

+ V

RGLL

)/2, V

Substrate Clock Waveform

V

SU B

FRG

100%

90%

10%

0%

is the minimum value of the coupling waveform in the period from Point A

RGLL

= V

RGH

- V

RGL

¥Õ

V

SU B

twhtr tf

6

Loading...

Loading...