Page 1

USER'S MANUAL ERRATA

This document contains the corrections of errors,

typos and omissions in the following document.

Samsung 8-bit CMOS S3C84E5/C84E9/P84E9 Microprocessor User's Manual

Document Number: 21.1-S3-C84E5/C84E9/P84E9-082005

Publication: August 2005

Page 2

S3C84E5/C84E9/P84E9 USER’S MANUAL ERRATA

ERRATA (VER 1.1)

Samsung 8-bit CMOS S3C84E5/C84E9/P84E9 Microprocessor User’s Manual

Document Number: 21.1-S3-C84E5/C84E9/P84E9-082005

Publication: August 2005

1. Features (PAGE 1-2)

Built-in RESET circuit (LVR)

• Low-Voltage reset (LVR value: 2.9 V)

Operating Voltage Range

• V

to 5.5V

LVR

2. Low Voltage Reset (PAGE 16-1)

The on-chip Low Voltage Reset, features static reset when supply voltage is below a reference voltage value

(Typical 2.9 V).

1

Page 3

USER’S MANUAL ERRATA S3C84E5/C84E9/P84E9

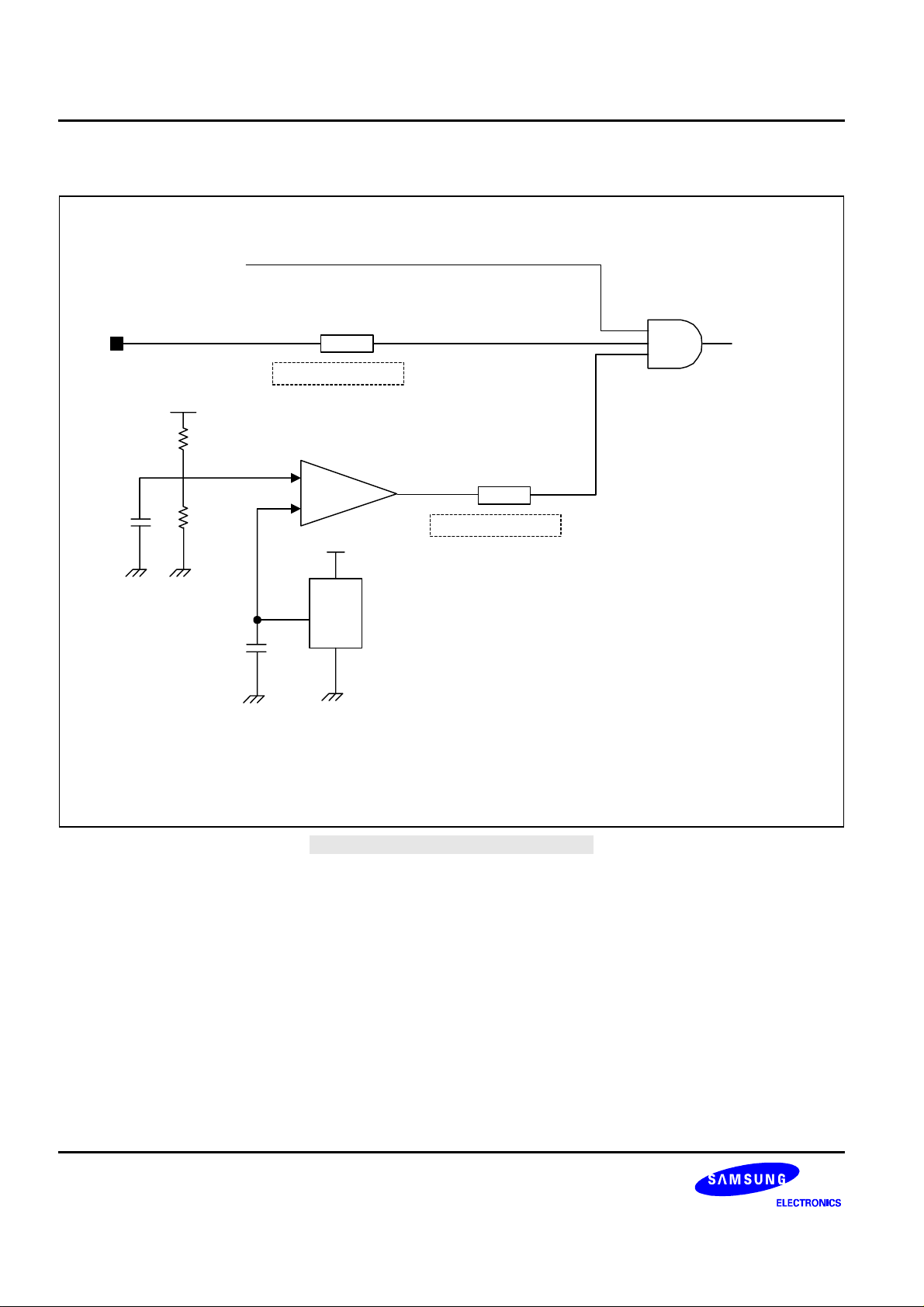

3. Low Voltage Reset (PAGE 16-2)

Watchdog RESET

nRESET

N.F

Longger than 1us

VDD

Internal System

RESET

VIN

+

Comparator

VREF

VDD

VREF

BGR

NOTES:

1. The target of voltage detection level is 2.9 V at VDD = 5 V

2. BGR is Band Gap voltage Reference

Longger than 1us

N.F

When the V

is lower than 2.9V

DD level

Figure 16-1. Low Voltage Reset Circuit

2

Page 4

S3C84E5/C84E9/P84E9 USER’S MANUAL ERRATA

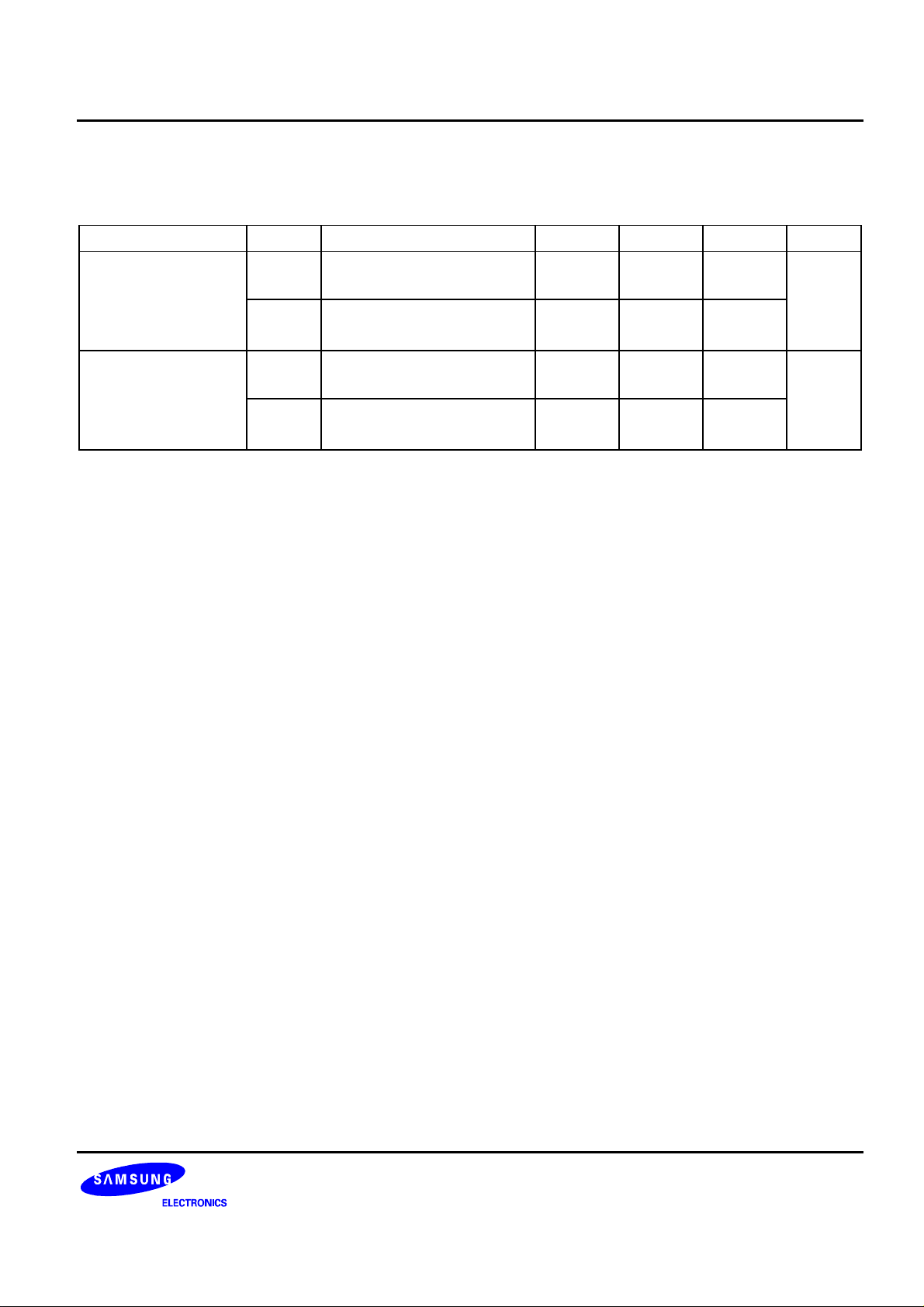

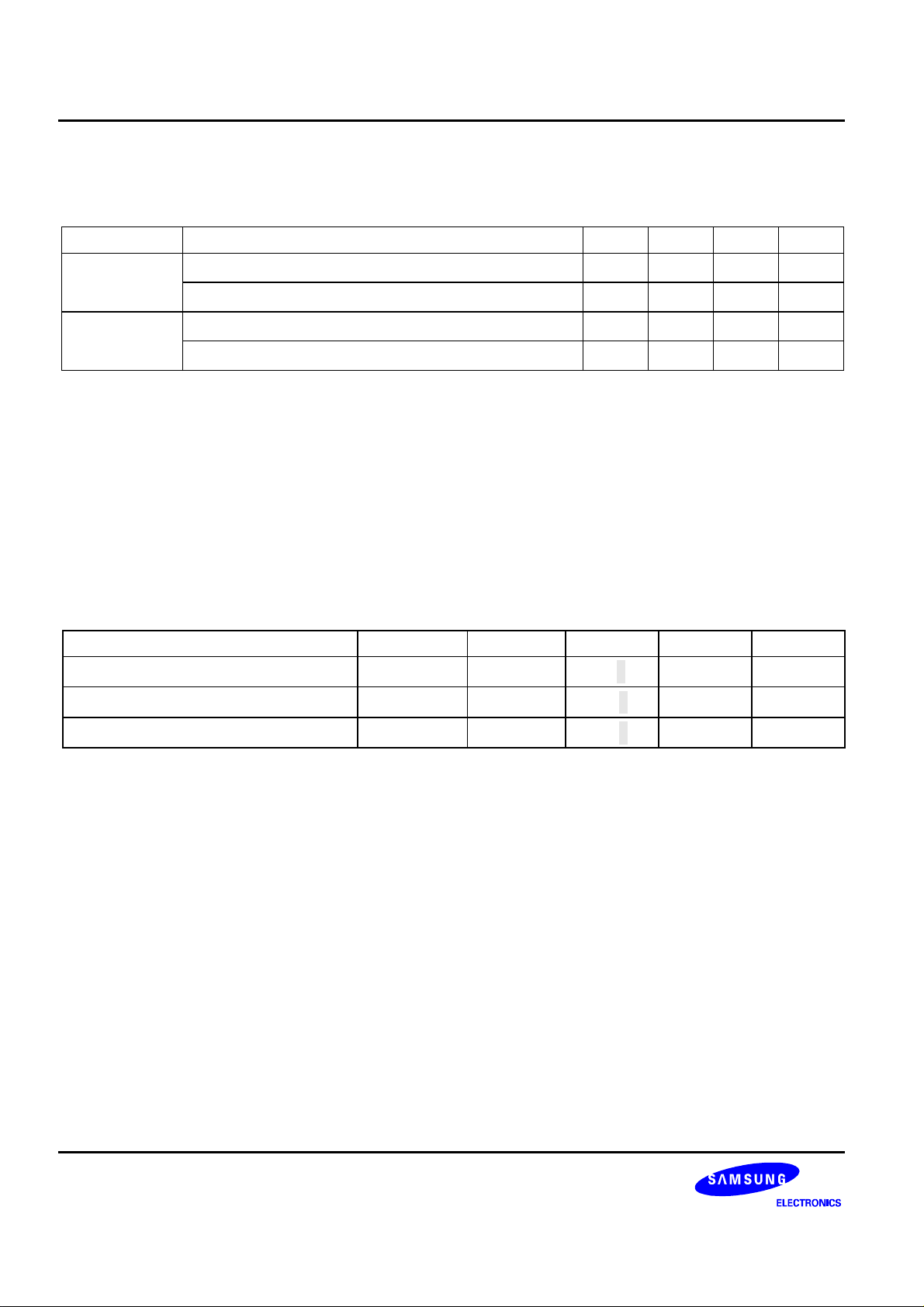

4. Table 17-3. D.C. Electrical Characteristics (PAGE 17-3)

(T

= – 25 °C to + 85 °C, V

A

DD

= V

to 5.5 V)

LVR

Parameter Symbol Conditions Min Typ. Max Unit

Input high voltage

V

V

IH1

DD

= V

to 5.5 V

LVR

0.8 VDD

–

VDD

All port and nRESET

Input low voltage

V

V

IH2

V

V

IL1

= V

DD

and XTIN

X

IN

= V

DD

(to 5.5 V

LVR

to 5.5 V

LVR

V

DD

– 0.5

– –

0.2VDD

All ports and nRESET

V

V

IL2

= V

DD

and XTIN

X

IN

to 5.5 V

LVR

0.4

V

V

3

Page 5

USER’S MANUAL ERRATA S3C84E5/C84E9/P84E9

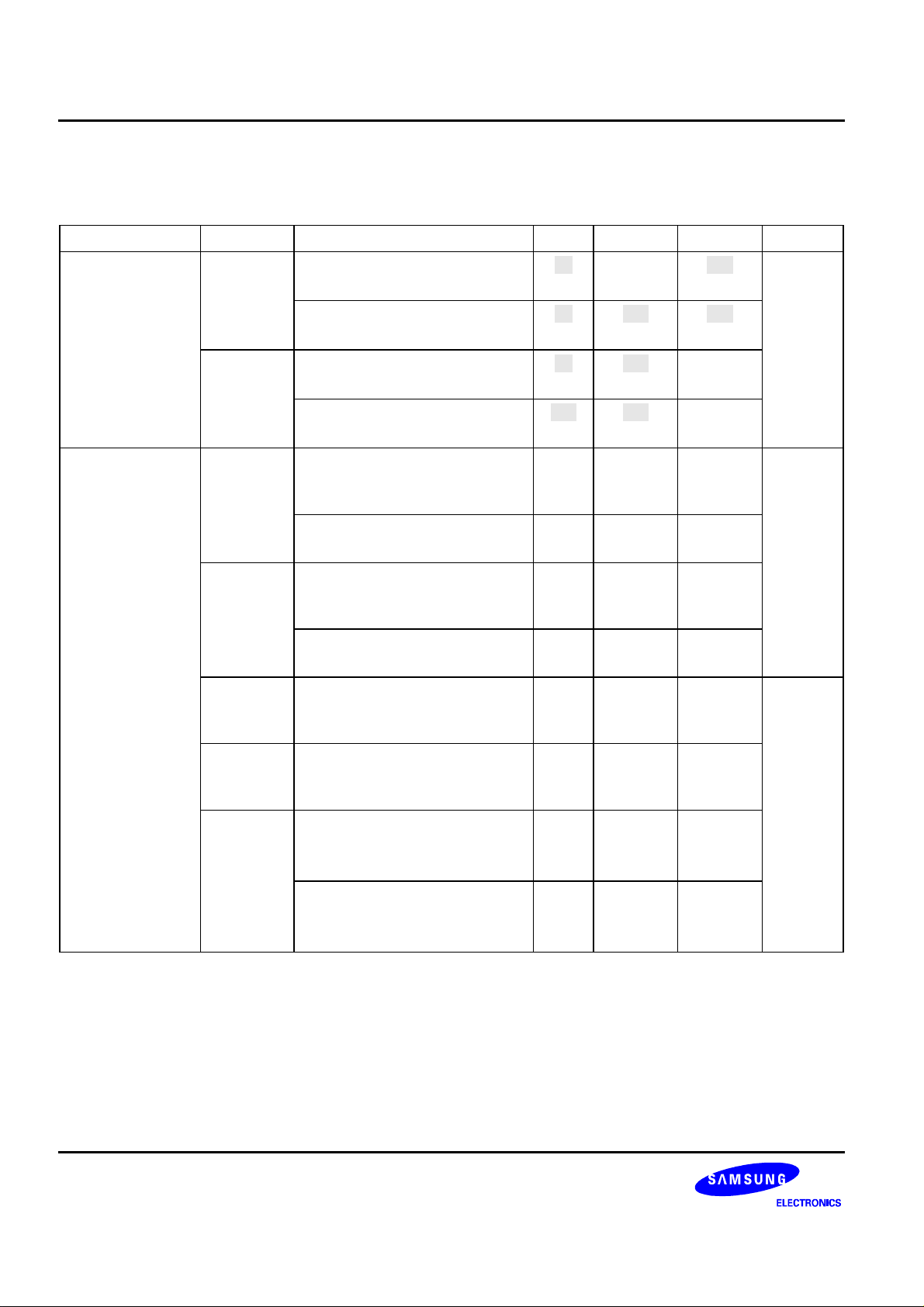

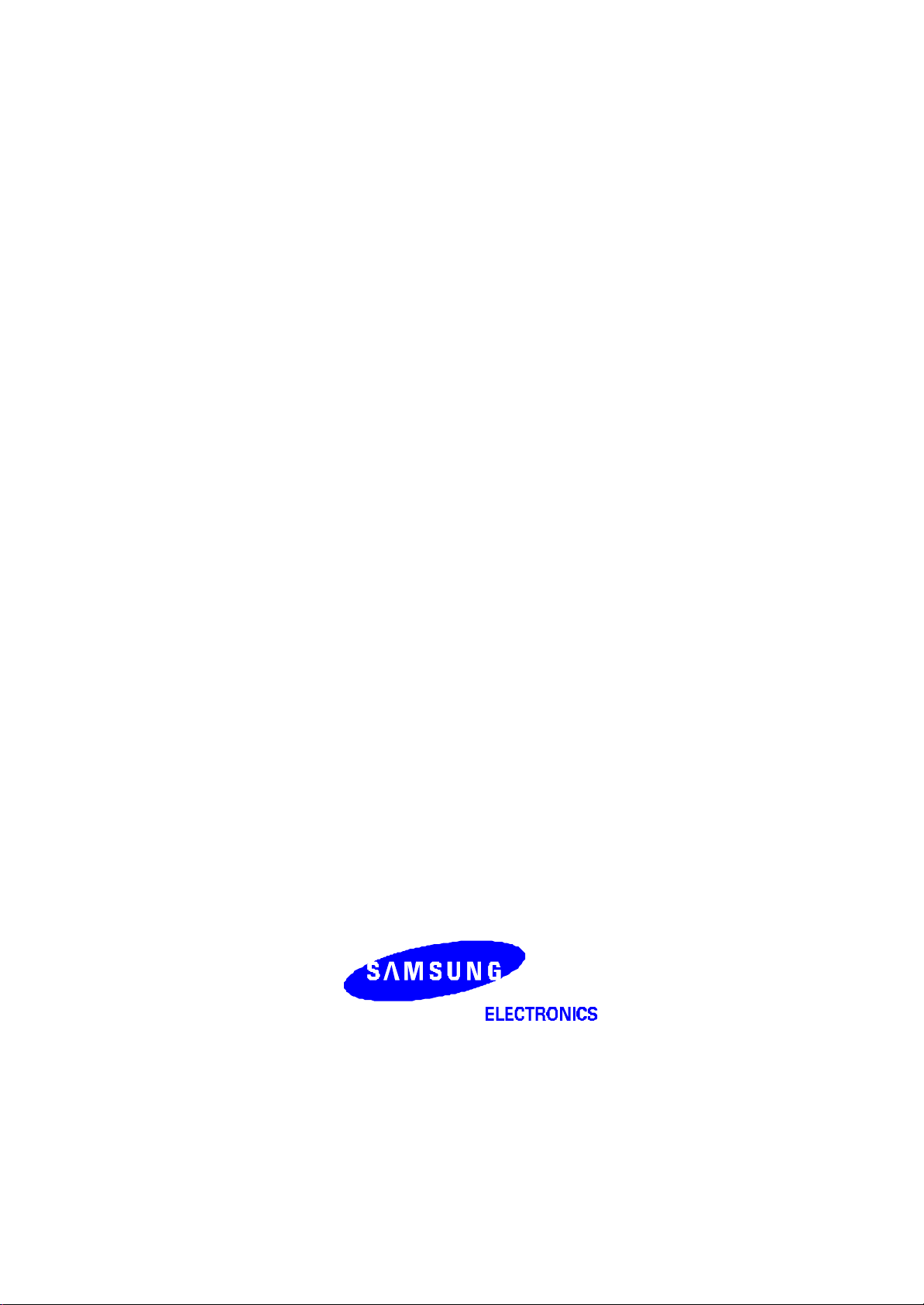

5. Table 17-3. D.C. Electrical Characteristics (PAGE 17-4)

(T

= – 25 °C to + 85 °C, V

A

DD

= V

to 5.5 V)

LVR

Parameter Symbol Conditions Min Typ. Max Unit

Pull-up resistor

R

P1

V

DD

= 5 V; V

= 0 V , T

IN

= 25°C

A

10 50 100

kΩ

All I/O pins except nRESET

V

DD

= 3 V; V

= 0 V, T

IN

= 25°C

A

20 100 400

All I/O pins except nRESET

R

P2

V

= 5 V; VIN = 0 V, T

DD

= 25°C

A

50 250 600

nRESET only

V

DD

= 3 V; V

= 0 V, T

IN

= 25°C

A

100 500 1000

nRESET only

Supply current

(1)

I

DD1

(2)

V

= 4.5V to 5.5V

DD

– 15 30 mA

RUN mode

12 MHz CPU clock

= V

V

DD

to 5.5 V

LVR

4 10

8 MHz CPU clock

V

I

DD2

= 4.5 V to 5.5 V

DD

3.4 7

Idle mode

12 MHz CPU clock

= V

V

DD

to 5.5 V

LVR

1 2.5

8 MHz CPU clock

I

DD3

Sub operating: main-osc stop

V

DD

= V

to 3.3 V

LVR

– 100 150 uA

32768 Hz crystal oscillator

I

DD4

Sub idle mode: main-osc stop

= V

V

DD

to 3.3 V

LVR

– 90 140

32768 Hz crystal oscillator

V

I

DD5

= 4.5 V to 5.5 V,

DD

T

= 25 °C

A

– 80 100

Stop mode

= V

V

DD

T

= 25 °C

A

to 3.3 V,

LVR

– 45 80

Stop mode

4

Page 6

S3C84E5/C84E9/P84E9 USER’S MANUAL ERRATA

6. Table 17-4. A.C. Electrical Characteristics (PAGE 17-5)

(T

= – 25 °C to + 85 °C, V

A

DD

= V

to 5.5 V)

LVR

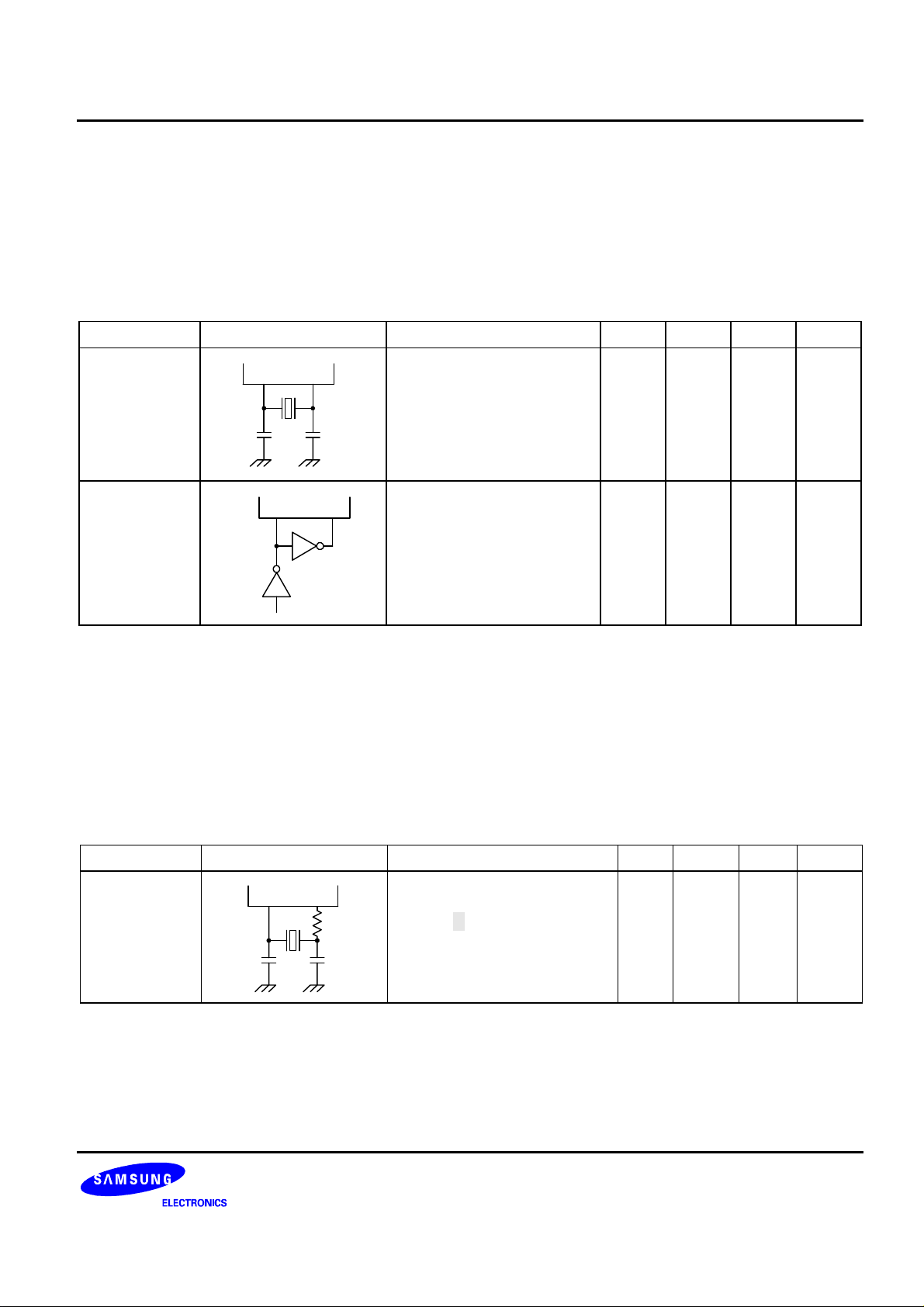

7. Table 17-5. Main Oscillator Frequency (PAGE 17-6)

(TA = – 25 °C + 85 °C, V

DD

= V

to 5.5 V)

LVR

Oscillator Clock Circuit Test Condition Min Typ. Max Unit

Main crystal or

ceramic

X

IN

C1 C2

= V

X

OUT

DD

to 5.5 V

LVR

1 – 12 MHz

V

External clock

(main system)

X

INXOUT

DD

= V

to 5.5 V

LVR

1 – 12

V

8. Table 17-6. Main Oscillator Clock Stabilization Time(PAGE 17-6)

(TA = – 25 °C + 85 °C, VDD = V

to 5.5 V)

LVR

9. Table 17-7. Sub Oscillator Frequency (PAGE 17-7)

(TA = –25 °C + 85 °C, V

Oscillator Clock Circuit Test Condition Min Typ. Max Unit

Crystal

= V

DD

XTINXT

to 5.5 V)

LVR

OUT

R

C1 C2

Crystal oscillation frequency

C1 = 100 pF, C2 = 100 pF

R = 330 Ω

XT

and XT

IN

are connected

OUT

with R and C by soldering.

32 32.768 34 kHz

5

Page 7

USER’S MANUAL ERRATA S3C84E5/C84E9/P84E9

10. Table 17-8. Subsystem Oscillator (crystal) Stabilization Time (PAGE 17-7)

(T

= 25 °C)

A

Oscillator Test Condition Min Typ. Max Unit

Normal mode

Strong mode

V

DD

= V

V

DD

= 4.5 V to 5.5 V

V

DD

= V

V

DD

to 3.3 V

LVR

to 3.3 V

LVR

– 800 1600 ms

– 10 s

– 400 800 ms

– 150 300

= 4.5 V to 5.5 V

11. Table 17-9. Data Retention Supply Voltage in Stop Mode (PAGE 17-8)

(T

= – 25 °C to + 85 °C, V

A

DD

= V

to 5.5 V)

LVR

12. Table 17-10. UART Timing Characteristics in Mode 0 (PAGE 17-10)

(T

= – 25 °C to + 85 °C, V

A

DD

= V

Parameter Symbol Min Typ. Max Unit

Serial port clock cycle time

Output data setup to clock rising edge

Serial port clock High, Low level width

to 5.5 V, Load capacitance = 80 pF)

LVR

t

HIGH

t

SCK

t

S1

, t

LOW

500

300

200

t

CPU

t

CPU

t

CPU

× 6

× 5

× 3

700 ns

–

400

6

Page 8

S3C84E5/C84E9/P84E9 USER’S MANUAL ERRATA

13. Table 17-11. A/D Converter Electrical Characteristics (PAGE 17-11)

(TA = – 25 °C to + 85 °C, VDD = V

to 5.5 V, VSS = 0 V)

LVR

14. Table 17-12. LVR (Low Voltage Reset) Circuit Characteristics (PAGE 17-12)

(T

= 25 °C)

A

Parameter Symbol Test Condition Min Typ Max Unit

LVR voltage level

V

LVR

= 25 °C

T

A

2.6 2.9 3.2 V

15. Figure 17-8. Operating Voltage Range(PAGE 17-12)

Main Oscillator Frequency

CPU Clock

12 MHz

8 MHz

1 MHz

1234567

VLVR 5.5 V

Supply Voltage (V)

Minimum instruction clock = 1/4 Oscillator clock

16. Table 19-2. Comparison of S3P84E9 and S3C84E5/C84E9 Features (PAGE 17-12)

Characteristic S3P84E9 S3C84E5/C84E9

Operating voltage (VDD) V

to 5.5 V V

LVR

LVR

to 5.5 V

7

Page 9

S3C84E5/C84E9/P84E9

8-BIT CMOS

MICROCONTROLLERS

USER'S MANUAL

Revision 1.1

Page 10

Important Notice

The information in this publication has been carefully

checked and is believed to be entirely accurate at the

time of publication. Samsung assumes no

responsibility, however, for possible errors or

omissions, or for any consequences resulting from

the use of the information contained herein.

Samsung reserves the right to make changes in its

products or product specifications with the intent to

improve function or design at any time and without

notice and is not required to update this

documentation to reflect such changes.

This publication does not convey to a purchaser of

semiconductor devices described herein any license

under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or

guarantee regarding the suitability of its products for

any particular purpose, nor does Samsung assume

any liability arising out of the application or use of any

product or circuit and specifically disclaims any and

all liability, including without limitation any

consequential or incidental damages.

"Typical" parameters can and do vary in different

applications. All operating parameters, including

"Typicals" must be validated for each customer

application by the customer's technical experts.

Samsung products are not designed, intended, or

authorized for use as components in systems

intended for surgical implant into the body, for other

applications intended to support or sustain life, or for

any other application in which the failure of the

Samsung product could create a situation where

personal injury or death may occur.

Should the Buyer purchase or use a Samsung

product for any such unintended or unauthorized

application, the Buyer shall indemnify and hold

Samsung and its officers, employees, subsidiaries,

affiliates, and distributors harmless against all claims,

costs, damages, expenses, and reasonable attorney

fees arising out of, either directly or indirectly, any

claim of personal injury or death that may be

associated with such unintended or unauthorized use,

even if such claim alleges that Samsung was

negligent regarding the design or manufacture of said

product.

S3C84E5/C84E9/P84E9 8-Bit CMOS Microcontrollers

User's Manual, Revision 1.1

Publication Number: 21.1-S3-C84E5/C84E9/P84E9-082005

© 2005 Samsung Electronics

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any

form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written

consent of Samsung Electronics.

Samsung Electronics' microcontroller business has been awarded full ISO-14001

certification (BSI Certificate No. FM24653). All semiconductor products are designed

and manufactured in accordance with the highest quality standards and objectives.

Samsung Electronics Co., Ltd.

San #24 Nongseo-Ri, Giheung-Eup

Yongin-City, Gyeonggi-Do, Korea

C.P.O. Box #37, Suwon 440-900

TEL: (82)-(31)-209-5238

FAX: (82)-(31)-209-6494

Home Page: http://www.samsung.com

Printed in the Republic of Korea

Page 11

Preface

The S3C84E5/C84E9/P84E9 Microcontroller User's Manual is designed for application designers and programmers

who are using the S3C84E5/C84E9/P84E9 microcontroller for application development. It is organized in two main

parts:

Part I Programming Model Part II Hardware Descriptions

Part I contains software-related information to familiarize you with the microcontroller's architecture, programming

model, instruction set, and interrupt structure. It has six chapters:

Chapter 1 Product Overview

Chapter 2 Address Spaces

Chapter 3 Addressing Modes

Chapter 1, "Product Overview, " is a high-level introduction to S3C84E5/C84E9/P84E9 with general product

descriptions, as well as detailed information about individual pin characteristics and pin circuit types.

Chapter 2, "Address Spaces," describes program and data memory spaces, the internal register file, and register

addressing. Chapter 2 also describes working register addressing, as well as system stack and user-defined stack

operations.

Chapter 3, "Addressing Modes," contains detailed descriptions of the addressing modes that are supported by the

S3C8-series CPU.

Chapter 4, "Control Registers," contains overview tables for all mapped system and peripheral control register values,

as well as detailed one-page descriptions in a standardized format. You can use these easy-to-read, alphabetically

organized, register descriptions as a quick-reference source when writing programs.

Chapter 5, "Interrupt Structure," describes the S3C84E5/C84E9/P84E9 interrupt structure in detail and further

prepares you for additional information presented in the individual hardware module descriptions in Part II.

Chapter 6, "Instruction Set," describes the features and conventions of the instruction set used for all S3C8-series

microcontrollers. Several summary tables are presented for orientation and reference. Detailed descriptions of each

instruction are presented in a standard format. Each instruction description includes one or more practical examples

of how to use the instruction when writing an application program.

A basic familiarity with the information in Part I will help you to understand the hardware module descriptions in Part

II. If you are not yet familiar with the S3C8-series microcontroller family and are reading this manual for the first time,

we recommend that you first read Chapters 1–3 carefully. Then, briefly look over the detailed information in Chapters

4, 5, and 6. Later, you can reference the information in Part I as necessary.

Chapter 4 Control Registers

Chapter 5 Interrupt Structure

Chapter 6 Instruction Set

Part II "hardware Descriptions," has detailed information about specific hardware components of the

S3C84E5/C84E9/P84E9 microcontroller. Also included in Part II are electrical, mechanical, OTP, and development

tools data. It has 14 chapters:

Chapter 7 Clock Circuit

Chapter 8 RESET and Power-Down

Chapter 9 I/O Ports

Chapter 10 Basic Timer

Chapter 11 8-bit Timer A/B

Chapter 12 16-bit Timer 1(0,1)

Chapter 13 UART

Two order forms are included at the back of this manual to facilitate customer order for S3C84E5/C84E9/P84E9

microcontrollers: the Mask ROM Order Form, and the Mask Option Selection Form. You can photocopy these

forms, fill them out, and then forward them to your loc al Samsung Sales Representative.

S3C84E5/C84E9/P84E9 MICROCONTROLLER iii

Chapter 14 Watch Timer

Chapter 15 A/D Converter

Chapter 16 Low Voltage Reset

Chapter 17 Electrical Data

Chapter 18 Mechanical Data

Chapter 19 S3P84E9 OTP version

Chapter 20 Development Tools

Page 12

Table of Contents

Part I — Programming Model

Chapter 1 Product Overview

S3C8-SERIES Microcontrollers .............................................................................................................1-1

S3C84E5/C84E9/P84E9 Microcontroller................................................................................................1-1

Features.............................................................................................................................................1-2

Block Diagram ....................................................................................................................................1-3

Pin Assignment ...................................................................................................................................1-4

Pin Assignment...................................................................................................................................1-5

Pin Descriptions..................................................................................................................................1-6

Pin Circuits .........................................................................................................................................1-8

Chapter 2 Address Spaces

Overview.............................................................................................................................................2-1

Program Memory (ROM)......................................................................................................................2-2

Register Architecture...........................................................................................................................2-3

Register Page Pointer (PP)..........................................................................................................2-5

Register Set 1.............................................................................................................................2-7

Register Set 2.............................................................................................................................2-7

Prime Register Space..................................................................................................................2-8

Working Registers.......................................................................................................................2-9

Using the Register Pointers..........................................................................................................2-10

Register Addressing ............................................................................................................................2-12

Common Working Register Area (C0h–Cfh)....................................................................................2-14

4-Bit Working Register Addressing................................................................................................2-15

8-Bit Working Register Addressing................................................................................................2-17

System and User Stack .......................................................................................................................2-19

Chapter 3 Addressing Modes

Overview.............................................................................................................................................3-1

Register Addressing Mode (R)..............................................................................................................3-2

Indirect Register Addressing Mode (IR) ..................................................................................................3-3

Indexed Addressing Mode (X) ...............................................................................................................3-7

Direct Address Mode (DA)....................................................................................................................3-10

Indirect Address Mode (IA) ...................................................................................................................3-12

Relative Address Mode (RA).................................................................................................................3-13

Immediate Mode (IM)...........................................................................................................................3-14

S3C84E5/C84E9/P84E9 MICROCONTROLLER v

Page 13

Table of Contents (Continued)

Chapter 4 Control Registers

Overview.............................................................................................................................................4-1

Chapter 5 Interrupt Structure

Overview.............................................................................................................................................5-1

Interrupt Types ............................................................................................................................5-2

S3C84E5/C84E9/P84E9 Interrupt Structure ...................................................................................5-3

Interrupt Vector Addresses...........................................................................................................5-5

Enable/Disable Interrupt Instructions (EI, DI) ..................................................................................5-7

System-Level Interrupt Control Registers .......................................................................................5-7

Interrupt Processing Control Points...............................................................................................5-8

Peripheral Interrupt Control Registers ............................................................................................5-9

System Mode Register (SYM)......................................................................................................5-10

Interrupt Mask Register (IMR).......................................................................................................5-11

Interrupt Priority Register (IPR) .....................................................................................................5-12

Interrupt Request Register (IRQ) ...................................................................................................5-14

Interrupt Pending Function Types..................................................................................................5-15

Interrupt Source Polling Sequence................................................................................................5-16

Interrupt Service Routines .............................................................................................................5-16

Generating Interrupt Vector Addresses ..........................................................................................5-17

Nesting of Vectored Interrupts.......................................................................................................5-17

Chapter 6 Instruction Set

Overview.............................................................................................................................................6-1

Data Types .................................................................................................................................6-1

Register Addressing ....................................................................................................................6-1

Addressing Modes .......................................................................................................................6-1

Flags Register (FLAGS)...............................................................................................................6-6

Flag Descriptions ........................................................................................................................6-7

Instruction Set Notation................................................................................................................6-8

Condition Codes..........................................................................................................................6-12

Instruction Descriptions ................................................................................................................6-13

vi S3C84E5/C84E9/P84E9 MICROCONTROLLER

Page 14

Table of Contents (Continued)

Part II Hardware Descriptions

Chapter 7 Clock Circuit

Overview.............................................................................................................................................7-1

System Clock Circuit ...................................................................................................................7-1

Clock Status During Power-Down Modes.......................................................................................7-2

System Clock Control Register (CLKCON).....................................................................................7-3

Chapter 8 RESET and Power-Down

System Reset.....................................................................................................................................8-1

Overview.....................................................................................................................................8-1

Normal Mode RESET Operation....................................................................................................8-1

Hardware RESET Values .............................................................................................................8-2

Power-Down Modes.............................................................................................................................8-5

Stop Mode ..................................................................................................................................8-5

Idle Mode....................................................................................................................................8-6

Chapter 9 I/O Ports

Overview.............................................................................................................................................9-1

Port Data Registers .....................................................................................................................9-2

Port 0.........................................................................................................................................9-3

Port 1.........................................................................................................................................9-5

Port 2.........................................................................................................................................9-7

Port 3.........................................................................................................................................9-12

Port 4.........................................................................................................................................9-14

Chapter 10 Basic Timer

Overview.............................................................................................................................................10-1

Basic Timer (BT) .........................................................................................................................10-1

Basic Timer Control Register (BTCON)..........................................................................................10-1

Basic Timer Function Des cription..................................................................................................10-3

S3C84E5/C84E9/P84E9 MICROCONTROLLER vii

Page 15

Table of Contents (Continued)

Chapter 11 8-bit Timer A/B

8-Bit Timer A.......................................................................................................................................11-1

Overview.....................................................................................................................................11-1

Function Description ....................................................................................................................11-2

Timer A Control Register (TACON)................................................................................................11-3

Block Diagram ............................................................................................................................11-4

8-Bit Timer B.......................................................................................................................................11-5

Overview.....................................................................................................................................11-5

Block Diagram ............................................................................................................................11-5

Timer B Control Register (TBCON)................................................................................................11-6

Timer B Pulse Width Calculations.................................................................................................11-7

Chapter 12 16-bit Timer 1(0, 1)

Overview.............................................................................................................................................12-1

Function Description ....................................................................................................................12-2

Timer 1(0,1) Control Register (T1CON0, T1CON1)...........................................................................12-3

Block Diagram ............................................................................................................................12-6

Chapter 13 UART

Overview.............................................................................................................................................13-1

Programming Procedure...............................................................................................................13-1

Uart Control Register (UARTCON) .................................................................................................13-2

Uart Interrupt Pending Register (UARTPND) ...................................................................................13-4

Uart Data Register (UDATA) .........................................................................................................13-5

Uart Baud Rate Data Register (BRDATAH, BRDATAL)....................................................................13-6

Baud Rate Calculations ................................................................................................................13-6

Block Diagram ....................................................................................................................................13-8

Uart Mode 0 Function Description.................................................................................................13-9

Uart Mode 1 Function Description.................................................................................................13-10

Uart Mode 2 Function Description.................................................................................................13-11

Serial Communication for Multiprocessor Configurations ..................................................................13-13

Chapter 14 Watch Timer

Overview.............................................................................................................................................14-1

Watch Timer Control Register (WTCON: R/W)...............................................................................14-2

Watch Timer Circuit Diagram........................................................................................................14-3

viii S3C84E5/C84E9/P84E9 MICROCONTROLLER

Page 16

Table of Contents (Continued)

Chapter 15 8-bit Analog-to-Digital Converter

Overview.............................................................................................................................................15-1

Function Description ............................................................................................................................15-1

A/D Converter Control Register (ADCON) .......................................................................................15-2

Internal Reference Voltage Levels..................................................................................................15-4

Conversion Timing .......................................................................................................................15-4

Internal A/D Conversion Procedure................................................................................................15-5

Chapter 16 Low Voltage RESET

Overview.............................................................................................................................................16-1

Chapter 17 Electrical Data

Overview.............................................................................................................................................17-1

Chapter 18 Mechanical Data

Overview.............................................................................................................................................18-1

Chapter 19 S3P84E9 OTP Version

Overview.............................................................................................................................................19-1

Operating Mode Characteristics ....................................................................................................19-3

Chapter 20 Development Tools

Overview.............................................................................................................................................20-1

Shine .........................................................................................................................................20-1

Sasm.........................................................................................................................................20-1

Sama Assembler.........................................................................................................................20-1

HEX2ROM..................................................................................................................................20-1

Target Boards .............................................................................................................................20-2

Otp............................................................................................................................................20-2

Otp Programming Socket Adapter.................................................................................................20-2

TB84E5/84E9 Target Board..........................................................................................................20-3

Idle Led ......................................................................................................................................20-4

Stop Led.....................................................................................................................................20-4

Port (P0.0, P0.1) Selection (SUB -OSC or normal input)..................................................................20-4

S3C84E5/C84E9/P84E9 MICROCONTROLLER ix

Page 17

List of Figures

Figure Title Page

Number Number

1-1 S3C84E5/C84E9/P84E9 Block Diagram................................................................1-3

1-2 S3C84E5/C84E9/P84E9 Pin Assignment (44-pin QFP)...........................................1-4

1-3 S3C84E5/C84E9/P84E9 Pin Assignment (42-pin SDIP) ..........................................1-5

1-4 Pin Circuit Type B (RESETB)...............................................................................1-8

1-5 Pin Circuit Type C...............................................................................................1-8

1-6 Pin Circuit Type D (P0.2-P0.7, P1, P4.3-P4.5) .......................................................1-9

1-7 Pin Circuit Type D-1 (P2, and P4.0-P4.2)...............................................................1-9

1-8 Pin Circuit Type E (P3) ........................................................................................1-10

1-9 Pin Circuit Type F (P0.0, P0.1).............................................................................1-10

2-1 Program Memory Address Space.........................................................................2-2

2-2 Internal Register File Organization.........................................................................2-4

2-3 Register Page Pointer (PP)..................................................................................2-5

2-4 Set 1, Set 2, Prime Area Register .........................................................................2-8

2-5 8-Byte Working Register Areas (Slices).................................................................2-9

2-6 Contiguous 16 Byte Working Register Block ..........................................................2-10

2-7 Non-Contiguous 16 Byte Working Register Block...................................................2-11

2-8 16-Bit Register Pair .............................................................................................2-12

2-9 Register File Addressing......................................................................................2-13

2-10 Common Working Register Area...........................................................................2-14

2-11 4-Bit Working Register Addressing........................................................................2-16

2-12 4-Bit Working Register Addressing Example..........................................................2-16

2-13 8-Bit Working Register Addressing........................................................................2-17

2-14 8-Bit Working Register Addressing Example..........................................................2-18

2-15 Stack Operations ................................................................................................2-19

3-1 Register Addressing ............................................................................................3-2

3-2 Working Register Addressing ...............................................................................3-2

3-3 Indirect Register Addressing to Register File ..........................................................3-3

3-4 Indirect Register Addressing to Program Memory ...................................................3-4

3-5 Indirect Working Register Addressing to Register File .............................................3-5

3-6 Indirect Working Register Addressing to Program or Data Memory ...........................3-6

3-7 Indexed Addressing to Register File......................................................................3-7

3-8 Indexed Addressing to Program or Data Memory with Short Offset...........................3-8

3-9 Indexed Addressing to Program or Data Memory....................................................3-9

3-10 Direct Addressing for Load Instructions..................................................................3-10

3-11 Direct Addressing for Call and Jump Instructions....................................................3-11

3-12 Indirect Addressing..............................................................................................3-12

3-13 Relative Addressing .............................................................................................3-13

3-14 Immediate Addressing .........................................................................................3-14

4-1 Register Description Format .................................................................................4-4

S3C84E5/C84E9/P84E9 MICROCONTROLLER xi

Page 18

List of Figures (Continued)

Figure Title Page

Number Number

5-1 S3C8-Series Interrupt Types.................................................................................5-2

5-2 S3C84E5/C84E9/P84E9 Interrupt Structure ...........................................................5-4

5-3 ROM Vector Address Area ...................................................................................5-5

5-4 Interrupt Function Diagram ...................................................................................5-8

5-5 System Mode Register (SYM)..............................................................................5-10

5-6 Interrupt Mask Register (IMR)...............................................................................5-11

5-7 Interrupt Request Priority Groups ..........................................................................5-12

5-8 Interrupt Priority Register (IPR) .............................................................................5-13

5-9 Interrupt Request Register (IRQ) ...........................................................................5-14

6-1 System Flags Register (FLAGS)...........................................................................6-6

7-1 Main Oscillator Circuit (Crystal or Ceramic Oscillator) .............................................7-1

7-2 Sub-System Oscillator Circuit (Crystal Oscillator)...................................................7-1

7-3 System Clock Circuit Diagram ..............................................................................7-2

7-4 System Clock Control Register (CLKCON).............................................................7-3

7-5 Oscillator Control Register (OSCCON)...................................................................7-4

7-6 STOP Control Register (STPCON) ........................................................................7-4

9-1 Port 0 High Byte Control Register (P0CONH).........................................................9-3

9-2 Port 0 Low Byte Control Register (P0CONL) ..........................................................9-4

9-3 Port 1 High-Byte Control Register (P1CONH).........................................................9-5

9-4 Port 1 Low-Byte Control Register (P1CONL) ..........................................................9-6

9-5 Port 2 High-Byte Control Register (P2CONH).........................................................9-8

9-6 Port 2 Low-Byte Control Register (P2CONL) ..........................................................9-9

9-7 Port 2 Interrupt Pending Register (P2INTPND) ........................................................9-10

9-8 Port 2 Interrupt Control Register (P2INT) ................................................................9-11

9-9 Port 3 High-Byte Control Register (P3CONH).........................................................9-12

9-10 Port 3 Low-Byte Control Register (P3CONL)..........................................................9-13

9-11 Port 4 High-Byte Control Register (P4CONH) .........................................................9-15

9-12 Port 4 Low-Byte Control Register (P4CONL)..........................................................9-15

9-13 Port 4 Interrupt Pending Register (P4INTPND)........................................................9-16

9-14 Port 4 Interrupt Control Register (P4INT) ................................................................9-16

10-1 Basic Timer Control Register (BTCON) ..................................................................10-2

10-2 Basic Timer Block Diagram ..................................................................................10-4

11-1 Timer A Control Register (TACON) ........................................................................11-3

11-2 Timer A Functional Block Diagram ........................................................................11-4

11-3 Timer B Functional Block Diagram ........................................................................11-5

11-4 Timer B Control Register (TBCON) ........................................................................11-6

11-5 Timer B Data Registers (TBDATAH, TBDATAL)......................................................11-6

11-6 Timer B Output Flip Flop Waveforms in Repeat Mode .............................................11-8

xii S3C84E5/C84E9/P84E9 MICROCONTROLLER

Page 19

List of Figures (Concluded)

Page Title Page

Number Number

12-1 Timer 1(0,1) Control Register (T1CON0, T1CON1)...................................................12-4

12-2 Timer A, Timer 1(0,1) Pending Register (TINTPND) .................................................12-5

12-3 Timer 1(0,1) Functional Block Diagram ..................................................................12-6

13-1 UART Control Register (UARTCON)......................................................................13-3

13-2 UART Interrupt Pending Register (UARTPND)........................................................13-4

13-3 UART Data Register (UDATA)...............................................................................13-5

13-4 UART Baud Rate Data Register (BRDATAH, BRDATAL) .........................................13-6

13-5 UART Functional Block Diagram ...........................................................................13-8

13-6 Timing Diagram for UART Mode 0 Operation ..........................................................13-9

13-7 Timing Diagram for UART Mode 1 Operation..........................................................13-10

13-8 Timing Diagram for UART Mode 2 Operation ..........................................................13-12

13-9 Connection Example for Multiprocessor Serial Data Communications.......................13-14

14-1 Watch Timer Circuit Diagram ................................................................................14-3

15-1 A/D Converter Control Register (ADCON)...............................................................15-2

15-2 A/D Converter Data Register (ADDATAH, ADDATAL)..............................................15-3

15-3 A/D Converter Circuit Diagram..............................................................................15-3

15-4 A/D Converter Timing Diagram ..............................................................................15-4

15-5 Recommended A/D Converter Circuit for Highest Absolute Accuracy........................15-5

16-1 Low Voltage Reset Circuit ....................................................................................16-2

17-1 Input Timing for External Interrupts (Ports 4 and 6)..................................................17-5

17-3 Clock Timing Measurement at XIN.........................................................................17-7

17-4 Stop Mode Release Timing Initiated by RESET......................................................17-8

17-5 Stop Mode (Main) Release Timing Initiated by Interrupts.........................................17-8

17-6 Stop Mode (Sub) Release Timing Initiated by Interrupts...........................................17-9

17-7 Waveform for UART Timing Characteristics ............................................................17-10

17-8 Operating Voltage Range.....................................................................................17-12

17-9 The Circuit Diagram to Improve EFT Characteristics................................................17-12

18-1 42-SDIP-600 Package Dimensions ........................................................................18-1

18-2 44-QFP-1010 Package Dimensions.......................................................................18-2

19-1 S3P84E9 Pin Assignments (42-SDIP Package).....................................................19-1

19-2 S3P84E9 Pin Assignments (44-QFP Package) ......................................................19-2

20-1 SMDS+ or SK-1000 Product Configuration .............................................................20-2

20-2 S3C84E5/S3C84E9/S3P84E9 Target Board Configuration.......................................20-3

20-3 44-Pin Connector pin assignment for TB84E5/84E9................................................20-5

20-4 TB84E5/84E9 Adapter Cable for 44pin Connector Package.....................................20-6

S3C84E5/C84E9/P84E9 MICROCONTROLLER xiii

Page 20

List of Tables

Table Title Page

Number Number

1-1 S3C84E5/C84E9/P84E9 Pin Descriptions ..............................................................1-6

2-1 S3C84E5/C84E9/P84E9 Register Type Summary ..................................................2-3

4-1 Set 1 Registers ...................................................................................................4-1

4-2 Set 1, Bank 0 Registers.......................................................................................4-2

4-3 Set 1, Bank 1 Registers.......................................................................................4-3

5-1 Interrupt Vectors ..................................................................................................5-6

5-2 Interrupt Control Register Overview........................................................................5-7

5-3 Interrupt Source Control and Data Registers ...........................................................5-9

6-1 Instruction Group Summary..................................................................................6-2

6-2 Flag Notation Conventions....................................................................................6-8

6-3 Instruction Set Symbols .......................................................................................6-8

6-4 Instruction Notation Conventions ...........................................................................6-9

6-5 OPCODE Quick Reference...................................................................................6-10

6-6 Condition Codes..................................................................................................6-12

8-1 S3C84E5/C84E9/P84E9 Set 1 Register Values After RESET ..................................8-2

8-2 S3C84E5/C84E9/P84E9 Set 1, Bank 0 Register Values After RESET......................8-3

8-3 S3C84E5/C84E9/P84E9 Set 1, Bank 1 Register Values After RESET......................8-4

9-1 S3C84E5/C84E9/P84E9 Port Configuration Overview..............................................9-1

9-2 Port Data Register Summary................................................................................9-2

14-1 Watch Timer Control Register (WTCON): Set 1, Bank 0, FAH, R/W.........................14-2

17-1 Absolute Maximum Ratings..................................................................................17-2

17-2 Input/Output Capacitance.....................................................................................17-2

17-3 D.C. Electrical Characteristics..............................................................................17-3

17-4 A.C. Electrical Characteristics..............................................................................17-5

17-2 Input Timing for RESET........................................................................................17-5

17-5 Main Oscillator Frequency (f

17-6 Main Oscillator Clock Stabilization Time (t

17-7 Sub Oscillator Frequency (f

17-8 Subsystem Oscillator (crystal) Stabilization Time (t

17-9 Data Retention Supply Voltage in Stop Mode.........................................................17-8

17-10 UART Timing Characteristics in Mode 0 (10 MHz)..................................................17-10

17-11 A/D Converter Electrical Characteristics ................................................................17-11

17-12 LVR(Low Voltage Reset) Circuit Characteristics ...................................................17-12

).......................................................................17-6

OSC1

)......................................................17-6

ST1

) ........................................................................17-7

OSC2

).........................................17-7

ST2

S3C84E5/C84E9/P84E9 MICROCONTROLLER xv

Page 21

List of Tables (Continued)

Table Title Page

Number Number

19-1 Descriptions of Pins Used to Read/Write the OTP..................................................19-3

19-2 Comparison of S3P84E9 and S3C84E5/C84E9 Features.........................................19-3

19-3 Operating Mode Selection Criteria.........................................................................19-3

20-1 Power Selection Settings for TB84E5/84E9............................................................20-4

20-2 Using Single Header Pins as the Input Path for External Trigger Sources..................20-4

20-3 The Port 0.0 and Port 0.1 selection setting............................................................20-5

xvi S3C84E5/C84E9/P84E9 MICROCONTROLLER

Page 22

List of Programming Tips

Description Page

Number

Chapter 2: Address Spaces

Using the Page Pointer for RAM clear (Page 0, Page 1) ..........................................................................2-6

Setting the Register Pointers................................................................................................................2-10

Using the RPs to Calculate the Sum of a Series of Registers ..................................................................2-11

Addressing the Common Working Register Area....................................................................................2-15

Standard Stack Operations Using PUSH and POP .................................................................................2-20

Chapter 11: 8-bit Timer A/B

To Generate 38 kHz, 1/3duty signal through P4.3...................................................................................11-9

To generate a one pulse signal through P4.3..........................................................................................11-10

Using the Timer A................................................................................................................................11-11

Using the Timer B................................................................................................................................11-12

Chapter 12: 16-bit Timer 1(0,1)

Using the Timer 1(0) ............................................................................................................................12-7

Chapter 14: Watch Timer

Using the Watch Timer ........................................................................................................................14-4

Chapter 15: A/D Converter

Configuring A/D Converter.....................................................................................................................15-6

S3C84E5/C84E9/P84E9 MICROCONTROLLER xvii

Page 23

List of Register Descriptions

Register Full Register Name Page

Identifier Number

ADCON A/D Converter Control Register F7H Set 1, Bank 0.................................................4-5

BTCON Basic Timer Control Register H Set 1 ....................................................................4-6

CLKCON System Clock Control Register D4H Set 1.............................................................4-7

FLAGS System Flags Register D5H Set 1........................................................................4-8

IMR Interrupt Mask Register DDH Set 1 .......................................................................4-9

IPH Instruction Pointer (High Byte) DAH Set 1..............................................................4-10

IPL Instruction Pointer (Low Byte) DBH Set 1..............................................................4-10

IPR Interrupt Priority Register FFH Set 1, Bank 0.........................................................4-11

IRQ Interrupt Request Register DCH Set 1...................................................................4-12

OSCCON Oscillator Control Register FBH Set 1,Bank 0 ......................................................4-13

P0CONH Port 0 Control Register (High Byte) E6H Set 1, Bank 0...........................................4-14

P0CONL Port 0 Control Register (Low Byte) E7H Set 1, Bank 0............................................4-15

P1CONH Port 1 Control Register (High Byte) E8H Set 1, Bank 0...........................................4-16

P1CONL Port 1 Control Register (Low Byte) E9H Set 1, Bank 0............................................4-17

P2CONH Port 2 Control Register (High Byte) EAH Set 1, Bank 0...........................................4-18

P2CONL Port 2 Control Register (Low Byte) EBH Set 1, Bank 0...........................................4-19

P2INT Port 2 Interrupt Control Register ECH Set 1, Bank 0 ...............................................4-20

P2INTPN D Port 2 Interrupt Pending Register EDH Set 1, Bank 0..............................................4-21

P3CONH Port 3 Control Register (High Byte) EEH Set 1, Bank 0...........................................4-22

P3CONL Port 3 Control Register (Low Byte) EFH Set 1, Bank 0............................................4-23

P4CONH Port 4 Control Register (High Byte) F0H Set 1, Bank 0...........................................4-24

P4CONL Port 4 Control Register (Low Byte) F1H Set 1, Bank 0 ............................................4-25

P4INT Port 4 Interrupt Control Register F2H Set 1, Bank 0................................................4-26

P4INTPND Port 4 Interrupt Pending Register F3H Set 1, Bank 0 ..............................................4-27

PP Register Page Pointer DFH Set 1..........................................................................4-28

RP0 Register Pointer 0 D6H Set 1................................................................................4-29

RP1 Register Pointer 1 D7H Set 1................................................................................4-29

SPH Stack Pointer (High Byte) D8H Set 1.....................................................................4-30

SPL Stack Pointer (Low Byte) D9H Set 1.....................................................................4-30

STPCON Stop Control Register E5H Set 1, Bank 0..............................................................4-31

SYM System Mode Register DEH Set 1........................................................................4-32

T1CON0 Timer 1(0) Control Register E8H Set 1, Bank 1.......................................................4-33

T1CON1 Timer 1(1) Control Register E9H Set 1, Bank 1.......................................................4-34

TACON Timer A Control Register E1H Set 1, Bank 1..........................................................4-35

TBCON Timer B Control Register D0H Set 1 ......................................................................4-36

TINTPND Timer A, Timer 1 Interrupt Pending Register E0H Set 1, Bank 1...............................4-37

UARTCON UART Control Register F6H Set 1, Bank 0.............................................................4-38

UARTPND UART Pending and parity control F4H Set 1, Bank 0..............................................4-40

WTCON Watch Timer Control Register FAH Set 1, Bank 0..................................................4-41

S3C84E5/C84E9/P84E9 MICROCONTROLLER xix

Page 24

List of Instruction Descriptions

Instruction Full Register Name Page

Mnemonic Number

ADC Add with Carry ....................................................................................................6-14

ADD Add....................................................................................................................6-15

AND Logical AND........................................................................................................6-16

BAND Bit AND..............................................................................................................6-17

BCP Bit Compare........................................................................................................6-18

BITC Bit Complement ..................................................................................................6-19

BITR Bit Reset ............................................................................................................6-20

BITS Bit Set ................................................................................................................6-21

BOR Bit OR ................................................................................................................6-22

BTJRF Bit Test, Jump Relative on False...........................................................................6-23

BTJRT Bit Test, Jump Relative on True.............................................................................6-24

BXOR Bit XOR ..............................................................................................................6-25

CALL Call Procedure ....................................................................................................6-26

CCF Complement Carry Flag .......................................................................................6-27

CLR Clear..................................................................................................................6-28

COM Complement .......................................................................................................6-29

CP Compare.............................................................................................................6-30

CPIJE Compare, Increment, and Jump on Equal...............................................................6-31

CPIJNE Compare, Increment, and Jump on Non-Equal........................................................6-32

DA Decimal Adjust....................................................................................................6-33

DA Decimal Adjust....................................................................................................6-34

DEC Decrement..........................................................................................................6-35

DECW Decrement Word.................................................................................................6-36

DI Disable Interrupts ................................................................................................6-37

DIV Divide (Unsigned).................................................................................................6-38

DJNZ Decrement and Jump if Non-Zero ..........................................................................6-39

EI Enable Interrupts.................................................................................................6-40

ENTER Enter..................................................................................................................6-41

EXIT Exit ....................................................................................................................6-42

IDLE Idle Operation......................................................................................................6-43

INC Increment ...........................................................................................................6-44

INCW Increment Word...................................................................................................6-45

IRET Interrupt Return ...................................................................................................6-46

JP Jump..................................................................................................................6-47

JR Jump Relative ......................................................................................................6-48

LD Load...................................................................................................................6-49

LD Load...................................................................................................................6-50

LDB Load Bit..............................................................................................................6-51

S3C84E5/C84E9/P84E9 MICROCONTROLLER xxi

Page 25

List of Instruction Descriptions (Continued)

Instruction Full Register Name Page

Mnemonic Number

LDC/LDE Load Memory......................................................................................................6-52

LDC/LDE Load Memory......................................................................................................6-53

LDCD/LDED Load Memory and Decrement...............................................................................6-54

LDCI/LDEI Load Memory and Increment ................................................................................6-55

LDCPD/LDEPD Load Memory with Pre-Decrement ........................................................................6-56

LDCPI/LDEPI Load Memory with Pre-Increment..........................................................................6-57

LDW Load Word ..........................................................................................................6-58

MULT Multiply (Unsigned) ..............................................................................................6-59

NEXT Next...................................................................................................................6-60

NOP No Operation.......................................................................................................6-61

OR Logical OR..........................................................................................................6-62

POP Pop from Stack...................................................................................................6-63

POPUD Pop User Stack (Decrementing)............................................................................6-64

POPUI Pop User Stack (Incrementing).............................................................................6-65

PUSH Push to Stack.....................................................................................................6-66

PUSHUD Push User Stack (Decrementing) ..........................................................................6-67

PUSHUI Push User Stack (Incrementing) ...........................................................................6-68

RCF Reset Carry Flag.................................................................................................6-69

RET Return................................................................................................................6-70

RL Rotate Left..........................................................................................................6-71

RLC Rotate Left through Carry .....................................................................................6-72

RR Rotate Right ........................................................................................................6-73

RRC Rotate Right through Carry ...................................................................................6-74

SB0 Select Bank 0 .....................................................................................................6-75

SB1 Select Bank 1 .....................................................................................................6-76

SBC Subtract with Carry..............................................................................................6-77

SCF Set Carry Flag.....................................................................................................6-78

SRA Shift Right Arithmetic ...........................................................................................6-79

SRP/SRP0/SRP1 Set Register Pointer ............................................................................................6-80

STOP Stop Operation....................................................................................................6-81

SUB Subtract .............................................................................................................6-82

SWAP Swap Nibbles......................................................................................................6-83

TCM Test Complement under Mask..............................................................................6-84

TM Test under Mask .................................................................................................6-85

WFI Wate for Interrupt.................................................................................................6-86

XOR Logical Exclusive OR ...........................................................................................6-87

xxii S3C84E5/C84E9/P84E9 MICROCONTROLLER

Page 26

S3C84E5/C84E9/P84E9 PRODUCT OVERVIEW

1 PRODUCT OVERVIEW

S3C8-SERIES MICROCONTROLLERS

Samsung's S3C8-series of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range

of integrated peripherals, and various mask-programmable ROM sizes. The major CPU features are:

— Efficient register-oriented architecture

— Selectable CPU clock sources

— Idle and Stop power-down mode released by interrupt or reset

— Built-in basic timer with watchdog function

A sophisticated interrupt structure recognizes up to eight-interrupt levels. Each level can have one or more

interrupt sources and vectors. Fast interrupt processing (within a minimum of four CPU clocks) can be assigned to

specific interrupt levels.

S3C84E5/C84E9/P84E9 MICROCONTROLLER

The S3C84E5/C84E9/P84E9 single-chip CMOS microcontrollers are fabricated using the highly advanced CMOS

process technology based on Samsung’s latest CPU architecture.

The S3C84E5 is a microcontroller with a 16K-byte mask-programmable ROM embedded.

The S3C84E9 is a microcontroller with a 32K-byte mask-programmable ROM embedded.

The S3P84E9 is a microcontroller with a 32K-byte OTP ROM embedded.

Using a proven modular design approach, Samsung engineers have successfully developed the

S3C84E5/C84E9/P84E9 by integrating the following peripheral modules with the powerful SAM8 core:

— Five programmable I/O ports (42SDIP: 34pins, 44QFP: 36pins)

— Eleven bit-programmable pins for external interrupts.

— One 8-bit basic timer for oscillation stabilization and watchdog function (system reset).

— Two 8-bit timer/counter and Two 16-bit timer/counter with selectable operating modes.

— One asynchronous UART

— 10-bit 8-channel A/D converter

The S3C84E5/C84E9/P84E9 is versatile microcontroller for home appliances and ADC applications, etc. They are

currently available in 44-pin QFP and 42-pin SDIP package.

1-1

Page 27

PRODUCT OVERVIEW S3C84E5/C84E9/P84E9

FEATURES

CPU

• SAM88RC CPU core

Memory

• 528-bytes internal register file

• 16K/32Kbytes internal program memory

(S3C84E5/C84E9:Mask ROM)

(S3P84E9:OTP)

Oscillation Sources

• Main clock oscillator (Crystal, Ceramic)

• CPU clock divider (1/1, 1/2, 1/8, 1/16)

• 32,768Hz Sub oscillator for watch timer

Instruction Set

• 78 instructions

• IDLE and STOP instructions added for power-

down modes

Instruction Execution Time

• 333 ns at 12-MHz f

(minimum)

OSC

Watch timer

• Real-time and interval time measurement

• Four-frequency outputs for buzzer sound

A/D Converter

• 10-bit resolution

• Eight-analog input channels

• 20us conversion speed at 10MHz f

ADC

clock.

Asynchronous UART

• One Asynchronous UART

• Programmable baud rate generator

• Supports serial data transmit/receive operations

with 8-bit, 9-bit in UART

Built-in RESET Circuit (LVR)

• Low-Voltage reset (LVR value: 2.9V)

Oscillation Frequency

• 1MHz to 12MHz external crystal oscillator

Interrupts

• 21 interrupt sources with 21 vectors.

• 8 level, 21 vector interrupt structure

I/O Ports

• Total 36 bit-programmable pins (44QFP)

Total 34 bit-programmable pins (42SDIP)

Timers and Timer/Counters

• One programmable 8-bit basic timer (BT) for

oscillation stabilization control or watchdog timer

function.

• One 8-bit timer/counter (Timer A) with three

operating modes; Interval mode, capture mode

and PWM mode.

• One 8-bit timer (Timer B) with carrier frequency

(or PWM) generator.

• Two 16-bit timer/counter (Timer 10,11) with

three operating modes; Interval mode, Capture

mode, and PWM mode.

Operating Temperature Range

• –25°C to + 85°C

Operating Voltage Range

• V

to 5.5V

LVR

Package Type

• 42 pin SDIP, 44 pin QFP

1-2

Page 28

S3C84E5/C84E9/P84E9 PRODUCT OVERVIEW

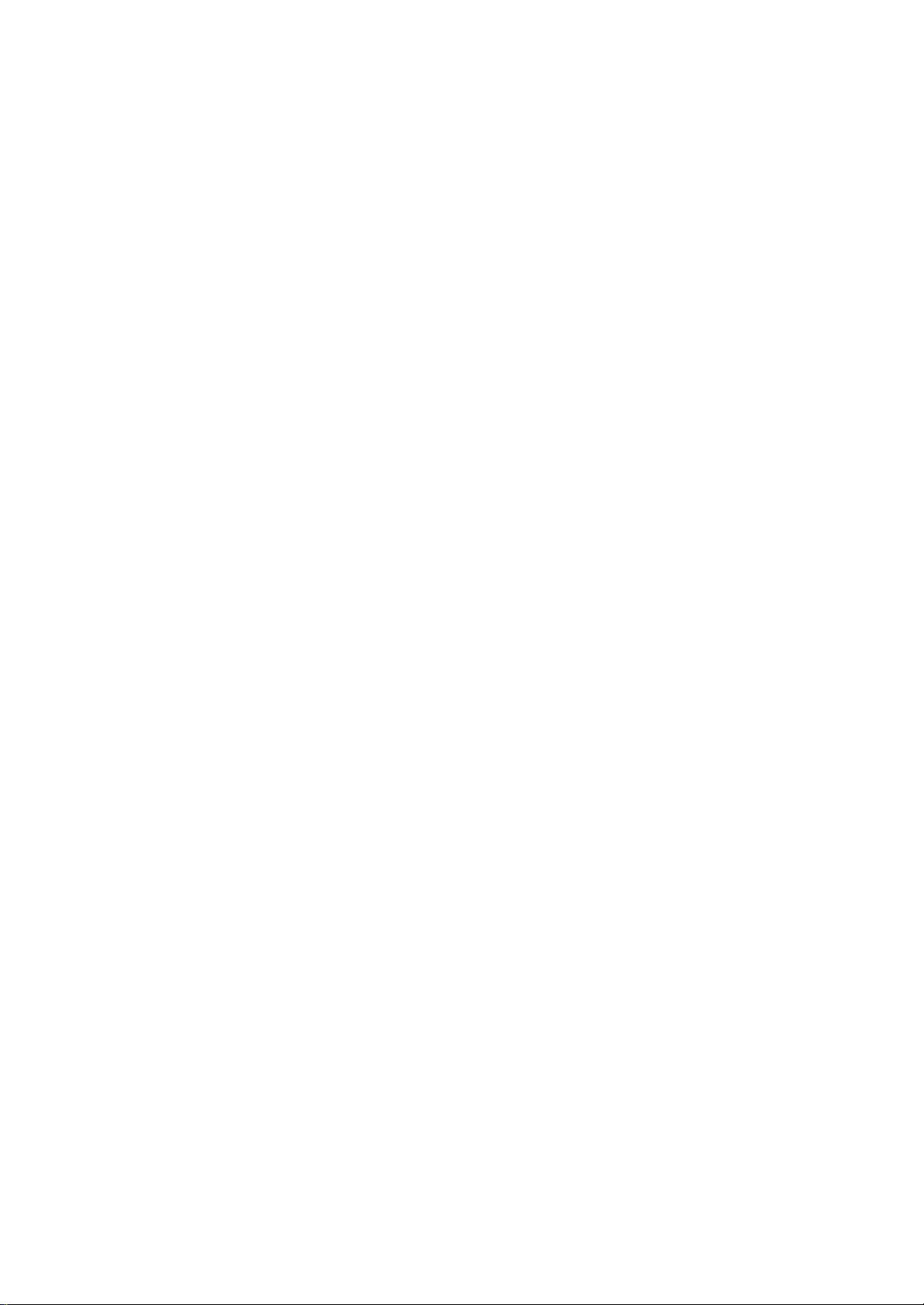

BLOCK DIAGRAM

Xin, XTin

Xout, XTout

nRESET

P1.0/TAOUT

P0.7/TACAP

P0.6 /T A C K

P4.3 /T B P WM

P1 .2 /T1OUT 0

P1 .1 /T1C K0

P0 .5 /T1C AP0

P0.4 /T 1OUT 1

P0.3 /T 1CK1

P0.2 /T 1CAP 1

P1.5/TxD

P1.4 /R x D

P1.3 /B Z O U T

OSC/nRESET

8-Bit

Basic Timer

8-Bit

Timer/Counter

A, B

16-Bit

Timer/Counter

10, 11

UART

Watch Timer

P0.0~P0.7

Port 0

I/O P o rt a n d In te rru p t C o n tro l

SAM88RC

CPU

16K/32K-Byte

ROM

P1.0~P1.5

528-Byte

RAM

Port 1

Port 2

Port 3

Port 4

A/D

P2.0~P2.7/

INT0 ~ IN T 7

P3.0~P3.7/

ADC0~ADC7

P4.0~P4.5

INT8 -IN T 1 0

ADC0~ADC7/

P3.0~P3.7

AV

REF

AVSS

Figure 1-1. S3C84E5/C84E9/P84E9 Block Diagram

1-3

Page 29

PRODUCT OVERVIEW S3C84E5/C84E9/P84E9

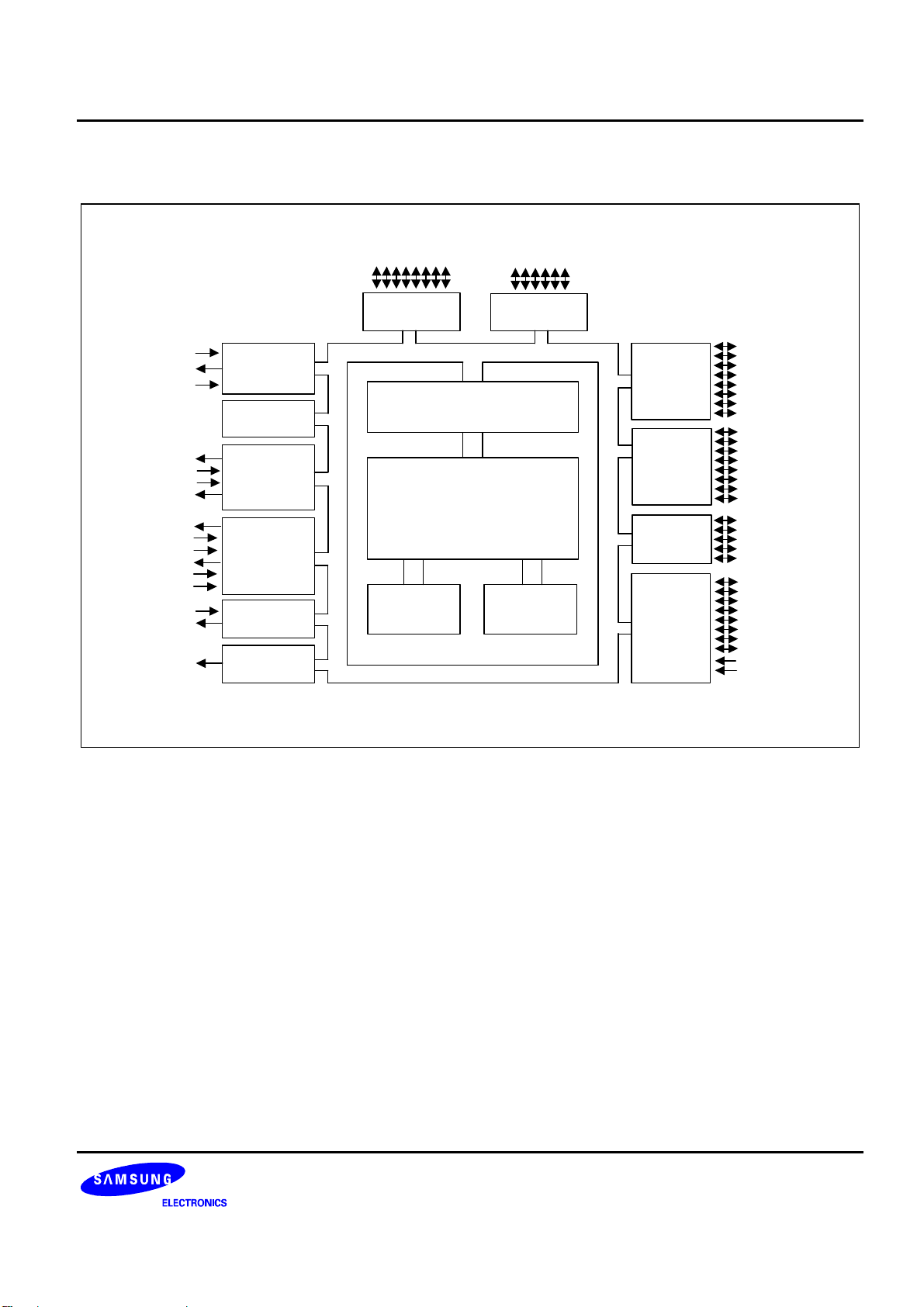

PIN ASSIGNMENT

P4.4

P0.2/T1CAP1

P0.3/T1CK1

P0.4/T1OUT1

P0.5/T1CAP0

P0.6/TACK

P0.7/TACAP

P1.0/TAOUT

P1.1/T1CK0

P1.2/T1OUT0

P1.3/BZOUT

4443424140393837363534

XTout/P0.1

XTin/P0.0

TBPWM/P4.3

INT10/P4.2

VDD

VSS

Xout

Xin

TEST

INT9/P4.1

INT8/P4.0 AVss

1

2

3

4

5

6

7

8

9

10

11

S3C84E5

S3C84E9

S3P84E9

Top View

(44-QFP)

1213141516171819202122

33

32

31

30

29

28

27

26

25

24

23

P1.4/RXD

P1.5/TXD

P3.7/ADC7

P3.6/ADC6

P3.5/ADC5

P3.4/ADC4

P3.3/ADC3

P3.2/ADC2

P3.1/ADC1

P3.0/ADC0

P4.5

AVref

nRESET

INT0/P2.0

INT1/P2.1

INT2/P2.2

INT3/P2.3

INT4/P2.4

INT5/P2.5

INT6/P2.6

INT7/P2.7

Figure 1-2. S3C84E5/C84E9/P84E9 Pin Assignment (44-pin QFP)

1-4

Page 30

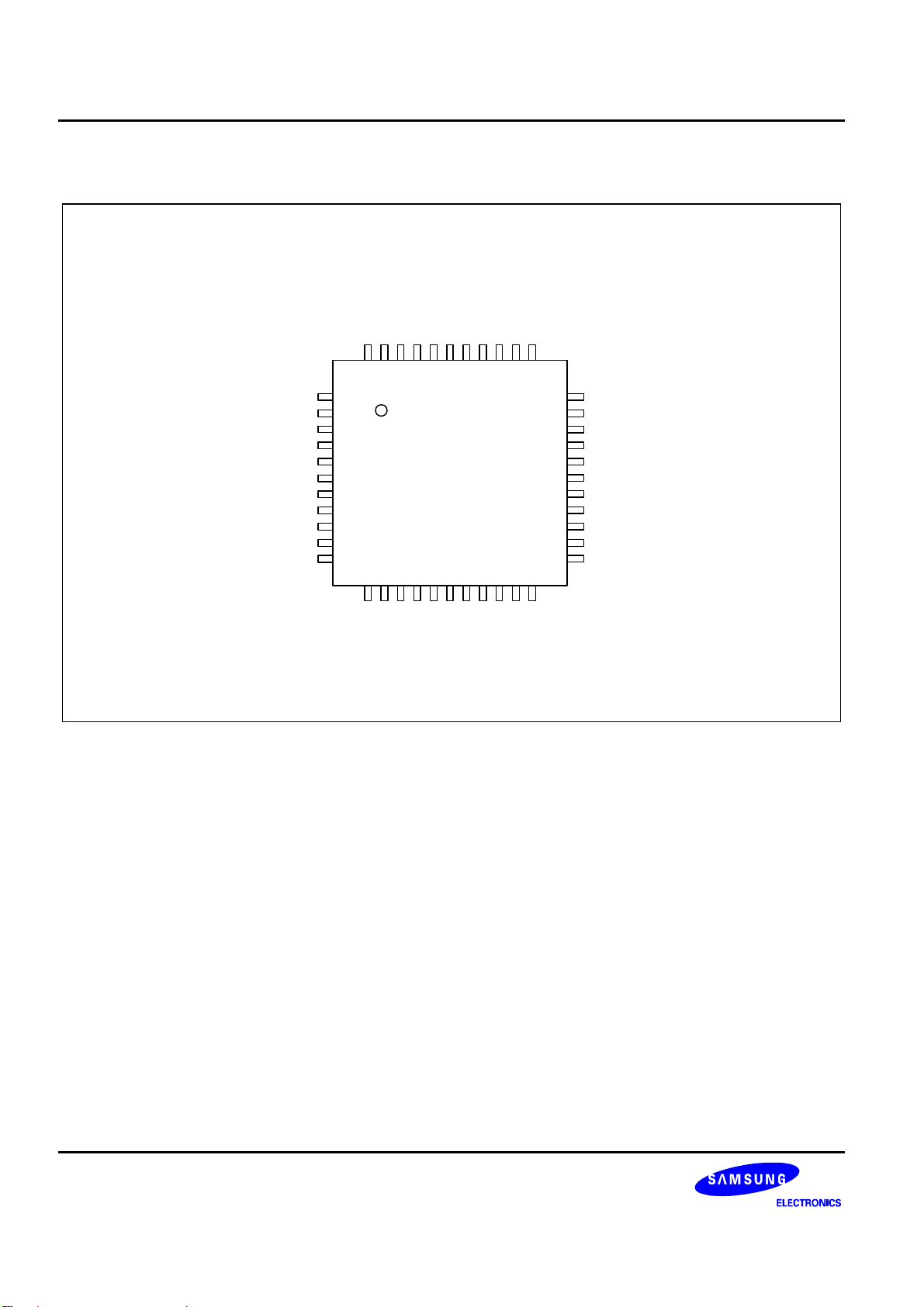

S3C84E5/C84E9/P84E9 PRODUCT OVERVIEW

PIN ASSIGNMENT

TACAP/P0.7

TACK/P0.6

T1CAP0/P0.5

T1OUT1/P0.4

T1CK1/P0.3

T1CAP1/P0.2

XTout/P0.1

XTin/P0.0

TBPWM/P4.3

INT10/P4.2

VDD

VSS

Xout

Xin

TEST

INT9/P4.1

INT8/P4.0

nRESET

INT0/P2.0

INT1/P2.1

INT2/P2.2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

S3C84E5

S3C84E9

S3P84E9

Top View

(42-SDIP)

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

P1.0/TAOUT

P1.1/T1CK0

P1.2/T1OUT0

P1.3/BZOUT

P1.4/RXD

P1.5/TXD

P3.7/ADC7

P3.6/ADC6

P3.5/ADC5

P3.4/ADC4

P3.3/ADC3

P3.2/ADC2

P3.1/ADC1

P3.0/ADC0

AVss

AVref

P2.7/INT7

P2.6/INT6

P2.5/INT5

P2.4/INT4

P2.3/INT3

Figure 1-3. S3C84E5/C84E9/P84E9 Pin Assignment (42-pin SDIP)

1-5

Page 31

PRODUCT OVERVIEW S3C84E5/C84E9/P84E9

PIN DESCRIPTIONS

Table 1-1. S3C84E5/C84E9/P84E9 Pin Descriptions

Pin

Name

Pin

Type

Pin

Description

P0.0–P0.7 I/O Bit programmable port; input or output mode

selected by software; input or push-pull output.

Software assignable pull-up resistor.

Alternately, can be used as I/O for Timer A,

Timer 1(0,1). P0.0 and P0.1 can alternately be

used for subsystem oscillator in/out mode

selected by software

P1.0–P1.5 I/O Bit programmable port; input or output mode

selected by software; input or push-pull output.

Software assignable pull-up resistor. Alternatively

can be used as Timer A, Timer 1(0), UART,

Watch Timer Buzzer output.

P2.0–P2.7 I/O Bit programmable port; input or output mode

selected by software; input or push-pull output.

Software assignable pull-up.

Alternately, can be used as inputs for external

interrupts INT0–INT7. (with noise filters and

interrupt controller)

P3.0–P3.7 I/O Bit programmable port; input or output mode

selected by software; input or push-pull output.

Software assignable pull-up.

Alternately, can be used as analog inputs for A/D

converter modules.

P4.0–P4.5 I/O Bit programmable port; input or output mode

selected by software; input or push-pull output.