Page 1

BSW rv0.1-0417-N01

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

PRODUCT OVERVIEW

S3C24A0

AN APPLICATION PROCESSOR FOR

2.5G/3G MOBILE PHONES

SOC R&D CENTER

SAMSUNG ELECTRONICS CORP.

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-1

Page 2

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

CONTENTS

CH1. INTRODUCTION

CH2. SROM

CH3. SDRAM

CH4. NAND

CH5. BUS MATRIX

CH6. INTERRUPT

CH7. PWM TIMER

CH8. WATCH DOG TIMER

CH9. DMA

CH10. RTC

CH11. UART

CH12. IRDA

CH13. IIC

CH14. IIS

CH15. SPI

CH16. AC97

CH17. USB HOST

CH18. USB DEVICE

CH19. MODEM

CH20. GPIO

CH21. CAMERA

CH22. MPEG4-OVERVIEW

CH23. MOTION ESTIMATION

CH24. MOTION COMPENSATION

CH25. DCTQ

CH26. VLX

CH27. POST

CH28. LCD

CH29. KEYPAD

CH30. ADC & TOUCH

CH31. SD/MMC

CH32. MEMORY STICK

CH33. CLOCK & POWER

CH34. MECHANICAL DATA

1-2

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 3

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

1 INTRODUCTION (PRELIMINARY)

1.1 ARCHITECTURAL OVERVIEW

The S3C24A0 is a 16/32-bit RISC microprocessor, which is designed to provide a cost-effective, low power, and

high performance micro- controller solution for mobile phones and general applications. To provide a sufficient H/W

performance for the 2.5G & 3G communication services, the S3C24A0 adopts dual-32-bit bus architecture and

includes many powerful hardware accelerators for the motion video processing, serial communications, and etc.

For the real time video conferencing, an optimized MPEG4 H/W Encoder/Decoder is integrated. To reduce total

system cost and enhance ov erall functionality, the S3C24A0 also includes following c om ponent s : separate 16KB

Instruction and 16KB Data Cache, MMU to handle virtual memory management, LCD controller (TFT), C amer a

Interface, MPEG-4 ME, MC, DCTQ, NAND Flash Boot loader, System Manager (power management & etc.),

SDRAM controller, 2-ch UART, 4-ch DMA, 4-ch Timers, General I/O Ports, IIC-BUS interface, USB Host, SD Host

& Multi-Media Card Interface, Memory Stick Interface, PLL for clock generation & etc. The S3C24A0 can be used

as a most powerful Application Processor for mobiles phones. For this application, the S3C24A0 has a Modem

Interface to communicate with various Modem Chips.

The S3C24A0 is developed using an ARM926EJ-S cor e , advanced 0.13um CMOS standard cells and memory

compliers. Its low-power, simple, elegant and fully static-design scheme is particularly suitable for cost-sensitive

and power-sensitive applications. Also, the S3C24A0 adopts a de-facto standard bus architecture – the AMBA

(Advanced Microcontroller Bus Architecture).

One of outstanding features of the S3C24A0 is its CPU core, a 16/32-bit ARM926EJ-S RISC processor designed

by ARM, Ltd. The ARM926EJ-S is a single chip MCU and Java enabled microprocessor. The ARM926EJ-S also

implements the MMU, the AMBA BUS, and the Harvard cache architecture with separate 16KB instruction and

16KB data caches, each cache with an 8-word line length.

By providing a complete set of common system peripherals, the S3C24A0 minimizes overall system costs and

eliminates the need to configure additional components.

1.2 FEATURES

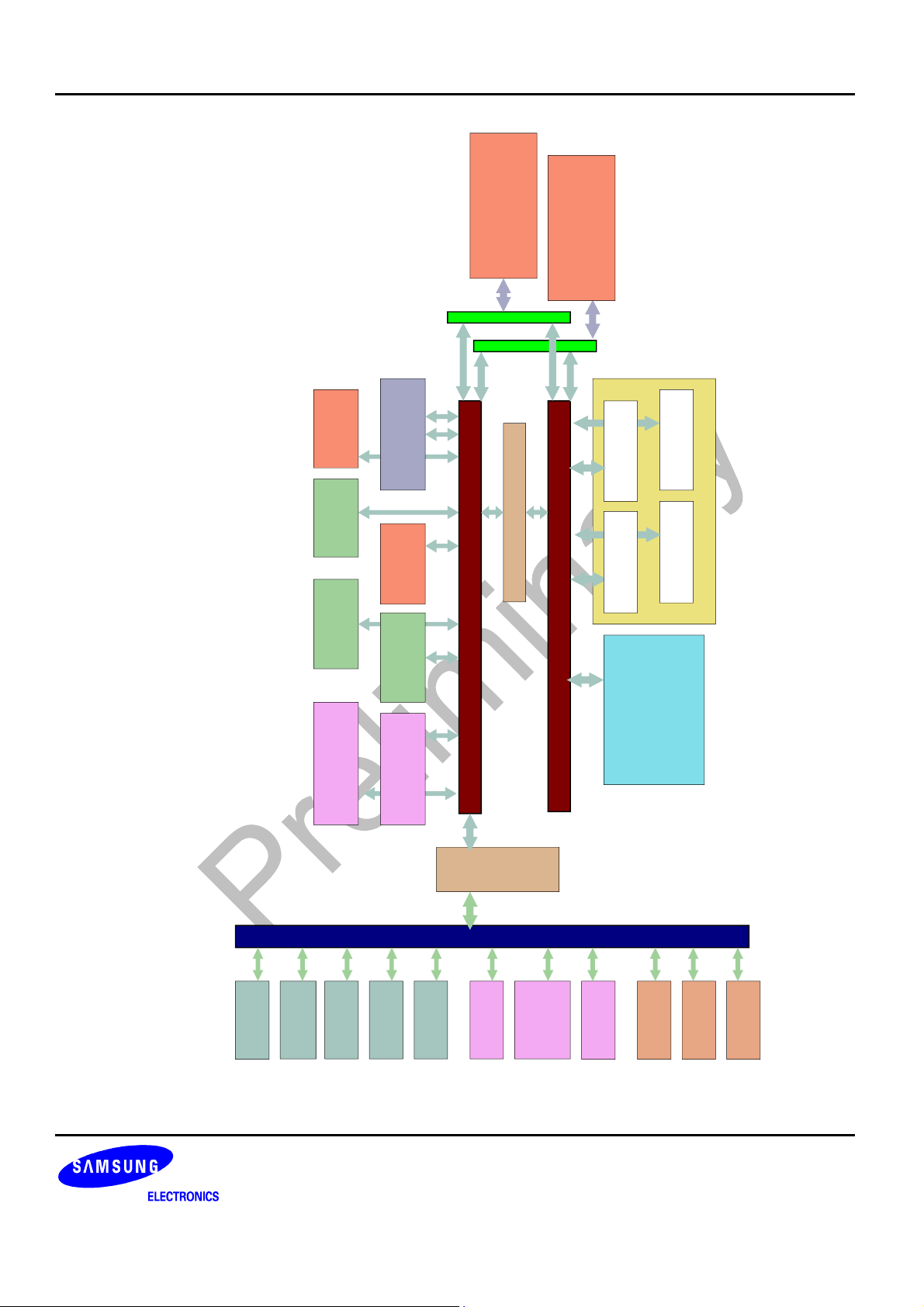

This section summarizes the features of the S3C24A0. Figure 1-1 is an overall block diagram of the S3C24A0.

1.2.1 Microprocessor and Overall Architecture

• SoC (System-on-Chip) for mobile phones and general embedded applications.

• 16/32-Bit RISC architecture and powerful instruction set with ARM926EJ- S CPU core.

• ARM’s Jazelle Java technology

• Enhanced ARM architecture MMU to support WinCE, Symbian and Linux

• Instruction cache, data cache, write buffer and Physical address TAG RAM to reduce the effect of main

memory bandwidth and latency on performance

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-3

Page 4

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

• 4 way set-associative cache with I-Cache (16KB) and D-Cache (16KB).

• 8-words per line with one valid bit and two dirty bits per line

• Pseudo random or round robin replacement algorithm.

• Write through or write back cache operation to update the main memory.

• The write buffer can hold 16 words of data and four addresses.

• ARM926EJ-S core supports the ARM debug architecture

• Internal AMBA (Advanced Microcontroller Bus Architecture) (AMBA2.0, AHB/APB)

• Dual AHB bus for high-performance processing (AHB-I & AHB-S)

1.2.2 Memory Subsystem

• High bandwidth Memory subsystem with two access channels (accesses from two AHB buses) and three-

channel memory ports

• Double the bandwidth with the simultaneous access capability

• ROM/SRAM/NOR-Flash/NAND-Flash channel

• One SDRAM channels

• Up to 1GB Address space

• Low-power SDRAM interface support : Mobile SDRAM function

- DS : Driver Strength Control

- TCSR : Temperature Compensated Self-Refresh Control

- PASR : Partial Array Self-Refresh Control

• NAND Flash Boot Loader with the ECC circuitry to support booting from NAND Flash

- 4KB Stepping Stone

- Support 1G, 2G bit NAND Flash

1.2.3 General Peripherals

• Interrupt Controller

- 61 Interrupt sources

(1 Watch D og Timer, 5 Timer, 6 UA RT, 18 External Interrupts, 4 DMA, 2 RTC, 3 ADC, 1 I2C, 1 AC97, 1

NAND Flash, 1 IrDA, 1 Memory Stick, 2 SPI, 1 SDI, 2 USB (Host and Device), 1 Keypad, 1 Modem

Interface, 2 Camera Interface, 4 MPEG, 2 LCD, 1 Battery Fault, 1 Post)

- Level/Edge mode on external interrupt source.

- Programmable polarity of edge and level.

- Supports FIQ (Fast Interrupt request) for very urgent interrupt request.

• Timer with PWM (Pulse Width Modulation)

- 4-ch 16-bit Timer with PWM / 1-ch 16-bit internal timer with DMA-based or interrupt-based operation

- Programmable duty cycle, frequency, and polarity

- Dead-zone generation.

- Support external clock source.

1-4

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 5

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

• 16-bit Watchdog Timer.

- Interrupt request or system reset at time-out.

• 4-ch DMA controller.

- Support memory to memory, IO to memory, memory to IO, and IO to IO

- Burst transfer mode to enhance the transfer rate.

• RTC (Real Time Clock)

- Full clock feature: msec, sec, min, hour, day, date, week, month, year.

- 32.768 KHz operation

- Alarm interrupt

- Time-tick interrupt

1.2.4 Serial Communication

• UART

- 2-channel UART with DMA-based or interrupt-based operation

- Supports 5-bit, 6-bit, 7-bit, or 8-bit serial data transmit/receive

- Supports external clock for the UART operation (XuCLK)

- Programmable baud rate

- Supports IrDA 1.0

- Loop back mode for testing

- Each channel has internal 64- byte Tx FIFO and 64-byte Rx FIFO

• IrDA

- Support IrDA 1.1 (1.152Mbps and 4Mbps)

- Support FIFO operation in the MIR and FIR mode

- Configurable FIFO Size (16-byte or 64-byte)

- Support Back-to-Back Transactions

- Support Software Selection Temic-IBM or HP Transceiver

- Support Little-endian access

• IIC-Bus Interface

- 1-ch Multi-Master IIC-Bus

- Serial, 8-bit oriented and bi-directional data transfers can be made at up to 100 Kbit/s in the standard

mode

• IIS-Bus Interface

- 1-ch IIS-bus for the audio-codec interface with DMA-based operation

- Serial, 8/16-bit per channel data transfers

- 128 Bytes (64-Byte + 64-Byte) FIFO for receive/transmit

- Supports IIS format and MSB-justified data format

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-5

Page 6

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

• SPI Interface

- 2-ch Serial Peripheral Interface Protocol version 2.11 com pa t ible

- 2x8 bits Shift register for receive/transmit.

- DMA-based or interrupt-based operation.

• AC97 Audio-CODEC Interface

- 48KHz 16-bit sampling

- 1-ch stereo PCM inputs / 1-ch stereo PCM outputs / 1-ch MIC input

• USB Host

- 2-port USB Host

- Complies with OHCI Rev. 1.0

- Compatible with the USB Specification version 1.1

• USB Device

- 1-port USB Device

- 5 End-points for USB Device

- Compatible with the USB Specification version 1.1

1.2.5 Parallel Communication

• Modem Chip Interface

- 8-bit Asynchronous SRAM interface-style interface

- On-chip 2KB dual-ported SRAM buffer

- Interrupt Request for Data Exchange

- Programmable Interrupt Port Address

• 32-bit GPIO

- Fully configurable 32-bit GPIO

1.2.6 Image and Video Processing

• Camera Inteface

- ITU601/ITU656 YCbCr 4:2:2 8/16-bit mode

- Image down scaling capability for variable applications

- Digital Zoom-In

- Image X, Y-flip, 180 rotation

- Input Image Window Cut

- Two master for dedicated DMA operation

- Programmable burst length for DMA operation

- Programmable polarity of video sync signals

- Wide horizontal line buffer (maximum 2048 pixel)

1-6

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 7

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

- Up to 4M pixel resolution support for scaled image (image preview or motion video capturing) and 16M

pixel for unscaled image (JPEG)

- Format conversion from YCrCb 4:2:2 to 4:2:0 for codec, and to RGB 4:4:4 for preview

• Hardware Accelerated MPEG4 Video Encoding/Decoding

- A AHB Interface

- Realtime MPEG-4 Video Encoding & Decoding

- Up to Simple Profile at Level 3 (352x288 at 30fps)

- Supports H.263 Base Line

• MPEG-4 ME (Motion Estimation)

- Highly optimized hard-wired engine

- Unrestricted Mode and Advanced Prediction Mode (4MV)

- Use the advanced MRMCS algorithm

- Half-pel search

- Programmable Image size up to 2048x2048

- Padding for Macro-block basis

- Search Range : [-16, 15.5]

- Intra/Inter Mode Decision MC (Motion Compensation)

• MC (Motion Compensation)

- Highly optimized hard-wired engine

- Unrestricted Mode and Advanced Prediction Mode (4MV)

- Half-pel search

- Programmable Image size up to 2048x2048

- Dedicated DMA

- Macroblock-based Pading

- Search Range : [-64, 63.5]

• DCTQ

- DCT/IDCT/Q/IQ operations•AMBA AHB Interface

- Support MPEG-4 Simple Profile Level 3 / H.263 Base-Line•Support programmable image size up to

4096x4096

- Macroblock-based processing

- Rate Control by Qp Information

- Local DMA

- Support MPEG-4 Encoding / Decoding

- Support JPEG DCT / IDCT Operation

- Operation unit : 1MB(MacroBlock) ~ 1 Frame

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-7

Page 8

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

• VLX

- VLC/VLD operations

- AMBA AHB Interface

- Support MPEG4 Simple Profile Level 3/ H.263. Baseline

- Macro block-based processing

- Dedicated DMA

- Only DCTQ coefficient VLC/VLD operation

- Only DC prediction operation in VLC

• Post Processor

- Dedicate DMA with Offset Address

- 3 Channel Scaling Pipelines for Video/Graphis Signal

- Input Format : YCbCr4:2:0, YCbCr4:2:2, or RGB 16b/24b

- Output Format : RGB 16b/24b

- Programmable Image Size (Source up to 4096x4096, Destination up to 2048x2048)

- Programmable Scale Ratio (Up-scale: up to Max. Destination Size, Down-scale: ~>1/64 in X & Y)

- Format Conversion for Video Signal (YCbCr4:2:0 or YCbCr4:2:2)

- Color Space Conversion (YCbCr2RGB)

- Separate Processing Clock from AHB Interface Clock

1.2.7 Display Control

• TFT LCD Interface

- 18-bit Parallel or 6bit*3 Interface

- 1/2/4/8-bpp Palletized or 8/16/18-bpp Non-Palletized Color-TFF support

- Supports 640x480, 320x240, 176x192 and others

- Up to 16 Mbyte virtual screen size

- Supports Multiple Virtual Display Screen (Supports Hardware Horizontal/Vertical Scrolling)

- Programmable timing control for different display panels

- Dual Buffer

• OSD (On Screen Display)

- Realtime overlay plane multiplexing

- Programmable OSD window positioning

- Per-pixel alpha blending for 18-bpp OSD images

- Fixedalpha- valuefor 8-/16-/1 8-bpp OSDimage

- 256-level alpha blending

- 24-bit color key support

- Dual buffer

1-8

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 9

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

1.2.8 Input Devices

• Keypad Interface

- Provides internal debouncing filter

- 5-input, 5-output pins for key scan in/out

• A/D Converter and Touch Screen Interface

- 8-ch multiplexed ADC

- Max. 500K samples/ sec and 10-bit resolution

1.2.9 Storage Devices

• SD Host

- Compatible with SD Memory Card Protocol version 1.0

- Compatible with SDIO Card Protocol version 1.0

- 64 Bytes FIFO for Tx/Rx

- DMA based or Interrupt based operation

- Compatible with Multimedia Card Protocol version 2.11

• Memory Stick Host

- Memory Stick version 1.3 compliant

1.2.10 System Management

• Little Endian format support

• System operating clock generation

- Two on-chip PLLs, MPLL & UPLL

- MPLL generates the system reference clock, 200MHz@1.2V

- UPLL generates clocks for the USB Host/Device, IrDA and Camera

• Power Management

- Clock-off control for individual components

- Various power-down modes are available such as IDLE, STOP and SLEEP

- Wake - up by one of external interrupts or by the RTC alarm interrupt, etc.

1.2.11 Electrical Characteristics

• Operating Conditions

- - Supply Voltage for Logic Core: 1.25V +/- 0.05V

- - External Memory Interface: 1.8V / 2.5V / 3.3V

- - External I/O Interface: 3.3V

• Operational Frequency

- - Max. 200MHz@1.25V

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-9

Page 10

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

1.2.12 Package

• 337-pin FBGA (0.5mm pitch, 13mm x 13mm)

1-10

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 11

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

SRAM/NOR/NAND

Memory Controller

Memory Controller

/ROM

SDRAM

IrDA1.1

Interface

Modem

4-Channel

DMA

Down Controller

System/Power

ARM926EJ

Inst. Data

USB 1.1

Host

INTC

NAND Boot

Loader

MPEG4 H/W Accelerator

Interface

ME/MC

Camera

AHB to AHB Bridge

Postprocessor

AHB-S

AHB-I

DCTQ/VLX

TFT LCD Interface

Digital Display

Controller

AHB to

APB Bridge

A

B

P

PI

I2C/I2S/S

UART*2

SD Host

Host

Memory

Stick

Device

USB1.1

Codec IF

Audio

Timer

KEYPAD

GPIO*32

ADC/

10-bit

Screen

Touch

Figure 1- 1 An Overall Block Diagram of the S3C24A0

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

TIMER*5

Watch Dog

1-11

Page 12

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

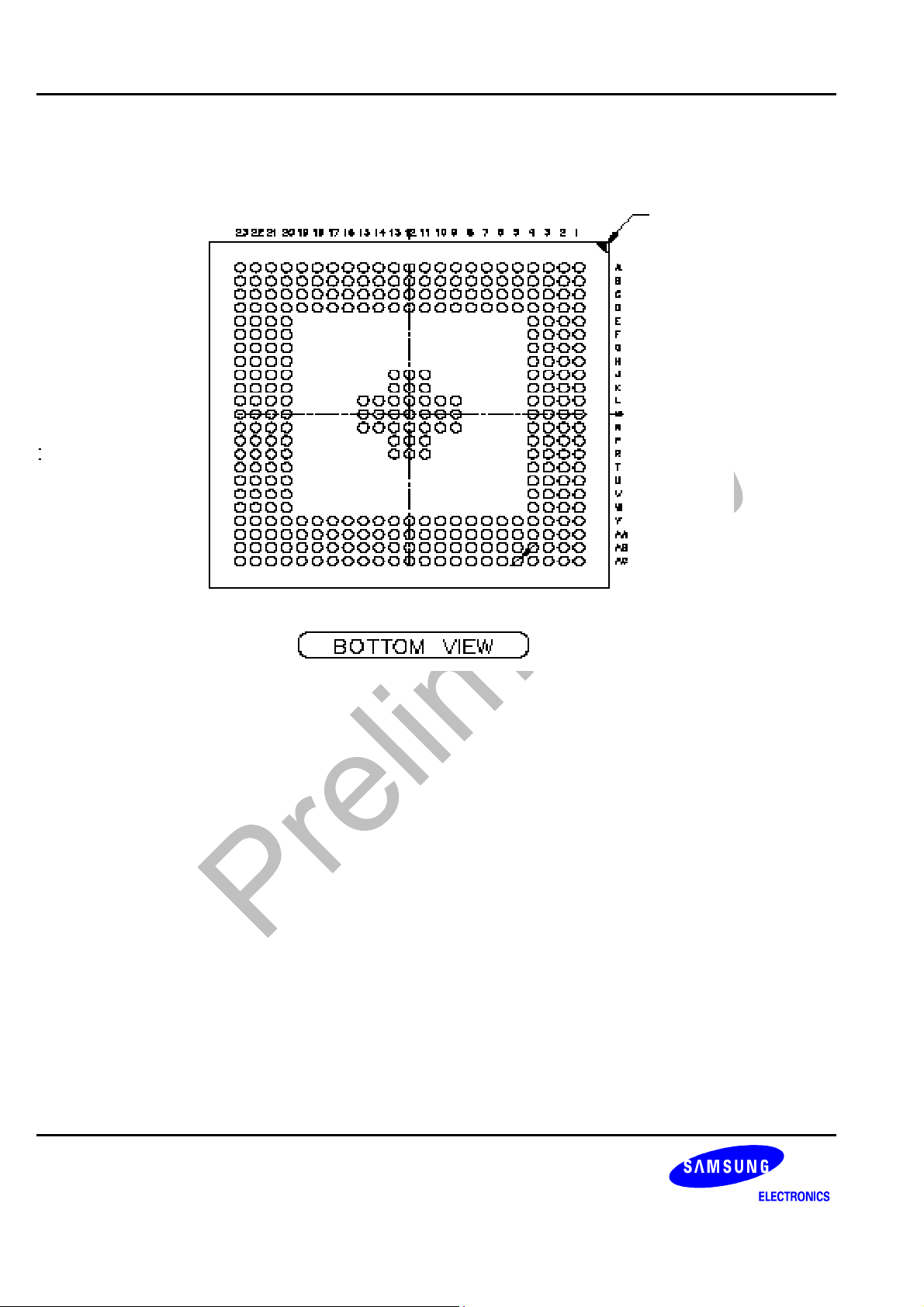

1.3.2 Pin Assignment

#A1 INDEX MARK

337-Pin FBGA Pin Assignment

1-12

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 13

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

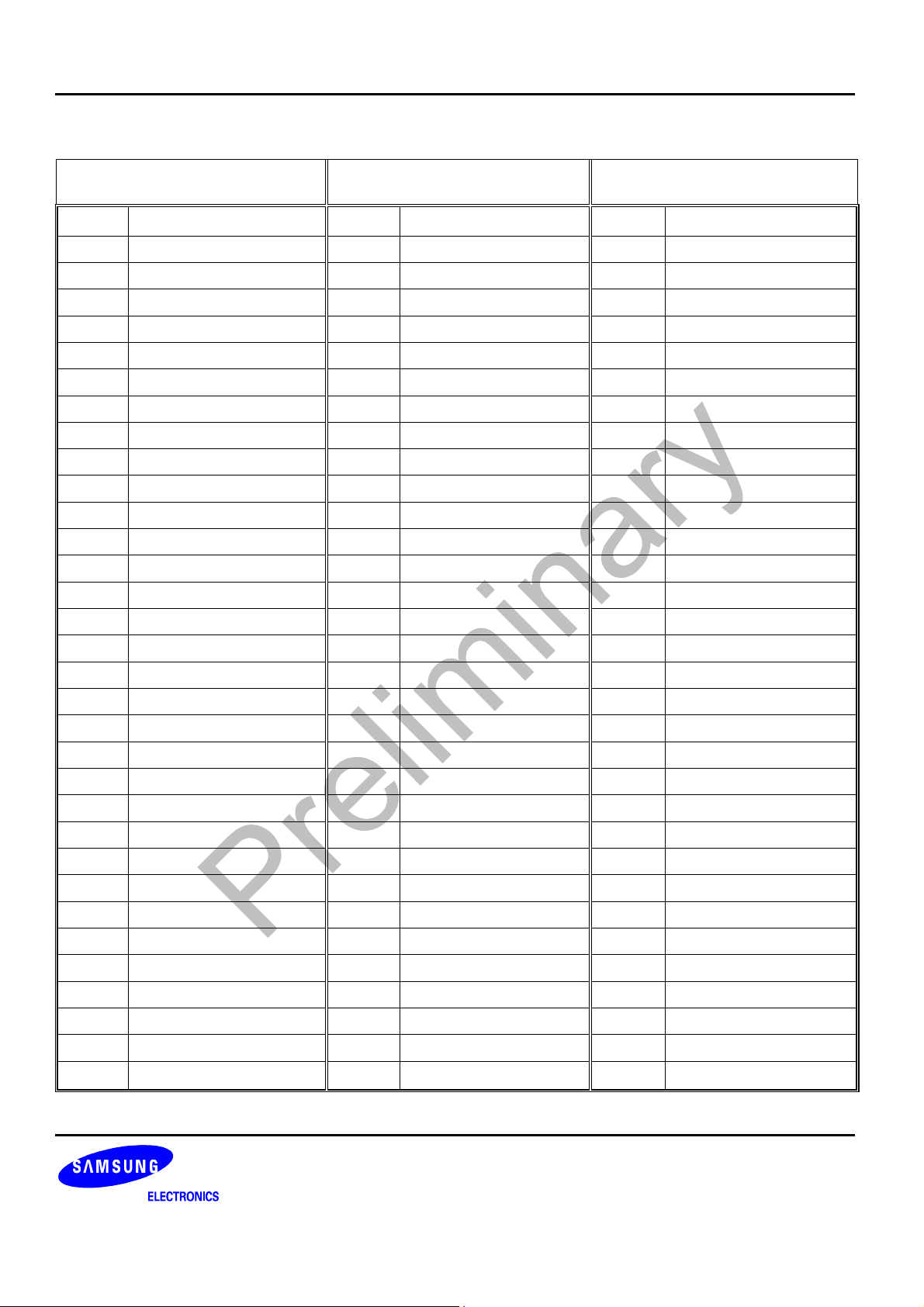

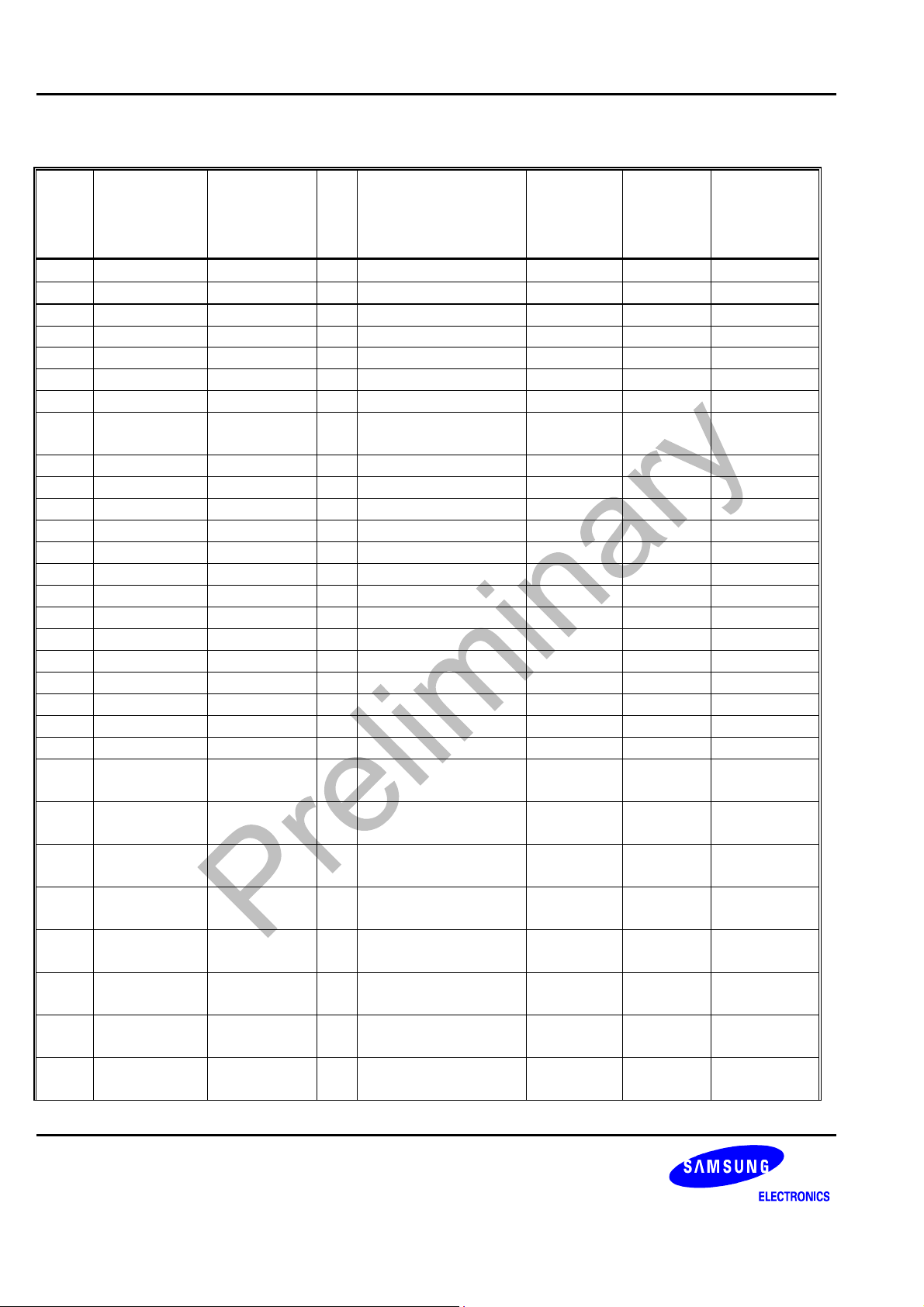

Table 1-1. 337-Pin FBGA Pin Assignments – Pin Number Order

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

A01 XCIYDATA[4] B11 XRDATA[1] C21 XRADDR [21]

A02 VSS_B B12 XRDATA[3] C22 XFNFPS

A03 XCICDATA[0] B13 XRDATA[7] C23 XFNFADV

A04 XCIYDATA[7] B14 XRADDR[5] D01 XJTDO

A05 XCIPCLK B15 XRNWBE[0] D02 XJTDI

A06 XVVD[5] B16 XRWEN D03 XVVD[2]

A07 XVVD[7] B17 XRCSN[2] D04 XCIRSTN

A08 XVVCLK B18 XRDATA[14] D05 XCIYDATA[5]

A09 XVDEN B19 XRADDR[11] D06 XCIVSYNC

A10 XCICDATA[7] B20 XRADDR[15] D07 XVVD[13]

A11 XRDATA[0] B21 XRADDR[22] D08 XVVD[14]

A12 XRDATA[5] B22 XFALE D09 XCICDATA[5]

A13 XRADDR [3] B23 XFNFACYC D10 XJRTCK

A14 XRADDR [7] C01 XJTMS D11 XVVSYNC

A15 XRNWBE[1] C02 XJTRSTN D12 XVVD[19]

A16 XRDATA[8] C03 XCICLK D13 XVVD[22]

A17 XRDATA[13] C04 XCICDATA[1] D14 XRADDR [4]

A18 XRADDR [10] C05 XVVD[4] D15 XRADDR [2]

A19 XRADDR [16] C06 XCIHREF D16 XRADDR [0]

A20 XRADDR [17] C07 XCICDATA[4] D17 XRADDR [14]

A21 XRADDR[20] C08 XCICDATA[6] D18 XRADDR [19]

A22 XRADDR [23] C09 XVHSYNC D19 XFCLE

A23 XFRNB[0] C10 XVVD[20] D20 XRADDR [8]

B01 XJTCK C11 XVVD[23] D21 XRADDR [12]

B02 XCIYDATA[0] C12 VDD_C D22 XFNFBW

B03 XCIYDATA[2] C13 XRDATA[6] D23 XRADDR [25]

B04 XCIYDATA[6] C14 XRADDR[1] E01 XGPIO[31]

B05 XCICDATA[2] C15 XRADDR [6] E02 X2CSDA

B06 XCICDATA[3] C16 XRWAITN E03 X2CSCL

B07 XVVD[11] C17 XRCSN[1] E04 XCIYDATA[1]

B08 XVVD[15] C18 XRDATA[10] E20 XFRNB[1]

B09 XVVD[18] C19 XRDATA[12] E21 XRADDR [24]

B10 XVVD[21] C20 XRADDR [9] E22 XPDATA[2]

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-13

Page 14

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-1. 337-Pin FBGA Pin Assignments – Pin Number Order

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

E23 XPDATA[1] J21 VDD_A M09 VSS_B

F01 XGPIO[28] J22 XPDQM[3] M10 VDD_F

F02 XGPIO[29] J23 XPDATA[8] M11 VSS

F03 XGPIO[30] K01 XGPIO[11] M12 VSS

F04 XCIYDATA[3] K02 XGPIO[14] M13 VSS

F20 XRADDR [18] K03 XGPIO[16] M14 VDD_A

F21 XPDATA[0] K04 XVVD[12] M15 VSS_D

F22 XPDATA[6] K11 VDD_B M20 XPADDR[2]

F23 XPDATA[3] K12 VSS M21 XPDATA[15]

G01 XGPIO[24] K13 VSS_E M22 XPADDR[1]

G02 XGPIO[26] K20 XRDATA[11] M23 XPADDR[3]

G03 XGPIO[27] K21 XPDATA[9] N01 X97SYNC

G04 XVVD[3] K22 XPDATA[10] N02 X97RESETN

G20 XRADDR [13] K23 XPDATA[11] N03 XGPIO[4]

G21 XPDATA[5] L01 XGPIO[7] N04 XGPIO[8]

G22 XPDQM[0] L02 XGPIO[10] N09 VDD_A

G23 XPDATA[7] L03 XGPIO[12] N10 VDD_B

H01 XGPIO[20] L04 XGPIO[21] N11 VSS

H02 XGPIO[23] L09 VDD_C N12 VSS

H03 XGPIO[22] L10 VDD_C N13 VSS

H04 XVVD[6] L11 VSS N14 VSS_D

H20 XPDATA[4] L12 VSS N15 VDD_D

H21 VDD_D L13 VSS N20 XRDATA[9]

H22 XPDQM[1] L14 VDD_E N21 XPADDR[4]

H23 XPDQM[2] L15 VSS_D N22 XPADDR[5]

J01 XGPIO[17] L20 XPDATA[14] N23 XPADDR[6]

J02 XGPIO[18] L21 XPDATA[12] P01 XURTSN

J03 XGPIO[25] L22 XPDATA[13] P02 X97SDO

J04 XVVD[10] L23 XPADDR[0] P03 X97BITCLK

J11 VSS_B M01 XGPIO[0] P04 XGPIO[5]

J12 VSS_E M02 XGPIO[6] P11 VSS_B

J13 VDD_E M03 VDD_B P12 VDD_F

J20 XRDATA[15] M04 XGPIO[19] P13 VSS_D

1-14

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 15

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

Table 1-1. 337-Pin FBGA Pin Assignments – Pin Number Order

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

P20 XRCSN[0] V03 XGTMODE[3] Y20 VDD_D

P21 XPDATA[16] V04 XUCLK Y21 XPDATA[25]

P22 XPADDR[7] V20 XRDATA[2] Y22 XPDATA[27]

P23 XPDATA[18] V21 XPDATA[29] Y23 XPDATA[26]

R01 XGTMODE[2] V22 XPWEN AA01 XRTCXTI

R02 XURXD V23 XPCASN AA02 XGREFCLKSEL[0]

R03 XGPIO[2] W01 XGTMODE[1] AA03 XGPWROFFN

R04 XGPIO[15] W02 XSPIMISO AA04 XADCAIN[5]

R11 VDD_A W03 XSPISSIN[0] AA05 XADCAVREF

R12 VDD_B W04 X2SCLK AA06 XADCAIN[2]

R13 VSS_D W20 VDD_D AA07 GND10

R20 XROEN W21 VDD_A AA08 VDD13

R21 XPDATA[17] W22 XPCSN[0] AA09 XSRESETN

R22 XPDATA[19] W23 XPCSN[1] AA10 XSXTOUT

R23 XPSCLK Y01 XSWRESETN AA11 XUSDP[0]

T01 X2SCDCLK Y02 XGTMODE[0] AA12 XUSDN[0]

T02 XUCTSN Y03 XSPICLK AA13 XMSBS

T03 X97SDI Y04 X2SDI AA14 XMIWEN

T04 XGPIO[13] Y05 XGBATFLTN AA15 XMIADR[8]

T20 XPDATA[24] Y06 XGPIO[1] AA16 XMIADR[6]

T21 XPDATA[20] Y07 XGPIO[3] AA17 XMIDATA[6]

T22 XPDATA[21] Y08 VDD15 AA18 VDD_A

T23 XPDATA[23] Y09 XSRSTOUTN AA19 XMIDATA[2]

U01 X2SDO Y10 XUDDP AA20 XMIADR[0]

U02 X2SLRCK Y11 XSDDAT[3] AA21 VDD_D

U03 XUTXD Y12 VDD20(VDDpadUSB) AA22 XPDATA[31]

U04 XGPIO[9] Y13 XMSSDIO AA23 XPDATA[28]

U20 XRDATA[4] Y14 XMSPI AB01 VDD10

U21 XPDATA[22] Y15 XMICSN AB02 XADCAIN[7]

U22 XPCKE Y16 XMIADR[10] AB03 XRTCXTO

U23 XPRASN Y17 XPADDR[13] AB04 XGREFCLKSEL[1]

V01 XSPIMOSI Y18 XMIADR[4] AB05 XADCAIN[0]

V02 XSPISSIN[1] Y19 XMIADR[2] AB06 VDD11

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-15

Page 16

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-1. 337-Pin FBGA Pin Assignments – Pin Number Order

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

AB07 GND12 AB21 XPADDR[11] AC12 XSDDAT[2]

AB08 XSUPLLCAP AB22 XPDATA[30] AC13 XSDDAT[0]

AB09 XSEXTCLK AB23 XPADDR[8] AC14 XMIADR[9]

AB10 XUSDP[1] AC01 GND9(VSSrtc) AC15 XMIADR[5]

AB11 XUDDN AC02 XADCAIN[6] AC16 XMIDATA[5]

AB12 XSDDAT[1] AC03 XADCAIN[4] AC17 XMIDATA[3]

AB13 GND19(VSSpadUSB) AC04 XADCAIN[3] AC18 XMIDATA[1]

AB14 XMIOEN AC05 XADCAIN[1] AC19 XMIADR[3]

AB15 XMIADR[7] AC06 XSMPLLCAP AC20 XPADDR[14]

AB16 XMIDATA[7] AC07 GND14 AC21 XPADDR[12]

AB17 XMIDATA[4] AC08 XGMONHCLK AC22 XPADDR[10]

AB18 XMIIRQN AC09 XSXTIN AC23 XPADDR[9]

AB19 XMIDATA[0] AC10 XUSDN[1]

AB20 XMIADR[1] AC11 XMSSCLKO

1-16

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 17

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

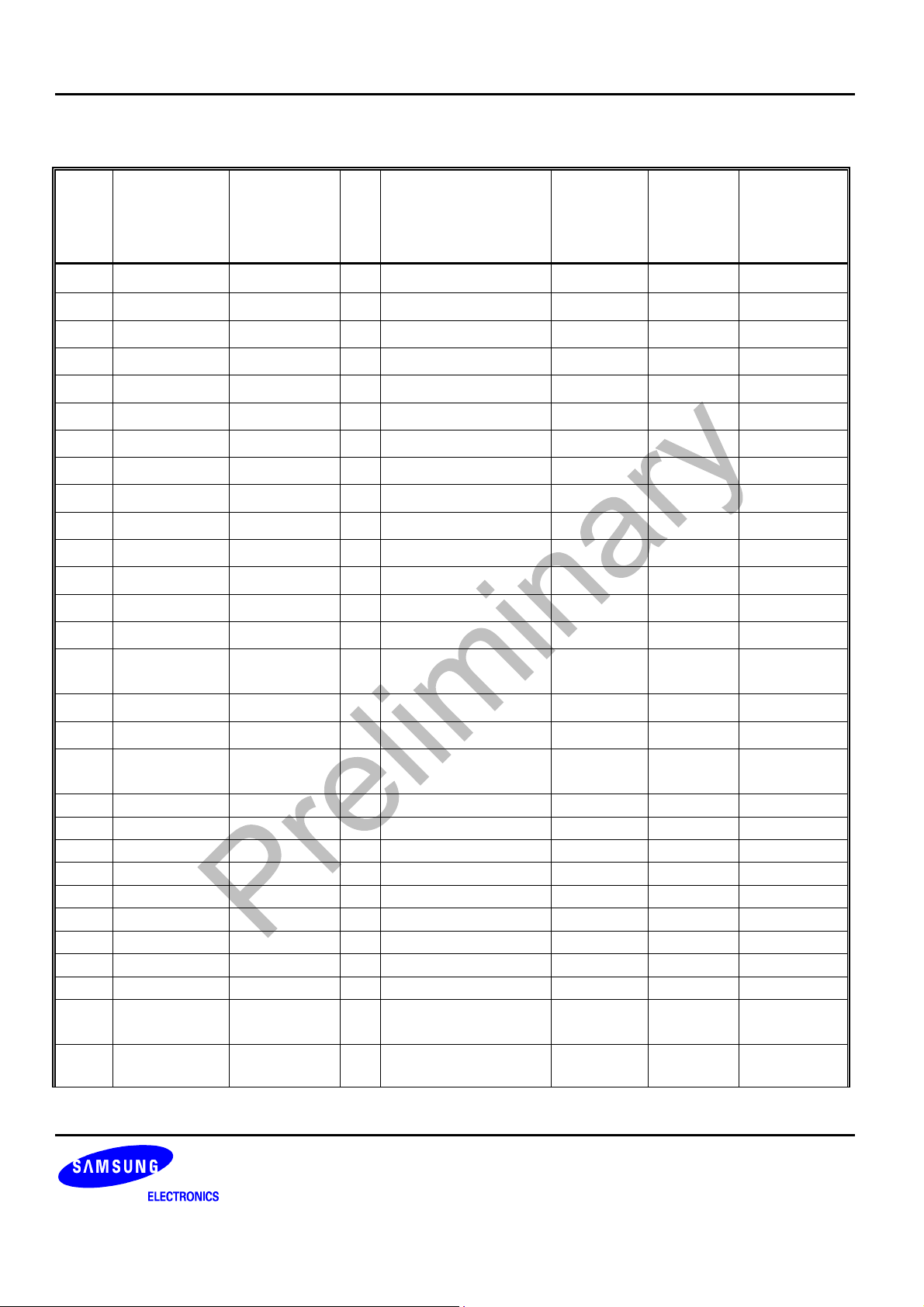

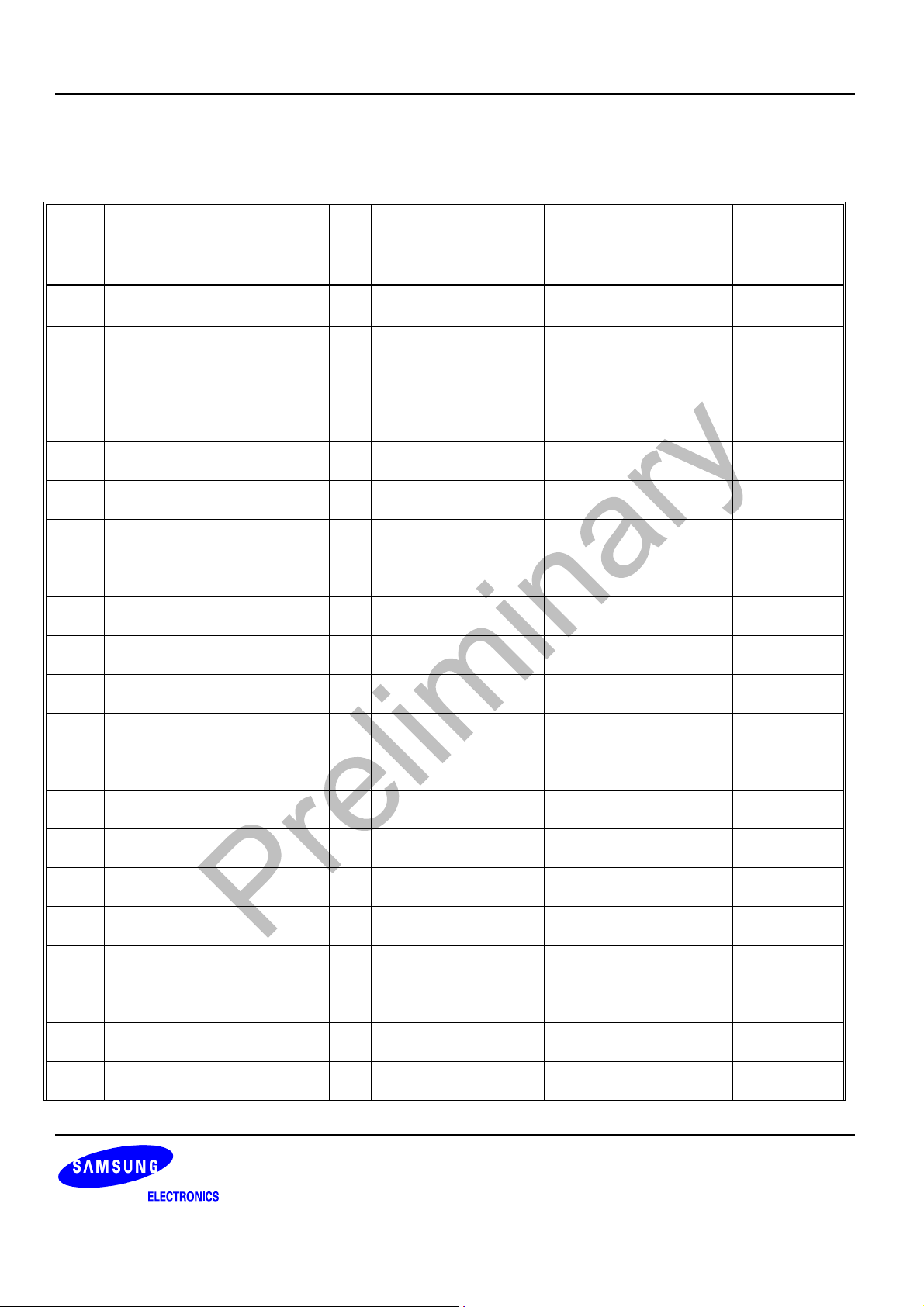

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

AA7 VSSadc VSSadc

AB7 VSSMpll VSSMpll

AC7 VSSUpll VSSUpll

AB13 VSSpadUSB VSSpadUSB

AC1 VSSrtc VSSrtc

AA18 VDDlogic VDDlogic

J21 VDDlogic VDDlogic

M14 VDDlogic VDDlogic

N9 VDDlogic VDDlogic

R11 VDDlogic VDDlogic

W21 VDDlogic VDDlogic

K11 VDDpadIO VDDpadIO

M3 VDDpadIO VDDpadIO

N10 VDDpadIO VDDpadIO

R12 VDDpadIO VDDpadIO

C12 VDDarm VDDarm

L10 VDDarm VDDarm

L9 VDDarm VDDarm

AA21 VDDpadSDRAM VDDpadSDRAM

H21 VDDpadSDRAM VDDpadSDRAM

N14 VSS VSS

N15 VDDpadSDRAM VDDpadSDRAM

W20 VDDpadSDRAM VDDpadSDRAM

Y20 VDDpadSDRAM VDDpadSDRAM

J13 VDDpadFlash VDDpadFlash

L14 VDDpadFlash VDDpadFlash

M10 VDDalive VDDalive

P12 VDDalive VDDalive

AB1 VDDrtc VDDrtc

AB6 VDDadc VDDadc

AA8 VDDMpll VDDMpll

Y8 VDDupll VDDupll

Y12 VDDpadUSB VDDpadUSB

K12 VSS VSS

L11 VSS VSS

L12 VSS VSS

L13 VSS VSS

Name Default Function I/O

I/O state@ Reset mode

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

I/O

State@SLEEP

mode

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

I/O

State@STOP

mode

Cell Type

(24A0A)

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-17

Page 18

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

M11 VSS VSS

M12 VSS VSS

M13 VSS VSS

N11 VSS VSS

N12 VSS VSS

N13 VSS VSS

A2 VSSpadIO VSSpadIO

J11 VSSpadIO VSSpadIO

M9 VSSpadIO VSSpadIO

P11 VSSpadIO VSSpadIO

L15 VSSpadSDRAM VSSpadSDRAM

M15 VSSpadSDRAM VSSpadSDRAM

P13 VSSpadSDRAM VSSpadSDRAM

R13 VSSpadSDRAM VSSpadSDRAM

J12 VSSpadFlash VSSpadFlash

K13 VSSpadFlash VSSpadFlash

E3

E2

Name

X2cSCL X2cSCL I/O I/H L or I H phbsud8sm

X2cSDA X2cSDA I/O I/H L or I H phbsud8sm

Default

Function

I/O state@ Reset mode

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

I/O

State@SLEEP

mode

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

PP P

I/O

State@STOP

mode

Cell Type

(24A0A)

T1

W4

Y4

U1

U2

P3

N2

T3

P2

N1

AB5

AC5

AA6

X2sCDCLK X2sCDCLK O H or L/L Hi-z or H or L H phot8

X2sCLK X2sCLK I/O L/L/L H or L or I L phbsu100ct8sm

X2sDI X2sDI I I - - phisu

X2sDO X2sDO O L/L Hi-z or H or L L phot8

X2sLRCK X2sLRCK I/O H/L/L H or L or I Pre phbsu100ct8sm

X97BITCLK X97BITCLK I I - - phis

X97RESETn X97RESETn O L/L Hi-z or H or L H phot8

X97SDI X97SDI I I - - phisu

X97SDO X97SDO O L/L Hi-z or H or L L phot8

X97SYNC X97SYNC O L/L Hi-z or H or L L phot8

XadcAIN[0] XadcAIN[0] Ain I - - phiar10_abb

XadcAIN[1] XadcAIN[1] Ain I - - phiar10_abb

XadcAIN[2] XadcAIN[2] Ain I - - phiar10_abb

1-18

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 19

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

AC4

AC3

AA4

AC2

AB2

AA5

A3

C4

B5

B6

C7

D9

C8

A10

I/O state@ Reset mode

Name

XadcAIN[3] XadcAIN[3] Ain I - - phiar10_abb

XadcAIN[4] XadcAIN[4] Ain I - - phiar10_abb

XadcAIN[5] XadcAIN[5] Ain I - - phiar10_abb

XadcAIN[6] XadcAIN[6] Ain I - - phiar10_abb

XadcAIN[7] XadcAIN[7] Ain I - - phiar10_abb

XadcAVREF XadcAVREF Ain I - - phia_abb

XciCDATA[0] XciCDATA[0] I I/H/L - - phbsu100ct8sm

XciCDATA[1] XciCDATA[1] I I/H/L - - phb su100ct8sm

XciCDATA[2] XciCDATA[2] I I/H/L - - phb su100ct8sm

XciCDATA[3] XciCDATA[3] I I/H/L - - phb su100ct8sm

XciCDATA[4] XciCDATA[4] I I/H/L - - phb su100ct8sm

XciCDATA[5] XciCDATA[5] I I/H/L - - phbsu100ct8sm

XciCDATA[6] XciCDATA[6] I I/H/L - - phb su100ct8sm

XciCDATA[7] XciCDATA[7] I I/H/L - - phb su100ct8sm

Default

Function

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

I/O

State@SLEEP

mode

I/O

State@STOP

mode

Cell Type

(24A0A)

C3

C6

A5

D4

D6

B2

E4

B3

F4

A1

D5

B4

A4

B22

D19

XciCLK XciCLK O L/L Hi-z or H or L L phot12sm

XciHREF XciHREF I I - - phis

XciPCLK XciPCLK I I - - phis

XciRSTn XciRSTn O L/L Hi-z or H or L Pre phot8

XciVSYNC XciVSYNC I I - - phis

XciYDATA[0] XciYDATA[0] I I - - phis

XciYDATA[1] XciYDATA[1] I I - - phis

XciYDATA[2] XciYDATA[2] I I - - phis

XciYDATA[3] XciYDATA[3] I I - - phis

XciYDATA[4] XciYDATA[4] I I - - phis

XciYDATA[5] XciYDATA[5] I I - - phis

XciYDATA[6] XciYDATA[6] I I - - phis

XciYDATA[7] XciYDATA[7] I I - - phis

XfALE XfALE O L/L Hi-z or H or L L phot8

XfCLE XfCLE O L/L Hi-z or H or L L phot8

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-19

Page 20

BSW rv0.1-0417-N01

r

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-2. 337-Pin FBGA Pin Assignments

I/O state@ Reset

Pin

Numbe

B23

C23

D22

C22

A23

E20

Y5

mode

Name

XfNFACYC XfNFACYC I I - - phis

XfNFADV XfNFADV I I - - phis

XfNFBW XfNFBW I I - - phis

XfNFPS XfNFPS I I - - phis

XfRnB[0] XfRnB[0] I I - - phisu

XfRnB[1] XfRnB[1] I I - - phisu

XgBATFLT XgBATFLT I H - - phis

Default

Function

(Data/En/PullupEn)

I/O

En(L)=>output

PullupEn(L)=>PullU

p

I/O

State@SLEEP

mode

I/O

State@STOP

mode

Cell Type

(24A0A)

AC8

M1

Y6

L2

K1

L3

T4

XgpIO[14]/EINT14/RTC_ALMINT XgpIO[14] I/O I/H/L H or L or I -

K2

XgpIO[15]/EINT15/XspiMOSI XgpIO[15] I/O I/H/L H or L or I -

R4

XgpIO[16]/EINT16/XspiMISO XgpIO[16] I/O I/H/L H or L or I -

K3

J1

XgpIO[18]/EINT18/XkpROW0 XgpIO[18] I/O I/H/L H or L or I -

J2

XgpIO[19]/PWM_ECLK/XkpROW

M4

XgpIO[2]/EINT2/PWM_TOUT0 XgpIO[2] I/O I/H/L H or L or I -

R3

H1

L4

XgMONHCLK XgMONHCLK O L/L Hi-z or H or L L phot8

XgpIO[0]/EINT0 XgpIO[0] I/O I/H/L H or L or I -

XgpIO[1]/EINT1 XgpIO[1] I/O I/H/L H or L or I -

XgpIO[10]/YMON XgpIO[10] I/O I/H/L H or L or I -

XgpIO[11]/EINT11 XgpIO[11] I/O I/H/L H or L or I -

XgpIO[12]/EINT12/XMON XgpIO[12] I/O I/H/L H or L or I -

XgpIO[13]/EINT13/XPON XgpIO[13] I/O I/H/L H or L or I -

XgpIO[17]/EINT17/XspiCLK XgpIO[17] I/O I/H/L H or L or I -

1

XgpIO[20]/PWM_TOUT0/

XkpROW2

XgpIO[21]/PWM_TOUT1/

XkpROW3

XgpIO[19] I/O I/H/L H or L or I -

XgpIO[20] I/O I/H/L H or L or I -

XgpIO[21] I/O I/H/L H or L or I -

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

phbsu100ct8s

m

1-20

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 21

BSW rv0.1-0417-N01

r

s

s

s

s

s

s

s

s

s

s

s

s

s

s

s

s

s

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

Table 1-2. 337-Pin FBGA Pin Assignments

I/O state@ Reset

Pin

Numbe

H3

H2

G1

J3

G2

G3

F1

F2

Y7

F3

E1

N3

P4

M2

L1

N4

U4

AA3

AA2

AB4

mode

Name Default Function I/O

XgpIO[22]/PWM_TOUT2/XkpROW4 XgpIO[22] I/O I/H/L H or L or I -

XgpIO[23]/PWM_TOUT3/XkpCOL0 XgpIO[23] I/O I/H/L H or L or I -

XgpIO[24]/EXTDMA_REQ0/

XkpCOL1

XgpIO[25]/EXTDMA_REQ1/

XkpCOL2

XgpIO[26]/EXTDMA_ACK0/

XkpCOL3

XgpIO[27]/EXTDMA_ACK1/XkpCOL4 XgpIO[27] I/O I/H/L H or L or I -

XgpIO[28]/XuCTSn1/RTC_ALMINT XgpIO[28] I/O I/H/L H or L or I -

XgpIO[29]/XuRTSn1/IrDA_SDBW XgpIO[29] I/O I/H/L H or L or I -

XgpIO[3]/EINT3/PWM_TOUT1 XgpIO[3] I/O I/H/L H or L or I -

XgpIO[30]/XuTXD1/IrDA_TXD XgpIO[30] I/O I/H/L H or L or I -

XgpIO[31]/XuRXD1/ IrDA_RXD XgpIO[31] I/O I/H/L H or L or I -

XgpIO[4]/EINT4/PWM_TOUT2 XgpIO[4] I/O I/H/L H or L or I -

XgpIO[5]/EINT5/ PWM_TOUT3 XgpIO[5] I/O I/H/L H or L or I -

XgpIO[6]/EINT6/EXTDMA_REQ0 XgpIO[6] I/O I/H/L H or L or I -

XgpIO[7]/EINT7 EXTDMA_REQ1 XgpIO[7] I/O I/H/L H or L or I -

XgpIO[8]/EINT8/ EXTDMA_ACK0 XgpIO[8] I/O I/H/L H or L or I -

XgpIO[9]/EINT9 EXTDMA_ACK1 XgpIO[9] I/O I/H/L H or L or I -

XgPWROFFn XgPWROFFn O H L H phob8

XgREFCLKSEL[0] XgREFCLKSEL[0] I H - - phis

XgREFCLKSEL[1] XgREFCLKSEL[1] I H - - phis

XgpIO[24] I/O I/H/L H or L or I -

XgpIO[25] I/O I/H/L H or L or I -

XgpIO[26] I/O I/H/L H or L or I -

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullU

p

I/O

State@SLEEP

mode

I/O

State@STOP

mode

Cell Type

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

phbsu100ct8

(24A0A)

m

m

m

m

m

m

m

m

m

m

m

m

m

m

m

m

m

1-21

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 22

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

Y2

W1

R1

V3

D10

B1

D2

D1

C1

C2

AA20

AB20

Y16

Y19

AC19

Y18

AC15

AA16

AB15

AA15

AC14

Y15

I/O state@ Reset mode

Name

XgTMODE[0] XgTMODE[0] I I - - phis

XgTMODE[1] XgTMODE[1] I I - - phis

XgTMODE[2] XgTMODE[2] I I - - phis

XgTMODE[3] XgTMODE[3] I I - - phis

XjRTCK XjRTCK O L - - phob8

XjTCK XjTCK I I - - phis

XjTDI XjTDI I I - - phisu

XjTDO XjTDO O I/H Hi-z or H or L Hi-z phot8

XjTMS XjTMS I I - - phisu

XjTRSTn XjTRSTn I I - - phisu

XmiADR[0] XmiADR[0] I I/H/L - - phbsu100ct8sm

XmiADR[1] XmiADR[1] I I/H/L - - phbsu100ct8sm

XmiADR[10] XmiADR[10] I I/H/L - - phbsu100ct8sm

XmiADR[2] XmiADR[2] I I/H/L - - phbsu100ct8sm

XmiADR[3] XmiADR[3] I I/H/L - - phbsu100ct8sm

XmiADR[4] XmiADR[4] I I/H/L - - phbsu100ct8sm

XmiADR[5] XmiADR[5] I I/H/L - - phbsu100ct8sm

XmiADR[6] XmiADR[6] I I/H/L - - phbsu100ct8sm

XmiADR[7] XmiADR[7] I I/H/L - - phbsu100ct8sm

XmiADR[8] XmiADR[8] I I/H/L - - phbsu100ct8sm

XmiADR[9] XmiADR[9] I I/H/L - - phbsu100ct8sm

XmiCSn XmiCSn I I - - phisu

Default

Function

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

I/O

State@SLEEP

mode

I/O

State@STOP

mode

Cell Type

(24A0A)

AB19

AC18

AA19

AC17

AB17

AC16

AA17

AB16

1-22

XmiDATA[0] XmiDATA[0] I/O I/H/L H or L or I - phbsu100ct8sm

XmiDATA[1] XmiDATA[1] I/O I/H/L H or L or I - phbsu100ct8sm

XmiDATA[2] XmiDATA[2] I/O I/H/L H or L or I - phbsu100ct8sm

XmiDATA[3] XmiDATA[3] I/O I/H/L H or L or I - phbsu100ct8sm

XmiDATA[4] XmiDATA[4] I/O I/H/L H or L or I - phbsu100ct8sm

XmiDATA[5] XmiDATA[5] I/O I/H/L H or L or I - phbsu100ct8sm

XmiDATA[6] XmiDATA[6] I/O I/H/L H or L or I - phbsu100ct8sm

XmiDATA[7] XmiDATA[7] I/O I/H/L H or L or I - phbsu100ct8sm

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 23

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

AB18

AB14

AA14

AA13

Y14

AC11

Y13

L23

M22

AC22

AB21

AC21

I/O state@ Reset mode

Name

XmiIRQn XmiIRQn O H/L Hi-z or H or L H phot8

XmiOEn XmiOEn I I - - phisu

XmiWEn XmiWEn I I - - phisu

XmsBS XmsBS O L/L Hi-z or H or L L phot8

XmsPI XmsPI I I - - phis

XmsSCLKO XmsSCLKO O H/L Hi-z or H or L H phot8

XmsSDIO XmsSDIO I/O I/H/L H or L or I -

XpADDR[0] XpADDR[0] O

XpADDR[1] XpADDR[1] O

XpADDR[10] XpADDR[10] O

XpADDR[11] XpADDR[11] O

XpADDR[12] XpADDR[12] O

Default

Function

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

L/L

L/L

L/L

L/L

L/L

I/O

State@SLEEP

mode

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

I/O

State@STOP

mode

Cell Type

(24A0A)

phbsu100ct12s

m

Y17

AC20

M20

M23

N21

N22

N23

P22

AB23

AC23

V23

U22

XpADDR[13] XpADDR[13] O

XpADDR[14] XpADDR[14] O

XpADDR[2] XpADDR[2] O

XpADDR[3] XpADDR[3] O

XpADDR[4] XpADDR[4] O

XpADDR[5] XpADDR[5] O

XpADDR[6] XpADDR[6] O

XpADDR[7] XpADDR[7] O

XpADDR[8] XpADDR[8] O

XpADDR[9] XpADDR[9] O

XpCASn XpCASn O H/L Hi-z or H or L Pre phot12sm

XpCKE XpCKE O L/L Hi-z or H or L L phot12sm

L/L

L/L

L/L

L/L

L/L

L/L

L/L

L/L

L/L

L/L

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Hi-z or H or L Pre phot12sm

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-23

Page 24

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

W22

W23

F21

E23

K22

K23

L21

L22

L20

M21

P21

R21

P23

R22

E22

T21

T22

U21

T23

T20

Y21

Y23

Y22

I/O state@ Reset mode

Name

XpCSN[0] XpCSN[0] O H/L Hi-z or H or L H phot12sm

XpCSN[1] XpCSN[1] O H/L Hi-z or H or L H phot12sm

XpDATA[0] XpDATA[0] I/O I/H/L H or L or I -

XpDATA[1] XpDATA[1] I/O I/H/L H or L or I -

XpDATA[10] XpDATA[10] I/O I/H/L H or L or I -

XpDATA[11] XpDATA[11] I/O I/H/L H or L or I -

XpDATA[12] XpDATA[12] I/O I/H/L H or L or I -

XpDATA[13] XpDATA[13] I/O I/H/L H or L or I -

XpDATA[14] XpDATA[14] I/O I/H/L H or L or I -

XpDATA[15] XpDATA[15] I/O I/H/L H or L or I -

XpDATA[16] XpDATA[16] I/O I/H/L H or L or I -

XpDATA[17] XpDATA[17] I/O I/H/L H or L or I -

XpDATA[18] XpDATA[18] I/O I/H/L H or L or I -

XpDATA[19] XpDATA[19] I/O I/H/L H or L or I -

XpDATA[2] XpDATA[2] I/O I/H/L H or L or I -

XpDATA[20] XpDATA[20] I/O I/H/L H or L or I -

XpDATA[21] XpDATA[21] I/O I/H/L H or L or I -

XpDATA[22] XpDATA[22] I/O I/H/L H or L or I -

XpDATA[23] XpDATA[23] I/O I/H/L H or L or I -

XpDATA[24] XpDATA[24] I/O I/H/L H or L or I -

XpDATA[25] XpDATA[25] I/O I/H/L H or L or I -

XpDATA[26] XpDATA[26] I/O I/H/L H or L or I -

XpDATA[27] XpDATA[27] I/O I/H/ L H or L or I -

Default

Function

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

I/O

State@SLEEP

mode

I/O

State@STOP

mode

Cell Type

(24A0A)

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

1-24

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 25

BSW rv0.1-0417-N01

r

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Numbe

AA23

V21

F23

AB22

AA22

H20

G21

F22

G23

J23

K21

I/O state@ Reset mode

Name Default Function I/O

XpDATA[28] XpDATA[28] I/O I/H/L H or L or I XpDATA[29] XpDATA[29] I/O I/H/L H or L or I -

XpDATA[3] XpDATA[3] I/O I/H/L H or L or I -

XpDATA[30] XpDATA[30] I/O I/H/L H or L or I -

XpDATA[31] XpDATA[31] I/O I/H/L H or L or I -

XpDATA[4] XpDATA[4] I/O I/H/L H or L or I -

XpDATA[5] XpDATA[5] I/O I/H/L H or L or I -

XpDATA[6] XpDATA[6] I/O I/H/L H or L or I -

XpDATA[7] XpDATA[7] I/O I/H/L H or L or I -

XpDATA[8] XpDATA[8] I/O I/H/L H or L or I -

XpDATA[9] XpDATA[9] I/O I/H/L H or L or I -

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

I/O

State@SLEEP

mode

State@STOP

mode

I/O

Cell Type

(24A0A)

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

phbsu100ct12s

m

G22

H22

H23

J22

U23

R23

V22

D16

C14

A18

B19

D21

XpDQM[0] XpDQM[0] O

XpDQM[1] XpDQM[1] O

XpDQM[2] XpDQM[2] O

XpDQM[3] XpDQM[3] O

XpRASn XpRASn O

XpSCLK XpSCLK I/O

XpWEn XpWEn O

XrADDR[0] XrADDR[0] O L/L Hi-z or H or L Pre phot8

XrADDR[1] XrADDR[1] O L/L Hi-z or H or L Pre phot8

XrADDR[10] XrADDR[10] O L/L Hi-z or H or L Pre phot8

XrADDR[11] XrADDR[11] O L/L Hi-z or H or L Pre phot8

XrADDR[12] XrADDR[12] O L/L Hi-z or H or L Pre phot8

H/L

H/L

H/L

H/L

H/L

H or L /L

H/L

Hi-z or H or L - phot12sm

Hi-z or H or L - phot12sm

Hi-z or H or L - phot12sm

Hi-z or H or L - phot12sm

Hi-z or H or L - phot12sm

H or L or I L phbst12

Hi-z or H or L H phot12sm

1-25

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 26

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-2. 337-Pin FBGA Pin Assignments

I/O state@ Reset

Pin

Number

Name Default Function I/O

mode

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

I/O

State@SLEEP

mode

I/O

State@STOP

mode

Cell Type

(24A0A)

G20

D17

B20

A19

A20

D15

A13

D14

B14

C15

A14

D20

XrADDR[13] XrADDR[13] O L/L Hi-z or H or L Pre phot8

XrADDR[14] XrADDR[14] O L/L Hi-z or H or L Pre phot8

XrADDR[15] XrADDR[15] O L/L Hi-z or H or L Pre phot8

XrADDR[16] XrADDR[16] O L/L Hi-z or H or L Pre phot8

XrADDR[17] XrADDR[17] O L/L Hi-z or H or L Pre phot8

XrADDR[2] XrADDR[2] O L/L Hi-z or H or L Pre phot8

XrADDR[3] XrADDR[3] O L/L Hi-z or H or L Pre phot8

XrADDR[4] XrADDR[4] O L/L Hi-z or H or L Pre phot8

XrADDR[5] XrADDR[5] O L/L Hi-z or H or L Pre phot8

XrADDR[6] XrADDR[6] O L/L Hi-z or H or L Pre phot8

XrADDR[7] XrADDR[7] O L/L Hi-z or H or L Pre phot8

XrADDR[8] XrADDR[8] O L/L Hi-z or H or L Pre phot8

C20

F20

D18

A21

C21

B21

A22

E21

D23

P20

1-26

XrADDR [9] XrADDR [9] O L/L Hi-z or H or L Pre phot8

XrADDR[18] XrADDR[18] O L/L/H Hi-z or H or L Pre

XrADDR[19] XrADDR[19] O L/L/H Hi-z or H or L Pre phbsu100ct8sm

XrADDR[20] XrADDR[20] O L/L/H Hi-z or H or L Pre phbsu100ct8sm

XrADDR[21] XrADDR[21] O L/L/H Hi-z or H or L Pre phbsu100ct8sm

XrADDR[22] XrADDR[22] O L/L/H Hi-z or H or L Pre phbsu100ct8sm

XrADDR[23] XrADDR[23] O L/L/H Hi-z or H or L Pre phbsu100ct8sm

XrADDR[24] XrADDR[24] O L/L/H Hi-z or H or L Pre phbsu100ct8sm

XrADDR[25] XrADDR[25] O L/L/H Hi-z or H or L Pre phbsu100ct8sm

XrCSn[0] XrCSn[0] O H/L Hi-z or H or L Pre phot8

phbsu100ct8sm

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 27

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

C17

B17

A11

B11

C18

K20

C19

A17

B18

I/O state@ Reset mode

Name

XrCSn[1] XrCSn[1] O H/L Hi-z or H or L Pre phot8

XrCSn[2] XrCSn[2] O H/L Hi-z or H or L Pre phot8

XrDATA[0] XrDATA[0] I/O I/H/L H or L or I -

XrDATA[1] XrDATA[1] I/O

XrDATA[10] XrDATA[10] I/O I/H/L H or L or I -

XrDATA[11] XrDATA[11] I/O I/H/L H or L or I -

XrDATA[12] XrDATA[12] I/O I/H/L H or L or I -

XrDATA[13] XrDATA[13] I/O I/H/L H or L or I -

XrDATA[14] XrDATA[14] I/O I/H/L H or L or I -

Default

Function

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

I/H/L

I/O

State@SLEEP

mode

H or L or I -

State@STOP

I/O

mode

Cell Type

(24A0A)

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

J20

V20

B12

U20

A12

C13

B13

A16

N20

B15

A15

R20

XrDATA[15] XrDATA[15] I/O I/H/L H or L or I -

XrDATA[2] XrDATA[2] I/O I/H/L H or L or I -

XrDATA[3] XrDATA[3] I/O I/H/L H or L or I -

XrDATA[4] XrDATA[4] I/O I/H/L H or L or I -

XrDATA[5] XrDATA[5] I/O I/H/L H or L or I -

XrDATA[6] XrDATA[6] I/O I/H/L H or L or I -

XrDATA[7] XrDATA[7] I/O I/H/L H or L or I -

XrDATA[8] XrDATA[8] I/O I/H/L H or L or I -

XrDATA[9] XrDATA[9] I/O I/H/L H or L or I -

XrnWBE[0] XrnWBE[0] O H/L Hi-z or H or L Pre phot8

XrnWBE[1] XrnWBE[1] O H/L Hi-z or H or L Pre phot8

XrOEn XrOEn O

H/L

Hi-z or H or L H phot8

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

phbsu100ct8sm

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-27

Page 28

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

AA1

AB3

C16

B16

AC13

AB12

AC12

Y11

AB9

AC6

Y3

W2

I/O state@ Reset mode

Name

XrtcXTI XrtcXTI Ain

XrtcXTO XrtcXTO Aout X - - rtc_osc

XrWAITn XrWAITn I I - - phis

XrWEn XrWEn O H/L Hi-z or H or L H phot8

XsdDAT[0] XsdDAT[0] I/O I/H/L H or L or I - phbsu100ct12sm

XsdDAT[1] XsdDAT[1] I/O I/H/L H or L or I - phbsu100ct12sm

XsdDAT[2] XsdDAT[2] I/O I/H/L H or L or I - phbsu100ct12sm

XsdDAT[3] XsdDAT[3] I/O I/H/L H or L or I - phbsu100ct12sm

XsEXTCLK XsEXTCLK I I - - phis

XsMPLLCAP XsMPLLCAP Aout X - - phob1_abb

XspiCLK XspiCLK I/O I/H/L H or L or I - phtbsu100ct8sm

XspiMISO XspiMISO I/O H/L/L H or L or I H phtbsu100ct8sm

Default

Function

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

L

I/O

State@SLEEP

mode

--rtc_osc

I/O

State@STOP

mode

Cell Type

(24A0A)

V1

W3

V2

AA9

Y9

AB8

Y1

AC9

AA10

V4

T2

AB11

Y10

P1

R2

AA12

XspiMOSI XspiMOSI I/O I/H/L H or L or I - phtbsu100ct8sm

XspiSSIn[0] XspiSSIn[0] I I - - phisu

XspiSSIn[1] XspiSSIn[1] I I - - phisu

XsRESETn XsRESETn I L - - phisu

XsRSTOUTn XsRSTOUTn O L Hi-z or H or L H phot8

XsUPLLCAP XsUPLLCAP Aout X - - phob1_abb

XsWRESETn XsWRESETn I L - - phisu

XsXTIN XsXTIN I H or L - -

XsXTOUT XsXTOUT O H or L - -

XuCLK XuCLK I I - - phis

XuCTSn XuCTS n I I - - phis

XudDN XudDN I/O I H or L or I - pbusb1

XudDP XudDP I/O I H or L or I - pbusb1

XuRTSn XuRTSn O H/L Hi-z or H or L H phot8

XuRXD XuRXD I I - - phisu

XusDN[0] XusDN[0] I/O X H or L or I - pbusb1

phsoscm26_schmit

t

phsoscm26_schmit

t

1-28

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 29

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

Table 1-2. 337-Pin FBGA Pin Assignments

Pin

Number

AC10

AA11

AB10

U3

A9

C9

A8

J4

B7

K4

I/O state@ Reset mode

Name

XusDN[1] XusDN[1] I/O X H or L or I - pbusb1

XusDP[0] XusDP[0] I/O X H or L or I - pbusb1

XusDP[1] XusDP[1] I/O X H or L or I - pbusb1

XuTXD XuTXD O H/L Hi-z or H or L H phot8

XvDEN XvDEN O L/L Hi-z or H or L L phot8

XvHSYNC XvHSYNC O

XvVCLK XvVCLK O H or L /L Hi-z or H or L L phot12sm

XvVD[6] XvVD[6] O L/L H or L or I Pre phot12sm

XvVD[7] XvVD[7] O L/L H or L or I Pre phot12sm

XvVD[8] XvVD[8] O L/L H or L or I Pre phot12sm

Default

Function

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

L/L

I/O

State@SLEEP

mode

Hi-z or H or L Pre phot8

I/O

State@STOP

mode

Cell Type

(24A0A)

D7

D8

B8

B9

D12

D3

C10

B10

D13

C11

G4

XvVD[9] XvVD[9] O L/L H or L or I Pre phot12sm

XvVD[10] XvVD[10] O L/L H or L or I Pre phot12sm

XvVD[11] XvVD[11] O L/L H or L or I Pre phot12sm

XvVD[12] XvVD[12] O L/L H or L or I Pre phot12sm

XvVD[13] XvVD[13] O L/L H or L or I Pre phot12sm

XvVD[0] XvVD[0] O L/L H or L or I Pre phot12sm

XvVD[14] XvVD[14] O L/L H or L or I Pre phot12sm

XvVD[15] XvVD[15] O L/L H or L or I Pre phot12sm

XvVD[16] XvVD[16] O L/L H or L or I Pre phot12sm

XvVD[17] XvVD[17] O L/L H or L or I Pre phot12sm

XvVD[1] XvVD[1] O L/L H or L or I Pre phot12sm

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-29

Page 30

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

Table 1-2. 337-Pin FBGA Pin Assignments

I/O state@ Reset mode

Pin

Number

C5

A6

H4

A7

D11

Name

XvVD[2] XvVD[2] O L/L H or L or I Pre phot12sm

XvVD[3] XvVD[3] O L/L H or L or I Pre phot12sm

XvVD[4] XvVD[4] O L/L H or L or I Pre phot12sm

XvVD[5] XvVD[5] O L/L H or L or I Pre phot12sm

XvVSYNC XvVSYNC O L/L Hi-z or H or L L phot8

Default

Function

I/O

(Data/En/PullupEn)

En(L)=>output

PullupEn(L)=>PullUp

Notes:

1.‘-‘ mark indicates the unchanged pin state

2. Hi-z or Pre means Hi-z or Previous value

3. P, I and O mean power, input and output respectively

4. AI/AO means analog input/output

I/O

State@SLEEP

mode

I/O

State@STOP

mode

Cell Type

(24A0A)

The table below show s I/O types and the descriptions.

I/O Type Descriptions

vdd12ih 1.2V Vdd for alive

vdd12ih_core 1.2V Vdd for internal logic

vdd33oph 3.3V Vdd for external logic

vdd33th_abb 3.3V Vdd for analog circuit

vdd30th_rtc 3.3V Vdd for rtc circuit

vdd33th_abb 3.3V Vdd for pll circuit

Vss Vss

Phis Input pad, LVCMOS schmitt-trigger level

Phisu Input pad, schmitt-trigger level, pull-up

Phisd Input pad, schmitt-trigger level, pull-down

Pbusb USB pad

phot8 Output pad, tri-state, Io=8mA

phob8 Output pad, Io=8mA

phot12sm Output pad, tri-state, medium slew rate, Io=12mA

1-30

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 31

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

phbst12sm Bi-directional pad, LVCMOS schmitt-trigger, pull-up resistor with

control, tri-state, Io=12mA

pbusb1 USB pad

Rtc-osc rtc X-tal

phob1-abb Analog pad

phiar10_abb Analog input pad with 10-ohm resistor

phia_abb Analog input pad

phsoscm26_shm itt Oscillator cell with enable and feedback resistor

phbsu100ct8sm Bi-directional pad, LVCMOS schmitt-trigger, 100Kohm pull-up resistor with

control, tri-state, Io=8mA

phbsu100ct12sm Bi-directional pad, LVCMOS schmitt-trigger, 100Kohm pull-up resistor with

control, tri-state, Io=12mA

phbsud8sm Bi-directional pad, schmitt-trigger, pull-up resistor with, open-drain

control, Io=8mA

Note) phbsu1 00c t8sm mea n s a bi-directional pad, but this means input pad so long as phbsu1 00c t8sm is used for

XciCDATA[7:0]

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-31

Page 32

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

1.3 PIN DESCRIPTIONS

1.3.1 I/O Signal Descriptions

1.3.1.1 External Memory Interface

• Shared Memory Bus (ROM/SRAM/NOR Flash/NAND Flash/External Bus)

Signal I/O Description

XrADDR[25:0] O XrADDR[25:0] (Address Bus for shared memory) outputs the memory address of the

corresponding bank .

XrDATA[15:0] IO XrDATA[15:0] (Data Bus) inputs data during memory read and outputs data during

memory write. The bus width is programmable among 8/16-bit.

XrCSn[2:0] O XrCSn[2:0] (Chip Select) are activated when the address of a memory is within the

address region of each bank. The number of access cycles and the bank size can be

programmed.

XrWEn O XrWEn (Write Enable) indicates that the current bus cycle is a write cycle.

XrOEn O XrOEn (Output Enable) indicates that the current bus cycle is a read cycle.

XrWAIT n I XrWAITn requests to prolong a current bus cycle. As long as XrWAITn n is L, the

current bus cycle cannot be completed.

XrnWBE[1:0 ] O Write Byte Enable

XfCLE O Nand Flash Command Latch Enable

XfALE O Nand Flash Address Latch Enable

XfNFPS I Nand Flash Page Size (0:256HWord, 1:512Byte)

or Advanced Page size(0:1K Hword , 1:2K Byte)

XfNFB W I Nand Flash Bus Width (0:8-bit, 1:16-bit)

XfNFACYC I Nand Flash Address Step (0:3-step, 1:4-step)

or Advanced Address step(0:4-step, 1:5-step)

XfNFADV I To Support adv anced 2G Nand Flash

XfRnB[1:0] I Nand Flash Ready and Busy

• SDRAM Bank 0

Signal I/O Description

XpCSN[1:0] O SDRAM bank 0 Chip Select

XpCASn O SDRAM bank 0 Column Address Strobe

XpRASn O SDRAM bank 0 Row Address Strobe

XpWEn O SDRAM bank 0 Write Enable

XpCKE O SDRAM bank 0 Clock Enable

XpDQM[3:0] O SDRAM bank 0 Data Mask

XpSCLK IO SDRAM bank 0 Clock

XpADDR[14:0] O SDRAM bank 0 Address bus

XpDATA[31:0] O SDRAM bank 0 Data bus

1-32

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 33

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

1.3.1.2 Serial Communication

• UART

Signal I/O Description

XuCLK I UART 0 clock signal

XuRXD0 I U AR T 0 receives data input

XuCTSn0 I U A R T 0 clear to send input signal

XuTXD0 O UART 0 transmits data output

XuRTSn0 O U A RT 0 request to send output signal

• IIC Bus

Signal I/O Description

X2cSDA IO IIC-bus data

X2cSCL IO IIC-bus clock

• IIS Bus

Signal I/O Description

X2sLRCK IO IIS-bus channel select clock

X2sDO O IIS-bus serial data output

X2sDI I IIS-bus serial data input

X2sCLK IO IIS-bus serial clock

X2sCDCLK O CODEC system clock

• SPI Bus

Signal I/O Description

XspiSSIn[1:0] I SPI chip select(only for slave mode)

XspiCLK IO SPI clock for channel 0

XspiMISO IO XspiMISO is the master data input line, when SPI is configured as a master.

When SPI is configured as a slave, these pins reverse its role. For channel 0

XspiMOSI IO XspiMOSI is the master data output line, when SPI is configured as a master.

When SPI is configured as a slave, these pins reverse its role. For channel 0

•

•

AC97

Signal I/O Description

X97BITCLK I AC-Link bit clock(12.288MHz) from AC97 Codec

X97SDI I AC-link Serial Data input from AC97 Codec

X97RESETn O AC- link Reset to Codec

X97SYNC O AC-link Frame Synchronization (Sampling Frequency 48Khz) from AC97 Controllor

X97SDO O AC-link Serial Data output to AC97 Codec

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-33

Page 34

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

• USB Host

Signal I/O Description

XusDN[1:0] IO DATA (–) from USB host

XusDP[1:0] IO DATA(+) from USB host

• USB Device

Signal I/O Description

XudDN IO DATA(–) for USB peripheral dev ice

XudDP IO DATA(+) for USB peripheral device

1.3.1.3 Parallel Communication

• GPIO

Signal I/O Description

XgpIO[31:0] IO General input/output ports

• Modem Interface (8-bit Parallel)

Signal I/O Description

XmiCSn I Chip select, driven by the Modem chip

XmiW En I Write enable, driven by the Modem chip

XmiOEn I Read enable, driven by the Modem chip

XmiADR[10:0] I Address bus, driven by the Modem chip

XmiDATA[7:0] IO Data bus, driven by the Modem chip

XmiIRQn O Interrupt request to the Modem chip

1.3.1.4 Image/Video Processing

• Camera Interface

Signal I/O Description

XciPCLK I Pixel Clock, driven by the Camera processor

XciVSYNC I Vertical Sync, driven by the Camera processor

XciHREF I Horizontal Sync, driven by the Camera processor

XciCDATA[7:0] I Pixel Data for CbCr in 16-bit mode, driven by the Camera processor

XciYDATA[7:0] I Pixel Data for YCbCr in 8-bit mode or for Y in 16-bit mode, driven by the Camera

processor

XciCLK O Master Clock to the Camera processor

XciRSTn O Software Reset to the Camera processor

1-34

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 35

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

1.3.1.5 Display Control

• TFT LCD Display Interface

Signal I/O Description

XvVD[17:0] O LCD pixel data output ports

XvVCLK O Pixel clock signal

XvVSYNC O Vertical synchronous signal

XvHSYNC O Horizontal synchronous signal

XvDEN O Data enable signal

1.3.1.6 Input Devices

• Analog-to-Digital Converter and Touch Screen Interface

Signal I/O Description

XadcAVREF AI ADC Reference top

XadcAIN[7:0] AI ADC Analog Input

1.3.1.7 Storage Devices

• Secure Digital (SD) and Memory Stick Interface

Signal I/O Description

XsdDAT[3:0] IO SD/MMC card receive/transmit Data

XmsPI I Input port used for insertion/extraction detect of Memory stick

XmsSDIO IO

SD/MMC card command signal port (default). If MemoryStick card enable, Memory

stick Serial data in/out port

XmsSCLKO O

XmsBS O

SD/MMC card Clock (default). If MemoryStick card enable, MemoryStick Clock

MemoryStick Serial bus control signal

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-35

Page 36

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

1.3.1.8 System Management

• Reset

Signal I/O Description

XsRESETn I XsRESETn suspends any operation in progress and places S3C24A0 into a known

reset state. For a reset, XsRESE Tn must be held to L level for at least 4 External clock

after the processor power has been stabilized.

XsWRESETn I

System Warm Reset. Reset the whole system while preserves the SDRAM contents

XsRSTOUTn O For external device reset control (XsRS T O UT n = XsRESETn & nWDTRST

& SW_RESET & XsWRESETn)

• Clock

Signal I/O Description

XsMPLLCAP AO Loop filter capacitor for main clock.

XsUPLLCAP AO Loop filter capacitor for USB clock.

XrtcXTI AI 32 KHz crystal input for RTC.

XrtcXTO AO 32 KHz crystal output for RTC.

XsXTIN I Crystal Input for internal osc circuit.

XsXTOUT O Crystal Input for internal osc circuit.

XsEXTCLK I External clock source.

• JTAG

Signal I/O Description

XjTRSTn I XjTRSTn (TAP Controller Reset) resets the TAP controller at start.

If debugger is used, A 10K pull-up resistor has to be connected.

If debugger(black ICE) is not used, TRSTn pin must be issued by a low active

pulse(Typically connected to XsRESETn)

XjTMS I XjTMS (TAP Controller Mode Select) controls the sequence of the TAP controller’s

states. A 10K pull-up resistor has to be connected to TMS pin.

XjTCK I XjTCK (TAP Controller Clock) provides the clock input for the JTAG logic.

A 10K pull-up resistor must be connected to TCK pin.

XjRTCK O X jRTCK (TAP Controller Returned Clock) provides the clock output for the JTAG logic.

XjTDI I XjTDI (TAP Controller Data Input) is the serial input for test instructions and data.

A 10K pull-up resistor must be connected to TDI pin.

XjTDO O XjTDO (TAP Controller Data Output) is the serial output for test instructions and data.

1-36

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 37

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

• Misc

Signal I/O Description

I Clock Source Selection

XgREFCLKSEL determines how the clock is made.

XgREFCLKSEL[1:0]

XgREFCLKSEL[0] - ‘0’ : Main clock source is from XsX TI N ,

‘1’ : Main clock source is from XsEXTC LK

XgREFCLKSEL[1] - ‘0’ : USB clock source is from XsXTIN

‘1’ : USB clock source is from XsEXT CLK

XgTMODE[3]

I ‘0’ : PAD JTAG(Selection of ARM core boundary scan)

‘1’ : ARM JTAG(Selection of S3C24A0 boundary scan)

XgTMODE[2:1]

I These signals must be reserved ‘00 ’

XgTMODE[0]

‘0’ : Normal Operation without NAND BOOT

‘1’ : Normal Operation with NAND BOOT

XgBATFLTn

I Probe for battery state (Does not wake up at Stop and Sleep mode in case of low

battery state)

XgPWROF F n O 1.2V core power on-off control signal

XgMONHCLK

O HCLK clock monitoring. HCLK clock can be monitored through this pin when the

ClkMonOn bit in the CLKCON register is set.

1.3.1.9 Power -supply Groups

• VDD

Signal I/O Description

XxVDDlogic P Core logic VDD (1.2V) for internal logic

XxVDDalive P S3C24A0 reset block and port status register VDD (1.2V).

It should be always supplied whether in normal mode or in Stop and Sleep mode.

XxVDDarm P Core logic VDD (1.2V) for CPU

XxVDDMpll P S3C24A0 MPLL analog and digital VDD (1.2 V).

XxVDDUpll P S3C24A0 UPLL analog and digital VDD (1.2V)

XxVDDpadIO P S3C24A0 I/O port VDD (3.3V)

XxVDDpadSDRAM P S3C24A 0 SDRAM memory IO VDD (3.3V)

XxVDDpadFlash P S3C24A0 NFLASH memory IO VDD (3.3V)

XxVDDpadUSB P S3C24A0 USB IO VDD (3.3V)

XrtcVDD P RTC VDD (3.3V)

(Although RTC function is not used, this pin should be conne cted to power)

XadcVDD P S3C24A0 ADC VDD(3.3V)

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-37

Page 38

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

• VSS

Signal I/O Description

Core logic VSS for internal logic

VSS for S3C24A0 reset block and port status register

VSS

P

Core logic VSS for CPU

S3C24A0 I/O port VSS

XxVSSpadSDRAM

XxVSSpadFlash

XxVSSpadUSB

P S3C24A0 SDRAM memory IO VSS

P S3C24A0 Flash memory IO VSS

P S3C24A0 USB IO VSS

XxVSSMpll P S3C24A0 MPLL analog and digital VSS.

XxVSSUpll P S3C24A0 UPLL analog and digital VSS

XrtcVSS P RTC VSS

XadcVSS P S3C24A0 ADC VSS

Note:

1. I/O means input/output.

2. AI/AO means analog input/output.

3. P means power.

1-38

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 39

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW

1.4 Address MAP

1.4.1 Address Space Assignment Overview

0xFFFF_FFFF

0x5000_0000

0x4800_0000

0x4400_0000

0x4000_0000

0x2000_0000

0x1800_0000

0x1000_0000

0x0c00_0000

0x0800_0000

0x0400_0000

0x0000_0000

SROM_BW[9] = 0

TMODE[2:0] = 000

Reserved

AHB_I SFRs

APB SFRs

AHB_S SFRs

Reserved Reserved Reserved

SDRAM

(XpCSn1)

SDRAM

(XpCSn0)

Stepping stone

(4KB, No CS)

SROM

(XrCSn2)

SROM

(XrCSn1)

SROM

(XrCSn0)

[Not using NAND flash for boot ROM]

SROM_BW[9] = 1

TMODE[2:0] = 000

Reserved Reserved

AHB_I SFRs

APB SFRs

SDRAM

(XpCSn1)

SDRAM

(XpCSn0)

Reserved Reserved

Stepping stone

(4KBytes)

SROM

(XrCSn1)

SROM

(XrCSn0)

TMODE[2:0] = 001

[Using NAND flash for boot ROM]

AHB_I SFRs

APB SFRs

AHB_S SFRs

SDRAM

(XpCSn1)

SDRAM

(XpCSn0)

SROM

(XrCSn2)

SROM

(XrCSn1)

Stepping stone

(4KBytes)

128MB

64MB

64MBAHB_S SFRs

128MB

128MB

64MB

64MB

64MB

64MB

Assigned

for

Special Function

Registers

Assigned

for

SDRAM Bank0/1

Accessible Region

Assigned

for

SROM Bank0/1/2

Accessible Region

NOTES:

1. SROM means ROM or SRAM type memory.

2. SFR means Special Function Register.

Figure 1-2. Address map

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

1-39

Page 40

BSW rv0.1-0417-N01

PRELIMINARY PRODUCT OVERVIEW S3C24A0 RISC MICROPROCESSOR

1.4.2 Device Specific Address Space

• AHB_S (System-side AHB Bus) Devices: Base = 0x4000_0000 (just above 1GB), Size = 64MB

- Physical Address = Base Address + Device Offset + Register Offset

Device Offset Size (MB) Group Device Note

0x00_0_0000 1 AHB_S SystemCtrl

0x01_0_0000 1 AHB_S Reserved

0x02_0_0000 1 AHB_S INTC

0x03_0_0000 1 AHB_S Reserved

0x04_0_0000 1 AHB_S DMA 0

0x05_0_0000 1 AHB_S DMA 1

0x06_0_0000 1 AHB_S DMA 2

0x07_0_0000 1 AHB_S DMA 3

0x08_0_0000 4 AHB_S Reserved

0x0C_0_0000 1 AHB_S MemCtrl

0x0D_0_0000 3 AHB_S Reserved

0x10_0_0000 1 AHB_S USB Host

0x11_0_0000 1 AHB_S Modem IF0

0x12_0_0000 6 AHB_S Reserved

0x18_0_0000 1 AHB_S IrDA

0x19_0_0000 7 AHB_S Reserved

0x20_0_0000 16 AHB_S EXT AHB

0x30_0_0000 16 AHB_S Reserved

0x40_0_0000 64 AHB_S APB devices Through AHB to APB Bridge

0x80_0_0000 128 AHB_S AHB_I devices Through AHB to AHB Bridge

• APB Devices: Base = 0x4000_0000

Device Offset Size (MB) Group Device Note

0x40_0_0000 1 APB PW M Timer

0x41_0_0000 1 APB W atch Dog Timer

0x42_0_0000 1 APB RTC

0x43_0_0000 1 APB Reserved

0x44_0_0000 1 APB UART

0x45_0_0000 1 APB SPI

0x46_0_0000 1 APB I2C

0x47_0_0000 1 APB I2S

0x48_0_0000 1 APB GPIO

0x49_0_0000 1 APB KEYPAD Interface

0x4A_0_0000 1 APB USB Device

0x4B_0_0000 5 APB Reserved

0x50_0_0000 1 APB AC97

0x51_0_0000 7 APB Reserved

0x58_0_0000 1 APB ADC/Touch Screen

0x59_0_0000 7 APB Reserved

0x60_0_0000 1 APB SD/MMC

0x61_0_0000 1 APB Memory Stick

0x62_0_0000 14 APB Reserved

0x70_0_0000 16 APB Reserved

1-40

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available.

Specifications and information herein are subject to change without notice.

Page 41

BSW rv0.1-0417-N01

S3C24A0 RISC MICROPROCESSOR PRELIMINARY PRODUCT OVERVIEW