Samsung S1T8528X01-Q0R0 Datasheet

ENHANCED-1 CHIP CT0 RF IC S1T8528

INTRODUCTION

S1T8528 is a 1 CHIP RF IC which can be used in high performance

CTO CLP systems at max. 60MHz. S1T8528 is designed to include a

receiver, PLL and COMPANDER to minimize PCB space

requirements. Improved RX characteristics such as inter-modulation,

spurious response and adjacent channel interface have been

included to satisfy the universal standards.

The 1 CHIP RF IC has considerably reduced the cost by including a

build-in 1’st mixer, low battery detector, fMCU, RSSI, RF regulator

and speaker amp. Also, it fulfills carrier detector threshold control,

speaker volume control, operating mode selection and MUTE function

using S/W, thus making external application easier.

48−QFP−1010E

FEATURES

• Operating voltage range: 2.0V ~ 5.5V

• Typical supply current: 8.9mA at 3.6V

• Built-in low battery detection function ( selectable 3.45V, 3.3V, 3.0V, 2.2V, 2.1V )

• Built-in speaker volume control and speaker amplifier

• Built-in splatter filter

• Support mode selection ( Active, Rx, Standby and Inactive mode )

• FM Receiver

— Excellent Receiver characteristics

< 10.7MHz crystal filter used >

Input sensitivity

0.7µVrms at 12dB

SINAD

— RSSI ( Linear ) and Carrier detector output ( Digital ) function

• Compander

— Easy gain control and application using external component

—-Included ALC (Automatic Level Control) circuit

• Universal PLL

— RX (TX) divided counter range : 1/16 ~ 1/16383

— Reference frequency divided counter range : 1/16 ~ 1/4095

— Lock detector signal output

— Serial interface with MICOM for controlling each block

— Clock Output for MICOM oscillator substitution. ( X-tal divided clock by 2, 3, 4 and 5 )

Adjacent channel

rejection

> 55dB > 60dB > 50dB

Spurious rejection

(image of the second IF)

ORDERING INFORMATION

Device Package Operating Temperature

+ S1T8528X01-Q0R0 48−QFP−1010E −20C to + 70C

+ : New product

Intermodulation

rejection

1

S1T8528 ENHANCED-1 CHIP CT0 RF IC

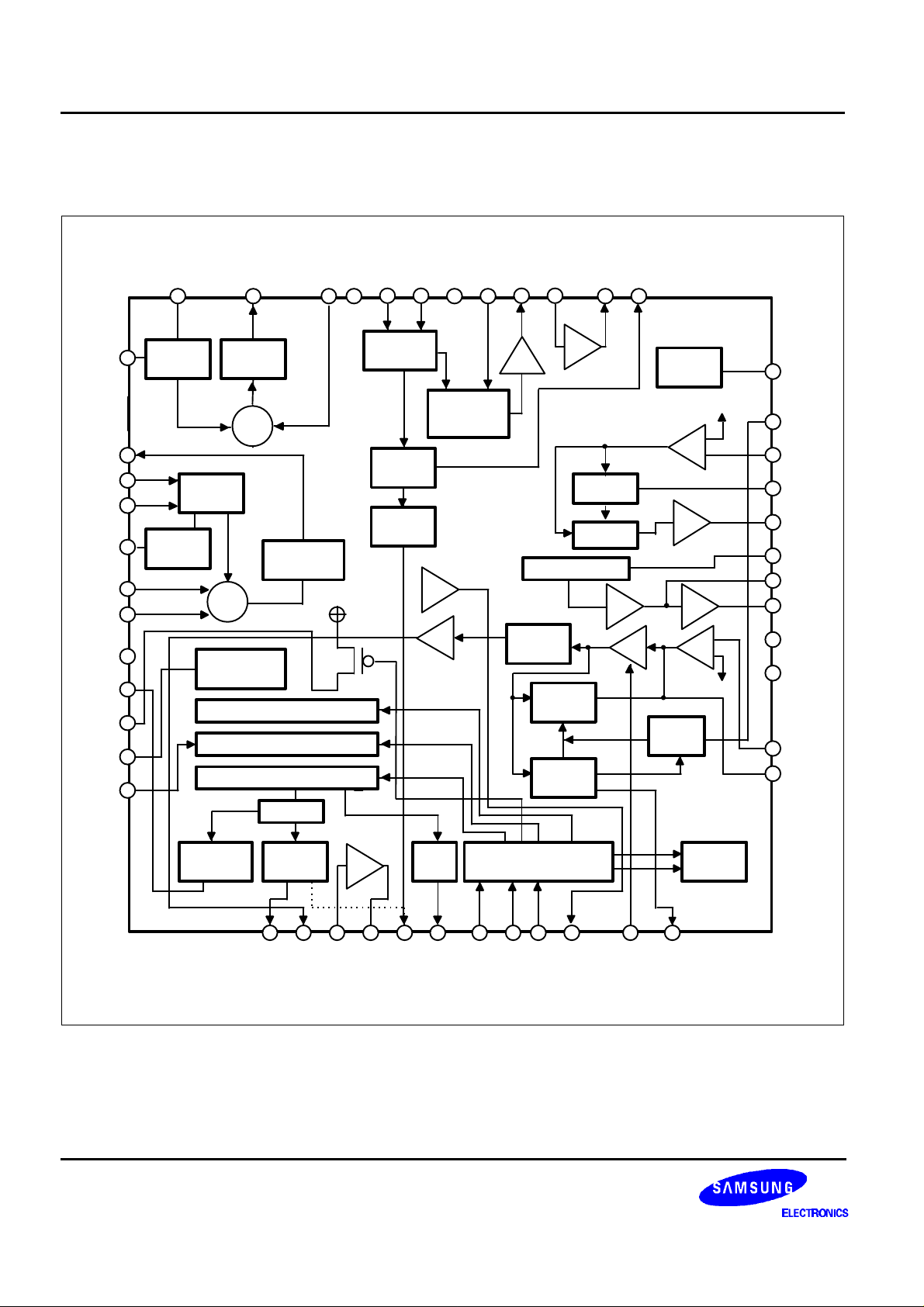

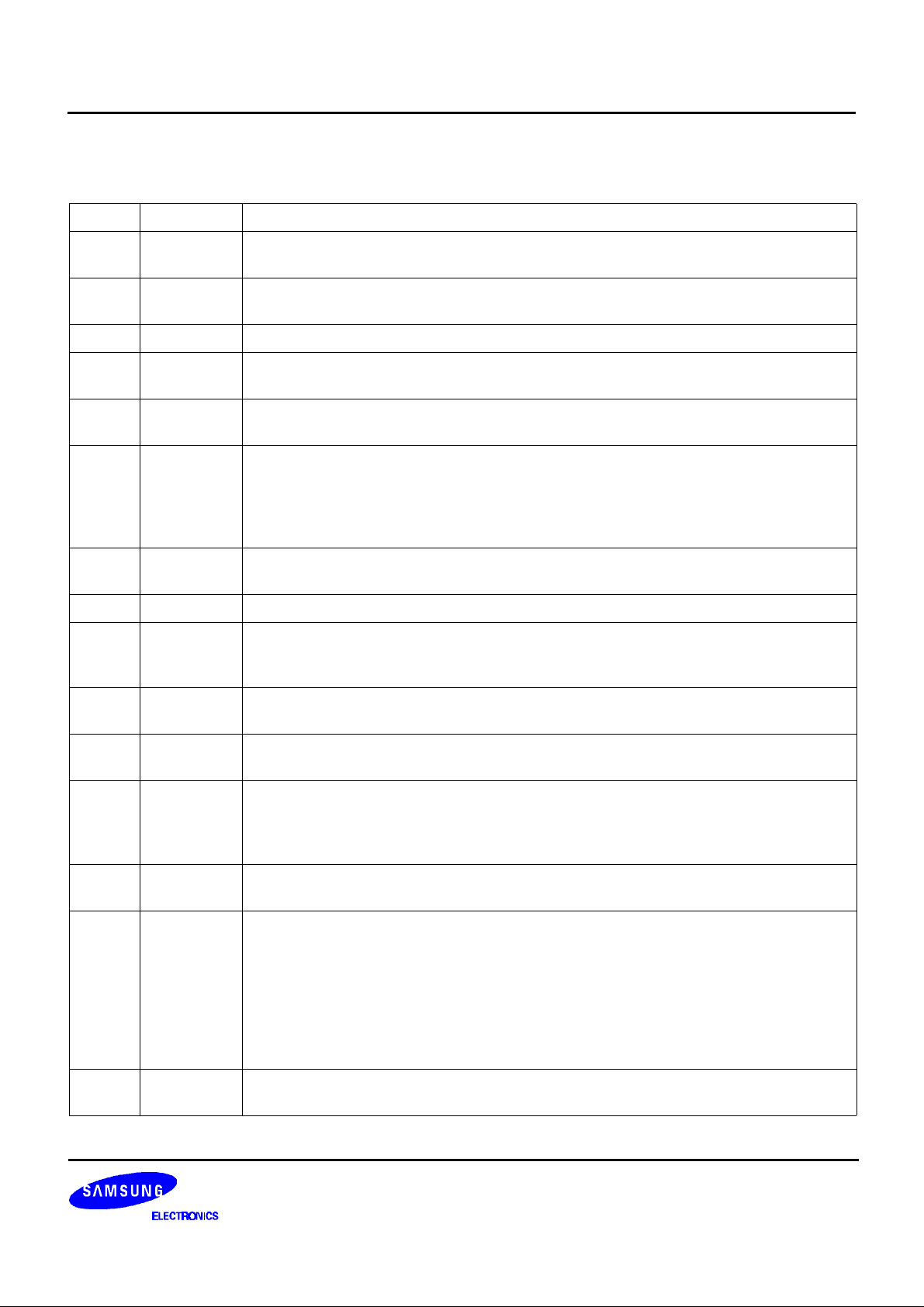

BLOCK DIAGRAM

2LOI

1MO

1LOI

1LOI

VCO

RX

1MI

1MI

GND

(PLL)

PDR

V

REF

(RF)

V

(PLL)

TIF

REF

37

38

39

40

41

42

43

44

45

46

47

48

2LOI

36

X-tal

OSC

2MO

35

IF AMP

(455KHz)

2nd

MIX

RX

VCO

Internal

cap.

IF AMP

(10.7MHz)

1st

MIX

PLL Regulator

( 2.05 V )

Programmable Counter ( RX )

Programmable Counter ( TX )

Programmable Counter ( REF )

4_25 CNT

RX Phase

Detector

TX Phase

Detector

2MI

34 33

VCC

(RX)

(RX)

VCC

32 31

Limiting

IF AMP

Carrier

Detector

Splatter

Filter

LI

RSSI

LD

Quadrature

Detector

Buffer

fMCU

(RX)

GND

QCI

29 28 27

30

AMP

Low

Battery

Detector

CONTROL

RAO

DSCI

FSK

COMP

Rectifier

Gain Cell

Volume control

Limiter

Gain Cell

Rectifier

26

DSCO

SPK

AMP1

25

SUM

AMP

RSSI

Regulator

(Vcc/2)

PRE AMP

ALC

+

-

SUM

AMP

SPK

AMP2

-

+

MIC

AMP

Compander

mute

VREF

VREF

V

REF

24

(COMP)

23

ALC

22

EPI

21

ERC

EO

20

SAI

19

SAO1

18

SAO2

17

VCC

16

(COMP)

GND

15

(COMP)

CPI

14

13

CPO

PDT

CO

SFI

SFO

6

CDO/LDT

CLKO

CLK

DATA

EN

LBD

AGIC

121110 9 8 754 3 1 2

CRC

2

ENHANCED-1 CHIP CT0 RF IC S1T8528

CDO/LDT

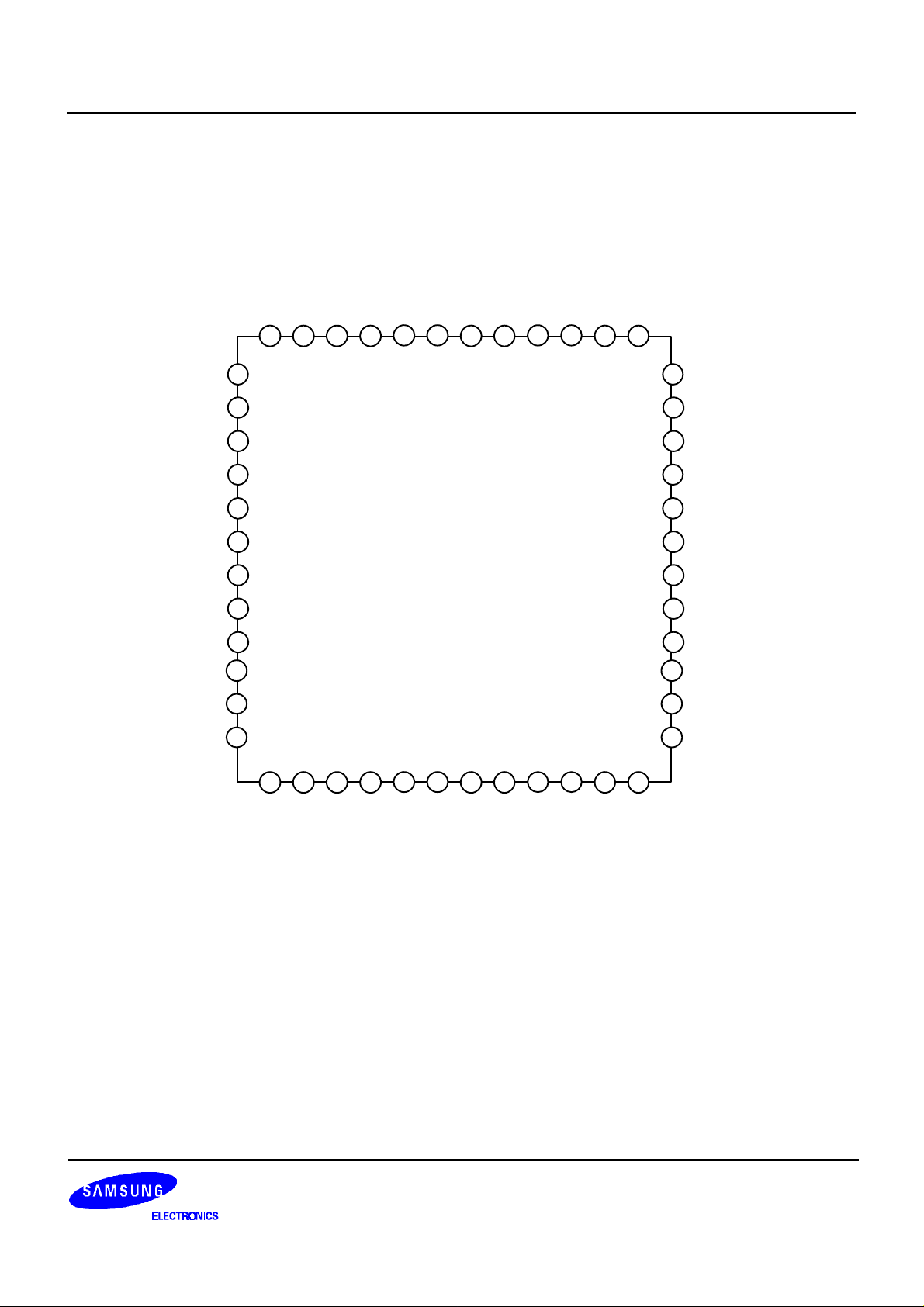

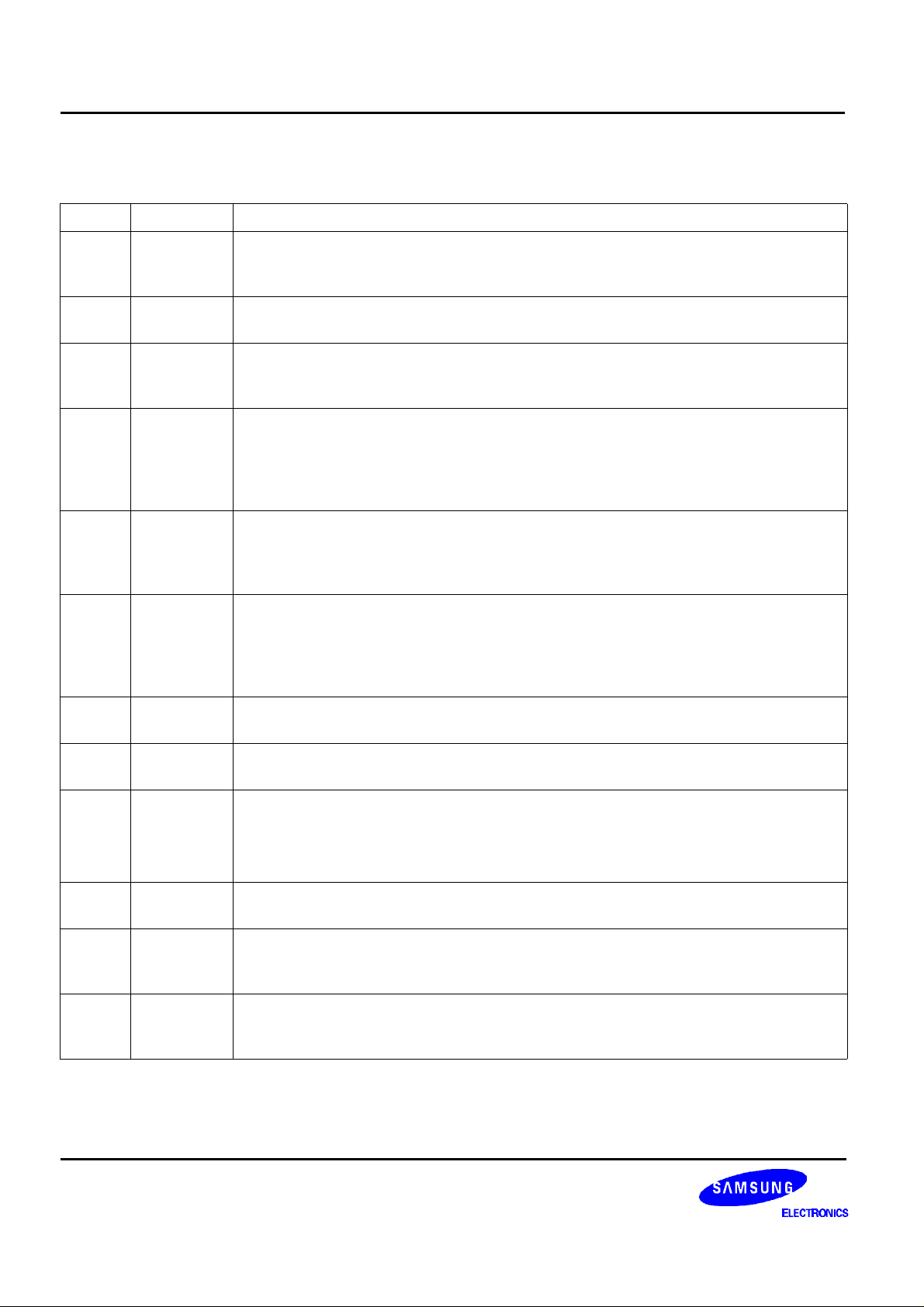

PIN CONFIGURATION

VCO

GND

V

REF(RF)

V

REF(PLL)

2LOI

1MO

1LOI

1LOI

RX

1MI

1MI

(PLL)

PDR

37

38

39

40

41

42

43

44

45

46

47

36

2LOI

35

2MO

34 33

2MI

(RX)

VCC

LI

LD

32 31

30

S1T8528

KB8528

(RX)

GND

QCI

29 28

RAO

DSCI

27 26

DSCO

RSSI

25

24

23

22

21

20

19

18

17

16

15

14

V

REF(COMP)

ALC

EPI

ERC

EO

SAI

SAO1

SAO2

VCC

(COMP)

GND

(COMP)

CPI

TIF

48

1

PDT

2

CO

3

SFI

4 5 6

SFO

7

CLKO

CLK

8

DATA

9

EN

10

11

LBD

12

AGIC

13

CRC

CPO

3

S1T8528 ENHANCED-1 CHIP CT0 RF IC

PIN DESCRIPTION

Pin No Symbol Description

1 PDT Phase detector output terminal of the transmitter at PLL.

If fTX > f

If fTX < f

If fTX = f

2 CO Compressor output terminal of compander: connected to the splatter filter amp input

terminal.

3 SFI Input terminal of Splatter filter amp.

4 SFO Output terminal of Splatter filter amp.

5 LDT/CDO LDT: Output terminal of transmitter lock detector in PLL block. Output is low if PLL is in

CDO: As an output terminal of the carrier detector buffer, connected to (RSSI ) terminal

or fTX is leading → the output is negative pulse

REF

or fTX is lagging → the output is positive pulse

REF

and the same phase → the output is High Impedance

REF

lock state and is high if PLL is in unlock state.

of MICOM. This pin outputs the contents of Meter Driver buffer which is turned

on/off, according to the signal level detected by Meter Driver.

6 f

MCU

Clock output terminal for MCU crystal.

This pin provides the clock source for MCU or other system as an output of

X-tal osc. ÷ 2/ ÷3/ ÷4/ ÷5. Which can be controlled by the bit of the control register.

Clock ON/OFF control is possible by MCU

7

8

9

CLK

DATA

EN

These pins are serial interface terminals for programming reference counter, auxiliary

reference counter, TX channel counter, RX channel counter and control block that

controls internal each block with 4 mode selection.

10 LBD Low Battery Detecting output. ( Selectable 3.45V, 3.3V, 3.0V, 2.2V, 2.0V ).

During the normal operation, output level is low, but it is high at low battery detection.

As this pin is an open collector type, it requires a pull-up resister.

11 AGIC This pin bypasses AC elements at the feedback loop which come from the SUM amp

block of COMPRESSOR. A capacitor should be connected between this terminal and

GND. ( C = 2.2uF )

12 CRC Converts waveform from the full wave rectifier to DC element at the rectifier block of

Compressor. ( RC = 33 msec at C = 3.3uF)

13 CPO- Pre-amp output terminal of Compressor.

Used as an input terminal for voice signals.

14 CPI Inverting type Pre-amp input terminal of Compressor.

15 GND

(COMP

) Ground.

Ground of Compander.

16 Vcc

(COMP)

Supply voltage.

Power supply terminal of Compander.

17 SAO 2 Output terminal of speaker amp 2.

This signal is the same as SAO1 output, but phase difference is 180° for SAO1 DC

voltage level is Vcc / 2.

4

ENHANCED-1 CHIP CT0 RF IC S1T8528

PIN DESCRIPTION (Continued)

Pin No Symbol Description

18 SAO 1 Output terminal of Speaker amp 1.

DC voltage level is Vcc/ 2.

19 SAI Speaker Amp 1 input terminal.

Between this terminal and Expander output terminal, apply DC coupled capacitor.

20 EO Output terminal of Expander

21 ERC Converts waveform from the full wave rectifier to DC element at the rectifier block of

Expander. ( RC = 33 msec at C = 3.3uF )

22 EPI Pre-amp inverting input terminal of Expander.

Adjusts the negative feedback loop gain. ( in application, gain is 5 )

23 ALC Reference current input terminal of Automatic Level Control ( ALC); Adjusts THD of

compressor output voltage to less than 3% or limits the frequency deviation of TX if the

input is higher than a certain level. The ALC circuit may be turned off depending on the

ALC reference current or the magnitude of output voltage may be limited if it is higher

than a certain level.

24 V

REF(COMP)

Reference voltage ( VREF= 1/2 VCC ). Supplies a regulator voltage to the Compressor

and Expander of COMPANDER.

25 RSSI Received Signal Strength Indicator terminal ( Analog type )

26 DSCO Output terminal of Data Slicing comparator.

Separates Frequency Shift Keying ( FSK ) serial data and executes data shaping and

limiting.

27 DSCI Input terminal of Data slicing comparator.

Non-inverting type with the negative input terminal biased to 1/2 Vcc.

28 RAO Recovered Audio Output terminal. Voice signals detected by the Quadrature Detector

are amplified and then output through this terminal.

29 QCI Quadrature coil input terminal.

The 455kHz oscillator circuit is an Lp = 680uH, Cp = 180pF valued LC tank circuit.

Voice signals are detected by mixture of 455kHz ( by phase difference ) which is

converted from mixer 2.

30 GND

RX

Ground .

Ground for Receiver.

31

LD

Limiter input and decoupling terminal.

Limiter block removes amplitude modulation elements caused by fading or FM signal

32

LI

noise. Limiting IF stage makes the second intermediate frequency amplify and limit.

The input impedance of the limiting IF amplifier is set to 1.5kΩ.

While FM waves are transmitted with constant magnitude, their magnitudes are slightly

modulated due to reflection from obstacles, fading phenomenon, noise wave and

mixing with AM wave elements before entering the receiver’s antenna.

The limiter makes amplitude uniform by removing these AM wave elements.

33 V

CC(RX)

Supply voltage.

Supplies power to the Receiver.

5

S1T8528 ENHANCED-1 CHIP CT0 RF IC

PIN DESCRIPTION (Continued)

Pin No Symbol Description

34 2MI Input terminal of mixer 2. Output from mixer 1 is entered to mixer 2 input terminal via

10.7MHz ceramic filter. Second mixer converts frequency to second intermediate

frequency ( 455kHz: AM IF ).

35 2MO Output terminal of Mixer 2. Second intermediate frequency ( 455kHz ), generated by

mixing first intermediate frequency ( 10.7MHz ) and Second Local Oscillator is output.

36

37

2LOI

2LOI

Input terminal of second local oscillator. These pins generate 2’nd local oscillation

frequency and are designed as colpitt type oscillator.

10.24MHz or 10.245MHz can be applied as for 2’nd local oscillator.

38 1MO Output terminal of mixer 1.

The signal from mixer 1 and the frequency of the first local oscillator are mixed to

produce the first intermediate frequency, which is the output through this terminal. The

output terminal is an emitter follower with an output impedance of 330Ω to match the

330Ω input / output impedance of the 10.7MHz ceramic filter.

39

40

1LOI

1LOI

Input terminal of the first local oscillator.

The local oscillator is a voltage controlled oscillator. Local oscillation frequency and

received frequency are mixed at mixer 1 and then converted to the first intermediate

frequency of 10.7MHz or 10.695MHz.

41 VCO

RX

The terminal which variable capacitor is included in the chip. Used as an input terminal

where 1st local oscillation frequency is changed by varying the capacitor connected

between 1st local oscillator terminals.

The internal variable capacitor has the value of 18.73 ~ 15.86 pF depending on the

applied voltage. ( 1.0 ~ 2.0V )

42

43

44 GND

1MI

1MI

(PLL)

Input terminal of Mixer1. This mixer is made of doubly balanced multiplier.

The received signal amplified at RF AMP is input to this terminal.

Ground.

Ground for analog at PLL.

45 PDR Phase detector output terminal of the receiver at PLL.

If fRX > f

If fRX < f

If fRX = f

or fRX is Leading → The output is negative pulse

REF

or fRX is Lagging → The output is positive pulse

REF

and the same phase → The output is high impedance

REF

46 V

REF(RF)

An internal PMOS pass transistor provides power supplier for the RF pre amplifier.

PMOS pass transistor is on in Active/Rx mode and off in Standby/Inactive mode.

47 V

REF(PLL)

PLL voltage reference output pin.

An internal voltage regulator provides a stable power supply voltage for the RX and TX

PLLs. (2.05V)

48 TIF Input terminal of TX channel counter.

AC coupling with TX VCO.

Minimum input level is 300 mVp-p ( at 60MHz ).

6

ENHANCED-1 CHIP CT0 RF IC S1T8528

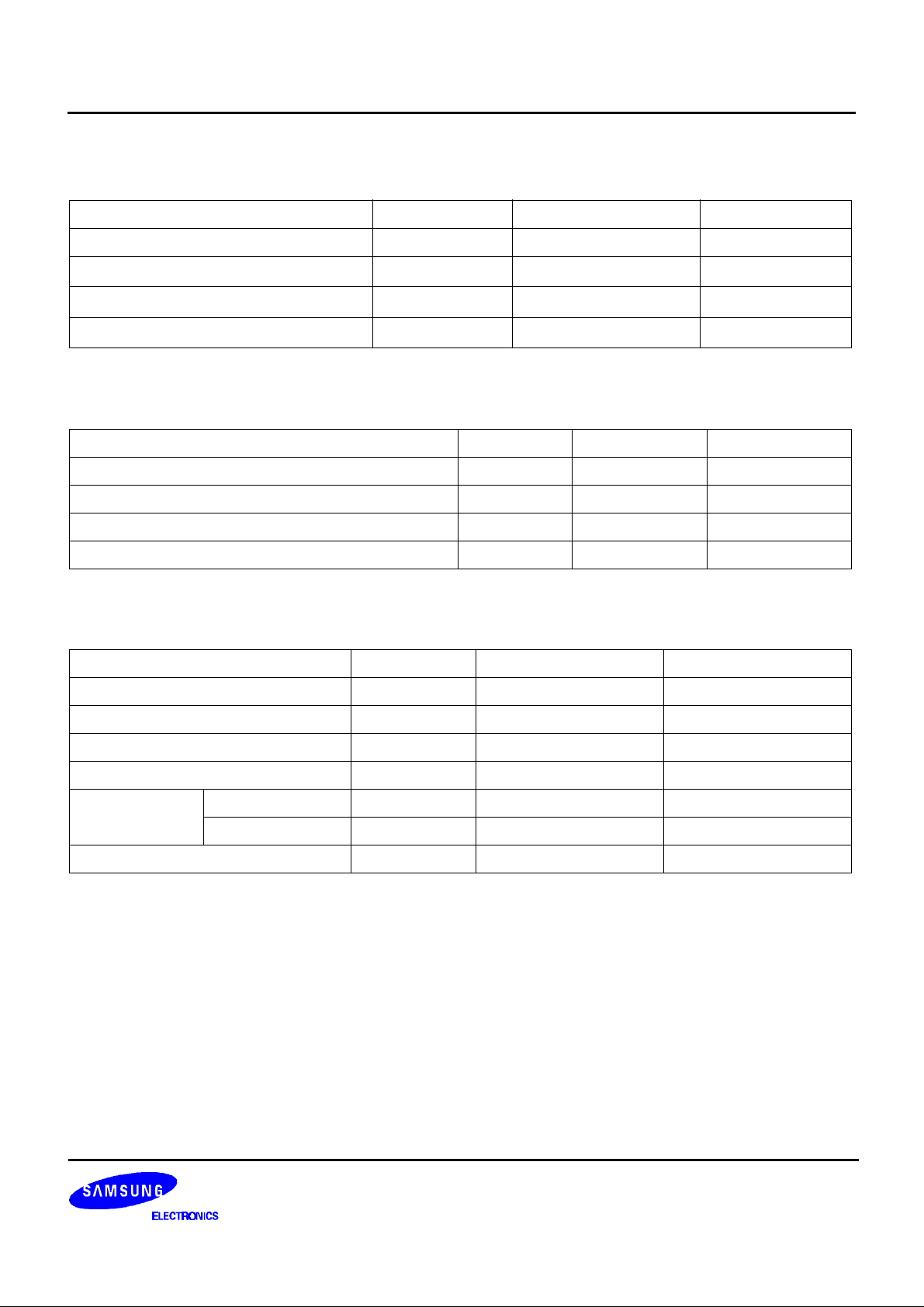

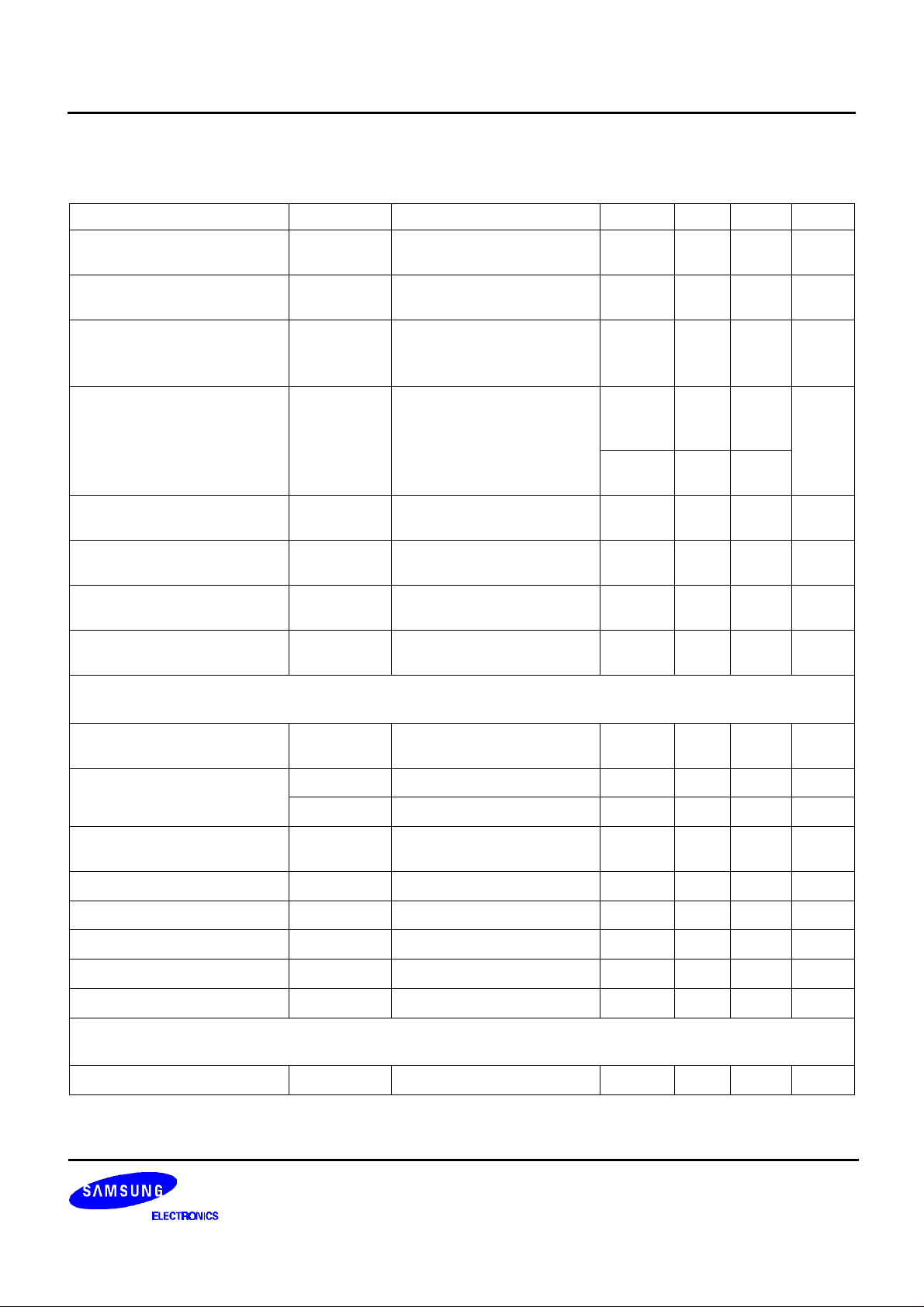

ABSOLUTE MAXIMUM RATINGS

Characteristic Symbol Value Unit

Maximum Supply Voltage Vcc 5.5 V

Power Dissipation P

Operating Temperature T

Storage Temperature T

D

OPR

SCG

600 mW

−20 — + 70 °C

−55 — + 150 °C

CURRENT CONSUMPTION AT EACH MODE ( VCC = 3.6V )

Modes Min. Typ. Max.

Active mode (Communication mode ) − 8.9mA −

RX mode − 4.8mA −

Stand-by mode − 700uA −

Inactive mode (Battery Saving Mode) − 50uA 70uA

CURRENT CONSUMPTION IN EACH BLOCK ( VCC = 3.6V )

Modes Min. Typ. Max.

Receiver part − 3.5mA 4.6mA

Expander part − 0.8mA 1.1mA

Speaker part − 1.0mA 1.4mA

compressor part − 1.7mA 2.1mA

PLL RX part − 1.2mA 1.6mA

TX part − 0.7mA 1.1mA

Total − 8.9mA 11.9mA

7

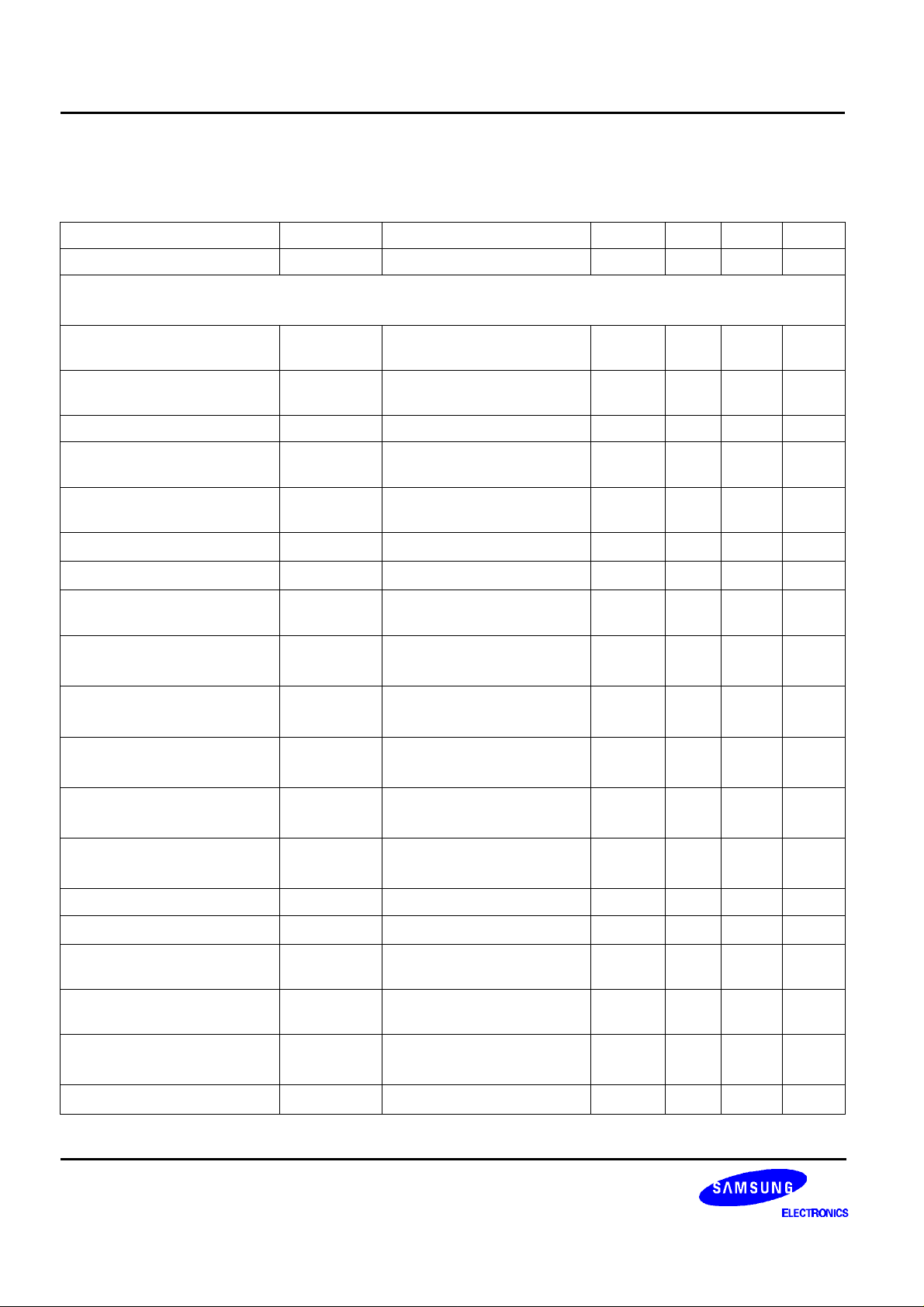

S1T8528 ENHANCED-1 CHIP CT0 RF IC

ELECTRICAL CHARACTERISTICS

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Operating Voltage Vcc − 2.0 − 5.5 V

RECEIVER

( VCC = 3.6V, fC = 49.7MHz, f

Sensitivity

(input for 12dB SINAD)

= ± 3kHz, f

DEV

V

SEN

= 1kHz,Ta = 25°C, unless otherwise specified )

MOD

MIX1 Matched Impedance

− 0.7 2.0 µVrms

Input

Input for -3dB Limiting V

LIM

MIX1 Matched Impedance

− 0.7 2.0 µVrms

Input

S/N Ratio S/N RFin = 1mVrms 48 55 − dB

Recovered Audio Output V

O(RA)

RFin = 1mVrms,

147 177 207 mVrms

After 2nd stage LPF

Recovered Audio Output

Voltage Drop

Detector Output Resistance R

Detect Output Voltage V

Detector Output Distortion THD

V

O(RAD

O(DET)

O(DET)

) Vcc = 5.5V → 2.0V

RFin = 1mVrms

RFin = 1mVrms − 1.2 − KΩ

RFin = 1mVrms 1.0 1.5 2.0 V

DET

RFin = 1mVrms

−3.0 −1.5 − dB

− 1.0 2.5 %

(with CCITT Filter)

Comparator Threshold

Voltage Difference

Comparator Output Voltage 1 V

Comparator Output Voltage 2 VOL V

First Mixer Conversion

Voltage Gain

∆V

∆G

TH

OH

V(1M)

V

R

V

R

R

V

= 360mVp-p

COMP

= 180KΩ

HYS

=360mVp-p

COMP

= 180kΩ

HYS

= 360mVp-p

COMP

= 180kΩ

HYS

MIX1 1/2

= 1mVrms

RL = 330kΩ

70 110 150 mV

Vcc-0.4 − − V

− 0.1 0.4 V

12 15 18 dB

Second Mixer Conversion

Voltage Gain

∆G

V(2M)

V

= 1mVrms

MIX2

RL = 1.5kΩ

18 22 26 dB

Demodulator Bandwidth DBW RFin = 1mVrms − 10 − kHz

Limiter Input Sensitivity V

I(LIM)

AM Rejection Ratio AMRR RFin = 1mVrms

Fc = 455kHz , −3dB Limiting − 20 40 uVrms

− 40 − dB

AM MOD = 30% @1kHz

First Mixer 3rd Order

Intercept Point

First Mixer Input Impedance R

First Mixer output Impedance Ro

8

IMD3 MIX1 Input 50Ω

Termination

C

I(1M)

I(1M)

(1M)

/

Fc = 50MHz − 690

Fc = 10.7MHz − 330 − Ω

− − 15 − dBm

− Ω

7.2

pF

ENHANCED-1 CHIP CT0 RF IC S1T8528

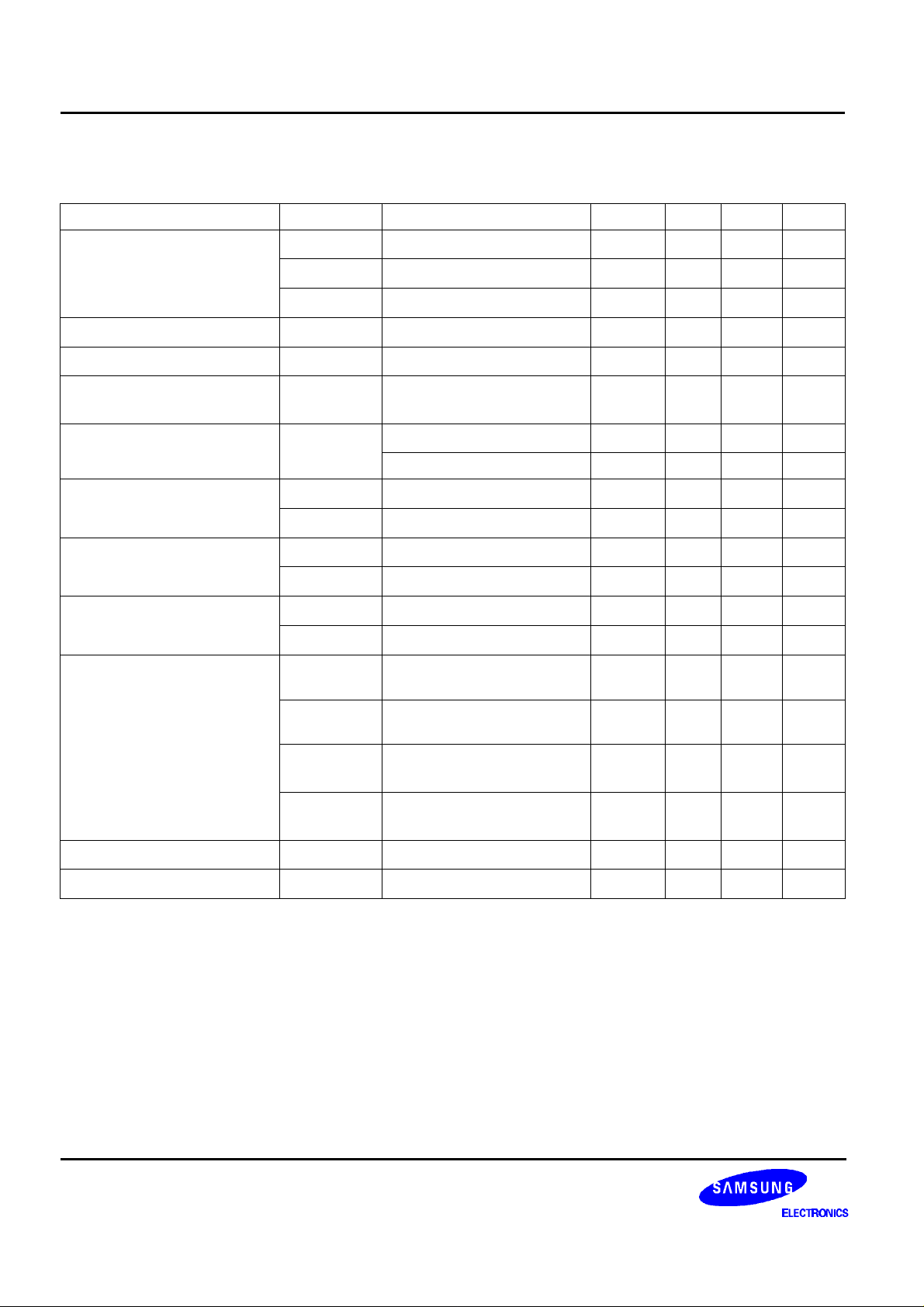

ELECTRICAL CHARACTERISTICS (Continued)

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Second Mixer input

R

I(2M)

Fc = 10.7MHz − 4 − kΩ

Impedance

Second Mixer output

Ro

(2M)

Fc = 455kHz − 1.5 − kΩ

Impedance

Carrier Detector Threshold CD

TH

MIX1 Single-Ended

Matching,

Default Threshold=1010

Low Battery Detector LBD LBD0 ~ LBD3 = 0 ( Default )

Only LBD2 = 0

Only LBD1 = 0

Only LBD3 = 0

LBD0 ~ LBD3 = 1

RSSI Slope V

RSSI

MIX1 Single-Ended

Matching

RSSI Output Voltage

Dynamic Range

Carrier Detect

Output High Voltage

Carrier Detect

Output Low Voltage

RSSI MIX1 Single-Ended

Matching

V

OH

RFin = 1µVrms

Default Threshold = 1010

V

OL

RFin = 10µVrms

Default Threshold = 1010

COMPRESSOR

( Vcc = 3.6V, fc = 1kHz, Ta = 25°C, unless otherwise specified )

− −95 − dBm

− 0.15 3.45

0.1 V

3.3

3.0

−0.1 2.2

0.075

2.1

− 30 − mV/dB

− 60 − dB

Vcc-0.4 − − V

− − 0.4 V

Standard Output Voltage Vo(com) Vinc = 63.2mVrms → 0dB

ALC disabled (pin 13)

Compressor Gain

Difference

Compressor Output

∆G

∆G

THD

V1(COM)

V2(COM)

COM

Vinc = −20dB −10 0 1.0 dB

Vinc = −40dB −1.5 0 1.5 dB

Vinc = 63.2mVrms → 0dB − 0.5 1.0 %

Distortion

Mute Attenuation Ratio ATT

Compressor Limiting Voltage V

MUTE

LIM(COM)

ALC VALC R

Splatter filter Vo(SF) V

Maximum Output Voltage V

OMIC(MAX)

Vinc = 0dB 60 80 − dB

Vinc = Variable 1.05 1.35 1.65 Vp-p

= 150kΩ, Vinc = 10dB 310 390 450 mVrms

ALC

= 63.2mVrms → 0 dB 269 316 363 mVrms

INC

RL = 10KΩ − 2.8 − Vp-p

EXPANDER

(Vcc = 3.6V, fc = 1kHz, Ta = 25°C, unless otherwise specified)

Standard Output Voltage V

O(EXP)

VinE = 63.2mVrms → 0dB 309 356 403 mVrms

269 316 363 mVrms

9

S1T8528 ENHANCED-1 CHIP CT0 RF IC

ELECTRICAL CHARACTERISTICS (Continued)

Characteristic Symbol Test Conditions Min. Typ. Max. Unit

Expander Gain Difference ∆G

∆G

∆G

Expander Output Distortion THD

Mute Attenuation Ratio ATT

Expander Maximum Output

V

OEXP(MAX)

Voltage

Maximum Output Voltage V

Input Current I

Input Voltage V

Output Current I

Output Voltage V

OSPK(MAX)

IH

I

IL

IH

V

IL

OH

I

OL

OH1

V1(EXP)

V2(EXP)

V3(EXP)

EXP

MUTE

VinE = −10dB −1.0 0 1.0 dB

VinE = − 20dB −1.5 0 1.5 dB

VinE =− 30dB −2.0 0 2.0 dB

VinE = 63.2mVrms → 0dB − 0.5 1.0 %

VinE = 63.2mVrms → 0dB 60 80 − dB

VinE = Variable

THD = 10%

800 − − mVrms

RL = 150Ω − 2.2 − Vp-p

RL = 600Ω − 3.0 - Vp-p

Vin = Vcc − − 5 µA

Vin = 0V −5 − − µA

− Vcc-0.3 − − V

− − − 0.3 V

Vout = Vcc 0.3 − − mA

Vout = 0V 0.3 − − mA

PDT,PDR: Io = -0.3mA

Vcc-0.4 − − V

( Sourcing )

PLL regulator voltage V

Regulator Load Current I

V

OL1

V

OH2

V

OL2

PLLREG

REG

PDT,PDR: Io = 0.3mA

( Sinking )

LD,f

: Io = − 0.1mA

MCU

( Sourcing )

LD,f

: Io = 0.1mA

MCU

( Sinking )

− 1.90 2.05 2.20 V

Vout = V

(OPEN)-0.05V − 3.0 − mA

REG

− − 0.4 V

Vcc-0.5 − − V

− − 0.5 V

10

ENHANCED-1 CHIP CT0 RF IC S1T8528

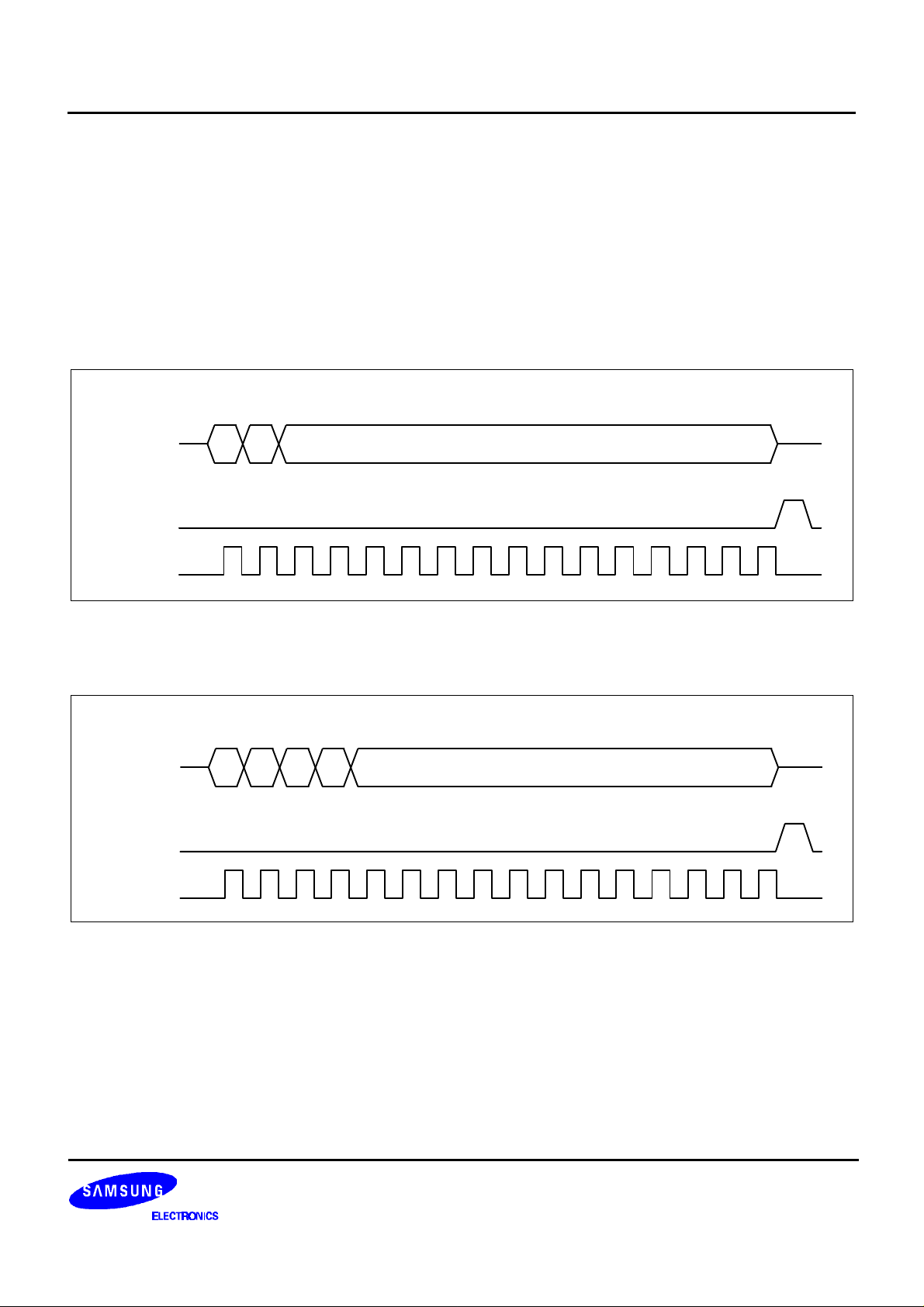

PLL PROGRAM SUMMARY

• MCU ( MICOM ) Serial Interface ( MSB : 1st INPUT )

Use CLK (Pin 7 ), DATA (Pin 8 ) , and EN (Pin 9 ) terminals for program.

DATA and CLK terminals are used for loading data to internal Shift - Register. When EN terminal is

‘Low’, It is possible to program TX-Channel Counter, RX - Channel Counter and various control

functions of PLL. When EN terminal is ‘High’, Program 1st Local Oscillator Capacitor Selection in

receiver for U.S.A - 25 CH function.

— TX - Register, RX-Register, Control Register

MSB LSB

DATA

PMC0 PMC1 14Bit DATA

EN

CLK

— Reference - Register

MSB LSB

DATA

PMC0PMC1UK_

EN

CLK

S1

UK_

S0

Figure 1.

12Bit DATA

Figure 2.

11

Loading...

Loading...