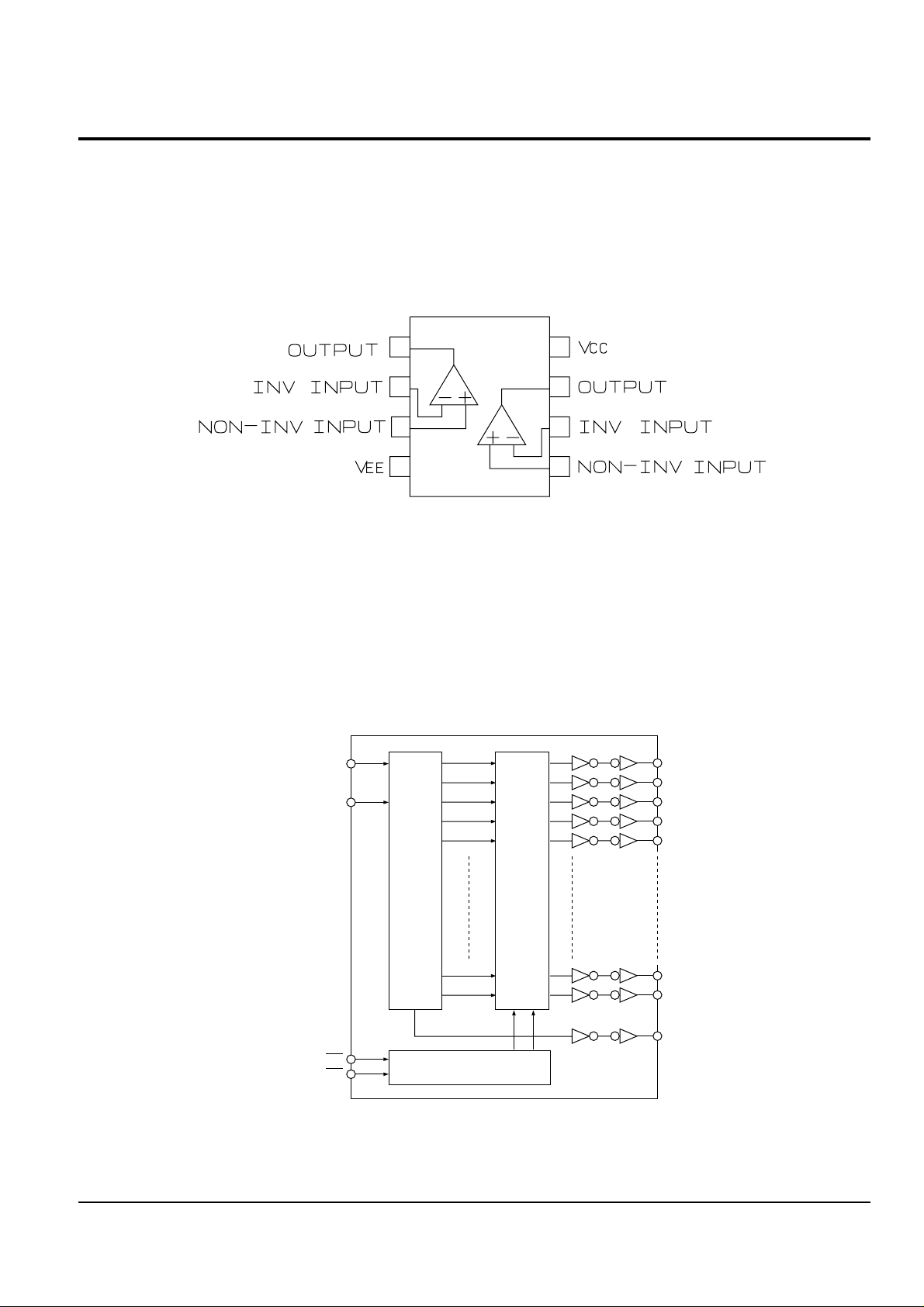

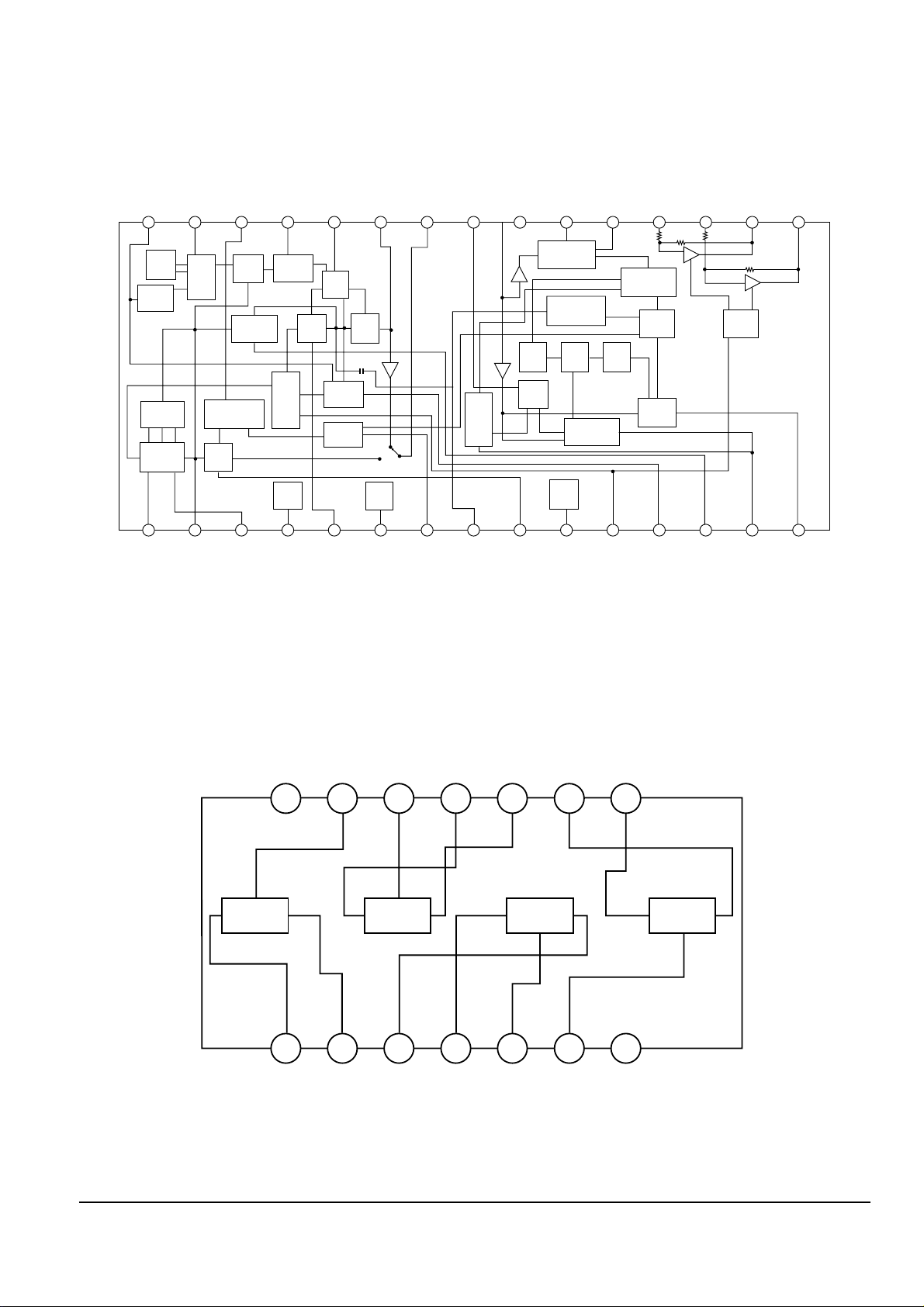

9. Block Diagrams

9-1 Main

Samsung Electronics

9-1

Samsung Electronics9-2

Block Diagrams

9-2 CD

SLED

MOTOR

SPINDLE

MOTOR

PICK - UP

TRACKING

ACTUATOR

FOCUSING

ACTUATOR

A.B.C.D.E.F

LD.PD

DISC

SP+

SP-

TRK+ TRK-

FCS-

17

18

11 12 26 27 1

2

+5V

19

10

25 3

43

46

50

48

71P/U IN

LIMIT S/W

OPEN/CLOSE MOTOR

2

10

DM- DM+

MOTOR DRIVER

OPEN/CLOSE S/W

41

69.70

65.66.

67.68

33.30

29.25

22.24.23

31

35.36.37

38

40

MOTOR CONTROL

S/W SENSOR

FOK

MAIN PCB MAIN PCB

MICOM CTRL LINE

POWER / AUDIO LINE

10

1

11

219

19

R

G

L

21

20

36.37.38

68

25.26.30

29

10.70.72

73.75.76

27

MCK. MDATA. MLT

ISTAT

SQDT. LKFS. SOS1

SQCK

A. GND

R-CH

L-CH

GND

B+

RESET

LOCK.SMEF.WDCH.SMON.SMSD

SL IN

SP IN

TE IN

EF IN

VREF

SL-

SL+

MOTOR/ACTUATOR DRIVER

6

ASSP

KB9223

NIC 9223

SCW1

SCW4

SIC1,SIC2,SIC3

DIGITAL SIGNAL PROCESSOR

16.9344MHz

66.69

8

EFM.TRCNT

LB1641/BA6209

UP/DOWM S/W

ROULETTE SENSOR

UP/DOWN

ROULETTE

MOTOR

MOTOR

SIC1,2,3

KA9258

NIC 9258

KS9286

NIC9286

NIC9223

KB9223

SUB PCB

9

9-3Samsung Electronics

Block Diagrams

DATA

CLK

STB

CLK

P1

P2

P3

P4

P5

P15

P16

SO

Controller Circuit

Shift Register

Latch Circuit

NJU3716M : JIC5

BA4560 : DIC4

9-3-1 Main

9-3 IC & TR Internal Diagrams

Samsung Electronics9-4

Block Diagrams

1

22

XIN

XOUT

16

FMIN

15

AMIN

3

CE

4

DI

5

CL

6

DO

17

VDD

21

Vss

C2B

1/F

P0WER

ON

RESET

7 8 9 10

BO1 BO2 BO3 BO4

11

IO1

13

IO2

18

PD

19

AIN

20

ADUT

12

IFIN

REFERENCE

DIVIDER

PHASE DETECTOR

CHARGE PUMP

UNLOCK

DETECTOR

UNIVERSAL

COUNTER

DATA SHIFT REGISTER

LATCH

12bita PROGRAMMABLE

DIVIDER

SWALLOW COUNTER

1/16, 1/17 4D1ts

1/2

L-N1

L-N2

L-N3

L-N4

R-N1

R-N2

R-N3

R-N4

11

12

13

14

10

9

8

7

100K

100K

100K

100K

100K

100K

100K

100K

G

G

0/30dB

2dB STEP

INPUT MULTIPLEXER

GAIN

MUXOUTL

15 16

27

26 25 23 24

TREBLE(L)

MOUT(L)

BN(L)

BOUT(L)

UN(L)

RR

MUXOUTR

TREBLE(R)

MOUT(R)

BN(R)

BOUT(R)

CREF

UN(R)

RR

17 18 20 19 20 21

22

2

4

3

5

30

1

29

6

AGND

R OUT

L OUT

DIGGND

SDA

SCL

SPKR ATT

LEFT

I CBUS DECDER + LATCHES

2

VOLUME TREBLE MIDDLE BASS

SPKR ATT

RIGHT

Verf

V3

VOLUME TREBLE MIDDLE BASS

LC72131 : TIC2

TDA7439: FIC2

9-5Samsung Electronics

Block Diagrams

DATA

CLK

STB

CLK

P1

P2

P3

P4

P5

P19

P20

SO

Controller Circuit

Shift Register

Latch Circuit

BIASC 1

VREFC 2

RREF 3

N.C. 4

N.C. 5

DIFOUT 6

CIN 7

AIN 8

VCC 9

PEAK

HOLD

PEAK

HOLD

PEAK

HOLD

PEAK

HOLD

PEAK

HOLD

PEAK

HOLD

PEAK

HOLD

RES

RES

RES

RES

RES

RES

RES

G4Hz

BPF

160Hz

BPF

400Hz

BPF

1KHz

BPF

2.5KHz

BPF

6.3KHz

BPF

15.6KHz

BPF

DIF

1 8

1 7

1 6

1 5

1 4

1 3

1 2

1 1

1 0

GND

AOUT

TEST

N.C.

N.C.

SEL

C

B

A

BIAS

VREF

REFFERENCE CURRENT

MPX

A

A-C

C

DES

BA3834S : UIC3

NJU3718 : UIC2

Samsung Electronics9-6

Block Diagrams

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

29 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ALC

DUFF

AM

OSC

AM

MIX

AM

RF AMF

AGC

AM

DET

AM

IF

SMFT

LEVEL

DET

FM

IF

FM

DET

REG GND

TUNING

DRIVE

S-CURVE

AM/FM

IF

BUFF

COMP

VCC

AM/FM

SW

VCC

PHASE DET

PILOT

DET

FF FF FF

STEREO

DRIVE

TRIG MUTE

STERO

SW

DECODER

PM

AM

SW A SW B SW C SW D

14 13 12 10 9 811

123 5674

LA1836: TIC1

LC4966: DIC2

Loading...

Loading...