V

查询KM681000BLT-5供应商

PRELIMINARY

KM681000B Family CMOS SRAM

128K x8 bit Low Power CMOS Static RAM

GENERAL DESCRIPTIONFEATURES

¡Ü

Process Technology : 0.6

¡Ü

Organization : 128Kx8

¡Ü

Power Supply Voltage : Single 5.0V

¡Ü

Low Data Retention Voltage : 2V(Min)

¡Ü

Three state output and TTL Compatible

¡Ü

Package Type : JEDEC Standard

§-

CMOS

¡¾

10%

32-DIP, 32-SOP, 32-TSOP I R/F

PRODUCT FAMILY

The KM681000B family is fabricated by SAMSUNG's advanced

CMOS process technology. The family can support various

operating temperature ranges and have various package types

for user flexibility of system design. The family also support low

data retention voltage for battery back-up operation with low

data retention current.

Product

Family

KM681000BL

KM681000BL-L

KM681000BLE

KM681000BLE-L

KM681000BLI

KM681000BLI-L

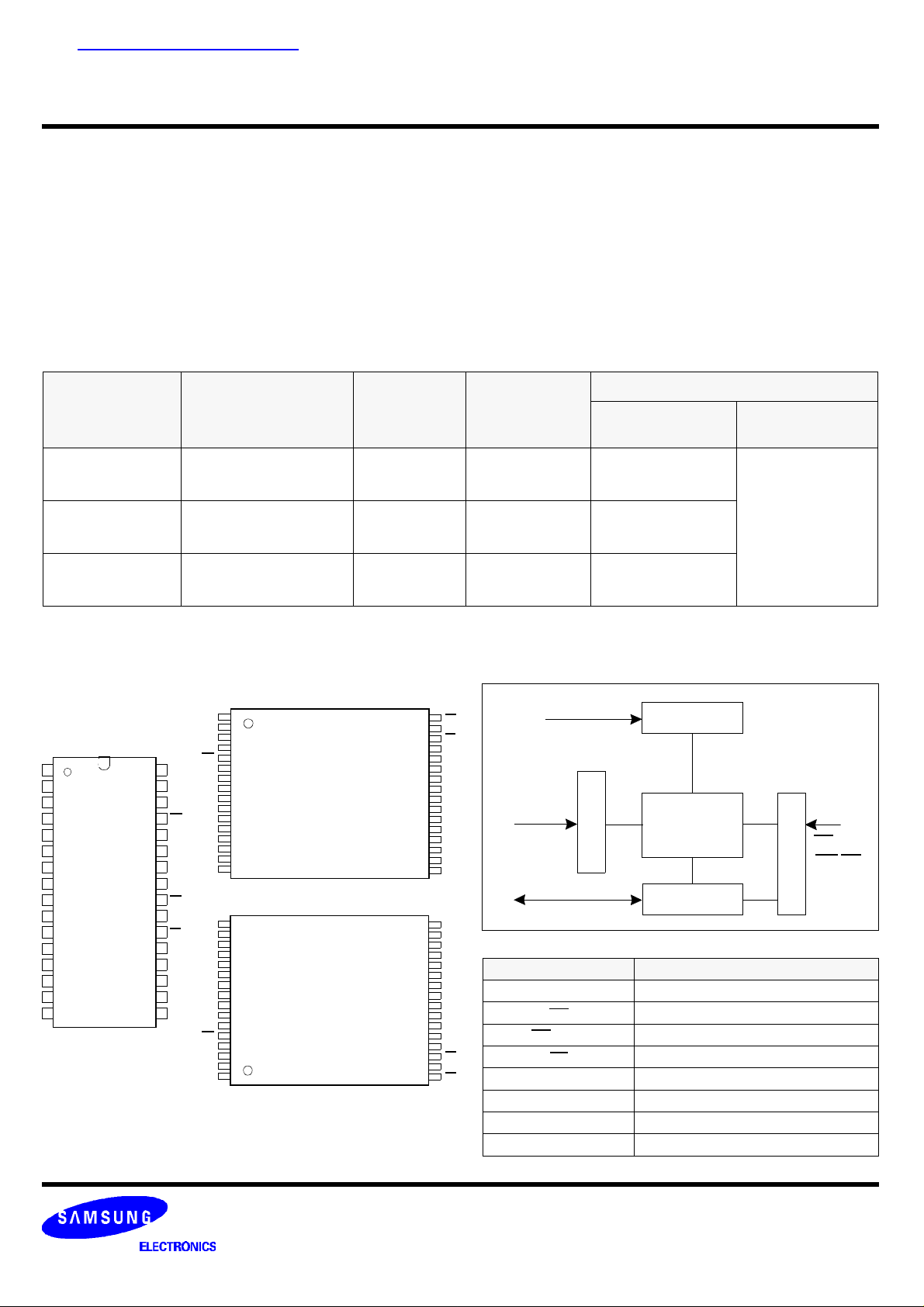

PIN DESCRIPTION

1

2

A16

3

A14

4

A12

5

A7

A6

6

A5

7

32-DIP

A4

A3

A2

A1

A0

SS

32-SOP

8

9

10

11

12

1

13

2

14

3

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Operating

Temperature

Commercial(0~7¡É) 55/70ns

Extended(-25~85¡É) 70/100ns

Industrial(-40~85¡É) 70/100ns

A11

1

A9

2

A8

3

A13

4

WE

5

CS2

CS2

6

A15

7

VCC

8

NC

9

A16

10

A14

11

A12

12

A7

13

A6

14

A5

15

A4

16

16

A4

15

A5

14

A6

13

A7

12

A12

11

A14

10

A16

9

NC

8

VCC

7

A15

6

5

WE

4

A13

3

A8

2

A9

1

A11

32-TSOP

Type I - Forward

32-TSOP

Type I-Reverse

VCC

A15

CS2

WE

A13

A8

A9

A11

OE

A10

CS1

I/O8

I/O7

I/O6

I/O5

I/O4

Speed PKG Type

32-DIP,32-SOP

32-TSOP I R/F

32-SOP

32-TSOP I R/F

32-SOP

32-TSOP I R/F

FUNCTIONAL BLOCK DIAGRAM

32

OE

31

A10

CS1

30

I/O8

29

I/O7

28

27

I/O6

26

I/O5

25

I/O4

24

VSS

23

I/O3

22

I/O2

21

I/O1

20

A0

19

A1

18

A2

17

A3

A3

17

18

A2

A1

19

20

A0

21

I/O1

22

I/O2

23

I/O3

24

VSS

25

I/O4

26

I/O5

27

I/O6

28

I/O7

29

I/O8

30

CS1

31

A10

32

OE

A0~3, A8~11

A4~7,

A12~16

Name Function

A0~A16 Address Inputs

WE Write Enable Input

CS1,CS2

OE Output Enable Input

I/O1~I/O18 Data Inputs/Outputs

Vcc Power

Vss Ground

N.C No Connection

I/O1~8

X-Decoder

Power Dissipation

Standby

(ISB1, Max)

§Ë

100

§Ë

20

§Ë

100

§Ë

50

§Ë

100

§Ë

50

Y-Decoder

Cell

Array

I/O Buffer

Chip Select Inputs

Operating

(ICC2)

70mA

Control Logic

CS1,CS2

WE,OE

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

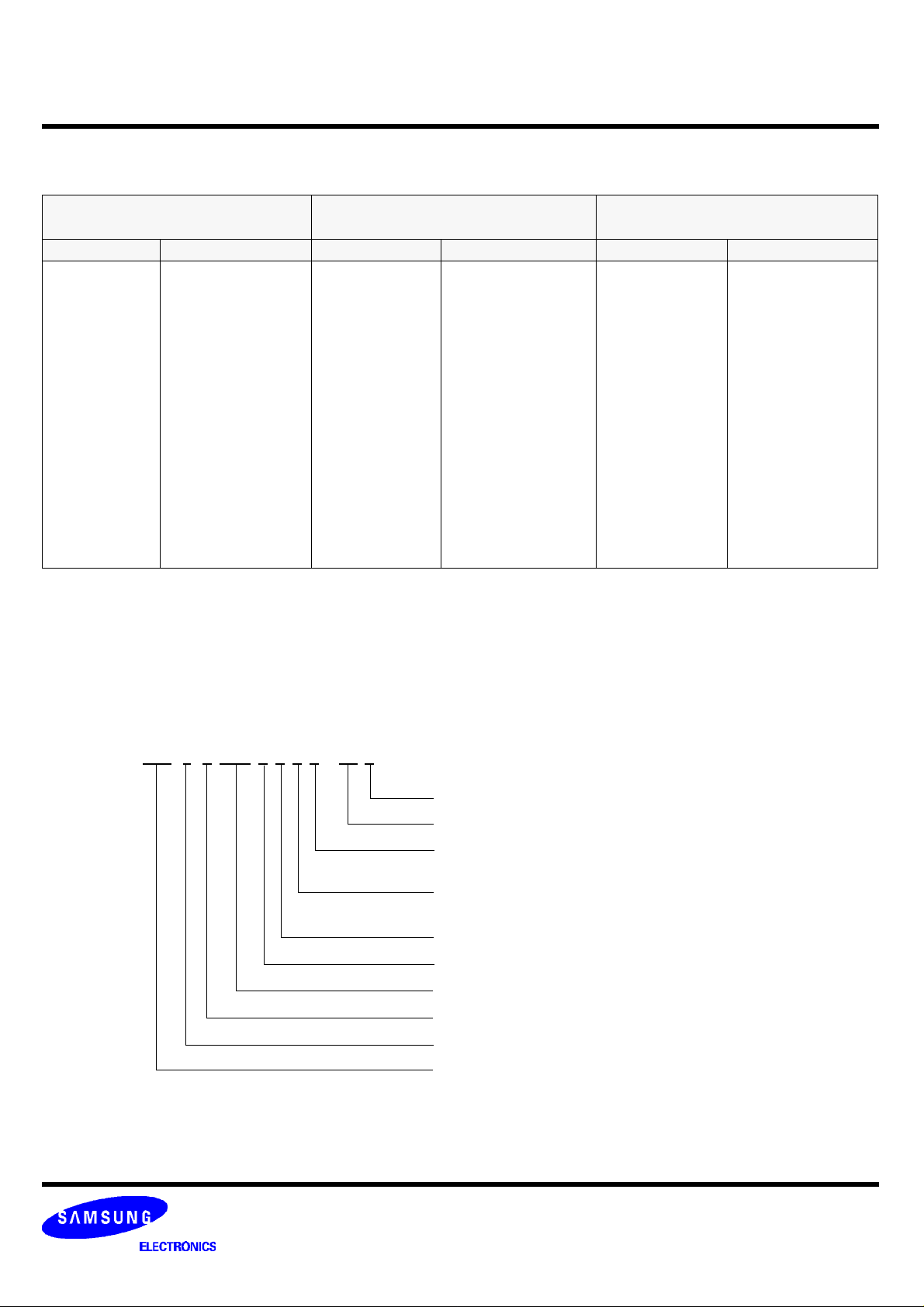

PRODUCT LIST & ORDERING INFORMATION

PRODUCT LIST

Commercial Temp Product

(0~70¡É)

Extended Temp Products

(-25~85¡É)

Industrial Temp Products

(-40~85¡É)

Part Name Function Part Name Function Part Name Function

KM681000BLP-5

KM681000BLP-5L

KM681000BLP-7

KM681000BLP-7L

KM681000BLG-5

KM681000BLG-5L

KM681000BLG-7

KM681000BLG-7L

KM681000BLT-5

KM681000BLT-5L

KM681000BLT-7

KM681000BLT-7L

KM681000BLR-5

KM681000BLR-5L

KM681000BLR-7

KM681000BLR-7L

32-DIP,55ns,L-pwr

32-DIP,55ns,LL-pwr

32-DIP,70ns,L-pwr

32-DIP,70ns,LL-pwr

32-SOP,55ns,L-pwr

32-SOP,55ns,LL-pwr

32-SOP,70ns,L-pwr

32-SOP,70ns,LL-pwr

32-TSOP F,55ns,L-pwr

32-TSOP F,55ns,LL-pwr

32-TSOP F,70ns,L-pwr

32-TSOP F,70ns,LL-pwr

32-TSOP R,55ns,L-pwr

32-TSOP R,55ns,LL-pwr

32-TSOP R,70ns,L-pwr

32-TSOP R,70ns,LL-pwr

KM681000BLGE-7

KM681000BLGE-7L

KM681000BLGE-10

KM681000BLGE-10L

KM681000BLTE-7

KM681000BLTE-7L

KM681000BLTE-10

KM681000BLTE-10L

KM681000BLRE-7

KM681000BLRE-7L

KM681000BLRE-10

KM681000BLRE-10L

32-SOP,70ns,L-pwr

32-SOP,70ns,LL-pwr

32-SOP,100ns,L-pwr

32-SOP,100ns,LL-pwr

32-TSOP F,70ns,L-pwr

32-TSOP F,70ns,LL-pwr

32-TSOP F,100ns,L-pwr

32-TSOP F,100ns,LL-pwr

32-TSOP R,70ns,L-pwr

32-TSOP R,70ns,LL-pwr

32-TSOP R,100ns,L-pwr

32-TSOP R,100ns,LL-pwr

KM681000BLGI-7

KM681000BLGI-7L

KM681000BLGI-10

KM681000BLGI-10L

KM681000BLTI-7

KM681000BLTI-7L

KM681000BLTI-10

KM681000BLTI-10L

KM681000BLRI-7

KM681000BLRI-7L

KM681000BLRI-10

KM681000BLRI-10L

32-SOP,70ns,L-pwr

32-SOP,70ns,LL-pwr

32-SOP,100ns,L-pwr

32-SOP,100ns,LL-pwr

32-TSOP F,70ns,L-pwr

32-TSOP F,70ns,LL-pwr

32-TSOP F,100ns,L-pwr

32-TSOP F,100ns,LL-pwr

32-TSOP R,70ns,L-pwr

32-TSOP R,70ns,LL-pwr

32-TSOP R,100ns,L-pwr

32-TSOP R,100ns,LL-pwr

ORDERING INFORMATION

KM6 8 X 1000 B X X X - XX X

L-Low Low Power, Blank-Low Power or High Power

Access Time : 5=55ns, 7=70ns, 10=100ns

Operating temperature : Blank=Commerial, I=Industrial, E=Extended,

Package Type : P-DIP, G=SOP, T=TSOP Forward, R=TSOP Reverse

L-Low Power or Low Low Power, Blank-High Power

Die Version : B=3 rd generation

¢¥

Density : 1000=1Mbit

Bank=5V, V=3.0~3.6V, U=2.7~3.3V

Organization : 8=x8

SEC Standard SRAM

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

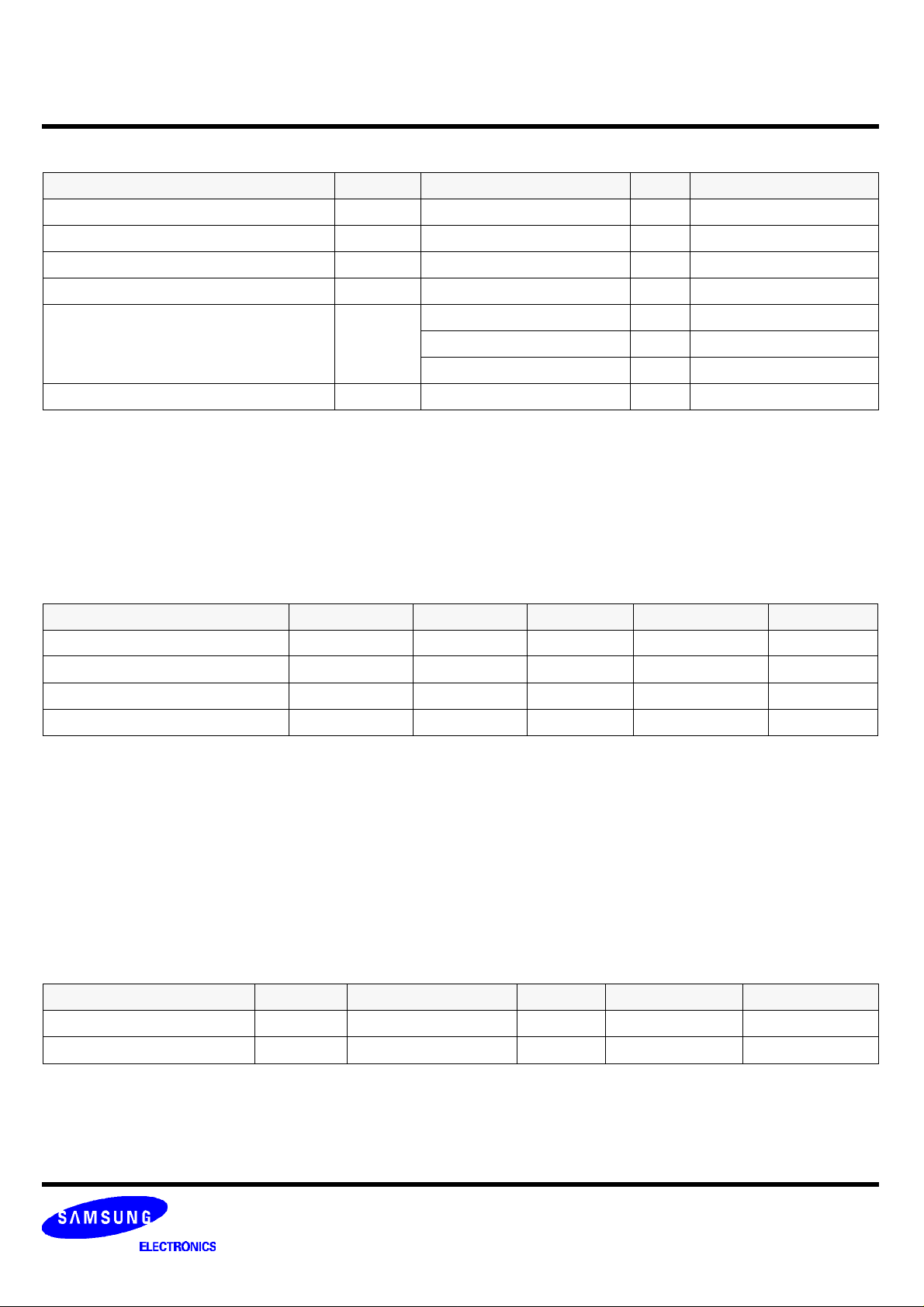

ABSOLUTE MAXIMUM RATINGS*

Item Symbol Ratings Unit Remark

Voltage on any pin relative to Vss VIN,VOUT -0.5 to 7.0 V Voltage on Vcc supply relative to Vss VCC -0.5 to 7.0 V Power Dissipation PD 1.0 W Storage temperature TSTG -65 to 150

0 to 70

Operating Temperature TA

Soldering temperature and time TSOLDER 260¡É, 10sec (Lead Only) - -

* Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the

device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

-25 to 85

-40 to 85

¡É

¡É

¡É

¡É

-

KM681000BL/L-L

KM681000BLE/LE-L

KM681000BLI/LI-L

RECOMMENDED DC OPERATING CONDITIONS*

Item Symbol Min Typ** Max Unit

Supply voltage Vcc 4.5 5.0 5.5 V

Ground Vss 0 0 0 V

Input high voltage VIH 2.2 - Vcc+0.5 V

Input low voltage VIL -0.5*** - 0.8 V

* 1) Commercial Product : TA=0 to 70¡É, unless otherwise specified

2) Extended Product : TA=-25 to 85¡É, unless otherwise specified

3) Industrial Product : TA=-40 to 85¡É, unless otherwise specified

¡É

** TA=25

*** VIL(min)=-3.0V for ¡Â 50ns pulse width

CAPACITANCE* (f=1MHz, TA=25

Item Symbol Test Condition Min Max Unit

Input capacitance CIN Vin=0V - 6 pF

¡É

)

Input/Output capacitance CIO Vio=0V - 8 pF

* Capacitance is sampled not 100% tested

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

DC AND OPERATING CHARACTERISTICS

Item Symbol Test Conditions* Mi Typ** Max Unit

Input leakage current ILI VIN=Vss to Vcc -1 - 1

Output leakage current ILO CS1=VIH or CS2=VIL or WE=VIL, VIO=Vss to Vcc -1 - 1

Operating power supply current ICC CS1=VIL, CS2=VIH, VIN=VIH or VIL, IIO=0mA - 7 15** mA

ICC1

Average operating current

ICC2

Output low voltage VOL IOL=2.1mA - - 0.4 V

Output high voltage VOH IOH=-1.0mA 2.4 - - V

Standby Current(TTL) ISB CS1=VIH, CS2=VIL - - 3 mA

KM681000BL

KM681000BL-L

Standby

Current (CMOS)

* 1) Commercial Product : TA=0 to 70¡É, Vcc=5.0V¡¾10%, unless otherwise specified

2) Extended Product : TA=-25 to 85¡É, Vcc=5.0V¡¾10%, unless otherwise specified

2) Industrial Product : TA=-40 to 85¡É, Vcc=5.0V¡¾10%, unless otherwise specified

** 20mA for Exteneded and Industrial Products

*** 15mA for Extended and Industrial Products

KM681000BLE

KM681000BLE-L

KM681000BLI

KM681000BLI-L

ISB1

Cycle time=1§Á 100% duty

CS1¡Â0.2V, CS2¡ÃVCC-0.2V

IIO=0mA CS1=VIL,CS2=VIH

Min cycle, 100% duty

CS1¡ÃVcc-0.2V

CS2¡ÃVcc-0.2V or

CS2¡Â0.2V

Other input=0~Vcc

L (Low Power)

LL (Low Low Power)--

L (Low Power)

LL (Low Low Power)--

L (Low Power)

LL (Low Low Power)--

- - 10*** mA

- - 70 mA

-

100

-

-

-

-

-

20

100

50

100

50

§Ë

§Ë

§Ë

§Ë

§Ë

§Ë

§Ë

§Ë

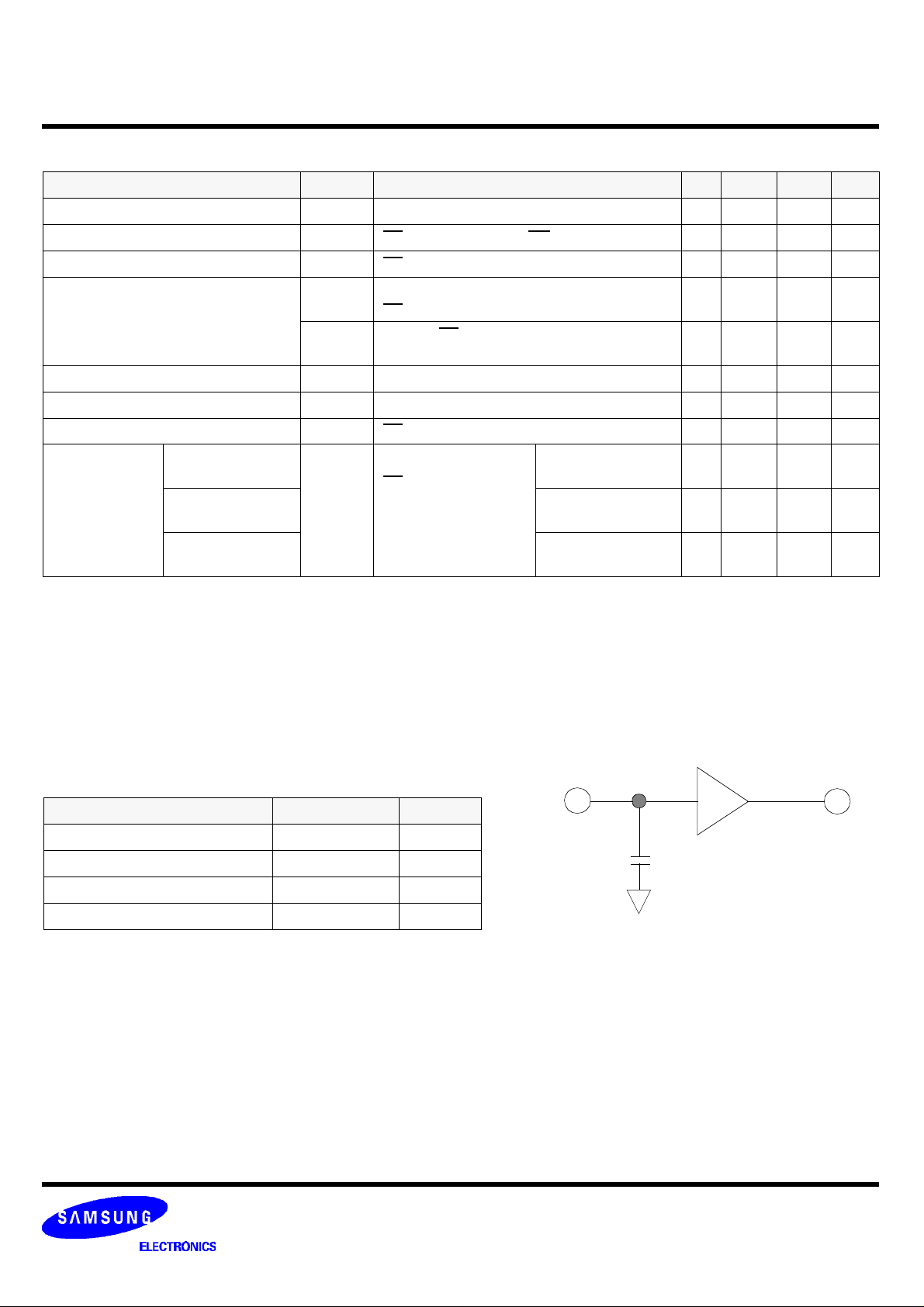

A.C CHARACTERISTICS

TEST CONDITIONS (1.Test Load and Test Input/Output Reference)*

Item Value Remark

Input pulse level 0.8 to 2.4V Input rising & falling time 5ns input and output reference voltage 1.5V Output load (See right) CL=100pF+1TTL -

* See DC Operating conditions

CL*

* Including scope and jig capacitance

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

TEST CONDITIONS (2. Temperature and Vcc Conditions)

Product Family Temperature Power Supply(Vcc) Speed Bin Comments

KM681000BL/L-L 0~70¡É 5.0V¡¾10% 55/70ns Commercial

KM681000BLE/LE-L -25~85¡É 5.0V¡¾10% 70/100ns Extended

KM681000BLI/LI-L -40~85¡É 5.0V¡¾10% 70/100ns Industrial

PARAMETER LIST FOR EACH SPEED BIN

Speed Bins

Parameter List Symbol

55ns 70ns 100ns

Min Max Min Max Min Max

Units

Read Read cycle time

Address access time

Chip select to output

Output enable to valid output

Chip select to low-Z output

Output enable to low-Z output

Chip disable to high-Z output

Output disable to high-Z output

Output hold from address change

Write Write cycle time

Chip select to end of write

Address set-up time

Address valid to end of write

Write pulse width

Write recovery time

Write to output high-Z

Data to write time overlap

Data hold from write time

End write to output low-Z

tRC

tAA

tCO1,tCO2

tOE

tLZ1,tLZ2

tOLZ

tHZ1,tHZ2

tOHZ

tOH

tWC

tCW

tAS

tAW

tWP

tWR

tWHZ

tDW

tDH

tOW

55 - 70 - 100 - ns

- 55 - 70 - 100 ns

- 55 - 70 - 100 ns

- 25 - 35 - 50 ns

10 - 10 - 10 - ns

5 - 5 - 5 - ns

0 20 0 25 0 30 ns

0 20 0 25 0 30 ns

10 - 10 - 10 - ns

55 - 70 - 100 - ns

45 - 60 - 80 - ns

0 - 0 - 0 - ns

45 - 60 - 80 - ns

40 - 50 - 60 - ns

0 - 0 - 0 - ns

0 20 0 25 0 30 ns

25 - 30 - 40 - ns

0 - 0 - 0 - ns

5 - 5 - 5 - ns

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

DATA RETENTION CHARACTERISTICS

Item Symbol Test Condition* Min Typ** Max Unit

Vcc for data retention VDR CS1***¡ÃVcc-0.2V 2.0 - 5.5 V

KM681000BL

KM681000BL-L

Data retention current IDR

Data retention set-up time

Recovery time

* 1) Commercial Product : TA=0 to 70¡É, unless otherwise specified

2) Extended Product : TA=-25 to 85¡É, unless otherwise specified

2) Industrial Product : TA=-40 to 85¡É, unless otherwise specified

¡É

** TA=25

*** CS1¡ÃVCC-0.2V,CS2¡ÃVCC-0.2V(CS1 controlled) or CS2¡Â0.2V(CS2 controlled)

KM681000BLE

KM681000BLE-L

KM681000BLI

KM681000BLI-L

tRDR

tRDR

DATA RETENTION TIMING DIAGRAM

1) CS1 Controlled

tSDR

VCC

4.5V

L-Ver

LL-Ver

Vcc=3.0V

CS1¡ÃVcc-0.2V

See data retention waveform

Data Retention Mode

L-Ver

LL-Ver

L-Ver

LL-Ver

-

-

-

-

-

-

0 - 5 - -

1

0.5

-

-

-

-

tRDR

50

10

50

25

50

25

§Ë

ms

2.2V

VDR

CS1

GND

2) CS2 controlled

VCC

4.5V

CS2

VDR

0.4V

GND

tSDR

CS1¡Ã VCC - 0.2V

Data Retention Mode

tRDR

CS2 ¡Â 0.2V

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

TIMMING DIAGRAMS

TIMING WAVEFORM OF READ CYCLE (1) (Address Controlled)

(CS1=OE=VIL, CS2= WE= VIH)

tRC

Address

tAA

tOH

Data Out

Previous Data Valid

Data Valid

TIMING WAVEFORM OF READ CYCLE (WE=VIH)

Address

CS1

CS2

OE

Data out

High-Z

tLZ

tRC

tOH

tAA

tCO1

tCO2

tHZ(1,2)

tOE

tOLZ

tOHZ

Data Valid

NOTES (READ CYCLE)

1. tHZ and tOHZ are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage le vels.

2. At any given temperature and voltage condition, tHZ(max.) is less than tLZ(min.) both for a given device and from device to device.

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

TIMING WAVEFORM OF WRITE CYCLE (1) (WE Controlled)

tWC

Address

tWR1(4)

CS1

CS2

WE

tAS(3)

Data in

Data out

Data Undefined

TIMING WAVEFORM OF WRITE CYCLE (2) (CS1 Controlled)

Address

tAS(3)

tWHZ

tCW(2)

tAW

tCW(2)

tWP(1)

tDW tDH

Data Valid

tOW

tWC

tWR1(4)

tCW(2)

CS1

tAW

CS2

tWP(1)

WE

Data in

tDW

Data Valid

tDH

Data out High-Z High-Z

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

TIMING WAVEFORM OF WRITE CYCLE (2) (CS2 Controlled)

tWC

Address

tWR2(4)

tAS(3)

CS1

tCW(2)

tAW

CS2

tCW(2)

tWP(1)

WE

tDH

High-Z

Data in

Data out High-Z

tDW

Data Valid

NOTES (WRITE CYCLE)

1. A write occurs during the overlap of low CS1, high CS2 and low WE. A write begins at the latest transition among CS1 going low, CS2 going high and WE

going low. A write ends at the earliest transition among CS1 going high, CS2 going low and WE going high, tWP is measured from the beginning or write

to the end of write.

2. tCW is measured from the later of CS1 going low or CS2 going high to the end of write.

3. tAS is measured from the address calid to the beginning of write.

4. tWR is measured from the end of write to the address change. tWR1 applied in case a write ends at CS1, or WE going high, tWR2 applied in case a write

ends at CS2 going to low.

FUNCTIONAL DESCRIPTION

CS1 CS2 WE OE Mode I/O Pin Current Mode

H X X X Power Down High-Z ISB,ISB1

X L X X Power Down High-Z ISB,ISB1

L H H H Output Disable High-Z ICC

L H H L Read Dout ICC

L H L X Write Din ICC

* X means don't care

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

PACKAGE DIMENSIONS

32 DUAL INLINE PACKAGE (600mil)

#32

13.60 ¡¾ 0.20

0.535 ¡¾ 0.008

#1

42.31

MAX

1.666

4.191 ¡¾ 0.20

1.650 ¡¾ 0.008

#17

#16

15.24

0.600

3.81 ¡¾ 0.20

0.150 ¡¾ 0.008

5.08

0.200

Units :MillimeterS(Inches)

+0.10

0.25

-0.05

+0.004

0.010

-0.002

¡É

0~15

MAX

0.46 ¡¾ 0.10

1.91

( )

0.075

0.018 ¡¾ 0.004

1.52 ¡¾ 0.10

0.060 ¡¾ 0.004

32 PLASTIC SMALL OUTLINE PACKAGE (525mil)

#32

#1

20.87

MAX

0.822

20.47 ¡¾ 0.20

0.806 ¡¾ 0.008

#17

#16

2.54

0.100

14.12 ¡¾ 0.30

0.556 ¡¾ 0.012

2.74 ¡¾ 0.20

0.108 ¡¾ 0.008

3.00

0.118

0.450 ¡¾ 0.008

MAX

0.38

MIN

0.015

11.43 ¡¾ 0.20

0.20

0.008

3.30 ¡¾ 0.30

0.130 ¡¾ 0.012

+0.10

-0.05

+0.004

-0.002

0~8

13.34

¡É

0.525

0.80 ¡¾ 0.20

0.031 ¡¾ 0.008

0.71

( )

0.028

0.41

0.016

+0.100

-0.050

+0.004

-0.002

1.27

0.050

0.05

0.002

MIN

0.10 MAX

0.004 MAX

Revision 0.3

April 1996

PRELIMINARY

KM681000B Family CMOS SRAM

PACKAGE DIMENSIONS

32 THIN SMALL OUTLINE PACKAGE TYPE I (0820F)

+0.10

0.20

-0.05

+0.004

0.008

-0.002

#1

0.50

0.0197

0~8

¡É

0.25

0.010

#16

TYP

20.00 ¡¾ 0.20

0.787 ¡¾ 0.008

18.40 ¡¾ 0.10

0.724 ¡¾ 0.004

#32

#17

Units :MillimeterS(Inches)

8.40

MAX

0.331

0.15

0.006

+0.10

-0.05

+0.004

-0.002

8.00

1.00 ¡¾ 0.10

0.039 ¡¾ 0.004

1.20

MAX

0.047

0.315

0.05

0.002

0.25

( )

0.010

MIN

0.45 ~0.75

0.018 ~0.030

32 THIN SMALL OUTLINE PACKAGE TYPE I (0820R)

0.50

0.0197

0~8

¡É

0.20

0.008

0.25

0.010

+0.10

-0.05

+0.004

-0.002

TYP

#16

#1

20.00 ¡¾ 0.20

0.787 ¡¾ 0.008

18.40 ¡¾ 0.10

0.724 ¡¾ 0.004

0.50

( )

0.020

#17

#32

0.15

0.006

MAX

8.00

8.40

0.331

1.00 ¡¾ 0.10

0.039 ¡¾ 0.004

1.20

MAX

0.047

+0.10

-0.05

+0.004

-0.002

1.10 MAX

0.004 MAX

0.25

( )

0.010

0.315

0.05

MIN

0.002

0.10 MAX

0.004 MAX

0.45 ~0.75

0.018 ~0.030

0.50

( )

0.020

Revision 0.3

April 1996

Loading...

Loading...