Samsung KM48L16031BT-G0, KM48L16031BT-FZ, KM48L16031BT-FY, KM48L16031BT-F0, KM44L32031BT-FZ Datasheet

...

- 1 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

DDR SDRAM Specification

Version 0.61

- 2 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

Revision History

Version 0 (May, 1998)

- First version for internal review

Version 0.1(June, 1998)

- Added x4 organization

Version 0.2(Sep,1998)

1. Added "Issue prcharge command for all banks of the device" as the fourth step of power-up squence.

2. In power down mode timing diagram, NOP condition is added to precharge power down exit.

Version 0.3(Dec,1998)

- Added QFC Function.

- Added DC current value

- Reduce I/O capacitance values

Version 0.4(Feb,1999)

-Added DDR SDRAM history for reference(refer to the following page)

-Added low power version DC spec

Version 0.5(Apr,1999)

-Revised following first showing for JEDEC standard

-Added DC target current based on new DC test condition

Version 0.6(July 1,1999)

1.Modified binning policy

From To

-Z (133Mhz) -Z (133Mhz/266Mbps@CL=2)

-8 (125Mhz) -Y (133Mhz/266Mbps@CL=2.5)

-0 (100Mhz) -0 (100Mhz/200Mbps@CL=2)

2.Modified the following AC spec values

*1 : Changed description method for the same functionality. This means no difference from the previous version.

3.Changed the following AC parameter symbol

From. To.

Output data access time from CK/CK tDQCK tAC

Version 0.61(August 9,1999)

- Changed the some values of "write with auto precharge" table for different bank in page 30.

From. To.

-Z -0 -Z -Y -0

tAC +/- 0.75ns +/- 1ns +/- 0.75ns +/- 0.75ns +/- 0.8ns

tDQSCK +/- 0.75ns +/- 1ns +/- 0.75ns +/- 0.75ns +/- 0.8ns

tDQSQ +/- 0.5ns +/- 0.75ns +/- 0.5ns +/- 0.5ns +/- 0.6ns

tDS/tDH 0.5 ns 0.75 ns 0.5 ns 0.5 ns 0.6 ns

tCDLR

*1

2.5tCK-tDQSS 2.5tCK-tDQSS 1tCK 1tCK 1tCK

tPRE

*1

1tCK +/- 0.75ns 1tCK +/- 1ns 0.9/1.1 tCK 0.9/1.1 tCK 0.9/1.1 tCK

tRPST

*1

tCK/2 +/- 0.75ns tCK/2 +/- 1ns 0.4/0.6 tCK 0.4/0.6 tCK 0.4/0.6 tCK

tHZQ

*1

tCK/2 +/- 0.75ns tCK/2 +/- 1ns +/- 0.75ns +/- 0.75ns +/-0.8ns

Asserted

command

For Different Bank

3 4

Old New Old New

Read Legal Illegal Legal Illegal

Read + AP

*1

Legal Illegal Legal Illegal

- 3 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

Revision History

-This revision history is for 64Mb and only for reference in other density.

Version 0.5 (JUN, 1997)

- First version for external release

- Center aligned DQ on reads and writes, 3.3V Vdd/Vddq, LVTTL for command and SSTL for DQ, DQS, CK and DM.

Version 0.6 (SEP. 1997)

- Changed to Edge alignedDQ on reads

- Add detailed discription for each functionality

Version 0.7 (JAN. 1998)

- Power supply: 3.3V +10%,-5% power supply for device operation (Vdd)

2.5V Power supply for I/O interface (Vddq)

- Interface: Add SSTL_2 for CK/DM (class I), DQ/DQS(class II) for KM416H431T.

* Put two part numbers, KM416H430T and KM416H431T.

- Clock input: Change to differential clock from single ended clock.

* Use CK, CK instead of CLK.

- Package: Change to 66pin TSOP-II, instead of 54pin TSOP-II

- tDQSS: Change to 0.75 ~ 1.25 tCK form 3ns ~ 1 tCK.

Add tSDQS(DQS-in setup time)

- In page 13, "DM can be ~" is modified to "DM must be ~".

- Tighten AC specs Change CK/CK hign/low level width from 0.4(min)/0.6(max)tCK to 0.45(min)/0.55(max)tCK.

-> Better input clock duty ratio from differential clock.

Version 0.8 (FEB. 1998)

- Correct pin rotation on pin 48 and 49 from 48-Vref, 49-Vss to 48-Vss, 49-Vref.

Version 0.9 (MAR. 1998)

- Change power-up sequence

. Add EMRS for DLL enable/disable

. Change DLL reset pin from A9 to A8 on MRS.

- Change speed range

. Add 133Mhz (266Mbps/pin), remove -12 (83Mhz)

- Change output load circuit

- Change input capacitance

- Add a comment on read interrupting write timing: Read command interrupting write can not be

issued at the next clock edge of write command.

- Modify the simplified state diagram on page 24.

Version 0.91 (May, 1998)

- Changed part number from KM416H430T/KM416H431T to KM416H4030T/KM416H4031T

- Added the 66pin package dimension on page 30.

- Changed Output Load Circuit 2 in page 29

- Removed CL=1.5

- Corrected typos

- 4 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

Contents

Revision History 2

DDR SDRAM Ordering Information 8

1. Key Features 9

1.1 Features 9

1.2 Operating Frequencies 9

1.3 Device Information by organization 9

2. Package Pinout & Dimension 10

2.1 Package Pintout 10

2.2 Input/Output Function Description 11

2.3 66 Pin TSOP(II)/MS-024FC Package Physical Dimension 12

3. Functional Description 13

3.1 Simplified State Diagram 13

3.2 Basic Functionality 14

3.2.1 Power-Up Sequence 14

3.2.2 Mode Register Definition 15

3.2.2.1 Mode Register Set(MRS) 15

3.2.2.2 Extended Mode Register Set(EMRS) 17

3.2.3 Precharge 18

3.2.4 No Operation(NOP) & Device Deselect 18

3.2.5 Row Active 19

3.2.6 Read Bank 19

3.2.7 Write Bank 19

3.3 Essential Functionality for DDR SDRAM 20

3.3.1 Burst Read Operation 20

3.3.2 Burst Write Operation 21

3.3.3 Read Interrupted by a Read 22

3.3.4 Read Interrupted by a Write & Burst Stop 22

3.3.5 Read Interrupted by a Precharge 23

3.3.6 Write Interrupted by a Write 24

- 5 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

3.3.7 Write Interrupted by a Read & DM 25

3.3.8 Write Interrupted by a Precharge & DM 26

3.3.9 Burst Stop 27

3.3.10 DM masking 28

3.3.11 Read With Auto Precharge 29

3.3.12 Write With Auto Precharge 30

3.3.13 Auto Refresh & Self Refresh 31

3.3.14 Power Down 32

4. Command Truth Table 33

5. Functional Truth Table 34

6. Absolute Maximum Rating 39

7. DC Operating Conditions & Specifications 39

7.1 DC Operating Conditions 39

7.2 DC Specifications 40

8. AC Operating Conditions & Timming Specification 41

8.1 AC Operating Conditions 41

8.2 AC Timming Parameters & Specification 42

9. AC Operating Test Conditions 44

10. Input/Output Capacitance 44

11. IBIS: I/V Characteristics for Input and Output Buffers 45

11.1 Normal strength driver 45

11.2 Half strength driver( will be included in the future) 47

12. QFC function 48

QFC definition 48

QFC timming on Read Operation 48

QFC timming on Write operation with tDQSSmax 49

QFC timming on Write operation with tDQSSmin 49

- 6 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

Table 1 : Operating frequency and DLL jitter

Table 2. : Column address configurtion

Table 3 : Input/Output function description

Table 4 : Burst address ordering for burst length

Table 5 : Bank selection for precharge by bank address bits

Table 6 : Operating description when new command asserted while

read with auto precharge is issued

Table 7 : Operating description when new command asserted while

write with auto precharge is issued

Table 8 : Command truth table

Table 9-1 : Functional truth table

Table 9-2 : Functional truth table (contiued)

Table 9-3 : Functional truth table (contiued)

Table 9-4 : Functional truth table (contiued)

Table 9-5 : Functional truth table (cotinued)

Table 10 : Absolute maximum raings

Table 11 : DC operating condtion

Table 12 : DC specification

Table 13 : AC operating condition

Table 14 : AC timing parameters and specifications

Table 15 : AC operating test conditions

Table 16 : Input/Output capacitance

Table 17 : Pull down and pull up current values

List of tables

9

10

11

16

18

29

30

33

34

35

36

37

38

39

39

40

41

42

44

44

46

- 7 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

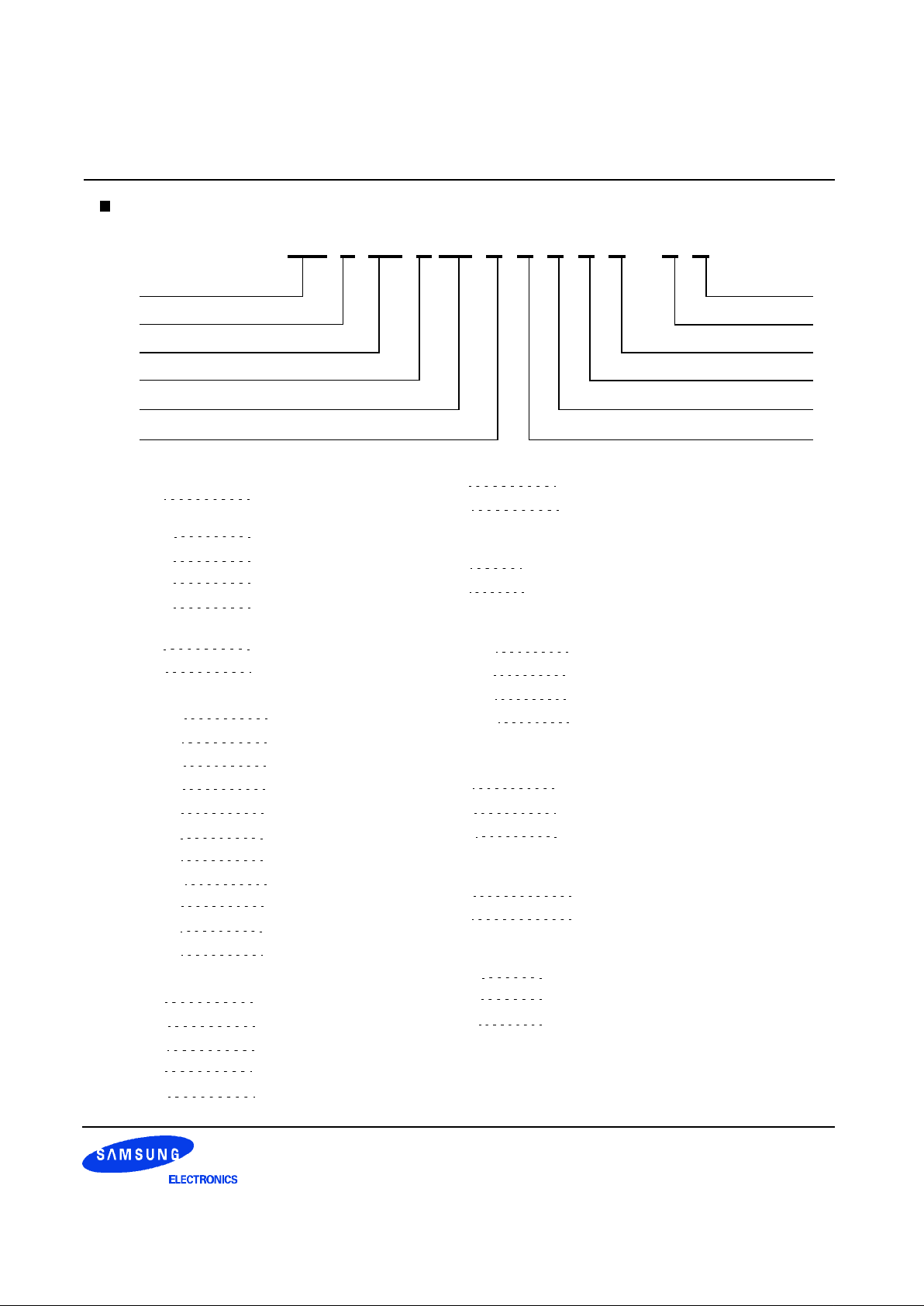

Figure 1 : 128Mb Package Pinout

Figure 2 : Package dimension

Figure 3 :State digram

Figure 4 : Power up and initialization sequence

Figure 5 : Mode register set

Figure 6 : Mode register set sequence

Figure 7 : Extend mode register set

Figure 8 : Bank activation command cycle timing

Figure 9 : Burst read operation timing

Figure 10 : Burst write operation timing

Figure 11 : Read interrupted by a read timing

Figure 12 : Read interrupted by a write and burst stop timing

Figure 13 : Read interrupted by a precharge timing

Figure 14 : Write interrupted by a write timing

Figure 15 : Write interrupted by a read and DM timing

Figure 16 : Write interrupted by a precharge and DM timing

Figure 17 : Burst stop timing

Figure 18 : DM masking timing

Figure 19 : Read with auto precharge timing

Figure 20 : Write with auto precharge timing

Figure 21 : Auto refresh timing

Figure 22 : Self refresh timing

Figure 23 : Power down entry and exit timing

Figure 24 : Output Load Circuit (SSTL_2)

Figure 25 : I / V characteristics for input/output buffers:

pull-up(above) and pull-down(below)

Figure 26 : QFC timing on read operation

Figure 27 : QFC timing on write operation with tDQSSmax

Figure 28 : QFC timing on write operation with tDQSSmin

List of figures

10

12

13

14

15

16

17

19

20

21

22

22

23

24

25

26

27

28

29

30

31

31

32

44

45

48

49

49

- 8 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

• 0 Mixed Interface(LVTTL & SSTL_3 & 3.3V VDDQ)

• 1 SSTL_2(2.5V VDDQ)

• T 66pin TSOP-II

• B BGA

• C u - BGA(CSP)

• Z 7.5ns, 133MHz@CL2 (266Mbps/pin)

• Y 7.5ns, 133MHz@CL2.5(266Mbps/pin)

• 0 10ns, 100MHz @CL2(200Mbps/pin)

• Blank 1st Gen.

• A 2nd Gen.

• B 3rd Gen.

• C 4th Gen.

• 4 4M

• 8 8M

• 16 16M

• 32 32M

• 64 64M

• 12 128M

• 25 256M

• 51 512M

• 1G 1G

• 2G 2G

• 4G 4G

• H DDR SDRAM(3.3V VDD)

• L DDR SDRAM(2.5V VDD)

• 4 x4

• 8 x8

• 16 x16

• 32 x32

• G Auto & Self Refresh

• F Auto & Self Refresh with Low Power

• 3 4 Banks

• 4 8 Banks

• 4 DRAM

DDR SDRAM ORDERING INFORMATION

KM 4 XX L XX X X X X X - X X

1. SAMSUNG Memory

2. Device

3. Organization

4. Product & Voltage(VDD)

12. Speed

11. Power

10. Package Type

9. Revision

5. Depth

8. Interface & Voltage(VDDQ)

7. Number of Bank

1. SAMSUNG Memory

2. Device

3. Organization

4. Product & Voltage(VDD)

5. Depth

7. Number of Bank

8. Interface & Voltage(VDDQ)

9. Revision

10. Package Type

11. Power

12. Speed

6. Refresh

• 0 64m/4K(15.6us)

• 1 32m/2K(15.6us)

• 2 128m/8K(15.6us)

• 3 64m/8K(7.8us)

• 4 128m/16K(7.8us)

6. Refresh

- 9 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

• Double-data-rate architecture; two data transfers per clock cycle

• Bidirectional data strobe(DQS)

• Four banks operation

• Differential clock inputs(CK and CK)

• DLL aligns DQ and DQS transition with CK transition

• MRS cycle with address key programs

-. Read latency 2, 2.5 (clock)

-. Burst length (2, 4, 8)

-. Burst type (sequential & interleave)

• All inputs except data & DM are sampled at the positive going edge of the system clock(CK)

• Data I/O transactions on both edges of data strobe

• Edge aligned data output, center aligned data input

• LDM,UDM/DM for write masking only

• Auto & Self refresh

• 15.6us refresh interval

• Maximum burst refresh cycle : 8

• 66pin TSOP II package

1. Key Features

1.1 Features

1.2 Operating Frequencies

PC266A(-Z) PC266B(-Y) PC200(-0)

Speed 133MHz@CL2 133MHz@CL2.5 100MHz@CL2

DLL jitter ±0.75ns ±0.75ns ±0.8ns

*CL : Cas Latency

Maximum Operation

Frequency

Table 1. Operating frequency and DLL jitter

1.3 Device information by Organization

Density Part No. Operating Freq. Interface Package

128Mb

KM44L32031BT-G(F)Z/Y/0

133/133/100MHz SSTL_2

66pin

TSOP II

KM48L16031BT-G(F)Z/Y/0

KM416L8031BT-G(F)Z/Y/0

- 10 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

VDD

1

66 PIN TSOP(II)

(400mil x 875mil)

DQ0

2

VDDQ

3

NC

4

DQ1

5

VSSQ

6

NC

7

DQ2

8

VDDQ

9

NC

10

DQ3 11

VSSQ 12

BA0

20

CS

19

RAS

18

CAS

17

WE

16

NC

15

VDDQ

14

NC 13

VDD

27

A3

26

A2

25

A1

24

A0

23

AP/A10

22

BA1

21

VSS

54

DQ7

53

VSSQ

52

NC

51

DQ6

50

VDDQ

49

NC

48

DQ5

47

VSSQ

46

NC

45

DQ4

44

VDDQ

43

A11

35

36

CKE

37

CK

38

DM

39

VREF

40

VSSQ

41

NC

42

VSS

55

A4

56

A5

57

A6

58

A7

59

A8

60

A9

34

(0.65 mm PIN PITCH)

33

32

31

30

29

28

61

62

63

64

65

66

NC

NC

NC

QFC/NC

NC

VDD

NC

DQS

NC

VSS

CK

NC

NC

32Mb x 4

16Mb x 8

VSS

NC

VSSQ

NC

DQ3

VDDQ

NC

NC

VSSQ

NC

DQ2

VDDQ

A11

CKE

CK

DM

VREF

VSSQ

NC

VSS

A4

A5

A6

A7

A8

A9

NC

DQS

NC

VSS

CK

NC

NC

VDD

NC

VDDQ

NC

DQ0

VSSQ

NC

NC

VDDQ

NC

DQ1

VSSQ

BA0

CS

RAS

CAS

WE

NC

VDDQ

NC

VDD

A3

A2

A1

A0

AP/A10

BA1

NC

NC

NC

QFC/NC

NC

VDD

Bank Address

BA0-BA1

Row Address

A0-A11

Auto Precharge

A10

MS-024FC

Organization Column Address

32Mx4 A0-A9, A11

16Mx8 A0-A9

8Mx16 A0-A8

DM is internally loaded to match DQ and DQS identically.

2.1 Package Pinout

FIgure 1. 128Mb package Pinout

Table 2. Column address configuration

1. Package Pinout & Dimension

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

BA0

CS

RAS

CAS

WE

LDM

VDDQ

DQ7

VDD

A3

A2

A1

A0

AP/A10

BA1

NC

LDQS

NC

QFC/NC

NC

VDD

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

A11

CKE

CK

UDM

VREF

VSSQ

DQ8

VSS

A4

A5

A6

A7

A8

A9

NC

UDQS

NC

VSS

CK

NC

NC

8Mb x 16

- 11 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

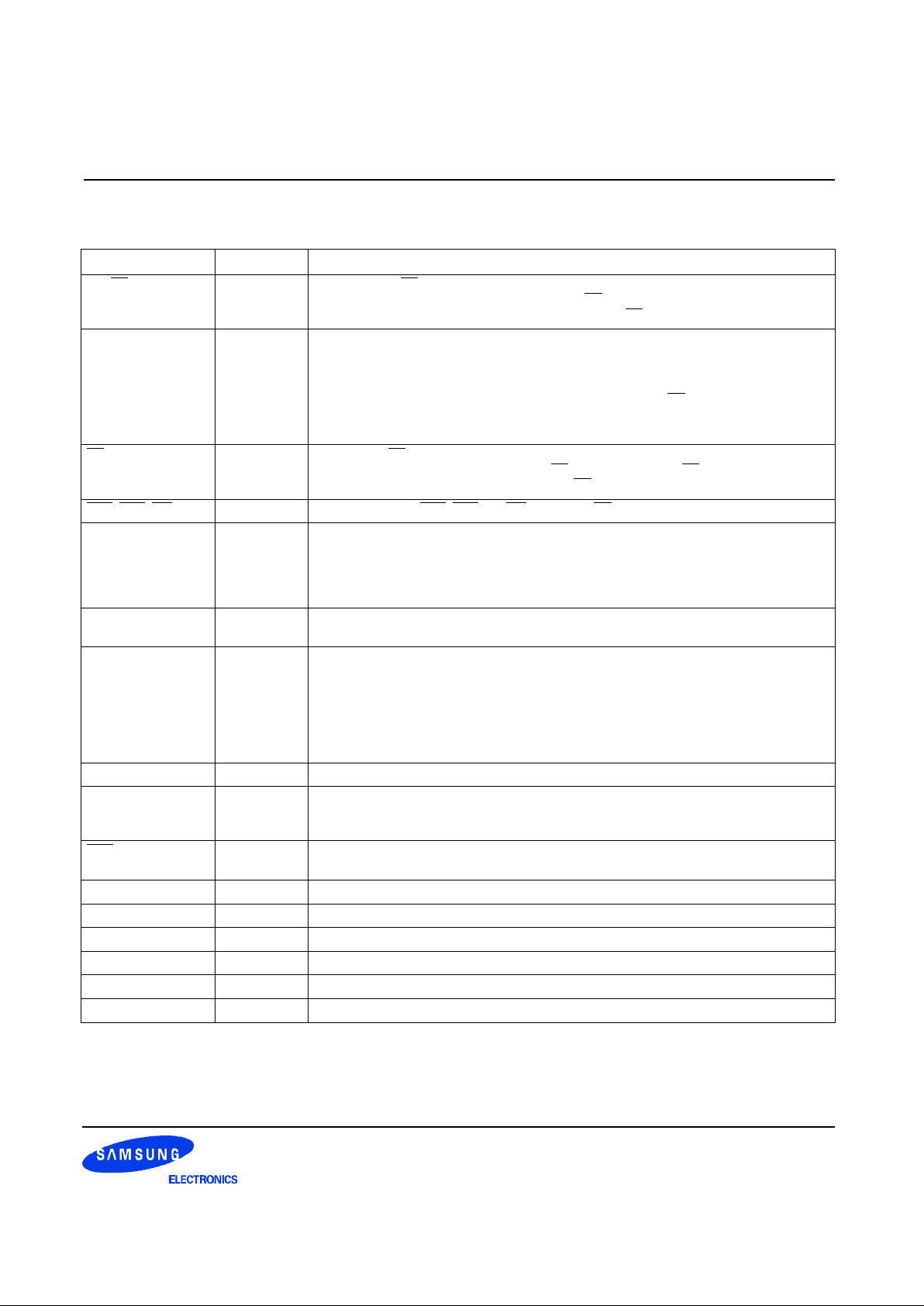

2.2 Input/Output Function Description

SYMBOL TYPE DESCRIPTION

CK, CK Input Clock : CK and CK are differential clock inputs. All address and control input signals are sam-

pled on the positive edge of CK/negative edge of CK. Output (read) data is referenced to both

edges of CK. Internal clock signals are derived from CK/CK.

CKE Input Clock Enable : CKE HIGH activates, and CKE LOW deactivates internal clock signals, and

device input buffers and output drivers. Deactivating the clock provides PRECHARGE

POWER-DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER-DOWN

(row ACTIVE in any bank). CKE is synchronous for all functions except for disabling outputs,

which is achieved asynchronously. Input buffers, excluding CK, CK and CKE are disabled

during power-down and self refresh modes, providing low standby power. CKE will recognize

an LVCMOS LOW level prior to VREF being stable on power-up.

CS Input Chip Select : CS enables(registered LOW) and disables(registered HIGH) the command

decoder. All commands are masked when CS is registered HIGH. CS provides for external

bank selection on systems with multiple banks CS is considered part of the command code.

RAS, CAS, WE Input Command Inputs : RAS, CAS and WE (along with CS) define the command being entered.

LDM,(U)DM Input Input Data Mask : DM is an input mask signal for write data. Input data is masked when DM is

sampled HIGH along with that input data during a WRITE access. DM is sampled on both

edges of DQS. DM pins include dummy loading internally, to matches the DQ and DQS load-

ing. For the x16, LDM corresponds to the data on DQ0-DQ7 ; UDM correspons to the data on

DQ8-DQ15.

BA0, BA1 Input Bank Addres Inputs : BA0 and BA1 define to which bank ACTIVE, READ, WRITE or PRE-

CHARGE command is being applied.

A [n : 0] Input Address Inputs : Provide the row address for ACTIVE commands, the column address and

AUTO PRECHARGE bit for READ/WRITE commands, to select one location out of the mem-

ory array in the respective bank. A10 is sampled during a PRECHARGE command to deter-

mine whether the PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH). If

only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also

provide the op-code during a MODE REGISTER SET command. BA0 and BA1 define which

mode register is loaded during the MODE REGISTER SET command (MRS or EMRS).

DQ I/O Data Input/Output : Data bus

LDQS,(U)DQS I/O Data Strobe : Output with read data, input with write data. Edge-aligned with read data, cen-

tered in write data. Used to capture write data. For the x16, LDQS corresponds to the data on

DQ0-DQ7 ; UDQS corresponds to the data on DQ8-DQ15.

QFC Output FET Control : Optional. Output during every Read and Write access. Can be used to control

isolation switches on modules.

NC - No Connect : No internal electrical connection is present.

VDDQ Supply DQ Power Supply : +2.5V ± 0.2V.

VSSQ Supply DQ Ground.

VDD Supply Power Supply : One of +3.3V ± 0.3V or +2.5V ± 0.2V (device specific).

VSS Supply Ground.

VREF Input SSTL_2 reference voltage.

Table 3. Input/Output Function Description

- 12 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

2.3 66 Pin TSOP(II)/MS-024FC Package Physical Dimension

Units : Millimeters

0.30±0.08

0.65TYP(0.71)

22.22±0.10

0.125

(0.80)

10.16±0.10

0×~8×

#1 #33

#66 #34

(1.50)

(1.50)

0.65±0.08

1.00±0.10

1.20MAX

(0.50) (0.50)(10.76)

11.76±0.20

(10×)(10×)

+0.075

-0.035

(0.80)

0.10 MAX

0.075 MAX

[ ]

0.05 MIN

(10×)

(10×)

(

R

0

.

1

5

)

0.210±0.05

0.665±0.05

(R

0.

1

5)

(

4

×

)

(

R

0

.

2

5

)

(

R0

.2

5)

0.45~0.75

0.25TYP

NOTE

1. ( ) IS REFERENCE

2. [ ] IS ASS’Y OUT QUALITY

Figure 2. Package dimension

- 13 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

3. Functional Description

3.1 Simplified State Diagram

READ

SELF

REFRESH

AUTO

REFRESH

POWER

DOWN

ROW

ACTIVE

READAWRITEA

WRITEA

PRE

CHARGE

POWER

ON

IDLE

MODE

POWER

DOWN

REGISTER

SET

REFS

REFSX

REFA

MRS

CKEL

CKEH

ACT

CKEL

CKEH

WRITE

WRITE

WRITEA

PRE

PRE

POWER

APPLIED

READA

PRE

PRE

READA

WRITEA READA

READ

READ

Automatic Sequence

Command Sequence

BURST STOP

WRITEA : Write with autoprecharge

READA : Read with autoprecharge

Figure 3. State diagram

- 14 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

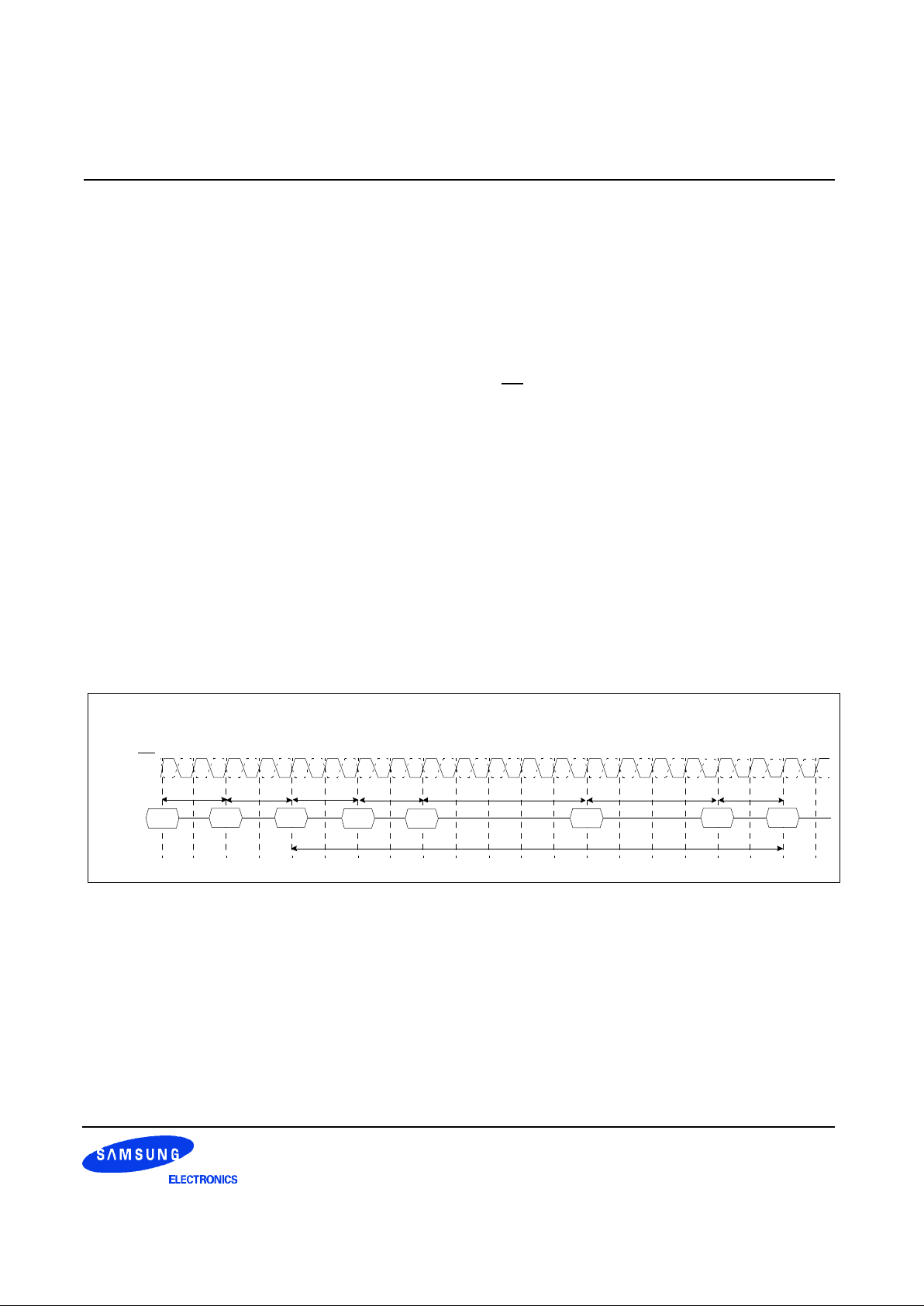

3.2.1 Power-Up and Initialization Sequence

The following sequence is required for POWER UP and Initialization.

1. Apply power and attempt to maintain CKE at a low state(all other inputs may be undefined.)

- Apply VDD before or at the same time as VDDQ.

- Apply VDDQ before or at the same time as VTT & Vref.

2. Start clock and maintain stable condition for a minimum of 200us.

3. The minimum of 200us after stable power and clock(CK, CK), apply NOP & take CKE high.

4. Issue precharge commands for all banks of the device.

5. Issue EMRS to enable DLL.(To issue "DLL Enable" command, provide "Low" to A0, "High" to BA0 and "Low"

to all of the rest address pins, A1~A11 and BA1)

6. Issue a mode register set command for "DLL reset". The additional 200 cycles of clock input is required to

lock the DLL.

(To issue DLL reset command, provide "High" to A8 and "Low" to BA0)

7. Issue precharge commands for all banks of the device.

8. Issue 2 or more auto-refresh commands.

9. Issue a mode register set command with low to A8 to initialize device operation.

*1 Every "DLL enable" command resets DLL. Therefore sequence 6 can be skipped during power up.

Instead of it, the additional 200 cycles of clock input is required to lock the DLL after enabling DLL.

*2 Sequence of 6 & 7 is regardless of the order.

Power up & Initialization Sequence

Command

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

tRP

2 Clock min.

precharge

ALL Banks

2nd Auto

Refresh

Mode

Register Set

Any

Command

tRFC

1st Auto

Refresh

tRFC

min.200 Cycle

EMRS

MRS

2 Clock min.

DLL Reset

*1

*2

*1

2 Clock min.

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

precharge

ALL Banks

tRP

CK

CK

3.2 Basic Functionality

Figure 4. Power up and initialization sequence

- 15 of 63 -

REV. 0.61 August 9. '99

128Mb DDR SDRAM Target

3.2.2 Mode Register Definition

3.2.2.1 Mode Register Set(MRS)

The mode register stores the data for controlling the various operating modes of DDR SDRAM. It programs

CAS latency, addressing mode, burst length, test mode, DLL reset and various vendor specific options to make

DDR SDRAM useful for variety of different applications. The default value of the mode register is not defined,

therefore the mode register must be written after EMRS setting for proper DDR SDRAM operation. The mode

register is written by asserting low on CS, RAS, CAS, WE and BA0(The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the mode register). The states of address pins A0 ~ A11 in

the same cycle as CS, RAS, CAS, WE and BA0 going low are written in the mode register. Two clock cycles

are requested to complete the write operation in the mode register. The mode register contents can be

changed using the same command and clock cycle requirements during operation as long as all banks are in

the idle state. The mode register is divided into various fields depending on functionality. The burst length uses

A0 ~ A2, addressing mode uses A3, CAS latency(read latency from column address) uses A4 ~ A6. A7 is used

for test mode. A8 is used for DLL reset. A7 must be set to low for normal MRS operation. Refer to the table for

specific codes for various burst lengths, addressing modes and CAS latencies.

Address Bus

CAS Latency

A6 A5 A4 Latency

0 0 0 Reserved

0 0 1 Reserved

0 1 0 2

0 1 1 Reserved

1 0 0 Reserved

1 0 1 Reserved

1 1 0 2.5

1 1 1 Reserved

Burst Length

A2 A1 A0

Latency

Sequential Interleave

0 0 0 Reserve Reserve

0 0 1 2 2

0 1 0 4 4

0 1 1 8 8

1 0 0 Reserve Reserve

1 0 1 Reserve Reserve

1 1 0 Reserve Reserve

1 1 1 Reserve Reserve

A7 mode

0 Normal

1 Test

A3 Burst Type

0 Sequential

1 Interleave

* RFU(Reserved for future use)

should stay "0" during MRS

cycle.

A8 DLL Reset

0 No

1 Yes

Mode Register

BA1 BA0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

RFU TM CAS Latency BT Burst LengthRFU DLL 0

BA0 An ~ A0

0 (Existing)MRS Cycle

1 Extended Funtions(EMRS)

Figure 5. Mode Register Set