Samsung DVD-709, DVD-909, Dvd-707 Reference Information

Samsung Electronics 2-1

2. Reference Information

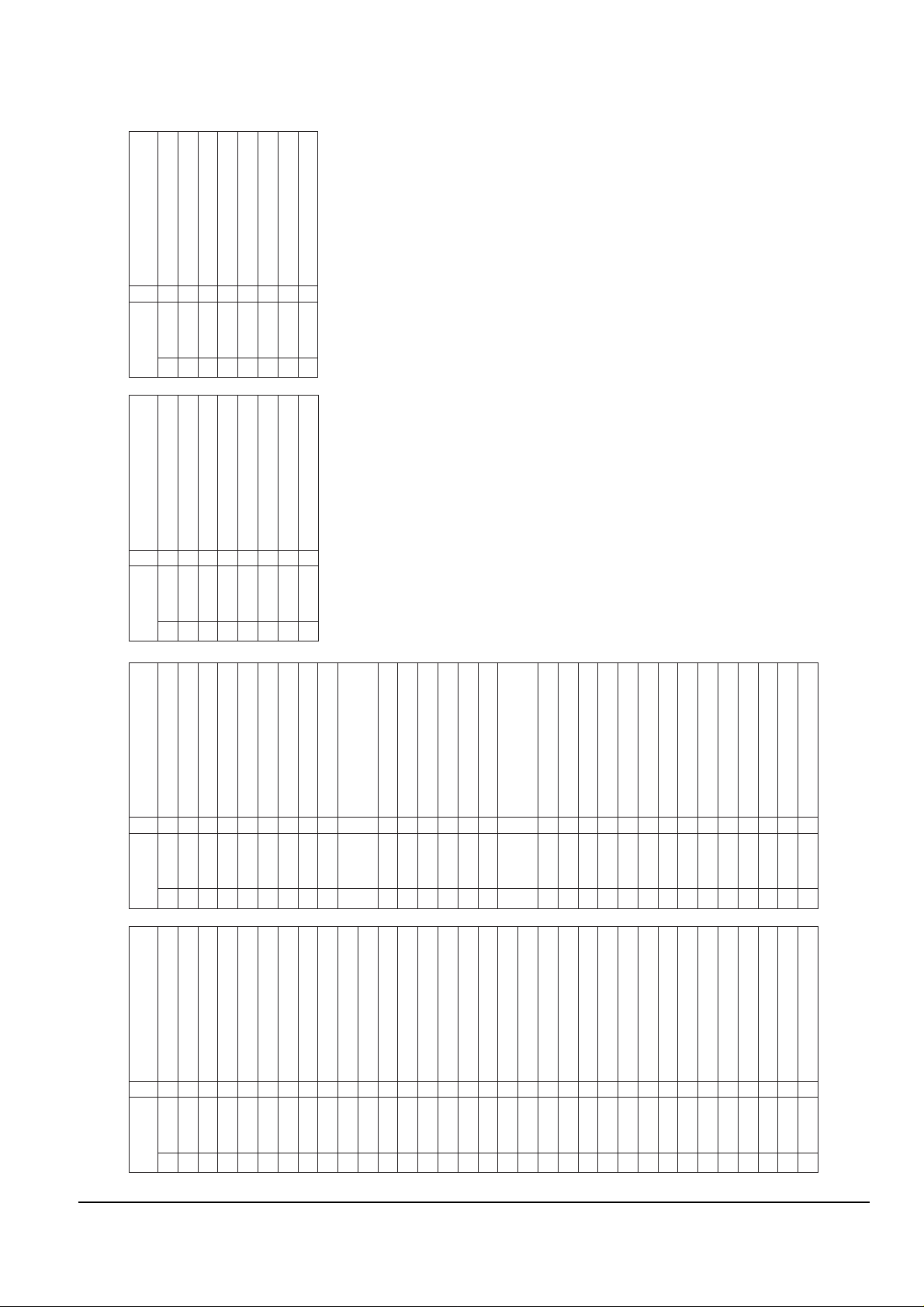

2-1 IC Dsecriptions

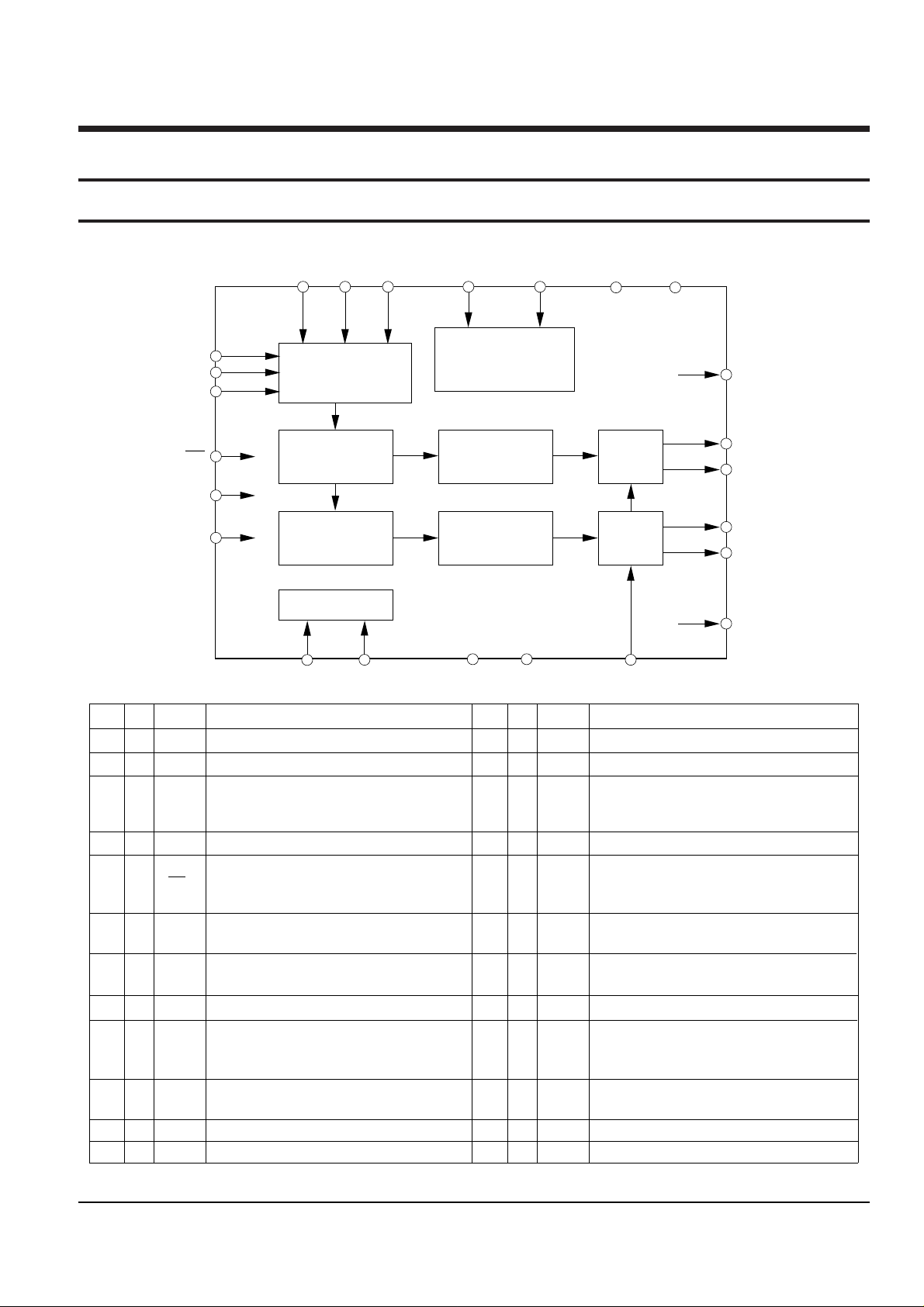

2-1-1 AIC1 (AK4324 ; Digital-to-Analog Converter)

Serial Input

Interface

De-emphasis

Control

8X

Interpolator

8X

Interpolator

∆ ∑

Modulator

SCF

SCF

∆ ∑

Modulator

Clock Divider

DIF0 DIF1 DIF2 DEM0 DEM1 AVDD AVSS

VREFDVSSDVDDCKSMCLK

LRCK

BICK

SDATA

SMUTE

DFS

DZFL

AOUTL+

AOUTL-

AOUTR+

AOUTR-

DZFR

PD

NAME

DVSS

DVDD

CKS

MCLK

BICK

SDATA

PD

I/O

I

I

I

I

I

PIN

1

2

3

4

5

6

I

7

LRCK

I

8

FUNCTION

NAME

I/O

PIN

FUNCTION

Digital ground pin

Digital power supply

Master clock select pin (Internal pull-down pin)

Nomal speed "L":MCLK = 256fs, "H":MCLK = 384fs

Double speed "L":MCLK = 128fs, "H":MCLK = 192fs

Master clock input pin

Power-Down mode pin. When at "L", the AK4324 is in

power-down and is held in rest.

The AK4324 should always be reset upon power-pin

I SMUTE

9

I DFS

10

I DEM0

11

Soft mute pin

When this pin goes "H", soft mute cycle is initiated

When returning "L", the output mute releases.

Audio serial data input pin

64fs clock is recommended to be input on this pin

Audio serial data input pin

2's complement MSB-first data is input on this pin.

Double speed sampling mode pin (Internal pull-down pin)

"L":normal speed, "H":double speed

L/R clock pin.

De-emphasis frequency select pin

I DEM1

12

De-emphasis frequency select pin

Note : Allinput pins except internal pull-down pins should not be left floating.

-

DZFL

O

Lch positive analog output pin

Analog ground pin

Voltage reference input pin

Analog power supply pin.

Rch zero input detect pin

Lch zero input detect pin

I DIF0

13

Digital input format pin

I DIF1

14

Digital input format pin

I DIF2

15

Digital input format pin

0 AOUTR-

16

Rch negative analog output pin

O AOUTR+

17

Rch positive analog output pin

O AOUTL-

AOUTL+

18

O

19

AVSS

-

20

VREF

O

21

AVDD

O

22

DZFR

O

23

24

Lch negative analog output pin

Reference Information

2-2 Samsung Electronics

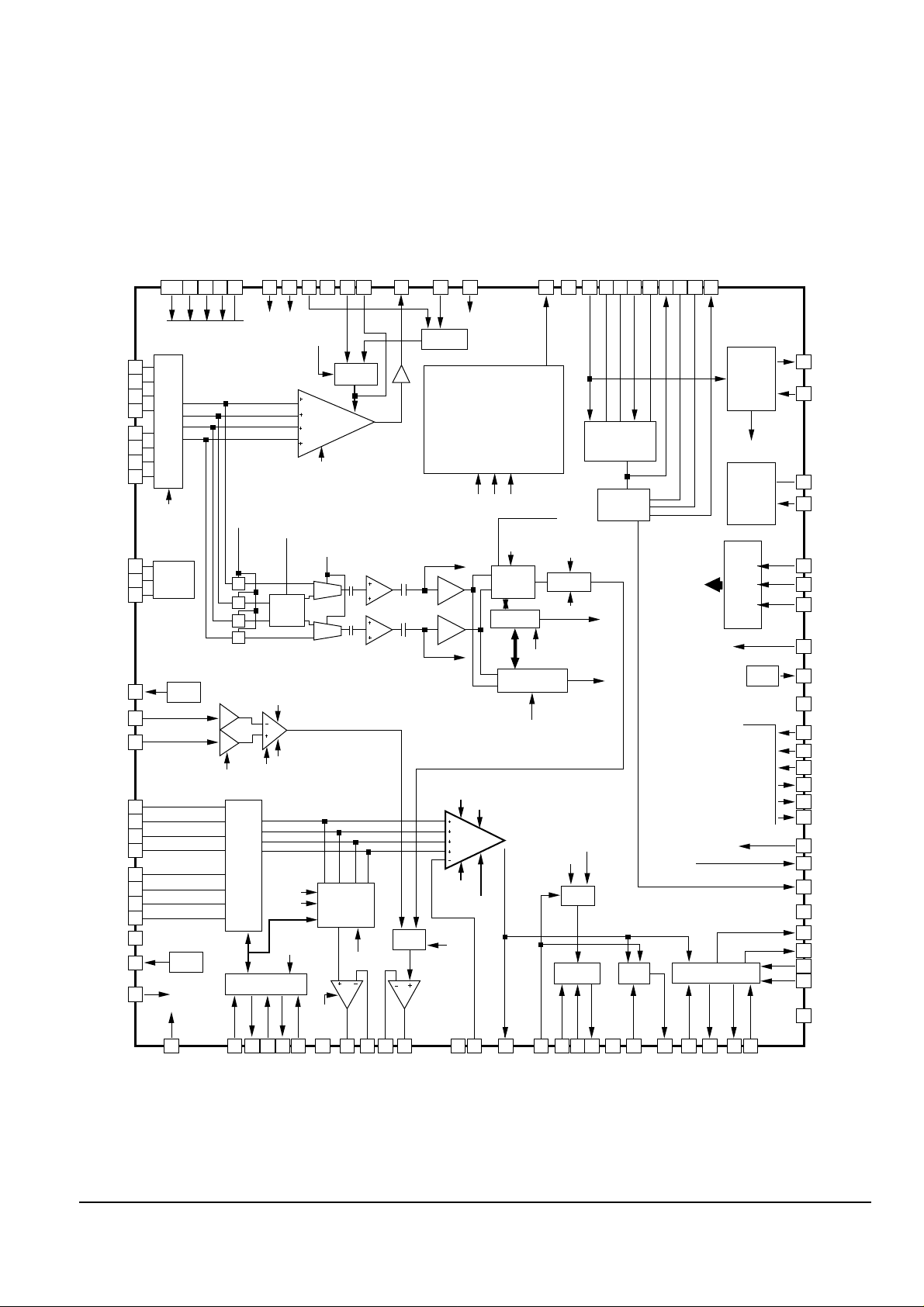

2-1-2 RIC1 (KS1461 ; RF)

100 99 98 97 96 95 94 93 92 91 90

VZOCTL

PLLGF

EQF

EQG

RDPF

AGCP

AGCB

AGCLEVEL

EQGND

AGCI

AGCC

89

RFAGCO

88

EQIN

87

BCATH

86

RFEQO

85

EQVCC

84

MIRRI

83

CP 1

81

MROFST

80

RFRPN

82

CB 1

78

CP 2

77

CB 2

76

RFCT

79

RFRP

75 BCAO

74 BCAI

73 RESET

72 OSC

71 STB

70 CLOCK

69 DATA

68 RREFDLY

67 VREFDPD

66 DPDGND

65 TE1RES

64 PLLCTL

63 DPDMUTE

62 FAUL TOUT

61 DPDEQ2

60 DPDEQ1

59 TE30FST

58 BCA

56 DPDVCC

55 DFCT2

54 DFCT1

53 DFCTTH1

52 DFCTTH2

51 DVCC

50

CC2

49

CC1

48

DFCT_CP2

47

DFCT_CP1

46

FOKB

45

FOKTH

44

DGND

43

ENV42ENVB

41

ENVP

40

ABCDI

39

ABCD

38

ABCDN

37

PDLIMITRES

36TE35

TEN

34

FEN

33

FE

32

AGND

31

PDCD

30

LDOCD

29

PDVD

28

LDODVD

27

VREFLP_BGI

26

OFSTHOLD

25

FOFST

24

VREFA

23

AVCC

22

DCD1

21

CCD1

20

BCD1

19

ACD1

18

DDVD1

17

CDVD1

16

BDVD1

15

ADVD1

14

F

13

E

12

VREFEQ

11

RREF

10

RREFEQ

9

RREFBF

8

DDVD

7

CDVD

6

BDVD

5

ADVD

4

DCD

3

CCD

2

BCD

1

ACD

to RF EQ

TUNING BLOCK

AGC-HOLD(OOH)

MUX

AGC_DET

RF

MUX

VREF

GENERATOR

CDRSEL(00H)

EQ

VC AMP

D

D

D

D

MUX3

GAIN_TE3(02H)

GCA

OFSTHOLD

TEOFST(04H)

TBAL(01H)

TE38

SUB

RF

MUX

D1

B1

C1

A1

FE

GAIN_FE(03H)

FE_0FST(05H)

CDRSEL(00H)

ANALOG

VC AMP

ALPC

LDONB(00H)

FOFST

OFSTHOLD

MUX

TESEL(OOH)

OFSTHOLD

ABCD_OFST(O6H)

ENVELOPE FOK DEFECT

MUX

ENV_SEL(02H)

EQIN

CDRSEL(OOH)

ABCD

SUM

GAIN_ABCD(OOH)

DELAY_SEL(00H)

PLLCTL

FAULTOUT

PDLIMITRES

TEOPST(04H)

PD,LPFDELAY

TE1_LIMIT

DELAY_SEL(OOH)

PLLCTL

TBAL(O1H)

HOLD_CTL(O8H)

DPDMUTE

DPD_MUTE(O2H)

SEOFHOLD

FLT_CTL(OOH)

CAL_ENDB(O2H)

COM

COM

DPDEQ2

DPDEQ1

GCA

GCA

EQ

EQ

CD1

S12

DVD1

DVD2

LDONB

FLT_CTL

CDRSEL

TESEL

AGC-HOLD

TBAL

GAIN_TE3

ENV_SEL

DVCTL_SEL

DPD_MUTE

GAIN_EQ

GAIN_FE

GAIN_ABCD

TE_OFST

FE_OFST

ABCD_OFST

DELAY_CD

DELAY_AB

PDLIMIT

ga_RFSUM

HOLD_CTL

ga_PLLDP

ga_PLLDN

to DPD

BLOCK

DPD

BLOCK

S/IF

BLOCK

AUTO

OFSTCTL

BCA

BLOCK

BCA

RFCT

&

MIRR

RFRP

TE1RES

CD1 S12 DVD1.2

RF

Equalizer

RF SLM

& AGC

A

B

C

D

GAIN_EQ(02H)

MIRR57

Reference Information

Samsung Electronics 2-3

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

CD optical main beam A AC coupling input port for RF

CD optical main beam B AC coupling input port for RF

CD optical main beam C AC coupling input port for RF

CD optical main beam D AC coupling input port for RF

DVD optical main beam A AC coupling input port for RF

DVD optical main beam B AC coupling input port for RF

DVD optical main beam C AC coupling input port for RF

DVD optical main beam D AC coupling input port for RF

RF AMP I/O buffer bias resistance connection port

RF EQ bias resistance connection port

Analog block bias resistance connection port

CAP connection port for RF EQ center voltage

CD optical sub beam E input port for SERVO

CD optical sub beam F input port for SERVO

DVD optical main beam A input port for SERVO

DVD optical main beam B input port for SERVO

DVD optical main beam C input port for SERVO

1 ACD

BCD

CCD

DCD

ADVD

BDVD

CDVD

DDVD

RREFBF

RREFEQ

RREF

VREFEQ

E

F

ADVD1

BDVD1

CDVD1

FUNCTIONPIN NAME I/O

I

I

I

I

I

I

I

I

-

-

O

I

I

I

I

I

-

38

37

36

35

34 FE Input port for AMP GAIN setting

Input port for TE AMP GAIN setting

TE AMP output port

Bias resistance port for PDLIMIT

Input port for ABCD AMP GAIN setting

FEN

TEN

TE

PDLIMTRES

ABCDN

FUNCTIONPIN NAME I/O

I

I

O

-

I

28

27

26

25

24

23

22

21

20

19

DVD optical main beam D input port for SERVO

CD optical main beam F input port for SERVO

CD optical main beam F input port for SERVO

CD optical main beam F input port for SERVO

CD optical main beam F input port for SERVO

Power voltage input port for analog part

CAP connection port for analog part

center voltage, Use at other block

CAP connection port for focus auto offset (OPEN)

ON/OFF connection port for auto offset block (L :

auto offset adjustment H : serial offset adjustment)

BANDGAP voltage input port for ALPC

DVD optical laser diode driving voltage output port

18 DDVD1

ACD1

BCD1

CCD1

DCD1

AVCC

VREFA

FOFST

OFSTHOLD

VREFLP_BGI

LDODVD

I

I

I

I

I

-/O

O

IOI

P

32

31

30

29 DVD optical laser monitor diode voltage input port

CD optical laser diode driving voltage output port

CD optical laser monitor diode voltage input port

Power GND port for analog part

PDDVD

LDOCD

PDCD

AGND

I

O

I

P

33 FE AMP output portFE

O

ABCD AC coupling input port for SERVO monitorABCDI I

48

47

46

45

44

43

42

41

40

ABCD AMP output port

Peak hold time constant setting RC

connection port for RF envelope detect

Bottom hold time constant setting RC

connection port for RF envelope detect

RF envelope detect output port

Power GND input port for digital circuit

Focus OK comparing level input port

Focus OK comparator output port

(L: FOCUS OK)

Peak hold time constant connection port SERVO

defect max. time setting

Peak hold time constant connection port PLL defect

min. time setting

39 ABCD

ENVP

ENVB

ENV

DGND

FOKTH

FOKB

DFCT_CP1

DFCT_CP2

O

-

-

O

I

O

-

-

P

62

61

60

59

58

57

56

55

54

53

52

51

50

49 Output port of peak detector for defect

AC coupling input port for defect

Power voltage input port for digital circuit

Resistance connection port for PLL defect comparat-

ing level setting

Resistance connection port for SERVO defect com-

parating level setting

Defect output port for SERVO

Defect output port for PLL

Power voltage input port for DPD TE

Mirror output port

BCA output port

Resistance connection port for 3BTE offset

DPD EQ (A+C) output port

DPD EQ (B+D) output port

DPD defect waveform output port (MONITOR)

CC1

CC2

DVCC

DVCTTH2

DFCTTH1

DFCT1

DFCT2

DPDVCC

MIRR

BCA

TE3OFST

DPDEQ1

DPDEQ2

FAULTOUT

O

P

-

-

I

O

O

P

O

O

-

O

O

O

64

DPD TE MUTE control port (H : MUTE)

DPD TE PLL variable input port

63 DPDMUTE

PLLCTL

I

I

FUNCTIONPIN NAME I/O FUNCTIONPIN NAME I/O

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65 DPD TE PLL variable bias resistance

Power GND input port for DPD TE

CAP connection port for DPD TE center

Bias resistance connection port for delta block

Data input port

Clock input port

Data enable input port

OSC time constant input port for auto offset block

Reset input port for auto offset block (L : RESET)

BCA FILTER1

BCA FILTER2

RF ripple center voltage output port for mirror

Bottom hold time constant RC connection port for

RFCT generation

Peak hold time constant RC connection port for

RFCT generation

RF ripple AMP output port for mirror

RF ripple AMP GAIN input port for mirror

RF ripple offset control port for mirror

Bottom hold time constant RC connection port for

RFCT generation

Peak hold time constant RC connection port for

RFCT generation

Input port for MIRR signal generation

Power voltage input port for RF EQ

RF EQ output port

BCA comparating level control port

TE1RES

DPDGND

VREFDPD

RREFDLY

DATA

CLOCK

STB

OSC

RESET

BCAI

BCAO

RFCT

CB2

CP2

RFRP

RFRPN

MROFST

CB1

CP1

MIRRI

EQVCC

RFEQO

BCATH

I

P

O

-

I

I

I

I

I

O

O

-

-

O

I

I

-

-

I

P

O

I

91

90

89

RFAGCO input port for RF EQ

RF AGC AMP output port

AGC time constant CAP connection port

When AGC is “HOLD”, AGC voltage input port

88 EQIN

RFAGCO

AGCC

AGCI

I

O

-

I

95

94

93

92 Power GND input port for RF EQ

AGC level control voltage input port

RF bottom hold time constant RC connection port for RF AGC

RF peak hold time constant RC connection port for RF AGC

EQGND

AGCLEVEL

AGCB

AGCP

P

I

-

-

100

99

98

97

96

Bias resistance connection port for RF EQ frequency setting

RF EQ boost gain control voltage input port

RF EQ peak frequency control voltage input port

RF EQ boost, peak frequency gain control port corre-

sponding to wideband PLL (PLLG. PLLF resistance

internal design)

RF EQ control port (When No. PLLG isn’t adjusted,

apply DC CTL voltage.)

RDPF

EQG

EQF

PLLGF

VZOCTL

-

I

I

I

I

Reference Information

2-4 Samsung Electronics

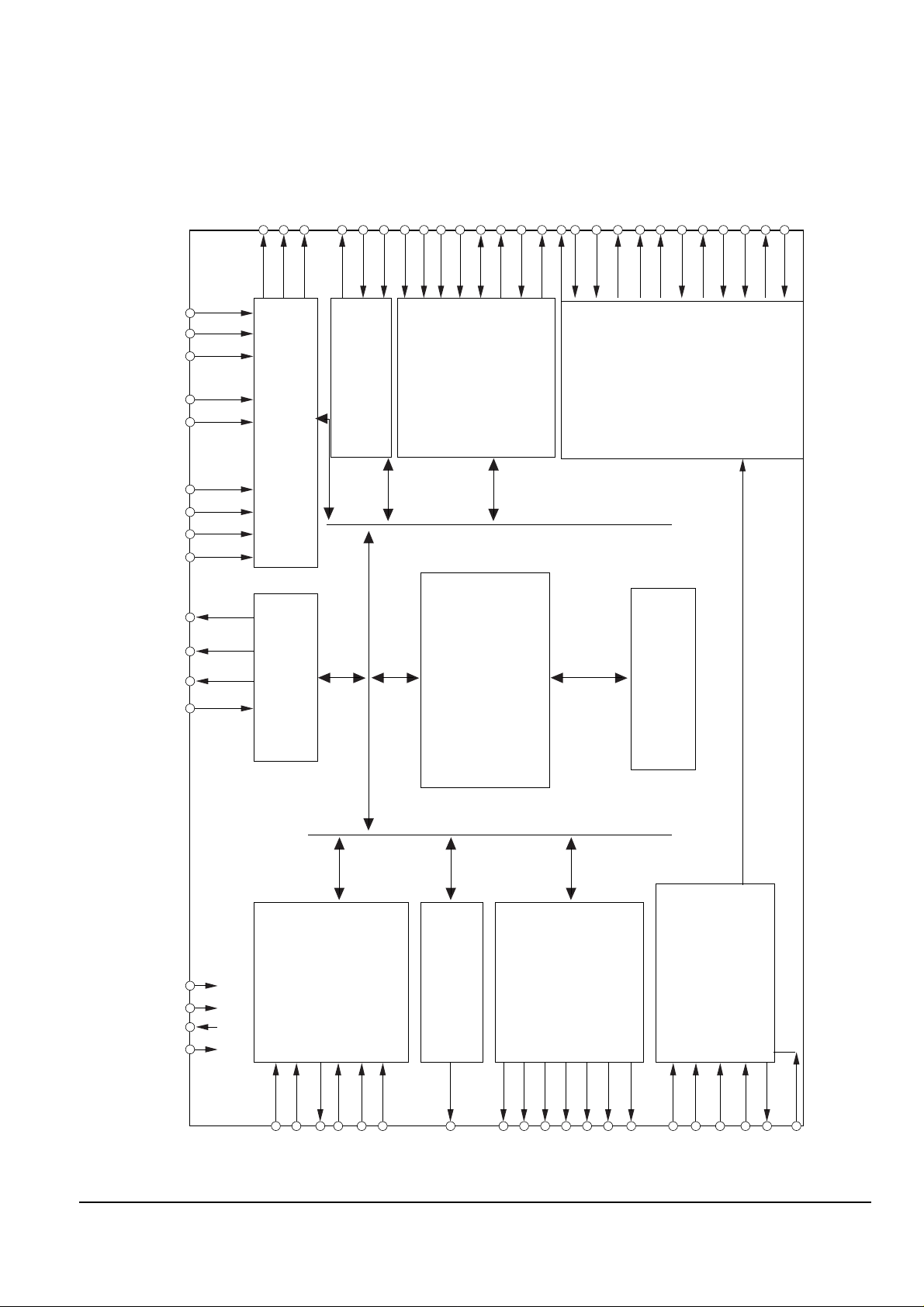

2-1-3 SIC1 (KS1452 ; Digital Servo)

A/D

CONVERTER

BLOCK

D/A

CONVERTER

BLOCK

TRACK

COUNTER

EFM

ASYMETRY

VREF

ENV

TZCO

SME

TE

FE

COUT

FOD

TRD

SLD

SPD

FBAL

TBAL

DVCTL

EFMI

RFI

ASYDVD

ASYCD

EFM

EFMOA

PLLHD

INTO_224

FDCTL

MAGICO

EQCTL

VCTRL

RVCO

PLCK

EFMRTD

RPD

RFD

PLLLOCK

MDOUT[3:0]

PSB

SENSE

MDATA[7:0]

MRDB

MWRB

CSB

DAB

SCOR

SQSI

SQCK

LDONB

TLKB

FLKB

DIRC

PS1

SSTOP

/PSO

SMON

LOCK

DFCT

FOKB

MIRR

TZCA

PHI1

XOUT

XO

XI

TEST

RSTB

TILTO

TILTI

ROM

DSP CORE

FOR

DIGITAL SERVO

TIMING

GENERATOR

I/O INTERFACE

BLOCK

SUB CODE

READ BLOCK

SYSCON

INTERFACE

BLOCK

WIDE

CAPTURE

RANGE PLL

Reference Information

Samsung Electronics 2-5

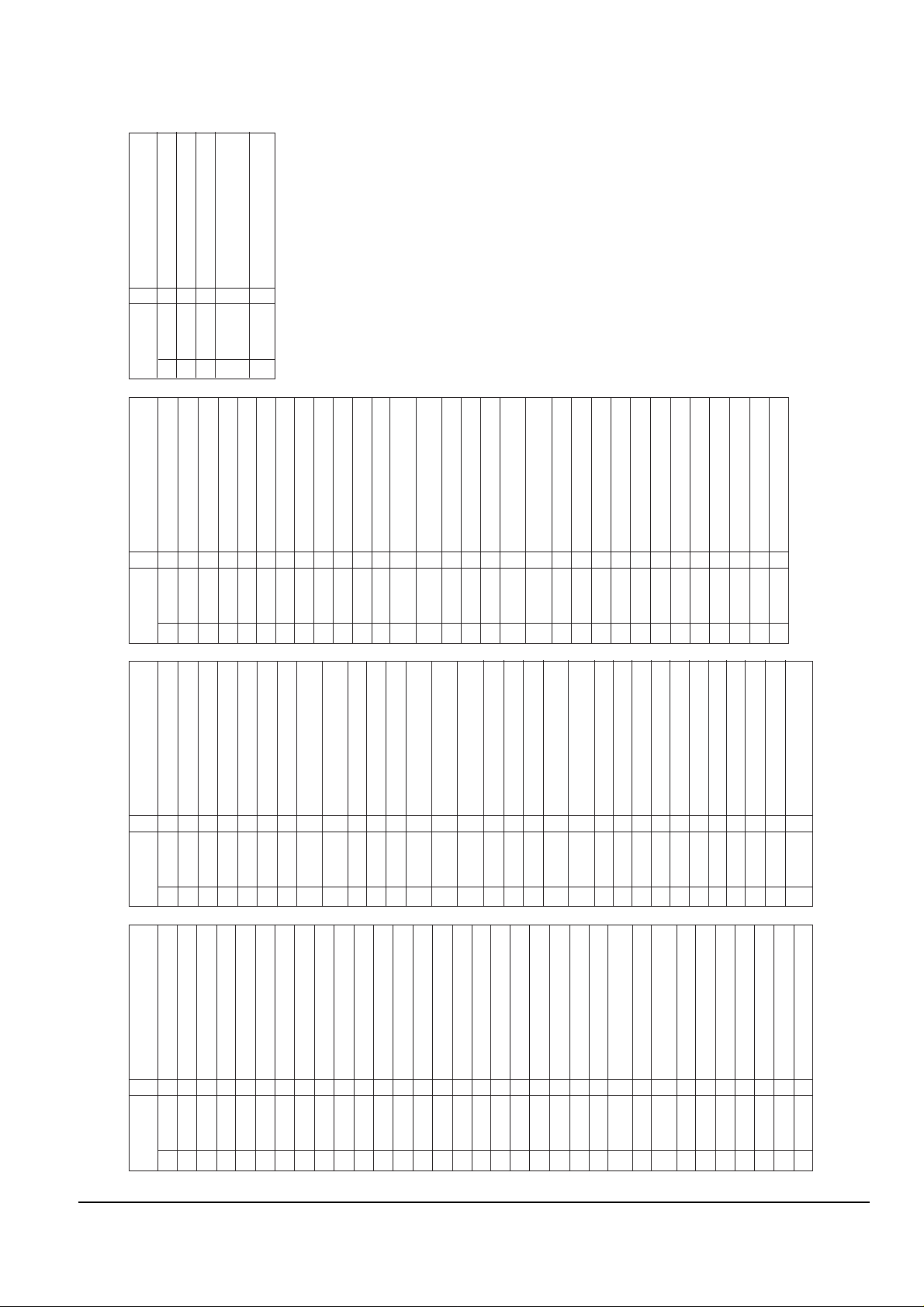

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

Mode data3 out controlled by micom

Limit switch/sled position sensor input pin0

Sled motor position sensor input pin 1

Test pin (L : normal H : test)

Counter clock

Focus servo lock signal output pin

Tracking servo lock signal output pin

0 : 1BIT 1 : 8BIT

System reset signal input pin

Micom chip select pin

Micom data/address select pin

Micom write clock signal input pin

Micom read clock signal input pin

Micom data pin 0

Micom data pin 1

Micom data pin 2

Micom data pin 3

Micom data pin 4

Micom data pin 5

Micom data pin 6

Micom data pin 7

Internal status monitor pin

Servo logic & ROM VDD power supply pin

System clock signal input pin

System clock signal output pin

Clock out (33.9688MHz) to DSP

Servo logic & ROM VSS power supply pin

Clock output pin for subcode data read

Subcode data input pin

Timing detection input pin for subcode data read

Motor ON signal input pin

Lock signal input pin

Direct jump control (for 1 track jump)

1 MDOUT3

SSTOP/PSO

PS1

TEST

COUT

FLKB

TLKB

PSB

RSTB

CSB

DAB

MWRB

MRDB

MDATA0

MDATA1

MDATA2

MDATA3

MDATA4

MDATA5

MDATA6

MDATA7

SENSE

DVDD

XI

XO

XOUT

DVSS

SQCK

SQSI

SCOR

SMON

LOCK

DIRC

FUNCTIONPIN NAME I/O

O

I

I

I

O

O

O

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

P

I

O

O

P

O

I

I

I

I

I

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

Focus OK signal input pin

PLL frequency detect control input pin

Laser diode ON signal output pin

Defect Detection signal input pin

Mirror signal input pin

PLL hold signal from micom

Servo interrupt monitor pin

PLL logic block VDD power supply pin

PLCK

Frequency lock detect output

(H : Lock L : Unlock)

Latched EFM output signal

PLL logic block VSS power supply pin

Resistor pin for VCO GAIN

Gain adjust resister for frequence detector

Gain adjust resister for phase detector

Control voltage for VCO

Input for hysteresis control of FD output (for test)

EFM offset adjustment pin

Tracking zero cross output pin

Servo CPU VDD power supply pin

EQ control signal

EFM signal for test

EFM signal

Asymmetric input signal for DVD

Asymmetric input signal for CD

RF input signal

Servo CPU VSS power supply pin

Analog block VSS power supply pin

Spindle error input pin

Reference voltage input pin

Tracking error signal input pin

34 FOKB

FDCTL

LDONB

DFCT

MIRR

PLLHD

INTO_224

PVDD

PLCK

PLLLOCK

EFMRTD

PVSS

RVCO

RFD

RPD

VCTL

MAGICO

EFMOA

TZCO

SVDD

EQCTL

EFMI

EFMO

LPFDVD

LPFCD

RFI

SVSS

AVSS

SME

VREF

TE

FUNCTIONPIN NAME I/O

I

I

O

I

I

I

O

P

O

O

O

P

I

I

I

I

I

I

O

P

O

I

O

I

I

I

P

P

I

I

I

72

71

70

69

68

67

66

Focus error signal input pin

RF envelope input pin

Tilt in (reserved)

Analog block VDD power supply pin

Tilt out (reserved)

Depth variation control signal output pin

Tracking balance signal output pin

Focus balance signal output pin

65 FE

ENV

TILTI

AVDD

TILTO

DVCTL

TBAL

FBAL

FUNCTIONPIN NAME I/O

I

I

I

P

O

O

O

O

80

79

78

77

76

75

74

73 Sled motor drive signal output pin

Spindle motor drive signal output pin

Focus actuator drive signal output pin

Tracking actuator drive signal output pin

TE signal for tracking zero cross input pin

Mode data 0 out controlled by micom

Mode data 1 out controlled by micom

Mode data 2 out controlled by micom

SLD

SPD

FOD

TRD

TZCA

MDOUT0

MDOUT1

MDOUT2

FUNCTIONPIN NAME I/O

O

O

O

O

I

O

O

O

Loading...

Loading...