Samsung 20071016100858718 Schematic Diagram 04

4

SAMSUNG PROPRIETARY

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

4

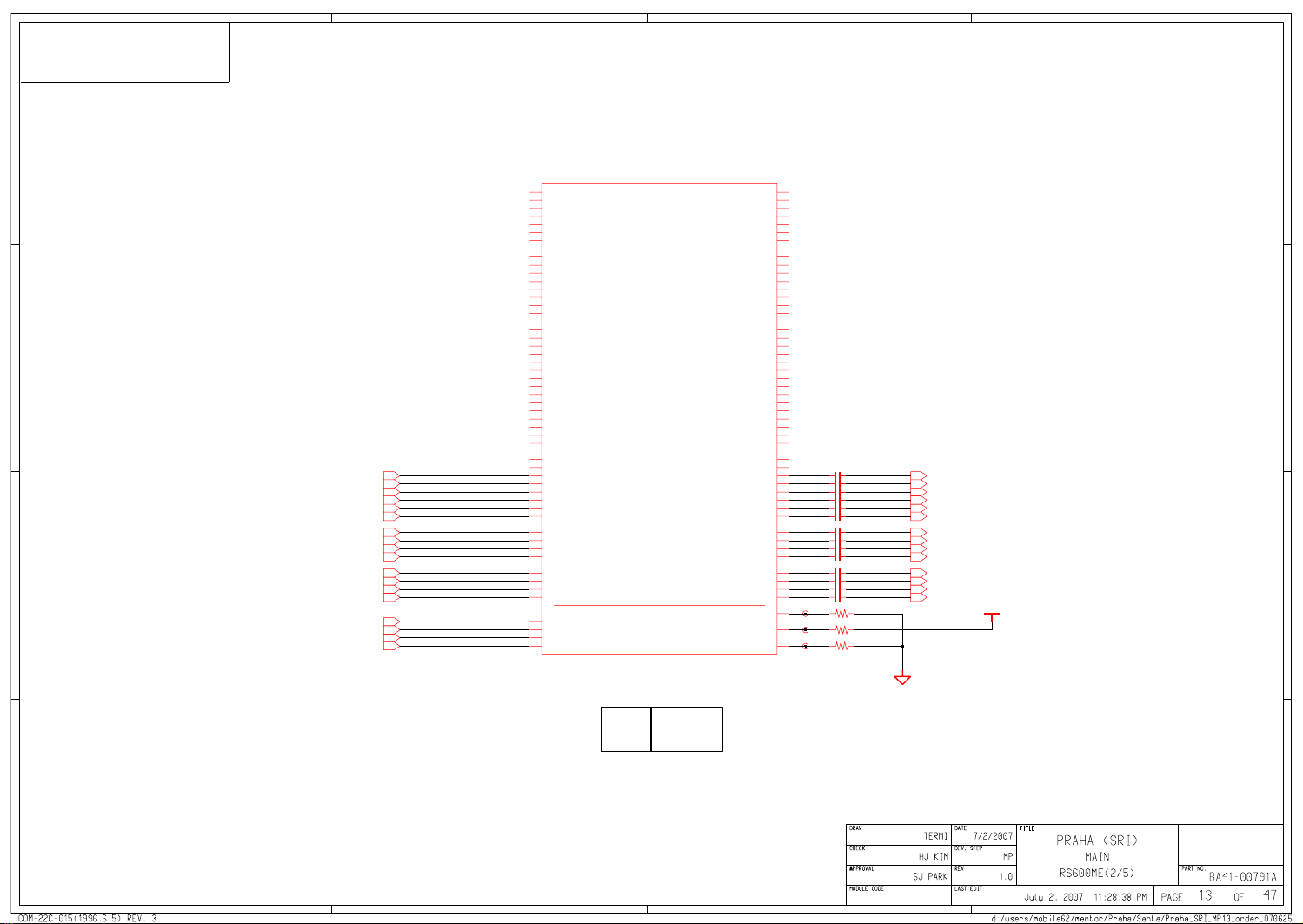

PRAHA (SRI)

CPU :

Chip Set :

Remarks :

Model Name :

PBA Name :

PCB Code :

Dev. Step :

T.R. Date :

DRAW

3

3

Intel Merom (800MHz)

RS600ME & SB600

Mobility Platform

PRAHA

MAIN

TPT : BA41-00791A

GCE : BA41-00792A

NAN : BA41-00811A

MP1.0 (8-Layer)

Samsung

1.0Revision :

2007.07.02

CHECK

APPROVAL

2

2

1

1

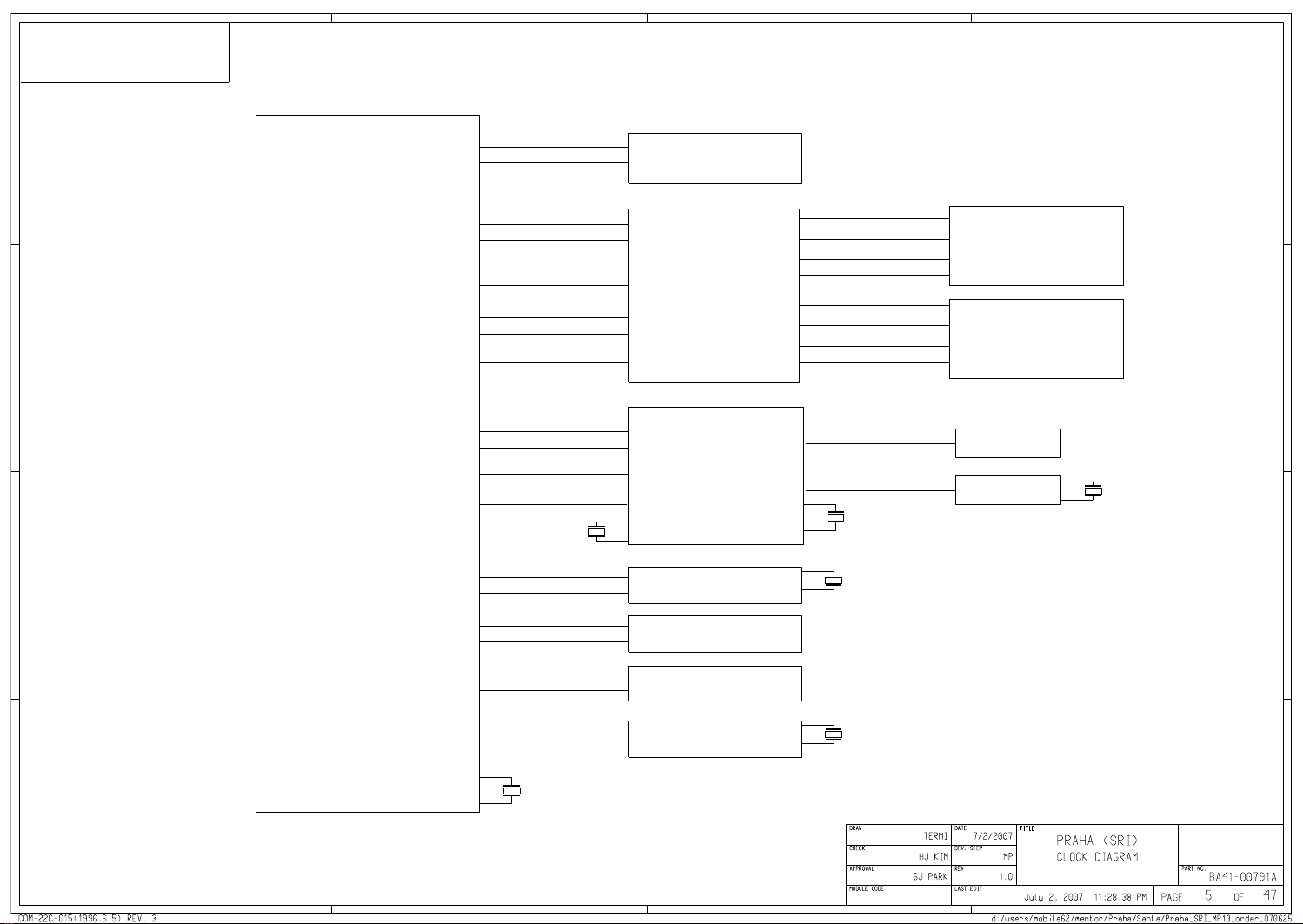

Table of Contents

Sheet 1. COVER

Sheet 2-6. DIAGRAM (Block/Power) & ANNOTATIONS

Sheet 7. CLOCK GENERATOR

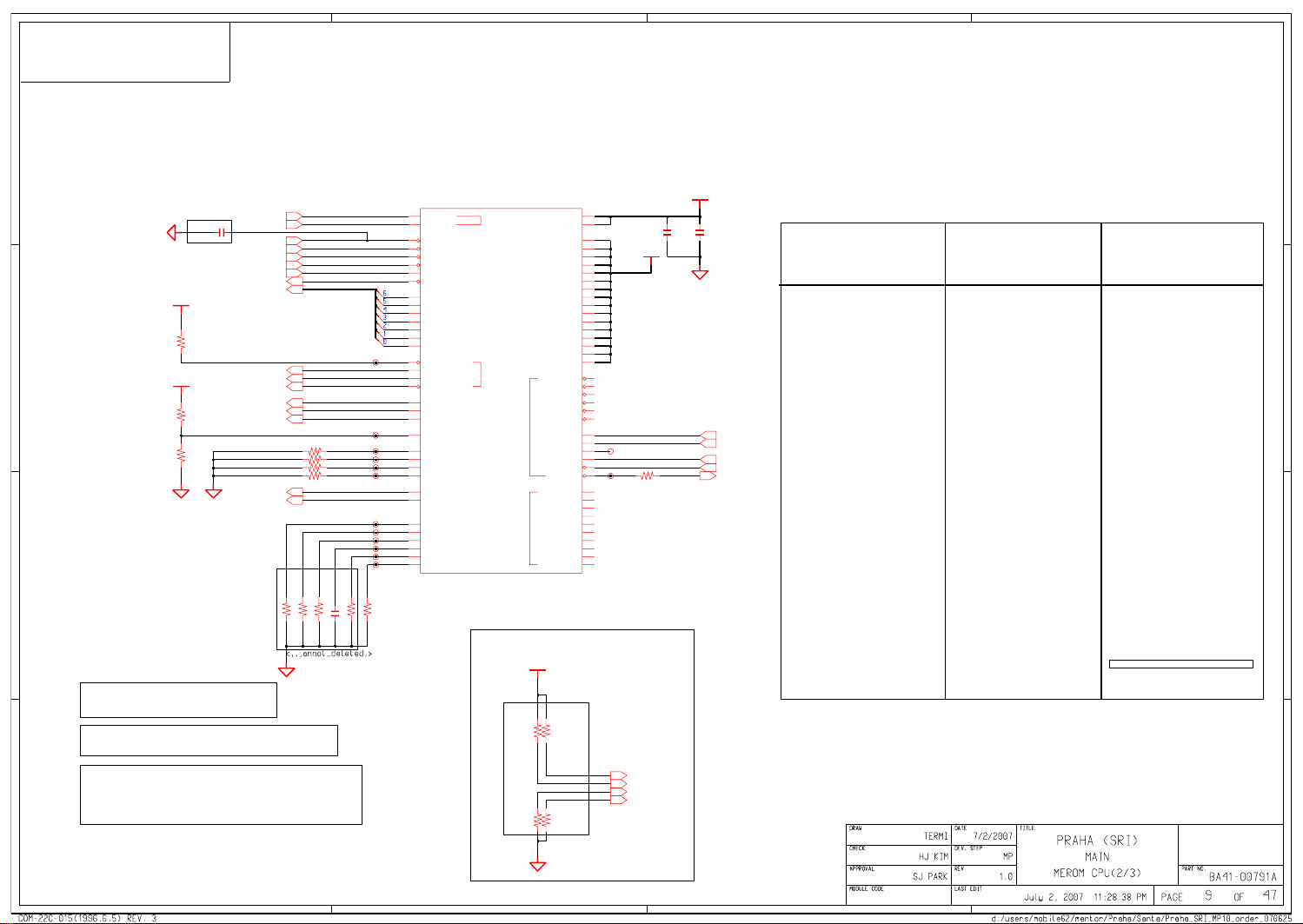

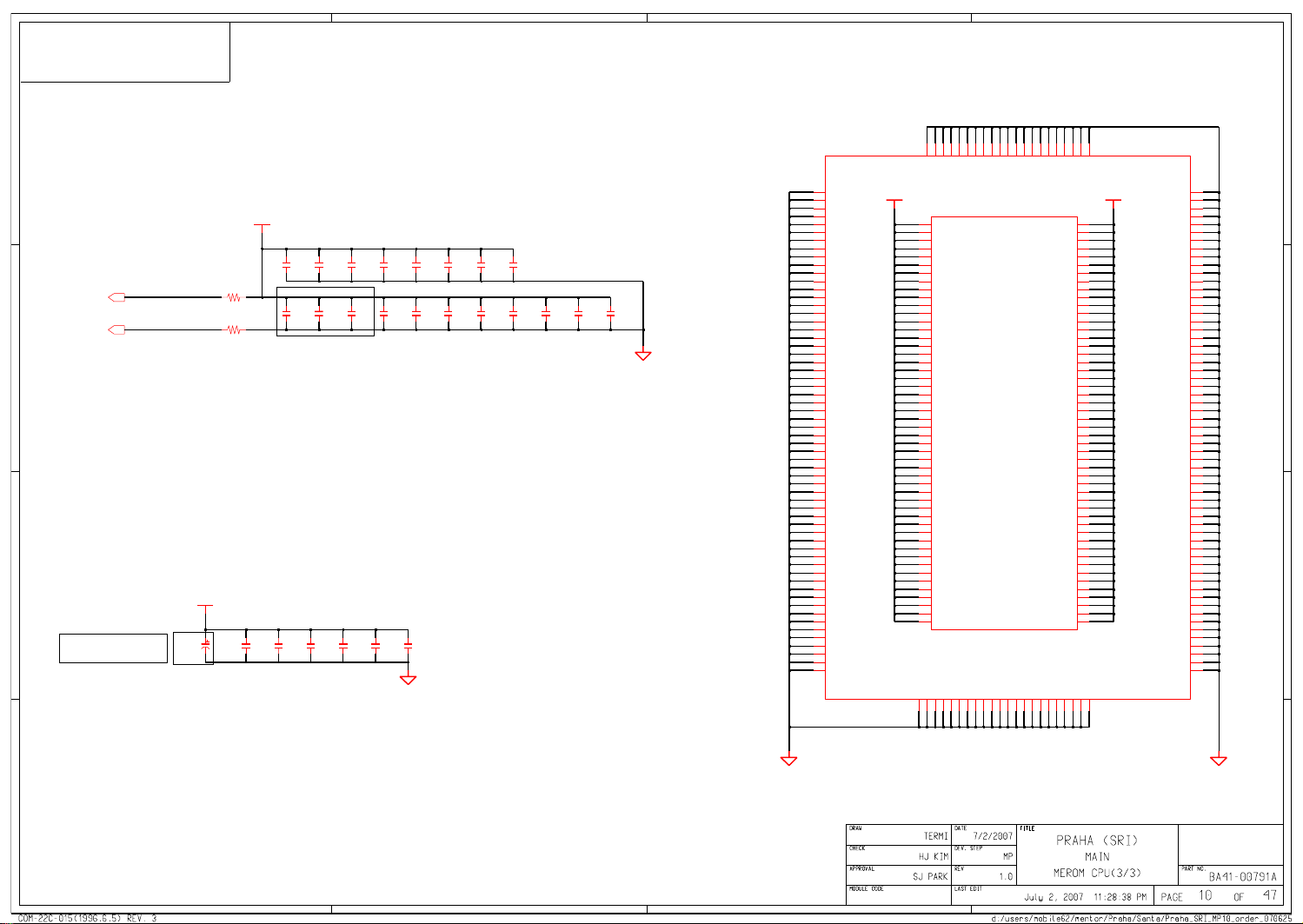

Sheet 8-10. Merom 800

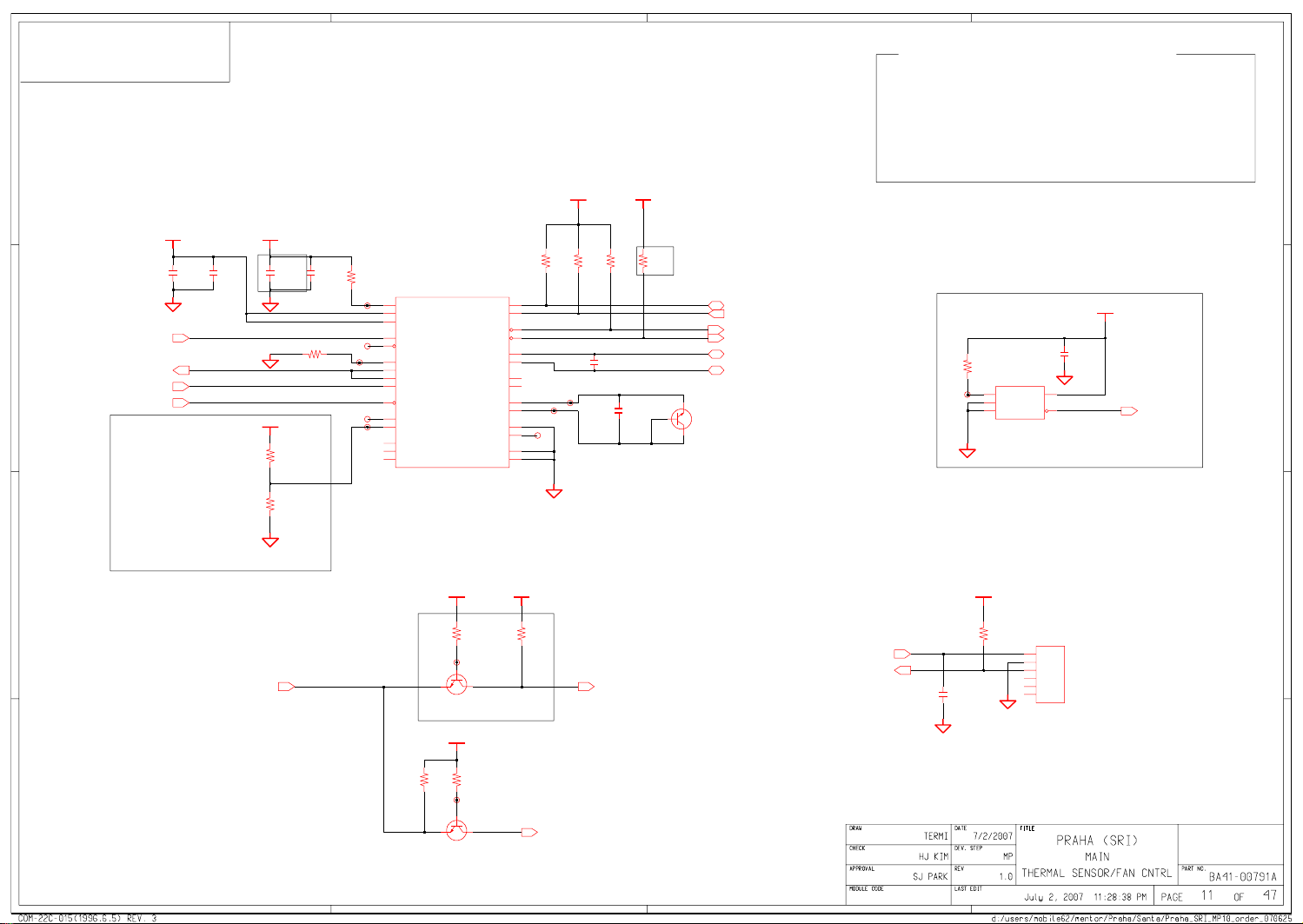

Sheet 11. THERMAL SENSOR / FAN CONTROL

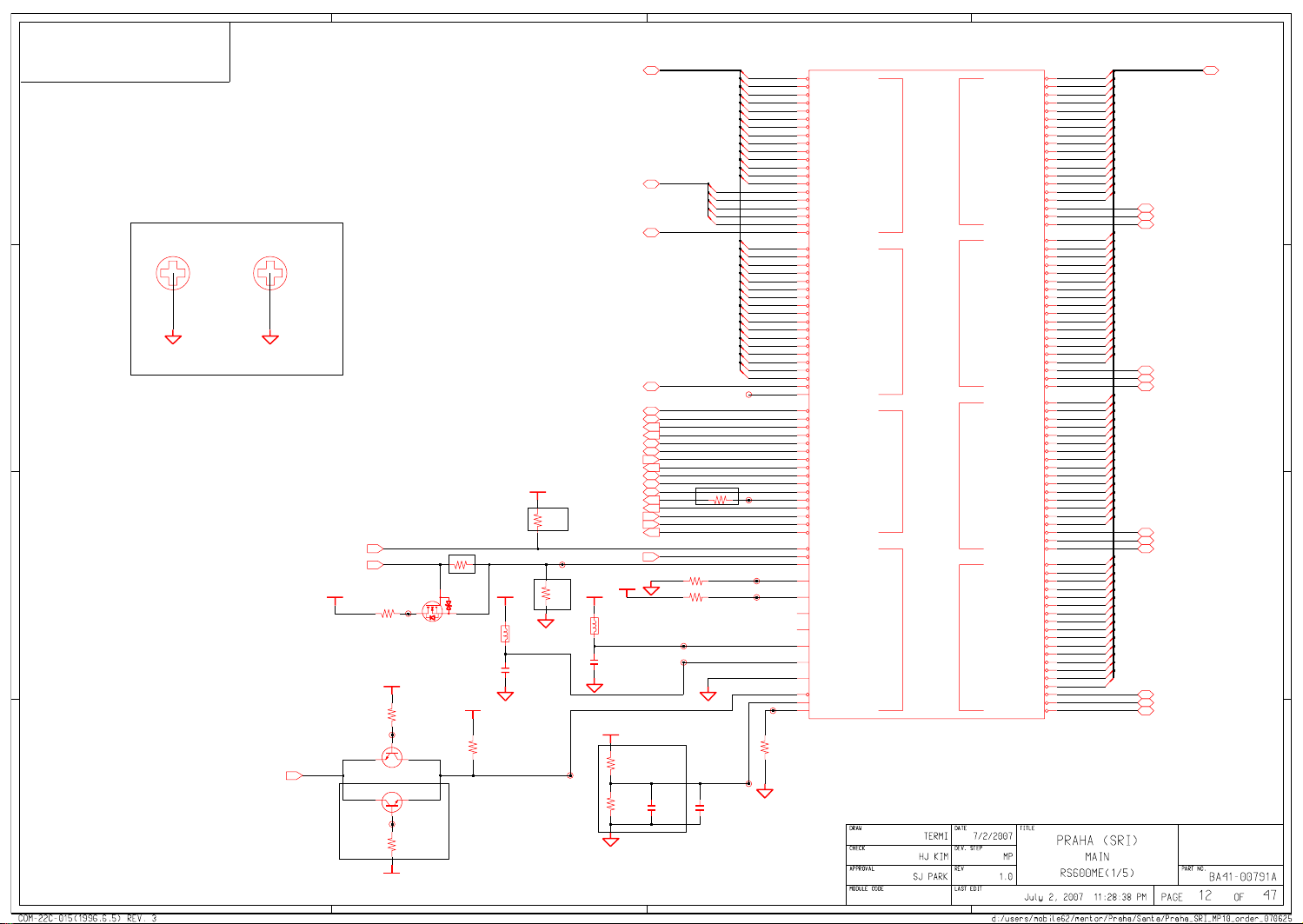

Sheet 12-16. RS600ME

Sheet17. DDR II SODIMM

Sheet18. DDR II TERMINATION

Sheet19-22. SB600

Sheet23. SB600 STRAPS

Sheet24. SPI ROM & DEBUG CARD CONN

Sheet25. LCD

Sheet26. CRT

Sheet27. EXPRESS CARD

Sheet28. 2 IN 1

Sheet29. MINICARD

Sheet30-32. AUDIO

Sheet33. HDD(SATA) & ODD(IDE)

Sheet34. MICOM

Sheet35. LOM WITH COMBO

Sheet36. USB & MDC

Sheet37. LED & BLUETOOTH & TOUCHPAD & KEYBOARD & LID S/W

Sheet38. CHARGER

Sheet39. P3.3V_AUX & P5.0V_AUX

Sheet40. P1.2V & P1.2V_AUX & VCCP

Sheet41. DDR2 POWER

Sheet42. CPU VRM

Sheet43. P1.5V POWER & SWITCHED POWER & MICOM RESET

Sheet44. ICT PORT

Sheet45. POWER DRAW & MOUNT HOLE

Sheet46-48. TP

D

D

C

C

B

B

Owner :

4

4

Confidential

SEC Mobile R & D Signature :

USE ICT PORT

A

A

X

3

3

2

2

1

1

SAMSUNG

ELECTRONICS

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

D

4

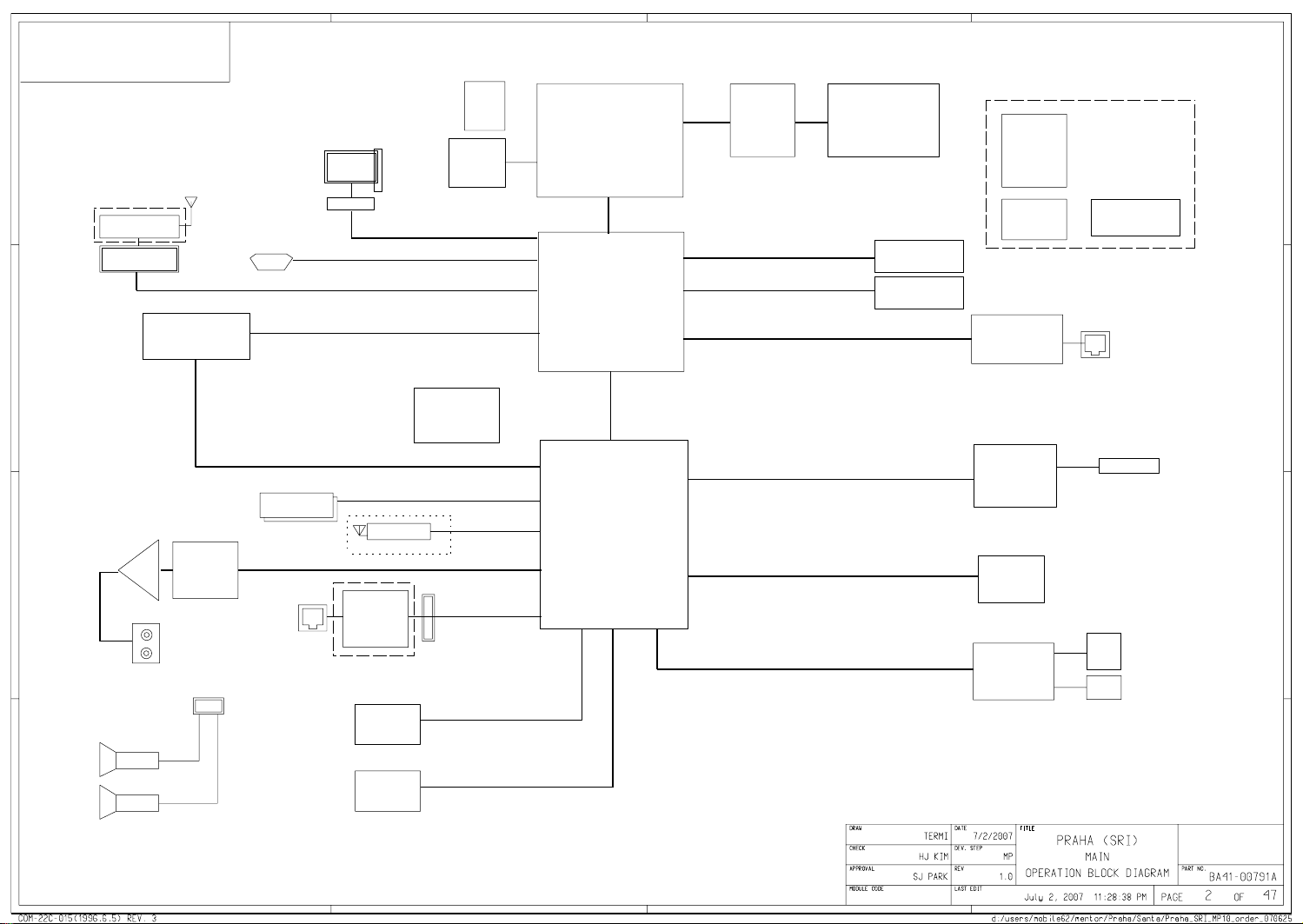

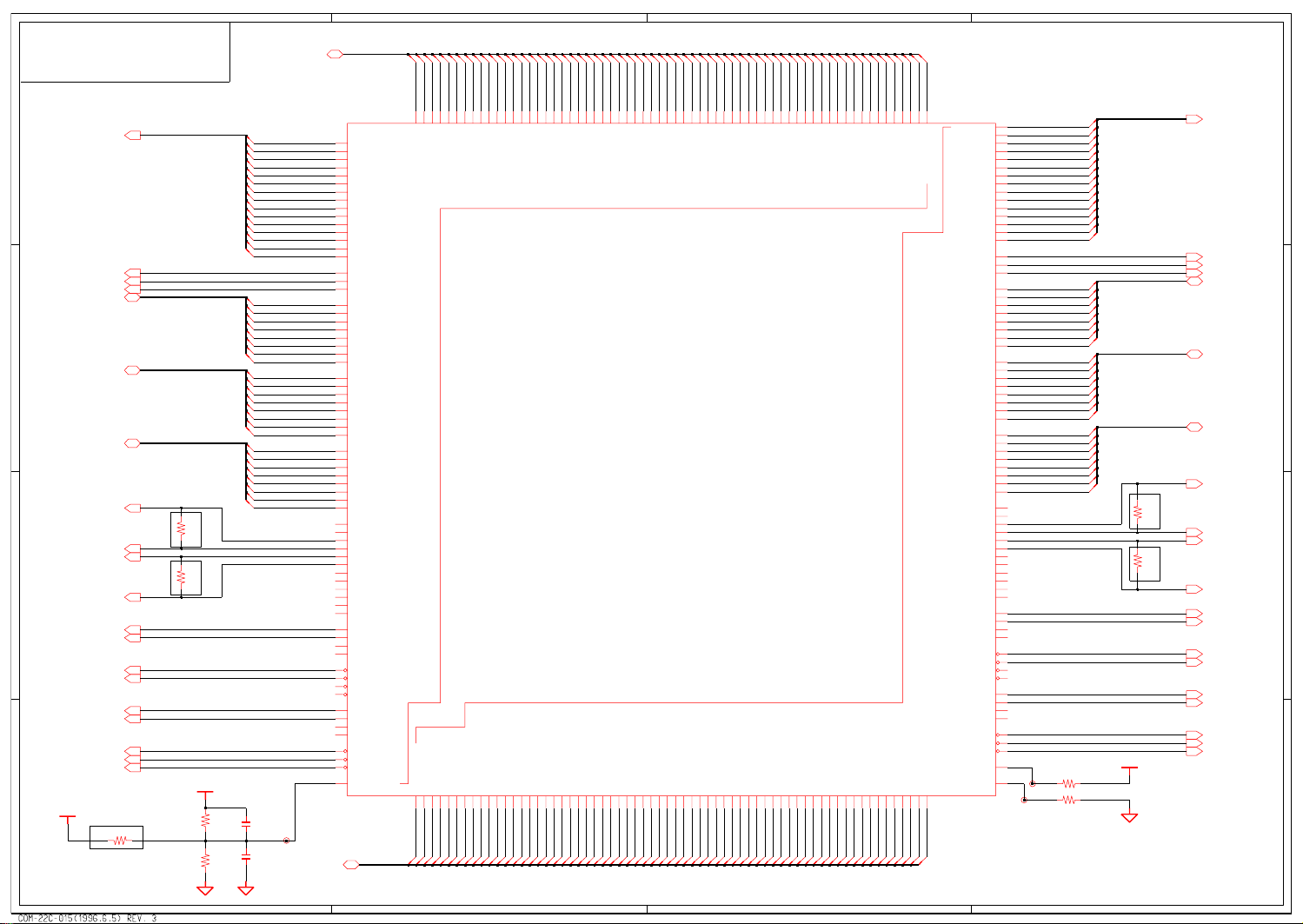

Wireless LAN

Mini Card

PG 29

ANT

Express Card

C

PG 27

PG 30

AUDIO

Audio

B

AMP

PG 31

AZALIA

Codec

ALC260

HP

PG 32

MIC-IN

PG 30

3

PG 26

CRT

PG 25

CRT

LCD

LVDS

FAN

PG 11

CPU

Thermal

Sensor

30P

1ch

PG 11

PCI Express

Mobile Processor

MEROM

(800MHz)

L2 Cache : 2 MB, 4MB

478pin

PG 8, 9,10

North Bridge

IMVP-6

Channel A

Channel B

RS600ME

PCI Express

Internal Graphics

Clocking

CK-410 for ATI

64 PIN

PG 7

USB 1

PG 39

USB 0,8,9

4P

PG 31

RJ11

PG 35

PG 33

ANT

Bluetooth

PG 37

Samsung

12P

AZALIA

MDC 1.5

PG 36

Confidential

HDD

USB 0,8,9

USB 5

AZALIA Primary

AZALIA Secondary

SATA

707 FCBGA

PG 12 ~ 16

4-Lane

A-Link Express

South Bridge

SB600

564 BGA

PG 19 ~ 22

PCI Express

USB 4

CPU

VRM

PG 42

2

DDR II 667/533

3.3V LPC, 33MHz

System

Connector

DC/DC

DDR II

SODIMM 0

DDR II

SODIMM 1

PG 17

PG 17

Charging

Circuit

PG 38

DDR II

VRM

PG 41

10/100 LOM

88E8039

PG 35

2 IN 1

AU6371

PG 28

SPI ROM

PG 24

MICOM

Hitachi H8S

2110B

PG 34

1

Switched PWR

PG 43

RJ45

PG 35

SD/MMC

PG 37

Touch

PAD

KBD

PG 37

D

C

PG 28

B

SPKR R

PG 33

A

SPKR L

4

ODD

3

PATA

A

SAMSUNG

ELECTRONICS

2

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

34

2

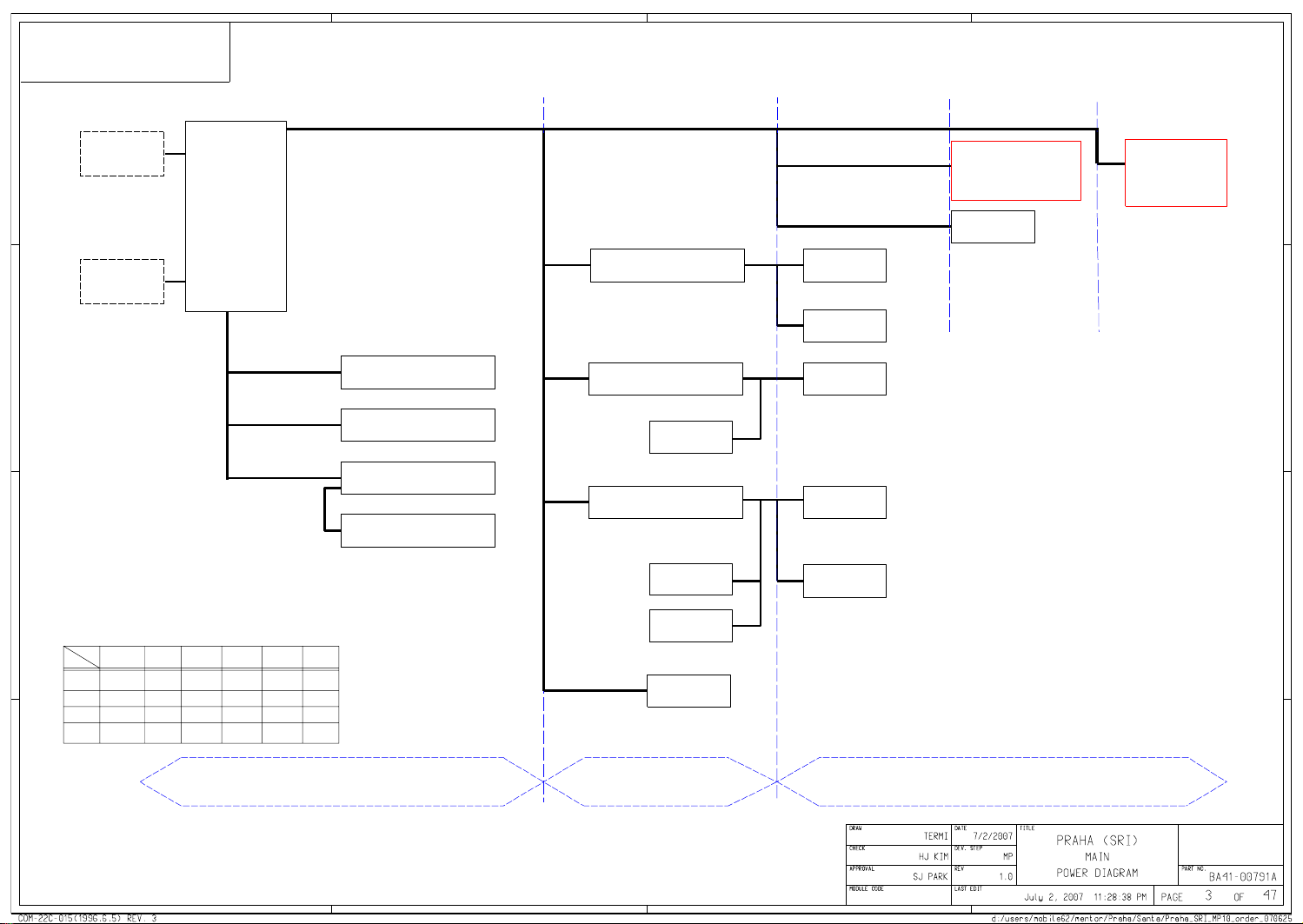

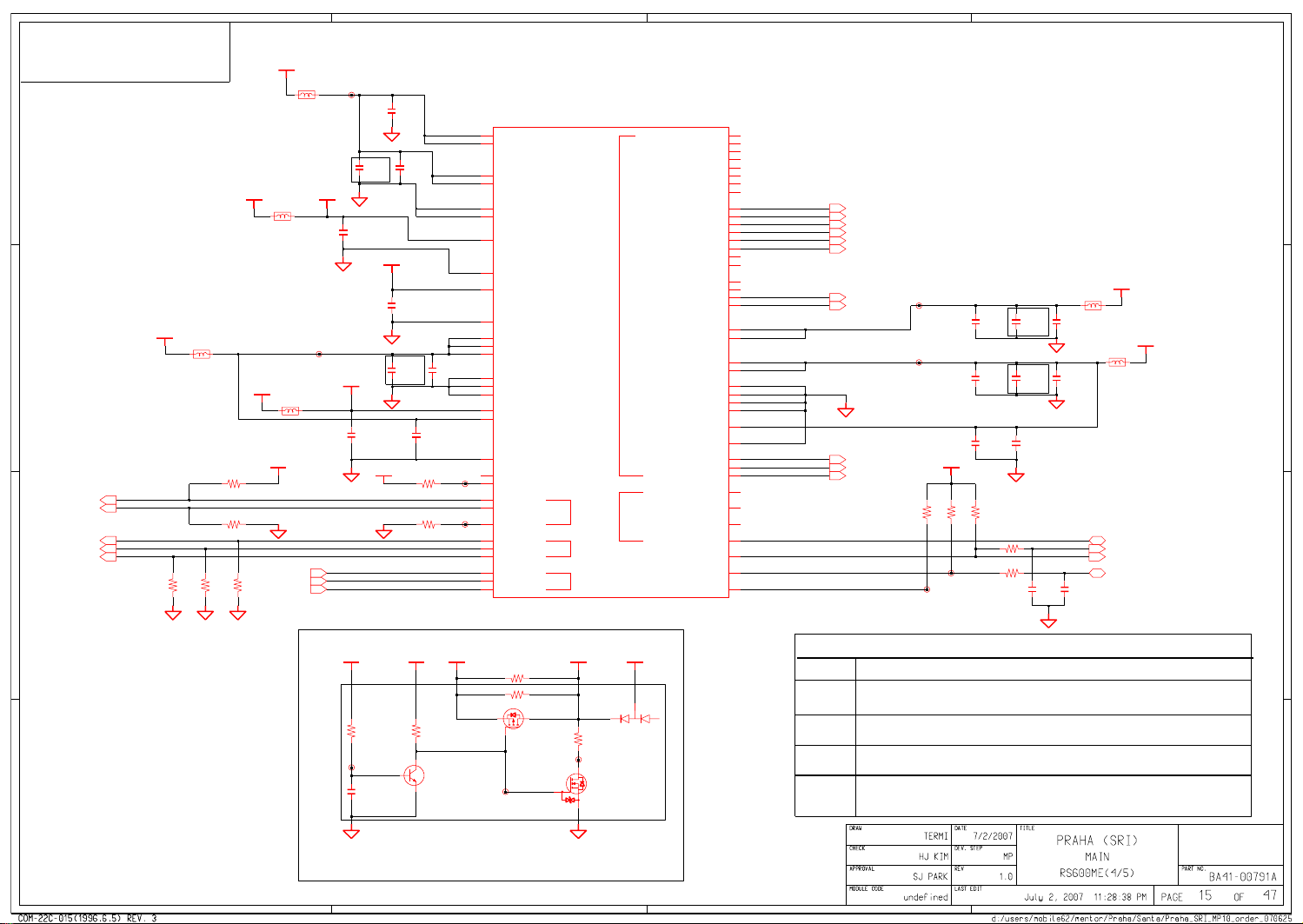

Power Diagram

1

D D

AC Adapter

KBC3_SUSPWRON

VDC

Battery DC

C

P12.0V_ALW

P5.0V_ALW

MICOM_P3.3V

P1.2V_ALW

P1.8V_AUX P1.8V

P1.2V_AUX

P3.3V_AUX

KBC3_PWRON

P0.9V

P5.0VP5.0V_AUX

P3.3V

KBC3_VRON

CPU

P1.05V

P1.2V

NB

SB

(VCCP)

P1.2V_PWRGD

VCC_CORE

CPU

Samsung

B

P2.5V_LAN

P1.5V

C

B

P1.2V_LAN

Rail

State

OFFONONS4

LOFFOFFONS5

A

4

VRON

PWRONSUSPWR+V+V*AUX+V*Always

HHONONONFull On

LHOFFONONS3

LH

L

S5 / S4

H

L

L

L

Confidential

MEM1_REF

S0S3

A

SAMSUNG

ELECTRONICS

3

2 1

D

C

B

A

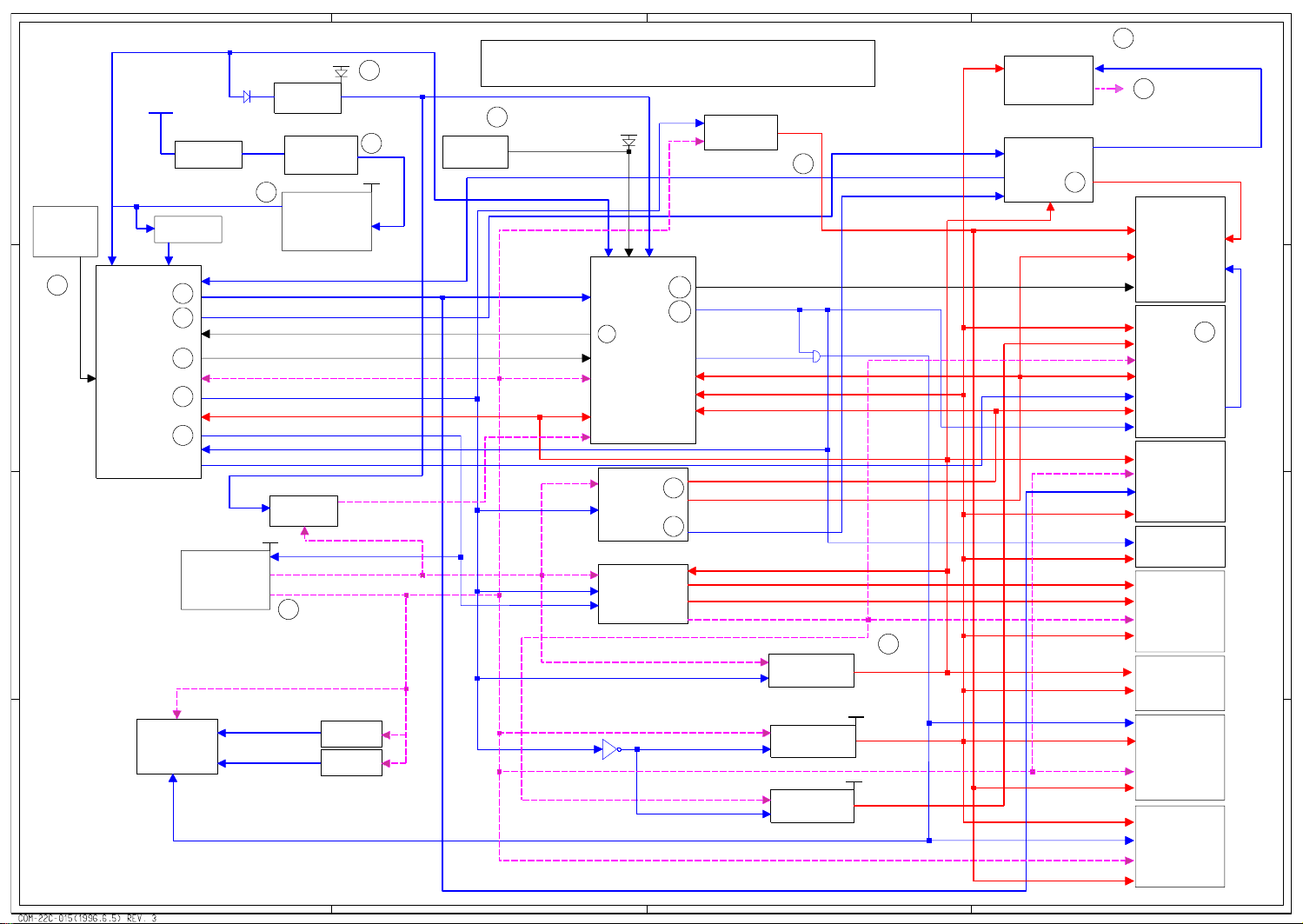

POWER

S/W

5

4

P12.0V_ALW

3) MICOM_P3.3V

KBC

5)KBC3_PWRSW#

88E8039

Sheet 35

4

MMBT3904

Sheet43

RHU002N06

(KBC3_RST#)

Sheet43

19

17

8

10

6

Sheet34

P5.0V_AUX & P3.3V_AUX

TPS51120

Sheet39

7) P3.3V_AUX

LOM

21-1) PEX3_RST#

P1.2V_ALW

MIC5258-1.2

Sheet43

AP4435GM

Sheet38

3

MICOM_P3.3V & P5V_ALW

TPS51120

Sheet39

18) VRM3_CPU_PWRGD

19) KBC3_PWRGD

17) CLK3_PWRGD#

9) CHP3_SLPS5#/S3#

8) KBC3_RSMRST#

7) P3.3V_AUX

10) KBC3_PWRON

11) P5.0V

6) KBC3_SUSPWRON

21-1) PLT3_RSTF#

18) KBC3_NBPWRGD

4) P1.2V_ALW

P1.2V_AUX

SI3456

Sheet43

V5FILT

6) KBC3_SUSPWRON

7) P5.0V_AUX

(2/2)

7) P3.3V_AUX

7

7-1) P1.2V_LAN

7-1) P2.5V_LAN

MICOM_P3.3V

VDC

(1/2)

10-1) KBC3_VRON

7-1) P1.2V_AUX

BCP69-16

Sheet 35

BCP69-16

Sheet 35

3

4

4) P1.2V_ALW

2

2) VDC

V5FILT

Battery

Sheet 19

Samsung

Confidential

POWER SEQUENCE

RTC

3

1

1) PRTC_BAT

3) MICOM_P3.3V

7) P3.3V_AUX

11) P5.0V

7-1) P1.2V_AUX

7) P5.0V_AUX

10-1) KBC3_VRON

10) KBC3_PWRON

MICOM_P3.3V

9

SB600

P1.2V & VCCP

SC415

Sheet 43

DDR2 POWER

SC486

Sheet 41

10) KBC3_PWRON

7) P3.3V_AUX

4) P1.2V_ALW

20

21

SB

Sheet 20-23

12

13

7) P5.0V_AUX

10) KBC3_PWRON

7) P3.3V_AUX

10) PWRON#

7) P1.8V_AUX

10) PWRON#

MIC5219B

Sheet 44

20) CPU1_PWRGDCPU

21) CHP3_ALINK_RST#

21)PEX3_RST#_CTRL

12) VCCP

11) P3.3V

12) P1.2V

21-1) PLT3_RSTF#

12) P1.2V

12) VCCP(1.05V)

13) P1.2V_PWRGD

11) P5.0V

11) 0.9V

7) MEM1_REF

7) P1.8V_AUX

2

Rev. 0.1

11) P1.5V

18

AP4435GM

Sheet 43

AP6680AGM

Sheet 43

AP680AGM

Sheet 43

2

CLOCK

CHIP

Sheet 8

17) CLK3_PWRGD#

18) VRM3_CPU_PWRGD

13) P1.2V_PWRGD

21-1) CHP3_NBRST#

21-1) PEX3_RST#

CPU

VRM

Sheet 45

11) P5.0V

20) CPU1_PWRGDCPU

18) KBC3_NBPWRGD

21-2) CHP3_NBRST#

19) KBC3_PWRGD

21-1) PLT3_RSTF#

11

11) P5.0V 11-1) VDD_AUD

P12.0V_ALW

11) P3.3V

P12.0V_ALW

11) P1.8V

20-1) PEX3_RST#

20-1) PEX3_RST#

14

11) P1.5V

12) VCCP

11) P3.3V

11) P1.8V

7) P1.8V_AUX

12) VCCP

12) P1.2V

11) P5.0V

7) P3.3V_AUX

11) P3.3V

11) P3.3V

11) P0.9V

7) MEM1_REF

7) P1.8V_AUX

11) P3.3V

11) P3.3V

11) P3.3V

7) P3.3V_AUX

11) P1.5V

11) P3.3V

7) P3.3V_AUX

11) P1.5V

1

15

15) CLK3_PWRGD#11) P3.3V

16

16) Clock Running

15) CLK3_PWRGD#

14) VCC_CORE

CPU

Sheet 8-10

NB

RS600ME

Sheet 12 - 16

Thermal

Sensor

Sheet 11

2-in-1

Controller

Sheet 28

DDR2

Memory

Sheet 17 - 18

Audio

Codec

Sheet 30

Express

Card

Sheet 27

Mini Card

WLAN

Sheet 29

1

D

22

C

22) CPU1_CPURST#

B

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

C

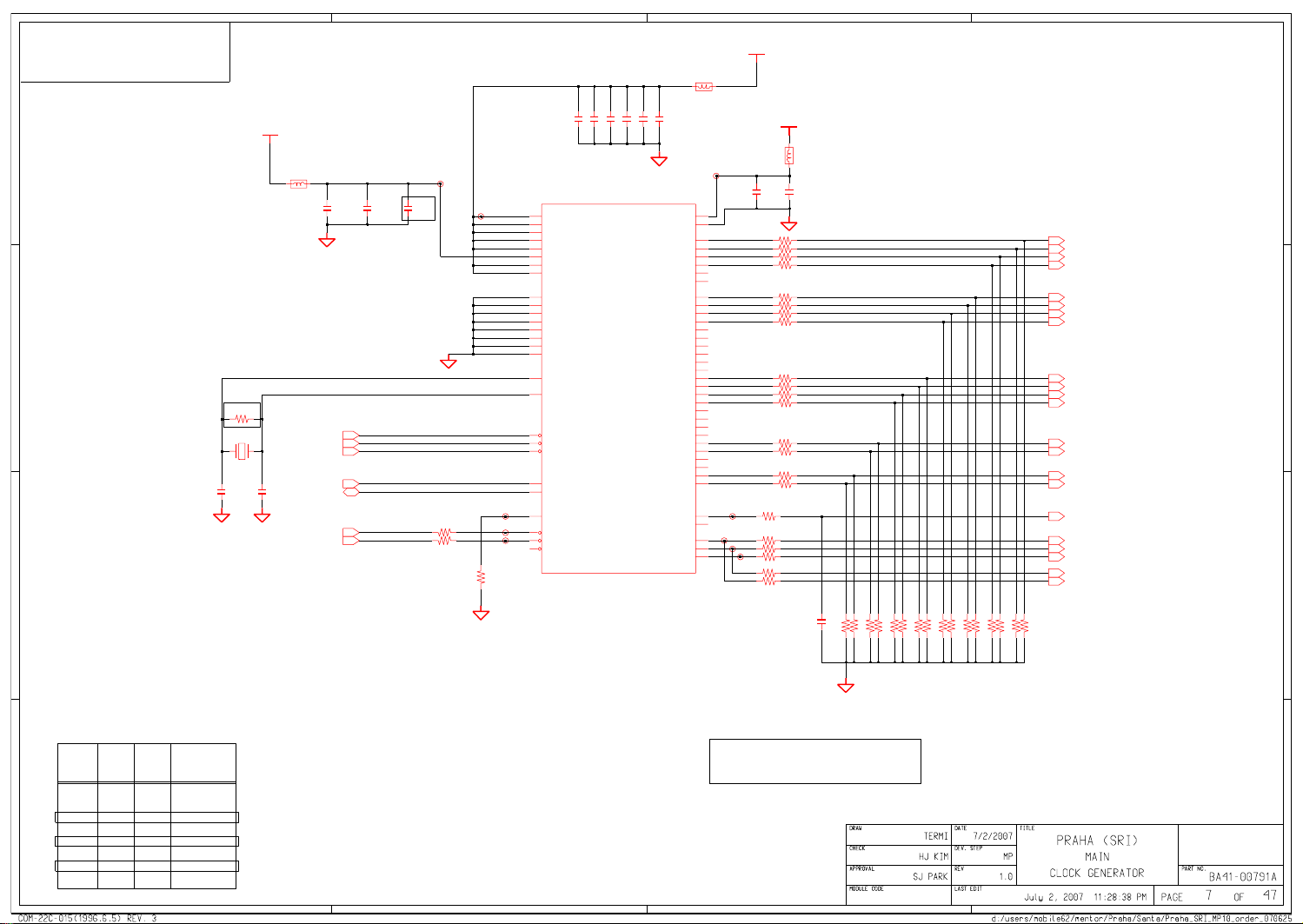

CLOCK GENERATOR

ICS951461

SLG84610

Samsung

B

CLK0_HCLK0

CLK0_HCLK0#

CLK0_HCLK1

CLK0_HCLK1#

CLK1_PCIEICH

CLK1_PCIEICH#

CLK1_NBSRC

CLK1_NBSRC#

CLK3_NB14M

CLK1_PCIERCLK

CLK1_PCIERCLK#

CLK3_USB48

CLK3_ICH14

25MHz

(FOR SATA)

CLK1_PCIELOM

CLK1_PCIELOM#

CLK1_MINIPCIEA

CLK1_MINIPCIEA#

CPU

(YONAH/MEROM)

RS600ME

SB600

LAN Controller (88E8039)

MINI CARD

CLK1_AMCLK1

CLK1_AMCLK1#

CLK1_AMCLK2

CLK1_AMCLK2#

CLK1_BMCLK1

CLK1_BMCLK1#

CLK1_BMCLK2

CLK1_BMCLK2#

SPI3_CLK

CLK3_PCLKMICOM

32.768KHz

(FOR RTC)

25MHz

SODIMM1

DDR2

CHANNEL A

SODIMM2

DDR2

CHANNEL B

SPI ROM

MICOM

10MHz

D

C

B

CLK1_EXPCARD

CLK1_EXPCARD#

Confidential

14.318 MHz

A

4

3

Express CARD

2-in-1 (AU6371)

12MHz

A

SAMSUNG

ELECTRONICS

2

1

4

SAMSUNG PROPRIETARY

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

EXCEPT AS AUTHORIZED BY SAMSUNG.

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

D

D

4

3

3

2

2

1

1

D

D

PCI Devices

Devices

USB

Hub to PCI

LPC bridge/IDE/AC97/SMBUS

Internal MAC

AC Link

Voltage Rails

VDC

VCC_CORE

C

C

B

B

VCCP

P0.9V

P1.2V

P1.5V

P1.5V_AUX

P1.8V

P1.8V_AUX

P1.8V_ALWS

P2.5V_LAN

MICOM_P3.3V

P3.3V

P3.3V_AUX

P5V

P5V_AUX

P5.0V_ALWS

P12V_ALWS

2

I C / SMB Address

Devices

SB600

SODIMM0

SODIMM1

CK-410 (Clock Generator)

USB PORT Assign

PORT NUMBER

0

1

4

5

IDSEL#

AD30(internal)

AD31(internal)

AD31(internal)

AD31(internal)

-

Primary DC system power supply (7 to 21V)

Core voltage for YONAH (0~1.5V)

YONAH Processor System Bus(PSB) Termination (1.05V)

0.9V switched power rail (off in S3-S5)

1.2V switched power rail (off in S3-S5)

1.5V switched power rail (off in S3-S5)

1.5V power rail (off in S4-S5)

1.8V switched power rail (off in S3-S5)

1.8V power rail(off in S4-S5)

1.8V power rail (Always On)

2.5V power rail (off in S4-S5)

3.3V always on power rail for MICOM

3.3V switched power rail (off in S3-S5)

3.3V power rail (off in S4-S5)

5.0V switched power rail (off in S3-S5)

5.0V power rail (off in S4-S5)

5.0V power rail (Always On)

12V power rail (Always On)

Address

Master

1010 0100

1010 0110

1101 001x

REQ/GNT#

Hex

A4h

A6h

D2h

ASSIGNED TO

Left side USB Port

USB Express Card

2-in-1 Memory Card

Bluetooth

Rear side USB Port8, 9

Interrupts

TYPE USAGE

Crystal

Crystal

Crystal

Crystal

Crystal

FREQUENCY

32.768KHz

25MHz

10MHz

14.318MHz

25MHz

12MHzCrystal 2-in-1 2-in-1 (SD/MMC)

CPU Core Voltage Table

Active Mode

VID(6:0)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0 1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

0

1

0

0

1

0

0

0

1

0

0

0

0

1

0

0

1

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

0

1

1

0

0

1

Samsung

Bus

SMBUS Master

-

Clock, Unused Clock Output Disable

Confidential

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

1

0

0

1

0

1

0

1

1

0

1

0

1

DPRSLPVR

DPRSTP*

PSI2*

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

1

1

01

0

1

1

0

1

1

0

1

1

1 1.4125 V

1

1

0

0

0

0

0

1

0

1

0

1

0

1

0

0

1

1

0

1

1

1

0

1

1

1

0

0

0

0

1

0

0

1

0

1

0

1

1

0

0

0

1

1

1

0

1

1

1

1

1

1

0

0

00

1

0

0

101.1750 V

0

0

1

0

0

0

0

1

1

1

1

0

1

1

1

0

0

0

1

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

1

0

1

1

1

1

10

Active

0

1

0 or 1

Voltage

1.5000 V

1.4875 V

1.4750 V 1

1.4625 V 1

1.4500 V

1.4375 V

1.4250 V 1

1.4000 V

1.3875 V

1.3750 V 1

1.3625 V

1.3500 V

1.3375 V

1.3250 V 1

1.3125 V

1.3000 V

1.2875 V

1.2750 V

1.2625 V

1.2500 V

1.2375 V

1.2250 V

1.2125 V

1.2000 V

1.1875 V

1.1625 V

1.1500 V

1.1375 V

1.1250 V

1.1125 V

1.1000 V

1.0875 V

1.0750 V

1.0625 V

1.0500 V

1.0375 V

1.0250 V

1.0125 V

Active/Deeper Sleep

Dual Mode Region

VID(6:0)

0

0

1

0

1

0

0

0

0

0

1

0

0

1

0

0

0

0

0

1

0

1

1

0

1

1

0

1

0

1

1

0

1

1

0

1

1

0

1

0

1

1

0

1

1

1

0

1

0

1

1

1

0

1

0

1

1

0

1

1

0

1

1

1

0

1

1

0

1

0

0

1

0

0

1

0

0

1

0

1

0

0

0

1

0

1

0

0

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

0

0

1

0

0

1

0

0

1

0

0

1

1

1

DPRSLPVR

DPRSTP*

PSI2*

DEVICE

SB600

SB600

MICOM

CLOCK-Generator

LAN

IMVP-6

0

0

1

0

1

0

1

1

0

1

0

1

10

1

0

0

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

0

0

1

0

0

0

0

1

1

0

1

0

1

1

0

0

1

0

0

1

0

110.7750 V

1

0

1

1

0

1

1

0

1

1

1

1

1

1

1

1

0

010.7000 V

0

0

0

0

1

0

0

0

1

0

010.6500 V

0

1

0

0

1

0

1

1

0

1

1

0

1

0

0

1

0

1

1

0

1

1

0

0

1

1

1

0

1

1

1

1

1

1

1

1

1

000

0

0

0

Deeper Slp

1

0

0 or 1

Real Time Clock

SATA

H8S-2110B

CK-410M

LOM

Deeper Sleep/Extended Deeper Sleep

Dual Mode Region

VID(6:0)

Voltage

1

0

1.0000 V

0.9875 V

1

0

0.9750 V

0.9625 V

0.9500 V

0.9375 V

1

0

0.9250 V

0.9125 V

1

1

0.9000 V

0

1

0.8875 V

0

0.8750 V

0.8625 V

1

0.8500 V

0

1

0.8375 V

0

0.8250 V

1

0.8125 V

0

0.8000 V

1

0.7875 V

0

1

0.7625 V

0

0.7500 V

0.7375 V

1

0

0.7250 V

0.7125 V

1

1

0

1

0.6875 V

0.6750 V

0

1

0.6625 V

0

1

0.6375 V

0

0.6250 V

1

0.6125 V

0

0.6000 V

0.5875 V

1

0.5750 V

0

0.5625 V

1

0.5500 V

0

0.5375 V

1

0.5250 V

0

0.5125 V

1

0.5000 V

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

*"1111111" : 0V power good asserted.

Crystal / Oscillator

Voltage

0

1

0

0

1

1

0

0

1

0

1

0

1

0

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

1

0

1

0

1

0

1

1

0

10

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0.4875 V

0.4750 V

0

0

1

0

1

0.4625 V

1

0

0

1

0.4500 V

1

0.4375 V

0

1

0.4250 V

0

1

1

0.4125 V

1

1

1

0

0.4000 V

0

0

1

0

0

0.3875 V

1

0.3750 V

0

0

1

0.3625 V

0

1

0

1

0.3500 V

0

1

0

0.3375 V

1

1

0.3250 V

0

1

1

1

1

0.3125 V

0

0

0.3000 V

0

0.2875 V

0

0

1

0

0

1

0.2750 V

0.2625 V

0

1

1

0.2500 V

1

0

0

1

0

0.2375 V

0.2250 V

1

1

0

1

1

0.2125 V

1

1

0.2000 V1

0

0

0

1

0

0.1875 V

0

0.1750 V

1

0

0

1

0

1

0.1625 V

0

0

1

0.1500 V

0.1375 V

1

1

0

0.1250 V

1

0

1

1

1

0.1125 V

1

0.1000 V

0

0

0

0

0

1

0.0875 V

0

0.0750 V

0

1

1

1

0

0.0625 V

0

0

1

0.0500 V

0.0375 V

0

1

1

0.0250 V

0

1

1

1

1

1

0.0125 V

0

0

1

0

0.0000 V

0

0

1

0.0000 V

0.0000 V

0

0

1

0.0000 V

1

0

1

0.0000 V

0

0

1

0

1

1

0.0000 V

1

0.0000 V

1

0

1

1

1

0.0000 V

C

C

B

B

System Power States

A

A

CHP3_SLPS1* S1, Powered-On-Suspend(POS) : In this state, all clocks(except the 32.768KHz clock) are stopped.

CHP3_SLPS3* S3, Suspend-To-RAM(STR) : The system context is maintained in system DRAM, but power is shut off to non-critical circuits.

CHP3_SLP4S* S4, Suspend-To-Disk(STD) : The Context of the system is maintained on the disk. All power is then shut off to the system except for the logic required to resume.

CHP3_SLPS5* S5, Soft Off(SOFF) : System context is not maintained. All power is shut off except for the logic required to restart. A full boot is required when waking.

The system context is maintained in system DRAM. Power is maintained to PCI, the CPU, memory controller, memory, and all other criticial subsystems.

Note that this state does not preclude power being removed from non-essential devices, such as disk drives. During this state, CPU can be selected

for either Deep Sleep or Deeper Sleep.

In Deeper Sleep, CPU voltage reduced in this state to reduce the leakage power.

Memory is retained, and refreshes continue. All clocks stop except RTC clock.

Externally appears same as S5, but may have different wake events.

4

4

3

3

*Yonah Processor (2.33 GHz / 800 MHz : TBD)

A

A

SAMSUNG

ELECTRONICS

2

2

1

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

Pt decoupling CAPS close to Clock Chip power pin

BLM18PG181SN1

B506

P3.3V

2

1

100nF

C576

100nF

C571

100nF

C573

100nF

10000nF

6.3V

C577

CPUT0

CPUC0

CPUT1

CPUC1

CPUT2

CPUC2

SRCCLKT0

SRCCLKC0

ATIGCLKT0

ATIGCLKC0

ATIGCLKT1

ATIGCLKC1

ATIGCLKT2

ATIGCLKC2

ATIGCLKT3

ATIGCLKC3

SRCCLKT1

SRCCLKC1

SRCCLKT2

SRCCLKC2

SRCCLKT3

SRCCLKC3

SRCCLKT4

SRCCLKC4

SRCCLKT5

SRCCLKC5

SRCCLKT6

SRCCLKC6

SRCCLKT7

SRCCLKC7

48MHZ_1

48MHZ_0

FSLA_REF0

FSLB_REF1

FSLC_REF2

C574

VDDAVDDCPU

GNDA

P3.3V

B504

BLM18PG181SN1

R59

R64

R63

R36

R34

R33

R38

R37

R42

R43

R45

R44

R39

R40

R67

R41

2.2K

33

2.2K

2.2K

33

33

C586

10000nF

6.3V

Route all CLK1 signal as different pair rule

33

33

33

33

33

33

33

33

33

33

33

33

33

33

33

33

1%

1%

1%

1%

49.9

49.9

49.9

R545

R567

R546

49.9

R547

C590

0.022nF

1%

49.9

R550

1%

49.9

R551

1%

49.9

R549

1%

49.9

R548

1%

49.9

R542

1%

49.9

R540

1%

49.9

R541

1%

49.9

R543

1%

49.9

R544

1%

49.9

R562

49.9 1%

R564

1%

49.9

R563

15-B4

15-B4

13-B3

13-B3

13-B3

13-B3

35-D4

35-D4

29-C4

29-C4

19-D4

19-D4

27-C4

27-C4

20-D2

15-B4

20-C3

9-D4

9-D4

9-C4

9-C4

9-C4

CLK0_HCLK0

CLK0_HCLK0#

CLK0_HCLK1

CLK0_HCLK1#

CLK1_PCIEICH

CLK1_PCIEICH#

CLK1_NBSRC

CLK1_NBSRC#

CLK1_PCIELOM

CLK1_PCIELOM#

CLK1_MINIPCIEA

CLK1_MINIPCIEA#

CLK1_PCIERCLK

CLK1_PCIERCLK#

CLK1_EXPCARD

CLK1_EXPCARD#

CLK3_USB48

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

CLK3_NB14M

CLK3_ICH14

C572

10nF

50

49

58

57

54

53

52

51

47

46

43

42

41

40

37

36

35

34

30

31

26

27

24

25

20

21

18

19

16

17

12

13

6

R66

5

63

62

R60

R61

61

R58

R57

D

C

B

D

P3.3V

B505

BLM18PG181SN1

C587

4700nF

6.3V

C589

100nF

10V

nostuff

C588

100nF

10V

C

1M

R568

nostuff

ITP3_DBRESET#

14.31818MHz

C54

0.022nF

1

2

Y501

C53

0.022nF

MINIPCIE3_CLKREQ#

CLK3_PWRGD#

CHP3_CPUSTP#

SMB3_CLK

SMB3_DATA

EXP3_CLKREQ#

B

9-B2

20-C320-A4

34-C3 42-C4

19-A4

27-C3 29-C220-C320-A417-B417-B2

17-B2

R65

27-C4

R28 R62

29-C4

Samsung

29-C2

27-C417-B420-A4 20-C3

0

0

R35

475

1%

100nF

C575

U8

ICS951461

56

44

VDD_SRC1

28

VDD_SRC2

23

VDD_SRC3

14

VDD_SRC4

4

VDD_48

39

VDD_ATIG

1

VDD_REF

55

GND_CPU

45

GND_SRC1

29

GND_SRC2

22

GND_SRC3

15

GND_SRC4

7

GND_48

38

GND_ATIG

64

GND_REF

2

X1

3

X2

60

RESET_IN*

8

VTTPWRGD*_PD

59

CPU_STOP*

9

SMBCLK

10

SMBDAT

48

IREF

11

CLKREQA*

32

CLKREQB*

33

CLKREQC*

Compatible Components

Silego : SLG84610

Confidential

FSB

FSA

BSEL0

CPU

0

A

0

0

0

1

1

1

BSEL1

0

0

1

0

0

1

1

FSC

BSEL2

0

1

0 200 MHz1

1

0

1

01

1

4

HOST CLK

266 MHz

333 MHz

400 MHz

133 MHz

100 MHz

166 MHz

RSVD

Merom 800MHz

Celeron 533MHz

Merom 667MHz

3

Place all te serias termination resistor as close as Clock Chip as possible

FSA, FSB, FSC of Clock chip are low thershold inputs

Vih_fs_min = 0.7V

Vil_fs_max - 0.35V

2

A

SAMSUNG

ELECTRONICS

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

VCCP

34

2

1

D

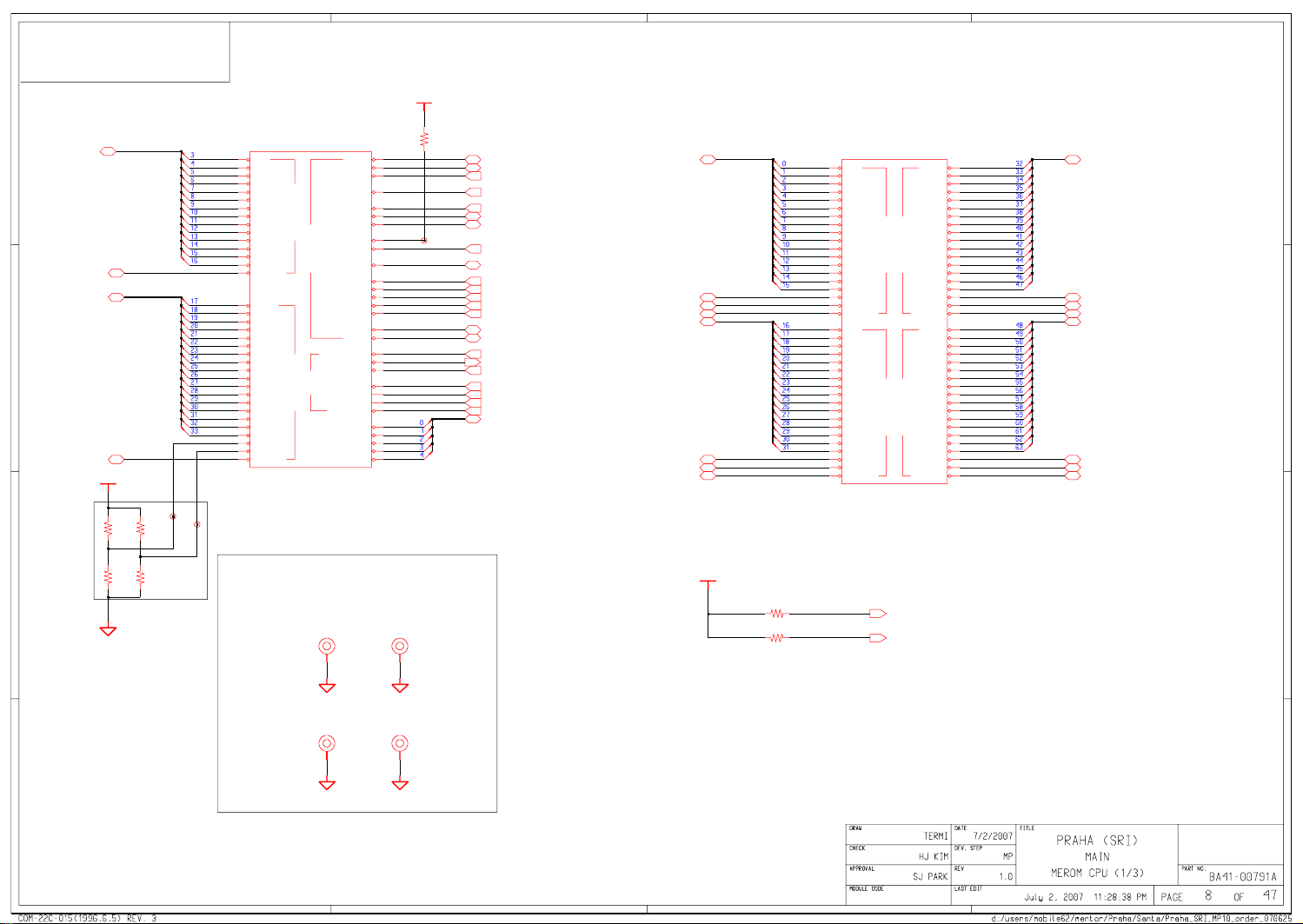

CPU1_A#(16:3)

CPU1_ADSTB0#

CPU1_A#(33:17)

12-D2

12-D2

12-D2

C

CPU1_ADSTB1#

B

12-C2 12-C1

VCCP

R1481KR149

1K

R147

R146

nostuff

1K

1K

nostuff

nostuff

nostuff

Pad for SRI Model

CPU500-1

MEROM-SOCKET

1 / 4

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

AA4

AB2

AA3

V1

005344461

**NOTE

A3*

A4*

A5*

A6*

0

A7*

A8*

A9*

A10*

A11*

A12*

ADDR GROUP

A13*

A14*

A15*

A16*

ADSTB0*

A17*

A18*

A19*

A20*

A21*

A22*

A23*

A24*

A25*

A26*

A27*

A28*

A29*

A30*

A31*

A32*

A33*

A34*

A35*

ADSTB1*

CONTROL

1

ICH

ADDR GROUP

CPU Bracket Hole

MT503

RMNT-38-70-1P

ADS*

BNR*

BPRI*

BR0*

DEFER*

DRDY*

DBSY*

IERR*

INIT*

LOCK*

RESET*

RS0*

RS1*

RS2*

TRDY*

HITM*

A20M*

FERR*

IGNNE*

STPCLK*

LINT0

LINT1

SMI*

REQ0*

REQ1*

REQ2*

REQ3*

REQ4*

HIT*

R169

H1

E2

G5

F1

H5

F21

E1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

A6

A5

C4

D5

C6

B4

A3

K3

H2

K2

J3

L1

56

12-C2

12-C2

12-C2

12-B2 8-B2

12-C2

12-C2

12-C2

19-A4

12-C2

44-C3 12-C2

12-B2

12-B2

12-B2

12-B2

12-B2

12-B2

19-A4

19-A4 8-B2

19-A4

19-A4

19-A4

19-A4

19-A4

12-D2

CPU1_ADS#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_DEFER#

CPU1_DRDY#

CPU1_DBSY#

CPU1_INIT#

CPU1_LOCK#

CPU1_CPURST#

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

CPU1_TRDY#

CPU1_HIT#

CPU1_HITM#

CPU1_A20M#

CPU1_FERR#

CPU1_IGNNE#

CPU1_STPCLK#

CPU1_INTR

CPU1_NMI

CPU1_SMI#

CPU1_REQ#(4:0)

CPU1_D#(15:0)

CPU1_DSTBN0#

CPU1_DSTBP0#

CPU1_DBI0# CPU1_DBI2#

CPU1_D#(31:16)

CPU1_DSTBN1#

CPU1_DSTBP1#

CPU1_DBI1#

12-D1

12-D1

12-D1

12-D1

12-D1

12-C1

12-C1

CPU500-2

MEROM-SOCKET

2 / 4

E22

D0*

F24

D1*

E26

D2*

G22

D3*

F23

D4*

G25

D5*

E25

D6*

E23

D7*

K24

D8*

G24

D9*

J24

D10*

J23

D11*

H22

D12*

F26

D13*

K22

D14*

H23

D15*

J26

DSTBN0*

H26

DSTBP0*

H25

DINV0*

N22

D16*

K25

D17*

P26

D18*

R23

D19*

L23

D20*

M24

D21*

L22

D22*

M23

D23*

P25

D24*

P23

D25*

P22

D26*

T24

D27*

R24

D28*

L25

D29*

T25

D30*

N25

D31*

L26

DSTBN1*

M26

DSTBP1*

N24

DINV1*

005344461

Samsung

VCCP

56

MT502

RMNT-38-70-1P

R180

R167

200

8-C319-A4

12-B2 8-D3

DATA GRP 0

DATA GRP 2

DSTBN2*

DSTBP2*

DINV2*

DATA GRP 1

DATA GRP 3

DSTBN3*

DSTBP3*

DINV3*

CPU1_FERR#

CPU1_BREQ#

D32*

D33*

D34*

D35*

D36*

D37*

D38*

D39*

D40*

D41*

D42*

D43*

D44*

D45*

D46*

D47*

D48*

D49*

D50*

D51*

D52*

D53*

D54*

D55*

D56*

D57*

D58*

D59*

D60*

D61*

D62*

D63*

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

12-D1

12-B1

12-B1

12-B1

12-D1

12-A1

12-A1

12-B1

CPU1_D#(47:32)

CPU1_DSTBN2#

CPU1_DSTBP2#

CPU1_D#(63:48)

CPU1_DSTBN3#

CPU1_DSTBP3#

CPU1_DBI3#

D

C

B

MT500

RMNT-38-70-1P

A

4

Confidential

MT501

RMNT-38-70-1P

3

2

A

SAMSUNG

ELECTRONICS

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

CPU500-3

MEROM-SOCKET

CLK0_HCLK0

CLK0_HCLK0#

C195

270pF

VCCP

R168

C

56

VCCP

R150

1K

1%

R151

2K

1%

nostuff

CPU1_SLP#

CPU1_DPSLP#

CPU1_DPRSTP#

CPU1_DPWR#

CPU1_PWRGDCPU

CPU1_PSI#

CPU1_VID(6:0)

CPU2_THERMDA

CPU2_THERMDC

CPU1_THRMTRIP#

CPU1_BSEL2

CPU1_BSEL1

CPU1_BSEL0

CPU1_VCCSENSE

CPU1_VSSSENSE

B

nostuff

nostuff

nostuff

nostuff

nostuff

R159

R160

R161

R162

1%

R171 1K

7-D1

7-C1

19-A4

12-B2

19-A4 44-C319-D2

42-B4

42-B4

11-C2

11-C2

11-B4

7-B1

7-B1

7-B1

10-C4

10-C4 42-B4

1%

0

1KR172

R185

19-C219-A4

42-B4

54.9

27.4

54.9

27.4

C112 100nF

19-D219-A412-A4

1%

1%

1%

1%

0

R141

Pad for SRI model

GTLREF : Keep the Voltage divider within 0.5"

of the first GTLREF0 pin with Zo=55ohm trace.

Minimize coupling of any switching signals to this net.

COMP0,2(COMP1,3) should be connected with Zo=27.4ohm(55ohm)

trace shorter than 1/2" to their respective Banias socket pins.

GND test points within 100mil of the VCC/VSSsense at the end of the line.

Route the VCC/VSSsense as a Zo=55ohm traces with equal length.

Observe 3:1 spacing b/w VCC/VSSsense lines and 25mil away

A

(preferred 50mil) from any other signal. And GND via 100mil away

from each of the VCC/VSS test point vias.

A22

BCLK0

A21

BCLK1

D7

SLP*

B5

DPSLP*

E5

DPRSTP*

D24

DPWR*

D6

PWRGOOD

AE6

PSI*

AE2

VID_6

AF3

VID_5

AE3

VID_4

AF4

VID_3

AE5

VID_2

AF5

VID_1

AD6

VID_0

D21

PROCHOT*

A24

THRMDA

B25

THRMDC

C7

THERMTRIP*

C21

BSEL2

B23

BSEL1

B22

BSEL0

AD26

GTLREF

Y1

COMP3

AA1

COMP2

U26

COMP1

R26

COMP0

AF7

VCCSENSE

AE7

VSSSENSE

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

Samsung

TEST5

A26

TEST6

0

005344461

R184

H CLK

3 / 4

THERMAL

XDP/ITP SIGNALS

RSVD

ITP DISABLE

VCCP

Confidential

R145

27.4

40.2

R142

150

VCCA_1

VCCA_2

VCCP_1

VCCP_2

VCCP_3

VCCP_4

VCCP_5

VCCP_6

VCCP_7

VCCP_8

VCCP_9

VCCP_10

VCCP_11

VCCP_12

VCCP_13

VCCP_14

VCCP_15

VCCP_16

PREQ*

PRDY*

BPM3*

BPM2*

BPM1*

BPM0*

TCK

TDO

TMS

TRST*

DBR*

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

nostuff

nostuff

R158

R144

475

1%

nostuff

nostuff

B26

C26

K6

J6

M6

N6

T6

R6

K21

J21

M21

N21

T21

R21

V21

W21

V6

G21

AC1

AC2

AC4

AD1

AD3

AD4

AC5

AA6

TDI

AB3

AB5

AB6

C20

R170

D2

F6

D3

D22

M4

N5

T2

V3

B2

C3

CPU1_TDI

9-C2

CPU1_TMS

9-C2

CPU1_TCK

9-C2

CPU1_TRST#

9-C2

VCCP

P1.5V

C199

C184

10nF

10000nF

6.3V

25V

CPU1_TCK

9-A3

CPU1_TDI

9-A3

CPU1_TMS

9-A3

CPU1_TRST#

9-A3

33

7-C320-A420-C3

ITP3_DBRESET#

CPU Core Voltage Table

Active Mode

VID(6:0)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

01

0

0

0

0

0

0

0

0

0

0

0

0

1

0 0.3875 V

0

0

0

1

0

0

0

1

0

0

0

0

1

0

0

1

0

0

1

0

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

0

0

0

1

0

0

1

0

1

0

0

0

1

0

1

1

0

0

1

1

0

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

1

0

0

1

0

0

0

0

1

0

01

0

0

1

0

0

0

1

0

0

0

1

0

0

0

1

1

0

1

0

0

DPRSLPVR

DPRSTP*

PSI2*

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

000

0

0

1

1

1

1

1

Active

0

1

0 or 1

0

0

1

0

1

1

1

0

0

100

0

1

1

1

1

1

0

0

0

1

1

0

1

0

0

1

0

1

0

1

1

0

0

1

0

0

1

1

1

0

0

1

0

1

0

1

1

1

1

0

0

1

0

1

0 1.1750 V

1

1

0

0

0

1

1

0

1

1

0

0

1

0

0

1

1

1

0

0

1

0

1

0

1

1

1

Voltage

1.5000 V

1.4875 V

1.4750 V

1.4625 V

1.4500 V

1.4375 V

1.4250 V

1.4125 V

1.4000 V

1.3875 V

1.3750 V

1.3625 V

1.3500 V

1.3375 V

1.3250 V

1.3125 V

1.3000 V

1.2875 V

1.2750 V

1.2625 V

1.2500 V

1.2375 V

1.2250 V

1.2125 V

1.2000 V

1.1875 V

1.1625 V

1.1500 V

1.1375 V

1.1250 V

1.1125 V

1.1000 V

1.0875 V

1.0750 V

1.0625 V

1.0500 V

1.0375 V

1.0250 V

1.0125 V

Active/Deeper Sleep

Dual Mode Region

VID(6:0)

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

1

0

0

1

0

0

0

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

1

1

1

0

1

0

1

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

0

0

1

1

0

0

1

0

0

1

0

0

1

0

0

0

1

0

1

0

0

1

0

0

1

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

0

1

0

0

1

0

1

1

0

1

DPRSLPVR

DPRSTP*

PSI2*

IMVP-6

1

0

0

1

0

0

0

1

1

1

1

0

1

0

1

1

01

1

1

1

1

1

1

1

0

0

0

0

0

0

0

1

0

0

01

1

0

1

0

0

1

0

1 0.8250 V

1

0

1

0

1

1

0

0

0

0

1

1

0

1

0

1

1

1

1

0

0

1

1

1

1

1

1

1

1

1

0

0

0

0

0

00

0

0

1

0

0

1

0

1

0

0

0

1

0

100.6250 V

1

1

1

0

1

0

0

0

1

0

1

0

1

0

1

0

1

1

1

0

1

1

1

1

1

1

1

1

1

0

0

00

0

Deeper Slp

1

0

0 or 1

Deeper Sleep/Extended Deeper Sleep

Dual Mode Region

VID(6:0)

Voltage

1

1.0000 V

0

1

0.9875 V

0

0.9750 V

1

0.9625 V

0

0.9500 V

0.9375 V

0

0.9250 V

1

1

0.9125 V

0.9000 V

0

1

0.8875 V

0.8750 V

0

1

0.8625 V

0.8500 V

0

1

0.8375 V

0

1

0.8125 V

0.8000 V

0

0.7875 V

1

0.7750 V

0

0.7625 V

1

0

0.7500 V

0.7375 V

1

0.7250 V

0

0.7125 V

1

1

0

0.7000 V

1

0.6875 V

0

0.6750 V

0.6625 V

1

0.6500 V

0

1

0.6375 V

0

1

0.6125 V

0.6000 V

0

1

0.5875 V

0.5750 V

0

1

0.5625 V

0

0.5500 V

0.5375 V

1

0

0.5250 V

0.5125 V

1

0.5000 V

0

0

0

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

*"1111111" : 0V power good asserted.

0

1

0

0

1

1

1

0

0

0

1

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

11

1

1

1

1

1

1

1

1

0

1

1

0

0

0

0

0

1

1

1

0

1

1

1

0

1

1

1

1

1

0

1

1

1

01

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

1

0

0

0

1

0

0

1

1

0

0

11

1

0

0

0

0

1

0

0

0

1

0

0

0

1

1

0

01

1

1

0

0

1

1

0

0

1

1

0

1

1

1

0

1

1

1

1

0

0

0

0

0

1

0

0

1

0

1

1

0

1

0

1

1

0

0

1

0

1

0

1

1

1

0

0

1

1

1

1

0

1

1

0

1

0

1

0

0

1

1

1

1

1

0

1

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

Voltage

1

0.4875 V

0.4750 V

0

0.4625 V

1

0

0.4500 V

0.4375 V0

1

0.4250 V

0

1

0.4125 V

0

0.4000 V

1

0.3750 V

0

1

0.3625 V

0.3500 V

0

0.3375 V

0.3250 V

0

1

0.3125 V

0

0.3000 V

1

0.2875 V

0

0.2750 V

1

0.2625 V

0

0.2500 V

1

0.2375 V

0

0.2250 V

0.2125 V

1

0.2000 V

1

0

1

0.1875 V

0

0.1750 V

0.1625 V

1

0.1500 V

0

0.1375 V

1

0

0.1250 V

0.1125 V

1

0

0.1000 V

0.0875 V

1

0.0750 V

0

1

0.0625 V

0

0.0500 V

0.0375 V

1

0.0250 V

0

1

0.0125 V

0

0.0000 V

11

0.0000 V

0.0000 V

0

0.0000 V

1

0

0.0000 V

1

0.0000 V

0

0.0000 V

0.0000 V

1

*Yonah Processor (2.33 GHz / 800 MHz : TBD)

SAMSUNG

ELECTRONICS

D

C

B

A

4

3

2

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

C

B

CPU1_VCCSENSE

CPU1_VSSSENSE

CHECK BULK CAP USING

IF IT DOUBLED

42-B49-B4

9-B4 42-B4

EC7

330uF

2.5V

OXI

VCCP

nostuff

R140

R143

C172

100nF

10V

Deleted 13 De-cap (Only use 19pcs out of 32)

VCC_CORE

1%100

1%100

C168

22000nF

6.3V

C196

22000nF

6.3V

nostuff

C167

C170

22000nF

22000nF

6.3V

6.3V

20%

20%

20%

C197

22000nF

6.3V

nostuff

20%

20%

20%

C198

22000nF

6.3V

nostuff

C174

22000nF

6.3V

20%

20%

C176

22000nF

6.3V

C169

22000nF

6.3V

20%

20%

C178

22000nF

6.3V

Samsung

C173

100nF

10V

100nF

100nF

C163

100nF

C162

100nF

10V10V 10V10V

C171

C164

Confidential

C165

C166

22000nF

6.3V

20%

20%

C177

22000nF

6.3V

C161

22000nF

6.3V6.3V

C181

22000nF22000nF

20%

20%

20%

C182

22000nF 22000nF

6.3V

6.3V

22000nF

20%

20%

C179 C180

6.3V

D

P21

P24

VSS_135N4VSS_136

VSS_137

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VSS_146

VSS_147

VSS_148

T4

T26

U21

P6

R2

VSS_138P3VSS_139

VSS_140

AE9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

AF9

B10

B12

B14

B15

B17

B18

B20

B7

B9

C10

C12

C13

C15

C17

C18

C9

D10

D12

D14

D15

D17

D18

D9

E10

E12

E13

E15

E17

E18

E20

E7

E9

F10

F12

F14

F15

F17

F18

F20

F7

F9

VSS_143

VSS_144

VSS_145

T1

R5

T23

R22

VSS_141

VCC_CORE

VSS_142

R25

VSS_120

VSS_119

VSS_118

VSS_117

VSS_116

VSS_115

VSS_114

VSS_113

VSS_112

VSS_111

VSS_110

VSS_109

VSS_108

VSS_107

VSS_106

VSS_105

VSS_104

VSS_103

VSS_102

VSS_101

VSS_100

VSS_99

VSS_98

VSS_97

VSS_96

VSS_95

VSS_94

VSS_93

VSS_92

VSS_91

VSS_90

VSS_89

VSS_88

VSS_87

VSS_86

VSS_85

VSS_84

VSS_83

VSS_82

VSS_81

VSS_80

VSS_79

VSS_78

VSS_77

VSS_76

VSS_75

VSS_74

VSS_73

VSS_72

VSS_71

VSS_70

VSS_69

VSS_68

VSS_67

VSS_66

VSS_65

VSS_64

VSS_63

VSS_62

VSS_61

K1

J5

J25

J22

J2

H6

H3

H24

H21

G4

G26

G23

G1

F8

F5

F25

F22

F2

F19

F16

F13

F11

E8

E6

E3

E24

E21

E19

E16

E14

E11

D8

D4

D26

D23

D19

D16

D13

D11

D1

C8

C5

C25

C22

C2

C19

C16

C14

C11

B8

B6

B24

B21

B19

B16

B13

B11

AF8

AF6

AF25

C

B

M25

N23

K23

K26

L21

L24

L3

VSS_121

VSS_122

VSS_123K4VSS_124

VSS_125

VSS_126

A11

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VCC_CORE

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AA7

AA9

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AB7

AB9

AC10

AC12

AC13

AC15

AC17

AC18

AC7

AC9

AD10

AD12

AD14

AD15

AD17

AD18

AD7

AD9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

A10

A12

A13

A15

A17

A18

A20

A7

A9

VSS_163

Y6

Y3

A14

A16

A19

A2

A23

A25

A4

A8

AA11

AA14

AA16

AA19

AA2

AA22

AA25

AB11

AB13

AB16

AB19

AB26

AC11

AC14

AC16

AC19

AC21

AC24

AD11

AD13

AD16

AD19

AD22

AB23

AD25

AE11

AE14

AE16

AE19

AE23

AE26

AF11

AF13

AF16

AF19

AF21

AA5

AA8

AB1

AB4

AB8

AC3

AC6

AC8

AD2

AD5

AD8

AE1

AE4

AE8

AF2

20%

20%

C183

22000nF

6.3V6.3V

VSS_127L6VSS_128M2VSS_129

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

MEROM-SOCKET

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

W1

W4

Y21

Y24

W23

W26

M22

VSS_130

VSS_131M5VSS_132N1VSS_133

CPU500-4

4 / 4

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

V2

V5

U3

U6

V22

V25

N26

VSS_134

VSS_149

VSS_150

U24

A

SAMSUNG

ELECTRONICS

4

3

2 1

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

D

C755

10000nF

6.3V

KBC3_PWRGD

C

FAN5_VDD CPU2_THERMDA

FAN3_FDBACK#

CPU3_THRMTRIP#

TRIP_SET

3.3 * R2 / (R1 + R2) = (T - 75) / 21

So: T = 90’C

11-B2

11-B2

11-B3

3

2

14

Refer To Thermal Sensor Layout Guidelines.

- Place the Thermal Sensor close to a remote diode.

- Keep traces away from high voltage (+12V bus)

- Keep traces away from fast data buses and CRT signal.

- Use recommended trace widths and spacings (10mil)

Thermal Monitor

R746

10K10K

0.47nF

P3.3V_AUX

R725

R727

10K

10K

nostuff

10mil width, 10mil spacing

C194

2.2nF

2

1

3

Between CPU and MCH

Must be apart from Heatsink

KBC3_THERM_SMDATA

34-B3

34-C3

KBC3_THERM_SMCLK

21-B1

THERM3_ALERT#

THERM_STP#

11-C143-C3

9-C4

CPU2_THERMDC

9-C4

MMBT3904

Q27

P3.3V

P3.3V_AUXP5.0V

C756

100nF

10V

34-C420-D3

C738

10000nF

6.3V

SHORT507

P3.3V_AUX

R723

R1

200K

1%

R724

R2

56K

1%

nostuff

C736

100nF

10V

R745

49.9

U512

1%

EMC2102

1

VDD_3V

24

VDD_5V_1

27

VDD_5V_2

14

POWER_OK

16

0

RESET#

10

FAN_MODE

25

FAN_1

26

FAN_2

28

TACH

13

THERMTRIP#

9

SHDN_SEL

11

TRIP_SET

8

NC_1

15

NC_2

21

NC_3

SMDATA

SMCLK

ALERT#

SYS_SHDN#

DN1

DP1

DN2

DP2

DN3

DP3

CLK_SEL

CLK_IN

GND

THRM_PAD

SMBUS Address "7A"

R747

22

23

19

12

2

3

4

5

6

7

17

18

20

29

C737

- Place a ground plane under the traces.

- Use guard traces flanking DXP and DXN and connecting to GND

OTP (NOSTUFF)

MICOM_P3.3V

nostuff

nostuff

11-C2

nostuff

THERM_STP#

R600

0

VTEMP

3

GND

2

HYST

15

LM26CIM5X-TPA

U507

C629

100nF

10V

V+

4

OS*

43-C3

D

C

Samsung

B

CPU1_THRMTRIP#

9-C4

A

4

VCCP

MMBT3904

Q528

Confidential

VCCP

R179

56

MMBT3904

Q527

1

1

R726

2K

1%

R683

2K

1%

P3.3V

R685

10K

nostuff

nostuff

nostuff

32

CHP3_SBTHRMTRIP#

20-C3

32

3

11-C4

CPU3_THRMTRIP#

2

Line Width = 20 mil

FAN5_VDD

FAN3_FDBACK#

FAN Control

P3.3V

R578

10K

11-C4

11-C4

C596

10000nF

6.3V

J2

HDR-4P-SMD

1

2

3

4

5

MNT1

6

MNT2

FAN Connector

3711-000922

B

A

SAMSUNG

ELECTRONICS

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

D

C

B

A

M1

HEAD

DIA

LENGTH

For heat pipe

CPU1_SLP#

M2

HEAD

DIA

LENGTH

CHP3_SUSSTAT#

KBC3_NBPWRGD

P1.8V

9-D4 19-A4 19-D2

SHORT8

Q16

3

CPU1_A#(33:3)

CPU1_REQ#(4:0)

CPU1_ADSTB0#

CPU1_ADSTB1#

CPU1_ADS#

CPU1_BNR#

CPU1_BPRI#

CPU1_DEFER#

CPU1_DRDY#

CPU1_DBSY#

CPU1_LOCK#

CPU1_CPURST#

CPU1_RS2#

R73

4.7K

nostuff

R71

1K

1%

nostuff

CPU1_RS1#

CPU1_RS0#

CPU1_BREQ#

CPU1_TRDY#

CPU1_HIT#

CPU1_HITM#

CPU1_DPWR#

CHP3_NBRST#

P1.8V

B23

BLM18PG181SN1

C122

2200nF

10V

VCCP

P1.8V_AUX

20-D3 34-B3

Samsung

34-C3

0

Q15

RHU002N06

VCCP

R76

4.7K

Confidential

1

3

2

Q17

MMBT3904

0

R72

nostuff

G

D

3

P1.2V

1

S

2

B22

BLM18PG181SN1

C119

2200nF

10V

P3.3V_NB

R82

20K

1%

MMBT3904

2

3

nostuff

nostuff

1

R77

2.2K

8-C4 8-D4

8-C3

8-C4

8-C4

8-D3

8-D3

8-D3

8-D3

8-D3

8-D3

8-C3

8-C3 44-C3

8-C3

8-C3

8-C3

8-D38-B2

8-C3

8-C3

8-C3

9-C4

19-C1

R588

VCCP

R108

R110

61.9

1%

R109

C607

127

1000nF

1%

6.3V

PLACE CLOSE TO NB

USE 10/10MIL WIDTH/SPACE

R152

nostuff

49.9

24.9 1%

C606

270pF

0

1

2

3

4

0

1%

2

U506-1

RS600ME

R86

4.7K

M42

M44

M38

W39

W42

M39

H42

AC39

W43

AA40

AC43

AA42

AA38

AC42

AD36

AD38

AA36

AD42

AD40

AD44

AD43

AA44

U46

R46

M47

H44

M46

M45

R47

R45

AT9

D10

AT5

AT4

AA35

W35

C17

K42

T39

P42

T43

P38

P44

P36

V40

V42

P39

K44

K40

T42

V44

V36

V38

K46

P45

K25

L45

L47

T45

K47

P46

T47

F10

B32

A31

V35

A32

A20

1 OF 5

CPU_A3#

CPU_A4#

CPU_A5#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A15#

CPU_A16#

CPU_REQ0#

CPU_REQ1#

CPU_REQ2#

CPU_REQ3#

CPU_REQ4#

CPU_ADSTB0#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPUA32#_NC

CPUA33#_NC

CPU_ADSTB1#

CPU_RESERVED

CPU_ADS#

CPU_BNR#

CPU_BPRI#

CPU_DEFER#

CPU_DRDY#

CPU_DBSY#

CPU_LOCK#

CPU_CPURST#

CPU_RS2#

CPU_RS1#

CPU_RS0#

CPU_BR0#

CPU_TRDY#

CPU_HIT#

CPU_HITM#

CPUDPWR#

SUS_STAT#

SYSRESET#

POWERGOOD

CPU_COMP_P

CPU_COMP_N

THERMALDIODE_P

THERMALDIODE_N

IOPLLVDD18

IOPLLVDD12

IOPLLVSS

CPUSLP#_RESERVED1

CPU_VREF

TESTMODE

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

ADDR.GROUP 0

ADDR.GROUP 1

P-4 AGTL + I/F

MISC CONTROL

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_DSTB0N#

CPU_DSTB0P#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_DSTB1N#

CPU_DSTB1P#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_DSTB2N#

CPU_DSTB2P#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

CPU_DSTB3N#

CPU_DSTB3P#

H46

G47

K45

G45

H45

G46

F45

F47

C46

A44

D46

C45

D47

B44

A43

B45

E47

E46

E45

E40

F44

E42

F40

H40

D44

D42

D40

E38

F36

E36

J34

F34

H38

D32

E34

K36

J38

J36

J32

F32

K32

D29

M29

K30

F30

E30

M27

F27

K27

D25

E27

J27

J25

F25

J30

H29

F29

C37

B40

B43

C42

C43

A42

B38

A41

C40

A38

C36

B36

A37

C38

B34

C34

A36

B41

C41

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

VCCP

1

CPU1_D#(63:0)

D

C

B

8-C2

8-C2

8-C2

8-B2

8-C2

8-C2

8-C1

8-C1

8-C1

8-B1

8-C1

8-C1

8-C28-D18-D2 8-C1

CPU1_DBI0#

CPU1_DSTBN0#

CPU1_DSTBP0#

CPU1_DBI1#

CPU1_DSTBN1#

CPU1_DSTBP1#

CPU1_DBI2#

CPU1_DSTBN2#

CPU1_DSTBP2#

CPU1_DBI3#

CPU1_DSTBN3#

CPU1_DSTBP3#

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

A

SAMSUNG

ELECTRONICS

4

3

2

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3 2

1

D

U506-2

RS600ME

2 OF 5

C3

GFX_RX0P

C2

GFX_RX0N

H5

GFX_RX1P

H4

GFX_RX1N

K8

GFX_RX2P

K6

GFX_RX2N

M8

GFX_RX3P

M6

GFX_RX3N

M5

GFX_RX4P

M4

GFX_RX4N

P9

GFX_RX5P

P8

GFX_RX5N

P4

GFX_RX6P

P5

GFX_RX6N

T6

GFX_RX7P

T5

GFX_RX7N

T9

GFX_RX8P

T10

GFX_RX8N

V5

GFX_RX9P

V6

GFX_RX9N

V9

AA10

AC10

AK10

AM10

AA6

AA5

AA9

AC5

AC6

AC9

AE6

AE5

AK6

AK5

AM2

AM1

AG5

AG6

AK9

AM5

AM6

AM9

AU3

AV3

V10

AJ2

AJ1

A5

B4

A6

B6

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX3P

SB_RX3N

SB_RX2P

SB_RX2N

SB_RX1P

SB_RX1N

SB_RX0P

SB_RX0N

GFX_CLKP

GFX_CLKN

SB_CLKP

PCIE I/F

PCIE CLK

C

PEX1_MINRX1P

PEX1_MINRX1N

PEX1_LANRX2P

PEX1_LANRX2N

PEX1_EXPRX3P

PEX1_ARX3P

PEX1_ARX3N

PEX1_ARX2P

PEX1_ARX2N

PEX1_ARX1P

B

PEX1_ARX1N

PEX1_ARX0P

PEX1_ARX0N

CLK1_NBSRC

CLK1_NBSRC#

CLK1_PCIEICH

CLK1_PCIEICH#

29-C4

29-C4

35-C4

35-C4

27-B4

27-B4

19-D4

19-D4

19-D4

Samsung

19-D4

19-D4

19-D4

19-D4

7-C1

7-C1

7-C1

7-C1

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX3P

SB_TX3N

SB_TX2P

SB_TX2N

SB_TX1P

SB_TX1N

SB_TX0P

SB_TX0N

PCE_CALI

PCE_CALRN

PCE_CALRPSB_CLKN

D2

E1

F2

F1

G2

G1

H2

K1

L2

L1

M2

M1

P2

R1

T2

T1

U2

U1

V2

W1

Y2

Y1

AA2

AA1

AB2

AC1

AD2

AD1

AE2

AE1

AF2

AG1

AG9

AG10

AK2

AL1

AH2

AH1

C60 100nF

AE9

AE10

C58 100nF

AN2

AN1

AP2

AT1

AU2

AU1

AV1

AV2

BA3

BA2

BA1

C61 100nF

100nFC62

100nFC59

100nFC57

100nF

C63

100nF10V

C64

100nF

C65

100nF

C66

C68

C67

100nF

C69

C70

1.47K

R577

2K

R575

562

R576

10V

10V

10V

10V

10V

10V

10V

10V

10V

10V100nF

10V100nF

10V

10V100nF

1%

1%

1%

29-C4

29-C4

35-C4

35-C4

27-B4

27-B4

19-C4

19-C4

19-C4

19-C4

19-C4

19-C4

19-D419-D4

19-D4

PEX1_MINTX1P

PEX1_MINTX1N

PEX1_LANTX2P

PEX1_LANTX2N

PEX1_EXPTX3P

PEX1_EXPTX3NPEX1_EXPRX3N

PEX1_ATX3P

PEX1_ATX3N

PEX1_ATX2P

PEX1_ATX2N

PEX1_ATX1P

PEX1_ATX1N

PEX1_ATX0P

PEX1_ATX0N

P1.2V

D

C

B

PEX1_MIN

Confidential

A

4

3

PEX1_LAN

PEX1_EXP

Mini Card I/F

LOM I/F

Express Card I/F

A

SAMSUNG

ELECTRONICS

12

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

MEM1_ADQ(63:0)

17-D4

3

6

0

7

5232

1

8

4

3

9

13

11

15

16

10

17

14

12

25

26

22

23

20

19

27

24

35

32

37

33

29

31

30

41

40

36534

39

38

2

48

42

44

43

51

50

46

45

49

52

47

60

555953

54

62

63

57

56

61

58

1

D

C

B

MEM1_AMA(14:0)

MEM1_ABS0

MEM1_ABS1

MEM1_ABS2

MEM1_ADM(7:0)

MEM1_ADQS(7:0)

MEM1_ADQS#(7:0)

CLK1_AMCLK1#

CLK1_AMCLK1

CLK1_AMCLK2#

CLK1_AMCLK2

MEM1_ACKE0

MEM1_ACKE1

MEM1_ACS0#

MEM1_ACS1#

MEM1_AODT0

MEM1_AODT1

MEM1_AWE#

MEM1_ACAS#

MEM1_ARAS#

MEM1_REF

R599

nostuff

17-D4

17-C4 18-C4

17-B4

17-B4

17-A4

17-C4

17-C4

17-C4

17-C4

17-C4 18-D4

17-C4 18-D4

17-B4

17-B4 18-C4

17-B4 18-C4

0

18-C4

18-C417-C4

18-C417-C4

18-D417-C4

18-D417-C4

18-D4

18-D417-B4

18-C417-C4

R74

100

1%

nostuff

nostuff

R153

100

1%

P1.8V_AUX

R597

1K

1%

R598

1K

1%

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

To reduce EMI noise

Nearby RS600ME

C622

100nF

10V

C623

100nF

10V

BE42

BF36

BG36

BE34

BF34

BE33

BF33

BE32

BG33

BG32

BE46

BE31

BF31

AV45

BF30

BD46

BD47

BE30

BG12

BE17

AN45

AH47

AD45

BE12

BE18

AM46

AG47

AC46

BF12

BF18

AM47