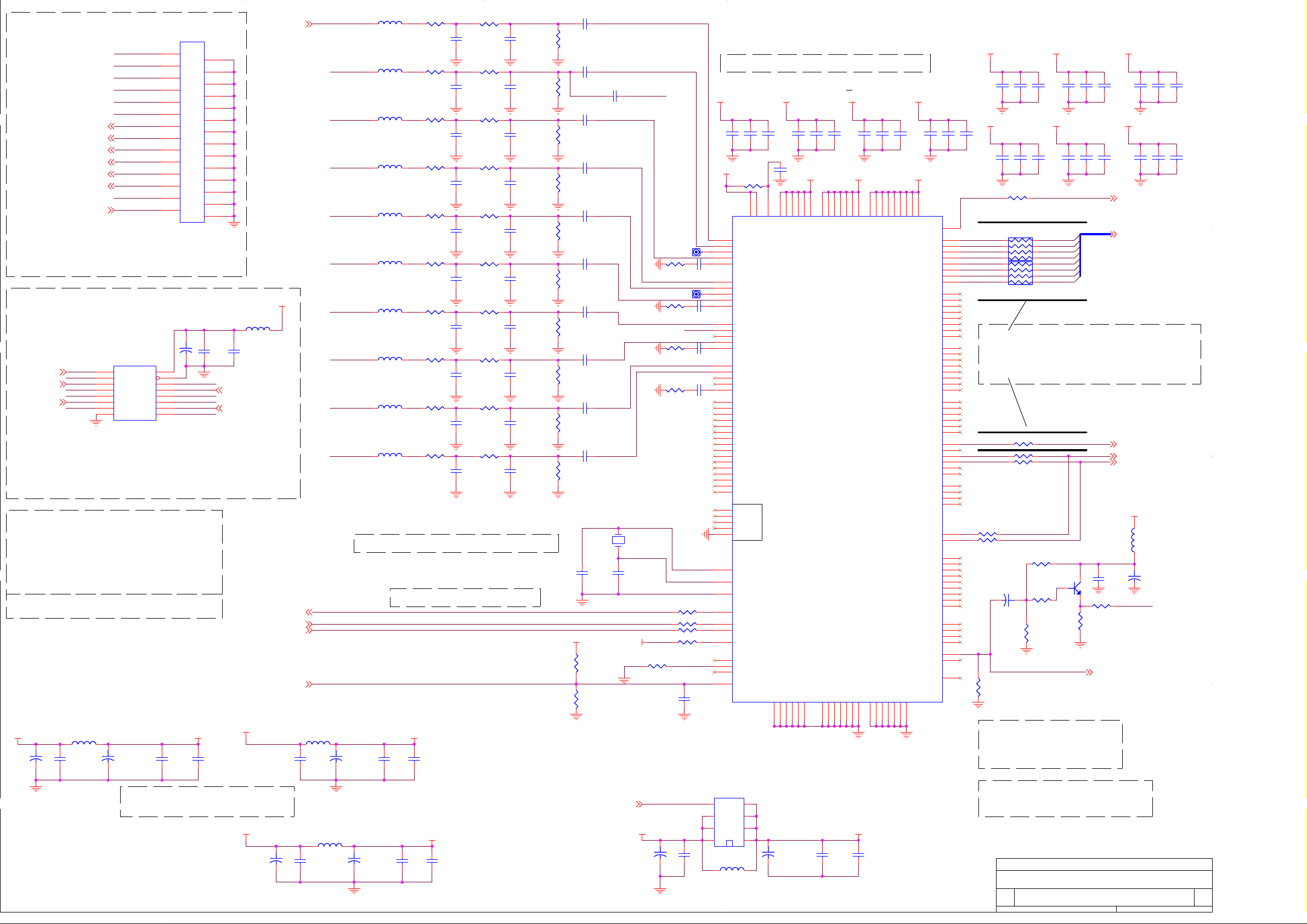

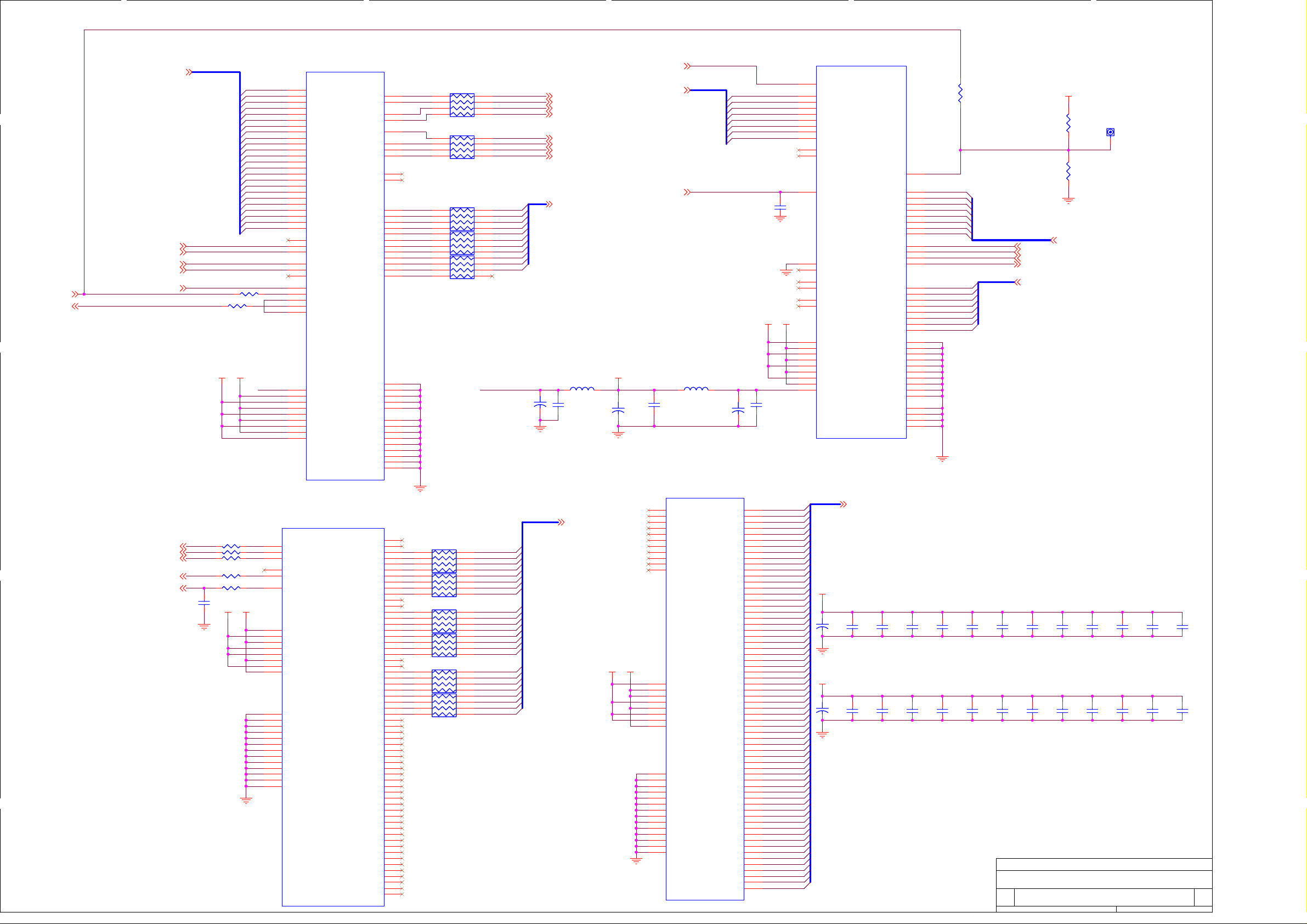

Page 1

5

SDA_12,3,4,11

SCL_12,3,4,11

FB22

FB22

BLM18AG471SN1

BLM18AG471SN1

C340

C340

100nF

100nF

VD1_SY/CV_COPY

VD1_RST_N

VD1 INPUT CON

J18

J18

VD1_SC

VD1_SY/CV

F_R/C

F_G

F_B

D D

PCB:

Video Signals in flat cable.

Need Shield GND between each wire.

VD1_Y4

VD1_Pb4

VD1_Pr4

CVBS_AUX3

AV1_L13

AV1_R13

F_LOUT13

F_FB

VD1_Y

VD1_Pb

VD1_Pr

CVBS_AUX

AV1_L

AV1_R

H1_VOUT

F_LOUT

28

26

24

22

20

18

16

14

12

10

8

6

4

2

28

26

24

22

20

18

16

14

12

10

8

6

4

2

CON28A

CON28A

27

27

25

25

23

23

21

21

19

19

17

17

15

15

13

13

11

11

9

9

7

7

5

5

3

3

1

1

TELETEXT RBG / F.SCART RGB Select

+

C199

+

C C

TTX_SEL11

VD1_TTX_B2

VD1_TTX_G2

TTX_SEL

F_B

VD1_TTX_B

VD1_B

F_G VD1_FB

VD1_TTX_G

VD1_G

U30

U30

FSAV330M

FSAV330M

1

S

2

1B1

3

1B2

4

1A

5

2B1

6

2B2

7

2A

GND83A

C199

ECBp10uF/10V

ECBp10uF/10V

16

VCC

15

EN

14

4B1

13

4B2

12

4A

11

3B1

10

3B2

9

F_FB

VD1_TTX_FB

F_R/C

VD1_TTX_R

VD1_R/C

C198

C198

100nF

100nF

VD1_SY/CV_COPY4

FB30

FB30

BLM18AG471SN1

BLM18AG471SN1

C410

C410

1nF

1nF

VD1_TTX_FB 2

VD1_TTX_R 2

+5V

PCB: Signal routing to/from the IC should be fine-tuned.

SW: TTX_SEL=0 SCART SELECTED, TTX_SEL=1 TV TEXT SELECTED

HW:

Check for 1Vp-p video input signal.

Video in the SAA7117 inputs is 0.64V.

If not change input resistor value

from NC to apropriate value.

SW: I2C BUS SLAVE ADDERESS : 0x40, 0x48

B B

PCB: See additional notes*

FB24

+3Va

+

+

ECBp10uF/10V

ECBp10uF/10V

C142

C142

FB24

BLM18AG471SN1

BLM18AG471SN1

C376

C376

100nF

100nF

+

+

C111

C111

ECBp10uF/10V

ECBp10uF/10V

C369

C369

100nF

100nF

C359

C359

100nF

100nF

SAA7113_CLK3

VD1_RST_N11

+1.8V

4

L5

3.3uHL53.3uH

VD1_Y

L8

3.3uHL83.3uH

VD1_SY/CV

L7

3.3uHL73.3uH

VD1_R/C

L13

L13

3.3uH

3.3uH

VD1_Pr

L10

L10

3.3uH

3.3uH

VD1_SC

L6

3.3uHL63.3uH

VD1_G

L12

L12

3.3uH

3.3uH

VD1_FB

L11

L11

3.3uH

3.3uH

VD1_B

L14

L14

3.3uH

3.3uH

VD1_Pb

L9

3.3uHL93.3uH

PCB: Put Xtal Capacitors' GND close to pin A4.

SAA7113_CLK

+

+

C102

C102

ECBp10uF/10V

ECBp10uF/10V

C334

C334

100nF

100nF

R15775R157

75

R16075R160

75

R15975R159

75

R16575R165

75

R16275R162

75

R15875R158

75

R16475R164

75

R16375R163

75

R16675R166

75

R16175R161

75

C172

C172

82pF

82pF

C175

C175

82pF

82pF

C174

C174

82pF

82pF

C180

C180

82pF

82pF

C177

C177

82pF

82pF

C173

C173

82pF

82pF

C179

C179

82pF

82pF

C178

C178

82pF

82pF

C181

C181

82pF

82pF

C176

C176

82pF

82pF

R140

R140

120

120

R143

R143

120

120

R142

R142

120

120

R148

R148

120

120

R145

R145

120

120

R141

R141

120

120

R147

R147

120

120

R146

R146

120

120

R149

R149

120

120

R144

R144

120

120

PCB: Put R232 close to the IC

VDDA1.8VDDA3.3

C337

C337

100nF

100nF

C155

C155

100pF

100pF

C158

C158

100pF

100pF

C157

C157

100pF

100pF

C163

C163

100pF

100pF

C160

C160

100pF

100pF

C156

C156

100pF

100pF

C162

C162

100pF

100pF

C161

C161

100pF

100pF

C164

C164

100pF

100pF

C159

C159

100pF

100pF

R124

R124

470

470

R121

R121

470

470

R123

R123

240

240

R129

R129

470

470

R126

R126

470

470

R122

R122

470

470

R128

R128

470

470

R127

R127

470

470

R130

R130

470

470

R125

R125

470

470

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

+3V

R431

R431

4k7

4k7

R255

R255

4k7

4k7

C114

C114

22nF

22nF

C118

C118

22nF

22nF

C116

C116

22nF

22nF

C123

C123

22nF

22nF

C120

C120

22nF

22nF

C115

C115

22nF

22nF

C122

C122

22nF

22nF

C121

C121

22nF

22nF

C124

C124

22nF

22nF

C119

C119

22nF

22nF

C332

C332

47pF

47pF

3

1 2

YIN

C117

C117

22nF

22nF

TP25 AI13TP25 AI13

R228 47R228 47

TP24 AI23TP24 AI23

R113 47R113 47

R112 47R112 47

R237 47R237 47

X4

X4

24.576 MHz / fundemental

24.576 MHz / fundemental

1 2

C318

C318

47pF

47pF

R232 NCR232 NC

R97 22R97 22

R99 22R99 22

+3V

R430 4.7KR430 4.7K

R101 10KR101 10K

C88NCC88

NC

PCB: Update capacitors amount after PCB layout.

VDDA1.8 VDDD1.8

C96

C96

270pf

270pf

VDDA1.8

J2

K1

1

K2

C314 22nFC314 22nF

1

C351 22nFC351 22nF

YIN

C350 22nFC350 22nF

N14

N13

B13

B14

C13

C12

A12

B12

A13

C14

D13

P13

P10

L10

M13

L3

K3

G4

G3

H2

J3

H1

E3

F2

F3

G1

F1

B1

D2

D1

E1

D3

N3

C4

C3

B2

D6

A5

B5

B6

C6

A3

B4

A4

A2

N9

N6

P3

N4

1 2

1 2

1 2

1 2

C360 22nFC360 22nF

C101

C101

680pf

680pf

R234

R234

3R3

3R3

P2

AI11

AI12

AI13

AI14

AI1D

AI21

AI22

AI23

AI24

AI2D

AI31

AI32

AI33

AI34

AI3D

AI41

AI42

AI43

AI44

AI4D

DMC17

DNC16

DNC15

DNC12

DNC11

DNC10

DNC9

DNC8

DNC7

DNC6

DNC5

DNC4

DNC3

DNC2

DNC1

DNC0

TMS

TDO

TDI

TCK

TRSTN

XTALO

XTALI

VSS(xtal)

XTOUT

SDA

SCL

RTCO

FSW

TESTCLK

GPIN

CE

VDD3.3

C302

C302

C305

C305

270pf

270pf

680pf

680pf

VDDD1.8

C361

C361

C309

C309

C325

C325

C301

C301

C312

C312

C304

M11

VSSD5

L11

270pf

270pf

VDD3.3

VDDD1M4VDDD3M8VDDD5

VSSD1

VSSD3

L4

L8

M3

VDDA0

VSSA0

M2

C304

680pf

680pf

K4

J4

3.3nF

3.3nF

270pf

270pf

680pf

680pf

3.3nF

3.3nF

C344

C344

100nF

100nF

C10

C8

F12

B3

N2

VDDD8

VDDD10

VDDD12

VDD(xtal)

VDDA_A18

VDDA_C18

VSSD8

VSSD12

VSSD10

VSSD7

D7

F11

D10

G11

C9

C5

D12

M5

M9

H12

VDDD4

VDDD7

SAA7117AE/V2

SAA7117AE/V2

VSSD2

VSSD4

L5

L9

VDDD2

J12

VDDD9

VDDD6

VDDD11

VDDD13

U23

U23

VSSD11

VSSD9

VSSD13

VSSD6

D9

D5

J11

D11

L1

VDDA1A

VSSA1

VSSA2

H3

C300

C300

3.3nF

3.3nF

J1

F4

VDDA2H4VDDA1

VDDA3

VDDA2A

VSSA4

VSSA3E4AGND

AGNDA

L2

C1

VDD3.3

VDDA3.3VDDD1.8

G2

D4

VDDA4

VDDA3A

ADTEST9

ADTEST8

ADTEST7

ADTEST6

ADTEST5

ADTEST4

ADTEST3

ADTEST2

ADTEST1

RSTOUTN

C2

C319

C319

270pf

270pf

E2

INT_A

VDDA4A

IPD7

IPD6

IPD5

IPD4

IPD3

IPD2

IPD1

IPD0

XPD7

XPD6

XPD5

XPD4

XPD3

XPD2

XPD1

XPD0

HPD7

HPD6

HPD5

HPD4

HPD3

HPD2

HPD1

HPD0

XCLK

XDQ

XRH

XRV

XTRI

XRDY

ICLK

IDQ

IGPH

IGPV

ITRI

ITRDY

IGP0

IGP1

LLC

LLC2_54

RTSO

RTS1

AMCLK

ASCLK

ALRCLK

AMXCLK

AOUT2

AOUT1

C299

C299

C308

C308

680pf

680pf

3.3nF

3.3nF

VDD3.3

P9

IPD7

K11

IPD6

J13

IPD5

J14

IPD4

H13

IPD3

H14

IPD2

H11

IPD1

G12

IPD0

G14

C11

A11

B10

A10

B9

A9

B8

A8

G13

F14

F13

E14

E12

E13

E11

D14

A7

B7

C7

D8

B11

A6

M14

L13

K12

K14

L12

N12

L14

K13

P4

N5

M10

N10

P6

M6

L6

N7

P7

L7

M7

P8

N8

P11

N11

P12

M12

N1

M1

P5

PCB:

1. Place GND trace at both data bus sides.

Connect GND trace to GND plane with multiple vias.

2. Place GND trace at both clock sides.

Connect GND trace to GND plane with multiple vias.

R453 47RR453 47R

R454 47RR454 47R R238

C112

C112

ECBp10uF/10V

ECBp10uF/10V

R399NCR399

NC

PCB:

VD1_CCD_V trace should

be in daisy chain

C328

C328

C287

C287

270pf

270pf

680pf

680pf

R10047R100

47

RP22

RP22

7 8

5 6

3 4

1 2

7 8

5 6

1 2

3 4

RP21

RP21

R95 47R95 47

R94 47R94 47

R93 47R93 47

+

+

VDDA3.3

C291

C291

C336

C336

C323

270pf

270pf

VDDA3.3

C324

C324

270pf

270pf

B

Q19

Q19

BC848B

BC848B

C323

680pf

680pf

C339

C339

680pf

680pf

V_IN[0..7]

C

E

R248

R248

470

470

3.3nF

3.3nF

C313

C313

3.3nF

3.3nF

47x4

47x4

V_IN7

V_IN6

V_IN5

V_IN4

V_IN3

V_IN2

V_IN1

V_IN0

47x4

47x4

R238

6.8K

6.8K

12

R23982R239

82

R240

R240

10K

10K

VDDA3.3

C320

C320

3.3nF

3.3nF

VDDA3.3

C109

C109

3.3nF

3.3nF

VD1_INT_N 11

V_IN[0..7] 6

VCLK 6

VD1_CCD_HS 2

VD1_CCD_VS 2

C377

C377

100nF

100nF

H1_VOUT

R25068R250

68

VD1_CCD_V 2

C322

C322

C352

C352

680pf

680pf

270pf

270pf

C321

C321

C343

C343

270pf

270pf

680pf

680pf

+5V

FB25

FB25

BLM18AG471SN1

BLM18AG471SN1

+

+

C149

C149

ECBp10uF/10V

ECBp10uF/10V

C333

C333

3.3nF

3.3nF

C327

C327

3.3nF

3.3nF

SI4431

PCB: Place 100nF capacitors near

A A

http://arizanotlari.com

SAA7117

5

+1.8V

C65

C65

ECBp10uF/10V

ECBp10uF/10V

+

+

FB17

FB17

BLM18AG471SN1

BLM18AG471SN1

C282

C282

100nF

100nF

+

+

C76

C76

ECBp10uF/10V

ECBp10uF/10V

4

C297

C297

100nF

100nF

VDDD1.8

C298

C298

100nF

100nF

LED1_N

3 2 1

LED1_N

+3V

+

+

ECBp10uF/10V

ECBp10uF/10V

C58

C58

C280

C280

100nF

100nF

SI4431

G4D

3

S

D

2

S

D

1

S

D

U39

U39

FB16

FB16

BLM18AG471SN1

BLM18AG471SN1

5

6

7

8

+

+

C70

C70

ECBp10uF/10V

ECBp10uF/10V

C288

C288

100nF

100nF

VDD3.3

C292

C292

100nF

100nF

HW/SW: AOUT1 available on SAA7119.

AOUT2 available on SAA7117.

PROFILO TELRA A.S.

PROFILO TELRA A.S.

PROFILO TELRA A.S.

Title

Title

Title

http://arizanotlari.com

http://arizanotlari.com

http://arizanotlari.com

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Video Decoder to PortB

Video Decoder to PortB

Video Decoder to PortB

112Monday, December 05, 2005

112Monday, December 05, 2005

112Monday, December 05, 2005

of

of

of

1.1

1.1

1.1

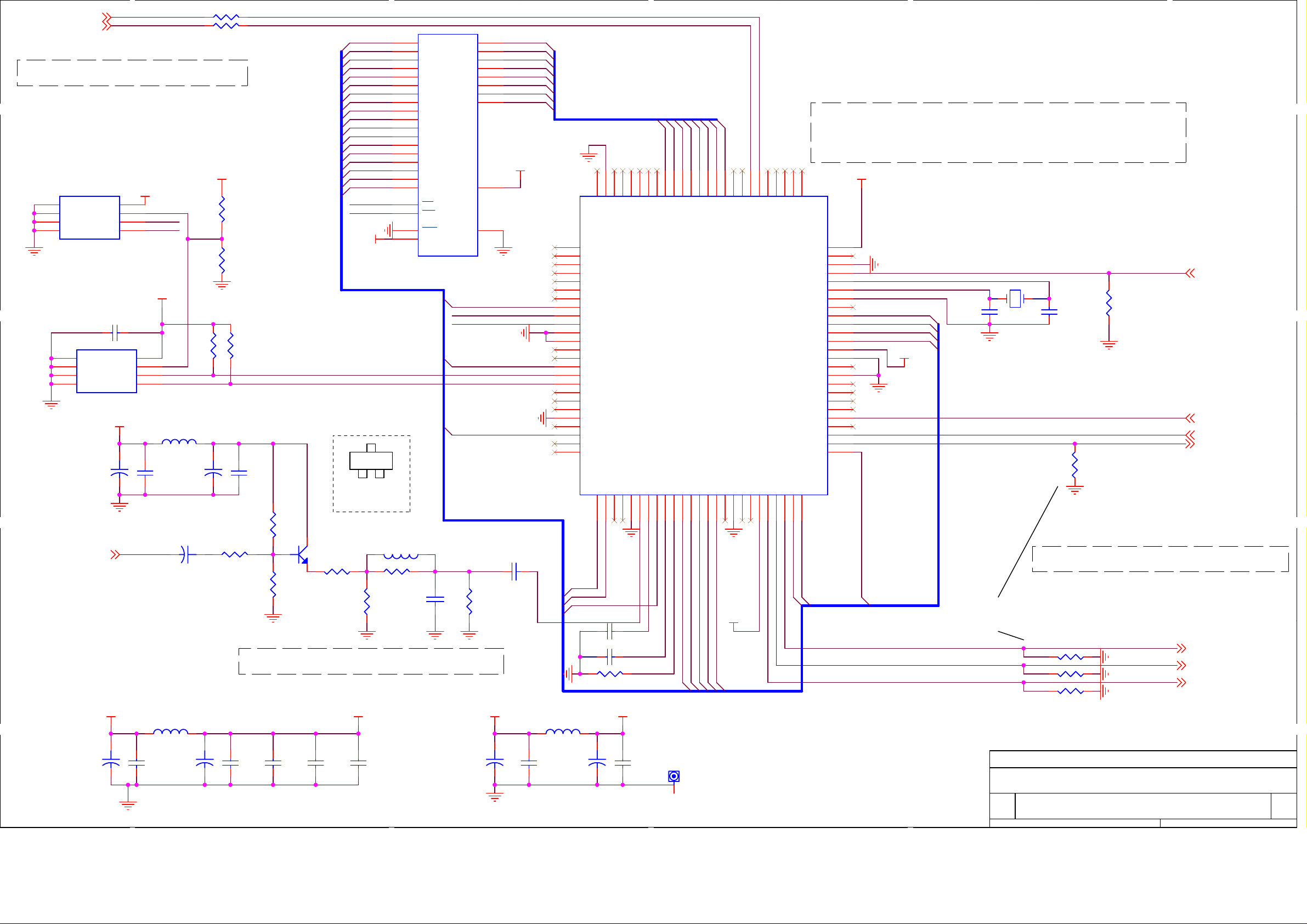

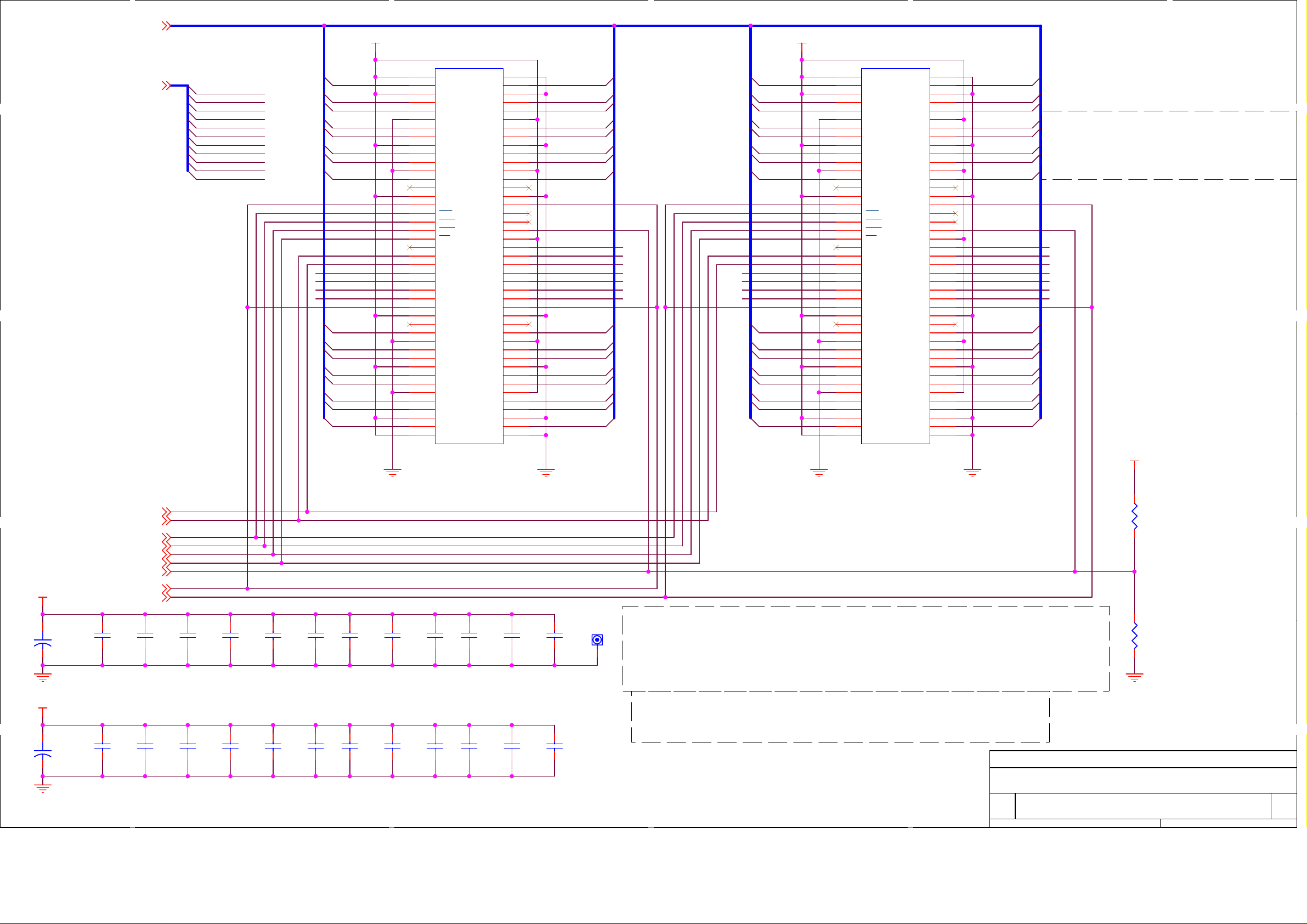

Page 2

5

SCL_11,3,4,11

SDA_11,3,4,11

R89 22R89 22

R88 22R88 22

SW: I2C BUS SLAVE ADDRESS: 0x60

D D

+3V

U37

U37

1

NC

2

NC

3

NC

GND4SDA

C C

1

2

3

C125

C125

ECBp10uF/10V

ECBp10uF/10V

VCC

WP

SCL

ST24C02B in So8

ST24C02B in So8

C283 100nFC283 100nF

U18

U18

NC

NC

NC

GND4SDA

ST24C02B in DIP8

ST24C02B in DIP8

B B

VD1_CCD_V1

+3V

8

7

6

5

VCC

WP

SCL

+5V

+

+

ECBp10uF/10V

ECBp10uF/10V

LM_SCL

LM_SDA

+3V

8

7

6

5

C372

C372

100nF

100nF

C98

C98

R256NCR256

NC

R257NCR257

NC

R217

R217

4.7K

4.7K

FB19

FB19

BLM18AG471SN1

BLM18AG471SN1

+

+

C105

C105

ECBp10uF/10V

ECBp10uF/10V

+

+

R229 3.9KR229 3.9K

Group delay

filter

Circuit

R219

R219

4.7K

4.7K

LM_SCL

LM_SDA

C316

C316

100nF

100nF

HW:

+3VTT

BE

BC848B

R230

R230

47K

47K

C

Q16

Q16

BC848B

E

BC848B

R103

R103

100

100

B

R226

R226

47K

47K

Video input signal 1Vptp Typical

TTX_A0

TTX_A1

TTX_A2

TTX_A3

TTX_A4

TTX_A5

TTX_A6

TTX_A7

TTX_A8

TTX_A9

TTX_A10

TTX_A11

TTX_A12

TTX_A13

TTX_A14

TTX_A15

TTX_A16

TTX_A17

TTX_RD_N

TTX_WR_N

TTX_A[0..17]

C

L1 10uHL1 10uH

R108 330R108 330

R107

R107

470

470

4

TTX_D0

20

A0

19

A1

18

A2

17

A3

16

A4

15

A5

14

A6

13

A7

3

A8

2

A9

31

A10

1

A11

12

A12

4

A13

U20

A14

A15

A16

A17

OE

WE

CS1

CS2

U20

C91

C91

150pF

150pF

11

7

10

9

32

5

30

6

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

VCC

GND

21

22

23

25

26

27

28

29

8

24

TTX_A14

TTX_RD_N

TTX_WR_N

TTX_A7

TTX_A6

R109

R109

10K

10K

TTX_D1

TTX_D2

TTX_D3

TTX_D4

TTX_D5

TTX_D6

TTX_D7

HY62U8200B

HY62U8200B

+3VTT

C92

C92

100nF

100nF

1

P2-7/PWM6

2

P3_0/ADC0

3

NC

4

P3_1/ADC1

5

P3_2/ADC2

6

P3_3/ADC3

7

NC

8

A14

9

RD_N

10

WR_N

11

VSSC

12

VSSP

13

P0_5

14

NC

15

A7

16

SCL_NVRAM

17

SDA_NVRAM

18

P0_2

19

NC

20

NC

21

VPE

22

P0_3

23

A6

24

P0_4

25

NC

C103 100nFC103 100nF

R110 24K %1R110 24K %1

TTX_D[0..7]

99

98

100

VSSC

P2-0/TPWM

A526A427P0_628P0_729VSSA30VCBS031VCBS132A15_BK33SYNC_FILTER34IREF35A1336A1237A338A239A140FRAME41VPE42COR_N43NC44VDDA45B46G47R48A049RAMBK1

TTX_A4

TTX_A5

3

TTX_D5

TTX_D4

TTX_D3

TTX_D6

TTX_D7

92

P2-1/PWM093P2-2/PWM194P2-3/PWM295P2-4/PWM396P2-5/PWM497P2-6/PWM5

U21

U21

SAA5361

SAA5361

TTX_A15

TTX_A12

TTX_A13

TTX_A3

TTX_D1

TTX_D0

TTX_D2

+3VTTa

TTX_A2

TTX_A1

2

1

PCB:

All U4 Pads should be longer then external perimeter

to allow manual soldering and rework.

+3VTT

76

81

SCL

SDA

VD1_TTX_B

78

80

P1-279P1-3

VD1_TTX_G

VD1_TTX_R

77

NC

P1_0

P1_1

VDDP

NC

RESET

RESET_N

XTALOUT

XTALIN

OSCGND

NC

A8

A9

A10

A11

VDDC

VSSC

NC

VSSP

NC

NC

NC

NC

VSYNC

NC

HSYNC

VDS

RAMBK0

50

TTX_A17

TTX_A0

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

TTX_A8

TTX_A9

TTX_A10

TTX_A11

+3VTT

VD1_CCD_VS

VD1_CCD_HS

VD1_TTX_FB

TTX_A16

Note:

VD1_TTX_R

VD1_TTX_G

VD1_TTX_B

R2581KR258

1K

C78

C78

56pF

56pF

1 2

X2

X2

12.00MHz

12.00MHz

C73

C73

56pF

56pF

R98

R98

150

150

PCB: Analog signal shoul be positioned over analog planes

Place resistors near FSAV330M in page 1

R106 150R106 150C93 100nFC93 100nF

R105 150R105 150

R104 150R104 150

TTX_RST 11

VD1_CCD_VS 1

VD1_CCD_HS 1

VD1_TTX_FB 1

VD1_TTX_R 1

VD1_TTX_G 1

VD1_TTX_B 1

84

82

AD085AD186AD287AD388AD489AD590AD691AD7

P1_483P1_5

+3V +3Va+3VTT +3VTTa

FB15

FB15

BLM18AG471SN1

BLM18AG471SN1

FB20

FB20

BLM18AG471SN1

BLM18AG471SN1

A A

C64

C64

ECBp10uF/10V

ECBp10uF/10V

+

+

C63

ECBp10uF/10V

ECBp10uF/10V

C273

C273

100nF

100nF

5

+

+

C307

C307

100nF

100nF

C79

C79

100nF

100nF

C72

C72

100nF

100nF

C306

C306

100nF

100nF

C90

C90

ECBp10uF/10V

ECBp10uF/10V

+

+

4

C104

C104

ECBp10uF/10V

ECBp10uF/10V

C329

C329

100nF

100nF

+

+

C94

C94

100nF

100nF

TP30

TP30

GND

GND

1

3

2

Title

Title

Title

http://arizanotlari.com

http://arizanotlari.com

http://arizanotlari.com

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

Teletext

Teletext

Teletext

of

of

of

212Friday, December 02, 2005

212Friday, December 02, 2005

212Friday, December 02, 2005

1

1.1

1.1

1.1

C63

http://arizanotlari.com

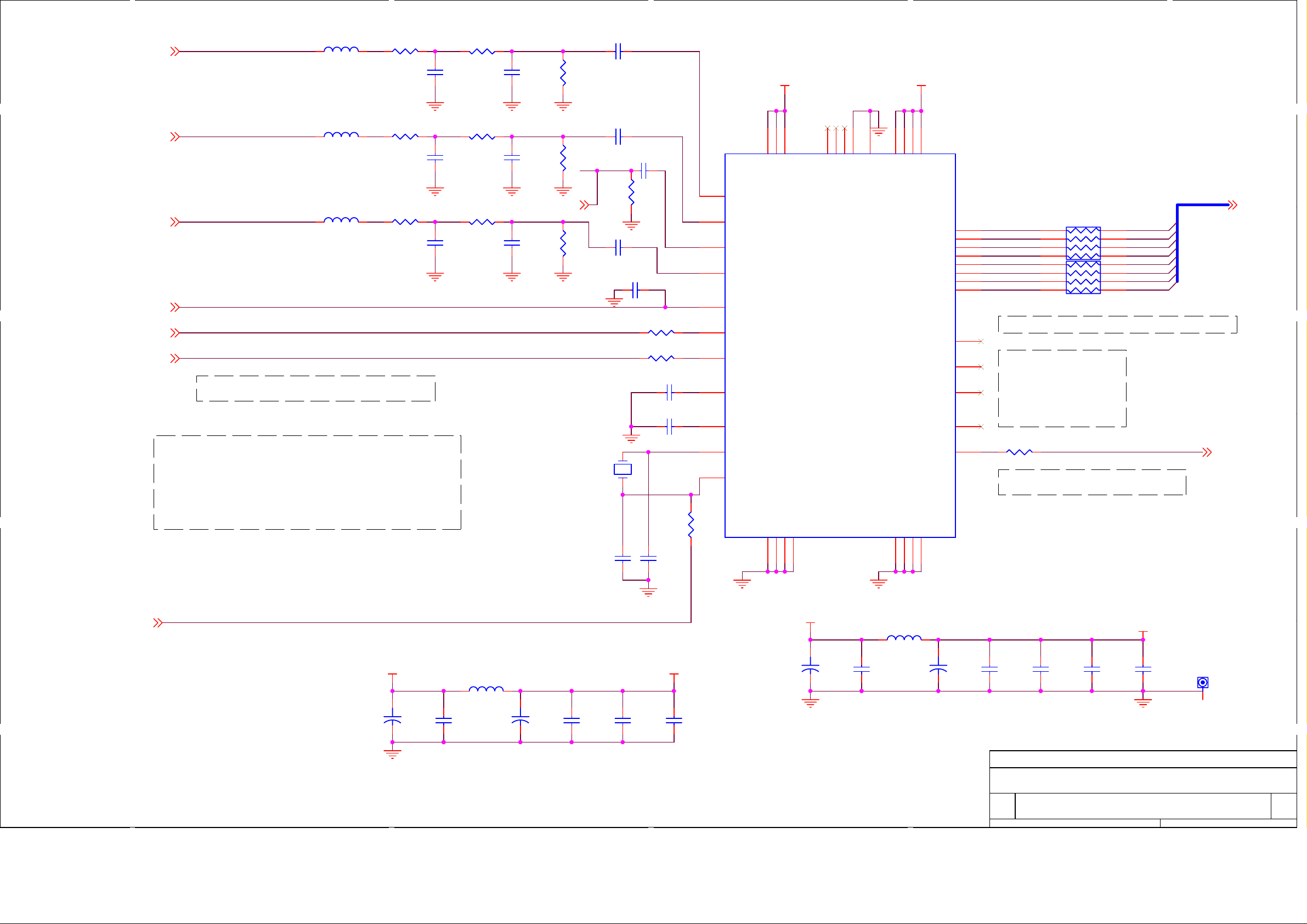

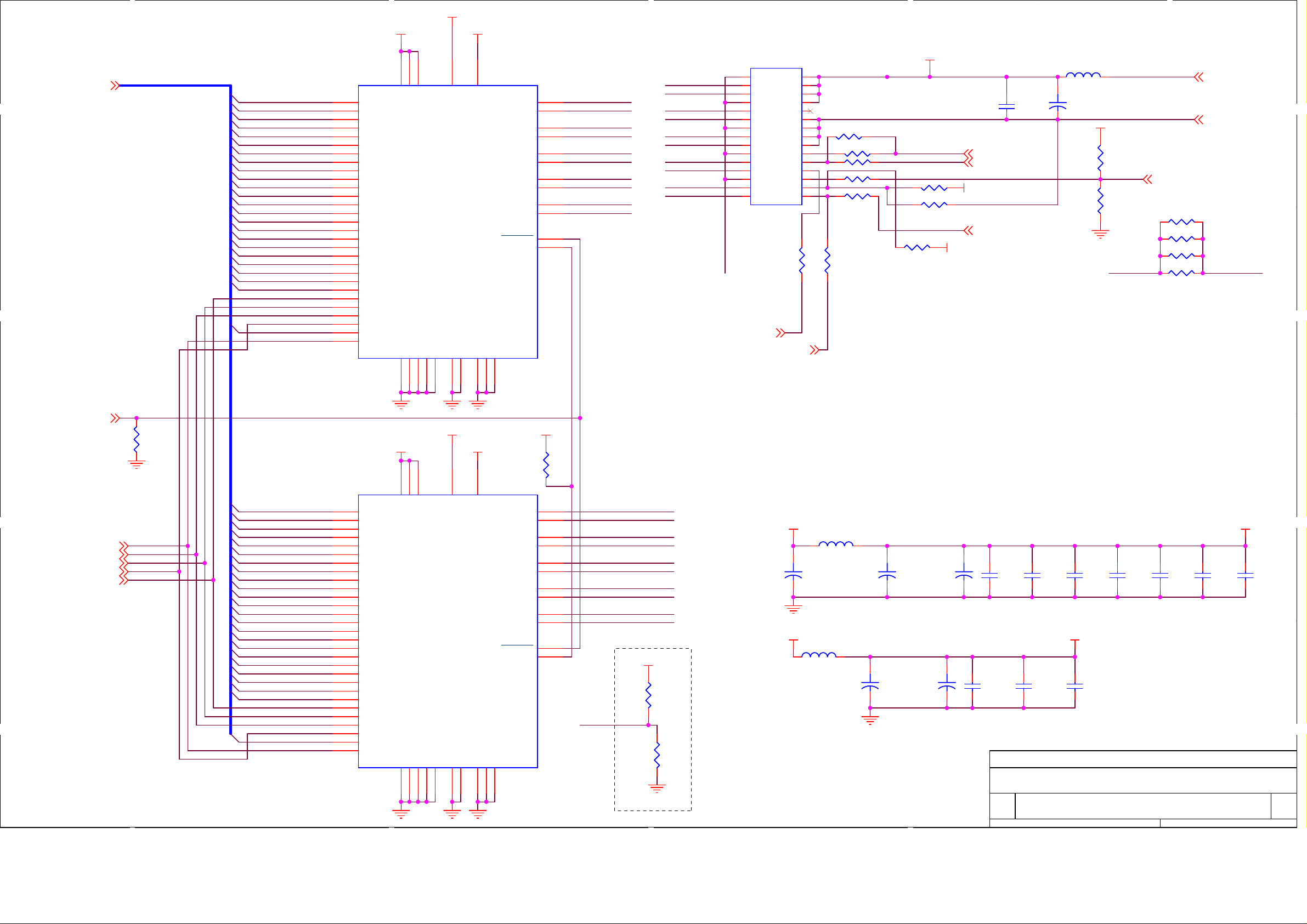

Page 3

5

5

4

3

2

1

R15675R156

VD2_CV4

VD2_CV

L4

3.3uHL43.3uH

D D

VD2_SY4

VD2_SC4

VD2_RST_N11

VD2_SY

VD2_SC

VD2_RST_N

L3

3.3uHL33.3uH

L2

3.3uHL23.3uH

75

C171

C171

82pF

82pF

R15575R155

75

C170

C170

82pF

82pF

R15475R154

75

C169

C169

82pF

82pF

R139 120R139 120

C154

C154

100pF

100pF

R138 120R138 120

C153

C153

100pF

100pF

R137 120R137 120

C152

C152

100pF

100pF

R134

R134

470

470

R135

R135

470

470

CVBS_AUX4

R133

R133

470

470

C C

SCL_11,2,4,11

SDA_11,2,4,11

SW: I2C BUS SLAVE ADDRESS: 0x4A

PCB:

Check for 1Vp-p video input signal.

Video in the SAA7113 inputs is 0.7V.

24.576 MHz

24.576 MHz

If not change input resistor value

C136 47nFC136 47nF

C138 47nFC138 47nF

CVBS_AUX

C134 47nFC134 47nF

X3

X3

R400

R400

470

470

C335 NCC335 NC

1 2

C527

C527

47nF

47nF

R227 22R227 22

R225 22R225 22

C137 47nFC137 47nF

C348 47nFC348 47nF

+3V_VD2A +3V_VD2D

U25

U25

3

10

42

VDDA1

VDDA0

VDDA2

4

AI11

7

AI12

43

AI21

1

AI22

40

CE

SAA7113H

SAA7113H

39

TMS

37

36

38

TDI

TCK

TDO

18

8

34

29

33

TRSTN

VDDI

VDDDA

VDDDE1

VDDDE2

VPO7

VPO6

VPO5

VPO4

VPO3

VPO2

VPO1

VPO0

BT.656

VD2_Y7

12

VD2_Y6

13

VD2_Y5

14

VD2_Y4

15

VD2_Y3

19

VD2_Y2

20

VD2_Y1

21

VD2_Y0

22

RP3247x4 RP3247x4

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

RP2747x4 RP2747x4

D_INA15

D_INA14

D_INA13

D_INA12

D_INA11

D_INA10

D_INA9

D_INA8

D_INA[0..23]

D_INA[0..23] 4,

PCB: Implement GND traces as in page 1

24

SCL

23

SDA

5

AI1D

RTCO

RTS1

RTS0

25

27

SW: I2C Address:

RTSO=0 0x48.

26

RTSO=1 0x4A.

(internal

Pull-up)

44

AI2D

31

XTAL

32

XTALI

AOUT

LLC

9

17

R231 47R231 47

DIN_CLK 4,5,6

PCB: Put resistor close to IC

from NC to apropriate value.

B B

C83

C82

C82

47pF

47pF

C83

47pF

47pF

R222NCR222

NC

VSSA1

VSSA0

2

11

AGND

VSSA2

6

41

VSSDE1

VSSDI

VSSDA

VSSDE2

16

28

30

35

SAA7113_CLK1

A A

5

http://arizanotlari.com

SAA7113_CLK

+

+

C141

C141

ECBp10uF/10V

ECBp10uF/10V

4

FB23

FB23

BLM18AG471SN1

BLM18AG471SN1

C383

C383

100nF

100nF

+

+

C110

C110

ECBp10uF/10V

ECBp10uF/10V

C349

C349

100nF

100nF

C135

C135

100nF

100nF

+3V_VD2A+3Va

ECBp10uF/10V

ECBp10uF/10V

C338

C338

100nF

100nF

3

C75

C75

+3V

FB8

FB8

BLM18AG471SN1

BLM18AG471SN1

+

+

C77

C77

100nF

100nF

ECBp10uF/10V

ECBp10uF/10V

C85

C85

+

+

C326

C326

100nF

100nF

Title

Title

Title

http://arizanotlari.com

http://arizanotlari.com

http://arizanotlari.com

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

C311

C311

100nF

100nF

Video Decoder to PortA

Video Decoder to PortA

Video Decoder to PortA

100nF

100nF

2

C95

C95

+3V_VD2D

C310

C310

100nF

100nF

TP12

TP12

GND

GND

1

1.1

1.1

1.1

of

of

of

312Friday, December 02, 2005

312Friday, December 02, 2005

312Friday, December 02, 2005

1

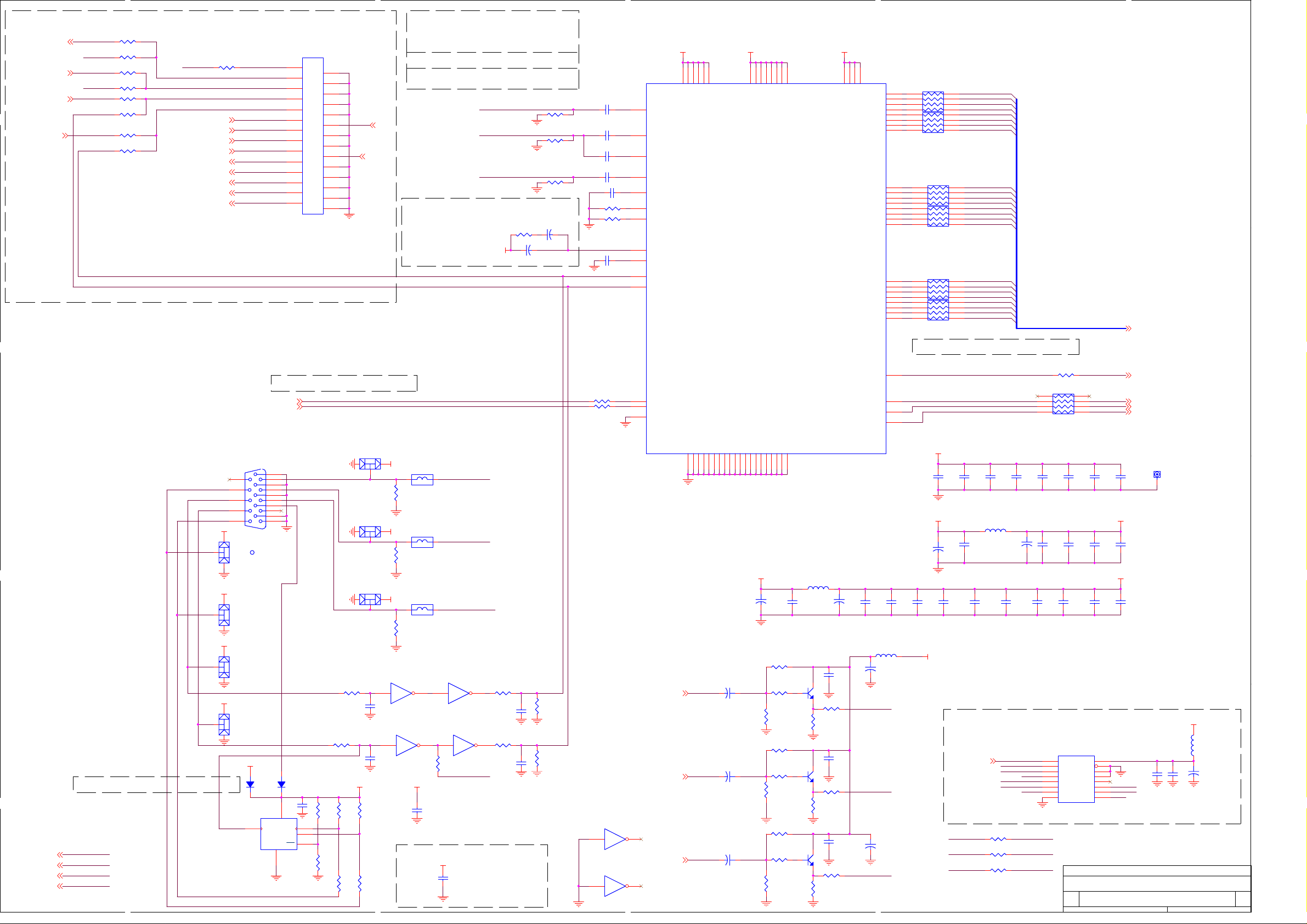

Page 4

5

RGB & Control CON

VGA_HSYNC

VGA_VSYNC

R259 0RR259 0R

R260 NCR260 NC

R261 0RR261 0R

R263 NCR263 NC

R264 0RR264 0R

R265 NCR265 NC

R266 0RR266 0R

R267 NCR267 NC

VGA_B

VD1_SY/CV_COPY1

IO_SPI_CS#11

IO_SPI_DOUT11

SCL_2_5V

SDA_2_5V

IO_ACD11

VD2_SC3

VD2_CV3

VD2_SY3

R262 NCR262 NC

IO_SPI_CS#

IO_SPI_DOUT

SCL_2_5V

SDA_2_5V

IO_ACD

VD2_SC

VD2_CV

VD2_SY

VD1_SY/CV_COPY

28

26

24

22

20

18

16

14

12

10

8

6

4

2

J17

J17

28

26

24

22

20

18

16

14

12

10

8

6

4

2

CON28A

CON28A

27

27

25

25

23

23

21

21

19

19

IO_SPI_DIN

17

17

15

15

13

13

11

11

9

9

7

7

5

5

3

3

1

1

IO_THEM_DET11

IO_PLZ_PA_MUTE11

IO_PLZ_PS_ON11

IO_THEM_DET

VGA_G

IO_PLZ_PA_MUTE

VGA_R

IO_PLZ_PS_ON

VGA_VSYNC

D D

IO_SPI_SCLK11

IO_SPI_SCLK

VGA_HSYNC

C C

4

IO_SPI_DIN

IO_VsON

PCB:

Signals in flat cable.

Need GND between each

wire.

PCB: Put 0R resistors close to FFC connector

PCB: Put NC resistors close to Graphics A/D

R/Pr

G/Y

B/Pb

R171 1KR171 1K

R170 1KR170 1K

R169 1KR169 1K

PCB: Close to pin 33

R118

HW: NC for MST9883

Values for AD9883A

+3V_AD3P

R118

NC(2.7K)

NC(2.7K)

C133

C133

NC(82nFNPO)

NC(82nFNPO)

C140 NC(8.2nF)NPOC140 NC(8.2nF)NPO

C186 47nFC186 47nF

C184 47nFC184 47nF

C185 1nFC185 1nF

C183 47nFC183 47nF

C147 100nFC147 100nF

R136 1KR136 1K

R116 1KR116 1K

C187 100nFC187 100nF

3

+3V

U29

U29

VDD11VDD22VDD23VDD69VDD78VDD

54

Rin

48

Gin

49

SOGIN

43

Bin

37

MIDSCV

38

CLAMP

29

COAST

33

FILT

58

REF

30

HSYNC

31

VSYNC

79

+3V_AD3A

VD39VD42VD45VD46VD51VD52VD59VD

MST9883

MST9883

62

+3V_AD3P

35

PVD26PVD27PVD34PVD

RA7

RA6

RA5

RA4

RA3

RA2

RA1

RA0

GA7

GA6

GA5

GA4

GA3

GA2

GA1

GA0

BA7

BA6

BA5

BA4

BA3

BA2

BA1

BA0

2

70

71

72

73

74

75

76

77

2

3

4

5

6

7

8

9

12

13

14

15

16

17

18

19

RP3447x4 RP3447x4

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

RP3347x4 RP3347x4

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

PCB: Implement GND traces as in page 1

for each 8 bits of data and clock

D_INA23

D_INA22

D_INA21

D_INA20

D_INA19

D_INA18

D_INA17

D_INA16

RP3147x4 RP3147x4

D_INA15

D_INA14

D_INA13

D_INA12

D_INA11

D_INA10

D_INA9

D_INA8

RP3047x4 RP3047x4

RP2947x4 RP2947x4

D_INA7

D_INA6

D_INA5

D_INA4

D_INA3

D_INA2

D_INA1

D_INA0

RP2847x4 RP2847x4

1

D_INA[0..23] 3,5,6

67

C182

C182

C411

C411

100nF

100nF

C418

C418

100nF

100nF

C425

C425

100nF

100nF

+

+

R2790RR279

0R

R2900RR290

0R

R3010RR301

0R

DATACK

HSOUT

VSOUT

SOGOUT

C405

C405

100nF

100nF

FB34

FB34

BLM18AG471SN1

BLM18AG471SN1

+

+

Ecap10uF/25V

Ecap10uF/25V

VD1_Y_COPY

VD1_Pb_COPY

+

+

Ecap10uF/25V

Ecap10uF/25V

VD1_Pr_COPY

2

C412

C412

C526

C526

66

64

65

C84

C84

ECBp10uF/10V

ECBp10uF/10V

C167

C167

100nF

100nF

C404

C404

100nF

100nF

+5V

+3V

SW: I2C BUS SLAVE ADDERESS : 0x98

SDA_11,2,3,11

SCL_11,2,3,11

D8

R288NCR288

NC

R296

R296

100

100

R28033R280

33

VGA_DDC_SCL

R27233R272

33

R291

R291

4.7K

4.7K

BAV99WD8BAV99W

D9

BAV99WD9BAV99W

D12

D12

BAV99W

BAV99W

C415

C415

10pF

10pF

+5Vg

VGA_DDC_SDA

A2C

A2C

A2C

R292

R292

4.7K

4.7K

R297

R297

100

100

AC

3

R26875R268

AC

3

R26975R269

AC

3

R27075R270

C416

C416

10pF

10pF

4

1

+5VSB

75

1

+5VSB

75

1

+5VSB

75

U32A

U32A

74LCX14

74LCX14

1 2

U32C

U32C

74LCX14

74LCX14

5 6

FB31

FB31

BLM18BB121SN1

BLM18BB121SN1

2

1

FB32

FB32

BLM18BB121SN1

BLM18BB121SN1

2

1

FB33

FB33

BLM18BB121SN1

BLM18BB121SN1

2

1

+3V

Place next to

C424

C424

pin 14

100nF

100nF

+5VSB

VGA_R

VGA_G

VGA_B

U32B

U32B

74LCX14

74LCX14

3 4

U32D

U32D

74LCX14

74LCX14

9 8

R283NCR283

NC

IO_VGA_SYNC_DET

C426

C426

100nF

100nF

R27333R273

33

VGA_HSYNC

C413

C413

10pF

10pF

R28133R281

33

C417

C417

10pF

10pF

Place in

connector

area

R276

R276

4K7

4K7

VGA_VSYNC

R284

R284

4K7

4K7

OnBoard PC RGB

J21 DB15-RRAJ21 DB15-RRA

6

VGA_RED_IN

+5VSB

D16

D16

1N4148

1N4148

U34

U34

24LCS21A

24LCS21A

VCLK7VCC

VGA_SCL_IN

VGA_SDA_IN

1

7

2

8

3

9

4

10

5

GND

4

VGA_GREEN_IN

VGA_BLUE_IN

VGA_HSYNC_IN

VGA_VSYNC_IN

VSYNC_DDC

D15

D15

1N4148

1N4148

C423

C423

100nF

100nF

8

6

SCL

5

SDA

3

WP

R2940RR294

0R

VGA_SCL_IN

+5Vg

3

AC

11

12

13

14

15

1

C

D10

D10

A

BAV99W

BAV99W

2

VGA_SDA_IN

VGA_HSYNC_IN

VGA_VSYNC_IN

B B

+5Vg

1

C

3

AC

D11

D11

A

BAV99W

BAV99W

2

+5VSB

1

C

3

AC

D13

D13

A

BAV99W

BAV99W

2

+5VSB

1

C

3

AC

D14

D14

A

BAV99W

BAV99W

2

PCB: Make the footprint compatible with 0805 footprint jumper

A A

VSYNC_DDC

IO_VGA_SYNC_DET11

VGA_DDC_SCL11

VGA_DDC_SDA11

VSYNC_DDC11

http://arizanotlari.com

IO_VGA_SYNC_DET

VGA_DDC_SCL

VGA_DDC_SDA

VSYNC_DDC

5

R168 22R168 22

R167 22R167 22

U32E

U32E

74LCX14

74LCX14

11 10

13 12

U32F

U32F

74LCX14

74LCX14

3

57

SDA

56

SCL

55

A0

GND1GND10GND20GND21GND24GND25GND28GND32GND36GND40GND41GND44GND47GND50GND53GND60GND61GND63GND68GND

80

+3Va

+

C197

C197

ECBp10uF/10V

ECBp10uF/10V

VD1_Y

VD1_Y1

VD1_Pb

VD1_Pb1

VD1_Pr

VD1_Pr1

+

+

C414

C414

Ecap10uF/25V

Ecap10uF/25V

+

+

C419

C419

Ecap10uF/25V

Ecap10uF/25V

+

+

C427

C427

Ecap10uF/25V

Ecap10uF/25V

+

R271 6.8KR271 6.8K

R274 82R274 82

12

R401

R401

10K

10K

R282 6.8KR282 6.8K

R286 82R286 82

12

R402

R402

10K

10K

R293 6.8KR293 6.8K

R295 82R295 82

12

R403

R403

10K

10K

BLM18AG471SN1

BLM18AG471SN1

C407

C407

100nF

100nF

B

Q23

Q23

MMBT3904

MMBT3904

B

Q24

Q24

MMBT3904

MMBT3904

B

Q25

Q25

MMBT3904

MMBT3904

FB29

FB29

ECBp10uF/10V

ECBp10uF/10V

C

E

R278

R278

470

470

C

E

R289

R289

470

470

C

E

R300

R300

470

470

AD9883_CLK

AD9883_HSYNC

AD9883_VSYNC

AD9883_SOGOUT

VDD - Digital Output PS

C362

C362

C357

C357

C347

100nF

100nF

FB18

FB18

BLM18AG471SN1

BLM18AG471SN1

C317

C317

100nF

100nF

C396

C396

100nF

100nF

C347

100nF

100nF

C100

C100

ECBp10uF/10V

ECBp10uF/10V

+

+

100nF

100nF

C403

C403

100nF

100nF

VGA RGB/HDTV YPbPr Select

HDTV_SEL

VD1_Pr_COPY R/Pr

VD1_Y_COPY G/Y

VD1_Pb_COPY B/Pb

VGA_R

VD1_Pr_COPY

VGA_G

VD1_Y_COPY

R455 0RR455 0R

R456 0RR456 0R

R457 0RR457 0R

HDTV_SEL

C406

C406

100nF

100nF

100nF

100nF

R/Pr

G/Y

C363

C363

+

+

R132 47R132 47

7 8

1 2

5 6

3 4

RP3547x4 RP3547x4

C259

C259

C237

C237

100nF

100nF

100nF

100nF

PVD - PLL PS

C382

C382

C356

C356

1nF

1nF

100nF

100nF

VD - Analog PS

C402

C402

C188

C188

100nF

100nF

100nF

100nF

U33

U33

FSAV450M

FSAV450M

1

S

2

1B1

3

1B2

4

1A

5

2B1

6

2B2

7

2A

GND83A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

16

VCC

15

EN

14

4B1

13

4B2

12

4A

11

3B1

10

3B2

9

http://arizanotlari.com

http://arizanotlari.com

http://arizanotlari.com

Custom

Custom

Custom

C375

C375

100nF

100nF

C368

C368

100nF

100nF

+3V_AD3A

C395

C395

100nF

100nF

VD1_Pb_COPY

+3V_AD3P+3V

VGA_B

B/Pb

DIN_CLK 3,5,6

D_HSYNC 5,6

D_VSYNC 5,6

D_CSYNC 6

TP7

TP7

GND

GND

C358

C358

100nF

100nF

1

C374

C374

1nF

1nF

C151

C151

100nF

100nF

C422

C422

C421

C421

1nF

1nF

100nF

100nF

Graphics A/D

Graphics A/D

Graphics A/D

+5V

1

FB35

FB35

BLM18AG471SN1

BLM18AG471SN1

12

C420

C420

+

+

Ecap10uF/25V

Ecap10uF/25V

412Monday, December 05, 2005

412Monday, December 05, 2005

412Monday, December 05, 2005

of

of

of

1.1

1.1

1.1

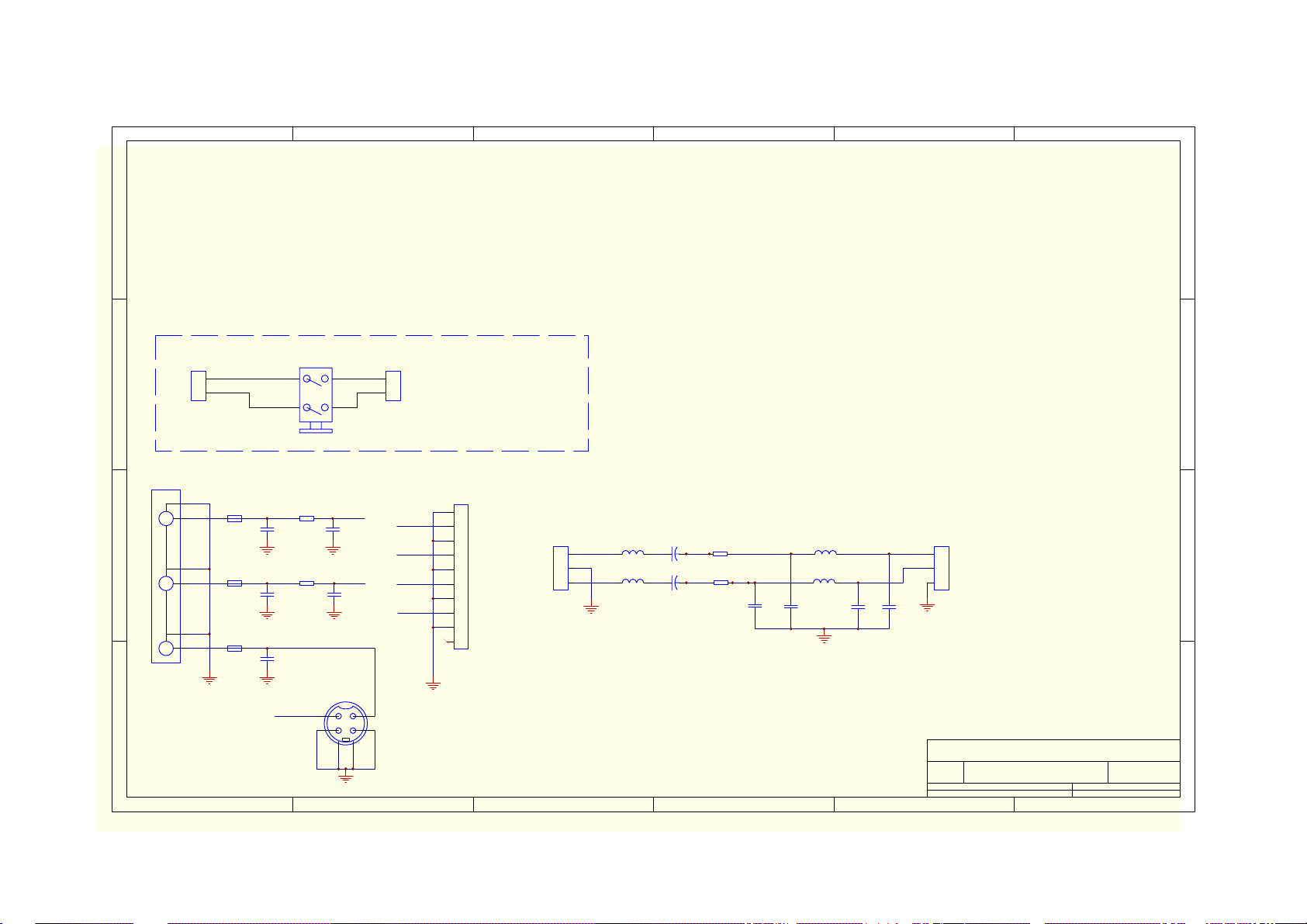

Page 5

5

SIDE A:

SIDE A:

SDRAM+PORT A

SDRAM+PORT A

U9A

N1

N2

N3

P1

P2

P3

P4

R1

R2

R3

T1

T2

T3

U1

U2

U3

V1

V2

W1

W2

W3

Y1

Y2

Y3

L4

M1

M2

M3

M4

N4

R4

H4

C2

D3

E3

U9A

VA_DATA0

VA_DATA1

VA_DATA2

VA_DATA3

VA_DATA4

VA_DATA5

VA_DATA[6

VA_DATA7

VA_DATA8

VA_DATA9

VA_DATA10

VA_DATA11

VA_DATA12

VA_DATA13

VA_DATA14

VA_DATA15

VA_DATA16

VA_DATA17

VA_DATA18

VA_DATA19

VA_DATA20

VA_DATA21

VA_DATA22

VA_DATA23

VA_VALID

VA_VSYNC

VA_HSYNC

VA_CSYNC

VA_ACTIVE

VA_FIELD

VA_CLK

MPLL_CLK

M_CLK_IN

M_CLK_OUT_A

M_CLK_OUT_B

D_INA[0..23]3,4,5

D_INA0

D_INA1

D_INA2

D_INA3

D_INA4

D D

D_VSYNC4,5

D_HSYNC4,5

Note:

D_CSYNC4

D_ACTIVE5

MN_CLK11

MEM_CLK7

MN_CLK

MEM_CLK

DIN_CLK3,4,5

D_ACTIVE

D_INA5

D_INA6

D_INA7

D_INA8

D_INA9

D_INA10

D_INA11

D_INA12

D_INA13

D_INA14

D_INA15

D_INA16

D_INA17

D_INA18

D_INA19

D_INA20

D_INA21

D_INA22

D_INA23

R2100 R2100

R570 R570

MN_CLK should be wired in daisy chain with GND

in both sides as follows:

1. First to MPLL_CLK via 0 Ohm resistor.

C C

2. Then to OPLL_CLK via 0 Ohm serial resistor and termination.

3. Pay attention termination should be at the end of trace.

OP_VSYNC8,9,10

OP_HSYNC8,9,10

OP_ENABLE8,9,10

B B

OP_FIELD8,10

OCLK_OUT8,9,10

C222NCC222

NC

+3V

+1.8V

R20 33R20 33

R21 33R21 33

R200 33R200 33

R933 R933

R19922 R19922

+1.8V

+3V

+1.8V_PLL

M20

M19

M18

M17

L18

L17

N16

P16

M16

L16

G16

H16

K16

J16

K12

T17

J13

L13

L12

M13

U17

V18

N13

L11

K13

M12

E17

U9C

U9C

J4

VCCAP

M5

VCCK

P5

VCC3I

J5

VCCK

K5

VCC3O

H5

VCCK

G5

VCC3O

N5

VCCK

L5

VCC3O

SIDE C: OUTPUT

SIDE C: OUTPUT

OP_VSYNC

OP_HSYNC

OP_ENABLE

OP_WINDOW_ACTIVE

OP_FIELD

OP_CLK

VCCK

VCC3O

VCCK

VCC3O

VCC3I

VCCK

VCC3O

VCK

GNDO

GNDO

GNDK

GNDO

GNDO

GNDK

GNDO

GNDO

GNDK

GNDK

GNDO

GNDK

GNDI

A A

OP_DATA_B55/OP_DATA_CR0

OP_DATA_B56/OP_DATA_CR1

OP_DATA_B57/OP_DATA_CR2

OP_DATA_B58/OP_DATA_CR3

OP_DATA_B59/OP_DATA_CR4

Monet203

http://arizanotlari.com

5

Monet203

4

M_BS1

M_BS0

M_DQM_B

M_DQM_A

M_WE_N

M_CAS_M

M_RAS_N

M_CS_N

VA_CLAMP

VA_COAST

M_ADDR0

M_ADDR1

M_ADDR2

M_ADDR3

M_ADDR4

M_ADDR5

M_ADDR6

M_ADDR7

M_ADD[8

M_ADDR9

M_ADDR10

M_ADDR11

GNDO

GNDO

GNDO

GNDK

GNDK

GNDK

GNDO

GNDO

GNDK

GNDAP

GNDI

GNDK

GNDO

GNDO

Monet203

Monet203

OP_DATA_A0

OP_DATA_A1

OP_DATA_A2

OP_DATA_A3

OP_DATA_A4

OP_DATA_A5

OP_DATA_A6

OP_DATA_A7

OP_DATA_A8

OP_DATA_A9

OP_DATA_A10

OP_DATA_A11

OP_DATA_A12

OP_DATA_A13

OP_DATA_A14

OP_DATA_A15

OP_DATA_A16

OP_DATA_A17

OP_DATA_A18

OP_DATA_A19

OP_DATA_A20

OP_DATA_A21

OP_DATA_A22

OP_DATA_A23

OP_DATA_A24

OP_DATA_A25

OP_DATA_A26

OP_DATA_A27

OP_DATA_A28

OP_DATA_A29

OP_DATA_B30

OP_DATA_B31

OP_DATA_B32

OP_DATA_B33

OP_DATA_B34

OP_DATA_B35

OP_DATA_B36

OP_DATA_B37

OP_DATA_B38

OP_DATA_B39

OP_DATA_B40

OP_DATA_B41

OP_DATA_B42

OP_DATA_B43

OP_DATA_B44

OP_DATA_B45

OP_DATA_B46

OP_DATA_B47

OP_DATA_B48

OP_DATA_B49

OP_DATA_B50

OP_DATA_B51

OP_DATA_B52

OP_DATA_B53

OP_DATA_B54

4

F2

F1

F4

E2

E1

D2

D1

C1

K3

L1

F3

G1

G2

G3

H1

H2

H3

J1

J2

J3

K1

K2

C3

D4

L10

H8

J9

M8

K9

L8

K10

G4

T4

J8

K8

E4

C20

C19

D20

D19

D18

E20

E19

E18

F20

F19

F18

F17

G20

G19

G18

G17

H20

H19

H18

H17

J20

J19

J18

J17

K20

K19

K18

K17

L20

L19

N20

N19

N18

N17

P20

P19

P18

P17

R20

R19

R18

R17

T20

T19

T18

U20

U19

U18

V20

V19

V17

W20

W19

W18

W17

Y20

Y19

Y18

Y17

Y16

RP13 33RP13 33

1 2

3 4

7 8

5 6

RP15 0RP15 0

1 2

3 4

5 6

7 8

RP14 33RP14 33

RP16 33RP16 33

RP17 33RP17 33

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

7 8

3 4

5 6

1 2

RP7 33RP7 33

1 2

3 4

5 6

7 8

1 2

3 4

7 8

5 6

RP1 33RP1 33

RP8 33RP8 33

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RP2 33RP2 33

RP9 33RP9 33

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RP3 33RP3 33

MEM_BS1 7

MEM_BS0 7

MEM_DQM_B 7

MEM_DQM_A 7

MEM_WE_N 7

MEM_CAS_N 7

MEM_RAS_N 7

MEM_CS_N 7

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

+1.8V_PLL

ETNT10uF/10V

ETNT10uF/10V

C57

C57

MEM_A[10..0] 7

BLM18AG471SN1

BLM18AG471SN1

+

+

FB4

FB4

C267

C267

10nF

10nF

ECBp10uF/10V

ECBp10uF/10V

Note:

Place capacitors near pin J4.

10nF colser to J4 then 10uF.

OP_A[0..23] 8,9,10

OP_A0

OP_A1

OP_A2

OP_A3

OP_A4

OP_A5

OP_A6

OP_A7

OP_A8

OP_A9

OP_A10

OP_A11

OP_A12

OP_A13

OP_A14

OP_A15

OP_A16

OP_A17

OP_A18

OP_A19

OP_A20

OP_A21

OP_A22

OP_A23

BLUE

GREEN

RED

C54

C54

3

3

+1.8V

2

SIDE B:

SIDE B:

CPU + PORT B + JTAG

CPU + PORT B + JTAG

U9B

C38NCC38

NC

V11

Y15

W15

V15

V14

W14

Y14

T10

T14

T12

T11

T13

U12

V4

W4

Y4

V5

W5

Y5

V6

W6

Y6

L3

L2

T7

T8

T9

U9B

VB_CLK

VB_DATA0

VB_DATA1

VB_DATA2

VB_DATA3

VB_DATA4

VB_DATA5

VB_DATA6

VB_DATA7

VB_VSYNC_O

VB_HSYNC_O

RESET_N

TEST

TDO

TDI

TCK

TMS

TRSTN

VCC3O

VCCK

VCC3O

VCCK

VCC3I

VCCK

VCC3O

VCCK

VCCAP

+3V

C16

C16

+

+

ETNT10uF/10V

ETNT10uF/10V

+1.8V

C22

C22

+

+

ETNT10uF/10V

ETNT10uF/10V

OPLL_CLK

CPU_ADDR0

CPU_ADDR1

CPU_ADDR2

CPU_ADDR3

CPU_ADDR4

CPU_ADDR5

CPU_ADDR6

CPU_ADDR7

CPU_CS_N

CPU_RD_N

CPU_WR_N

CPU_IRQ

CPU_DB0

CPU_DB1

CPU_DB2

CPU_DB3

CPU_DB4

CPU_DB5

CPU_DB6

CPU_DB7

GNDAP

Monet203

Monet203

MEM_DQ[63..0] 7

C228

C228

100nF

100nF

C230

C230

100nF

100nF

GNDO

GNDO

GNDK

GNDO

GNDO

GNDK

GNDI

GNDO

GND

GNDK

GNDO

GNDK

GND0

C243

C243

100nF

100nF

C234

C234

100nF

100nF

U13

V7

W7

Y7

V8

W8

Y8

V9

W9

Y10

W10

V10

Y9

W11

Y11

V12

W12

Y12

V13

W13

Y13

V3

U4

N8

U5

N10

N9

U14

U16

M10

L9

M9

L10

N12

N11

C255

C255

100nF

100nF

C239

C239

100nF

100nF

R1830R183

0

CPU_A0

CPU_A1

CPU_A2

CPU_A3

CPU_A4

CPU_A5

CPU_A6

CPU_A7

CPU_D0

CPU_D1

CPU_D2

CPU_D3

CPU_D4

CPU_D5

CPU_D6

CPU_D7

C254

C254

100nF

100nF

C246

C246

100nF

100nF

MN_CS_N

CPU_RD_N

CPU_WR_N

MN_IRQ

CPU_D[0..7]

C252

C252

100nF

100nF

C251

C251

100nF

100nF

CPU_A[0..7]

MN_CS_N 11

CPU_RD_N 11

CPU_WR_N 11

MN_IRQ 11

CPU_D[0..7] 11,12

C249

C249

C250

C250

100nF

100nF

100nF

100nF

C253

C253

C245

C245

100nF

100nF

100nF

100nF

Title

Title

Title

http://arizanotlari.com

http://arizanotlari.com

http://arizanotlari.com

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

VCLK1

V_IN[0..7]1

MN_RST_N11

+

+

+1.8V+3V

U10

U11

U15

M17

V16

W16

E14

E12

E11

E13

E10

D17

H12

H11

J11

H13

D16

C18

K11

J12

H10

J10

M11

C41

C41

100nF

100nF

U9D

U9D

K4

NC1

U6

NC2

U7

NC3

U8

NC4

U9

NC5

NC6

NC7

NC8

NC9

NC10

NC11

VCC3O

E9

VCCK

VCCK

VCC3O

VCCK

E7

VCC3I

VCC3O

E8

VCCK

D5

GNDI

GNDO

GNDK

GNDO

GNDO

GNDK

GNDO

GNDO

GND

GNDK

GNDO

GNDO

H9

GNDK

GND

VCLK

V_IN[0..7]

MN_RST_N

FB3

FB3

BLM18AG471SN1

BLM18AG471SN1

C25

C25

ETNT10uF/10V

ETNT10uF/10V

SIDE D: SDRAM

SIDE D: SDRAM

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

Monet203

Monet203

V_IN0

V_IN1

V_IN2

V_IN3

V_IN4

V_IN5

V_IN6

V_IN7

+1.8V

+3V

+

+

C224

C224

10nF

10nF

MEM_DQ0

A1

MEM_DQ1

B1

MEM_DQ2

A2

MEM_DQ3

B2

MEM_DQ4

A3

MEM_DQ5

B3

MEM_DQ6

A4

MEM_DQ7

B4

MEM_DQ8

C4

MEM_DQ9

A5

MEM_DQ10

B5

MEM_DQ11

C5

MEM_DQ12

A6

MEM_DQ13

B6

MEM_DQ14

C6

MEM_DQ15

D6

MEM_DQ16

A7

MEM_DQ17

B7

MEM_DQ18

C7

MEM_DQ19

D7

MEM_DQ20

A8

MEM_DQ21

B8

MEM_DQ22

C8

MEM_DQ23

D8

MEM_DQ24

A9

MEM_DQ25

B9

MEM_DQ26

C9

MEM_DQ27

D9

MEM_DQ28

A10

MEM_DQ29

B10

MEM_DQ30

C10

MEM_DQ31

D10

MEM_DQ32

A11

MEM_DQ33

B11

MEM_DQ34

C11

MEM_DQ35

D11

MEM_DQ36

A12

MEM_DQ37

B12

MEM_DQ38

C12

MEM_DQ39

D12

MEM_DQ40

A13

MEM_DQ41

B13

MEM_DQ42

C13

MEM_DQ43

D13

MEM_DQ44

A14

MEM_DQ45

B14

MEM_DQ46

C14

MEM_DQ47

D14

MEM_DQ48

A15

MEM_DQ49

B15

MEM_DQ50

C15

MEM_DQ51

D15

MEM_DQ52

A16

MEM_DQ53

B16

MEM_DQ54

C16

MEM_DQ55

A17

MEM_DQ56

B17

MEM_DQ57

C17

MEM_DQ58

A18

MEM_DQ59

B18

MEM_DQ60

A19

MEM_DQ61

B19

MEM_DQ62

A20

MEM_DQ63

B20

2

1

+3V

R184NCR184

NC

R209NCR209

NC

CPU_A[0..7] 11

C244

C244

100nF

100nF

C240

C240

100nF

100nF

MN203

MN203

MN203

1

TP3

TP3

CLK

CLK

C229

C229

100nF

100nF

C233

C233

100nF

100nF

1

C232

C232

C227

C227

100nF

100nF

C231

C231

100nF

100nF

512Friday, December 02, 2005

512Friday, December 02, 2005

512Friday, December 02, 2005

100nF

100nF

C242

C242

100nF

100nF

of

of

of

C223

C223

100nF

100nF

C247

C247

100nF

100nF

1.1

1.1

1.1

Page 6

5

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_DQ[63..0]

MEM_DQ0

MEM_DQ1

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_A10

MEM_A0

MEM_A1

MEM_A2

MEM_DQ[63..0]6

MEM_A[10..0]6

D D

C C

MEM_DQ16

MEM_DQ17 MEM_DQ30

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

4

U10

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

NC

VDD

DQM0

WE

CAS

RAS

CS

NC

BA0

BA1

A10/AP

A0

A1

A2

DQM2

VDD

NC

DQ16

VSSQ

DQ17

DQ18

VDDQ

DQ19

DQ20

VSSQ

DQ21

DQ22

VDDQ

DQ23

VDD

U10

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

NC

VSS

DQM1

NC

NC

CLK

CKE

A9

A8

A7

A6

A5

A4

A3

DQM3

VSS

NC

DQ31

VDDQ

DQ30

DQ29

VSSQ

DQ28

DQ27

VDDQ

DQ26

DQ25

VSSQ

DQ24

VSS

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

MEM_DQ15

MEM_DQ14

MEM_DQ13

MEM_DQ12

MEM_DQ11

MEM_DQ10

MEM_DQ9

MEM_DQ8

MEM_A9

MEM_A8

MEM_A7

MEM_A6

MEM_A5

MEM_A4

MEM_A3

MEM_DQ31

MEM_DQ29

MEM_DQ28

MEM_DQ27

MEM_DQ26

MEM_DQ25

MEM_DQ24

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

K4S643232F-TC/L70

K4S643232F-TC/L70

3

+3V+3V

1

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_BS0MEM_BS0

MEM_BS1MEM_BS1

MEM_A10

MEM_A0

MEM_A1

MEM_A2

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

VDD

2

DQ0

3

VDDQ

4

DQ1

5

DQ2

6

VSSQ

7

DQ3

8

DQ4

9

VDDQ

10

DQ5

11

DQ6

12

VSSQ

13

DQ7

14

NC

15

VDD

16

DQM0

17

WE

18

CAS

19

RAS

20

CS

21

NC

22

BA0

23

BA1

24

A10/AP

25

A0

26

A1

27

A2

28

DQM2

29

VDD

30

NC

31

DQ16

32

VSSQ

33

DQ17

34

DQ18

35

VDDQ

36

DQ19

37

DQ20

38

VSSQ

39

DQ21

40

DQ22

41

VDDQ

42

DQ23

43

VDD

K4S643232F-TC/L70

K4S643232F-TC/L70

U5

U5

2

VSS

DQ15

VSSQ

DQ14

DQ13

VDDQ

DQ12

DQ11

VSSQ

DQ10

DQ9

VDDQ

DQ8

NC

VSS

DQM1

NC

NC

CLK

CKE

DQM3

VSS

NC

DQ31

VDDQ

DQ30

DQ29

VSSQ

DQ28

DQ27

VDDQ

DQ26

DQ25

VSSQ

DQ24

VSS

A9

A8

A7

A6

A5

A4

A3

1

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

MEM_DQ47

MEM_DQ46

MEM_DQ45MEM_DQ2

MEM_DQ44

MEM_DQ43

MEM_DQ42

MEM_DQ41

MEM_DQ40

MEM_A9

MEM_A8

MEM_A7

MEM_A6

MEM_A5

MEM_A4

MEM_A3

MEM_DQ63

MEM_DQ62

MEM_DQ61

MEM_DQ60

MEM_DQ59

MEM_DQ58

MEM_DQ57

MEM_DQ56

Note:

In PCB layout you can change

SDRAM data bus connection

to avoid crossing signals.

+3V

MEM_BS16

MEM_WE_N6

MEM_CAS_N6

MEM_RAS_N6

MEM_CS_N6

MEM_DQM_A6

MEM_DQM_B6

10nF

10nF

MEM_CLK6

C19

C19

MEM_BS06

C30

C219

C219

10nF

10nF

C18

C18

10nF

10nF

C220

C220

10nF

10nF

C221

C221

10nF

10nF

C30

10nF

10nF

C31

C31

10nF

10nF

C33

C33

10nF

10nF

B B

+3V

+

+

C15

C15

ETNT10uF/10V

ETNT10uF/10V

MEM_BS1

MEM_BS0

MEM_WE_N

MEM_CAS_N

MEM_RAS_N

MEM_CS_N_0

MEM_CLK

MEM_DQM_A

MEM_DQM_B

C225

C225

10nF

10nF

10nF

10nF

C226

C226

C36

C36

10nF

10nF

C37

C37

10nF

10nF

TP17

TP17

GND

GND

1

PCB:

- SDRAM used size is 16MB.

- MEM_CLK resistors are located at the end of bus chain.

- All memory signals must be routed in a daisy chain,

R29

R29

150

150

R28

R28

150

150

- Traces should be between 2" to 4" length. Not more.

+3V

PCB:

Place 10uF/10V TANT capacitor near each SDRAM.

A A

+

+

C56

C56

ETNT10uF/10V

ETNT10uF/10V

10nF

10nF

C32

C32

C261

C34

C34

10nF

10nF

C35

C35

10nF

10nF

C241

C241

10nF

10nF

C238

C238

10nF

10nF

C48

C48

10nF

10nF

C261

10nF

10nF

5

C266

C266

10nF

10nF

C265

C265

10nF

10nF

C262

C262

10nF

10nF

C263

C263

10nF

10nF

C264

C264

10nF

10nF

4

Update number of 10nF capacitors after layout.

Title

Title

Title

http://arizanotlari.com

http://arizanotlari.com

http://arizanotlari.com

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

3

2

Date: Sheet

SDRAM 64Mbit x 2

SDRAM 64Mbit x 2

SDRAM 64Mbit x 2

612Friday, December 02, 2005

612Friday, December 02, 2005

612Friday, December 02, 2005

1

1.1

1.1

1.1

of

of

of

http://arizanotlari.com

Page 7

5

OP_A[0..23]6,9,10

D D

Note:

2 LVDS components

placed one on other.

Only one instaled.

C C

OP_A[0..23]

RV0

RV1

RV2

RV3

RV4

RV7

RV5

GY0

GY1

GY2

GY6

GY7

GY3

GY4

GY5

BU0

BU6

BU7

BU1

BU2

BU3

BU4

BU5

RV6

OP_A16

OP_A17

OP_A18

OP_A19

OP_A20

OP_A23

OP_A21

OP_A8

OP_A9

OP_A10

OP_A14

OP_A15

OP_A11

OP_A12

OP_A13

OP_A0

OP_A6

OP_A7

OP_A1

OP_A2

OP_A3

OP_A4

OP_A5

OP_FIELD

OP_HSYNC

OP_VSYNC

OP_ENABLE

OP_A22

OCLK_OUT

51

52

54

55

56

2

3

4

6

7

8

10

11

12

14

15

16

18

19

20

22

23

24

25

27

28

30

50

31

4

+3V_LVDS +3V_LVDS

1

U4

U4

TxIN0

TxIN1

TxIN2

TxIN3

TxIN4

TxIN5

TxIN6

TxIN7

DS90C385MTD

DS90C385MTD

TxIN8

TxIN9

TxIN10

TxIN11

TxIN12

TxIN13

TxIN14

TxIN15

TxIN16

TxIN17

TxIN18

TxIN19

TxIN20

TxIN21

TxIN22

TxIN23

TxIN24

TxIN25

TxIN26

TxIN27

TxCLKIN

5

+3V_LVDS_PLL

9

26

VCC1

VCC9

VCC26

LVDS DRIVER

GND5

GND13

GND21

GND29

13

21

29

53

34

GND53

33

44

PLL_VCC

LVDS_VCC

PLL_GND33

PLL_GND3535LVDS_GND36

36

LVDS CONNECTOR TO FPD

DIRECETED OUTPUT

Direct LVDS Driver

R_RxIN0-

R_FB

48

47

46

45

42

41

40

39

38

37

32

17

R_RxIN0+

R_RxIN1-

R_RxIN1+

R_RxIN2-

R_RxIN2+

R_RxCLKIN-

R_RxCLKIN+

R_RxIN3-

R_RxIN3+

TxOUT0-

TxOUT0+

TxOUT1-

TxOUT1+

TxOUT2-

TxOUT2+

TxCLKOUT-

TxCLKOUT+

TxOUT3-

TxOUT3+

PWRDWN

LVDS_GND43

LVDS_GND49

43

49

3

R_RxIN3+

R_RxIN3-

R_RxCLKIN+

R_RxCLKIN-

R_RxIN2+

R_RxIN2-

R_RxIN1+

R_RxIN1-

R_RxIN0+

R_RxIN0-

GND_TFT

SDA_3_5V

J6

J6

MX53505

MX53505

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

SCL_3_5V

R3040RR304

0R

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

SDA_3_5V

R445 NCR445 NC

R442 NCR442 NC

R176 NCR176 NC

R180 0R180 0

R182 NCR182 NC

R3060RR306

0R

SCL_3_5V

2

V_TFT

IO_LVDS_OPTION

ROTATE_OPTION

IO_PLZ_I2C_READY

R177 NCR177 NC

R181 NCR181 NC

R398 NCR398 NC

+3V

Note: +5V for Samsung 32" , AU 26", AU 31.5"

1

+12V for LG Philips 32"

FB1

FB1

BLM31PG121SN1

V_TFT +V_TFT_IN

C1

100nFC1100nF

IO_VsON/DLP_RST/LVDS_OPT

HW_OPT5

V_TFT

PWM_BRT 11,12

Notes:

1. LVDS_OPTION for LCD AU31.5 and LCD Samsung 32"

2. Rotate Option for LCD AU31.5"

3. LCD AU 26" , LCD LG 32", PDP 42" LG,

and PDP 42" SDI Samsung no control

Note:

Install Direct LVDS for SDI PDP & TBD.

BLM31PG121SN1

+

+

C4

C4

ECBp470uF/16

ECBp470uF/16

+3V

R434

R434

4.7K

4.7K

R435

R435

4.7K

4.7K

+V_TFT_IN

GND_TFT

IO_BL_ON_N/PLZ_I2C_READY 11

R302 NCR302 NC

R303 NCR303 NC

R305 NCR305 NC

R307 0RR307 0R

GND_TFT

GND_TFTGND

Install Shifted LVDS for LG PDP & TBD.

IO_LVDS_PD_OUT_N11

R308

R308

4.7K

4.7K

B B

OCLK_OUT6,9,10

OP_VSYNC6,9,10

OP_HSYNC6,9,10

OP_ENABLE6,9,10

OP_FIELD6,10

OCLK_OUT

OP_VSYNC

OP_HSYNC

OP_ENABLE

OP_FIELD

A A

5

IO_LVDS_PD_OUT_N

RV2

OP_A18

RV3

OP_A19

RV4

OP_A20

RV5

OP_A21

RV6

OP_A22

RV1

OP_A17

RV7

OP_A23

GY2

OP_A10

GY3

OP_A11

GY4

OP_A12

GY0

OP_A8

GY1

OP_A9

GY5

OP_A13

GY6

OP_A14

GY7

OP_A15

BU2

OP_A2

BU0

OP_A0

BU1

OP_A1

BU3

OP_A3

BU4

OP_A4

BU5

OP_A5

BU6

OP_A6

BU7

OP_A7

OP_FIELD

OP_HSYNC

OP_VSYNC

OP_ENABLE

RV0

OP_A16

OCLK_OUT

51

52

54

55

56

10

11

12

14

15

16

18

19

20

22

23

24

25

27

28

30

50

31

2

3

4

6

7

8

U2NCU2

TxIN0

TxIN1

TxIN2

TxIN3

TxIN4

TxIN5

TxIN6

TxIN7

TxIN8

TxIN9

TxIN10

TxIN11

TxIN12

TxIN13

TxIN14

TxIN15

TxIN16

TxIN17

TxIN18

TxIN19

TxIN20

TxIN21

TxIN22

TxIN23

TxIN24

TxIN25

TxIN26

TxIN27

TxCLKIN

R1791KR179

1K

TxOUT0-

TxOUT0+

TxOUT1-

TxOUT1+

TxOUT2-

TxOUT2+

TxOUT3-

TxOUT3+

PWRDWN

R_FB

LVDS_GND49

49

+3V_LVDS

48

47

46

45

42

41

40

39

38

37

32

17

Rotated LVDS Driver

R_RxIN0R_RxIN0+

R_RxIN1R_RxIN1+

R_RxIN2R_RxIN2+

R_RxCLKINR_RxCLKIN+

R_RxIN3R_RxIN3+

+3V

R16NCR16

NC

3

(150)

R17NCR17

NC

(150)

OCLK_OUT

+3V_LVDS_PLL

+3V_LVDS+3V_LVDS

1

9

VCC1

GND5

5

13

26

VCC9

GND13

21

VCC26

NC

GND21

GND29

GND53

29

53

34

44

PLL_VCC

PLL_GND33

PLL_GND3535LVDS_GND36

33

36

LVDS_VCC

TxCLKOUT-

TxCLKOUT+

LVDS_GND43

43

4

Note:

MN203 OP signals should be wired in

daisy chain as follows:

CLK termination at the end of

trace.

+3V +3V_LVDS

FB2

FB2

BLM18AG471SN1

BLM18AG471SN1

+

C11

C11

ECBp10uF/10V

ECBp10uF/10V

+

+3V

FB13

FB13

BLM18AG471SN1

BLM18AG471SN1

C9

C9

ECBp10uF/10V

ECBp10uF/10V

C7

C7

ECBp10uF/10V

ECBp10uF/10V

+

+

+

+

C8

C8

ECBp10uF/10V

ECBp10uF/10V

C10

C10

ECBp10uF/10V

ECBp10uF/10V

2

Note:

MN203 OP signals should be wired in

daisy chain as follows:

1. LVDS Tx DS90C385 x2 (One installed)

2. Direct RGB

3. 120-pin connector to output module.

4. CLK termination at the end of

trace.

+

+

+

+

C209

C209

100nF

100nF

C211

C211

100pF

100pF

Title

Title

Title

Profilo Main Board

Profilo Main Board

Profilo Main Board

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

C214

C214

100nF

100nF

C217

C217

100nF

100nF

C208

C208

100nF

100nF

+3V_LVDS_PLL

C215

C215

100pF

100pF

LVDS Transmmiter

LVDS Transmmiter

LVDS Transmmiter

C207

C207

100nF

100nF

1

C218

C218

100nF

100nF

C213

C212

C212

100nF

100nF

of

of

of

712Friday, December 02, 2005

712Friday, December 02, 2005

712Friday, December 02, 2005

C213

100nF

100nF

1.1

1.1

1.1

http://arizanotlari.com

Page 8

5

4

3

2

1

D D

R369

R369

10K

10K

B

Q28

Q28

MMBT3904

MMBT3904

E

C

J22

J22

CON12

CON12

1

2

3

4

5

6

7

8

9

10

11

12

Oplus

Signal

Name

SCL_DLP

SDA_DLP

HW_OPT5

IO_VsON/DLP_RST/LVDS_OPT

IO_DLP_LAMPLITZ

IO_DLP_LAMPENSW

IO_DLP_SYNCVAL

R19 22RR19 22R

R18 22RR18 22R

SCL_3_5V

SDA_3_5V

IO_DLP_PWRGOOD

IO_DLP_RST

IO_DLP_SYNCVAL

IO_DLP_LAMPENSW

IO_VsON/DLP_RST/LVDS_OPT

IO_DLP_LAMPLITZ

HW_OPT5

SDA_3_5V

SDA_3_5V

R368

R367

R367

4K7

4K7

Q27

Q27

MMBT3904

MMBT3904

+5V +3V

R368

10K

10K

B

E

C

R371 NCR371 NC

+3V+5V

R370

R370

4.7K

4.7K

SDA_3

SDA_3

C C

R372

C5

C5

ECBp10uF/10V

ECBp10uF/10V

+3V

R309

R309

4K7

4K7

+

+

C210

C210

100nF

100nF

R310

R310

4K7

4K7

SCL_3_5V

SCL_3_5V

R372

4K7

4K7

Q29

Q29

MMBT3904

MMBT3904

R373

R373

10K

10K

B

E

C

B

E

R376 NCR376 NC

R374

R374

10K

10K

Q30

Q30

MMBT3904

MMBT3904

C

R375

R375

4.7K

4.7K

SCL_3

SCL_3

+5V

+

C216

C216

100nF

100nF

+

C14

C14

ECBp10uF/10V

ECBp10uF/10V

B B

A A

Title

Title

Title

Profilo Main Board

Profilo Main Board

Profilo Main Board

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

DLP Engine Interface

DLP Engine Interface

DLP Engine Interface

1

of

of

of

812Friday, December 02, 2005

812Friday, December 02, 2005

812Friday, December 02, 2005

1.1

1.1

1.1

http://arizanotlari.com

Page 9

5 4 3 2 1

OnBoard HDMI Interface

J23

J23

21

SHELL2

HP DET

+5V

GND

DDC DATA

DDC CLK

NC

CE Remote

CK-

CK Shield

20

D0 Shield

D1 Shield

D2 Shield

SHELL1

HDMI CON

HDMI CON

CK+

D0D0+

D1D1+

D2D2+

D D

HP_DET

19

18

17

HDMI_SDA_IN

16

HDMI_SCL_IN

15

14

CEC

13

RXC-

12

11

RXC+

10

RX0-

9

8

RX0+

7

RX1-

6

5

RX1+

4

RX2-

3

2

RX2+

1

HDMI_5V

R4271KR427

Q31

Q31

BC848B

BC848B

1K

D20

D20

1 2

1N4148

1N4148

C429

C429

Ecap10uF/25V

Ecap10uF/25V

C

R443 1KR443 1K

B

E

R319

R319

100

100

+5V

12

D21

D21

1N4148

+5V_DVI

IO_HDMI_HPD_CTRL

1N4148

+

+

C430

C430

100nF

100nF

R447 NCR447 NC

+3V

R446NCR446

NC

IO_HDMI_CEC 11

D_INA[0..23]

D_INA[0..23]

D_VSYNC

RP3647x4RP3647x4

1 2

D_ACTIVE

D_VSYNC

D_HSYNC

DIN_CLK

D_ACTIVE

D_HSYNC

3 4

5 6

7 8

DIN_CLK

RP3747x4RP3747x4

D_INA1

D_INA0

1 2

3 4

D_INA3

D_INA2

5 6

7 8

RP3847x4RP3847x4

D_INA5

D_INA4

1 2

3 4

D_INA7

D_INA6

5 6

7 8

RP3947x4RP3947x4

D_INA9

D_INA8

1 2

3 4

D_INA11

D_INA10

5 6

7 8

RP4047x4RP4047x4

D_INA13

D_INA12

1 2

3 4

D_INA16

D_INA15

D_INA14

5 6

7 8

D_INA17

1 2

3 4

D_INA19

D_INA18

5 6

7 8

RP4147x4RP4147x4

EDID Circuitry

HDMI_SCL_IN

HDMI_SDA_IN

R378NCR378

NC

R314 100R314 100

R428NCR428

C C

NC

IO_HDMI_CEC

R429NCR429NC

U35

U35

24LCS21A

24LCS21A

7

VCLK

1

E0

2

E1

4

GND

8

6

SCL

VCC

5

SDA

3

WP

R317NCR317

NC