TSZ02201-BD2610GWGW-1-2

© 2012 ROHM Co., Ltd. All rights reserved.

TSZ22111・14・001

www.rohm.com

Power Management Integrated Circuit

BD2610GW

●General Description

BD2610GW is a Power Management Integrated Circuit

(PMIC) designed for “Crystal Cove”. It comprises a part of

a platform named “Bay Trail” to minimize the system

board-area.

●Features

Voltage Rails

■ 6 buck regulators

VCC: Initial 1.0V, I

OMAX

= 8A

IMVP7 SVID compliant, on-the –fly variable

voltage, 10mV/ step

VNN: Initial 1.0V, I

OMAX

= 8A

IMVP7 SVID compliant, on-the –fly variable

voltage, 10mV/ step

V1P0A: 1.0V, I

OMAX

= 1.9A

Fixed output voltage

V1P05S: 1.05V, I

OMAX

= 900mA

Fixed output voltage

V1P8A: 1.8V, I

OMAX

= 1.627A

Fixed output voltage

VDDQ: 1.24V, I

OMAX

= 2.8A

Fixed output voltage

■ 2 buck-boost regulators

V2P85S: 2.85V, I

OMAX

= 550mA

Fixed output voltage

V3P3A: 3.3V, I

OMAX

= 1569mA

Fixed output voltage

■ 1 boost regulator

V5P0S: 5.0V, I

OMAX

= 955mA

Fixed output voltage

■ 5 LDO regulators

VDDQ_VTT: VDDQ/2, I

= 325mA Fixed

OMAX

output voltage

V1P2A: 1.2V, I

OMAX

= 30mA

Fixed output voltage

VREFDQ0: 0.6V (initial value), I

OMAX

= 10mA

5bit VID, 20mV/ step

VREFDQ1: 0.6V (initial value), I

OMAX

= 10mA

5bit VID, 20mV/ step

VREFT/VREFB: 2.0V, I

OMAX

= 1mA

Fixed output voltage

■ BOS (Best Of Supply) / Power Mux Switch

VUSBPHY (V3P3A): 630mΩ (Max.)

VUSBPHY (VSYS): 450mΩ (Max.)

VSDIO (V3P3A): 280mΩ (Max.)

VSDIO (V1P8A): 70mΩ(Max.)

■ General Switch

V1P2S: 480mΩ (Max.)

V1P2SX: 110mΩ (Max.)

V1P8S: 210mΩ (Max.)

V1P8SX: 115mΩ (Max.)

V2P85SX: 190mΩ (Max.)

VHDMI: 590mΩ (Max.)

VSYS_S: 590mΩ (Max.)

Serial Interface

■ I2C interface provides access to configuration

registers.

■ SVID is Intel’s proprietary interface, which enables

the BD2610GW to control regulators for VCC and

VNN.

Burst Control

■ Burst Control Unit supervises the VSYS voltage.

Analog & Digital Battery

■ Communication and battery size reading

GPIO

■ Supports 1.8V CMOS-mode and

Open-drain-mode ( tolerant up to VSYS+ 0.3V)

■ Supports 3.3V CMOS-mode and 3.3V+0.3V

tolerant (Open-drain capable)

GPADC unit

General Purpose ADC for temperature/ voltage/

current measurements. Voltage measurement

accuracy: ±16LSB

Current measurement accuracy: ±10%

Die Temperature measurement accuracy: ±10°C

Temperature monitoring subsystem

■ Continually monitors up to 2 battery thermistors and

up to 3 system-thermistors

○Product structure:Silicon monolithic integrated circuit ○This product is not designed protection against radioactive rays

.

1/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

●Contents

1 Introduction ................................................................................................................................................................................ 7

1-1 Typical Application Circuit ................................................................................................................................................. 7

1-2 Simplified Block Diagram ................................................................................................................................................. 10

1-3 Recommended Component PCB Layout ........................................................................................................................ 11

1-5 Package Dimension (corresponded with rev0.98; 2.4 Package ) .................................................................................. 14

1-5-1 Thermal Derating Curve ............................................................................................................................................. 14

1-6 Ball Configuration ............................................................................................................................................................. 15

1-7 Ball List (corresponded with rev0.98; 2.3 Pin List) ........................................................................................................ 16

2 Electrical Characteristics ........................................................................................................................................................ 28

2-1 Absolute Maximum Ratings (corresponded with rev0.98; 2.5.1 Operational Ratings)................................................ 28

2-2 Operating Ratings (corresponded with rev0.98; 3.2 System Power Map) .................................................................... 31

2-3 Voltage Rails Description ................................................................................................................................................. 32

2-3-1 Voltage Rails - Maximum current and Protection ................................................................ ................................ .... 34

2-4 Current Consumption ....................................................................................................................................................... 36

2-5 Details of Analog Electrical Characteristics ................................................................................................................... 38

2-5-1 VCC (corresponded with_rev0.98; 3.5.1 VCC ) ........................................................................................................ 38

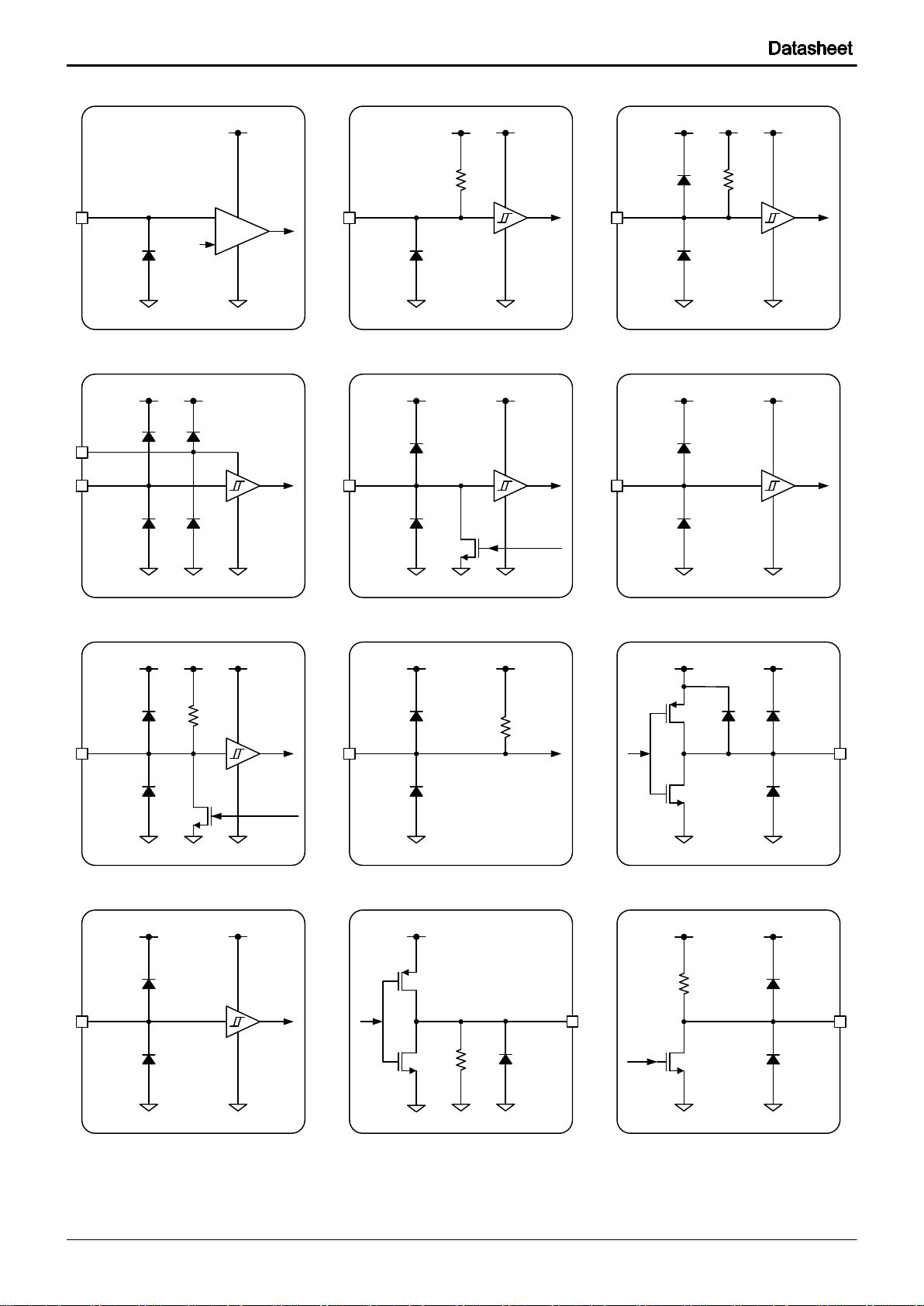

2-5-1-1 VCC Block Diagram (corresponded with_rev0.98; 3.5.1.2 VCC Block Diagram ) ........................................... 38

2-5-1-2 VCC Electrical Characteristics ........................................................................................................................... 39

2-5-1-3 VCC Typical Performance Curve ........................................................................................................................ 40

2-5-2 VNN (corresponded with_rev0.98; 3.5.2 VNN ) ........................................................................................................ 44

2-5-2-1 VNN Block Diagram (corresponded with_rev0.98; 3.5.2.2 VNN Block Diagram ) ........................................... 44

2-5-2-2 VNN Electrical Characteristics ........................................................................................................................... 45

2-5-2-3 VNN Typical Performance Curve ........................................................................................................................ 46

2-5-3 V1P0A (with V1P0S and V1P0SX) (corresponded with_rev0.98; 3.5.3 V1P0A ) ..................................................... 50

2-5-3-1 V1P0A, V1P0S, and V1P0SX Block Diagram (corresponded with_rev0.98; 3.5.3.3 V1P0A Block Diagram )50

2-5-3-2 V1P0A, V1P0S, and V1P0SX Electrical Characteristics ................................................................................... 51

2-5-3-3 V1P0A Typical Performance Curve .................................................................................................................... 52

2-5-4 V1P05S (corresponded with_rev0.98; 3.5.4 V1P05S ) ............................................................................................. 54

2-5-4-1 V1P05S Block Diagram (corresponded with_rev0.98; 3.5.4.3 V1P05S Block Diagram )................................ 54

2-5-4-2 V1P05S Electrical Characteristics ...................................................................................................................... 55

2-5-4-3 V1P05S Typical Performance Curve .................................................................................................................. 56

2-5-5 V1P8A (with V1P8U, V1P8S, and V1P8SX) (corresponded with_rev0.98; 3.5.5 V1P8A ) ...................................... 58

2-5-5-1 V1P8A, V1P8U, V1P8S, and V1P8SX Block Diagram (corresponded with_rev0.98; 3.5.5.3 V1P8A Block

Diagram ) .......................................................................................................................................................................... 58

2-5-5-2 V1P8A, V1P8U, V1P8S, and V1P8SX Electrical Characteristics ...................................................................... 59

2-5-5-3 V1P8A Typical Performance Curve .................................................................................................................... 60

2-5-6 VDDQ (with V1P2S and V1P2SX) (corresponded with_rev0.98; 3.5.6 VDDQ ) ...................................................... 62

2-5-6-1 VDDQ, V1P2S, and V1P2SX Block Diagram (corresponded with_rev0.98; 3.5.6.3 VDDQ Block Diagram) .. 62

2-5-6-2 VDDQ, V1P2S, and V1P2SX Electrical Characteristics .................................................................................... 63

2-5-6-3 VDDQ Typical Performance Curve ..................................................................................................................... 64

2-5-7 V2P85S (with V2P85SX) (corresponded with_rev0.98; 3.5.11 V2P85S) ................................................................. 67

2-5-7-1 V2P85S and V2P85SX Block Diagram (corresponded with_rev0.98; 3.5.11.3 V2P85S Block Diagram) ....... 67

2-5-7-2 V2P85S and V2P85SX Electrical Characteristics .............................................................................................. 68

2-5-7-3 V2P85S Typical Performance Curve .................................................................................................................. 69

2-5-8 V3P3A (with Switches) (corresponded with_rev0.98; 3.5.12 V3P3A) ..................................................................... 71

2-5-8-1 V3P3A, V3P3U, V3P3S, VUSBPHY, and VSDIO Bock Diagram (corresponded with_rev0.98; 3.5.12.3 V3P3A

Block Diagram) ................................................................................................................................................................. 71

2-5-8-2 V3P3A, V3P3U, V3P3S, VUSBPHY, and VSDIO Electrical Characteristics ...................................................... 72

2-5-8-3 V3P3A Typical Performance Curve .................................................................................................................... 73

2-5-9 V5P0S (with VHOST, VBUS, and VHDMI) (corresponded with_rev0.98; 3.5.13 V5P0S) ........................................ 76

2-5-9-1 V5P0S, VHOST, VBUS, and VHDMI Block Diagram (corresponded with_rev0.98; 3.5.13.3 V5P0S Block

Diagram) ........................................................................................................................................................................... 76

2-5-9-2 V5P0S, VHOST, VBUS, and VHDMI Electrical Characteristics ......................................................................... 78

2-5-9-3 V5P0S Typical Performance Curve .................................................................................................................... 79

2-5-10 VDDQ_VTT (corresponded with_rev0.98; 3.5.3.7 VDDQ_VTT) ............................................................................. 81

2-5-10-1 VDDQ_VTT Block Diagram (corresponded with_rev0.98; 3.5.3.3 V1P0A Block Diagram) .......................... 81

2-5-10-2 VDDQ_VTT Electrical Characteristics .............................................................................................................. 81

2-5-10-3 VDDQ_VTT Typical Performance Curve .......................................................................................................... 82

2-5-11 V1P2A (corresponded with_rev0.98; 3.5.5.8 V1P2A) ............................................................................................. 83

2-5-11-1 V1P2A Block Diagram (corresponded with_rev0.98; 3.5.5.3 V1P8A Block Diagram ) .................................. 83

2-5-11-2 V1P2A Electrical Characteristics ................................................................................................ ...................... 83

2-5-11-3 V1P2A Typical Performance Curve .................................................................................................................. 84

2-5-12 VREFDQ0 / VREFDQ1 (corresponded with_rev0.98; 3.5.5.9 VREFDQ0 / 3.5.5.10 VREFDQ1 ) ........................... 85

2-5-12-1 VREFDQ Block Diagram (corresponded with_rev0.98; 3.5.5.3 V1P8A Block Diagram) ............................... 85

2-5-12-2 VREFDQ Electrical Characteristics .................................................................................................................. 86

2-5-12-3 VREFDQ Typical Performance Curve ............................................................................................................... 87

2-5-13 VREFT/VREFB (corresponded with_rev0.98; 3.5.7 VREF) .................................................................................... 88

2/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

2-5-13-1 VREFT/VREFB Block Diagram .......................................................................................................................... 88

2-5-13-2 VREFT/VREFB Electrical Characteristics (corresponded with_rev0.98; 3.5.7 VREF) .................................. 88

2-5-14 VSYS Switches (corresponded with_rev0.98; 3.5.8 VSUS_U, 3.5.9 VSYS_SX, 3.5.10 VSYS_S) ........................ 89

2-5-14-1 VSYS Switches Block Diagram ........................................................................................................................ 89

2-5-14-2 VSYS Switches Electrical Characteristics ....................................................................................................... 90

2-5-14-3 VSYS Switches Control Registers ................................................................................................................... 91

2-5-15 VREF25 ...................................................................................................................................................................... 93

2-5-15-1 Block Diagram ................................................................................................................................................... 93

2-5-15-2 Electrical Characteristics .................................................................................................................................. 93

2-5-16 Back-up Supply Charging (corresponded with_rev0.98; 4.8.1 Back-up Supply Charging) ............................... 94

2-5-16-1 BKUPCHG Block Diagram ................................................................................................................................ 94

2-5-16-2 BKUPCHG Electrical Characteristics ............................................................................................................... 94

2-5-17 GPADC (corresponded with_rev0.98; 4.7 ADC) ................................................................................................ ..... 95

2-5-17-1 GPADC Block Diagram ...................................................................................................................................... 96

2-5-17-2 GPADC Electrical Characteristics .................................................................................................................... 97

2-5-17-3 GPADC Typical Performance Curve ................................ ................................................................................. 98

2-5-17-3-1 Die Temperature .......................................................................................................................................... 99

2-5-17-3-2 Battery and System Temperature ............................................................................................................ 100

2-5-17-3-3 VR Current Monitor (corresponded with_rev0.98; 3.5.15 Current Monitor) ......................................... 101

2-5-18 SVID Interface (corresponded with_rev0.98; 3.4.1 SVID) .................................................................................... 104

2-5-18-1 SVID Block Diagram ................................................................................................ ................................ ........ 104

2-5-18-2 SVID Electrical Characteristics ...................................................................................................................... 105

2-5-18-3 Data Sampling and Timing .............................................................................................................................. 106

3 Control of Voltage Rails......................................................................................................................................................... 107

3-1 SVID I/F (corresponded with_rev0.98; 3.4.1 SVID) ....................................................................................................... 107

3-1-1 SVID Command Set (corresponded with_rev0.98; 3.4.1.4 SVID Command Set) ................................................. 107

3-1-2 SVID Register Set (corresponded with_rev0.98; 3.4.1.5 SVID Register Set) ....................................................... 108

3-1-3 VID DAC Table for VCC & VNN (corresponded with_rev0.98; 3.4.6 VID DAC Table for VCC & VNN) ................ 111

3-2 Low Power State Control Signals .................................................................................................................................. 113

3-3 VCC Control (corresponded with_rev0.98; 3.5.1 VCC) ................................................................................................ 113

3-3-1 VCC Power States .................................................................................................................................................... 113

3-3-1-1 PS0 – Active State ............................................................................................................................................. 114

3-3-1-2 PS1 – NA............................................................................................................................................................. 115

3-3-1-3 PS2 – C6 at S0idle ............................................................................................................................................. 115

3-3-1-4 PS3 – C6 at S0IX ................................................................................................................................................ 115

3-3-2 VCC Register ............................................................................................................................................................ 115

3-4 VNN Control (corresponded with_rev0.98; 3.5.2 VNN) ................................................................................................ 117

3-4-1 VNN Power States .................................................................................................................................................... 117

3-4-1-1 Active State (S0 State) ....................................................................................................................................... 118

3-4-1-2 S0IX State ........................................................................................................................................................... 118

3-4-2 VNN Register ............................................................................................................................................................ 118

3-5 V1P0A (corresponded with_rev0.98; 3.5.3 V1P0A) ....................................................................................................... 119

3-5-1 V1P0A Power States ................................................................................................................................................. 119

3-5-1-1 Active State (S0 State) ....................................................................................................................................... 119

3-5-1-2 S0IX State ........................................................................................................................................................... 119

3-5-1-3 S3 & S4 State...................................................................................................................................................... 119

3-5-2 V1P0A Register ......................................................................................................................................................... 119

3-5-2-1 V1P0S Register (corresponded with_rev0.98; 3.5.3.5 V1P0S) ....................................................................... 120

3-5-2-2 V1P0SX Register (corresponded with_rev0.98; 3.5.3.6 V1P0SX) .................................................................. 120

3-6 V1P05S (corresponded with_rev0.98; 3.5.4 V1P05S) ................................................................................................... 121

3-6-1 V1P05S Power States ............................................................................................................................................... 121

3-6-1-1 Active State (S0 State) ....................................................................................................................................... 121

3-6-1-2 S0IX State ........................................................................................................................................................... 121

3-6-2 V1P05S Register ....................................................................................................................................................... 121

3-7 V1P8A (corresponded with_rev0.98; 3.5.5 V1P8A) ....................................................................................................... 122

3-7-1 V1P8A Power States ................................................................................................................................................. 122

3-7-1-1 Active State (S0 State) ....................................................................................................................................... 122

3-7-1-2 S0IX State ........................................................................................................................................................... 122

3-7-1-3 S3 & S4 State...................................................................................................................................................... 122

3-7-2 V1P8A Register ......................................................................................................................................................... 122

3-7-2-1 V1P8U Register (corresponded with_rev0.98; 3.5.5.5 V1P8U) ....................................................................... 123

3-7-2-2 V1P8S Register (corresponded with_rev0.98; 3.5.5.6 V1P8S) ....................................................................... 123

3-7-2-3 V1P8SX Register (corresponded with_rev0.98; 3.5.5.7 V1P8SX) .................................................................. 124

3-8 VDDQ (corresponded with_rev0.98; 3.5.6 VDDQ)......................................................................................................... 125

3-8-1 VDDQ Power States .................................................................................................................................................. 125

3-8-1-1 Active State (S0 State) ....................................................................................................................................... 125

3-8-1-2 S0IX State ........................................................................................................................................................... 125

3-8-1-3 S3 State .............................................................................................................................................................. 125

3-8-2 VDDQ Register.......................................................................................................................................................... 125

3-8-2-1 V1P2S Register (corresponded with_rev0.98; 3.5.6.5 V1P2S) ....................................................................... 126

3/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

3-8-2-2 V1P2SX Register (corresponded with_rev0.98; 3.5.6.6 V1P2SX) .................................................................. 127

3-9 V2P85S ................................................................................................ ................................ ............................................. 128

3-9-1 V2P85S Register (corresponded with_rev0.98; 3.5.11 V2P85S) ........................................................................... 128

3-9-1-1 V2P85SX Register (corresponded with_rev0.98; 3.5.11.4 V2P85SX) ............................................................. 129

3-10 V3P3A (corresponded with_rev0.98; 3.5.12 V3P3A) ................................................................................................... 130

3-10-1 V3P3A Register ....................................................................................................................................................... 130

3-10-1-1 V3P3U Register (corresponded with_rev0.98; 3.5.12.4 V3P3U) ................................................................... 131

3-10-1-2 V3P3S Register (corresponded with_rev0.98; 3.5.12.5 V3P3S) ................................................................... 131

3-10-1-3 VUSBPHY Control (corresponded with_rev0.98; 3.5.12.6 VUSBPHY)......................................................... 132

3-10-1-4 VSDIO Register (corresponded with_rev0.98; 3.5.12.7 VSDIO) ................................................................... 132

3-11 V5P0S (corresponded with_rev0.98; 3.5.13 V5P0S) ................................................................................................... 133

3-11-1 V5P0S Register ....................................................................................................................................................... 133

3-11-1-1 VHOST Register (corresponded with_rev0.98; 3.5.13.4 VHOST) ................................................................. 134

3-11-1-2 VBUS Control (corresponded with_rev0.98; 3.5.13.5 VBUS) ....................................................................... 135

3-11-1-3 VHDMI Control (corresponded with_rev0.98; 3.5.13.6 VHDMI) .................................................................... 136

3-12 VDDQ_VTT (corresponded with_rev0.98; 3.5.3.7 VDDQ_VTT) .................................................................................. 137

3-12-1 VDDQ_VTT Register ................................................................ ............................................................................... 137

3-13 VREFDQ0 / VREFDQ1 (corresponded with_rev0.98; 3.5.5.9 VREFDQ0 / 3.5.5.10 VREFDQ1) ................................. 138

3-13-1 Register ................................................................................................................................................................... 138

4 Interfaces and Subsystems .................................................................................................................................................. 140

4-1 Battery Subsystem (corresponded with_rev0.98; 4.1 Battery Subsystem) ............................................................... 140

4-1-1 Block diagram........................................................................................................................................................... 140

4-1-2 Battery Presence Detection (corresponded with_rev0.98; 4.1.2.1 Battery Presence Detection)....................... 141

4-1-2-1 Battery Presence Detection Electrical Characteristics .................................................................................. 141

4-1-3 Battery Voltage Monitor (corresponded with_rev0.98; 4,1,1 Features of Battery Subsystem) .......................... 141

4-1-4 BATID(BSI) Sensing (corresponded with_rev0.98; 4,1,2.2 BSI Sensing) ............................................................. 141

4-1-5 Digital Battery Communication (corresponded with_rev0.98; 4,1,2.3 Digital Battery Communication) ........... 141

4-1-5-1 Digital Battery Communication Electrical Characteristics ............................................................................. 142

4-1-6 Battery Temperature Monitor (corresponded with_rev0.98; 4,1,1 Features of Battery Subsystem) ................. 142

4-2 Back-up Battery Management (corresponded with_rev0.98; 4,8 Back-up Battery Management) ............................ 143

4-2-1 Block diagram........................................................................................................................................................... 143

4-2-2 Register ..................................................................................................................................................................... 144

4-2-3 External application circuit...................................................................................................................................... 144

4-3 I/O Characteristics (corresponded with_rev0.98; 4,2 I/O Requirements) ................................................................... 145

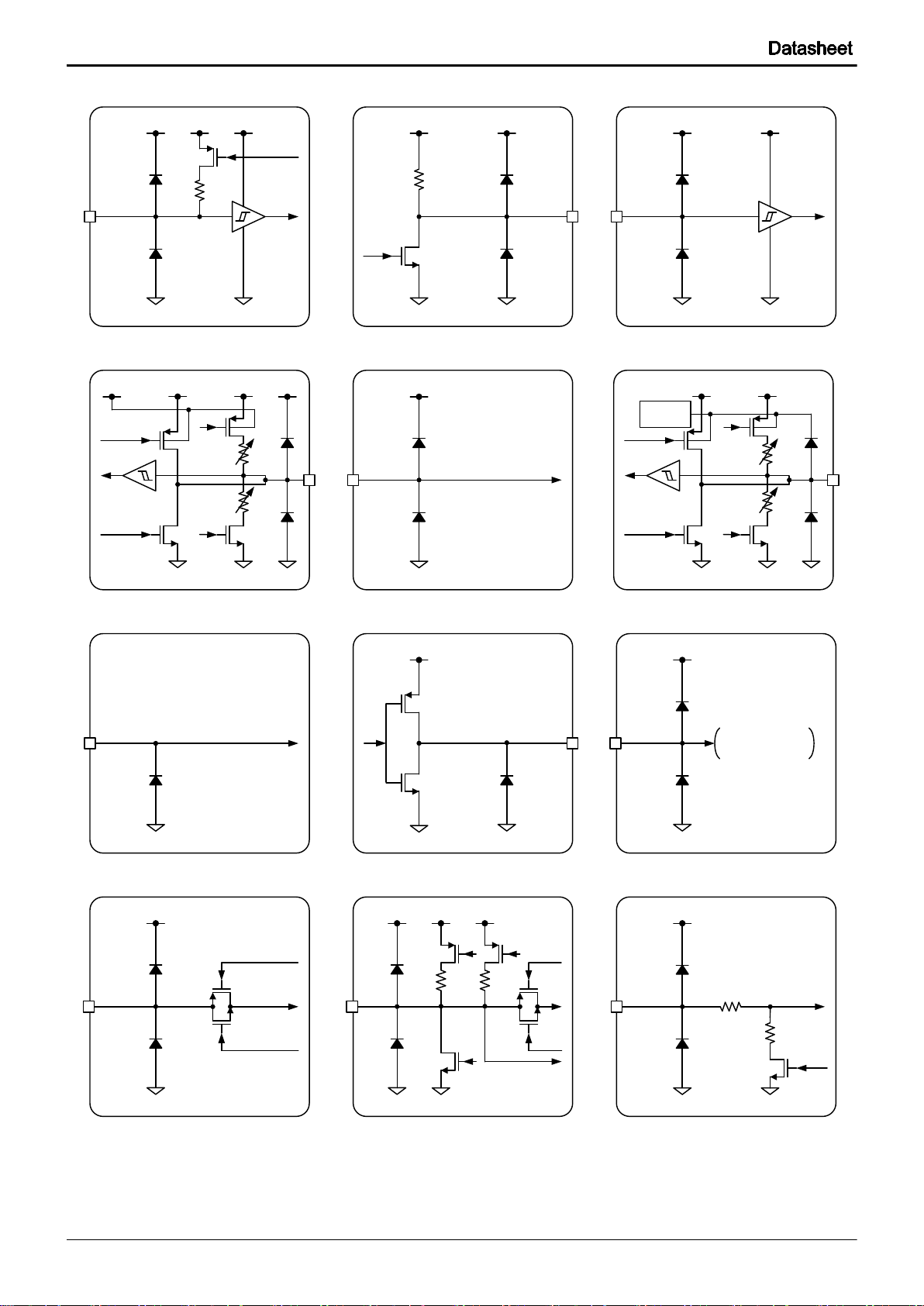

4-3-1 Block diagram........................................................................................................................................................... 145

4-3-2 I2C (Slave) (corresponded with_rev0.98; 4,3 SOC I2C (Slave)) ............................................................................ 146

4-3-2-1 I2C (Slave) Block Diagram ................................................................................................................................ 146

4-3-2-2 I2C (Slave) Electrical Characteristics .............................................................................................................. 147

4-3-2-3 I2C (Slave) Protocol ........................................................................................................................................... 149

4-3-2-4 Register .............................................................................................................................................................. 150

4-3-3 I2C (Master for Debugging) (corresponded with_rev0.98; 4,4 I2C (Master for Debugging)) .............................. 151

4-3-3-1 I2C (Master) Block Diagram .............................................................................................................................. 151

4-3-3-2 I2C (Master) Electrical Characteristics ............................................................................................................ 151

4-3-4 Sideband / SOC Control Signals (corresponded with_rev0.98; 4,6 Sideband / SOC Control Signals) ............. 153

4-3-4-1 Sideband / SOC Control Signals Block Diagram ............................................................................................ 153

4-3-4-2 Sideband / SOC Control Signals Electrical Characteristics........................................................................... 154

4-3-4-3 Pin Description .................................................................................................................................................. 155

4-3-4-3-1 RSMRST_B .................................................................................................................................................. 155

4-3-4-3-2 DRAMPWROK ............................................................................................................................................. 155

4-3-4-3-3 SLP_S0IX_B ................................................................................................................................................ 155

4-3-4-3-4 SLP_S3_B ................................................................................................ ................................ .................... 155

4-3-4-3-5 SLP_S4_B ................................................................................................ ................................ .................... 155

4-3-4-3-6 VCCAPWROK .............................................................................................................................................. 155

4-3-4-3-7 COREPWROK .............................................................................................................................................. 155

4-3-4-3-8 PLTRST_B ................................................................................................................................................... 156

4-3-4-3-9 SUSPWRDNACK ......................................................................................................................................... 156

4-3-4-3-10 ACPRESENT .............................................................................................................................................. 156

4-3-4-3-11 BATLOW_B ................................................................................................................................................ 156

4-3-4-3-12 IRQ ............................................................................................................................................................. 156

4-3-4-3-13 THERMTRIP_B .......................................................................................................................................... 156

4-3-4-3-14 PROCHOT_B ............................................................................................................................................. 156

4-3-4-3-15 SDMMC3_1P8_EN ..................................................................................................................................... 156

4-3-4-3-16 SDMMC3_PWR_EN_B .............................................................................................................................. 157

4-3-4-3-17 Power Button and Utility Button .............................................................................................................. 158

4-3-4-3-18 PWRBTNIN_B and PWRBTN_B ............................................................................................................... 159

4-3-4-3-19 Forcing a Cold Off..................................................................................................................................... 160

4-3-4-3-20 UIBTN_B .................................................................................................................................................... 161

4-3-4-3-21 SDWN_B .................................................................................................................................................... 161

4-3-4-4 Configuration Registers .................................................................................................................................... 161

4-3-5 GPIO (corresponded with_rev0.98; 4,9 GPIO)........................................................................................................ 164

4/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

4-3-5-1 GPIO Block Diagram ......................................................................................................................................... 165

4-3-5-2 GPIO Electrical Characteristics ........................................................................................................................ 166

4-3-6 PWM (corresponded with_rev0.98; 4,9.4 PWM) ..................................................................................................... 167

4-3-6-1 PWM Block Diagram .......................................................................................................................................... 167

4-3-6-2 PWM Description ............................................................................................................................................... 167

4-3-6-3 PWM Electrical Characteristics ........................................................................................................................ 168

4-3-6-4 PWM Control Register ....................................................................................................................................... 168

4-3-7 Display Panel Control (corresponded with_rev0.98; 4,9.5 Display Panel Control) ............................................. 170

4-3-7-1 Display Panel Control Block Diagram ............................................................................................................. 170

4-3-8 External Charger Control ......................................................................................................................................... 172

4-3-8-1 External Charger Control Block Diagram ........................................................................................................ 172

4-3-8-2 External Charger Control Electrical Characteristics ...................................................................................... 173

5 Control and Monitoring ......................................................................................................................................................... 174

5-1 Non – Volatile Memory (NVM)......................................................................................................................................... 174

5-1-1 Initial load Sub-system ............................................................................................................................................ 174

5-1-1-1 Execution ........................................................................................................................................................... 174

5-1-1-1-1 Execution ........................................................................................................................................................ 174

5-1-1-2 Initial Load Instruction Memory ....................................................................................................................... 175

5-1-1-3 External I2C-EEPROM Access Registers ........................................................................................................ 176

5-1-1-3-1 External I2C-EEPROM access sequence .................................................................................................. 178

5-1-1-4 Initial Load Sequence ........................................................................................................................................ 179

5-1-1-5 Initial Load Control Registers ........................................................................................................................... 180

5-1-1-6 Instruction Set ................................................................................................................................................... 181

5-1-1-6-1 Type 1 Instruction ....................................................................................................................................... 181

5-1-1-6-2 Type 2 Instruction ....................................................................................................................................... 181

5-1-1-6-3 Type 3 Instruction ....................................................................................................................................... 181

5-1-1-6-4 Type 0 Instruction ....................................................................................................................................... 181

5-1-1-6-5 Code Set ...................................................................................................................................................... 182

5-1-1-7 Down load flow .................................................................................................................................................. 183

5-1-1-8 Download program Format ............................................................................................................................... 184

5-1-1-9 CRC16 ................................................................................................................................................................. 184

5-2 Task List Processor ........................................................................................................................................................ 185

5-2-1 Execution .................................................................................................................................................................. 185

5-2-2 TLP Instruction Memory (TLP IM) ........................................................................................................................... 185

5-2-2-1 TLP Instruction Memory Access Registers ..................................................................................................... 186

5-2-2-2 TLP Instruction Memory Boundary Registers ................................................................................................. 187

5-2-3 Instruction Set .......................................................................................................................................................... 190

5-2-3-1 TLP: Power Sequencing.................................................................................................................................... 190

5-2-3-1-1 VR_ON, VR_OFF ......................................................................................................................................... 191

5-2-3-1-2 IO_CTRL ...................................................................................................................................................... 191

5-2-3-1-3 NOP .............................................................................................................................................................. 192

5-2-3-1-4 END .............................................................................................................................................................. 192

5-3 Input Power Source Detection ....................................................................................................................................... 193

5-3-1 Valid Battery Voltage Detection Thresholds .......................................................................................................... 197

5-3-2 System Voltage (VSYS) Detection Threshold ........................................................................................................ 200

5-3-3 Battery Removal Detection ...................................................................................................................................... 200

5-3-4 USB Adapter (VBUS) Detection Threshold ............................................................................................................ 201

5-3-5 AC/DC Adapter (VDCIN) Detection Threshold ........................................................................................................ 202

5-3-5-1 Power Source Detect Configuration Register ................................................................................................. 203

5-3-6 External Charger Control Signals ........................................................................................................................... 203

5-4 Power States .................................................................................................................................................................... 205

5-4-1 G3 State ..................................................................................................................................................................... 207

5-4-2 SOC G3 State ............................................................................................................................................................ 207

5-4-3 SOC S0 State ............................................................................................................................................................ 208

5-4-4 S0IX State .................................................................................................................................................................. 208

5-4-5 SOC S3 State ............................................................................................................................................................ 210

5-4-6 SOC S4 State ............................................................................................................................................................ 211

5-5 Power State Transitions .................................................................................................................................................. 212

5-5-1 Cold Boot .................................................................................................................................................................. 213

5-5-2 Warm Reset ............................................................................................................................................................... 218

5-5-3 Enter SOC S0IX ......................................................................................................................................................... 218

5-5-4 Exit SOC S0IX ........................................................................................................................................................... 221

5-5-5 Enter SOC S3 ............................................................................................................................................................ 224

5-5-6 Exit SOC S3............................................................................................................................................................... 226

5-5-7 Enter SOC S4 ............................................................................................................................................................ 229

5-5-8 Exit SOC S4............................................................................................................................................................... 232

5-5-9 Cold Off ..................................................................................................................................................................... 234

5-5-10 Modem Reset .......................................................................................................................................................... 242

5-6 PMIC Control Events and Indicators ............................................................................................................................. 244

5-6-1 PMIC Resets .............................................................................................................................................................. 244

5/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

5-6-2 MODEMCTRL ............................................................................................................................................................ 245

5-6-3 Wake Events ............................................................................................................................................................. 246

5-6-4 PMIC Catastrophic and Critical Events .................................................................................................................. 247

5-6-5 Reset Source Indicators .......................................................................................................................................... 248

5-6-6 Wake Source Indicators ........................................................................................................................................... 249

5-7 IRQ.................................................................................................................................................................................... 250

5-7-1 Overview ................................................................................................................................................................... 250

5-7-2 Interrupt Descriptions .............................................................................................................................................. 250

5-7-3 First-Level Interrupts (IRQLVL1) ............................................................................................................................. 251

5-7-4 Second-Level Interrupts .......................................................................................................................................... 252

5-8 Applications of General Purpose ADC .......................................................................................................................... 255

5-8-1 GPADC Manual Conversion Requests .................................................................................................................... 256

5-8-2 VR CURRENT Monitoring ........................................................................................................................................ 260

5-8-2-1 VR CURRENT Monitoring Specification .......................................................................................................... 261

5-8-3 Thermal Monitoring .................................................................................................................................................. 263

5-8-3-1 Thermal Sensor (Thermistor) Configuration ................................................................................................... 264

5-8-3-2 Thermal Measurement Results and Alerts ...................................................................................................... 264

5-8-3-3 Critical Thermal Events ..................................................................................................................................... 273

5-9 General Purpose I/O ........................................................................................................................................................ 277

5-9-1 Control Registers ..................................................................................................................................................... 277

5-9-2 Initial Value of GPIO Registers ................................................................................................................................ 278

5-9-3 GPIO IRQ Registers .................................................................................................................................................. 278

5-10 Burst Control Unit ......................................................................................................................................................... 281

5-10-1 BCU Block Diagram ............................................................................................................................................... 281

5-10-2 BCU VSYS Input Trip Points ................................................................................................................................ .. 282

5-10-2-1 BCU VSYS Trip Point Thresholds .................................................................................................................. 282

5-10-2-2 VSYS Waveform Example with Zones ........................................................................................................... 284

5-10-2-3 BCU VSYS Trip Point Registers ..................................................................................................................... 285

5-10-3 BCU Output Control Signals ................................................................................................................................. 287

5-10-3-1 BCU Output Control Logic Diagrams ............................................................................................................ 288

5-10-3-2 BCU Output Control Signal Behavior Registers ........................................................................................... 289

5-10-4 BCU Interrupts and Status Flags .......................................................................................................................... 290

5-10-4-1 BCU Interrupt Logic and Behavior ................................................................................................................. 291

5-10-4-2 BCU Interrupt Registers .................................................................................................................................. 291

5-10-4-3 BCU Status Flag Registers ............................................................................................................................. 292

5-11 Debug Ports ................................................................................................................................................................... 294

5-11-1 SVID Debug Bus ..................................................................................................................................................... 294

5-11-2 I2C Debug Bus ........................................................................................................................................................ 296

6 Register Map .......................................................................................................................................................................... 298

Notice ......................................................................................................................................................................................... 304

6/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

SPI

V2P85S

Buck-Boost

Converter

2.9V 550mA

VSYS

V2P85S

V3P3A

Buck-Boost

Converter

3.3V 1569mA

V5P0S

Boost

Converter

5.0V 955mA

PWM-

Pulse Width Modulated

Outputs

Power

Sequencer

I2C Interface

(Slave, Master)

System Control-

Reset, Power,

and

Control Signals

Buck Converters

Buck-Boost Converters

DIGITAL Interface

ADC / Power Interface

State

Machine

Registers

Multi-phase BuckConverters

BD2610GW

VDCIN

Power Source

Detection

GPIOHV-

High Voltage

General Purpose I/O

BCU-

Burst Control Unit

Output Signals

VSYS_SX_EN_B

VSYS_S

VSYS_U_EN_B

Power Switch

Control

Switch

VSYS2 Switch

VBUS

I2C_VIO

I2C_CLK

I2C_DATA

DEBUG_I2C_CLK

DEBUG_I2C_DATA

DEBUG_CS

SVID

(Slave)

SVID_CLK

SVID_DIO

DEBUG_SVID_CLK

DEBUG_SVID_DIO

SVID_ALERT_B

DEBUG_SVID_ALERT_B

PWRBTNIN_B

PWRBTN_B

SLP_S0IX_B

SLP_S3_B

SLP_S4_B

PLTRST_B

SUSPWRNACK

ULPI_VBUS_EN

THERMTRIP_B

BCUDISA

BCUDISB

BCUDISCRIT

PWM2

PWM1

PWM0

Display Panel

Control

BACKLIGHT_EN

PANEL_EN

ACPRESENT

BATLOW_B

SDWN_B

MODEM_OFF_B

COREPWROK

RSMRST_B

IRQ

PROCHOT_B

DRAMPWROK

VCCAPWROK

GPIO1VDD

GPIO1P0_UIBTN_B

GPIO1P1

GPIO1P2

GPIO1P3

GPIO1P4

GPIO1P5

GPIO1P6

GPIO1P7

GPIOLV-

LOW Voltage

General Purpose I/O

GPIO0VDD

GPIO0P0_BATIDIN

GPIO0P1_BATIDOUT

GPIO0P2

GPIO0P3

GPIO0P4

GPIO0P5

GPIO0P6

GPIO0P7

ADCVDD

SYSTHERM0

SYSTHERM1

SYSTHERM2

BPTHERM0

BPTHERM1

SDMMC3_1P8_EN

SDMMC3_PWR_EN_B

BATID

VREFT

VREFB

VBATSENSE

VSYS1

VSYS2

VBATBKUP

I2CM_CLK

I2CM_DATA

BACKUP

Registers

VSYS

SwitchVSYS

MUX

Switch

V3P3A

VSYS2

VUSBPHY

V1P2S

Switch

VDDQ

V1P2SX_VIN

V1P2SX

Switch

VSYS_S

VSYS_U

VSYS_SX

VUSBPHY

V1P2S

V1P2SX

V1P8S

Switch

V1P8A

V1P8S_VIN

V1P8SX

Switch

V1P8S

V1P8SX

V2P85SX

Switch

V2P85SX_VIN

V2P85S

VSYS_SX_FB

VSYS_U_FB

V3P3U_EN_B

SwitchV3P3A V3P3U

V3P3U_FB

V3P3S_EN_B

SwitchV3P3A V3P3S

V3P3S_FB

VHOST_EN

Current Limit

Switch

V5P0S VHOST

VBUS_EN

Current Limit

Switch

V5P0S VBUS

VHDMI

VHDMI_VIN

V2P85SX

Current Limit

Switch

V5P0S

VHDMI

V1P8U_EN_B

SwitchV1P8A V1P8U

V1P8U_FB

V1P0S_EN

V1P0SX_EN

SwitchV1P0A

SwitchV1P0A V1P0SX

V1P0S

V1P0S_FB

V1P0SX_FB

MUX

Switch

VSDIO

VSDIO

V1P8A

V3P3A

VSDIO_V1P8A_VIN

VSDIO_V3P3A_VIN

Power Switch & External Switch Control

V1P2A

Liner Voltage Regulator

1.2V 30mA

VDDQ_VTT

Liner Voltage Regulator

VDDQ/2 325mA

VREFDQ0

Liner Voltage Regulator

0.6V-1.22V 10mA

VDDQ_VTT_VIN

VDDQ_VTT

VDDQ_VTT_GND

V1P8S

V1P0A

VDDQ_VTT

VDDQ_VTT_FB

V1P8A

V3P3A

From Main Battery Pack

USB

V1P2A

V1P8S_VIN

VREF25_0

VREF25_1

VREF25_2

GND0

GND1

GND2

GND3

GND4

GND5

VLP

Liner Voltage Regulator

VREF25

RTC_POR

V2P85S_VIN

V2P85S_LX0

V2P85S_GND

V2P85S_FBP

V2P85S_LX1

V2P85S

FEED BACK

VNN_FBP

VNN

VNN

5Multi-Phase

Buck Converter

0.65V -1.2V

8A

VSYS

VNN_COMP

VSYS

VNN_GND4

VNN_LX4

VNN_VIN4

VNN_GND0

VNN_LX0

VNN_VIN0

GND SENSE

VCC_FBN

VCC

VCC

5Multi-Phase

Buck Converter

0.65V -1.2V

8A

VSYS

VCC_COMP

VSYS

VCC_GND4

VCC_LX4

VCC_VIN4

VCC_GND0

VCC_LX0

VCC_VIN0

FEED BACK

VCC_FBP

V1P0A

VSYS

V1P0A_GND0,1

V1P0A_LX0,1

V1P0A_VIN0,1

V1P0A_FBP

V1P05S

VSYS

V1P05S_GND

V1P05S_LX

V1P05S_VIN

V1P05S_FBP

V1P8A

VSYS

V1P8A_GND

V1P8A_LX

V1P8A_VIN

V1P8A_FBP

VDDQ

VSYS

VDDQ_GND0,1

VDDQ_LX0,1

VDDQ_VIN0,1

VDDQ_FBP

VSYS

V3P3A

V3P3A_VIN

V3P3A_LX00,01

V3P3A_GND

V3P3A_FBP

V3P3A_LX10,11

V3P3A

V5P0S

VSYS

V5P0S_GND0,1

V5P0S_LX0,1

V5P0S0,1

V5P0S_FB

VREFDQ0

V1P8S_VIN

Charger

Control

CHGDET_B

CHGRINT_B

ILIM0

ILIM1

AC Adapter

GPADC

Referance

GPADC1

10bits Analog to Digital

Converters

GPADC2

10bits Analog to Digital

Converters

(VR Current Monitor)

VCC Output Current

VNN Output Current

V1P0A Output Current

V1P05S Output Current

VDDQ Output Current

From Main Battery Pack

Digital Battery Communication

Interface

Die Temp

VREF25

V1P8SV1P8S

V1P0SV1P0S

Power Botton

V1P0S

SOC

Platform

External

EEPROM

MISC

VCC Current Monitor

VNN Output

Current Monitor

V1P0A Output

Current Monitor

V1P05S Output

Current Monitor

VDDQ Output

Current Monitor

V1P0A

Buck Converter

1.0V 1900mA

V1P05S

Buck Converter

1.05V 900mA

V1P8A

Buck Converter

1.8V 1627mA

VDDQ

Buck Converter

1.24V 2800mA

L

VNN

C

IVNN

C

OVNN

C

IVNN

L

VNN

L

VCC

L

VCC

C

IVCC

C

OVCC

VDDQ_VTT_R

VREFDQ1

Liner Voltage Regulator

0.6V-1.22V 10mA

VREFDQ1

V1P8S_VIN

VSYS

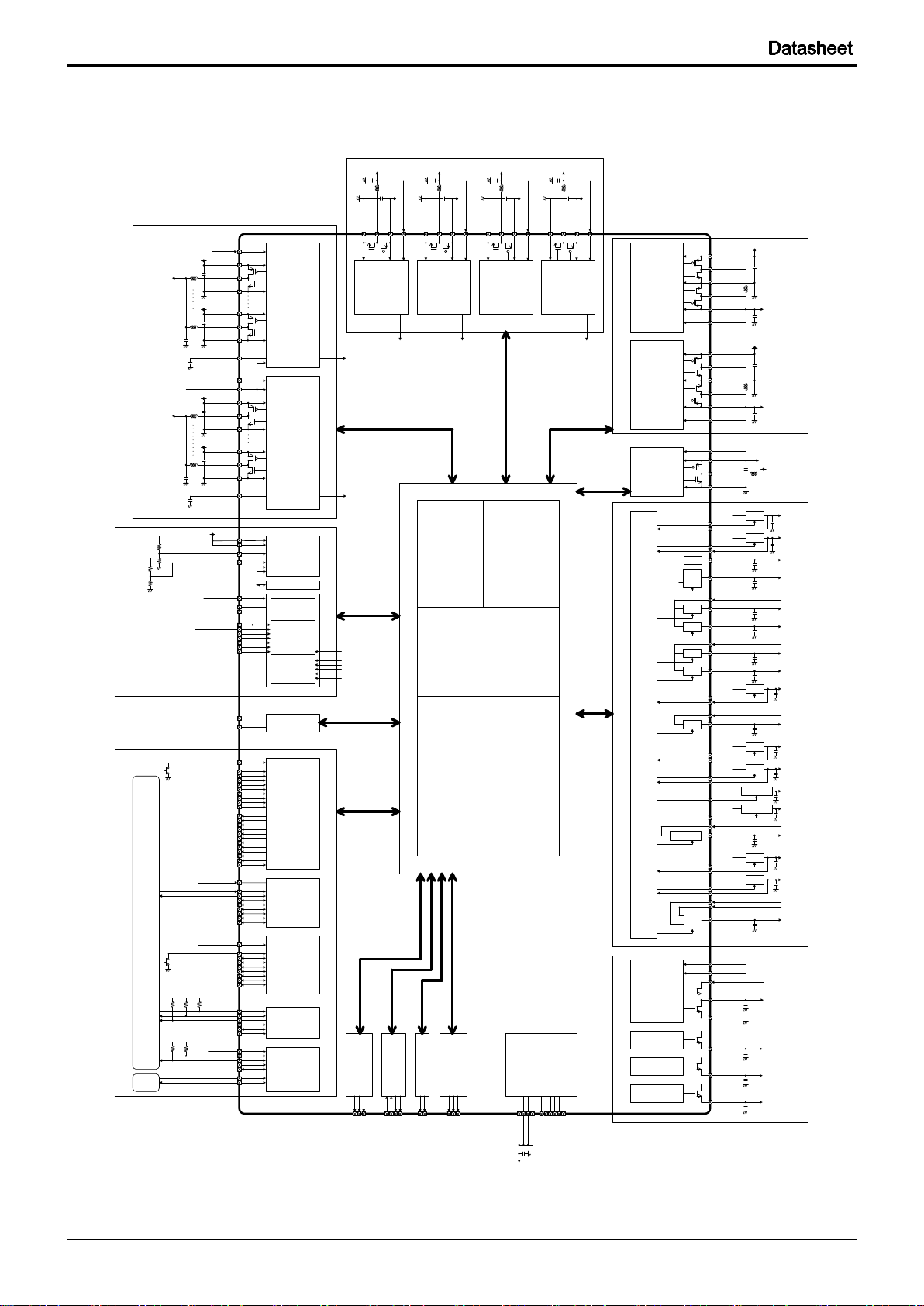

1 Introduction

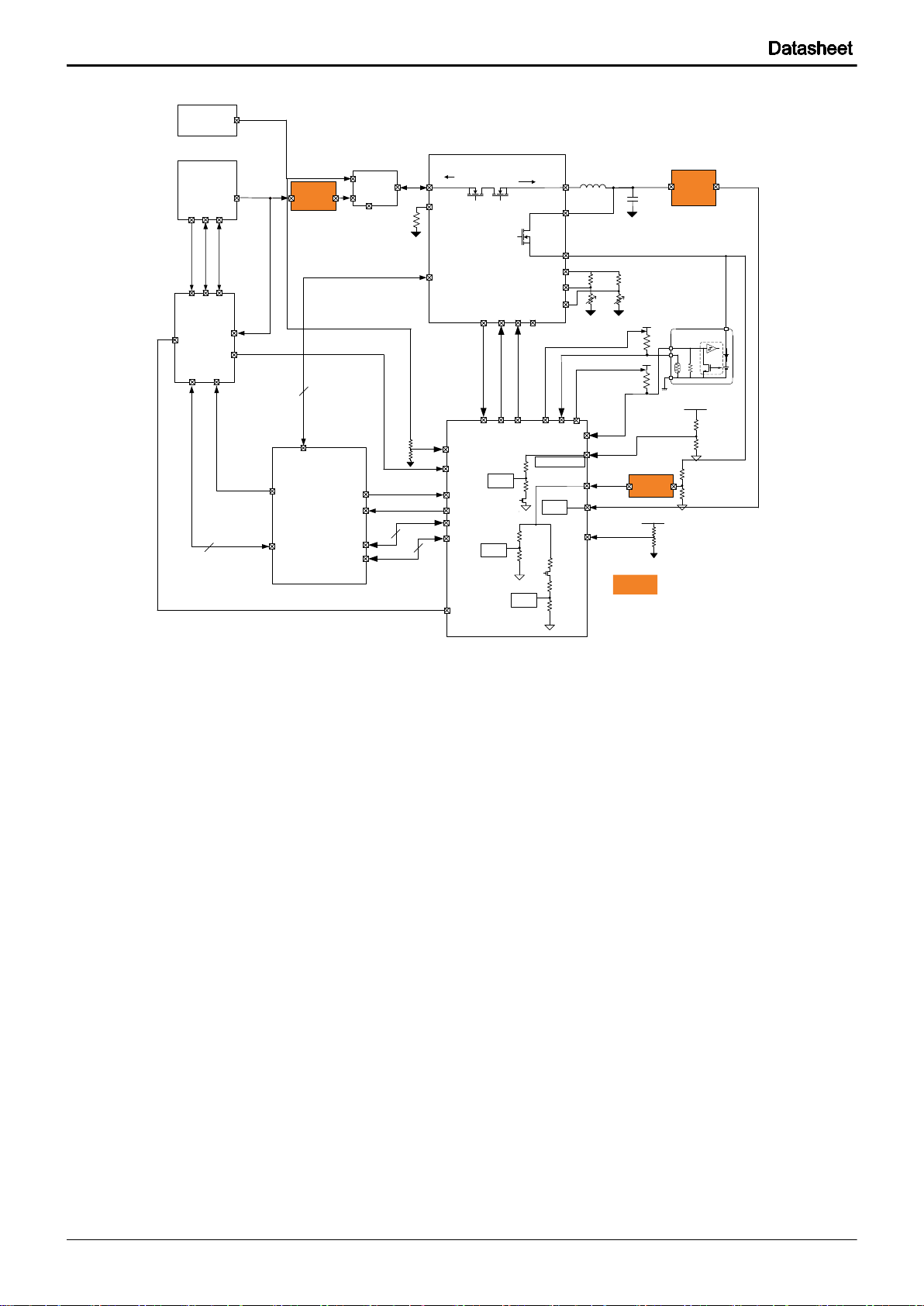

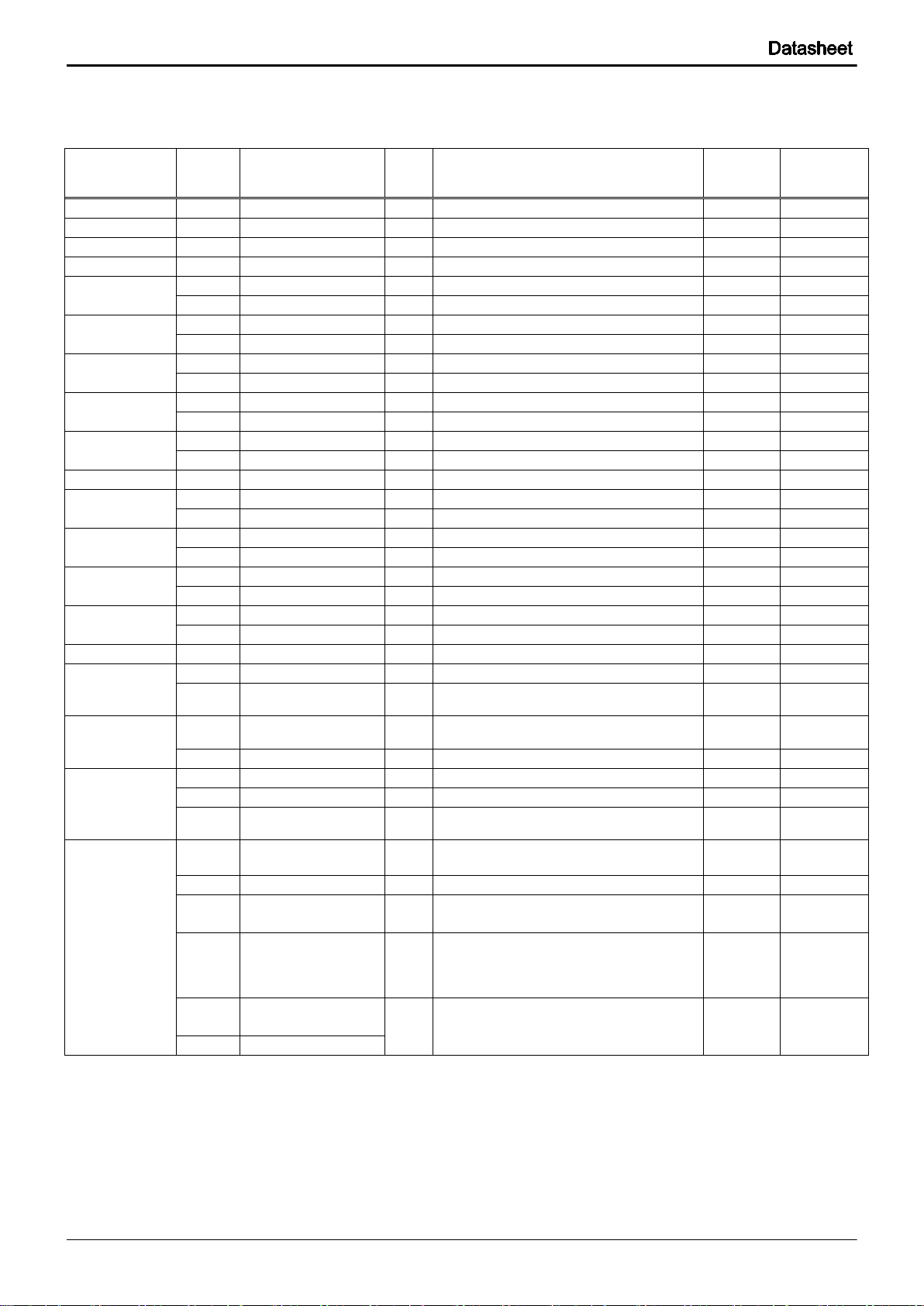

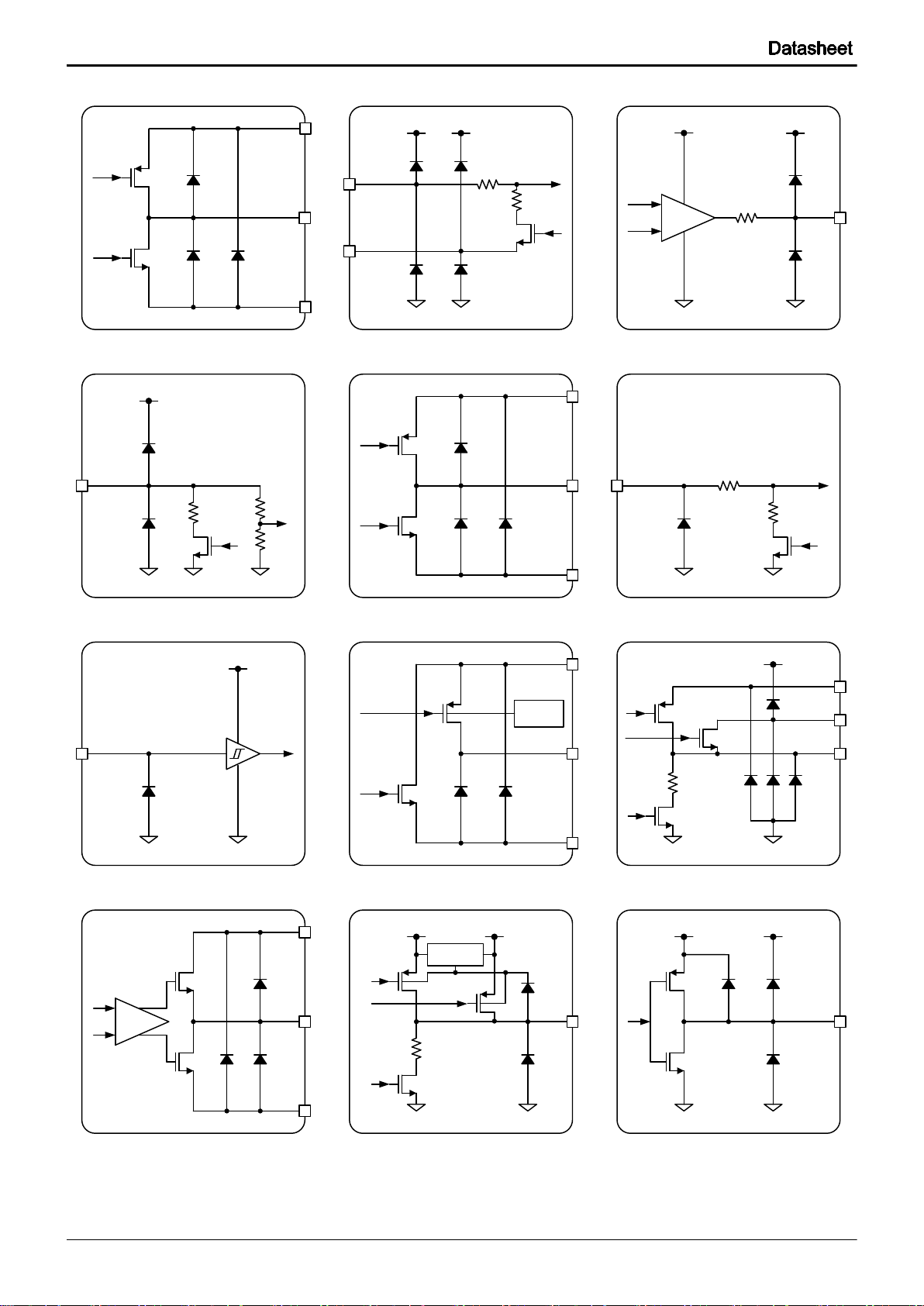

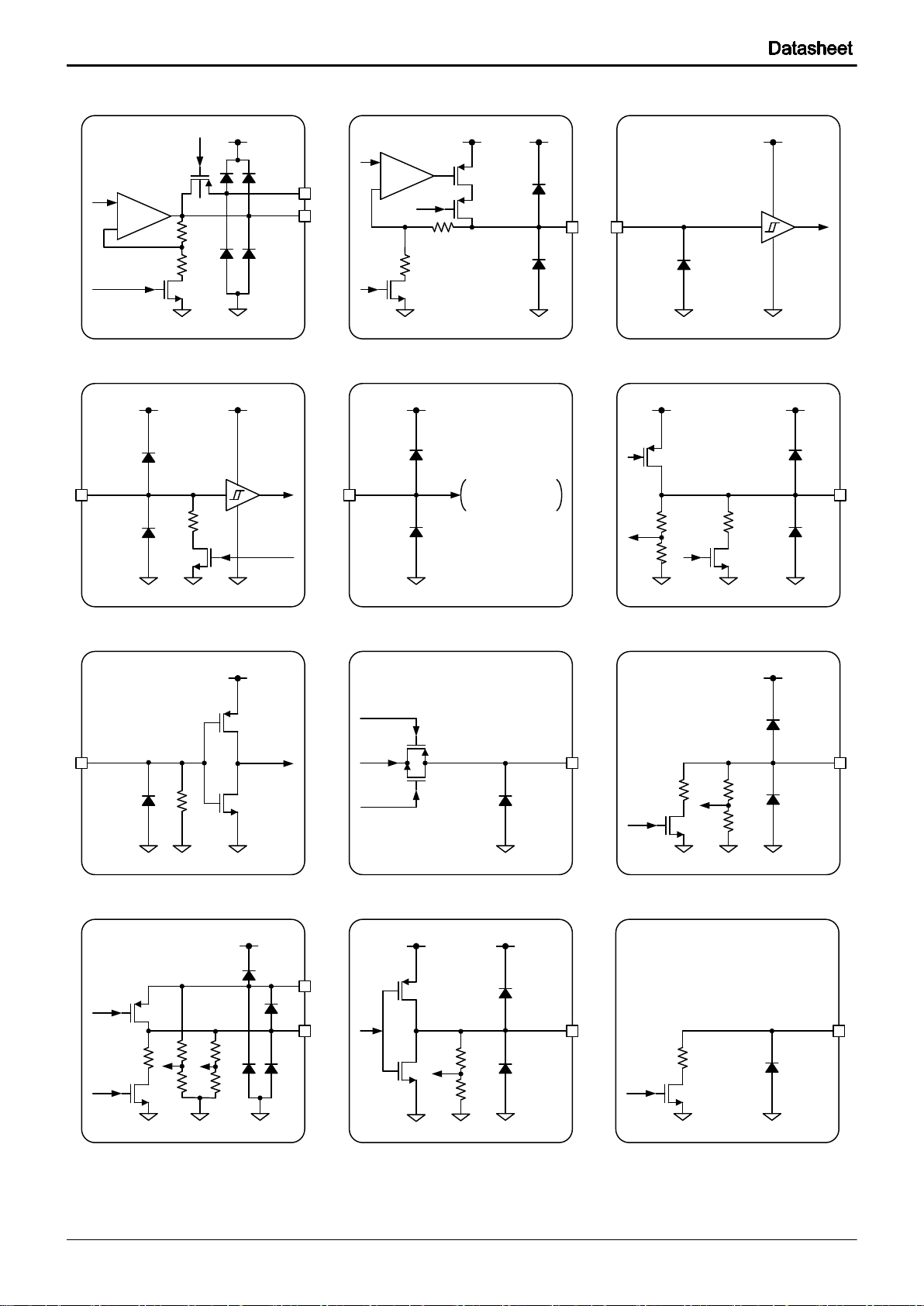

1-1 Typical Application Circuit

Fig. 1-1 Typical Application Circuit

7/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

SPI

V2P85S

Buck-Boost

Converter

2.9V 550mA

VSYS

V2P85S

V3P3A

Buck-Boost

Converter

3.3V 1569mA

V5P0S

Boost

Converter

5.0V 955mA

PWM-

Pulse Width Modulated

Outputs

Power

Sequencer

I2C Interface

(Slave, Master)

System Control-

Reset, Power,

and

Control Signals

Buck Converters

Buck-Boost Converters

DIGITAL Interface

ADC / Power Interface

State

Machine

Registers

Multi-phase BuckConverters

BD2610GW

VDCIN

Power Source

Detection

GPIOHV-

High Voltage

General Purpose I/O

BCU-

Burst Control Unit

Output Signals

VSYS_SX_EN_B

VSYS_S

VSYS_U_EN_B

Power

Switch

Control

Switch

VSYS2 Switch

VBUS

I2C_VIO

I2C_CLK

I2C_DATA

DEBUG_I2C_CLK

DEBUG_I2C_DATA

DEBUG_CS

SVID

(Slave)

SVID_CLK

SVID_DIO

DEBUG_SVID_CLK

DEBUG_SVID_DIO

SVID_ALERT_B

DEBUG_SVID_ALERT

_B

PWRBTNIN_B

PWRBTN_B

SLP_S0IX_B

SLP_S3_B

SLP_S4_B

PLTRST_B

SUSPWRNACK

ULPI_VBUS_EN

THERMTRIP_B

BCUDISA

BCUDISB

BCUDISCRIT

PWM2

PWM1

PWM0

Display Panel

Control

BACKLIGHT_EN

PANEL_EN

ACPRESENT

BATLOW_B

SDWN_B

MODEM_OFF_B

COREPWROK

RSMRST_B

IRQ

PROCHOT_B

DRAMPWROK

VCCAPWROK

GPIO1VDD

GPIO1P0_UIBTN_B

GPIO1P1

GPIO1P2

GPIO1P3

GPIO1P4

GPIO1P5

GPIO1P6

GPIO1P7

GPIOLV-

LOW Voltage

General Purpose I/O

GPIO0VDD

GPIO0P0_BATIDIN

GPIO0P1_BATIDOUT

GPIO0P2

GPIO0P3

GPIO0P4

GPIO0P5

GPIO0P6

GPIO0P7

ADCVDD

SYSTHERM0

SYSTHERM1

SYSTHERM2

BPTHERM0

BPTHERM1

SDMMC3_1P8_EN

SDMMC3_PWR_EN_B

BATID

VREFT

VREFB

VBATSENSE

VSYS1

VSYS2

VBATBKUP

I2CM_CLK

I2CM_DATA

BACKUP

Registers

VSYS

SwitchVSYS

MUX

Switch

V3P3A

VSYS2

VUSBPHY

V1P2S

Switch

VDDQ

V1P2SX_VIN

V1P2SX

Switch

VSYS_S

VSYS_U

VSYS_SX

VUSBPHY

V1P2S

V1P2SX

V1P8S

Switch

V1P8A

V1P8S_VIN

V1P8SX

Switch

V1P8S

V1P8SX

V2P85SX

Switch

V2P85SX_VIN

V2P85S

VSYS_SX_FB

VSYS_U_FB

V3P3U_EN_B

SwitchV3P3A V3P3U

V3P3U_FB

V3P3S_EN_B

SwitchV3P3A V3P3S

V3P3S_FB

VHOST_EN

Current Limit

Switch

VSYS VHOST

VBUS_EN

Current Limit

Switch

VSYS VBUS

VHDMI

VHDMI_VIN

V2P85SX

Current Limit

Switch

VSYS

VHDMI

V1P8U_EN_B

SwitchV1P8A V1P8U

V1P8U_FB

V1P0S_EN

V1P0SX_EN

SwitchV1P0A

SwitchV1P0A V1P0SX

V1P0S

V1P0S_FB

V1P0SX_FB

MUX

Switch

VSDIO

VSDIO

V1P8A

V3P3A

VSDIO_V1P8A_VIN

VSDIO_V3P3A_VIN

Power Switch & External Switch Control

V1P2A

Liner Voltage Regulator

1.2V 30mA

VDDQ_VTT

Liner Voltage Regulator

VDDQ/2 325mA

VREFDQ0

Liner Voltage Regulator

0.6V-1.22V 10mA

VDDQ_VTT_VIN

VDDQ_VTT

VDDQ_VTT_GND

V1P8S

V1P0A

VDDQ_VTT

VDDQ_VTT_FB

V1P8A

V3P3A

From Main Battery Pack

USB

V1P2A

V1P8S_VIN

VREF25_0

VREF25_1

VREF25_2

GND0

GND1

GND2

GND3

GND4

GND5

VLP

Liner Voltage Regulator

VREF25

RTC_POR

V2P85S_VIN

V2P85S_LX0

V2P85S_GND

V2P85S_FBP

V2P85S_LX1

V2P85S

FEED BACK

VNN_FBP

VNN

VNN

5Multi-Phase

Buck Converter

0.65V -1.2V

8A

VSYS

VNN_COMP

VSYS

VNN_GND4

VNN_LX4

VNN_VIN4

VNN_GND0

VNN_LX0

VNN_VIN0

GND SENSE

VCC_FBN

VCC

VCC

5Multi-Phase

Buck Converter

0.65V -1.2V

8A

VSYS

VCC_COMP

VSYS

VCC_GND4

VCC_LX4

VCC_VIN4

VCC_GND0

VCC_LX0

VCC_VIN0

FEED BACK

VCC_FBP

V1P0A

VSYS

V1P0A_GND0,1

V1P0A_LX0,1

V1P0A_VIN0,1

V1P0A_FBP

V1P05S

VSYS

V1P05S_GND

V1P05S_LX

V1P05S_VIN

V1P05S_FBP

V1P8A

VSYS

V1P8A_GND

V1P8A_LX

V1P8A_VIN

V1P8A_FBP

VDDQ

VSYS

VDDQ_GND0,1

VDDQ_LX0,1

VDDQ_VIN0,1

VDDQ_FBP

VSYS

V3P3A

V3P3A_VIN

V3P3A_LX00,01

V3P3A_GND

V3P3A_FBP

V3P3A_LX10,11

V3P3A

V5P0S_GND0,1

V5P0S_LX0,1

V5P0S0,1

V5P0S_FB

VREFDQ0

V1P8S_VIN

Charger

Control

CHGDET_B

CHGRINT_B

ILIM0

ILIM1

AC Adapter

GPADC

Referance

GPADC1

10bits Analog to Digital

Converters

GPADC2

10bits Analog to Digital

Converters

(VR Current Monitor)

VCC Output Current

VNN Output Current

V1P0A Output Current

V1P05S Output Current

VDDQ Output Current

From Main Battery Pack

Digital Battery

Communication

Interface

Die Temp

VREF25

V1P8SV1P8S

V1P0SV1P0S

Power Botton

V1P0S

SOC

Platform

External

EEPROM

MISC

VCC Current Monitor

VNN Output

Current Monitor

V1P0A Output

Current Monitor

V1P05S Output

Current Monitor

VDDQ Output

Current Monitor

V1P0A

Buck Converter

1.0V 1900mA

V1P05S

Buck Converter

1.05V 900mA

V1P8A

Buck Converter

1.8V 1627mA

VDDQ

Buck Converter

1.24V 2800mA

L

VNN

C

IVNN

C

OVNN

C

IVNN

L

VNN

L

VCC

L

VCC

C

IVCC

C

OVCC

VDDQ_VTT_R

VREFDQ1

Liner Voltage Regulator

0.6V-1.22V 10mA

VREFDQ1

V1P8S_VIN

VSYS

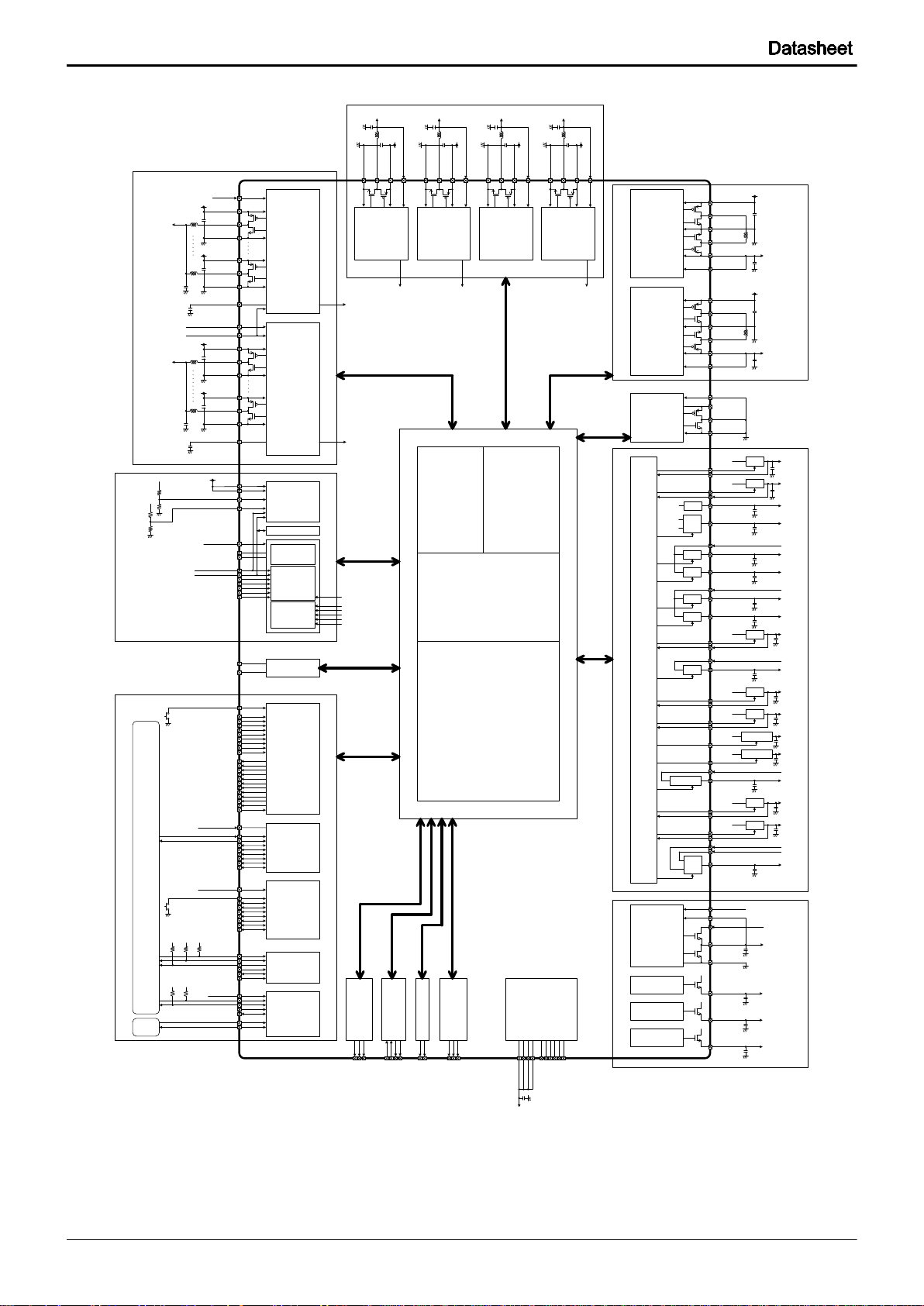

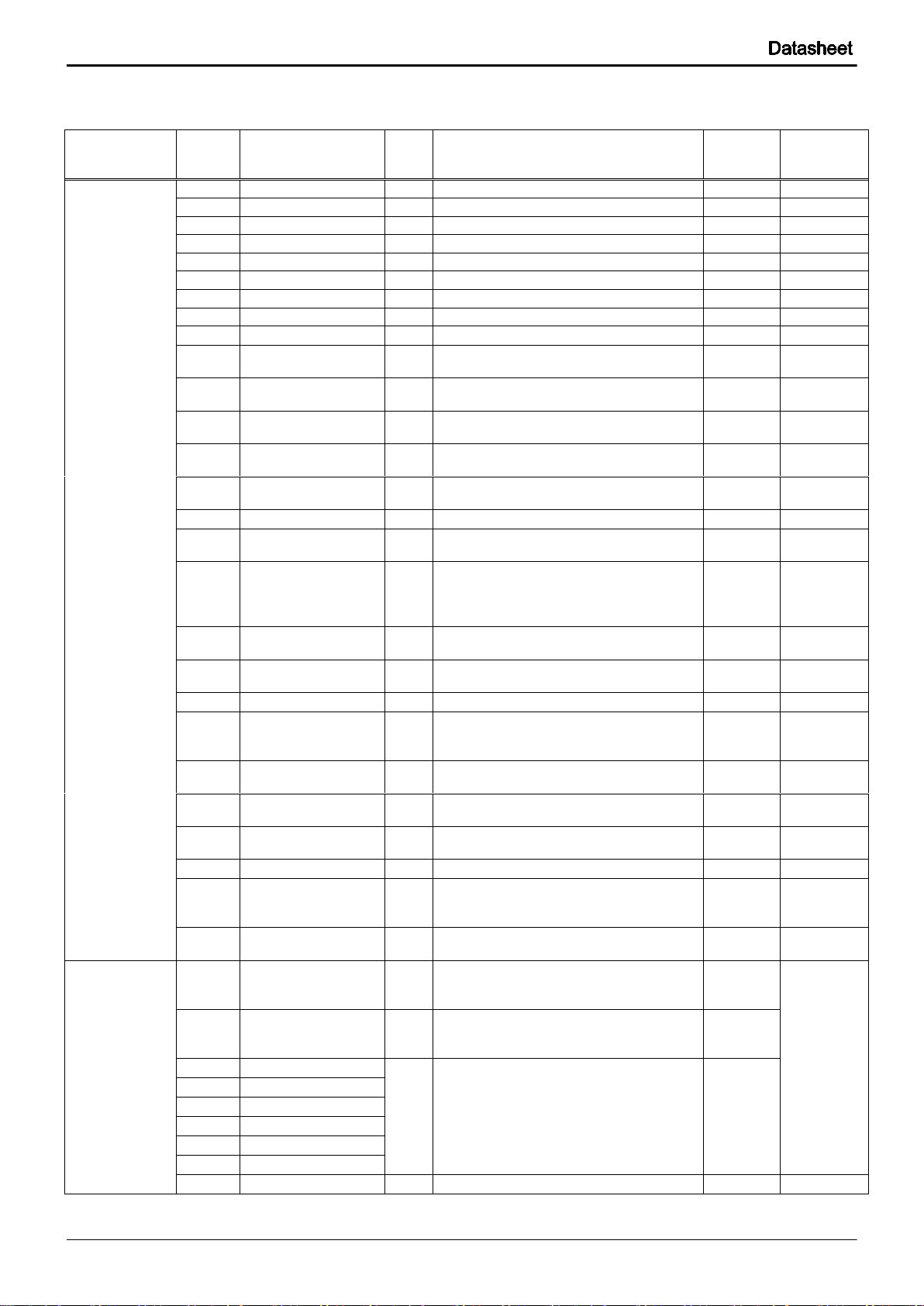

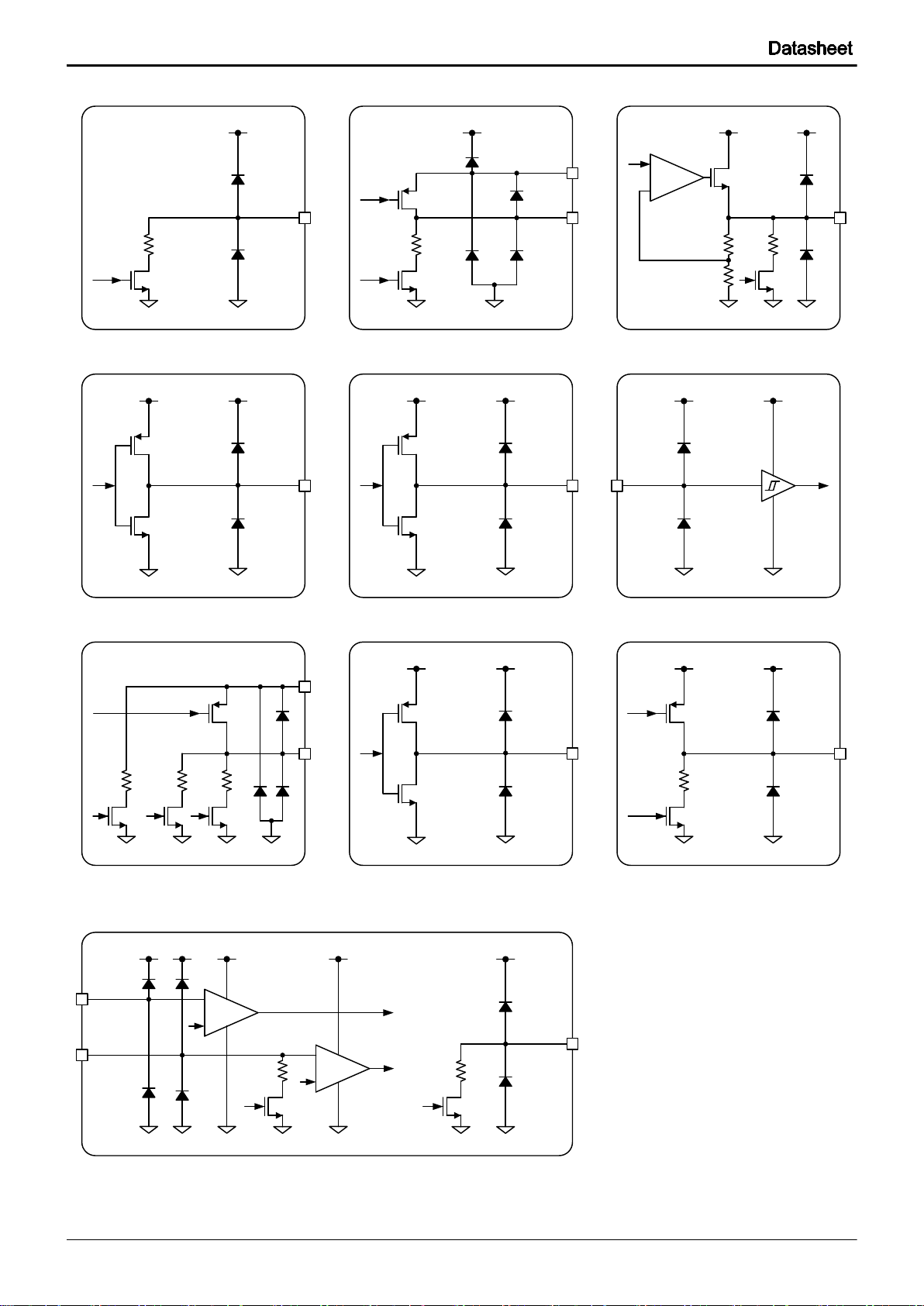

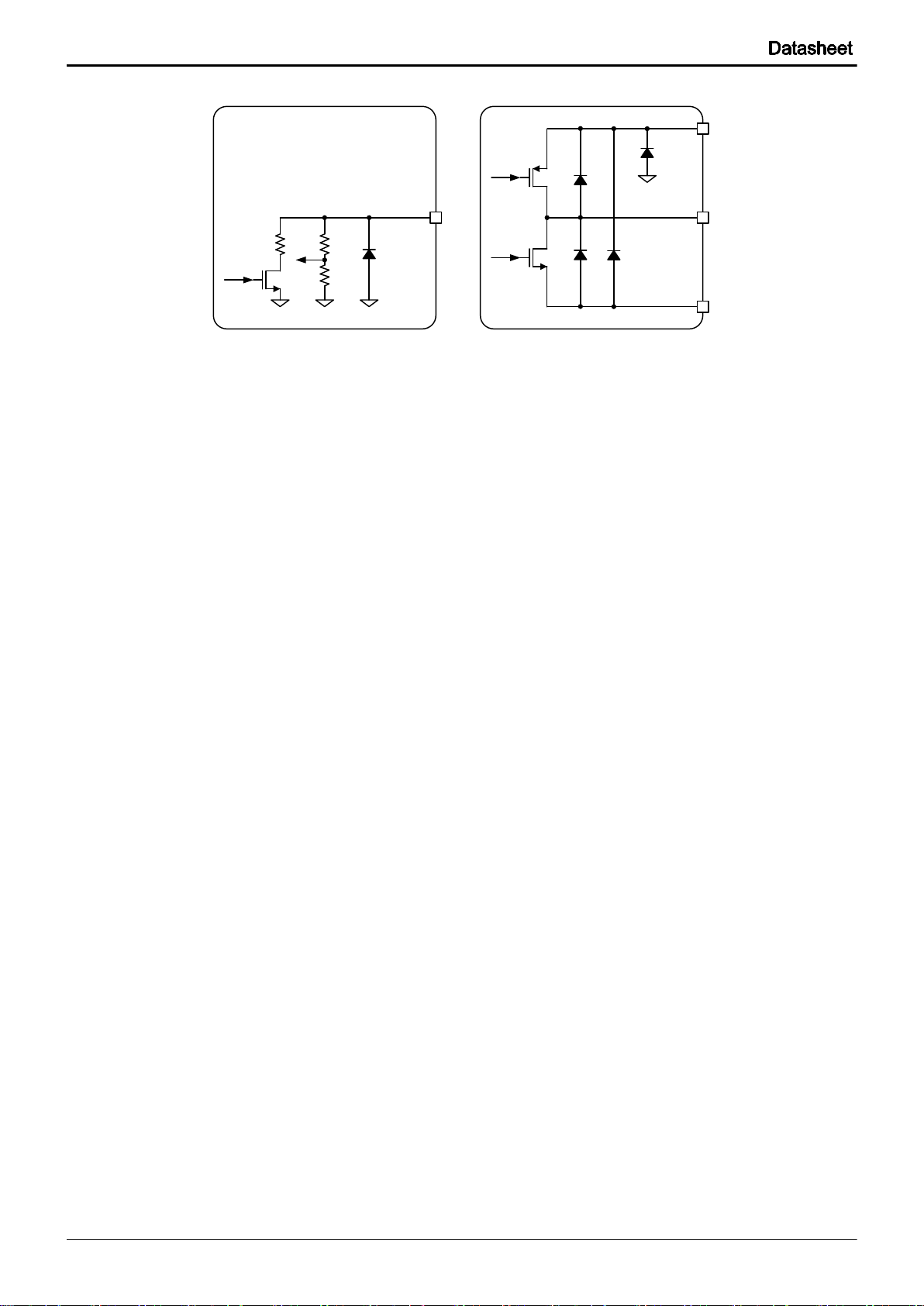

Fig. 1-2 VSYS = 5V Application Circuit

8/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

2cell-Battery

Charger

VBUS

SW

SYS

BAT

1.2 A max

when in

VOTG boost

mode

VCHG

15m

Ħ

max

VBUS

VLV 2 SOC

I2C _2

GPIOz

LCHR

VSYS_A

/CE

I2C

SVID

VUSBPHY

I2C

SVID

USB PHY

VBUS

VBAT

CHGDET #

ID D+ D-

RST#

ULPI

12

2

3

AC Adapter

Micro -AB

connector

ID D+ D -

VBUS

VAC

VDC

Power

Select

2

I2C

VREFT

ILIM

TS 1

ILI M1

ULPI

TS 2

4A max in

charging

mode

VBUS

REGN

ILI M0

CHGDET_B

ILI M0

ILI M1

VDCIN

VDCIN

BATID

VUSBPHY

VDC

VBUS

CH

GRINT _BINT

VBATSENSE

NTC NTC

R

BSI

0~130kΩ

Digital

Battery

Communication

Battery Pack

t°

VREFB

All VSYS

BATIDIN

BATIDOUT

Buffer

Buck

Converter

Boost

Converter

VSYS_B

R

R

Added Device

VSYSSENSE(A2sample-name)

I2CM_SZ(A1sample-name)

VSYS_A

R=178kΩ

R=1500kΩ

R=500kΩ

R=196kΩ

BCU

BATDET

R=6000kΩ

R=2000kΩ

BATMON

R=125kΩ

R=100kΩ

R=25kΩ

UVLO

OVP

BPTH ER M

VRE F

B

VRE F

T

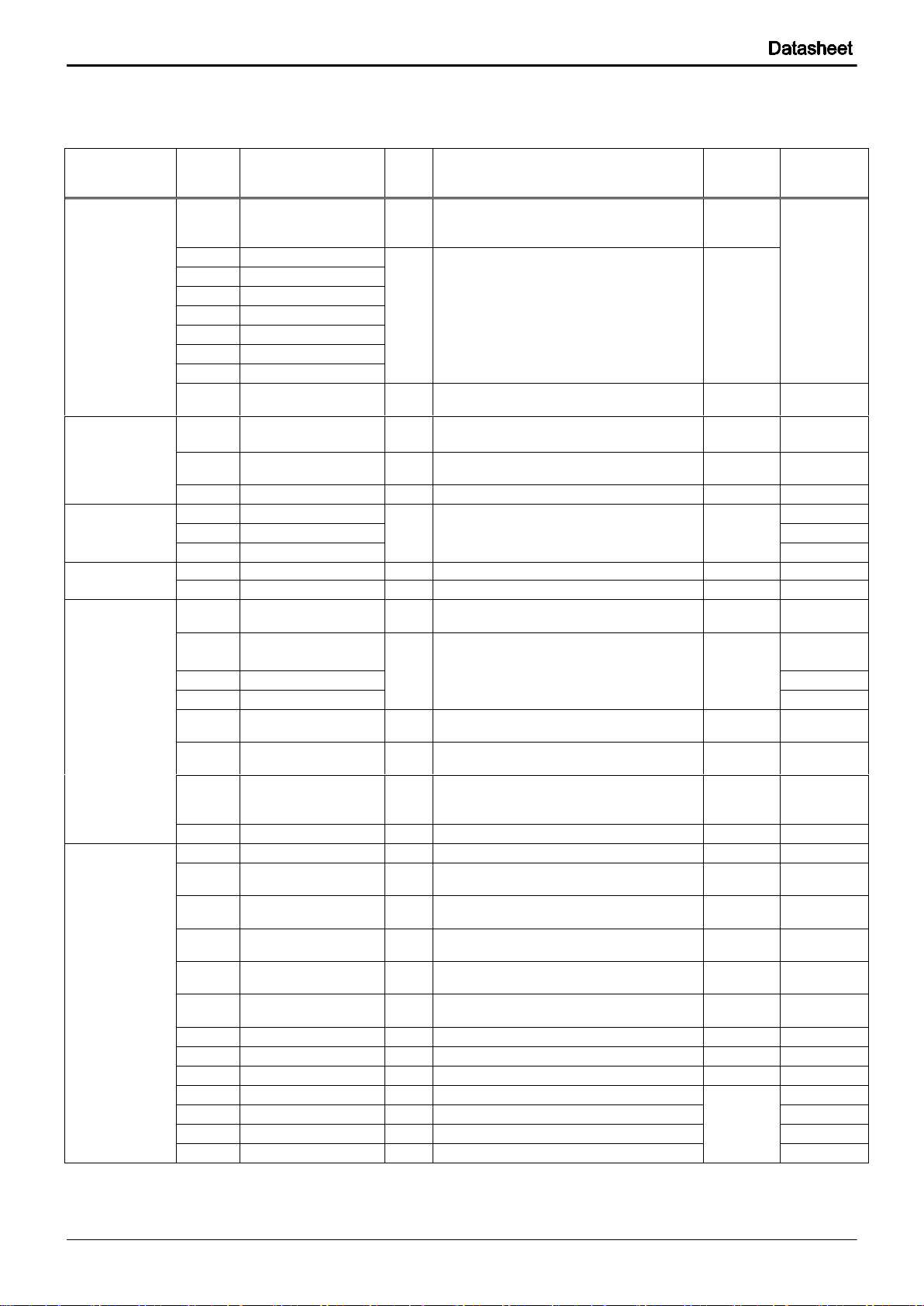

Fig. 1-3 2-cell battery system

9/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

5V AC/DC

ADAPTER

USB

POWER

BATTERY

PACK

POWER

MUX

CHARGER

VOLTAGE

REGULATORS

BD2610GW

I2C

VDDQ_VTT

SVID

I2C

SVID

VCC

VNN

V1P0A

V1P0S

V1P05S

VDDQ

VREFDQ0

V1P2SX

V1P8A

V1P8U

V1P8SX

VREFT

V3P3A

V3P3U

V3P3S

VUSBPHY

VSDIO

V2P85S

V2P85SX

V5P0S

VBUS

VHOST

VHDMI

VSYS_U

VSYS_S

VSYS_SX

V1P2A

INPUT PWER

DETECTION

& CONTROL

ADC

SEQUENCING

STATE

MACHINE

SOC + Platform

Devices

PUSH

BUTTON

DET

PWM

& GPIO

DISPLAY

BACKLIGHT

GP SYSTEM

CONTROL

SENSORS

VDCIN

VBUS

VBATSENSE

VSYS1

RSMRST_B

PLTRST_B

SLP_S0IX_B

SLP_S3_B

SLP_S4_B

SUSPWRDNACK

PWRBTNIN_B

GPIO1P0_UIBTN_B

PWRBTN_B

VSYS

VREF25

Backup

Battery

Charger

VRTC

VREFDQ1

V1P0SX

V1P2S

V1P8S

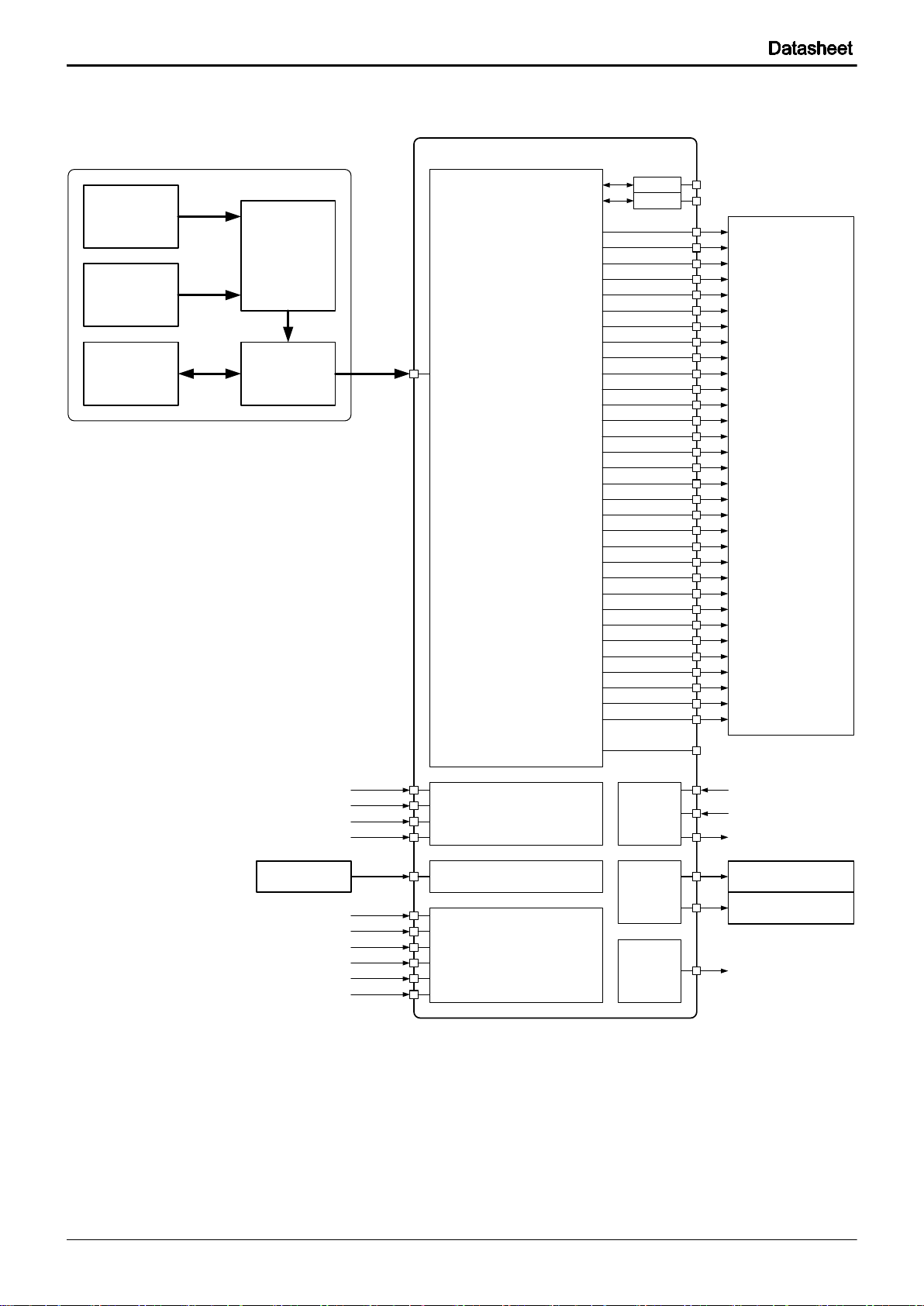

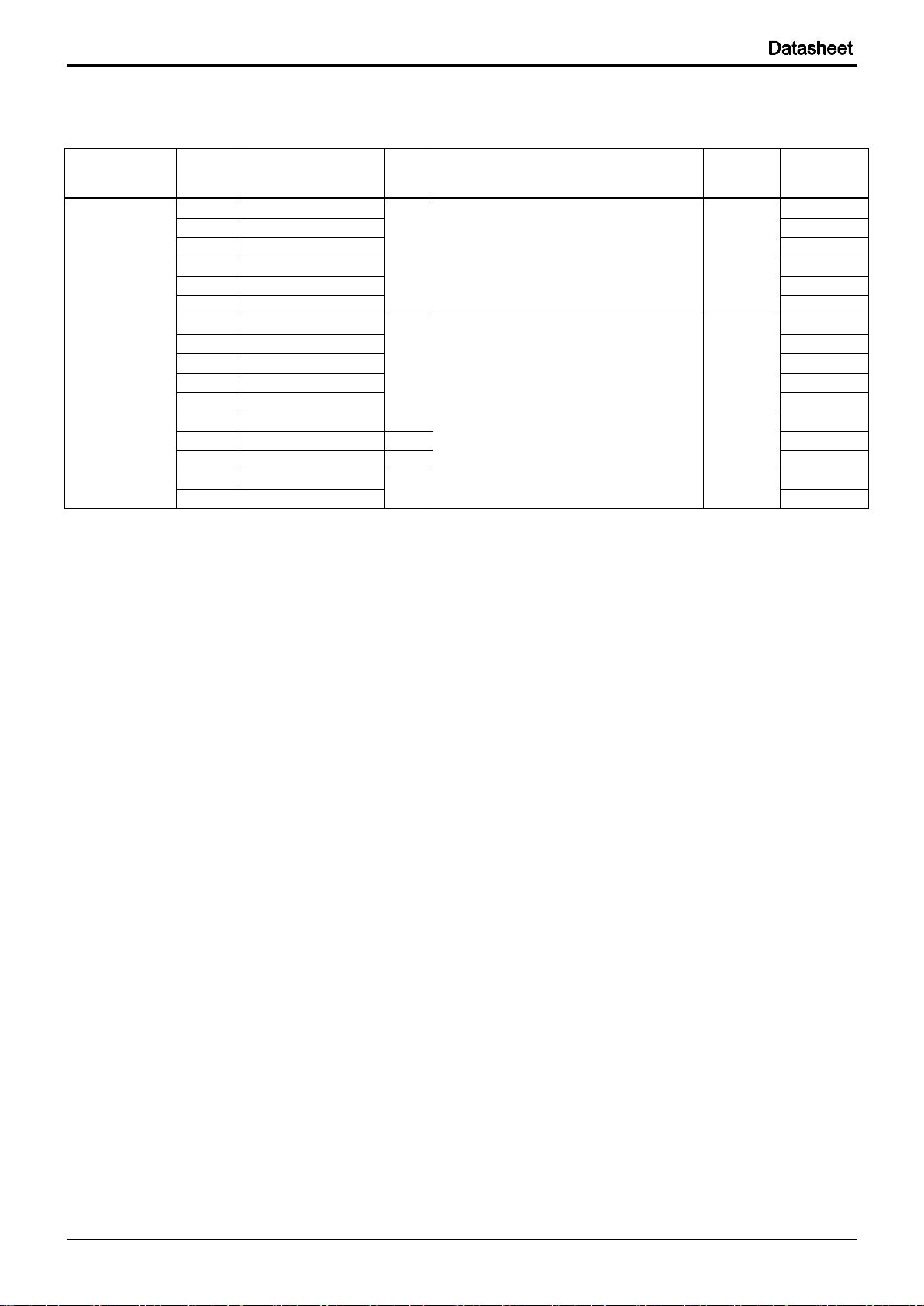

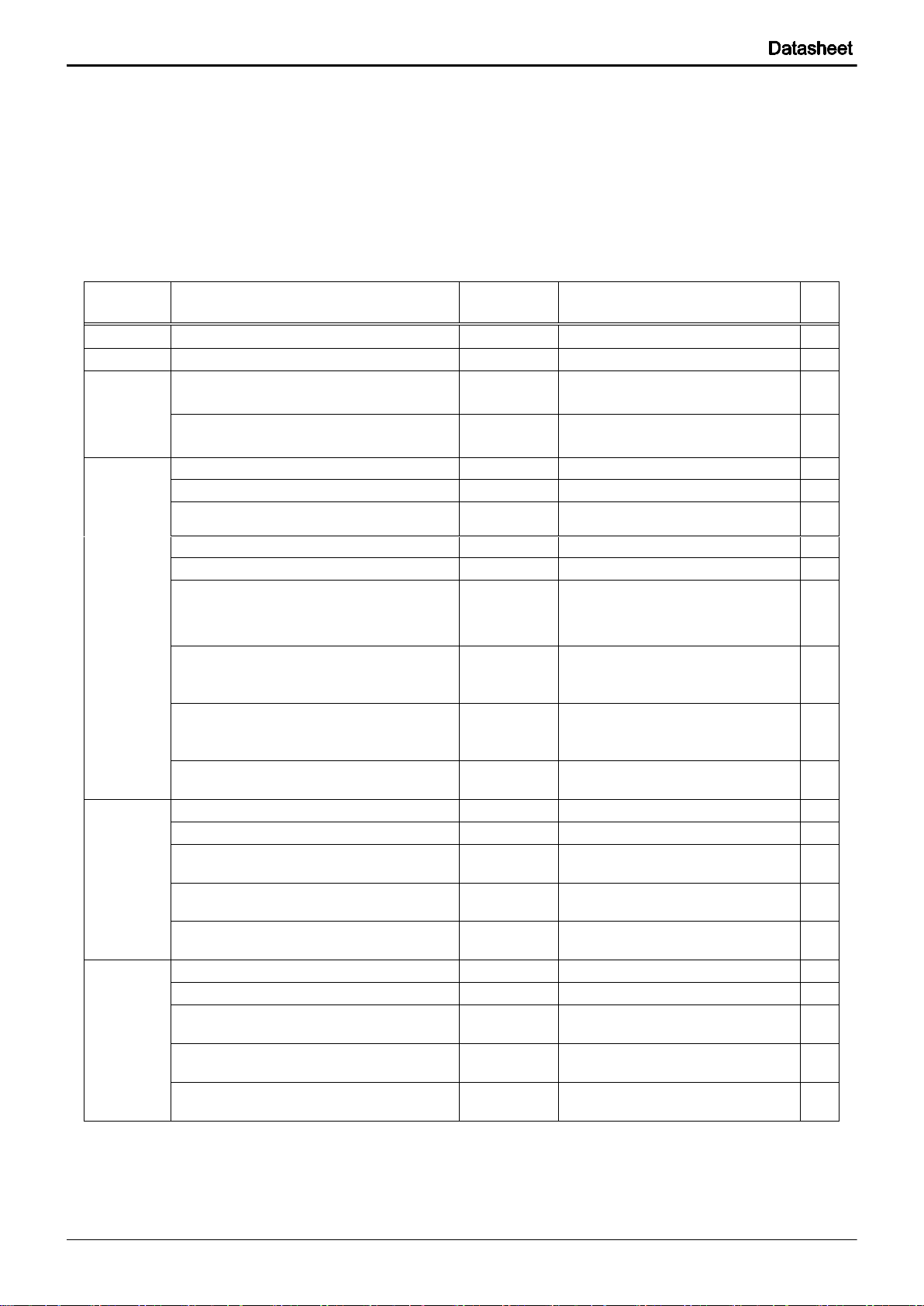

1-2 Simplified Block Diagram

Fig. 1-4 Simplified Block Diagram

10/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

PCB Layout 1 (TBD)

1-3 Recommended Component PCB Layout

Fig. 1-5 PCB Layout (Height: 1.0mm)

11/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

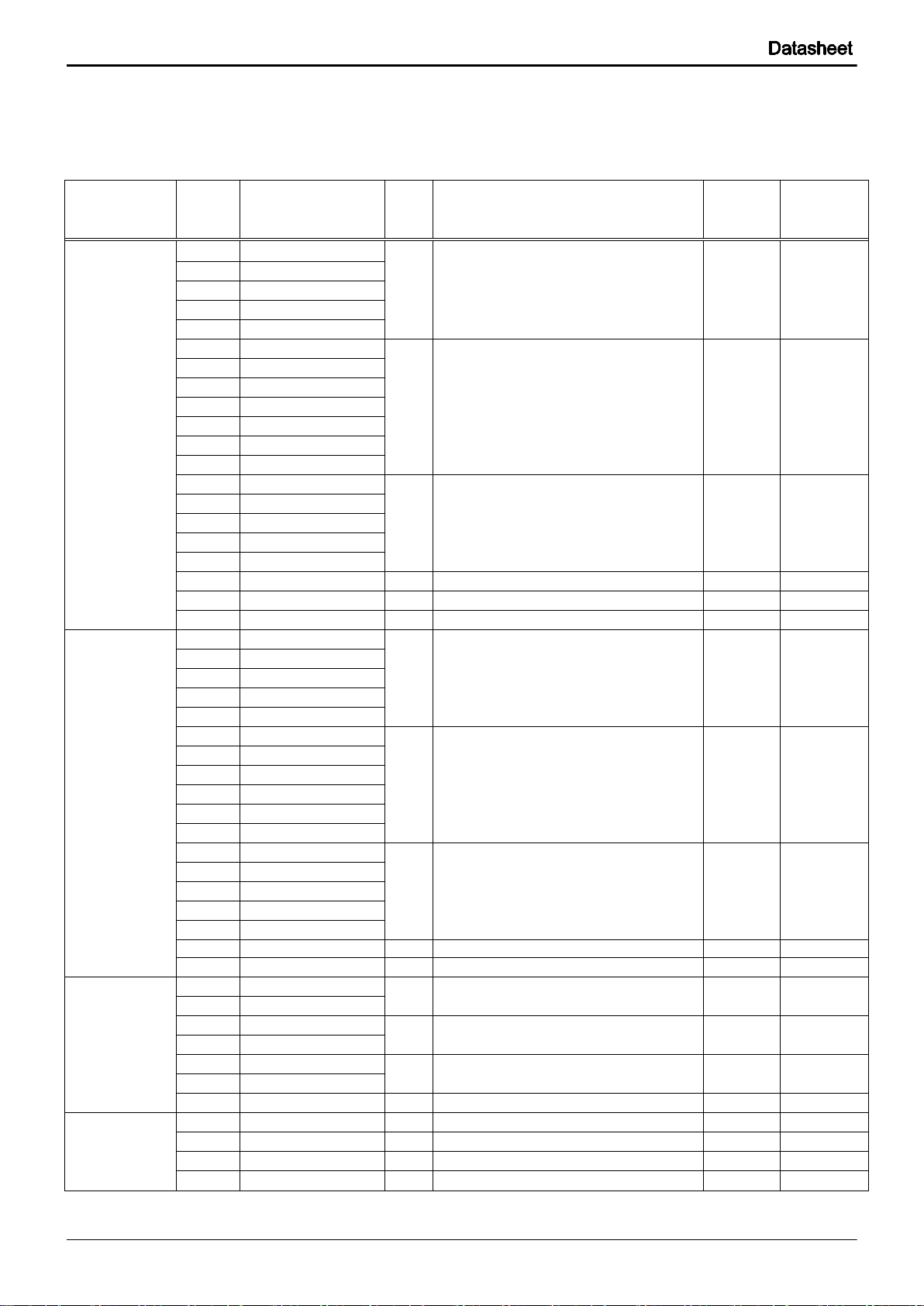

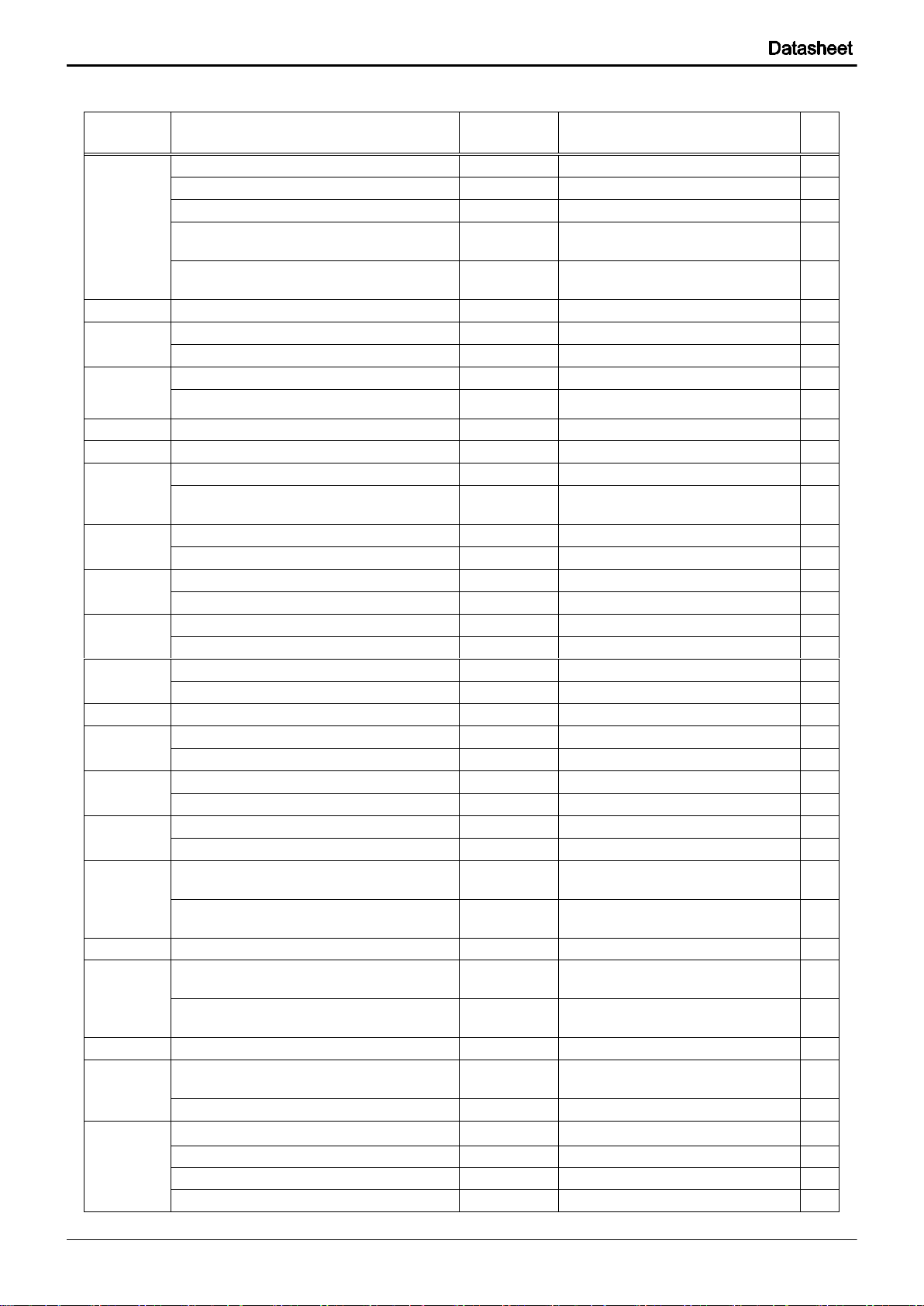

BOM List 1 (TBD)

1-4 BOM List

Table. 1-1 BOM List (1)

12/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

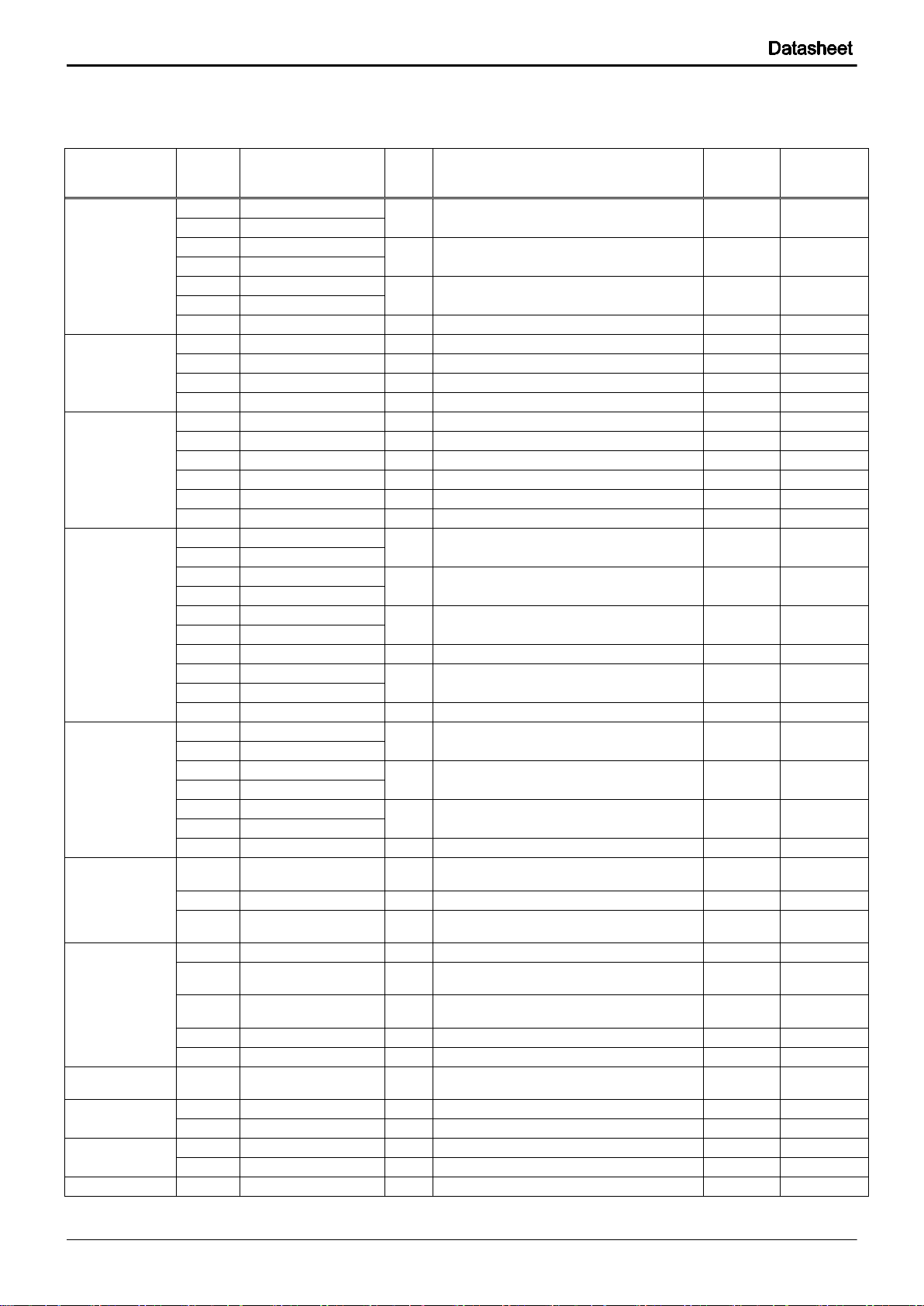

BOM List 2 (TBD)

Table. 1-2 BOM List (2)

13/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

0

1

2

3

4

5

6

0 25 50 75 100 125 150

Power Dissipation [W]

Ambient Temperature [°C]

P

DMAX

=5.1W

θja = 24.4 °C/W

ROHM2610

Lot No.

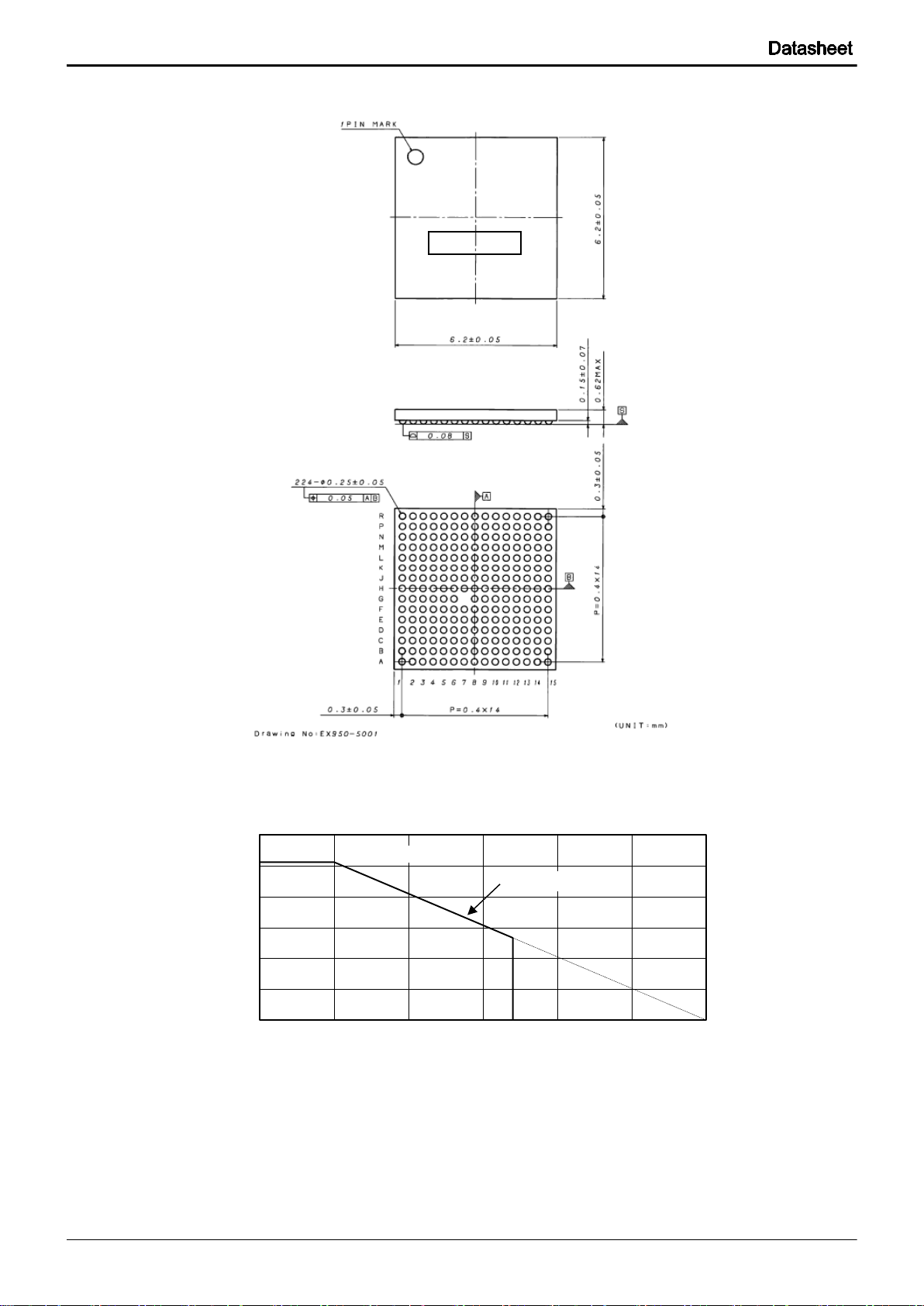

1-5 Package Dimension (corresponded with rev0.98; 2.4 Package )

Fig. 1-6 Package Dimension (Tentative)

1-5-1 Thermal Derating Curve

* 41mW/C is de-rated under the temperature of 25°C or higher. The value is with the test subject mounted on 170mm x 180mm x

1.6mm (Glass epoxy FR-4 PCB). The data is a simulated reference data, therefore, ROHM Co. ,Ltd. assumes no responsibility or

liability whatsoever for any damages resulting from the unusual or unexpected operation, such as neglect/improper installation,

alteration, or accident arising from improper handling,.

Fig. 1-7 Thermal Derating Curve

14/305

BD2610GW

© 2012 ROHM Co., Ltd. All rights reserved.

www.rohm.com

TSZ22111・15・001

TSZ02201-BD2610GW-1-2

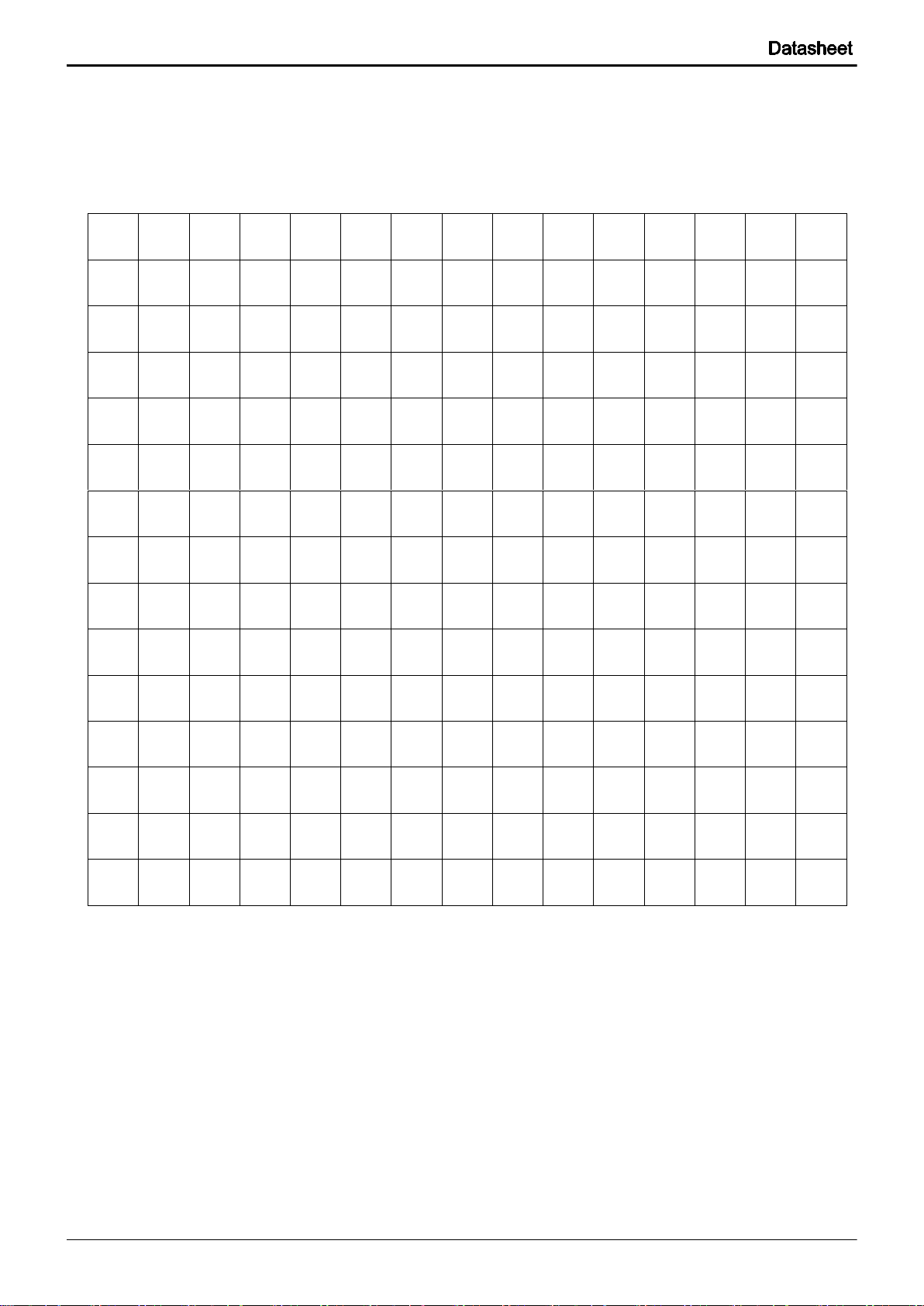

1 2 3 4 5 6 7 8 9

10

11

12

13

14

15 A

DEBUG

_SVID

_CLK

DEBUG

_SVID

_ALERT

_B

VNN

_LX3

VNN

_VIN3

VNN

_LX4

VNN

_GND4

V1P8A

_GND

V1P8A

_LX

V1P8A

_VIN

V1P2SX

_VIN

VDDQ

_VIN0

VDDQ

_LX0

VDDQ

_GND0

T4

T5

A

B

DEBUG

_SVID

_DATA

T9

VNN

_GND3

BCU

DISA

VNN

_VIN4

VREFD

Q0

V1P8SX

V1P8S

_VIN

V1P8S

V1P2SX

VDDQ

_VIN1

VDDQ

_LX1

VDDQ

_GND1

T3

T7

B

C

VNN

_LX2

VNN

_GND2

VNN

_GND23

GND3

GPIO1

VDD

VREFD

Q1

V1P2A

V1P8U

_FB

V1P8A

_FBP

V1P2S

VDDQ

_VTT

_VIN

VDDQ

_VTT

VDDQ

_VTT

_GND

VDDQ

_VTT

_FB

V2P85S

C

D

VNN

_VIN2

SDMMC

3_PWR

_EN_B

VNN_C

OMP

PWR

BTN_B

BCU

DISCRIT

PWM2

ILIM0

ILIM1

VREF25

_2

V1P8U

_EN_B

VDDQ

_VTT

_R

VDDQ

_FBP

GND2

V2P85S

_LX1

V2P85S

_GND

D

E

VNN

_LX1

VNN

_VIN1

VBAT

BKUP

SVID

_CLK

BCU

DISB

PWM1

GPIO1

P0_UI

BTN_B

VDCIN

VBUS

GPIO1

P5

GPIO1

P7

VSYS

_SX

_EN_B

V2P85S

_FBP

V2P85S

_LX0

V2P85S

_VIN

E

F

VNN

_GND1

VNN

_FBP

GND4

SVID

_DIO

SVID

_ALERT

_B

PWM0

GPIO1

P1

GPIO1

P2

GPIO1

P3

VSYS_U

_EN_B

V3P3U

_EN_B

V3P3A

_FBP

V2P85S

X

_VIN

V2P85S

X

V3P3A_

0

F

G

VSDIO

_V1P8A

_VIN

VSDIO

VSDIO

_V3P3A

_VIN

VCC

_FBN

BACK

LIGHT

_EN

SDWN

_B

GPIO1

P6

GPIO1

P4

VSYS

_SX

_FB

VSYS_U

_FB

V3P3U

_FB

V3P3S

_FB

V3P3A_1 V3P3A

_LX11

G

H

VNN

_LX0

VNN

_VIN0

VSYS1

BAT

LOW_B

ACP

RESENT

PANEL

_EN

RTC

_POR

SDMMC

3

_1P8

_EN

GPIO0

P7

VBUS

_EN

VHOST

_EN

V3P3S

_EN_B

VUSB

PHY

V3P3A

_LX10

V3P3A

_GND

H

J

VNN

_GND0

VCC

_FBP

VREF25

_1

RSM

RST_B

VCCAP

WROK

IRQ

THERM

TRIP_B

PWR

BTN

IN_B

GPIO0

P6

GPIO0

P5

GPIO0

P2

VSYS_S

GPIO0

VDD

V3P3A

_LX00

V3P3A

_LX01

J

K

VCC

_GND0

MODEM

_OFF_B

DRAM

PWROK

CORE

PWROK

PLT

RST_B

PRO

CHOT_B

SLP_

S4_B

SYS

THERM0

VBAT

SENSE

GPIO0

P4

GPIO0

P1_BAT

IDOUT

V1P0SX

_FB

VSYS2

V3P3A

_VIN1

V3P3A

_VIN0

K

L

VCC

_LX0

VCC

_VIN0

SLP

_S0IX_B

SUSPW

R

DNACK

SLP

_S3_B

ULPI

_VBUS

_EN

SYS

THERM1

SYS

THERM2

BP

THERM1

GPIO0

P3

GPIO0

P0_BAT

IDIN

V1P0S

_FB

VHDMI

_VIN

V5P0S0

V5P0S1

L

M

VCC

_VIN1

CHG

RINT_B

VCC

_COMP

I2C

_VIO

I2C