Page 1

Renesas 32-Bit Single-Chip RISC Microprocessor

SuperH RISC engine Family/SH7040 Series

(CPU Core SH-2)

Rev.6.00

2003.5.26

SH7040, SH7041, SH7042,

SH7043, SH7044, SH7055

Group

Hardware Manual

32

查询SH7040A供应商

Page 2

Page 3

Renesas 32-Bit Single-Chip RISC

Microprocessor

SuperH RISC engine Family/

SH7040 Series (CPU Core SH-2)

SH7040, SH7041, SH7042,

SH7043, SH7044, SH7055

Group

Hardware Manual

REJ09B0044-0600O

Page 4

Cautions

Keep safety first in your circuit designs!

1 . Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but

there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or

property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement

of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

1 . These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation

product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any

other rights, belonging to Renesas Technology Corporation or a third party.

2 . Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights,

originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in

these materials.

3 . All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents

information on products at the time of publication of these materials, and are subject to change by Renesas Technology

Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact

Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product

information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies

or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the

Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

4 . When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and

algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the

information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss

resulting from the information contained herein.

5 . Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used

under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an

authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any

specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater

use.

6 . The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these

materials.

7 . If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license

from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is

prohibited.

8 . Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

Page 5

Preface

The SH7040 Series (SH7040, SH7041, SH7042, SH7043, SH7044, SH7045) single-chip RISC

(Reduced Instruction Set Computer) microprocessors integrate a Renesas Technology-original

RISC CPU core with peripheral functions required for system configuration.

The CPU has a RISC-type instruction set. Most instructions can be executed in one clock cycle,

which greatly improves instruction execution speed. In addition, the 32-bit internal-bus

architecture enhances data processing power. With this CPU, it has become possible to assemble

low cost, high performance/high-functioning systems, even for applications that were previously

impossible with microprocessors, such as real-time control, which demands high speeds. In

particular, the SH7040 series has a 1-kbyte on-chip cache, which allows an improvement in CPU

performance during external memory access.

In addition, the SH7040 series includes on-chip peripheral functions necessary for system

configuration, such as large-capacity ROM and RAM, timers, a serial communication interface

(SCI), an A/D converter, an interrupt controller, and I/O ports. Memory or peripheral LSIs can be

connected efficiently with an external memory access support function. This greatly reduces

system cost.

There are versions of on-chip ROM: mask ROM, PROM, and flash memory. The flash memory

can be programmed with a programmer that supports SH7040 series programming, and can also

be programmed and erased by software.

This hardware manual describes the SH7040 series hardware. Refer to the programming manual

for a detailed description of the instruction set.

Related Manual

SH7040 series instructions

SH-1/SH-2/SH-DSP Programming Manual

Please consult your Renesas Technology sales representative for details for development

environment system.

Page 6

Page 7

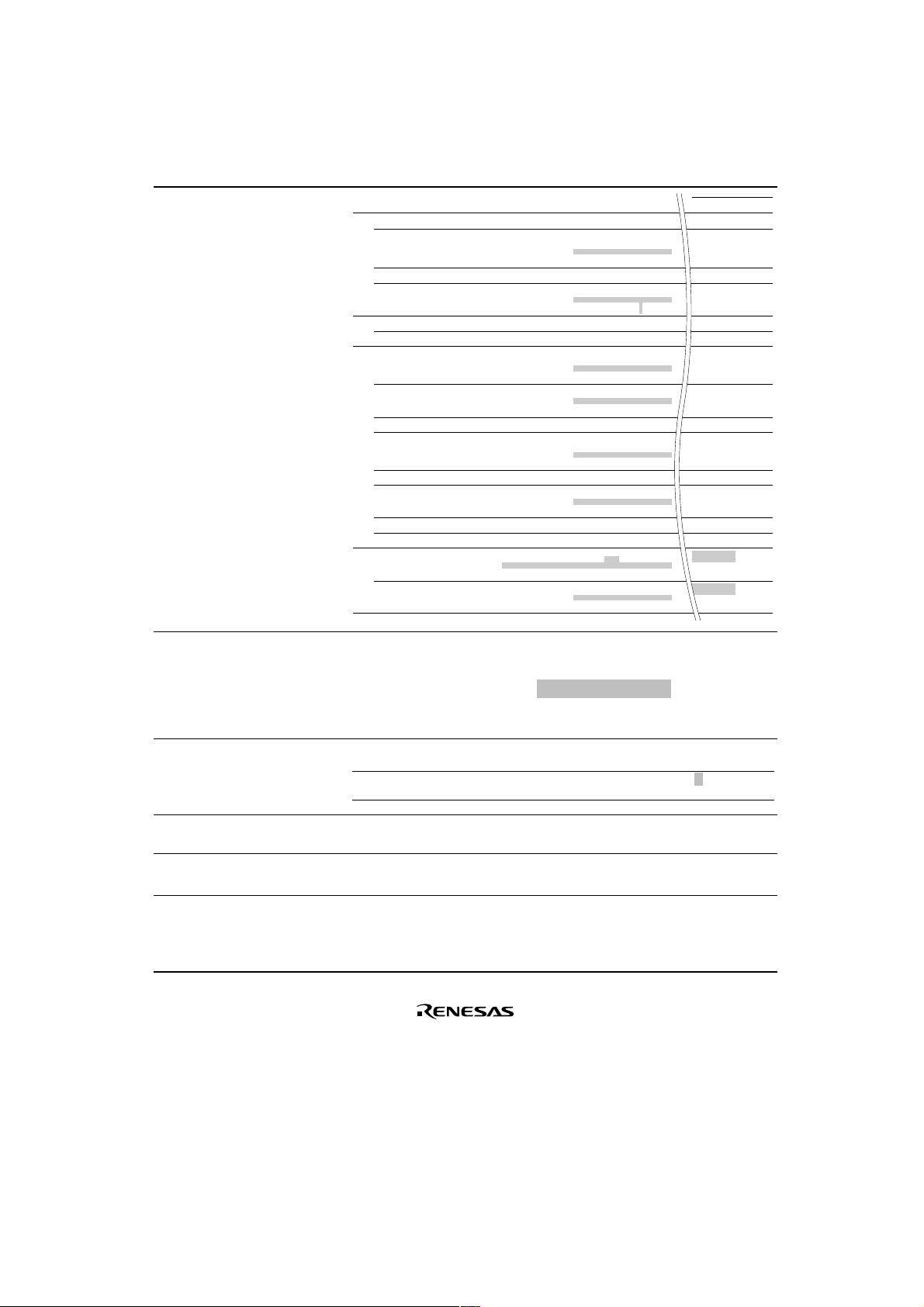

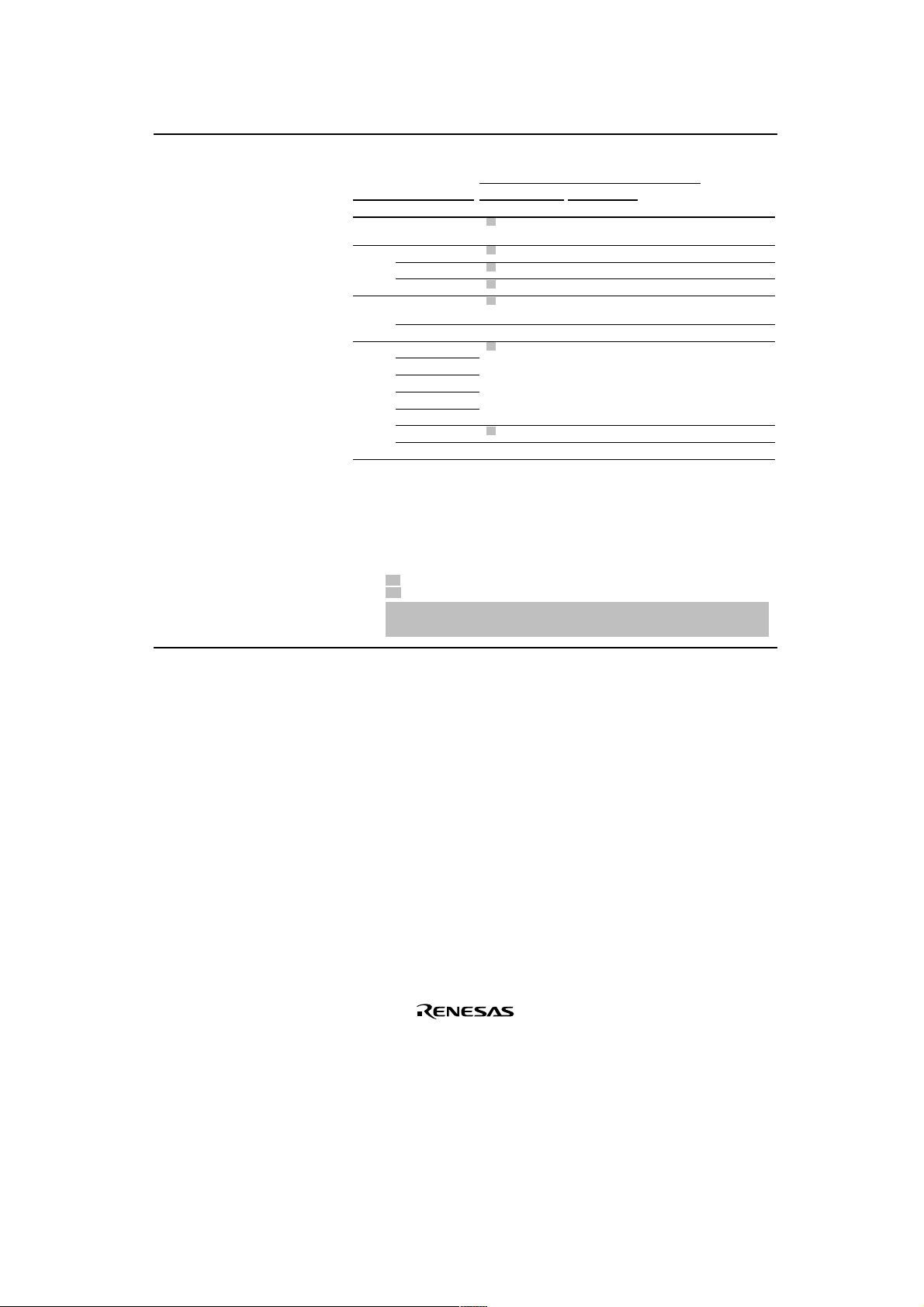

List of Items Revised or Added for This Version

Section Page Description

1.1.1 SH7040 Series

Features

Notes on the

SH7040 Series

Specifications

7,

9

Type Abbreviation Package Frequency Voltage Type Name ROM

ZTAT SH7042 128 kB 16 bits ±15LSB

FLASH SH7044F 256 kB 16 bits ±4LSB

MASK SH7040A 64 kB 16 bits ±4LSB

ROM

less

Note: Package with Copper used as the lead material.

Mask

Version

SH7042A A mask

SH7043 128 kB 32 bits ±15LSB

SH7043A A mask 128 kB 32 bits ±4LSB

A mask

SH7045F A mask 256 kB 32 bits ±4LSB

A mask

SH7041A A mask 64 kB 32 bits ±4LSB

SH7042 128 kB 16 bits ±15LSB

SH7042A A mask 128 kB 16 bits ±4LSB

SH7043 128 kB 32 bits ±15LSB

SH7043A A mask 128 kB 32 bits ±4LSB

SH7044 A mask 256 kB 16 bits ±4LSB

SH7045 A mask 256 kB 32bits ±4LSB

A mask

SH7040A 16 bits ±4LSB

SH7041A A mask 32 bits ±4LSB

A/D

External

Bus Width

Accuracy

(5Vversion)

(High-Speed)

(Mid-Speed)

(High-Speed)

(Mid-Speed)

(Mid-Speed)

(Mid-Speed)

(Mid-Speed)

(Mid-Speed)

(High-Speed)

(Mid-Speed)

(High-Speed)

(Mid-Speed)

(Mid-Speed)

(Mid-Speed)

(Mid-Speed)

(Mid-Speed)

On-chip

ROM

128 kB 16 bits ±4LSB

Operating

Temp

QFP2020-112 –20°C to 75°C 28 MHz

–20°C to 75°C 28 MHz

QFP2020-112

TQFP1414-120

QFP2020-112Cu*

QFP2020-144 –20°C to 75°C 28 MHz

QFP2020-144

–20°C to 75°C 28 MHz

QFP2020-144Cu*

QFP2020-112 –20°C to 75°C 28 MHz 5 V HD64F7044F28 See “256 kB Flash

QFP2020-144 –20°C to 75°C 28 MHz 5 V HD64F7045F28 See “256 kB Flash

–20°C to 75°C 28 MHz

QFP2020-112

TQFP1414-120

QFP2020-112Cu*

QFP2020-144

–20°C to 75°C 28 MHz

QFP2020-144Cu*

QFP2020-112 –20°C to 75°C 28 MHz

QFP2020-112

–20°C to 75°C 28 MHz

TQFP1414-120

QFP2020-112Cu*

QFP2020-144 –20°C to 75°C 28 MHz

QFP2020-144

–20°C to 75°C 28 MHz

QFP2020-144Cu*

QFP2020-112 –20°C to 75°C 28 MHz 5 V HD6437044F28 See “256 kB Mask

QFP2020-144 –20°C to 75°C 28 MHz 5 V HD6437045F28 See “256 kB Mask

–20°C to 75°C 28 MHz

QFP2020-112

TQFP1414-120

QFP2020-112Cu*

QFP2020-144

–20°C to 75°C 28 MHz

QFP2020-144Cu*

16 MHz

16 MHz

16 MHz

28 MHz

16 MHz

16 MHz

16 MHz

28 MHz

16 MHz

16 MHz

16 MHz

28 MHz

16 MHz

16 MHz

28 MHz

16 MHz

16 MHz

16 MHz

16 MHz

28 MHz

16 MHz

16 MHz

16 MHz

28 MHz

16 MHz

16 MHz

16 MHz

28 MHz

16 MHz

16 MHz

28 MHz

16 MHz

5 V

3.3 V

5 V

3.3 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

3.3 V

5 V

3.3 V

5 V

3.3 V

5 V

3.3 V

HD6477042F28

HD6477042VF16

HD6477042AF28

HD6477042AVF16

HD6477042AVX16

HD6477042ACF28

HD6477042AVCF16

HD6477043F28

HD6477043VF16

HD6477043AF28

HD6477043AVF16

HD6477043ACF28

HD6477043AVCF16

HD6437040AF28

HD6437040AVF16

HD6437040AVX16

HD6437040ACF28

HD6437040AVCF16

HD6437041AF28

HD6437041AVF16

HD6437041ACF28

HD6437041AVCF16

HD6437042F28

HD6437042VF16

HD6437042AF28

HD6437042AVF16

HD6437042AVX16

HD6437042ACF28

HD6437042AVCF16

HD6437043F28

HD6437043VF16

HD6437043AF28

HD6437043AVF16

HD6437043ACF28

HD6437043AVCF16

HD6417040AF28

HD6417040AVF16

HD6417040AVX16

HD6417040ACF28

HD6417040AVCF16

HD6417041AF28

HD6417041AVF16

HD6417041ACF28

HD6417041AVCF16

Notes on the SH7040 Series Specifications

See “128 kB

PROM”

See “128 kB

PROM”

See “128 kB

PROM”

See “128 kB

PROM”

Memory”

Memory”

See “64 kB Mask

ROM”

See “64 kB Mask

ROM”

See “128 kB Mask

ROM”

See “128 kB Mask

ROM”

See “128 kB Mask

ROM”

See “128 kB Mask

ROM”

ROM”

ROM”

Electrical

Characteristics

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

See “Electrical

Characteristics”

1.4 The F-ZTAT

Version Onboard

Programming

Figure 1.6 Condition

Transfer for Flash

Memory

2.4 Instruction Set

by Classification

Table 2.16 Branch

Instructions

4.2.3 Notes on

Board Design

4.5 Usage Notes

11.1.4 Register

Configuration

Table 11.2 DMAC

Registers

42

70

—

83 to

85

218

Note amended

Notes: For transferring between user mode and user program mode,

proceed while CPU is not programming or erasing the flash

memory.

* RAM emulation permitted

Table amended

BF/S label 10001111dddddddd Delayed branch, if T = 0, disp × 2 +

PC → PC; if T = 1, nop

2/1

*

Deleted

Newly added

Note *5 deleted

—

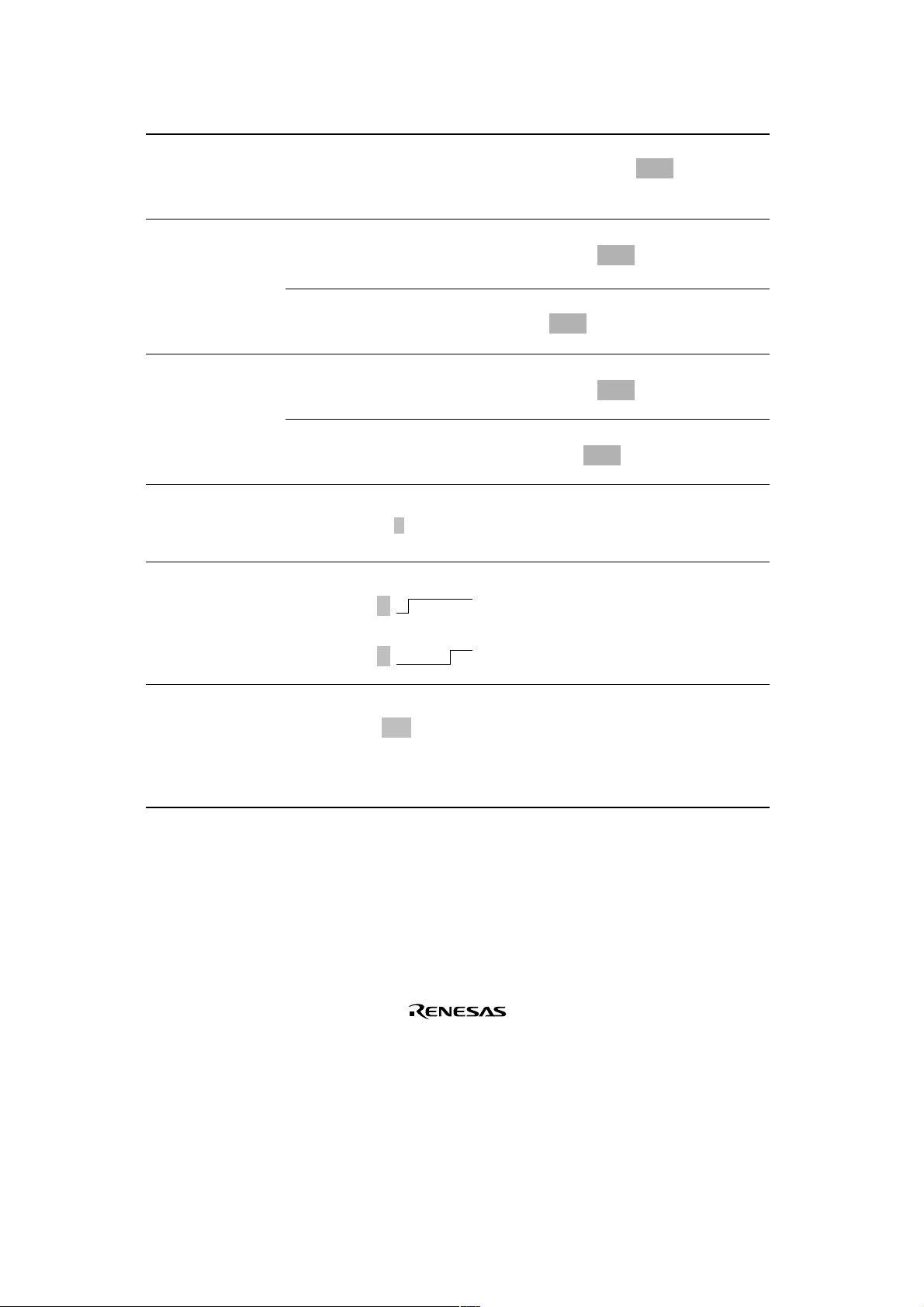

Page 8

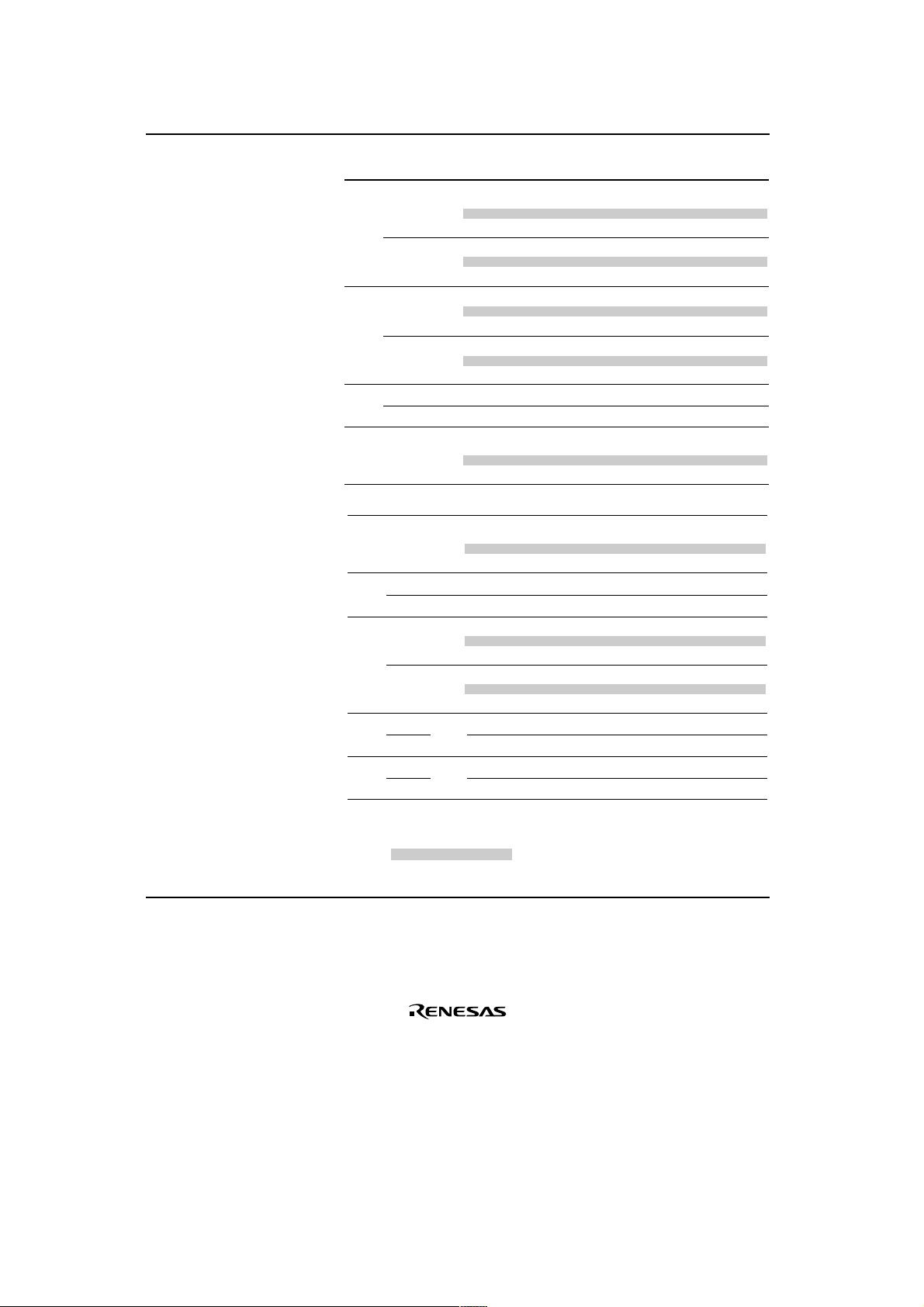

Section Page Description

11.2.3 DMA

Transfer Count

Registers 0–3

220 Description amended

The data for the upper 8 bits of a DMATCR is 0 when read.

(DMATCR0–

DMATCR3)

11.2.4 DMA

Channel Control

Registers 0–3

(CHCR0–CHCR3)

221 Description amended

• Bits 31–21—Reserved bits: Data are 0 when read. The write

value always be 0.

224 Description amended

• Bit 7—Reserved bits: Data is 0 when read. The write value

always be 0.

11.2.5 DMAC

Operation Register

(DMAOR)

226 Description amended

• Bits 15–10—Reserved bits: Data are 0 when read. The write

value always be 0.

227 Description amended

• Bits 7–3—Reserved bits: Data are 0 when read. The write

value always be 0.

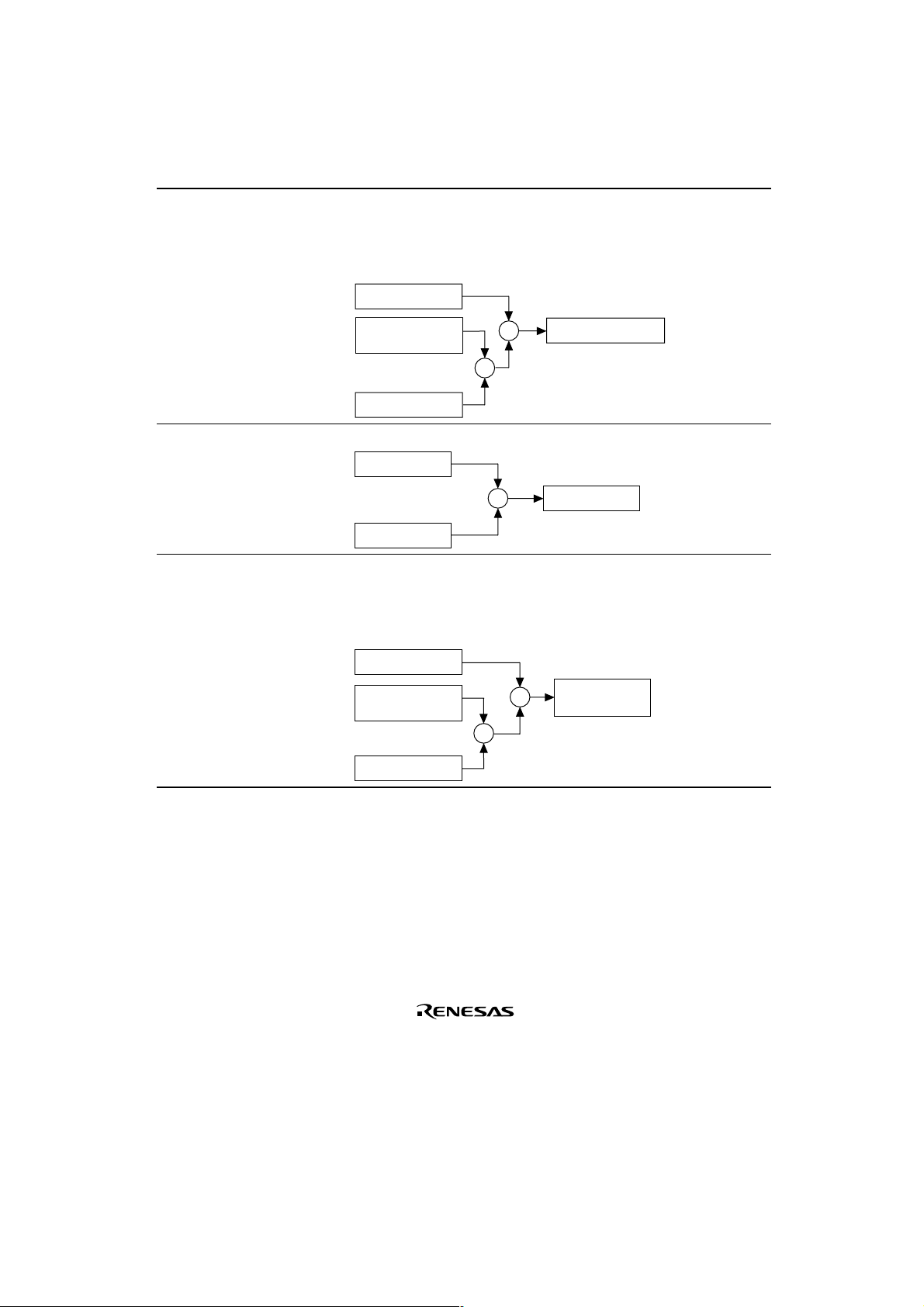

11.3.3 Channel

233

Figure amended

Priority

Figure 11.3 Round

Robin Mode

12.4.5 Cascade

337

Channel 0 is given the lowest

priority.

Figure amended

Connection Mode

Figure 12.23

TCLKC

Cascade Connection

Operation Example

(Phase Counting

TCLKD

Mode)

12.4.9

373

Figure amended

Complementary

PWM Mode

When BDC = 1, N = 0, P = 0, FB = 0, output active level = high

Figure 12.55

Example of Output

Phase Switching by

External Input (1)

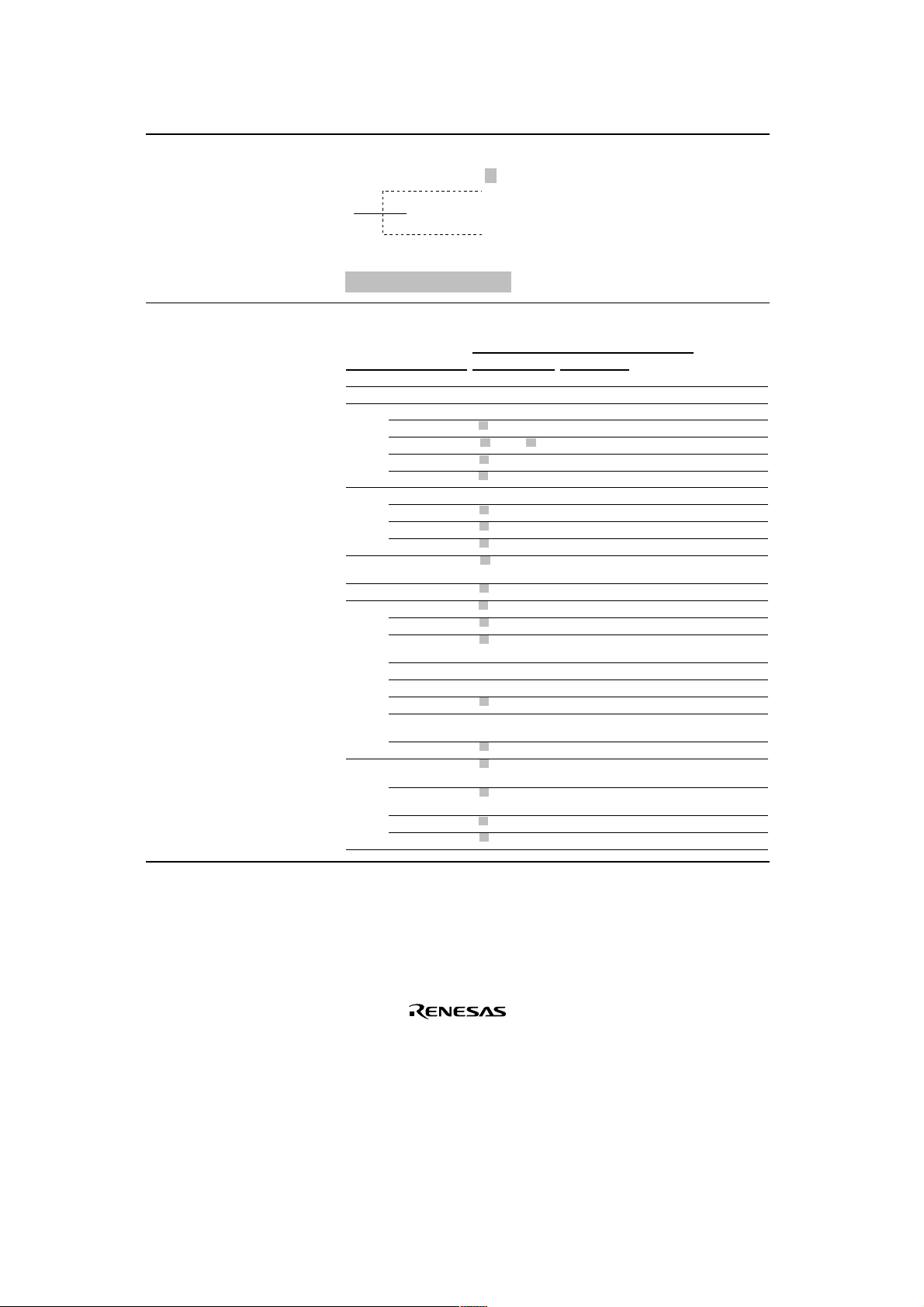

Page 9

Section Page Description

12.9.2 Block

Diagram

Figure 12.125 POE

Block Diagram

444

Note added

*

TIOC3B

*

TIOC3D

*

TIOC4A

*

TIOC4C

*

TIOC4B

*

TIOC4D

Note: * Includes multiplexed pins.

12.11.5 Usage

Notes

14.2.8 Bit Rate

Register (BRR)

Table 14.3 Bit Rates

and BRR Settings in

Asynchronous Mode

(cont)

Table 14.4 Bit Rates

and BRR Settings in

Clocked

Synchronous Mode

(cont)

14.3.4 Clock

Synchronous

Operation

Figure 14.22

Example of SCI

Receive Operation

453

491

Section added

Table amended

Bit Rate

(Bits/s) n N Error (%)

110 3 119 0.00

150 3 87 0.00

300 2 175 0.00

600 1 87 0.00

1200 1 175 0.00

2400 1 87 0.00

4800 0 175 0.00

9600 0 87 0.00

14400 0 58 –0.56

19200 0 43 0.00

28800 0 28 1.15

31250 0 26 0.12

38400 0 21 0.00

495 Table amended

3.5M —— —— 01

5M 0 0

7M —— 00

529

Figure amended

Bit 7 Bit 0

27.0336

*

—— ——

*

RxI request

Page 10

Section Page Description

15.4.9 A/D

562

33 MHz deleted

Conversion Time

Table 15.8

Operating Frequency

and CKS Bit Settings

15.6 Notes on Use

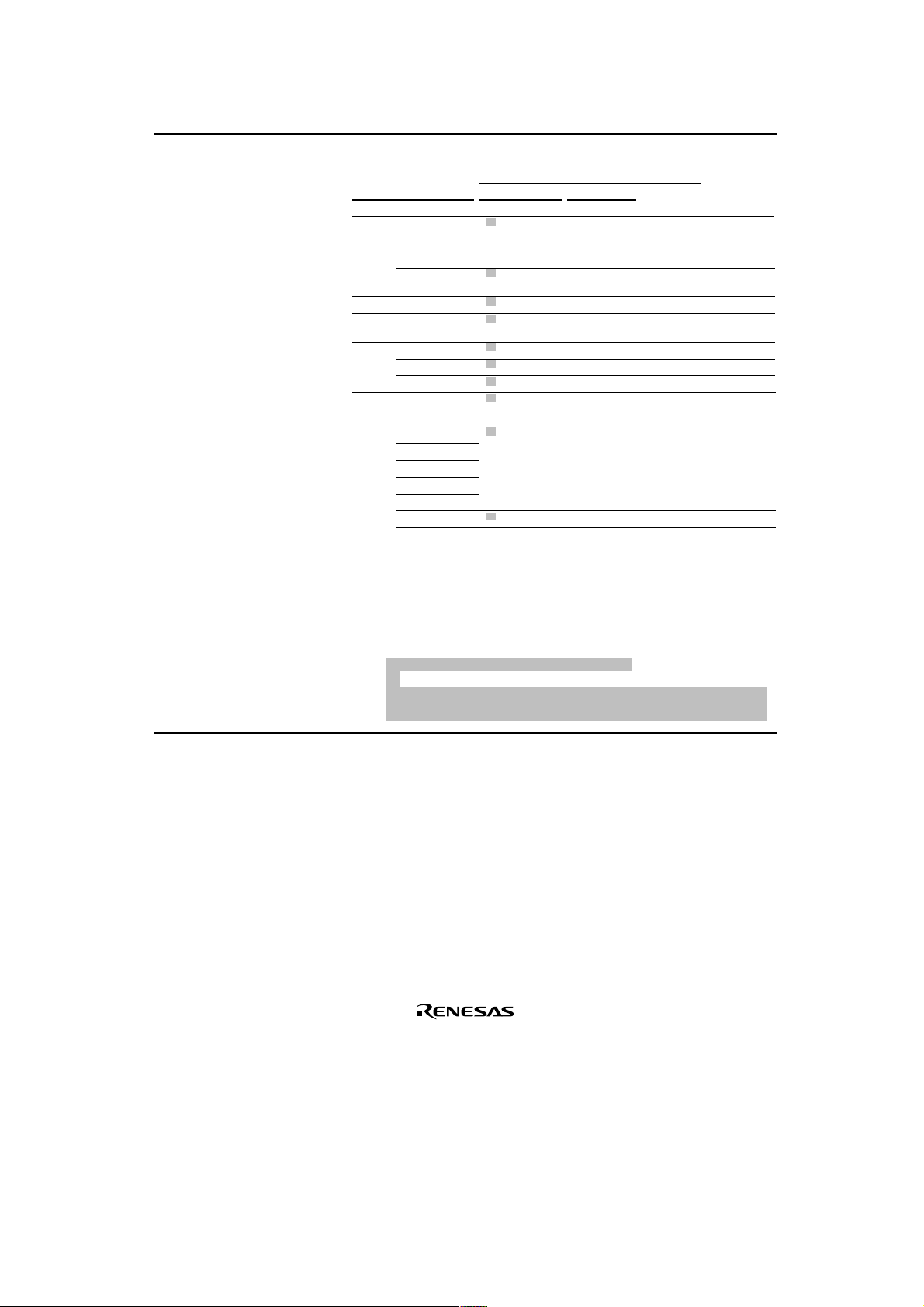

564

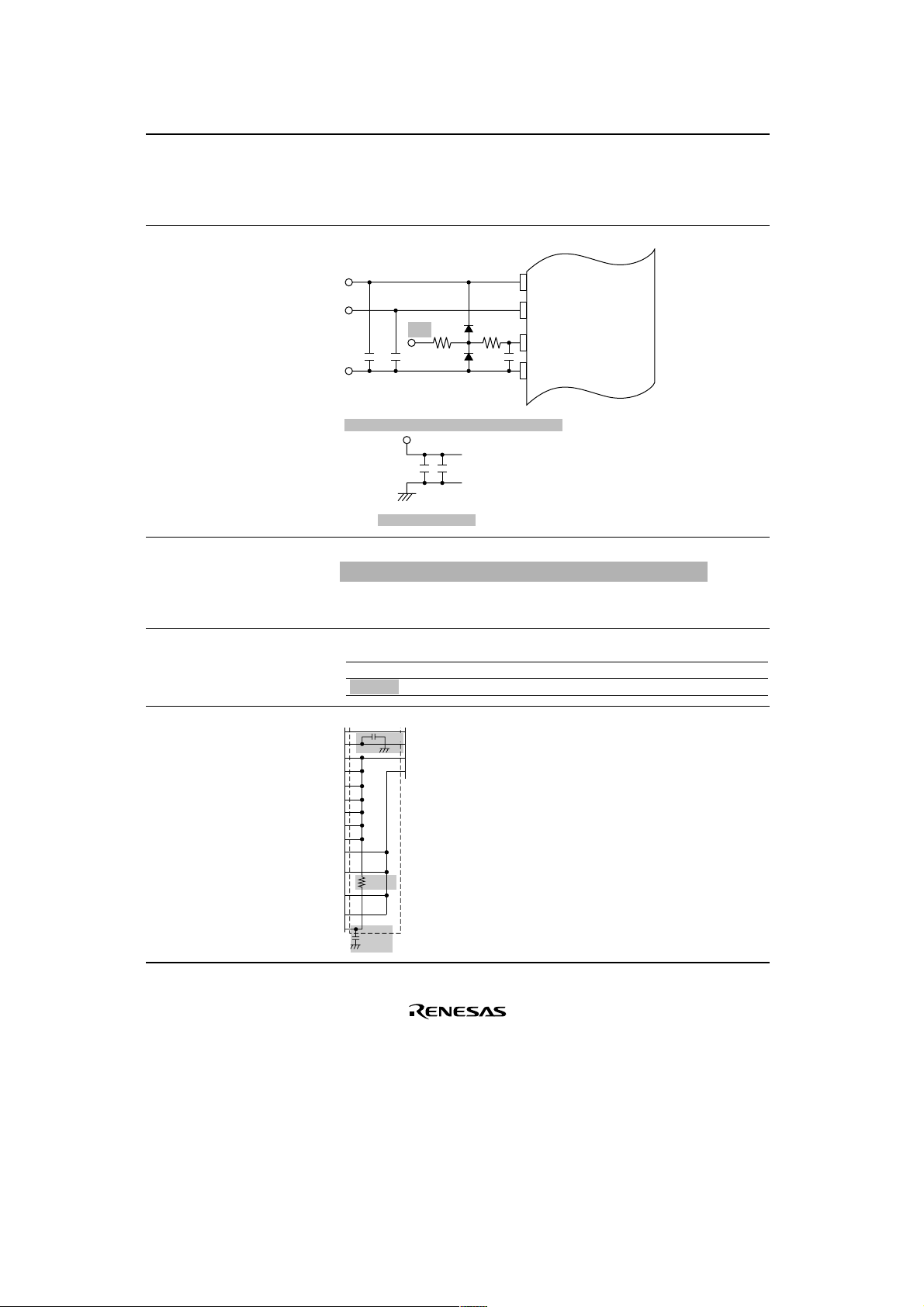

Figure amended

Figure 15.14

Example of a

Protection Circuit for

the Analog Input Pins

1

Notes: Numbers are only to be noted as reference value

*1

Rin

AVcc

AVref

2

*

100Ω

AN0 to AN7

0.1µF*1*

AVss

This LSI

16.7.2 Handling of

Analog Input Pins

Figure 16.8 Example

of Analog Input Pin

Protection Circuit

19.2 Port A

Table 19.2 Port A,

FP-144 Version

21.2.2 Socket

Adapter Pin

Correspondence and

Memory Map

Figure 21.2 SH7042

Pin and HN27C101

Pin Correspondence

(112-Pin Version)

585

649

671

10µF

*2 Rin: Input impedance

0.01µF

Note amended

Notes: Numbers are only to be noted as reference value

Table amended

PA16 (I/O)/AH (output) PA16 (I/O)/AH (output) PA16 (I/O)

PA15 (I/O)/CK (output) PA15 (I/O)/CK (output) PA15 (I/O)/CK (output)

Figure amended

2 nF

100 Ω

0.1 µF

Page 11

Section Page Description

21.2.2 Socket

Adapter Pin

Correspondence and

672

Figure amended

2 nF

Memory Map

Figure 21.3 SH7042

Pin and HN27C101

Pin Correspondence

(120-Pin Version)

100 Ω

0.1 µF

Figure 21.4 SH7043

Pin and HN27C101

Pin Correspondence

(144-Pin Version)

22.2.2 Mode

Transition Diagram

Figure 22.2 Flash

Memory Mode

Transitions

673 Figure amended

2 nF

100 Ω

0.1 µF

683

Note amended

Execute transition between the user mode and user program mode

while the CPU is not programming or erasing the flash memory

Page 12

Section Page Description

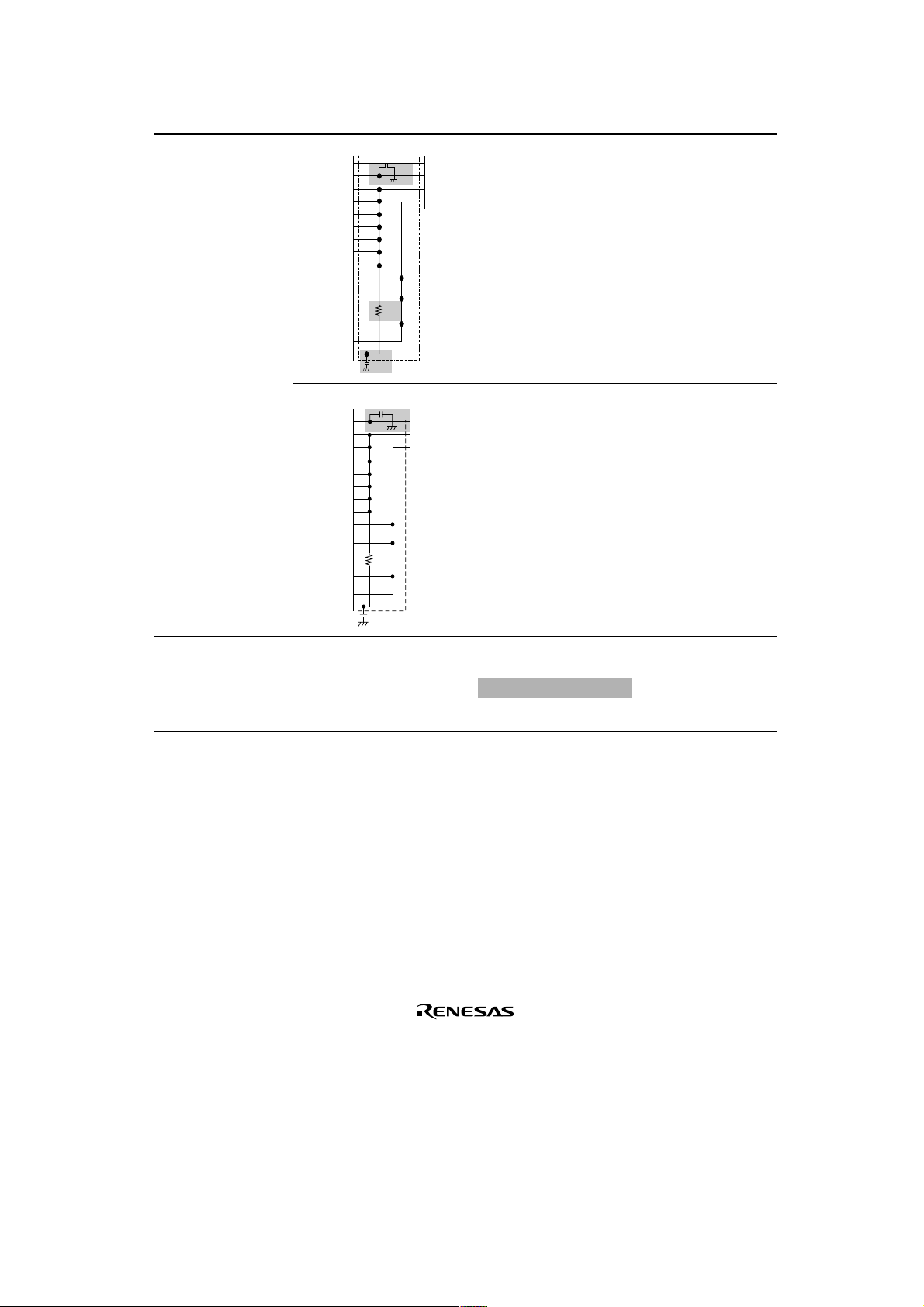

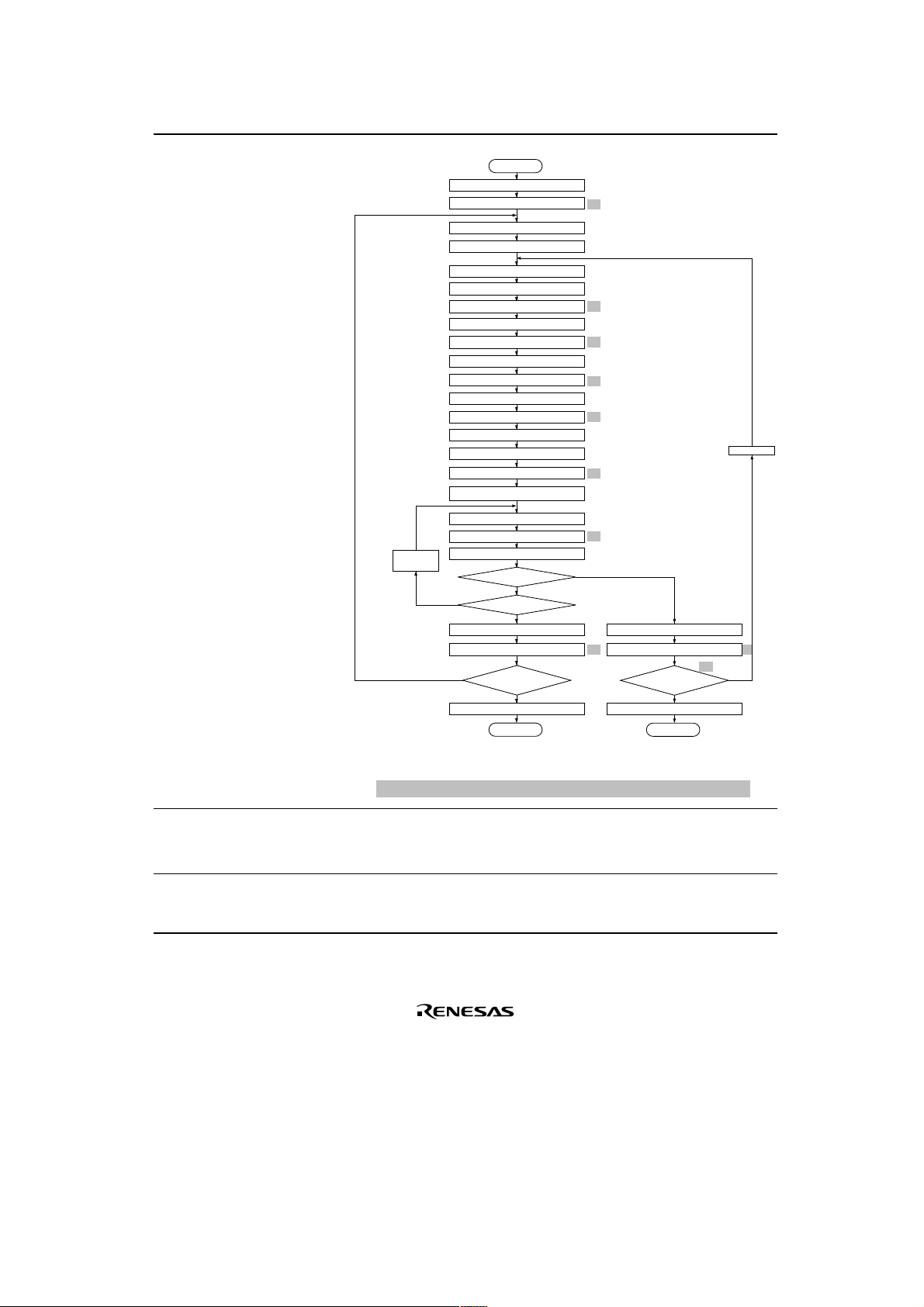

22.7.2 Program-

706

Figure amended

Verify Mode

Figure 22.13

Program/Program

Verify Flow

Verify

Increment address

NG

Start

Set SWE bit in FLMCR1

Wait 10 µs

Store 32-byte program data in

reprogram data area

n = 1

m = 0

Write 32-byte data in reprogram data area

in RAM to flash memory consecutively

Enable WDT

Set PSU1(2) bit in FLMCR1(2)

Wait 50 µs

Set P1(2) bit in FLMCR1(2)

Wait 200 µs

Clear P1(2) bit in FLMCR1(2)

Wait 10 µs

Clear PSU1(2) bit in FLMCR1(2)

Wait 10 µs

Disable WDT

Set PV1(2) bit in FLMCR1(2)

Wait 4 µs

Dummy write of H'FF to verify address

Wait 2 µs

Read verify data

3

Program data = verify data?

OK

Reprogram data computation

Transfer reprogram data to reprogram

data area

End of 32-byte

data verification?

OK

Clear PV1(2) bit in FLMCR1(2)

Wait 4 µs

flag = 0?

OK

Clear SWE bit in FLMCR1

*

5

*

4

*

1

*

5

*

Start of programming

5

*

End of programming

5

*

5

*

5

*

5

*

2

*

m = 1

NG

3

*

4

*

5

*

NG NG

Clear SWE bit in FLMCR1

n ≥ 1000

5

*

*5

OK

n ← n + 1

End of programming

Note *5 added.

*5 Make sure to set the wait times and repetitions as specified.

Programming may not complete correctly if values other than

the specified ones are used.

Programming failure

Page 13

Section Page Description

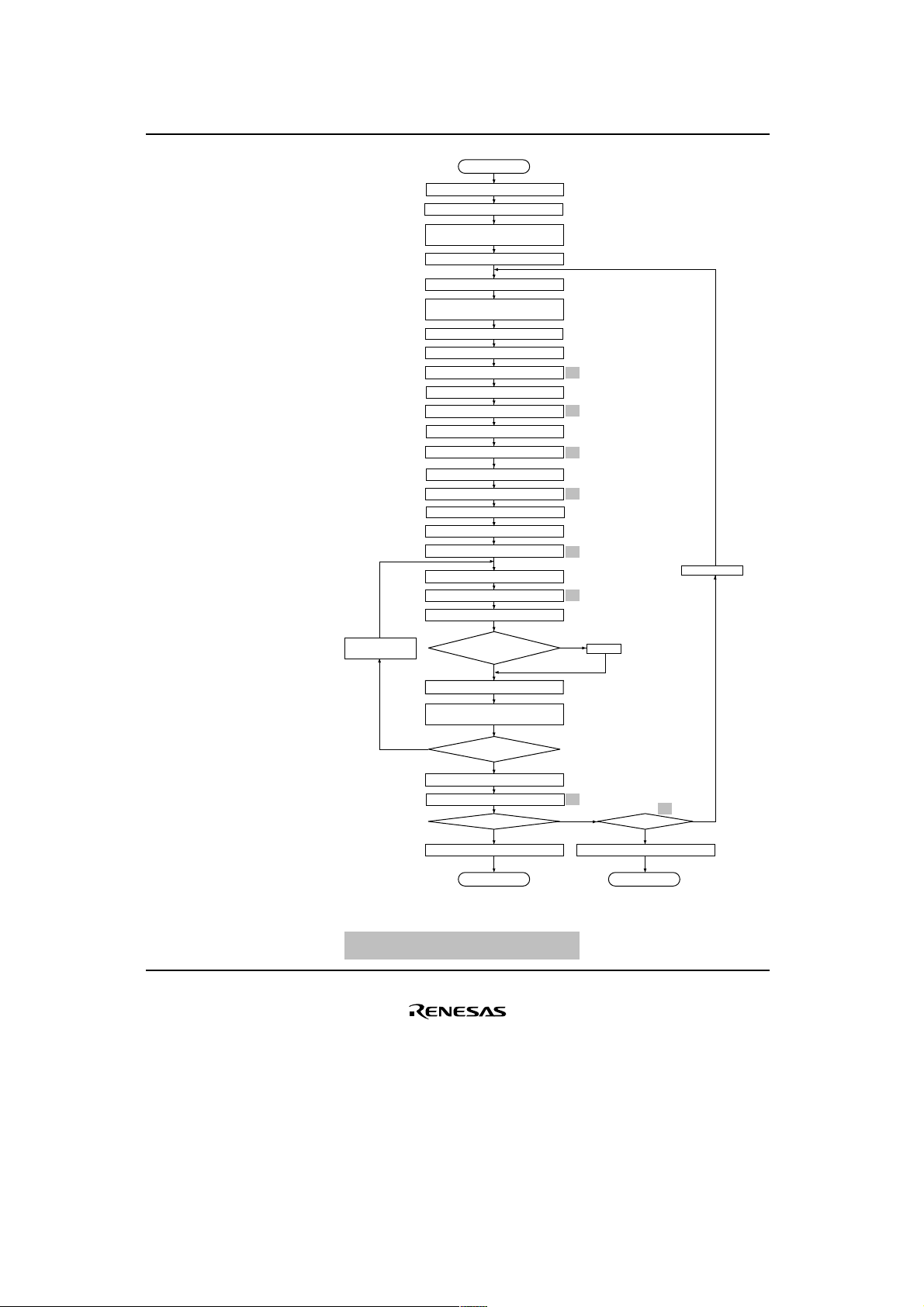

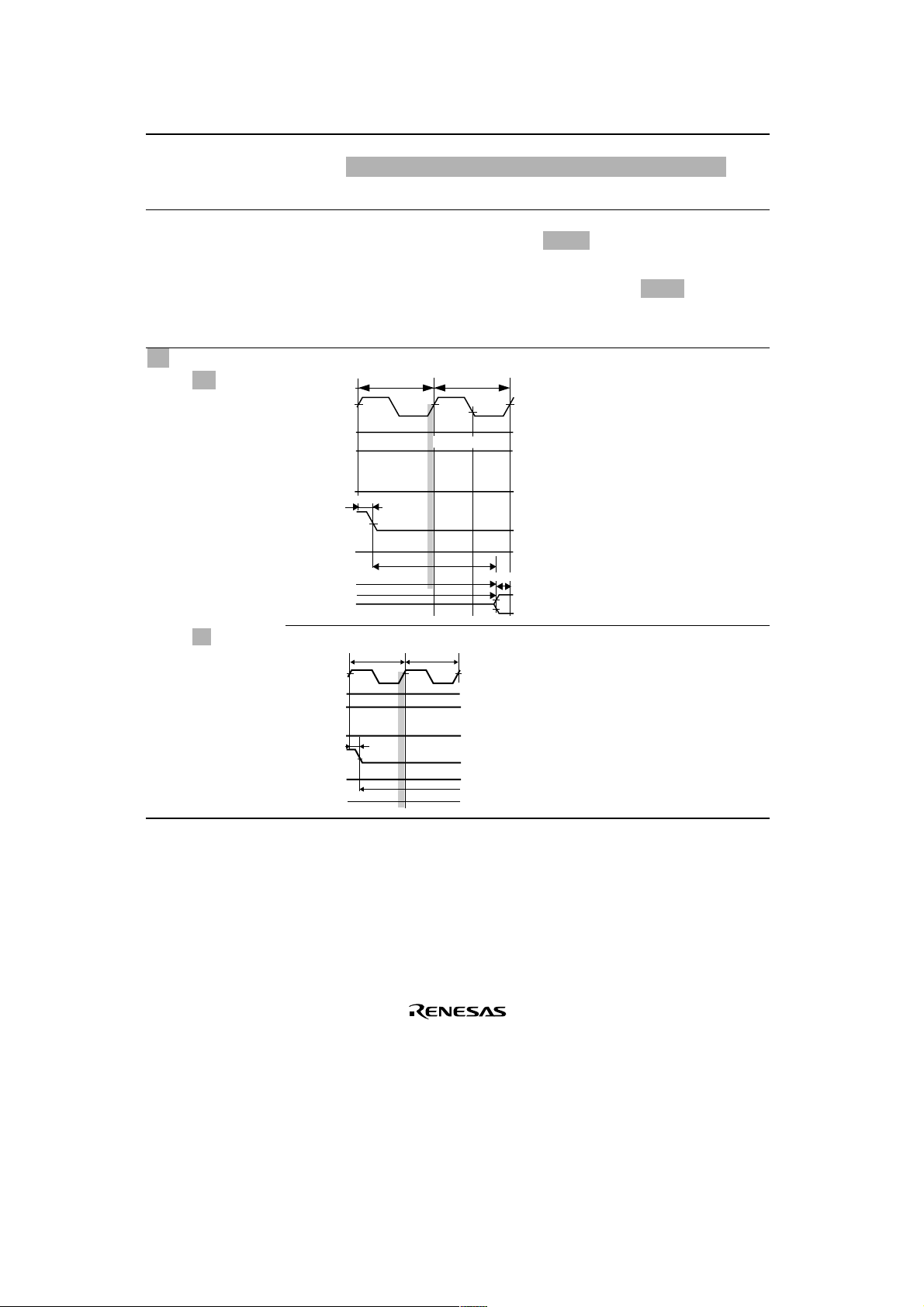

22.7.4 Erase-Verify

713

Figure amended

Mode

Figure 22.14

Erase/Erase-Verify

Flowchart

Increment

address

Notes: *1 Preprogramming (setting erase block data to all “0”) is not necessary.

*2 Verify data is read in 32-bit (longword) units.

*3 Set only one bit in EBR1(2). More than one bit cannot be set.

*4 Erasing is performed in block units. To erase a number of blocks, each block must be erased in turn.

*5 Make sure to set the wait times and repetitions as specified. Erasing may not complete correctly if values other

than the specified ones are used.

*1

Start

Set SWE bit in FLMCR1

Wait 10 µs

n = 1

Set EBR1(2)

Enable WDT

Set ESU1(2) bit in FLMCR1(2)

Wait 200 µs

Set E1(2) bit in FLMCR1(2)

Wait 5 ms

Clear E1(2) bit in FLMCR1(2)

Wait 10 µs

Clear ESU1(2) bit in FLMCR1(2)

Wait 10 µs

Disable WDT

Set EV1(2) bit in FLMCR1(2)

Wait 20 µs

Set block start address to verify address

H'FF dummy write to verify address

Wait 2 µs

Read verify data

Verify data = all "1"?

NG

Clear EV1(2) bit in FLMCR1(2)

*4

NG

Clear SWE bit in FLMCR1

OK

Last address of block?

OK

Wait 5 µs

End of

erasing of all erase

blocks?

OK

End of erasing

*5

*3

*5

Start erase

*5

Halt erase

*5

*5

*5

*5

*2

NG

Clear EV1(2) bit in FLMCR1(2)

*5 *5

Wait 5 µs

*5

n ≥ 60?

Clear SWE bit in FLMCR1

OK

Erase failure

n ← n + 1

NG

24.4.2 Canceling the

Standby Mode

25. Electrical

Characteristics (5V,

33.3 MHz Version)

747

—

Cancellation by a Manual Reset deleted

Deleted

Page 14

Section Page Description

25.2 DC

Characteristics

751 Note amended

*2 5 mA in the A mask version, except for F-ZTAT products.

Table 25.2 DC

Characteristics

25.3.2 Control

Signal Timing

Table 25.5 Control

Signal Timing

754 Note amended

Note: * The RES, MRES, NMI, BREQ, and IRQ7–IRQ0 signals are

asynchronous inputs, but when thesetup times shown here

are provided, the signals are considered to have produced

changes at clock rise (for RES, MRES, BREQ) or clock fall

(for NMI and IRQ7–IRQ0). If the setup times are not

provided, recognition is delayed until the next clock rise or

fall.

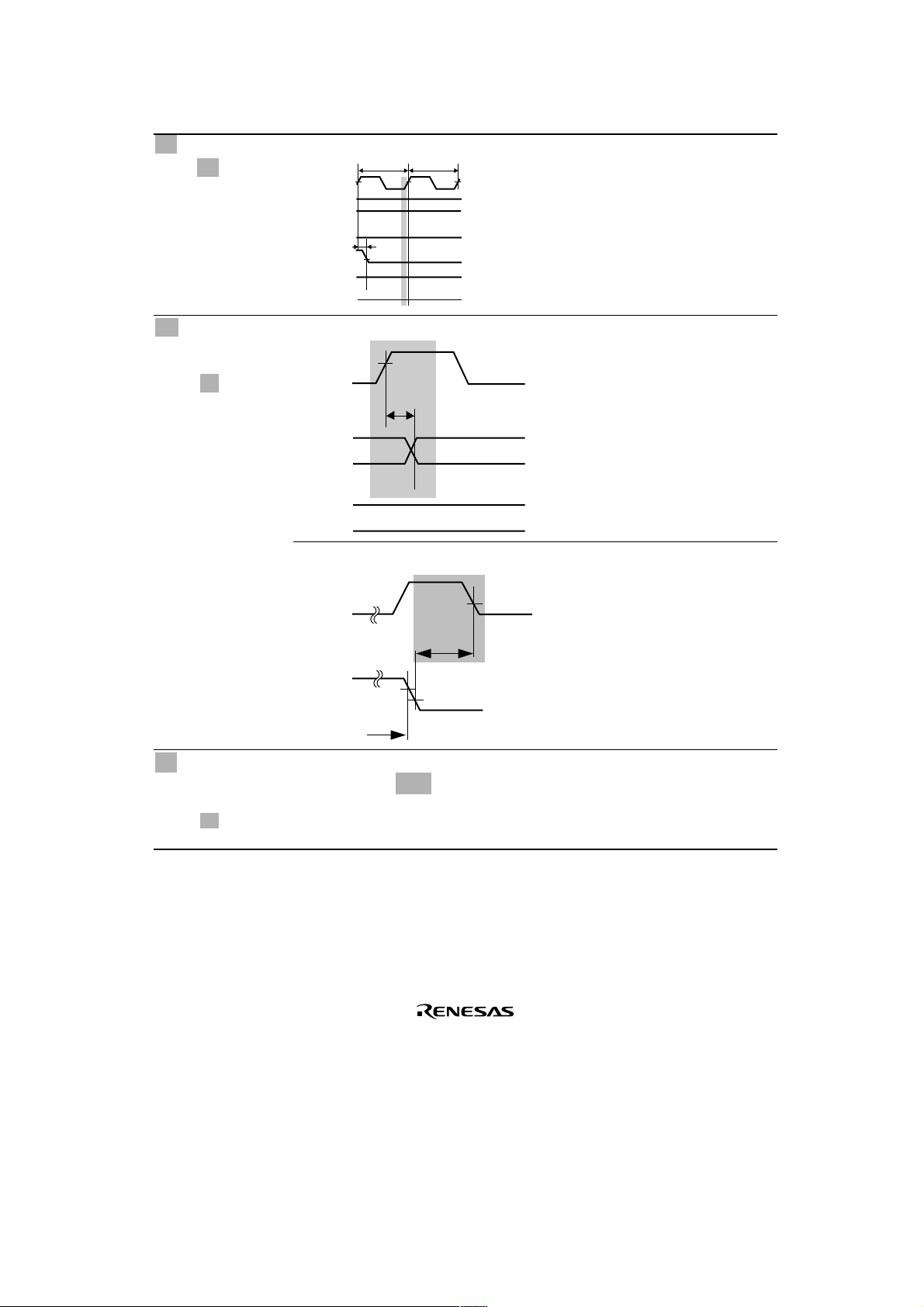

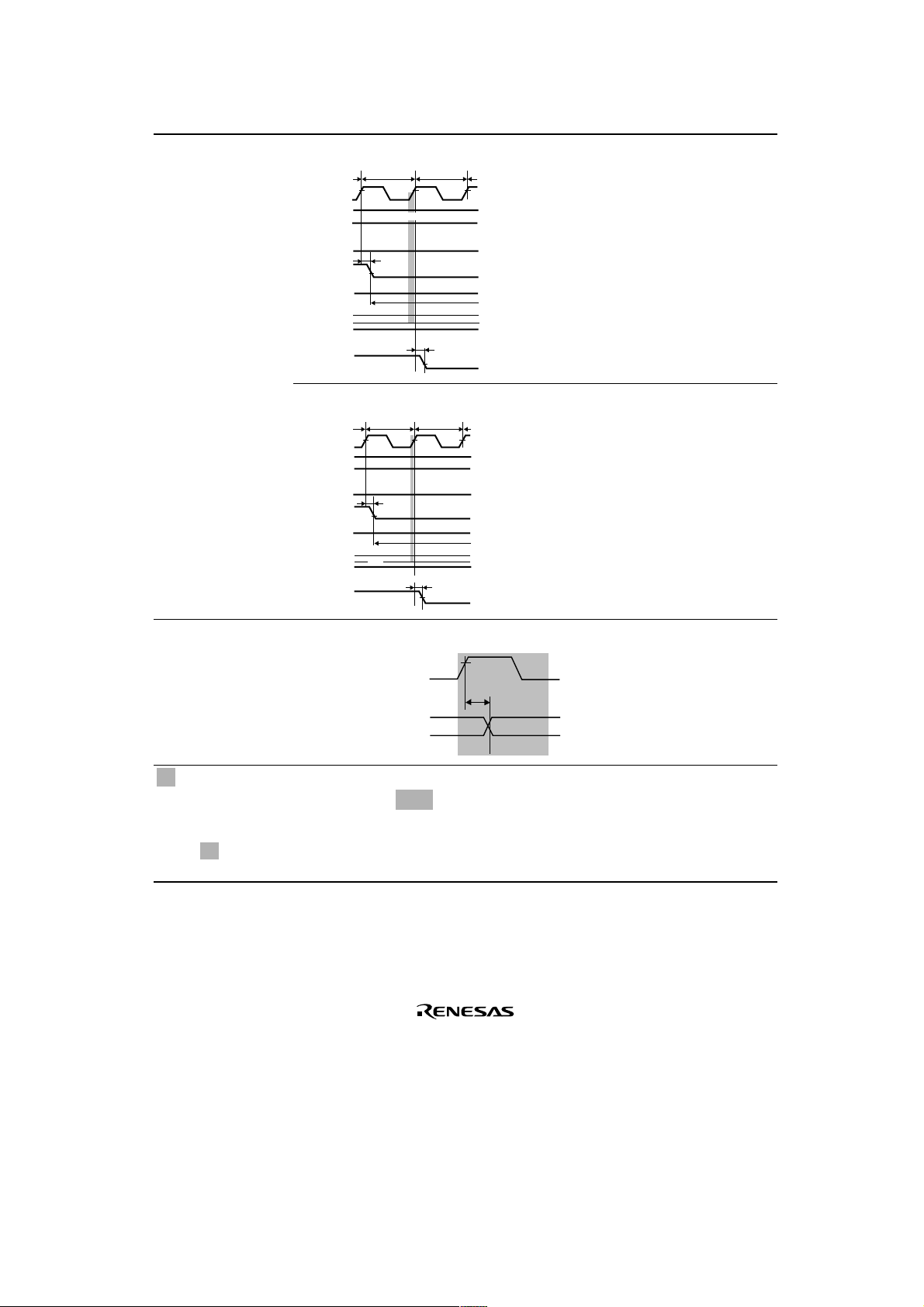

25.3.3 Bus Timing

Figure 25.12 DRAM

763 Figure amended

Tcw1 Tc2

Cycle (Normal Mode,

1 Wait, TPC=0,

RCD=0)

Column address

t

CASD1

t

CAC

t

t

RAC

t

AA

RDS

Figure 25.13 DRAM

Cycle (Normal Mode,

2 Waits, TPC=1,

RCD=1)

764 Figure amended

Tcw1 Tcw2

Column address

t

CASD1

t

CAC

t

AA

Page 15

Section Page Description

25.3.3 Bus Timing

Figure 25.14 DRAM

764 Figure amended

Tcw1 Tcw2

Cycle (Normal Mode,

3 Waits, TPC=1,

RCD=1)

t

CASD1

t

CAC

t

AA

Column

25.3.5 Multifunction

Timer Pulse Unit

Timing

Figure 25.23 MTU

I/O Timing

Figure 25.24 MTU

Clock Input Timing

25.3.11 Measuring

Conditions for AC

Characteristics

Figure 25.33 Output

Load Circuit

770 Figure amended

t

TOCD

770 Figure amended

t

TCKS

778

Title amended

Output Load Circuit

Page 16

Section Page Description

25.4 A/D Converter

779

Table amended

Characteristics

Table 25.16 A/D

Converter Timing (A

mask)

Non-linearity error

Offset error

Full scale error

Quantize error

*

*

*

*

26.2 DC

Characteristics

Table 26.2 DC

Characteristics

26.3.2 Control

Signal Timing

Table 26.5 Control

Signal Timing

26.3.3 Bus Timing

Figure 26.12 DRAM

Cycle (Normal Mode,

1 Wait, TPC = 0,

RCD = 0)

782

783

786

795

Table amended

Schmitt

trigger input

voltage

PA2, PA5, PA6–

PA9,

PE0–PE15

–

+

V

VCC×

0.07

——

– V

T

T

+

V

VT

≥ VCC× 0.9V (min)

VT– ≤ VCC× 0.2V (max)

Table amended

Analog

supply

current

*3 2 mA in the A mask version of MASK products.

AI

CC

AI

ref

— 48

— 0.5 1

*

mA f = 16.7MHz

3

mA QFP144 version only

Note amended

Notes: *1 SH7042/43 ZTAT (excluding A mask) are 3.2V.

*2 The RES, MRES, NMI, BREQ, and IRQ7–IRQ0 signals

are asynchronous inputs, but when the setup times

shown here are provided, the signals are considered to

have produced changes at clock rise (for RES, MRES,

BREQ) or clock fall (for NMI and IRQ7–IRQ0). If the

setup times are not provided, recognition is delayed until

the next clock rise or fall.

Figure amended

Tcw1 Tc2

Column address

t

CASD1

t

CAC

t

AA

t

RAC

t

RDS

Page 17

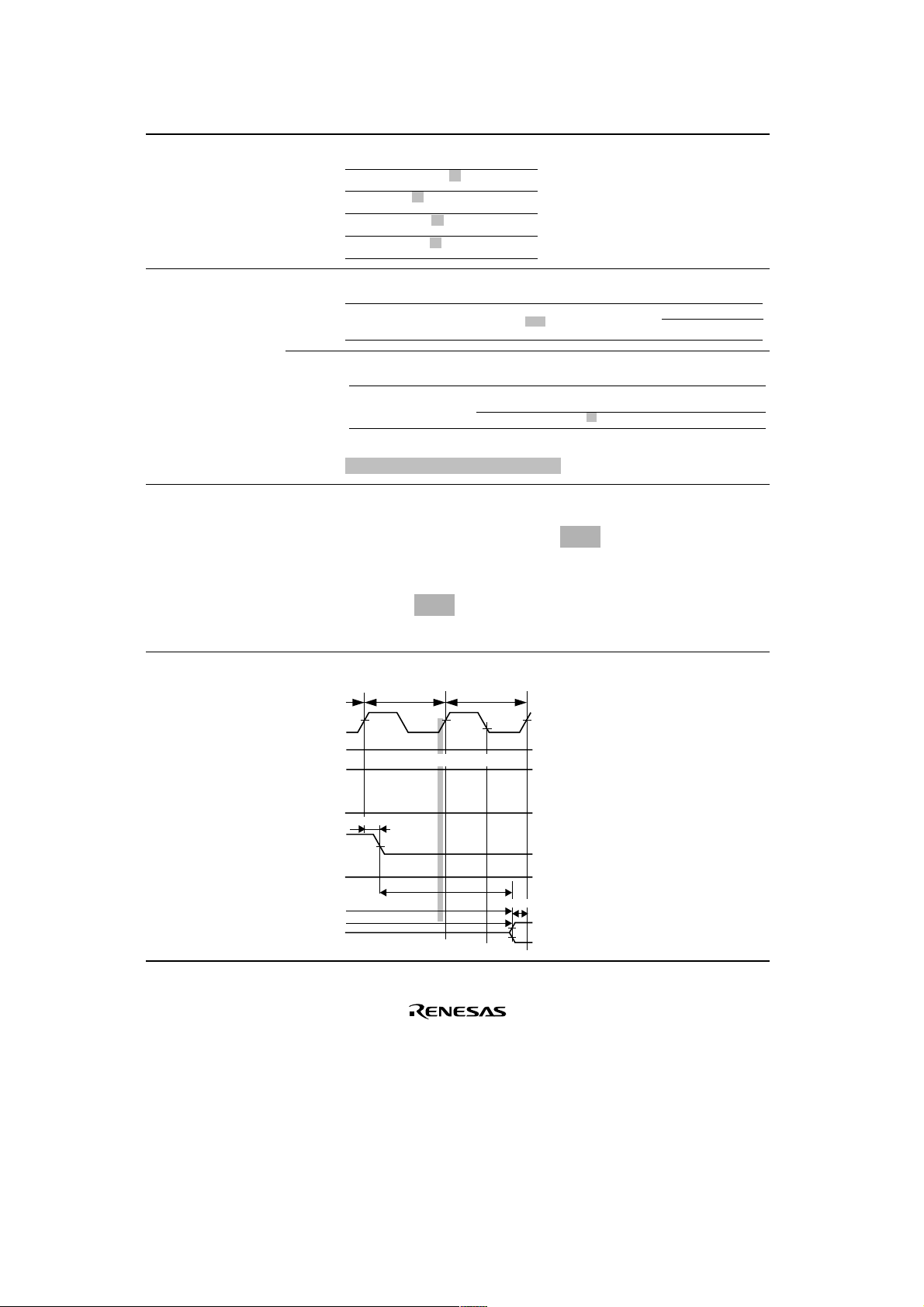

Section Page Description

26.3.3 Bus Timing

Figure 26.13 DRAM

796

Figure amended

Tcw1 Tcw2

Cycle (Normal Mode,

2 Waits, TPC = 1,

RCD = 1)

t

CASD1

t

RAC

Column address

t

CAC

t

AA

t

CASD1

Figure 26.14 DRAM

Cycle (Normal Mode,

3 Waits, TPC = 1,

RCD = 1)

26.3.5 Multifunction

Timer Pulse Unit

Timing

Figure 26.23 MTU

I/O Timing

26.3.11

Measurement

Conditions for AC

Characteristics

Figure 26.33 Output

Load Circuit

796

802

810

Figure amended

Tcw1 Tcw2

Column address

t

CASD1

t

CAC

t

AA

t

RAC

t

CASD1

Figure amended

CK

Output

compare output

Title amended

Output Load Circuit

t

TOCD

Page 18

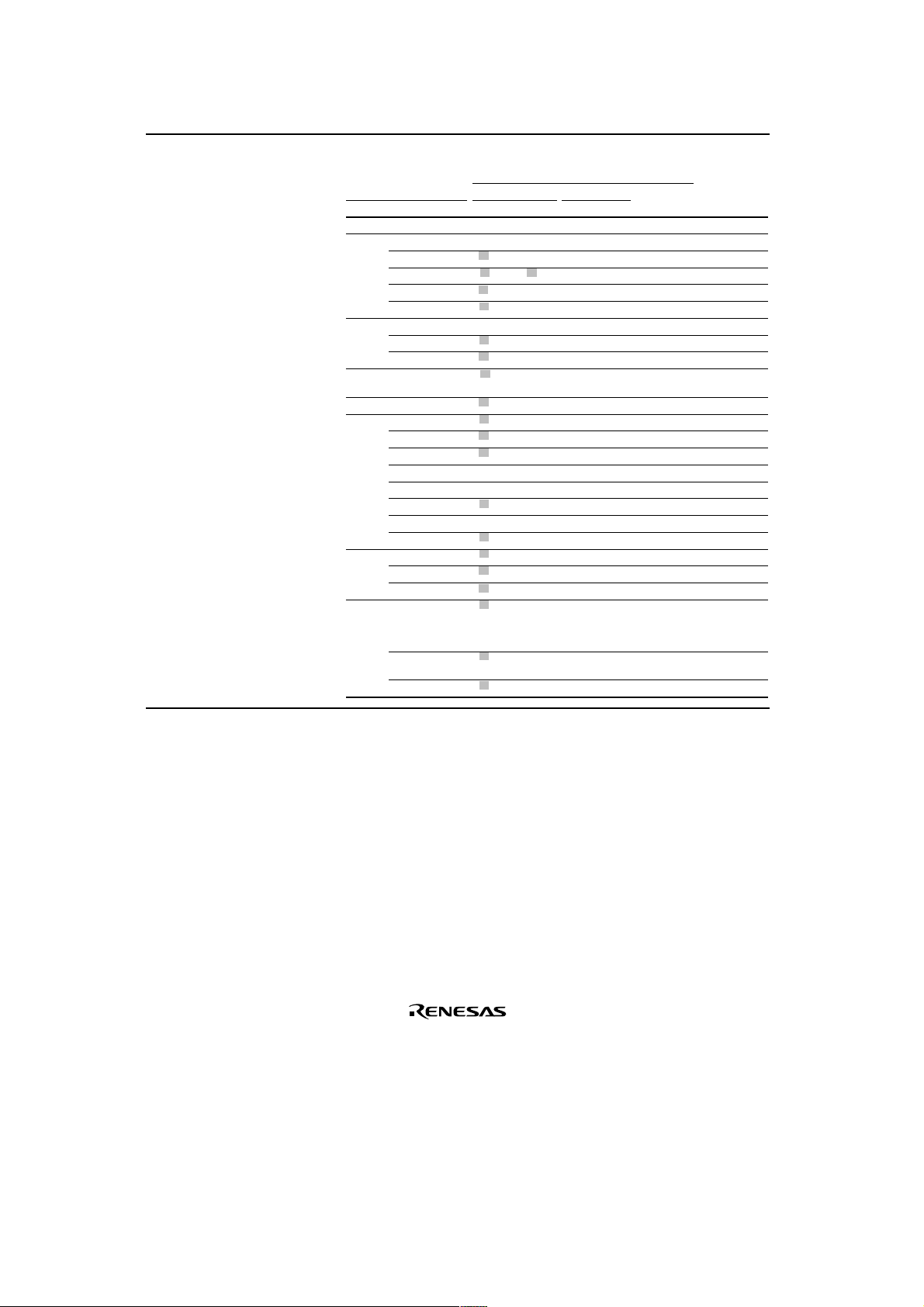

Section Page Description

Appendix B Block

844

Note added

Diagrams

Figure B.19

On-chip flash memory

PB4/IRQ2/POE2/

CASH,PB3/IRQ1/

POE1/CASL

Block Diagram

(F-ZTAT Version)

Note: * Only when n = 4.

*

A17

Appendix C Pin

States

Table C.1 Pin

Modes During Reset,

Power-Down, and

Bus Right Release

Modes (144 Pin)

865

Table amended

Pin modes

Pin Function Reset Power-Down

Class Pin Name Power-OnManual Standby Sleep Release Right Release

1

Clock CK O O H

*

System RES IIIII I

control

MRES Z

WDTOVF O

BREQ Z

BACK Z

4

*

IZII Z

3

*

4

*

4

*

3

*

O

OOO O

IZII I

OZOL L

Interrupt NMI I I I I I I

4

IRQ0–IRQ7 Z

IRQOUT (PD30) Z

IRQOUT (PE15) Z

Address

A0–A21 O

bus

Data bus D0–D31 Z

Bus WAIT Z

control

RD/WR, RAS Z

CASH, CASL,

CASLH, CASLL

*

IZII Z

4

*

OH

4

*

OZHO Z

2

*

OZOZ Z

4

*

I/O Z I/O Z Z

4

*

IZIZ Z

4

*

OOOZ Z

4

*

Z

OOOZ Z

1

*

RD HOZOZ Z

CS0, CS1 HOZOZ Z

4

CS2, CS3 Z

WRHH, WRHL,

WRH, WRL

AH Z

DMAC DACK0, DACK1

(PD26, PD27)

DACK0, DACK1

(PE14, PE15)

DRAK0, DRAK1 Z

DREQ0, DREQ1 Z

*

OZOZ Z

HOZOZ Z

4

*

OZOZ Z

4

*

Z

OO

4

*

Z

OZOO Z

4

*

OO

4

*

IZII Z

1

*

1

*

Bus Right Standby in Bus

OO O

1

HO H

OO O

OO O

*

1

*

1

*

Page 19

Section Page Description

Appendix C Pin

866

Table amended

States

Table C.1 Pin

Modes During Reset,

Power-Down, and

Bus Right Release

Modes (144 Pin)

(cont)

Pin Function Reset Power-Down

Class Pin Name Power-OnManual Standby Sleep Release Right Release

MTU TIOC0A–TIOC0D,

TIOC1A–TIOC1D,

TIOC2A–TIOC2D,

TIOC3A, TIOC3C

TIOC3B,TIOC3D,

TIOC4A–TIOC4D

TCLKA–TCLKD Z

Port

POE0–POE3 Z

control

SCI SCK0–SCK1 Z

TXD0–TCD1 Z

RXD0–RXD1 Z

A/D ADTRG Z

converter

AN0–AN7 Z I Z I I Z

I/O Port PA0–PA23 Z

PB0–PB9

PC0–PC15

PD0–PD31

PE0–PE8,PE10

PE9,PE11–PE15 Z

PF0–PF17 Z I Z I I Z

Notes: 1. There are instances where bus right release and transition to software standby mode

occur simultaneously due to the timing between BREQ and internal operations. In such

cases, standby mode results, but the standby state may be different.

The initial pin states depend on the mode. See section 18, Pin Function Controller

(PFC), for details.

2. I: Input, O: Output, H: High-level output, L: Low-level output, Z: High impedance,

K: Input pin with high impedance, output pin mode maintained.

*1 If the standby control register port high-impedance bits are set to 1, output pins become

high impedance.

*2 A21–A18 will become input ports after power-on reset.

*3 Input in the SH7044/SH7045 F-ZTAT version.

*4 General use I/O ports PAn, PBn, PCn, PDn, and PEn, as well as pins multiplexed with

them, are unstable during the RES setup time (t

goes to low level.

Pin modes

Bus Right Standby in Bus

4

*

Z

I/O K

4

*

Z

I/O Z I/O I/O Z

4

*

IZII Z

4

*

IZII Z

4

*

I/O Z I/O I/O Z

4

*

OO

4

*

IZII Z

4

*

IZII Z

4

*

I/O K

4

*

I/O Z K I/O Z

1

*

I/O I/O K

1

*

OO O

1

*

K I/O K

) immediately after the RES pin

RESS

1

*

1

*

1

*

Page 20

Section Page Description

Appendix C Pin

867

Table amended

States

Table C.2 Pin

Modes During Reset,

Power-Down, and

Bus Right Release

Modes (112 Pin,

120 Pin)

Pin Function Reset Power-Down

Class Pin Name Power-OnManual Standby Sleep Release Right Release

Clock CK O O H

System RES IIIII I

control

MRES Z

WDTOVF O

BREQ Z

BACK Z

Interrupt NMI I I I I I I

IRQ0–IRQ7 Z

IRQOUT Z

Address

A0–A21 O

bus

Data bus D0–D31 Z

Bus WAIT Z

control

RDWR, RAS Z

CASH, CASL Z

RD HOZOZ Z

CS0, CS1 HOZOZ Z

CS2, CS3 Z

WRH, WRL HOZOZ Z

AH Z

DMAC DACK0–DACK1 Z

DRAK0–DRAK1 Z

DREQ0–DREQ1 Z

MTU TIOC0A–TIOC0D,

TIOC1A–TIOC1D,

TIOC2A–TIOC2D,

TIOC3A, TIOC3C

TIOC3B,TIOC3D,

TIOC4A–TIOC4D

TCLKA–TCLKD Z

Pin modes

Bus Right Standby in Bus

1

*

OO O

4

*

IZII Z

3

*

4

*

4

*

4

*

4

*

*

4

*

4

*

4

*

4

*

4

*

4

*

4

*

4

*

4

*

4

*

Z

4

*

Z

4

*

3

*

O

OOO O

IZII I

OZOL L

IZII Z

OZHO Z

2

OZOZ Z

I/O Z I/O Z Z

IZIZ Z

OOOZ Z

OOOZ Z

OZOZ Z

OZOZ Z

OZOO Z

OZOO Z

IZII Z

1

I/O K

*

I/O I/O K

I/O Z I/O I/O Z

IZII Z

1

*

Page 21

Section Page Description

Appendix C Pin

868

Table amended

States

Table C.2 Pin

Modes During Reset,

Power-Down, and

Bus Right Release

Modes (112 Pin,

120 Pin) (cont)

Pin Function Reset Power-Down

Class Pin Name Power-OnManual Standby Sleep Release Right Release

Port

POE0–POE3 Z

control

SCI SCK0–SCK1 Z

TXD0–TCD1 Z

RXD0–RXD1 Z

A/D

ADTRG Z

converter

control

AN0–AN7 Z I Z I I Z

I/O Port PA0–PA15 Z

PB0–PB9

PC0–PC15

PD0–PD15

PE0–PE8–PE10

PE9,PE11–PE15 Z

PF0–PF7 Z I Z I I Z

Notes: 1. There are instances where bus right release and transition to software standby mode

occur simultaneously due to the timing between BREQ and internal operations. In such

cases, standby mode results, but the standby state may be different.

The initial pin states depend on the mode. See section 18, Pin Function Controller

(PFC), for details.

2. I: Input, O: Output, H: High-level output, L: Low-level output, Z: High impedance,

K: Input pin with high impedance, output pin mode maintained.

*1 If the standby control register port high-impedance bits are set to 1, output pins become

high impedance.

*2A21–A18 will become input ports after power-on reset.

*3 Input in the SH7044/SH7045 F-ZTAT version.

*4 General use I/O ports PAn, PBn, PCn, PDn, and PEn, as well as pins multiplexed with

them, are unstable during the RES setup time (t

goes to low level.

Pin modes

Bus Right Standby in Bus

4

*

IZII Z

4

*

I/O Z I/O I/O Z

4

*

OO

4

*

IZII Z

4

*

IZII Z

4

*

I/O K

4

*

I/O Z K I/O Z

1

*

OO O

1

*

K I/O K

) immediately after the RES pin

RESS

1

*

1

*

Page 22

Section Page Description

Appendix E Product

Code Lineup

Table E.1 SH7040,

SH7041, SH7042,

876,

877

Table amended

Product

Type

SH7040A Mask ROM

verion

SH7043, SH7044,

and SH7045 Product

Lineup

ROM less

verion

SH7041A Mask ROM

verion

ROM less

verion

SH7042 Mask ROM

verion

Z-TAT

version

SH7042A Mask ROM

verion

Product

Type

SH7042A Z-TAT

version

SH7043 Mask ROM

version

Z-TAT

version

SH7043A Mask ROM

version

Z-TAT

version

SH7044 Mask ROM

version

F-ZTAT

version

SH7045 Mask ROM

version

F-ZTAT

version

(***) is the ROM code.

NoteS: 1. Package with Copper used as the lead material.

2. *** in the Order Model No. is the ROM code, consisting of a letter and a two-digit

number (ex. E00). The letter indicates the voltage and frequency, as shown below.

• E, F, G, H: 5.0 V, 28 MHz

• P, Q, R: 3.3 V, 16 MHz

Mask

Product Code Mark Code Package Order Model No.*

Version

A MASK HD6437040AF28

HD6437040AVF16

HD6437040AVX16

HD6437040ACF28

HD6437040AVCF16

A MASK HD6417040AF28

HD6417040AVF16

HD6417040AVX16

HD6417040ACF28

HD6417040AVCF16

A MASK HD6437041AF28

HD6437041AVF16

HD6437041ACF28

HD6437041AVCF16

A MASK HD6417041AF28

HD6417041AVF16

HD6417041ACF28

HD6417041AVCF16

– HD6437042F28

HD6437042VF16

– HD6477042F28

HD6477042VF16

A MASK HD6437042AF28

HD6437042AVF16

HD6437042AVX16

HD6437042ACF28

HD6437042AVCF16

Mask

Product Code Mark Code Package Order Model No.*

Version

A MASK HD6477042AF28

HD6477042AVF16

HD6477042AVX16

HD6477042ACF28

HD6477042AVCF16

– HD6437043F28

HD6437043VF16

– HD6477043F28

HD6477043VF16

A MASK HD6437043AF28

HD6437043AVF16

HD6437043ACF28

HD6437043AVCF16

A MASK HD6477043AF28

HD6477043AVF16

HD6477043ACF28

HD6477043AVCF16

A MASK HD6437044F28 HD6437044(***)F28 QFP2020-112 HD6437044***F

HD64F7044F28 HD64F7044F28 QFP2020-112 HD64F7044F28

A MASK HD6437045F28 HD6437045(***)F28 QFP2020-144 HD6437045***F

HD64F7045F28 HD64F7045F28 QFP2020-144 HD64F7045F28

HD6437040A (***)F28

HD6437040A(***)VF16

HD6437040A(***)VX16

HD6437040A(***)CF28

HD6437040A(***)VCF16

HD6417040AF28

HD6417040AVF16

HD6417040AVX16

HD6417040ACF28

HD6417040AVCF16

HD6437041A(***)F28

HD6437041A(***)VF16

HD6437041A(***)CF28

HD6437041A(***)VCF16

HD6417041AF28

HD6417041AVF16

HD6417041ACF28

HD6417041AVCF16

HD6437042 (***)F28

HD6437042 (***)VF16

HD6477042F28

HD6477042VF16

HD6437042A(***)F28

HD6437042A(***)VF16

HD6437042A(***)VX16

HD6437042A(***)CF28

HD6437042A(***)VCF16

HD6477042AF28

HD6477042AVF16

HD6477042AVX16

HD6477042ACF28

HD6477042AVCF16

HD6437043(***)F28

HD6437043(***)VF16

HD6477043F28

HD6477043VF16

HD6437043A(***)F28

HD6437043A(***)VF16

HD6437043A(***)CF28

HD6437043A(***)VCF16

HD6477043AF28

HD6477043AVF16

HD6477043ACF28

HD6477043AVCF16

QFP2020-112

QFP2020-112

TQFP1414-120

QFP2020-112Cu*

QFP2020-112Cu*

QFP2020-112

QFP2020-112

TQFP1414-120

QFP2020-112Cu*

QFP2020-112Cu*

QFP2020-144

QFP2020-144

QFP2020-144Cu*

QFP2020-144Cu*

QFP2020-144

QFP2020-144

QFP2020-144Cu*

QFP2020-144Cu*

QFP2020-112

QFP2020-112

QFP2020-112

QFP2020-112

QFP2020-112

QFP2020-112

TQFP1414-120

QFP2020-112Cu*

QFP2020-112Cu*

QFP2020-112

QFP2020-112

TQFP1414-120

QFP2020-112Cu*

QFP2020-112Cu*

QFP2020-144

QFP2020-144

QFP2020-144

QFP2020-144

QFP2020-144

QFP2020-144

QFP2020-144Cu*

QFP2020-144Cu*

QFP2020-144

QFP2020-144

QFP2020-144Cu*

QFP2020-144Cu*

HD6437040A***F

HD6437040A***F

HD6437040A***X

1

HD6437040A***CF

1

HD6437040A***CF

HD6417040AF28

HD6417040AVF16

HD6417040AVX16

1

HD6417040ACF28

1

HD6417040AVCF16

HD6437041A***F

HD6437041A***F

1

HD6437041A***CF

1

HD6437041A***CF

HD6417041AF28

HD6417041AVF16

1

HD6417041ACF28

1

HD6417041AVCF16

HD6437042***F

HD6437042***F

HD6477042F28

HD6477042VF16

HD6437042A***F

HD6437042A***F

HD6437042A***X

1

HD6437042A***CF

1

HD6437042A***CF

HD6477042AF28

HD6477042AVF16

HD6477042AVX16

1

HD6477042ACF28

1

HD6477042AVCF16

HD6437043***F

HD6437043***F

HD6477043F28

HD6477043VF16

HD6437043A***F

HD6437043A***F

1

HD6437043A***CF

1

HD6437043A***CF

HD6477043AF28

HD6477043AVF16

1

HD6477043ACF28

1

HD6477043AVCF16

2

2

Page 23

Contents

Section 1 SH7040 Series Overview............................................................................. 1

1.1 SH7040 Series Overview................................................................................................... 1

1.1.1 SH7040 Series Features........................................................................................ 1

1.2 Block Diagram................................................................................................................... 11

1.3 Pin Arrangement and Pin Functions.................................................................................. 13

1.3.1 Pin Arrangment..................................................................................................... 13

1.3.2 Pin Arrangement by Mode ................................................................................... 16

1.3.3 Pin Functions ........................................................................................................ 37

1.4 The F-ZTAT Version Onboard Programming................................................................... 42

Section 2 CPU..................................................................................................................... 45

2.1 Register Configuration....................................................................................................... 45

2.1.1 General Registers (Rn) ......................................................................................... 45

2.1.2 Control Registers .................................................................................................. 46

2.1.3 System Registers................................................................................................... 47

2.1.4 Initial Values of Registers .................................................................................... 47

2.2 Data Formats...................................................................................................................... 48

2.2.1 Data Format in Registers ...................................................................................... 48

2.2.2 Data Format in Memory....................................................................................... 48

2.2.3 Immediate Data Format........................................................................................ 48

2.3 Instruction Features ........................................................................................................... 49

2.3.1 RISC-Type Instruction Set ................................................................................... 49

2.3.2 Addressing Modes ................................................................................................ 52

2.3.3 Instruction Format ................................................................................................ 56

2.4 Instruction Set by Classification........................................................................................ 59

2.5 Processing States ............................................................................................................... 72

2.5.1 State Transitions................................................................................................... 72

2.5.2 Power-Down State................................................................................................ 74

Section 3 Operating Modes............................................................................................. 77

3.1 Operating Modes, Types, and Selection............................................................................ 77

3.2 Explanation of Operating Modes....................................................................................... 78

3.3 Pin Configuration............................................................................................................... 79

Section 4 Clock Pulse Generator (CPG)..................................................................... 81

4.1 Overview............................................................................................................................ 81

4.1.1 Block Diagram...................................................................................................... 81

4.2 Oscillator............................................................................................................................ 81

4.2.1 Connecting a Crystal Oscillator............................................................................ 81

i

Page 24

4.2.2 External Clock Input Method............................................................................... 82

4.3 Prescaler............................................................................................................................. 83

4.4 Oscillator Halt Function..................................................................................................... 83

4.5 Usage Notes....................................................................................................................... 83

4.5.1 Oscillator Usage Notes......................................................................................... 83

4.5.2 Notes on Board Design......................................................................................... 84

4.5.3 Spread Spectrum Clock Generator Usage Notes.................................................. 85

Section 5 Exception Processing..................................................................................... 87

5.1 Overview............................................................................................................................ 87

5.1.1 Types of Exception Processing and Priority......................................................... 87

5.1.2 Exception Processing Operations......................................................................... 88

5.1.3 Exception Processing Vector Table...................................................................... 89

5.2 Resets................................................................................................................................. 90

5.2.1 Power-On Reset.................................................................................................... 91

5.2.2 Manual Reset ........................................................................................................ 91

5.3 Address Errors ................................................................................................................... 92

5.3.1 Address Error Exception Processing .................................................................... 93

5.4 Interrupts............................................................................................................................ 93

5.4.1 Interrupt Priority Level......................................................................................... 94

5.4.2 Interrupt Exception Processing............................................................................. 94

5.5 Exceptions Triggered by Instructions................................................................................ 94

5.5.1 Trap Instructions................................................................................................... 95

5.5.2 Illegal Slot Instructions......................................................................................... 95

5.5.3 General Illegal Instructions................................................................................... 96

5.6 When Exception Sources Are Not Accepted..................................................................... 96

5.6.1 Immediately after a Delayed Branch Instruction.................................................. 96

5.6.2 Immediately after an Interrupt-Disabled Instruction............................................ 96

5.7 Stack Status after Exception Processing Ends................................................................... 97

5.8 Notes on Use...................................................................................................................... 98

5.8.1 Value of Stack Pointer (SP).................................................................................. 98

5.8.2 Value of Vector Base Register (VBR) ................................................................. 98

5.8.3 Address Errors Caused by Stacking of Address Error Exception Processing...... 98

Section 6 Interrupt Controller (INTC)......................................................................... 99

6.1 Overview............................................................................................................................ 99

6.1.1 Features................................................................................................................. 99

6.1.2 Block Diagram...................................................................................................... 99

6.1.3 Pin Configuration ................................................................................................. 101

6.1.4 Register Configuration ......................................................................................... 101

6.2 Interrupt Sources................................................................................................................ 102

6.2.1 NMI Interrupts...................................................................................................... 102

6.2.2 User Break Interrupt............................................................................................. 102

ii

Page 25

6.2.3 IRQ Interrupts....................................................................................................... 102

6.2.4 On-Chip Peripheral Module Interrupts................................................................. 103

6.2.5 Interrupt Exception Vectors and Priority Rankings ............................................. 103

6.3 Description of Registers..................................................................................................... 108

6.3.1 Interrupt Priority Registers A–H (IPRA–IPRH)................................................... 108

6.3.2 Interrupt Control Register (ICR) .......................................................................... 109

6.3.3 IRQ Status Register (ISR) .................................................................................... 110

6.4 Interrupt Operation............................................................................................................. 112

6.4.1 Interrupt Sequence................................................................................................ 112

6.4.2 Stack after Interrupt Exception Processing........................................................... 114

6.5 Interrupt Response Time.................................................................................................... 114

6.6 Data Transfer with Interrupt Request Signals ................................................................... 116

6.6.1 Handling DTC Activating and CPU Interrupt Sources,

but Not DMAC Activating Sources ..................................................................... 117

6.6.2 Handling DMAC Activating Sources but Not CPU Interrupt

or DTC Activating Sources .................................................................................. 118

6.6.3 Handling DTC Activating Sources but Not CPU Interrupt

or DMAC Activating Sources .............................................................................. 118

6.6.4 Treating CPU Interrupt Sources but Not DTC

or DMAC Activating Sources .............................................................................. 118

Section 7 User Break Controller (UBC)..................................................................... 119

7.1 Overview............................................................................................................................ 119

7.1.1 Features................................................................................................................. 119

7.1.2 Block Diagram...................................................................................................... 119

7.1.3 Register Configuration ......................................................................................... 120

7.2 Register Descriptions......................................................................................................... 121

7.2.1 User Break Address Register (UBAR)................................................................. 121

7.2.2 User Break Address Mask Register (UBAMR) ................................................... 122

7.2.3 User Break Bus Cycle Register (UBBR).............................................................. 123

7.3 Operation ........................................................................................................................... 126

7.3.1 Flow of the User Break Operation ....................................................................... 126

7.3.2 Break on On-Chip Memory Instruction Fetch Cycle ........................................... 128

7.3.3 Program Counter (PC) Values Saved................................................................... 128

7.4 Use Examples..................................................................................................................... 128

7.4.1 Break on CPU Instruction Fetch Cycle ................................................................ 128

7.4.2 Break on CPU Data Access Cycle........................................................................ 129

7.4.3 Break on DMA/DTC Cycle.................................................................................. 130

7.5 Cautions on Use................................................................................................................. 130

7.5.1 On-Chip Memory Instruction Fetch..................................................................... 130

7.5.2 Instruction Fetch at Branches............................................................................... 130

7.5.3 Contention between User Break and Exception Handling................................... 131

7.5.4 Break at Non-Delay Branch Instruction Jump Destination.................................. 131

iii

Page 26

Section 8 Data Transfer Controller (DTC)................................................................. 133

8.1 Overview............................................................................................................................ 133

8.1.1 Features................................................................................................................. 133

8.1.2 Block Diagram...................................................................................................... 134

8.1.3 Register Configuration ......................................................................................... 135

8.2 Register Description .......................................................................................................... 135

8.2.1 DTC Mode Register (DTMR) .............................................................................. 135

8.2.2 DTC Source Address Register (DTSAR)............................................................. 138

8.2.3 DTC Destination Address Register (DTDAR)..................................................... 138

8.2.4 DTC Initial Address Register (DTIAR) ............................................................... 139

8.2.5 DTC Transfer Count Register A (DTCRA) ......................................................... 139

8.2.6 DTC Transfer Count Register B (DTCRB).......................................................... 140

8.2.7 DTC Enable Registers (DTER) ............................................................................ 140

8.2.8 DTC Control/Status Register (DTCSR)............................................................... 141

8.2.9 DTC Information Base Register (DTBR)............................................................. 143

8.3 Operation ........................................................................................................................... 143

8.3.1 Overview of Operation......................................................................................... 143

8.3.2 Activating Sources................................................................................................ 145

8.3.3 DTC Vector Table ................................................................................................ 145

8.3.4 Register Information Placement........................................................................... 148

8.3.5 Normal Mode........................................................................................................ 149

8.3.6 Repeat Mode......................................................................................................... 149

8.3.7 Block Transfer Mode............................................................................................ 150

8.3.8 Operation Timing ................................................................................................. 151

8.3.9 DTC Execution State Counts................................................................................ 151

8.3.10 DTC Usage Procedure .......................................................................................... 153

8.3.11 DTC Use Example................................................................................................ 153

8.4 Cautions on Use................................................................................................................. 154

Section 9 Cache Memory (CAC).................................................................................. 155

9.1 Overview............................................................................................................................ 155

9.1.1 Features................................................................................................................. 155

9.1.2 Block Diagram...................................................................................................... 156

9.1.3 Register Configuration ......................................................................................... 156

9.2 Register Explanation.......................................................................................................... 157

9.2.1 Cache Control Register (CCR)............................................................................. 157

9.3 Address Array and Data Array .......................................................................................... 158

9.3.1 Cache Address Array Read/Write Space.............................................................. 159

9.3.2 Cache Data Array Read/Write Space ................................................................... 159

9.4 Cautions on Use................................................................................................................. 160

9.4.1 Cache Initialization............................................................................................... 160

9.4.2 Forced Access to Address Array and Data Array................................................. 160

9.4.3 Cache Miss Penalty and Cache Fill Timing ......................................................... 160

iv

Page 27

9.4.4 Cache Hit after Cache Miss.................................................................................. 162

Section 10 Bus State Controller (BSC) ......................................................................... 163

10.1 Overview............................................................................................................................ 163

10.1.1 Features................................................................................................................. 163

10.1.2 Block Diagram...................................................................................................... 164

10.1.3 Pin Configuration ................................................................................................. 165

10.1.4 Register Configuration ......................................................................................... 166

10.1.5 Address Map......................................................................................................... 167

10.2 Description of Registers..................................................................................................... 169

10.2.1 Bus Control Register 1 (BCR1)............................................................................ 169

10.2.2 Bus Control Register 2 (BCR2)............................................................................ 172

10.2.3 Wait Control Register 1 (WCR1)......................................................................... 175

10.2.4 Wait Control Register 2 (WCR2)......................................................................... 177

10.2.5 DRAM Area Control Register (DCR) .................................................................. 178

10.2.6 Refresh Timer Control/Status Register (RTCSR) ................................................ 181

10.2.7 Refresh Timer Counter (RTCNT) ........................................................................ 183

10.2.8 Refresh Time Constant Register (RTCOR).......................................................... 184

10.3 Accessing Ordinary Space................................................................................................. 185

10.3.1 Basic Timing......................................................................................................... 185

10.3.2 Wait State Control ................................................................................................ 186

10.3.3 CS Assert Period Extension.................................................................................. 188

10.4 DRAM Access................................................................................................................... 189

10.4.1 DRAM Direct Connection.................................................................................... 189

10.4.2 Basic Timing......................................................................................................... 190

10.4.3 Wait State Control ................................................................................................ 191

10.4.4 Burst Operation..................................................................................................... 195

10.4.5 Refresh Timing..................................................................................................... 197

10.5 Address/Data Multiplex I/O Space Access........................................................................ 199

10.5.1 Basic Timing......................................................................................................... 199

10.5.2 Wait State Control ................................................................................................ 200

10.5.3 CS Assertion Extension ........................................................................................ 201

10.6 Waits between Access Cycles........................................................................................... 201

10.6.1 Prevention of Data Bus Conflicts......................................................................... 201

10.6.2 Simplification of Bus Cycle Start Detection ........................................................ 203

10.7 Bus Arbitration................................................................................................................... 203

10.8 Memory Connection Examples......................................................................................... 205

10.9 On-Chip Peripheral I/O Register Access........................................................................... 210

10.10 CPU Operation when Program is in External Memory..................................................... 211

Section 11 Direct Memory Access Controller (DMAC).......................................... 213

11.1 Overview............................................................................................................................ 213

11.1.1 Features................................................................................................................. 213

v

Page 28

11.1.2 Block Diagram...................................................................................................... 215

11.1.3 Pin Configuration ................................................................................................. 216

11.1.4 Register Configuration ......................................................................................... 217

11.2 Register Descriptions......................................................................................................... 218

11.2.1 DMA Source Address Registers 0–3 (SAR0–SAR3)........................................... 218

11.2.2 DMA Destination Address Registers 0–3 (DAR0–DAR3).................................. 219

11.2.3 DMA Transfer Count Registers 0–3 (DMATCR0–DMATCR3)......................... 220

11.2.4 DMA Channel Control Registers 0–3 (CHCR0–CHCR3)................................... 221

11.2.5 DMAC Operation Register (DMAOR) ................................................................ 226

11.3 Operation........................................................................................................................... 228

11.3.1 DMA Transfer Flow............................................................................................. 228

11.3.2 DMA Transfer Requests....................................................................................... 230

11.3.3 Channel Priority.................................................................................................... 232

11.3.4 DMA Transfer Types ........................................................................................... 235

11.3.5 Address Modes ..................................................................................................... 235

11.3.6 Dual Address Mode .............................................................................................. 237

11.3.7 Bus Modes ............................................................................................................ 244

11.3.8 Relationship between Request Modes and Bus Modes by DMA Transfer

Category ............................................................................................................... 245

11.3.9 Bus Mode and Channel Priority Order................................................................. 246

11.3.10 Number of Bus Cycle States and DREQ Pin Sample Timing.............................. 246

11.3.11 Source Address Reload Function ......................................................................... 263

11.3.12 DMA Transfer Ending Conditions ....................................................................... 264

11.3.13 DMAC Access from CPU .................................................................................... 265

11.4 Examples of Use................................................................................................................ 265

11.4.1 Example of DMA Transfer between On-Chip SCI and External Memory .......... 265

11.4.2 Example of DMA Transfer between External RAM and External Device

with DACK........................................................................................................... 266

11.4.3 Example of DMA Transfer between A/D Converter and On-Chip Memory

(Address Reload On) (Excluding A Mask) .......................................................... 266

11.4.4 Example of DMA Transfer between A/D Converter and Internal Memory

(Address Reload On) (A Mask)............................................................................ 268

11.4.5 Example of DMA Transfer between External Memory and SCI1 Send Side

(Indirect Address On)........................................................................................... 270

11.5 Cautions on Use................................................................................................................. 272

Section 12 Multifunction Timer Pulse Unit (MTU) .................................................. 273

12.1 Overview............................................................................................................................ 273

12.1.1 Features................................................................................................................. 273

12.1.2 Block Diagram...................................................................................................... 276

12.1.3 Pin Configuration ................................................................................................. 278

12.1.4 Register Configuration ......................................................................................... 280

12.2 MTU Register Descriptions............................................................................................... 283

vi

Page 29

12.2.1 Timer Control Register (TCR) ............................................................................. 283

12.2.2 Timer Mode Register (TMDR)............................................................................. 288

12.2.3 Timer I/O Control Register (TIOR) ..................................................................... 290

12.2.4 Timer Interrupt Enable Register (TIER)............................................................... 306

12.2.5 Timer Status Register (TSR) ................................................................................ 309

12.2.6 Timer Counters (TCNT)....................................................................................... 312

12.2.7 Timer General Register (TGR)............................................................................. 313

12.2.8 Timer Start Register (TSTR) ................................................................................ 313

12.2.9 Timer Synchro Register (TSYR).......................................................................... 314

12.2.10 Timer Output Master Enable Register (TOER).................................................... 315

12.2.11 Timer Output Control Register (TOCR)............................................................... 317

12.2.12 Timer Gate Control Register (TGCR) .................................................................. 318

12.2.13 Timer Subcounter (TCNTS)................................................................................. 320

12.2.14 Timer Dead Time Data Register (TDDR) ............................................................ 321

12.2.15 Timer Period Data Register (TCDR).................................................................... 321

12.2.16 Timer Period Buffer Register (TCBR)................................................................. 322

12.3 Bus Master Interface.......................................................................................................... 322

12.3.1 16-Bit Registers .................................................................................................... 322

12.3.2 8-Bit Registers ...................................................................................................... 323

12.4 Operation........................................................................................................................... 324

12.4.1 Overview............................................................................................................... 324

12.4.2 Basic Functions..................................................................................................... 325

12.4.3 Synchronous Operation ........................................................................................ 330

12.4.4 Buffer Operation................................................................................................... 333

12.4.5 Cascade Connection Mode................................................................................... 336

12.4.6 PWM Mode .......................................................................................................... 337

12.4.7 Phase Counting Mode........................................................................................... 341

12.4.8 Reset-Synchronized PWM Mode......................................................................... 348

12.4.9 Complementary PWM Mode ............................................................................... 352

12.5 Interrupts............................................................................................................................ 377

12.5.1 Interrupt Sources and Priority Ranking ................................................................ 377

12.5.2 DTC/DMAC Activation ....................................................................................... 379

12.5.3 A/D Converter Activation..................................................................................... 379

12.6 Operation Timing............................................................................................................... 380

12.6.1 Input/Output Timing............................................................................................. 380

12.6.2 Interrupt Signal Timing ........................................................................................ 385

12.7 Notes and Precautions........................................................................................................ 389

12.7.1 Input Clock Limitations........................................................................................ 389

12.7.2 Note on Cycle Setting........................................................................................... 389

12.7.3 Contention between TCNT Write and Clear ........................................................ 390

12.7.4 Contention between TCNT Write and Increment................................................. 391

12.7.5 Contention between Buffer Register Write and Compare Match......................... 392

12.7.6 Contention between TGR Read and Input Capture .............................................. 394

vii

Page 30

12.7.7 Contention between TGR Write and Input Capture............................................. 395

12.7.8 Contention between Buffer Register Write and Input Capture ............................ 396

12.7.9 Contention between TGR Write and Compare Match ......................................... 397

12.7.10 TCNT2 Write and Overflow/Underflow Contention in Cascade Connection ..... 397

12.7.11 Counter Value during Complementary PWM Mode Stop ................................... 399

12.7.12 Buffer Operation Setting in Complementary PWM Mode................................... 399

12.7.13 Reset Sync PWM Mode Buffer Operation and Compare Match Flag ................. 400

12.7.14 Overflow Flags in Reset Sync PWM Mode ......................................................... 402

12.7.15 Notes on Compare Match Flags in Complementary PWM Mode ....................... 405

12.7.16 Contention between Overflow/Underflow and Counter Clearing........................ 407

12.7.17 Contention between TCNT Write and Overflow/Underflow............................... 408

12.7.18 Cautions on Transition from Normal Operation or PWM Mode 1

to Reset-Synchronous PWM Mode...................................................................... 409

12.7.19 Output Level in Complementary PWM Mode and Reset-Synchronous PWM

Mode..................................................................................................................... 409

12.7.20 Cautions on Using the Chopping Function in Complementary PWM Mode

or Reset Synchronous PWM Mode (A Mask Excluded)...................................... 409

12.7.21 Cautions on Carrying Out Buffer Operation of Channel 0 in PWM Mode

(A Mask Excluded)............................................................................................... 409

12.7.22 Cautions on Restarting with Sync Clear of Another Channel

in Complementary PWM Mode (A Mask Excluded)........................................... 410

12.8 MTU Output Pin Initialization........................................................................................... 411

12.8.1 Operating Modes .................................................................................................. 411

12.8.2 Reset Start Operation............................................................................................ 411

12.8.3 Operation in Case of Re-Setting Due to Error During Operation, Etc. ................ 412

12.8.4 Overview of Initialization Procedures and Mode Transitions in Case of Error

during Operation, Etc............................................................................................ 412

12.9 Port Output Enable (POE)................................................................................................. 443

12.9.1 Features................................................................................................................. 443

12.9.2 Block Diagram...................................................................................................... 444

12.9.3 Pin Configuration ................................................................................................. 445

12.9.4 Register Configuration.......................................................................................... 445