Page 1

Renesas Electronics

R-IN32M3 Series

edition

・

・

User's Manual

User’s Manual: Board design

R-IN32M3-EC

R-IN32M3-CL

All information contained in these materials, including products and product specifications, represents

information on the product at the time of publication and is subject to change by Renesas Electronics

Corp. without notice. Please review the latest information published by Renesas Electronics Corp.

through various means, including the Renesas Electronics Corp. website (http://www.renesas.com)

Document number: R18UZ0021EJ0400

Issue date: Dec. 28, 2018

www.renesas.com

Page 2

Notice

1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the

operation of semiconductor products and application examples. You are fully responsible for the incorporation of these

circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for

any losses incurred by you or third parties arising from the use of these circuits, software, or information.

2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas

Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever

for any damages incurred by you resulting from errors in or omissions from the information included herein.

3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property

rights of third parties by or arising from the use of Renesas Electronics products or technical information described in

this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other

intellectual property rights of Renesas Electronics or others.

4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or

in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such

alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High

Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade,

as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio

and visual equipment; home electronic appliances; machine tools; personal electronic equipment;

and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster

systems; anti-crime systems; and safety equipment et c.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a

direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may

cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality

grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas

Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable

for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for

which the product is not intended by Renesas Electro ni cs.

6. You should use the Renesas Electronics products described in this document within the range specified by Renesas

Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage

range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no

liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified

ranges.

7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products

have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use

conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to

implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by

fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software

including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging

degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very

difficult, please evaluate the safety of the final products or systems manufactured by you.

8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental

compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all

applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation,

the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your

noncompliance with applicable laws and regulations.

9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems

whose manufacture, use, or sale is prohibited under any applicable domestic or fore ign la ws or regulations. You

should not use Renesas Electronics products or technology described in this document for any purpose relating to

military applications or use by the military, including but not limited to the development of weapons of mass destruction.

When exporting the Renesas Electronics products or technology described in this document, you should comply with

the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or

otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set

forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as

a result of unauthorized use of Renesas Electronics products.

11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of

Renesas Electronics.

12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this

document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its

majority-owned subsidiaries.

(Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

Page 3

Arm® and Cortex® are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere.

belongs to the respective owners.

Instructions for the use o f product

In this section, the precautions are described for over whole of CMOS device.

Please refer to this manual about individual precaution.

When there i s a mention unlike the text of this manual, a mention of the text takes first priority.

1.Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation w ith an unused pin in

the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, associated shoot-through

current flows internally, and malfun cti ons occur due to the false recognition of the pin state as an input signal

become possible. Unused pins should be h and led as descr i b ed under Ha ndl ing of Unu sed Pins in the manu al.

2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register sett in gs and pins are

undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not

guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not

guaranteed from the moment when power is supplied until the power reaches the level at which resetting has

been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do not access these

addresses; the correct operation of LSI is not guaranteed if they are accessed.

4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When

switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset,

ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to

a clock signal produced with an external resonator (or by an external oscillator) while program execution is in

progress, wait until the target clock signal is stable.

・

All rights reserved.

・Ethernet is a registered trademark of Fuji Xerox Co., Ltd.

・IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers Inc.

・TRON is an acronym for "The Real-time Operation system Nucleus".

・ITRON is an acronym for "Industrial TRON".

・µITRON is an acronym for "Micro Industrial TRON".

・TRON, ITRON, and µITRON do not refer to any specific product or products.

・EtherCAT

GmbH, Germany.

・CC-Link and CC-Link IE Field are registered trademarks of the CC-Link Partner Association (CLPA).

Additionally all product names and service names in this document are a trademark or a registered trademark which

・

®

and TwinCAT® are registered trademark and patented technology, licensed by Beckhoff Automation

Page 4

Particular attention should be paid to the precautionary notes when using the manual. These notes occur

within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer

point in this document.

refer to it.

Document Name

Document Number

R-IN32M3 Series Datasheet

R18DS0008EJ****

R-IN32M3 Series User’s Manual R-IN32M3-EC

R18UZ0003EJ****

R-IN32M3 Series User’s Manual R-IN32M3-CL

R18UZ0005EJ****

R-IN32M3 Series User’s Manual: Peripheral Modules

R18UZ0007EJ****

R-IN32M3 Series Programming Manual: Driver

R18UZ0009EJ****

R-IN32M3 Series Programming Manual: OS

R18UZ0011EJ****

R-IN32M3 Series User’s Manual Peripheral: Board design edition

This manual

How to use this manual

1. Purpose and Target Readers

This manual is intended for users who wish to understand the functions of Industrial Ethernet network LSI

"R-IN32M3-EC/CL" for designing application of it. It is assumed that the reader of this manual has general knowledge in

the fields of electrical engineering, logic circuits, and microcontrollers.

to the text of the manual for details.

The mark "<R>" means the updated point in this revision. The mark "<R>" let users search for the updated

Related

Documents

The related documents indicated in this public ation may include preliminary versions. However,

preliminary versions a re not marked as such. Please be understanding of this beforehand. In addition,

because we make document at development, planning of each core, the related document may be the

document for individual customers. Last four digits of document number (described as ****) indicate

version information of each document. Please download the latest document from our web site and

The document related to R-IN32M3 Series

Page 5

2. Not at ion of Numbers and Symbols

Weight in data notation: Left is high-order column, right is low-order column

Active low notation:

xxxZ (capital letter Z after pin name or signal name)

or xxx_N (capital letter _N after pin name or signal name)

or xxnx (pin name or signa l name contains small letter n)

Note:

explanation of (Note) in the text

Caution:

Item deserving extra attention

Remark:

Supplementary explanation to the text

Numeric notation:

Binary: xxxx , xxxxB or n’bxxxx (n bits)

Decimal: xxxx

Hexadecimal: xxxxH or n’hxxxx (n bits)

Prefixes representing powers of 2 (address space, memory capacity):

K (kilo): 2

M (mega): 2

G (giga): 2

Data Type:

Word: 32 bits

Halfword: 16 bits

Byte: 8 bits

10

= 1024

20

= 10242

30

= 10243

Page 6

Contents

1. Outline ........................................................................................................................................................... 1

1.1 Definitio n of Pin Hand ling and Symbols in This Manual ................................................................................... 1

2. Power/Reset Pins .......................................................................................................................................... 2

2.1 Power-O n/O ff Se q ue nc e ..................................................................................................................................... 2

2.2 Power Supply Pins .............................................................................................................................................. 3

2.3 Reset Pins ........................................................................................................................................................... 4

3. Clock Input Pins ............................................................................................................................................. 5

3.1 Features of Pins ................................................................................................................................................... 5

3.2 Notes on Configuring the Oscillation Circuit ..................................................................................................... 6

3.3 Oscillation Circuit Configurati on Example ........................................................................................................ 7

4. PLL Power Pins ............................................................................................................................................. 8

4.1 Recommended Configuration of Filter ............................................................................................................... 8

4.2 Notes on Placement of Peripheral Components .................................................................................................. 9

5. Built-in Regulator Pin (R-IN32M3-EC only) ................................................................................................. 10

5.1 Built-in Regulator Used .................................................................................................................................... 10

5.2 Built-in Regulator Unused ................................................................................................................................ 12

6. GPIO Port Pins ............................................................................................................................................ 13

7. Ethernet PHY Pins (R-IN32M3-EC Only) .................................................................................................... 14

7.1 Ethernet PH Y Power Supply Pins ..................................................................................................................... 14

7.2 100Base-TX Pins .............................................................................................................................................. 15

7.3 100Base-FX Pins (Optical Fiber)...................................................................................................................... 19

8. GMII Pins (R-IN32M3-CL Only) ................................................................................................................... 20

8.1 Selection of GMII Peripheral Components ....................................................................................................... 21

8.2 Circuit Design around GMII ............................................................................................................................. 21

8.3 Pattern Design around GMII ............................................................................................................................. 21

Contents-1

Page 7

9. CC-Link Pins ................................................................................................................................................ 22

10. Notes of CC-Link IE Field Use (Only R-IN32M3-CL) .................................................................................. 24

11. External MCU/Memory Interface Pins ......................................................................................................... 25

11.1 External MCU Interface .................................................................................................................................... 26

11.1.1 Asynchronous SRAM Interface Mode ..................................................................................................... 27

11.1.2 Synchronous SRAM Interface Mode ....................................................................................................... 29

11.1.3 Synchronous SRAM-Type Transfer Mode .............................................................................................. 30

11.2 External Memory Interface ............................................................................................................................... 31

11.2.1 Asynchronous SRAM MEMC ................................................................................................................. 31

11.2.2 Synchronous Burst Access MEM C ......................................................................................................... 34

12. Serial Flash ROM Connection Pins ............................................................................................................. 37

13. As ynchro nous Ser i al Interf ac e J Connec ti on Pins ...................................................................................... 38

14. I2C Connection Pins..................................................................................................................................... 39

15. EtherCAT EEPROM I2C Connection Pins (R-IN32M3-EC Only) ................................................................ 40

16. CAN Pi ns ..................................................................................................................................................... 41

17. CSIH Pins <R> ............................................................................................................................................ 42

17.1 One Master and One Slave ............................................................................................................................... 42

17.2 One Master and Two Slaves ............................................................................................................................. 42

18. JTAG/Trace Pins ......................................................................................................................................... 43

19. Implementation Conditions .......................................................................................................................... 46

20. Package Information .................................................................................................................................... 47

21. Mount Pad Information ................................................................................................................................ 48

22. BSCAN Information ..................................................................................................................................... 49

22.1 BSCAN Operating Conditions .......................................................................................................................... 49

22.2 Maximum Operating Frequency of TCK .......................................................................................................... 49

22.3 IDCODE ........................................................................................................................................................... 49

22.4 BSCAN Non-Supported Pins ............................................................................................................................ 50

Contents-2

Page 8

22.5 How to Get BSDL ............................................................................................................................................ 51

22.6 Notes on Using BSDL <R> .............................................................................................................................. 51

23. IBIS Information ........................................................................................................................................... 52

24. Marking Information ..................................................................................................................................... 53

24.1 R-IN32M3-EC .................................................................................................................................................. 53

24.2 R-IN32M3-CL .................................................................................................................................................. 53

25. Thermal Design <R> ................................................................................................................................... 54

25.1 Deciding on whether Particular Measures for Heat Dissipation are Required .................................................. 54

25.1.1 Estimating Tj ........................................................................................................................................... 54

25.1.2 Estimating Power Consumptio n .............................................................................................................. 54

25.1.3 Thermal Resistances under the JEDEC Conditions (for θja and Ψjt) ...................................................... 55

25.1.4 Results of Estimating Power Consumption of the 1-V Sub-Systems at Tj .............................................. 55

25.1.5 Relation between Temperature Increases (∆t) and Thermal Resistance (θja) at a Given Ambient

Temperature ............................................................................................................................................. 57

25.2 Examples of Measures for Heat Dissipation ..................................................................................................... 58

25.2.1 Measures for Heat Release in Designing the Board ................................................................................. 59

25.2.2 Heat Dissipation from the Per iphery (Including the Casing) ................................................................... 61

25.3 Points for Caution ............................................................................................................................................. 62

25.3.1 Internal Regulator .................................................................................................................................... 62

25.3.2 Handling of Unused Pins ......................................................................................................................... 62

26. Countermeasure for Noise <R> .................................................................................................................. 64

26.1 Stopping Cl ock Output ..................................................................................................................................... 64

Contents-3

Page 9

List of Figures

Figure 1.1

Figure 2.1 Recommended Sequence of Power-On/Off .......................................................................................... 2

Figure 3.1 Example of GND Pat tern for the Components for External Constants ................................................. 6

Figure 3.2 Configuration Example of the Oscillation Circuit ................................................................................ 7

Figure 4.1 Recommended Configuration of Filter ................................................................................................. 8

Figure 4.2 Schematic View from Below the Board ................................................................................................ 9

Figure 5.1 Wiring Example of the Regulator Unit (Built-in Regulator Used) ..................................................... 10

Figure 5.2 Layout Example of the Regulator Section .......................................................................................... 11

Figure 5.3 Wiring Exa mple of the Regulator Unit (Internal Regulator is Not Used) ........................................... 12

Figure 7.1 Decoupling Capacitors for Power Supply ........................................................................................... 14

Figure 7.2 Connection Example of R-IN32M3-EC and RJ-45 Connector (Pulse Transformer Incorporated) ..... 15

Figure 7.3 Connection Example of R-IN32M3-EC, Pulse Transformer, and RJ-45 Connector........................... 16

Figure 7.4 Wiring Example of the Differential Signal Trans mission Line (1) ..................................................... 17

Figure 7.5 Wiring Example of the Differential Signal Transmissio n Line (2) ..................................................... 18

Figure 7.6 Wiring Example of the Differential Signal Trans mission Line (3) ..................................................... 18

Figure 7.7 Interface Circuit with Optica l Transceiver .......................................................................................... 19

Figure 8.1 Connection Image of R-IN32M3-CL and Gigabit Ethernet PHY ....................................................... 20

Figure 9.1 Connection Example for CC-Link Remote Device Station ................................................................ 23

Figure 11.1 Connection Example of 32-Bit External MCU Interface (Asynchronous SRAM Interface Mode) .... 27

Figure 11.2 Connection Example of 16-Bit External MCU Interface (Asynchronous SRAM Interface Mode) .... 27

Figure 11.3 Connection Example of 32-Bit External MCU Interface (Synchronous SRAM Interface Mode) ...... 29

Figure 11.4 Connection Example of 16-Bit External MCU Interface (Synchronous SRAM Interface Mode) ...... 29

Figure 11.5 Connection Example of 32-Bit External MCU Interface (Synchronous SRAM-Type Transfer

Figure 11.6 Connection Example of 16-Bit External MCU Interface (Synchronous SRAM-Type Transfer

Figure 11.7 Connection Example with 32-Bit SRAM (Asynchronous SRAM MEMC) ........................................ 32

Figure 11.8 Connection Example with 16-Bit SRAM (Asynchronous SRAM MEMC) ........................................ 32

Figure 11.9 Connection Example with 32-Bit Paged ROM (Asynchronous SRAM MEMC) ............................... 33

Figure 11.10 Connection Example with 16-Bit Paged ROM (Asynchronous SRAM MEMC) .............................. 33

Figure 11.11 Connection Example with 32-Bit SRAM (Synchronous Burst Access MEMC) ............................... 35

Figure 11.12 Connection Example with 16-Bit SRAM (Synchronous Burst Access MEMC) ............................... 35

Figure 11.13 Connection Example with 32-Bit Paged RO M (Synchronous Burst Acc ess MEMC) ....................... 36

Figure 11.14 Connection Example with 16-Bit Paged ROM (Synchronous Burst Access MEMC) ....................... 36

Figure 12.1 Connection Example with Serial Flash ROM <R> ............................................................................. 37

Figure 13.1 Connection Example between R-IN32M3 and UART Device ........................................................... 38

Figure 14.1 Connection Example between R-IN32M3 and I2C Slave Device ....................................................... 39

Figure 15.1 Connection Example between R-IN32M3-EC and EtherCAT EEPROM .......................................... 40

Figure 16.1 Connection Example between R-IN32M3 and CAN Transceiver ...................................................... 41

Figure 17.1 Direct Master/Slave Connection ......................................................................................................... 42

Definition of GND Symbols ................................................................................................................. 1

Mode) .................................................................................................................................................. 30

Mode) ................................................................................................................................................. 30

Contents-4

Page 10

Figure 17.2 Connection between One Master and Two Slaves .............................................................................. 42

Figure 18.1 Connection Example of JTAG Interface (20-Pin Half-Pitch without Trace) ...................................... 43

Figure 18.2 Connection Example of JTAG Interface (20-Pin Half-Pitch with T race) ........................................... 44

Figure 18.3 Connection Example of JTAG Interface (20-Pin Full-Pitch) .............................................................. 45

Figure 19.1 Implementation Flow .......................................................................................................................... 46

Figure 19.2 Infrared Reflow Temperature Profile .................................................................................................. 46

Figure 20.1 Package Information ........................................................................................................................... 47

Figure 21.1 Mount Pad Sizes ................................................................................................................................. 48

Figure 24.1 R-IN32M3-EC Marking Info rmation .................................................................................................. 53

Figure 24.2 R-IN32M3-CL Marking Info rmation .................................................................................................. 53

Contents-5

Page 11

List of Tables

Table 1.1

Table 5.1 List of Recommended Parts for Use ....................................................................................................... 11

Table 7.1 Parts List (100Base-TX interface) .......................................................................................................... 16

Table 7.2 Part List (100Base-FX Interface) ............................................................................................................ 19

Table 11.1 Mode Selection of External MCU/Memory Connection..................................................................... 25

Table 22.1 List of BSCAN No n-Supported Pins<R> ........................................................................................... 50

Definition of Pin Handling ........................................................................................................................ 1

Contents-6

Page 12

Description

Low level

This pin is connected to GND.

High level

This pin supplies VDD33 (3.3 V).

Frame GNDAnalog GND

GND

R18UZ0021EJ0400

R-IN32M3 Series: Board design edition Dec. 28, 2018

1. Outline

This manual is intended for being us ed by engi neers that work on a circuit and P C B design that is equipp ed with an

Ethernet communication LSI from the R-IN32M3 series made by Renesas Electronics. Target devices are the

R-IN32M3-EC and R-IN32M3-CL devices.

It is recommended to st udy this manual caref ully and to fo l low the recommendati ons during the circui t and boa rd design.

1.1 Definition o f Pin Handling and Symbols in This Manual

Pin handling and symbols are defined as follows in this manual.

Table 1.1 Definition of Pin Handling

Figure 1.1 Definition of GND Symbols

R18UZ0021EJ0400 Page 1 of 64

Dec. 28, 2018

Page 13

R-IN32M3 Series: Board design edition 2. Power/Reset Pins

I/O voltage

(VDD33)

100ms

0.1 VDD10

GND

Internal voltage

(VDD10)

100ms

0.1 VDD10

0.9 VDD33

PHY voltage

Note

(VDD15)

.

The timing for PHY power supply voltage VDD15 only needs to be observed, when the internal

regulator in the R-IN32M3-EC device is not used.

2. Power/Reset Pins

2.1 Power-On/Off Sequence

Power structure of the R-IN32M3 series is internal power (VDD10: 1.0V) and I/O power (VDD33: 3.3V) and PHY

power supply (VDD15: 1.5V). (PHY power is subject only R-IN32M3-EC.)

Power is recommended to put the I/O p ower after switching on the internal power supply. In addition, power-off is

recommend internal power-off after cut-off of I/O power (see section 2.1, Power-On/Off Sequence).

In the case of supplying internal power after I/O power, note that I/O value becomes indefinite due to uncertain mode

while I/O is powered on but internal power isn’t, whether it is in input mode or output mode. Also, 3.3 V must be applied

to the I/O pins only after applying the power supply voltages.

Power on/off time difference, that regardless of the power-on sequence, it does not matter which power supply is applied

to (or removed from) the device first, but it is recommended to ensure 100ms or less time difference between the

application or removal of each power supply. The 100ms or less time measurement is based on the period from 10% to

90% of each voltage range.

Figure 2.1 Recommended Seq uence of Power-On/Off

Note

R18UZ0021EJ0400 Page 2 of 64

Dec. 28, 2018

Page 14

R-IN32M3 Series: Board design edition 2. Power/Reset Pins

Terminal Name

Feature

Connection Example

PLL_VDD

PLL voltage (VDD) (1.0 V)

See section 4, PLL Power Pins.

PLL_GND

PLL GND potential (GND)

See section 4, PLL Power Pins.

such as a regulator or DC-DC converter.

such as a regulator or DC-DC converter.

GND

GND potential (GND)

Connect GND of system board.

such as a regulator or DC-DC converter.

LX

Built-in regulator 1.5 V output

(3.3 V)

(GND)

BVDD

Power supply for built-in regulator (3.3 V)

BGND

GND potential for built-in regulator (GND)

FB

Feedback input for built-in regulator

PHY

for Rx/Tx pin (1.5 V) - Port 0

Ethernet PHY Power Supply

for Rx/Tx pin (1.5 V) - Port 1

VDDACB

Analog power supply for Ethernet PHY (3.3 V)

AGND

Analog GND potential for PHY (3.3 V)

VDD15

Core voltage for Ethernet PHY (1.5 V)

VDDAPLL

Analog power supply for Ethernet PHY (1.5 V)

(GND)

(3.3 V)

VDDQ_PECL_B0

PECL buffer power supply (3.3 V)

VDDQ_PECL_B1

PECL buffer power supply (3.3 V)

Notes 1.

R-IN32M3-EC only

2.

R-IN32M3-CL only

2.2 Power Supply Pins

This is a list of power supply pins of the R-IN32M3.

Connect thes e pins according to t he descript ion given in the "Connection Example" column.

VDD33 I/O voltage (3.3 V) Supply a power supply from the power unit

VDD10 Internal voltage (1.0 V) Supply a power supply from the power unit

VDDQ_MII

Note1

AVDD_REG

AGND_REG

Note1

EXTRES

Note2

Note1

Note1

Note1

Note1

Note1

Reference resistance joining pin for Ethernet

P0VDDARXTX

P1VDDARXTX

Note1

Note1

Note1

Note1

VSSAPLLCB

Note1

Ethernet I/O voltage (3.3 V) Supply a power supply from the power unit

See section 5.1, Built-in Regulator Used.

Analog power supply for built-in regulator

Analog GND potential for built-in regulator

Connect to AGND through 12.4kΩ±1%.

Note1

Analog power supply

See section 7.1,

Pins.

Note1

Analog power supply

Analog GND potential for Ethernet PHY

VDD33ESD

Note1

Analog test power supply for Ethernet PHY

Note1

Note1

R18UZ0021EJ0400 Page 3 of 64

Dec. 28, 2018

Page 15

R-IN32M3 Series: Board design edition 2. Power/Reset Pins

Pin Name

Feature

Connection Example

RESETZ

Reset input

-

HOTRESETZ

Hot reset input

-

PONRZ

Power-on reset input for built in RAM

-

TRSTZ

JTAG reset signal

See section 16, CAN Pins.

RSTOUTZ

External reset output

-

Note.

R-IN32M3-CL only

2.3 Reset Pins

This is a list of rese t pins of R-IN32M3.

As a width at low level of at least 100 ms is required for the reset input signals, secure this by applying the low level of

the reset signal over the oscillation stabilization time of the external o scillator (25 MHz).

In addition, de-assert the RESETZ and HOTRESETZ signals after de-asserting the PONRZ signal.

Note

R18UZ0021EJ0400 Page 4 of 64

Dec. 28, 2018

Page 16

R-IN32M3 Series: Board design edition 3. Clock Input Pins

Pin Name

I/O

Features

・

・When external clock input mode is used (OSCTH = 1), set XT1 to the low level.

・

・

・

oscillator to XT2.

・

High level: XT2 is to be connected to an oscillator.

3. Clock Input Pins

3.1 Features of Pins

The following table shows the pin functions for clock supply to the device.

XT1 IN

XT2 IN/OUT

OSCTH IN

External resonator connection pin.

External resonator connection pins.

When "OSCTH = 0", this pin is the output.

When external clock input mode is used (OSCTH = 1), input the clock from an external

Selects the clock oscillation sour ce to be conne cted to t he clock pin.

Low level: XT1 and XT2 are to be connected to a resonator.

R18UZ0021EJ0400 Page 5 of 64

Dec. 28, 2018

Page 17

R-IN32M3 Series: Board design edition 3. Clock Input Pins

R-IN32M3

OSCTH

XT1 XT2

Board

GND pattern

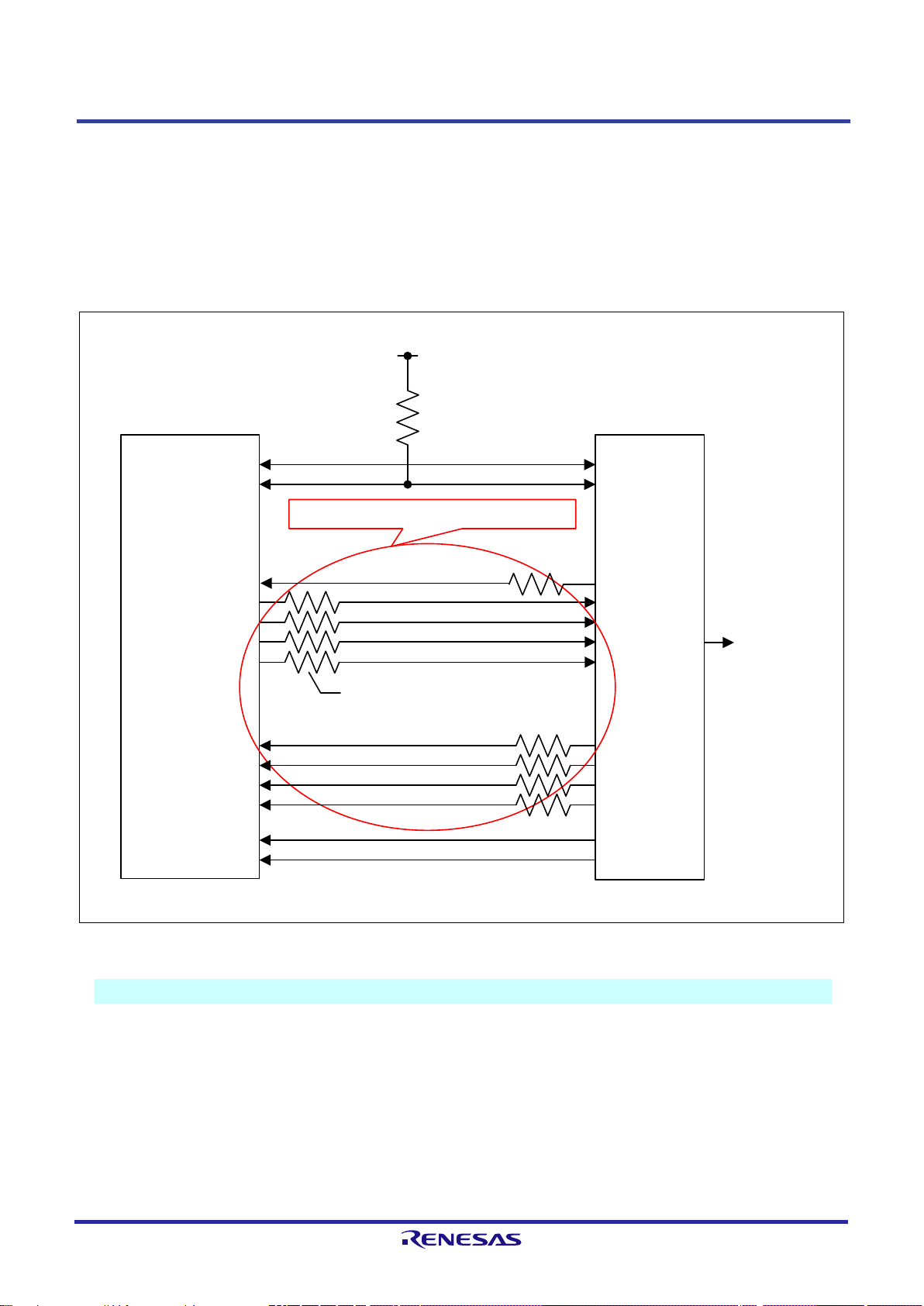

3.2 Notes on Configuring the Oscillation Circuit

As the R-IN32M3 series includes an oscillation block, oscillation circuits are easily configurable by externally

connecting a resonator and components for external constan ts. Though c onfiguring an oscill ation circuit is ea sy, the

configured circuit is analog and operates at a high frequency, so note s that differ for logic become applicable.

To achieve stable operation of the o scilla tion circuit, set components for external constants to the optimum values

(capacitors on the input and output sid e s, a nd limiting resistors) and observe the following points required for an analog

circuit.

・Place the oscillation circuit near the R-IN32M3.

・Place the oscillation circuit as far as p ossible from high-frequency inp ut pins such as clock pins.

・Place the resonators and compone nts fo r external constants immediately close to the input and output pins of oscillat ion

circuit, and keep the connections as sho rt as possible.

・Make the ground connections of the capacitors to the GND pin s of R-IN32M3 as short and thick as possible.

・Make the lead wires between the resonator and capacitors as short as possible.

・Surround the components for external constant parts by as much GND wiring as is possible.

Figure 3.1 Example of GND Pattern for the Components for External Cons ta nts

In addition, the following points to note should be observed in evaluating and deter mining the external constants.

・The range o f oscillating operati on may vary due to the diele c tr ic c onstant of the board’s material, so use the actual

printed circuit board that will be used in the finished desi gn.

・Check use of the board with the developed R-IN32M3 and the actual resonator to be mounted on it.

R18UZ0021EJ0400 Page 6 of 64

Dec. 28, 2018

Page 18

R-IN32M3 Series: Board design edition 3. Clock Input Pins

(1

)

Resonator input mode (

2

)

External clock input mode

OSCTH

XT1

XT2

Resonator

C

1

C

2

Rd

OSCTH

XT1

XT2

Though Rd is an element to suppress the

excitation current and negative resistance of the

resonator, it may not be required depending on

the resonator to be used.

In external clock input mode, drive

XT1 to the low level.

R-IN32M3 R-IN32M3

VDD33(3.3V)

.

The

When a resonator is to be used, contact the resonator manufacturer

corresponding part number and external c onstant

Renesas

•

•

3.3 Oscillation Circuit Configuration Example

The following figure shows typical examples of oscillation circuits.

Figure 3.2 Configuration Example of the Oscillation Circuit

Caution

R18UZ0021EJ0400 Page 7 of 64

Dec. 28, 2018

input of the R-IN32M3 is fixed to 25 MHz.

recommends the following oscillator and resonator manufacturers.

Nihon Dempa Kogyo Co., Ltd. (NDK)

URL: http://www.ndk.com/en/index.html

KYOCERA Crystal Device Corporation

URL: http://1 www.kyocera-crystal.jp/

and ask for a

s.

Page 19

R-IN32M3 Series: Board design edition 4. PLL Power Pins

C1

PLL

PLL_GND

PLL_VDD

R-IN32M3

VDD10(1.0V)

C2

C1: 0.1-µF ceramic capacitor

C2: ≥ 4.7-µF c apac itor

FB

FB

FB: Impedance: 600Ω@100 MHz / DC resistance component: 0.3Ω or below

Reference ferrite be ads: TDK MPZ2012S601A, MPZ1608S601A

.

Put C1

C2

the R-IN32M3 as C1.

4. PLL Power Pins

The PLL circuit is susceptible to no ise. To reduce the influence of noise, it is recommended to place filters in the power

supply pin of the PLL. Also if user avoid the interference noise of the PLL board and power supply, the usage of user

ferrite beads (FB).

4.1 Recommended Configuration of Filter

Figure 4.1 shows the recommended configuration of the filter for the PLL power supply pins.

Figure 4.1 Recommended Configuration of Filter

Caution

as close as possible to the PLL_VDD and PLL_GND pins.

placement is less critical and there is no problem even if it can't be arranged as close to

R18UZ0021EJ0400 Page 8 of 64

Dec. 28, 2018

Page 20

R-IN32M3 Series: Board design edition 4. PLL Power Pins

PLL_

GND

PLL_

VDD

C1

Pay part icu lar attent ion t o the effe cts of

noise fr om signal s with wiring running

parallel to these lines in this region.

C2

FB

GND

FB

Power supply

.

PLL_VDD and P

Longer

increase, more readily leading to effects.

4.2 Notes on Placement of Peripheral Components

The 0.1-µF ceramic capacitor (C1) should be placed immediately close to R-IN32M3 (in the immediate vicinity of t h e

pin).

Figure 4.2 is a schematic view from below the board.

In addition, the wiring pattern s for the electrolytic capacitor (C2) and ferrite beads running parallel to other signal lines

should be avoided.

Figure 4.2 Schematic View from Below the Board

Caution

wiring leads to stronger crosstalk because the LC components of the wiring

LL_GND lines should be as short and thick as possible in PCB wiring.

R18UZ0021EJ0400 Page 9 of 64

Dec. 28, 2018

Page 21

R-IN32M3 Series: Board design edition 5. Built-in Regulator Pin (R-IN32M3-E C only)

+

+

L1 (10 uH)

D1

C2

(22uF; Tantalum)

C1

(22uF;

Tantalum)

R-IN32M3-EC

BVDD

LX

BGND /

AGND_REG

FB

VDD15

Swit chi ng regulat or input

GND for switc hing regulato r

Regulator output 1.5 V

Feedback regulator

Supply 1.5 V input

VDD33 (3.3 V)

AVDD_REGSwit chi ng regulat or input

TEST1

TEST2

TEST3

C1

(22 uF,

Tantalum)

C1a

(22 uF,

Ceramic)

R

(100mΩ)

C2

(22 uF,

Tantalum)

C2a

(22 uF,

Ceramic)

5. Built-in Regulator Pin (R-IN32M3-EC only)

In the R-IN32M3-EC, supplying 1.5 V to the VDD15, VDDAPLL, and PxVDDARXTX (x = 0, 1) pins is required as an

internal power supply for Ethernet PHY.

Since the R-IN32M3-EC is equipped with a regulator, there is no need to generate power externally. When not using a

built-in regulator, see section 6.2, Built-in Regulator Un us ed and design.

5.1 Built-in Regulator Used

Make wiring and layout as follows at the time of the built-in regulator in use.

Figure 5.1 Wiring Example of the Regulator Unit (Built-in Regulator Used)

If tantalum capacitors are not available, it is possible to use a resistor and a ceramic capacitor for C1, and a ceramic

capacitor for C2.

R18UZ0021EJ0400 Page 10 of 64

Dec. 28, 2018

Page 22

R-IN32M3 Series: Board design edition 5. Built-in Regulator Pin (R-IN32M3-E C only)

R-IN32M3

BVDD

LX

BGND /

AGND_REG

AVDD_REG

FB

Swit chi ng regulat or input

GND fo r swi tch i n g

regulator

Regulator output 1.5V

Feedback regulator

+

+

L1: 10 uH

C1: 22uF (Tantalum)

D1

C2: 22 uF (Tantalum)

AVDD, BVDD pattern

LX patt ern

VOUT pattern

(Connection to VDD15 power plane)

GND patter n

Parts

Type

Characteristics

Recommend Ports

D1

Schottky diode

30 V, 1 A

STPS1L30UPBF (ST)

L1

Inductor

10 uH

VLC5028T (TDK)

ESR: 75 to 300 mΩ

C1a, C2a

Ceramic capacitor

22 uF±10%

GRM32ER71A226KE20L (Murata)

R

Resistor

100 mΩ±1%

MCR18EZHFLR100 (ROHM)

Figure 5.2 Layout Example of the Regulator Section

Table 5.1 List of Recommended Parts for Use

C1, C2 Tantalum capacitor 22 uF±20%

PSLB21A226M (NEC TOKIN)

R18UZ0021EJ0400 Page 11 of 64

Dec. 28, 2018

Page 23

R-IN32M3 Series: Board design edition 5. Built-in Regulator Pin (R-IN32M3-E C only)

Unused open

R-IN32M3-EC

BVDD

LX

BGND /

AGND_REG

FB

VDD15

Switching regulator input

GND for s witching

regulator

Regulator output 1.5 V

Feedback r egulator

Supply 1.5 V input

VDD33 (3.3 V)

VDD15 (1.5 V)

Note

AVDD_REG

Switching regulator input

VDD15

VDD15

TEST1

TEST2

TEST3

VDD33 (3.3 V)

Note.

Supply stable power supply.

5.2 Built-in Regulator Unused

When the built-in regula tor is not in use, ma ke wiring and layout as follows.

Figure 5.3 Wiring Example of the Regulator Unit (Internal Regulator is Not Used)

R18UZ0021EJ0400 Page 12 of 64

Dec. 28, 2018

Page 24

R-IN32M3 Series: Board design edition 6. GPIO Port Pins

6. GPIO Port Pins

GPIO is a general-purpose I/O port. As for the internal configuration, see the section in the fo llowing do cument.

R-IN32M3-EC: User’s Manual R-IN32M3-EC "2.3.6 Port Signals"

R-IN32M3-CL: User’s Manu al R-IN32M3-CL "2.5.6 P ort Signals"

R18UZ0021EJ0400 Page 13 of 64

Dec. 28, 2018

Page 25

R-IN32M3 Series: Board design edition 7. Ethernet PHY Pins (R-IN32M3-EC Only)

R-IN32M3

AGND

P0VDDARXTX

P1VDDARXTX

VDD33ESD

VSSAPLLCB

VDDAPLL

VDDACB

GND

VDD15 (1.5 V)

VDD33 (3.3 V)

Decoupling capacitors

0.1 µF and 22 µF

FB

Decoupling capacitors 10 nF and 22 nF

(as close to the pins as possible)

7. Ethernet PHY Pins (R-IN32M3-EC Only)

7.1 Ethernet PHY Power Supply Pins

As for analog power supply pins for the built-in Ethernet P HY of the R-IN32M3-EC, power separation by ferrite beads

(FB) and the configuration of filters as follows are recommended.

Figure 7.1 Decoupling Capacitors for Power Supply

R18UZ0021EJ0400 Page 14 of 64

Dec. 28, 2018

Page 26

R-IN32M3 Series: Board design edition 7. Ethernet PHY Pins (R-IN32M3-EC Only)

3.3 V

Note1

R-IN32M3-EC

RJ-45

(Pulse transformer incorporated)

CT_TD

Px_RX_P

Px_RX_N

RD+

RD-

CT-RD

Px_TX_N

TD+Px_TX_P

TD-

3.3 V

Note1

C4

C3

Shield

C1 C2

R1

R2 R3 R4

R5 R6

10 nF / 2 kV

Note2

Note2

Note2

Note2

Remark.

x = 0 or 1

Notes 1.

Same potential with VDDACB and VDD33ESD

2.

Same potential with AGND

7.2 100Base-TX Pins

This is an example of connection us ing the pulse transformer.

Figure 7.2 Connection Example of R-IN32M3-EC and RJ-45 Connector (Pulse Transformer Incorporated)

R18UZ0021EJ0400 Page 15 of 64

Dec. 28, 2018

Page 27

R-IN32M3 Series: Board design edition 7. Ethernet PHY Pins (R-IN32M3-EC Only)

No te 2 No te 2

3.3V

No te 1

R-IN32M3-EC

Px_RX_P

Px_RX_N

Px_TX_N

Px_TX_P

3.3V

No te 1

C4C3

C1

C2

R1 R2

R3 R4 R5 R6

Transformer

ShieldC5

R7

R9

R8

R10

RJ-45

1

2

3

4

5

6

7

8

10 nF / 2 kV

No te 2 No te 2

Remark.

x = 0 or 1

Notes 1.

Same potential with VDDACB and VDD33ESD

2.

Same potential with AGND

Part

Type

Characteristics

Recommended Components

R1, R2, R3, R4

Resistor

49.9Ω±1% 1/16W

-

R5, R6

Resistor

10Ω±1% 1/16W

-

R7, R8, R9, R10

Resistor

75Ω±1% 1/16W

-

C1

Capacitor

10 nF to 100 nF

-

C2

Capacitor

10 nF to 100 nF

-

C3

Capacitor

10 nF to 22 nF

-

C4

Capacitor

10 nF to 22 nF

-

C5

Capacitor

4.7 nF±10%

-

One channel

Pulse Electronics H1012NL, H1102NL

Two channels

Pulse Electronics H1270N+, HX1294

incorporated)

Note.

We recommend 1/8W when using in harsh environments, such as at high temperatur e.

Figure 7.3 Connection Example of R-IN32M3-EC, Pulse Transformer, and RJ-45 Connector

Table 7.1 Parts List (100Base-TX interface)

Note

Note

Pulse transformer

RJ-45 connector (Pulse transformer

Two channels Pulse Electronics JG0-0031NL

R18UZ0021EJ0400 Page 16 of 64

Dec. 28, 2018

Page 28

R-IN32M3 Series: Board design edition 7. Ethernet PHY Pins (R-IN32M3-EC Only)

impedance. (See Figure 7.6)

influence the impedance.

(c)

The diameter of the vias should be almost equal to the trace width. (See Figure 7.6)

The wiring o n the board, note the following.

• Long wires should be avoided. R-IN32M3 and, the transformer, and the connector should be placed together as

close as possibl e.

• Crossing of differential traces with other lines and among ea ch other sho ul d be avoided. The component s should be

placed that way that crossing of differential pairs of TxP/N and RxP/N is not necessary.

• Differential lines should be routed straight and as short as possible.

• Lines should bend with 135 degree angle or more. (Figure 7.4)

• Traces between R-IN32M3-EC, transformer and RJ-45 connector should be designed with a differential impedance

of 100Ω±10% and with an impedance of 50Ω related to GND.

• The traces of a differential pair should match in length. 0.5mm is the maximum deviation. Adjustments of the length

should be done at the connector, device or transformer.

• Additional to the length the single traces should be designed symmetrical. They should be pa rallel and r outed in the

same layer with continuous width and a preferable fixed spacing. Components, vias and connections should also be

symmetrical.

• Stubs should be avoided.

• Preferable is a large edge gap at differential pairs. An empty space of five times of the trace width between

differential pair and other signals, planes or components is recommended.

• Differential lines should not cross edges of the GND/supply plane, other planes or voids in the layer below. For

continuous impedance a GND plane in the layer below is preferable.

• Beneath the magnetics no lines or planes should be rout ed.

• Preferable differential pairs sho uld be routed via as little vias as possible. If vias are necessary, note the following:

Vias of the related plane (e.g. AGND) should be placed near the signal vias. The distance between signal

(a)

via and GND via should be equal to the distance between the layers to avoid a discontinuity of the

(b) Void and no planes between and around the signal vias. Metal of planes close to the differential vias could

Figure 7.4 Wiring Example of the Differential Signal Transmission Line (1)

R18UZ0021EJ0400 Page 17 of 64

Dec. 28, 2018

Page 29

R-IN32M3 Series: Board design edition 7. Ethernet PHY Pins (R-IN32M3-EC Only)

g

g

w

w

s

wa

w

w

w

void

a

w

w

w

a

w

a

void

w

a

a

Figure 7.5 Wiring Example of the Differential Signal Transmission Line (2)

Figure 7.6 Wiring Example of the Differential Signal Transmission Line (3)

R18UZ0021EJ0400 Page 18 of 64

Dec. 28, 2018

Page 30

R-IN32M3 Series: Board design edition 7. Ethernet PHY Pins (R-IN32M3-EC Only)

AFBR-5978Z

QFBR-5978AZ

VDD33 (3.3 V)

R-IN32M3-EC

Optic al tra nsceiv er

Px_TD_OUT_N

Tdata+

Px_TD_OUT_P

SD

Tdata-

Rdata+Px_RD_P

Px_RD_N

Px_SD_P

Px_SD_N

Rdata-

Txdis

R1

R2

R3

R4 R5

R6 R7

R9R8

R10

Px_FX_EN_OUT

VDDQ_PECL_Bx

Remark.

x = 0 or 1

Part

Type

Characteristics

Recommended components

R1, R2

Resistor

150Ω±1%

-

R3, R4, R7

Resistor

130Ω±1%

-

R5, R6, R9

Resistor

82Ω±1%

-

R8

Resistor

86.6Ω±1%

-

R10

Resistor

127Ω±1%

-

AFBR-5978Z, QFBR-5978AZ

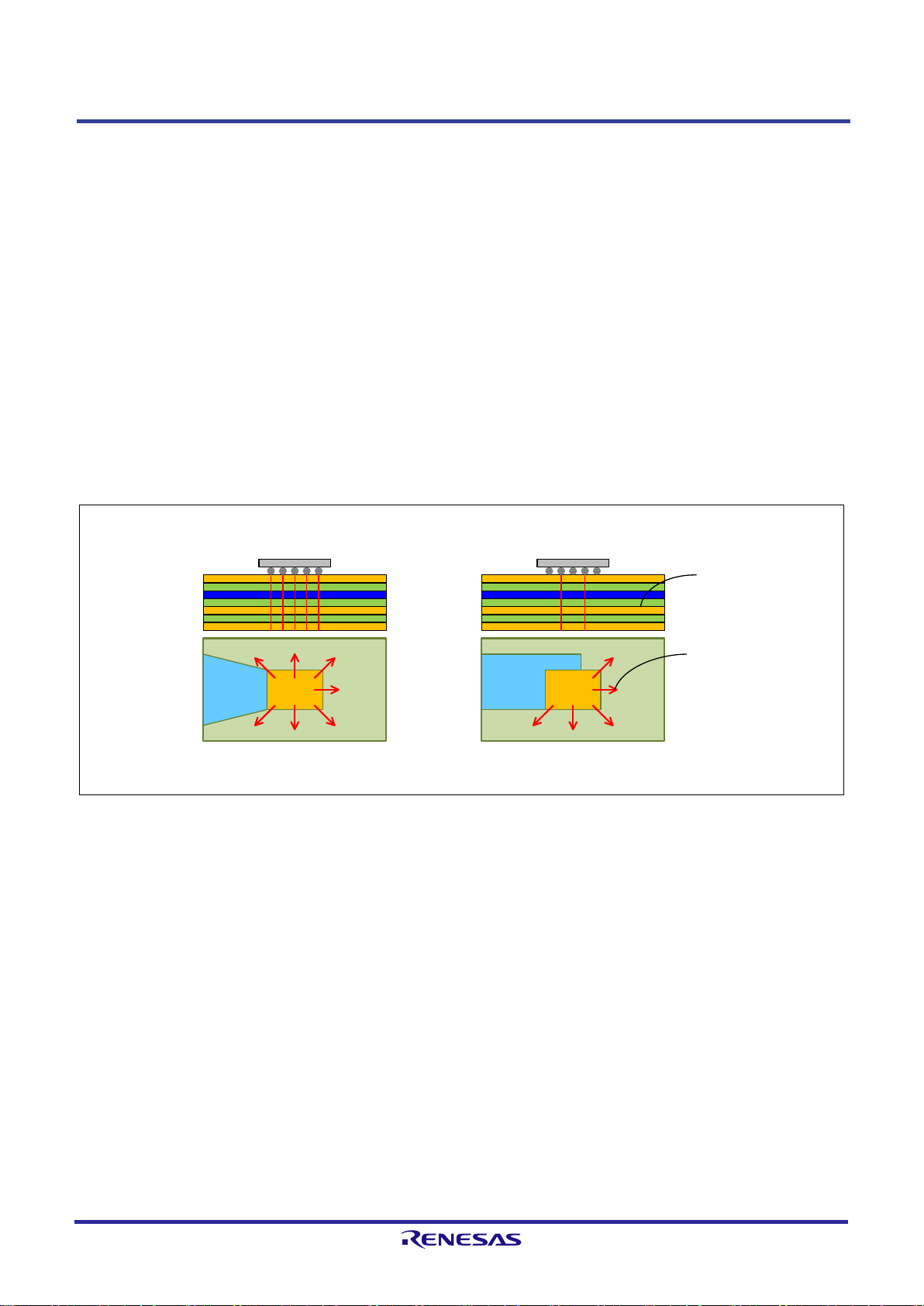

7.3 100Base-FX Pins (Optical Fiber)

An example of a connection with an optical fiber module is indicated belo w. As for the notes of the differential signal

transmission line, refer to "7.2 100Base-TX Pins".

Figure 7.7 Interface Circuit with Optical Transceiver

Table 7.2 Part List (100Base-FX Interface)

Optical transceiver One channel AvagoTechnologies

R18UZ0021EJ0400 Page 19 of 64

Dec. 28, 2018

Page 31

R-IN32M3 Series: Board design edition 8. GMII Pins (R-IN32M3-CL Only)

R-IN32M3-CL

ETHm_TXC

ETHm_GTXC

ETHm_TXDx

ETHm_TXEN

ETHm_TXER

RJ45

connector

Gigabit Ethernet PHY

TX_CLK

GTX_CLK

TXDx*

TX_EN

TX_ER

Dam ping res is tor: 33Ω±5%

RX_CLK

RXDx*

RX_DV

RX_ER

GND sh i e ld

GND sh i e ld

ETHm_RXC

ETHm_RXDx

ETHm_RXDV

ETHm_RXER

ETHm_COL

ETHm_CRS

ETH_MDC

ETH_MDIO

MDC

MDIO

COL

CRS

VDD33 (3.3 V)

Wires are recommended t o be short

and equal-length.

GND sh i e ld

4.7kΩ

Remark.

m = 0, 1, x = 0 to 7

8. GMII Pins (R-IN32M3-CL Only)

Figure 8.1 shows a connection image of R-IN32M3-CL and Gigabit Ethernet PHY.

The value of damping resistors should be 33Ω within a tolerance of 5%, and the damping resistors should be put in the

nearest point of the R-IN32M3-CL. In addition, wires of target pins (which is GTXC, TXDx, TXEN and TXER) are

recommended to be short and equal-length.

Figure 8.1 Connection Image of R-IN32M3-CL and Gigabit Ethernet PHY

R18UZ0021EJ0400 Page 20 of 64

Dec. 28, 2018

Page 32

R-IN32M3 Series: Board design edition 8. GMII Pins (R-IN32M3-CL Only)

8.1 Selection of GMII Peripheral Components

Select the parts with care to the following.

• Selection of PHY

Full-duplex products IEEE802.3 1000BASE-T.

Parts that have the auto-negotiation functi on.

Parts with a GMII interface.

Parts that have the auto MDI/MD I X negotiation function.

Operable parts at 125 MHz about MDC clock frequency.

• Selection of the crystal oscillator for PHY

Regarding Jitter and frequency, select the parts to adapt to the requirement of the PHY.

8.2 Circuit Design around GMII

Design the GMII peripheral circuits with care to the following.

• Wiring of GMII

Put the damping resistor of overshoot/undershoot protection.

• For PHY address

Set to the same address as the port number of the R-IN32M3-CL to the PH Y address.

Connect the PHY assigned to address 0 to MAC port 0, and connect the PHY assigned to addre s s 1 to MAC port 1.

8.3 Pattern Design around GMII

Design the pattern of GMII peripheral circuits with care to the fo l lowing.

• Wiring of GMII

The wiring pattern of the signal (GMII) to connect R-IN32M3-CL and PHY should be the shortest. Choose the

thickness of the wiring pattern and signal lines for the p a tte rn to be an impedance of 50Ω.

Do not bend at 45 degrees or less to signal pattern.

For the power/GND pattern, use t he wiring with a t hick pattern as much as possible.

R18UZ0021EJ0400 Page 21 of 64

Dec. 28, 2018

Page 33

R-IN32M3 Series: Board design edition 9. CC-Link Pins

CC-Link Partner Association (CLPA)

TEL: 052-919-1588

FAX: 052-916-8655

Email: info@cc-link.org

Web: https://www.cc-link.org/

9. CC-Link Pins

The connec t ion example for CC-Link Remote device statio n is shown i n Figure 9.1.

For notes on the implementation of the CC-Link, refer to CC-Link Sp ec ific ations: Implementation Spec ific ation

(BAP-05027) issued by the CC-Link Partner Association. Please contact the CC-Link Partner Association (CLPA) with

any requests for the corresponding material.

R18UZ0021EJ0400 Page 22 of 64

Dec. 28, 2018

Page 34

R-IN32M3 Series: Board design edition 9. CC-Link Pins

R-IN32M3

CCS_RD (P53)

CCS_SD (P54)

CCS_SDGATEON (P52)

2

3

5

4

SN75ALS181SN

13

14

5 V

47 k

47 k

680

680

4

5

6

MC177050-A401

3

2

1

10

9

11

12

6

7

8

1

DA

DB

DC

SLD

FG

3300 pF

50 V

HZU6.2ZTRF-E

CCS_STATION_NO_7 (P77)

CCS_STATION_NO_6 (P76)

CCS_STATION_NO_5 (P75)

CCS_STATION_NO_4 (P74)

CCS_STATION_NO_3 (P73)

CCS_STATION_NO_2 (P72)

CCS_STATION_NO_1 (P71)

CCS_STATION_NO_0 (P70)

8

4

2

1

8

4

2

1

CCS_BS_8 (RP05)

CCS_BS_4 (RP04)

CCS_BS_2 (RP03)

CCS_BS_1 (RP02)

8

4

2

1

STATION NO

X10

STATION NO

X1

B.RATE

CCS_ERRZ (P25)

CCS_RUNZ (P26)

CCS_LNKRUNZ (P50)

CCS_RDZ (P51)

CCS_SDZ (RP00)

VDD33 (3.3 V)

CCS_IOTENSU (P22)

CCS_SENYU1 (P24)

CCS_SENYU0 (P23)

CCS_REFSTB (P10)

Note1

CCS_WDTZ (P13)

CCM_CLK80M

Not e 3

CCS_MON3 (P34)

CCS_MON2 (P33)

CCS_MON1 (P32)

CCS_MON0 (P06)

CCS_MON7 (P05)

CCS_MON6 (P04)

CCS_MON5 (P03)

CCS_MON4 (P11)

CCS_RESOUT (P07)

CCS_FUSEZ (P36)

8

4

2

1

123

4

876

5

330

RN-10k

LED

35605-5153-B00 PE

VCC

GND

Output

OE

DSO321SR (80 MHz)

33

0.1 uF

4

2

3

1

INTPxZ (P00)

RDENL (Pxx)

Not e 2

VDD33 (3.3 V)

VDD33 (3.3 V)

.

The

interrupt function (INTPZ).

2.

The RDENL pin should be connected to a general output port.

3.

This pin is multiplexed with CC-Link (intelligent device station).

Figure 9.1 Connection Example for CC-Link Remote Device Station

Notes 1

CCS_REFSTB (P10) pin is needed to be connected to the port pin which has external

R18UZ0021EJ0400 Page 23 of 64

Dec. 28, 2018

Page 35

R-IN32M3 Series: Board design edition 10. Notes of CC-Link IE Field Use (Only R-IN32M3-CL)

10. Notes of CC-Link IE Field Use (Only R-IN32M3-CL)

When booting in external memory boot mode, external serial flash ROM boot mode, and instruction RAM boot mode,

drive the P33 (multiple xed with CCI_WAITEDGEH) and P34 (multiplexed with CCI_WRLENH) pins high during a

reset.

If the P33 and P34 pins are driven low during a reset, accessing the CC-Link IE field from the CPU in the R-IN32M3 is

not possible.

R18UZ0021EJ0400 Page 24 of 64

Dec. 28, 2018

Page 36

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

Mode Setting

External Connection Mode

MEMIFSEL

MEMCSEL

HIFSYNC

ADMUXMODE

Asynchronous SRAM MEMC

Synchronous burst access MEMC

Asynchronous SRAM interface mode

Synchronous SRAM interface mode

Low

-

Setting prohibited

Low

Setting prohibited

(address/data multiplexed)

.

Before access to the CC

(MEMIFSEL high, M EMCSEL low, HIFSYNC hi gh). (The CC

the R-IN32M3-CL.)

11. External MCU/Memory Interface Pins

This LSI is able to connect to an external MCU o r memory.

The connection mode is decided by the signal level of the MEMIFSEL, MEMCSEL, HIFSYNC, and ADMUXMODE

pins as sho wn in Table 11.1.

Table 11.1 Mode Selection of External MCU/Memory Connection

Low Low - - External memory interface

High - - External memory interface

High Low Low - External MCU interface

High - External MCU interface

Note

High

High

High External MCU interface

Note

-Link IE field, select the synchronous SRAM interface mode

The connection example for each modes is shown in the following sec tio n s.

Synchronous SRAM-type transfer mod e

-Link IE field is incorporated only in

R18UZ0021EJ0400 Page 25 of 64

Dec. 28, 2018

Page 37

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

11.1 External MCU Interface

The external MCU interface is multiplexed with the external memory interface. When the MEMIFSEL pin is set to the

high level, i t functio ns as the external MCU interface.

The external MCU interface supports the asynchronous SRAM interface mode and the synchronous SRAM interface

mode. When the level of a HIFSYNC pin is high, it functions as a synchronous SRAM interface, and when HIFSYNC is

set to low, it functions as an asynchro nous SRAM interface. (see Table 11.1.)

Moreover, the external MCU interface supports t he synchronous SRAM type trans fer of clock synchronization so that

mass data can be accessed at high speed. This function is enabled by setting the MEMIFSEL and MEMCSEL pins to the

high level.

R18UZ0021EJ0400 Page 26 of 64

Dec. 28, 2018

Page 38

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

R-IN32M3

External MCU

A2-A20

D0-D31

CSZ

HPGCSZ

Note4

HA2-HA20

Note5

HD0-HD31

PGCSZ

RDZ

HCSZ

HRDZ

WAITZHWAITZ

WRSTBZHWRSTBZ

Interrupt, port pinHERROUTZ

Note3

HBUSCLK

HWRZ0 / HBENZ0 (WRZ0) / BENZ0

(WRZ1) / BENZ1

(WRZ2) / BENZ2

(WRZ3) / BENZ3

HWRZ1 / HBENZ1

HWRZ2 / HBENZ2

HWRZ3 / HBENZ3

R-IN32M3

External MCU

A1-A20

D0-D15

CSZ

HPGCSZ

HA1-HA20

Note6

HD0-HD15

PGCSZ

Note4

RDZ

HCSZ

HRDZ

WAITZHWAITZ

WRSTBZHWRS TBZ

Interrupt, port pinHERROUTZ

Note3

HWRZ0 / HBENZ0 (WRZ0) / BENZ0

(WRZ1) / BENZ1HWRZ1 / HBENZ1

HBUSCLK

.

The details of signal connection depend on the bus

Confirm the product specification of MCU which is connected to this LSI.

.

HWRZ0

functions are selected by the level on the HWRZSEL pin.

.

Connecting the

general-purpose port input of the MCU to be connected, if required.

11.1.1 Asynchronous SRAM Interface Mode

The following figure shows a general connection example in asynchronous SRAM interface mode, whe n this LSI chip is

connected as a slave device to an external MCU.

Figure 11.1 Connection Example of 32-Bit Ext ern al MCU I nterf ac e (Asynchronous SRAM Interface Mode)

Figure 11.2 Connection Example of 16-Bit External MCU Interface (Asynchronous SRAM Interface Mode)

Notes 1

2

3

R18UZ0021EJ0400 Page 27 of 64

Dec. 28, 2018

-HWRZ3 and HBENZ0-HBENZ3 are multiplexed on the same pins, and the pin

HERROUTZ signal is not indispensable. Connect it to an interrupt or

interface specification of the host MCU.

Page 39

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

4.

This is a chip-select signal supporting paged access. Connect it if required.

.

Connected the address signal for a 4

this LSI.

.

Connected the address signal for a 2

this LSI.

5

6

-byte boundary from the destinatio n to the H A2 pin of

-byte boundary from the destinatio n to the H A1 pin of

R18UZ0021EJ0400 Page 28 of 64

Dec. 28, 2018

Page 40

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

R-IN32M3

External MCU

A2-A20

D0-D31

CSZ

HPGCSZ

HA2-HA20

Note5

HD0-HD31

PGCSZ

Note4

RDZ

HCSZ

HRDZ

WAITZHWAITZ

WRSTBZHWRSTBZ

Interrupt, port pinHERROUTZ

Note3

HBUSCLK

HWRZ0 / HBENZ0 (WRZ0) / BENZ0

(WRZ1) / BENZ1

(WRZ2) / BENZ2

(WRZ3) / BENZ3

HWRZ1 / HBENZ1

HWRZ2 / HBENZ2

HWRZ3 / HBENZ3

BUSCLK

R-IN32M3

External MCU

A1-A20

D0-D15

CSZ

HPGCSZ

HA1-HA20

Note6

HD0-HD15

PGCSZ

Note4

RDZ

HCSZ

HRDZ

WAITZHWAITZ

WRSTBZHWRS TBZ

Interrupt, port pinHERROUTZ

Note3

HWRZ0 / HBENZ0 (WRZ0) / BENZ0

(WRZ1) / BENZ1HWRZ1 / HBENZ1

HBUSCLK BUSCLK

.

The details of signal connection depend on the bus

Confirm the product specification of MCU which is connected to this LSI.

.

HWRZ0

functions are selected by the level on the HWRZSEL pin.

.

Connecting the

general-purpose port input of the MCU to be connected, if required.

4.

This is a chip-select signal supporting paged access. Connect it if required.

5.

Connected the address signal for a 4

this LSI.

6.

Connected the address signal for a 2

this LSI.

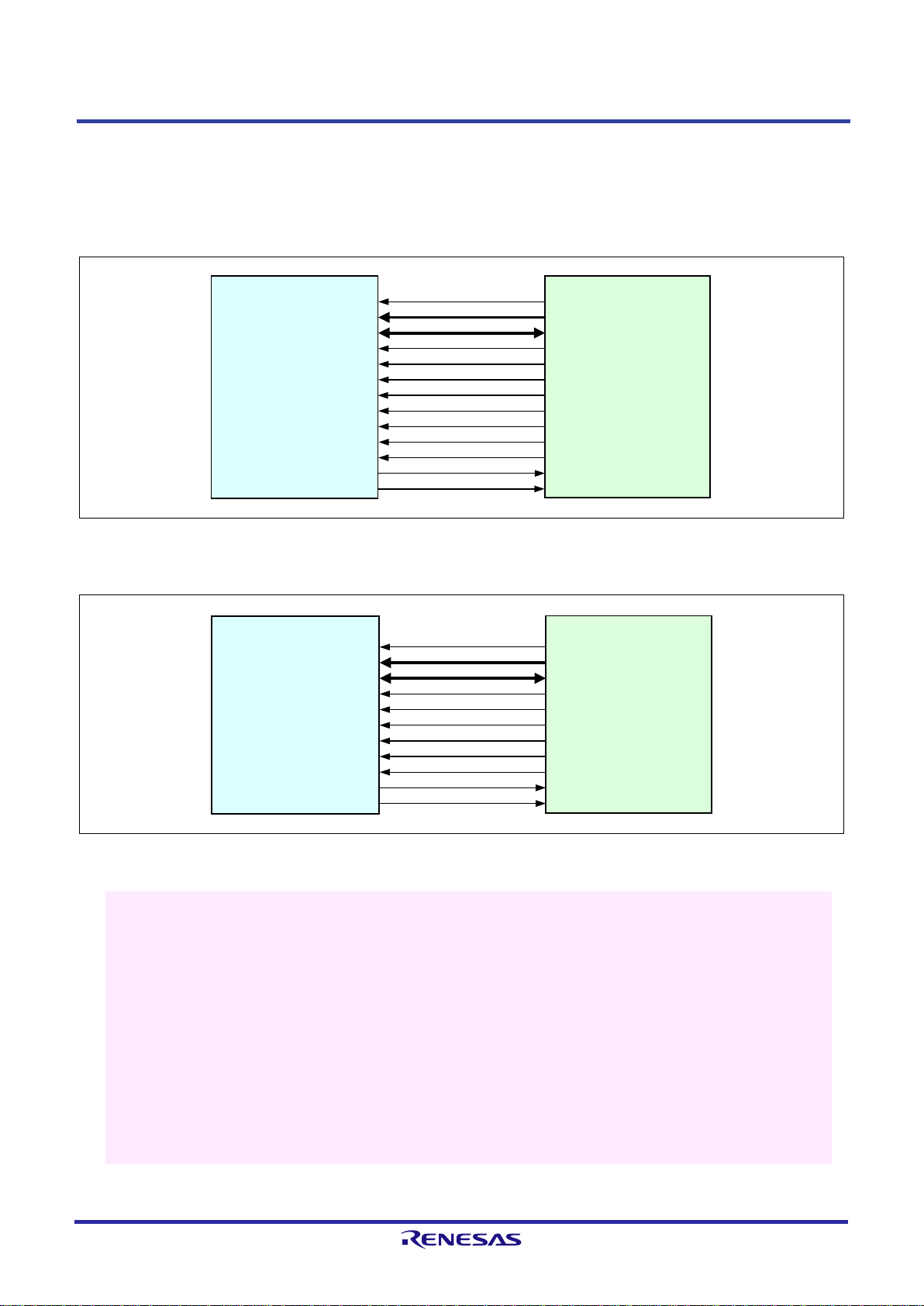

11.1.2 Synchronous SRAM Interface Mode

The following figure shows a general connection example in synchro nous SRAM interface mode, when this LSI chip is

connected as a slave device to an external MCU.

Figure 11.3 Connection Example of 32-Bit External MCU Interf ace (Synchronous SRAM Interface Mode)

Figure 11.4 Connection Example of 16-Bit External MCU Interface (Synchronous SRAM Interface Mode)

Notes 1

2

-HWRZ3 and HBENZ0-HBENZ3 are multiplexed on the same pi ns, and the pin

interface specification of the host MCU.

3

R18UZ0021EJ0400 Page 29 of 64

Dec. 28, 2018

HERROUTZ signal is not indispensable. Connect it to an interrupt or

-byte boundary from the destinatio n to the H A2 pin of

-byte boundary from the destination to the HA1 pin of

Page 41

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

R-IN32M3

External MCU

D0-D31

CSZ

HBCYSTZ

HD0-HD31

BCYSTZ / ADV

RDZ

HCS Z

HRDZ

WAITZHWAITZ

WRSTBZHW RS TBZ

Interrupt, port pinHERROUTZ

Note 3

HBUSCLK

HWRZ0 / HBENZ0 BENZ0

BENZ1

BENZ2

BENZ3

HWRZ1 / HBENZ1

HWRZ2 / HBENZ2

HWRZ3 / HBENZ3

BUSCLK

HWRZSEL

Note 2

R-IN32M3

External MCU

D0-D15

CSZ

HBCYSTZ

HD0-HD15

BCYSTZ / ADV

RDZ

HCS Z

HRDZ

WAITZHWAITZ

WRSTBZHW RS TBZ

Interrupt, port pinHERROUTZ

Note 3

HWRZ0 / HBENZ0 BENZ0

BENZ1HWRZ1 / HBENZ1

HBUSCLK BUSCLK

A17-A20

Note 5

HA16-HA19

Note 4

HWRZSEL

Note 2

.

The details of signal connection depend on the bus

Confirm the product specification of MCU which is connected to this LSI.

2.

In this mode, the HWRZSEL pin has to be set to low level.

3.

Connecting the

general-purpose port input of the MCU to be connected, if required.

4.

Connected the address signal for a

pin of this LSI.

5.

Accessed is by byte-wise addressing.

11.1.3 Synchronous SRAM-Type Transfer Mode

The following figure shows a general connection example in synchronous SRAM-type transfer mode, when this LSI c hi p

is connected as a slave device to an external MCU. When setting this mode, enable "address/data multiplex" function (the

ADMUXMODE pin should be driven high).

Figure 11.5 Connection Example of 32-Bit External MCU Interface (Synchronous SRAM-Type Transfer

Mode)

Figure 11.6 Connection Example of 16-Bit External MCU Interf ace (Synchronous SRAM-Type Transfer

Mode)

Notes 1

R18UZ0021EJ0400 Page 30 of 64

Dec. 28, 2018

HERROUTZ signal is not indispensable. Connect it to an interrupt or

128-Kbyte boundary from the destination to the HA16

interface specification of the host MCU.

Page 42

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

11.2 External Memory Interface

This section describes the connection as a master device to an external memory.

The operating connection mode of the external memory interface depends on the level of the signal on the MEMCSEL

pin (see Table 11.1).

11.2.1 Asynchronous SRAM MEMC

The asynchronous SRAM MEMC is externally connectable to paged ROM, ROM, SRAM, or peripheral devices with an

interface similar to the SRAM interface via a 16- or 32-bit bus.

The externa l MCU interfaces for the asynchronous SRAM MEMC and the synchronous metho d burst access MEMC are

multiplexed with each other. When both the MEMCSEL and MEMIFSEL pins are at the low level, the asynchronous

SRAM MEMC can be used.

When both the BOOT0 and BOOT1 pins are at the low level, booting up proceeds from the memory connected to CSZ0.

R18UZ0021EJ0400 Page 31 of 64

Dec. 28, 2018

Page 43

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

R-IN32M3

SRAM

(256 Kwords × 16 bits)

A0-A17

I/O1-I/O16

/CS

/UB

/WE

RDZ

A2-A19

D16-D31

/OE

/LB

CSZn

(WRZ3) / BENZ3

(WRZ2) / BENZ2

(WRZ1) / BENZ1

WRSTBZ

D0-D15

(WRZ0) / BENZ0

SRAM

(256 Kwords × 16 bits)

A0-A17

I/O1-I/O16

/CS

/UB

/WE

/OE

/LB

R-IN32M3

SRAM

(256 Kwords × 16 bits)

A0-A17

I/O1-I/O16

/CS

/UB

/WE

RDZ

A1-A18

/OE

/LB

CSZn

(WRZ1) / BENZ1

WRSTBZ

D0-D15

(WRZ0) / BENZ0

Remark.

n = 0 to 3

11.2.1.1 Connection Example with SRAM

The following figure shows an example when t his LSI chip is connected to SRAM.

Figure 11.7 Connection Example with 32-Bit SRAM (Asynchronous SRAM MEMC)

Figure 11.8 Connection Example with 16-Bit SRAM (Asynchronous SRAM MEMC)

R18UZ0021EJ0400 Page 32 of 64

Dec. 28, 2018

Page 44

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

R-IN32M3

RDZ

A2-A21

D16-D31

CSZ0

D0-D15

WRSTBZ

Paged ROM

(1 Mword × 16 bits)

A0-A19

O0-O15

/CE

/OE

/WE

Paged ROM

(1 Mword × 16 bits)

A0-A19

O0-O15

/CE

/OE

/WE

R-IN32M3

Paged ROM

(1 Mword × 16 bits)

A0-A19

O0-O15

/CE

RDZ

A1-A20

/OE

CSZ0

D0-D15

/WEWRSTBZ

Caution.

The on-page mode of paged ROM is available only when the ROM is connected to CSZ0.

11.2.1.2 Connection Example with Paged ROM

The following figure shows an example when this LSI chip is connected to paged ROM.

Figure 11.9 Connection Example with 32-Bit Paged ROM (Asynchronous SRAM MEMC)

Figure 11.10 Connectio n Example with 16-Bit Paged ROM (Asynchronous SRAM MEMC)

R18UZ0021EJ0400 Page 33 of 64

Dec. 28, 2018

Page 45

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

11.2.2 Synchronous Burst Access MEMC

The synchronous burst access MEMC is externally connectable to paged ROM, ROM, SRAM, PSRAM, NOR-flash

memory, or peripheral devices with an interface similar to the SRAM interface via a 16- or 32-bit bus.

By setting t he ADMUXMODE pin to high level, the address signals can be multiplexed to be output from data pins.

The external MCU interfaces for the synchronous burst access MEMC and the asynchronous SRAM MEMC are

multiplexed with each other. When the MEMCSEL and MEMIFSEL pins are set to high level and low level respectively,

the synchronous burst access MEMC can be used.

When both the BOOT0 and BOOT1 pins are at low level, booting up proceeds from the memory connected to CSZ0.

R18UZ0021EJ0400 Page 34 of 64

Dec. 28, 2018

Page 46

R-IN32M3 Series: Board design edition 11. External MCU/Memory Interface Pins

R-IN32M3

RDZ

A2-A19

Note

D16-D31

CSZn

(WRZ3) / BENZ3

(WRZ2) / BENZ2

(WRZ1) / BENZ1

WRSTBZ

D0-D15

(WRZ0) / BENZ0

BUSCLK

SRAM

(256 Kwords × 16 bits)

A0-A17

Note

I/O1-I/O16

/CS

/UB

/WE

/OE

/LB

BUSCLK

SRAM

(256 Kwords × 16 bits)

A0-A17

注

BUSCLK

I/O1-I/O16

/CS

/OE

/UB

/WE

/LB

R-IN32M3

SRAM

(256 Kwords × 16 bits)

A0-A17

Note

I/O1-I/O16