Page 1

Target Spec

R61509V

260k-color, 240RGB x 432-dot graphics liquid crystal

controller driver for Amorphous-Silicon TFT Panel

REJxxxxxxx-xxxx

Rev.0.11

April 25, 2008

Description ......................................................................................................... 6

Features ......................................................................................................... 7

Power Supply Specifications .............................................................................. 8

Differences Between R61509 and R61509V ...................................................... 9

Block Diagram.................................................................................................... 10

Block Function.................................................................................................... 11

1. System Interface..................................................................................................................................................... 11

2. External Display Interface (RGB, VSYNC interfaces)........................................................................................ 12

3. Address Counter (AC) ...........................................................................................................................................12

4. Graphics RAM (GRAM)........................................................................................................................................13

5. Grayscale Voltage Generating Circuit..................................................................................................................13

6. Liquid Crystal Drive Power Supply Circuit ..........................................................................................................13

7. Timing Generator .................................................................................................................................................. 13

8. Oscillator (OSC)..................................................................................................................................................... 13

9. Liquid crystal driver Circuit .................................................................................................................................. 13

10. Internal Logic Power Supply Regulator............................................................................................................... 13

Pin Function........................................................................................................ 14

Pad Arrangement ................................................................................................ 19

Pad coordinate..................................................................................................... 21

Bump Arrangement............................................................................................. 36

Connection Example........................................................................................... 37

GRAM Address Map .......................................................................................... 38

Instruction ......................................................................................................... 40

Rev. 0.11 April 25, 2008, page 1 of 181

Page 2

R61509V Target Spec

Outline ..........................................................................................................................................................................40

Instruction Data Format.............................................................................................................................................. 40

Index (IR) .....................................................................................................................................................................41

Display control ............................................................................................................................................................. 41

Device code read (R000h) ...................................................................................................................................... 41

Driver Output Control (R001h).............................................................................................................................. 41

LCD Drive Wave Control (R002h)......................................................................................................................... 42

Entry Mode (R003h) ............................................................................................................................................... 42

Display Control 1 (R007h) ..................................................................................................................................... 45

Display Control 2 (R008h) ..................................................................................................................................... 46

Display Control 3 (R009h) ..................................................................................................................................... 48

8 Color Control (R00Bh) ........................................................................................................................................49

External Display Interface Control 1 (R00Ch) ......................................................................................................50

External Display Interface Control 2 (R00Fh) ......................................................................................................52

Panel Interface Control 1 (R010h)......................................................................................................................... 53

Panel Interface Control 2 (R011h)......................................................................................................................... 55

Panel Interface Control 3 (R012h)......................................................................................................................... 56

Panel Interface Control 4 (R013h)......................................................................................................................... 58

Panel Interface Control 5 (R014h)......................................................................................................................... 59

Panel Interface Control 6 (R020h)......................................................................................................................... 60

Panel Interface Control 7 (R021h)......................................................................................................................... 62

Panel Interface Control 8 (R022h)......................................................................................................................... 63

Panel Interface Control 9 (R023h)......................................................................................................................... 65

Frame Marker Control (R090h) ............................................................................................................................. 66

Power Control............................................................................................................................................................... 67

Power Control 1 (R100h) .......................................................................................................................................67

Power Control 2 (R101h) .......................................................................................................................................69

Power Control3 (R102h) ........................................................................................................................................ 73

Power Control 4 (R103h) .......................................................................................................................................74

RAM Access..................................................................................................................................................................75

RAM Address Set (Horizontal Address) (R200h) RAM Address Set (Vertical Address) (R201h) ........................75

GRAM Data Write (R202h) ....................................................................................................................................76

GRAM Data Read (R202h).....................................................................................................................................77

NVM Data Read / NVM Data Write (R280h)......................................................................................................... 78

Window Address Control ............................................................................................................................................. 81

Window Horizontal RAM Address Start (R210h), Window Horizontal RAM Address End (R211h) ................... 81

Window Vertical RAM Address Start (R212h), Window Vertical RAM Address End (R213h) ............................81

γ Control .......................................................................................................................................................................82

γ Control 1 ~ 14 (R300h to R309h) ........................................................................................................................ 82

Base Image Display Control ........................................................................................................................................ 84

Base Image Number of Line (R400h) ..................................................................................................................... 84

Base Image Display Control (R401h) ....................................................................................................................84

Base Image Vertical Scroll Control (R404h) .........................................................................................................84

Partial Display Control ................................................................................................................................................ 88

Partial Image 1: Display Position (R500h), RAM Address 1 (Start Line Address) (R501h), RAM Address 1 (End Line Address)

(R502h) ................................................................................................................................................................ 88

Pin Control ................................................................................................................................................................... 89

Test Register (Software Reset) (R600h) .................................................................................................................89

Rev. 0.11 April 25, 2008, page 2 of 181

Page 3

R61509V Target Spec

NVM Control ................................................................................................................................................................ 90

NVM Access Control 1 (R6F0h), NVM Access Control 2 (R6F1h), NVM Access Control 3 (R6F2h).................90

Instruction List.................................................................................................... 92

Reset Function .................................................................................................... 93

Basic Mode Operation of the R61509V.............................................................. 95

Interface and Data Format .................................................................................. 96

System Interface.................................................................................................. 99

80-System 18-bit Bus Interface ................................................................................................................................... 100

80-System 16-bit Bus Interface ................................................................................................................................... 101

80-System 9-bit Bus Interface ..................................................................................................................................... 104

Data Transfer Synchronization in 9-bit Bus Interface Operation ............................................................................105

80-System 8-bit Bus Interface ..................................................................................................................................... 106

Serial Interface............................................................................................................................................................. 109

VSYNC Interface................................................................................................ 112

Notes to VSYNC Interface Operation .........................................................................................................................114

FMARK Interface ............................................................................................... 116

FMP Setting Example.................................................................................................................................................. 120

RGB Interface ..................................................................................................... 121

RGB Interface ..............................................................................................................................................................121

Polarities of VSYNCX, HSYNCX, ENABLE, and DOTCLK Signals ....................................................................... 122

Setting Example of Display Control Clock in RGB Interface Operation .................................................................123

RGB Interface Timing ................................................................................................................................................. 124

16-/18-Bit RGB Interface Timing ...........................................................................................................................124

RAM access via system interface in RGB interface operation .................................................................................. 125

16-Bit RGB Interface ...................................................................................................................................................126

18-bit RGB Interface....................................................................................................................................................127

Notes to RGB Interface Operation ..............................................................................................................................128

RAM Address and Display Position on the Panel .............................................. 129

Instruction Setting Example........................................................................................................................................132

Window Address Function ................................................................................. 134

Scan Mode Setting .............................................................................................. 135

8-Color Display Mode ........................................................................................ 136

Frame-Frequency Adjustment Function ............................................................. 137

Relationship between Liquid Crystal Drive Duty and Frame Frequency ................................................................. 137

Rev. 0.11 April 25, 2008, page 3 of 181

Page 4

R61509V Target Spec

Partial Display Function ..................................................................................... 139

Liquid Crystal Panel Interface Timing ............................................................... 140

Internal Clock Operation.............................................................................................................................................140

RGB Interface Operation............................................................................................................................................. 141

γ Correction Function.......................................................................................... 142

γ

Correction Function .................................................................................................................................................. 142

γ

Correction Circuit......................................................................................................................................................142

γ

Correction Registers .................................................................................................................................................. 143

Reference level adjustment registers ...........................................................................................................................143

Interpolation Registers.................................................................................................................................................145

Frame Memory Data and the Grayscale Voltage .......................................................................................................148

Power Supply Generating Circuit ....................................................................... 149

Power Supply Circuit Connection Example 1 (VCI1 = VCIOUT) ............................................................................149

Power Supply Circuit Connection Example 2 (VCI1 = VCI Direct Input)............................................................... 150

Specifications of Power-supply Circuit External Elements................................ 151

Voltage Setting Pattern Diagram ........................................................................ 152

Liquid Crystal Application Voltage Waveform and Electrical Potential ..................................................................153

VCOMH and VREG1OUT Voltage Adjustment Sequence............................... 154

NVM Control...................................................................................................... 155

NVM Load (Register Resetting) Sequence ................................................................................................................. 156

NVM Write Sequence................................................................................................................................................... 157

NVM Erase Sequence .................................................................................................................................................. 158

Power Supply Setting Sequence ......................................................................... 159

Notes to Power Supply ON Sequence ................................................................ 161

Instruction Setting Sequence and Refresh Sequence.......................................... 162

Display ON/OFF Sequences and Refresh Sequence ................................................................................................. 162

Shutdown Mode Sequences .........................................................................................................................................163

Partial Display Setting ................................................................................................................................................. 166

Absolute Maximum Ratings ............................................................................... 167

Electrical Characteristics .................................................................................... 168

DC Characteristics ....................................................................................................................................................... 168

Step-up Circuit Characteristics.............................................................................................................................. 170

Internal Reference Voltage: Condition .................................................................................................................. 170

Power Supply Voltage Range ................................................................................................................................. 171

Output Voltage Range ............................................................................................................................................ 171

AC Characteristics .......................................................................................................................................................172

Rev. 0.11 April 25, 2008, page 4 of 181

Page 5

R61509V Target Spec

Clock Characteristics ............................................................................................................................................. 172

80-system 18-/16-/9-/8-bit Bus interface Timing Characteristics ......................................................................... 172

Clock Synchronous Serial Interface Timing Characteristics.................................................................................173

RGB Interface Timing Characteristics...................................................................................................................173

LCD Driver Output Characteristics....................................................................................................................... 174

Reset Timing Characteristics .................................................................................................................................174

Notes to Electrical Characteristics .............................................................................................................................. 175

Test Circuits..................................................................................................................................................................176

Timing Characteristics.................................................................................................................................................177

80-system Bus Interface..........................................................................................................................................177

Clock Synchronous Serial Interface ....................................................................................................................... 178

Reset Operation ...................................................................................................................................................... 178

LCD Driver and VCOM Output Characteristics ...................................................................................................179

Rev. 0.11 April 25, 2008, page 5 of 181

Page 6

R61509V Target Spec

Description

The R61509V is a single-chip liquid crystal controller driver LSI for a-Si TFT panel, incorporating RAM

for a maximum 240 RGB x 432 dot graphics display, gate driver, source driver and power supply circuits.

For efficient data transfer, the R61509V supports high-speed interface via 8-/9-/16-/18-bit ports as system

interface to the microcomputer. As moving picture interface, the R61509V also supports RGB interface

(VSYNCX, HSYNCX, DOTCLK, ENABLE and DB17-0).

The power supply circuit incorporates step-up circuit and voltage follower circuit to generate TFT liquid

crystal panel drive voltages.

The R61509V’s power management functions such as 8-color display and shut down and so on make this

LSI an ideal driver for the medium or small sized portable products with color display systems such as

digital cellular phones or small PDAs, where long battery life is a major concern.

Rev. 0.11 April 25, 2008, page 6 of 181

Page 7

R61509V Target Spec

Features

•

A single-chip controller driver incorporating a gate circuit and a power supply circuit for a maximum

240RGB x 432dots graphics display on amorphous TFT panel in 262k colors

•

System interface

– High-speed interfaces via 8-, 9-, 16-, 18-bit parallel ports

– Clock synchronous serial interface

• Moving picture display interface

– 16-/18-bit RGB interface (VSYNCX, HSYNCX, DOTCLK, ENABLE, DB17-0)

– VSYNC interface (System interface + VSYNCX)

– FMARK interface (System interface + FMARK)

• Window address function to specify a rectangular area in the internal RAM to write data

• Write data within a rectangular area in the internal RAM via moving picture interface

– Reduce data transfer by specifying the area in the RAM to rewrite data

– Enable displaying the data in the still picture RAM area with a moving picture simultaneously

•

Abundant color display and drawing functions

– Programmable for 262k-color display

– Partial display function

• Low -power consumption architecture (allowing direct input of interface I/O power supply)

– Shut down function

– 8-color display function

Input power supply voltages: IOVCC (interface I/O power supply)

VCC (logic regulator power supply)

VCI (liquid crystal analog circuit power supply)

•

Incorporates a liquid crystal drive power supply circuit

– Source driver liquid crystal drive/VCOM power supply: DDVDH

VCL

– Gate drive power supply: VGH

VGL

– VCOM drive (VCOM power supply): VCOMH

VCOML

• Liquid crystal power supply startup sequencer

•

TFT storage capacitance: Cst only (common VCOM formula)

•

233,280-byte internal RAM

•

Internal 720-channel source driver and 432-channel gate driver

• Single-chip solution for COG module with the arrangement of gate circuits on both sides of the glass

substrate

• Internal NVM

User identification code: 8 bits

VCOM level adjustment: 7 bits x 2. Rewriting is available up to 5 times

Rev. 0.11 April 25, 2008, page 7 of 181

Page 8

R61509V Target Spec

Power Supply Specifications

Table 1

No. Item R61509V

1 TFT data lines 720 output

2 TFT gate lines 432 output

3 TFT display storage capacitance Cst only (Common VCOM formula)

4 Liquid crystal

drive output

5 Input voltage

S1~S720 V0 ~ V63 grayscales

G1~G432 VGH-VGL

VCOM Change VCOMH-VCOML amplitude with electronic volume

Change VCOMH with either electronic volume or from

VCOMR

IOVCC

(interface voltage)

VCC

(logic regulator power

supply)

1.65V ~ 3.3V

Power supply to IM0_ID, IM1-2, RESETX, DB17-0, RDX,

SDI, SDO, WR_SCL, RS, CSX, VSYNCX, HSYNCX,

DOTCLK, ENABLE, FMARK

Connect to VCC and VCI on the FPC when the electrical

potentials are the same.

2.5V ~ 3.3V

Connect to IOVCC and VCI on the FPC when the electrical

potentials are the same.

VCI

(liquid crystal drive

power supply voltage)

6 Liquid crystal

drive

voltages

DDVDH 4.5 ~ 6.0V (VCI1 x 2)

VGH 10 ~ 18.0 V (VCI1 x 5, 6)

VGL -4.5 ~ -13.5V (VCI1 x –3, -4, -5)

VGH-VGL max. 28V

VCL -1.9 ~ -3.0V (VCI1 x -1)

VCI-VCL max. 6V

2.5V ~ 3.3V

Connect to IOVCC and VCC on the FPC when the electrical

potentials are the same.

See “DC characteristics” in Chapter “Electrical Characteristics” for voltage spec.

Rev. 0.11 April 25, 2008, page 8 of 181

Page 9

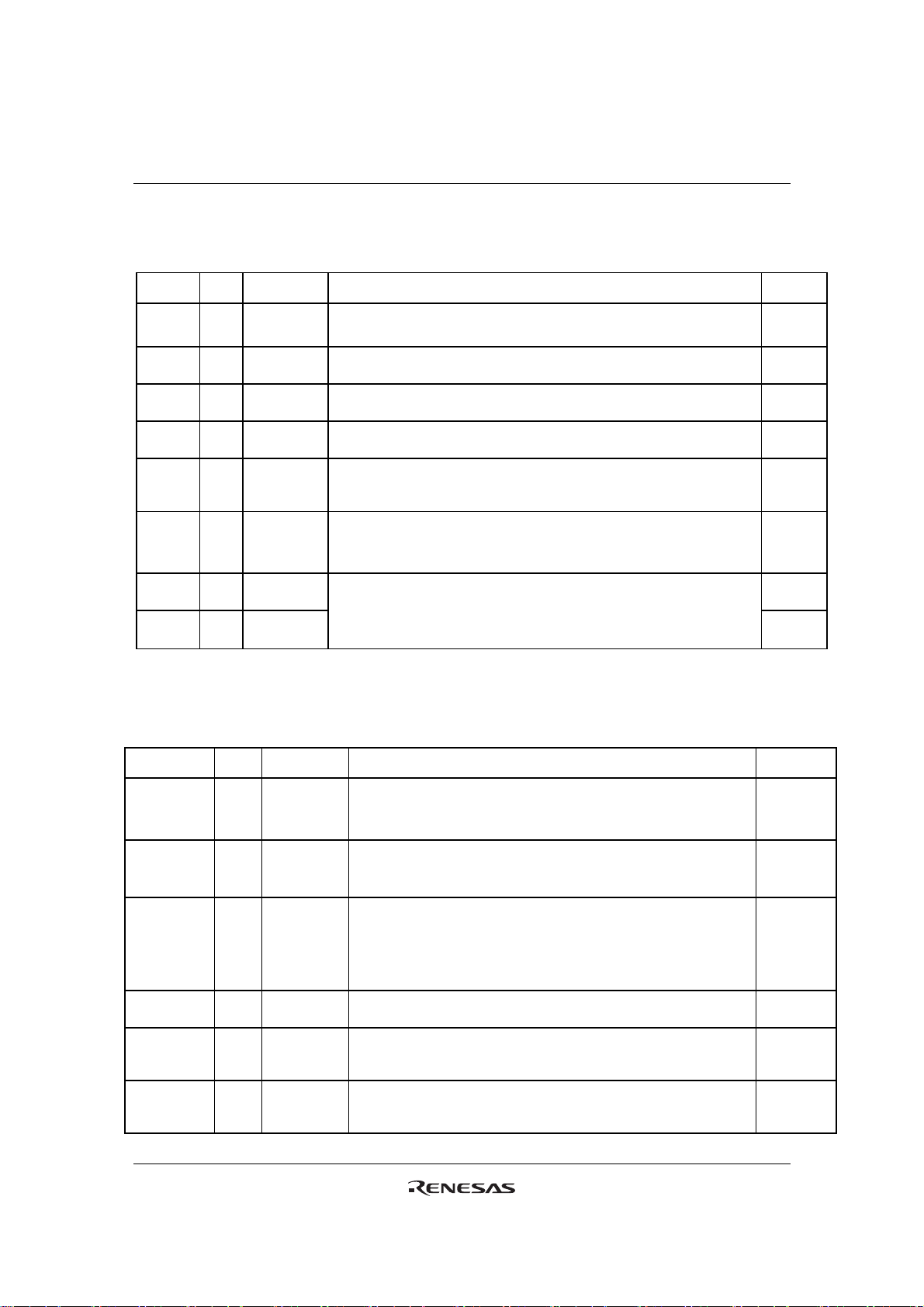

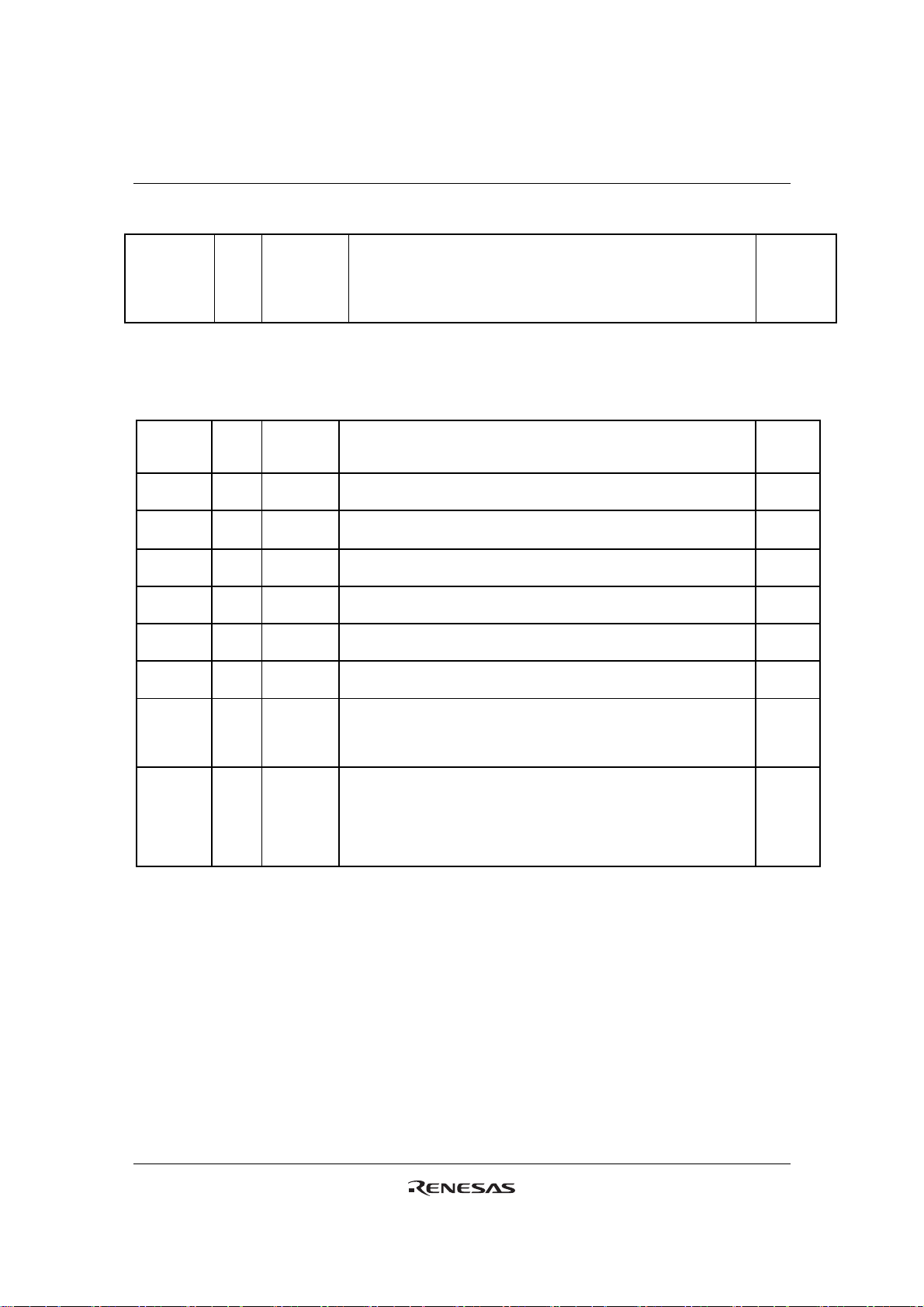

Difference Between R61509 and R61509V 2008.04.18

Index Command

(Pin) System Interface

IM2-0=011, TRI=1, DFM=0 8bit 3 transfer (2bit-8bit-8bit) Supported Deleted

R000h Device Code Read 1509H B509H

R002h LCD Drive Waveform Control

NW[1-0] --> NW bit is deleted. 1, 2, 3 or 4 line inversion 1 line inversion

R003h Entry Mode

R006h Outline Sharpening Control

EGMODE, AVST[2:0], ADST[2:0]DTHU[1:0], DTHL[1:0] Outline Sharpening Function Supported Deleted

R007h Display Control 1

R008h Display Control 2

R009h Display Control 3

R00Bh Low Power Control

R00Ch External Display Interface Control

R012h Panel Interface Control 3

R020h Panel Interface Control 4

R021h Panel Interface Control 5

VEQWI[1-0]-->VEQWI[2-0] Defines VCOM equalize period. 0, 1, 2 or 3 clock period 0, 1, 2, 3, 4, 5, 6 or 7 clock period

RTNE[6-0]-->RTNE[5-0] Defines number of clock per line. 16-127 clocks 16 - 63 clocks

NOWE[3-0]-->NOWE[2-0] Defines gate non overlap period. 0 - 15 clocks 0 - 7 clocks

SDTE[3-0]-->SDTE[2-0] Defines source output delay period. 0 - 15 clocks 0 - 7 clocks

R092h MDDI Sub-display Control

R100h Power Control 1

R101h Power Control 2

R102h Power Control 3

R103h Power Control 4

R110h Power Control 6

R112h Power Control 7

R280h

NVM Data Read / NVM Data Write

R281h VCOM High Voltage 1

R282h VCOM High Voltage 2

R300h-R309h Gamma Control

R400h

R401h

R503h-R505h Partial Image Control

Base Image Number of Line

Base Image Display Control

PTDP1[8-0] PTSA1[8-0] PTEA1[8-0] --> Deleted. Settings for partial image 2. Partial image 1 and 2 Partial image 1 only

R600h Software Reset

R606h i80-I/F Endian Control

See each register's description for detail.

Code Function R61509 R61509V

HWM High Speed RAM Write Supported Deleted

Sets data format when writing 16bit

EPF[1-0]

PTDE[1-0]-->PTDE0 Controls partial image 1 and 2. Partial image 1 and 2 Partial image 1

data in 18bit format. Supported Deleted

Deleted. (Because the sequence is changed. See "Power Supply

VON Starts VCOM output Manual setting

Setting Sequence" for detail. )

Deleted. (Because the sequence is changed. See "Power Supply

GON Sets gate output to OFF level. Manual setting

Setting Sequence" for detail. )

Deleted. (Because the sequence is changed. See "Power Supply

DTE Starts gate scan Manual setting

Setting Sequence" for detail. )

Deleted. (Because the sequence is changed. See "Power Supply

D[1-0] Starts/halts display operation Manual setting

FP[3-0] Defines front porch 2-14 lines (in units of 1 line) 3-128 lines (in units of 1 line)

BP[3-0] Defines back porch 2-14 lines (in units of 1 line) 3-128 lines (in units of 1 line)

PTG[1-0] --> Deleted. Sets gate scan mode Normal scan / interval scan Normal scan only (Interval scan is not available)

ISC[3:0] Sets gate scan cycle 3, 5, 7, 9, 11, 13 or 15 frames Deleted

PTS[2-0] -->PTS Sets source output level V0-V31 V0-V63

VEM[0] --> VEM[1-0] Execute VCOM equalize. VCOMH to VCOML only VCOML to VCOMH / VCOMH to VCOML (See description)

Setting Sequence" for detail. )

Selects 6bit 3 transfer via RGB

RIM[1-0]=10

interface Supported Deleted

Defines data format for sub display

SIM[1:0] --> Deleted.

SAP[1-0]

interface operation. Supported Deleted

Adjusts bias current in source

amplifier. Supported

Deleted. (Because the sequence is changed. See "Power Supply

Setting Sequence" for detail. )

Deleted. (Because the sequence is changed. See "Power Supply

SAP --> SOAPON Enables source amplifier Supported

BT[2-0] Defines step-up factor DDVDH: x2, VCL:x-1, VGH: x6, x7, VGL: x-3, x-4, x-5 DDVDH: x2, VCL: x-1, VGH: x5, x6, VGL: x-3, x-4, x-5

Setting Sequence" for detail. )

Deleted. (Because the sequence is changed. See "Power Supply

APE --> Deleted. Enables power supply circuit Supported

SLP --> Deleted. Selects sleep mode. Supported Deleted

DC1[2-0] Defines step-up factor for DCDC1. Not synchronized with internal clock (Default) Synchronized with internal clock (Default)

DC2[2-0] Defines step-up factor for DCDC2. Not synchronized with internal clock (Default) Synchronized with internal clock (Default)

VRH[3-0] Sets a factor to generate 4bit (VRH [3:0]) 5bit (VRH [4:0]). Enables minute setting.

Setting Sequence" for detail. )

Defines reference level to generate

VRG1R --> Deleted.

VCOMG Defines VCOM amplitude VCOML can be set at GND level Deleted

VREG1OUT Selects external or internal reference voltage. Internal reference voltage only

Deleted. (Because the sequence is changed. See "Power Supply

PSE Enables power supply sequencer Supported

Setting Sequence" for detail. )

Deleted. (Because the sequence is changed. See "Power Supply

TBT[1-0] Used in power supply sequencer Supported

UID[3:0] User code UID[3:0] VCM[6-0] UID[7-0]

VCM1[4-0] Defines VCOMH 1level VCM1[4-0] NVM specification changed. VCM bit is moved to R280h.

Setting Sequence" for detail. )

Deleted. (Because the R61509V supports both NVM write and erase

VCMSEL , VCM2[4-0] Defines VCOMH 2level VCMSEL VCM2

Gamma Control Gamma control method changed. 84 bit 100 bit (New gamma correction method)

NL0[5-0] Specifies LCD drive line. 16 - 432 line (in units of 8 lines) 240 - 432 lines (in units of 8 lines)

functions).

Defines source output level in non-lit

NDL0

display area V31-V0 V63-V0

Inverts grayscale level in the display

REV0

SRST--> TRSR Software Reset Software Reset Only secret test registers are initialized.

TCREV[1] , TCREV[0] Selects the order of receiving data. Supported Deleted

area V31-V0 V63-V0

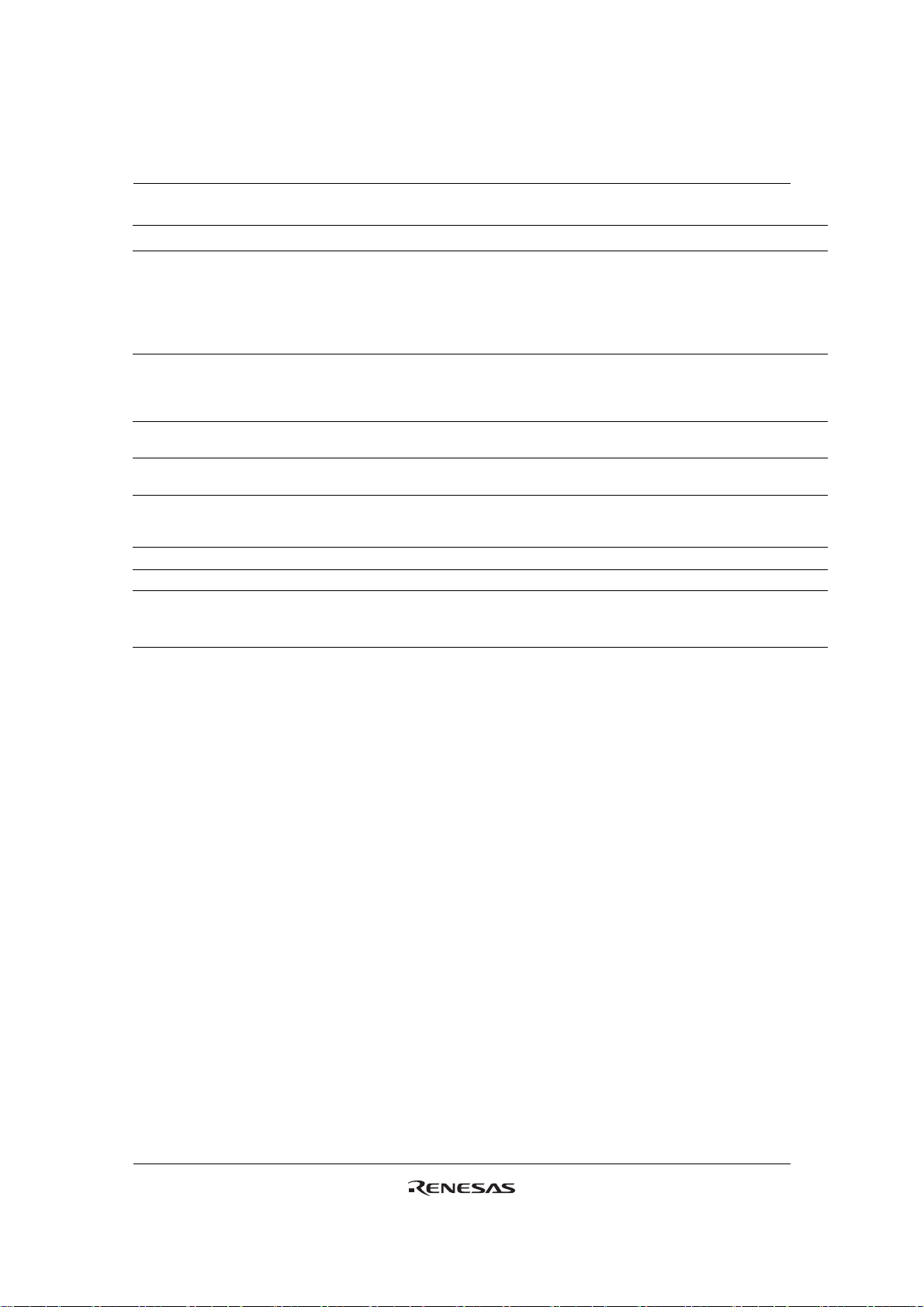

Page 10

R61509V Target Spec

A

K

K

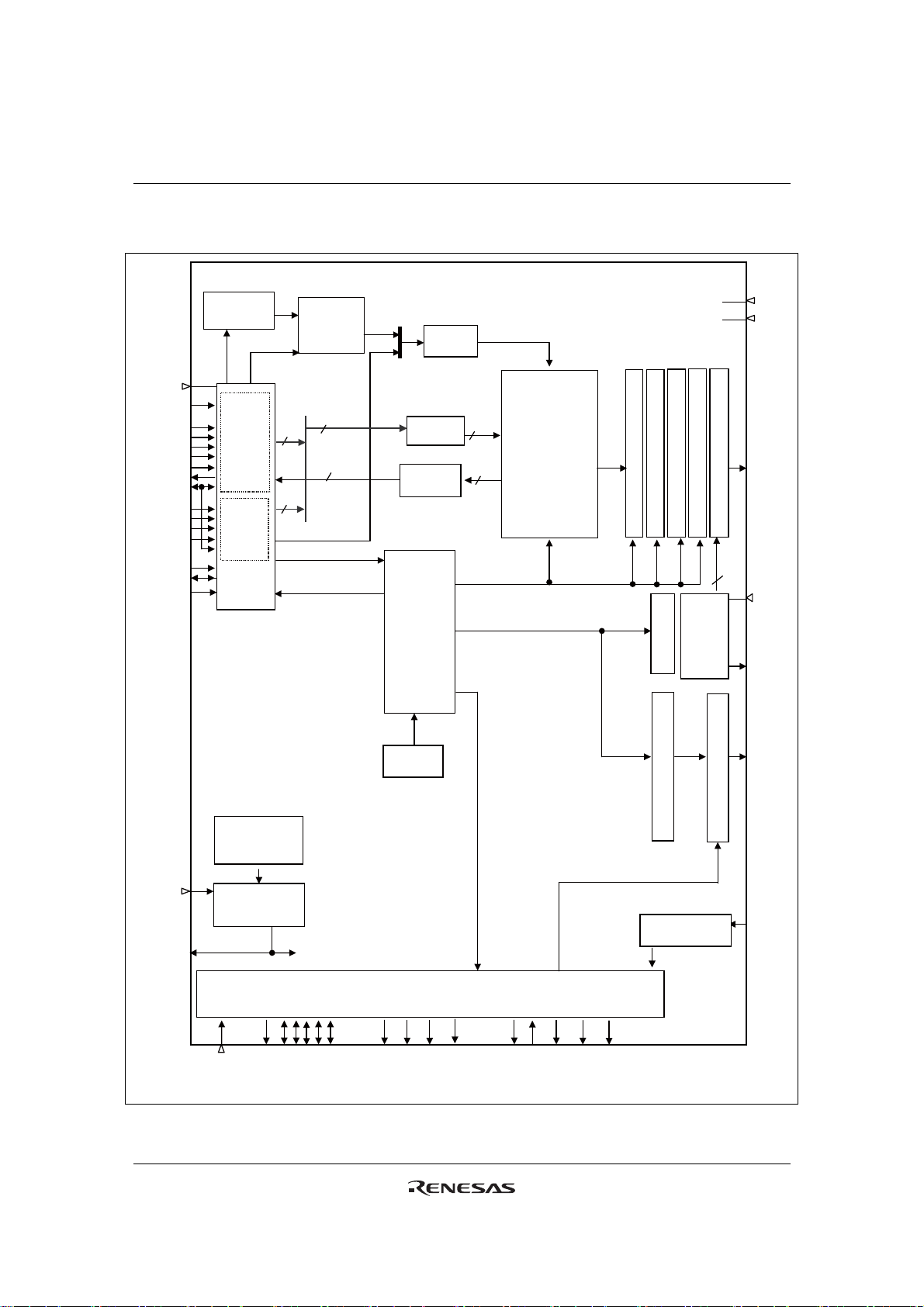

Block Diagram

IOVCC

㩷

IM2-1, IM0_ID

㩷

㩷

CSX

㩷

RS

WR_SCL

㩷

RDX

㩷

SDI

SDO

㩷

DB17-0

㩷

VSYNCX

㩷

HSYNCX

㩷

DOTCL

ENABLE

㩷

㩷

RESETX

㩷

FMAR

PROTECT

㩷

㩷

Index

Register (IR)

System

㩷

interface

㩷

㩷

18 bit

16 bit

9 bit

8 bit

Serial

㩷

㩷

External

㩷

display

㩷

interface

㩷 㩷

18

㩷

㩷

18

Control

Register

(CR)

18

18

GND

㩷

GND

Address

Counter

㩷

㩷

㩷

Write data

latch

Read data

㩷

latch

18

㩷

18

㩷

㩷

Graphic RAM

(GRAM)

233,280byte

Latch circuit

Latch circuit

M alternation

Latch Circuit

㩷

Source line drive circuit

V63-0

㩷

㩷

Timing

generator

㩷

㩷

Gamma

correction circuit

Grayscale voltage

VGS

㩷

VMON

generating circuit

Oscillator

㩷

Internal reference

voltage generating

circuit

㩷 㩷

VCC

㩷

㩷

Internal logic

power supply

circuit

㩷

㩷

㩷

㩷

㩷

㩷

VDD

㩷

Scandatageneratingcircuit

NVM

㩷

VGL

VCL

㩷

VCOM

VCOML

VCOMH

VCOMR

VREG1OUT

㩷

VCI1

VCI

C11P/C11M

C12P/C12M

LCD drive level generating circuit

C21P/C21M

C22P/C22M

C13P/C13M

DDVDH

VGH

Figure 1

Rev. 0.11 April 25, 2008, page 10 of 181

G1-G432

㩷

Gate line drive circuit

VPP1,

VPP3A,3B

Page 11

R61509V Target Spec

Block Function

1. System Interface

The R61509V supports 80-system high-speed interface via 8-, 9-, 16-, 18-bit parallel ports and a clock

synchronous serial interface. The interface is selected by setting the IM2-0 pins.

The R61509V has 16-bit index register (IR), 18-bit write-data register (WDR), and 18-bit read-data register

(RDR). The IR is the register to store index information from control register and internal GRAM. The

WDR is the register to temporarily store write data to control register and internal GRAM. The RDR is the

register to temporarily store the read data from the GRAM. The write data from the host processor to the

internal GRAM is first written to the WDR and then automatically written to the internal GRAM by

internal operation. The data is read via RDR from the internal GRAM. Therefore, invalid data is sent to

the data bus when the R61509V performs the first read operation from the internal GRAM. Valid data is

read out when the R61509V performs the second and subsequent read operation.

The R61509V allows writing instructions consecutively by executing the instruction in the same cycle

when it is written (0 instruction cycle).

Table 2 Register Selection (80-System 8-/9-/16-/18-Bit Parallel Interface)

WRX RDX RS Function

0 1 0 Write index to IR

1 0 0 Setting disabled

0 1 1 Write to control register or internal GRAM via WDR

1 0 1 Read from internal GRAM and register via RDR

Table 3 Register Selection (Clock Synchronous Serial Interface)

Start byte

R/W RS Function

0 0 Write index to IR

1 0 Setting disabled

0 1 Write to control register or internal GRAM via WDR

1 1 Read from internal GRAM and register via RDR

Rev. 0.11 April 25, 2008, page 11 of 181

Page 12

R61509V Target Spec

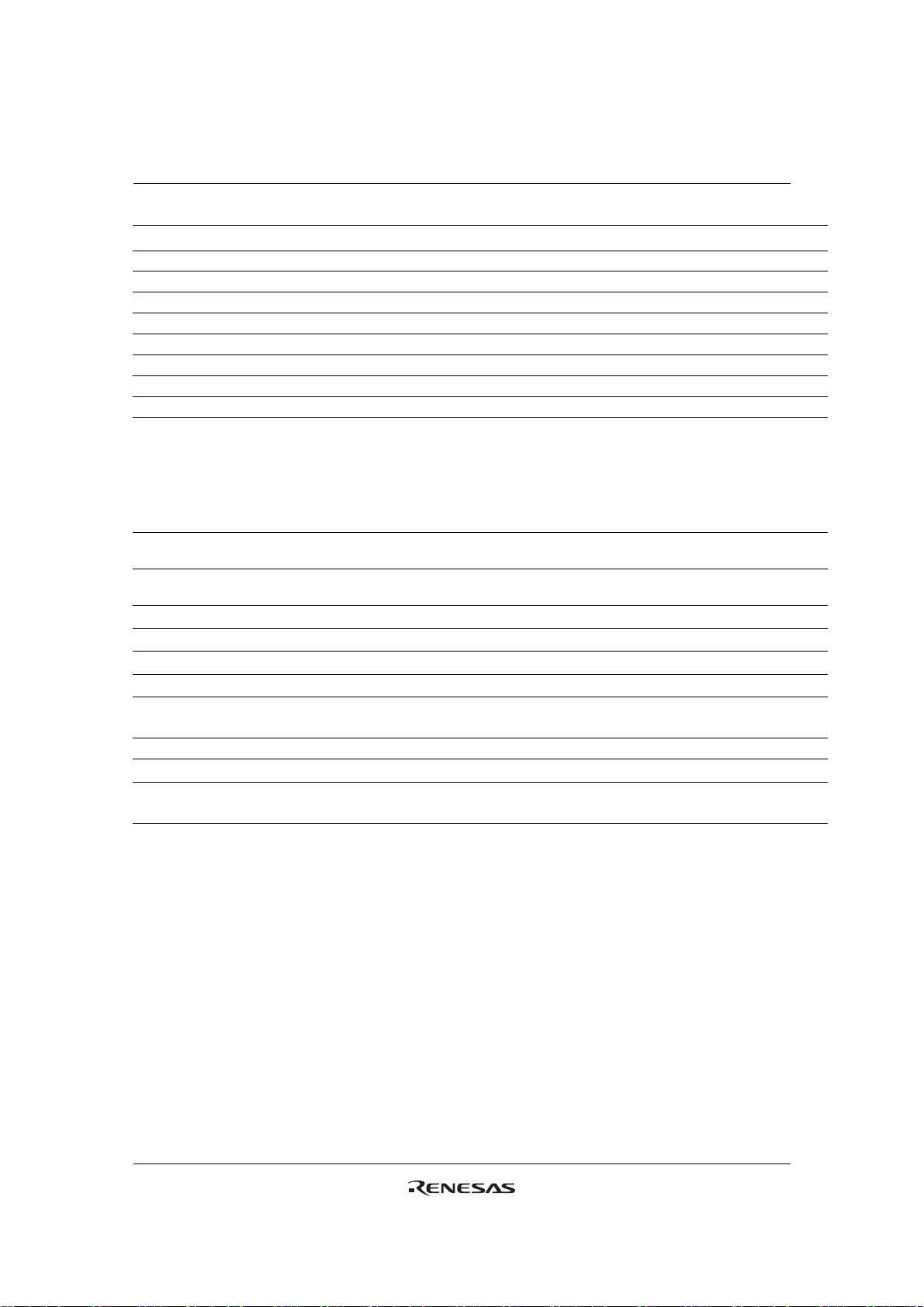

Table 4

IM2 IM1 IM0 System interface DB pins RAM write data

0 0 0

0 0 1

0 1 0

0 1 1

1 0 *

80-system 18-bit

interface

80-system 9-bit

interface

80-system 16-bit

interface

80-system 8-bit

interface

Clock

synchronous

serial interface

DB17-0 Single transfer (18 bits)

DB17-9 2-transfer (1st: 9 bits, 2nd: 9 bits)

DB17-10,

DB8-1

DB17-10

Single transfer (16 bits)

2-transfer (1

2-transfer (1

2-transfer (1

3-transfer (1

st

: 2 bits, 2nd: 16 bits)

st

: 16 bits, 2nd: 2 bits)

st

: 8 bits, 2nd: 8 bits)

st

: 6 bits, 2nd: 6 bits, 3rd: 6

bits)

(SDI,

2-transfer (1

st

: 8 bits, 2nd: 8 bits)

SDO)

1 1 0 Setting disabled - - -

1 1 1 Setting disabled - - -

Instruction write

transfer

Single transfer

(16 bits)

2-transfer

st

(1

: 8 bits, 2nd: 8

bits)

Single transfer

(16 bits)

2-transfer

(1st: 8 bits, 2nd: 8

bits)

2-transfer

(1st: 8 bits, 2nd: 8

bits)

2. External Display Interface (RGB, VSYNC interfaces)

The R61509V supports RGB and VSYNC interfaces as the external interface to display moving picture.

When the RGB interface is selected, the display operation is synchronized with externally supplied

synchronous signals (VSYNCX, HSYNCX, and DOTCLK). In RGB interface operation, data (DB17-0) is

written in synchronization with these signals when the polarity of enable signal (ENABLE) allows write

operation in order to prevent flicker when updating display data.

In VSYNC interface operation, the display operation is synchronized with the internal clock except frame

synchronization, which synchronizes the display operation with the VSYNCX signal. The display data is

written to the internal GRAM via system interface. When writing data via VSYNC interface, there are

constraints in speed and method in writing data to the internal RAM. For details, see Section “VSYNC

Interface”.

The R61509V allows switching interface by instruction according to the display image (still and/or moving

picture). This allows data to be transferred only when the data is updated hence less power consumption

during moving picture display.

3. Address Counter (AC)

The address counter (AC) gives an address to the internal GRAM. When the index of a register is written

to the IR, the address information is sent from the IR to the AC. After data is written to GRAM, the

address in the AC is automatically updated plus or minus 1. The window address function enables writing

data only within the rectangular area specified in the GRAM.

Rev. 0.11 April 25, 2008, page 12 of 181

Page 13

R61509V Target Spec

4. Graphics RAM (GRAM)

GRAM stands for graphics RAM, which can store bit-pattern data of 233,280 (240RGB x 432 (dots) x

18(bits)) bytes at maximum, using 18 bits per pixel.

5. Grayscale Voltage Generating Circuit

The grayscale voltage generating circuit generates liquid crystal drive voltages according to the grayscale

data in the γ-correction registers to enable 262k-color display. For details, see the γ-Correction Register

section.

6. Liquid Crystal Drive Power Supply Circuit

The liquid crystal drive power supply circuit generates DDVDH, VGH, VGL and VCOM levels to drive

liquid crystal.

7. Timing Generator

The timing generator generates a timing signal for the operation of internal circuits such as the internal

GRAM. The timing signal for display operations such as RAM read and the timing signal for internal

operations such as RAM access from the host processor are generated separately in order to avoid mutual

interference.

8. Oscillator (OSC)

The R61509V generates the RC oscillation clock internally. Using an external oscillation resistor is not

possible. The oscillation frequency is set to 678 kHz before shipment (for details, see Electrical

Characteristics). Use the frame frequency adjustment function to change the number of display lines and

the frame frequency. While the R61509V is shut down, RC oscillation halts so that reduce power

consumption is reduced.

9. Liquid crystal driver Circuit

The liquid crystal driver circuit of the R61509V consists of a 720-output source driver (S1 ~ S720) and a

432-output gate driver (G1~G432). The display pattern data is latched when all of 240RGB data are

inputted. The latched data control the source driver and output drive waveforms. The gate driver for

scanning gate lines outputs either VGH or VGL level. The shift direction of 720-bit source output from the

source driver can be changed by setting the SS bit and the shift direction of gate output from the gate driver

can be changed by setting the GS bit. The scan mode by the gate driver can be changed by setting the SM

bit.

10. Internal Logic Power Supply Regulator

The internal logic power supply regulator generates internal logic power supply VDD.

Rev. 0.11 April 25, 2008, page 13 of 181

Page 14

R61509V Target Spec

Pin Function

Table 5 External Power Supply

Signal I/O Connect to Function

VCC I

IOVCC I

GND I

VCI I

VCILVL I

AGND I

VPP1 I

VPP3A I

Power

supply

Power

supply

Power

supply

Power

supply

Reference

power

supply

Power

supply

Power

supply

Power

supply

Power supply for Internal VDD regulator.

VCC≧IOVCC

Power supply for interface pins. ―

GND level for internal logic and interface pins. GND=0V. ―

Power supply for liquid crystal power supply analog circuit. ―

Connect to an external power supply at the same level as VCI the

power supply for liquid crystal power supply analog circuit. In case of

COG, connect to VCI on the FPC to prevent noise.

Analog GND (for logic regulator and liquid crystal power supply).

AGND = 0V.

In case of COG, connect to GND on the FPC to prevent noise.

Power supply for internal NVM.

See section “NVM Control” for input voltages during write and erase

operation using VPP1-VPP3A pins.

Note 1: VCC, GND and AGND pins are allocated several different places on the chip. Make sure to connect

all of them to power following “Connection Example”.

When not

used

―

―

―

Open or

AGND

Open or

AGND

Table 6 Bus Interface (Amplitude: IOVCC~GND)

Signal I/O Connect to Function

CSX I

RS I

Host

processor

Host

processor

Chip selection signal. (Amplitude: IOVCC-GND)

Low: The R61509V is selected and accessible.

High: The R61509V is not selected and not accessible.

Register selection signal. (Amplitude: IOVCC-GND)

Low: Index register is selected.

High: Control register is selected.

Write strobe signal when 80-system bus interface is selected.

Data are written when Low level.

Synchronous clock signal when clock synchronous serial

interface is selected.

WRX_SCL I

Host

processor

(Amplitude: IOVCC-GND)

RDX I

SDI I

SDO O

Host

processor

Host

processor

Host

processor

Read strobe signal when 80-system bus interface is selected.

Data are read when Low level. (Amplitude: IOVCC-GND)

Serial data input pin when clock synchronous serial interface is

selected. Data are inputted on the rising edge of SCL signal.

(Amplitude: IOVCC-GND)

Serial data output pin when clock synchronous serial interface is

selected. Data are outputted on the falling edge of SCL signal.

(Amplitude: IOVCC-GND)

Rev. 0.11 April 25, 2008, page 14 of 181

When not

used

IOVCC

IOVCC

IOVCC

IOVCC

GND

/IOVCC

Open

Page 15

R61509V Target Spec

18-bit parallel bi-directional data bus for 80-system interface

operation (Amplitude: IOVCC-GND).

8-bit I/F: DB17-DB10 are used.

9-bit I/F: DB17-DB9 are used.

16-bit I/F: DB17-DB10 and DB8-1 are used.

18-bit I/F: DB17-DB0 are used.

18-bit parallel bi-directional data bus for RGB interface operation

(Amplitude: IOVCC-GND).

16-bit I/F: DB17-DB13 and DB11-1 are used.

18-bit I/F: DB17-DB0 are used.

Data enable signal for RGB interface operation.

Low: accessible (selected)

High: Not accessible (Not selected)

The polarity of ENABLE signal can be inverted by setting the

EPL bit. (Amplitude: IOVCC-GND).

Frame synchronous signal. Low active. (Amplitude: IOVCCGND).

Line synchronous signal, Low active. (Amplitude: IOVCC-GND)

Dot clock signal. Data is input on the rising edge of DOTCLK.

(Amplitude: IOVCC-GND)

Frame head pulse. (Amplitude: IOVCC-GND)

FMARK is used when writing data to the internal RAM.

Select host processor interface. (Amplitude: IOVCC-GND)

IM2 IM1

IM0

0 0 0

0 0 1

0 1 0

0 1 1

1 0

*

(ID)

System Interface

80-system 18-bit

interface

80-system 9-bit

interface

80-system 16-bit

interface

80-system 8-bit

interface

Clock synchronous

serial interface

DB pins

in use

Colors

DB17-0 262,144

DB17-9 262,144

DB17-10,

8-1

DB17-10

262,144

(Note 1)

262,144

(Note 2)

― 65536

1 1 0 Setting inhibited ― ―

1 1 1 Setting inhibited ―

―

Note 1: 65,536 colors in one-transfer operation.

Note 2: 65,536 colors in two-transfer operation.

Reset pin. The R61509V is reset when RESETX is low. Make

sure to execute a power on reset after turning power on.

(Amplitude: IOVCC-GND)

GND /

IOVCC

GND /

IOVCC

GND /

IOVCC

GND /

IOVCC

GND /

IOVCC

Open

―

―

DB[17:0] I/O

ENABLE I

VSYNCX I

HSYNCX I

DOTCLK I

FMARK O

IM2-1,

IM0_ID

I

RESETX I

Host

processor

Host

processor

Host

processor

Host

processor

Host

processor

Host

processor

GND /

IOVCC

Host

processor

or external

RC circuit

Rev. 0.11 April 25, 2008, page 15 of 181

Page 16

R61509V Target Spec

Reset protect pin. The R61509V enters a reset protect status by

fixing PROTECT to GND level disabling hardware reset. With

this, erroneous operations caused by noise are prevented.

Low: Hardware reset is disabled (Reset protect status)

IOVCC

PROTECT I

Host

processor

High: Hardware reset is enabled. (Normal status)

Table 7 Internal Power Supply Circuit

When

not

used

―

―

―

―

―

―

Signal I/O

VDD O

VCI1 O

DDVDH O

VGH O

VGL O

VCL O

C11P,

C11M,

C12P,

I/O

C12M

C13P,

C13M,

C21P,

C21M,

I/O

C22P,

C22M

Connect

to

Stabilizing

capacitor

Stabilizing

capacitor

Stabilizing

capacitor

Stabilizing

capacitor

Stabilizing

capacitor

Stabilizing

capacitor

Step-up

capacitor

Step-up

capacitor

Function

Output from internal logic regulator. Connect to a stabilizing

capacitor.

Reference voltage for step-up circuit 1. Make sure that DDVDH,

VGH and VGL output voltages do no go exceed the ratings.

Power supply for the source driver liquid crystal drive unit and

VCOM drive. Connect to a stabilizing capacitor.

Power supply for the gate driver liquid crystal drive unit.

Connect to a stabilizing capacitor.

Power supply for the gate driver liquid crystal drive unit.

Connect to a stabilizing capacitor.

Power supply for VCOML drive. ―

Make sure to connect capacitors for internal step-up circuit 1.

Make sure to connect capacitors for internal step-up circuit 2. ―

Rev. 0.11 April 25, 2008, page 16 of 181

Page 17

R61509V Target Spec

Table 8 LCD drive

Signal I/O Connect to Function

VREG1OUT O Stabilizing

capacitor

Output voltage generated from the reference voltage VCIR. The factor

is determined by instruction (VRH bits).

VREG1OUT is used for (1) source driver grayscale reference voltage

VREG1OUT, (2) VCOMH level reference voltage, and (3) VCOM

amplitude reference voltage. Connect to a stabilizing capacitor.

VREG1OUT =4.0V ~ (DDVDH – 0.5)V

VCOM O TFT panel

common

electrode

Power supply to the TFT panel’s common electrode. VCOM alternates

between VCOMH and VCOML. The alternating cycle is set by internal

register. Also, the VCOM output can be started and halted by register

setting.

VCOMH O Stabilizing

capacitor

VCOML O Stabilizing

capacitor

VCOMR I Variable

resistor or

The High level of VCOM amplitude. The output level can be adjusted

by either external resistor (VCOMR) or electronic volume.

The Low level of VCOM amplitude. The output level can be adjusted

by instruction (VDV bits). VCOML = (VCL+0.5) V ~ 0V

Connect a variable resistor when adjusting the VCOMH level between

VREG1OUT and GND.

open

VGS I GND Reference level for the grayscale voltage generating circuit.

S1~S720 O LCD Liquid crystal application voltages. Open

G1~G432 O LCD Gate line output signals.

VGH: The gate line is selected.

VGL: The gate line is not selected.

When not in

use

―

―

―

―

Open

―

Open

Rev. 0.11 April 25, 2008, page 17 of 181

Page 18

R61509V Target Spec

Table 9 Others (test, dummy pins)

Signal I/O Connect to Function

VTEST O Open Test pin. Leave open. Open

VREFC I GND Test pin. Make sure to fix to the GND level. -

VREFD O Open Test pin. Leave open. Open

VREF O Open Test pin. Leave open. Open

VDDTEST I GND Test pin. Make sure to fix to the GND level. -

VMON O Open Test pin. Leave open. Open

VCIR O Open Test pin. Leave open. Open

GNDDUM110,

AGNDDUM1

-5,

VCCDUM,

IOVCCDUM

1-2

DUMMYR

1-4

VGLDMY

1-4

DUMMYA ― Open Dummy pad. Leave open. OPEN

DUMMYB ― Open Dummy pad. Leave open. OPEN

DUMMYC ― Open Dummy pad. Leave open. OPEN

TESTO1-15 O ― Dummy pad. Leave open. OPEN

TEST

1-5

TS0-8 O Open Test pin. Leave open. OPEN

VPP3B I AGND Test pin. Connect to AGND. ―

TSC I GND Test pin. Connect to GND.

O - Pins to fix the electrical potentials of unused interface and test pins. Open

- - DUMMYR1 and DUMMYR4, DUMMYR2 and DUMMYR3 are shortcircuited within the chip for COG contact resistance measurement.

O Unused

gate line

I GND Test pin. Connect to GND. GND

Output VGL level. Use when fixing unused gate line of the panel. Open

When not in

use

Open

GND

Patents of dummy pin, which is used to fix to VCC or GND are granted.

PATENT ISSUED:

United States Patent No. 6,924,868

United States Patent No. 6,323,930

Japanese Patent No. 3,980,066

Korean Patent No. 401,270

Taiwanese Patent No. 175,413

Rev. 0.11 April 25, 2008, page 18 of 181

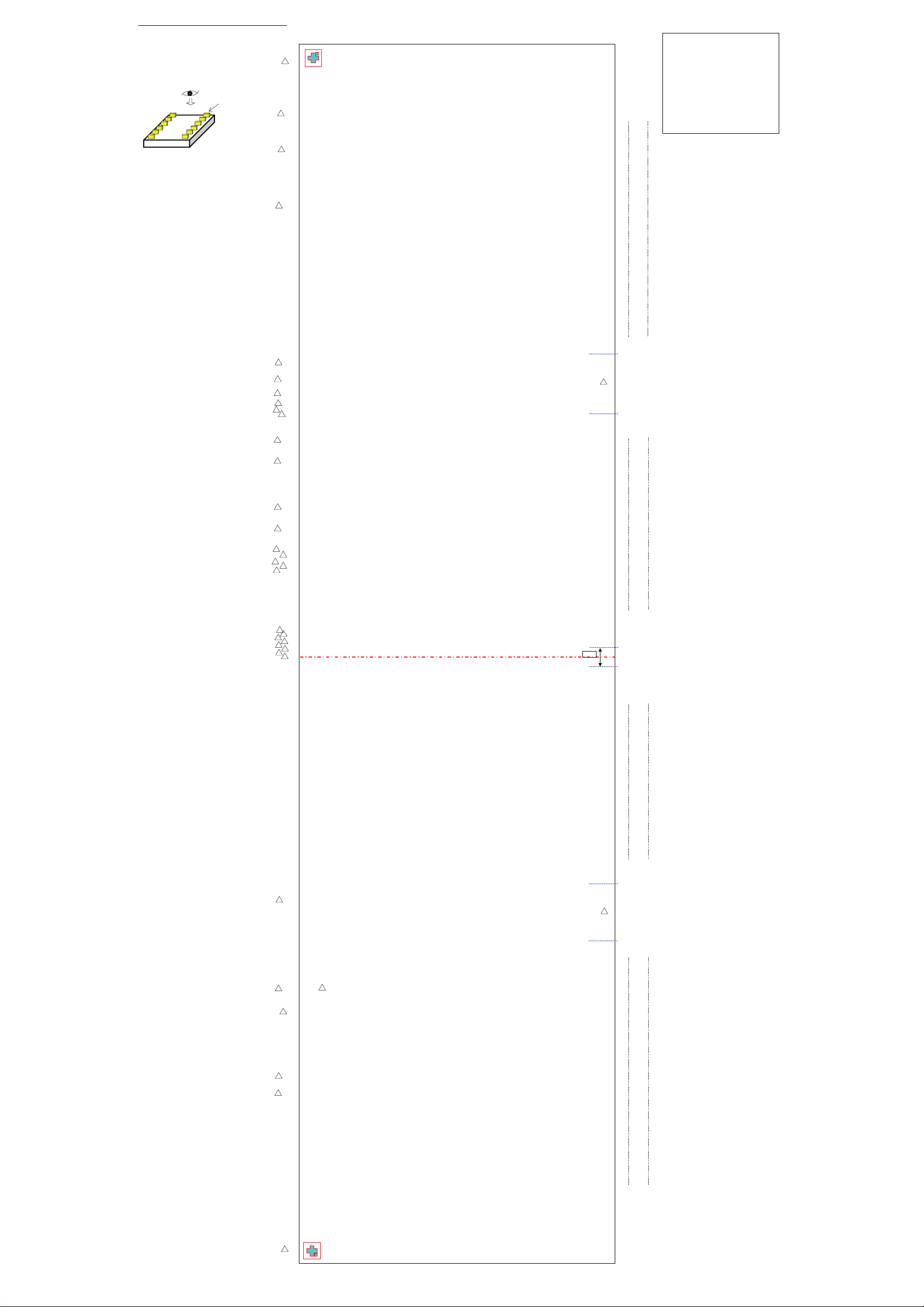

Page 19

R61509V Pad Arrangement Rev 0.6

Top View

BUMP

Chip

No □ DUMMYR4 1434

1 DUMMYR1 □ □ VGLDMY4 1431

2 DUMMYR2 □ □ G1 1430

3 AGNDDUM1 □ □ G3 1429

4 VPP3B □ □ G5 1428

5 VPP3B □ □ G7 1427

6 VPP3B □ □ G9 1426

7 VPP3B □

8 AGNDDUM2 □

9 VPP3A □

10 VPP3A □

11 VPP1 □

12 VPP1 □

13 VPP1 □

14 VPP1 □

15 VPP1 □

16 VPP1 □

17 VPP1 □

18 GNDDUM1 □

19 VDDTEST □ Connect to GNDDUM1

20 VREFC □ Connect to GNDDUM1

21 VREFD □ Open

22 VREF □ Open

23 VCCDUM1 □

24 DUMMYA □ Open

25 DUMMYA □ Open

5

26 DUMMYA □ Open

27 DUMMYA □ Open

28 DUMMYA □ Open

29 GNDDUM2 □

30 AGND □

31 AGND □

32 AGND □

33 AGND □

34 AGND □

35 AGND □

36 GND □

37 GND □

38 GND □

39 GND □

40 GND □

41 VCC □

42 VCC □

43 VCC □

44 VCC □

45 VCC □

46 VCC □

47 VCC □

48 TS8 □ Open

49 TS7 □ Open

50 TS6 □ Open

51 TS5 □ Open

52 TS4 □ Open

53 TS3 □ Open

54 TS2 □ Open

55 TS1 □ Open

56 TS0 □ Open

57 TEST5 □ Connect to GNDDUM3 □ G427 1217

58 TEST4 □ Connect to GNDDUM3 □ G429 1216

59 TEST3 □ Connect to GNDDUM3 □ G431 1215

60 TEST2 □ Connect to GNDDUM3 □ VGLDMY3 1214

61 TEST1 □ Connect to GNDDUM3

62 GNDDUM3 □

5

63 TSC □ Connect to GNDDUM3

64 IM2 □ Connect to IOVCCDUM1/GNDDUM3

65 IM1 □

8

66 IM0_ID □ Connect to IOVCCDUM1/GNDDUM3

67 IOVCCDUM1 □ No PAD

68 PROTECT □

8

69 RESETX □

70 GNDDUM4 □

71 DUMMYB □ Open

5

72 DUMMYB □ Open

8

73 VSYNCX □

74 HSYNCX □ □ TESTO14 1213

75 IOVCCDUM2 □ □ S1 1212

76 ENABLE □ □ S2 1211

77 DOTCLK □ □ S3 1210

78 DB17 □ □ S4 1209

79 DB16 □ □ S5 1208

80 GNDDUM5 □

5

81 DB15 □

82 DB14 □

83 DB13 □

84 DB12 □

85 GNDDUM6 □

5

86 DB11 □

87 DB10 □

88 DB9 □

89 IOVCC □

90 IOVCC □

91 IOVCC □

92 IOVCC □

93 IOVCC □

94 IOVCC □

95 DB8 □

5

96 GNDDUM7 □

97 DB7 □

98 DB6 □

99 DB5 □

100 DB4 □

101 GNDDUM8 □

5

102 DB3 □

103 DB2 □

104 DB1 □

105 DB0 □

5

106 GNDDUM9 □

107 CSX □

108 RS □

8

109 WRX_SCL □

110 RDX □

5

111 GNDDUM10 □

112 FMARK □

113 SDI □

114 SDO □

115 VDD □

116 VDD □

117 VDD □

118 VDD □

119 VDD □

120 VDD □

121 VDD □ □ S356 857

122 VDD □ □ S357 856

123 VDD □ □ S358 855

124 VMON □ Open □ S359 854

125 VCOM □ □ S360 853

126 VCOM □ □ TESTO13 852

1

127 VCOM □ □ TESTO12 851

128 VCOM □ □ TESTO11 850

129 VCOM □ □ TESTO10 849

130 VCOM □

1

131 VCOM □

132 VCOM □

133 VCOMH □

134 VCOMH □ □ TESTO9 848

135 VCOMH □ □ TESTO8 847

136 VCOMH □ □ TESTO7 846

137 VCOMH □ □ TESTO6 845

138 VCOMH □ □ S361 844

139 VCOML □ □ S362 843

140 VCOML □ □ S363 842

141 VCOML □ □ S364 841

142 VCOML □ □ S365 840

143 VCOML □

144 VCOML □

145 GND □

146 GND □

147 GND □

148 GND □

149 GND □

150 GND □

151 GND □

152 GND □

153 GND □

154 VGS □

155 AGND □

156 AGND □

157 AGND □

158 AGND □

159 AGND □

160 AGND □

161 AGND □

162 AGND □

163 AGND □

164 VTEST □ Open

165 VCIR □ Open

166 VREG1OUT □

167 VCOMR □

168 C11M □

169 C11M □

170 C11M □

171 C11M □

172 C11M □

173 C11P □

174 C11P □

175 C11P □

176 C11P □

177 C11P □

178 C12M □

179 C12M □

180 C12M □ □ S716 489

181 C12M □ □ S717 488

182 C12M □ □ S718 487

183 C12P □ □ S719 486

184 C12P □ □ S720 485

185 C12P □ □ TESTO5 484

186 C12P □

187 C12P □

188 DDVDH □

189 DDVDH □

190 DDVDH □

191 DDVDH □

192 DDVDH □ No PAD

193 DDVDH □

194 DDVDH □

195 DDVDH □

196 DDVDH □

197 VCI1 □

198 VCI1 □

199 VCI1 □ □ VGLDMY2 483

200 VCI1 □ □ G432 482

201 VCI □ □ G430 481

202 VCI □ □ G428 480

203 VCI □

204 VCI □

205 VCI □

206 VCI □

207 VCILVL □

208 DUMMYC □ Open

209 DUMMYC □ Open

210 DUMMYC □ Open

5

211 DUMMYC □ Open

212 DUMMYC □ Open

213 GND □

214 GND □

215 GND □

216 GND □

217 GND □

218 AGND □

219 AGND □

220 AGND □

221 AGND □

222 AGND □

223 VGL □

224 VGL □

225 VGL □

226 VGL □

227 VGL □

228 VGL □

229 VGL □

230 VGL □

5

231 VGL □

232 AGNDDUM3 □

233 AGNDDUM4 □

234 VGH □

5

235 VGH □

236 VGH □

237 VGH □

238 VGH □

239 VGH □

240 AGNDDUM5 □

241 VCL □

242 VCL □

243 VCL □

244 C13M □

245 C13M □

246 C13M □

247 C13P □

248 C13P □

249 C13P □

250 C21M □

251 C21M □

252 C21M □

253 C21P □

254 C21P □

255 C21P □

256 C22M □

257 C22M □ □ G10 271

258 C22M □ □ G8 270

259 C22P □ □ G6 269

260 C22P □ □ G4 268

261 C22P □ □ G2 267

262 TESTO1 □ □ VGLDMY1 266

(1-a)

7

4

4

8

8

8

1

1

1

1

1

1

5

3

Connect to IOVCCDUM1/GNDDUM3

6

□ DUMMYR3 1433

1

840um

1

□ TESTO4 265

□ TESTO2 263

□ TESTO15 1432

□ TESTO3 264

Rev0.00 2007.12.13 First virsion

Rev0.10 2007.12.27 R61517's VCOMA, VCOMB --> R61509V's VCOM

Rev0.20 2008.02.13 Rev Mark 1 PAD No. 24~28, 71, 72, 208-217 changed to NC1-NC17

Rev0.21 2008.02.14 Rev Mark 2 NC's application voltage decided.

Rev0.30 2008.02.19 Rev Mark 4 VPP3C-->VPP3B, VPP2-->VPP1

Rev0.31 2008.02.27 Rev Mark 5 NC1-5-->DUMMYA

NC6-7-->DUMMYB

NC8-12-->DUMMYC

GNDDUM5-->GNDDUM2

GNDDUM6-->GNDDUM3

GNDDUM7-->GNDDUM4

GNDDUM8-->GNDDUM5

GNDDUM9-->GNDDUM6

No

GNDDUM10-->GNDDUM7

VLOUT1-->DDVDH

VLOUT2-->VGH

VLOUT3-->VGL

Rev0.4 2008.03.14 Rev Mark 6 DUMMYC's description "Open" added.

Rev0.5 2008.04.02 Rev Mark 7 Alignment mark (1-a) (1-b) added.

Rev0.6 2008.04.21 Rev Mark 8 Pin names changed.

Pad No66 IM0/ID→IM0_ID

Pad No69 RESET→RESETX

Pad No73 VSYNC→VSYNCX

Pad No74 HSYNC→HSYNCX

Pad No107 CS→CSX

Pad No109 WR/SCL→WRX_SCL

Pad No110 RD→RDX

7

(1-b)

Page 20

R61509V Target Spec

Y

Y

●Chip size: 19.03mm x 0.76mm

●Chip thickness: 280μm (typ)

●Pad coordinates: Pad center

●Coordinate origin: Chip center

●Au bump size

1. 50μm x 90μm (I/O side: No.1-262)

2. 15μm x 100μm (LCD output side: No.263-1434)

●Au bump pitch: See pad coordinate

●Au bump height:12μm

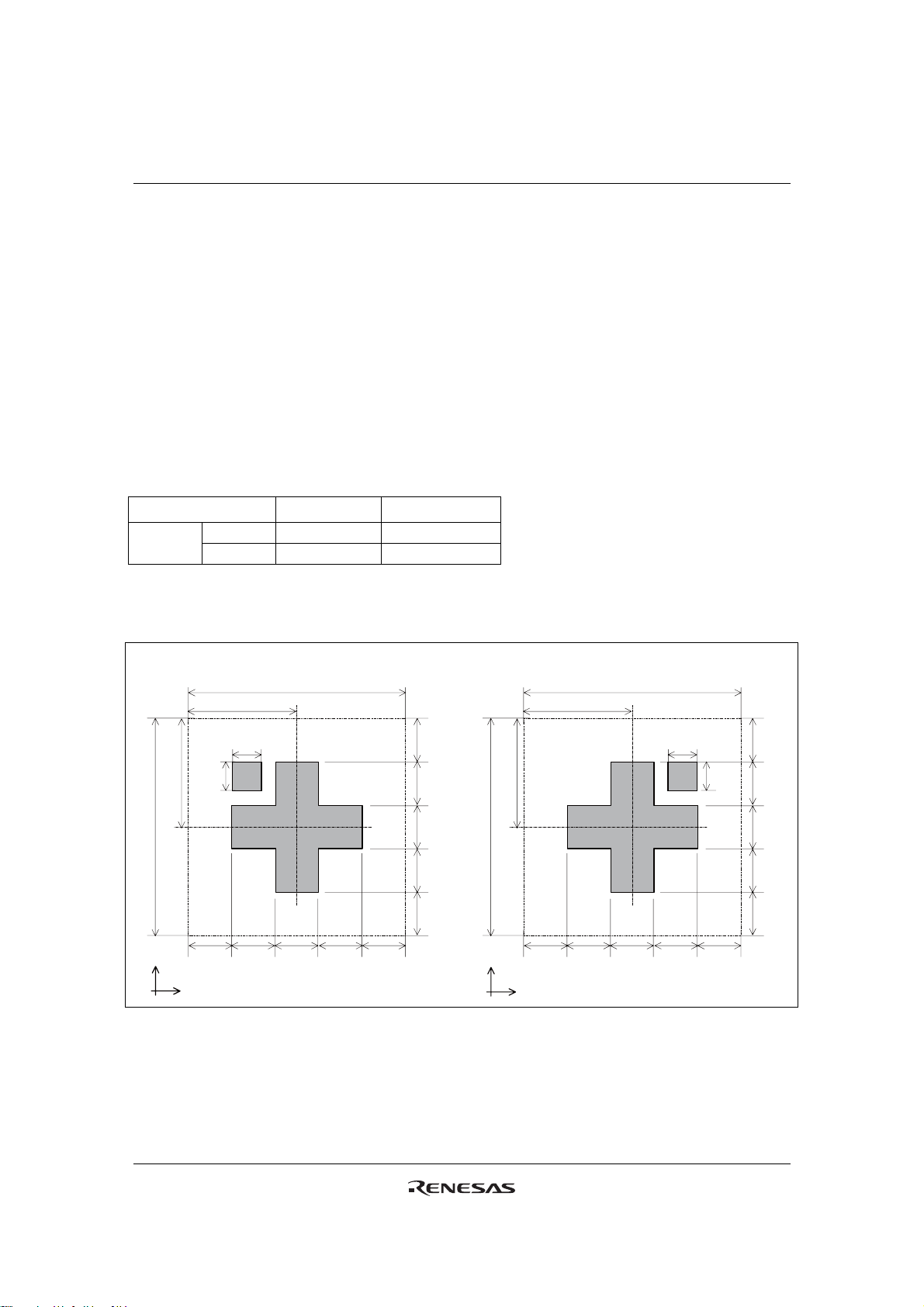

● Alignment mark

Table 10

Alignment marks X-axis Y-axis

Type A

(1-a) -9381.0 -251.0

(1-b) 9381.0 -251.0

-size

150um : Alignment Mark Area

Y

1-a: ( Left Alignment Mark )

150um : Alignment Mark Area X-size

75um

20um

20um

㩷

75um

㩷

㩷

30um 30um 30um 30um 30um

㩷

X

㩷

Alignment

Mark Area

30um

30um

30um

30um

30um

Figure 2

-size

150um : Alignment Mark Area

Y

1-b: ( Right Alignment Mark )

150um : Alignment Mark Area X-size

75um

Alignment

Mark Area

75um

30um 30um 30um 30um 30um

X

20um

20um

30um

30um

30um

30um

30um

Rev. 0.11 April 25, 2008, page 20 of 181

Page 21

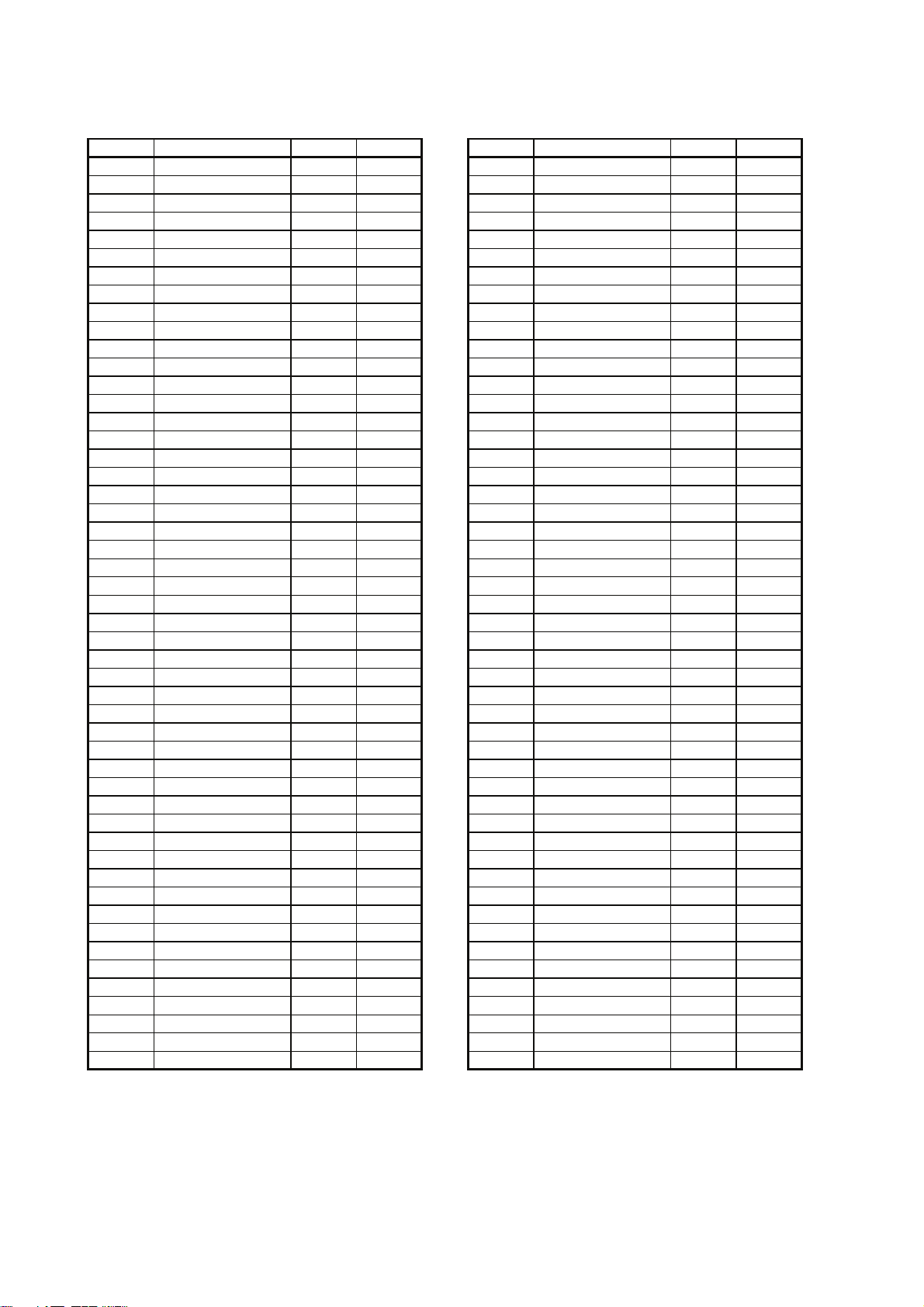

R61509V Pad Coordinate (Unit:μm)

pad No pad name X Y pad No pad name X Y

1 DUMMYR1 -9135.0 -269.0 51 TS5 -5635.0 -269.0

2 DUMMYR2 -9065.0 -269.0 52 TS4 -5565.0 -269.0

3 AGNDDUM1 -8995.0 -269.0 53 TS3 -5495.0 -269.0

4 VPP3B -8925.0 -269.0 54 TS2 -5425.0 -269.0

5 VPP3B -8855.0 -269.0 55 TS1 -5355.0 -269.0

6 VPP3B -8785.0 -269.0 56 TS0 -5285.0 -269.0

7 VPP3B -8715.0 -269.0 57 TEST5 -5215.0 -269.0

8 AGNDDUM2 -8645.0 -269.0 58 TEST4 -5145.0 -269.0

9 VPP3A -8575.0 -269.0 59 TEST3 -5075.0 -269.0

10 VPP3A -8505.0 -269.0 60 TEST2 -5005.0 -269.0

11 VPP1 -8435.0 -269.0 61 TEST1 -4935.0 -269.0

12 VPP1 -8365.0 -269.0 62 GNDDUM3 -4865.0 -269.0

13 VPP1 -8295.0 -269.0 63 TSC -4795.0 -269.0

14 VPP1 -8225.0 -269.0 64 IM2 -4725.0 -269.0

15 VPP1 -8155.0 -269.0 65 IM1 -4655.0 -269.0

16 VPP1 -8085.0 -269.0 66 IM0_ID -4585.0 -269.0

17 VPP1 -8015.0 -269.0 67 IOVCCDUM1 -4515.0 -269.0

18 GNDDUM1 -7945.0 -269.0 68 PROTECT -4445.0 -269.0

19 VDDTEST -7875.0 -269.0 69 RESETX -4375.0 -269.0

20 VREFC -7805.0 -269.0 70 GNDDUM4 -4305.0 -269.0

21 VREFD -7735.0 -269.0 71 DUMMYB -4235.0 -269.0

22 VREF -7665.0 -269.0 72 DUMMYB -4165.0 -269.0

23 VCCDUM1 -7595.0 -269.0 73 VSYNCX -4095.0 -269.0

24 DUMMYA -7525.0 -269.0 74 HSYNCX -4025.0 -269.0

25 DUMMYA -7455.0 -269.0 75 IOVCCDUM2 -3955.0 -269.0

26 DUMMYA -7385.0 -269.0 76 ENABLE -3885.0 -269.0

27 DUMMYA -7315.0 -269.0 77 DOTCLK -3815.0 -269.0

28 DUMMYA -7245.0 -269.0 78 DB17 -3745.0 -269.0

29 GNDDUM2 -7175.0 -269.0 79 DB16 -3675.0 -269.0

30 AGND -7105.0 -269.0 80 GNDDUM5 -3605.0 -269.0

31 AGND -7035.0 -269.0 81 DB15 -3535.0 -269.0

32 AGND -6965.0 -269.0 82 DB14 -3465.0 -269.0

33 AGND -6895.0 -269.0 83 DB13 -3395.0 -269.0

34 AGND -6825.0 -269.0 84 DB12 -3325.0 -269.0

35 AGND -6755.0 -269.0 85 GNDDUM6 -3255.0 -269.0

36 GND -6685.0 -269.0 86 DB11 -3185.0 -269.0

37 GND -6615.0 -269.0 87 DB10 -3115.0 -269.0

38 GND -6545.0 -269.0 88 DB9 -3045.0 -269.0

39 GND -6475.0 -269.0 89 IOVCC -2975.0 -269.0

40 GND -6405.0 -269.0 90 IOVCC -2905.0 -269.0

41 VCC -6335.0 -269.0 91 IOVCC -2835.0 -269.0

42 VCC -6265.0 -269.0 92 IOVCC -2765.0 -269.0

43 VCC -6195.0 -269.0 93 IOVCC -2695.0 -269.0

44 VCC -6125.0 -269.0 94 IOVCC -2625.0 -269.0

45 VCC -6055.0 -269.0 95 DB8 -2555.0 -269.0

46 VCC -5985.0 -269.0 96 GNDDUM7 -2485.0 -269.0

47 VCC -5915.0 -269.0 97 DB7 -2415.0 -269.0

48 TS8 -5845.0 -269.0 98 DB6 -2345.0 -269.0

49 TS7 -5775.0 -269.0 99 DB5 -2275.0 -269.0

50 TS6 -5705.0 -269.0 100 DB4 -2205.0 -269.0

2008.04.21 rev0.1

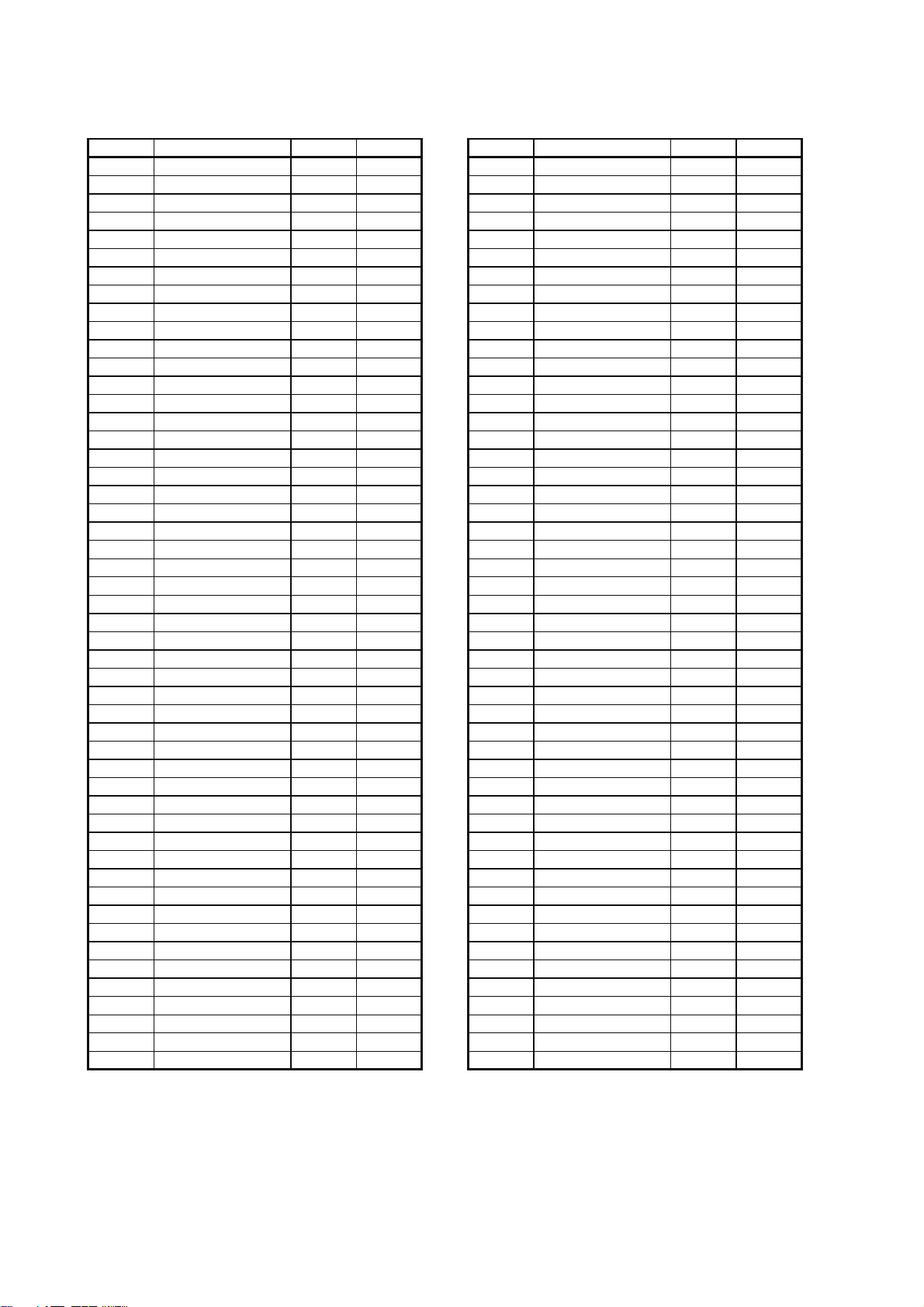

Page 22

R61509V Pad Coordinate (Unit:μm)

pad No pad name X Y pad No pad name X Y

101 GNDDUM8 -2135.0 -269.0 151 GND 1365.0 -269.0

102 DB3 -2065.0 -269.0 152 GND 1435.0 -269.0

103 DB2 -1995.0 -269.0 153 GND 1505.0 -269.0

104 DB1 -1925.0 -269.0 154 VGS 1575.0 -269.0

105 DB0 -1855.0 -269.0 155 AGND 1645.0 -269.0

106 GNDDUM9 -1785.0 -269.0 156 AGND 1715.0 -269.0

107 CSX -1715.0 -269.0 157 AGND 1785.0 -269.0

108 RS -1645.0 -269.0 158 AGND 1855.0 -269.0

109 WRX_SCL -1575.0 -269.0 159 AGND 1925.0 -269.0

110 RDX -1505.0 -269.0 160 AGND 1995.0 -269.0

111 GNDDUM10 -1435.0 -269.0 161 AGND 2065.0 -269.0

112 FMARK -1365.0 -269.0 162 AGND 2135.0 -269.0

113 SDI -1295.0 -269.0 163 AGND 2205.0 -269.0

114 SDO -1225.0 -269.0 164 VTEST 2275.0 -269.0

115 VDD -1155.0 -269.0 165 VCIR 2345.0 -269.0

116 VDD -1085.0 -269.0 166 VREG1OUT 2415.0 -269.0

117 VDD -1015.0 -269.0 167 VCOMR 2485.0 -269.0

118 VDD -945.0 -269.0 168 C11M 2555.0 -269.0

119 VDD -875.0 -269.0 169 C11M 2625.0 -269.0

120 VDD -805.0 -269.0 170 C11M 2695.0 -269.0

121 VDD -735.0 -269.0 171 C11M 2765.0 -269.0

122 VDD -665.0 -269.0 172 C11M 2835.0 -269.0

123 VDD -595.0 -269.0 173 C11P 2905.0 -269.0

124 VMON -525.0 -269.0 174 C11P 2975.0 -269.0

125 VCOM -455.0 -269.0 175 C11P 3045.0 -269.0

126 VCOM -385.0 -269.0 176 C11P 3115.0 -269.0

127 VCOM -315.0 -269.0 177 C11P 3185.0 -269.0

128 VCOM -245.0 -269.0 178 C12M 3255.0 -269.0

129 VCOM -175.0 -269.0 179 C12M 3325.0 -269.0

130 VCOM -105.0 -269.0 180 C12M 3395.0 -269.0

131 VCOM -35.0 -269.0 181 C12M 3465.0 -269.0

132 VCOM 35.0 -269.0 182 C12M 3535.0 -269.0

133 VCOMH 105.0 -269.0 183 C12P 3605.0 -269.0

134 VCOMH 175.0 -269.0 184 C12P 3675.0 -269.0

135 VCOMH 245.0 -269.0 185 C12P 3745.0 -269.0

136 VCOMH 315.0 -269.0 186 C12P 3815.0 -269.0

137 VCOMH 385.0 -269.0 187 C12P 3885.0 -269.0

138 VCOMH 455.0 -269.0 188 DDVDH 3955.0 -269.0

139 VCOML 525.0 -269.0 189 DDVDH 4025.0 -269.0

140 VCOML 595.0 -269.0 190 DDVDH 4095.0 -269.0

141 VCOML 665.0 -269.0 191 DDVDH 4165.0 -269.0

142 VCOML 735.0 -269.0 192 DDVDH 4235.0 -269.0

143 VCOML 805.0 -269.0 193 DDVDH 4305.0 -269.0

144 VCOML 875.0 -269.0 194 DDVDH 4375.0 -269.0

145 GND 945.0 -269.0 195 DDVDH 4445.0 -269.0

146 GND 1015.0 -269.0 196 DDVDH 4515.0 -269.0

147 GND 1085.0 -269.0 197 VCI1 4585.0 -269.0

148 GND 1155.0 -269.0 198 VCI1 4655.0 -269.0

149 GND 1225.0 -269.0 199 VCI1 4725.0 -269.0

150 GND 1295.0 -269.0 200 VCI1 4795.0 -269.0

2008.04.21 rev0.1

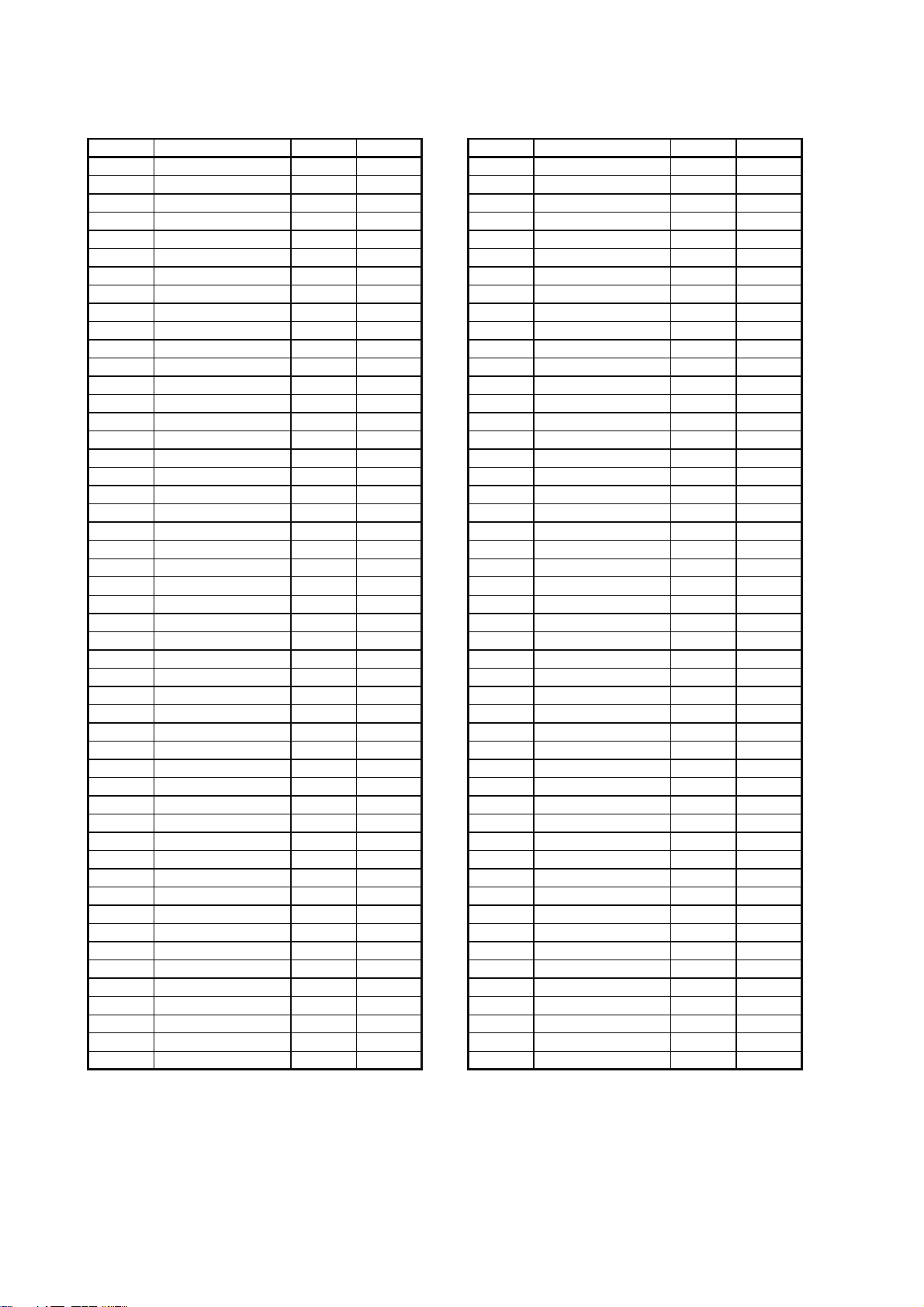

Page 23

R61509V Pad Coordinate (Unit:μm)

pad No pad name X Y pad No pad name X Y

201 VCI 4865.0 -269.0 251 C21M 8365.0 -269.0

202 VCI 4935.0 -269.0 252 C21M 8435.0 -269.0

203 VCI 5005.0 -269.0 253 C21P 8505.0 -269.0

204 VCI 5075.0 -269.0 254 C21P 8575.0 -269.0

205 VCI 5145.0 -269.0 255 C21P 8645.0 -269.0

206 VCI 5215.0 -269.0 256 C22M 8715.0 -269.0

207 VCILVL 5285.0 -269.0 257 C22M 8785.0 -269.0

208 DUMMYC 5355.0 -269.0 258 C22M 8855.0 -269.0

209 DUMMYC 5425.0 -269.0 259 C22P 8925.0 -269.0

210 DUMMYC 5495.0 -269.0 260 C22P 8995.0 -269.0

211 DUMMYC 5565.0 -269.0 261 C22P 9065.0 -269.0

212 DUMMYC 5635.0 -269.0 262 TESTO1 9135.0 -269.0

213 GND 5705.0 -269.0 263 TESTO2 9397.5 157.0

214 GND 5775.0 -269.0 264 TESTO3 9382.5 276.0

215 GND 5845.0 -269.0 265 TESTO4 9367.5 157.0

216 GND 5915.0 -269.0 266 VGLDMY1 9352.5 276.0

217 GND 5985.0 -269.0 267 G2 9337.5 157.0

218 AGND 6055.0 -269.0 268 G4 9322.5 276.0

219 AGND 6125.0 -269.0 269 G6 9307.5 157.0

220 AGND 6195.0 -269.0 270 G8 9292.5 276.0

221 AGND 6265.0 -269.0 271 G10 9277.5 157.0

222 AGND 6335.0 -269.0 272 G12 9262.5 276.0

223 VGL 6405.0 -269.0 273 G14 9247.5 157.0

224 VGL 6475.0 -269.0 274 G16 9232.5 276.0

225 VGL 6545.0 -269.0 275 G18 9217.5 157.0

226 VGL 6615.0 -269.0 276 G20 9202.5 276.0

227 VGL 6685.0 -269.0 277 G22 9187.5 157.0

228 VGL 6755.0 -269.0 278 G24 9172.5 276.0

229 VGL 6825.0 -269.0 279 G26 9157.5 157.0

230 VGL 6895.0 -269.0 280 G28 9142.5 276.0

231 VGL 6965.0 -269.0 281 G30 9127.5 157.0

232 AGNDDUM3 7035.0 -269.0 282 G32 9112.5 276.0

233 AGNDDUM4 7105.0 -269.0 283 G34 9097.5 157.0

234 VGH 7175.0 -269.0 284 G36 9082.5 276.0

235 VGH 7245.0 -269.0 285 G38 9067.5 157.0

236 VGH 7315.0 -269.0 286 G40 9052.5 276.0

237 VGH 7385.0 -269.0 287 G42 9037.5 157.0

238 VGH 7455.0 -269.0 288 G44 9022.5 276.0

239 VGH 7525.0 -269.0 289 G46 9007.5 157.0

240 AGNDDUM5 7595.0 -269.0 290 G48 8992.5 276.0

241 VCL 7665.0 -269.0 291 G50 8977.5 157.0

242 VCL 7735.0 -269.0 292 G52 8962.5 276.0

243 VCL 7805.0 -269.0 293 G54 8947.5 157.0

244 C13M 7875.0 -269.0 294 G56 8932.5 276.0

245 C13M 7945.0 -269.0 295 G58 8917.5 157.0

246 C13M 8015.0 -269.0 296 G60 8902.5 276.0

247 C13P 8085.0 -269.0 297 G62 8887.5 157.0

248 C13P 8155.0 -269.0 298 G64 8872.5 276.0

249 C13P 8225.0 -269.0 299 G66 8857.5 157.0

250 C21M 8295.0 -269.0 300 G68 8842.5 276.0

2008.04.21 rev0.1

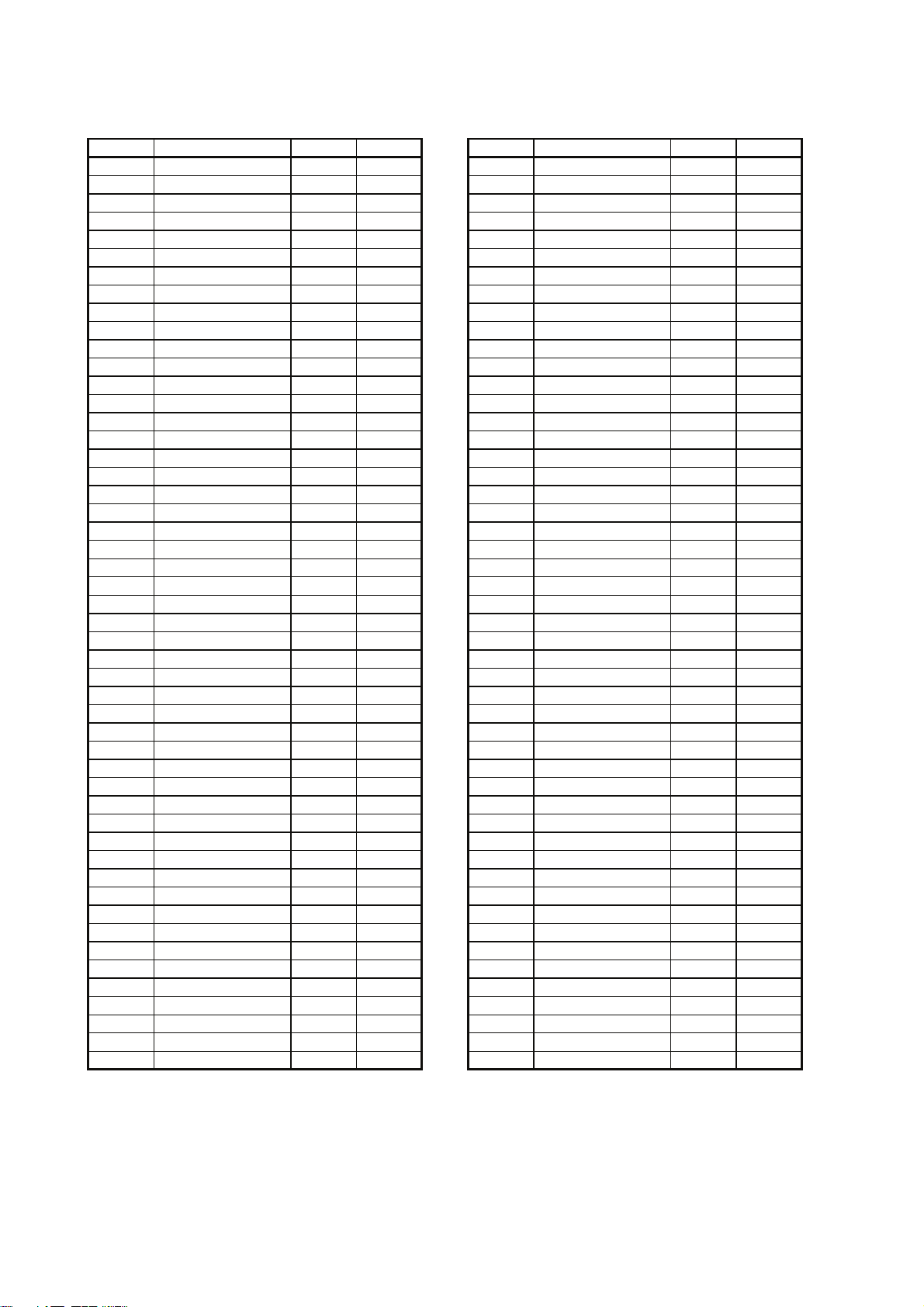

Page 24

R61509V Pad Coordinate (Unit:μm)

pad No pad name X Y pad No pad name X Y

301 G70 8827.5 157.0 351 G170 8077.5 157.0

302 G72 8812.5 276.0 352 G172 8062.5 276.0

303 G74 8797.5 157.0 353 G174 8047.5 157.0

304 G76 8782.5 276.0 354 G176 8032.5 276.0

305 G78 8767.5 157.0 355 G178 8017.5 157.0

306 G80 8752.5 276.0 356 G180 8002.5 276.0

307 G82 8737.5 157.0 357 G182 7987.5 157.0

308 G84 8722.5 276.0 358 G184 7972.5 276.0

309 G86 8707.5 157.0 359 G186 7957.5 157.0

310 G88 8692.5 276.0 360 G188 7942.5 276.0

311 G90 8677.5 157.0 361 G190 7927.5 157.0

312 G92 8662.5 276.0 362 G192 7912.5 276.0

313 G94 8647.5 157.0 363 G194 7897.5 157.0

314 G96 8632.5 276.0 364 G196 7882.5 276.0

315 G98 8617.5 157.0 365 G198 7867.5 157.0

316 G100 8602.5 276.0 366 G200 7852.5 276.0

317 G102 8587.5 157.0 367 G202 7837.5 157.0

318 G104 8572.5 276.0 368 G204 7822.5 276.0

319 G106 8557.5 157.0 369 G206 7807.5 157.0

320 G108 8542.5 276.0 370 G208 7792.5 276.0

321 G110 8527.5 157.0 371 G210 7777.5 157.0

322 G112 8512.5 276.0 372 G212 7762.5 276.0

323 G114 8497.5 157.0 373 G214 7747.5 157.0

324 G116 8482.5 276.0 374 G216 7732.5 276.0

325 G118 8467.5 157.0 375 G218 7717.5 157.0

326 G120 8452.5 276.0 376 G220 7702.5 276.0

327 G122 8437.5 157.0 377 G222 7687.5 157.0

328 G124 8422.5 276.0 378 G224 7672.5 276.0

329 G126 8407.5 157.0 379 G226 7657.5 157.0

330 G128 8392.5 276.0 380 G228 7642.5 276.0

331 G130 8377.5 157.0 381 G230 7627.5 157.0

332 G132 8362.5 276.0 382 G232 7612.5 276.0

333 G134 8347.5 157.0 383 G234 7597.5 157.0

334 G136 8332.5 276.0 384 G236 7582.5 276.0

335 G138 8317.5 157.0 385 G238 7567.5 157.0

336 G140 8302.5 276.0 386 G240 7552.5 276.0

337 G142 8287.5 157.0 387 G242 7537.5 157.0

338 G144 8272.5 276.0 388 G244 7522.5 276.0

339 G146 8257.5 157.0 389 G246 7507.5 157.0

340 G148 8242.5 276.0 390 G248 7492.5 276.0

341 G150 8227.5 157.0 391 G250 7477.5 157.0

342 G152 8212.5 276.0 392 G252 7462.5 276.0

343 G154 8197.5 157.0 393 G254 7447.5 157.0

344 G156 8182.5 276.0 394 G256 7432.5 276.0

345 G158 8167.5 157.0 395 G258 7417.5 157.0

346 G160 8152.5 276.0 396 G260 7402.5 276.0

347 G162 8137.5 157.0 397 G262 7387.5 157.0

348 G164 8122.5 276.0 398 G264 7372.5 276.0

349 G166 8107.5 157.0 399 G266 7357.5 157.0

350 G168 8092.5 276.0 400 G268 7342.5 276.0

2008.04.21 rev0.1

Page 25

R61509V Pad Coordinate (Unit:μm)

pad No pad name X Y pad No pad name X Y

401 G270 7327.5 157.0 451 G370 6577.5 157.0

402 G272 7312.5 276.0 452 G372 6562.5 276.0

403 G274 7297.5 157.0 453 G374 6547.5 157.0

404 G276 7282.5 276.0 454 G376 6532.5 276.0

405 G278 7267.5 157.0 455 G378 6517.5 157.0

406 G280 7252.5 276.0 456 G380 6502.5 276.0

407 G282 7237.5 157.0 457 G382 6487.5 157.0

408 G284 7222.5 276.0 458 G384 6472.5 276.0

409 G286 7207.5 157.0 459 G386 6457.5 157.0

410 G288 7192.5 276.0 460 G388 6442.5 276.0

411 G290 7177.5 157.0 461 G390 6427.5 157.0

412 G292 7162.5 276.0 462 G392 6412.5 276.0

413 G294 7147.5 157.0 463 G394 6397.5 157.0

414 G296 7132.5 276.0 464 G396 6382.5 276.0

415 G298 7117.5 157.0 465 G398 6367.5 157.0

416 G300 7102.5 276.0 466 G400 6352.5 276.0

417 G302 7087.5 157.0 467 G402 6337.5 157.0

418 G304 7072.5 276.0 468 G404 6322.5 276.0

419 G306 7057.5 157.0 469 G406 6307.5 157.0

420 G308 7042.5 276.0 470 G408 6292.5 276.0

421 G310 7027.5 157.0 471 G410 6277.5 157.0

422 G312 7012.5 276.0 472 G412 6262.5 276.0

423 G314 6997.5 157.0 473 G414 6247.5 157.0

424 G316 6982.5 276.0 474 G416 6232.5 276.0

425 G318 6967.5 157.0 475 G418 6217.5 157.0

426 G320 6952.5 276.0 476 G420 6202.5 276.0

427 G322 6937.5 157.0 477 G422 6187.5 157.0

428 G324 6922.5 276.0 478 G424 6172.5 276.0

429 G326 6907.5 157.0 479 G426 6157.5 157.0

430 G328 6892.5 276.0 480 G428 6142.5 276.0

431 G330 6877.5 157.0 481 G430 6127.5 157.0

432 G332 6862.5 276.0 482 G432 6112.5 276.0

433 G334 6847.5 157.0 483 VGLDMY2 6097.5 157.0

434 G336 6832.5 276.0 484 TESTO5 5887.5 157.0

435 G338 6817.5 157.0 485 S720 5872.5 276.0

436 G340 6802.5 276.0 486 S719 5857.5 157.0

437 G342 6787.5 157.0 487 S718 5842.5 276.0

438 G344 6772.5 276.0 488 S717 5827.5 157.0

439 G346 6757.5 157.0 489 S716 5812.5 276.0

440 G348 6742.5 276.0 490 S715 5797.5 157.0

441 G350 6727.5 157.0 491 S714 5782.5 276.0

442 G352 6712.5 276.0 492 S713 5767.5 157.0

443 G354 6697.5 157.0 493 S712 5752.5 276.0

444 G356 6682.5 276.0 494 S711 5737.5 157.0

445 G358 6667.5 157.0 495 S710 5722.5 276.0

446 G360 6652.5 276.0 496 S709 5707.5 157.0

447 G362 6637.5 157.0 497 S708 5692.5 276.0

448 G364 6622.5 276.0 498 S707 5677.5 157.0

449 G366 6607.5 157.0 499 S706 5662.5 276.0

450 G368 6592.5 276.0 500 S705 5647.5 157.0

2008.04.21 rev0.1

Page 26

R61509V Pad Coordinate (Unit:μm)

pad No pad name X Y pad No pad name X Y

501 S704 5632.5 276.0 551 S654 4882.5 276.0

502 S703 5617.5 157.0 552 S653 4867.5 157.0

503 S702 5602.5 276.0 553 S652 4852.5 276.0

504 S701 5587.5 157.0 554 S651 4837.5 157.0

505 S700 5572.5 276.0 555 S650 4822.5 276.0

506 S699 5557.5 157.0 556 S649 4807.5 157.0

507 S698 5542.5 276.0 557 S648 4792.5 276.0

508 S697 5527.5 157.0 558 S647 4777.5 157.0

509 S696 5512.5 276.0 559 S646 4762.5 276.0

510 S695 5497.5 157.0 560 S645 4747.5 157.0

511 S694 5482.5 276.0 561 S644 4732.5 276.0

512 S693 5467.5 157.0 562 S643 4717.5 157.0

513 S692 5452.5 276.0 563 S642 4702.5 276.0

514 S691 5437.5 157.0 564 S641 4687.5 157.0

515 S690 5422.5 276.0 565 S640 4672.5 276.0

516 S689 5407.5 157.0 566 S639 4657.5 157.0

517 S688 5392.5 276.0 567 S638 4642.5 276.0

518 S687 5377.5 157.0 568 S637 4627.5 157.0

519 S686 5362.5 276.0 569 S636 4612.5 276.0

520 S685 5347.5 157.0 570 S635 4597.5 157.0

521 S684 5332.5 276.0 571 S634 4582.5 276.0

522 S683 5317.5 157.0 572 S633 4567.5 157.0

523 S682 5302.5 276.0 573 S632 4552.5 276.0

524 S681 5287.5 157.0 574 S631 4537.5 157.0

525 S680 5272.5 276.0 575 S630 4522.5 276.0

526 S679 5257.5 157.0 576 S629 4507.5 157.0

527 S678 5242.5 276.0 577 S628 4492.5 276.0

528 S677 5227.5 157.0 578 S627 4477.5 157.0

529 S676 5212.5 276.0 579 S626 4462.5 276.0

530 S675 5197.5 157.0 580 S625 4447.5 157.0

531 S674 5182.5 276.0 581 S624 4432.5 276.0

532 S673 5167.5 157.0 582 S623 4417.5 157.0

533 S672 5152.5 276.0 583 S622 4402.5 276.0

534 S671 5137.5 157.0 584 S621 4387.5 157.0

535 S670 5122.5 276.0 585 S620 4372.5 276.0

536 S669 5107.5 157.0 586 S619 4357.5 157.0

537 S668 5092.5 276.0 587 S618 4342.5 276.0

538 S667 5077.5 157.0 588 S617 4327.5 157.0

539 S666 5062.5 276.0 589 S616 4312.5 276.0

540 S665 5047.5 157.0 590 S615 4297.5 157.0

541 S664 5032.5 276.0 591 S614 4282.5 276.0

542 S663 5017.5 157.0 592 S613 4267.5 157.0

543 S662 5002.5 276.0 593 S612 4252.5 276.0

544 S661 4987.5 157.0 594 S611 4237.5 157.0

545 S660 4972.5 276.0 595 S610 4222.5 276.0

546 S659 4957.5 157.0 596 S609 4207.5 157.0

547 S658 4942.5 276.0 597 S608 4192.5 276.0

548 S657 4927.5 157.0 598 S607 4177.5 157.0