RTL8187B-GR

WIRELESS LAN NETWORK INTERFACE

CONTROLLER

DATASHEET

Rev. 1.0

09 October 2006

Track ID: JATR-1076-21

Realtek Semiconductor Corp.

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

Tel.: +886-3-578-0211. Fax: +886-3-577-6047

www.realtek.com.tw

RTL8187B

Datasheet

COPYRIGHT

©2006 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.

DISCLAIMER

Realtek provides this document “as is”, without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

TRADEMARKS

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

USING THIS DOCUMENT

This document is intended for the software engineer’s reference and provides detailed programming information.

Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process.

REVISION HISTORY

Revision |

Release Date |

Summary |

1.0 |

2006/10/09 |

First release. |

Wireless LAN Network Interface Controller |

ii |

Track ID: JATR-1076-21 Rev. 1.0 |

|

|

|

|

|

|

|

RTL8187B |

|

|

|

|

|

|

|

Datasheet |

|

|

|

|

|

|

||

|

|

|

|

Table of Contents |

|

||

|

1. |

GENERAL DESCRIPTION ............................................................................................................................................... |

|

|

1 |

||

|

2. |

FEATURES .......................................................................................................................................................................... |

|

|

2 |

||

|

3. |

SYSTEM APPLICATIONS ................................................................................................................................................ |

|

|

3 |

||

|

4. |

BLOCK DIAGRAM ............................................................................................................................................................ |

|

|

4 |

||

|

5. |

PIN ASSIGNMENTS........................................................................................................................................................... |

|

|

5 |

||

|

5.1. GREEN PACKAGE AND VERSION IDENTIFICATION ........................................................................................................... |

|

|

5 |

|||

|

6. |

PIN DESCRIPTIONS.......................................................................................................................................................... |

|

|

6 |

||

|

6.1. USB TRANSCEIVER INTERFACE ...................................................................................................................................... |

|

|

6 |

|||

|

6.2. |

EEPROM INTERFACE ..................................................................................................................................................... |

|

|

6 |

||

|

6.3. |

POWER PINS .................................................................................................................................................................... |

|

|

6 |

||

|

6.4. |

LED INTERFACE.............................................................................................................................................................. |

|

|

7 |

||

|

6.5. ATTACHMENT UNIT INTERFACE ...................................................................................................................................... |

|

|

7 |

|||

|

|

6.5.1. |

RTL8225 RF Chipset .............................................................................................................................................. |

|

|

7 |

|

|

|

6.5.2. |

RTL8255 RF Chipset .............................................................................................................................................. |

|

|

8 |

|

|

6.6. CLOCK AND OTHER PINS................................................................................................................................................. |

|

|

9 |

|||

|

7. CPU ACCESS TO ENDPOINT DATA............................................................................................................................ |

|

|

10 |

|||

|

7.1. |

CONTROL TRANSFER..................................................................................................................................................... |

|

|

10 |

||

|

7.2. |

BULK TRANSFER ........................................................................................................................................................... |

|

|

10 |

||

|

8. |

USB REQUEST.................................................................................................................................................................. |

|

|

11 |

||

|

8.1. |

GET DESCRIPTOR-DEVICE............................................................................................................................................. |

|

|

11 |

||

|

8.2. GET DESCRIPTOR-DEVICE QUALIFIER (HIGH SPEED).................................................................................................... |

|

|

11 |

|||

|

8.3. |

GET DESCRIPTOR-CONFIGURATION .............................................................................................................................. |

|

|

12 |

||

|

8.4. GET DESCRIPTOR-STRING INDEX 0 ............................................................................................................................... |

|

|

13 |

|||

|

8.5. GET DESCRIPTOR-STRING INDEX 1 ............................................................................................................................... |

|

|

13 |

|||

|

8.6. GET DESCRIPTOR-STRING INDEX 2 ............................................................................................................................... |

|

|

13 |

|||

|

8.7. GET DESCRIPTOR-STRING INDEX 3 ............................................................................................................................... |

|

|

14 |

|||

|

8.8. GET DESCRIPTOR-STRING INDEX 4 ............................................................................................................................... |

|

|

14 |

|||

|

8.9. GET DESCRIPTOR-STRING INDEX 5 ............................................................................................................................... |

|

|

15 |

|||

|

8.10. GET DESCRIPTOR-OTHER SPEED CONFIGURATION.................................................................................................... |

|

|

15 |

|||

|

8.11. |

|

SET ADDRESS ............................................................................................................................................................ |

|

|

16 |

|

|

8.12. |

|

SET INTERFACE 0 ...................................................................................................................................................... |

|

|

16 |

|

|

8.13. SET FEATURE DEVICE ............................................................................................................................................... |

|

|

16 |

|||

|

8.14. CLEAR FEATURE DEVICE .......................................................................................................................................... |

|

|

17 |

|||

|

8.15. |

|

SET CONFIG 0............................................................................................................................................................ |

|

|

17 |

|

|

8.16. |

|

SET CONFIG 1............................................................................................................................................................ |

|

|

17 |

|

|

9. EEPROM (93C46 OR 93C56) CONTENTS.................................................................................................................... |

|

|

18 |

|||

|

9.1. EEPROM REGISTERS SUMMARY.................................................................................................................................. |

|

|

21 |

|||

|

9.2. EEPROM POWER MANAGEMENT REGISTERS SUMMARY ............................................................................................. |

21 |

|||||

|

10. |

USB PACKET BUFFERING........................................................................................................................................ |

|

|

22 |

||

|

10.1. TRANSMIT BUFFER MANAGER .................................................................................................................................. |

|

|

22 |

|||

|

10.2. RECEIVE BUFFER MANAGER ..................................................................................................................................... |

|

|

22 |

|||

|

|

|

|

Track ID: JATR-1076-21 Rev. 1.0 |

|||

|

Wireless LAN Network Interface Controller |

iii |

|||||

|

|

|

|

RTL8187B |

|

|

|

|

|

Datasheet |

|

|

|

|

|

|

|

10.3. |

PACKET RECOGNITION .............................................................................................................................................. |

22 |

|

||

11. |

FUNCTIONAL DESCRIPTION .................................................................................................................................. |

23 |

|

||

|

11.1. TRANSMIT & RECEIVE OPERATIONS.......................................................................................................................... |

23 |

|

||

|

|

11.1.1. |

Transmit ............................................................................................................................................................... |

23 |

|

|

|

11.1.2. |

Receive ................................................................................................................................................................. |

27 |

|

11.2. |

RX COMMAND........................................................................................................................................................... |

29 |

|

||

11.3. |

LOOPBACK OPERATION ............................................................................................................................................. |

29 |

|

||

|

11.4. TX ENCAPSULATION (WITH RTL8187B INTERNAL BASEBAND PROCESSOR)............................................................ |

29 |

|

||

|

11.5. RX DECAPSULATION (WITH RTL8187B INTERNAL BASEBAND PROCESSOR) ........................................................... |

30 |

|

||

11.6. |

QOS FUNCTIONS ....................................................................................................................................................... |

30 |

|

||

|

11.7. CONTENTION-BASED ADMISSION CONTROL FUNCTIONS ........................................................................................... |

30 |

|

||

|

11.8. DURATION FIELD PROCESSING .................................................................................................................................. |

31 |

|

||

11.9. |

LED FUNCTIONS ....................................................................................................................................................... |

31 |

|

||

|

|

11.9.1. |

Link Monitor......................................................................................................................................................... |

31 |

|

|

|

11.9.2. |

Infrastructure Monitor ......................................................................................................................................... |

31 |

|

|

|

11.9.3. |

Rx LED ................................................................................................................................................................. |

32 |

|

|

|

11.9.4. |

Tx LED ................................................................................................................................................................. |

33 |

|

|

|

11.9.5. |

Tx/Rx LED ............................................................................................................................................................ |

33 |

|

|

|

11.9.6. |

LINK/ACT LED .................................................................................................................................................... |

34 |

|

12. |

APPLICATION DIAGRAM......................................................................................................................................... |

35 |

|

||

13. |

ELECTRICAL CHARACTERISTICS........................................................................................................................ |

36 |

|

||

|

13.1. TEMPERATURE LIMIT RATINGS ................................................................................................................................. |

36 |

|

||

13.2. |

DC CHARACTERISTICS .............................................................................................................................................. |

36 |

|

||

13.3. |

AC CHARACTERISTICS .............................................................................................................................................. |

37 |

|

||

|

|

13.3.1. Serial EEPROM Interface Timing (93C46(64*16)/93C56(128*16))................................................................... |

37 |

|

|

14. |

MECHANICAL DIMENSIONS................................................................................................................................... |

38 |

|

||

|

14.1. MECHANICAL DIMENSIONS NOTES............................................................................................................................ |

39 |

|

||

15. |

ORDERING INFORMATION ..................................................................................................................................... |

39 |

|

||

|

|

|

|

|

|

|

|

List of Tables |

|

TABLE 1. USB TRANSCEIVER INTERFACE ..................................................................................................................................... |

|

6 |

|

TABLE 2. EEPROM INTERFACE .................................................................................................................................................... |

|

6 |

|

TABLE 3. POWER PINS ................................................................................................................................................................... |

|

6 |

|

TABLE 4. LED INTERFACE............................................................................................................................................................. |

|

7 |

|

TABLE 5. ATTACHMENT UNIT INTERFACE ..................................................................................................................................... |

|

7 |

|

TABLE 6. |

RTL8255 RF CHIPSET.................................................................................................................................................... |

|

8 |

TABLE 7. |

CLOCK AND OTHER PINS................................................................................................................................................ |

|

9 |

TABLE 8. |

GET DESCRIPTOR-DEVICE............................................................................................................................................ |

|

11 |

TABLE 9. |

GET DESCRIPTOR- DEVICE QUALIFIER (HIGH SPEED) .................................................................................................. |

11 |

|

TABLE 10. GET DESCRIPTOR-CONFIGURATION ............................................................................................................................. |

|

12 |

|

TABLE 11. GET DESCRIPTOR-STRING INDEX 0 .............................................................................................................................. |

|

13 |

|

TABLE 12. GET DESCRIPTOR-STRING INDEX 1 .............................................................................................................................. |

|

13 |

|

TABLE 13. GET DESCRIPTOR-STRING INDEX 2 .............................................................................................................................. |

|

13 |

|

TABLE 14. GET DESCRIPTOR-STRING INDEX 3 .............................................................................................................................. |

|

14 |

|

TABLE 15. GET DESCRIPTOR-STRING INDEX 4 .............................................................................................................................. |

|

14 |

|

Wireless LAN Network Interface Controller |

iv |

Track ID: JATR-1076-21 Rev. 1.0 |

|

|

RTL8187B |

|

Datasheet |

TABLE 16. GET DESCRIPTOR-STRING INDEX 5 .............................................................................................................................. |

15 |

TABLE 17. GET DESCRIPTOR-OTHER SPEED CONFIGURATION ...................................................................................................... |

15 |

TABLE 18. SET ADDRESS .............................................................................................................................................................. |

16 |

TABLE 19. SET INTERFACE 0 ......................................................................................................................................................... |

16 |

TABLE 20. SET FEATURE DEVICE.................................................................................................................................................. |

16 |

TABLE 21. CLEAR FEATURE DEVICE ............................................................................................................................................. |

17 |

TABLE 22. SET CONFIG 0 .............................................................................................................................................................. |

17 |

TABLE 23. SET CONFIG 1 .............................................................................................................................................................. |

17 |

TABLE 24. EEPROM (93C46 OR 93C56) CONTENTS.................................................................................................................... |

18 |

TABLE 25. EEPROM REGISTERS SUMMARY ................................................................................................................................ |

21 |

TABLE 26. EEPROM POWER MANAGEMENT REGISTERS SUMMARY............................................................................................ |

21 |

TABLE 27. TX DESCRIPTOR FORMAT ............................................................................................................................................ |

23 |

TABLE 28. TX STATUS DESCRIPTOR.............................................................................................................................................. |

24 |

TABLE 29. RX DESCRIPTOR FORMAT ............................................................................................................................................ |

27 |

TABLE 30. RX STATUS DESCRIPTOR.............................................................................................................................................. |

28 |

TABLE 31. TX BEACON INTERRUPT............................................................................................................................................... |

29 |

TABLE 32. TX CLOSE DESCRIPTOR................................................................................................................................................ |

29 |

TABLE 33. TEMPERATURE LIMIT RATINGS.................................................................................................................................... |

36 |

TABLE 34. DC CHARACTERISTICS................................................................................................................................................. |

36 |

TABLE 35. EEPROM ACCESS TIMING PARAMETERS .................................................................................................................... |

37 |

TABLE 36. ORDERING INFORMATION ............................................................................................................................................ |

39 |

|

List of Figures |

|

FIGURE 1. BLOCK DIAGRAM.......................................................................................................................................................... |

4 |

|

FIGURE 2. PIN ASSIGNMENTS......................................................................................................................................................... |

5 |

|

FIGURE 3. RX LED ...................................................................................................................................................................... |

32 |

|

FIGURE 4. TX LED ...................................................................................................................................................................... |

33 |

|

FIGURE 5. |

TX/RX LED ................................................................................................................................................................ |

33 |

FIGURE 6. |

LINK/ACT LED......................................................................................................................................................... |

34 |

FIGURE 7. |

APPLICATION DIAGRAM.............................................................................................................................................. |

35 |

FIGURE 8. |

SERIAL EEPROM INTERFACE TIMING ........................................................................................................................ |

37 |

Wireless LAN Network Interface Controller |

v |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

1. General Description

The Realtek RTL8187B is a low-profile highly integrated cost-effective Wireless LAN USB 2.0 network interface controller that integrates a USB 2.0 PHY, SIE (Serial Interface Engine), 8051 MCU, a Wireless LAN MAC, and a Direct Sequence Spread Spectrum/OFDM baseband processor onto one chip. It provides USB high speed (480Mbps), and full speed (12Mbps), and supports 9 endpoints for transfer pipes. To reduce protocol overhead, the RTL8187B supports Short InterFrame Space (SIFS) burst mode to send packets back-to-back. A protection mechanism prevents collisions among 802.11b nodes. The RTL8187B fully complies with IEEE 802.11a/b/g, WMM, 802.11e, and CCX specifications.

To reduce protocol overhead, the RTL8187B supports Short InterFrame Space (SIFS) burst mode to send packets back-to-back. A protection mechanism prevents collisions among 802.11b nodes.

Direct Sequence Spread Spectrum (DSSS), Complementary Code Keying (CCK), and Orthogonal Frequency Division Multiplexing (OFDM) baseband processing are implemented to support all IEEE 802.11a, 802.11b, and 802.11g data rates. Differential phase shift keying modulation schemes, DBPSK and DQPSK with data scrambling capability, are available, along with complementary code keying to provide data rates of 1, 2, 5.5, and 11Mbps, with long or short preamble. A high-speed Fast Fourier Transform (FFT)/Inverse Fast Fourier Transform (IFFT), combined with BPSK, QPSK, 16QAM and 64QAM modulation of the individual sub-carriers, provides data rates of 6, 9, 12, 18, 24, 36, 48 and 54Mbps, with rate-compatible punctured convolutional coding with a coding rate of 1/2, 2/3, and 3/4.

An enhanced signal detector, an adaptive frequency domain equalizer, and a soft-decision Viterbi decoder are built-in to alleviate severe multipath effects. Efficient IQ-imbalance calibration, DC offset, phase noise, frequency offset, and timing offset compensation reduce radio frequency front-end impairments. Selectable digital transmit and receiver FIR filters are provided to meet the requirements of transmit spectrum masks, and to reject adjacent channel interference, respectively. Both in the transmitter and receiver, programmable scaling in the digital domain trades the quantization noise against the increased probability of clipping. Robust signal detection, symbol boundary detection, and channel estimation perform well at the minimum sensitivity.

The RTL8187B supports fast receiver Automatic Gain Control (AGC) and antenna diversity functions, and an adaptive transmit power control function to obtain better performance in the analog portions of the transceiver. It also has on-chip digital-to-analog converters and analog-to-digital converters for analog I and Q inputs and outputs, transmit TSSI and receiver RSSI inputs, and transmit and receiver AGC outputs.

The RTL8187B keeps network maintenance costs low and eliminates usage barriers. The RTL8187B is highly integrated and requires no ‘glue’ logic or external memory.

The installation for antenna is fixed as vertical polarization.

Wireless LAN Network Interface Controller |

1 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

2. Features

128-Pin LQFP with ‘Green’ package

State machine implementation without external memory (RAM, flash) requirement

Complies with IEEE 802.11a/b/g standards

Supports descriptor-based buffer management

Integrated Wireless LAN MAC and Direct Sequence Spread Spectrum/OFDM Baseband Processor in one chip

Enhanced signal detector, adaptive frequency domain equalizer, and soft-decision Viterbi decoder to alleviate severe multipath effects

Processing Gain compliant with FCC

On-Chip A/D and D/A converters for I/Q Data, AGC, and Adaptive Power Control

Supports both transmit and receive Antenna Diversity

Data rates of 1, 2, 5.5, 6, 9, 11, 12, 18, 24, 36, 48, and 54Mbps

Supports 40MHz OSC as the internal clock source. The frequency deviation of the OSC must be within 25 PPM on IEEE 802.11g and 20 PPM on IEEE 802.11a

IEEE 802.11g protection mechanisms for both RTS/CTS and CTS-to-self

Burst-mode support for dramatically enhanced throughput

DSSS with DBPSK and DQPSK, CCK modulations and demodulations supported with long and short preamble

OFDM with BPSK, QPSK, 16QAM and 64QAM modulations and demodulations supported with rate compatible punctured convolutional coding with coding rate of 1/2, 2/3, and 3/4

Efficient IQ-imbalance calibration, DC offset, phase noise, frequency offset and timing offset compensation reduce analog front-end impairments

Selectable digital transmit and receiver FIR filters provided to meet transmit spectrum mask requirements and to reject adjacent channel interference

Programmable scaling both in transmitter and receiver to trade quantization noise against the increased probability of clipping

Fast receiver Automatic Gain Control (AGC) & antenna diversity functions

Complies with WMM, 802.11e, and CCX specifications

Complies with 802.11h, 802.11i, 802.11j specifications

Hardware-based IEEE 802.11i encryption/decryption engine, including 64-bit/128-bit WEP, TKIP, and AES

Supports Wi-Fi alliance WPA and WPA2 security

Contains two large independent transmit and receive FIFO buffers

Advanced power saving mode when the LAN and wakeup function are not used

Wireless LAN Network Interface Controller |

2 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

Uses 93C46 (64*16-bit EEPROM) or 93C56 (128*16-bit EEPROM) to store resource configuration and ID parameter data

LED pins for various network activity indications

Six GPIO pins supported

Supports digital loopback capability on both ports

Scatter and gather operation

Complies with USB Specification 2.0

Supports Full-speed (12Mbps) and High-speed (480Mbps)

Embedded standard 8051 CPU with enhanced features:

Four cycles per instruction

Variable clock speed cuts power consumption

Supports 9 endpoints:

64-Byte buffer for control endpoint

Two 512-Byte buffers for bulk IN endpoint

Seven 512-Byte buffers for bulk OUT endpoint

3.3V and 1.5V power supplies required

5V tolerant I/Os

0.15µm CMOS process

3. System Applications

USB Dongle WLAN adapter

Embedded WLAN solution in notebook, desktop, mobile phone, and motherboard

Wireless LAN Network Interface Controller |

3 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

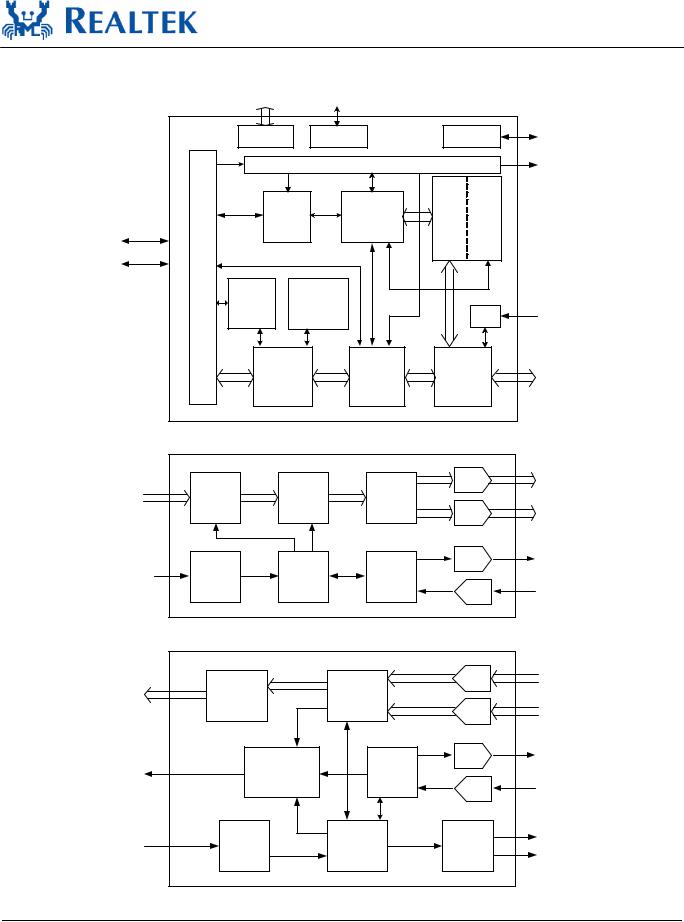

4. Block Diagram

MAC |

EEPROM |

LED Driver |

|

Serial |

Radio and |

||

|

Interface |

|

|

Control |

Synthesizer |

||

|

|

|

|

|

|

|

|

|

Power and TX/RX Timing Control Logic |

Control |

|||||

|

|

Interrupt |

RTS, CTS, |

Frame Length |

Register |

Frame Type Discriminator |

|

|

|

Control |

ACK Frame |

|

|||

D+ |

|

Logic |

Generator |

|

|||

|

|

|

|

||||

D- |

|

|

|

|

|

|

|

Register+ |

WEP/ |

Checksum |

|

|

|

|

|

TKIP/ |

|

|

|

|

|||

IE |

AES |

|

Logic |

|

|

CCA/ |

From BBP |

Engine |

|

|

|

|

|||

S |

|

|

|

|

|

NAV |

|

|

|

|

FIFO |

Transmit/ |

MAC/BBP |

||

|

|

FIFO |

|

Receive |

|||

|

|

Control |

|

||||

|

|

|

Logic |

Interface |

|||

|

|

|

Logic |

|

|||

|

|

|

Interface |

|

|||

BBP, TX Section

MAC/BBP |

|

|

DAC |

TXI |

Scrambler |

Coding |

Digital |

|

|

Interface |

Filter |

|

||

|

|

TXQ |

||

|

|

|

DAC |

|

From |

|

|

DAC |

TXAGC |

Register |

TX State |

TX AGC |

|

|

MAC |

Machine |

Control |

|

|

|

TXDET |

|||

|

|

ADC |

||

|

|

|

BBP, RX Section

MAC/BBP |

|

|

ADC |

RXI |

|

Descrambler |

Decoding |

|

|

|

|

Interface |

|

|

|

||

|

|

ADC |

RXQ |

|

|

|

|

|

|

||

|

Clear Channel |

RX AGC |

DAC |

RXAGC |

|

To MAC |

Assessment/ |

|

|

|

|

Control |

|

|

|

||

|

Signal Quality |

|

ADC |

RSSI |

|

|

|

|

|

||

From |

|

RX State |

Antenna |

ANTSEL |

|

Register |

Diversity |

|

|||

MAC |

Machine |

ANTSELB |

|

||

|

Control |

|

|||

|

|

|

|||

|

Figure 1. |

Block Diagram |

|

|

|

Wireless LAN Network Interface Controller |

4 |

|

Track ID: JATR-1076-21 |

Rev. 1.0 |

|

RTL8187B

Datasheet

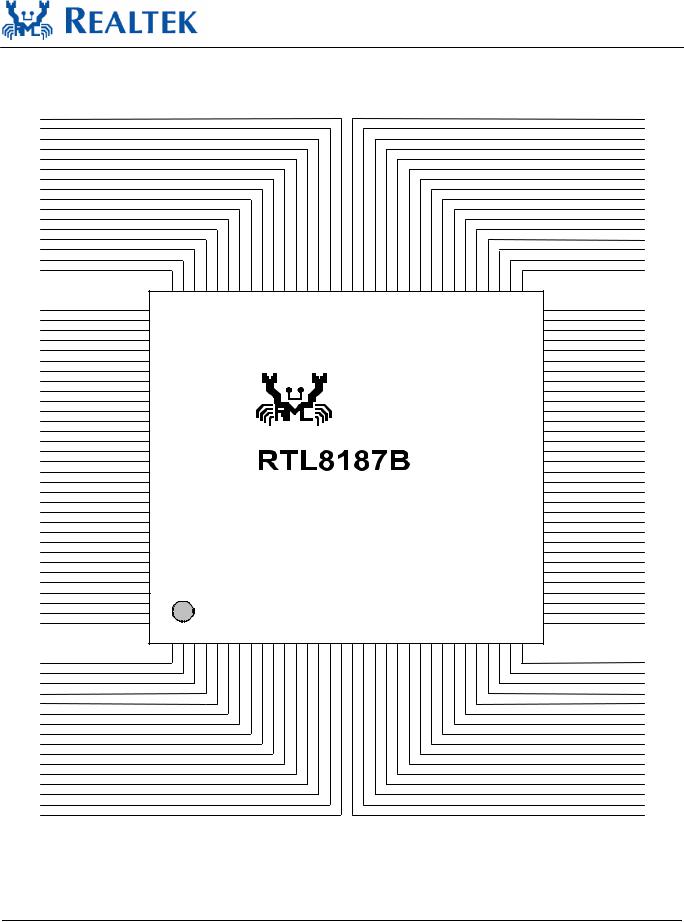

5. Pin Assignments

Figure 2. Pin Assignments

5.1.Green Package and Version Identification

Green package is indicated by a ‘G’ in the location marked ‘T’ in Figure 2.

Wireless LAN Network Interface Controller |

5 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

6. Pin Descriptions

In order to reduce pin count, and therefore size and cost, some pins have multiple functions. In such cases, the functions are separated with a ‘/’ symbol. Refer to the Pin Assignments diagram on page 5 for a graphical representation.

The following signal type codes are used in the tables:

I: Input. |

S/T/S: Sustained Tri-State. |

O: Output |

O/D: Open Drain. |

T/S: Tri-State bi-directional input/output pin. |

|

6.1.USB Transceiver Interface

Table 1. USB Transceiver Interface

Symbol |

Type |

Pin No |

Description |

HSDP |

I/O |

26 |

High speed USB D+ signal |

HSDM |

I/O |

24 |

High speed USB D- signal |

RREF |

N/A |

31 |

External Reference. Requires 1% precision 6.25K resistor to ground |

6.2.EEPROM Interface

|

|

|

Table 2. EEPROM Interface |

|

Symbol |

Type |

Pin No |

|

Description |

EESK |

O |

51 |

|

EESK in 93C46 (93C56) programming or auto-load mode. |

EEDI |

O |

39 |

|

EEDI in 93C46 (93C56) programming or auto-load mode. |

EEDO |

I/O |

36 |

|

EEDO in 93C46 (93C56) programming or auto-load mode. |

EECS |

O |

47 |

|

EEPROM Chip Select. 93C46 (93C56) chip select. |

6.3. |

Power Pins |

|

|

|

|

||||

|

|

|

|

|

|

|

|

Table 3. Power Pins |

|

|

Symbol |

|

Type |

|

|

Pin No |

|

Description |

|

|

VCC3 |

|

P |

40, 59, 78, 93, 111 |

|

+3.3V (Digital). |

|||

|

AVDD |

|

P |

2, 9, 22, 29, 127 |

|

+3.3V (Analog). |

|||

|

VCCK |

|

P |

44, 53, 72, 82, 90, 105, |

+1.5V. |

||||

|

|

|

|

115 |

|

|

|

|

|

|

GNDK |

|

P |

41, 45, 52, 60, 73, 80, |

Ground (Digital). |

||||

|

|

|

|

83, |

91, |

92, |

106, |

110, |

|

|

|

|

|

116 |

|

|

|

|

|

|

AGND |

|

P |

3, 10, 21, 23, 30, 123, |

Ground (Analog). |

||||

|

|

|

|

126 |

|

|

|

|

|

Wireless LAN Network Interface Controller |

6 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

6.4.LED Interface

|

|

|

|

Table 4. |

LED Interface |

|

|

|

|

|

|

Symbol |

Type |

Pin No |

Description |

|

|

|

|

|

|

|

|

LED0, 1 |

O |

48, 56 |

|

|

|

LED Pins (Active low) |

|

|

|

||

|

|

|

|

LEDS1~0 |

|

00 |

01 |

|

10 |

11 |

|

|

|

|

|

LED0 |

|

TX/RX |

TX/RX |

|

TX |

LINK/ACT |

|

|

|

|

|

LED1 |

|

Infrastructure |

LINK |

|

RX |

Infrastructure |

|

|

|

|

|

During |

power down mode, |

the LED signals are logic high. |

|

||||

6.5.Attachment Unit Interface

6.5.1.RTL8225 RF Chipset

Symbol |

Type |

Pin No |

RIFSCK |

O |

57 |

|

|

|

RIFSD |

I/O |

61 |

RFLE |

O |

58 |

CALEN |

O |

77 |

CALMODE |

O |

108 |

|

|

|

LNA_HL |

O |

88 |

ANTSEL |

O |

87 |

|

|

|

ANTSELB |

O |

95 |

|

|

|

TRSW |

O |

104 |

TRSWB |

O |

103 |

VCOPDN |

O |

49 |

A_PAPE |

O |

85 |

B_PAPE |

O |

107 |

RFTXEN |

O |

102 |

RFRXEN |

O |

113 |

GPIO0 |

O |

67 |

GPIO1 |

O |

68 |

GPIO2 |

O |

69 |

GPIO3 |

O |

70 |

Table 5. Attachment Unit Interface

Description

Serial Clock Output.

For the RTL8225 RF chipset, all operation mode switching and register setting is done via a 4-wire serial interface.

Serial Data Input/Output. Serial Enable control. Serial Read/Write control. Receiver Output.

I and Q channel AC coupling high-pass corner frequency selection. The output function of this pin is not used in the RTL8225 RF chipset.

Not used in the RTL8225 RF chipset. Antenna Select.

The antenna detects signal change states as the receiver switches from antenna to antenna during the acquisition process in antenna diversity mode. This is a complement for ANTSELB for differential drive of antenna switches.

Antenna Select B.

The antenna detects signal change states as the receiver switches from antenna to antenna during the acquisition process in the antenna diversity mode. This is a complement for ANTSEL for differential drive of antenna switches. Transmit/Receive path select.

The TRSW select signal controls the direction of the Transmit/Receive switch. Output Pin as shutdown mode select digital input.

2.4GHz Transmit Power Amplifier Power Enable. Not used in the RTL8225 RF chipset.

Not used in the RTL8225 RF chipset. Not used in the RTL8225 RF chipset. General purpose input/output pin.

General purpose input/output pin. General purpose input/output pin. General purpose input/output pin.

Wireless LAN Network Interface Controller |

7 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

Symbol |

Type |

Pin No |

GPIO4 |

O |

100 |

GPIO5 |

O |

94 |

VREFO |

X |

118 |

VRP |

X |

119 |

VRN |

X |

120 |

RXIP |

I |

121 |

RXIN |

I |

122 |

RXQP |

I |

124 |

RXQN |

I |

125 |

RXAGC |

I |

4 |

TXAGC |

O |

5 |

RSSI |

I |

6 |

TSSI0 |

I |

7 |

TSSI1 |

I |

8 |

TXQP |

I |

11 |

TXQN |

I |

12 |

TXIP |

O |

14 |

TXIN |

O |

13 |

TXQTP |

O |

15 |

TXQTN |

O |

16 |

TXITP |

O |

17 |

TXITN |

O |

18 |

Description

General purpose input/output pin.

General purpose input/output pin.

Not used in the RTL8225 RF chipset.

Not used in the RTL8225 RF chipset.

Not used in the RTL8225 RF chipset.

Receive (Rx) In-phase Analog Data.

Receive (Rx) Quadrature-phase Analog Data.

Not used in the RTL8225 RF chipset. Not used in the RTL8225 RF chipset.

Analog Input to the Receive Power A/D Converter for Receive AGC Control. Input to the Transmit Power A/D Converter for 2.4GHz Transmit AGC Control. Not used in the RTL8225 RF chipset.

Not used in the RTL8225 RF chipset.

Not used in the RTL8225 RF chipset.

Transmit (TX) Quadrature-phase Analog Data.

Transmit (TX) In-phase Analog Data.

6.5.2.RTL8255 RF Chipset

|

|

|

|

Table 6. RTL8255 RF Chipset |

|

|

||

|

Symbol |

Type |

Pin No |

Description |

|

|

|

|

|

RIFSCK |

O |

57 |

Serial Clock Output. |

|

|

||

|

|

|

|

For the RTL8255 RF chipset, all operation mode switching and register setting is |

|

|||

|

|

|

|

done via a 3-wire serial interface. |

|

|

||

|

RIFSD |

O |

61 |

Serial Data Input/Output. |

|

|

||

|

RFLE |

O |

58 |

Serial Enable control. |

|

|

||

|

CALEN |

X |

77 |

Not used in the RTL8255 RF chipset. |

|

|

||

|

CALMODE |

O |

108 |

Receiver Output. |

|

|

|

|

|

|

|

|

I and Q channel AC coupling high-pass corner frequency selection. The output |

|

|||

|

|

|

|

function of this pin is not used in the RTL8255 RF chipset. |

|

|||

|

LNAHL |

O |

88 |

Not used in the RTL8255 RF chipset. |

|

|

||

|

ANTSEL |

O |

87 |

Antenna Select. |

|

|

|

|

|

ANTSELB |

O |

95 |

The antenna detects signal change states as the receiver switches from antenna to |

|

|||

|

|

|

|

antenna during the acquisition process in antenna diversity mode. |

|

|||

|

TRSW |

O |

104 |

Transmit/Receive path select. |

|

|

||

|

TRSWB |

O |

103 |

The TRSW select signal controls the direction of the Transmit/Receive switch. |

|

|||

|

VCOPDN |

O |

49 |

Not used in the RTL8255 RF chipset. |

|

|

||

|

APAPE |

O |

85 |

2.4GHz Transmit Power Amplifier Power Enable. |

|

|||

|

BPAPE |

O |

107 |

5GHz Transmit Power Amplifier Power Enable. |

|

|||

|

|

|

|

|

|

|

Track ID: JATR-1076-21 Rev. 1.0 |

|

Wireless LAN Network Interface Controller |

8 |

|

||||||

RTL8187B

Datasheet

Symbol |

Type |

Pin No |

RFTXEN |

O |

102 |

RFRXEN |

O |

113 |

GPIO[0] |

O |

67 |

GPIO[1] |

O |

68 |

GPIO[2] |

O |

69 |

GPIO[3] |

O |

70 |

GPIO[4] |

O |

100 |

GPIO[5] |

O |

94 |

VREFO |

X |

118 |

VRP |

X |

119 |

VRN |

X |

120 |

RXIP |

I |

121 |

RXIN |

I |

122 |

RXQP |

I |

124 |

RXQN |

I |

125 |

RXAGC |

O |

4 |

TXAGC |

O |

5 |

RSSI |

I |

6 |

TSSI0 |

I |

7 |

TSSI1 |

I |

8 |

TXQP |

O |

11 |

TXQN |

O |

12 |

TXIP |

O |

14 |

TXIN |

O |

13 |

TXQTP |

O |

15 |

TXQTN |

O |

16 |

TXITP |

O |

17 |

TXITN |

O |

18 |

Description

Not used in the RTL8255 RF chipset.

Not used in the RTL8255 RF chipset.

General purpose input/output pin.

General purpose input/output pin.

General purpose input/output pin.

General purpose input/output pin.

General purpose input/output pin.

General purpose input/output pin.

Not used in the RTL8255 RF chipset.

Not used in the RTL8255 RF chipset.

Not used in the RTL8255 RF chipset.

Receive (Rx) In-phase Analog Data.

Receive (Rx) Quadrature-phase Analog Data.

Not used in the RTL8255 RF chipset. Not used in the RTL8255 RF chipset.

Analog Input to the Receive Power A/D Converter for Receive AGC Control. Input to the Transmit Power A/D Converter for 2.4GHz Transmit AGC Control. Input to the Transmit Power A/D Converter for 5GHz Transmit AGC Control. Transmit (TX) Quadrature-phase Analog Data.

Transmit (TX) In-phase Analog Data.

Not used in the RTL8255 RF chipset.

Not used in the RTL8255 RF chipset.

6.6.Clock and Other Pins

Table 7. Clock and Other Pins

Symbol |

Type |

Pin No |

Description |

R15K |

I/O |

1 |

This pin must be pulled low by a 15K Ω resistor. |

XI |

I |

20 |

40MHz clock Input. |

EXTRSTB |

I |

32 |

Pull high 3.3V. If pulled low, the whole chip will be reset. |

Wireless LAN Network Interface Controller |

9 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

7. CPU Access to Endpoint Data

7.1.Control Transfer

Control transfers configure and send commands to a device. Because they are so important, they employ extensive USB error checking. The host reserves a portion of each USB frame for control transfers. Control transfers consist of two or three stages. The SETUP stage contains eight bytes of USB control data. An optional DATA stage contains more data, if required. The STATUS stage allows the device to indicate successful completion of a control operation.

7.2.Bulk Transfer

Bulk data is bursty, traveling in packets of 8, 16, 32, or 64 bytes at full speed, or at 512 bytes at high speed. Bulk data has guaranteed accuracy due to an automatic retry mechanism for erroneous data. The host schedules transmission of bulk packets when there is available bus time.

Wireless LAN Network Interface Controller |

10 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

8. USB Request

8.1.Get Descriptor-Device

Table 8. Get Descriptor-Device

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

80 |

06 |

00 |

01 |

00 |

00 |

|

Lengh_L |

|

Length_H |

High Speed Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

|

DATA6 |

DATA7 |

12 |

01 |

00 |

02 |

00 |

00 |

|

00 |

40 |

|

DA |

0B |

87 |

81 |

00 |

01 |

|

01 |

02 |

|

03 |

01 |

|

|

|

|

|

|

|

|

Full Speed Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

|

DATA6 |

DATA7 |

12 |

01 |

10 |

01 |

00 |

00 |

|

00 |

40 |

|

DA |

0B |

87 |

81 |

00 |

01 |

|

01 |

02 |

|

0301

8.2.Get Descriptor-Device Qualifier (High Speed)

Table 9. Get DescriptorDevice Qualifier (High Speed)

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

80 |

06 |

00 |

06 |

00 |

00 |

Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

0A |

06 |

00 |

02 |

00 |

00 |

|

01 |

00 |

|

|

|

|

|

wLengthL wLengthH

Lengh_L Length_H

DATA6 |

DATA7 |

00 |

40 |

|

|

Wireless LAN Network Interface Controller |

11 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

8.3.Get Descriptor-Configuration

Table 10. Get Descriptor-Configuration

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

80 |

06 |

00 |

02 |

00 |

00 |

High Speed Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

09 |

02 |

51 |

00 |

01 |

01 |

|

FA |

09 |

04 |

00 |

00 |

09 |

|

FF |

02 |

07 |

05 |

83 |

02 |

|

00 |

07 |

05 |

04 |

02 |

00 |

|

07 |

05 |

05 |

02 |

00 |

02 |

|

05 |

06 |

02 |

00 |

02 |

00 |

|

07 |

02 |

00 |

02 |

00 |

07 |

|

02 |

00 |

02 |

00 |

07 |

05 |

|

00 |

02 |

00 |

07 |

05 |

|

0B |

02 |

00 |

07 |

05 |

0C |

02 |

|

00 |

|

|

|

|

|

|

Full Speed Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

09 |

02 |

51 |

00 |

01 |

01 |

|

FA |

09 |

04 |

00 |

00 |

09 |

|

FF |

02 |

07 |

05 |

83 |

02 |

|

00 |

07 |

05 |

04 |

02 |

40 |

|

07 |

05 |

05 |

02 |

40 |

00 |

|

05 |

06 |

02 |

40 |

00 |

00 |

|

07 |

02 |

40 |

00 |

00 |

07 |

|

02 |

40 |

00 |

00 |

07 |

05 |

|

40 |

00 |

00 |

07 |

05 |

|

0B |

00 |

00 |

07 |

05 |

0C |

02 |

|

00 |

|

|

|

|

|

|

wLengthL wLengthH

Length_L Length_H

DATA6 |

DATA7 |

04 |

80 |

FF |

FF |

00 |

02 |

02 |

00 |

00 |

07 |

07 |

05 |

05 |

89 |

0A |

02 |

02 |

00 |

00 |

02 |

|

|

DATA6 |

DATA7 |

04 |

80 |

FF |

FF |

40 |

00 |

00 |

00 |

00 |

07 |

07 |

05 |

05 |

89 |

0A |

02 |

02 |

40 |

40 |

00 |

|

|

Wireless LAN Network Interface Controller |

12 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

8.4.Get Descriptor-String Index 0

Table 11. Get Descriptor-String Index 0

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

80 |

06 |

00 |

03 |

00 |

00 |

Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

04 |

03 |

09 |

04 |

- |

- |

|

wLengthL wLengthH

Lengh_L Length_H

DATA6 DATA7

--

8.5.Get Descriptor-String Index 1

Table 12. Get Descriptor-String Index 1

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

80 |

06 |

01 |

03 |

09 |

04 |

|

Lengh_L |

|

Length_H |

Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

|

DATA6 |

DATA7 |

10 |

03 |

52 |

00 |

65 |

00 |

|

61 |

00 |

|

6C |

00 |

74 |

00 |

65 |

00 |

|

6B |

00 |

|

8.6.Get Descriptor-String Index 2

Table 13. Get Descriptor-String Index 2

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

80 |

06 |

02 |

03 |

09 |

04 |

|

Lengh_L |

|

Length_H |

Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

|

DATA6 |

DATA7 |

2B |

03 |

52 |

00 |

54 |

00 |

|

4C |

00 |

|

38 |

00 |

31 |

00 |

38 |

00 |

|

37 |

00 |

|

42 |

00 |

20 |

00 |

57 |

00 |

|

4C |

00 |

|

41 |

00 |

4E |

00 |

20 |

00 |

|

41 |

00 |

|

64 |

00 |

6` |

00 |

70 |

00 |

|

74 |

00 |

|

65 |

00 |

72 |

|

|

|

|

|

|

|

Wireless LAN Network Interface Controller |

13 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

8.7.Get Descriptor-String Index 3

Table 14. Get Descriptor-String Index 3

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

80 |

06 |

03 |

03 |

09 |

04 |

Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

1A |

03 |

30 |

00 |

30 |

00 |

|

30 |

00 |

34 |

00 |

63 |

00 |

|

30 |

00 |

30 |

00 |

30 |

00 |

|

31 |

00 |

|

|

|

|

|

wLengthL wLengthH

Lengh_L Length_H

DATA6 |

DATA7 |

65 |

00 |

30 |

00 |

30 |

00 |

|

|

8.8.Get Descriptor-String Index 4

Table 15. Get Descriptor-String Index 4

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

80 |

06 |

04 |

03 |

09 |

04 |

|

Lengh_L |

|

Length_H |

Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

|

DATA6 |

DATA7 |

2C |

03 |

57 |

00 |

69 |

00 |

|

72 |

00 |

|

65 |

00 |

6C |

00 |

65 |

00 |

|

73 |

00 |

|

73 |

00 |

20 |

00 |

4E |

00 |

|

65 |

00 |

|

74 |

00 |

77 |

00 |

6F |

00 |

|

72 |

00 |

|

6B |

00 |

20 |

00 |

43 |

00 |

|

61 |

00 |

|

72 |

00 |

64 |

00 |

|

|

|

|

|

|

Wireless LAN Network Interface Controller |

14 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

8.9.Get Descriptor-String Index 5

Table 16. Get Descriptor-String Index 5

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

80 |

06 |

05 |

03 |

09 |

04 |

|

Lengh_L |

|

Length_H |

Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

|

DATA6 |

DATA7 |

30 |

03 |

55 |

00 |

53 |

00 |

|

42 |

00 |

|

20 |

00 |

48 |

00 |

53 |

00 |

|

20 |

00 |

|

48 |

00 |

65 |

00 |

72 |

00 |

|

69 |

00 |

|

61 |

00 |

6C |

00 |

20 |

00 |

|

43 |

00 |

|

6F |

00 |

6E |

00 |

76 |

00 |

|

65 |

00 |

|

72 |

00 |

74 |

00 |

65 |

00 |

|

72 |

00 |

|

8.10.Get Descriptor-Other Speed Configuration

Table 17. Get Descriptor-Other Speed Configuration

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

80 |

06 |

00 |

07 |

00 |

00 |

|

Lengh_L |

|

Length_H |

High Speed Data Transaction

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

|

DATA6 |

DATA7 |

09 |

07 |

51 |

00 |

01 |

01 |

|

04 |

80 |

|

FA |

09 |

04 |

00 |

00 |

09 |

|

FF |

FF |

|

FF |

02 |

07 |

05 |

83 |

02 |

|

00 |

02 |

|

00 |

07 |

05 |

04 |

02 |

00 |

|

02 |

00 |

|

07 |

05 |

05 |

02 |

00 |

02 |

|

00 |

07 |

|

05 |

06 |

02 |

00 |

02 |

00 |

|

07 |

05 |

|

07 |

02 |

00 |

02 |

00 |

07 |

|

05 |

89 |

|

02 |

00 |

02 |

00 |

07 |

05 |

|

0A |

02 |

|

00 |

02 |

00 |

07 |

05 |

|

0B |

|

02 |

00 |

02 |

00 |

07 |

05 |

0C |

02 |

|

00 |

02 |

|

00 |

|

|

|

|

|

|

|

|

|

Wireless LAN Network Interface Controller |

15 |

Track ID: JATR-1076-21 Rev. 1.0 |

|

|

|

|

|

|

|

|

|

|

RTL8187B |

|

|

|

|

|

|

|

|

|

|

|

Datasheet |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Full Speed Data Transaction |

|

|

|

|

|

|

|

|

||

|

DATA0 |

DATA1 |

DATA2 |

DATA3 |

DATA4 |

|

DATA5 |

|

DATA6 |

DATA7 |

|

|

09 |

07 |

51 |

00 |

01 |

01 |

|

04 |

80 |

|

|

|

FA |

09 |

04 |

00 |

00 |

09 |

|

FF |

FF |

|

|

|

FF |

02 |

07 |

05 |

83 |

02 |

|

40 |

00 |

|

|

|

00 |

07 |

05 |

04 |

02 |

40 |

|

00 |

00 |

|

|

|

07 |

05 |

05 |

02 |

40 |

00 |

|

00 |

07 |

|

|

|

05 |

06 |

02 |

40 |

00 |

00 |

|

07 |

05 |

|

|

|

07 |

02 |

40 |

00 |

00 |

07 |

|

05 |

89 |

|

|

|

02 |

40 |

00 |

00 |

07 |

05 |

|

0A |

02 |

|

|

|

40 |

00 |

00 |

07 |

05 |

|

0B |

|

02 |

40 |

|

|

00 |

00 |

07 |

05 |

0C |

02 |

|

40 |

00 |

|

|

|

00 |

|

|

|

|

|

|

|

|

|

|

8.11.Set Address

Table 18. Set Address

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

00 |

05 |

addrL |

addrH |

00 |

00 |

00 |

|

00 |

|

Note: No data transaction.

8.12.Set Interface 0

Table 19. Set Interface 0

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

01 |

0B |

00 |

00 |

00 |

00 |

00 |

|

00 |

|

Note: No data transaction.

8.13.Set Feature Device

Table 20. Set Feature Device

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

00 |

03 |

01 |

00 |

00 |

00 |

00 |

|

00 |

|

Note: No data transaction.

Wireless LAN Network Interface Controller |

16 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

8.14.Clear Feature Device

Table 21. Clear Feature Device

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

00 |

01 |

01 |

00 |

00 |

00 |

00 |

|

00 |

|

Note: No data transaction.

8.15.Set Config 0

Table 22. Set Config 0

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

00 |

09 |

00 |

02 |

00 |

00 |

00 |

|

00 |

|

Note: No data transaction.

8.16.Set Config 1

Table 23. Set Config 1

Setup Transaction

BmReq |

bReq |

wValueL |

wValueH |

wIndexL |

wIndexH |

|

wLengthL |

|

wLengthH |

00 |

09 |

01 |

00 |

00 |

00 |

00 |

|

00 |

|

Note: No data transaction.

Wireless LAN Network Interface Controller |

17 |

Track ID: JATR-1076-21 Rev. 1.0 |

RTL8187B

Datasheet

9. EEPROM (93C46 or 93C56) Contents

The RTL8187B supports the attachment of an external EEPROM. The 93C46 is a 1Kbit EEPROM (the 93C56 is a 2Kbit EEPROM). The EEPROM interface provides the ability for the RTL8187B to read from, and write data to, an external serial EEPROM device. If the EEPROM is not present, the RTL8187B initialization uses default values for the Operational Registers. Software can read and write to the EEPROM using “bit-bang” accesses via the 9346CR Register.

Although it is actually addressed by words, its contents are listed below by bytes for convenience. After the initial power on or auto-load command in the 9346CR, the RTL8187B performs a series of EEPROM read operations from the 93C46 (93C56).

Note: It is suggested to obtain Realtek approval before changing the default settings of the EEPROM.

|

|

|

Table 24. EEPROM (93C46 or 93C56) Contents |

|||||

|

Bytes |

Contents |

|

Description |

|

|

|

|

|

00h |

29h |

|

These 2 bytes contain the ID code word for the RTL8187B. The RTL8187B will load |

|

|||

|

01h |

81h |

|

the contents of the EEPROM into the corresponding location if the ID word (8129h) is |

|

|||

|

|

|

|

correct. |

|

|

|

|

|

02h-03h |

VID |

|

USB Vendor ID. |

|

|

|

|

|

04h-05h |

DID |

|

USB Device ID. |

|

|

|

|

|

06h |

ChannelPlan |

|

Channel Plan: Map of channels to be scanned. |

|

|

||

|

07h |

Reserved |

|

- |

|

|

|

|

|

08h |

Reserved |

|

- |

|

|

|

|

|

09h |

Version |

|

Bit [7:6] Interface Selection |

|

|

||

|

|

|

|

00 : USB |

|

|

|

|

|

|

|

|

01 : Mini Card |

|

|

|

|

|

|

|

|

02 : Reserved |

|

|

|

|

|

|

|

|

03 : Reserved |

|

|

|

|

|

|

|

|

Bit [5:0] The EEPROM version. |

|

|

||

|

0Ah |

Tx Power Base |

|

Tx power of the serving base station. |

|

|

||

|

0Bh |

Reserved |

|

- |

|

|

|

|

|

0Ch |

RFChipID |

|

RF Chip ID. |

|

|

|

|

|

|

|

|

The identifier of the RF chip. |

|

|

||

|

0Dh |

CONFIG3 |

|

RTL8187B Configuration register 3. |

|

|

||

|

|

|

|

Operational register FF59h. |

|

|

||

|

0Eh~13h |

MAC Address |

|

MAC Address. |

|

|

|

|

|

|

|

|

After the auto-load command or a hardware reset, the RTL8187B loads MAC |

|

|||

|

|

|

|

Addresses to IDR0~IDR5 of the I/O registers of the RTL8187B. |

|

|||

|

14h |

TxPower12 |

|

Transmit Power Level for 802.11b(g)-defined channel_ID 12 |

|

|||

|

|

|

|

(center frequency=2467MHz). |

|

|

||

|

15h |

CONFIG1 |

|

RTL8187B Configuration register 1. |

|

|

||

|

|

|

|

Operational register FF52h. |

|

|

||

|

|

|

|

Bit[5:2] : USB receive sensitivity |

|

|

||

|

16h~17h |

CRC |

|

16-bit CRC value of EEPROM content. Reserved for Software use. |

|

|||

|

18h |

CONFIG2 |

|

RTL8187B Configuration register 2. |

|

|

||

|

|

|

|

Operational register FF53h. |

|

|

||

|

|

|

|

|

|

|

Track ID: JATR-1076-21 Rev. 1.0 |

|

Wireless LAN Network Interface Controller |

18 |

|

||||||

RTL8187B

Datasheet

|

Bytes |

Contents |

Description |

|

|

|

|

|

19h |

CONFIG4 |

RTL8187B Configuration register 4. |

|

|

||

|

|

|

Operational register FF5Ah. |

|

|

||

|

1Ah~1Dh |

ANA_PARM |

Analog Parameter for the RTL8187B. |

|

|

||

|

|

|

Operational registers of the RTL8187B are from 54h to 57h. |

|

|||

|

|

|

Reserved. Do not change this field without Realtek approval. |

|

|||

|

1Eh |

TESTR |

RTL8187B Test Mode Register. |

|

|

||

|

|

|

Operational register FF5Bh. |

|

|

||

|

|

|

Reserved. Do not change this field without Realtek approval. |

|

|||

|

1Fh |

CONFIG5 |

RTL8187B Configuration register 5. |

|

|

||

|

|

|

Operational register FFD8h. |

|

|

||

|

20h |

TxPower36 |

Transmit Power Level for 802.11a-defined channel_ID 36 |

|

|||

|

|

|

(Center frequency=5180MHz). |

|

|

||

|

21h |

TxPower40 |

Transmit Power Level for 802.11a-defined channel_ID 40 |

|

|||

|

|

|

(Center frequency=5200MHz). |

|

|

||

|

22h |

TxPower44 |

Transmit Power Level for 802.11a-defined channel_ID 44 |

|

|||

|

|

|

(Center frequency=5220MHz). |

|

|

||

|

23h |

TxPower48 |

Transmit Power Level for 802.11a-defined channel_ID 48 |

|

|||

|

|

|

(Center frequency=5240MHz). |

|

|

||

|

24h |

TxPower52 |

Transmit Power Level for 802.11a-defined channel_ID 52 |

|

|||

|

|

|

(Center frequency=5260MHz). |

|

|

||

|

25h |

TxPower56 |

Transmit Power Level for 802.11a-defined channel_ID 56 |

|

|||

|

|

|

(Center frequency=5280MHz). |

|

|

||

|

26h |

TxPower60 |

Transmit Power Level for 802.11a-defined channel_ID 60 |

|

|||

|

|

|

(Center frequency=5300MHz). |

|

|

||

|

27h |

TxPower64 |

Transmit Power Level for 802.11a-defined channel_ID 64 |

|

|||

|

|

|

(Center frequency=5320MHz). |

|

|

||

|

28h |

TxPower149 |

Transmit Power Level for 802.11a-defined channel_ID 149 |

|

|||

|

|

|

(Center frequency=5745MHz). |

|

|

||

|

29h |

TxPower153 |

Transmit Power Level for 802.11a-defined channel_ID 153 |

|

|||

|

|

|

(Center frequency=5765MHz). |

|

|

||

|

2Ah |

TxPower157 |

Transmit Power Level for 802.11a-defined channel_ID 157 |

|

|||

|

|

|

(Center frequency=5785MHz). |

|

|

||

|

2Bh |

TxPower161 |

Transmit Power Level for 802.11a-defined channel_ID 161 |

|

|||

|

|

|

(Center frequency=5805MHz). |

|

|

||

|

2Ch |

TxPower1 |

Transmit Power Level for 802.11b(g)-defined channel_ID 1 |

|

|||

|

|

|

(center frequency=2412MHz). |

|

|

||

|

2Dh |

TxPower2 |

Transmit Power Level for 802.11b(g)-defined channel_ID 2 |

|

|||

|

|

|

(center frequency=2417MHz). |

|

|

||

|

2Eh |

TxPower3 |

Transmit Power Level for 802.11b(g)-defined channel_ID 3 |

|

|||

|

|

|

(center frequency=2422MHz). |

|

|

||

|

2Fh |

TxPower4 |

Transmit Power Level for 802.11b(g)-defined channel_ID 4 |

|

|||

|

|

|

(center frequency=2427MHz). |

|

|

||

|

30h |

TxPower5 |

Transmit Power Level for 802.11b(g)-defined channel_ID 5 |

|

|||

|

|

|

(center frequency=2432MHz). |

|

|

||

|

31h |

TxPower6 |

Transmit Power Level for 802.11b(g)-defined channel_ID 6 |

|

|||

|

|

|

(center frequency=2437MHz). |

|

|

||

|

|

|

|

|

|

Track ID: JATR-1076-21 Rev. 1.0 |

|

Wireless LAN Network Interface Controller |

19 |

|

|||||

RTL8187B

Datasheet

Bytes |

Contents |

32h-35h |

ANA_PARM2 |

36h TxPower11

37h Optional functions

38h |

TxPower13 |

|

|

39h |

TxPower14 |

|

|

3Ah-73h |

Manufacture String |

|

& |

|

Product String |

|

|

74h-79h |

- |

7Ah |

TxPower7 |

|

|

7Bh |

TxPower8 |

|

|

7Ch |

TxPower9 |

|

|

7Dh |

TxPower10 |

|

|

7Eh |

CustomerID |

7Fh |

SW Antenna |

|

Diversity |

Description

Analog Parameter 2 for RTL8187B.