RTL8309SB

SINGLE-CHIP 9-PORT 10/100MBPS SWITCH CONTROLLER

DATASHEET

Rev. 1.4

09 July 2004

Track ID: JATR-1076-21

RTL8309SB

Datasheet

COPYRIGHT

©2004 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted,

transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written

permission of Realtek Semiconductor Corp.

DISCLAIMER

Realtek provides this document “as is”, without warranty of any kind, neither expressed nor implied, including, but not limited

to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this

document at any time. This document could include technical inaccuracies or typographical errors.

TRADEMARKS

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are

trademarks/registered trademarks of their respective owners.

USING THIS DOCUMENT

This document provides detailed user guidelines to achieve the best performance when implementing a 2-layer board PC

design with the RTL8309SB Single-Chip 9-port 10/100Mbps Switch Controller.

Though every effort has been made to assure that this document is current and accurate, more information may have become

available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional

information that may help in the development process.

Single-Chip 9-Port 10/100Mbps Switch Controller ii Track ID: JATR-1076-21 Rev. 1.4

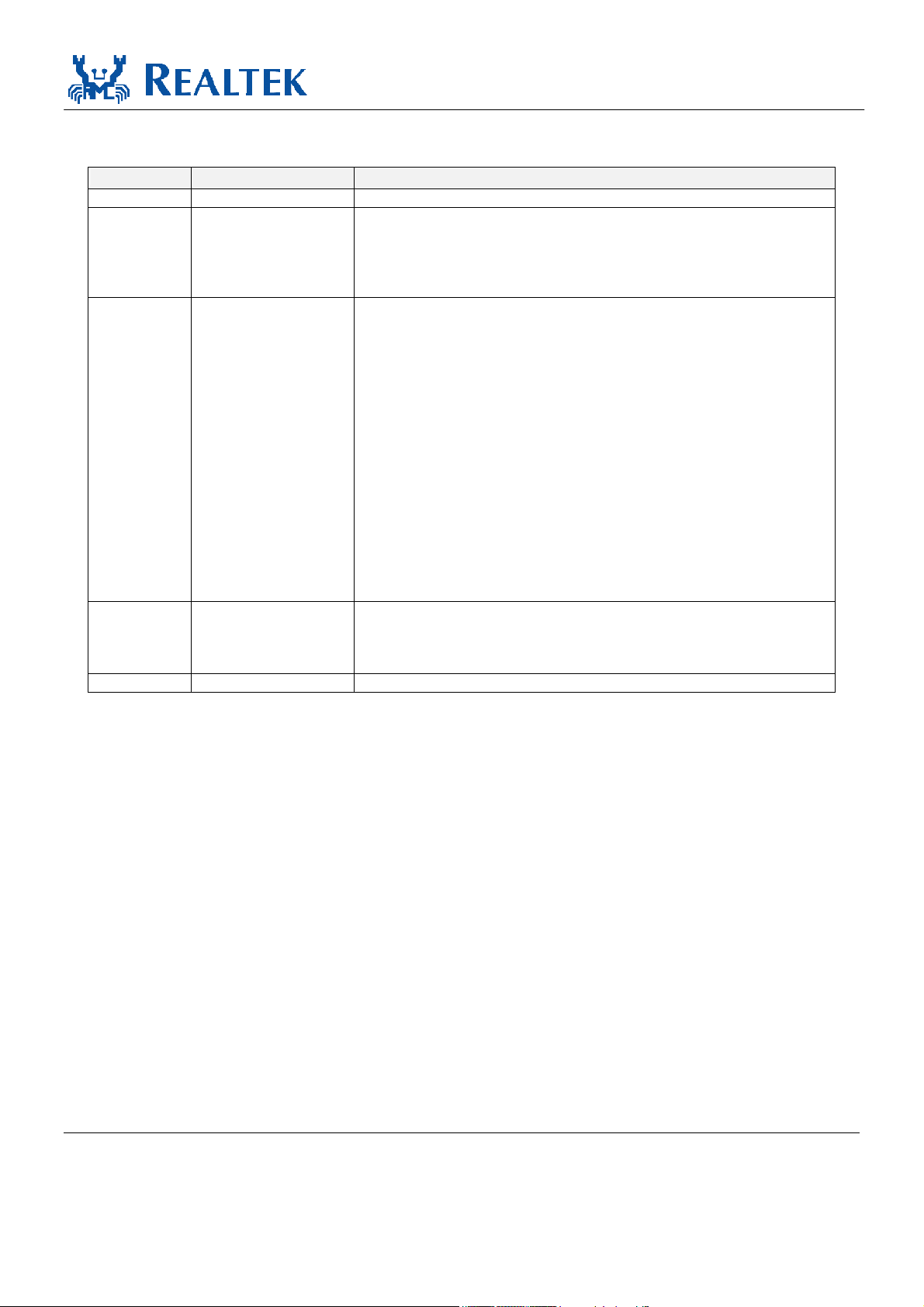

REVISION HISTORY

RTL8309SB

Datasheet

Revision Release Date

1.0 2003/04/12 First release.

1.1 2003/05/15 Revised pin descriptions.

1.2 2003/12/01 Revised pin description of Dis_VLAN.

1.3 2004/06/10 Removed PHY0~PHY7 REG2 and REG3 info.

1.4 2004/07/09 Removed QoS feature for IPv6.

Summary

Revised description for Bi-color LED.

New Bi-color LED Reference Schematic figure.

Add 3.3V items to electrical characteristics.

Add thermal operating range temperatures.

Revised pin description of Max_Pause_Count.

Revised default VLAN membership configuration for Disable VLAN

function in PHY register 16.11.

Update default value of Differential Service Code Point [B] in EEPROM

and PHY registers.

Update default value of VLAN ID [A] membership in EERPOM.

Update default value of ISP MAC Address in EEPROM.

Update default value of Port 8 VLAN Index in EEPROM.

Revised the definition for WAN port specification in EEPROM and PHY

registers.

Revised the definition for CPU port specification in EEPROM and PHY

registers.

Removed the Bypass CRC function in EEPROM.

Removed the Good Link Quality Threshold function in EEPROM and

PHY registers.

Add explanation of Indirect Access Data in PHY 7 Register 17~20.

Update pin number ordering on Pin Description Table.

Change the term “Auto MDIX” to “Crossover Detection and auto

correction”.

Single-Chip 9-Port 10/100Mbps Switch Controller iii Track ID: JATR-1076-21 Rev . 1.4

RTL8309SB

Datasheet

Table of Contents

1. GENERAL D ESCRIPTION................................................................................................................................................1

2. FEATURES...........................................................................................................................................................................3

3. BLOCK DIAGRAM.............................................................................................................................................................4

4. PIN ASSIGNMENTS...........................................................................................................................................................5

5. PIN DESCRIPTIONS..........................................................................................................................................................7

5.1. MEDIA CONNECTION PINS ..........................................................................................................................................7

5.2. MII PORT MAC INTERFACE PINS ...............................................................................................................................7

5.3. MISCELLANEOUS PINS ................................................................................................................................................9

5.4. PORT LED PINS ..........................................................................................................................................................9

5.5. SERIAL EEPROM AND SMI PINS .............................................................................................................................11

5.6. STRAPPING PINS........................................................................................................................................................12

5.7. POWER PINS..............................................................................................................................................................16

6. EEPROM REGISTER DESCRIPTION..........................................................................................................................17

6.1. GLOBAL CONTROL REGISTERS..................................................................................................................................17

6.1.1. Global Control Register0...................................................................................................................................17

6.1.2. Global Control Register1...................................................................................................................................17

6.1.3. Global Control Register2...................................................................................................................................18

6.1.4. Global Control Register3...................................................................................................................................18

6.1.5. Global Control Register4...................................................................................................................................19

6.1.6. Global Control Register5...................................................................................................................................19

6.1.7. Global Control Register6...................................................................................................................................19

6.1.8. Global Control Register7...................................................................................................................................19

6.2. PORT 0~7 CONTROL PINS..........................................................................................................................................20

6.2.1. Port 0 Control 0..................................................................................................................................................20

6.2.2. Port 0 Control 1..................................................................................................................................................20

6.2.3. Port 0 Control 2..................................................................................................................................................21

6.2.4. Port 0 Control 3..................................................................................................................................................21

6.2.5. Port 0 Control 4..................................................................................................................................................21

6.2.6. IP Addr ess...........................................................................................................................................................22

6.2.7. Port 1 Control 0..................................................................................................................................................23

6.2.8. Port 1 Control 1..................................................................................................................................................23

Single-Chip 9-Port 10/100Mbps Switch Controller iv Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

6.2.9. Port 1 Control 2..................................................................................................................................................24

6.2.10. Port 1 Control 3..................................................................................................................................................24

6.2.11. Port 1 Control 4..................................................................................................................................................24

6.2.12. IP Mask ..............................................................................................................................................................25

6.2.13. Port 2 Control 0..................................................................................................................................................25

6.2.14. Port 2 Control 1..................................................................................................................................................26

6.2.15. Port 2 Control 2..................................................................................................................................................26

6.2.16. Port 2 Control 3..................................................................................................................................................26

6.2.17. Port 2 Control 4..................................................................................................................................................27

6.2.18. Switch MAC Address ..........................................................................................................................................27

6.2.19. Port 3 Control 0..................................................................................................................................................28

6.2.20. Port 3 Control 1..................................................................................................................................................28

6.2.21. Port 3 Control 2..................................................................................................................................................29

6.2.22. Port 3 Control 3..................................................................................................................................................29

6.2.23. Port 3 Control 4..................................................................................................................................................29

6.2.24. ISP MAC Address...............................................................................................................................................30

6.2.25. Port 4 Control 0..................................................................................................................................................30

6.2.26. Port 4 Control 1..................................................................................................................................................30

6.2.27. Port 4 Control 2..................................................................................................................................................31

6.2.28. Port 4 Control 3..................................................................................................................................................31

6.2.29. Port 4 Control 4..................................................................................................................................................31

6.3. MII PORT CONTROL PINS..........................................................................................................................................32

6.3.1. MII Port Control 0..............................................................................................................................................32

6.3.2. MII Port Control 1..............................................................................................................................................32

6.3.3. MII Port Control 2..............................................................................................................................................33

6.3.4. CPU Port and WAN Port....................................................................................................................................33

6.4. PORT 5~7 CONTROL PINS..........................................................................................................................................34

6.4.1. Port 5 Control 0..................................................................................................................................................34

6.4.2. Port 5 Control 1..................................................................................................................................................34

6.4.3. Port 5 Control 2..................................................................................................................................................35

6.4.4. Port 5 Control 3..................................................................................................................................................35

6.4.5. Port 5 Control 4..................................................................................................................................................35

6.4.6. Port 6 Control 0..................................................................................................................................................36

6.4.7. Port 6 Control 1..................................................................................................................................................36

6.4.8. Port 6 Control 2..................................................................................................................................................36

Single-Chip 9-Port 10/100Mbps Switch Controller v Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

6.4.9. Port 6 Control 3..................................................................................................................................................37

6.4.10. Port 6 Control 4..................................................................................................................................................37

6.4.11. Port 7 Control 0..................................................................................................................................................38

6.4.12. Port 7 Control 1..................................................................................................................................................38

6.4.13. Port 7 Control 2..................................................................................................................................................38

6.4.14. Port 7 Control 3..................................................................................................................................................39

6.4.15. Port 7 Control 4..................................................................................................................................................39

7. PHY REGISTERS DESCRIPTION.................................................................................................................................40

7.1. PHY 0 REGISTERS ....................................................................................................................................................40

7.1.1. PHY 0 Register 0: Control.................................................................................................................................. 40

7.1.2. PHY 0 Register 1: Status ....................................................................................................................................41

7.1.3. PHY 0 Register 4: Auto-Negotiation Advertisement...........................................................................................42

7.1.4. PHY 0 Register 5: Auto-Negotiation Link Partner Ability..................................................................................42

7.1.5. PHY 0 Register 6: Auto-Negotiation Expansion.................................................................................................43

7.1.6. PHY 0 Register 16: Global Control 0.................................................................................................................43

7.1.7. PHY 0 Register 17: Global Control 1.................................................................................................................45

7.1.8. PHY 0 Register 18: Global Control 2.................................................................................................................46

7.1.9. PHY 0 Register 19: Global Control 3.................................................................................................................46

7.1.10. PHY 0 Register 22: Port 0 Control 0..................................................................................................................46

7.1.11. PHY 0 Register 23: Port 0 Control 1..................................................................................................................48

7.1.12. PHY 0 Register 24: Port 0 Control 2 & VLAN Entry [A]...................................................................................48

7.1.13. PHY 0 Register 25: VLAN Entry [A]..................................................................................................................48

7.2. PHY 1 REGISTERS ....................................................................................................................................................49

7.2.1. PHY 1 Register 0: Control.................................................................................................................................. 49

7.2.2. PHY 1 Register 1: Status ....................................................................................................................................49

7.2.3. PHY 1 Register 4: Auto-Negotiation Advertisement...........................................................................................49

7.2.4. PHY 1 Register 5: Auto-Negotiation Link Partner Ability..................................................................................49

7.2.5. PHY 1 Register 6: Auto-Negotiation Expansion.................................................................................................49

7.2.6. PHY 1 Register 16~17: IP Priority Address [A].................................................................................................49

7.2.7. PHY 1 Register 18~19: IP Priority Address [B].................................................................................................49

7.2.8. PHY 1 Register 22: Port 1 Control 0..................................................................................................................50

7.2.9. PHY 1 Register 23: Port 1 Control 1..................................................................................................................50

7.2.10. PHY 1 Register 24: Port 1 Control 2 & VLAN Entry [B]...................................................................................50

7.2.11. PHY 1 Register 25: VLAN Entry [B]..................................................................................................................50

Single-Chip 9-Port 10/100Mbps Switch Controller vi Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

7.3. PHY 2 REGISTERS ....................................................................................................................................................50

7.3.1. PHY 2 Register 0: Control.................................................................................................................................. 50

7.3.2. PHY 2 Register 1: Status ....................................................................................................................................50

7.3.3. PHY 2 Register 4: Auto-Negotiation Advertisement...........................................................................................50

7.3.4. PHY 2 Register 5: Auto-Negotiation Link Partner Ability..................................................................................51

7.3.5. PHY 2 Register 6: Auto-Negotiation Expansion.................................................................................................51

7.3.6. PHY 2 Register 16~17: IP Priority Mask [A] ....................................................................................................51

7.3.7. PHY 2 Register 18~19: IP Priority Mask [B] ....................................................................................................51

7.3.8. PHY 2 Register 22: Port 2 Control 0..................................................................................................................51

7.3.9. PHY 2 Register 23: Port 2 Control 1..................................................................................................................51

7.3.10. PHY 2 Register 24: Port 2 Control 2 & VLAN Entry [C]...................................................................................52

7.3.11. PHY 2 Register 25: VLAN Entry [C]..................................................................................................................52

7.4. PHY 3 REGISTERS ....................................................................................................................................................52

7.4.1. PHY 3 Register 0: Control.................................................................................................................................. 52

7.4.2. PHY 3 Register 1: Status ....................................................................................................................................52

7.4.3. PHY 3 Register 4: Auto-Negotiation Advertisement...........................................................................................52

7.4.4. PHY 3 Register 5: Auto-Negotiation Link Partner Ability..................................................................................52

7.4.5. PHY 3 Register 6: Auto-Negotiation Expansion.................................................................................................52

7.4.6. PHY 3 Register 16~18: Switch MAC Address ....................................................................................................52

7.4.7. PHY 3 Register 22: Port 3 Control 0..................................................................................................................53

7.4.8. PHY 3 Register 23: Port 3 Control 1..................................................................................................................53

7.4.9. PHY 3 Register 24: Port 3 Control 2 & VLAN Entry [D]..................................................................................53

7.4.10. PHY 3 Register 25: VLAN Entry [D]..................................................................................................................53

7.5. PHY 4 REGISTERS ....................................................................................................................................................54

7.5.1. PHY 4 Register 0: Control.................................................................................................................................. 54

7.5.2. PHY 4 Register 1: Status ....................................................................................................................................54

7.5.3. PHY 4 Register 4: Auto-Negotiation Advertisement...........................................................................................54

7.5.4. PHY 4 Register 5: Auto-Negotiation Link Partner Ability..................................................................................54

7.5.5. PHY 4 Register 6: Auto-Negotiation Expansion.................................................................................................54

7.5.6. PHY 4 Register 16~18: ISP MAC Address......................................................................................................... 54

7.5.7. PHY 4 Register 22: Port 4 Control 0..................................................................................................................54

7.5.8. PHY 4 Register 23: Port 4 Control 1..................................................................................................................54

7.5.9. PHY 4 Register 24: Port 4 Control 2 & VLAN Entry [E]...................................................................................55

7.5.10. PHY 4 Register 25: VLAN Entry [E]..................................................................................................................55

Single-Chip 9-Port 10/100Mbps Switch Controller vii Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

7.6. PHY 5 REGISTERS ....................................................................................................................................................55

7.6.1. PHY 5 Register 0: Control.................................................................................................................................. 55

7.6.2. PHY 5 Register 1: Status ....................................................................................................................................55

7.6.3. PHY 5 Register 4: Auto-Negotiation Advertisement...........................................................................................55

7.6.4. PHY 5 Register 5: Auto-Negotiation Link Partner Ability..................................................................................55

7.6.5. PHY 5 Register 6: Auto-Negotiation Expansion.................................................................................................55

7.6.6. PHY 5 Register 16: MII Port Control 0..............................................................................................................56

7.6.7. PHY 5 Register 17: MII Port Control 1 & VLAN Entry [I]................................................................................57

7.6.8. PHY 5 Register 18: VLAN Entry [I]...................................................................................................................57

7.6.9. PHY 5 Register 19: CPU Port & WAN Port.......................................................................................................57

7.6.10. PHY 5 Register 22: Port 5 Control 0..................................................................................................................58

7.6.11. PHY 5 Register 23: Port 5 Control 1..................................................................................................................58

7.6.12. PHY 5 Register 24: Port 5 Control 2 & VLAN Entry [F]...................................................................................58

7.6.13. PHY 5 Register 25: VLAN Entry [F]..................................................................................................................58

7.7. PHY 6 REGISTERS ....................................................................................................................................................59

7.7.1. PHY 6 Register 0: Control.................................................................................................................................. 59

7.7.2. PHY 6 Register 1: Status ....................................................................................................................................59

7.7.3. PHY 6 Register 4: Auto-Negotiation Advertisement...........................................................................................59

7.7.4. PHY 6 Register 5: Auto-Negotiation Link Partner Ability..................................................................................59

7.7.5. PHY 6 Register 6: Auto-Negotiation Expansion.................................................................................................59

7.7.6. PHY 6 Register 22: Port 6 Control 0..................................................................................................................59

7.7.7. PHY 6 Register 23: Port 6 Control 1..................................................................................................................59

7.7.8. PHY 6 Register 24: Port 6 Control 2 & VLAN Entry [G]..................................................................................60

7.7.9. PHY 6 Register 25: VLAN Entry [G]..................................................................................................................60

7.8. PHY 7 REGISTERS ....................................................................................................................................................61

7.8.1. PHY 7 Register 0: Control.................................................................................................................................. 61

7.8.2. PHY 7 Register 1: Status ....................................................................................................................................61

7.8.3. PHY 7 Register 4: Auto-Negotiation Advertisement...........................................................................................61

7.8.4. PHY 7 Register 5: Auto-Negotiation Link Partner Ability..................................................................................61

7.8.5. PHY 7 Register 6: Auto-Negotiation Expansion.................................................................................................61

7.8.6. PHY 7 Register 16: indirect Access Control.......................................................................................................61

7.8.7. PHY 7 Register 17~20: Indirect Access Data.....................................................................................................62

7.8.8. PHY 7 Register 22: Port 7 Control 0..................................................................................................................62

7.8.9. PHY 7 Register 23: Port 7 Control 1..................................................................................................................62

Single-Chip 9-Port 10/100Mbps Switch Controller viii Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

7.8.10. PHY 7 Register 24: Port 7 Control 2 & VLAN Entry [H] ..................................................................................62

7.8.11. PHY 7 Register 25: VLAN Entry [H]..................................................................................................................63

7.9. PHY 8 REGISTERS ....................................................................................................................................................63

7.9.1. PHY 8 Register 0: Control.................................................................................................................................. 63

7.9.2. PHY 8 Register 1: Status ....................................................................................................................................64

7.9.3. PHY 8 Register 4: Auto-Negotiation Advertisement...........................................................................................64

7.9.4. MII Port NWay Mode .........................................................................................................................................65

7.9.5. MII Port Force Mode.........................................................................................................................................65

8. FUNCTIONAL DESCRIPTION.......................................................................................................................................66

8.1. PHYSICAL LAYE R TRANSCEIVER FUNCTIONAL OVERVIEW .......................................................................................66

8.1.1. Auto Negotiation for UTP ..................................................................................................................................66

8.1.2. 100Base-Tx T ransmit Function ..........................................................................................................................66

8.1.3. 100Base-Tx Receive Function............................................................................................................................66

8.1.4. 10Base-T T r ansmit Function..............................................................................................................................67

8.1.5. 10Base-T Receive Function................................................................................................................................67

8.1.6. Link Monitor.......................................................................................................................................................67

8.1.7. Power Saving Mode............................................................................................................................................67

8.1.8. Power-Down Mode.............................................................................................................................................67

8.1.9. Auto Crossover Detection...................................................................................................................................68

8.2. SWITCH CORE FUNCTIONAL OVERVIEW....................................................................................................................68

8.2.1. Address Search, Learning, and Aging................................................................................................................68

8.2.2. Flow Control...................................................................................................................................................... 69

8.2.3. Half Duplex Operation.......................................................................................................................................69

8.2.4. Backpressure ......................................................................................................................................................70

8.2.5. UTP Port Status Configuration..........................................................................................................................70

8.2.6. MII Port (The 9th Port)......................................................................................................................................70

8.3. ADVANCED FUNCTIONALITY OVERVIEW...................................................................................................................74

8.3.1. Port-Based VLAN...............................................................................................................................................74

8.3.2. 802.1Q Tagged-VID based VLAN.......................................................................................................................76

8.3.3. QoS Operation....................................................................................................................................................77

8.3.4. Insert/Remove VLAN Priority Tag......................................................................................................................78

8.3.5. Port VID (PVID) ................................................................................................................................................79

8.3.6. Port Trunking.....................................................................................................................................................79

8.3.7. ISP MAC Address Translation............................................................................................................................79

8.3.8. Lookup Table Access...........................................................................................................................................81

Single-Chip 9-Port 10/100Mbps Switch Controller ix Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

8.3.9. Serial Management Interface (SMI)...................................................................................................................81

8.3.10. Broadcast S t orm Control....................................................................................................................................82

8.3.11. Broadcast In/Out Drop.......................................................................................................................................82

8.3.12. EEPROM Configuration Interface.....................................................................................................................83

8.3.13. 24LC02 Device Operation..................................................................................................................................83

8.3.14. Head-of-Line Blocking.......................................................................................................................................84

8.3.15. MII Port Diagnostic Loopback...........................................................................................................................85

8.3.16. Loop Detection...................................................................................................................................................86

8.3.17. LEDs (Light Emitting Diodes)............................................................................................................................87

9. CHARACTERISTICS.......................................................................................................................................................90

9.1. ABSOLUTE MAXIMUM RATI N G S ................................................................................................................................90

9.2. OPERATING RANGE ...................................................................................................................................................90

9.3. DC CHARACTERISTICS .............................................................................................................................................90

9.4. AC CHARACTERISTICS .............................................................................................................................................91

9.5. DIGITAL TIMING CHARACTERISTICS .........................................................................................................................92

9.6. THERMAL CHARACTERISTICS ...................................................................................................................................94

10. SYSTEM APPLICA TIONS...........................................................................................................................................95

11. DESIGN AND LA YOUT GUIDE..................................................................................................................................96

12. MECHANICAL DIMENSIONS................................................................................................................................... 99

12.1. NOTES FOR 128-PIN PQFP DIMENSIONS ................................................................................................................100

Single-Chip 9-Port 10/100Mbps Switch Controller x Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

List of Tables

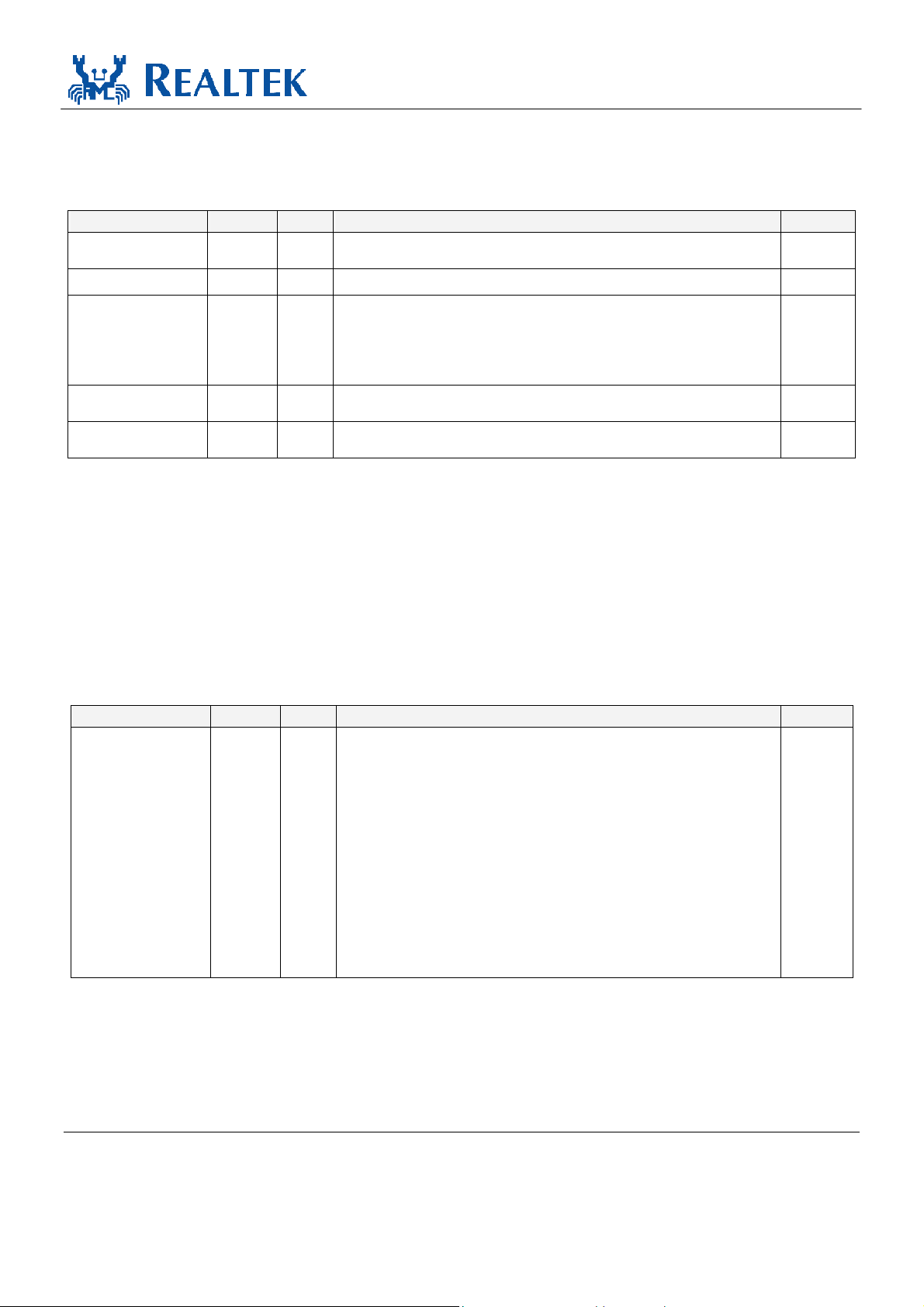

Table 1. Pin Assignments.............................................................................................................................6

Table 2. Media Connection Pins..................................................................................................................7

Table 3. MII Port MAC Interface Pins ........................................................................................................7

Table 4. Miscellaneous Pins.........................................................................................................................9

Table 5. Port LED Pins ................................................................................................................................9

Table 6. Serial EEPROM and SMI Pins ....................................................................................................11

Table 7. Strapping Pins ..............................................................................................................................12

Table 8. Power Pins ...................................................................................................................................16

Table 9. Global Control Register0 .............................................................................................................17

Table 10. Global Control Register1 .............................................................................................................17

Table 11. Global Control Register2 .............................................................................................................18

Table 12. Global Control Register3 .............................................................................................................18

Table 13. Global Control Register4 .............................................................................................................19

Table 14. Global Control Register5 .............................................................................................................19

Table 15. Global Control Register6 .............................................................................................................19

Table 16. Global Control Register7 .............................................................................................................19

Table 17. Port 0 Control 0............................................................................................................................20

Table 18. Port 0 Control 1............................................................................................................................20

Table 19. Port 0 Control 2............................................................................................................................21

Table 20. Port 0 Control 3............................................................................................................................21

Table 21. Port 0 Control 4............................................................................................................................21

Table 22. IP Address ....................................................................................................................................22

Table 23. Port 1 Control 0............................................................................................................................23

Table 24. Port 1 Control 1............................................................................................................................23

Table 25. Port 1 Control 2............................................................................................................................24

Table 26. Port 1 Control 3............................................................................................................................24

Table 27. Port 1 Control 4............................................................................................................................24

Table 28. IP Mask ........................................................................................................................................25

Table 29. Port 2 Control 0............................................................................................................................25

Table 30. Port 2 Control 1............................................................................................................................26

Table 31. Port 2 Control 2............................................................................................................................26

Table 32. Port 2 Control 3............................................................................................................................26

Table 33. Port 2 Control 4............................................................................................................................27

Single-Chip 9-Port 10/100Mbps Switch Controller xi Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

Table 34. Switch MAC Address ..................................................................................................................27

Table 35. Port 3 Control 0............................................................................................................................28

Table 36. Port 3 Control 1............................................................................................................................28

Table 37. Port 3 Control 2............................................................................................................................29

Table 38. Port 3 Control 3............................................................................................................................29

Table 39. Port 3 Control 4............................................................................................................................29

Table 40. ISP MAC Address........................................................................................................................30

Table 41. Port 4 Control 0............................................................................................................................30

Table 42. Port 4 Control 1............................................................................................................................30

Table 43. Port 4 Control 2............................................................................................................................31

Table 44. Port 4 Control 3............................................................................................................................31

Table 45. Port 4 Control 4............................................................................................................................31

Table 46. MII Port Control 0 .......................................................................................................................32

Table 47. MII Port Control 1 .......................................................................................................................32

Table 48. MII Port Control 2 .......................................................................................................................33

Table 49. CPU Port and WAN Port..............................................................................................................33

Table 50. Port 5 Control 0............................................................................................................................34

Table 51. Port 5 Control 1............................................................................................................................34

Table 52. Port 5 Control 2............................................................................................................................35

Table 53. Port 5 Control 3............................................................................................................................35

Table 54. Port 5 Control 4............................................................................................................................35

Table 55. Port 6 Control 0............................................................................................................................36

Table 56. Port 6 Control 1............................................................................................................................36

Table 57. Port 6 Control 2............................................................................................................................36

Table 58. Port 6 Control 3............................................................................................................................37

Table 59. Port 6 Control 4............................................................................................................................37

Table 60. Port 7 Control 0............................................................................................................................38

Table 61. Port 7 Control 1............................................................................................................................38

Table 62. Port 7 Control 2............................................................................................................................38

Table 63. Port 7 Control 3............................................................................................................................39

Table 64. Port 7 Control 4............................................................................................................................39

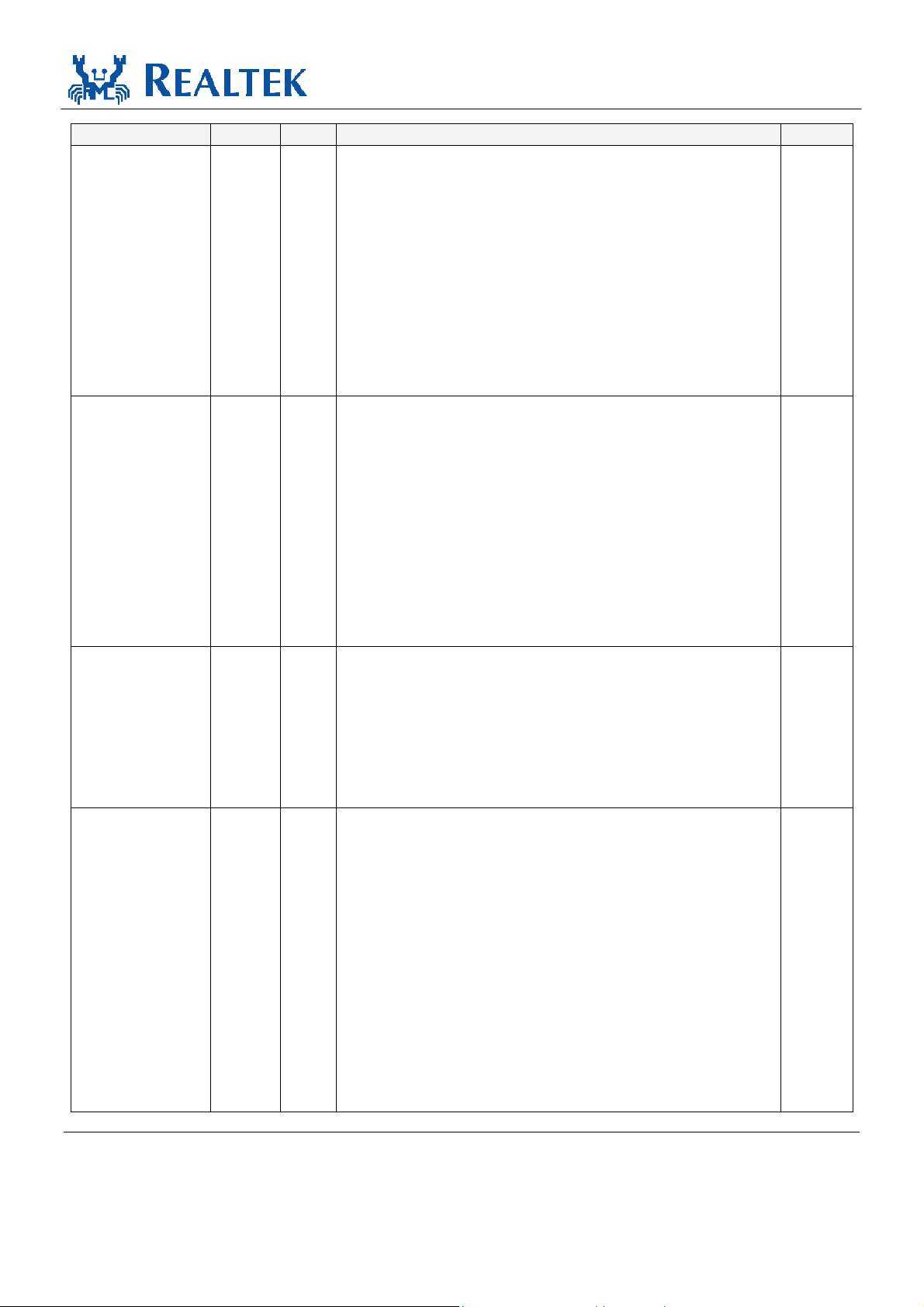

Table 65. PHY 0 Register 0: Control...........................................................................................................40

Table 66. PHY 0 Register 1: Status .............................................................................................................41

Table 67. PHY 0 Register 4: Auto-Negotiation Advertisement...................................................................42

Table 68. PHY 0 Register 5: Auto-Negotiation Link Partner Ability..........................................................42

Single-Chip 9-Port 10/100Mbps Switch Controller xii Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

Table 69. PHY 0 Register 6: Auto-Negotiation Expansion .........................................................................43

Table 70. PHY 0 Register 16: Global Control 0..........................................................................................43

Table 71. PHY 0 Register 17: Global Control 1..........................................................................................45

Table 72. PHY 0 Register 18: Global Control 2..........................................................................................46

Table 73. PHY 0 Register 19: Global Control 3..........................................................................................46

Table 74. PHY 0 Register 22: Port 0 Control 0 ...........................................................................................46

Table 75. PHY 0 Register 23: Port 0 Control 1 ...........................................................................................48

Table 76. PHY 0 Register 24: Port 0 Control 2 & VLAN Entry [A]...........................................................48

Table 77. PHY 0 Register 25: VLAN Entry [A]..........................................................................................48

Table 78. PHY 1 Register 16~17: IP Priority Address [A]..........................................................................49

Table 79. PHY 1 Register 18~19: IP Priority Address [B] ..........................................................................49

Table 80. PHY 1 Register 24: Port 1 Control 2 & VLAN Entry [B]...........................................................50

Table 81. PHY 1 Register 25: VLAN Entry [B]..........................................................................................50

Table 82. PHY 2 Register 16~17: IP Priority Mask [A]..............................................................................51

Table 83. PHY 2 Register 18~19: IP Priority Mask [B] ..............................................................................51

Table 84. PHY 2 Register 24: Port 2 Control 2 & VLAN Entry [C]...........................................................52

Table 85. PHY 2 Register 25: VLAN Entry [C]..........................................................................................52

Table 86. PHY 3 Register 16~18: Switch MAC Address ............................................................................53

Table 87. PHY 3 Register 24: Port 3 Control 2 & VLAN Entry [D]...........................................................53

Table 88. PHY 3 Register 25: VLAN Entry [D]..........................................................................................53

Table 89. PHY 4 Register 16~18: ISP MAC Address .................................................................................54

Table 90. PHY 4 Register 24: Port 4 Control 2 & VLAN Entry [E] ...........................................................55

Table 91. PHY 4 Register 25: VLAN Entry [E] ..........................................................................................55

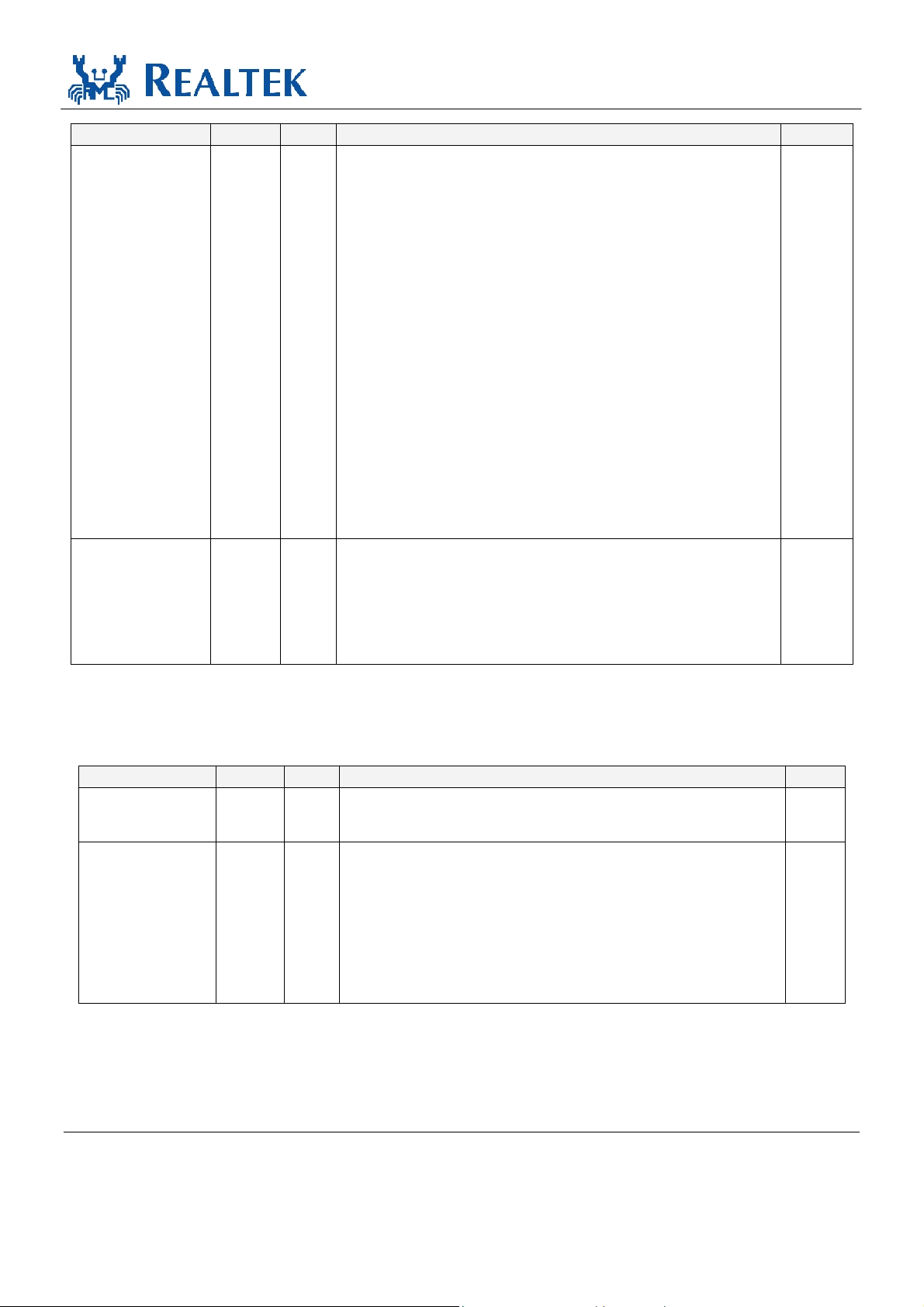

Table 92. PHY 5 Register 16: MII Port Control 0.......................................................................................56

Table 93. PHY 5 Register 17: MII Port Control 1 & VLAN Entry [I] ........................................................57

Table 94. PHY 5 Register 18: VLAN Entry [I] ...........................................................................................57

Table 95. PHY 5 Register 19: CPU Port & WAN Port ................................................................................57

Table 96. PHY 5 Register 24: Port 5 Control 2 & VLAN Entry [F] ...........................................................58

Table 97. PHY 5 Register 25: VLAN Entry [F] ..........................................................................................58

Table 98. PHY 6 Register 24: Port 6 Control 2 & VLAN Entry [G]...........................................................60

Table 99. PHY 6 Register 25: VLAN Entry [G]..........................................................................................60

Table 100. PHY 7 Register 16: Indirect Access Control .............................................................................61

Table 101. PHY 7 Register 17~20: Indirect Access Data............................................................................62

Table 102. PHY 7 Register 24: Port 7 Control 2 & VLAN Entry [H].........................................................62

Table 103. PHY 7 Register 25: VLAN Entry [H]........................................................................................63

Single-Chip 9-Port 10/100Mbps Switch Controller xiii Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

Table 104. PHY 8 Register 0: Control.........................................................................................................63

Table 105. PHY 8 Register 1: Status............................................................................................................64

Table 106. PHY 8 Register 4: Auto-Negotiation Advertisement.................................................................64

Table 107. MII Port NWay Mode ................................................................................................................65

Table 108. MII Port Force Mode .................................................................................................................65

Table 109. 802.1Q VLAN Tag Frame Format .............................................................................................78

Table 110. IPv4 Frame Format ....................................................................................................................78

Table 111. SMI Read/Write Cycles..............................................................................................................81

Table 112. Loop Frame Format ...................................................................................................................86

Table 113. Speed and Bi-Color Link/Act Truth Table.................................................................................88

Table 114. Absolute Maximum Ratings.......................................................................................................90

Table 115. Operating Range ........................................................................................................................90

Table 116. DC Characteristics .....................................................................................................................90

Table 117. AC Characteristics......................................................................................................................91

Table 118. Digital Timing Characteristics ...................................................................................................93

Table 119. Thermal Operating Range..........................................................................................................94

Table 120. Thermal Resistance....................................................................................................................95

Single-Chip 9-Port 10/100Mbps Switch Controller xiv Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

List of Figures

Figure 1. Block Diagram .............................................................................................................................4

Figure 2. Pin Assignments ...........................................................................................................................5

Figure 3. MII Port Application ..................................................................................................................71

Figure 4. MII Port Operating Mode Overview..........................................................................................72

Figure 5. VLAN Grouping Example .........................................................................................................75

Figure 6. Tagged and Untagged Packet Forwarding When 802.1Q Tag Aware VLAN is Disabled .........76

Figure 7. ISP MAC Outbound Process......................................................................................................80

Figure 8. ISP MAC Inbound Process.........................................................................................................80

Figure 9. Input Drop vs. Output Drop .......................................................................................................82

Figure 10. Start and Stop Definition............................................................................................................83

Figure 11. Output Acknowledge ..................................................................................................................84

Figure 12. Random Read .............................................................................................................................84

Figure 13. Sequential Read..........................................................................................................................84

Figure 14. MII Port Loopback .....................................................................................................................85

Figure 15. Loop Example ............................................................................................................................86

Figure 16. Floating and Pull-down of LED Pins .........................................................................................87

Figure 17. Two-Pin Bi-Color LED for SPD Floating or Pull-high..............................................................88

Figure 18. Two-Pin Bi-Color LED for SPD Pull-down...............................................................................88

Figure 19. Bi-Color LED Reference Schematic..........................................................................................89

Figure 20. Reception Data Timing of MII/SNI/SMI Interface ....................................................................92

Figure 21. Transmission Data Timing of MII/SNI/SMI Interface...............................................................92

Figure 22. Cross-section of 128-Pin PQFP..................................................................................................94

Figure 23. Application for Transformer with Connected Central Tap.........................................................97

Figure 24. Bob Smith Termination ..............................................................................................................98

Single-Chip 9-Port 10/100Mbps Switch Controller xv Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

1. General Description

The RTL8309SB is a 128-pin, ultra low power, high-performance 8-port Fast Ethernet single-chip switch

with one extra MII port for specific applications. It integrates all the functions of a high speed switch

system—including SRAM for packet buffering, non-blocking switch fabric, address management, one

general use MII interface, eight 10/100Base-TX transceivers, and nine Media Access Controllers—into a

single 0.18µm CMOS device. It provides compatibility with all industry standard Ethernet and Fast

Ethernet devices. Only a 25MHz crystal is required; the EEPROM is optional to save BOM costs.

The embedded packet storage SRAM in the RTL8309SB features superior memory management

technology to efficiently utilize the memory space. An integrated 1024-entry look-up table stores MAC

address and associated information in a 10-bit direct mapping scheme. The table provides read/write

access from the SMI interface, and each of the entries can be configured as a static entry. A static entry

indicates that this entry is controlled by the external management processor and automatic aging and

learning of the entry will not take place. To prevent MAC address mapping collisions, the embedded 16-

entry Content-Addressable Memory (CAM) offers another memory space for recording the MAC address

when the mapped entry in the lookup table is occupied. For each incoming packet, the RTL8309SB

searches the entries in the lookup table and the 16-entry CAM simultaneously. Then it obtains the correct

destination port information to determine which output port the packet should be forwarded to. The aging

time of the RTL8309SB is around 300 seconds (this may be sped up to 800µs via EEPROM

configuration).

The ninth port of the RTL8309SB implements a MAC module without a PHY transceiver to provide an

MII interface for connection with an external PHY or MAC in specific applications. This MII interface

may be set to MII PHY mode, SNI PHY mode, or MII MAC mode to work with an external MAC

module in a routing engine application, PHY module in a HomePNA application, or other physical layer

transceivers. In order to operate correctly, both sides of the connection must be configured to the same

speed, duplex, and flow control settings. Four pins are used for the ninth port to force the link status. This

interface should be 2.5V or 3.3V compatible depending on the voltage supplied to the power pin VDDIO

of this interface.

The RTL8309SB is capable of preventing broadcast storms by setting strapping pins upon system reset.

When this function is enabled, it will drop broadcast packets after receiving 64 continuous broadcast

packets. This counter will be reset to 0 every 800ms or when the RTL8309SB receives a non-broadcast

packet.

The RTL8309SB displays the port status via four LED indicators (with optional blinking time setting).

These LEDs blink for diagnostic purposes at system reset time. The RTL8309SB provides various type of

Single-Chip 9-Port 10/100Mbps Switch Controller 1 Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

LED combinations to fit different applications. Eight combinations of link, activity, speed, duplex, and

collision, are available. Bi-color LED mode is also supported on the Link/Act LED.

The RTL8309SB supports standard 802.3x flow control frames for full duplex, and optional backpressure

for half duplex. It determines when to invoke the flow control mechanism by checking the availability of

system resources, including the packet buffers and transmitting queues. If one of the forwarding ports is

blocked, or system resources are unavailable, broadcast frames will be dropped according to the system

configuration. The RTL8309SB support two types of dropping methods. The input dropping method will

not forward broadcast packets to any output ports and will drop these packets directly. The output

dropping method will forward broadcast packets to non-blocked ports only.

To improve real-time and multimedia networking applications, the RTL8309SB supports four types of

QoS (Quality of Service). These are based on (1) Port-based priority, (2) 802.1p/Q VLAN priority tag, (3)

TOS field in IPv4 header, (4) Specific IP address. Each output port supports a weighted ratio of high-

priority and low-priority queues to fit bandwidth requirements in different applications.

The RTL8309SB provides 802.1Q port-based VLAN operation to separate logical connectivity from

physical connectivity. Each port may be set to any topology via EEPROM upon reset or SMI after reset.

The RTL8309SB also provides options to meet special application requirements. The first option is the

ARP VLAN function, which is used to select to broadcast ARP frames to all VLANs or only forward

ARP frames to the originating VLAN. The second option is the Leaky VLAN function, which is used to

select to send unicast frames to other VLANs or only forward unicast frames to the originating VLAN.

The VLAN tags can be inserted or removed on a per-port basis.

In router applications, the router may want to know which input port this packet came from. The

RTL8309SB supports Port VID (PVID) for each port to insert a PVID in the VLAN tag on egress. In this

function, the VID information carried in the VLAN tag will be changed to PVID. The RTL8309SB also

provides an option to admit VLAN tagged packet with a specific PVID only. If this function is enabled, it

will drop non-tagged packets and packets with an incorrect PVID.

Each physical layer channel consists of a 4B5B encoder/decoder, Manchester encoder/decoder, transmit

output driver, scrambler/descrambler, output wave shaping, filters, digital adaptive equalizer, PLL circuit,

and DC restoration circuit for clock/data recovery. This integrated chip benefits from low power

consumption and offers advanced functions with flexible configuration for a small workgroup switch,

multimedia, or real-time traffic mixed with other data type traffic, and other applications.

Single-Chip 9-Port 10/100Mbps Switch Controller 2 Track ID: JATR-1076-21 Rev. 1.4

2. Features

RTL8309SB

Datasheet

Integrates eight 10/100 transceivers and nine

MAC units for 10Base-T and 100Base-TX.

Embedded SRAM for packet storage.

On-chip 1024-entry look-up table in direct

mapping mode.

Embedded 16-entry CAM for hash collision

mapping.

Provides read/write access to look-up table

entries via SMI interface.

Provides non-blocking wire speed reception

and transmission.

Flow control fully supported:

Half-duplex: backpressure flow control.

Full-duplex: IEEE 802.3x flow control.

Support for 4 LEDs per-port in various

combinations for comprehensive

applications.

Optional loop detection function with an

LED to indicate the existence of a loop.

Supports MII loopback.

LEDs blink upon reset for LED diagnostics.

Flexible system configuration by strapping

pins, EEPROM, or SMI interface.

Optional crossover detection and auto

correction for plug-and-play.

Fully compliant with IEEE 802.3/802.3u.

Optional Forwarding/Filtering reserved

control frames (DID=

0180C2000003~0180C200000F).

Optional Broadcast Input/Output Drop flow

control.

Optional maximum packet length

1536/1552 Bytes.

Supports two Power Reduction methods:

Supports QoS function:

QoS based on: (1) Port-based priority (2)

802.1p VLAN tag (3) DiffServ/TOS field

in TCP/IP header (4) IP address.

Supports two-level priority queues with

various weighting ratios.

Queue service rate based on weighted

round robin algorithm.

Optional auto turn off Flow Control for

1~2 sec to avoid head-of-line blocking.

Supports MII interface connection to external

MAC or PHY via 3 modes.

PHY mode MII for router applications.

PHY mode SNI for router applications.

MAC mode MII for HomePNA or other

PHY applications.

Flexible 802.1Q port/tag-based VLAN.

Optional 802.1Q tag-VID aware function.

Optional VLAN Ingress Tag Admit

Control.

Optional VLAN Ingress Member set

filtering.

Optional ARP VLAN for broadcast packet.

Optional Leaky VLAN for unicast packet.

Optional 802.1P/Q tag insertion or removal

on per-port basis (egress).

25MHz crystal input.

0.18µm, CMOS technology.

128-pin PQFP package.

1.8V core voltage.

Independent power options for 2.5V or 3.3V

MII interface.

Power saving mode (automatic cable

detection).

Power down mode (via PHY

register 0.11).

Single-Chip 9-Port 10/100Mbps Switch Controller 3 Track ID: JATR-1076-21 Rev. 1.4

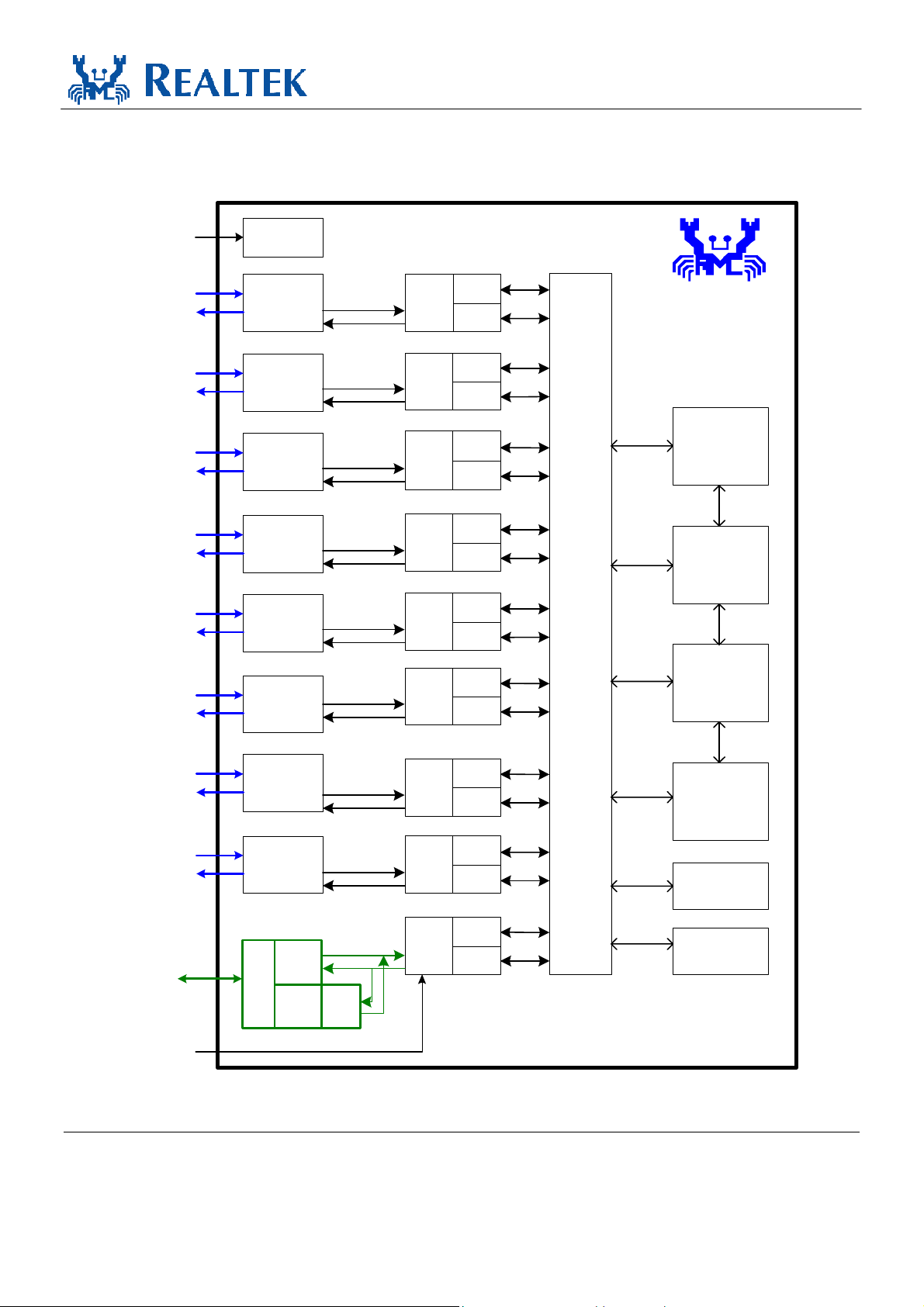

3. Block Diagram

RTL8309SB

Datasheet

IBREF

RX+-[0]

TX+-[0]

RX+-[1]

TX+-[1]

RX+-[2]

TX+-[2]

RX+-[3]

TX+-[3]

RX+-[4]

TX+-[4]

RX+-[5]

TX+-[5]

Wave form

Shapi ng

10Base-T or

100Base -TX

PHYcei ver

10Base-T or

100Base -TX

PHYcei ver

10Base-T or

100Base -TX

PHYcei ver

10Base-T or

100Base -TX

PHYcei ver

10Base-T or

100Base -TX

PHYcei ver

10Base-T or

100Base -TX

PHYcei ver

10/100

MAC 0

10/100

MAC 1

10/100

MAC 2

10/100

MAC 3

10/100

MAC 4

10/100

MAC 5

Flow

Control

TX/RX

FIFO

Flow

Control

TX/RX

FIFO

Flow

Control

TX/RX

FIFO

Flow

Control

TX/RX

FIFO

Flow

Control

TX/RX

FIFO

Flow

Control

TX/RX

FIFO

RTL8309S B

Look-up Table

(1024-entries)

Swi tch Fabric, VLAN, QoS, Trunking

Queue

Management

Buffer

Management

RX+-[6]

TX+-[6]

RX+-[7]

TX+-[7]

MII

Signal

P8MODE[1:0]

13

10Base-T or

100Base -TX

PHYcei ver

10Base-T or

100Base -TX

PHYcei ver

MAC

Mode

/

Inter

face

PHY

Mode

Mode

Select

10/100

MAC 6

10/100

MAC 7

10/100

MAC 8

Flow

Control

TX/RX

FIFO

Flow

Control

TX/RX

FIFO

Flow

Control

TX/RX

FIFO

Packet Buffer

EEPROM

Interface

Control

Registers

Figure 1. Block Diagram

Single-chip 9-port 10/100Mbps Switch Controller 4 Track ID: JATR-1076-21 Rev. 1.4

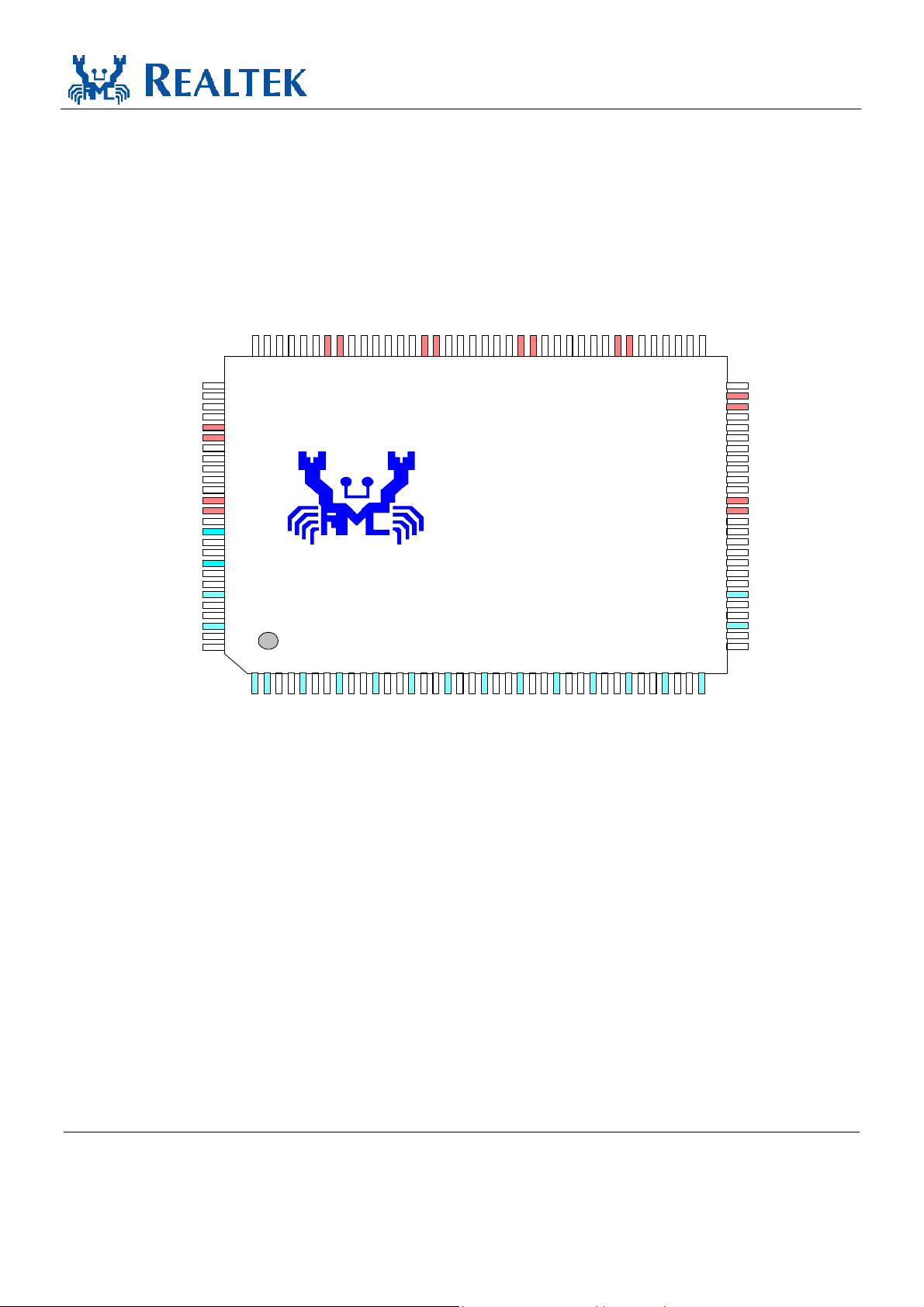

4. Pin Assignments

P3_LED[1]/Dis_Trunk

P3_LED[0]/LED_MODE[2]

P2_LED[3]/LED_MODE[1]

P2_LED[2]/LED_MODE[0]

P2_LED[1]/MII_MODE[1]

En_AutoXover/P1_LED[3]

En_ANEG/P1_LED[2]

En_FCTRL/P1_LED[1]

En_BKPRS/P1_LED[0]

Force_Duplex/P0_LED[3]

Force_Speed/P0_LED[2]

En_BRD_CTRL/P0_LED[1]

En_RST_BLNK/P0_LED[0]

EnEEPROM/LoopLED#

VDDD

VSSD

VDDD

VSSD

Test pin

VSSPLL

VDDPLL

Test Pin

IBREF

VDDA

TXON[0]

TXOP[0]

VSSA

RXIP[0]

RXIN[0]

P2_LED[0]/MII_MODE[0]

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

X1

X2

118

119

120

121

122

123

124

125

126

127

128

1

989799

101

100

2

P3_LED[2]/En_Forward

VSSD

VDDD

949693

9876543

P4_LED[1]/En_Agrs_Back

P4_LED[2]/Max_Pkt_Len

P4_LED[0]/En_48pass1

P3_LED[3]/En_Defer

90

919592

12

13

10

11

P5_LED[3]/Dis_DS_Pri

P6_LED[0]/QWeight[0]

VSSD

VDDD

VSSD

P4_LED[3]/Max_Pause_Count

89

P5_LED[1]/Sel_PortPri[1]

P5_LED[0]/Sel_PortPri[0]

868587

88

P6_LED[1]/QWeight[1]

P5_LED[2]/Dis_VLAN_Pri

828481

VDDD

798380

P6_LED[3]/Dis_LeakyVLAN

P6_LED[2]/Dis_VLAN

78

77

RTL8309SB

22

21

20

19

18

17

16

15

14

23

26

25

24

P7_LED[0]/Dis_ARPVLAN

76

27

P7_LED[1]/LED_BLNK_TIME

28

P7_LED[3]/Dis_FC_AutoOff

P7_LED[2]/Port_LED_LOC

747375

30

29

RTL8309SB

Datasheet

VSSD

VDDD

MRXD[2]/PTXD[2]

MRXD[3]/PTXD[3]

707269

343837

33

32

31

MRXC/PTXC

MRXD[0]/PTXD[0]

MRXDV/PTXEN

MRXD[1]/PTXD[1]

677168

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

36

35

MCOL/PCOL

VSSIO

VDDIO

MTXD[3]/PRXD[3]

MTXD[2]/PRXD[2]

MTXD[1]/PRXD[1]

MTXD[0]/PRXD[0]

MTXEN/PRXDV

MTXC/PRXC

SDA_MDIO

SCL_MDC

VSSD

VDDD

MII_LNK_STA#

MII_DUP_STA

MII_SPD_STA

MII_FCTRL_STA

RESET#

NC

Test Pin

VDDA

TXON[7]

TXOP[7]

VSSA

RXIP[7]

RXIN[7]

VDDA

VSSA

VDDA

VSSA

RXIP[2]

RXIN[2]

TXOP[2]

TXON[2]

VSSA

RXIP[1]

RXIN[1]

TXOP[1]

TXON[1]

VDDA

VSSA

RXIP[3]

RXIN[3]

TXOP[3]

TXON[3]

VDDA

VSSA

RXIP[4]

RXIN[4]

TXOP[4]

TXON[4]

VDDA

VSSA

RXIP[5]

RXIN[5]

TXOP[5]

TXON[5]

VDDA

VSSA

RXIP[6]

RXIN[6]

VDDA

TXOP[6]

TXON[6]

Figure 2. Pin Assignments

Single-chip 9-port 10/100Mbps Switch Controller 5 Track ID: JATR-1076-21 Rev. 1.4

RTL8309SB

Datasheet

Codes used in the following tables: ‘A’ stands for analog; ‘D’ stands for digital, ‘I’ stands for input; ‘O’ stands for output.

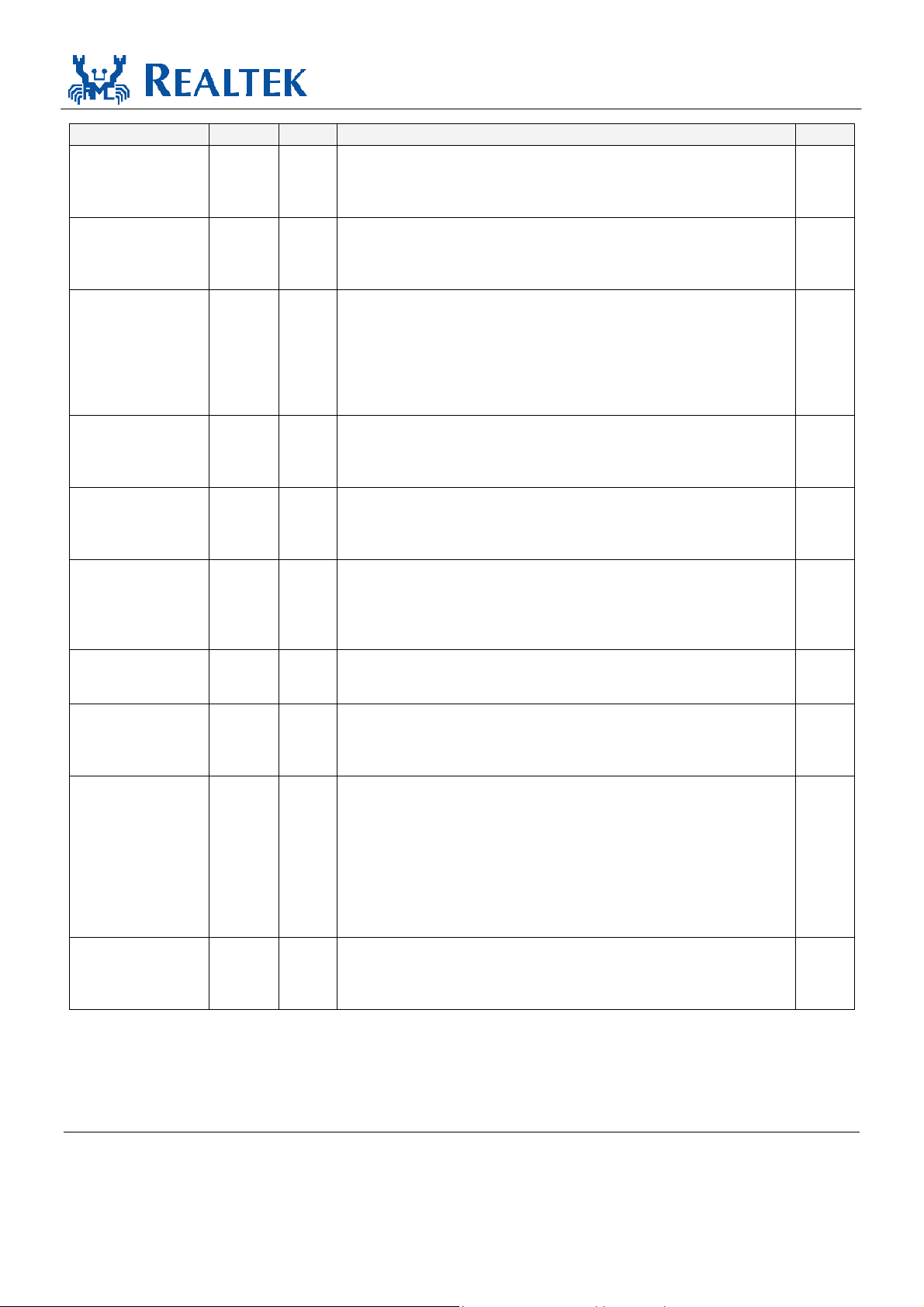

Table 1. Pin Assignments

Name Pin No. Type Name Pin No Type

VDDA,

VSSA,

TXON[1],

TXOP[1],

VSSA,

RXIP[1],

RXIN[1],

VDDA,

RXIN[2],

RXIP[2],

VSSA,

TXOP[2],

TXON[2],

VDDA,

TXON[3],

TXOP[3],

VSSA,

RXIP[3],

RXIN[3],

VDDA,

RXIN[4],

RXIP[4],

VSSA,

TXOP[4],

TXON[4],

VDDA,

TXON[5],

TXOP[5],

VSSA,

RXIP[5],

RXIN[5],

VDDA,

RXIN[6],

RXIP[6],

VSSA,

TXOP[6],

TXON[6],

VDDA,

RXIN[7],

RXIP[7],

VSSA,

TXOP[7],

TXON[7],

VDDA,

NC,

NC

RESET#

MII_FCTRL_STA,

MII_SPD_STA,

MII_DUP_STA,

MII_LNK_STA#,

VDDD,

VSSD,

SCL_MDC,

SDA_MDIO,

MTXC/PRXC,

MTXEN/PRXDV,

MTXD[0]/PRXD[0],

MTXD[1]/PRXD[1],

MTXD[2]/PRXD[2],

MTXD[3]/PRXD[3],

VDDIO,

VSSIO,

MCOL/PCOL

1,

2,

3,

4,

5,

6,

7,

8,

9,

10,

11,

12,

13,

14,

15,

16,

17,

18,

19,

20,

21,

22,

23,

24,