Realtek RTL8103E-GR, RTL8103EL-GR Schematic [ru]

RTL8103E-GR

RTL8103EL-GR

INTEGRATED FAST ETHERNET CONTROLLER

FOR PCI EXPRESS™ APPLICATIONS

DATASHEET

(CONFIDENTIAL: Development Partners Only)

Rev. 1.3

08 August 2008

Track ID: JATR-1076-21

Realtek Semiconductor Corp.

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan

Tel.: +886-3-578-0211. Fax: +886-3-577-6047

www.realtek.com

RTL8103E & RTL8103EL

Datasheet

COPYRIGHT

©2008 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced,

transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any

means without the written permission of Realtek Semiconductor Corp.

DISCLAIMER

Realtek provides this document “as is”, without warranty of any kind, neither expressed nor implied,

including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in

this document or in the product described in this document at any time. This document could include

technical inaccuracies or typographical errors.

TRADEMARKS

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document

are trademarks/registered trademarks of their respective owners.

LICENSE

This product is covered by one or more of the following patents:US5,307,459, US5,434,872,

US5,732,094, US6,570,884, US6,115,776, and US6,327,625.

USING THIS DOCUMENT

This document is intended for the software engineer’s reference and provides detailed programming

information.

Though every effort has been made to ensure that this document is current and accurate, more information

may have become available subsequent to the production of this guide. In that event, please contact your

Realtek representative for additional information that may help in the development process.

REVISION HISTORY

Revision Release Date Summary

1.0 2008/05/28 First Release

1.1 2008/07/08 Corrected typing error

1.2 2008/07/29 Updated licensing information

1.3 2008/08/08 Added Deep Slumber Mode (DSM) power saving to features list on page 2.

Integrated Fast Ethernet Controller for PCI Express ii Track ID: JATR-1076-21 Rev. 1.3

RTL8103E & RTL8103EL

Datasheet

Table of Contents

1. GENERAL DESCRIPTION..............................................................................................................................................1

2. FEATURES.........................................................................................................................................................................2

3. SYSTEM APPLICATIONS...............................................................................................................................................2

4. PIN ASSIGNMENTS .........................................................................................................................................................3

4.1. RTL8103E (64-PIN) ....................................................................................................................................................3

4.2. PACKAGE IDENTIFICATION...........................................................................................................................................3

4.3. RTL8103EL (48-PIN)..................................................................................................................................................4

4.4. PACKAGE IDENTIFICATION...........................................................................................................................................4

5. PIN DESCRIPTIONS.........................................................................................................................................................5

5.1. POWER MANAGEMENT/ISOLATION ..............................................................................................................................5

5.2. PCI EXPRESS INTERFACE .............................................................................................................................................5

5.3. EEPROM ....................................................................................................................................................................6

5.4. TRANSCEIVER INTERFACE............................................................................................................................................6

5.5. CLOCK .........................................................................................................................................................................6

5.6. REGULATOR AND REFERENCE......................................................................................................................................6

5.7. LEDS ...........................................................................................................................................................................7

5.8. POWER AND GROUND ..................................................................................................................................................7

5.9. GPIO ...........................................................................................................................................................................7

5.10. NC (NOT CONNECTED) PINS AND TEST PINS ...............................................................................................................8

6. FUNCTIONAL DESCRIPTION.......................................................................................................................................8

6.1. PCI EXPRESS BUS INTERFACE......................................................................................................................................8

6.1.1. PCI Express Transmitter ........................................................................................................................................8

6.1.2. PCI Express Receiver.............................................................................................................................................8

6.2. LED FUNCTIONS..........................................................................................................................................................9

6.2.1. Link Monitor...........................................................................................................................................................9

6.2.2. Rx LED ...................................................................................................................................................................9

6.2.3. Tx LED .................................................................................................................................................................10

6.2.4. Tx/Rx LED ............................................................................................................................................................10

6.2.5. Customizable LED Configuration ........................................................................................................................11

6.3. PHY TRANSCEIVER ...................................................................................................................................................12

6.3.1. PHY Transmitter...................................................................................................................................................12

6.3.2. PHY Receiver .......................................................................................................................................................12

6.4. EEPROM INTERFACE................................................................................................................................................13

6.5. POWER MANAGEMENT...............................................................................................................................................14

6.6. VITAL PRODUCT DATA (VPD)...................................................................................................................................16

6.7. RECEIVE-SIDE SCALING (RSS) ..................................................................................................................................16

6.7.1. Receive-Side Scaling (RSS) Initialization.............................................................................................................16

6.7.2. RSS Operation ......................................................................................................................................................17

7. CHARACTERISTICS......................................................................................................................................................18

7.1. ABSOLUTE MAXIMUM RATINGS ................................................................................................................................18

7.2. RECOMMENDED OPERATING CONDITIONS .................................................................................................................18

7.3. CRYSTAL REQUIREMENTS..........................................................................................................................................18

7.4. TRANSFORMER CHARACTERISTICS ............................................................................................................................19

7.5. OSCILLATOR REQUIREMENTS ....................................................................................................................................19

7.6. THERMAL CHARACTERISTICS.....................................................................................................................................19

7.7. DC CHARACTERISTICS...............................................................................................................................................20

7.8. AC CHARACTERISTICS...............................................................................................................................................21

Integrated Fast Ethernet Controller for PCI Express iii Track ID: JATR-1076-21 Rev. 1.3

RTL8103E & RTL8103EL

Datasheet

7.8.1. Serial EEPROM Interface Timing........................................................................................................................21

7.9. PCI EXPRESS BUS PARAMETERS................................................................................................................................22

7.9.1. Differential Transmitter Parameters....................................................................................................................22

7.9.2. Differential Receiver Parameters.........................................................................................................................23

7.9.3. REFCLK Parameters............................................................................................................................................23

7.9.4. Auxiliary Signal Timing Parameters ....................................................................................................................27

8. MECHANICAL DIMENSIONS......................................................................................................................................28

8.1. RTL8103E (64-PIN QFN)..........................................................................................................................................28

8.2. RTL8103EL (48-PIN LQFP)......................................................................................................................................29

8.3. MECHANICAL DIMENSIONS NOTES (RTL8103EL 48-PIN).........................................................................................30

9. ORDERING INFORMATION........................................................................................................................................31

Integrated Fast Ethernet Controller for PCI Express iv Track ID: JATR-1076-21 Rev. 1.3

RTL8103E & RTL8103EL

Datasheet

List of Tables

TABLE 1. POWER MANAGEMENT/ISOLATION ...............................................................................................................................5

TABLE 2. PCI EXPRESS INTERFACE..............................................................................................................................................5

TABLE 3. EEPROM .....................................................................................................................................................................6

TABLE 4. TRANSCEIVER INTERFACE ............................................................................................................................................6

TABLE 5. CLOCK ..........................................................................................................................................................................6

TABLE 6. REGULATOR AND REFERENCE ......................................................................................................................................6

TABLE 7. LEDS............................................................................................................................................................................7

TABLE 8. POWER AND GROUND ...................................................................................................................................................7

TABLE 9. GPIO PINS ....................................................................................................................................................................7

TABLE 10. NC (NOT CONNECTED) PINS ........................................................................................................................................8

TABLE 11. LED SELECT (IO REGISTER OFFSET 17H~18H)..........................................................................................................11

TABLE 12. CUSTOMIZED LEDS ...................................................................................................................................................11

TABLE 13. EEPROM INTERFACE ................................................................................................................................................13

TABLE 14. ABSOLUTE MAXIMUM RATINGS ................................................................................................................................18

TABLE 15. RECOMMENDED OPERATING CONDITIONS .................................................................................................................18

TABLE 16. CRYSTAL REQUIREMENTS..........................................................................................................................................18

TABLE 17. TRANSFORMER CHARACTERISTICS ............................................................................................................................19

TABLE 18. OSCILLATOR REQUIREMENTS ....................................................................................................................................19

TABLE 19. THERMAL CHARACTERISTICS.....................................................................................................................................19

TABLE 20. DC CHARACTERISTICS ...............................................................................................................................................20

TABLE 21. EEPROM ACCESS TIMING PARAMETERS ..................................................................................................................21

TABLE 22. DIFFERENTIAL TRANSMITTER PARAMETERS ..............................................................................................................22

TABLE 23. DIFFERENTIAL RECEIVER PARAMETERS.....................................................................................................................23

TABLE 24. REFCLK PARAMETERS .............................................................................................................................................23

TABLE 25. AUXILIARY SIGNAL TIMING PARAMETERS.................................................................................................................27

TABLE 26. ORDERING INFORMATION ..........................................................................................................................................31

List of Figures

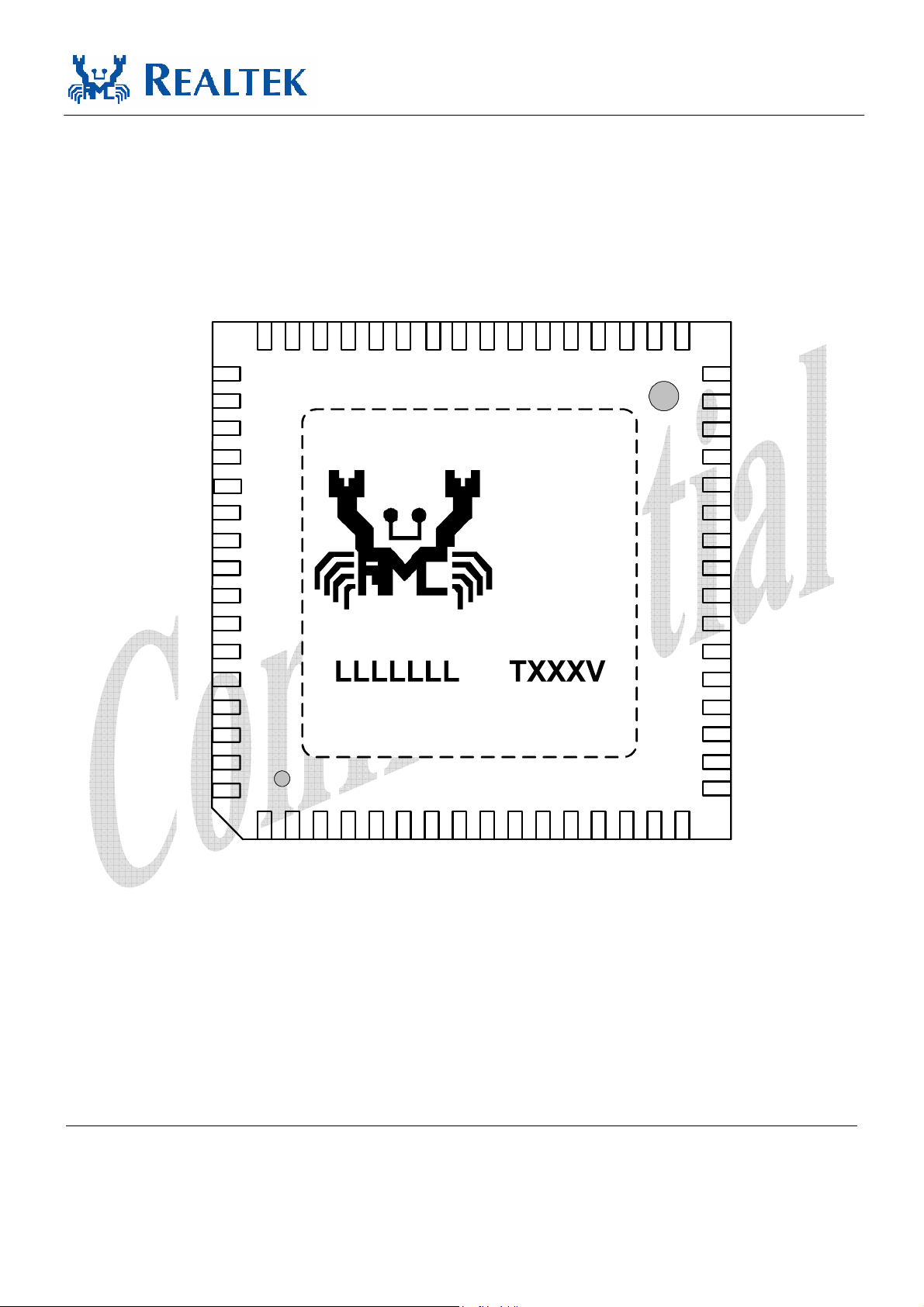

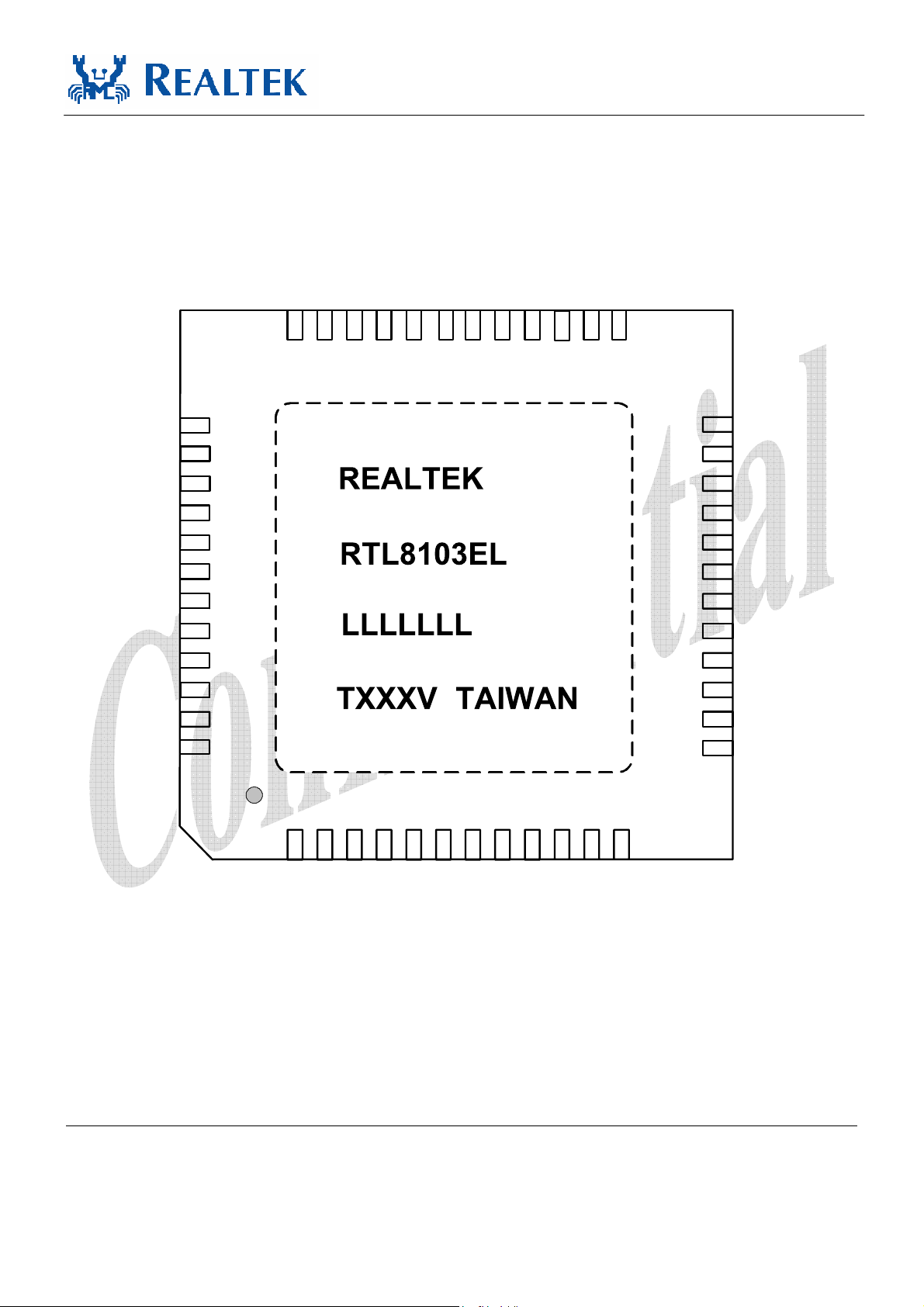

FIGURE 1. PIN ASSIGNMENTS (RTL8103E 64-PIN) ......................................................................................................................3

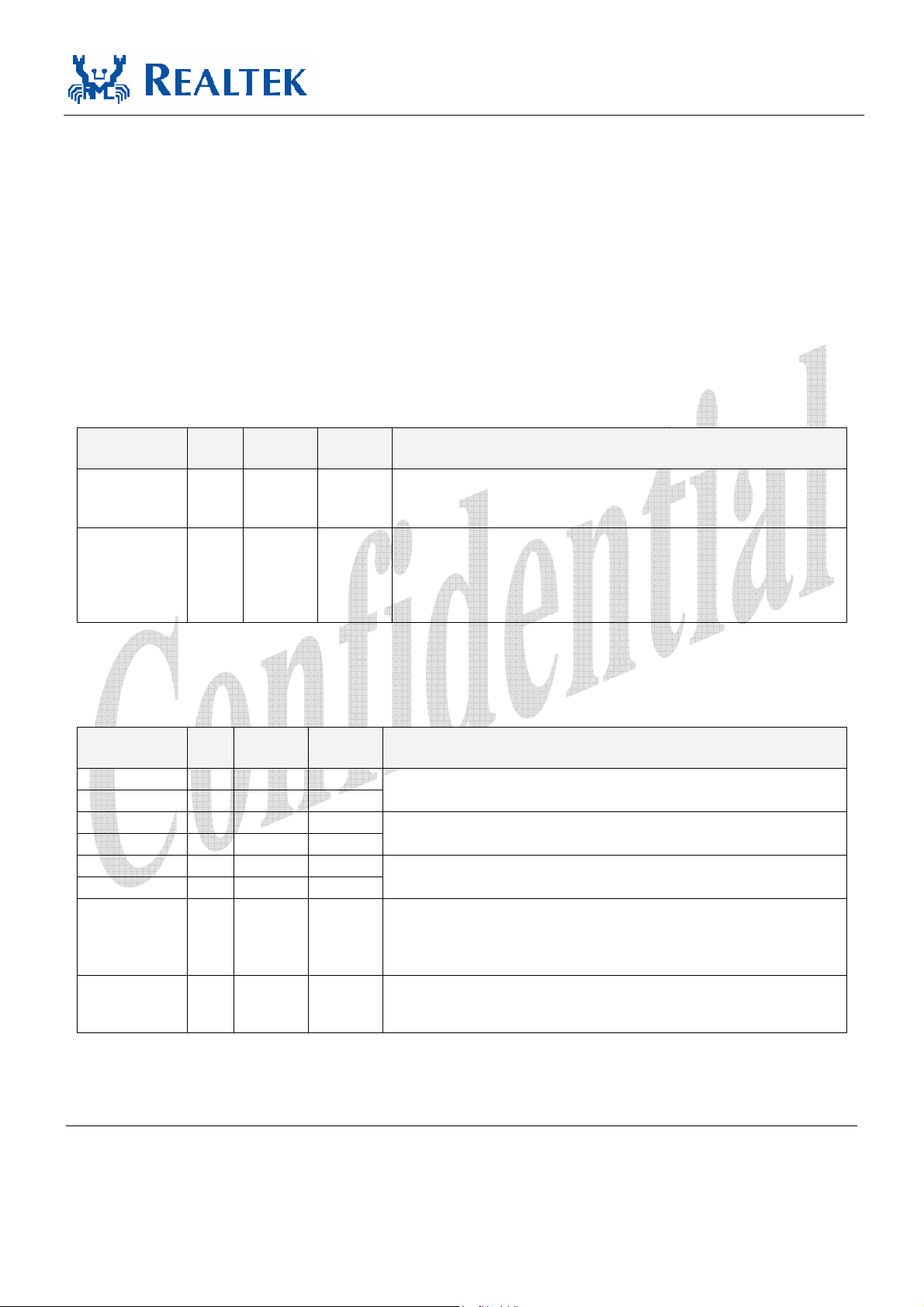

FIGURE 2. PIN ASSIGNMENTS (RTL8103EL 48-PIN)....................................................................................................................4

FIGURE 3. RX LED.......................................................................................................................................................................9

FIGURE 4. TX LED.....................................................................................................................................................................10

FIGURE 5. TX/RX LED...............................................................................................................................................................10

FIGURE 6. SERIAL EEPROM INTERFACE TIMING ......................................................................................................................21

FIGURE 7. SINGLE-ENDED MEASUREMENT POINTS FOR ABSOLUTE CROSS POINT AND SWING ..................................................25

FIGURE 8. SINGLE-ENDED MEASUREMENT POINTS FOR DELTA CROSS POINT ...........................................................................25

FIGURE 9. SINGLE-ENDED MEASUREMENT POINTS FOR RISE AND FALL TIME MATCHING ........................................................25

FIGURE 10. DIFFERENTIAL MEASUREMENT POINTS FOR DUTY CYCLE AND PERIOD ...................................................................26

FIGURE 11. DIFFERENTIAL MEASUREMENT POINTS FOR RISE AND FALL TIME ...........................................................................26

FIGURE 12. DIFFERENTIAL MEASUREMENT POINTS FOR RINGBACK............................................................................................26

FIGURE 13. REFERENCE CLOCK SYSTEM MEASUREMENT POINT AND LOADING .........................................................................27

FIGURE 14. AUXILIARY SIGNAL TIMING......................................................................................................................................27

Integrated Fast Ethernet Controller for PCI Express v Track ID: JATR-1076-21 Rev. 1.3

RTL8103E & RTL8103EL

Datasheet

1. General Description

The Realtek RTL8103E(L)-GR Fast Ethernet controller combines an IEEE 802.3 10/100Base-T

compliant Media Access Controller (MAC), PCI Express bus controller, and embedded

One-Time-Programmable (OTP) memory. With state-of-the-art DSP technology and mixed-mode signal

technology, the RTL8103E(L) offers high-speed transmission over CAT 5 UTP cable or CAT 3 UTP

(10Mbps only) cable. Functions such as Crossover Detection & Auto-Correction, polarity correction,

adaptive equalization, cross-talk cancellation, echo cancellation, timing recovery, and error correction are

implemented to provide robust transmission and reception capability at high speeds.

The device supports the PCI Express 1.1 bus interface for host communications with power management,

and is compliant with the IEEE 802.3u specification for 10/100Mbps Ethernet. It also supports an

auxiliary power auto-detect function, and will auto-configure related bits of the PCI power management

registers in PCI configuration space. The RTL8103E(L) features embedded One-Time-Programmable

(OTP) memory to replace the external EEPROM (93C46/93C56).

Advanced Configuration Power management Interface (ACPI)—power management for modern

operating systems that are capable of Operating System-directed Power Management (OSPM)—is

supported to achieve the most efficient power management possible. PCI MSI (Message Signaled

Interrupt) and MSI-X are also supported.

In addition to the ACPI feature, remote wake-up (including AMD Magic Packet™ and Microsoft

Wake-up frame) is supported in both ACPI and APM (Advanced Power Management) environments. To

support WOL from a deep power down state (e.g., D3cold, i.e., main power is off and only auxiliary

exists), the auxiliary power source must be able to provide the needed power for the RTL8103E(L).

The RTL8103E(L) is fully compliant with Microsoft

Checksum and Segmentation Task-offload (Large send and Giant send) features, and supports IEEE 802

IP Layer 2 priority encoding and IEEE 802.1Q Virtual bridged Local Area Network (VLAN). The above

features contribute to lowering CPU utilization, especially benefiting performance when in operation on a

network server.

®

NDIS5, NDIS6 (IPv4, IPv6, TCP, UDP)

®

The RTL8103E(L) supports Receive Side Scaling (RSS) to hash incoming TCP connections and

load-balance received data processing across multiple CPUs. RSS improves the number of transactions

per second and number of connections per second, for increased network throughput.

The device also features inter-connect PCI Express technology. PCI Express is a high-bandwidth, low pin

count, serial, interconnect technology that offers significant improvements in performance over

conventional PCI and also maintains software compatibility with existing PCI infrastructure. The device

embeds an adaptive equalizer in the PCIE PHY for ease of system integration and excellent link quality.

The equalizer enables the length of the PCB traces to reach 20 inches.

The RTL8103E(L) is suitable for multiple market segments and emerging applications, such as desktop,

mobile, workstation, server, communications platforms, and embedded applications.

Built-in linear regulators provide the RTL8103E(L)’s core power, as well as reducing layout area and

external BOM costs. The RTL8103E supports the Deep Slumber Mode (DSM) power saving feature. See

the separate DSM application notes for details (the RTL8103EL does not support the DSM feature).

Note: RTL8103 model differences are listed in section 9 Ordering Information, page 31.

Integrated Fast Ethernet Controller for PCI Express 1 Track ID: JATR-1076-21 Rev. 1.3

2. Features

RTL8103E & RTL8103EL

Datasheet

Integrated 10/100 transceiver

Auto-Negotiation with Next Page

capability

Supports PCI Express™ 1.1

Supports pair swap/polarity/skew

correction

Crossover Detection & Auto-Correction

Wake-on-LAN and remote wake-up

support

Customizable LEDs

®

Microsoft

NDIS5, NDIS6 Checksum

Offload (IPv4, IPv6, TCP, UDP) and

Segmentation Task-offload (Large send

and Giant send) support

Supports Full Duplex flow control

(IEEE 802.3x)

Fully complies with IEEE 802.3,

IEEE 802.3u

Supports IEEE 802.1Q VLAN tagging

Serial EEPROM

Embedded OTP memory can replace

the external EEPROM

Transmit/Receive on-chip buffer

support

Supports power down/link down power

saving

Built-in Regulator

Supports PCI MSI (Message Signaled

Interrupt) and MSI-X

Supports Receive-Side Scaling (RSS)

Embeds an adaptive equalizer in PCI

express PHY (PCB traces can reach up

to 20 inches)

Supports Deep Slumber Mode (DSM)

power saving feature (RTL8103E

64-pin QFN only)

Supports IEEE 802.1P Layer 2 Priority

Encoding

64-pin QFN (RTL8103E) & 48-pin

LQFP (RTL8103EL) Green package

3. System Applications

PCI Express™ Fast Ethernet on Motherboard, Notebook, or Embedded system

Integrated Fast Ethernet Controller for PCI Express 2 Track ID: JATR-1076-21 Rev. 1.3

4. Pin Assignments

4.1. RTL8103E (64-Pin)

K

S

EEDI/AUX

VDD33

EEDO

EE

RTL8103E & RTL8103EL

Datasheet

DVDD12

EECS

TEST3

TEST4

TEST5

NC

TEST2

VDD33

ISOLATEB

TEST0

TEST1

CLKREQB

DVDD 12

GPI

GPO

NC

VDD 33

LED3

LED 2

LED 1

LED 0

DVDD 12

NC

CKXTAL 1

CKXTAL 2

NC

VCTRL12 D

RSET

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

123456789

65 GND (Exposed Pad)

RTL8103 E

10 11 12 13 14 15 16

3

31

30

29

28

27

26

25

24

23

22

21

20

19

18

1

2

7

NC

EGND

HSON

HSOP

EVDD12

REFCLK_M

REFCLK_P

EGND

HSIN

HSIP

NC

DVDD12

PERSTB

LANWAKEB

MAPIN 1

MAPIN 0

VCTRL12A

NC

MDIP0

MDIN0

AVDD33

MDIP1

MDIN1

NC

NC

NC

NC

NC

NC

NC

VDD33

DVDD12

Figure 1. Pin Assignments (RTL8103E 64-Pin)

4.2. Package Identification

Green package is indicated by a ‘G’ in the location marked ‘T’ in Figure 1.

The version is shown in the location marked ‘V’.

Integrated Fast Ethernet Controller for PCI Express 3 Track ID: JATR-1076-21 Rev. 1.3

4.3. RTL8103EL (48-Pin)

RTL8103E & RTL8103EL

Datasheet

VDD33

LED0

NC

NC

CKXTAL1

CKXTAL2

NC

NC

37

38

39

40

41

42

43

44

/AUX

LED1/EESK

DVDD12

36 35 34 33 32 31 30 29 28 27 26

LED3/EEDO

LED2/EEDI

GND

EECS

VDD33

DVDD12

ISOLATEB

PERSTB

B

E

K

LANWA

25

B

Q

E

CLKR

24

23

22

21

20

19

18

17

NC

NC

GNDTX

HSON

HSOP

VDDTX

REFCLK_M

REFCLK _ P

VCTRL12D

RSET

GND

VCTRL12A

45

46

47

48

1 2 3 4 5 6 7 8 9 101112

NC

MDIN0

MDIP0

AVDD33

Figure 2. Pin Assignments (RTL8103EL 48-Pin)

MDI P1

ND

NC

G

MDIN1

NC

12

DDVD

NC

4.4. Package Identification

Green package is indicated by a ‘G’ in the location marked ‘T’ in Figure 2.

The version is shown in the location marked ‘V’.

NC

16

15

14

13

HSIN

HSIP

GND

DVDD 12

Integrated Fast Ethernet Controller for PCI Express 4 Track ID: JATR-1076-21 Rev. 1.3

5. Pin Descriptions

The signal type codes below are used in the following tables:

I: Input S/T/S: Sustained Tri-State

O: Output O/D: Open Drain

T/S: Tri-State bi-directional input/output pin

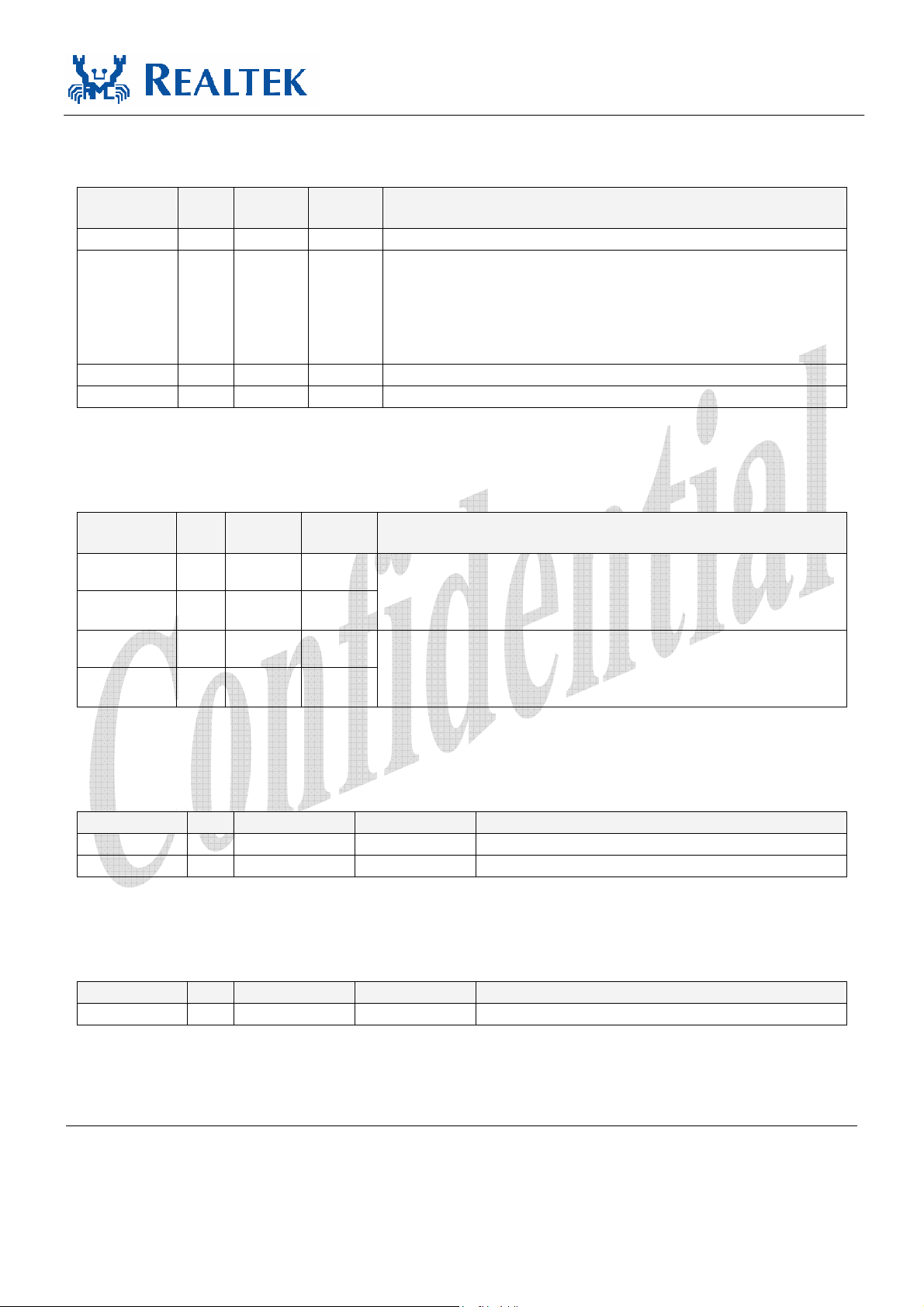

5.1. Power Management/Isolation

Table 1. Power Management/Isolation

Symbol Type Pin No

(64-Pin)

LANWAKEB O/D 19 26

ISOLATEB I 36 28

Pin No

(48-Pin)

Description

Power Management Event: Open drain, active low.

Used to reactivate the PCI Express slot’s main power rails and

reference clocks.

Isolate Pin: Active low.

Used to isolate the RTL8103E(L) from the PCI Express bus. The

RTL8103E(L) will not drive its PCI Express outputs (excluding

LANWAKEB) and will not sample its PCI Express input as long as the

Isolate pin is asserted.

RTL8103E & RTL8103EL

Datasheet

5.2. PCI Express Interface

Table 2. PCI Express Interface

Symbol Type Pin No

(64-Pin)

REFCLK_P I 26 17

REFCLK_M I 27 18

HSOP O 29 20

HSON O 30 21

HSIP I 23 15

HSIN I 24 16

PERSTB I 20 27

CLKREQB O/D 33 25

Pin No

(48-Pin)

Description

PCI Express Differential Reference Clock Source: 100MHz ± 300ppm.

PCI Express Transmit Differential Pair.

PCI Express Receive Differential Pair.

PCI Express Reset Signal: Active low.

When the PERSTB is asserted at power-on state, the RTL8103E(L)

returns to a pre-defined reset state and is ready for initialization and

configuration after the de-assertion of the PERSTB.

Reference Clock Request Signal.

This signal is used by the RTL8103E(L) to request starting of the PCI

Express reference clock.

Integrated Fast Ethernet Controller for PCI Express 5 Track ID: JATR-1076-21 Rev. 1.3

RTL8103E & RTL8103EL

5.3. EEPROM

Table 3. EEPROM

Symbol Type Pin No

(64-Pin)

EESK O 48 35 Serial Data Clock.

EEDI/AUX OI 47 34

EEDO I 45 33 Input from Serial Data Output Pin of EEPROM.

EECS O 44 32 EECS: EEPROM chip select.

Pin No

(48-Pin)

Description

EEDI: Output to serial data input pin of EEPROM.

AUX: Input pin to detect if Aux. Power exists or not on initial power-on.

This pin should be connected to EEPROM. To support wakeup from

ACPI D3cold or APM power-down, this pin must be pulled high to Aux.

Power via a resistor. If this pin is not pulled high to Aux. Power, the

RTL8103E(L) assumes that no Aux. Power exists.

5.4. Transceiver Interface

Table 4. Transceiver Interface

Symbol Ty pe Pin No

(64-Pin)

MDIP0 IO 3 2

MDIN0 IO 4 3

MDIP1 IO 6 5

MDIN1 IO 7 6

Pin No

(48-Pin)

Description

In MDI mode, this pair acts as the BI_DA+/- pair, and is the transmit pair

in 10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the BI_DB+/- pair, and is the

receive pair in 10Base-T and 100Base-TX.

In MDI mode, this pair acts as the BI_DB+/- pair, and is the receive pair

in 10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the BI_DA+/- pair, and is the

transmit pair in 10Base-T and 100Base-TX.

Datasheet

5.5. Clock

Table 5. Clock

Symbol Ty pe Pin No (64-Pin) Pin No (48-Pin) Description

CKXTAL1 I 60 41 Input of 25MHz Clock Reference.

CKXTAL2 O 61 42 Output of 25MHz Clock Reference.

5.6. Regulator and Reference

Table 6. Regulator and Reference

Symbol Ty pe Pin No (64-Pin) Pin No (48-Pin) Description

RSET I 64 46 Reference. External resistor reference.

Integrated Fast Ethernet Controller for PCI Express 6 Track ID: JATR-1076-21 Rev. 1.3

Loading...

Loading...