Page 1

Page 2

5iFlE'_

RADIO

CORPORATION

OF

AMERICA

I

•

ELECTRONIC

DATA

PROCESSING

SYSTEM

7C25i

TRAINING

~RADIO

CORPORATION

70-25-801

MANUAL

o F

AMERICA

Page 3

The

information

is

subject

Revisions

of

such

First

Printing:

Second

to

change

may

changes

Printing:

contained

without

be

issued

and/or

to

additions.

December, 1964

January,

herein

notice.

advise

1965

Page 4

TABLE OF CONTENTS

Page

General

Description

High-Speed

Introduction

HSM

Hexadecimal

Exercise

Data

and

Instruction

Data

Unpacked

Edited

Machine

Exercise

Interrupt

Introduction

Programming

Processing

Interrupt

Types

I/O

Interrupt

Operation

Arithmetic

Elapsed

Inhibiting

Exercise

Summary

. . . . • • • • • . . . • . • . • • . • . • . . • • • . • • • • • . • . . • • • • . • . . . . • • . • . . 1

Memory

• • . • . . . • • • • . • . • • . • . • . • . • . • . . • • • . • • . • • • . • • • • • • . . . • • • • • • 3

.••..•.•••...•.•....•.•.••.•..•••..•..••••••..••••••.•..

Addressing

..••••••..•.•••••.••.••.•.•.•.•..•.••.•..••.•••...•..

Numbering

System

• . . • • • . • . . • . • . . • • • . • . • • • • . • • • • . . • • • . . • • • • • • 4

.••••••......•.•.•.•.••••••.•.•.••••••.•••••••••..•.•..•••

Formats

Format

Format

Instruction

Format

. . . . • . • . • . • . • • • • • . • . • • . • • • • • • • • • • • • . • . • • • • • • • • • • . • • • • . • 6

.•.•...••••••......•..•..•••..•.•..•.•.•••.•.•.••.••••

........•.•.••.•••••.•.•..•.•••••..•.•.••••...••

.•.•..•••••••••.•.•••••••.••••.••••.••••.••.••••.•••

Format

•.•...••.••••••••...••.••.•.••.•.•.••....••••

.•••.•..•.•..••..••••••••••••.••••••••.•..•.••••••..••••.•

.••..•.•..•••.•.••.••••.••••.•.....••.•••..••••••.•.••.••.•.•

••.•.•.•..•••....•.•.•..•..•..•.•.....••.•.••..••••..•..

State

of

Interrupt

Code

Timer

Interrupt

States.

State

• . • . • . • • • . . . • . . . . . . • • • • • • . • . • . . • • . • • . . • • • • . • • . . . • • • • • . • 9

•.

Overflow

. . • . • • • . • • . • . • . • . • . • • • . • • • • . • • . • . • • . • • • • • • . • • • • • • • 9

. . . . . . . . • . . . . . . • . . . . • • • . • . • . . • . . . . . . . . . . . • . . . . . . . • . • • 9

. • • . • • . . . . . . . • . • . • . . . . • . . . . . . . . . . . • • • • • • . • . . • . . • . . . • 9

. . • • • . . • • • • • • . • . • . • • . • • • • • . . • . • . . . . . . • • . • . • . • . • . . • . • • 9

Trap

.•...•••••.•.•.•••••••........•..••.....•........•

and

Divide

Interrupt.

Exception

. . . . . • . • . . . . . • . • . . . . . . . • . . . . . . . . . . . .

. . . . . • . • . . . • . . . . . . . . . • . • . . . . • . . . • • • • • . . . . . . . • . . 11

•••..•••.••.•..•.•..••....•...•....•.•••......•....

...•....•.............•.................•......•...•....•.

of

Interrupt

Logic

..•..•..•.•...•...•.•......••.•....•..•......

3

3

5

6

6

6

7

7

9

9

10

10

11

11

12

Elapsed

Time

Introduction

Format

Addressing

Self-Defining

Expressions

Implied

Assembler

Define

Origin

Constant

Program

Run

Equate

Base

Extended

Exercise

Clock.

to

the

Requirements

• • • • . • • • • • • • . • • • . • • • . . • . • . • . • • • . • • • . • • • • • • . . . • . • • • • . .

RCA

70/25

Assembly

Language . ..•

• • • . • . • • • . • . • • • . • • • . • . . • • . • • •

•••.•.•••.•.•••.•.•••...•••.••••.•••.••.•..••••..

. . • • • • . • • . • • • • . • • • . . • • • . • . • . • • • • • . • . . • . • • • . • • • • • • . • • • . • • •

Values

•••••.••••.•••••.•.•.•••.••.••••.•••••••••.•..•.•.

• . • • • . • . • • • • • • • . . • • • . . . • . • . • . • . • • • • • . . • . • • • • • • • • • . • • • • . . 16

Lengths

and

Register

..........•.•.•.....•..•...•.•......•.•.•...•.....•.•

Controlling

Storage

Code

Definition

Linking

Segment

Code

Mnemonic

Codes

(DS)

•.••.•••..••••••••.•...•••.••••...••••..•••.

.•.•.•.••..•.•.•••••••.•.••••.••••••••.•..•.•.••

(ORG) • . • . . . • . • . • . . • • . • • . . . . . . . • • . . • . • . • • . . • . . • . . . . . . • •

(DC)

Codes

Controlling

(EQU)

Controlling

Instructions

...•.•.•...•.••.••.•.....••...

(ENTRY

and

Codes

EXTRH)

(START,

.•.•.•........

END,

....•....•.........•........•..•.....•.......•••

Codes

(USING, DROP)

.........•..................

. • . . . • . • . • . • • . . • . • . . . . . . . . . . . • . . • • . • . . . •

CSECT)

. . . . . . . . . . . . . . . . • . . 20

0 • • • • • • • • • • • • • •

0 • • • • • • • • • • • • • • •

.....•.•.•.•.......•...•......•.........•.................

13

14

14

14

16

17

17

18

18

18

19

21

21

21

22

Page 5

TABLE

OF

CONTENTS

(Continued)

Page

Instruction

Data

Move

Packing

Decimal

Arithmetic

Decimal

Decimal

Decimal

Exercises

Data

Editing

Examples

Exercises

Comparison

Compare

Compare

Branch

Branch

Branch

Set

P2

Exercises

Load

and

Load

Store

Complement

Movement

Character

Exercises

and

Exercises

Add (AP)

Multiply

Divide

.............

Instruction

..

......

and

Branching

Logical

Decimal

on

Condition

and

Link

on

Count

Register

Store

Instructions

Multiple

Multiple

Instructions

(MVC)

....

Unpacking

.....

Instructions

and

Subtract

(MP) . . . . . . .

(DP)

........

(ED)

.

Instructions

(C

LC) .

(CP)

(BC)

(BAL) .

(BCT) .

(STP2) .

(LM) .

(STM) . .

Data

(PACK

(SP)

24

24

24

25

and

UNPK).

26

27

29

29

30

.

.

31

31

33

34

35

37

37

37

38

38

39

39

39

41

41

41

Binary

Arithmetic

Binary

Exercise

Logical

Instructions

Logical

Logical

Exclusive

Use

of

Test

Under

Data

Translation,

InputlOutput

Introduction.

Read

Instructions

Writing

Controlling

Error

Flow

Chart

Standard

Sensing

Peripheral

Summary

Example

Exercise

Instructions

Add (AB)

and

Subtract

....

And

(NC) .

Or

(OC)

Or

(XC)

Logicals

Mask

Instruction

Translate

. . . . . . . . . . . .

. . . . . . . . .

(RDF)

Data

(WR)

and

Peripheral

Recognition

of

Device

Exceptional

Unit

of

1/0

of

110

Basic

Byte

Sense

Logic

Coding

. . . . . . .

II

Conditions

........

.

(TM).

(TR)

and

(RDR)

(WRE) .

Devices

0

Logic.

.....

Bytes

..

.

.

(SB) .

.

42

42

42

45

45

45

45

46

.

47

47

49

49

49

50

50

51

52

53

53

54

55

56

57

ii

Page 6

FOREWORD

70/25

This

manual

mayvaryinlengthfrom

outside

depending

recent

self-study.

Principal

self-study

is

designed

assignments

upon

the

programming

references

situations

1.

2.

TRAINING

for

use

about

15

and

work

experience

experience

which

are:

70/25

70/25

of

should

Assembly

System

in

formal

classroom

sessions)

the

student.

may

find

be

Manual

Reference

MANUAL

training

hours

to

used

(with

45

hours

People

the

in

either

Manual

programs

text

appropriate

or

with

good

helpful

formal

which

more,

and

in

or

iii

Page 7

GENERAL

DESCRIPTION

INTRODUCTION

The

RCA

70/25

Spectra

70

Data

small-to-medium

with

communications

high-volume

capabilitie

70/25

The

RCA

stored

Speed

the

appropriate

Systems

HIGH-SPEED

The

High-Speed

device

grams

16,384,

smallest

of

eight

location

consisting

instruction,

register.

0ry

address.

The

Memory

the

time

a

memory

in

storage.

message

s.

PROCESSOR

70/25

program,

Magnetic

standard

MEMORY

that

provides

and

data.

32,768,

addressable

information

maybe

of

two

and a base

The

it

takes

register

is

the

intermediate

Processing

scale

gear,

data

the

series.

processor.

70/25

switching

Processor

digital

Core

Memory,

Input/Output

Interface

Memory

storage

The

or

65,536

unit

bits

accessed

is a general-purpose,

machine

Program

logic

Unit.

(HSM)

and

memory

bytes.

in

memory,

and a parity

with a 16-bit

parts: a displacement

address

sum

of

the

two

form

Cycle

is

1.

5

microseconds,

to

transfer

and

four

to

regenerate

member

It

is a powerful

has

high-speed,

or

remote

that

includes

Control,

for

the

is a magnetic

work

area

capacity

A

and

bit.

binary

carried

stored

an

effective

bytes

in a general

from

of

Equipped

processing

High-

Spectra

core

for

pro-

is

either

byte

is

consists

Each

byte

address

in

mem-

which

HSM

the

bytes

the

and

70

the

an

is

to

70/25

hardware.

ence

of

interrupt

the

Interrupt

INSTRUCTION COMPLEMENT

The

RCA

70/25

instructions

1.

DATA

HANDLING

The

data-handling

ment

of

data

without

or

late

changing

edited

for

instruction

conditions,

State.

Order

which

fields

format

printing

facilitates

It

automatically

Code

can

be

instructions

within

or

during

validation.

2.

ARITHMETIC

This

set

and

Divide

Subtract

to

perform

3.

DECISION

The

decision

comparing

the

branching

Condition

and

Link

simplify

includes

instructions,

operations.

Boolean

of

Code

and

subroutine

INSTRUCTIONS

Decimal

as

It

also

Operations

AND

CONTROL

and

control

both

Decimal

to a location

Indicator.

Branch-Qn-Count

linkage,

coding.

4.

INPUT/OUTPUT

senses

and

transfers

consists

divided

HSM.

it

the

code

into

four

allow

for

Data

may

can

be

packed,

movement. A Trans-

conversion

Add,

Subtract,

well

as

Binary

incorporates

on

bit

structures.

instructions

and

in

HSM

Also

included

allow

Binary

according

instructions

and

control

the

control

of

thirty-one

classeso

the

be

unpacked

and

Multiply

Add

the

fields,

are

Branch

of

iterative

pres-

movemoved

data

and

ability

for

the

and

to

that

to

a

PROGRAM CONTROL

The

Program

the

program

be

interpreted

only

after

process

of

the

instruction

staticizing.

then

executed

AUTOMATIC

The

RCA

tions

in

sing

State

State

is

that

causes

the

Interrupt

stored

it

of

interpreting

An

by

INTERRUPT

70/25

one

of

and

the

normal

interrupt

State.

Control

and

has

instruction

the

can

two

the

executes

in

the

HSM.

executed

been

in

and

the

by

brought

placing

proper

Program

staticize

and

programming

Interrupt

mode

will

State.

of

operation. A condition

transfer

Interrupt

the

An

the

Program

out

registers

is

first

Control

execute

states;

is

mechanized

instructions

instruction

of

HSM.

the

components

staticized

logic.

all

the

The

Processing;

the

computer

Control

is

called

instruc-

Proces-

in

of

can

The

and

to

the

Read

and

Write

the

processor

to

the

70/25.

to

control

from

INSTRUCTION FORMAT

There

70/25;

tion.

the

error

are

six-byte,

The

operation

remaining

storage

addresses,

instructions

and

Included

devices

conditions.

three

four-byte,

first

byte

code.

Depending

byte~

refer

all

basic

identification.

DATA

FORMAT

The

basic

unit

of

storage

peripheral

are

the

and

to

instruction

of

every

to

field

or

contain

transfer

data

equipment

necessary

recognize

instructions

and

formats

and a two-byte

instruction

on

the

instruction,

lengths,

register

peripheral

is

the

byte,

between

on-line

recover

instruc-

which

in

the

is

the

the

and

device

can

Page 8

represent,

or

numeric

packed

Extended

(EBCDIC) .

INPUT

The

devices

format.

/OUTPUT

RCA

through

in

the

unpacked

character,

Data

is

Binary-Coded-Decimal

70/25

communicates

eight

I/O

format,

or

two

represented

channels.

numeric

Interchange

with

one

digits

in

HSM

peripheral

alphabetic

in

the

in

the

Code

Each

peripheral

electronics

the

status

generated

Each

channel

ing

execution

processor.

in

the

system

powerful

in

of

the

by

an

is a separate

overlap

An

II

overlap

device

order

to

device,

I/O

command.

0

termination

to

facilitate

capabilities.

contains

transmit

and any

simultaneous

with

other

interrupt

efficient

its

own

to

the

error

mode,

channels

use

control

processor

conditions

allow-

and

is

included

of

these

the

2

Page 9

HIGH-SPEED

MEMORY

INTRODUCTION

The

RCA

70/25

(HSM)

planes.

(4 x 64 x 64

sable

information

Bit

Bit

Four

register

may

Each

unit

Identification

(X

= 0

or

1)

bytes

of

and

consist

plane

bytes).

in

bits

microseconds.

side

or

in

parallel.

MEMORY

REGISTER

0

1

2

magnetic

of

contains

The

memory,

and a parity

27

P

X

X X X X X

HSM

may

regenerated

These

core

one,

byte

and

BYTE

6 25

2

be

transferred

four

High-Speed

two

or

16,384(10)

is

the

smallest

is

made

bit.

24

in

memory

bytes

are

Memory

four

memory

byte

locations

addres-

up

of

3

22

2

21

X X X

to a memory

within

moved

side

HSM

eight

0

2

1.5

by

Examples:

215

0 0

0

0

0 0

0

1

The

first

of

HSM

quires

one

(1).

Within

bits,

BINARY ADDRESS

13

212

214

0

0

1

1

211

2

0 0 0 0 0 0 0

0

0 0 0

0

0

0

0

1

0

0

0 0 0

1 1

1

example

location

the

25.

adding

BINARY

0

2

3

2

24

the

70/25

are

allocated

10

9

8

2

2

0

1

1 0

0

1 1 1 1

0 0

0

1 1

1

27

2

shows

The

of

the

2n value

DECIMAL

instruction

for

each

1

st

ADDRESS

6

5

24

2

2

1 1

0 0

1

1 0 1

0

0 1

1 1

1 1 1 1

1

0 0 0 0

1

1

1 1

the

binary

conversion

of

EQUIVALENT

1

8

16

-

25

format

memory

3

0

22 21

2

2

1

0

0

1

0

1

1

1 1

1

1

I 0

0

o I 0

1 1

1

1

representation

to

decimal

all

bits

two

address.

2nd

ADDRESS

DECIMAL

EQUIVALENT

109

879

4.094

16.512

65,535

that

bytes,

25

reare

16

To

save

processing

ware

moves

whenever

or

serial

limits

defined

byte

units

of

memory,

first

word.

the

third

term

used

locations

several

70/25

boundaries

HSM

ADDRESSING

The

address

a

binary

dress

the

(65,536).

3

instructions

possible,

transfer

by a specific

are

locations

The

with

to

describe

0,

4,

instructions

(see

of

number.

highest

called

second

8,

etc.

8,

etc.

page

each

time,

returning

when

words.

0,

begins

Even

the

The

41).

byte

Sixteen

location

the

memory

and

data

to a byte

necessary

operation.

The

1,

2,

and

with

Word

initial

addresses

must

location

bits

are

of a four

in

first

3,

boundary

byte

begin

is

required

access

four

byte

after

to

stay

These

four

constitute

location

of

each

contained

at

even-word

expressed

plane

hard-

units

byte

within

four

bytes

the

4,

and

is

the

word;

as

to

ad-

system

in

An

address

ment

of

12

a

base

address

fifteen

The

Bl

most

or

General

B2

containing

B

FIELD

Assume

40,000(10)

is

divided

bits

contained

which

Registers.

significant

fields,

the

associated

0001

(2)

1000(2) -

1111(2) -

0000(2) -

that

General

.

into

is

four

designate

-

General

General

General-

No

base

two

parts:

in

the

pre-stored

bits

of

the

base

address.

Register

Register

Register

address

Register

(1) a displace-

instruction,

in

one

each

address,

General

1

8

15

One

and

(2)

of

the

the

Register

contains

3

Page 10

147

When

an

is

added

the

two

address

example

the

is

added

register

resulting

of

This

technique

addresses

is a fixed

least

significant

for

base

locations

addresses.

This

addressing

larger

dresses

The

r-,--

r----

maximum

2,048

211

1

members

1.024

10

2

1 1 1 1

OP M

the

base

called

to

1,

in

makes

within

length

address

which

exceed

value

256

128

9

8

2

2

F(16)

the

actually

the

an

instructions.

of

bits

values,

require

concept

of

.

64 32

27

26 2

1 1 1 1 1

(16)

instruction

to

is

value

above,

displacement,

may

512

0001(2)

is

staticized

address.

effective

base

effective

it

unnecessary

used

address

address

The

address,

in

Each

12

bits.

However,

of

general

registers

it

is

13,

possible

14, 15,

is a necessary

the

Spectra

16-bit

70

lengths.

of a displacement

--

16

4 2

1

8

3

5

22 21

24

2

2°

1

1

4000(10)

the

displacement

absolute

execution.

in

to

carry

displacement

since

may

series

is

DECIMAL

VALUE

POWER

OF

BINARY

ADDRESS

sum

and

is

In

4000(10)

40000(10)

44000(10)

lengthy

the

be

used

to

access

or

16

feature

where

4095(10)'

-~

TWO

the

the

16

bit

ad-

128

256

512

1024

2048

4095

of

in

16

32

64

powers

hexadecimal

press

through F have

values

symbols

of

its

10

the

base,

basic

through

for

system

digits.

been

the

digital

any

value

requires

assigned

15

in

can

The

to

order

values

be

expressed.

sixteen

alphabetic

represent

to

of

the

symbols

letters

the

maintain

hexadecimal

The

to

ex-

decimal

single

A

system.

Each

symbol

expressed

fore,

two

sent a byte,

an

HSM

HEXADECIMAL

2

4

8

in

by

four

hexadecimal

and

address.

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

the

bits

four

hexadecimal

hexadecimal

in

the

binary

marks

are

BINARY

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

system

system.

required

marks

DECIMAL

I

I

I

can

10

11

12

13

14

15

can

There-

to

repre-

express

0

1

2

3

4

5

6

7

8

9

be

When

addressing

4095(10)'

a

displacement.

D1

or

value

B2

fields.

no

D2

fields

0000(2)

base

HEXADECIMAL

The

binary

is

not a convenient

hexadecimal

the

base

the

binary

The

upon

(0-9)

positional

sixteen,

decimal

the

number

to

represent

system,

numbering

representation

system

notation

locations

address

The

need

12-bit

becomes a direct

is

placed

NUMBERING

in

the

SYSTEM

although

notation

for

system,

is a convenient

of

is a numbering

ten.

It

uses

the

basic

digits.

that

indicates

between

be

associated

address

carried

address

corresponding

efficient

the

for

programmer.

which

method

HSM

addresses.

ten

single

By a system

multiplication

0000(10)

when

the

operates

to

express

system

symbols

and

with

in

the

the

B1

and

70/25,

The

based

on

of

by

Conversion

4

of

The

The

to

decimal

4 x

binary

its

decimal

1 x 2

Hexadecimal

number

100

+ 7 x

number

equivalence

5

+ 0 x 24 + 1 x 2

to

Decimal

472

represents:

10

+ 2 x 1 = (472)10

(101101)2

by:

3

+ 1 x 22 + 0 x

32 + 0 + 8 + 4 + 0

+ 1 x 2

+ 1 = (45)10

A

hexadecimal

value

by

by

the

appropriate

multiplying

number

the

value

is

converted

hexadecimal

of

1 Gn .

can

be

0

to a decimal

converted

21

characters

Page 11

Examples:

1.

Convert

1 x

4096

2.

Convert

3 x

3 x 256

The

first

(I024h6

actual

Each

hexadecimal

four

bits.

binary

its

binary

3

16

2

16

768

example

which

machine

Therefore,

by

replacing

value.

(1024)16

+ 0 x

+

(3AFj16

+

10 x 16

+

10 x 16

+

has a decimal

to

Decimal

16

2

+ 2 x

16

1

+ 4 x

16

o + 32 + 4 = (4132)10

to

Decimal

1

+

15 x 16

+ 15 x 1

160

+

shows

(binary)

0001000000100100

address

character

hexadecimal

each

hexadecimal

0

15

the

hexadecimal

value

can

= (943)10

of

(4132)10.

is:

be

represented

is

character

0

address

converted

The

by

to

with

2.

3.

4.

5.

6.

An

effective

of

a

Base

address

___

specify

pute

an

The

decimal

exceed

Convert

binary:

a.

A4E8(16)

b.

E82C(16)

c.

3D71(16)

Convert

decimal:

a.

B5F9(16)

b.

F93D(16)

and!

which

effective

___

following

following

HSM

and a ___

values

or

base

address

address.

value

_

address

are

of a displacement

hexadecimal

hexadecimal

_

stored

fields

is

will

the

of

be

absolute

in

an

used

numbers

numbers

sum

.

The

instruction

to

com-

may

not

to

to

(0001000000100100)2 = 4096

The

second

dress

Exercise:

1.

A

a

the

3AF

has a decimal

byte

___

70/25

example

consists

bit,

and

HSM.

shows

is

of

the

that

value

__

___

+ 32 + 4 (4132)10

the

hexadecimal

of

943.

information

addressable

bits

unit

ad-

and

in

7.

8.

Convert

decimal:

a.

b.

c.

Convert

decimal:

a.

b.

following

1100011000001010(2)

0000101001001110(2)

0010110001100000(2)

following

55067(10)

7007(10)

binary

decimal

numbers

numbers

to

to

hexa-

hexa-

5

Page 12

DATA

AND

INSTRUCTION

FORMAT

DATA

FORMATS

When

representing

character

(packed

UNPACKED FORMAT

A

byte

represent

format,

any

play

Some

the

hexadecimal

indicated

Char.

(unpacked

format).

in

the

one

for

characters

output

A

B

C

D

E

F

G

H C8

I

of

the

in

Hex.

Cl

C2

C3

C4

C5

C6

C7

C9 R

Char.

BLANK

.

(Period)

such

unpacked

alphabetic

example

that

as

more

representation

the

tables

ALPHABETIC

Char.

J

K

L

M

N

0

P

Q

SPECIAL

<

(

+

& 50

$

*

)

data, a byte

format),

format

or

numeric

is

required

are

to

appear

the

Printer

commonly

below.

Hex.

Char.

Dl

D2

S E2

D3

T

D4

U

D5

V

D6

W

D7

X E7 7 F7

y

D8

D9

Z E9 9 F9

CHARACTERS

Hex.

EO

4B

4C

4D

4E

5B

5C =

5D

may

store a single

or

two

numeric

uses

all

eight

character.

for

the

storage

on

any

type

or

Typewriter.

used

characters,

of

their

bytes

NUMERIC

Hex.

Char.

0

1

2

3

E3

E4 4

E5 5 F5

E6

6 F6

E8 8 F8

Char.

-

(Minus

/ Hyphen)

,

(Comma)

%

# 7B

@

t (Quote)

Space

Hex.

60

61

6B

6C

7C

7D

7E

40

digits

bits

of

are

Hex.

FO

Fl

F2

F3

F4

to

This

of

dis-

and

as

PACKED

In

digits

sign

The

packed

a

UNPACKED

PACKED

It

either

has

SIGN RECOGNITION

In

is

If

one

negative.

Mter a decimal

result

Thus,

data

L

(11 punch)

a

EDITED FORMAT

DATA

packed

except

in

the

following

and

byte

shown

should

be

packing

its

zone

decimal

recognized

(1)

All

(2)

Qriftherightmostbitisa(0}z

(1110)2'

the

sign

of

the

is

one

(1100)2

(1101)2

in

preparing

fields,

e.,

for a negative

zone

portion

FORMAT

data

for

four

example

packed

in

noted

and

arithmetic

as

one

has a low-order

remaining

of

for

for

the

in

the

format,

the

low-order

hexadecimal

or

numeric

positive

bits

arithmetic

the

positive

negative

user

least

of

one

rightmost

shows

format.

1

FO 1 F3

16

103

I

(as

in

the

unpacking a field

portions

operations

ifthe

(1111)2

bits

following:

source

may

follow

field

an

significant

(11012),

byte

stores

byte

bits.

the

Each

location

format.

1 F1 I

1 21 1

example

sign

bit

of

is

(0)

2'

operation

card

existing

overpunch

two

which

contains

same

field

represents

F6

1 F2 1 F1 I 80 I

OS

I

above)

the

rightmo

reversed.

the

sign

position

Le.,

(1)

2'

and

it

is

considered

the

sign

input

for

procedures,

of

the

position

generates

decimal

the

in

un-

that

when

st

byte

of a field

contains:

(1010)2'

at

least

of

the

numeric

minus

A

decimal

assumed

of

the

right

portion,

all

ones

However,

before

arithmetic

numeric

to

contain a sign

most

will

have

(11112),

the

decimal

it

may

be

operation.

byte.

the

used

field

in

All

four

numeric

as

in

unpacked

the

high-order

other

bytes,

high-order

field

an

operand

format

four

in

the

bits a value

must

be

packed

in a decimal

is

bits

zone

of

6

A

packed

format

A

field

sary

I -

numeric

with a single

in

edited

edit

symbols.

1

1 -

field

EDIT

form

is

01 01

0

may

instruction

unpacked

23

I

+

1

2

1

be

and

placed

(see

contains

48

3

in

page

neces-

4

edited

33).

1

-I

Page 13

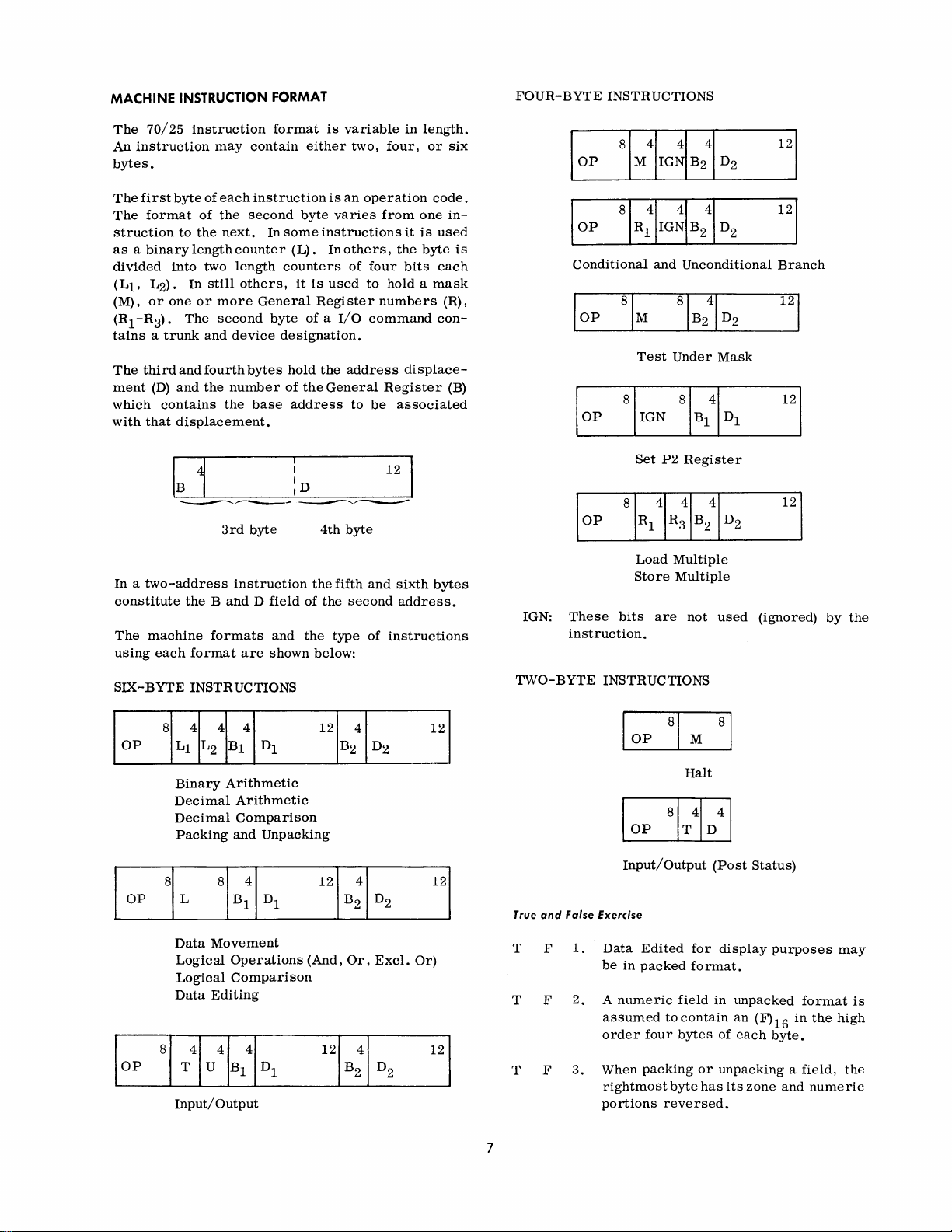

MACHINE

The

An

bytes.

The

The

struction

as a binary

divided

(Ll'

(M),

(R

1

tains a trunk

The

ment

which

with

INSTRUCTION FORMAT

70/25

instruction

first

byte

format

to

into

L2).

or

one

-R3).

third

and

(D)

and

contains

that

displacement.

instruction

may

of

each

of

the

the

next.

length

counter

two

length

In

still

or

more

The

second

and

device

fourth

the

number

the

3rd

format

contain

instruction

second

In

some

counters

others,

General

byte

designation.

bytes

of

base

byte

either

byte

instructions

(L).

it

is

Register

of a I/O

hold

the

the

address

4th

is

variable

two,

is

an

operation

varies

In

others , the

of

four

used

to

command

address

General

to

be

byte

in

length.

four,

or

code.

from

one

it

is

used

byte

bits

each

hold a mask

numbers

con-

displace-

Register

associated

six

in-

is

(R),

(B)

FOUR-BYTE

lop

1

op

Conditional

INSTRUCTIONS

81M41IG~IB241D2

81

R:IIG~I

Test

Set

B241

and

Unconditional

Under

P2

Register

D2

Mask

121

121

Branch

In a two-address

constitute

The

using

SIX-BYTE

the

machine

each

format

INSTRUCTIONS

Binary

Decimal

Decimal

Packing

Data

Logical

Logical

Data

Band D field

formats

Movement

instruction

are

Arithmetic

Arithmetic

Comparison

and

Operations

Comparison

Editing

the

of

and

the

shown

below:

Unpacking

(And,

the

fifth

second

type

Or,

and

sixth

address.

of

instructions

Excl.

Or)

bytes

IGN:

TWO-

True

T F

T F

These

instruction.

BYTE

and

False

1.

2. A numeric

Load

Multiple

Store

Multiple

bits

are

not

INSTRUCTIONS

Halt

Input/Output

Exercise

Data

Edited

be

in

packed

assumed

order

four

field

to

contain

bytes

format.

for

used

(Post

display

in

unpacked

an

of

each

(ignored)

Status)

purposes

(F)16

byte.

format

in

the

by

the

may

is

high

Input/

Output

7

T F

3.

When

packing

rightmost

portions

or

byte

has

reversed.

unpacking a field,

its

zone

and

numeric

the

Page 14

T F

T F

4.

5.

The

negati

The

tion

a

general

values

ve

Bl

or

format

(1101)2

signs.

B2

fields

contain

register.

and

of

the

(1001)2

machine

HSM

are

valid

instruc-

address

of

T F

T

Each

a

12

An

either

instruction

displacement

bit

address.

two,

three,

6.

7.

F

field

is

variable

four,

accommodates

in

length;

or

six

bytes.

8

Page 15

INTRODUCTION

An

interrupt

the

detection

for

an

of

sensing

matic

mechanized

software

unnecessary

develops,

demands.

response

PROGRAMMING

All

instructions

(1)

the

State

of

operation.

transfer

State

the

original

facility

immediate

for

transfer

in

with

and

This

independently

Processing

(P2).

The

from

where

it

Processing

of

to

eliminate s program

provides

exceptional

program

exceptional

of

control

the

RCA

the

hardware

halt

the

system

STATES

are

executed

State

Processing

An

interrupt

the

Processing

remains

conditions,

conditions

70/25

computer

allows

of

his

(P1) ,

until

State.

an

automatic

response.

to

software

hardware.

interrupt

sensing

the

user

production

in

one

or

State

is

causes

State

instructed

means

and a method

The

function

and

the

has

Combining

makes

when

an

of

external

to

program

processing.

of

two

(2)

the

Interrupt

the

normal

the

computer

to

the

Interrupt

to

return

INTERRUPT

The

an

for

auto-

been

it

error

a

states:

mode

to

to

counter

instruction

tions

puter

(see

resets

returns

interruptable.

"PENDING"

State.

Interrupt

instruction.

to

the

lows

automatic

interrupt

process.

TYPES

system

instruction

is

may

remains

page

the

Control

occurs

the

Process

address

the

point

OF

INTERRUPT

is

now

in

the

is

staticized

updated

to

be

39)

P2

be

executed.

executed

in

this

is

executed.

counter

to

Any

until

the

to

contain

state

Pl.

interrupt

computer

only

Therefore,

after

interrupt,

of

the

instruction

where

linkage

permits

considerations

Interrupt

the

the

All

in

the

P2

until a STPP2

The

to

its

The

Interrupt

after

the

when

that

interrupt

the

when

State.

contents

address

thirty-one

state,

STPP2

original

attempted

returns

to

termination

the

system

the

P1

immediately

took

user

programming

Each

of

of

instruc-

and

the

instruction

instruction

value,

State

will

the

Process

counter

place.

to

disregard

time

the

the

next

com-

and

is

not

of

returns

holds

fol-

This

his

P2

be

an

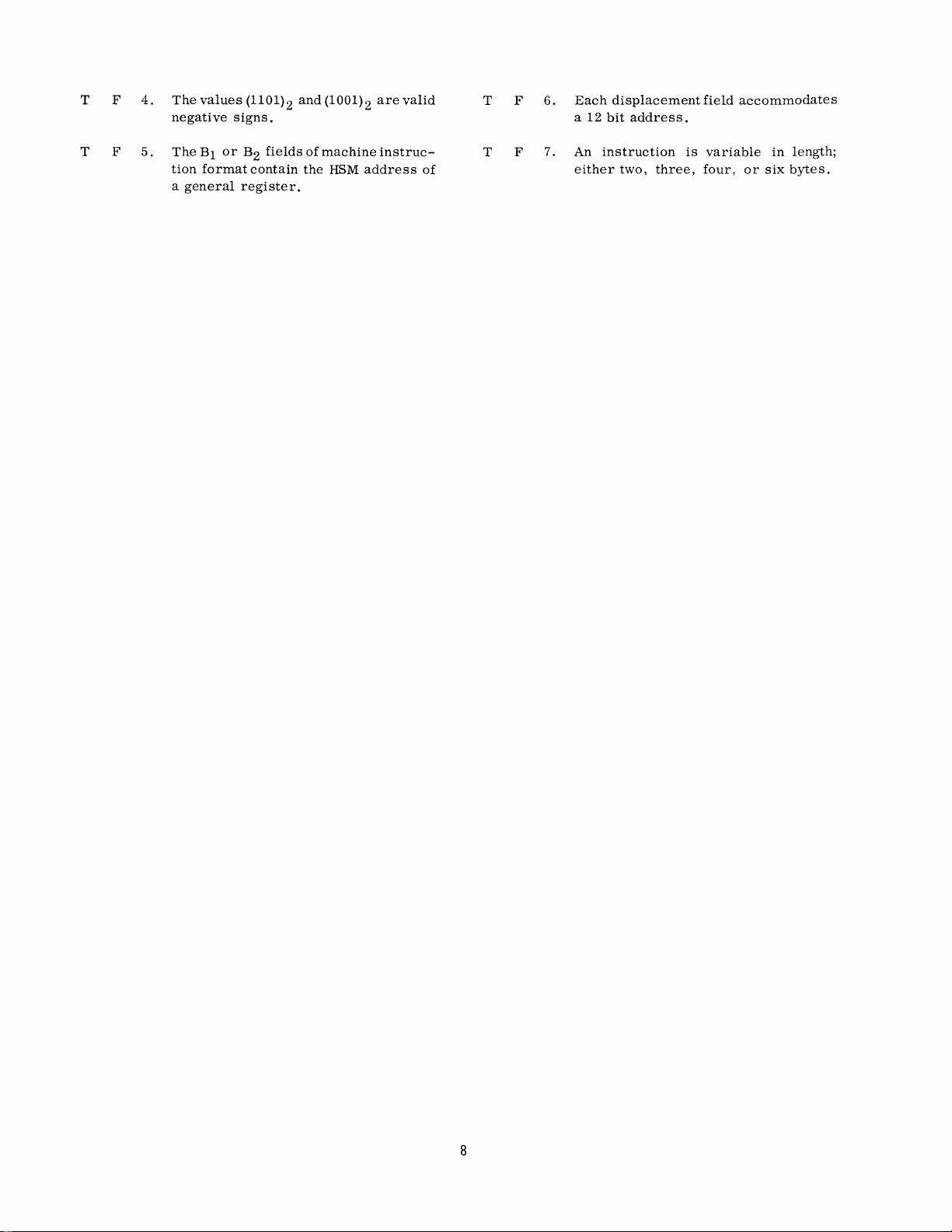

PROCESSING

During

the

address

stored

and

forty-one

121512141213121212111210129128127126125124123122121120

Each

time

the

contents

the

address

instructions

computer

the

in

the

BYTE

an

remains

STATE

execution

of

the

P1

counter

(29)16'

(40)10

instruction

of

the

P1

of

the

may

be

of

next

PI

counter

next

executed

in

this

instructions

instruction

(reserved

COUNTER

is

staticized

is

instruction.

in

state

in

to

be

HSM

BYTE

(41)10

in

updated

All

the

P1

until

the

executed

forty

the

P1

to

thirty-one

state.

an

interrupt

occurs.

INTERRUPT

When

interrupt

to

the

counter

five

STATE

an

exceptional

initiated,

instruction

(reserved

(2D)16)'

BYTE

(44)10

condition

the

whose

HSM

P2

hardware

address

forty-four

COUNTER

is

detected,

transfers

is

(2C)16

stored

in

and

P1

state

(28)16

state

contain

The

and

control

the

P2

forty-

is

an

I

There

are

Processing

1.

I/O

Device

2.

Operation

3.

Arithmetic

4.

Elapsed

1/0

INTERRUPT

An

interrupt

Input/Output

indicates

1.

The

I/O

fully

Indicator

(see

page

2.

The

channel

tion

is

command

event,

set

to

The

purpose

notify

system

able.

With

four

State:

(Manual

Code

Overflow

Timer

occurs

Command.

one

of

two

instruction

(ERROR).

bit

53).

and

now

free,

(NORMAL

the

26

(1)2'

(see

of

software

this

conditions

Trap

Overflow

after

possible

was

In

in

the

Standard

device

and

bit

of

the

page

normal

that

knowledge,

that

can

or

Termination)

or

Divide

the

A

Exception

termination

termination

terminating

not

completed

this

case,

the

Device

that

executed

ready

to

receive

TERMINATION).

Standard

Device

53).

termination

an

the

I/O

interrupt

channel

software

interrupt

of

interrupt

conditions:

success-

Secondary

Byte

the

instruc-

the

Byte

is

can

each

is

(1) 2

next

In

this

is

avail-

the

is

to

use

9

Page 16

efficiently

taining

A

communications

control

generates

ruption

the

Standard

Prior

the

eight

by

the

an

is

distinguished

to

entering

matically:

1.

Stores

The

present

in

the

20 - 21

forty-three

overlap

I/O

operator

I/O

Device

the

state

Channels.

device

Interrupt.

Byte

the

ofthe

value

ofthe

bits

(2Bh6'

capabilities

request,

at

the

console

Console

by

the

fact

is

set

P2

state,

Condition

Condition

of

the

reserved

of a system

or a request

typewriter

that

to

(1)2'

the

computer

Code

Code

request

the

Indicator,

is

HSM

con-

for

also

inter-

27

bit

auto-

stored

location

of

OPERATION CODE

If

an

instruction

code

is

not

one

of

interrupt

Operation

Prior

is

Code

to

entering

initiated.

matically:

1.

2.

Stores

in

Stores

interrupt

two

the

20 - 21

(2A)16'

the

the

state

illegal

in

TRAP

is

staticized

the

Trap.

the

bits

the

thirty-one

This

P2

state,

of

the

Condition

oflocation

operation

reserved

in

which

legitimate

interrupt

the

forty-three

code

HSM

the

Operation

codes,

is

called

computer

Code

Indicator

that

caused

location

auto-

(2Bh

forty-

an

an

6'

the

The

2.

Stores

Number)

reserved

Device

the

3.

Stores

rupting

forty-six

See

page

Byte.

The

P2

struction

occurs.

a

Branch

(00) 2

indicates

I/O

device.

stored

routine

For

example,

one

on

been

depressed,

contain:

~~

Condition

Trunk

127

~~

Number

53

counter

of a routine

This

On

in a reserved

to

identify

Trunk

the

identification

of

HSM

Number

Number

BYTE

126

125124123\

Trunk

the

Standard

device

(2Eh6'

for a desc

contains

routine

Condition

that

The

Trunk

the

if

the

three,

then

Code

Indicator

the

interrupting

location

is

stored

is

(47)10

in

the

ription

to

tests

interrupt

and

area

device

Console

and

HSM

is

(Trunk

forty-seven

in

the

stored

in

22\ 21

Device

Number

Device

Byte

reserved

of

the

the

address

be

executed

the

Condition

instruction).

had

been

Device

of

HSM,

that

caused

Typewriter

the

Interrupt

location

then

set

and

device

(2Fh6'

20 - 23 bits,

the

24 -27

120

for

the

HSM

Standard

of

the

when

interrupt

Code

A

setting

caused

Number

have

allowing

the

interrupt.

is

button

forty-seven

to

(00)

Device

in

The

and

bits.

Inter-

location

Device

first

(with

by

been

Device

had

would

2'

the

in-

of

an

the

BYTE

The

two

dicate

3.

high-order

the

length

00

01

or

11

Sets

the

routine

(01)2

indicates

an

illegal

viously

the

situation,

be

an

error,

latter

case,

struction

For

example,

for

Convert

on

the

could

10

Condition

tests

staticized

that

70/25.

be

bits

of

the

two-byte

four-byte

six-byte

the

that

operation

the

illegal

or

an

the

interrupt

is

not

the

Decimal

However,

simulated

state.

ARITHMETIC OVERFLOW

A

carry

out

of

the

high-order

operand

(FAh6

causes

(FD) 16

rupt

during

or a Subtract

interrupt.

operation

occ

urs

.

the

If

are

the

(42)10

of

the

instruction.

Code

to

Condition

the

interrupt

code

in

the

PI

operation

intentional

part

of

70/45

would

by

instructions

AND

DIVIDE EXCEPTION

execution

Decimal

operands

not

properly

Operation

instruction

instruction

instruction

(01)2'

The

Code. A setting

was

in

the

instruction

state.

Depending

could

interrupt.

could

simulate

the

70/25

order

operation

cause

the

decimal

code

an

position

of

an

Add

(FBh6

of a Divide

edited,

Code

in-

interrupt

caused

by

pre-

on

actually

In

the

an

in-

code.

(4E)16

interrupt

conversion

in

the

P2

of

the

first

Decimal

instruction

Decimal

an

inter-

of

Trunk

3

Device

1

the

ferring

10

Hardware

20 - 21

(2Bh6'

and

to

stores

bits

resets

the

the

of

the

Interrupt

state

reserved

code

State.

of

to

the

Condition

location

(10)2'

forty-three

before

Code

trans-

in

Page 17

ELAPSED

TIMER

INTERRUPT

Exercise:

General

clock.

power)

added

register

intervals

value

Before

of

reserved

reset

INHIBITING

All

be

(31)16

selected

the

tion.

eight

and

A

and

channels

If

channel

addressed

Three

forty-eight

Timer,

CHANNEL

A

mask

plex

arithmetic

INTERRUPT PRIORITIES

the

to

pre-stored

transfer

the

Condition

to

interrupts

inhibited.

allows

eight

The

I/O

a (0)2

mask

seven

an

interrupt

bit

interrupt,

Register

Every

power

the

contents

overflows,

between

location

(11)2'

INTERRUPT

the

I/O

channels.

rightmost

bit

positions,

channels,

bit

inhibits

of

10010110

to

interrupt,

zero,

remains

to

that

positions

(30)

Arithmetic

interrupts.

of

101

in

overflow

Op

Code

16-2/3

except

three,

on

16

I/O

Elapsed

Overflow

Divide

Zero

serves

milliseconds

supply

generates a (1) 2 bit

of

Register

interrupt

interrupts

in

the

register

to

the

P2

state,

Code

is

stored

forty-three

the

Operation

Reserved

user

to

HSM

inhibit

The

bit

positions

(20-27),

0-7.

A (1)2

it.

LOCATION

allows

and

five,

an

I/O

channel

busy

until a Post

channel,

is

(22_2°)

allow

the

user

Overflow,

the

22_20 allows

but

inhibits

or

divide

Trap -immediate

Timer

and

Exception

as

takes

is

controlled

(see

the

in

the

(2Bh6'

location

interrupt

user

places a mask

of

the

correspond

bit

permits

49 (31)16

channels

inhibits

and

six.

Status

executed

in

reserved

to

inhibit

and

21=Overflow

22=Timer

0co

2

Timer

interrupt

exception.

1

2

3

an

elapsed

(using

Zero.

place.

page

current

20 - 21bits

and

Code

Trap

forty-nine

reserved

one,

two,

interrupt

is

inhibited,

instruction,

(see

page

the

MULTIPLEX

Multiplex

and

caused

time

60

cycle

that

When

the

The

time

by

the

13).

setting

the

code

may

on

all

into

loca-

to

the

interrupt

four

from

the

53).

location

Elapsed

Channel

Multi-

by

is

of

or

T F

T F

T F

T F

T F

T F

T F

T F

T F

T F

T F

T F

T F

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

Only

fifteen

structions

Interrupt

The

main

Processing

The

Processing

ruptible.

The

Interrupt

The

Condition

changing

The

Condition

prior

to

The

two

in

the

reserved

The

Processing

counter

next

instruction.

The

PI

interrupt.

The

computer

until

another

The

operation

Operation

The

Standard

an

Operation

Interrupt

only

interrupt

Describe

Describe

Trap.

Write

the

possible

be

stored?

Describe

memory

interrupt

of

the

can

State.

program

State.

State

Code

states.

Code

going

into

program

to

indicate

counter

remains

interrupt

Code

Device

Code

from

that

the

use

two

uses

masks

interrupts.

what

when

each

takes

place.

thirty-one

be

executed

is

State

is

not

is

is

always

the

P2

counters

area

of

State

the

is

destroyed

occurs.

code

is

Trap.

Byte

Trap.

any

r/o

can

be

of

HSM

of

the

necessary

Where

is

stored

of

the

70/25

in

executed

is

not

interruptable.

stored

prior

set

state.

are

stored

memory.

uses

only

address

of

by

in

the

P2

stored

is

stored

device

inhibited.

location

Operation

to

inhibit

must

in

reserved

four

types

inthe

in

the

inter-

to

one

the

the

state

on

is

the

49.

Code

all

they

to

00

an

on

of

11

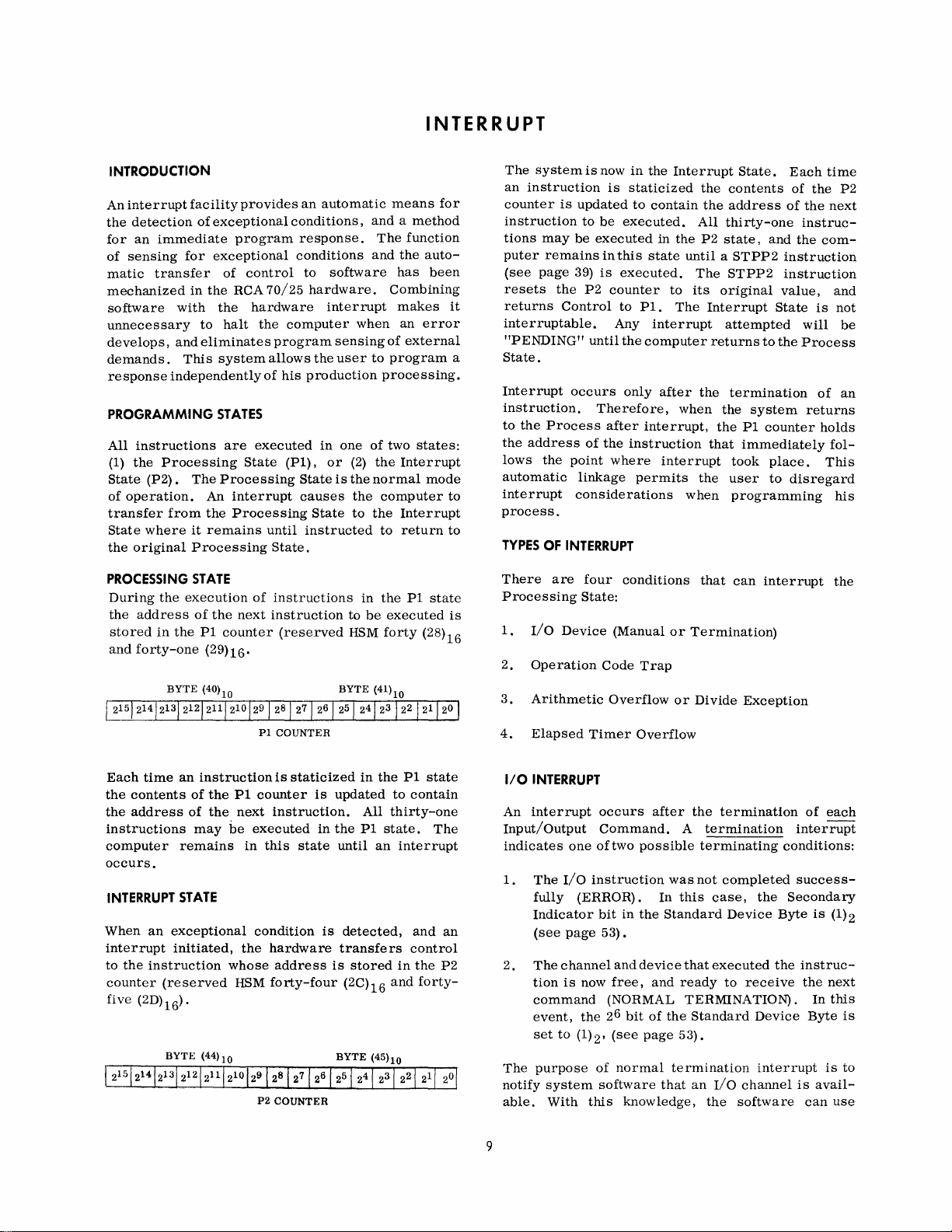

Page 18

SUMMARY

OF

70/25

INTERRUPT

LOGIC

Instruction

Store:

1.

CC

2.

Op

in

Code

Store

in

HSM

HSM

in

CC

43

Op

43

HSM

Arith.

Code

42

Overflow

Trap

Interrupt

Indicator

Set?

Yes

I/O

Op

Code

Arithmetic

Overflow

Elapsed

or

Trap?

Neither

or

Timer?

No

I/O

Store:

1.

2.

3.

Instruction

Interrupt

Inhibi

CC

in

TK

and

Stand.

ted

Mask?

HSM 49

No

HSM

43

DV#

in HSM

DV.

Byte

Set

CC

to

(00)2

Interrupt

"Pending!!

By

47

in

HSM

Yes

48

Return

Transfer

to

Interrupt

Identify

(CC

Setting)

Process

Accordingly

STP2

Register

to

Processing

State

Interrupt

and

12

r

HARDWARE

PROGRAMMING

1

State

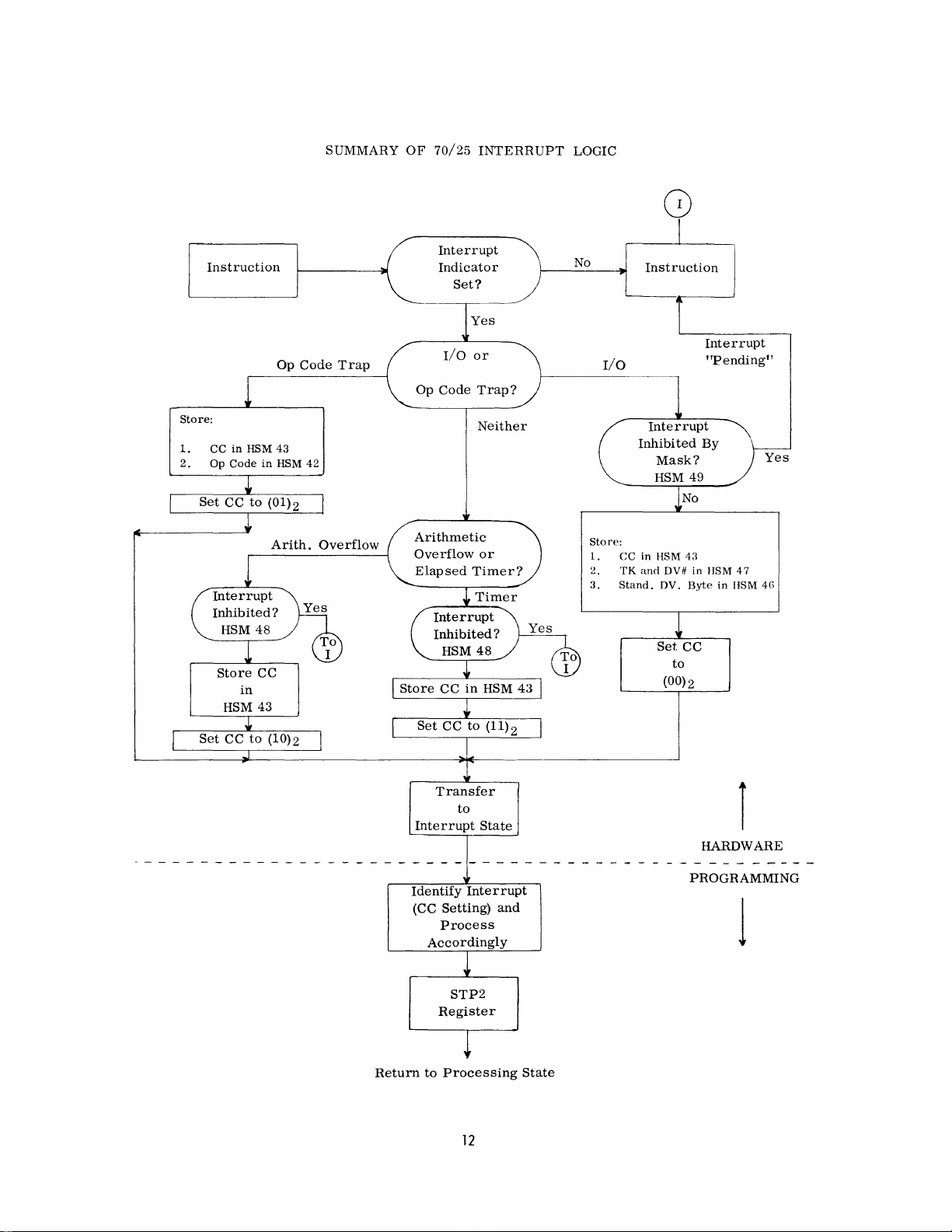

Page 19

The

least

significant

first

General

clock.

every

bit

register

(see

time

tion

A (1) 2

as

If

is

of

follows:

1 ADD

50 ADDS

3000

180000

the

The

16-2/3

added

overflow

page

interval

the

value

is

added

50

CYCLE

EVERY

EVERY

ADDS

EVERY

ADDS

EVERY

Timer

70/25

to

11).

(16,777,215>10'

the

Timer

place

power,

The

meaningful

16-2/3

1

1

contains

approximately

or

77

number

time

MILLISECONDS

SECOND

30

SECONDS

MINUTE

30

MINUTES

1 HOUR

Register,

power

milliseconds

the

contents

develops,

The

programmer

between

stored

to

the

POWER

20

MILLISECONDS

SECOND

MINUTE

HOUR

is

set

the

first

all

93

hours

later

of

adds

intervals

60

CYC

24

bits

of

may

serve

supply

(60

of

Register

an

these

interrupts

in

the

register.

low

order

1 ADD

60 ADDS

3600

ADDS

216000

ADDS

to a value

add

causes

zeros,

hours

later,

using

required

are

indicated

LE

POWER

Register

as

an

generates

cycle

interrupt

may

bit

of

60

CYCLE

EVERY

16-2/3

EVERY

SECOND

EVERY

MINUTE

EVERY

HOUR

of

overflow

using

60

cycle

to

clock

1 ADD

60 ADDS

1800

ADDS

3600

ADDS

108,000

216,000

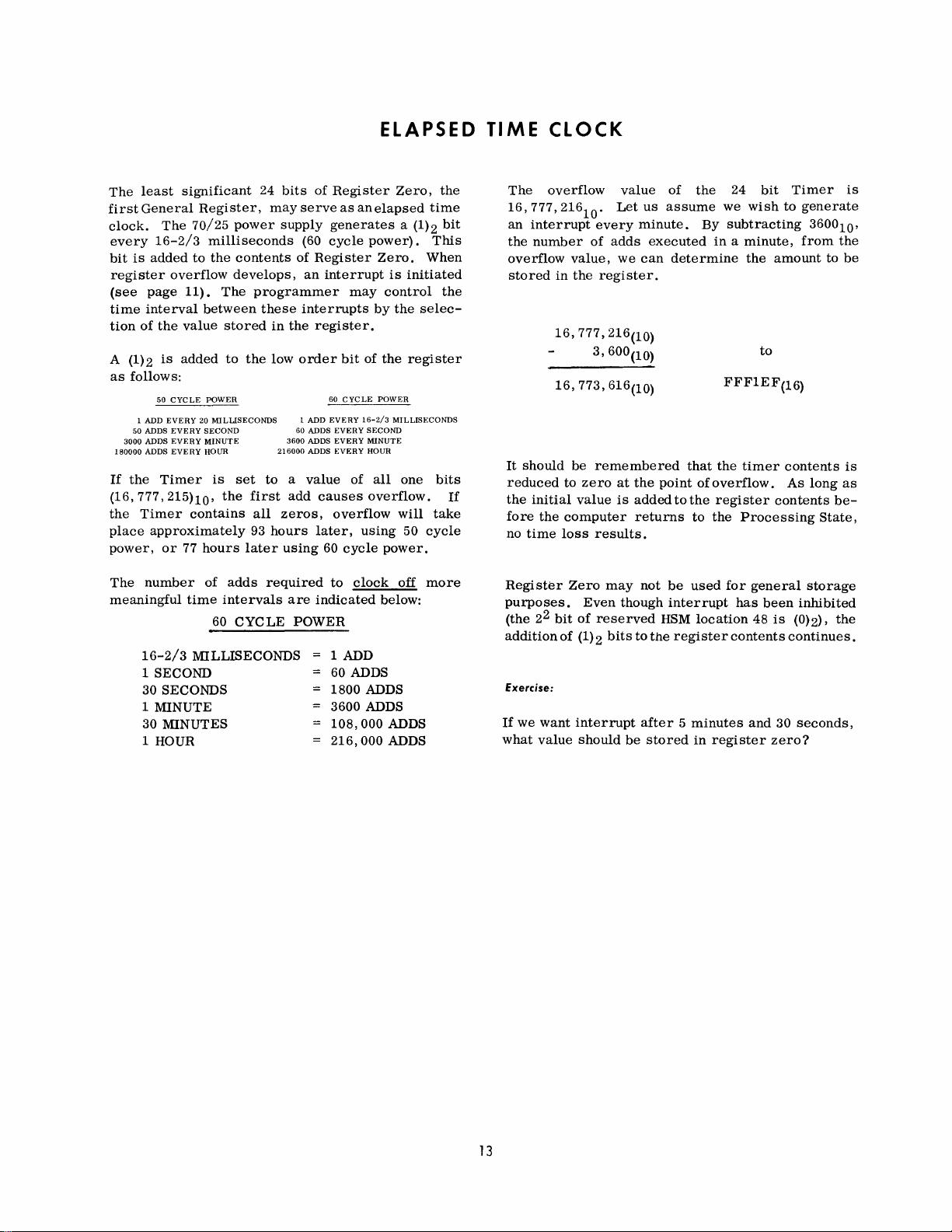

ELAPSED

Zero,

the

elapsed

power).

Zero.

by

the

POWER

all

overflow.

power.

below:

a (1)2

When

is

initiated

control

the

selec-

register

MILLISECONDS

one

will

50

cycle

off

more

ADDS

ADDS

time

bit

This

the

bits

take

If

TIME

The

CLOCK

overflow

16,777,21610.

an

interrupt

the

number

overflow

stored

It

should

reduced

the

initial

fore

the

no

time

Regi

ster

purposes.

(the

22

addition

Exercise:

If

we

want

what

value

value

Let

every

of

adds

value,

we

in

the

register.

16,777,216(10)

3,600(10)

16,773,616(10)

be

remembered

to

zero

at

the

value

is

added

computer

loss

Zero

Even

bit

of

of

(1) 2

returns

results.

may

though

reserved

bits

to

interrupt

should

be

of

the

us

assume

minute.

executed

can

determine

point

to

not

be

we

By

in a minute,

that

the

of

overflow.

the

register

to

the

used

interrupt

HSM

location

the

register

after 5 minutes

stored

in

register

24

bit

wish

to

subtracting

the

amount

to

FFF1EF(16)

timer

contents

As

contents

Processing

for

general

has

been

48

is

contents

and

continues.

30

zero?

Timer

generate

360010'

from

to

long

State,

storage

inhibited

(0)2),

seconds,

is

the

be

is

as

be-

the

13

Page 20

INTRODUCTION

ASSEMBLY

TO

THE

RCA

LANGUAGE

70/25

FORMAT

The

ming

REQUIREMENTS

RCA

70/25

system

machine-oriented

program

system.

statements

Program

forms

1.

2.

3.

for

The

written

Form.

one

of

Generates

Allocates

Notifies

subsequent

source

the

the

function.

OPERATION

Every

output

OPERATION

the

NAME

The

it

is

location

NAME

alphabetic

tion

that

only

asterisk

is

to

OPERAND

statement,

listing

above

FIELD

NAME

desired

of

entry

of

alphabetic

do

not

exception

may

be

used

FIELD

FIELD

comment,

field

three

field

to

the

(A-Z)

exceed a total

appear

for

Assembly

designed

program

language

on

Each

following

an

object

data

areas

assembler

except a line

(Cols.

functions.

(Cols.

symbolically

field

generated

symbol

character

and/or

to

the

symbol

in

an

output

is

an

automatic

to

translate

into a machine-coded

execution

on

consists

the

RCA

Spectra

single-line

functions:

program

or

instruction.

constants.

to

perform a specific

used

must

have

10-14)

1-6

only)

specifying

may

identify

by

the

must

consist

followed

numeric

Col.

listing

of

1

six

entry

if

by

(0-9)

characters.

above

the

comment.

program-

a

symbolic

the

RCA

of

one-line

70

Assembly

statement

solely

an

entry

be

used

the

leftmost

statement.

of

at

least

any

combina-

characters

is

statement

70/25

per-

for

in

one

when

that

an

the

of

The

one

The

an

line

IDENTIFICATION

The

contents

functions.

positions,

assigned

positions,

is

used

counter.

zeros.

number

77-80

ADDRESSING

A

symbolic

of

addressing

symbol

location,

sired

the

struction

As

stated

bination

There

six

characters,

as

Each

either

or

from

has

it

in

the

address

on

of

are

columns

to

columns,

the

If

previously,

the

two

phabetic.

The

following

symbols:

VALID

Al

STKNKI

C

INI

FIELD

of

the

In

the

START

73-76,

the

object

initial

not

numeric,

object

derived

zeros.

name

is

and

referencing a location.

been

used

may

be

OPERAND

of

the

left

the

'NAMEd'

alphabetics

restrictions:

(2)

are

IDENTIFICATION

statement,

may

contain a name

program.

77-80,

setting

are

ofthe

the

instruction

from

the

most

in

the

referenced

field.

end

line

the

symbol

(A-Z)

the

first

examples

If

numeric,

Assembly

counter

the

value

frequently

NAME

as

frequently

The

value

of

the

of

assembly

may

or

(1) no

name

character

of

valid

has a sequence

field

the

first

the

last

the

starts

in

used

field

to

assigned

data

field

be

any

numerics

may

must

and

has

two

four

to

four

contents

sequence

at

all

columns

means

When

define

as

de-

or

in-

coding.

com-

(0-9).

exceed

be

al-

invalid

be

a

a

is

The

OPERAND

OPERATION

specifies

that a constant

OPERAND

If

an

instruction

OPERAND

for

that

particular

COMMENTS

A

comment

lowing

from

blank

may

in

Column

the

the

required

column.

be

used

FIELD

field

field.

field

Thus,

entry

Operation

field

must

instruction.

may

appear

OPERAND

OPERAND

The

entire

for a comment

1.

has

is

follow

entry.

entries

if

the

is

being

the

value

Code

the

in

any

It

entry

statement

if

an

as

required

OPERATION

defined,

of

the

constant.

appears,

prescribed

statement

must

line

by

be

separated

at

least

(to

line

Col.

asterisk

by

the

field

the

the

format

fol-

one

71)

appears

INVALID

The

symbolics

HSM

LOCATION

tained

and

begin

14

OPN

BEGINERR

IA

IN.I

Assembler

that

address

COUNTER, a program

by

the

Assembler,

makes

at

HSM

assignments.

location

(Space

(Too

(First

(Period

builds a table

appear

is

in

assigned

2000.

invalid

many

character

characters)

invalid

character)

not

character)

containing

the

name

field. A specific

to

each

symbolic.

counter

generates

these

Assume a routine

alphabetic)

all

The

main-

addresses

is

the

to

Page 21

The

Controlling

NAME

places

the

counter.

instructions,

always

able.

placed

the

contains

If

in

current

a

Consider

ASSEMBLY

STATEMENT

*Note

that

the

to

orient

the

instruction

**NO

SYMBOL

IMPLICIT

BASE

Code,

OPERATION

START

initial

As

value

memory

the

counter

the

statement

the

table,

value

in

the

following

CONTENTS

OF

LINE

A

5-byte

field

A

2-byte

field

A

lO-byte

Constant

A

6-byte

Instruction

A

4-byte

Instruction

Location

Counter

to

an

(TAG)

ASSIGNED.

ADDRESS

OPERAND

Xt7D~t

of

(2000ho

is

allocated

is

incremented

address

at

the

contains a name,

and

assigned

the

counter.