Page 1

Microprocessor

Products

User Manual

for

the

COSMAC

Microprocessor

Page 2

User Manual

for the

COS

MAC

Microprocessor

RCA I Solid State Division I Somerville, NJ 08876

Copyright 1975

(All

rights reserved under Pan-American Copyright Convention)

Printed

in

USA/5-75

by

RCA

Corporation

Page 3

2

Information furnished

reliable.

However,

its

use;

third

granted

patent

nor

parties

rights

for

by

implication

no

any

infringements

which

of

RCA.

Trademark(s) Registered ®

M,arca(s) Registrada(s)

by

RCA

responsibility

may

result

or

otherwise

is

believed

of

from

is

assumed

patents

its

under

to

use.

be

or

accurate

by

other

No

any

RCA

rights

license

patent

and

for

of

is

or

Page 4

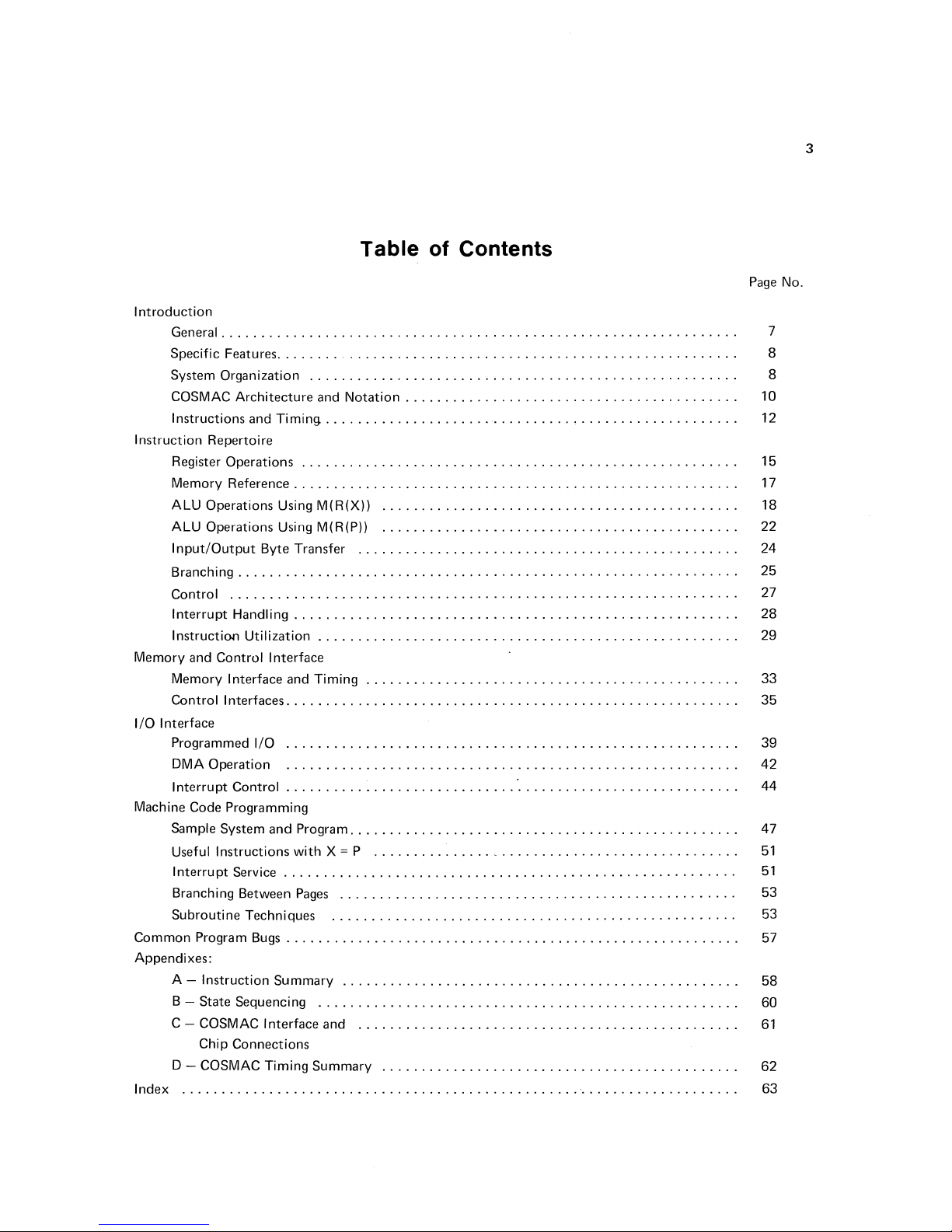

Table of Contents

Introduction

General. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Specific Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

System Organization

COSMAC

Instructions and Timing.

Instruction

Register Operations

Memory Reference

ALU

ALU

I

nput/Output

Branching.

Control

Interrupt

Instruction

Memory

Memory

Control Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O

Interface

Programmed

DMA

Interrupt

Machine Code Programming

Sample System and Program. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Useful Instructions

I nterru

Branching Between

Subroutine Techniques

Common Program

Appendixes:

A -

B - State Sequencing

C - COSMAC Interface and

D -

Index

..................................................

Architecture

Repertoire

Operations Using

Operations Using M(R(P))

Byte Transfer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

................................................................

Handling.

Utilization

and Control Interface

Interface and

I/O

Operation

Control

pt

Service . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bugs.

Instruction

Chip Connections

COSMAC

......................................................

and

Notation.

..

. . . . . . .

......................................................

.......................................................

M(R(X))

................................................

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

...

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Timing

with

Pages

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Summary

.....................................................

Timing

Summary

......................................

X = P

..................................................

..................................................

................................................

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

..

. . . . . . . . .

...............

.............................................

..

. . . . . . . . . • . . . . . . . . . . . . . . . . . . . . 12

. . . . . . . . . 33

,..............................

'.

. . . . . . . . . . . . . . . . . . . 63

.

.

Page

8

15

17

18

22

24

27

28

35

39

42

44

51

51

53

53

58

60

61

62

3

No.

Page 5

4

Page 6

The

RCA

Microprocessor

suitable

either

engineers,

set

circuits. Because

driven,

and

flag

programming

response,

them

mation

MPM-102

for

use in a

special

or

This User Manual provides a

and

of

simple, easy-to-use

For

systems

and

direct-memory-access

the

use

of

inputs,

This manual also describes

This basic

command

long

in

developing

on

the

"Program

wide

general-purpose

assumes

designers,

the

processor

the

I/O

interface

lines, processor

errors

are discussed,

branch,

manual

operation

and

is

simpler

Development

Foreword

(COSMAC)

range

of

in

detailed

no

familiarity

instructions.

this

manual illustrates practical

is

lines.

machine-code

subroutine

intended

and

more

of

the

RCA COSMAC

is

stored-program

nature.

guide

with

Examples are given

capable

modes,

to

Guide

detailed

The

latter

state

and

various

linkage

help design engineers

powerful

for

an

LSI

CMOS

computer

to

the

computers.

of

supporting

examples

include

indicators,

programming

programming

and

nesting.

products

Microprocessor

the

COSMAC

8-bit

register-oriented

systems

COSMAC Microprocessor. It

It describes

to

illustrate

methods

input/output

are provided

direct-memory-access

and

external

methods

techniques

understand

based on

Microprocessor".

and

the

the

of

adding

timing

and

the

microprocessors.

software

central

products.

microprocessor

operation

external

(I/O) devices

for

the

use

and

pulses.

gives

detailed

are

described,

COSMAC

support

system

processing

These

systems

is

written

of

each

memory

of

interrupt

Microprocessor

Users requiring infor-

for

architecture

instruction.

and

in

polled,

the

I/O

instructions

inputs,

examples.

including

should

refer

interrupt-

unit.

It

may

be

electrical

and

its

control

external

Potential

interrupt

and

aid

to

the

is

Page 7

6

Page 8

7

I ntrod

uction

General

The COSMAC Microprocessor has been developed

cations. COSMAC

communications,

The

RCA COSMAC Microprocessor

for use

in

a wide range

or

general-purpose in

COSMAC

operation

behavior

program(s)

the

components

cuting

control

supply,

features

High noise

maximum

reduced by means

circuitry. A single-phase clock, internal direct-memory-access (DMA)

program

at

total

support

language

COSMAC

The

28-pin dual-in-line package).

summarizes

codes are called instructions. Sequences

or

function

stored

basic advantage

The COSMAC microprocessor includes all

instructions

features are also provided

Microprocessor

system-control,

combine

COSMAC's low-power, single-voltage CMOS

immunity

COSMAC

system

The 40-pin COSMAC system interface

interrupt,

system

Microprocessor programming

software

programming

provides a

COSMAC microprocessor comprises

the

is

suitable for use

and

other

of

nature.

operations

of

in

memory.

of a stored-program

(memory

compatibility

and

which have been

cost

to

minimize

and

flexibility

of

an efficient

program load

cost

reduction.

and

support

set

COSMAC

in

business,

applications where

stored-program

They

are

byte-oriented, a byte

are specified by sequences

a COSMAC-based system. System

This ability

microprocessor)

stored

to

facilitate

is

only

a small

and

programming costs are also major considerations. A

the

wide

temperature

with

for

COSMAC does

hardware are available

is

sometimes

of

efficient, easy-to-Iearn

Appendix

system

part

total system cost.

standard,

both

current

one-byte

mode,

is

facilitated

indicated

interface signals.

stored

is

a CMOS

computer

to

change

computer.

in

a variety

of

in

standard

system

of

total

tolerance

high-volume memories assures

and

instruction

is

designed

and

static

not

by

two

C shows

and

tested

within RCA in a wide variety

education,

program

byte-oriented

systems

of

one-byte

of

instructions,

function

Reduced

of

different

the

circuits required

types

design.

system

circuitry

facilitate use

future

format.

to

circuitry

require an external

a variety

for

when

only a few

instructions

conservatively designed LSI chips (one 40-pin

the

required

entertainment,

control

or

products.

being eight bits.

functions

or

product

minimizes power-supply

applications. Program storage

minimize external I/O and

are

of

use

which

interconnections

is

central processing

operation

called programs,

are easily changed

without

cost

results

systems

of

memories. Extensive input/output

cost.

in

hostile

other

bootstrap

support

in

developing COS MAC systems. Machine-

short

are simple

instrumentation,

desired.

unit

(CPU). It

These systems can be

codes

stored

in a

determine

by

extensive

for

mode,

COS MAC

programs

programs need

hardware

from

using identical

or

products.

fetching,

Memory,

environments.

minimum

interpreting,

input,

unique

and

flexible I/O

features

ROM.

or

to

use.

for

these

set

packaging costs.

memory

requirements

memory

software.

to

two

of

appli-

control,

is

suitable

either

special

memory.

modifying

modification

output,

explicitly

be developed.

LSI

These

the

specific

hardware

and

(I/O)

power-

of

COSMAC

cost

control

instructions,

aimed

Extensive

and

chips

the

is

exe-

and

are

one

and

Page 9

8

Specific Features

The advanced features and

• static

•

• high noise

•

•

•

•

•

•

•

•

•

•

•

• 16 x

COS/MOS

full

military

TTL

compatibility

8-bit

parallel

built-in

any

combination

direct

memory

flexible

program

on-chip

four

I/O

one-byte

59

easy-to-use

16

temperature

immun

organization

program-load

addressing

programmed

interrupt

DMA

facility

flag

inputs

instruction

instructions

matrix

of

circuitry,

ity,

wide

facility

of

standard

I/O

mode

directly

format

registers

operating

no

minimum

characteristics

clock

range

operating-voltage range

with

bidirectional

RAM/ROM

up

to

65,536

via

bytes

mode

testable

with

for

use

by

two

as

branch

machine cycles

multiple

of

the

RCA

COSMAC

frequency

data bus

common

interface

instruction

for

each

instruction

program counters, data

Microprocessor

pointers,

or

data registers

User

Manual for the

include:

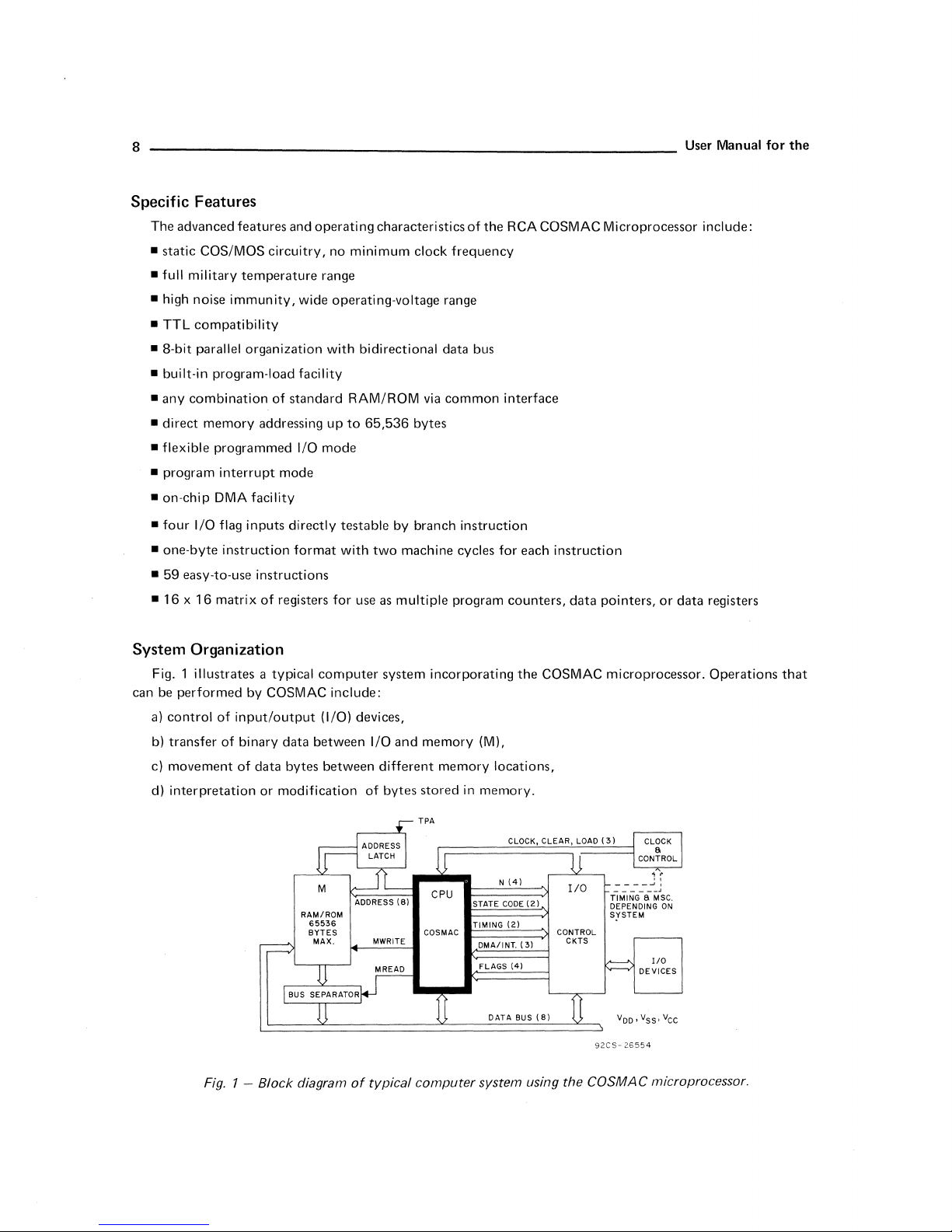

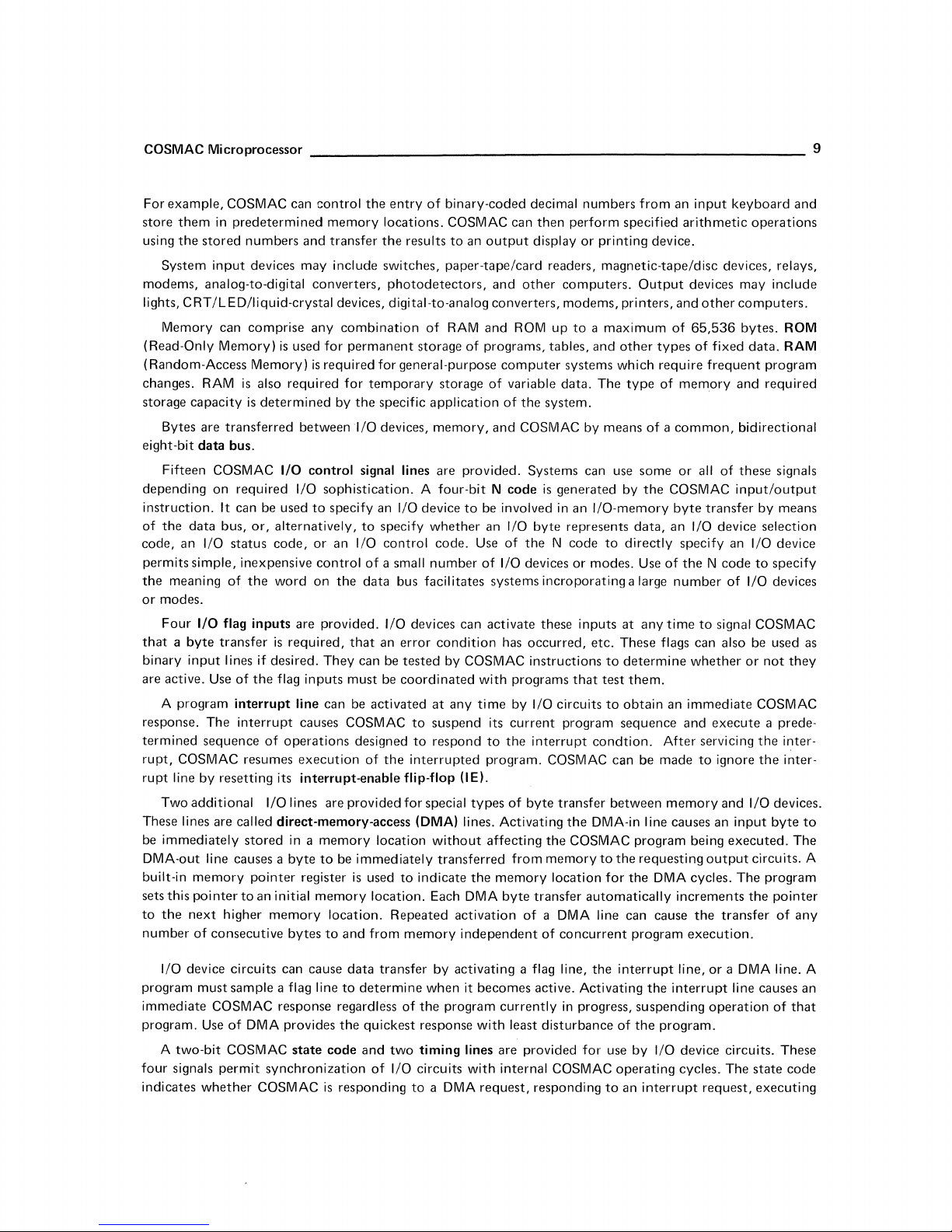

System Organization

Fig. 1

illustrates a typical

can

be

performed

a)

control

b)

transfer

c)

movement

d)

interpretation

of

input/output

of

Fig. 1 -

by

COSMAC

binary

of

data bytes between

or

Block

computer

include:

(I/O)

data between

modification

RAMIROM

65536

BYTES

MAX.

diagram

system

devices,

I/O

and

different

of

bytes stored in

MWRITE

of

typical

incorporating

memory

memory

CPU

STATE

MAC

TIMING

COS

computer

the

COSMAC

(M),

locations,

memory.

N

(41

CODE

(21

(21

DMA/INT.

(31

FLAGS

(41

DATABUS(BI

system using

I/O

CONTROL

CKTS

the

microprocessor.

____

jr

______

TIMING

DEPENDING

SYSTEM

92C5-

COSMAC

J

B MSC.

1/0

DEVICES

26554

microprocessor.

ON

Operations

that

Page 10

COSMAC Microprocessor

_____________________________

_

9

For example, COSMAC can control

store

them

in

predetermined

using

the

stored

System

numbers

input

devices may include switches,

and

modems, analog-to-digital converters,

lights,

CRT

/lED/liquid-crystal

Memory can comprise

(Read-Only Memory)

(Random-Access Memory)

changes.

storage

eight-bit

RAM

capacity

Bytes are

data

is

also required

is

determined

transferred

bus.

Fifteen COSMAC I/O

depending

instruction.

of

the

code, an I/O

permits

the

or

modes.

Four

that a byte

binary

are active. Use

A program

response.

termined

rupt,

rupt

Two

These

be immediately

on

required I/O sophistication. A

It

can be used

data

bus,

or,

status

simple, inexpensive

meaning

of

I/O flag

the

inputs

transfer

input

lines if desired.

of

the

interrupt

The

interrupt

sequence

of

COSMAC resumes

line by resetting its

additional I/O lines are provided

lines are called direct-memory-access (DMA) lines. Activating

stored

DMA-out line causes a

built-in

sets this

to

number

the

memory

pointer

next

higher

of

consecutive

pointer

to

an initial

any

is

used

is

between ·1/0 devices,

control

to

alternatively,

code,

or

control

word

on

are provided. I/O devices can activate these

is

required,

flag inputs

line can be activated

causes COSMAC

operations

execution

interrupt-enable

in a

byte

register

memory

memory

bytes

the

entry

of

binary-coded decimal numbers

memory

transfer

locations. COSMAC can

the

results

to

an

paper-tape/card

photodetectors,

devices, digital-to-analog converters, modems, printers,

combination

for

permanent

of

RAM

storage

of

required for general-purpose

for

temporary

by

the

specific application

storage

memory,

signal lines are provided. Systems can use

four-bit N code

specify an I/O device

to

specify

an I/O

the

They

of

data

that

can be

must

control

a small

bus facilitates systems incroporating a large

an

error

tested

be

coordinated

to

designed

of

to

the

interrupted

to

whether

code.

number

condition

by COSMAC instructions

at

any

suspend its

respond

flip-flop (I E).

for

special

types

memory

to

location

be immediately

is

used

to

indicate

without

transferred

the

location. Each DMA

location.

to

and

Repeated

from

memory

activation

independent

from

then

output

perform

display

specified

or

printing device.

readers, magnetic-tape/disc devices, relays,

and

other

computers.

and

ROM

up

to a maximum

programs, tables,

computer

of

variable

of

and

systems which require

data.

the

system.

COSMAC by means

and

The

Output

other

type

of a common,

some

is

generated by

the

be involved in an I/O-memory

an I/O

Use

of

with

time

to

program. COSMAC

affecting

byte

of

the N code

I/O devices

has

occurred,

programs

by I/O circuits

current

the

interrupt

of

byte

transfer

the

from

memory

memory

byte

location

transfer

of

a DMA line can cause

of

concurrent

represents

or

inputs

that

data,

to

directly

modes. Use

at

any

etc.

These flags can also be used

to

determine

test

them.

to

obtain

program sequence

condtion.

can

be made

between

the

DMA-in line causes an

COSMAC program being

to

the

requesting

for

the

automatically

program

an

input

keyboard

arithmetic

operations

devices may include

and

other

computers.

of

types

of

memory

65,536

of

bytes. ROM

fixed

data.

frequent

and

program

required

bidirectional

or

all

of

these signals

COSMAC

byte

input/output

transfer

by means

an I/O device selection

specify an I/O device

of

the N code

number

time

to

whether

an

immediate

and

After servicing

to

memory

to

specify

of

I/O devices

signal COSMAC

or

not

COSMAC

execute

a prede-

the

ignore

the

and

I/O devices.

input

byte

executed.

output

circuits. A

DMA cycles.

increments

the

The

the

transfer

program

pointer

execution.

RAM

they

interinter-

of

and

as

to

The

any

I/O device circuits can cause

program

immediate

program. Use

four

indicates

two-bit

A

signals

must

sample a flag line

COSMAC response regardless

of

DMA provides

COSMAC

permit

whether

state

synchronization

COSMAC

data

to

determine

the

quickest

code

and

is

responding

transfer

of

two

of

I/O circuits

to a DMA

by

activating a flag line,

when

it

becomes

the

program

response

timing

currently

with

lines are provided

with

internal COSMAC

request,

active. Activating

in

progress, suspending

least

disturbance

for

responding

the

interrupt

of

use

operating

to

line,

or

a DMA line. A

the

interrupt

line causes an

operation

the

program.

by

I/O device circuits. These

cycles.

The

an

interrupt

request,

of

that

state

code

executing

Page 11

10

__________________________________

an

input/output

signal a new processor

set

and

reset

Bytes are

lines

to

control

the

data

is

generated

level

instruction,

I/O

controller

transmitted

memory

bus

and a memory

which

or

state

code,

flip-flops.

to

and

read/write

write pulse

is

used by

none

to

from

the

of

thp.se. The

latch

memory

cycles. During a

is

system

timing

memory

by

generated

to

gate

signals are used

address bits,

means

of

memory

by

COSMAC

the

memory

the

write

output

to

take

common

cycle,

at

the

byte

by

the

memory

memory

the

appropriate

data

from

data

bus. COSMAC provides

byte

to

be

time. A memory

onto

the

common

User Manual

and

I/O systems

the

bus,

written

data

appears

bus.

for

and

the

to

to

two

on

read

COSMAC provides eight

form

of

two

successive 8-bit bytes. The more significant (high-order) address

address lines first, followed by

required

4096-byte

from

timing

eight

for

input

operation

step.

mode

COSMAC

results in a

sixteen general-purpose 16-bit

binary

decimal digits (0,1,2, ... E,F)

Appendix

0011.

order

individual 16-bit

16-bit A register.

lines

the

incremented

register

N,

left half

can be

hex digit in N are

to

select a

memory

the

high-order address

pulses

address lines. An internal COSMAC register holds

the

remainder

Three

additional

determines

with

The

load signal line holds

is

discussed

strobes

of

operating

system

in

would

the

the

Architecture

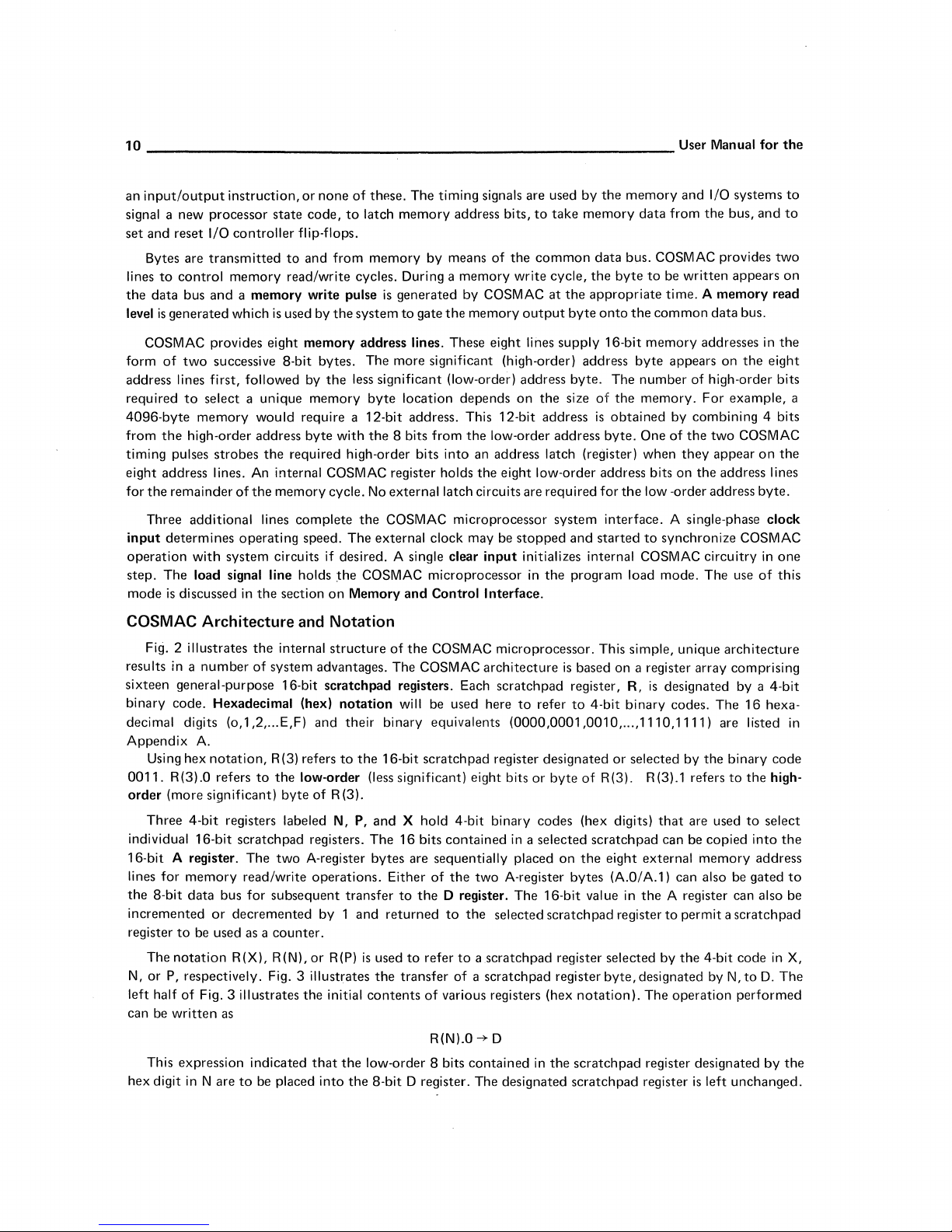

Fig. 2 illustrates

number

code.

A.

Using hex

R (3).0 refers

(more significant)

Three

4-bit

for

memory

8-bit

data

to

be used as a

The

notation

or

P, respectively. Fig. 3 illustrates

of

Fig. 3 illustrates

written

This expression indicated

the

of

Hexadecimal (hex)

notation,

to

registers labeled N, P,

scratch

The

read/write

bus

for

or

decremented

R(X), R(N),

as

to

be placed

memory

unique

lines

memory

require a 12-bit address. This 12-bit address

byte

the

required high-order bits

memory

complete

speed.

circuits if desired. A single clear

section

and

internal

system

R (3) refers

the

low-order (less significant) eight bits

byte

of

pad registers.

two

A-register

operations.

subsequent

counter.

or

the

that

address

the

less significant (low-order) address

byte

with

the

cycle. No

the

on

external

the

COSMAC microprocessor

The

external clock may be

COSMAC microprocessor in

Memory

Notation

structure

advantages. The COSMAC

scratchpad

notation

and

their

binary equivalents

to

the

16-bit

R(3).

and

The

bytes

Either

transfer

by 1 and

R(P)

initial

into

returned

is

used

the

contents

the

low-order 8 bits

the

8-bit

lines. These eight lines

location

8 bits

and

of

the

registers. Each

will be used here

X hold 4-bit binary

16

are sequentially placed

to

to

transfer

D register. The designated

depends

from

the

low-order address

into

an address latch (register)

the

eight

latch circuits are required

input

Control

COSMAC microprocessor. This simple,

scratch

bits

of

the

refer

of

R(N)_O

Interface.

architecture

scratchpad

(0000,0001,0010,

pad register

contained

the

D register.

to

to a scratchpad

of

various registers (hex

in

two

A-register

the

selected

a scratch pad register

-7

D

contained

supply

byte.

on

the

size

low-order address bits

system

stopped

to

The

and

initializes internal COSMAC

the

program load

is

based on a register array

register, R,

refer

to

designated

or

byte

of

codes

(hex digits)

a selected

on

the

bytes

16-bit

scratch

register selected

notation).

in

the

scratch

scratch

16-bit

memory

byte

The

number

of

the

memory.

is

obtained

byte.

One

when

for

the

low -order address

interface. A single-phase

started

to

is

4-bit

binary

...

,1110,1111)

or

selected by

R (3). R (3).1 refers

scratch

pad can be

eight

external

(A.O/ A.1) can also be gated

val

ue in

the

pad register

byte,

designated by

The

pad register designated

pad register

addresses in

appears

by

of

synchronize

mode.

designated by a

codes.

that

A register can also be

to

by

operation

on

of

high-order bits

For

combining

the

two

they

appear

on

the

address lines

circuitry

The

unique

architecture

The

are listed in

the

are used

copied

memory

permit a scratch

the

4-bit

N,

is

left

the

the

eight

example,

4 bits

COSMAC

on

the

byte.

clock

COSMAC

in

one

use

of

this

comprising

4-bit

16

hexa-

binary

code

to

the

high-

to

select

into

the

address

to

pad

code

in

X,

to

D.

The

performed

by

the

unchanged.

a

Page 12

COSMAC Microprocessor

_____________________________

11

MEMORY

ADDRESS

(4)

R SELECT

'"":&-.....,,"""~:-i

R(9).1

R(9).0

R(

AU

R(A).O

R(E).I

R(F).I

(8)

SCRATCH

-REG

(8)

I STE

R

PAD

RS

I/O

COMMAND

8

-BIT

92CM-26420

BUS

BI-DIRECTIONAL

DATA

BUS

(8)

Fig. 2 - Internal structure

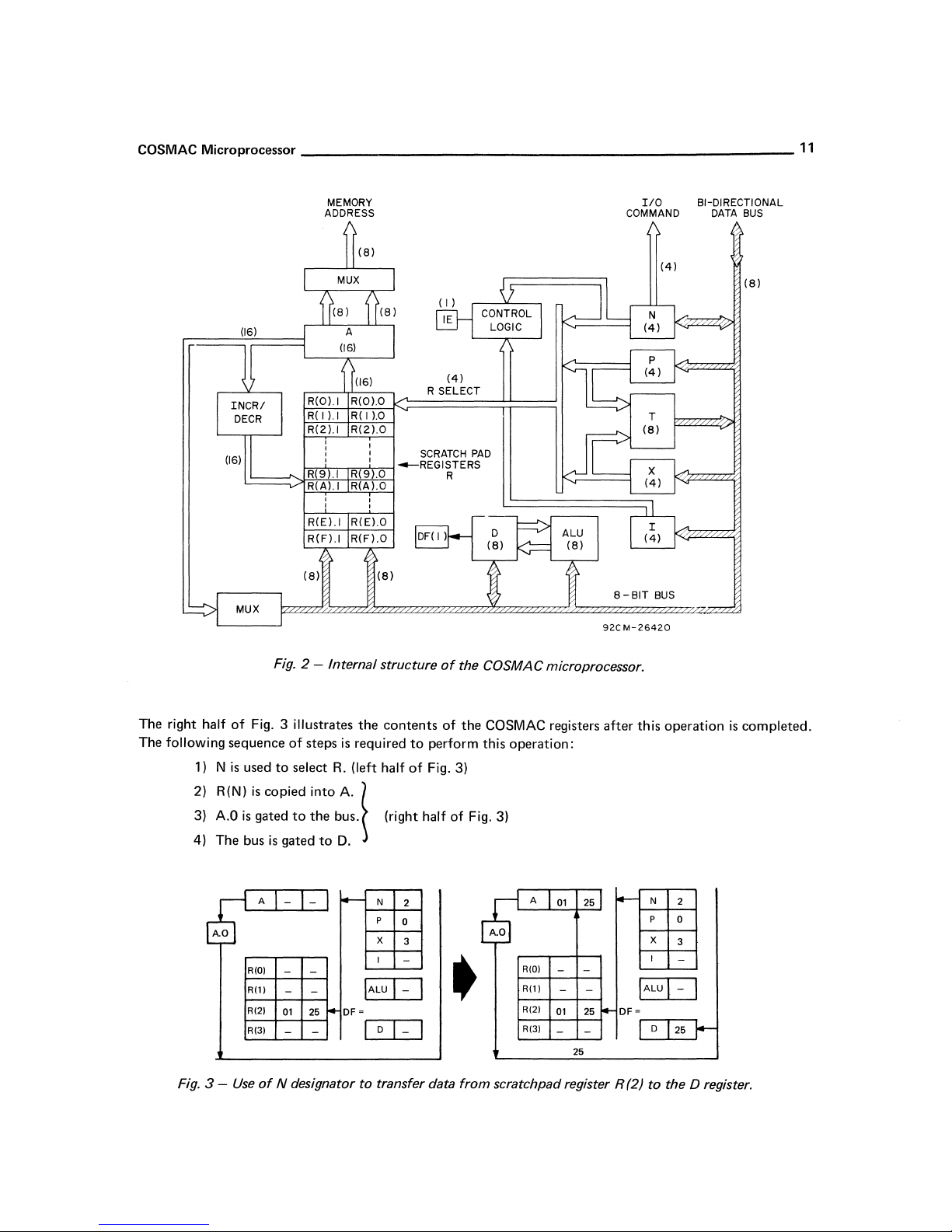

The right half

of

Fig. 3 illustrates

The following sequence

1) N is

2) R(N)

3)

4) The bus

Fig. 3 -

A.O

used

to

is

copied into A. \

is

gated

is

A

~

RIOI

Rill

RI2J

R(3)

Use

of

N designator

of

select

to

gated

- -

- -

- -

01

-

steps

the

to

~

25

-

the

is

required

R.

(left half

bus.

D.

-

DF=

to

contents

to

of

(right half

N

2

p

0

X

3

I

-

IALU

I-

I

D

I-

I

I

transfer data

of

the COSMAC microprocessor.

of

the

COSMAC registers

perform this

operation:

Fig. 3)

of

Fig. 3)

A

01

A.O

RIO)

- -

R(ll

- -

R(2)

•

from

scratchpad register R (2) to the D register.

R(31

01

- -

25

25

25

after

f---

I--

DF=

this

operation

N

p

X

I

IALU I-

D

25

is

completed.

2

0

3

-

I

I-

Page 13

12

__________________________________________________

__

User Manual

for

the

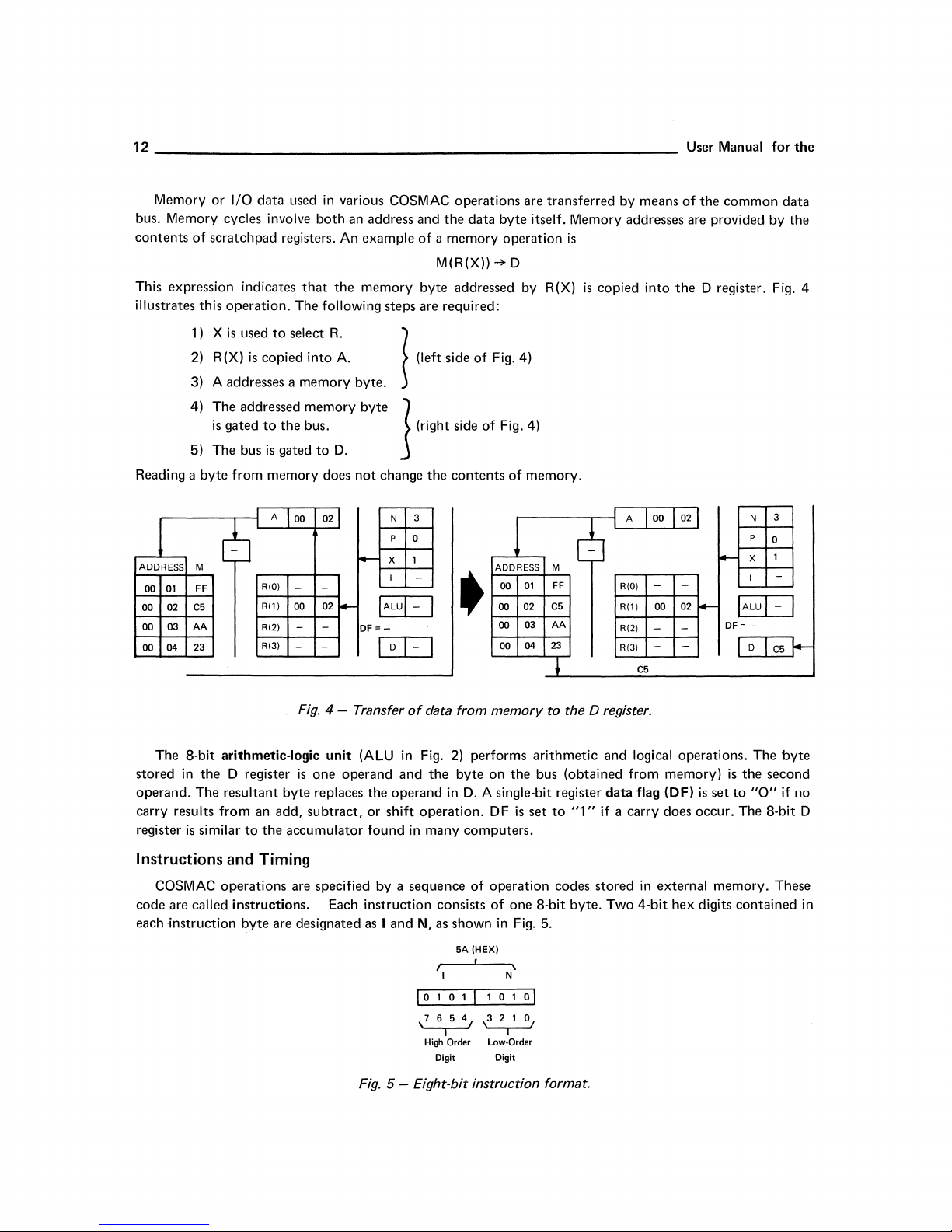

Memory or I/O data used

bus. Memory cycles involve

contents

This expression indicates

illustrates this operation. The following steps are required:

Reading a byte from memory does

ADDRESS M

00

00

00

00

of

scratchpad registers. An example

1)

X

is

used

to

2)

R(X)

is

copied into A.

3)

A addresses a memory byte.

4)

The addressed memory

is

gated

to

5)

The bus

is

A

6

01

02

03

04

FF

C5

AA

23

R(O)

R(l)

R(2)

R(3)

that

select

the

gated

00 02

-

00

-

-

in

various COSMAC operations are transferred by means

both

bus.

to

-

-

02

-

the

R.

D.

~

an address and

memory byte addressed by R(X)

byte

not

change

N

p

x 1

l-

I

IALUI-

DF=-

D

I

the

data

of

a memory operation

M(R(X))

~

(I.ft

,;d.

of

J I,;.h.

3

0

the

,;d.

of

contents

-

I

I-

I

of

the

common

byte itself. Memory addresses are provided

is

-+

D

is

F;

F;

•.

41

•.

41

of

memory.

copied into

the

D register. Fig. 4

by

data

the

Fig. 4 - Transfer

The 8-bit arithmetic-logic

stored

in

the

D register

operand. The

carry

results from an add, subtract, or shift operation. DF

register

Instructions and

COSMAC operations are specified by a sequence

code are

each instruction byte are designated

resultant byte replaces

is

similar

to

the

Timing

called instructions. Each instruction consists

unit

(ALU

is

one operand and

accumulator

Fig. 5 -

of

in

Fig. 2) performs arithmetic and logical operations. The

the

operand

found

in

as

I and N, as shown

10

,7654,

Eight-bit

data

from

memory

the

byte on

in

many computers.

5A

I \

I N

1 0 1 I 1 0 1 0 I

I

High Order Low-Order

Digit Digit

the

D.

A single-bit register

is

of

operation codes stored

of

one 8-bit byte. Two 4-bit hex digits contained in

in

Fig. 5.

(HEX)

~

----.-

instruction format.

to

the D register.

bus (obtained from memory)

data

set

to

flag (DF)

"1"

if a carry does occur. The 8-bit D

in

is

external memory. These

set

byte

is

the

second

to

"0"

if no

Page 14

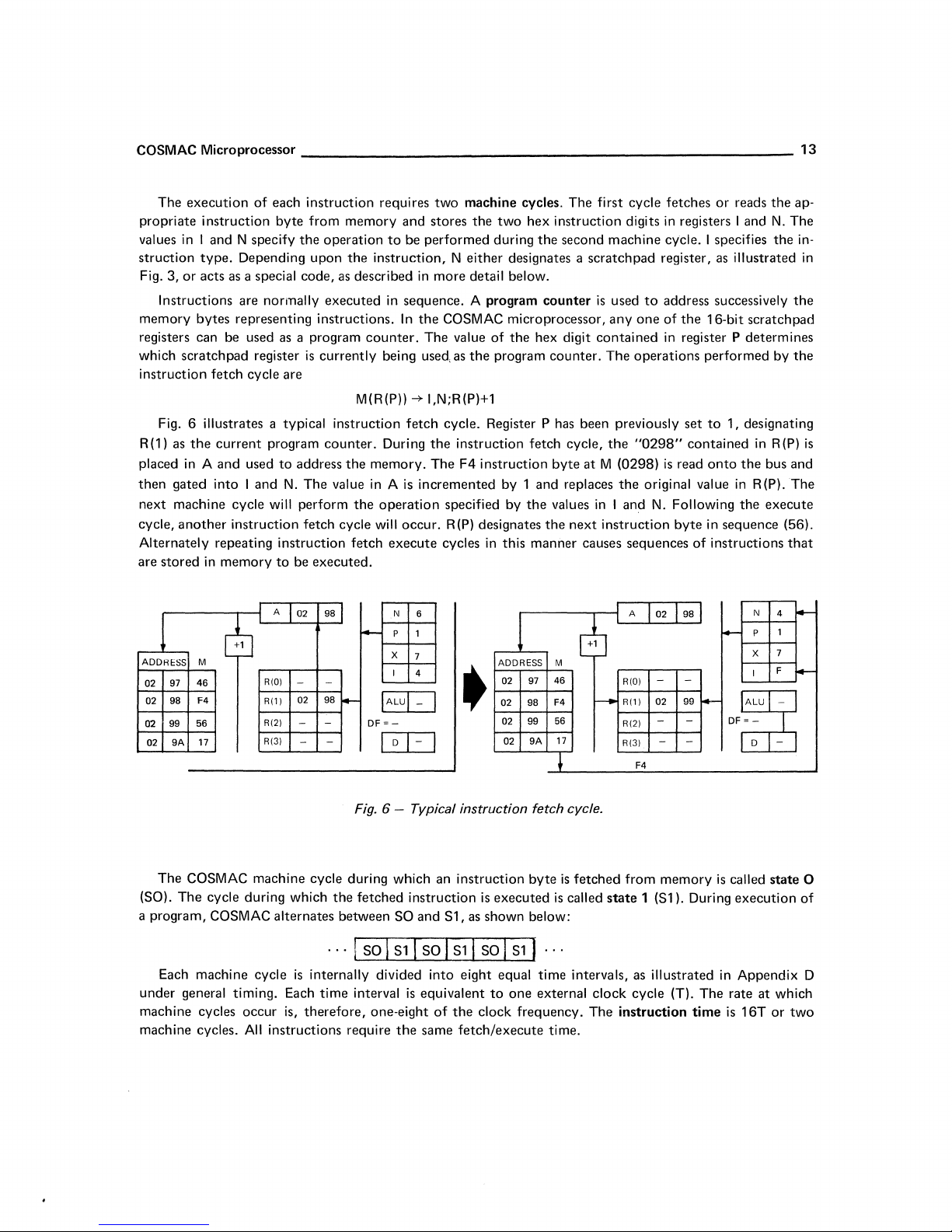

COSMAC Microprocessor

The

execution

propriate instruction

values in I and N specify

struction

Fig. 3,

memory bytes representing instructions.

registers can be used as a program

which scratch pad register

instruction fetch cycle are

R (1) as

placed

then

next machine cycle will perform

cycle,

Alternately repeating instruction fetch

are stored

type.

or

acts as a special code, as described

Instructions

Fig. 6 illustrates a typical instruction

the

in

A and used

gated into I and

another

in

of

Depending upon

are normally executed

current

instruction fetch cycle will occur.

memory

_____________________________

each instruction requires

byte

from memory and stores

the

operation

the

instruction, N

counter.

is

currently being used, as

M{R{P))

program

to

counter.

to

address

N.

The value in A

be executed.

the

memory. The F4 instruction

the

operation

two

machine cycles. The first cycle fetches

the

two

hex instruction digits

to

be performed during

either

designates a scratch pad register, as illustrated

in

more detail below.

in

sequence. A program

In

the

COSMAC microprocessor,

The value

-+ I,N;R{P)+l

fetch

cycle. Register P has been previously

During

the

is

incremented by 1 and replaces

execute

cycles

of

the

the

program

instruction fetch cycle,

specified by

R{P)

designates

the

in

this manner causes sequences

in

registers I and

the

second machine cycle. I specifies

counter

hex digit

counter.

the

byte

values

next

is

used

anyone

contained

The

the

at

M (0298)

the

in

I and

instruction

to

address successively

of

the

in

register P determines

operations performed by

set

"0298"

contained

is

read

original value

N.

Following

byte

of

13

or

reads

the

ap-

N.

The

the

in-

in

the

16-bit scratchpad

the

to

1, designating

in

R (P)

is

onto

the

bus and

in

R{P).

The

the

execute

in sequence (56).

instructions

that

A

02

98

cfu

ADDRESS

02

02

02

02

(SO).

a program, COSMAC alternates between SO and S1,

M

46

97

F4

98

99

56

17

9A

The COSMAC machine cycle during which an instruction

The

cycle during which

R(O)

R(l)

R(2)

R(3)

- -

02 98

-

-

-

-

-

the

...

Each machine cycle

under

general timing. Each

machine

machine cycles.

cycles occur is,

All

is

internally divided into eight equal time intervals, as illustrated

time

therefore,

instructions require

N

6

P 1

-

X

7

I

4

IALul-

DF=-

I

Fig. 6 - Typical instruction fetch cycle.

fetched instruction

I SO I

interval

one-eight

D I-

S1

I SO I

is

equivalent

the

I

•

I

Sl

of

the

same

fetch/execute

as

I SO I

A

02

ADDRESS

02 97

02

98

02

99

9A

02

byte

is

executed

shown below:

S1

I

to

one

clock frequency. The instruction

M

46

F4

56

17

~

is

fetched

is

called

...

external

time.

cb

R(O)

R(l)

r--

R(2)

R(3)

from

state

clock

-

02

-

- -

F4

memory

1 (S1). During execution

cycle (T). The rate

98

I

I-

-

99

-

- DF

is

in

time

N

4

p

1

--

7

X

F

I

~

=-

D -

~

called

state

0

of

Appendix D

at

which

is

16T

or

two

Page 15

14

Page 16

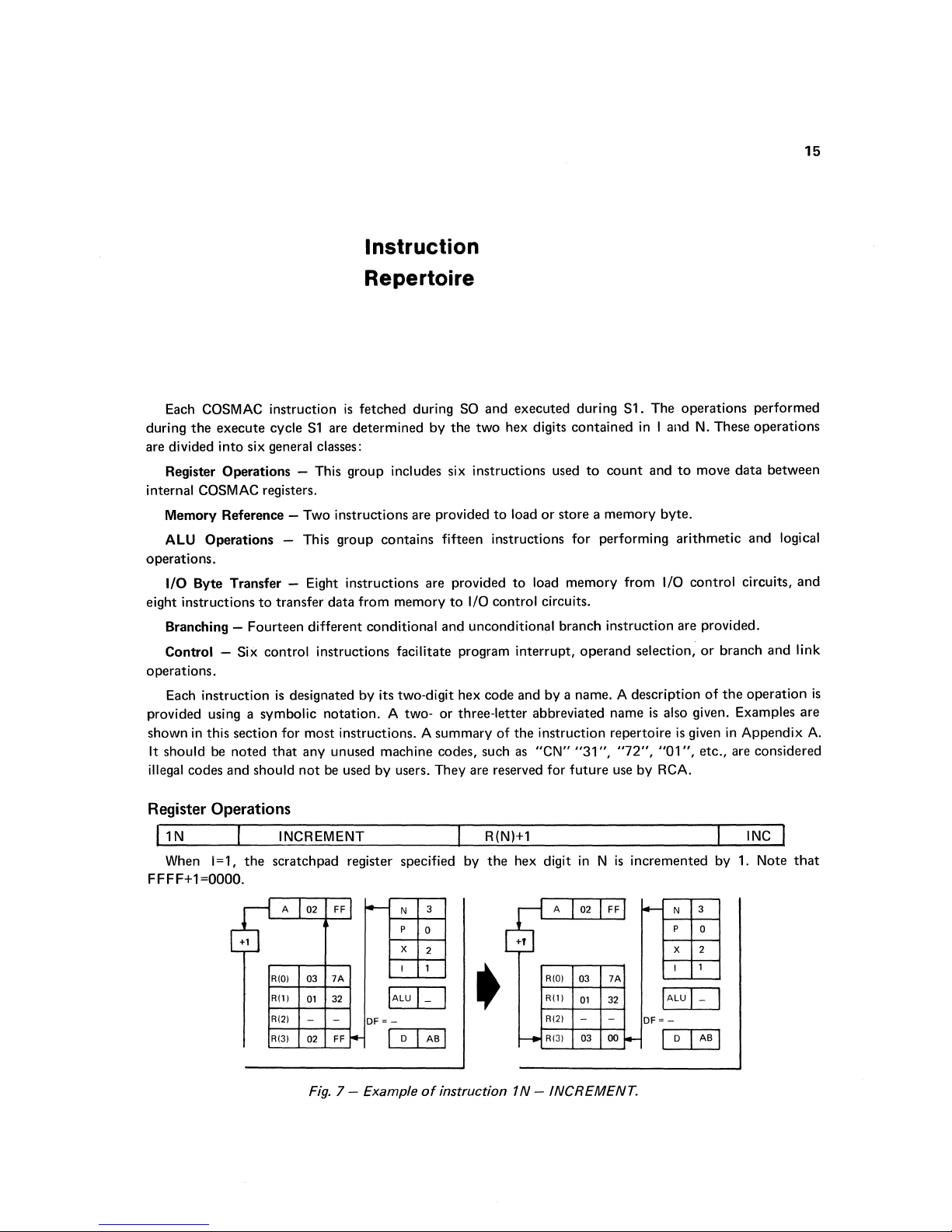

Instruction

Repertoire

15

Each COSMAC instruction

during

the

execute

are divided

Register

internal COSMAC registers.

Memory Reference - Two instructions are provided

ALU

operations.

I/O

eight instructions

Branching -

Control - Six control instructions facilitate program

operations.

Each instruction

provided using a symbolic

shown

It should be

illegal codes and should

into

Operations - This group includes six instructions used

Operations

Byte Transfer - Eight instructions are provided

in

this section for most instructions. A

cycle

six general classes:

- This

to

transfer

Fourteen

is

designated

noted

that

is

fetched during SO

S1

are

determined

group

contains

data

from

different

any unused machine codes, such as

not

conditional and unconditional branch instruction are provided.

by

its two-digit hex

notation.

be

used by users.

by

the

fifteen instructions

memory

A two- or three-letter abbreviated

to

summary

They

Register Operations

11

N INCREMENT

When 1=1,

FFFF+1=0000.

the

scratch pad register specified by

and

executed

two

hex digits

to

load

to

I/O control circuits.

interrupt,

code

and by a name. A description

of

the

are reserved for

R(N)+1

the

hex digit

during S1. The

contained

or

store a

for

load

memory

operand

instruction repertoire

"CN"

"31

future

in N is

to

count

memory

performing

from

name

",

"72",

use by RCA.

incremented

operations

in I and

and

selection,

is

N.

to

move

byte.

arithmetic

I/O

control

or

of

also given. Examples are

is

given

"01

",

etc.,

performed

These

operations

data

and logical

circuits,

branch

the

operation

in

Appendix

are considered

INC

by

1.

between

and

Note

and

link

is

A.

that

A

02

+1

03

RIOI

Rill

01

RI21

- -

RI31

02

Fig.

FF

I--

7A

32

FF

7 - Example

f4-

DF

IALU

~-

I

N

p

X

I

I-

D

I

3

0

2

1

I

AB

I

of

instruction

+f

•

r-

TN

A

02 FF

03

7A

01

32

-

-

03

00

l-

RIOI

Rill

RI21

R(31

-INCREMENT.

l-

DF

N

p

x 2

I

IALU

~-

D

I

I-

I

3

0

1

AB

I

I

Page 17

16

User Manual

for

the

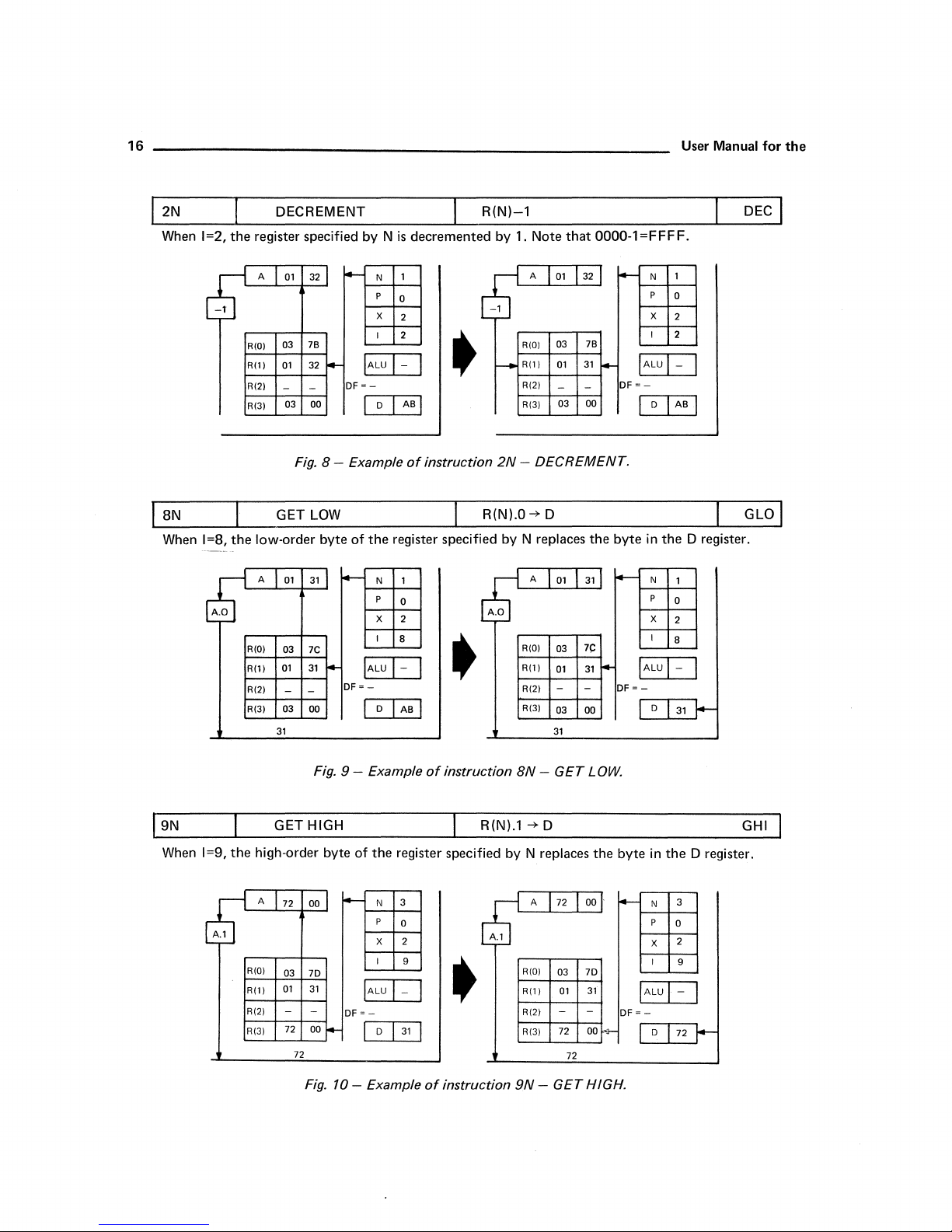

2N DECREMENT

When

1=2,

the

register specified by N

A

01

32

~

-T

03 7B

RWI

01

32

- -

03

Fig.

01

03

01

- -

03 00

00

LOW

31

7C

31

4-

DF

8 - Example

byte

of

-

..

DF=

8N

When

1=8,

A.O

Rill

RI21

RI31

GET

the

low-order

A

RIOI

Rill

RI21

RI31

31 31

R(N)-l

is

decremented by 1. Note

1

N

p

0

X

2

2 I

IALU

I-

=-

I

the

IALU

-

I

I

D

I AB I

of

instruction

register specified by N replaces

N 1

p

0

X

2

I

B

I-

I

D

I AB I

-1

-

•

2N

R(N).O-+ D

•

that

0000-1=FFFF.

A

01

32

7B

03

RWI

01

Rill

RI21

RI31

- DECREMENT.

{ A

RWI

Rill

RI21

RI31

31

- -

03 00

01

7(:

03

01

31

-

-

03 00

~

the

31

f4-

-

DF

byte

-

DF=-

IALul

=-

I

IALU

N

P

X

I

D

in

N

P

X

I

D

1

0

2

2

-

I AB I

the

D register.

1

0

2

8

I-

31

DEC

I

I

Fig. 9 - Example

GET HIGH

When

1=9,

the

high-order byte of

A

72

00

A.l

RIOI

03 7D

01

- -

72

72

31

00

Fig.

Rill

RI21

RI31

~

DF

=-

f4-

10

- Example

of

instruction

R(N).l

the

register specified by N replaces

N 3

p

X 2

I 9

IALU

D

I

I-

I

0

I

31

I

•

of

instruction

~

9N -GET

8N -GET

-+

D

72

A

RIOI

03 7D

01

Rill

-

RI21

72 00

RI31

72

LOW.

the

00 .

31

-

.;-

HIGH.

byte

-

DF=

in

N

p

IALU

-

X

I

D

the

D register.

3

0

2

9

I-

72

GHI

I

Page 18

COSMAC Microprocessor

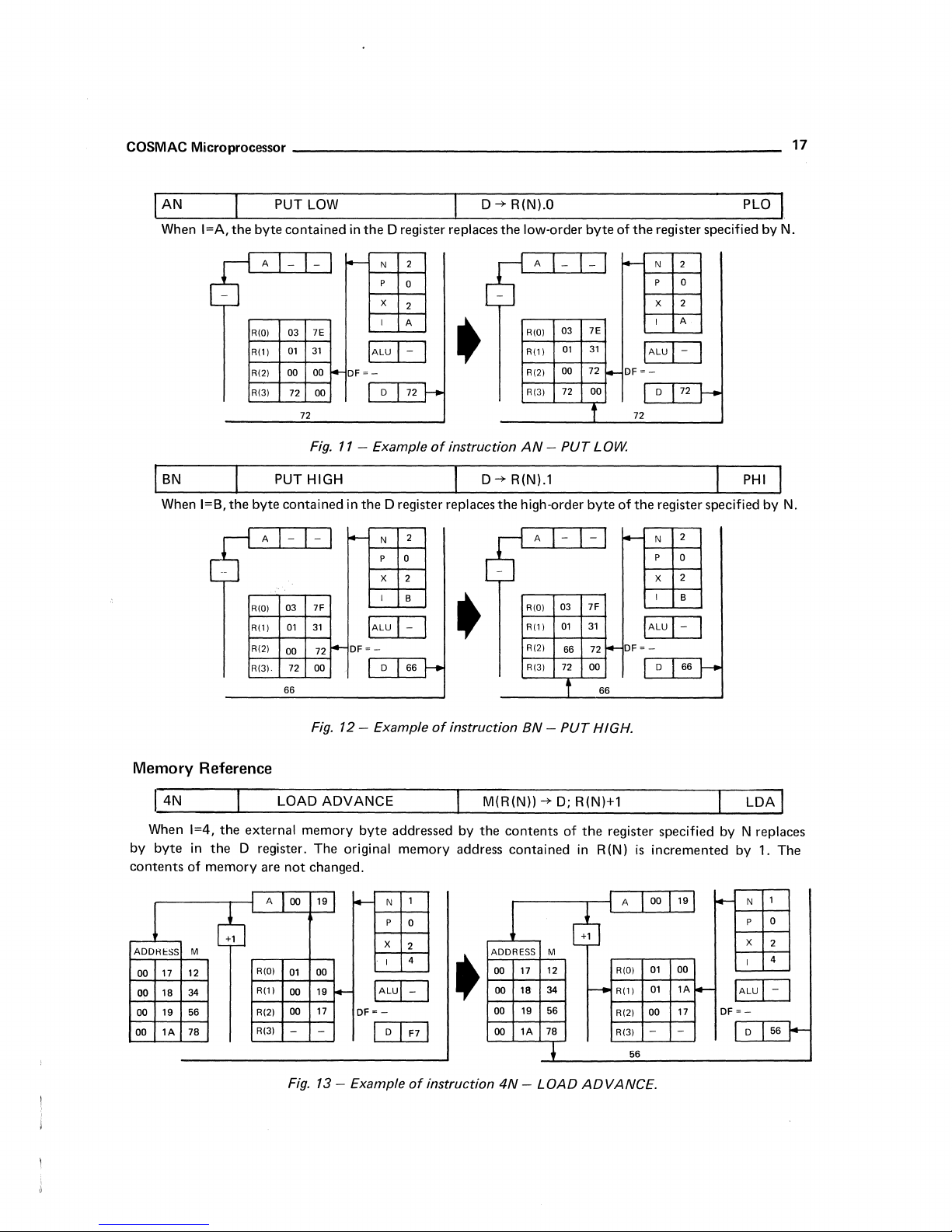

PUT LOW

When I=A,

the

byte

_____________________________

D--*

contained

in

the

D register replaces

the

R(N).O PLO

low-order

byte

of

the

register specified

by

_

17

N.

When I=B,

~

the

-1

A

RIOI

R(1)

RI21

RI31

PUT HIGH

byte

contained

A

03

RIOI

Rill

RI21

00

R131·

66

-

03 7E

01

31

00

00 I-DF

72

72

Fig.

- -

01

31

72

-

7F

00

00

72

I+-

N

t--

p

X

I

IALU

~-

D

11

- Example

in

the

D register replaces

N

l-

p

X

I

IALU

DF~

D 66

2

0

2

A

I-

I

72

•

of

instruction

D--*

the

2 A

0

2

B

I-

I

•

A

-

03 7E

RIOI

Rill

00

RI21

RI31

AN -PUT

R(N).l

high-order

- -

03

RIOI

01

Rill

RI21

R(31

-

l-

31

01

72

72

00

1

LOW.

byte

IALU

DF

~-

I-

72

of

the

l-

7F

31

66 72

72 00 D

t

66

I+-

DF

IALU

~-

N

2

p

0

2

X

A

I

I-

I

D

72J--

PHI

register specified by

2

N

p

0

2

X

I

B

I-

I

66 r-

N.

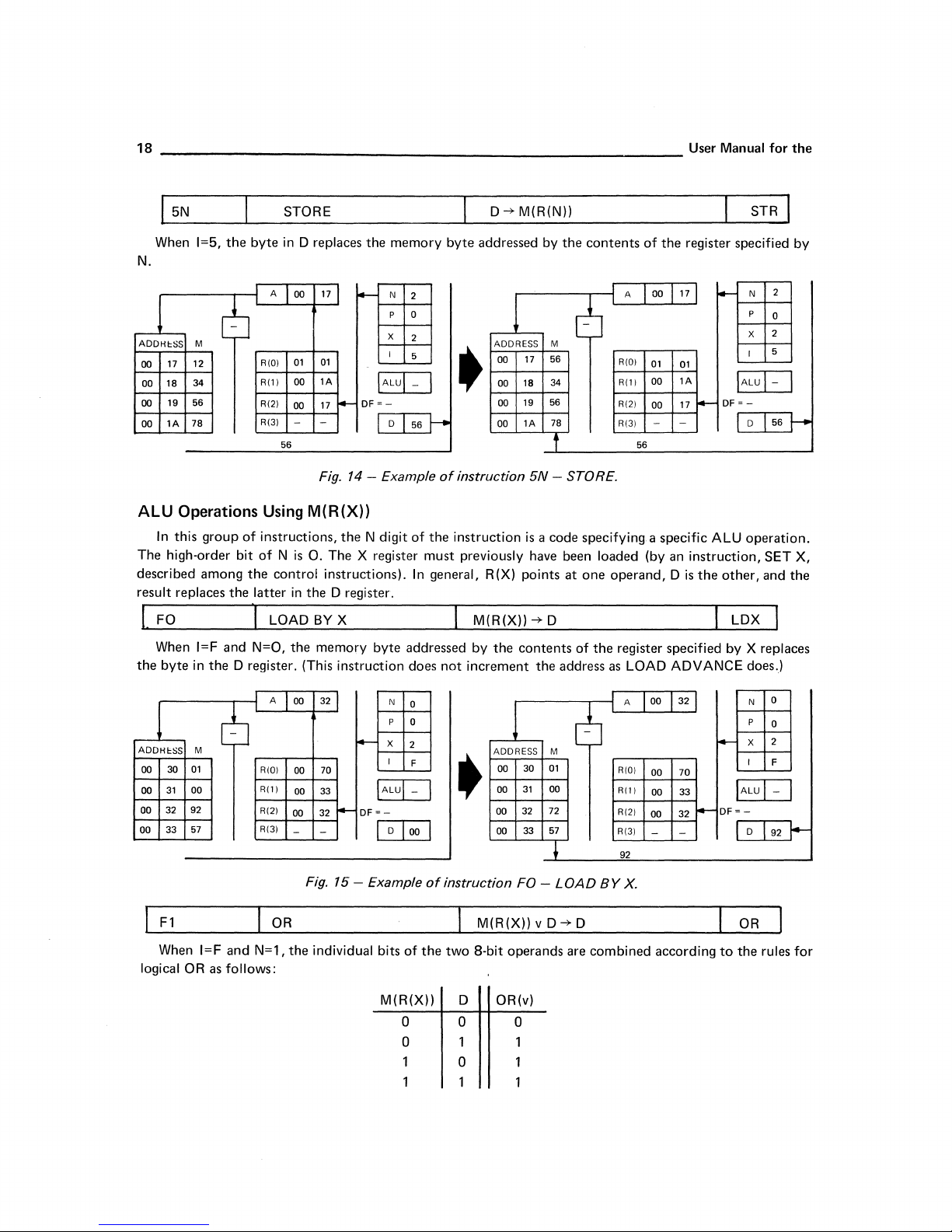

Memory

When

by

byte

contents

ADDKIoSS M

17 12

00

18

00

19 56

00

lA

00

Reference

1=4,

the

in

the

D register.

of

memory

~

34

78

LOAD

external

memory

are

not

A

00

R(oI

01

Rill

00

00

RI21

RI31

- -

Fig. 13 - Example

Fig. 12 - Example

ADVANCE

byte

addressed

The

original

memory

changed.

N

p

X

I

IALul-

~-

D I F7 I

I

1

0

2

4

of

00

19

-

19

-

17

DF

of

instruction

M(R(N))

by

the

address

I

•

instruction

BN -PUT

--*

contents

contained

ADDRESS M

17

18

1A

12

34

56

78

00

00

00 19

00

t

4N -LOAD

HIGH.

D;

R(N)+1

of

the

in

R(N)

dJ

r-

ADVANCE.

register specified by N replaces

is

A

RIOI

RI11

RI21

R(31

56

incremented

19

00

01 00

lA

01

17

00

-

-

I--

-

DF

by 1.

N

p

X

I

IALU

~-

D

The

1

0

2

4

I -I

56..1-

Page 19

________________________________________________________________

18

User Manual

for

the

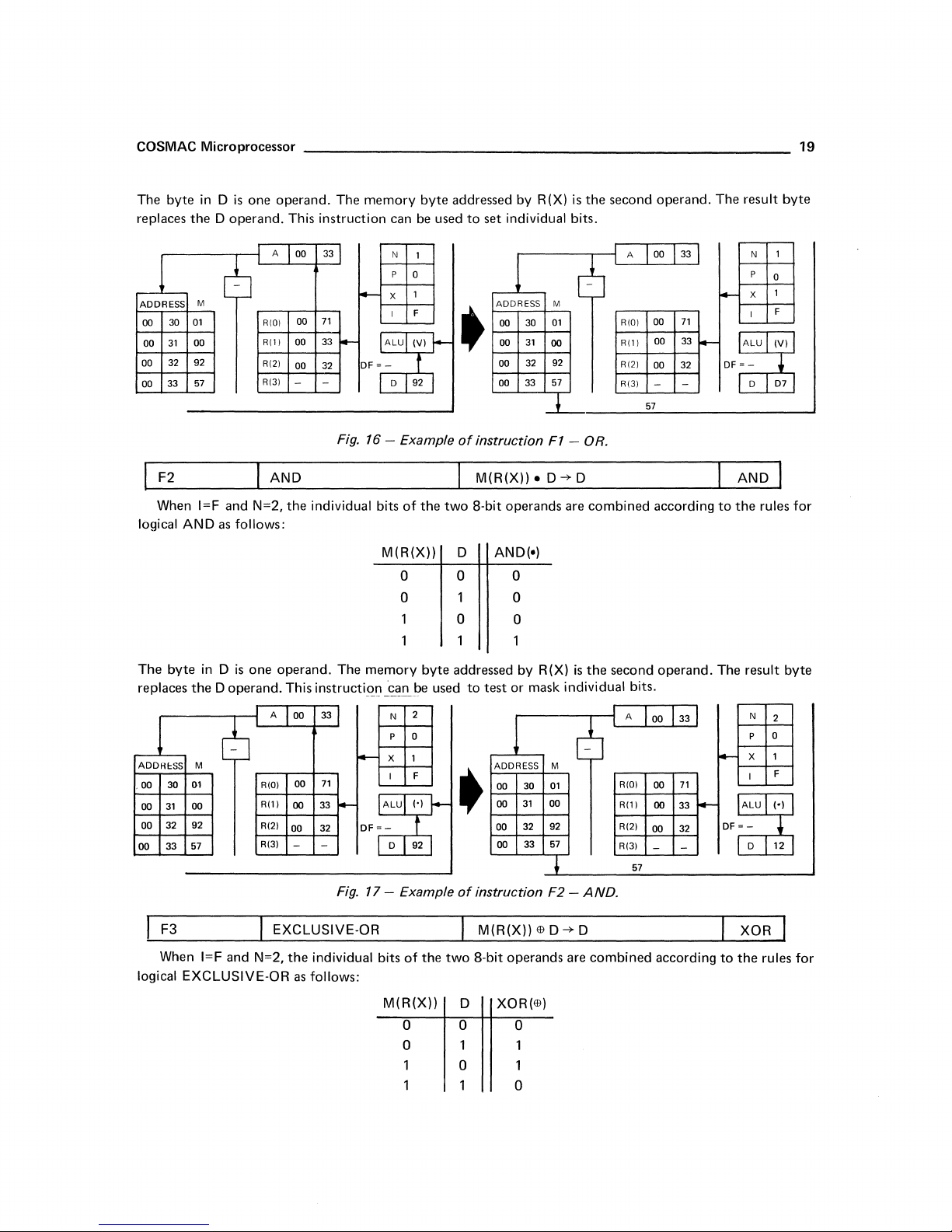

5N

When 1=5,

N.

ADDHt:SS M

17

00

00 18

00

00

ALU

The

described

result

the

12

34

56

19

78

1A

Operations Using

In

this

group

high-order bit

among

replaces

FO

When

I=F

byte

in

the

STORE

the

byte

in

A

00

cb

01 01

RIOI

00

Rill

RI21

00

RI31

-

56

of

instructions,

of N is

the

control

the

latter

in

I LOAD

and

N=O,

the

D register. (This

D replaces

171

lA

17

I-

-

f-

the

DF

X

IALUI-

=-

Fig. 14 - Example

M(R(X))

the N digit

O.

The

X register

instructions).

the

D register.

BY

X

memory

byte

instruction does

memory

N

2

p

0

2

I

5

D

56

of

must

In

addressed

byte

I

of

instruction

the

instruction

previously

general,

not

increment

D -i> M(R(N))

addressed

ADDRESS M

17

00

18

00

19

00

1A

00

is a code

R(X)

points

M(R(X))

by

the

contents

STR

by

the

contents

6

56

34

56

78

f

5N

- STORE.

specifying. a

have

been

at

one

-i> D I LDX ]

of

the

the

address

of

A 00

RIOI

01

00

Rill

RI21

00

RI31

-

56

loaded

(by an

operand, D is

register

as LOAD

the

register specified

17

l-

01

1A

DF

17

r-

-

specific

ALU

instruction,

the

other,

specified

by

ADVANCE

N

p

X

I

IALul

=-

D

operation.

and

X replaces

does.)

2

0

2

5

-

56]-

SET

by

I

X,

the

ADDHcSS

30

00

31

00

32 92

00

00 33

F1

When I=F

logical

M

01

00

57

OR

cb

and

as

follows:

A

RIOI

Rill

RI21

RI31

OR

N=1,

32

00

l-

70

00

33

00

32

00

-

-

Fig. 15 - Example

the

individual

-

IALUI

DF

=-

I

bits

M(R(X))

N

p

x

I

D 1

0

0

2

F

-

00

of

a

a

I

•

I

of

instruction

the

two

D

a

a

ADDRESS M

00 30

31

00

32

00

00

33

FO -

M(R(X)) v D

8-bit

operands

OR(v)

a

01

00

72

57

LOAD

-i>

are

BY

D

combined

A

RIOI

Rill

RI21

RI31

92

X.

32

00

70

00

33

00

I-

32

00

-

-

according

l-

DF=

to

N

x

I

IALU

D

OR

the

P

0

0

2

F

I-

92

rules

I

for

Page 20

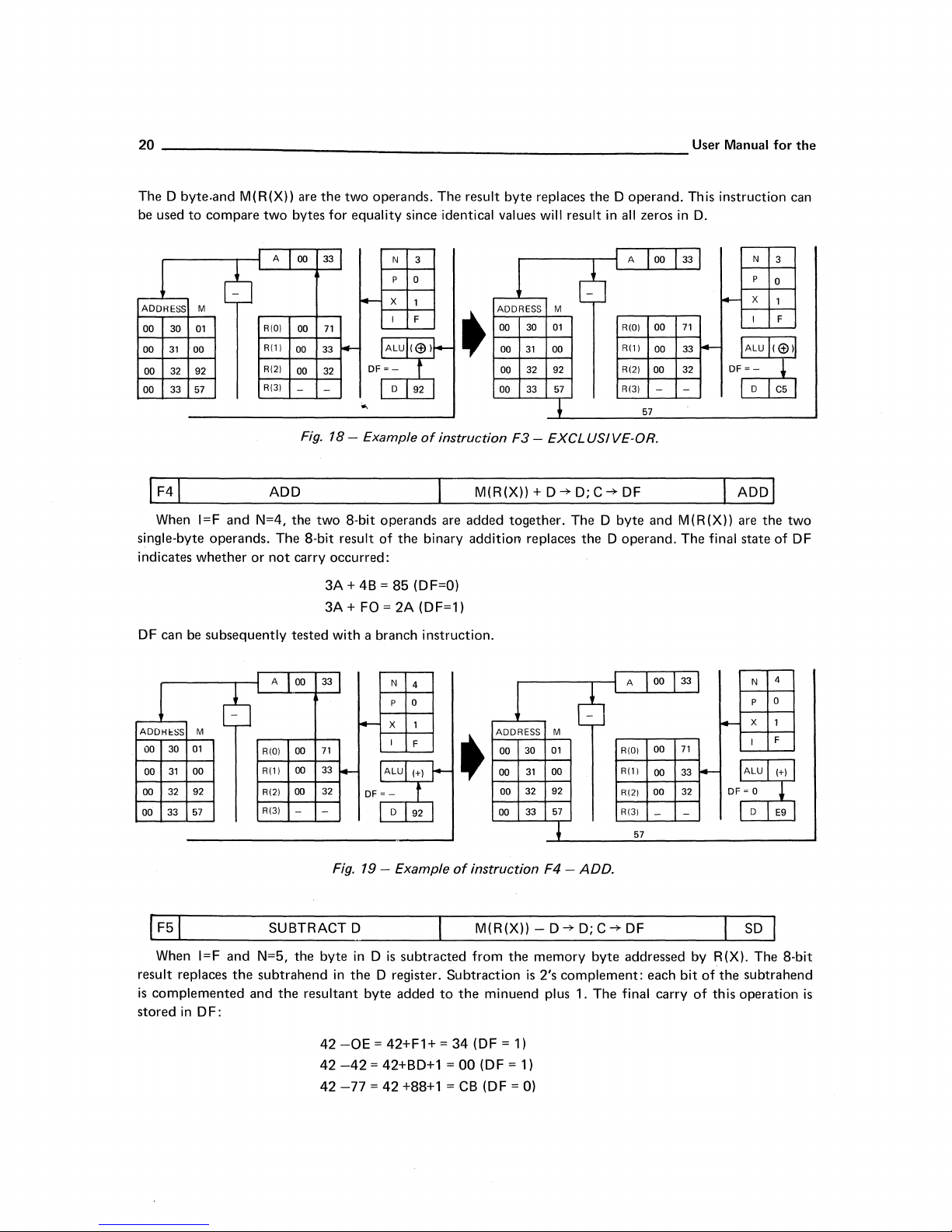

COSMAC Microprocessor

The

byte

in D

is

one operand. The

replaces the D operand. This

memory

instruction

can

byte

be

addressed

used

to

by

R(X)

is

the second operand. The result

set individual bits.

19

byte

A

00

6

30

31

32 92

33

F2

When

byte

30

31

32

33

M

01

00

57

I=F

and N=2, the individual bits

AND

as

follows:

in D

is

one operand. The

cb

M

01

00

92

57

RiOl

Rill

RI21

RI31

AND

A

RIO)

Rill

R(2)

R(3)

00

00

00 32

-

00

00

00

00

-

ADDRESS

00

00

oo

00

logical

The

replaces the D operand. This

ADDH~SS

00

00

00

00

33

71

33

-

-

Fig. 16 - Example

f-

OF

=-

N

1

p

0

1

X

F

I

ALU

(V)

t

92

D

of

the

M(R(X))

r-

o 0 o

o 0

memory

instructi~n

33

f-

71

33

I-

OF=-

32

-

Fig.

17

byte

_~a~be

N

P 0

used

2

x 1

I F

I·)

ALU

f

92

D

- Example

•

of

instruction

M(R(X)).

two

8-bit

D

o 0

addressed

to

test

•

of

instruction

ADDRESS M

00

01

30

00

31

00

00

00

AND(·)

ADDRESS M

00

00

00

00

00

92

32

57

33

F1

- OR.

D

-?-

operands are combined according

by

R(X)

or

mask

individual

01

30

00

31

92

32

57

33

+

F2 -AND.

RIOI

Rll)

R(2)

R(3)

D

is

the

second operand. The result

bits.

A

cb

RIOI

Rll)

R(2)

R13)

57

71

33

00

32

00

57

33

00

71

00

00

33

32

00

-

-

N

AND

to

the

rules

N

p

X

~

I

I-

OF

=-

D 12

~

0

for

byte

2

0

1

F

F3

When

I=F

logical

EXCLUSIVE-OR

EXCLUSIVE-OR

and N=2,

the

individual bits

as

follows:

of

the

M(R(X))

o 0

o 1

two

I

M(R(X))

8-bit

D

o

Ell

D

operands are

XOR(Ell)

o

o

-?-

D

combined

according

to

XOR

the

rules

for

Page 21

20

_______________________________

User Manual for

the

The 0 byte.and M(R(X)) are

be used

ADDRESS

00

00

00

00

30

31

32

33

to

compare

M

01

00

92

57

two

A

cb

R(O)

Rill

R(2)

R(31

the

two

bytes for equality since identical values will result in

33

00

-

00

71

33

00

-

00

32

-

-

'"

Fig.

18 - Example

ADD

When I=F

single-byte operands. The 8-bit result

indicates

OF can be

and

whether

N=4, the

or

two

not

carry occurred:

8-bit operands are added together. The 0

3A + 4B =

3A+

FO = 2A (OF=1)

subsequently tested with a branch instruction.

operands. The result byte replaces

N 3

p

0

X

DF

1

I

F

ALU

(@)/--

=-

t

•

92

of

instruction

binary addition replaces

(OF=O)

of

D

the

85

ADDRESS

00

00

00

00

M(R(X))+O~O;C~OF

M

30

01

31

00

32

92

33 57

F3

- EXCLUSIVE-OR.

the

0 operand. This instruction can

all

zeros

in

O.

R(O)

00

71

R(lI

R(21

R(3)

57

00

00

33

32

I Aool

byte

and

M(R(X)) are

the

0 operand. The final state of OF

N

the

3

0

two

cb

ADDHI:SS

00

00

00

00

result replaces

is

stored

M

01

30

31

00

32

92

33

57

When I=F

and

the

complemented and

in

OF:

A

RIOI

Rill

R(21

R(3)

33

00

71

00

33

00

32

00

-

-

Fig. 19 - Example

SUBTRACT 0

N=5,

the

byte

subtrahend

the

in

resultant byte added

42

42

42

-

ALU

-

DF

=-

in 0 is

the

0 register.

-OE

= 42+F1+ =

-42

= 42+BO+1 =

-77 = 42

N

4

p

0

X

1

I

F

(+1

/--

t

D

92

subtracted

+88+1 =

ADDRESS M

01

30

00

31

00

00

•

00

of

instruction F4 -

M(R(X))-O~O;C~OF

from

Subtraction

to

the

minuend plus 1.

34

(OF = 1)

00

(OF = 1)

CB

(OF = 0)

00

92

32

57

33

the

memory byte addressed by R(X). The 8-bit

is

2's complement: each

ADD.

The

00

RIOI

R(lI

00

00

RI21

RI31

-

57

final carry

71

33

32

bit

of

the

of

this operation

4

N

0

P

SO

subtrahend

is

Page 22

COSMAC Microprocessor

21

A final value

in D

is

ADDAcSS

00

30

31

00

00 32

00

33

When I=F and N=7,

byte replaces the minuend in D. This operation

ADDHcSS

30

00

31

00

00

32

33

00

exactly

M

01

00

92

57

M

01

00

92

57

of

"0"

in DF indicates

100

(hexadecimal) greater than the

A

00

33 N

6

6

RIO)

00

RI1

)

00 33

R(2)

00 32

R(3)

- -

Fig.

SUBTRACT

the

A

00

RIO)

00

R(1)

00

00

R(2)

R(3)

-

-

71

I-

OF

20

- Example

M

memory

33 N 7

-

71

~

33

32

-

that

the subtrahend

5

p

0

X

1

I F

ALU

1-)

=-

t

0

92

of

byte addressed

p

a

x

1

I

F

ALU

OF

HI-

=-

t

0

92

was

larger than the minuend.

true

(negative) difference.

ADDRESS M

00

30

00

31

00

•

instruction

D·M(R(X)) ~ D; C ~ DF

by

is

identical

•

32 92

00

33

F5 -SUBTRACT

R(X)

is

to

F5

ADDRESS M

30

00

31

00

00

32

00

33

A

c6

01

00

57

1

subtracted

with

01

00

92

57

RIO)

R(1

)

R(2)

R(3)

D.

from

the operands reversed.

R(O)

R(1

R(2)

R(3)

)

57

57

00

00

00

00

-

the

00

00

00

In

this

case

33

l-

71

33

I-

OF

32

-

byte

in D. The result

71

33

32

ALU

= a

SM

the

N

p

x

I

0

N

p a

value

5

a

1

F

1-)

~

C5

Fig. 21 - Example

SHIFT

When I=F and N=6, the 8 bits in D are shifted right one

D

bit

is

placed in DF. The final value

instructions in this group,

operand or

to

divide

by

M(R(X))

2.

RIGHT

of

is

not

1

RIO)

-

-

R(1)

-

-

R(2)

R(3)

-

-

Fig.

DF~

-

-

22

- Example

Cirili

the

high·order D

used. This

6

P a

x 1

I F

of

instruction F7 -

ISHI

of

instruction

SUBTRACT

FT D RIGHT 1 BIT;

bit

position. The original value

bit

is

always

instruction

•

can

R(O)

- -

R(1)

- -

R(2)

- -

R(3)

- -

F6 -SHIFT

LSB

"0".

be

~

In

this

used

to

RIGHT.

M.

DF;

0

~

MSB I SHR

of

the

instruction,

test successive bits

P a

6

x 1

I F

m

LU-

OF

= 1

~

o

79

low·order

unlike

other

of

the

Page 23

22

ALU

Operations Using M(R(P))

In

this

group

of

ALU

bits

of N are a code

In

general,

immediate

The

use

pointers

to

byte.

of

them.

specifying

R (P)

points

The

D register supplies

immediate

instructions,

the

same

to

one

of

data

is

a useful

the

N digit has a 1

ALU

the

operands,

the

second

way

operation

the

operand,

to

avoid

in

the

as

instructions

byte

in

memory

and

setting

high-order

using

after

then

receives

up

special

bit

position.

M(

the

the

constant

User Manual

The

R (X) l.

except

instruction

result.

areas

remaining

when

N=6.

byte,

called

in

memory

for

three

the

the

and

When I=F

byte

in

execution

next.

This

and

R(N)

ADDK~SS

27

03

03 28

03 29

2A

03

and

N=8,

D.

Because

ofthis

instruction

the

instruction,

is

LDX uses R(X).

6

M

F8

92

F9

57

RIO)

R(1)

R(2)

R(3)

OR

LOAD IMMEDIATE

the

one

A

memory

current

of

three

LDI

03 28

the

byte

program

instruction

which

and

LDA

i+-

03

28

I-

71

00

33

00

-

-

Fig.

23

- Example

IMMEDIATE

OF

IALUI-

=-

I

immediately

counter

byte

load D

each

increment

8

N

p

0

X

2

I

F

I

o

121

1

of

instruction

M(R(P)) -+

following

represented

following

from

memory.

the

ADDRESS M

03

03

03

•

03

F8 -LOAD

M(R(P)) v D -+

D;

R(P)+1

the

current

by

R(P)

is

incremented

the

immediate

byte

It uses R(P) as a

pointer

after

use,

cb

27 F8

28 92

29 F9 R(2)

2A

57

+

IMMEDIA

D;

--

R(P)+1

instruction

again

placed in D will be

pointer,

but

LDX

does

A

03 28

RIO)

R(1)

R(3)

92

03

00

00

-

TE.

29

I-

71

33

-

I

LDI

byte

replaces

by 1 during

while

LDA

not.

N

p

-

X

I

IALUI,-

OF

=-

0

ORI

I

the

the

fetched

uses

8

0

2

F

1

92 I--

When I=F

the

memory

ADDKbS

03

27

03 28

03 29

03

2A

M

F8

92

F9

57

and

N=9, a logical

byte

immediately

6

A

RIO)

Rill

R(2)

R(3)

03

03

00

00 33

- -

Fig.

OR

following

2A

i+-

2A

-

71

24

- Example

operation

the

N

p

X

I

ALU

OF

=-

0

is

F9

instruction

9

0

2

F

(V)

t

92

of

instruction

performed

ADDRESS M

03

03

03 29

•

03

is

F9

similar

the

second

27 F8

28

92

F9

2A

57

~

- OR

to

F1.

The D byte

operand.

cb

RIO)

--

R(1)

R(2)

R(3)

IMMEDIA

A

57

TE.

The

03

03

00

00

-

is

one

operand,

result goes

2A

I-

28

I--

71

OF

33

-

X

ALU

=-

0

to

N

p

I

D.

9

0

2

F

(V)

+

07

and

Page 24

COSMAC Microprocessor

AND

IMMEDIATE

I M(R(P)) . D -+

D;

R(P)+l

23

ANI

When I=F and

the

memory

ADDRESS M

2B

2C

20

2E

When

FA

OF

FB

Fa

I=F

03

03

03

03

operand, and

instruction

ADDRESS M

2B

20

2E

2C

FA

OF

FB

Fa

03

03

03

03

N=A,

byte

immediately

dJ

and N=B,

the

can

be

used

dJ

Fig.

a logical

AND

following

03

03 2C

00

00

-

Fig.

2C

t-

71

33

-

25

- Example

A

R(QI

R(ll

R(21

R(31

EXCLUSIVE-OR

an

EXCLUSIVE-OR

memory

A

R(OI

Rill

R(21

R(31

26

byte

to

complement

2E

03

'

2E

03

f-

71

00

33 DF

00

-

-

- Example

operation

the

FA

N

A

p

=-

X

I

ALU

0

0

2

F

('1

r

07

I+-

OF

of

IMMEDIATE

immediately

the

D register when

N

B

p

I-

of

0

X

2

I

F

«!)

ALU

=-

t

0 07

instruction

is

performed similar

instruction

ADDRESS M

03 2B

03

03

•

03 2E

instruction

FA -

I M(R(P))

operation similar

following

I

FB -

the FB

the

ADDRESS M

03

03

03

•

03

EXCLUSIVE-OR

to

F2. The D

is

the second operand.

cb

FA

r---

2C

OF

FB

20

Fa

~

AND

IMMEDIA

EB

D -+ D;

immediate

R(P)+l

to

F3

is

instruction

byte

performed. The D

c6

FA

2B

2C

20

2E

t-

OF

FB

Fa

l

IMMEDIA

R(OI

R(ll

R(21

R(31

A

R(OI

R(ll

R(21

R(31

byte

is

one operand, and

A

03

2C

20

03

-

71

00

33

00

-

-

OF

TE.

is

the

second operand. This

is

"F

F".

2E

03

2F

03

~

71

00

33

00

-

-

FO

TE.

N

A

p

~

OF

0

X 2

I F

=-

o 07

~

XRI

byte

is

one

N

B

p

ALU

=-

0

X

I F

«!)

0

2

F7

)

+

I-

OF

ADD

IMMEDIATE

When I=F and N=C,

byte

immediately

dJ

2F

30 80

FD

31

92

32

M

FC

ADDReSS

03

03

03

03

the

following

A

03

RIOI

03

Rill

RI21

R(31

two

the

00

00

-

Fig. 27 - Example

operands

FC

30

f-

30

71

33

-

are

instruction

C

N

p

X

I

ALU

=-

D

of

0

2

F

(+)

F7

instruction

r-

DF

added

is

t

I

M(R(P))+D

as

the

other

•

-+

in F4. The D

operand.

ADDRESS M

FC

2F

03

30 80

03

31

03

03 32

FD

92

~

FC -

ADD

D;

C -+

DF;

byte

is

c6

r---

IMMEDIA

R(P)+l

one operand, and

80

00

00

03

03

-

30

71

33

-

31

-

A

R(OI

R(ll

R(21

R(31

TE.

the

~

OF

ADI

N

p

X

I

ALU

=-

0

memory

C

0

2

F

(+)]

1

77

Page 25

________________________________________________________________

24

User Manual

for

the

When I=F

memory

ADDH~SS

03

2F

03

30

03

31

32

03

When I=F

the

memory

equivalent

ADDRESS

33

03

34

03

35

03

36

33

and

byte

immediately

c6

M

FC

80

FD

92

and

byte

to

FD

cb

M

FF

lA

62

6A

SUBTRACT

N=D,

the

following

A

03

RIOI

03

Rll)

00

R(2)

00

R(3)

- - D 77

Fig.

28

- Example

SUBTRACT

N=F,

the

immediately

with

the

operands

03 34

A

RIO)

03

R(l)

00

R(2)

00

R(3)

-

Fig.

29

- Example

D IMMEDIATE I M(R(P))-D

two

32

71

33

32

l-

operands

f--

the

FD

N D

p

X

I

ALU

~-

DF

of

instruction

are

subtracted

instruction

0

2

F

HI-

f

•

M IMMEDIATE I D-M(R(P))

two

operands

following

are

the

subtracted

FF

instruction

reversed.)

F

N

p

0

X 2

I F

ALU

H

~-

f

lB

D

of

instruction

•

34

71

33

-

4-

OF

-

-+

D; C

-+

DF;

R(P)+1

as

in

F5.

is

the

minuend.

ADDRESS M

03

2F

03

30

03

31

03

32

FD

- SUBTRACT D

as

in

F7.

represents

ADDRESS

03

33

34

03

35

03

03

36

The D byte

c6

FC

80

FD·

92

+

-+

D; C

-+

The D byte

the

cb

M

FF

lA

62

6A

t

f--

f--

is

A

03

RIOI

03

RllI

00

R(2)

00

R(3) -

92

IMMEDIA

DF;

R(P)+1

represents

subtrahend.

A

03

RIO)

03

R(l)

00

00

R(2)

-

R(3)

lA

the

TE.

FF -SUBTRACT M IMMEDIATE.

I SDI I

subtrahend,

32

1

I-

33

-

71

DF

33

-

I SMI I

the

minuend,

(This

instruction

34

I-

35

-

71

DF ~ 1

33

-

ALU

~

ALU

1

D

D

and

N 0

p 0

X

I

N

p

X

I

2

F

H

+

lB

F

0

2

F

H

1

01

the

and

is

Input/Output

Byte Transfer

N=O-7

When 1

four

ADDRESS M

00

00

00

00

bits

31

32 34

33

34

=6