Page 1

Features

• Single Package Fully-integrated ROM Mask 4-bit Microcontroller with RF Transmitter

• Low Power Consumption in Sleep Mode (< 1 µA Typically)

• Maximum Output Power (10 dBm) with Low Supply Current (9.5 mA Typically)

• 2.0 V to 4.0 V Operation Voltage for Single Li-cell Power Supply

• -40°C to +125°C Operation Temperature

• SSO24 Package

• About Seven External Components

• Flash Controller for Application Program Available

Microcontroller

with UHF

Description

The ATAR862-8 is a single p ackage triple -chip circuit. It combines a UHF AS K/FSK

transmitter with a 4-bit microcontrol le r and a 512 -b it EEP ROM. It supp orts highly integrated solutions in car access and tire pressure monitoring applications, as well as

manifold applicatio ns in the indus tri al and c onsumer segme nt. It i s available for the

frequency range of 429 MHz to 439 MHz with data rates up to 32 kbaud.

For further frequenc y ranges s uch a s 3 10 MHz to 330 MHz and 868 MHz to 928 MHz

separate data sheets are available.

The device contains a ROM mask version microcontroller and an additional data

EEPROM.

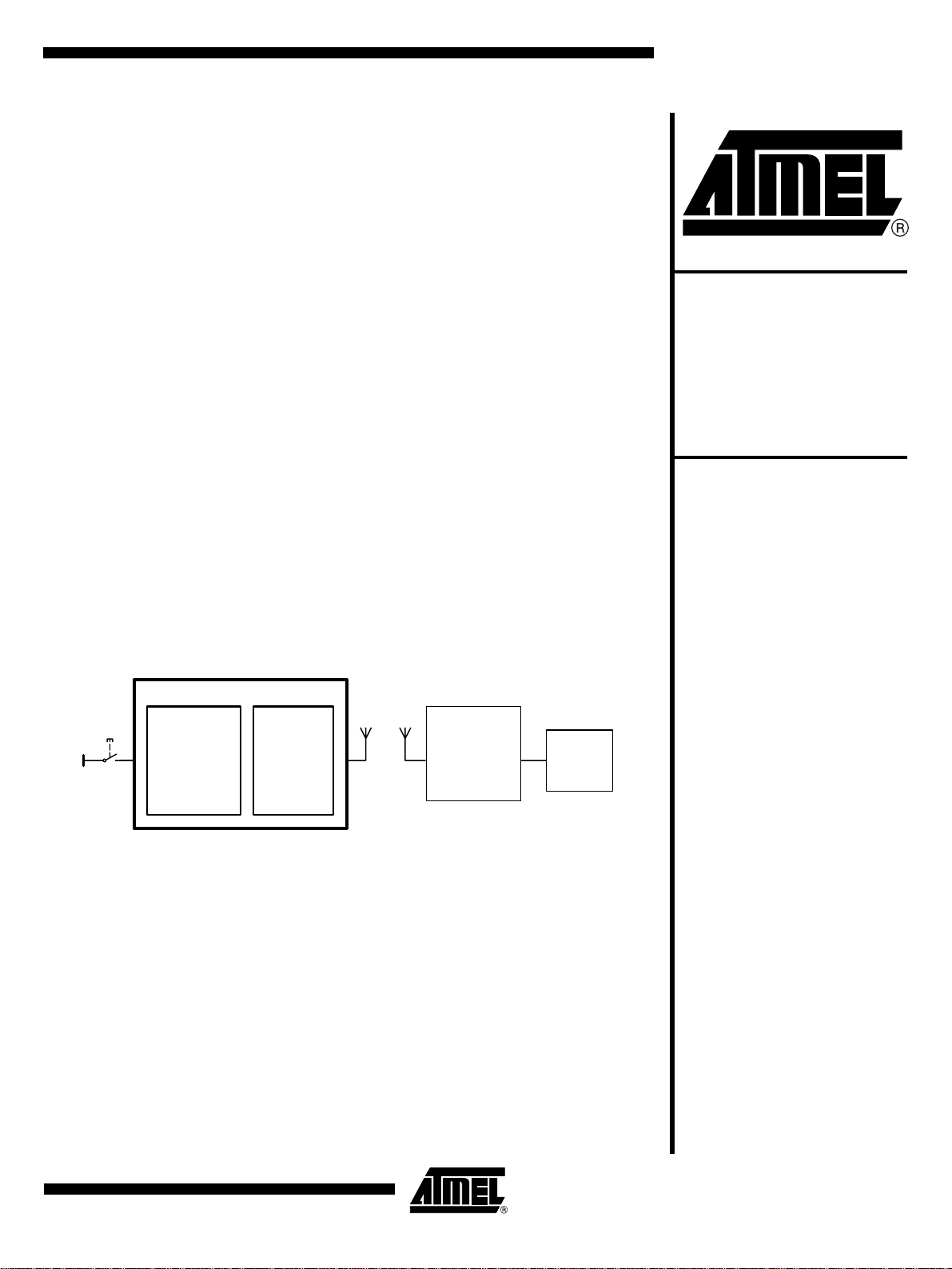

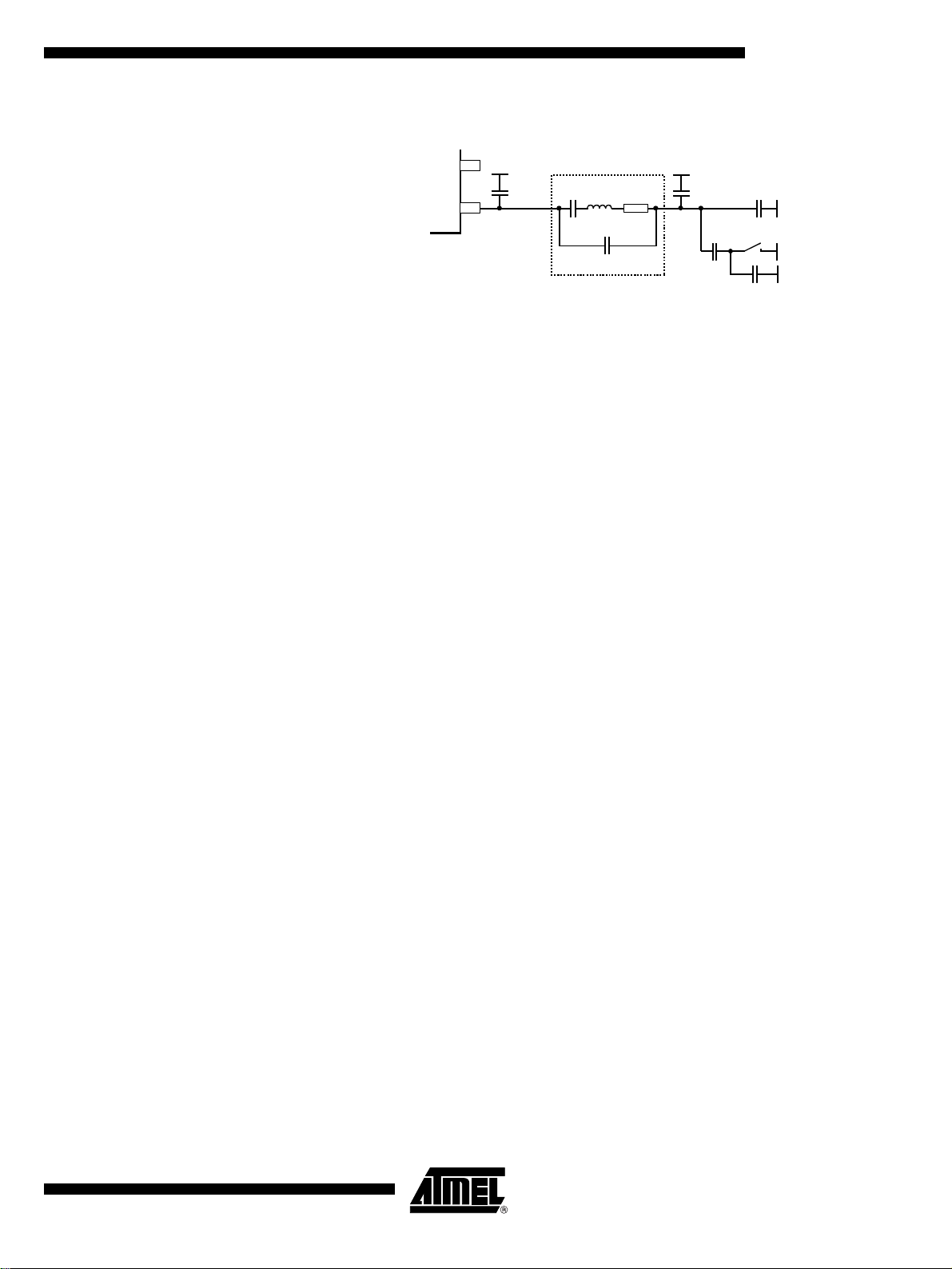

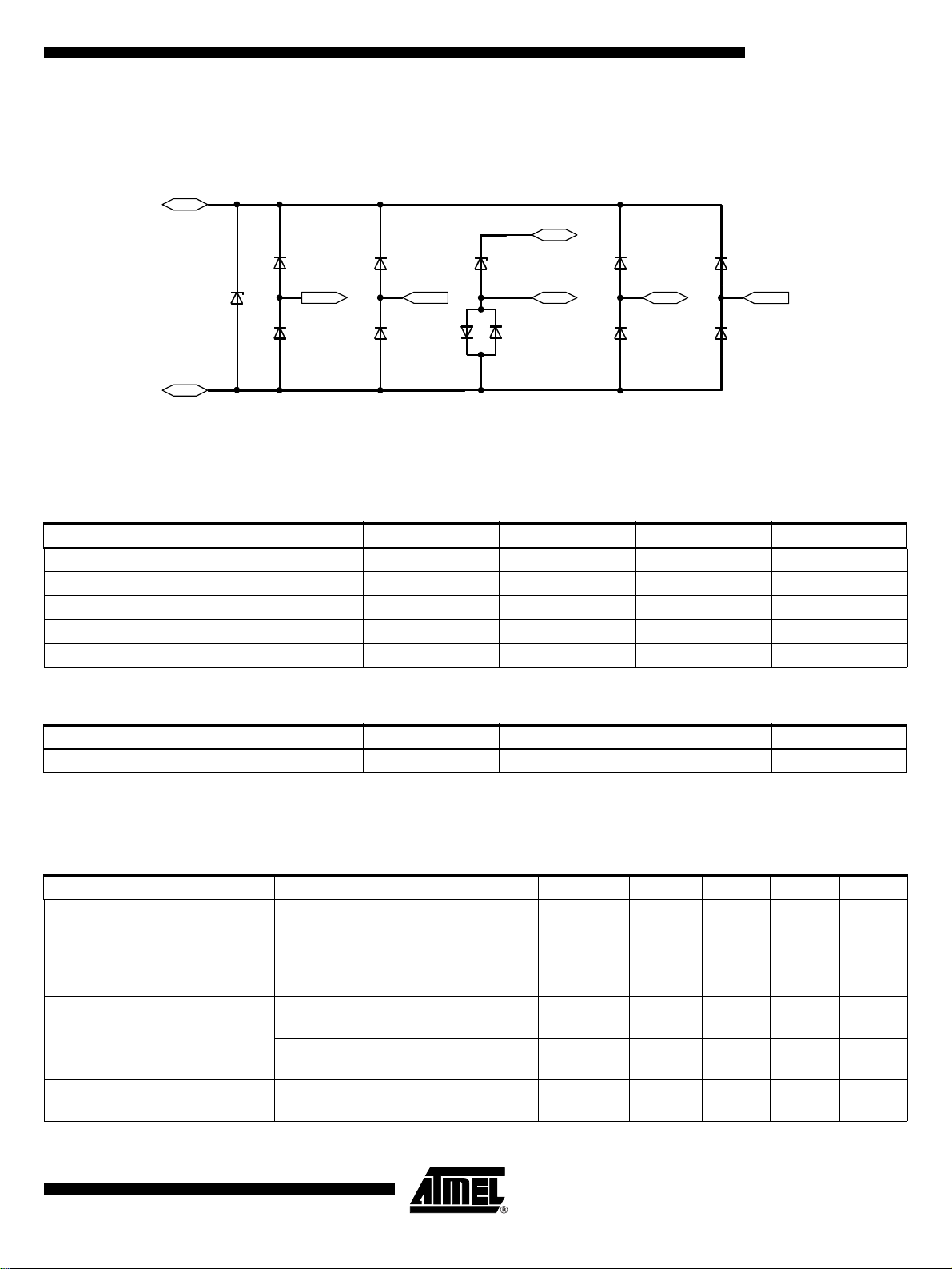

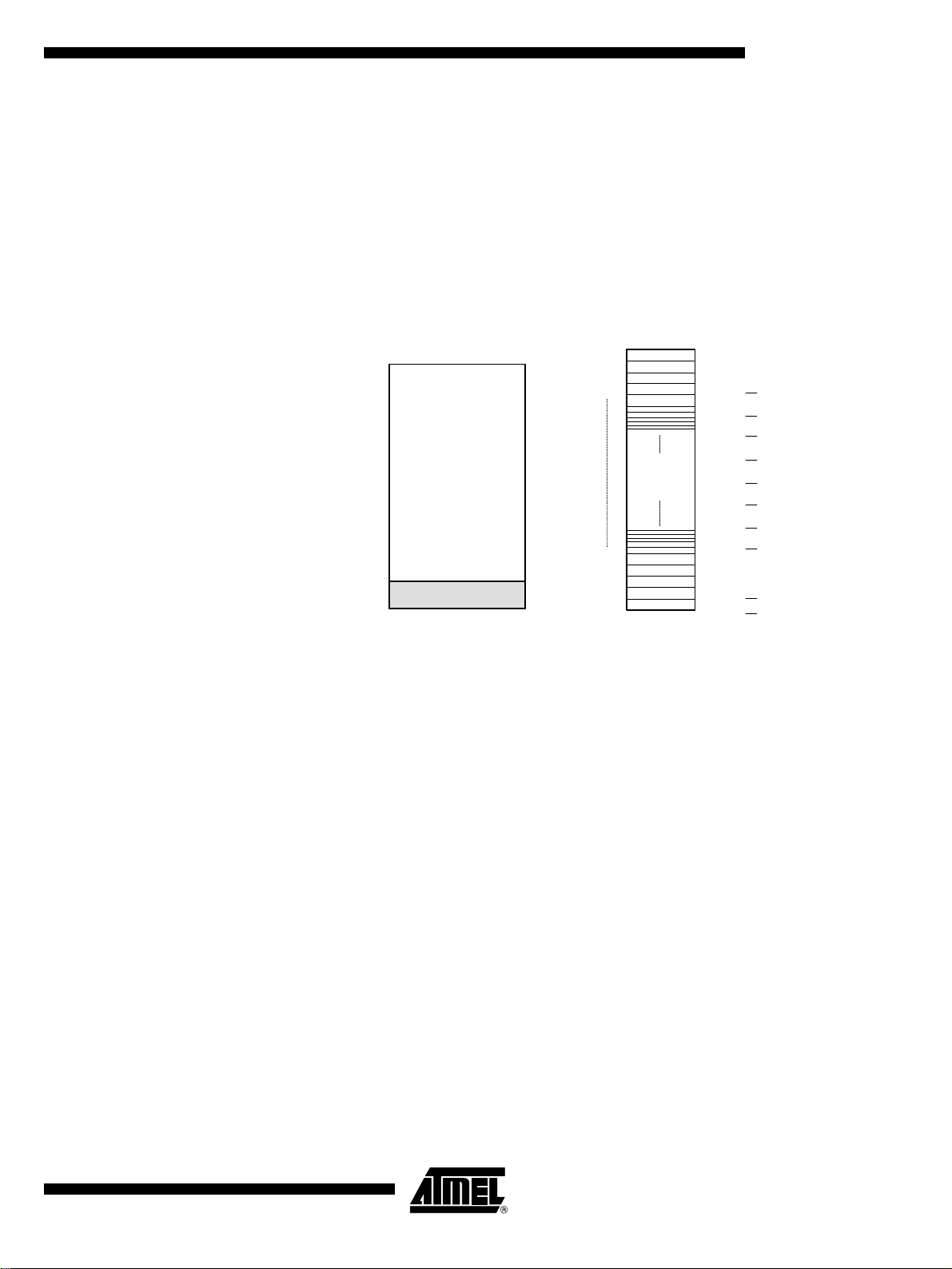

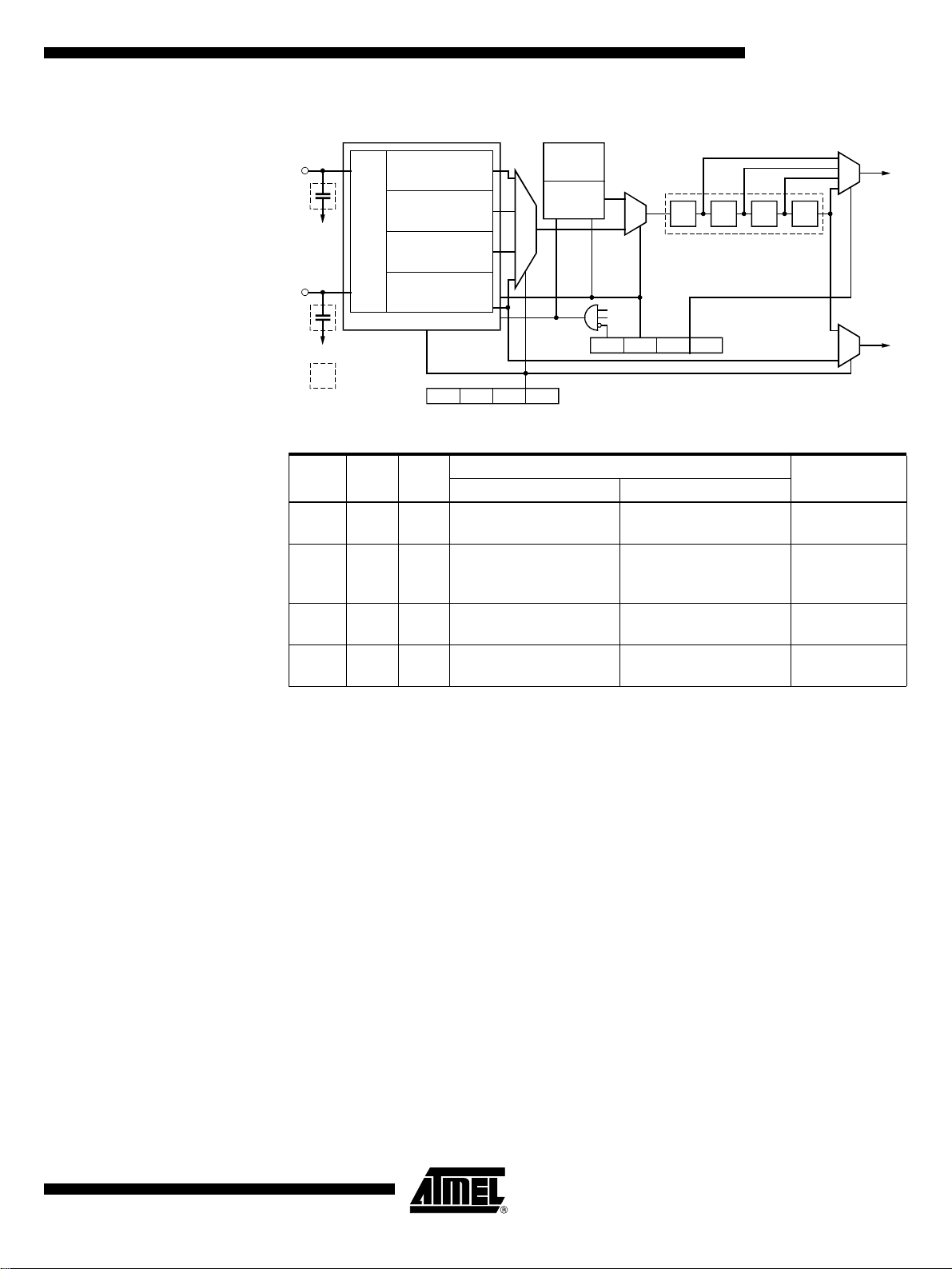

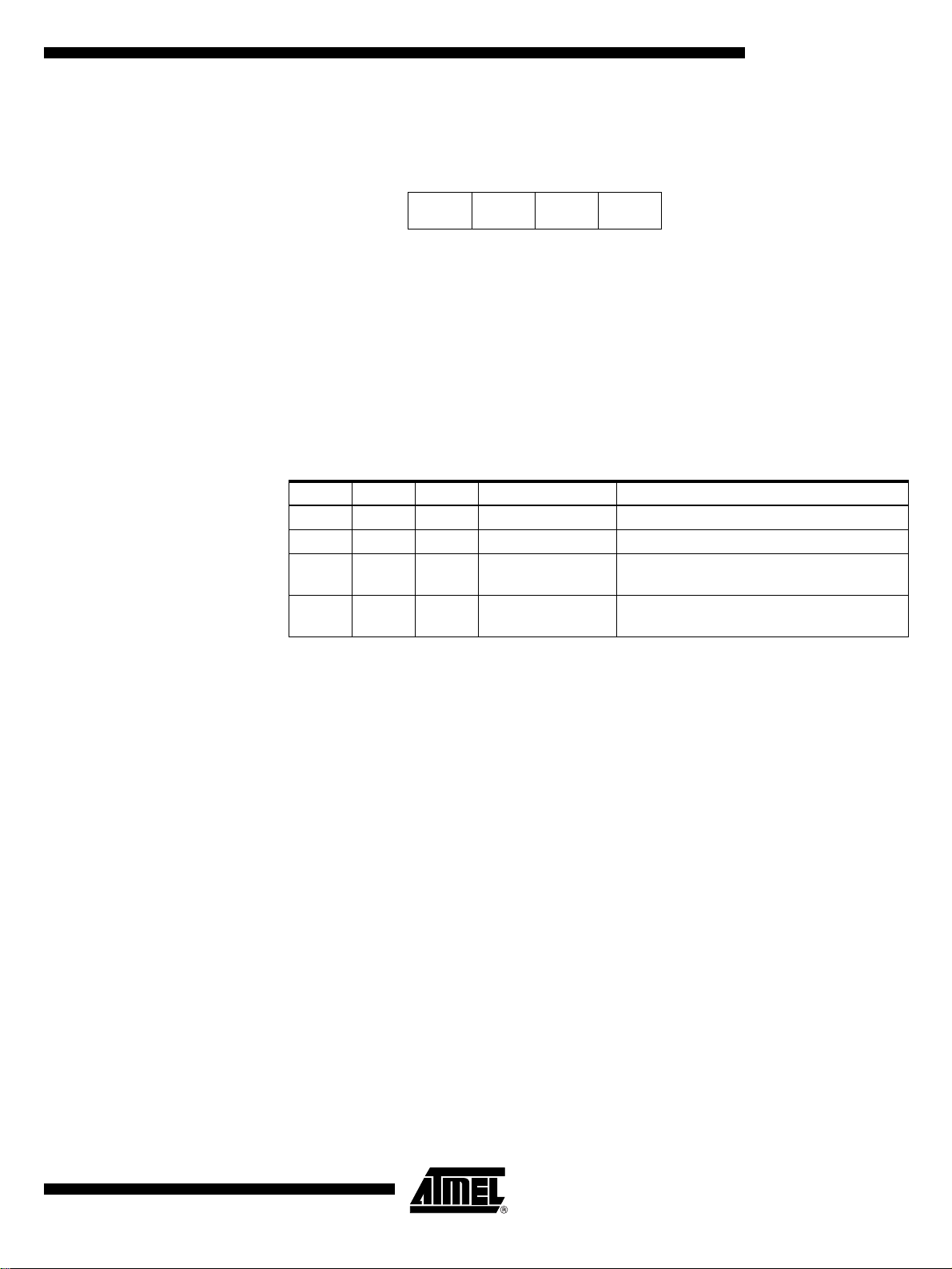

Figure 1. Application Diagram

ATAR862-8

Antenna

UHF ASK/FSK

Receiver

Micro-

controller

Keys

Micro-

controller

PLL-

Transmitter

ASK/FSK

Transmitter

ATAR862-8

Preliminary

Rev. 4589B–4BMCU–02/03

1

Page 2

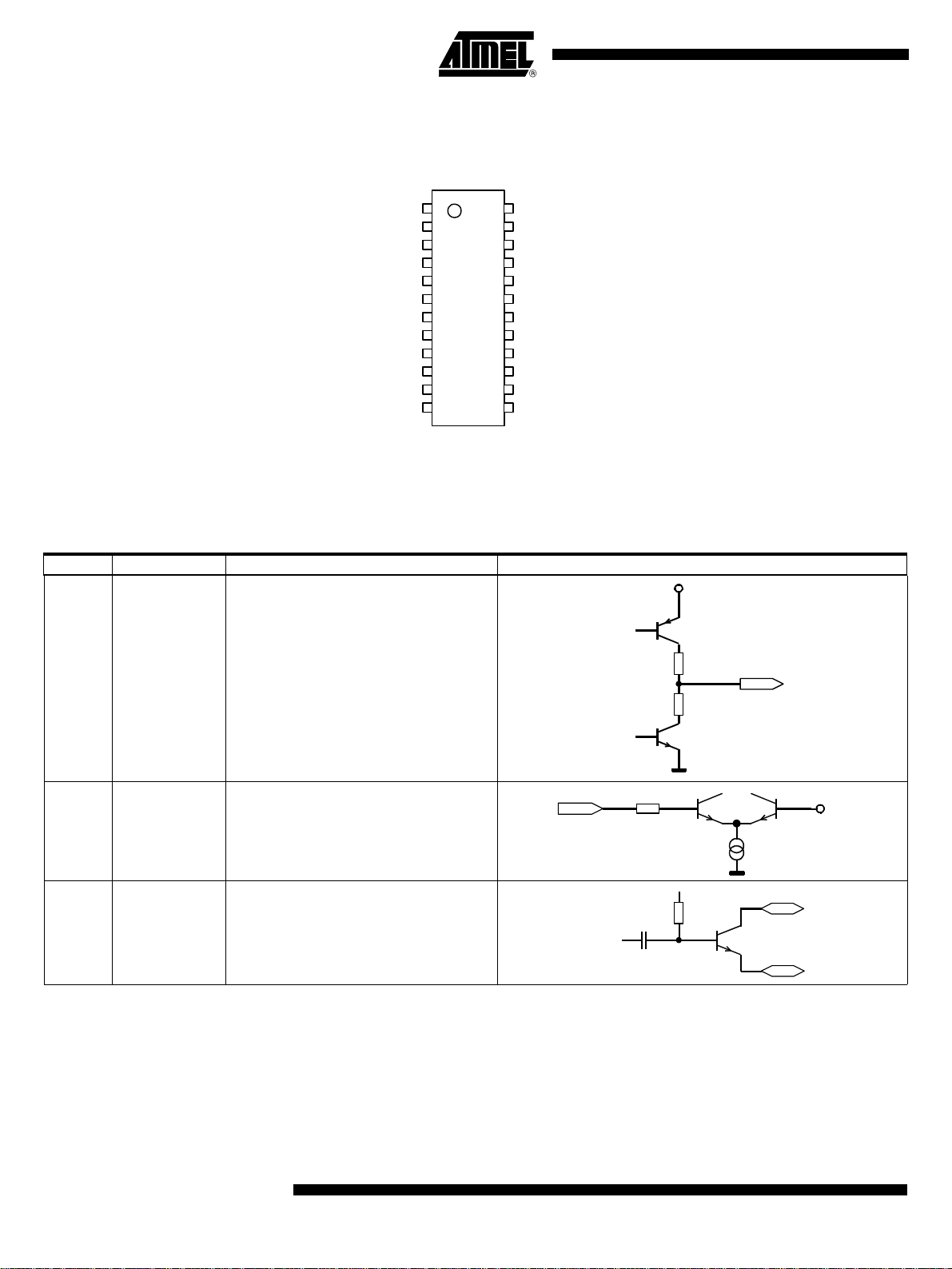

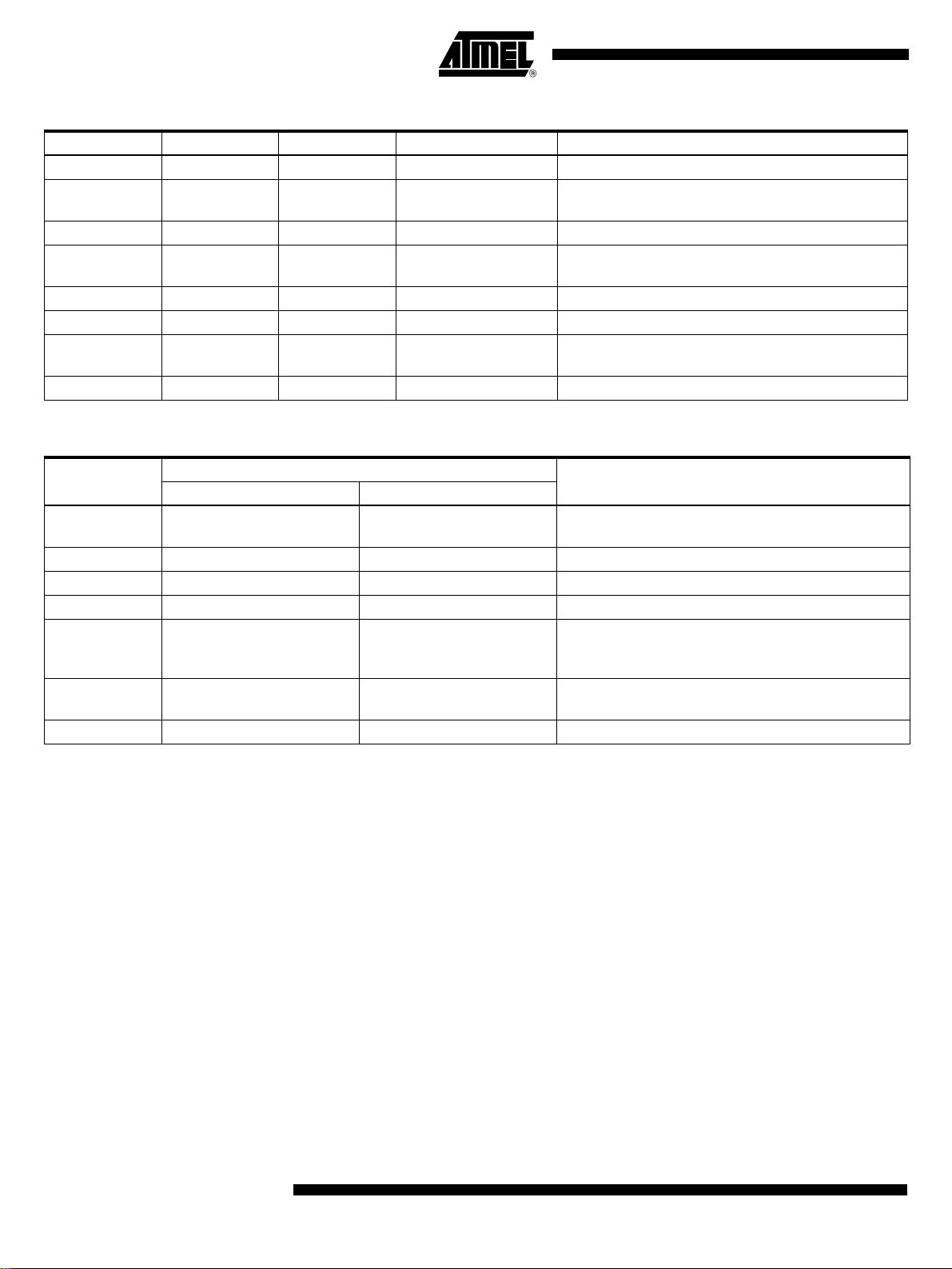

Pin Configuration

Figure 2. Pinning SSO24

XTAL

VS

GND

ENABLE

NRESET

BP63/T3I

BP20/NTE

BP23

BP41/T2I/VMI

BP42/T2O

BP43/SD/INT3

VSS

1

2

3

4

5

6

7

8

9

10

11

12

ANT1

24

ANT2

23

PA_ENABLE

22

CLK

21

BP60/T3O

20

OSC2

19

OSC1

18

BP50/INT6

17

BP52/INT1

16

BP53/INT1

15

BP40/SC/INT3

14

VDD

13

Pin Description: RF Part

Pin Symbol Function Configuration

1 CLK Clock output signal for microcontroller

The clock output fre quency is set by the

crystal to f

XTAL

/4

VS

100

CLK

2 PA_ENABLE Switches on power amplifier, used for

ASK modulation

3

4

ANT2

ANT1

Emitter of antenna output stage

Open collector antenna output

PA_ENABLE

50k

100

Uref=1.1V

20 µA

ANT1

ANT2

2

ATAR862-8

4589B–4BMCU–02/03

Page 3

Pin Description: RF Part (Continued)

Pin Symbol Function Configuration

5 XTAL Connection for crystal

ATAR862-8

VS

VS

1.5k

XTAL

182 mA

6 VS Supply voltage ESD protection circuitry (see Figure 8)

7 GND Ground ESD protection circuitry (see Figure 8)

8 ENABLE Enable input

ENABLE

200k

Pin Description: Microcontroller Part

Name Type Function Alternate Function Pin-No.

V

DD

V

SS

BP20 I/O Bi-directional I/O line of Port 2.0 NTE-test mode enable, see also section "Master Reset" 7

BP40 I/O Bi-directional I/O line of Port 4.0 SC-serial clock or INT3 external interrupt input 14

BP41 I/O Bi-directional I/O line of Port 4.1

BP42 I/O Bi-directional I/O line of Port 4.2 T2O Timer 2 output 10

BP43 I/O Bi-directional I/O line of Port 4.3 SD serial data I/O or INT3-external interrupt input 11

BP50 I/O Bi-directional I/O line of Port 5.0 INT6 external interrupt input 17

BP52 I/O Bi-directional I/O line of Port 5.2 INT1 external interrupt input 16

BP53 I/O Bi-directional I/O line of Port 5.3 INT1 external interrupt input 15

BP60 I/O Bi-directional I/O line of Port 6.0 T3O Timer 3 output 20

BP63 I/O Bi-directional I/O line of Port 6.3 T3I Timer 3 input 6

OSC1 I Oscillator input

OSC2 O Oscillator output

NRESET I/O Bi-directional reset pin – 5

– Supply voltage – 13

– Circuit ground – 12

VMI voltage monitor input or T2I external clock input

Timer 2

4-MHz crystal input or 32-kHz crystal input or external

clock input or external trimming resistor input

4-MHz crystal output or 32-kHz crystal output or external

clock input

1.2k

18

19

Reset State

NA

NA

Input

Input

9

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

I/O

4589B–4BMCU–02/03

3

Page 4

UHF ASK/FSK Transmitter Block

Features

• Integrated PLL Loop Filter

• ESD Protection (4 kV HBM/200 V MM, Except Pin 2: 4 kV HBM/100 V MM) also at ANT1/ANT2

• High Output Power (5.5 dBm) with Low Supply Current (8.5 mA Typically)

• Modulation Scheme ASK/FSK

– FSK Modulation is Achieved by Connecting an Additional Capacitor between the XTAL Load Capacitor and the Open-

drain Output of the Modulating Microcontroller

• Easy to Design-in Due to Excellent Isolation of the PLL from the PA and Power Supply

• Single Li-cell for Power Supply

• Supply Voltage 2.0 V to 4.0 V in the Temperature Range of -40°C to +85 °C/+125°C

• Single-ended Antenna Output with High Efficient Pow er Amplifier

• CLK Output for Clocking the Microcontroller

• One-chip Solution with Minimum External Circuitry

• 125°C Operation for Tire Pressure Systems

Description

The PLL transmitter block has been developed for the demands of RF low -cost transmission systems, at data rates up to

32 kbaud. The transmitting frequency range is 686 MHz to 928 MHz. It can be used in both FSK and ASK systems.

4

ATAR862-8

4589B–4BMCU–02/03

Page 5

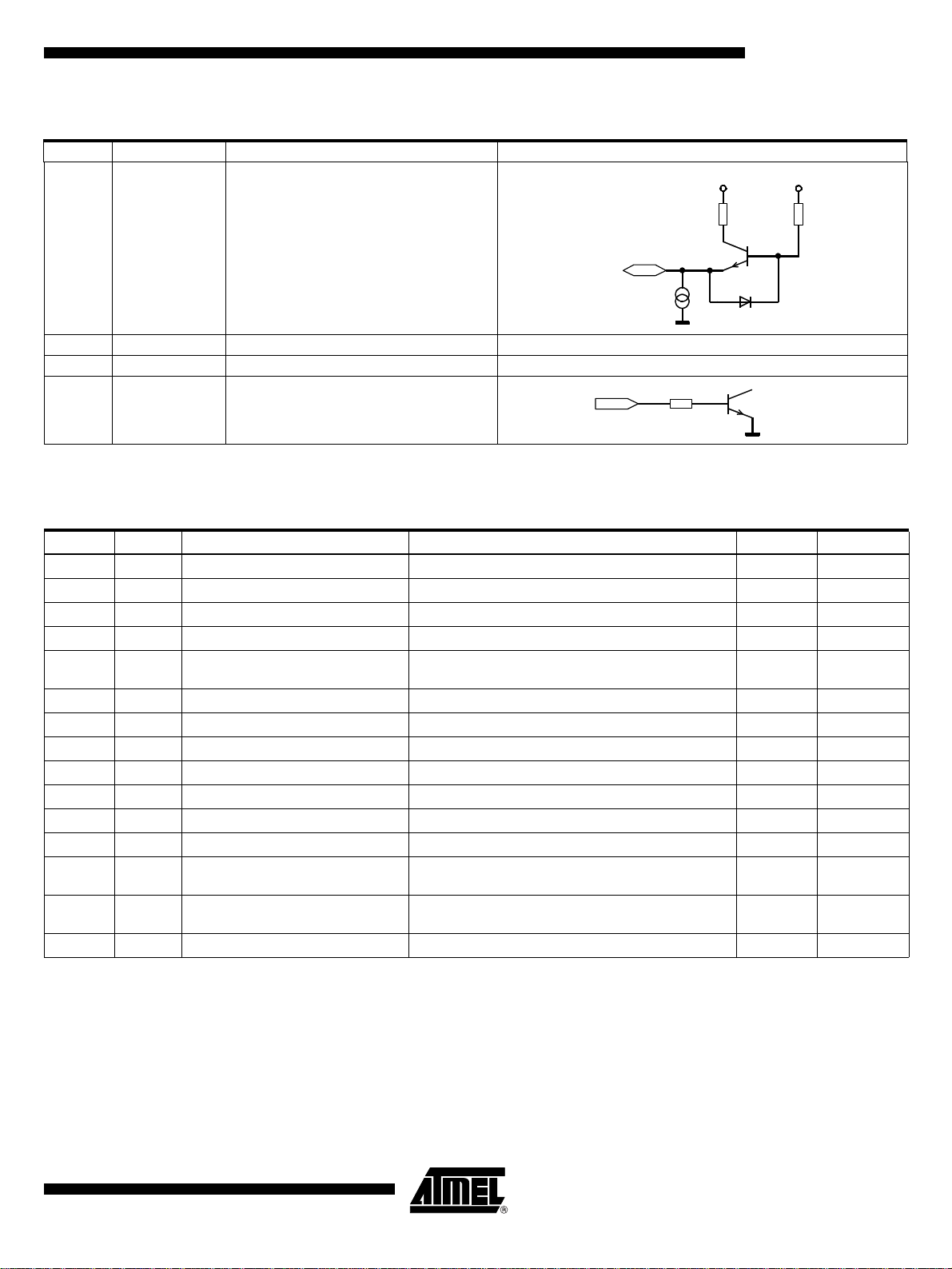

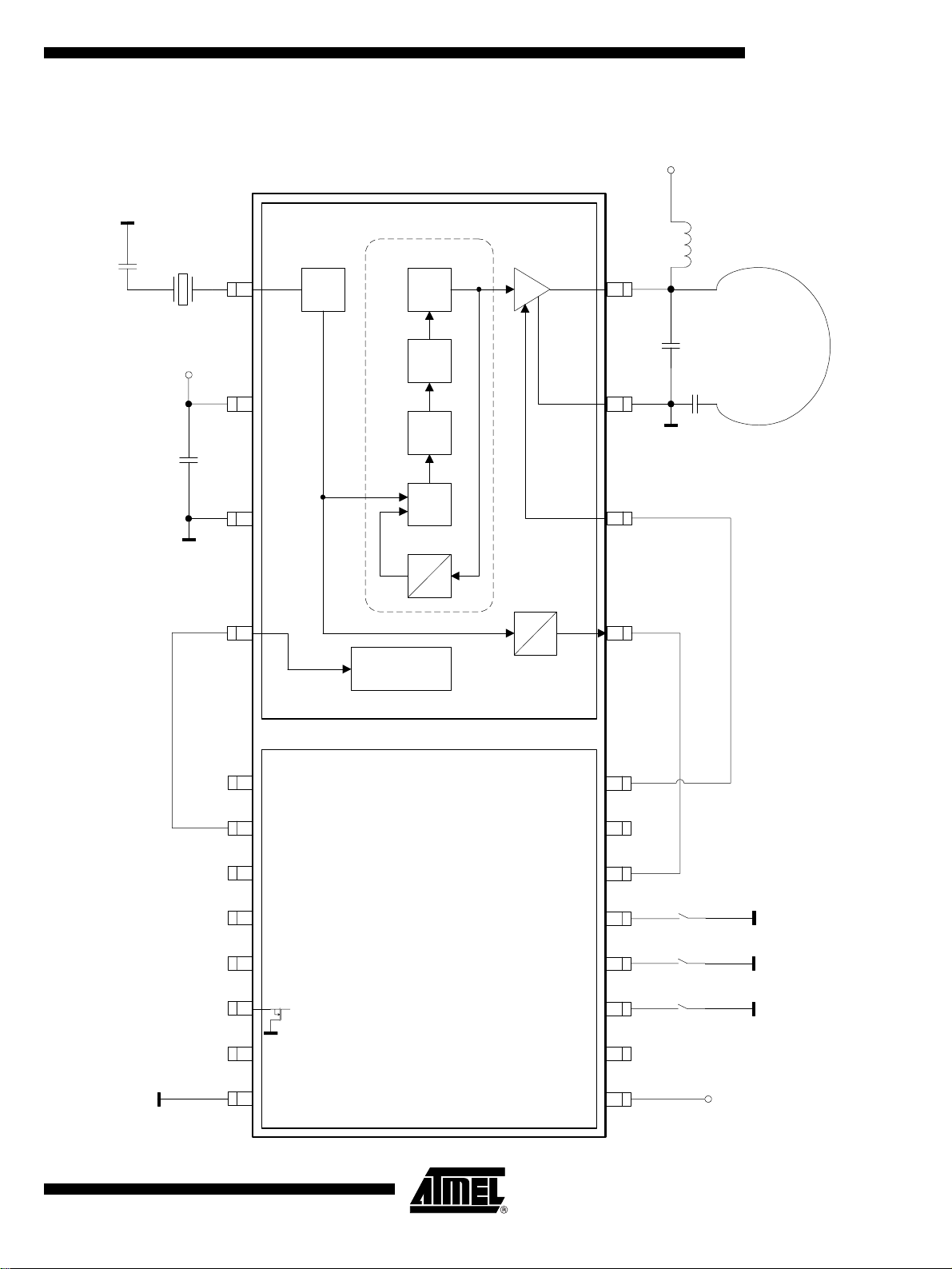

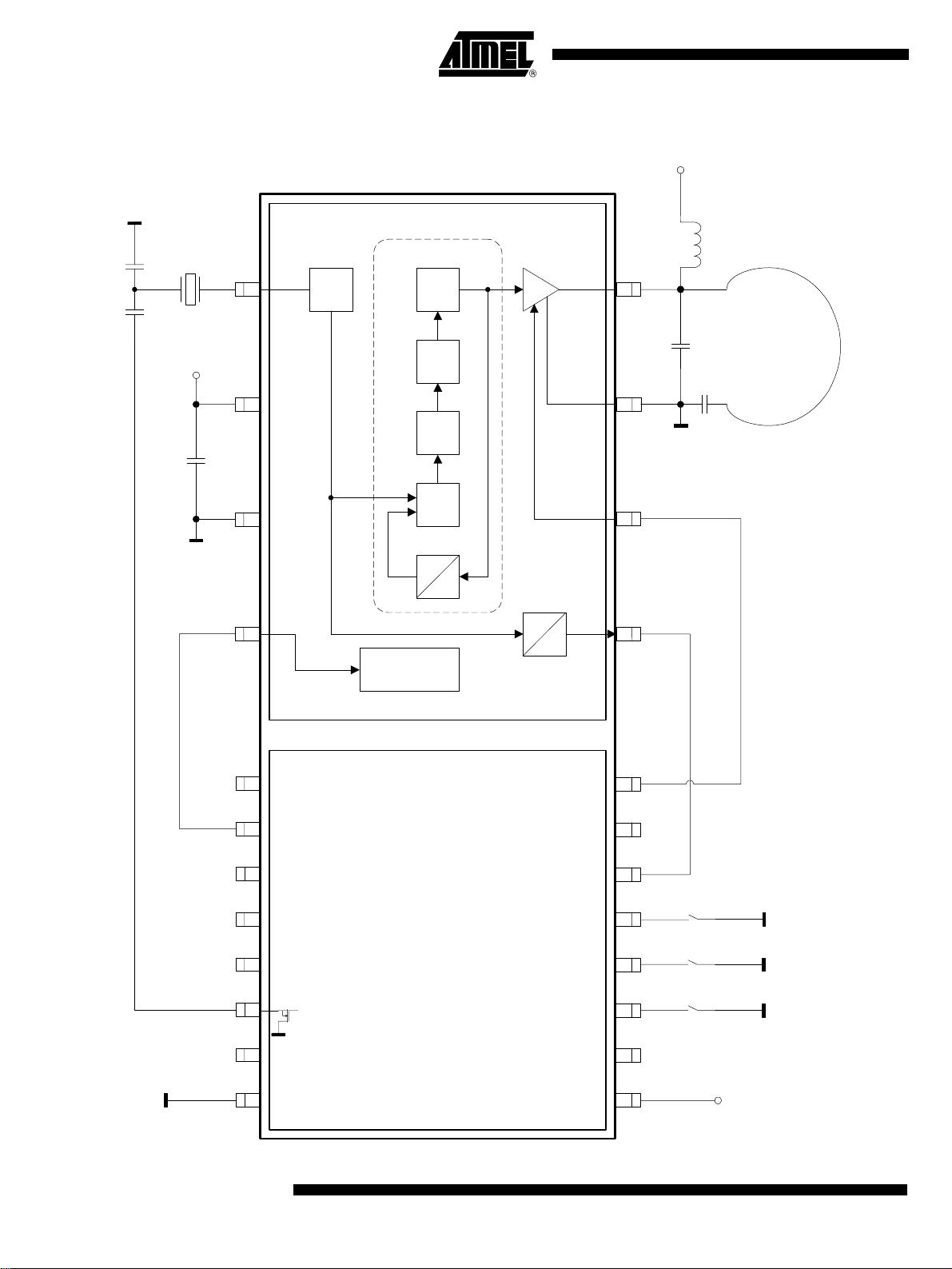

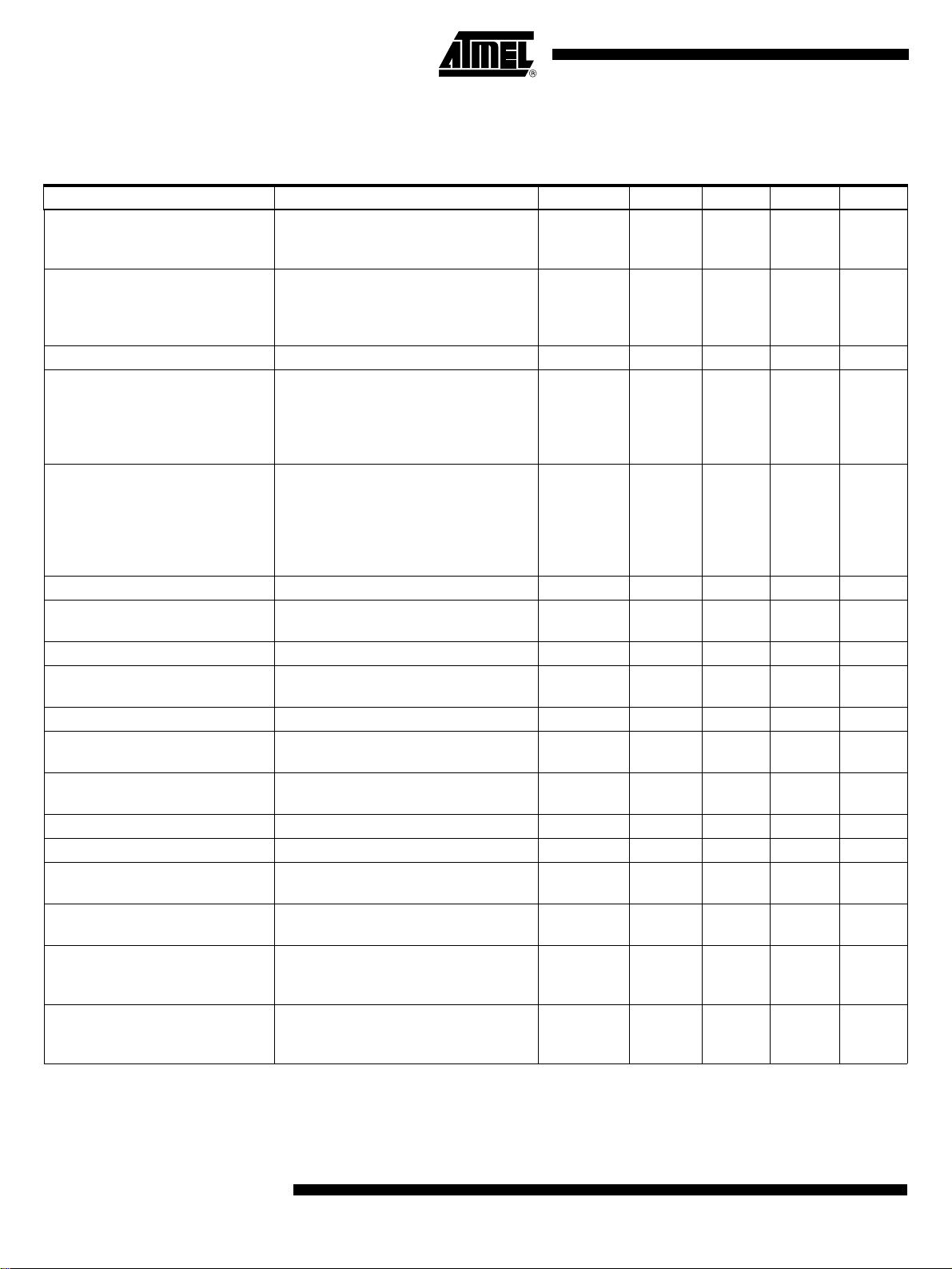

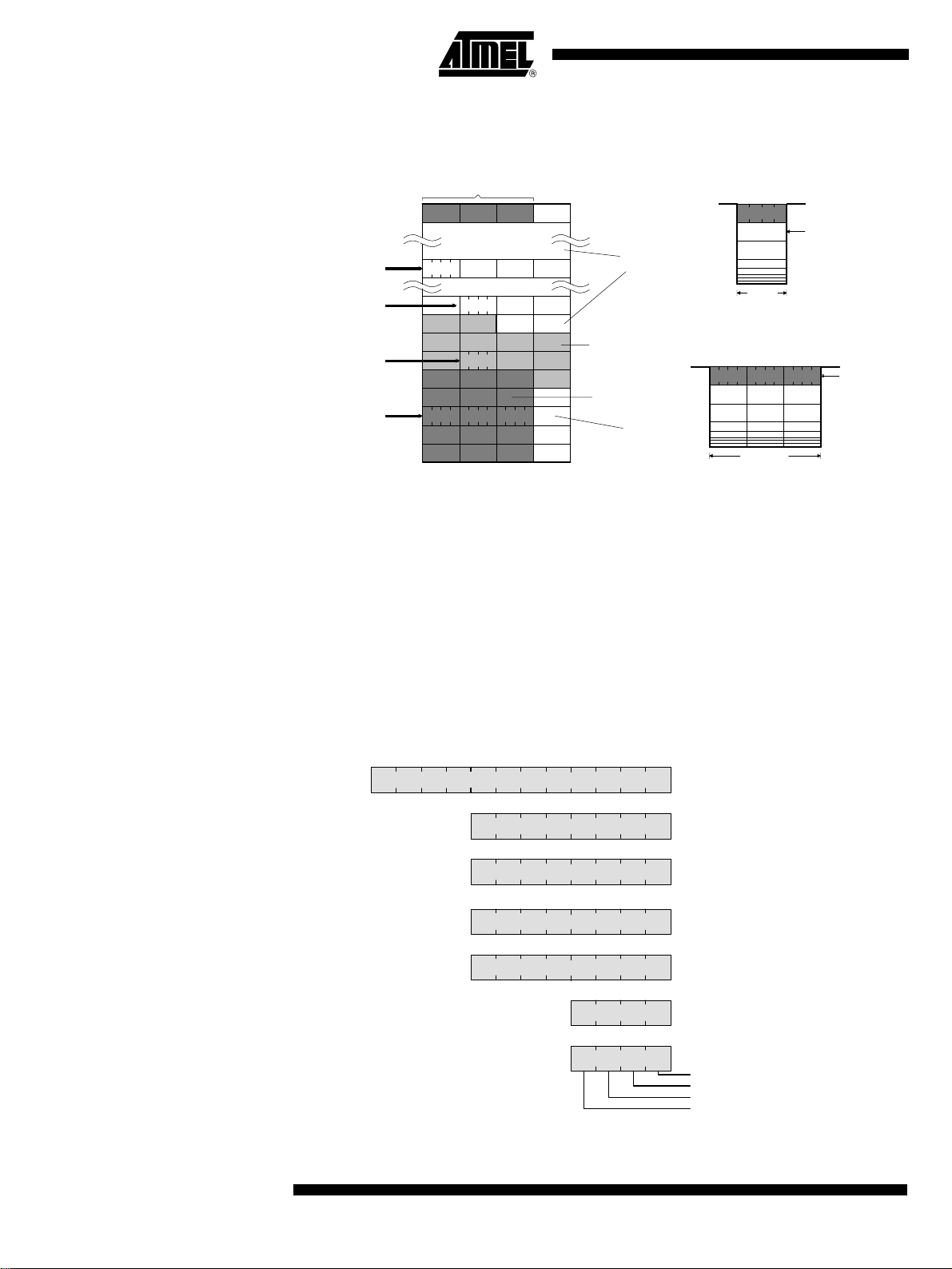

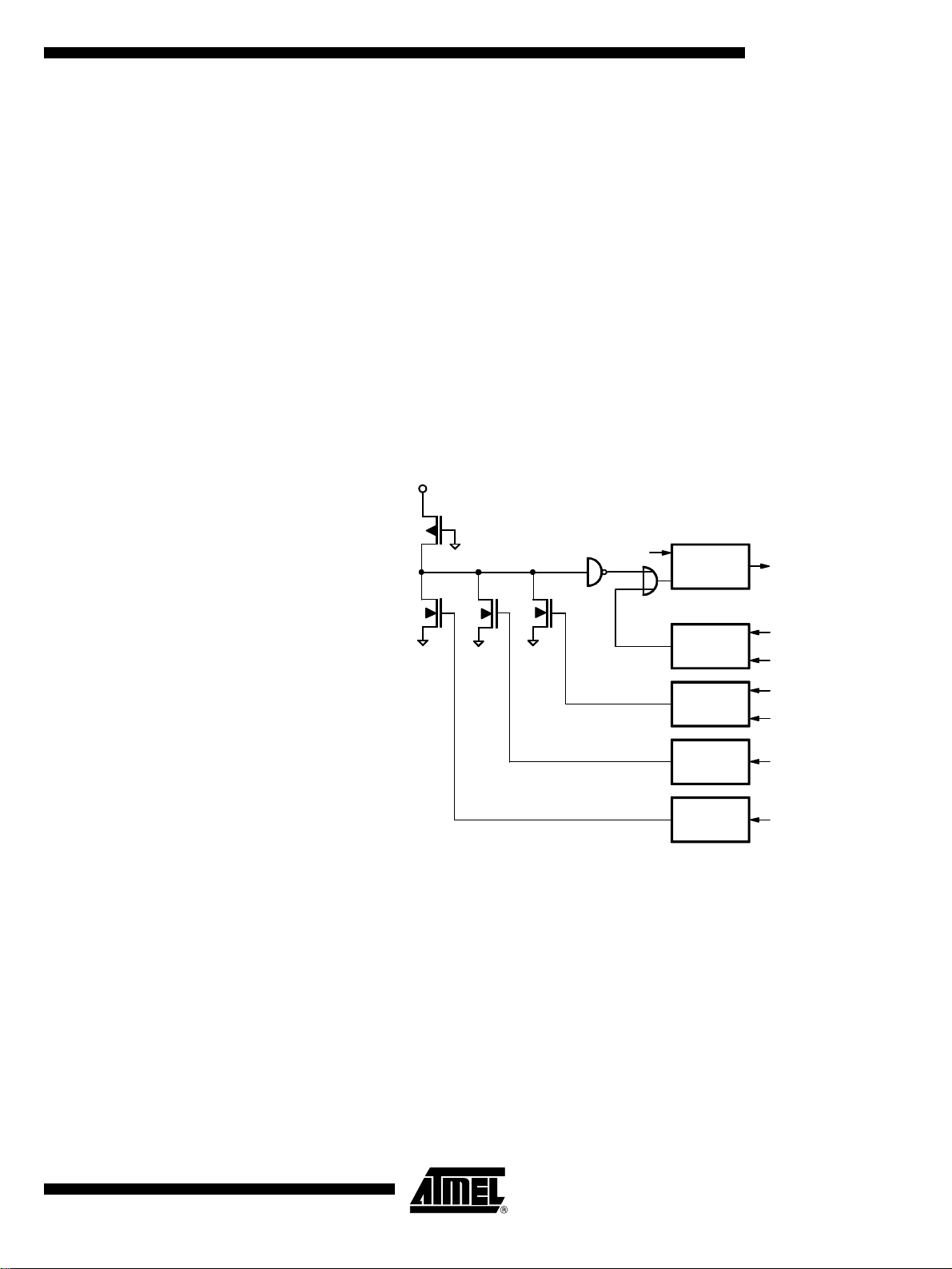

Figure 3. Block Diagram

ATAR862-8

ATAR862-8

CLK

PA_ENABLE

ANT2

ANT1

OSC2

OSC1

V

DD

V

SS

NRESET

BP20/NTE

BP23

BP10

BP13

BP21

BP22

Brown-out protect.

RESET

Voltage monitor

External input

VMI

Port 1

n

o

i

t

c

2

e

t

r

r

i

o

d

P

a

t

a

D

f

4

PA

RC

oscillators

ROM

4 K x 8 bit

4-bit CPU core

Power up /

down

f

32

PFD

CP

LF

VCO

PLL

Crystal

oscillators

Clock management

clock input

RAM

256 x 4 bit

I/O bus

External

XTO

UTCM

Timer 1

interval- and

watchdog timer

Timer 2

8/12-bit timer

with modulator

SSI

Serial interface

Timer 3

8-bit

timer / counter

with modulator

and demodulator

ENABLE

VS

GND

XTAL

µC

T2I

T2O

SD

SC

T3O

T3I

4589B–4BMCU–02/03

Data direction +

alternate function

Port 4

BP40

BP41

INT3

VMI

SC

T2I

BP42

T2O

BP43

INT3

SD

Data direction +

interrupt control

Port 5

BP51

INT6

BP52

BP50

INT1

INT6

BP53

INT1

Data direction +

alternate function

Port 6

BP60

T3O

BP63

T3I

EEPROM

32 x 16 bit

5

Page 6

General Desc ription The fully-integrated PLL transmitter that allows particularly simple, low-cost RF minia-

ture transmitters to be assembled. The VCO is locked to 64 ´ f

13.5672 MHz crystal is needed for a 868.3 MHz transmitter nad a 14.2969 MHz crystal

for a 915 MHz transmitter. All other PLL and VCO peripheral elements are integrated.

The XTO is a series res onance oscillator so that only one capac itor together with a

crystal connected in series to GND are needed as external elements.

The crystal oscillator togethe r with the PLL nee ds maximum < 1 ms unti l the PLL is

locked and the CLK ou tput is sta ble. A wait time of ³ 4 ms until the CLK is used for the

microcontroller and the PA is switched on.

The power amplifier is an open-collector output delivering a current pulse which is nearly

independent from t he load imped ance. The del ivered ou tput power is controlle d via the

connected load impedance.

This output configuration enables a simple matching to any kind of antenna or to 50 W. A

high power efficiency of h =P

results when an opti mized load im pedanc e of Z

ply voltage.

out

/(I

´ VS) of 24% for the power amplifier at 868.3 MHz

S,PA

= (166 + j226) W is used at 3 V sup-

Load

XTAL

, thus, a

Functional Description

If ENABLE = L and PA_ENABLE = L, the circuit is in standby mode consuming only a

very small amount of current, so that a lithium cell used as power supply can work for

several years.

With ENABLE = H, the XTO, PLL and the CLK driver are switched on. If PA_ENABLE

remains L, only the PLL and the XT O are r unn ing and the CLK si gn al is del iver ed to the

microcontroller. The VCO locks to 64 times the XTO frequency.

With ENABLE = H and PA_ENABLE = H, the PLL, XTO, CLK driver and the power

amplifier are on. With PA_ENABLE, the power amplifier can be switched on and off,

which is used to perform the ASK modulation.

ASK Transmission The PLL transmit ter bl oc k is a ct iv ated by ENA BL E = H. PA _E NAB LE m us t r em ain L for

t ³ 4 m s, then the CLK signal can be taken to clock the microcontroller and the output

power can be modulated by means of pin PA_ENABLE. After transmission,

PA_ENABLE is switched to L and the microcontroller switches back to internal clocking.

The PLL transmitter block is switched back to standby mode with ENABLE = L.

FSK Transmission The PLL transmit ter bl oc k is a ct iv ated by ENA BL E = H. PA _E NAB LE m us t r em ain L for

t ³ 4 ms, then the CLK signal can be taken to cl ock the microcontroller and the power

amplifier is sw itch ed on with PA_ENA BLE = H . The ch ip is then r eady for FSK modul ation. The microcontroller starts to switch on and off the capacitor between the XTAL load

capacitor and GND with an open-drain output port, thus changing the reference frequency of the PLL. If the switch is closed, the output frequency is lower than if the switch

is open. After tra nsmission PA_E NABLE is switch ed to L and the micro controller

switches back to internal clockin g. The PLL transm itter block is switc hed back to

standby mode with ENABLE = L.

The accuracy of the frequency deviation with XTAL pulling method is about ±25% when

the following tolerances are considered.

6

ATAR862-8

4589B–4BMCU–02/03

Page 7

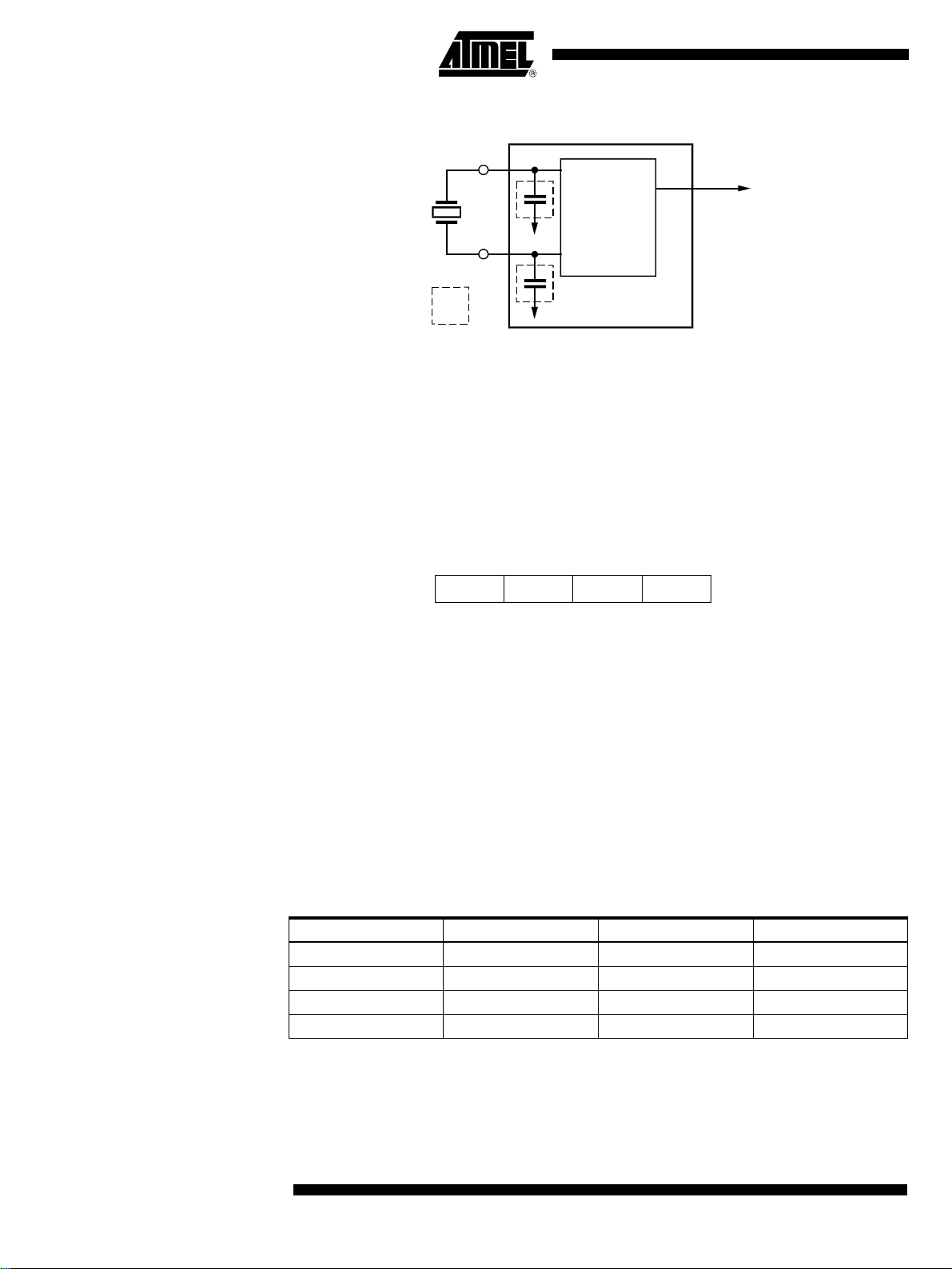

Figure 4. Tolerances of Frequency Modulation

~

V

S

C

XTAL

~

Stray1

CMLMR

Crystal equivalent circuit

C

0

ATAR862-8

C

Stray2

S

C

4

C

5

C

Switch

Using C

capacitances on each side of the crystal of C

capacitance of the crystal of C

=9.2pF ±2%, C5= 6.8 pF ±5%, a switch port with C

4

= 3.2 pF ±10% and a crystal with CM= 13 fF ±10%, an

0

Stray1=CStray2

= 3 pF ±10% , str ay

Switch

= 1 pF ±10%, a para llel

FSK deviation of ±21.5 kHz typical with worst case tolerances of ±16.8 kHz to

±28.0 kHz results.

CLK Output An output CLK signal is provided for a connected microcontroller. The delivered signal is

CMOS compatible if the load capacitance is lower than 10 pF.

Clock Pulse Take Over The clock of the crystal oscillator can be used for clocking the microcontroller. Atmel’s

M4xCx9x has the special feature of starting with an integrated RC-oscillator to switch on

the PLL transmitter block with ENABLE = H, and after 4 ms to assume the clock signal

of the transmission IC, so the message can be sent with crystal accuracy.

Output Matching and Power Setting

The output power is set by the l oad impe dance o f the ante nna. Th e maximum output

power is achieved with a load impedance of Z

There must be a low resistive path to V

to deliver the DC current.

S

Load,opt

= (166 + j226) W at 868.3 MHz.

The delivered current pulse of the power amplifier is 7.7 mA and the maximum output

power is delivered to a resistive load of 475 W if the 0.53 pF output capacitance of the

power amplifier is compensated by the load impedance.

An optimum load impedance of:

Z

= 475 W || j/(2 ´p0.53 pF) = (166 + j226 ) W thus results for the maxi mum output

Load

power of 5.5 dBm.

4589B–4BMCU–02/03

The load impedance is def ine d as th e im ped anc e s ee n from the PL L tr ans m itte r blo ck’s

ANT1, ANT2 into the ma tching network . Do not confus e this la rge si gnal load impedance with a small signal input impedance delivered as input characteristic of RF

amplifiers and me asured fr om the appl icatio n into the IC i nstead of from the IC into th e

application for a power amplifier.

Less output power is achieved by lowering the real parallel part of 475 W where the

parallel imaginary part should be kept constant.

Output power measurement can be done with the cir cuit shown in Figure 5. Note that

the component values must be changed to compensate the individual board parasitics

until the PLL transmitter block has the right load impedance Z

= (166 + j226) W.

Load,opt

Also the damping of the cable used to measure the output power must be calibrated.

7

Page 8

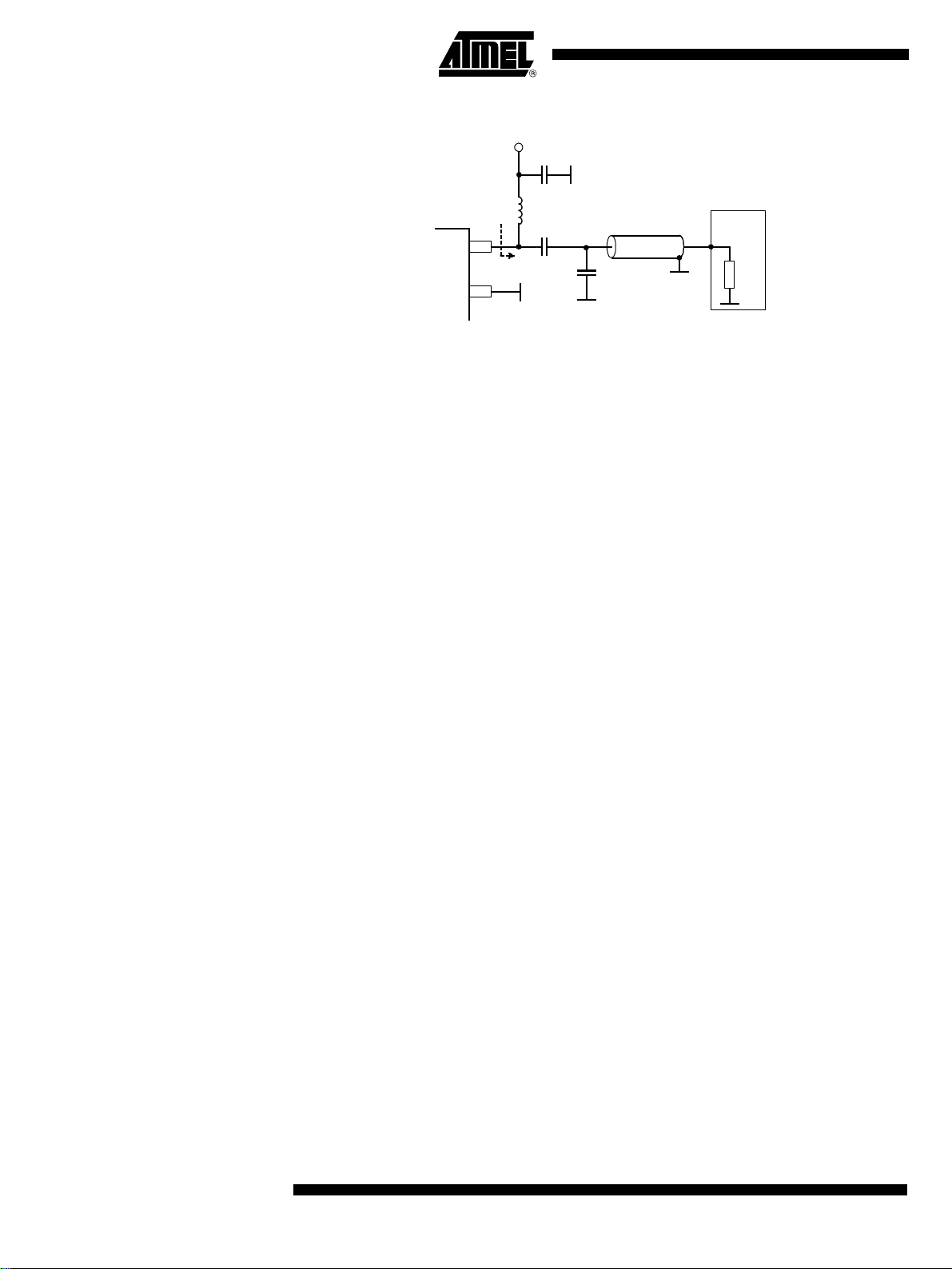

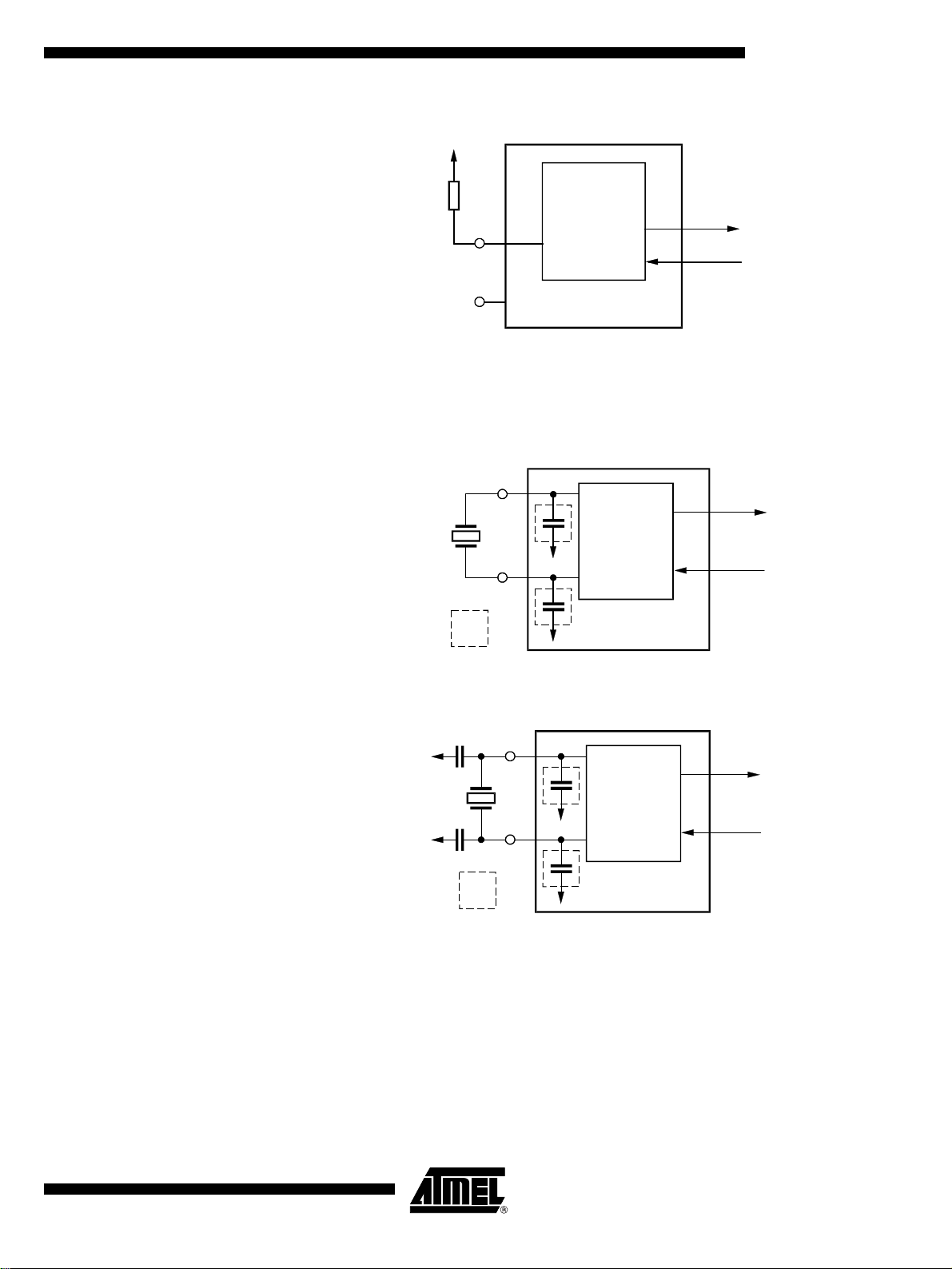

Figure 5. Output Power Measurement

V

S

C1 = 1n

~

ANT1

ANT2

~

L1 = 10n

Z

C

= 1.5p

Lopt

2

C = 2.7p

3

Z = 50 W

Power

meter

R

in

50 W

Application Circuit For the supply-voltage blocking capacitor C

(see Figure 6 and Figure 7). C

amplifier where C

typically is 3. 9 pF/NP0 and C2 is 1pF/NP0; for C2 two capacitors in

1

series should be us ed to achiev e a better tole rance val ue and to hav e the possi bility to

realize the Z

C

forms together with the pin s of the PLL tr ansm itter blo ck an d the PC B boar d wires a

1

by using standard valued capacitors.

Load,opt

series resonance lo op that supp resses the 1

PCB is important. Normally, the best suppression is achiev ed when C

close as possible to the pins ANT1 and ANT2.

The loop antenna should not exceed a width of 1.5 mm, otherwise the Q-factor of the

loop antenna is too high.

L

(»50 nH to 100 nH) can be printed on PCB. C4 should be selected so the XTO runs

1

on the load resonance fr equency of the crysta l. Normal ly, a valu e of 12 pF results for a

15 pF load-capacitance crystal.

and C2 are used to match the loop antenna to the power

1

, a value of 68 nF/X7R is recommended

3

st

harmonic, thus, the position of C1 on the

is placed as

1

8

ATAR862-8

4589B–4BMCU–02/03

Page 9

Figure 6. ASK Application Circuit

ATAR862-8

VS

C4

XTAL

VS

XTAL

VS

C3

GND

ENABLE

L1

241

ANT1

23

ANT2

22

PA_ENABLE

21

CLK

C1

Loop

Antenna

C2

PLL

VCO

LF

CP

PFD

32

PA

f

4

f

XTO

2

3

4

Power up/down

4589B–4BMCU–02/03

NRESET

BP63/T3I

BP20/NTE

BP23

BP41/T2I/VMI

BP42/T2O

BP43/SD/

INT3

VSS

10

11

12

5

6

7

8

9

BP60/T3O

20

OSC2

19

OSC1

18

BP50/INT6

17

BP52/INT1

16

BP53/INT1

15

BP40/SC/INT3

17

VDD

13

S1

S2

S3

VS

9

Page 10

Figure 7. FSK Application Circuit

VS

C4

C5

XTAL

VS

XTAL

VS

C3

GND

ENABLE

L1

241

ANT1

23

ANT2

22

PA_ENABLE

21

CLK

C1

Loop

Antenna

C2

PLL

VCO

LF

CP

PFD

32

PA

f

4

f

XTO

2

3

4

Power up/down

10

NRESET

5

BP63/T3I

BP20/NTE

BP41/T2I/VMI

BP42/T2O

BP43/SD/

INT3

6

7

BP23

8

9

10

11

VSS

12

ATAR862-8

BP60/T3O

20

OSC2

19

OSC1

18

BP50/INT6

17

BP52/INT1

16

BP53/INT1

15

BP40/SC/INT3

17

VDD

13

S1

S2

S3

VS

4589B–4BMCU–02/03

Page 11

Figure 8. ESD Protection Circuit

VS

ATAR862-8

ANT1

CLK PA_ENABLE

GND

ANT2

XTAL ENABLE

Absolute Maximum Ratings

Parameters Symbol Min. Max. Unit

Supply voltage V

Power dissipation P

Junction temperature T

Storage temperature T

Ambient temperature T

tot

Stg

amb

S

j

-55 +125 °C

-55 +125 °C

5V

100 mW

150 °C

Thermal Resistance

Parameters Symbol Value Unit

Junction ambient R

thJA

170 K/W

Electrical Characteristics

VS = 2.0 V to 4.0 V, T

Typical values are given at V

Parameters Test Conditions Symbol Min. Typ. Max. Unit

Supply current Power down,

Supply current Power up, PA off, VS= 3 V

Output power VS= 3.0 V, T

4589B–4BMCU–02/03

= -40°C to +125°C unless otherwise specified.

amb

= 3.0 V and T

S

V

ENABLE

V

PA_ENABLE

V

PA_ENABLE

= 25°C. All parameters are referred to GND (Pin 7).

amb

< 0.25 V , -40°C to +85°C

< 0.25 V, -85°C to +125°C

< 0.25 V, +25°C

(100% correlation tested)

ENABLE

ENABLE

> 1.7 V, V

= 3.0 V

S

> 1.7 V, V

amb

V

Power up, V

V

f = 868.3 MHz, Z

PA-EN ABLE

PA-EN ABLE

=25°C

Load

<0.25V

>1.7V

= (166 + j226) W

I

S_Off

I

S

I

S_T r ansmit

P

Ref

350

7

<10

3.7 4.8 mA

8.5 11 mA

3.5 5.5 8 dBm

nA

µA

nA

11

Page 12

Electrical Characteristics (Continued)

VS = 2.0 V to 4.0 V, T

Typical values are given at V

= -40°C to +125°C unless otherwise specified.

amb

= 3.0 V and T

S

= 25°C. All parameters are referred to GND (Pin 7).

amb

Parameters Test Conditions Symbol Min. Typ. Max. Unit

Output power v ariation for the full

temperature range

Output power v ariation for the full

temperature range

Achievable output-power range Selectable by load impedance P

Spurious emission f

T

= -40°C to +85°C

amb

= 3.0 V

V

S

= 2.0 V

V

S

= -40°C to +125°C

T

amb

V

= 3.0 V

S

= 2.0 V

V

S

= P

P

Out

CLK

Ref

= f0/128

+ DP

Ref

DP

Ref

DP

Ref

DP

Ref

DP

Ref

Out_typ

-1.5

-4.0

-2.0

-4.5

dB

dB

dB

dB

-3 +5.5 dBm

Load capacitance at Pin CLK = 10 pF

fO ± 1´ f

± 4 ´ f

f

O

CLK

CLK

-52

-52

dBc

dBc

other spurious are lower

Oscillator frequency XTO

(= phase comparator frequency)

f

= f0/32

XTO

= resonant frequency of the

f

XTAL

XTAL, C

£ 10 fF, load capacitance

M

selected accordingly

T

= -40°C to +85°C,

amb

= -40°C to +125°C

T

amb

f

XTO

-30

-40

f

XTAL

+30

+40

ppm

ppm

PLL loop bandwidth 250 kHz

Phase noise of phase

comparator

Referred to f

25 kHz distance to carrier

PC

= f

XT0,

-116 -110 dBc/Hz

In loop phase noise PLL 25 kHz distance to carrier -80 -74 dBc/Hz

Phase noise VCO at 1 MHz

at 36 MHz

Frequency range of VCO f

Clock output frequen cy (CMOS

microcontroller compatible)

Voltage swing at Pin CLK C

£ 10 pF V

Load

VCO

0h

V

868 928 MHz

VS´ 0.8

0l

-89

-120

/256 MHz

f

0

V

-86

-117

´ 0.2

S

dBc/Hz

dBc/Hz

V

V

Series resonance R of the c rystal Rs 110 W

Capacitive load at Pin XT0 7pF

FSK modulation frequency rate Duty cycle of the modulation signal =

50%

ASK modulation frequency rate Duty cycle of the modulation signal =

50%

ENABLE input Low level input voltage

High level input voltage

Input current high

PA_ENABLE input Low level input voltage

High level input voltage

Input current high

V

Il

V

Ih

I

In

V

Il

V

Ih

I

In

032kHz

032kHz

0.25

1.7

20

0.25

1.7

5

V

V

µA

V

V

µA

12

ATAR862-8

4589B–4BMCU–02/03

Page 13

Microcontroller Block

ATAR862-8

Features

• Extended Temperature Range for High Temperature up to 125°C

• 4-Kbyte ROM, 256 x 4-bit RAM

• 16 Bi-directional I/Os

• Up to Seven External/Internal Interrupt Sources

• Multifunction Timer/Counter

-IR Remote Control Carrier Generator

-Biphase-, Manchester- and Pulse-width Modulator and Demodulator

-Phase Control Function

• Programmable System Clock with Prescaler and Five Different Clock Sources

• Supply-voltage Range (2.0 V to 4.0 V)

• Very Low Sleep Current (< 1 µA)

• 32 x 16-bit EEPROM (ATAR892 Only)

• Synchronous Serial Interface (2-wire, 3-wire)

• Watchdog, POR and Brown-out Function

• Voltage Monitoring Inclusive Lo_BAT Detect

• Flash Controller T48C862 Available (SSO24)

Description The ATAR862-8 is a member of Atmel’s fami ly of 4-bit single-chip micr ocontrollers. It

offers highest integration for IR and RF data communication, remote-control and phasecontrol applications. The ATAR862-8 is suitable for the transmitter side as well as the

receiver side. It contains ROM, RAM, parallel I/O ports, two 8-bit programmable multifunction timer/co unters with mod ulator and de modulator fun ction, voltag e supervis or,

interval timer with wat chdog fun ction and a soph istic ated on -chip cl ock gene ration with

external clock input, integrated RC-oscillator, 32-kHz and 4-MHz crystal-oscillators. The

ATAR862-8 has an EEPROM as a third chip in one package.

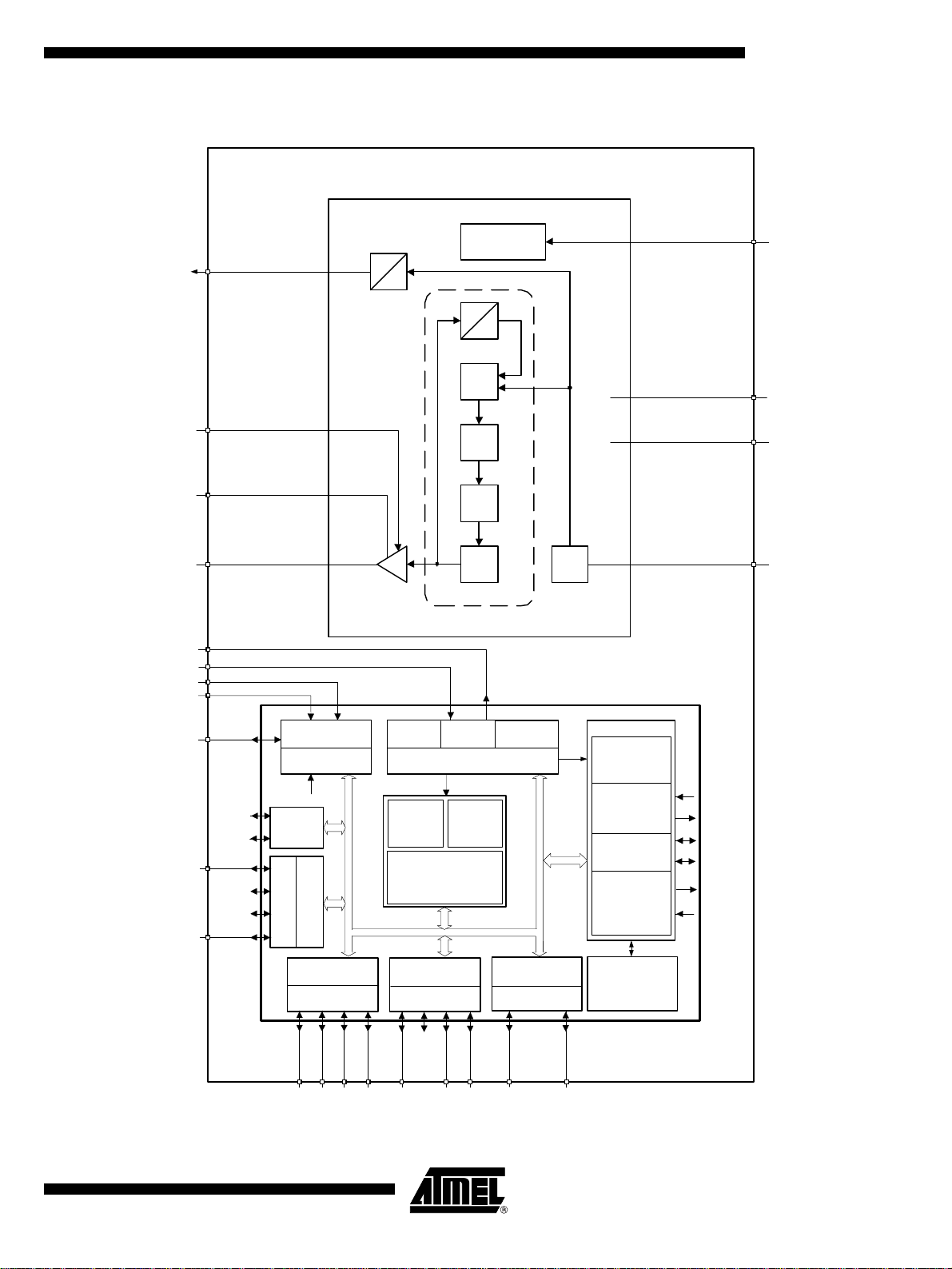

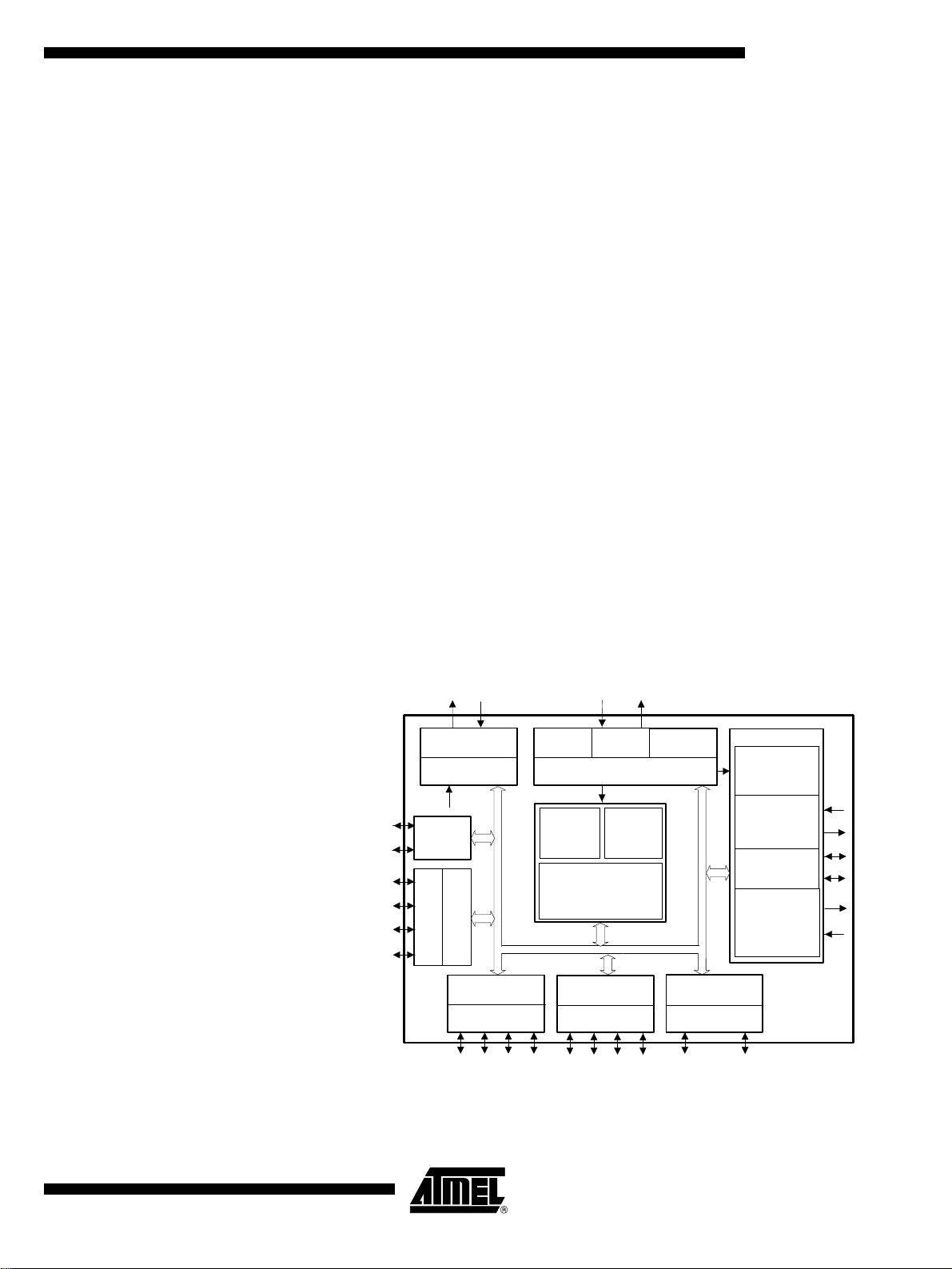

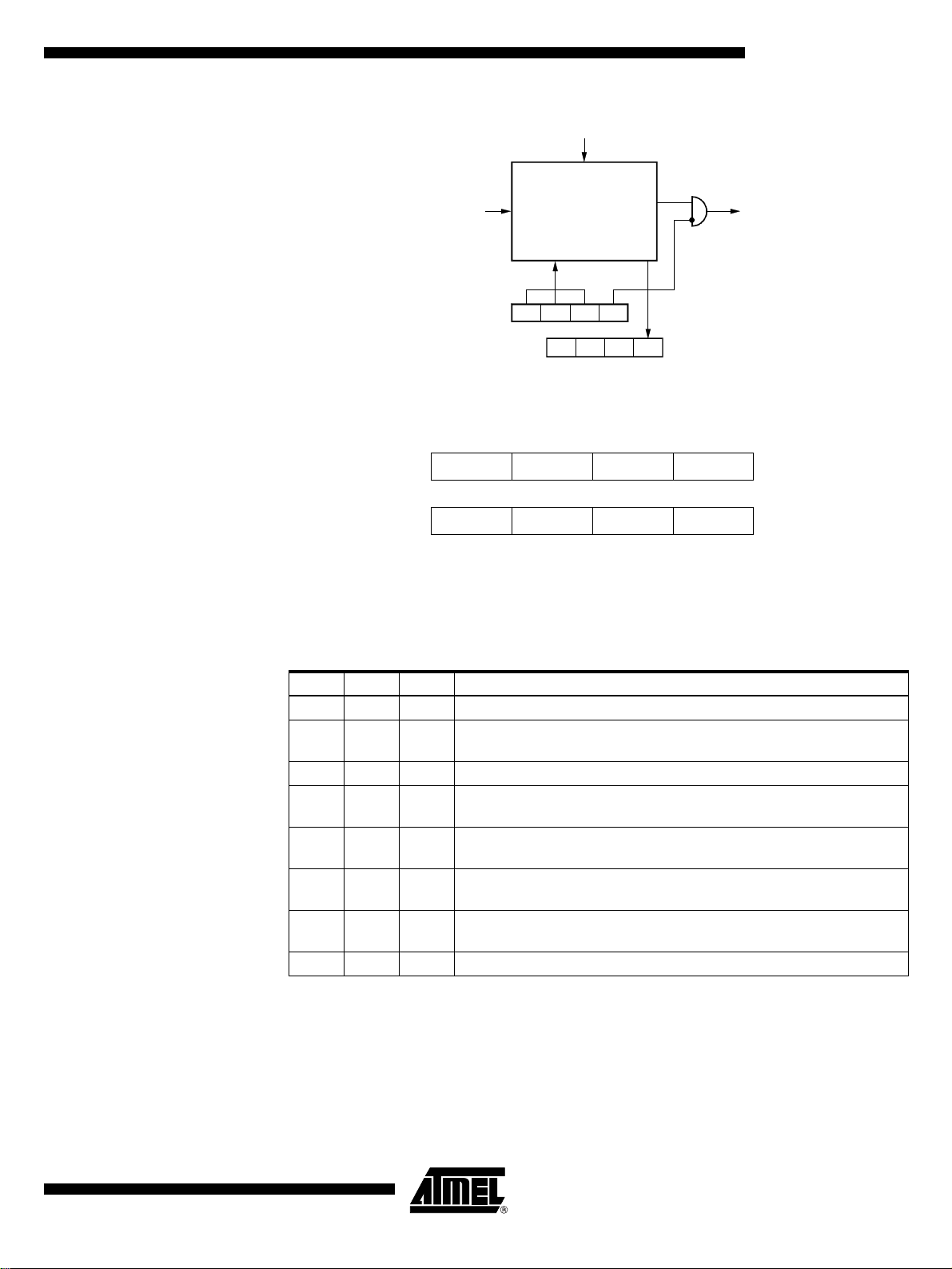

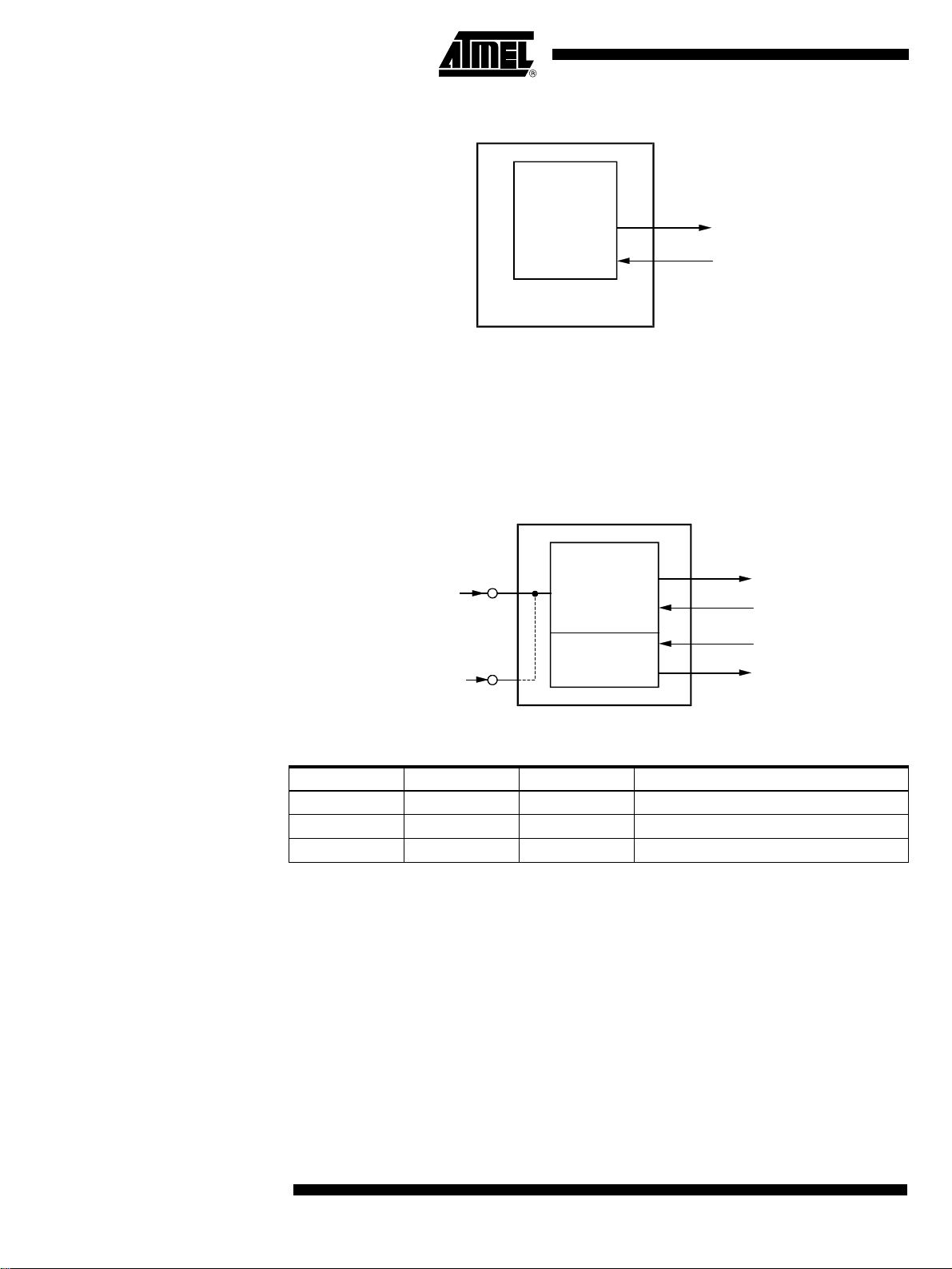

Figure 9. Block Diagram

V

SS

Brown-out prot ect.

RESET

Voltage monitor

External input

VMI

BP10

BP13

BP20/NTE

BP21

BP22

BP23

Port 1

n

o

i

t

c

2

e

t

r

r

i

o

d

P

a

t

a

D

Data direction +

alternate fu nc tion

BP40

INT3

SC BP41

V

DD

Port 4

BP42

T2O

BP43

VMI

T2I SD

INT3

OSC1 OSC2

RC

oscillators

Crystal

oscillators

Clock management

ROM RAM

4 K x 8 bit

MARC4

4-bit CPU core

Data direction +

interrupt control

Port 5

BP51

INT6

BP52

BP50

INT6

256 x 4 bit

INT1

clock input

I/O bus

BP53

INT1

External

Data direction +

alternate function

Port 6

BP60

T3O

UTCM

Timer 1

interval- and

watchdog timer

Timer 2

8/12-bit timer

with modulator

SSI

Serial interface

Timer 3

8-bit

timer / counter

with modulator

and demodulator

BP63

T3I

T2I

T2O

SD

SC

T3O

T3I

4589B–4BMCU–02/03

13

Page 14

Introduction The ATAR862-8 is a member of Atmel’s family of 4-bit single-c hip microcontrol lers. It

contains ROM, RAM, parallel I /O ports, two 8-b it programmable m ultifunction

timer/counters, volt age s upervisor , inte rval ti mer wit h watch dog function and a sophi sticated on-chip clock generation with integrated RC-, 32-kHz and 4-MHz crystal

oscillators.

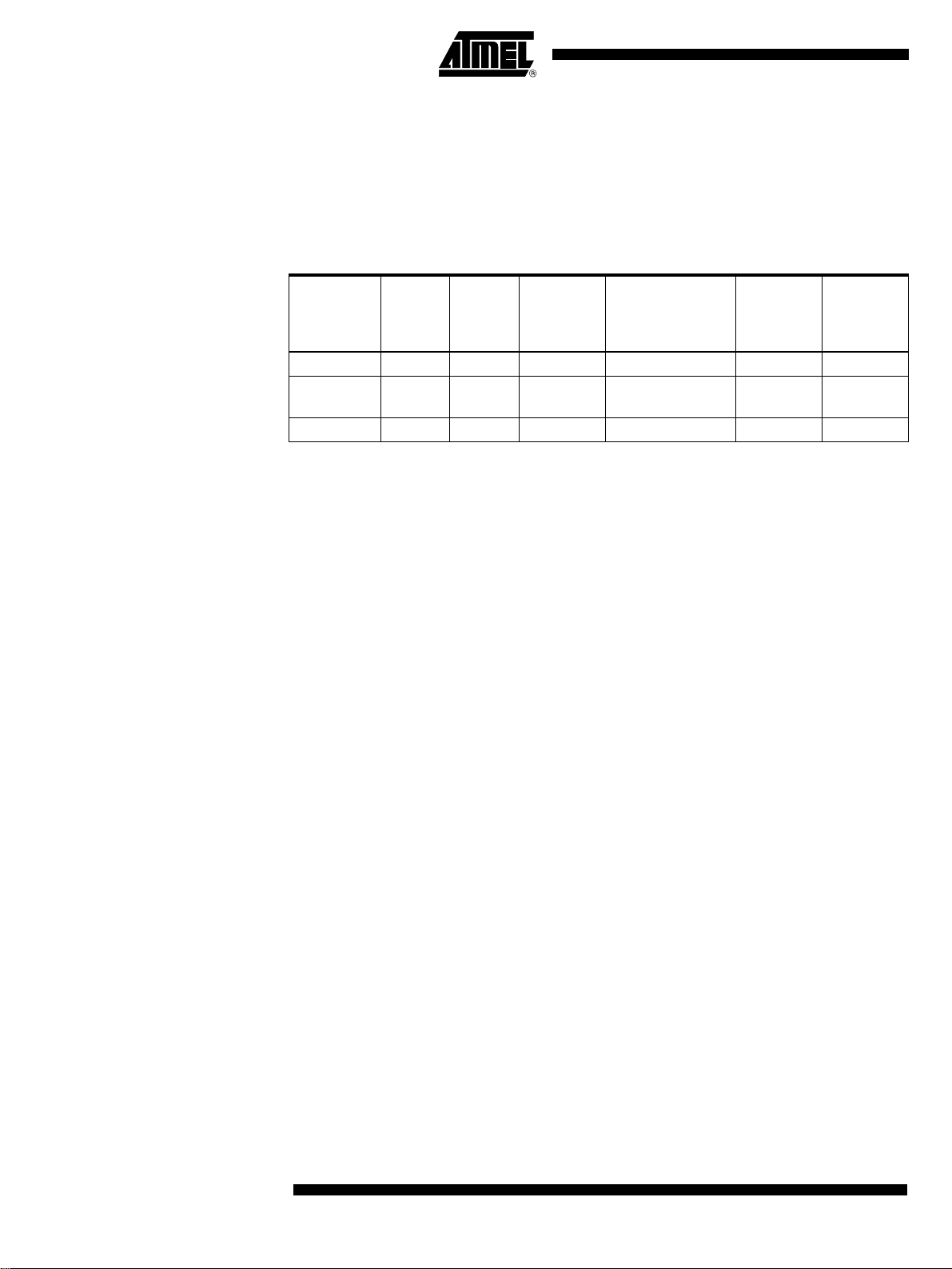

Table 1. Available Variants of M4xCx9x

Version Type ROM E2PROM Peripheral Packages

Flash

device

Production ATAR862 4-Kbyte Mask ROM 64-bytes SSO24

T48C862 4-Kbyte EEPROM 64-bytes SSO24

MARC4 Architecture General Desc ription

The MARC4 microcontroller consists of an advanced stack-based, 4-bit CPU core and

on-chip peripherals . The CPU i s based o n the Harvard ar chit ectur e with ph ysical ly separated program memory (ROM) and data memory (RAM). Three independent buses,

the instruction bus, the memory bus and the I/O bus, are used for parallel communication between ROM, RAM and peripherals. This enhances program execution speed by

allowing both inst ructio n pre fetchi ng, and a si multan eous commu nicat ion to the on -chip

peripheral circuitry. The extremely powerful integr ated interrupt controller with associated eight prioritized interrupt levels supports fast and efficient processing of hardware

events. The MARC4 is designed for the high-level programming language qFORTH.

The core includes both an expressi on and a return stack. This architecture e nables

high-level language programming without any loss of efficiency or code density.

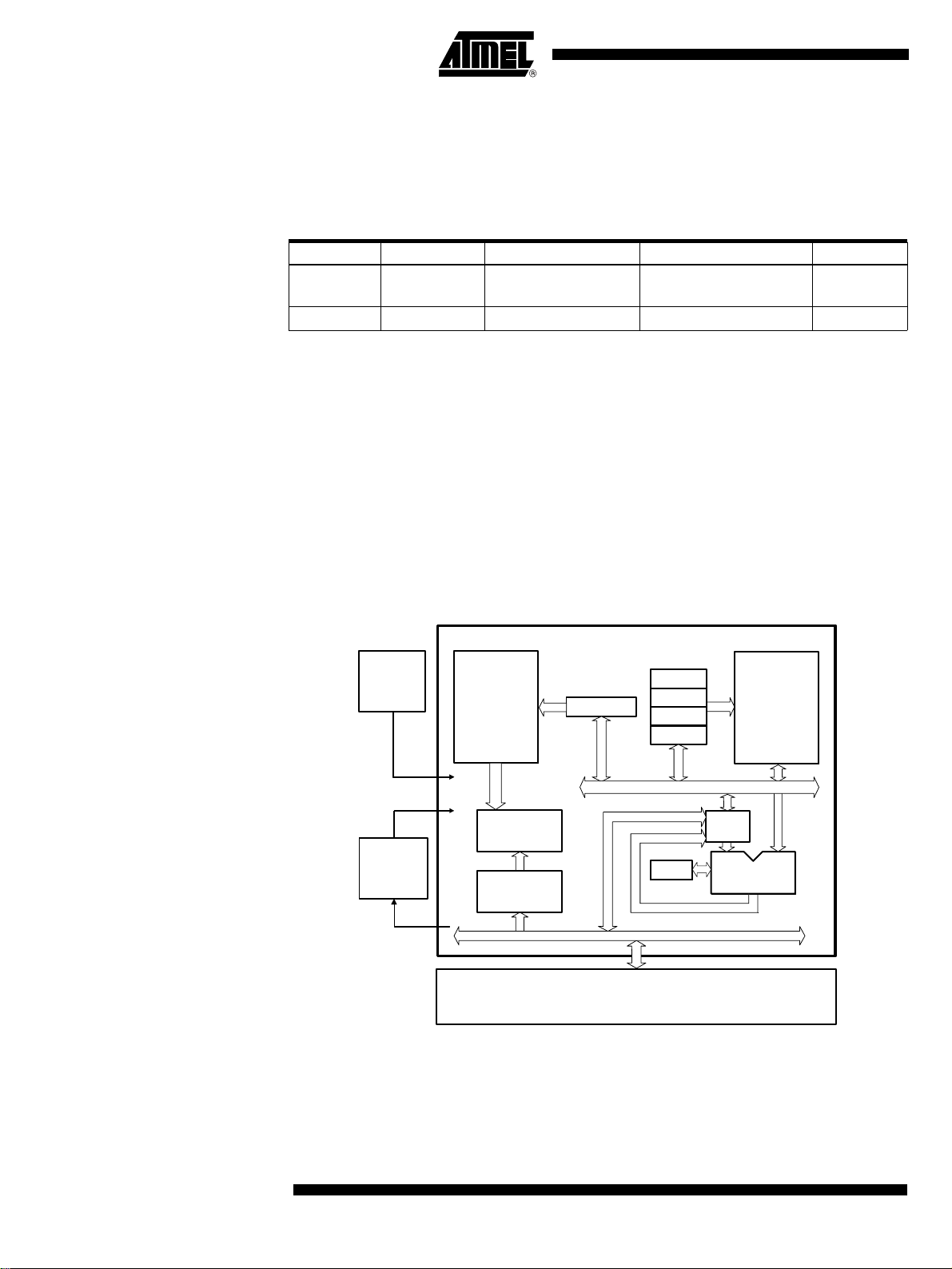

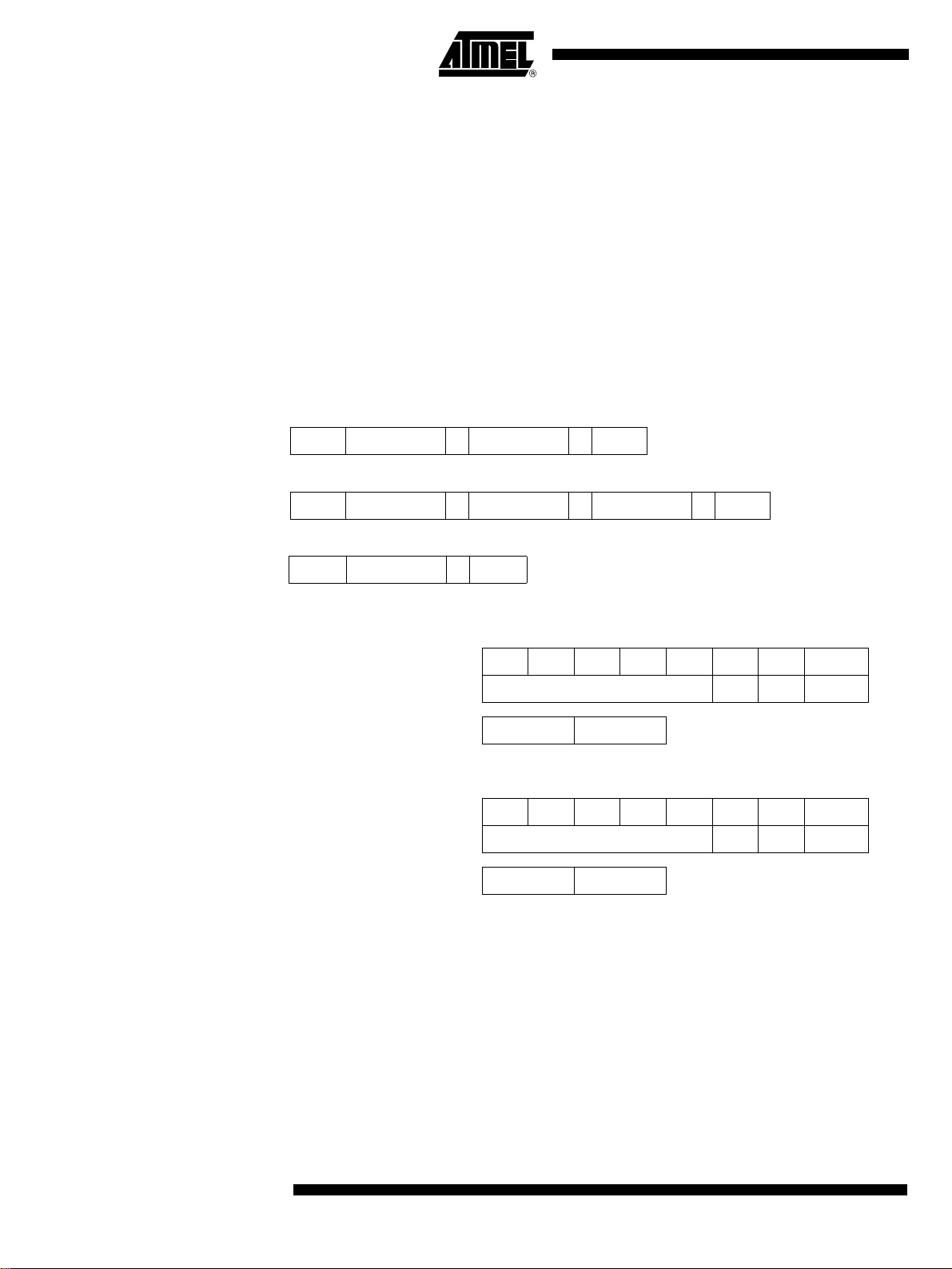

Figure 10. MARC4 Core

MARC4 CORE

SP

RP

CCR

X

Y

RAM

256 x 4-bit

TOS

ALU

Reset

Clock

System

clock

Sleep

Reset

Program

memory

Instruction

bus

Instruction

decoder

Interrupt

controller

PC

Memory bus

I/O bus

Components of MARC4 Core

14

ATAR862-8

On-chip peripheral modules

The core contai ns ROM, RAM, ALU, prog ram cou nter, RAM ad dress r egiste rs, instr uction decoder and interrupt controller. The following sections describe each functional

block in more detail.

4589B–4BMCU–02/03

Page 15

ATAR862-8

ROM The program memory (ROM) is mask programmed with the customer applic ation pro-

gram during the fabrica tion of the micro controller. The ROM is addres sed by a 12-bit

wide program cou nter, thu s pr edefin ing a max imum pr ogram bank s ize of 4 Kbyt es. A n

additional 1-Kbyte of ROM exists, which is rese rved for q ual ity control self-test software

The lowest user ROM address segment is taken up by a 512-byte Zero page which contains predefined start addresses for interrupt service routi nes and special su broutines

accessible with single byte instructions (SCALL).

The corresponding memory map is shown in Figur e 4. Look-up tab les of consta nts can

also be held in ROM and are accessed via the MARC4’s built-in table instruction.

Figure 11. ROM Map of the Microcontroller Block

1F8h

FFFh

7FFh

1FFh

000h

ROM

(4 K x 8 bit)

Zero page

1F0h

1E8h

1E0h

Zero

page

SCALL addresses

020h

018h

010h

008h

000h

1E0h

1C0h

180h

140h

100h

0C0h

080h

040h

008h

000h

INT7

INT6

INT5

INT4

INT3

INT2

INT1

INT0

$RESET

$AUTOSLEEP

RAM The microcontroller block contains 256 x 4-bit wide static random access memory

(RAM), which is used for the expression stack. The return stack and data memory are

used for variables and arrays. The RAM is addressed by any of the four 8-bit wide RAM

address registers SP, RP, X and Y.

Expression Stack The 4-bit wide expression stack is addressed with the expression stack pointer (SP). All

arithmetic, I/O and memory reference operations take their operands, and return their

results to the expression stack. The MARC4 performs the operations with the top of

stack items (TOS and TOS-1). The TOS register contains the top element of the expression stack and works in the same way as an accumulat or. This stack is als o used for

passing parameters betw een sub routi nes and as a sc ratch pad area for temporary storage of data.

Return Stack The 12-bit wide return stack is ad dr es se d by the re tu rn s tac k p oin ter ( RP ) . It i s us ed for

storing return ad dresses of subr outines, interrupt r outines and for keeping l oop index

counts. The return stack can also be used as a temporary storage area.

The MARC4 instructi on se t s up por ts th e e xc ha nge of da ta b etwe en the top el em ents of

the expression stack and the return stack. The two stacks within the RAM have a user

definable location and maximum depth.

4589B–4BMCU–02/03

15

Page 16

Figure 12. RAM Map

FCh

X

Y

RAM

(256 x 4-bit)

Autosleep

FFh

Global

variables

Expression stack

30

TOS

TOS-1

TOS-2

4-bit

SP

SP

RAM address register:

RP

04h

00h

TOS-1

Expression

stack

Return

stack

07h

03h

Global

v

variables

Return stack

011

RP

12-bit

Registers The microcontroll er ha s se ven p rogramm able regis ters a nd o ne co nditio n cod e reg ister

(see Figure 13).

Program Counter (PC) The program counte r is a 12 -bit reg ister which c ontains th e ad dress o f the nex t inst ruc-

tion to be fetched from the ROM. Instructions currently being executed are decoded in

the instruction decoder to determine the internal micro-operations. For linear code (no

calls or branches), the prog ram counte r is increm ented with every instructio n cycle. If a

branch-, call-, return-instruction or an interrupt is executed, the program counter is

loaded with a new address . The program co unter is also used with the tab le instruc tion

to fetch 8-bit wide ROM constants.

Figure 13. Programming Mode l

PC

11

RP

SP

X

Y

7

7

7

TOS

C

CCR

--

0

Program counter

0

00

Return stack pointer

0

Expression stack pointer

0

RAM address register (X)

07

RAM address register (Y)

03

Top of stack register

03

B

Condition code register

I

Interrupt enable

Branch

Reserved

Carry / borrow

16

ATAR862-8

4589B–4BMCU–02/03

Page 17

ATAR862-8

RAM Address Registers The RAM is addressed with the four 8-bit wide RAM address registers: SP, RP, X and Y.

These registers allow access to any of the 256 RAM nibbles.

Expression Stack Pointer (SP) The stack poi nter conta ins the add ress of the next-to-t op 4-bit it em (TOS-1 ) of the

expression stack. The pointer is automatically pre-incremented if a nibble is moved onto

the stack or post-decremented if a nibble is removed from the stack. Every post-decrement operation moves the item (TOS-1) to the TOS register before the SP is

decremented. Afte r a reset, the stac k pointer ha s to be initia lized with ">SP S0" t o allocate the start address of the expression stack area.

Return Stack Pointer (RP) The return stack pointer points to the top element of the 12-bit wide r eturn stack. T he

pointer automatically pre-increments if an element is moved onto the stack, or it postdecrements if an element is removed from the stack. The return stack pointer increments and decrements in steps of 4. This means that every time a 12-bit element is

stacked, a 4-bit RAM location is left unwritten. This location is used by the qFORTH

compiler to allocate 4-bit variables. After a reset the return stack pointer has to be initialized via ">RP FCh".

RAM Address Registers (X and Y)

Top of Stack (TOS) The top of stack register is the ac cumul ator of the MA RC4. Al l arit hmetic/lo gic, m emory

Condition Code Register (CCR)

Carry/Borrow (C) The carry/borrow flag indicat es that the bor rowi ng o r car ry ing out of a ri thm eti c logi c unit

Branch (B) The branch flag co ntrol s the con di tio nal progr a m br an ch ing . S hou ld the br anc h flag has

Interrupt Enable (I) The interrupt enable flag globally enables or disables the triggering of all interrupt rou-

The X and Y registers are used to add ress any 4-bit item in the RAM. A fetch ope ratio n

moves the addressed nibble onto the TOS. A store operation moves the TOS to the

addressed RAM location. By using either the pre-increment or post-decrement addressing mode arrays in the RAM can be compared, filled or moved.

reference and I/O operati ons use thi s regis ter. The TOS regis ter rec eives da ta from th e

ALU, ROM, RAM or I/O bus.

The 4-bit wide condition code register contains the branch, the carry and the interrupt

enable flag. The se bits ind icate the curren t stat e of the CPU . The CCR flags are se t or

reset by ALU oper ations. The i nstructions SET_BCF, T OG_BF, CCR! and DI allow

direct manipulation of the condition code register.

(ALU) occurred during the last arithmetic operation. During shift and rotate operations,

this bit is used as a fifth bit. Boolean operations have no effect on the C-flag.

been set by a previous instruction, a conditional branch will cause a jump. This flag is

affected by arithmetic, logic, shift, and rotate operations.

tines with the excepti on of the no n-maska ble rese t. After a rese t or while ex ecuting th e

DI instruction, the interrupt enable flag is reset, thus disabling all interrupts. The core will

not accept any further interrupt requests until the interrupt enable flag has been set

again by either executing an EI or SLEEP instruction.

4589B–4BMCU–02/03

17

Page 18

ALU The 4-bit ALU performs all the arithmetic, logical, shift and rotate operations with the top

two elements of the expression stack (TOS and TOS-1) and returns the result to the

TOS. The ALU operations affects the carry/borrow and branch flag in the condition code

register (CCR).

Figure 14. ALU Zero-address Operations

RAM

SP

TOS-1

TOS-2

TOS-3

TOS-4

TOS

ALU

CCR

I/O Bus The I/O ports and the registers of the peripheral module s ar e I/O mappe d. Al l com mun i-

cation between the c ore a nd th e on -chip per ipher als ta ke place via th e I/O bu s a nd th e

associated I/O control. With the MARC4 IN and OUT instructions, the I/O bus allows a

direct read or write access to one of the 16 primary I/O addresses. More about the I/O

access to the o n-chi p perip hera ls is des cribed in the sec tion "Peri pher al Mo dules" . Th e

I/O bus is internal and is not accessible by the customer on the final microcontroller

device, but it is use d as the inter face for the MA RC4 emulat ion (see als o the sectio n

"Emulation").

Instruction Set The MARC4 instruct ion set is optimized for the high level progra mming language

qFORTH. Many MARC4 instructions are qFORTH words. This enables the compiler to

generate a fast and compact progr am code. The CP U has an inst ructi on pipelin e allowing the controller to prefetch an instruction from ROM at the same time as the present

instruction is being executed. The MARC4 is a zero-address machine, the instructions

contain only the oper ation to be p erfor med an d no so urce or de stina tion ad dress f ields .

The operations are impli citl y pe rf ormed on the data placed on the stack. There are oneand two-byte instructions which are executed within 1 to 4 machine cycles. A MARC4

machine cycle is made up of two system clock cycles (SYSCL). Most of the instructions

are only one byte long and are executed in a single machine cycle. For more information

refer to the "MARC4 Programmer’s Guide".

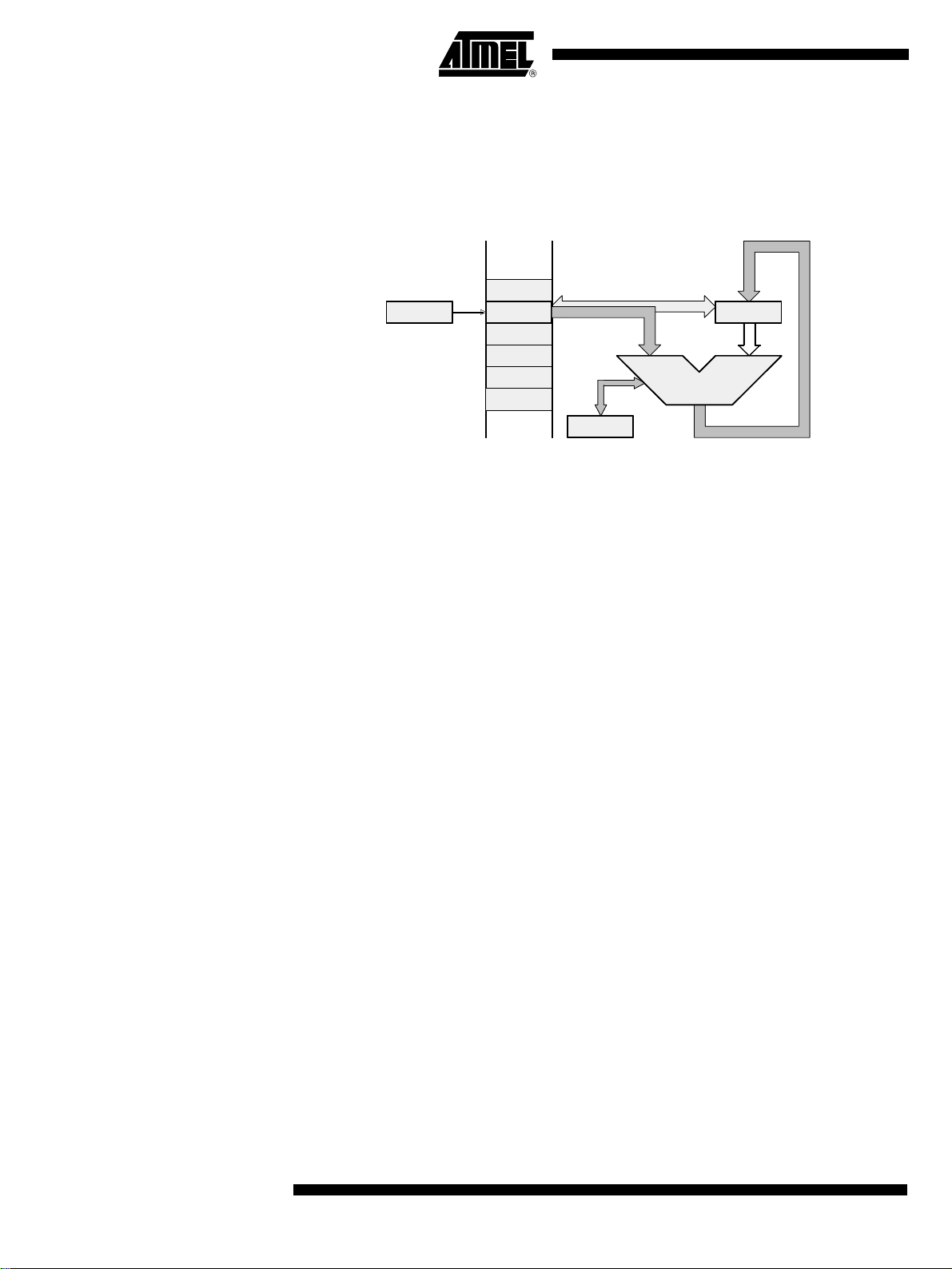

Interrupt Structure The MARC4 can handle interrupts with eight different priority levels. They can be gener-

ated from the internal and external interrup t sources or by a softwar e interrup t from the

CPU itself. Each interrupt level has a hard-wired priority and an associated vector for the

service routine in the ROM (see Table 1). The programmer can postpone the processing

of interrupts by resetting the interrupt enable flag (I) in the CCR. An interrupt occurrence

will still be registered, but the interrupt routine only started after the I-flag is set. All interrupts can be masked, and the priority individually software configured by programming

the appropriate control register of the interrupting module (see section "Peripheral

Modules").

18

ATAR862-8

4589B–4BMCU–02/03

Page 19

ATAR862-8

Interrupt Processing For processing the eight interrupt levels, the MARC4 includes an interrupt controller with

two 8-bit wide interrup t pending and inter rupt active registers. The interr upt control ler

samples all interrupt requests during every non-I/O instruction cycle and latches these in

the interrupt pending register. If no higher priority interrupt is present in the interrupt

active register, it signals the CPU to interrupt the current program execution. If the interrupt enable bit is set, the processor enters an interrupt acknowledge cycle. During this

cycle a short call (S CALL) ins truction to the serv ice routin e is exec uted and the current

PC is saved on the return stack. An interrupt service routine is completed with the RTI

instruction. T his inst ruct io n rese ts t he c orres pondi ng b its in t he i nterru pt pendi ng/act ive

register and fetches the return address from th e return stack to the prog ram counter .

When the interrupt enable flag is reset (triggering of interrupt routines is disabled), the

execution of new interrupt service routines is inhibited but not the logging of the interrupt

requests in the inte rrupt pe nding re giste r. The e xecution of the i nterrup t is d elayed u ntil

the interrupt enable flag is set again. Note that interrupts are only lost if an interrupt

request occurs wh ile the corre sponding bi t in the pendin g register is s till set (i.e ., the

interrupt service routine is not yet finished).

It should be noted that automatic stacking of the RBR is not carried out by the hardware

and so if ROM banking is used, the RBR must be stacked on the expression stack by

the application program and res tored before the RTI. After a mast er reset (power-o n,

brown-out or watchdog reset), the interru pt enable flag and the inter rupt pending and

interrupt active register are all reset.

Interrupt Latency The interrup t latency is the time from the occur renc e of the i nte rrup t to th e i nter rupt se r-

vice routine being activated. This is extremely short (taking between 3 to 5 machine

cycles depending on the state of the core).

Figure 15. Interrupt Handling

INT7

7

6

5

4

3

Priority level

2

1

0

Main /

Autosleep

INT5

INT5 active

INT3

INT3 active

INT7 active

RTI

INT2

RTI

INT2 pending

SWI0

INT2 active

INT0 pending

RTI

RTI

INT0 active

RTI

Main /

Autosleep

4589B–4BMCU–02/03

Time

19

Page 20

Table 2. Interrupt Priority Table

Interrupt Priority ROM Address Interrupt Opcode Function

INT0 Lowest 040h C8h (SCALL 040h) Software interrupt (SWI0)

INT1 | 080h D0h (SCALL 080h)

INT2 | 0C0h D8h (SCALL 0C0h) Timer 1 interrupt

INT3 | 100h E8h (SCALL 100h)

INT4 | 140h E8h (SCALL 140h) Timer 2 interrupt

INT5 | 180h F0h (SCALL 180h) Timer 3 interrupt

INT6 | 1C0h F8h (SCALL 1C0h)

INT7 Highest 1E0h FCh (SCALL 1E0h) Voltage monitor (VM) interrupt

External hardware interrupt, any edge at BP52 or

BP53

SSI interrupt or external hardware interrupt at BP40

or BP43

External hardware interrupt, at any edg e at BP50 or

BP51

Table 3. Hardware Interrupts

Interrupt Mask

Interrupt

INT1 P5CR

INT2 T1M T 1IM Timer 1

INT3 SISC SIM SSI buffer full/empty or BP40/BP43 interrupt

INT4 T2CM T2IM Timer 2 compare match/overflow

T3CM1

INT5

INT6 P5CR

INT7 VCM VI M External/in ternal v ol tage monitoring

T3CM2

T3C

P52M1, P52M2

P53M1, P53M2

T3IM1

T3IM2

T3EIM

P50M1, P50M2

P51M1, P51M2

Interrupt SourceRegister Bit

Any edge at BP52

any edge at BP53

Timer 3 compare register 1 match

Timer 3 compare register 2 match

Timer 3 edge event occurs (T3I)

Any edge at BP50,

any edge at BP51

Software Interrupts The programmer ca n generate interrupts by using the software interrupt ins truction

(SWI), which is supporte d in qFO RTH by pre defined m acros na med SW I0...SW I7. Th e

software triggered interrupt operates exactly like any hardware triggered interrupt. The

SWI instruction takes the top two elements from the expression stack and writes the corresponding bits via the I/O bus to th e i nter rup t pending register. Therefore, by us in g th e

SWI instruction, interrupts can be re-prioritized or lower priority processes scheduled for

later execution.

Hardware Interrupts In the microcontroller block, there are el even har dw ar e i nterr upt so ur ce s with s eve n d if-

ferent levels. Each source can be masked individually by mask bits in the corresponding

control registers. An overview of the possible hardware configurations is shown in

Table 3.

20

ATAR862-8

4589B–4BMCU–02/03

Page 21

ATAR862-8

Master Reset The master reset forces the CPU into a well-defined condition. It is unmaskable and is

activated independent of the current program state. It can be triggered by either initial

supply power-up, a short collapse of the power supply, brown-out detection circuitry,

watchdog time-out, or an externa l input cl ock supe rvisor stage (see Figure 9). A mas ter

reset activation will rese t the i nterr upt enab le fl ag, the in ter rupt pe ndi ng r egis ter and th e

interrupt active register. During the power-on reset, phase, the I/O bus control signals

are set to reset m ode, th ereby , init ializi ng al l on- chip periphe rals . All b i-di rection al por ts

are set to input mode.

Attention: During any reset phase, the BP20/NTE input is driven towards V

additional internal strong pull-up transistor. This pin must not be pulled down to V

by an

DD

SS

dur-

ing reset by any external circuitry representing a resistor of less than 150 kW.

Releasing the reset res ults in a sh ort call inst ructi on (opc ode C1h) to the R OM add ress

008h. This activates the initializ ation routine $RESET which in turn has to initia lize all

necessary RAM variables, stack pointers and peripheral configuration registers (see

Table 6).

Figure 16. Reset Configuration

V

DD

Pull-up

CL

NRST

Reset

timer

res

CL=SYSCL/4

Power-on

reset

Brown-out

detection

Internal

reset

V

DD

V

SS

V

DD

V

SS

Po we r-on Reset and Brown-out Detection

4589B–4BMCU–02/03

Watch-

dog

Ext. clock

supervisor

res

CWD

ExIn

The microcontrolle r bloc k has a ful ly in tegr ate d po wer -on r eset an d br own -o ut de tect io n

circuitry. For reset generation no external components are needed.

These circuits ensure that the core is held in the reset state until the minimum operating

supply voltage has been reached. A reset condition will also be generated should the

supply voltage drop momentarily below the minimum operating l evel except when a

power-down mode is activated (the core is in SLEEP mode and the peripheral clock is

stopped). In this power-down mode the brown-out detection is disabled.

Two values for the brown-out voltage threshold are programmable via the BOT-bit in the

SC-register.

21

Page 22

A power-on reset pulse i s generat ed by a VDD rise across the default BOT voltage level

(1.7 V). A brown-out reset pulse is generated when V

falls below the br own-o ut volt -

DD

age threshold. T wo values for t he brown-o ut volt age thres hold are programma ble via

the BOT-bit in the SC-register. When the controller runs in the upper supply voltage

range with a high system clock frequency, the high threshold must be used. When it

runs with a lower system c lock freq uency , the lo w thresho ld and a wider su pply v oltag e

range may be chosen. F or further details , see the e lectrical speci fication and the SCregister description for BOT programming.

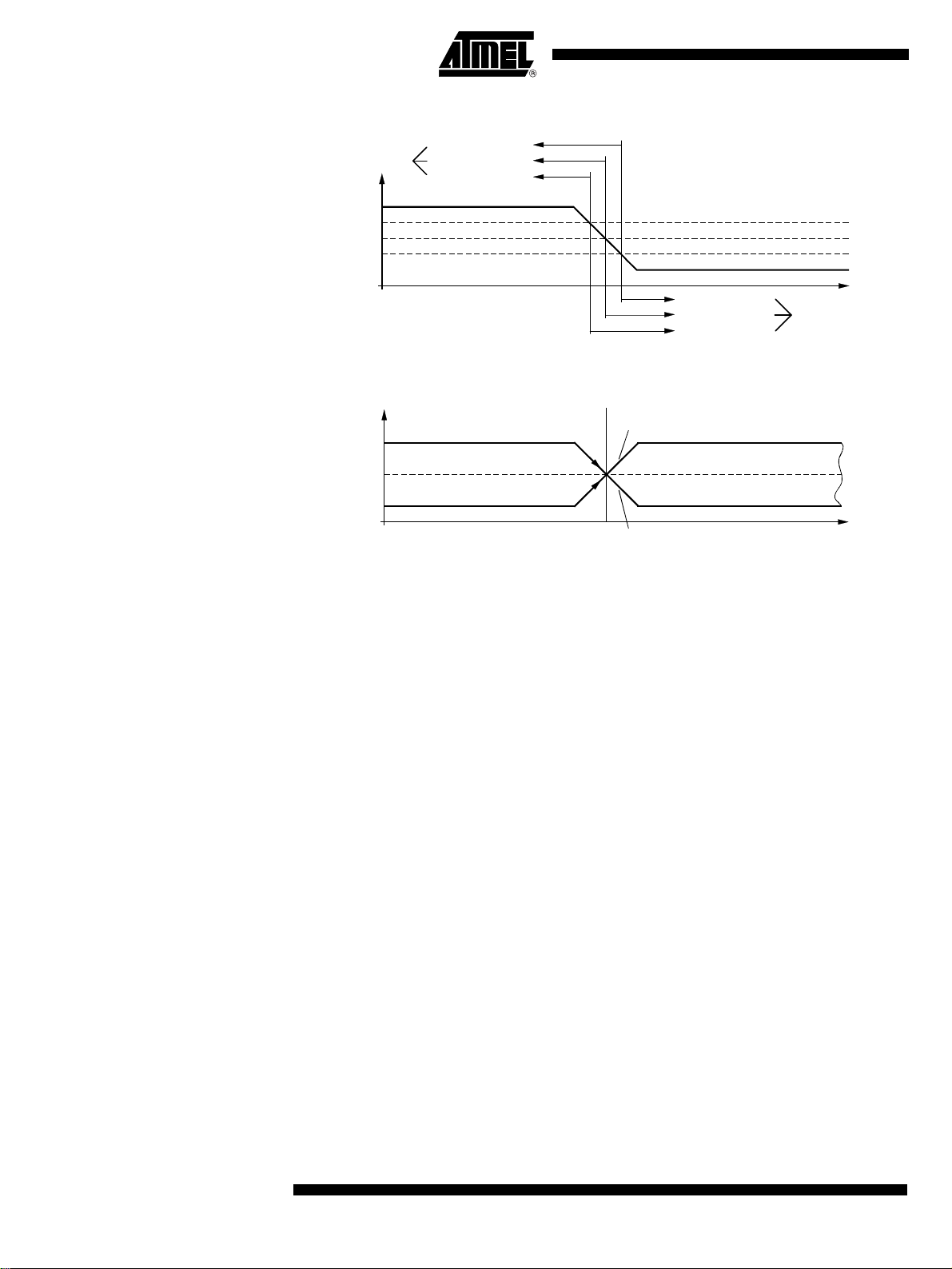

Figure 17. Brown-out Detection

V

DD

2.0 V

1.7 V

t

CPU

Reset

CPU

Reset

BOT = '1'

BOT = '0'

d

t

d

t

t

d

td= 1.5 ms (typically)

BOT = 1, low brown-out voltage threshold 1.7 V (is reset value).

BOT = 0, high brown-out voltage threshold 2.0 V.

Watchdog Reset The watchdog’s function can be enabled at the WDC-register and triggers a reset with

every watchdog counter overflow. To suppress the watchdog reset, the watchdog

counter must be regularly reset by reading the watchdog register address (CWD). The

CPU reacts in exactly the same manner as a reset stimulus from any of the above

sources.

External Clock Supervisor The exte rnal i nput clo ck su per vis or func ti on c an be enab led if the ex te rnal i npu t cl ock is

selected within the CM- and SC-reg isters of the clock module . Th e CPU reacts in

exactly the same manner as a reset stimulus from any of the above sources.

Voltage Monitor The voltage monitor consists of a comparator with internal voltage reference. It is used

to supervise the supply voltage or an external voltage at the VMI-pin. The comparator

for the supply voltage has three internal programmable thresholds one lower threshold

(2.2 V), one middle threshold (2.6 V) and one higher threshold (3.0 V). For external voltages at the VMI-pin, the comparator threshold is set to V

indicates if the supervised voltage is below (VMS = 0) or above (VMS = 1) this threshold. An interrupt can be g enerated wh en the V MS-b it is set or res et to de tect a risin g or

falling slope. A voltage monitor interrupt (INT7) is enabled when the interrupt mask bit

(VIM) is reset in the VMC-register.

= 1.3 V. The VMS-bit

BG

22

ATAR862-8

4589B–4BMCU–02/03

Page 23

Figure 18. Voltage Monitor

BP41/

VMI

VMC :

Voltage monitor

IN

VM2

VM1 VM0 VIM

ATAR862-8

V

DD

OUT

INT7

Voltage Monitor Control/ Status Register

VMST :

- - res

VMS

Primary register address: "F’hex"

Bit 3Bit 2Bit 1Bit 0

VMC: Write VM2 VM1 VM0 VIM Reset value: 1111b

VMST: Read – – reserved VMS Reset value: xx11b

VM2: Voltage monitor Mode bit 2

VM1: Voltage monitor Mode bit 1

VM0: Voltage monitor Mode bit 0

VM2 VM1 VM0 Function

1 1 1 Disable voltage monitor

110

101Not allowed

100

011

010

001

000Not allowed

External (VIM-input), internal reference thresho ld (1.3 V), interrupt

with negative slope

External (VMI-input), internal reference thresho ld (1.3 V), interrupt

with positive slope

Internal (supply voltage), high threshold (3.0 V), interrupt with

negative slope

Internal (supply voltage), middle threshold (2.6 V), interrupt with

negative slope

Internal (supply voltage), low threshold (2.2 V), interrupt with

negative slope

4589B–4BMCU–02/03

VIM Voltage Interrupt Mask bit

VIM = 0, voltage monitor interrupt is enabled

VIM = 1, voltage monitor interrupt is disabled

VMS Voltage Monitor Status bit

VMS = 0, the voltage at the comparator input is below V

VMS = 1, the voltage at the comparator input is above V

Ref

Ref

23

Page 24

Figure 19. Internal Supply Voltage Supervisor

Low threshold

VMS = 1

V

DD

3.0 V

2.6 V

2.2 V

Middle threshold

High threshold

Low threshold

Middle threshold

High threshold

VMS = 0

Figure 20. External Input Voltage Supervisor

VMI

Negative slope

VMS = 1

1.3 V

VMS = 0

Positive slope

Internal reference level

Interrupt positive slope

VMS = 1

VMS = 0

Interrupt negative slope

t

Clock Generation

Clock Module The microcontroller block contains a clock module with 4 different internal osc illator

types: two RC-oscillators, one 4-MHz crystal oscillator and one 32-kHz crystal oscillator.

The pins OSC1 and OSC2 are the interf ace to c onnect a crysta l either to th e 4-MHz, or

to the 32-kHz crystal oscillator. OSC1 can be used as input for external clocks or to connect an external tri mming res isto r for the R C-o scill ator 2. All ne cess ary ci rcuitr y, exce pt

the crystal and the t rimm ing r esis tor, i s i nte grated on -chi p. O ne of t hes e o scil lat or ty pes

or an external input clock can be selected to generate the system clock (SYSCL).

24

ATAR862-8

In applications that do not require exact timing, it is possible to use the fully integrated

RC-oscillator 1 without any external components. The RC-oscillator 1 center frequency

tolerance is better than ± 50%. The RC-oscillator 2 is a trimmable oscillator whereby the

oscillator frequency can be trimmed with an external resistor attached between OSC1

and V

. In this configuration, the RC-oscillator 2 frequency can be maintained stable

DD

with a tolerance of ± 15% over the full operating temperature and voltage range.

The clock module is programmable via software with the clock management register

(CM) and the system configuration register (SC). The requir ed oscillator c onfiguration

can be selected with the OS1-bit and the OS0-bit in the SC-register. A programmable

4-bit divider stage allows the adjustment of the system clock speed. A special feature of

the clock management is that an external oscillator may be used and switched on and

off via a port pin for the power-down mode. Before the external clock is switched off, the

internal RC-oscillator 1 must be s elected with the CCS-bit and then the SLEE P mode

may be activated. In this state an interrupt can wake up the controller with the RC-oscillator, and the external oscillator can be activated and selected by software. A

synchronization stage avoids too short clock periods if the clock source or the clock

speed is changed. If an external input clock is selected, a supervisor circuit monitors the

external input and gen er ate s a har dwa re reset if the external clock sou rce f ail s or dr ops

below 500 kHz for more than 1 ms.

4589B–4BMCU–02/03

Page 25

Figure 21. Clock Module

ATAR862-8

OSC1

OSC2

*

*

*

mask option

Oscin

Oscout

Ext. clock

ExIn

RC oscillator2

R

Trim

4-MHz oscillator

Oscin

Oscout

32-kHz oscillator

Oscin

Oscout

BOT - - - OS1 OS0

SC:

Table 4. Clock Modes

Mode OS1 OS0

111

201

310

400

ExOut

Stop

RCOut2

Stop

4Out

Stop

32Out

RC-oscillator 1

(internal)

RC-oscillator 1

(internal)

RC-oscillator 1

(internal)

RC-oscillator 1

(internal)

RC

oscillator 1

IN1

Osc-Stop

RCOut1

ControlStop

NSTOP CCS CSS1 CSS0CM:

IN2

Sleep

WDL

Cin

/2 /2 /2 /2

Clock Source for SYSCL

External input clock C

RC-oscillator 2 with

external trimming

resistor

4-MHz oscillator C

32-kHz oscillator 32 kHz

Divider

SYSCL

Cin/16

32 kHz

SUBCL

Clock Source

for SUBCLCCS = 1 CCS = 0

/16

in

C

/16

in

/16

in

Oscillator Circuits and External Clock Input Stage

RC-oscillator 1 Fully Integrated

The clock module generates two output clocks. One is the system clock (SYSCL) and

the other the periphery (SUBCL). The SYSCL can supply the core and the peripherals

and the SUBCL can supply only the peripherals with cloc ks. The modes for clock

sources are programmable with the OS1-bit and OS0-bit in the SC-register and the

CCS-bit in the CM-regi ste r.

The microcontroller block se ries consi sts of fou r different in ternal os cillators: t wo RCoscillators, one 4-MHz crystal oscillator, one 32-kHz crystal oscillator and one external

clock input stage.

For timing insensitive applications, it is possible to use the fully integrated RC

oscillator 1. It operates without any external components and saves additional costs.

The RC-oscillator 1 center frequency tolerance is better than ±50% over the full temperature and voltage range. The bas ic center frequency of the RC-oscillato r 1 is

f

» 3.8 MHz. The RC oscillator 1 is selected by default after power-on reset.

O

4589B–4BMCU–02/03

25

Page 26

Figure 22. RC-oscillator 1

RC

oscillator 1

RcOut1

Stop

Control

RcOut1

Osc-Stop

External Input Clock The OSC1 or OSC2 (mask option) can be driven by an external clock source provided it

meets the specified duty cycle, rise and fall times and input level s. Additionally, the

external clock stage conta ins a superv isory circuit for the input clock . The supervi sor

function is controlled via the OS1, OS0-bit in the SC-register and the CCS-bit in the CMregister. If the external input clock is missing for more than 1 ms and CCS = 0 is set in

the CM-register, the supervisory circuit generates a hardware reset.

Figure 23. External Input Clock

RC-oscillator 2 with External Trimming Resistor

Ext. input clock

OSC1

Ext.

Clock

or

OSC2

Ext.

Clock

OS1 OS0 CCS Supervisor Reset Output (Res)

110 Enable

111 Disable

x 0 x Disable

ExIn

Clock monitor

ExOut

Stop

RcOut1

Osc-Stop

CCS

Res

The RC-oscillator 2 is a high resolution trimmable oscillator whereby the oscillator frequency can be tri mmed with an exte rnal resistor betw een OSC1 and V

. In this

DD

configuration, the RC-oscillator 2 frequency can be maintained stable with a tolerance of

± 10% over the full operating temperature and a voltage range V

from 2.5 V to 6.0 V.

DD

For example: An output frequency at the RC-oscillator 2 of 2 MHz can be obtained by

connecting a resistor R

=360kW (see Figure 16).

ext

26

ATAR862-8

4589B–4BMCU–02/03

Page 27

ATAR862-8

Figure 24. RC-oscillator 2

V

DD

R

ext

OSC1

OSC2

4-MHz Oscillator The microcontroller block 4-MHz oscillator options need a crystal or ceramic resonator

connected to the OSC1 and OSC2 pins to establish oscillation. All the necessary oscillator circuitry is integrated, except the actual crystal, resonator, C3 and C4.

Figure 25. 4-MHz Crystal Oscillator

RC

oscillator 2

R

Trim

RcOut2

Stop

RcOut2

Osc-Stop

OSC1

XTAL

4 MHz

OSC2

*

mask option

Figure 26. Ceramic Resonator

C3

OSC1

OSC2

C4

*

mask option

Cer.

Res

*

C1

*

C2

*

C1

*

C2

Oscin

4-MHz

oscillator

Oscout

Oscin

oscillator

Oscout

4-MHz

4Out

Stop

4Out

Stop

4Out

Osc-Stop

4Out

Osc-Stop

32-kHz Oscillator Some appli catio ns requ ire long- term tim e kee ping o r lo w res olution t iming . In thi s c ase,

an on-chip, low power 32-kHz cr ystal oscillator can be use d to generate both the

SUBCL and the SYSCL. In this mode, power consumption is greatly reduced. The

32-kHz crystal oscillator can not be stopped while the power-down mode is in operation.

27

4589B–4BMCU–02/03

Page 28

Figure 27. 32-kHz Crystal Oscillator

OSC1

XTAL

32 kHz

OSC2

*

mask option

*

C1

*

C2

Oscin

32-kHz

oscillator

Oscout

32Out

32Out

Clock Management The clock management register controls the system clock divider and synchronization

stage. Writing to this register triggers the synchronization cycle.

Clock Management Register (CM)

Bit 3 Bit 2 Bit 1 Bit 0

CM: NSTOP CCS CSS1 CSS0 Reset value: 1111b

Auxiliary register address: "3"hex

NSTOP Not STOP peripheral clock

NSTOP = 0, stops the peripheral clock while the core is in SLEEP mode

NSTOP = 1, enables the peripheral clock while the core is in SLEEP mode

CCS Core Clock Select

CCS = 1, the internal RC-oscillator 1 generates SYSCL

CCS = 0, the 4-MHz crystal oscillator, the 32-kHz crystal oscillator, an external

clock source or the internal RC-oscillator 2 with the external resistor at OSC1

generates SYSCL dependent on the setting of OS0 and OS1 in the system

configuration register

CSS1 Core Speed Select 1

CSS0 Core Speed Select 0

CSS1 CSS0 Divider Note

0016–

1 1 8 Reset value

104–

012–

28

ATAR862-8

4589B–4BMCU–02/03

Page 29

ATAR862-8

System Configuration Register (SC)

Primary register address: "3"hex

Bit 3Bit 2Bit 1Bit 0

SC: write BOT – OS1 OS0 Reset value: 1x11b

BOT Brown-Out Threshold

BOT = 1, low brown-out voltage threshold (1.7 V)

BOT = 0, high brown-out voltage threshold (2.0 V)

OS1 Oscillator Select 1

OS0 Oscillator Select 0

Mode OS1 OS0 Input for SUBCL Selected Oscillators

111 C

201 C

310 C

400 32 kHz

Note: If bit CCS = 0 in the CM-register, the RC-oscillator 1 always stops.

16 RC-oscillator 1 and external input clock

in/

/16 RC-oscillator 1 and RC-oscillator 2

in

/16

in

RC-oscillator 1 and 4-MHz crystal

oscillator

RC-oscillator 1 and 32-kHz crystal

oscillator

Power-down Modes The sleep mode is a shut-down condition which is used to reduce the average system

power consumption in applications where the microcontroller is not fully utilized. In this

mode, the system clock is stopped. The sleep mode is entered via the SLEEP instruction. This instruction sets the interrupt enable bit (I) in the condition code register to

enable all interrup ts and stops the core. Durin g the sleep mode the periphe ral modules

remain active and are able to gene rate interrupt s. The microco ntroller exits the s leep

mode by carrying out any interrupt or a reset.

The sleep mode c an only be kept whe n none of th e interr upt pend ing or ac tive re gister

bits are set. The application of the $AUTOSLEEP routine ensures the correct function of

the sleep mode. For standard applications use the $AUTOSLEEP r outine to enter the

power-down mode. Using the S LE EP in str uc tion i ns tea d of th e $A UTO SLE E P follo win g

an I/O instruction requ ires to ins ert 3 non-I/O inst ructi on cyc les (for exam ple N OP N OP

NOP) between the IN or OUT command and the SLEEP command.

The total power consumption is directly proportional to the active time of the microcontroller. For a rough estimation of the expected average system current consumption, the

following formula should be used:

I

(VDD,f

total

IDD depends on VDD and f

syscl

) = I

syscl

+ (IDD ´ t

Sleep

active/ttotal

)

4589B–4BMCU–02/03

29

Page 30

The microcontroller block has various power-down modes. During the sleep mode the

clock for the MARC4 core is stopped. With the NSTOP-bit in the clock management register (CM), it is programmable if the clock for the on-chip peripherals is active or stopped

during the slee p mode. I f the cl ock for t he core a nd the pe ripheral s is stop ped, the

selected oscillator is switched off. An exception is the 32-kHz oscillator, if it is selected it

runs continuously independent of the NSTOP-bit. If the oscillator is stopped or the

32-kHz oscillator is selected, power consumption is extremely low.

Table 5. Power-down Modes

RC-oscillator 1

Brown-

CPU

Mode

Active RUN NO Active RUN RUN YES

Power-

down

SLEEP SLEEP YES STOP STOP RUN STOP

Note: 1. Osc-Stop = SLEEP and NSTOP and WDL

Core

SLEEP NO Active RUN RUN YES

Osc-

Stop

(1)

out

Function

RC-oscillator 2

4-MHz

Oscillator

32-kHz

Oscillator

External

Input

Clock

Peripheral Modules

Addressing Peripheral s Accessing the peripheral modules takes place via the I/O bus (see Figure 20). The IN or

OUT instructions allow direct addressing of up to 16 I/O modul es. A dual register

addressing scheme has be en ado pted to ena ble dir ect a ddressi ng of the prim ary regi ster. To address the auxiliary register, the access must be switched with an auxiliary

switching m odul e. Thus , a si ngle IN (or OU T) to the module address will read (or write

into) the module primar y register . Accessin g the auxili ary registe r is perform ed with the

same instruction preceded by writing the module address into the auxiliary switching

module. Byte wide registers are accessed by multiple IN- (or OUT-) instructions. For

more complex peripheral modules, with a larger number of registers, extended addressing is used. In this case, a bank of up to 16 subport registers are indirectly addressed

with the subport address. The first OUT-instruction writes the subport address to the

subaddress register, the second IN- or OUT-instruction reads data from or writes data to

the addressed subport.

30

ATAR862-8

4589B–4BMCU–02/03

Page 31

Figure 28. Example of I/O Addressing

ATAR862-8

Module ASW

Auxiliary Switch

Module

Primary Reg.

Example of

qFORTH

program code

Module M1

(Address Pointer)

Subaddress Reg.

1

Indirect Subport Access

(Subport Register Write)

1 Addr. (SPort) Addr. (M1) OUT

2 SPort _Data Addr. (M1) OUT

(Subport Register Read)

1 Addr. (SPort) Addr. (M1) OUT

2 Addr. (M1) IN

(Subport Register Write Byte)

1 Addr. (SPort) Addr. (M1) OUT

2 SPort _Data(lo) Addr. (M1) OUT

2 SPort _Data(hi) Addr. (M1) OUT

(Subport Register Read Byte)

1 Addr. (SPort) Addr. (M1) OUT

2 Addr. (M1) IN (hi)

2 Addr. (M1) IN (lo)

Bank of

Primary Reg.

Subport Fh

Subport Eh

Subport 1

Subport 0

2

Module M2 Module M3

Aux. Reg.

5

Primary Reg.

3

4

I/O bus

Dual Register Access

(Primary Register Write)

3 Prim._Data Addr. (M2) OUT

(Auxiliary Register Write)

4 Addr. (M2) Addr. (ASW) OUT

5 Aux._Data Addr. (M2) OUT

(Primary Register Read)

3 Addr. (M2) IN

(Auxiliary Register Read)

4 Addr. (M2) Addr. (ASW) OUT

5 Addr. (M2) IN

(Auxiliary Register Write Byte)

4 Addr. (M2) Addr. (ASW) OUT

5 Aux._Data (lo) Addr. (M2) OUT

5 Aux._Data (hi) Addr. (M2) OUT

Primary Reg.

6

to other modules

Single Register Access

(Primary Register Write)

6 Prim._Data Addr.(M3) OUT

(Primary Register Read)

6 Addr. (M3) IN

Addr.(ASW) = Auxiliary Switch Module address

Addr.(Mx) = Module Mx address

Addr.(SPort) = Subport address

Prim._Data = Data to be written into Primary Register

Aux._Data = Data to be written into Auxiliary Register

Prim._Data(lo)= Data to be written into Auxiliary Register (low nibble)

4589B–4BMCU–02/03

Prim._Data(hi) = Data to be written into Auxiliary Register (high nibble)

SPort_Data(lo) = Data to be written into SubPort (low nibble)

SPort_Data(hi) = Data to be written into SubPort (high nibble)

(lo) = SPort_Data (low nibble)

(hi) = SPort_Data (high nibble)

31

Page 32

Table 6. Peripheral Address es

Port Address Name

1 P1DAT W/R 1xx1b Port 1 - data register/input data M3

2 P2DAT W/R 1111b Port 2 - data register/pin data M2

Auxiliary P2CR W 1111b Port 2 - control register M2

3 SC W 1x11b System configuration register M3

CWD R xxxxb Watchdog reset M3

Auxiliary CM W/R 1111b Clock management register M 2

4 P4DAT W/R 1111b Port 4 - data register/pin data M2

Auxiliary P4CR W 1111 1111b Port 4 - control register (byte) M2

5 P5DAT W/R 1111b Port 5 - data register/pin data M2

Auxiliary P5CR W 1111 1111b Port 5 - control register (byte) M2

6 P6DAT W/R 1xx1b Port 6 - data register/pin data M2

Auxiliary P6CR W 1111b Port 6 - control register (byte) M2

7 T12SUB W – Data to Timer 1/2 subport M1

Subport address

0 T2C W 0000b Timer 2 control register M1

1 T2M1 W 1111b Timer 2 mode register 1 M1

2 T2M2 W 1111b Timer 2 mode register 2 M1

3 T2CM W 0000b Timer 2 compare mode register M1

4 T2CO1 W 1111b Timer 2 compare register 1 M1

5 T2CO2 W 1111 1111b Timer 2 compare register 2 (byte) M1

6– – – Reserved –

7– – – Reserved –

8 T1C1 W 1111b Timer 1 control register 1 M1

9 T1C2 W x111b Timer 1 control register 2 M1

A WDC W 1111b Watchdog control register M1

B-F – – – Reserved –

8 ASW W 1111b Auxiliary/switch register ASW

9 STB W xxxx xxxxb Serial transmit buffer (byte) M2

SRB R xxxx xxxxb Serial receive buffer (byte) M2

Auxiliary SIC1 W 1111b Serial interface control register 1 M2

A SISC W/R 1x11b Serial interface status/control register M2

Auxiliary SIC2 W 1111b Serial interface control register 2 M2

B T3SUB W/R – Data to/from Timer 3 subport M1

Subport address

0 T3M W 1111b Timer 3 mode register M1

1 T3CS W 1111b Timer 3 clock select register M1

2 T3CM1 W 0000b Timer 3 compare mode register 1 M1

3 T3CM2 W 0000b Timer 3 compare mode register 2 M1

4 T3CO1 W 1111 1111b Timer 3 compare register 1 (byte) M1

4 T3CP R xxxx xxxxb Timer 3 capture register (byte) M1

5 T3CO2 W 1111 1111b Timer 3 compare register 2 (byte) M1

6-F – – – Reserved –

C T3C – W 0000b Timer 3 control register M3

T3ST – R x000b Timer 3 status register M3

D – – – – Reserved –

E – – – – Reserved –

F VMC – W 1111b Voltage monitor control register M3

VMST – R xx11b Voltage monitor status register M3

Write/

Read Reset Value Register Function Module Type

32

ATAR862-8

4589B–4BMCU–02/03

Page 33

ATAR862-8

Bi-directional Ports With the exception of Port 1 and Port 6, all other ports (2, 4 and 5) are 4 bits wide. Port 1

and Port 6 have a data width of 2 bits (bit 0 and bit 3 ). All ports may be used for data

input or output. Al l ports ar e equippe d with Schmi tt trigg er inputs an d a variet y of mask

options for open- dra in, o pen-sou rce, full- compl ement ary ou tput s, pu ll-up and p ull- down

transistors. All Port Data Registers (PxDAT) are I/O mapped to the primary address register of the respective port address and the Port Control Register (PxCR), to the

corresponding auxiliary register.

There are five different directional ports available:

Port 1 2-bit wide bi-directional port with automatic full bus width direction switching.

Port 2 4-bit wide bitwise-programmable I/O port.

Port 5 4-bit wide bitwise-programmable bi-directional port with optional strong

pull-ups and programmable interrupt logic.

Port 4 4-bit wide bitwise-programmable bi-directional port also provides the I/O

interface to Timer 2, SSI, voltage monitor input and external interrupt input.

Port 6 2-bit wide bitwise-programmable bi-directional port also provides the I/O

interface to Timer 3 and external interrupt input.

Bi-directional Port 1 In Port 1 th e data direct ion r egister is not indepe ndentl y sof tware pr ogramma ble, th e

direction of the complete port being s witched a utomatically when an I/ O instructio n

occurs (see Figure 21 ). The por t is sw itched to output mode via an OU T i ns tru ction and

to input via an IN instruction. The data written to a port will be stored into the output data

latches and appears immediately at the port pin following the OUT instruction. After

RESET all output l atches are set to "1 " and the port is switched to input mod e. An IN

instruction reads the condition of the associated pins.

Note: Care must be taken when switching the bi-directional port from output to input. The

capacitive pin loading at this port in conjunction with the high resistance pull-ups may

cause the CPU to read the contents of the output data register rather than the exter nal

input state. To avoid this, one of the following programming techniques should be used:

Use two IN-instructions and DROP the first data nibble. The first IN switches the port

from output to input and the DROP removes the first invalid nibble. The second IN reads

the valid pin state.

Use an OUT-instruction f oll o wed by an IN-instruction. Via the OUT-instruction, th e ca pac itive load is charged or discharged depending on the optional pull-up/pull-down

configurati on. W rite a "1" for pin s with pull- up res istor s and a "0" for pins with pull- down

resistors.

4589B–4BMCU–02/03

33

Page 34

Figure 29. Bi-directional Port 1

V

DD

I/O Bus

*

Static

pull-up

BP1y

Static

pull-down

OUT

IN

Master re set

(Data out)

D

P1DATy

R

Reset

(Direction)

SQQ

R

NQ

*) Mask options

Switched

*

pull-up

**

V

DD

*

Switched

pull-down

Bi-directional Port 2 As all othe r bi- direct ional ports , this por t in clud es a bitwise pro grammab le Control Reg-

ister (P2CR), which enables the individual programmi ng of each port bit as input or

output. It also opens up the possibility of reading the pin condition when in output mode.

This is a useful feature for self testing and for serial bus applications.

Port 2, however, has an increased drive capability and an additional low resistance pullup/-down transistor mask option.

Care should be taken connecting external components to BP20/NTE. During any reset

phase, the BP20/NTE input is driven towards V

transistor. This pin must not be pulled down (active or passi ve) to V

by an additional internal strong pull-up

DD

during reset by

SS

any external cir cuitry r epresen ting a res istor of l ess than 15 0 kW. This prevents the circuit from unintended switching to test mode enable through the application circuitry at

pin BP20/NTE. Resistors less than 150 kW might lead to an undefined state of the internal test logic thus disabling the application firmware.

To avoid any conflict with the optional internal pull-down transistors, BP20 handles the

pull-down options in a different way than all other ports. BP20 is the only port that

switches off the pull-down transistors during reset.

Figure 30. Bi-directional Port 2

V

I/O Bus

I/O Bus

Master reset

I/O Bus

(Data out)

D

P2DATy

S

S

D

P2CRy

(Direction)

Switched

pull-up

*

*

Q

V

*

*

Q

Mask options

*

DD

*

Switched

pull-down

Static

Pull-up

*

BP2y

Static

*

Pull-down

DD

34

ATAR862-8

4589B–4BMCU–02/03

Page 35

ATAR862-8

Port 2 Data Register (P2DAT) Primary register address: "2"hex

Bit 3 * Bit 2 Bit 1 Bit 0

P2DAT3 P2DAT2 P2DAT1 P2DAT0 Reset value: 1111b

* Bit 3 -> MSB, Bit 0 -> LSB

Port 2 Control Register (P2CR) Auxiliary register address: "2"hex

Bit 3Bit 2Bit 1Bit 0

P2CR3 P2CR2 P2CR1 P2CR0 Reset value: 1111b

Value: 1111b means all pins in input mode

Code

3 2 1 0 Function

x x x 1 BP20 in input mode

x x x 0 BP20 in output mode

x x 1 x BP21 in input mode

x x 0 x BP21 in output mode

x 1 x x BP22 in input mode

x 0 x x BP22 in output mode

1 x x x BP23 in input mode

0 x x x BP23 in output mode

Bi-directional Port 5 As all othe r bi- direct ional ports , this por t in clud es a bitwise pro grammab le Control Reg-

ister (P5CR), which allows the individual programming of each port bit as input or

output. It also opens up the possibility of reading the pin condition when in output mode.

This is a useful feature for self testing and for serial bus applications.

The port pins can also be used as external interrupt inputs (see F igure 23 and Figure

24). The interru pts (INT1 and INT 6) can be ma sked or inde pendent ly co nfigured to trigger on either edge. The interrupt configuration and port direction is controlled by the Port

5 Control Register (P5CR). An additional low resistance pull-up/-down transistor mask

option provides an internal bus pull-up for serial bus applications.

The Port 5 Data Register (P5DAT) is I/O mapped to the primary address r egister of

address "5"h and the Port 5 Control Register (P5CR) to the corresponding auxiliary register. The P5CR is a byte-wide register and is configured by writing first the low nibble

and then the high nibble (see section "Addressing Peripherals").

35

4589B–4BMCU–02/03

Page 36

Figure 31. Bi-directional Port 5

I/O Bus

(Data out)

I/O Bus

Master reset

IN enable

D

P5DATy

S

Q

Mask options

Figure 32. Port 5 External Interrupts

BP52

Data in

Bidir. Port

IN_Enable

I/O-bus

V

DD

*

INT1 INT6

Switched

pull-up

*

*

V

DD

Static

pull-up

*

BP5y

V

*

*

DD

*

Switched

pull-down

I/O-bus

Static

*

Pull-down

Data in

Bidir. Port

IN_Enable

BP51

BP53

Data in

Bidir. Port

IN_Enable

Decoder Decoder Decoder Decoder

P53M2 P53M1 P52M2 P52M1 P51M2 P51M1 P50M2 P50M1

P5CR:

Data in

Bidir. Port

IN_Enable

BP50

Port 5 Data Register (P5DAT) Primary register address: "5"hex

Bit 3Bit 2Bit 1Bit 0

P5DAT3 P5DAT2 P5DAT1 P5DAT0 Reset value: 1111b

Port 5 Control Register (P5CR)

Auxiliary register address: "5"hex

Byte Write

Bit 3Bit 2Bit 1Bit 0

First write cycle P51M2 P51M1 P50M2 P50M1 Reset value: 1111b

Bit 7Bit 6Bit 5Bit 4

Second wr ite cycle P53M2 P53M1 P52M2 P52M1 Reset value: 1111b

36

ATAR862-8

4589B–4BMCU–02/03

Page 37