Page 1

Features

General

• High-performance, Low-power secureAVR

– 135 Powerful Instructions (Most Executed in a Single Clock Cycle)

• Low Power Idle and Power-down Modes

• Bond Pad Locations Conforming to ISO 7816-2

• ESD Protection to ± 6000V

• Operating Ranges: 1.62 to 5.5V

• Compliant with GSM, 3GPP and EMV 2000 Specifications; PC Industry Compatible

• Available in Wafers, Modules, and Industry-standard Packages

™

RISC Architecture

Memory

• 96K Bytes of ROM Program Memory plus 32KBytes of ROM with specific access

• 18K Bytes of EEPROM, Including 128 OTP Bytes and 384-byte Bit-addressable Area

– 1 to 64-byte Program / Erase

– 2 ms Program / 2 ms Erase

– Typically More than 500,000 Write/Erase Cycles at a Temperature of 25

– 10 Years Data Retention

• 4K Bytes of RAM

o

C

Peripherals

• One ISO 7816 Controller

– Up to 625 kbps at 5 MHz

– Compliant with T=0 and T=1 Protocols

• One I/O Port

• Programmable Internal Oscillator (up to 20 MHz for Internal CPU Clock)

• Two 16-bit Timers

• Random Number Generator (RNG)

• 2-level, 7-vector Interrupt Controller

• Hardware DES and Triple DES DPA Resistant

• Checksum Accelerator

• CRC 16 & 32 Engine (Compliant with ISO/IEC 3309)

Secure

Microcontroller

for Smart Cards

AT90SC

9618RT

Summary

Security

• Dedicated Hardware for Protection Against SPA/DPA Attacks

• Advanced Protection Against Physical Attack, Including Active Shield

• Environmental Protection Systems

• V oltage Monitor

• Frequency Monitor

• Temperature Monitor

• Light Protection

• Secure Memory Management/Access Protection (Supervisor Mode)

Certification

• EAL4+

• VISA

• CAST

6555AS–SPD–15May0 7

Note: This is a summary document. A complete document will be

available under NDA. For more information, please contact your

local Atmel sales office.

Page 2

AT90SC9618RT

Development Tools

• Voyager Emulation Platform (ATV4) to Support Software Development

• IAR Embedded Workbench

• Software Libraries and Application Notes

®

V3.20 Debugger or Atmel’s AVR Studio® Version 4.07 or Above

Description

The AT90SC9618RT is a low-power, high-performance, 8/16-bit microcontroller with ROM program memory and EEPROM

data memory, based on the secureAVR RISC architecture. By executing powerful instructions in a single clock cycle, the

AT90SC9618RT achi eves throughpu ts close to 1 M IPS pe r MHz . Its Harv ard ar chitec ture in cludes 32 ge neral p urpos e

working regi sters d irectl y connec ted to th e ALU, al lowin g two ind epende nt regis ters t o be acces sed in on e sing le ins truction executed in one clock cycle.

The AT90SC9618RT uses the secureAVR that allows the linear addressing of up to 8M bytes of code and up to 16M bytes

of data as well as a number of new functional and security features.

The AT90SC9618RT includes 18K bytes of Atmel’s high density, non volatile memory.

Additional security features include power and frequency protection logic, logical scrambling on program data and

addresses, Power Analysis countermeasures and memory accesses controlled by a supervisor mode.

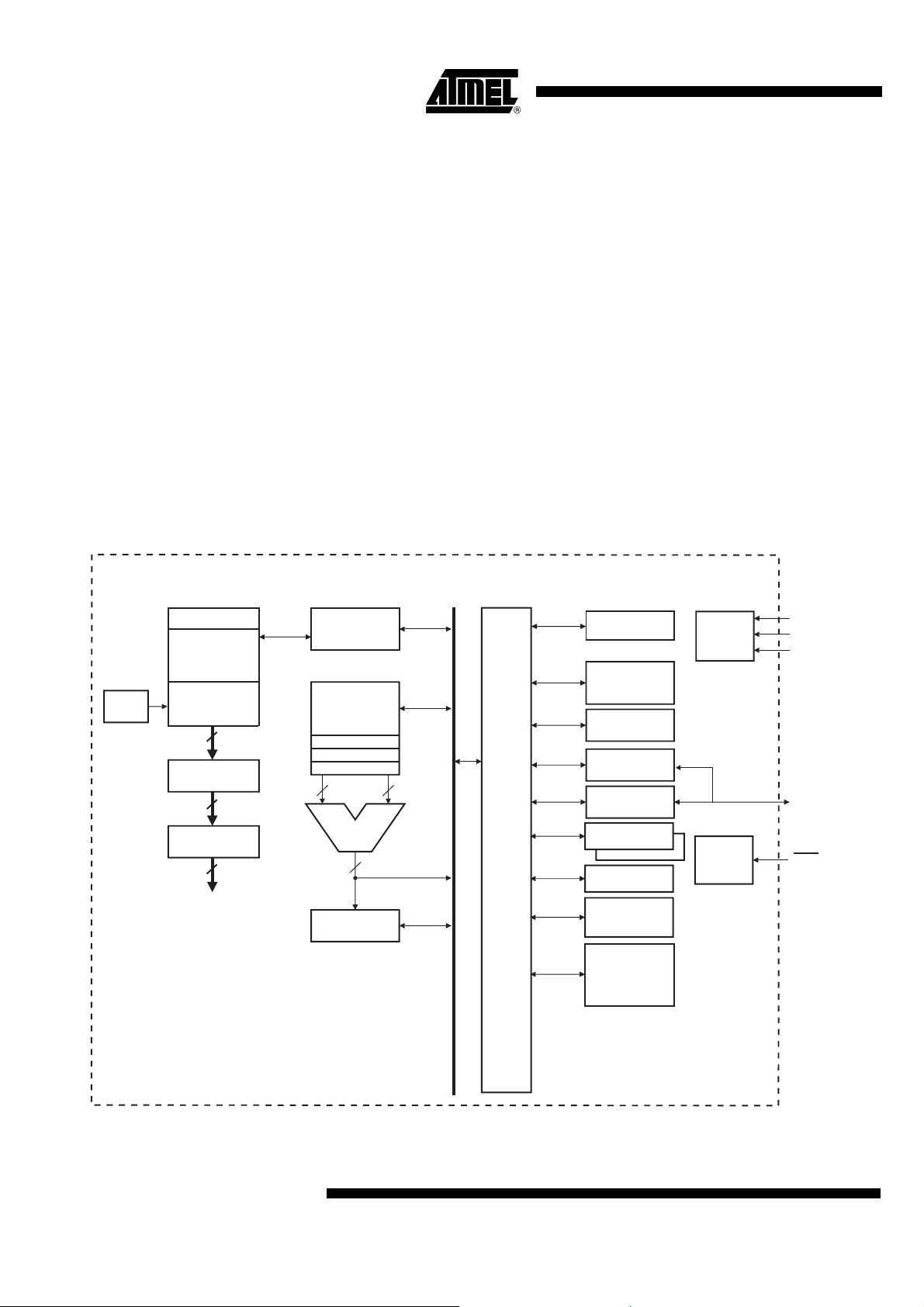

Figure 1 shows the AT90SC9618RT secureAVR RISC Architecture.

Figure 1. AT90SC9618RT secureAVR RISC Architecture

Data B us

8-bit

PC

OTP

EEPROM

User Memory

Program

Memory

16

Instruction

Reg ist er

16

Instruction

Decoder

16

Control

Lines

Access

Control

General

Purpose

Reg ist ers

X

Y

Z

88

ALU

8

St at us

Reg ist er

Access

Control

RNG

RAM

Data Memory

Interrupt

Unit

IS O 7816

Controller

IS O 7816

I/O Port 0

Timer

DE S

DPA C ounter

measures

CRC and

Checksum

Accelerator

Secu re

Control

Reset

Circuit

CLK

GND

VCC

IN/OUT0

RST

2

6555AS–SPD–15May07

Page 3

Atmel Corporation Atmel Operations

2325 Orchard Parkway

San Jose, CA 95131, USA

Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

Regional Headquarters

Europe

Atmel Sarl

Route des Arsenaux 41

Case Postale 80

CH-1705 Fribourg

Switzerland

Tel: (41) 26-426-5555

Fax: (41) 26-426-5500

Asia

Room 1219

Chinachem Gol den P laza

77 Mody Road Tsimshatsui

East Kowloon

Hong Kong

Tel: (852) 2721-9778

Fax: (852) 2722-1369

Japan

9F, Tonetsu Shinkawa Bldg.

1-24-8 Shin kawa

Chuo-ku, Tokyo 104-0033

Japan

Tel: (81) 3-3523-3551

Fax: (81) 3-3523-7581

Memory

2325 Orchard Parkway

San Jose, CA 95131, USA

Tel: 1(408) 441-0311

Fax: 1(408) 436-4314

Microcontrollers

2325 Orchard Parkway

San Jose, CA 95131, USA

Tel: 1(408) 441-0311

Fax: 1(408) 436-4314

La Chantrerie

BP 70602

44306 Nantes Cedex 3, France

Tel: (33) 2- 40-1 8-18- 18

Fax: (33) 2- 40-18- 19-6 0

ASIC/ASSP/Secure Products

Zone Industrielle

13106 Rousset Cedex, France

Tel: (33) 4- 42-5 3-60- 00

Fax: (33) 4- 42-53- 60-0 1

1150 East Cheyenne Mtn. Blvd.

Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300

Fax: 1(719) 540-1759

Scottish Enterprise Technology Park

Maxwell Building

East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000

Fax: (44) 1355-242-743

RF/Automotive

Theresienstrasse 2

Postfach 3535

74025 Heilbro nn, Ge rmany

Tel: (49) 71-31-67-0

Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd.

Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300

Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom

Avenue de Rochepleine

BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00

Fax: (33) 4- 76-58- 34-8 0

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any

intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-

TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY

WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR

PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT

OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no

representations or warranties with respect to the accuracy or completen ess of the contents of this document and reserves the right to make changes to specifications

and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel’s products are not

intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2007. All rights reserved. Atmel®, logo and combinations thereof, and others are registered trademarks. Everywhere You

SM

, and others are the trademarks of A tmel Corporation or its subsidiaries. Ot her terms and product names may be trademark s of others .

Are

Printed on recycled paper.

6555AS–SPD–15May07

Loading...

Loading...