Page 1

Features

• 80C52X2 Core (6 Clocks per Instruction)

– Maximum Core Frequency 40 MHz in X1 Mode

– Dual Data Pointer

– Full-duplex Enhanced UART (EUART)

– Three 16-bit Timer/Counters: T0, T1 and T2

– 256 Bytes of Scratchpad RAM

• 32-Kbyte On-chip Flash In-System Programming through USB or UART

• 4-Kbyte EEPROM for Boot (3-Kbyte) and Data (1-Kbyte)

• On-chip Expanded RAM (XRAM): 1024 Bytes

• USB Module with Interrupt on Transfer Completion

– Endpoint 0 for Control Transfers: 32-byte FIFO

– 6 Programmable Endpoints with In or Out Directions and with Bulk, Interrupt or

Isochronous Transfers

• Endpoint 1, 2, 3: 32-byte FIFO

• Endpoint 4, 5: 2 x 64-byte FIFO with Double Buffering (Ping-pong Mode)

• Endpoint 6: 2 x 512-byte FIFO with Double Buffering (Ping-pong Mode)

– Suspend/Resume Interrupts

– Power-on Reset and USB Bus Reset

– 48 MHz DPLL for Full-speed Bus Operation

– USB Bus Disconnection on Microcontroller Request

• 5 Channels Programmable Counter Array (PCA) with 16-bit Counter, High-speed

Output, Compare/Capture, PWM and Watchdog Timer Capabilities

• Programmable Hardware W atchdog T imer (One-time Ena bled with Reset-out): 50 ms to

6s at 4 MHz

• Keyboard Interrupt Interface on Port P1 (8 Bits)

• SPI Interface (Master/Slave Mode)

• 34 I/O Pins

• 4 Direct-drive LED Outputs with Programmable Current Sources: 2-6-10 mA Typical

• 4-level Priority Interrupt System (11 sources)

• Idle and Power-down Modes

• 0 to 32 MHz On-chip Oscillator with Analog PLL for 48 MHz Synthesis

• Voltage Regulator and Reference Output: 3.3V/4 mA

• Low Power Voltage Range

– 3.0V to 3.6V

– 30 mA Max Operating Current (at 40 MHz)

– 100 µA Max Power-d own Current

• Self-powered USB Voltage Range (Not Available on First Version)

– 3.6V to 5.5V

– 30 mA Max Operating Current (at 40 MHz)

– 200 µA Max Power-d own Current

• Commercial and Industrial Temperature Range

• Packages: PLCC52, VQFP64, MLF48, SO28

8-bit Flash

Microcontroller

with Full Speed

USB Device

AT89C5131

Rev. 4136A–USB–03/03

Page 2

Description AT89C5131 is a high-performance Flash version of the 80C51 single-chip 8-bit micro-

controllers with full speed USB functions.

AT89C5131 features a full-speed USB module compatible with the USB specifications

Version 1.1 and 2.0. This module integrates the USB transceivers with a 3.3V voltage

regulator and the Serial Interface Engine (SIE) with Digital Phase Locked Loop and

48 MHz clock recovery. USB Event detection logic (Reset and Suspend/Resume) and

FIFO buffers supporting the mandatory control Endpoint (EP0) and up to 6 versatile

Endpoints (EP1/EP2/EP3/EP4/EP5/EP6) with minimum software overhead are also part

of the USB module.

AT89C5131 retains the features of the Atmel 80C52 with extended Flash capacity (32Kbyte), 256 bytes of intern al RAM, a 4-level in terrup t system , two 16- bit timer /coun ters

(T0/T1), a full duplex enhanced UART (EUART) and an on-chip oscillator.

In addition, AT89C 5131 has a n on-chip e xpanded RAM of 1024 bytes (XRAM) , a dualdata pointer, a 16-bi t up/do wn Timer (T2), a Prog ramma ble Counte r Arr ay (PCA ), up to

4 programmable LED current sources, a programmable hardware watchdog and a

power-on reset.

AT89C5131 has tw o soft war e- sele cta bl e m ode s of r e duc ed ac tivi ty for fu rther r ed uct io n

in power consumption . In the id le mode th e CPU is fr ozen while th e timers, th e serial

ports and the interrupt system are still operating. In the power-down mode the RAM is

saved, the peripheral clock is frozen, but the dev ice has full wake- up capabil ity through

USB events or external interrupts.

2

AT89C5131

4136A–USB–03/03

Page 3

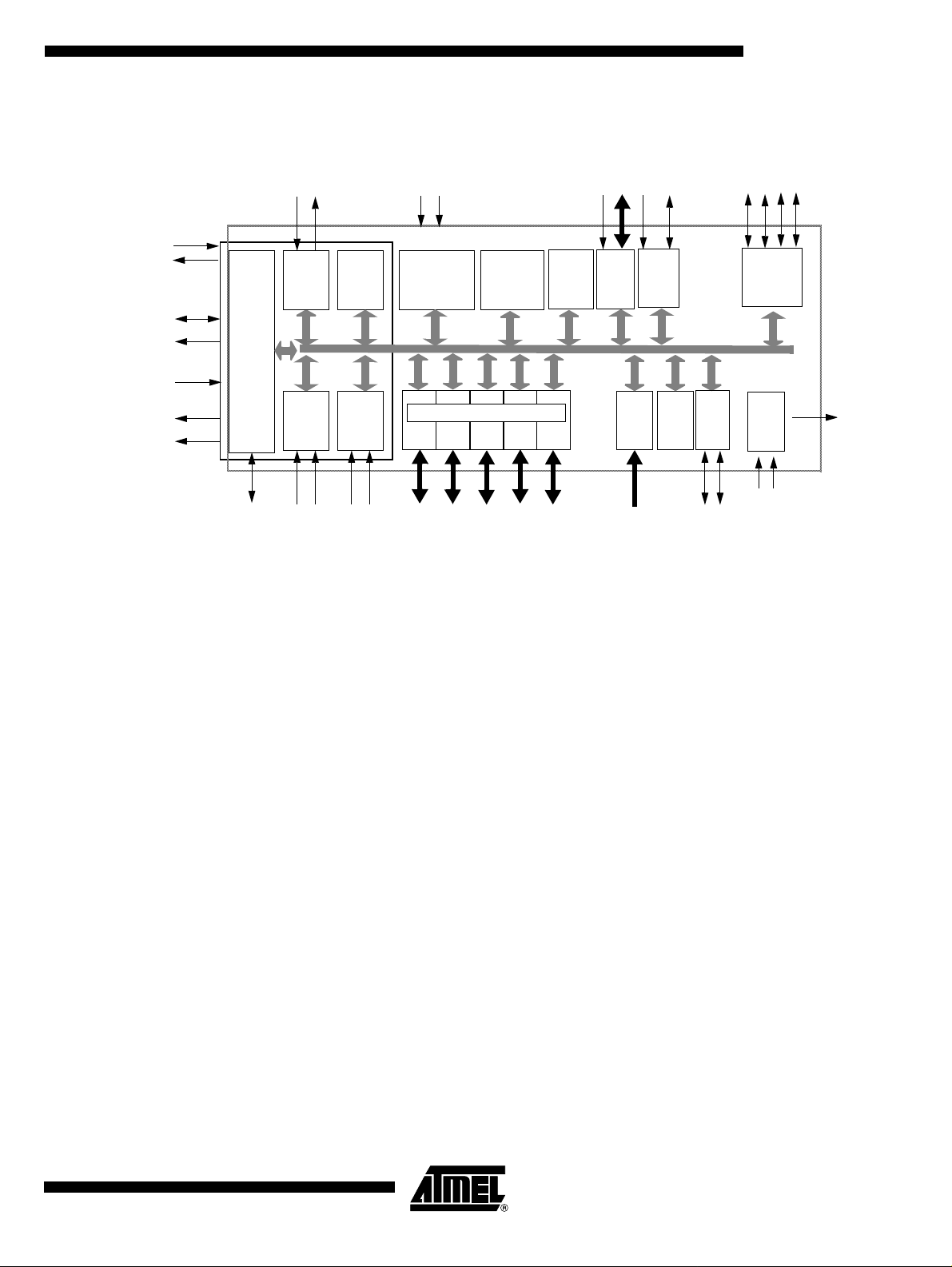

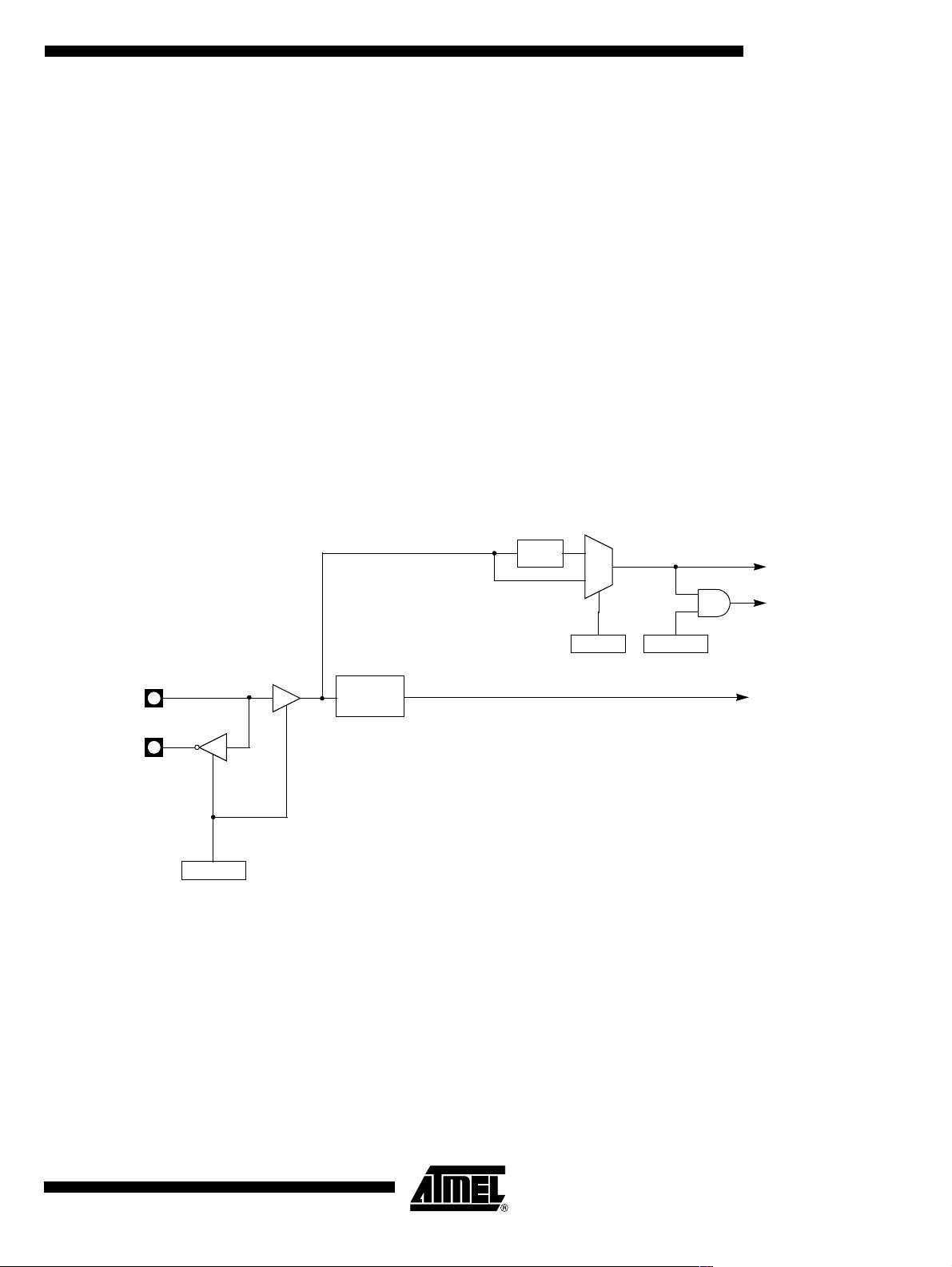

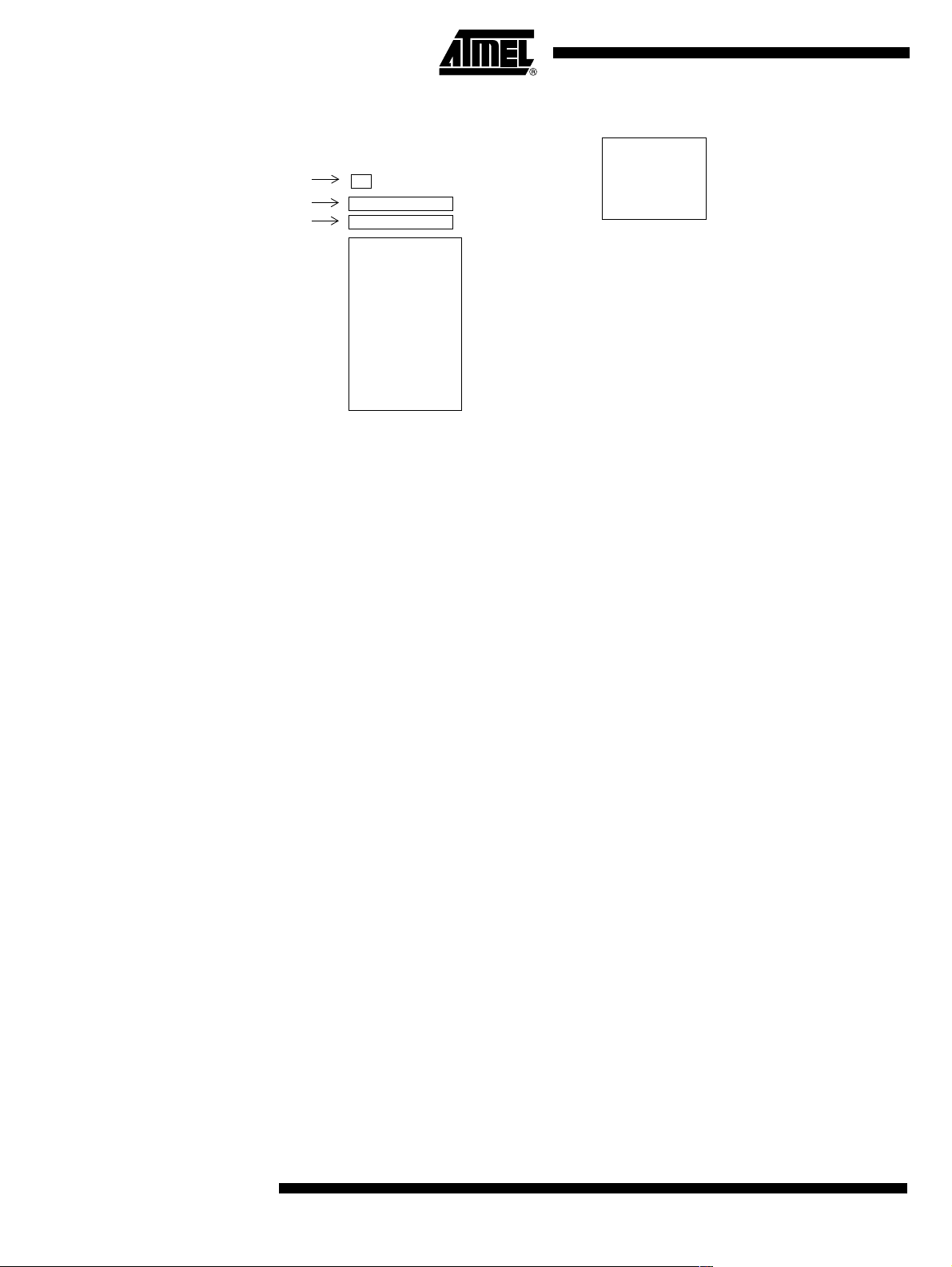

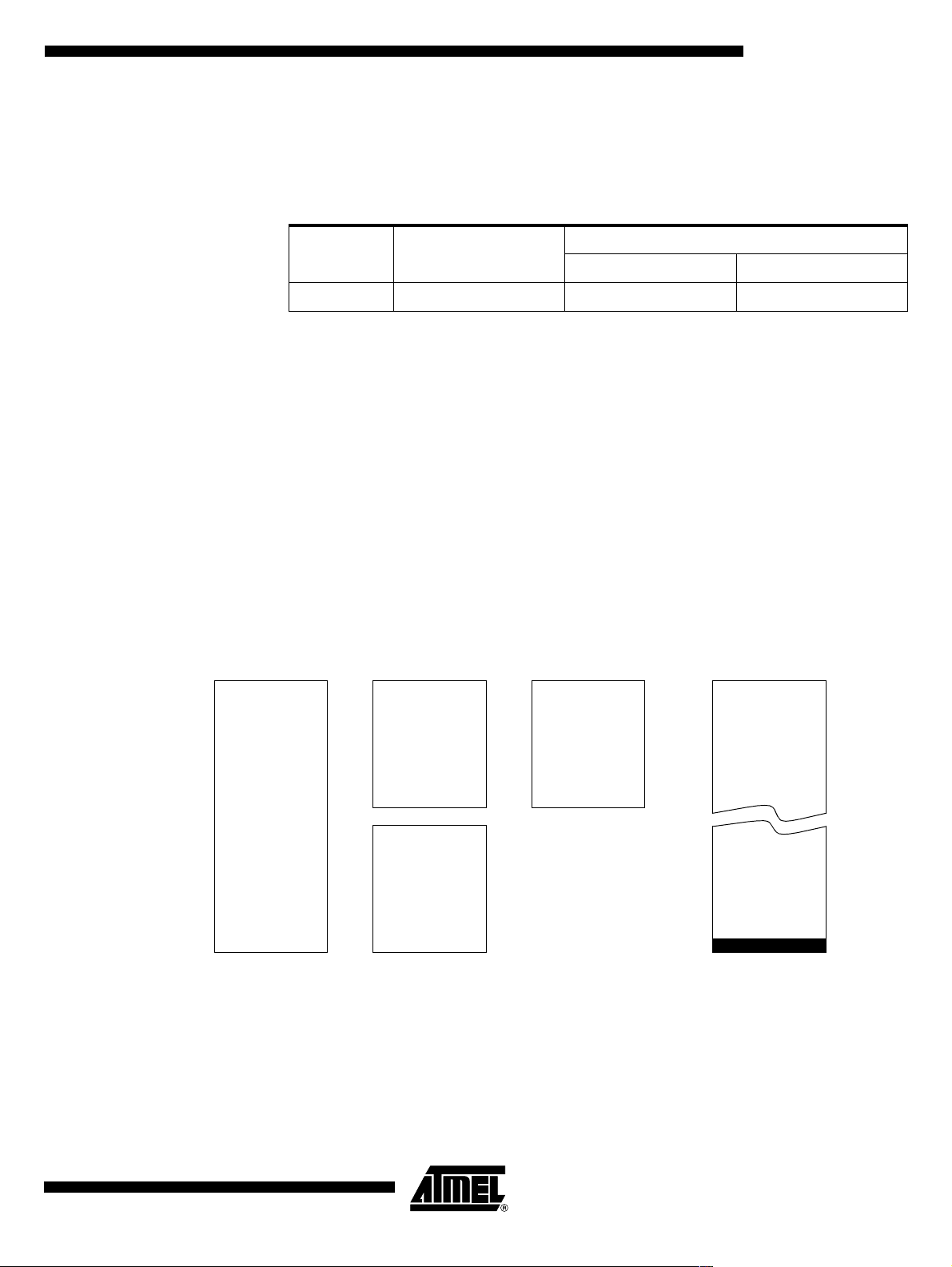

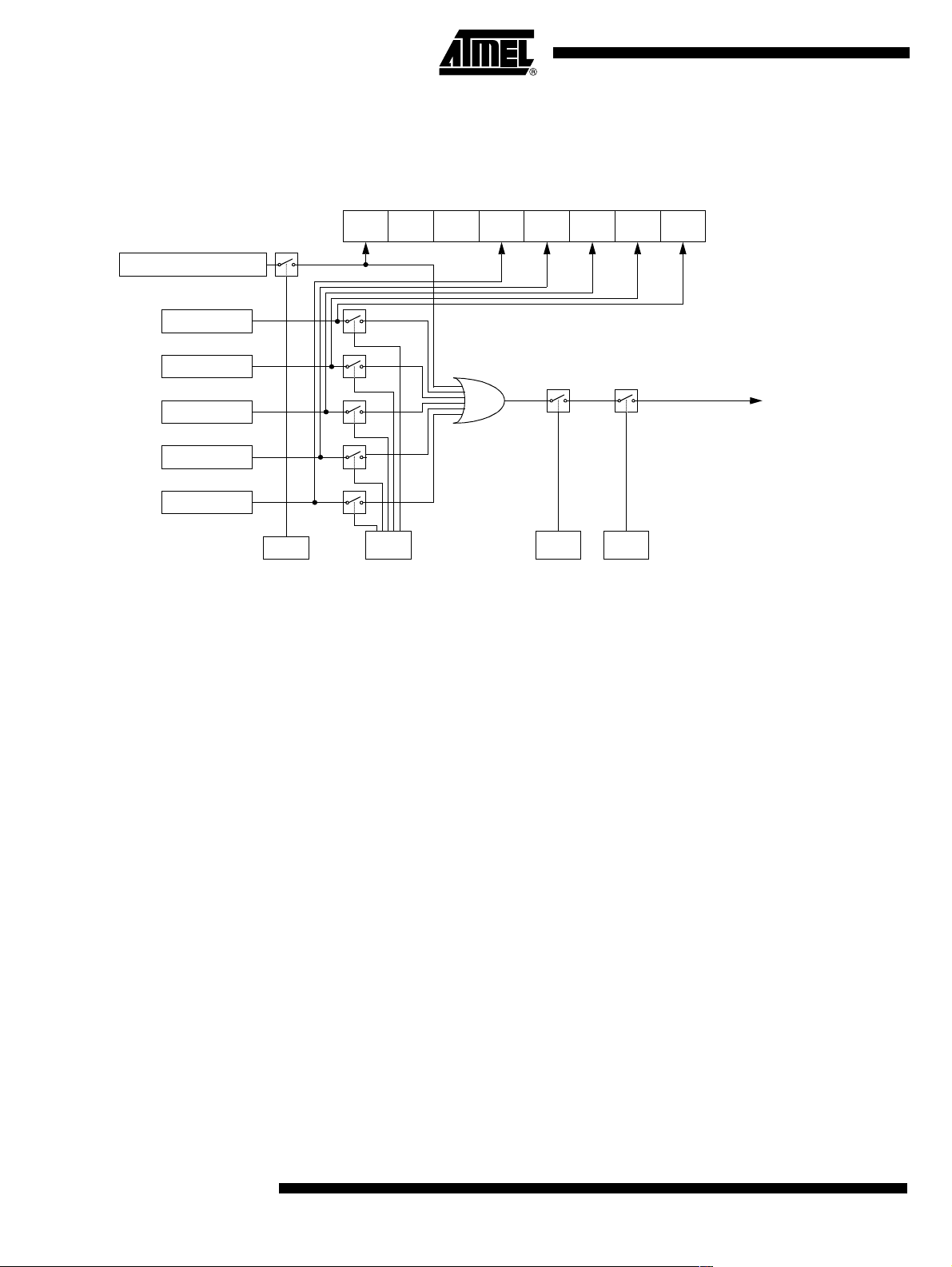

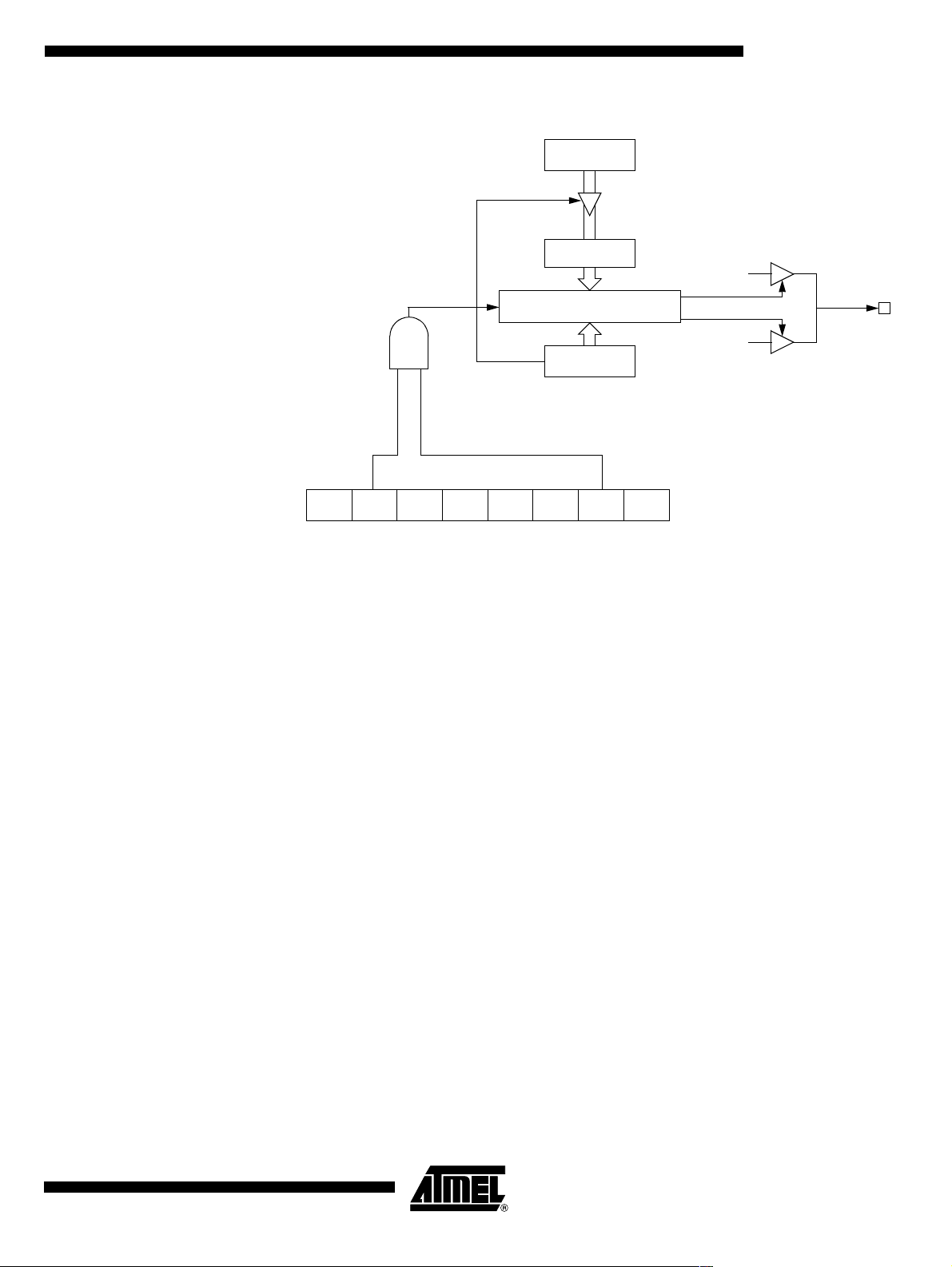

Block Diagram

XTAL1

XTAL2

ALE

PSEN

EA

CPU

RxD

(2)(2)

EUART

+

BRG

TxD

C51

CORE

RAM

256x8

VDD

VSS

32Kx8 Flash

EEPROM

4Kx8

XRAM

1Kx8

ECI

(1)(1)

PCA

CEX

T2EX

(1)

(1)

Timer2

T2

AT89C5131

SS

MISO

MOSI

SCK

(1) (1) (1)

(1)

SPI

(2)

RD

(2)

WR

RST

Notes: 1. Alternate function of Port 1

2. Alternate function of Port 3

3. Alternate function of Port 4 (Alternate function of Port 4 on PLCC52, under evaluation)

Timer 0

Timer 1

(2) (2) (2) (2)

T0

T1

INT

Ctrl

INT0

Parallel I/O Ports & Ext. Bus

Port 0

Port 1

P1

INT1

P0

Port 2

P2

Port 3

P3

Port 4

P4

Key

Board

KIN

Watch

Dog

USB

D -

D +

Regu-

lator

AVSS

VREF

AVDD

4136A–USB–03/03

3

Page 4

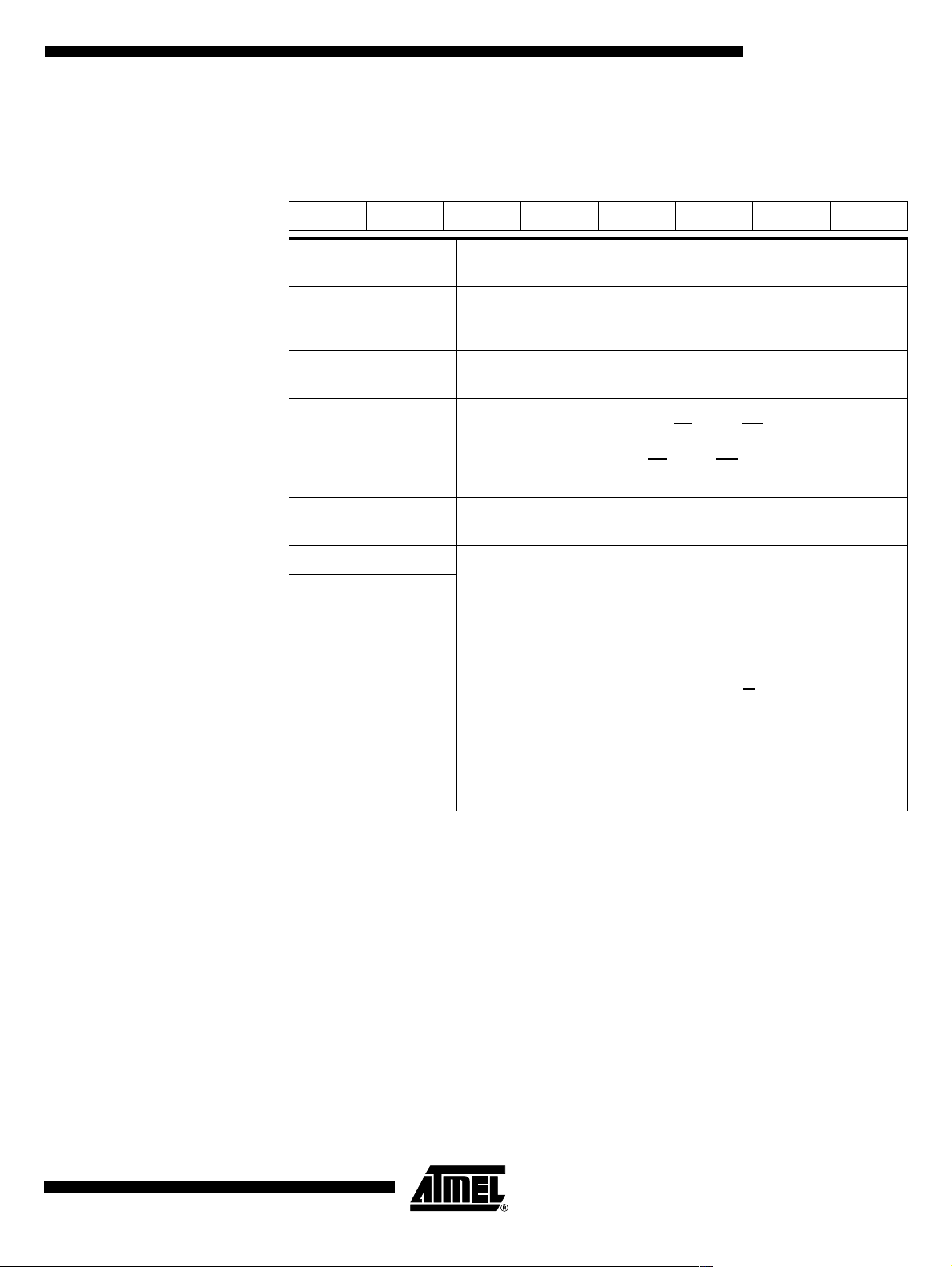

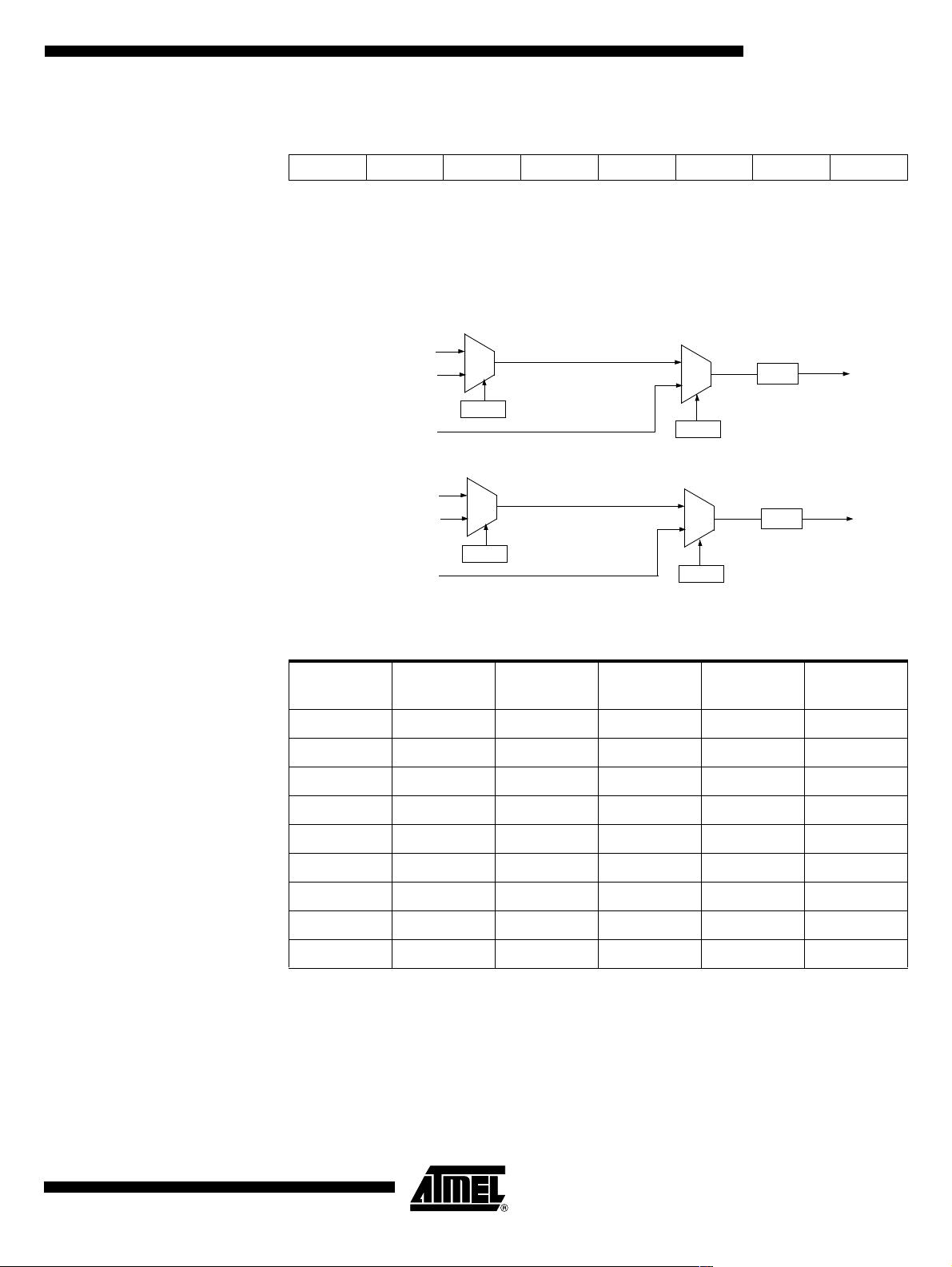

Pinout Description

Pinout

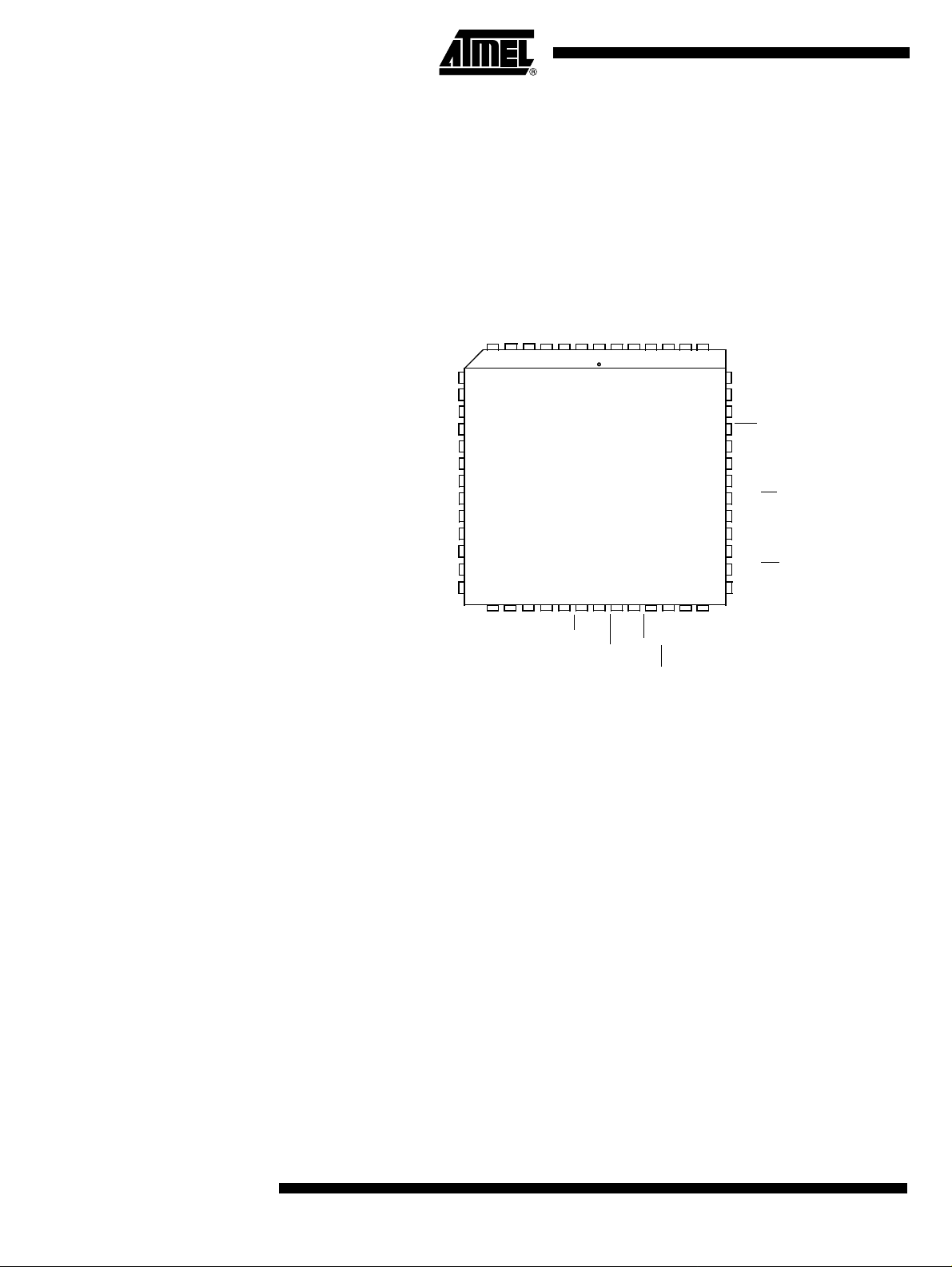

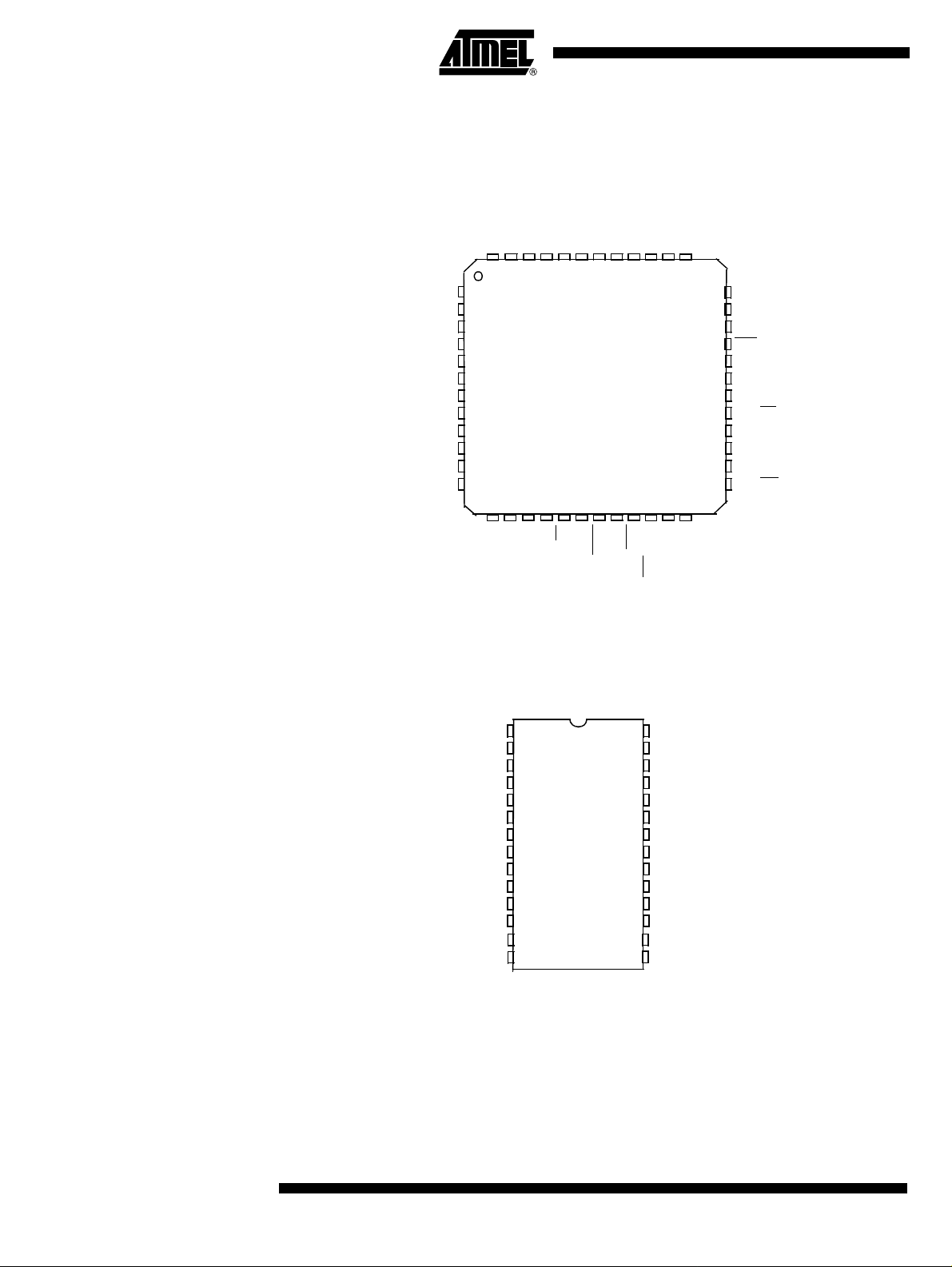

Figure 1. AT89C5131 52-pin PLCC Pinout

P4.0

P1.7/CEX4/KIN7/MOSI

P1.6/CEX3/KIN6/SCK

P2.2/A10

P1.5/CEX2/KIN5/MISO

5 4 3 2 1 6

7 47

P4.1

8

VDD

AVDD

NC

AVSS

9

10

11

12

13

14

15

16

17

18

19

20

2122 26252423 292827 30 31

D-

PLLF

D+

PLCC52

NC

VREF

P2.3/A11

P2.4/A12

P2.5/A13

XTAL2

XTAL1

P2.6/A14

P2.7/A15

P3.0/RxD

P2.0/A8

P2.1/A9

P0.0/AD0

52 51 50 49 48

EA

ALE

PSEN

P1.4/CEX1/KIN4

P3.1/TxD

P1.3/CEX0/KIN3

P3.2/INT0

P1.2/ECI/KIN2

32 33

/LED0

P3.3/INT1

P1.1/T2EX/KIN1/SS

P3.4/T0

P1.0/T2/KIN0

NC

46

P0.1/AD1

45

P0.2/AD2

44

43

RST

42

P0.3/AD3

VSS

41

P0.4/AD4

40

39

P3.7/RD/LED3

P0.5/AD5

38

37

P0.6/AD6

36

P0.7/AD7

35

P3.6/WR/LED2

NC

34

P3.5/T1/LED1

4

AT89C5131

4136A–USB–03/03

Page 5

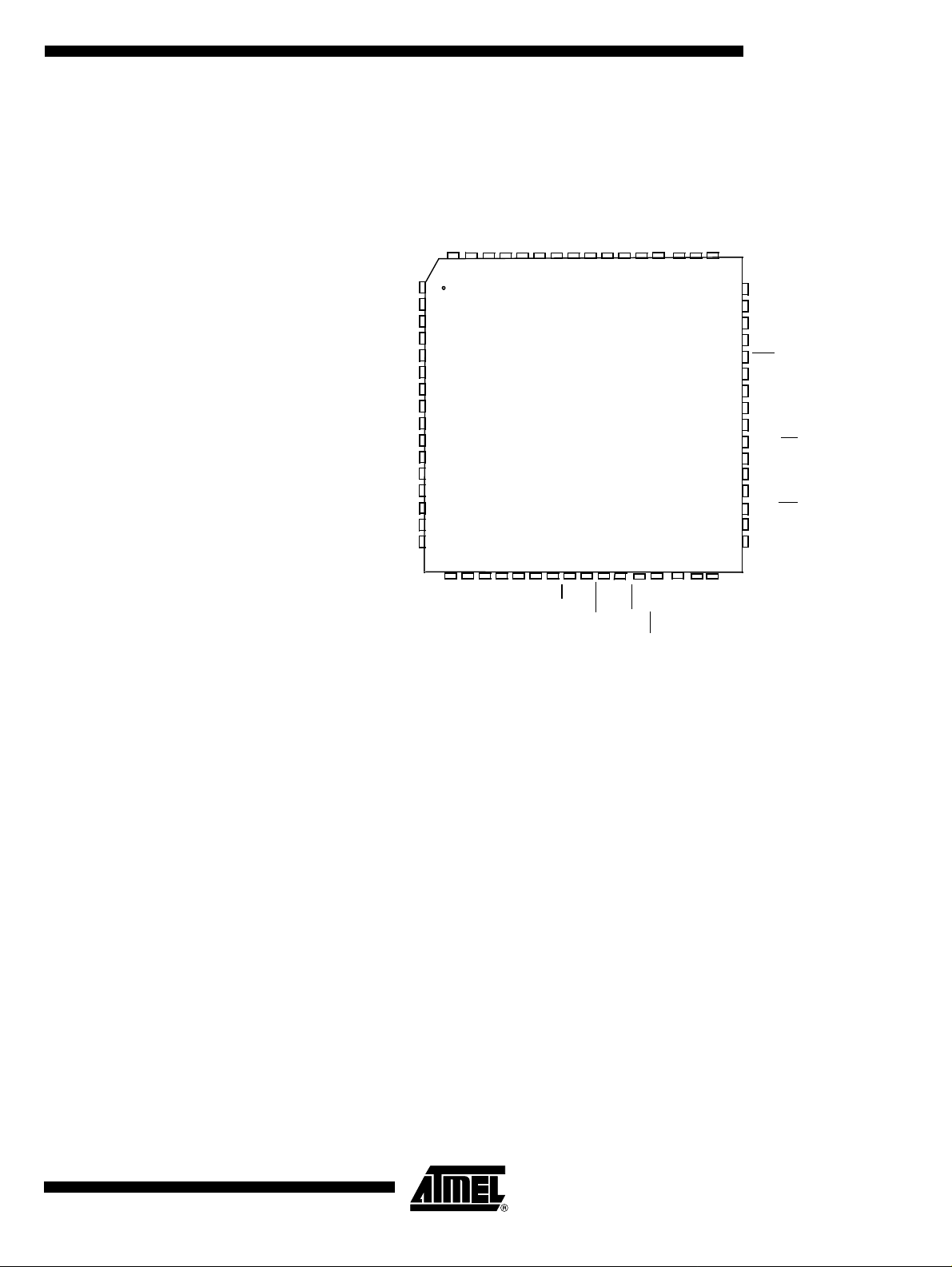

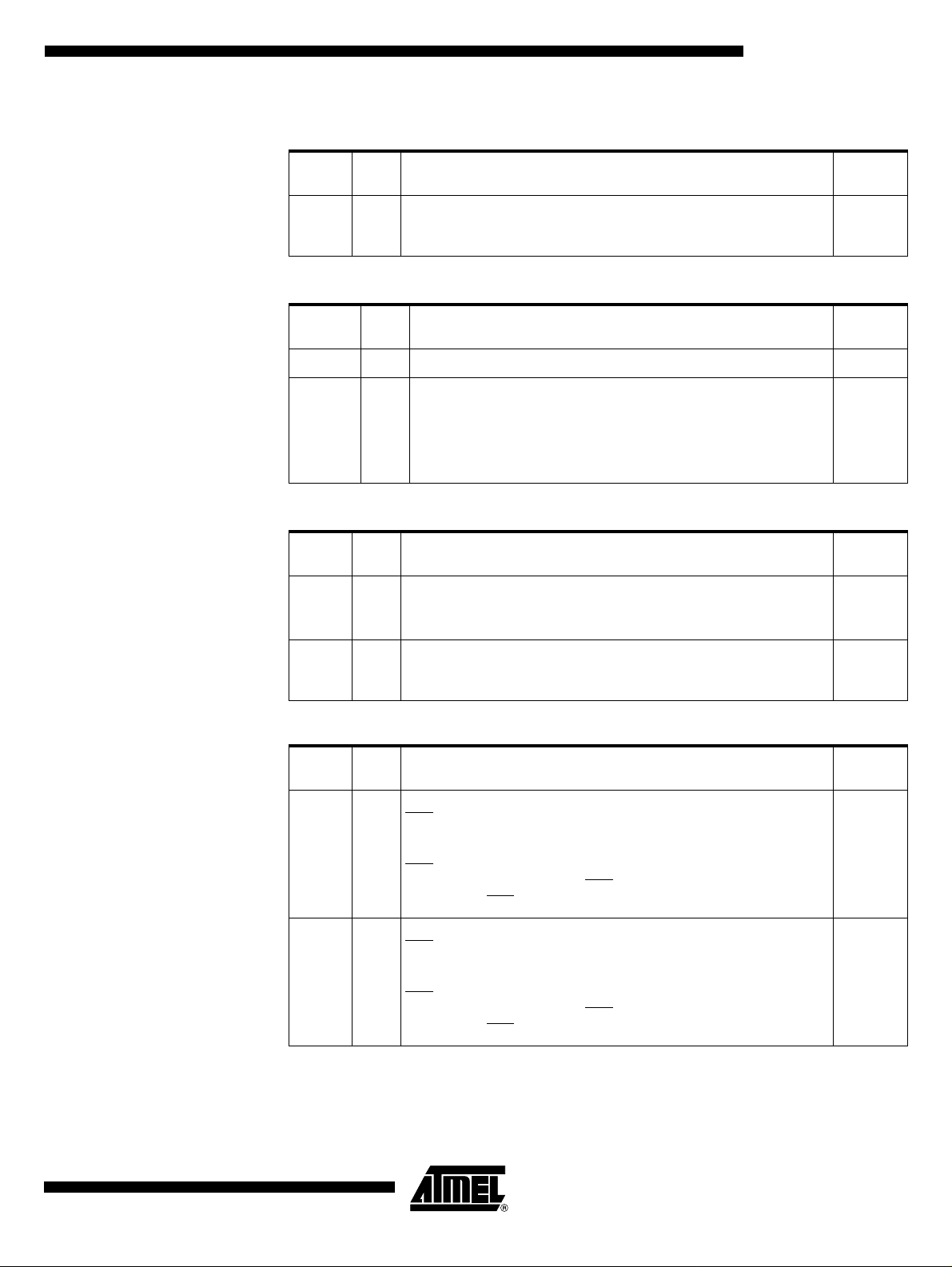

Figure 2. AT89C5131 64-pin VQFP Pinout

P4.0

NC

P2.3/A11

P2.4/A12

P2.5/A13

XTAL2

XTAL1

P2.6/A14

P2.7/A15

VDD

AVDD

NC

AVSS

NC

P3.0/RxD

NC

NC

NC

P4.1

64

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

P1.6/CEX3/KIN6/SCK

P1.7/CEX4/KIN7/MOSI

62 61 60 59 58 63

17 18 22212019 252423 26 27

P2.1/A9

P2.2/A10

P1.5/CEX2/KIN5/MISO

57 56 55 54 53

VQFP64

AT89C5131

P2.0/A8

P0.0/AD0

P1.4/CEX1/KIN4

28

P1.3/CEX0/KIN3

29

52

P1.2/ECI/KIN2

51 50

30

P1.1/T2EX/KIN1/SS

31 32

P1.0/T2/KIN0

NC

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

NC

NC

P0.1/AD1

P0.2/AD2

RST

P0.3/AD3

VSS

NC

P0.4/AD4

P3.7/RD/LED3

P0.5/AD5

P0.6/AD6

P0.7/AD7

P3.6/WR/LED2

NC

NC

NC

NC

PLLF

D-

D+

NC

EA

ALE

VREF

PSEN

/LED0

P3.1/TxD

P3.2/INT0

P3.3/INT1

NC

P3.4/T0

P3.5/T1/LED1

4136A–USB–03/03

5

Page 6

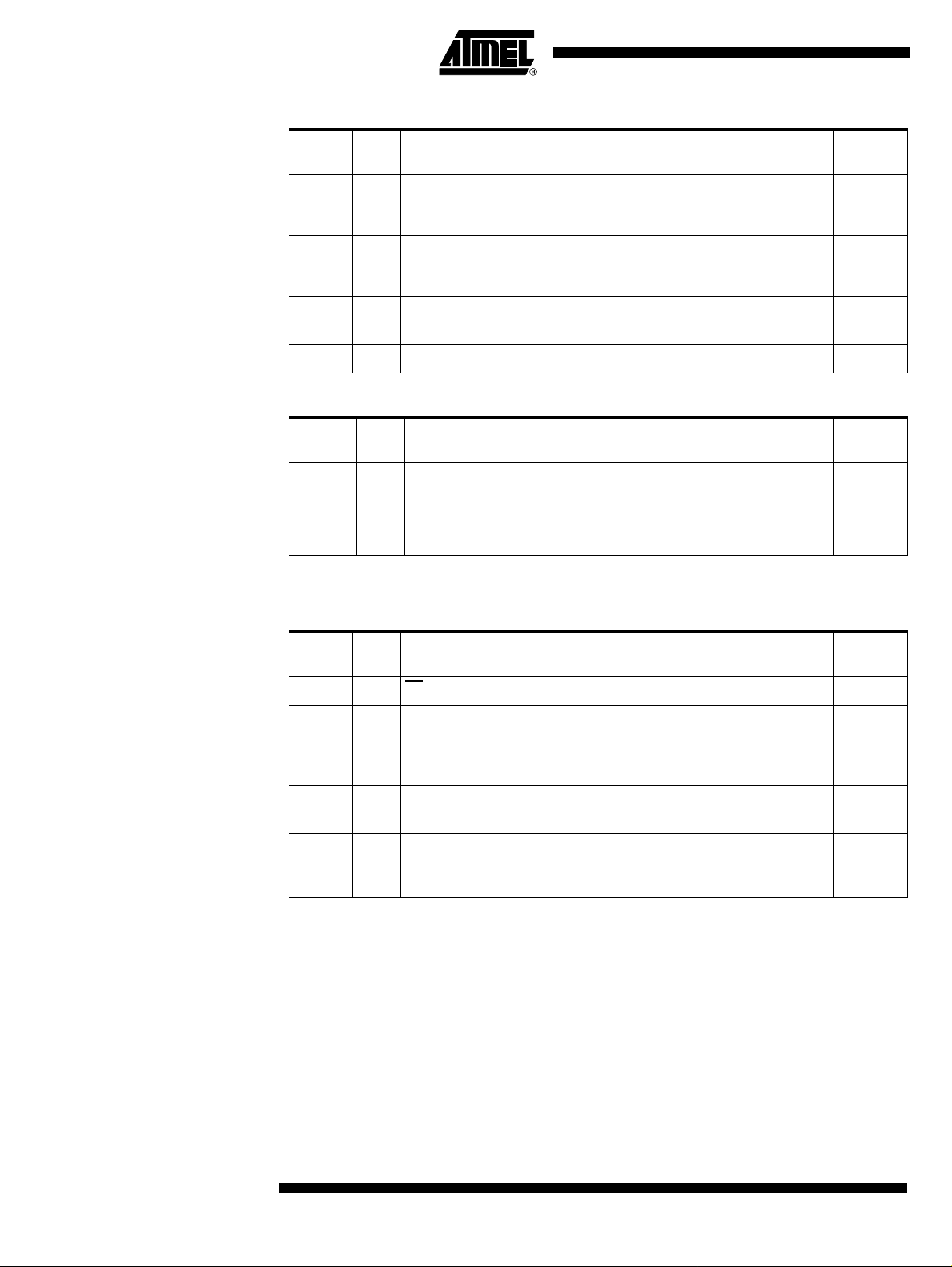

Figure 3. AT89C5131 48-pin MLF Pinout

P4.0

P1.7/CEX4/KIN7/MOSI

P1.6/CEX3/KIN6/SCK

P1.5/CEX2/KIN5/MISO

P2.2/A10

46 45 44 43 42 47

48

1

P4.1

XTAL2

XTAL1

VDD

AVDD

AVSS

2

3

4

5

6

7

8

9

10

11

12

MLF 48

1314 18171615 212019 22 23

D-

D+

EA

PLLF

VREF

P2.3/A11

P2.4/A12

P2.5/A13

P2.6/A14

P2.7/A15

P3.0/RxD

P2.0/A8

P2.1/A9

P0.0/AD0

41 40 39 38 37

ALE

PSEN

P3.1/TxD

P1.4/CEX1/KIN4

P3.2/INT0

P1.3/CEX0/KIN3

/LED0

P3.3/INT1

P1.2/ECI/KIN2

P3.4/T0

24

P1.1/T2EX/KIN1/SS

25

P3.5/T1/LED1

P1.0/T2/KIN0

36

P0.1/AD1

35

P0.2/AD2

34

33

RST

32

P0.3/AD3

31

VSS

P0.4/AD4

30

29

P3.7/RD/LED3

P0.5/AD5

28

27

P0.6/AD6

P0.7/AD7

26

P3.6/WR/LED2

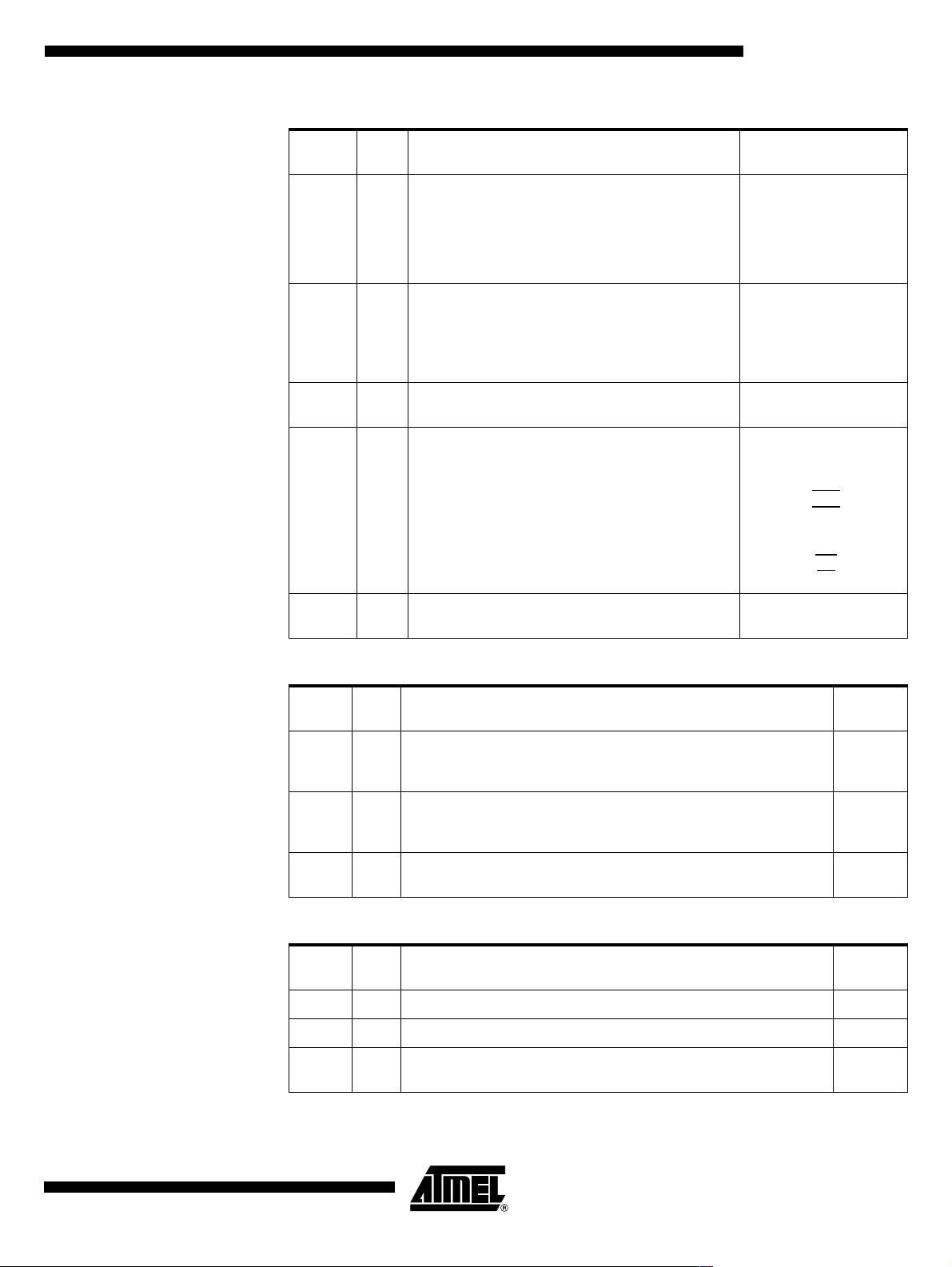

Figure 4. AT89C5131 28-pin SO Pinout

P1.5/CEX2/KIN5/MISO

P1.6/CEX3/KIN6/SCK

P1.7/CEX4/KIN7/MOSI

P3.0/RxD

1

2

3

P4.0

4

P4.1

5

XTAL2

XTAL1

VDD

AVSS

PLLF

D-

D+

VREF P3.1/TxD

SO28

6

7

8

9

10

11

12

13

14

28

P1.4/CEX1/KIN4

P1.3/CEX0/KIN3

27

26

P1.2/ECI/KIN2

25

P1.1/T2EX/KIN1/SS

P1.0/T2/KIN0

24

23

RST

VSS

22

21

P3.7/RD/LED3

P3.6/WR/LED2

20

P3.5/T1/LED1

19

P3.4/T0

18

P3.3/INT1/LED0

17

P3.2/INT0

16

15

6

AT89C5131

4136A–USB–03/03

Page 7

AT89C5131

Signals All the AT89C5131 signals are detailed by functionality on Table 1 through Table 11.

Table 1. Keypad Interface Signal Description

Signal

Name Type Description

Alternate

Function

KIN[7:0) I

Keypad Input Lines

Holding one of these pins high or low for 24 oscillator periods triggers a

keypad interrupt if enabled. Held line is reported in the KBCON register.

Table 2. Programmable Counter Array Signal Description

Signal

Name Type Description

ECI I External Clock Input P1.2

Capture External Input

CEX[4:0] I/O

Compare External Output

Table 3. Serial I/O Signal Description

Signal

Name Type Description

Serial Input

RxD I

TxD O

The serial input is P3.0 after reset, but it can also be configured to P4.0 by

software.

Serial Output

The serial output is P3.1 after reset, but it can also be configured to P4.1 by

software.

P1[7:0]

Alternate

Function

P1.3

P1.4

P1.5

P1.6

P1.7

Alternate

Function

P3.0

P3.1

4136A–USB–03/03

Table 4. Timer 0, Timer 1 and Timer 2 Signal Description

Signal

Name Type Description

Timer 0 Gate Input

INT0

serves as external run control for timer 0, when selected by GATE0

bit in TCON register.

INT0 I

INT1 I

External Interrupt 0

input set IE0 in the TCON register. If bit IT0 in this register is set, bits

INT0

IE0 are set by a falling edge on INT0

a low level on INT0

Timer 1 Gate Input

serves as external run control for Timer 1, when selected by GATE1

INT1

bit in TCON register.

External Interrupt 1

input set IE1 in the TCON register. If bit IT1 in this register is set, bits

INT1

IE1 are set by a falling edge on INT1

a low level on INT1

.

.

. If bit IT0 is cleared, bits IE0 is set by

. If bit IT1 is cleared, bits IE1 is set by

Alternate

Function

P3.2

P3.3

7

Page 8

Table 4. Timer 0, Timer 1 and Timer 2 Signal Description (Continued)

Signal

Name Type Description

Alternate

Function

T0 I

T1 I

T2

T2EX I Timer/Counter 2 Reload/Capture/Direction Control Input P1.1

Timer Counter 0 External Clock Input

When Timer 0 operates as a counter, a falling edge on the T0 pin

increments the count.

Timer/Counter 1 External Clock Input

When Timer 1 operates as a counter, a falling edge on the T1 pin

increments the count.

IOTimer/Counter 2 External Clock Input

Timer/Counter 2 Clock Output

Table 5. LED Signal Description

Signal

Name Ty p e Description

Direct Drive LED Output

LED[3:0] O

These pins can be directly connected to the Cathode of standard LEDs

without external current limiting resistors. The typical current of each

output can be programmed by software to 2, 6 or 10 mA. Several outputs

can be connected together to get higher drive capabilities.

Table 6. SPI Signa l De scr ip tion

Signal

Name Type Description

P3.4

P3.5

P1.0

Alternate

Function

P3.3

P3.5

P3.6

P3.7

Alternate

Function

SS I/O SS

MISO I/O

SCK I/O

MOSI

I/O

: SPI Slave Select P1.1

MISO: SPI Master Input Slave Output line

When SPI is in master mode, MISO receives data from the slave

peripheral. When SPI is in slave mode, MISO outputs data to the master

controller.

SCK: SPI Serial Clo ck

SCK outputs clock to the slave peripheral or receive clock from the master

MOSI: SPI Master Output Slave Input line

When SPI is in master mode, MOSI outputs data to the slave peripheral.

When SPI is in slave mode, MOSI receives data from the master controller

P1.5

P1.6

P1.7

8

AT89C5131

4136A–USB–03/03

Page 9

AT89C5131

Table 7. Ports Signal Description

Signal

Name Type Description Alternate Function

Port 0

P0 is an 8-bit open-drain bidirectional I/O port. Port 0

P0[7:0] I/O

P1[7:0] I/O

pins that have 1s written to them float and can be used

as high impedance inputs. To avoid any parasitic current

consumption, Floating P0 inputs must be pulled to V

.

V

SS

Port 1

P1 is an 8-bit bidirectional I/O port with internal pull-ups,

except for P1.6 and P1.7 that are true open drain

outputs.

DD

or

AD[7:0]

KIN[7:0]

T2

T2EX

ECI

CEX[4:0]

P2[7:0] I/O

P3[7:0] I/O

P4[1:0] I/O

Port 2

P2 is an 8-bit bidirectional I/O port with internal pull-ups.

Port 3

P3 is an 8-bit bidirectional I/O port with internal pull-ups.

Port 4

P4 is an 2-bit bidirectional I/O port.

Table 8. Clock Signal Description

Signal

Name Type Description

XTAL1 I

XTAL2 O

Input to the on-chip inv e r ting oscillator amplifie r

To use the internal oscillator, a crystal/resonator circuit is connected to this

pin. If an external oscillator is used, its output is connected to this pin.

Output of the on-chip inverting oscillator amplifier

To use the internal oscillator, a crystal/resonator circuit is connected to this

pin. If an external oscillator is used, leave XTAL2 uncon nected.

A[15:8]

LED[3:0]

RxD

TxD

INT0

INT1

T0

T1

WR

RD

Alternate

Function

-

-

4136A–USB–03/03

PLLF I

PLL Low Pass Filter input

Receives the RC network of the PLL low pass filter.

Table 9. USB Signa l Desc ript ion

Signal

Name Type Description

D+ I/O USB Data + signal -

D- I/O USB Data - signal -

VREF O

USB Reference Voltage

Connect this pin to D+ using a 1.5 kΩ resistor to use the Detach function.

-

Alternate

Function

-

9

Page 10

Table 10. System Signal Description

Signal

Name Type Description

Alternate

Function

AD[7:0] I/O

A[15:8] I/O

RD I/O

WR I/O

RST I

ALE O

Multiplexed Address/Data LSB for external access

Data LSB for Slave port access (used for 8-bit and 16-bit modes)

Address Bus MSB for external access

Data MSB for Slave port access (used for 16-bit mode only)

Read Signal

Read signal asserted during external data memory read operation.

Control input for slave port read access cycles.

Write Signal

Write signal asserted during external data memory write operation.

Control input for slave write access cycles.

Reset Input

Holding this pin low for 64 oscillator periods while the oscillator is running

resets the device. The Port pins are driven to their reset conditions when a

voltage lower than V

This pin has an internal pull-up resistor which allows the device to be reset

by connecting a capacitor between this pin and VSS.

Asserting RST

the chip to normal operation.

This pin is set to 0 for at least 12 oscillator periods when an internal reset

occurs.

Address Latch Enable Output

The falling edge of ALE strobes the address into external latch. This signal

is active only when reading or writing external memory using MOVX

instructions.

is applied, whether or not the oscillator is running.

IL

when the chip is in Idle mode or Power-down mode returns

P0[7:0]

P2[7:0]

P3.7

P3.6

-

-

PSEN O

EA I

Program

Test mode entry signal. This pin must be set to V

External Access Enable

This pin must be held low to force the device to fetch code from external

program memory starting at address 0000h. It is latched during reset and

cannot be dynamically changed during operation.

Table 11. Power Signal Description

Signal

Name Type Description

AVSS GND

AVDD PWR

VSS GND

VDD PWR

Alternate Ground

AVSS is used to supply the on-chip PLL.

Alternate Ground

AVDD is used to supply the on-chip PLL.

Digital Ground

VSS is used to supply the buffer ring and the digital core.

Digital Supply Voltage

VDD is used to supply the buffer ring on all versions of the device.

It is also used to power the on-chip voltage regulator of the Standard

versions or the digital core of the Low Power versions.

for normal operation.

DD

-

-

Alternate

Function

-

-

-

-

10

AT89C5131

4136A–USB–03/03

Page 11

Table 11. Power Signal Description (Continued)

Signal

Name Type Description

3V Voltag e Reference

VREF is used to supply the on-chip USB differential drivers.

VREF PWR

It is internally connected to the on-chip voltage regulator output of the

standard versions, which must be connected to an external decoupling

capacitor and can be connected to D+ with a 15 kΩ resistor.

It must be provided from outside on the Low Power versions, which have

no internal voltage regulator.

AT89C5131

Alternate

Function

-

4136A–USB–03/03

11

Page 12

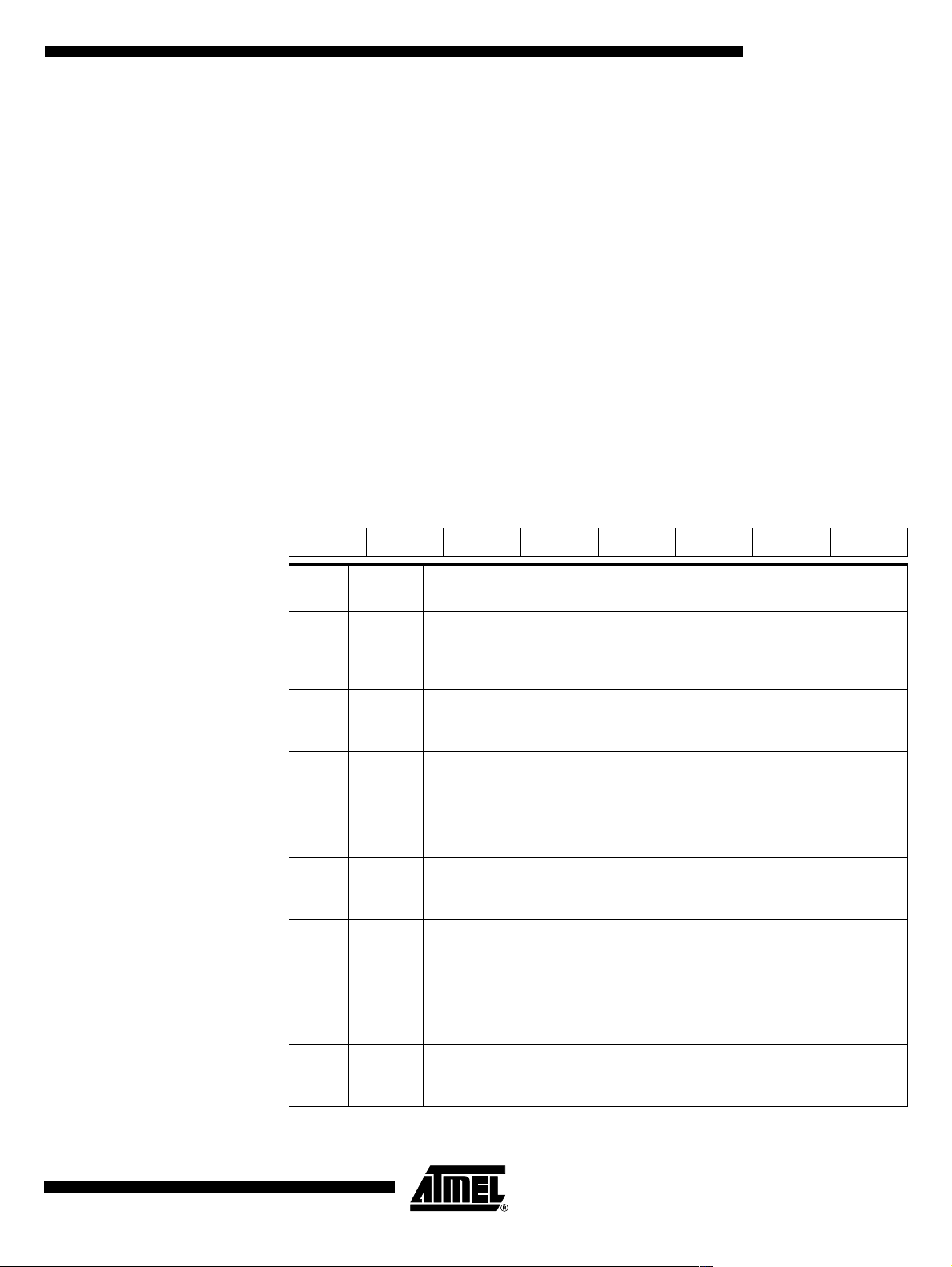

SFR Mapping The Special Function Registers (SFRs) of the AT89C5131 fall into the following

categories:

• C51 core registers: ACC, B, DPH, DPL, PSW, SP

• I/O port registers: P0, P1, P2, P3, P4

• Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2,

RCAP2L, RCAP2H

• Serial I/O port registers: SADDR, SADEN, SBUF, SCON

• PCA (Programmable Counter Array) registers: CCON, CMOD, CCAPMx, CL, CH,

CCAPxH, CCAPxL (x: 0 to 4)

• Power and clock control registers: PCON

• Hardware Watchdog Timer registers: WDTRST, WDTPRG

• Interrupt system registers: IE0, IPL0, IPH0, IE1, IPL1, IPH1

• Keyboard Interface registers: KBE, KBF, KBLS

• LED register: LEDCON

• Serial Port Interface (SPI) registers: SPCON, SPSTA, SPDAT

• USB registers: Uxxx (17 registers)

• PLL registers: PLLCON, PLLDIV0

• BRG (Baud Rate Generator) registers: BRL, BDRCON

• Flash register: FCON (FCON access is reserved for the Flash API and ISP

software)

• EEPROM register: EECON

• Clock Prescaler register: CKRL

• 32 kHz Sub Clock Oscillator registers: CKSEL

• Others: AUXR, AUXR1, CKCON0, CKCON1

12

AT89C5131

4136A–USB–03/03

Page 13

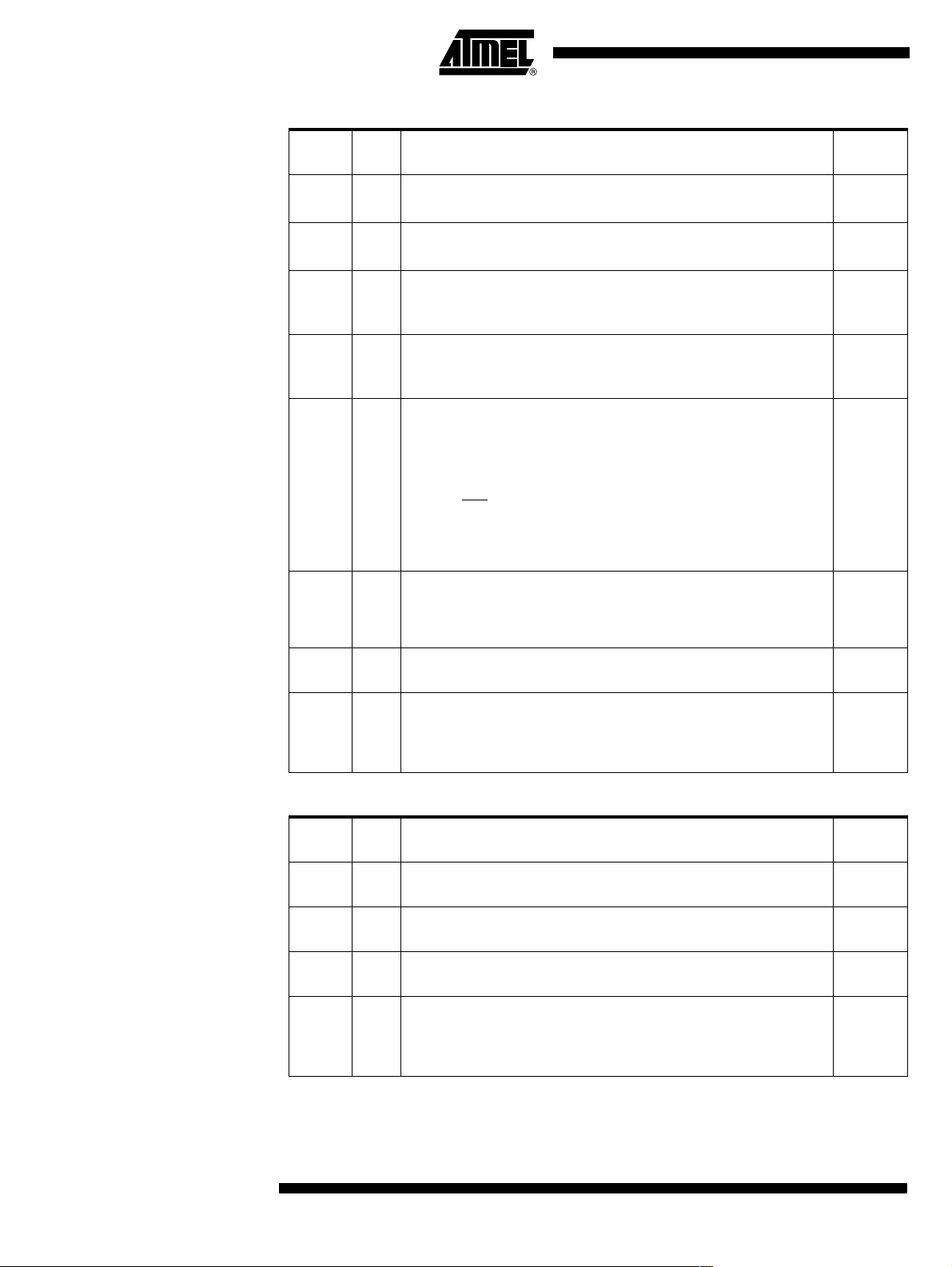

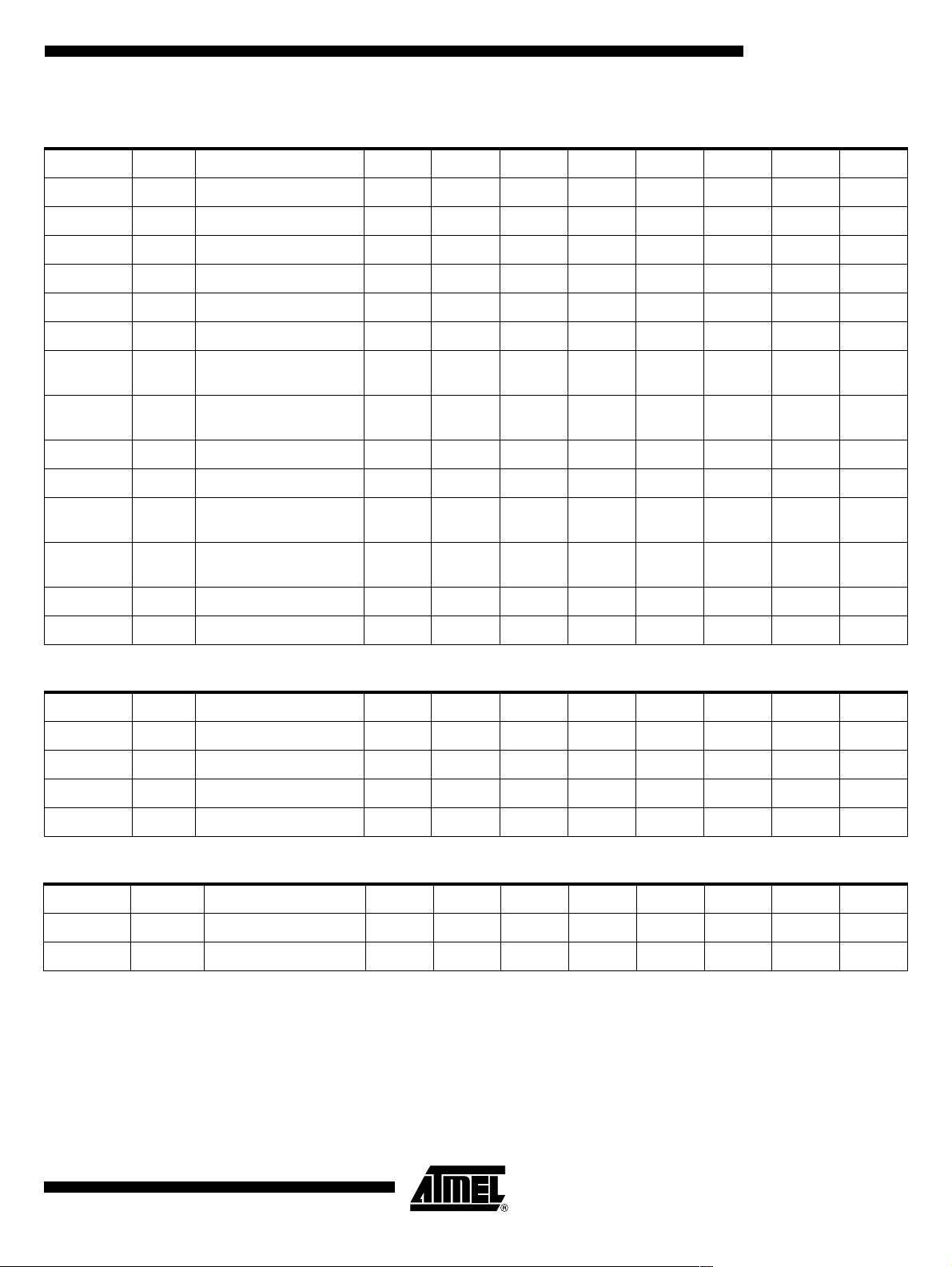

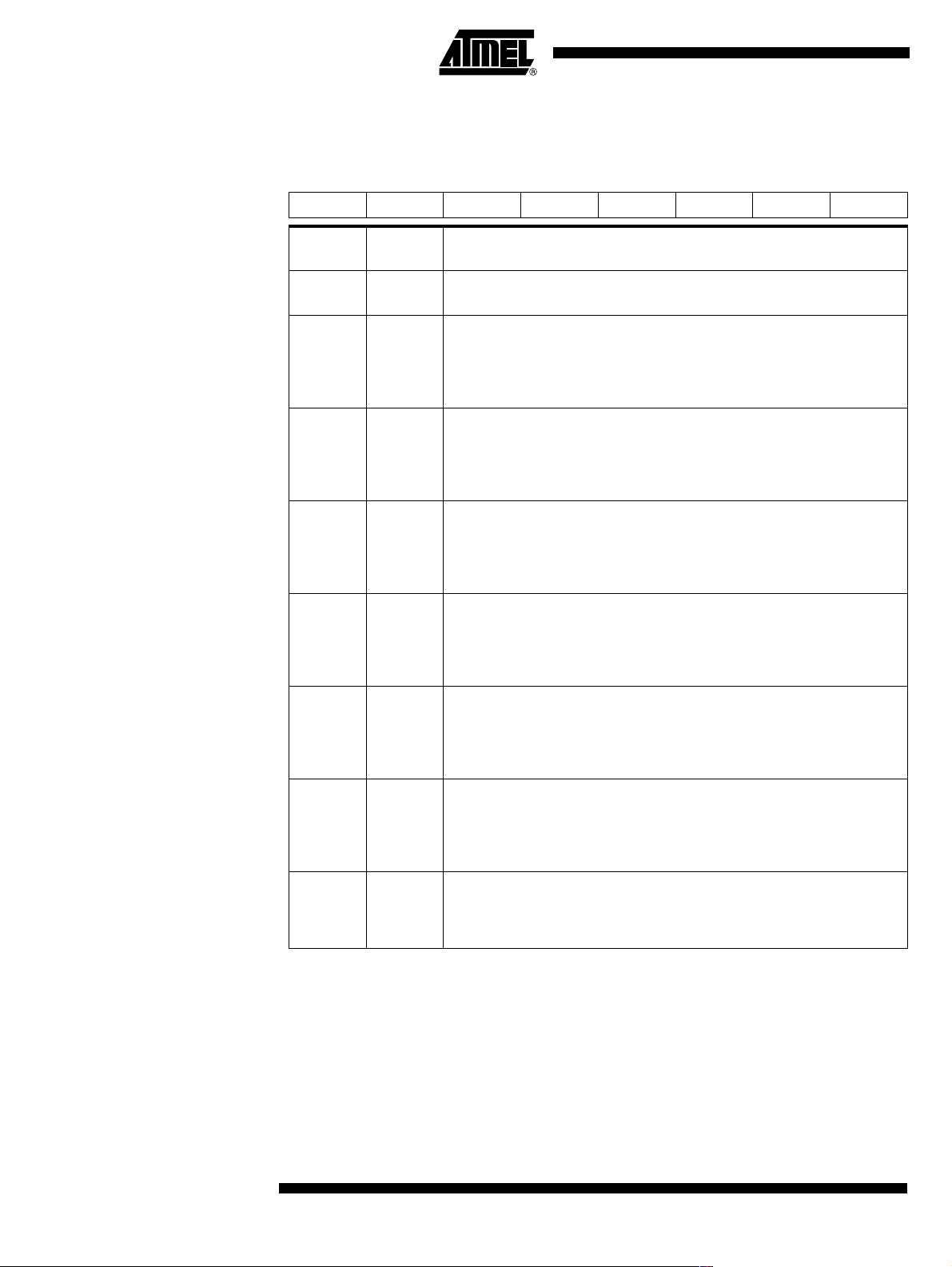

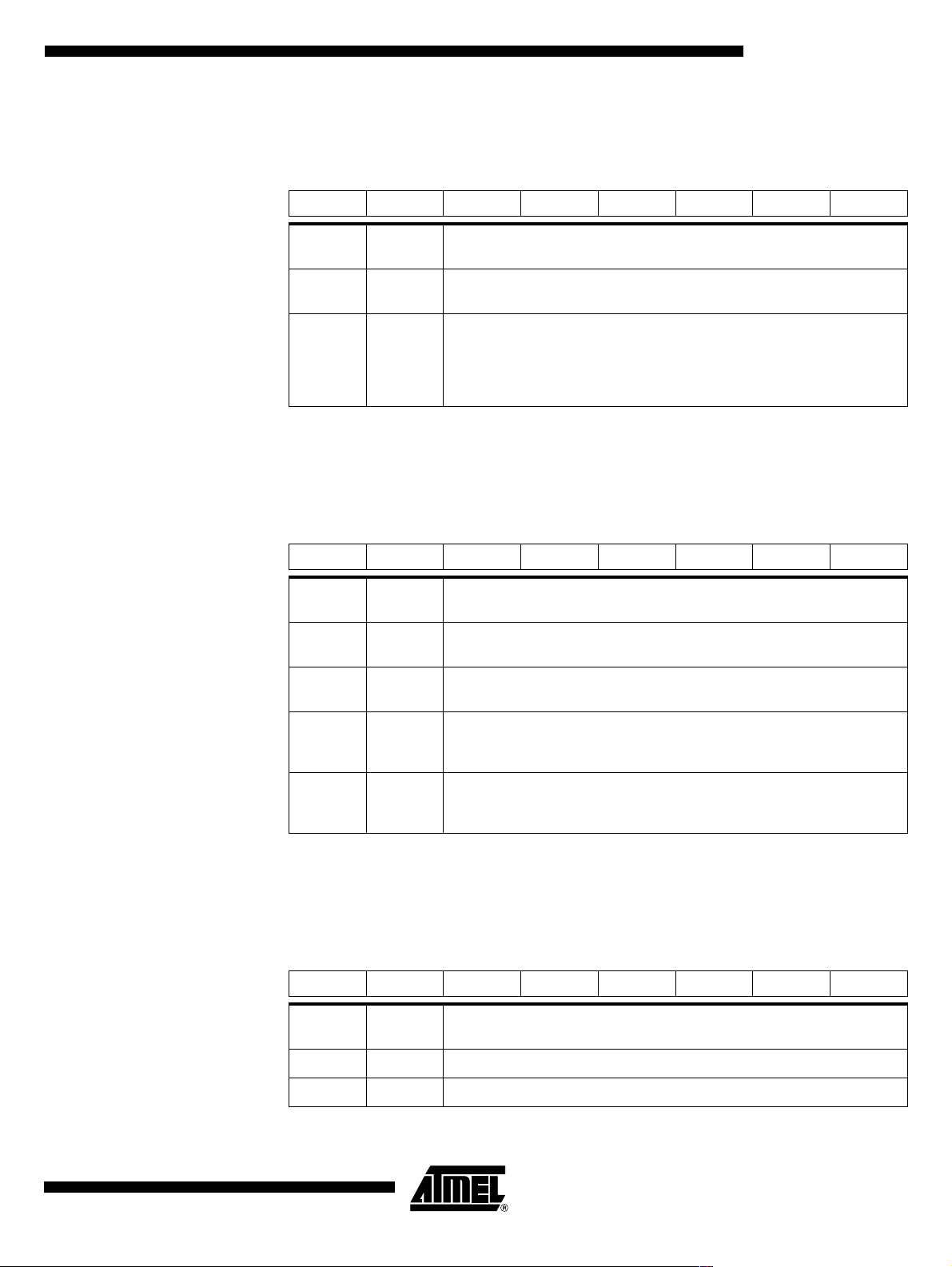

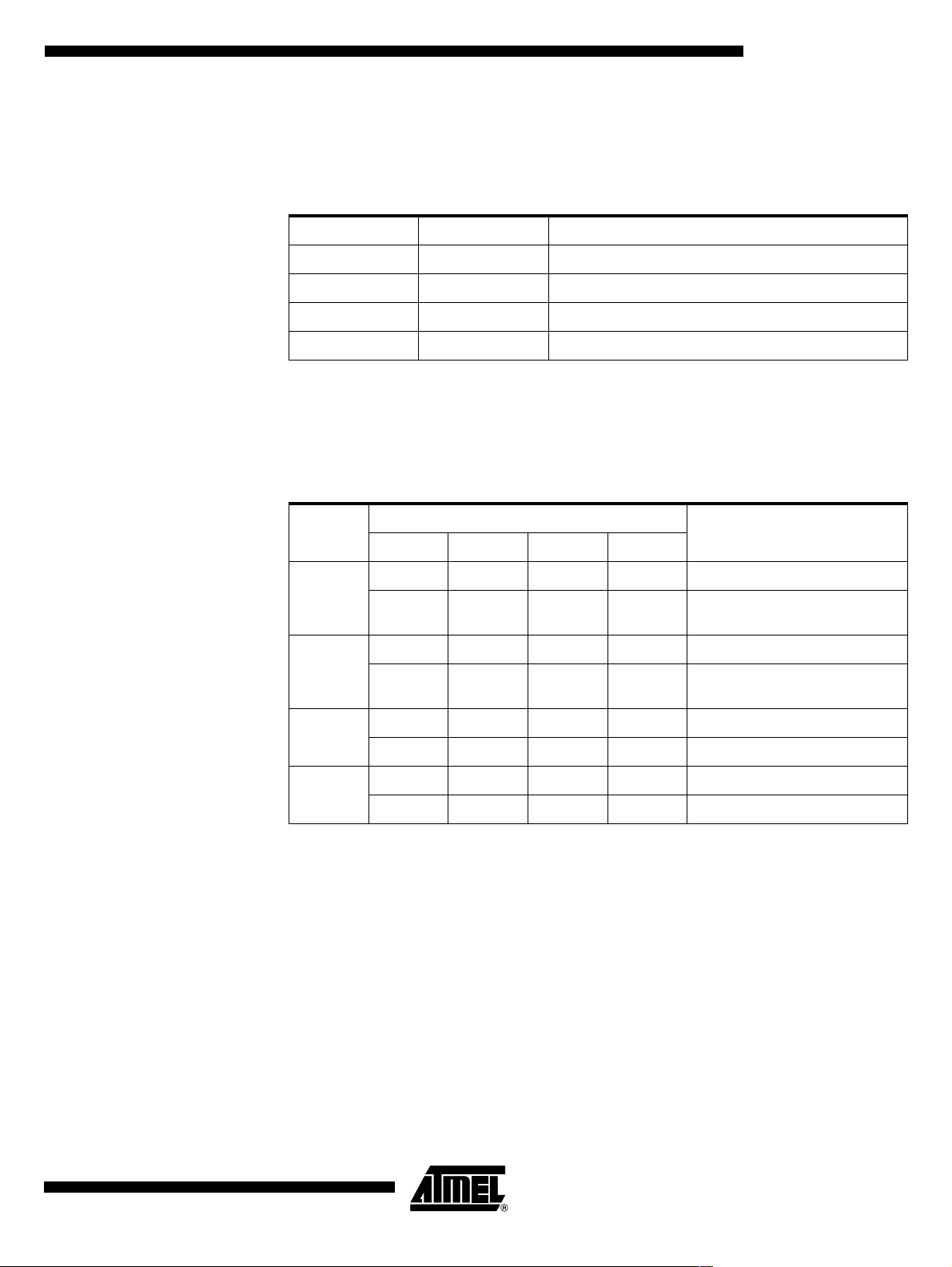

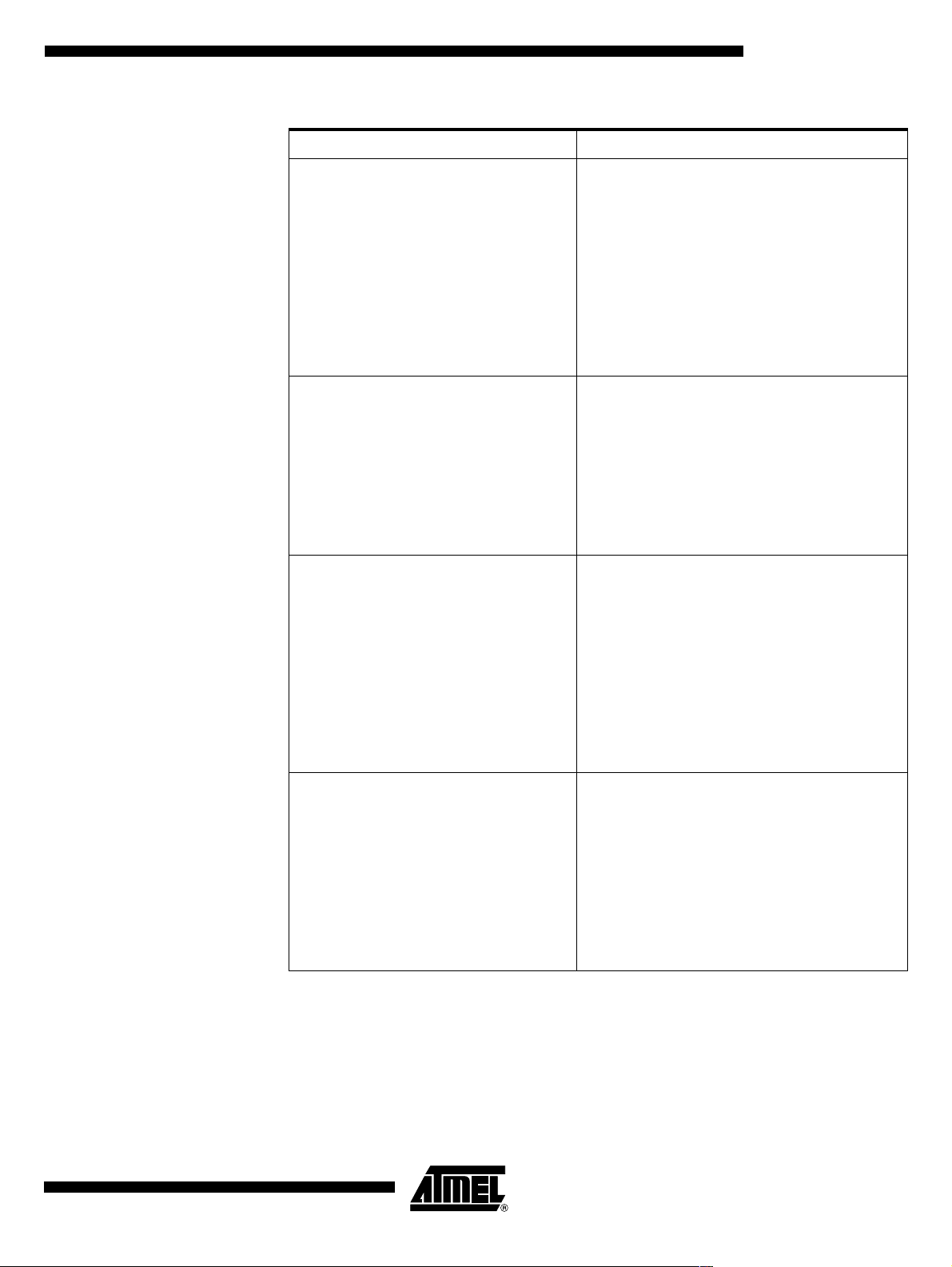

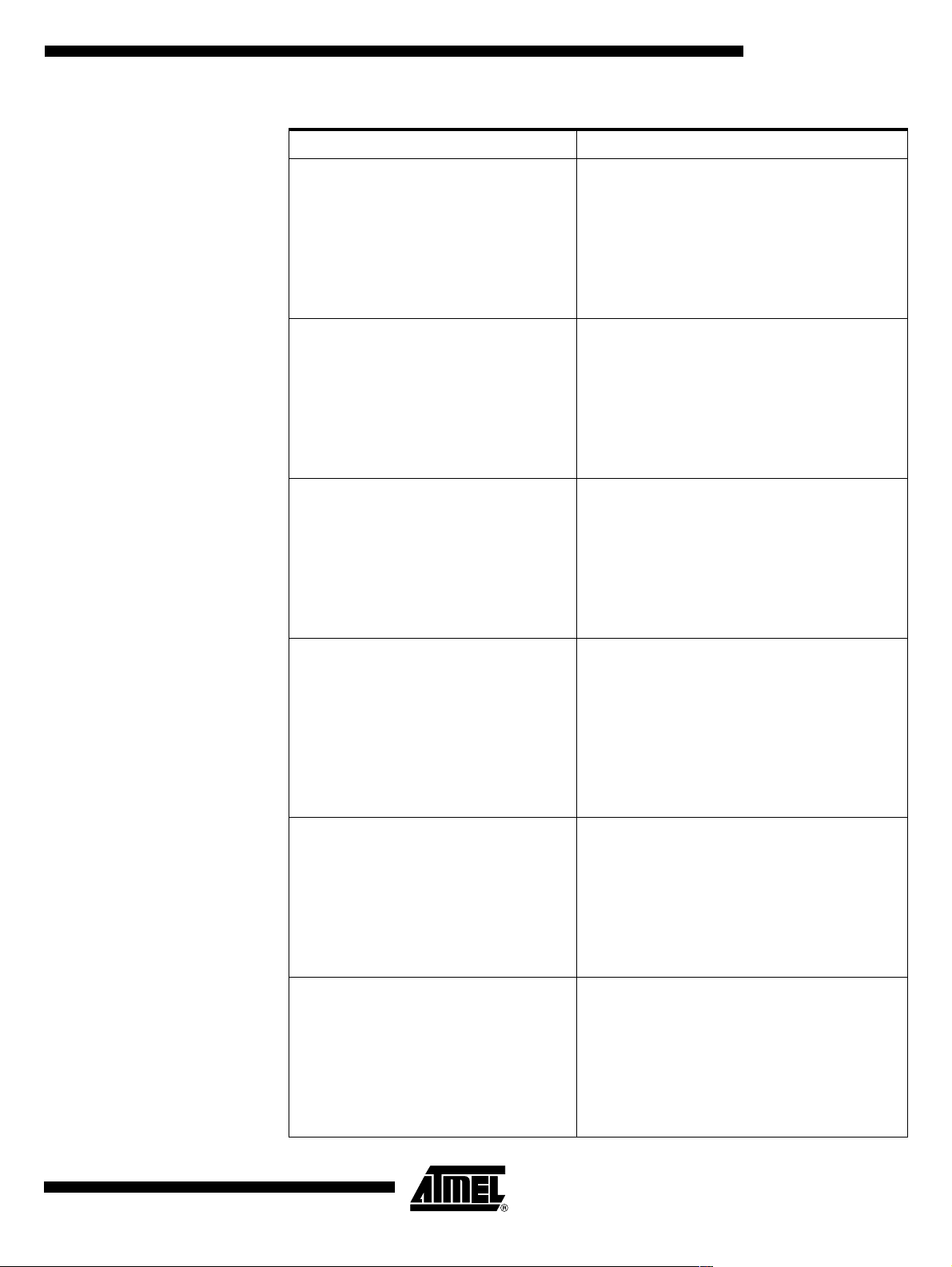

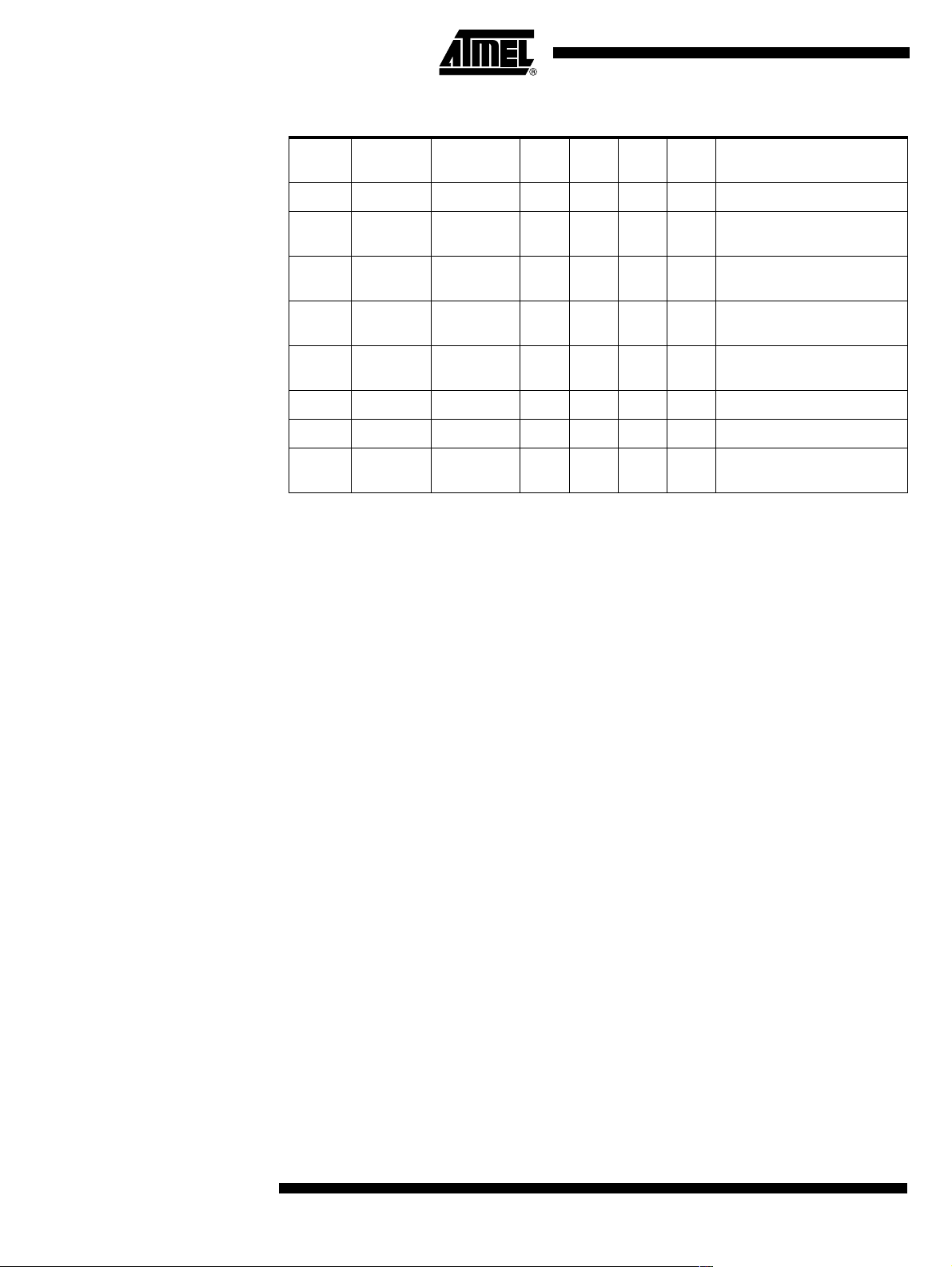

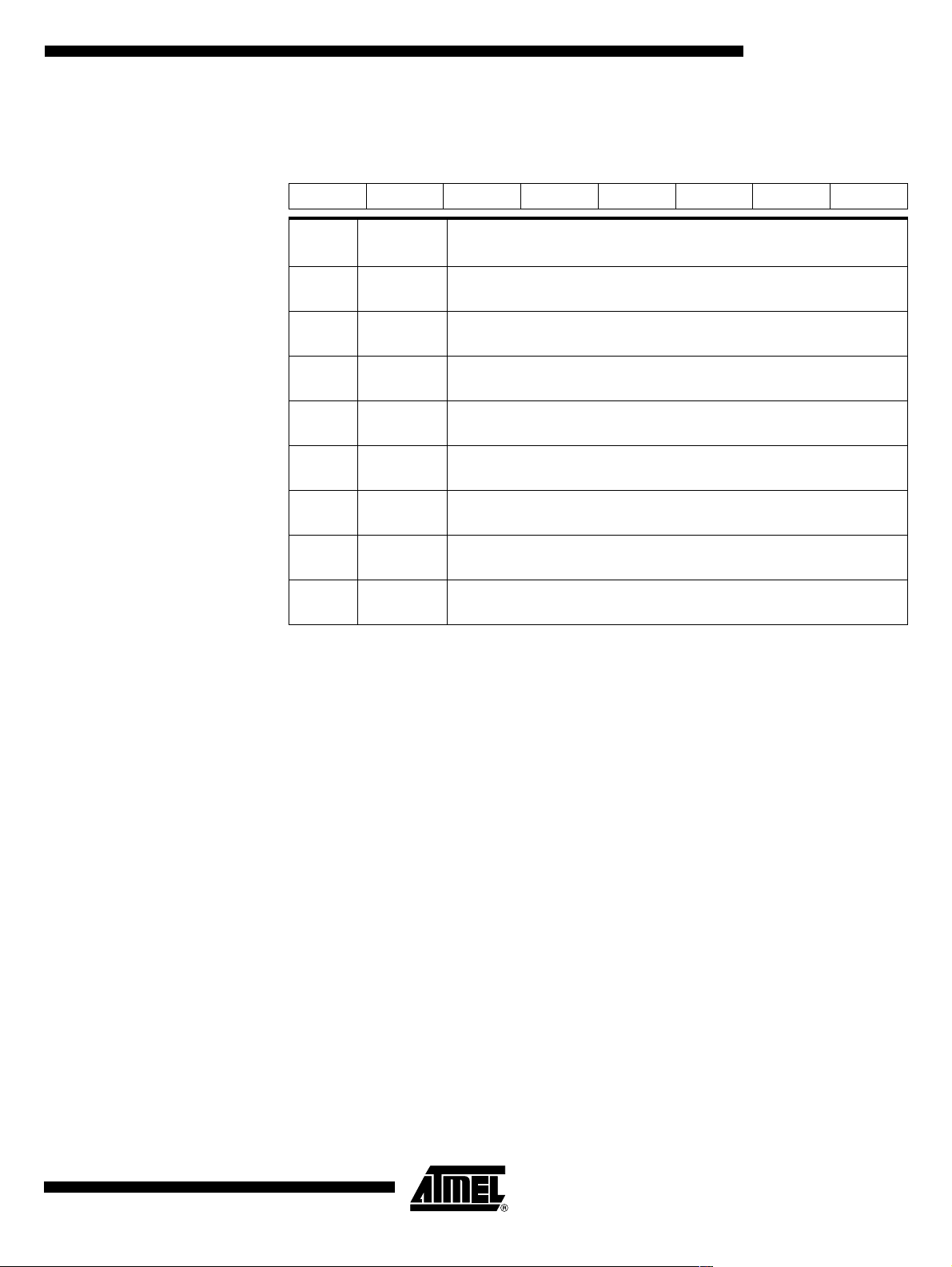

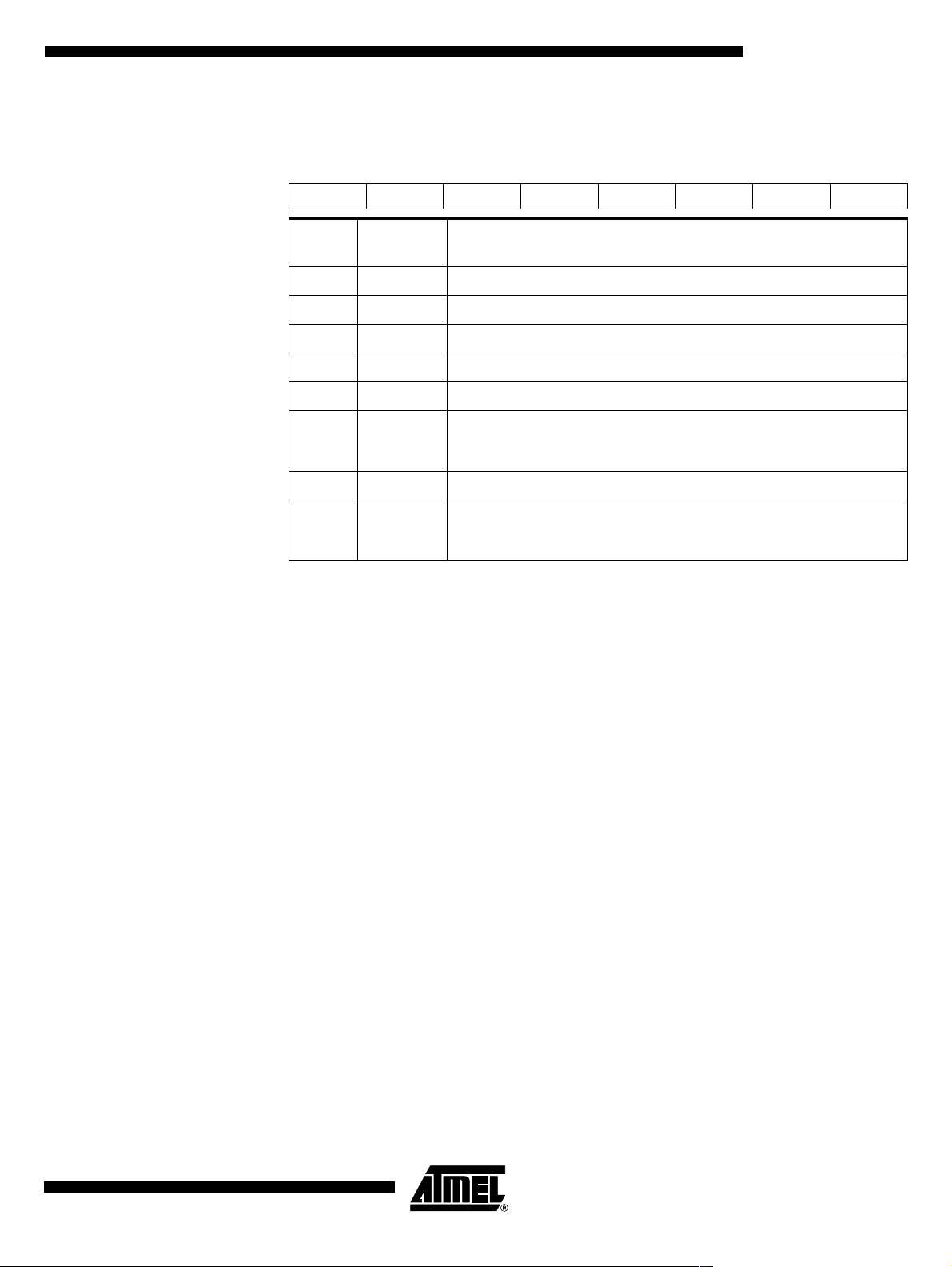

Table 12. SFR Descriptions

Reserved

Bit

Addressable Non-Bit Addressable

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

AT89C5131

The table below shows all SFRs with their address and their reset value.

F8h

F0h

E8h

E0h

D8h

D0h

C8h

C0h

B8h

B0h

UEPINT

0000 0000

B

0000 0000

ACC

0000 0000

CCON

00X0 0000

PSW

0000 0000

T2CON

0000 0000

P4

X XXX 1111

IPL0

X000 000

P3

1111 1111

CH

0000 0000

LEDCON

0000 0000

CL

0000 0000

CMOD

00XX X000

FCON (1)

XXXX 0000

T2MOD

XXXX XX00

SADEN

0000 0000

IE1

XXXX X000

CCAP0H

XXXX XXXX

CCAP0L

XXXX XXXX

UBYCTLX

0000 0000

CCAPM0

X000 0000

EECON

0000 0000

RCAP2L

0000 0000

UEPIEN

0000 0000

UFNUML

0000 0000

IPL1

XXXX X000

CCAP1H

XXXX XXXX

CCAP1L

XXXX XXXX

UBYCTHX

0000 0000

CCAPM1

X000 0000

RCAP2H

0000 0000

SPCON

0001 0100

UFNUMH

0000 0000

IPH1

XXXX X111

CCAP2H

XXXX XXXX

CCAP2L

XXXX XXXX

CCAPM2

X000 0000

UEPCONX

1000 0000

TL2

0000 0000

SPSTA

0000 0000

USBCON

0000 0000

CCAP3H

XXXX XXXX

CCAP3L

XXXX XXXX

CCAPM3

X000 0000

UEPRST

0000 0000

TH2

0000 0000

SPDAT

XXXX XXXX

USBINT

0000 0000

CCAP4H

XXXX XXXX

CCAP4L

XXXX XXXX

CCAPM4

X000 0000

UDPADDL

0000 0000

UEPSTAX

0000 0000

USBADDR

0000 0000

USBIEN

0000 0000

UDPADDH

0000 0000

UEPDATX

0000 0000

UEPNUM

0000 0000

IPH0

X000 0000

FFh

F7h

EFh

E7h

DFh

D7h

CFh

C7h

BFh

B7h

A8h

A0h

98h

90h

88h

80h

IE0

0000 0000

P2

1111 1111

SCON

0000 0000

P1

1111 1111

TCON

0000 0000

P0

1111 1111

0/8 1/9 2/A 3/ B 4/C 5/D 6/E 7/F

SADDR

0000 0000

SBUF

XXXX XXXX

TMOD

0000 0000

SP

0000 0111

AUXR1

XXXX X0X0

BRL

0000 0000

TL0

0000 0000

DPL

0000 0000

PLLCON

XXXX XX00

BDRCON

XXX0 0000

TL1

0000 0000

DPH

0000 0000

PLLDIV0

0000 0000

0000 0000

0000 0000

Note: 1. FCON access is reserved for the Flash API and ISP software.

KBLS

TH0

KBE

0000 0000

TH1

0000 0000

WDTRST

XXXX XXXX

KBF

0000 0000

AUXR

XX0X 0000

CKCON1

0000 0000

WDTPRG

XXXX X000

CKCON0

0000 0000

PCON

00X1 0000

AFh

A7h

9Fh

97h

8Fh

87h

4136A–USB–03/03

13

Page 14

The Special Function Registers (SFRs) of the AT89C5131 fall into the following

categories:

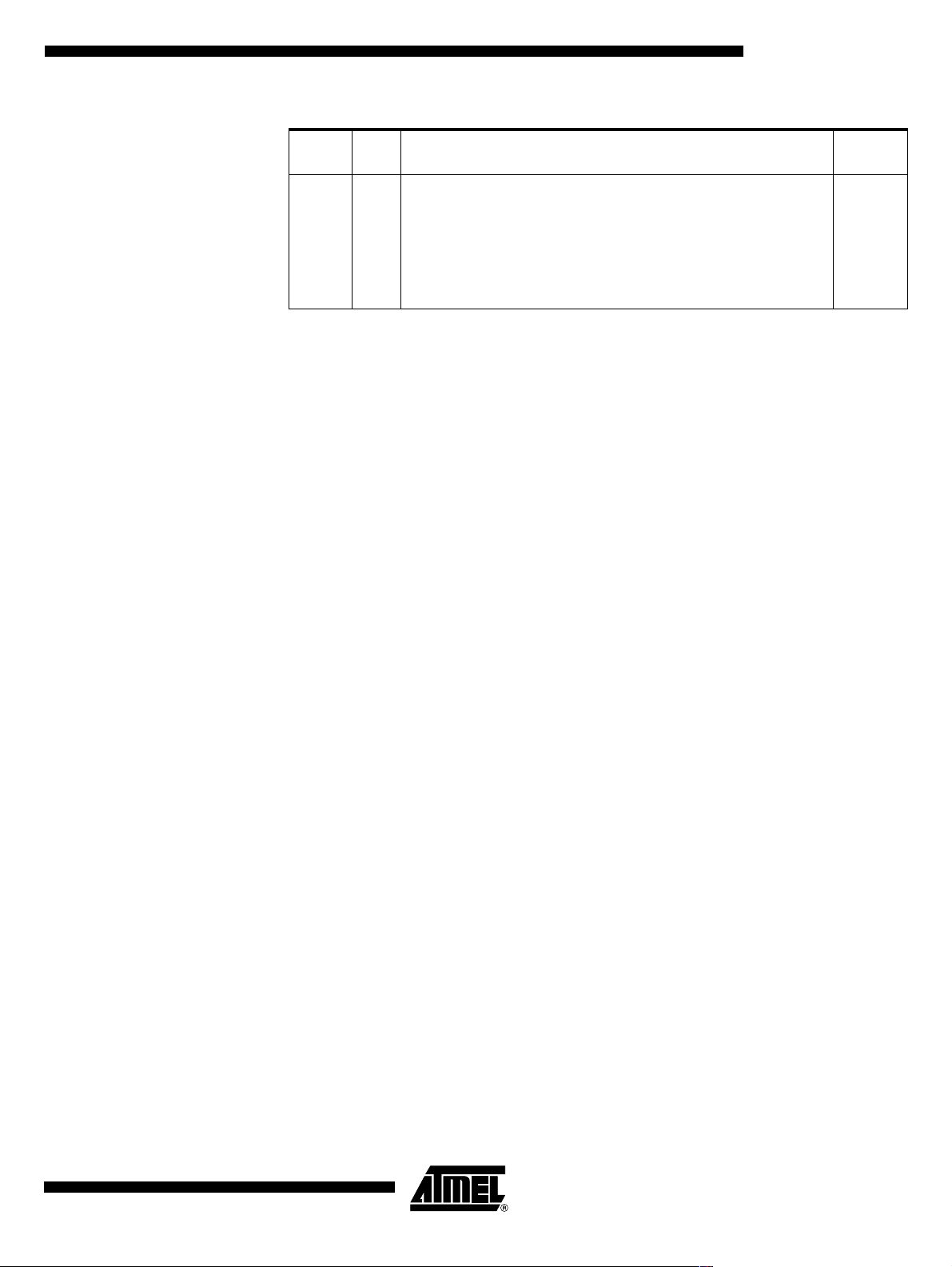

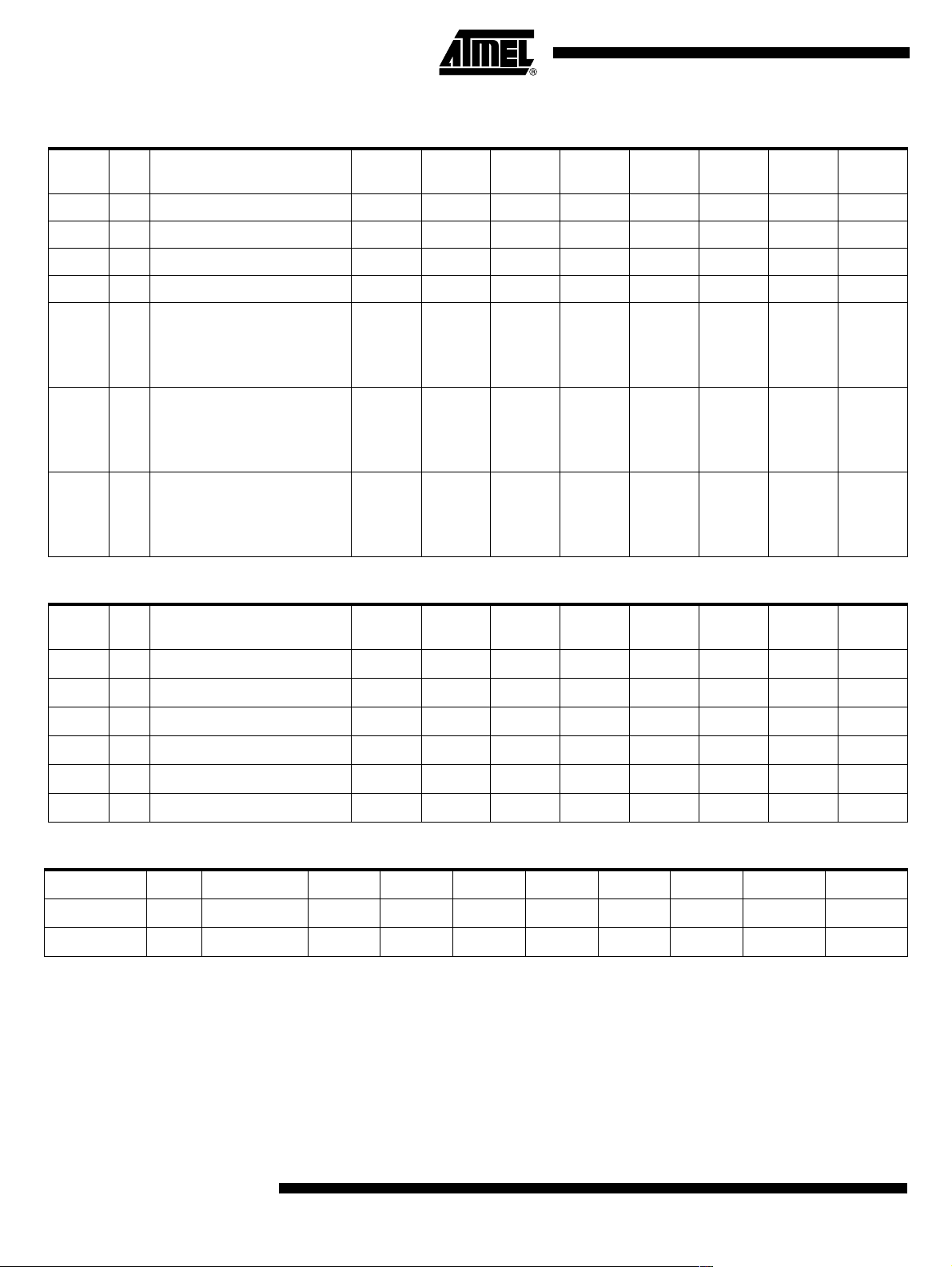

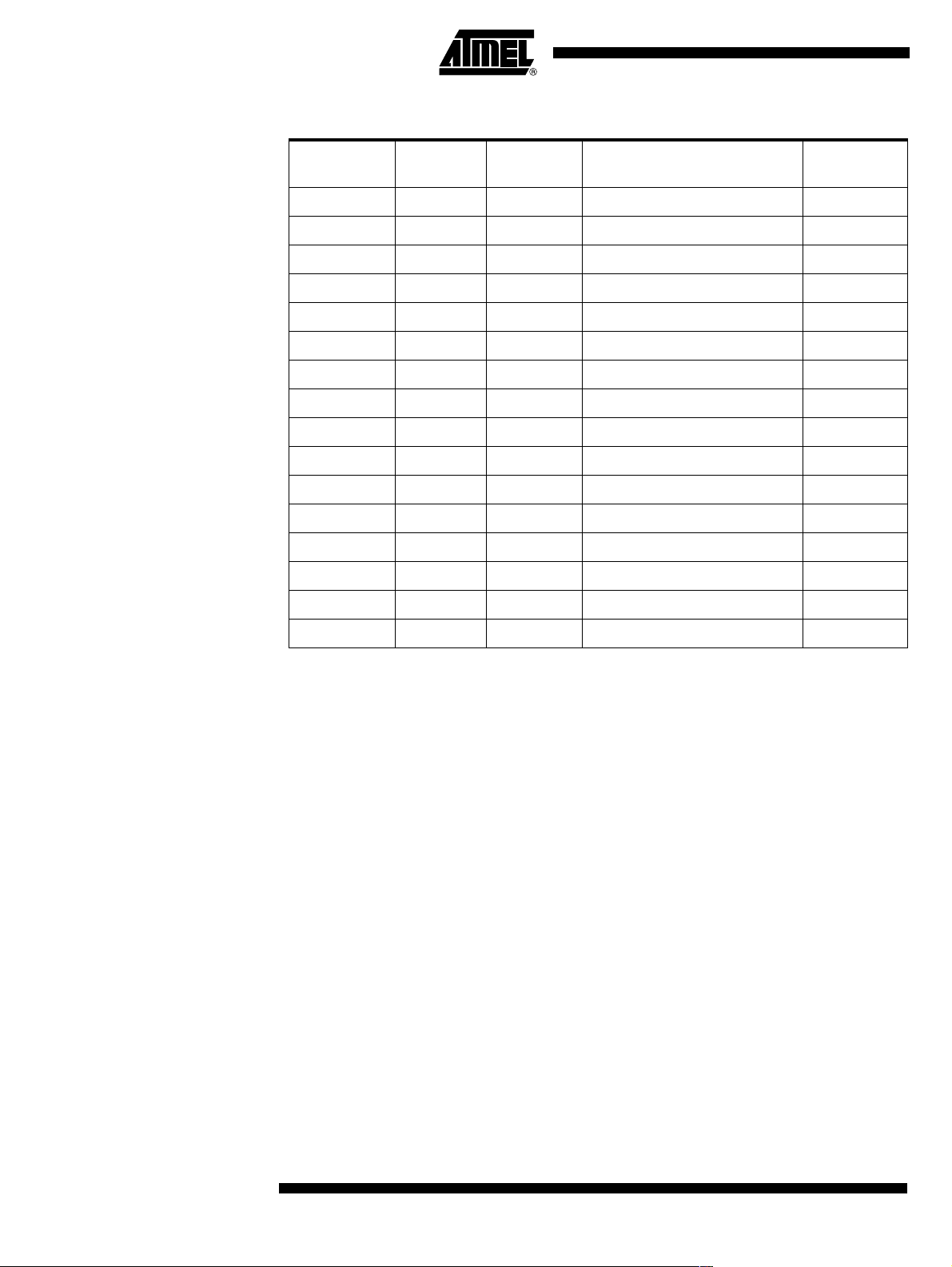

Table 13. C51 Core SFRs

MnemonicAddName 76543210

ACC E0h Accumulator

B F0h B Register

PSW D0h

SP 81h

DPL 82h

DPH 83h

Program Status

Word

Stack Po in ter

LSB of SPX

Data Pointer

Low byte

LSB of DPTR

Data Pointer

High byte

MSB of DPTR

Table 14. I/O Port SFRs

MnemonicAddName 76543210

P0 80h Port 0

P1 90h Port 1

P2 A0h Port 2

P3 B0h Port 3

P4 C0h Port 4 (x2)

14

AT89C5131

4136A–USB–03/03

Page 15

AT89C5131

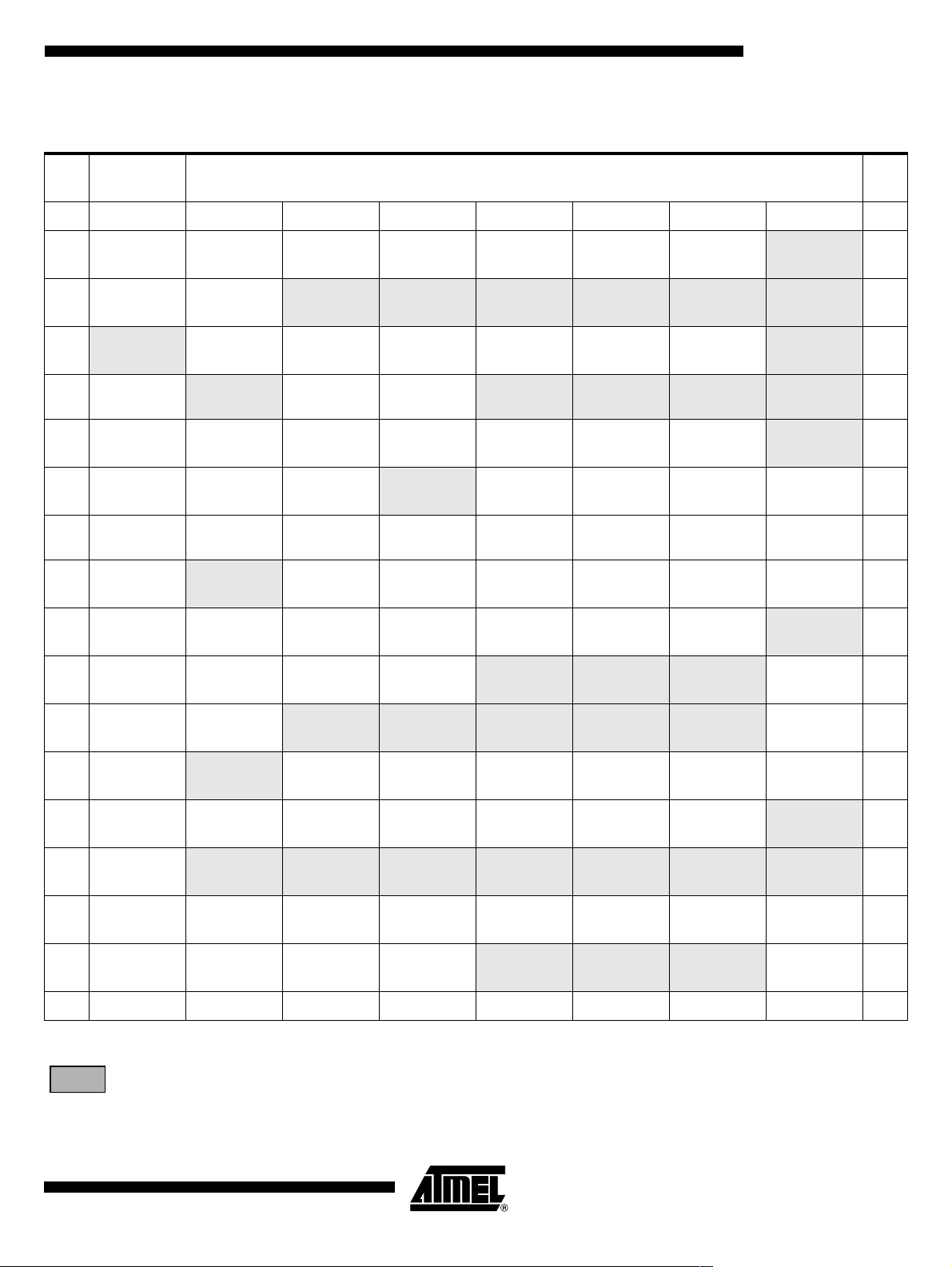

Table 15. Timer SFR’s

MnemonicAddName 76543210

TH0 8Ch Timer/Counter 0 High byte

TL0 8Ah Timer/Counter 0 Low byte

TH1 8Dh Timer/Counter 1 High byte

TL1 8Bh Timer/Counter 1 Low byte

TH2 CDh Timer/Counter 2 High byte

TL2 CCh Timer/Counter 2 Low byte

TCON 88h

TMOD 89h

T2CON C8h Timer/Counter 2 control TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2# CP/RL2#

T2MOD C9h Timer/Counter 2 Mode T2OE DCEN

RCAP2H CBh

RCAP2L CAh

WDTRST A6h WatchDog Timer Reset

WDTPRG A7h WatchDog Timer Program S2 S1 S0

Timer/Counter 0 and 1

control

Timer/Counter 0 and 1

Modes

Timer/Counter 2

Reload/Capture High byte

Timer/Counter 2

Reload/Capture Low byte

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

GATE1 C/T1# M11 M01 GATE0 C/T0# M10 M00

Table 16. Serial I/O Port SFR’s

MnemonicAddName 76543210

SCON 98h Serial Control FE/SM0 SM1 SM2 REN TB8 RB8 TI RI

SBUF 99h Serial Data Buffer

SADEN B9h Slave Address Mask

SADDR A9h Slave Address

Table 17. Baud Rate Generator SFR’s

MnemonicAddName 76543210

BRL 9Ah Baud Rate Reload

BDRCON 9Bh Baud Rate Control BRR TBCK RBCK SPD SRC

15

4136A–USB–03/03

Page 16

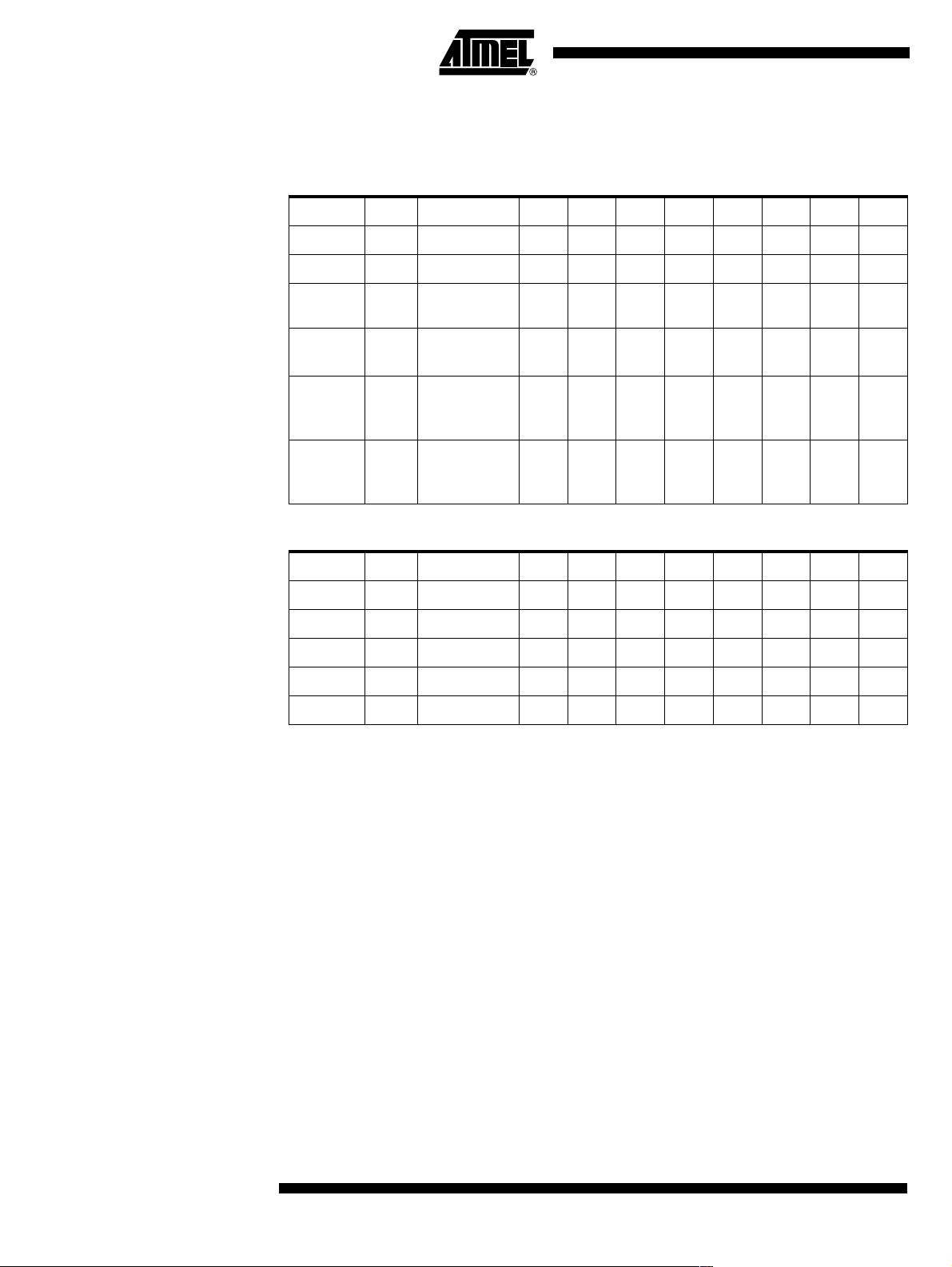

Table 18. PCA SFR’s

Mnemonic Add Name 7 6 5 4 3 2 1 0

CCON D8h PCA Timer/Counter Control CF CR CCF4 CCF3 CCF2 CCF1 CCF0

CMOD D9h PCA Timer/Counter Mode CIDL WDTE CPS1 CPS0 ECF

CL E9h PCA Timer/Counter Low byte

CH F9h PCA Timer/Counter High byte

CCAPM0

CCAPM1

CCAPM2

CCAPM3

CCAPM4

CCAP0H

CCAP1H

CCAP2H

CCAP3H

CCAP4H

CCAP0L

CCAP1L

CCAP2L

CCAP3L

CCAP4L

DAh

PCA Timer/Counter Mode 0

DBh

PCA Timer/Counter Mode 1

DCh

PCA Timer/Counter Mode 2

DDh

PCA Timer/Counter Mode 3

DEh

PCA Timer/Counter Mode 4

FAh

PCA Compare Capture Module 0 H

FBh

PCA Compare Capture Module 1 H

FCh

PCA Compare Capture Module 2 H

FDh

PCA Compare Capture Module 3 H

FEh

PCA Compare Capture Module 4 H

EAh

PCA Compare Capture Module 0 L

EBh

PCA Compare Capture Module 1 L

ECh

PCA Compare Capture Module 2 L

EDh

PCA Compare Capture Module 3 L

EEh

PCA Compare Capture Module 4 L

CCAP0H7

CCAP1H7

CCAP2H7

CCAP3H7

CCAP4H7

CCAP0L7

CCAP1L7

CCAP2L7

CCAP3L7

CCAP4L7

ECOM0

ECOM1

ECOM2

ECOM3

ECOM4

CCAP0H6

CCAP1H6

CCAP2H6

CCAP3H6

CCAP4H6

CCAP0L6

CCAP1L6

CCAP2L6

CCAP3L6

CCAP4L6

CAPP0

CAPP1

CAPP2

CAPP3

CAPP4

CCAP0H5

CCAP1H5

CCAP2H5

CCAP3H5

CCAP4H5

CCAP0L5

CCAP1L5

CCAP2L5

CCAP3L5

CCAP4L5

CAP0

CAP1

CAP2

CAP3

CAP4

CCAP0H4

CCAP1H4

CCAP2H4

CCAP3H4

CCAP4H4

CCAP0L4

CCAP1L4

CCAP2L4

CCAP3L4

CCAP4L4

MAT0

MAT1

MAT2

MAT3

MAT4

CCAP0H3

CCAP1H3

CCAP2H3

CCAP3H3

CCAP4H3

CCAP0L3

CCAP1L3

CCAP2L3

CCAP3L3

CCAP4L3

TOG0

TOG1

TOG2

TOG3

TOG4

CCAP0H2

CCAP1H2

CCAP2H2

CCAP3H2

CCAP4H2

CCAP0L2

CCAP1L2

CCAP2L2

CCAP3L2

CCAP4L2

PWM0

PWM1

PWM2

PWM3

PWM4

CCAP0H1

CCAP1H1

CCAP2H1

CCAP3H1

CCAP4H1

CCAP0L1

CCAP1L1

CCAP2L1

CCAP3L1

CCAP4L1

ECCF0

ECCF1

ECCF2

ECCF3

ECCF4

CCAP0H0

CCAP1H0

CCAP2H0

CCAP3H0

CCAP4H0

CCAP0L0

CCAP1L0

CCAP2L0

CCAP3L0

CCAP4L0

Table 19. Interrupt SFR’s

Mnemonic Add Name 7 6 5 4 3 2 1 0

IE0 A8h Interrupt Enable Control 0 EA EC ET2 ES ET1 EX1 ET0 EX0

IE1 B1h Interrupt Enable Control 1 EUSB ESPI EKB

IPL0 B8h Interrupt Priority Control Low 0 PPCL PT2L PSL PT1L PX1L PT0L PX0L

IPH0 B7h Interrupt Priority Control High 0 PPCH PT2H PSH PT1H PX1H PT0H PX0H

IPL1 B2h Interrupt Priority Control Low 1 PUSBL PSPIL PKBL

IPH1 B3h Interrupt Priority Control High 1 PUSBH PSPIH PK BH

Table 20. PLL SFRs

MnemonicAddName 765432 1 0

PLLCON A3h PLL Control PLLEN PLOCK

PLLDIV A4h PLL Divider R3 R2 R1 R0 N3 N2 N1 N0

16

AT89C5131

4136A–USB–03/03

Page 17

AT89C5131

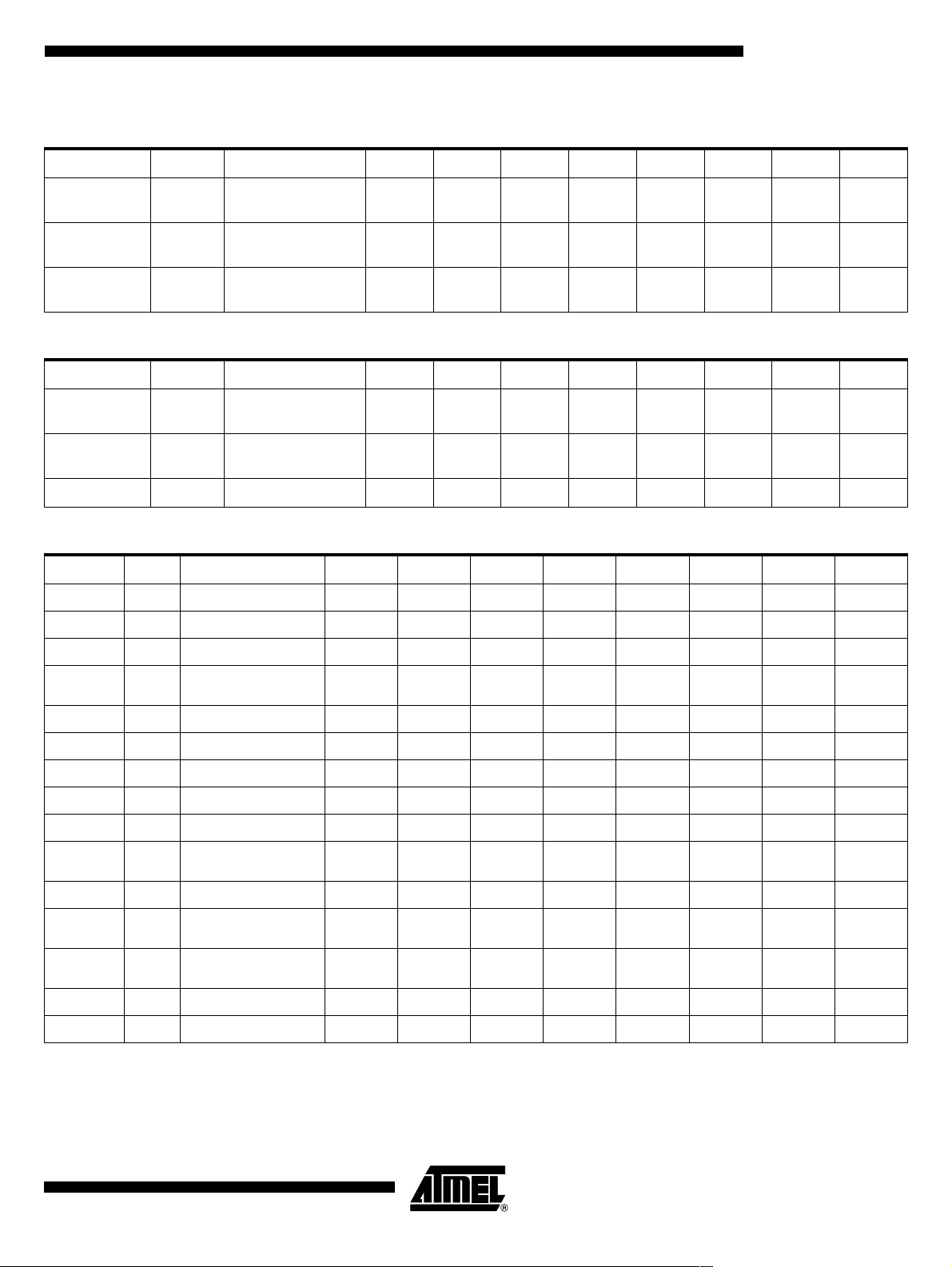

Table 21. Keyboard SFRs

MnemonicAddName 76543210

KBF 9Eh

KBE 9Dh

KBLS 9Ch

Keyboard Flag

Register

Keyboard Input Enable

Register

Keyboard Level

Selector Register

KBF7 KBF6 KBF5 KBF4 KBF3 KBF2 KBF1 KBF0

KBE7 KBE6 KBE5 KBE4 KBE3 KBE2 KBE1 KBE0

KBLS7 KBLS6 KBLS5 KBLS4 KBLS3 KBLS2 KBLS1 KBLS0

Table 22. SPI SFRs

MnemonicAddName 76543210

SPCON C3h

SPSTA C4h

Serial Peripheral

Control

Serial Peripheral

Status-Control

SPR2 SPEN SSDIS MSTR CPOL CPHA SPR1 SPR0

SPIF WCOL SSERR MODF - - - -

SPDAT C5h Serial Peripheral Data R7 R6 R5 R4 R3 R2 R1 R0

Table 23. USDB SFR’s

MnemonicAddName 76543210

USBCON BCh USB Global Control USBE SUSPCLK SDRMWUP DETACH UPRSM RMWUPE CONFG FADDEN

USBADDR C6h USB Address FEN UADD6 UADD5 UADD4 UADD3 UADD2 UADD1 UADD0

USBINT BDh USB Global Interrupt - - WUPCPU EORINT SOFINT - - SPINT

USBIEN BEh

USB Global Interrupt

Enable

- - EWUPCPU EEORINT ESOFINT - - ESPINT

UEPNUMC7hUSB Endpoint Number----EPNUM3EPNUM2EPNUM1EPNUM0

UEPCONX D4h USB Endpoint X Control EPEN - - - DTGL EPDIR EPTYPE1 EPTYPE0

UEPSTAX CEh USB Endpoint X Status DIR RXOUTB1 STALLRQ TXRDY STLCRC RXSETUP RXOUTB0 TXCMP

UEPRST D5h USB Endpoint Reset - EP6RST EP5 RST EP4RST EP3RST EP2RST EP1RST EP0RST

UEPINT F8h USB Endpoint Interrupt - EP6INT EP5INT EP4INT EP3INT EP2INT EP1INT EP0INT

UEPIEN C2h

UEPDATX CFh USB Endpoint X FIFO Data FDAT7 FDAT 6 FDAT5 FDAT4 FDAT3 FDAT2 FDAT1 FDAT0

UBYCTLX E2h

UBYCTHX E3h

UFNUML BAh USB Frame Number Low FNUM7 FNUM6 FNUM5 FNUM4 FNUM3 FNUM2 FNUM1 FNUM0

UFNUMH BBh USB Frame Number High - - CRCOK CRCERR - FNUM10 FNUM9 FNUM8

USB Endpoint Interrupt

Enable

USB Byte Counter Low (EP

X)

USB Byte Counter High

(EP X)

- EP6INTE EP5INTE EP4INTE EP3INTE EP2INTE EP1INTE EP0INTE

BYCT7 BYCT6 BYCT5 BYCT4 BYCT3 BYCT2 BYCT1 BYCT0

-----BYCT10BYCT9BYCT8

4136A–USB–03/03

17

Page 18

Table 24. Other SFR’s

MnemonicAddName 76543210

PCON 87h Power Control SMOD1 SMOD0 - POF GF1 GF0 PD IDL

AUXR 8Eh Auxiliary Register 0 DPU - M0 - XRS1 XRS2 EXTRAM A0

AUXR1 A2h Auxiliary Register 1 - - ENBOOT - GF3 - - DPS

CKCON0 8Fh Clock Control 0 - WDX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2

CKCON1AFhClock Control 1-------SPIX2

LEDCON F1h LED Control LED3 LED2 LED1 LED0

FCON D1h Flash Control FPL3 FPL2 FPL1 FPL0 FPS FMOD1 FMOD0 FBUSY

EECON D2h EEPROM Contol EEPL3 EEPL2 EEPL1 EEPL0 - - EEE EEBUSY

18

AT89C5131

4136A–USB–03/03

Page 19

AT89C5131

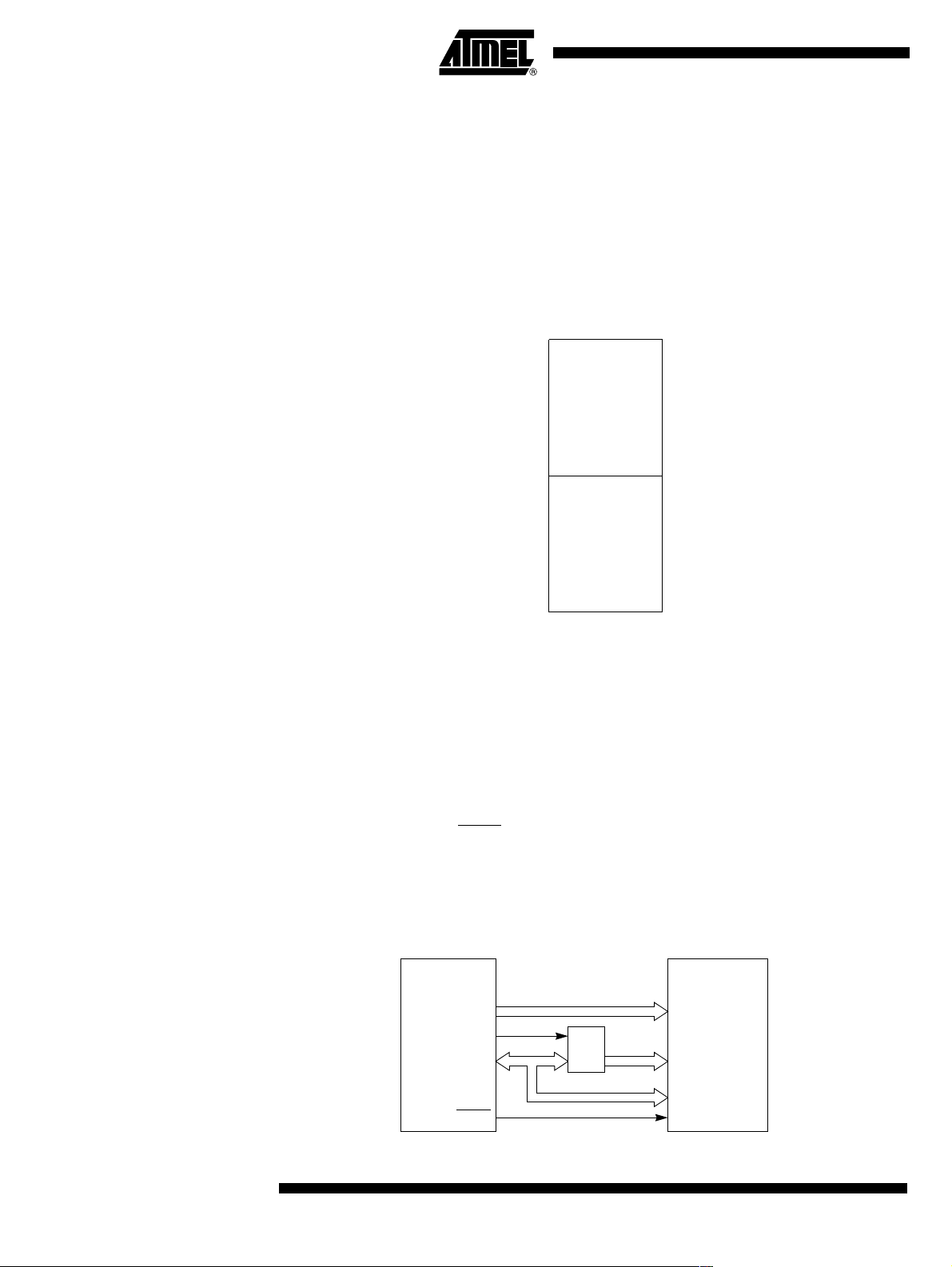

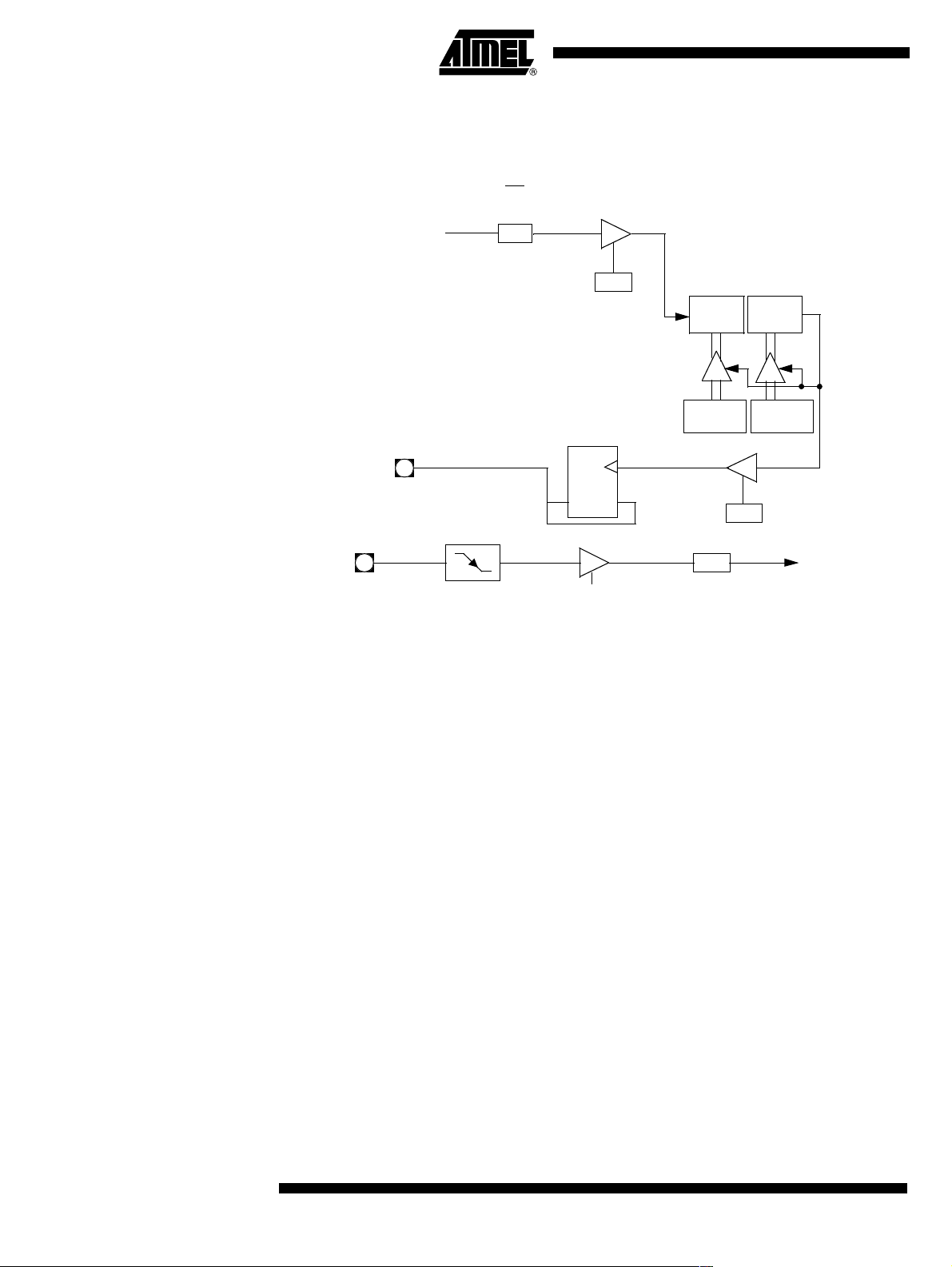

Clock Controller

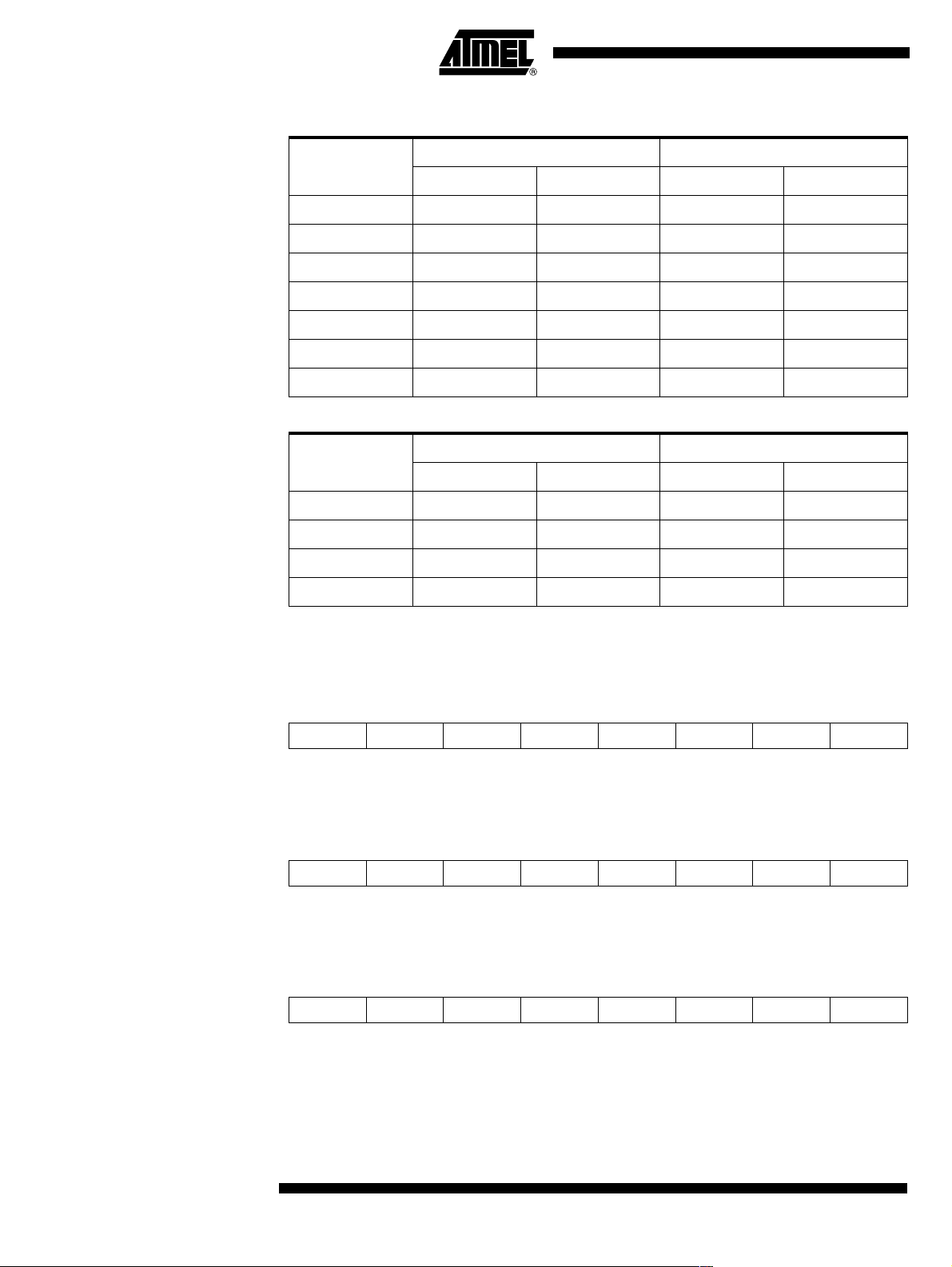

Introduction The AT89C5131 c lock co ntroller is based on an o n-chip oscillat or feedin g an on- chip

Phase Lock Loop (PLL). All the internal clocks to the peripherals and CPU core are generated by this controller.

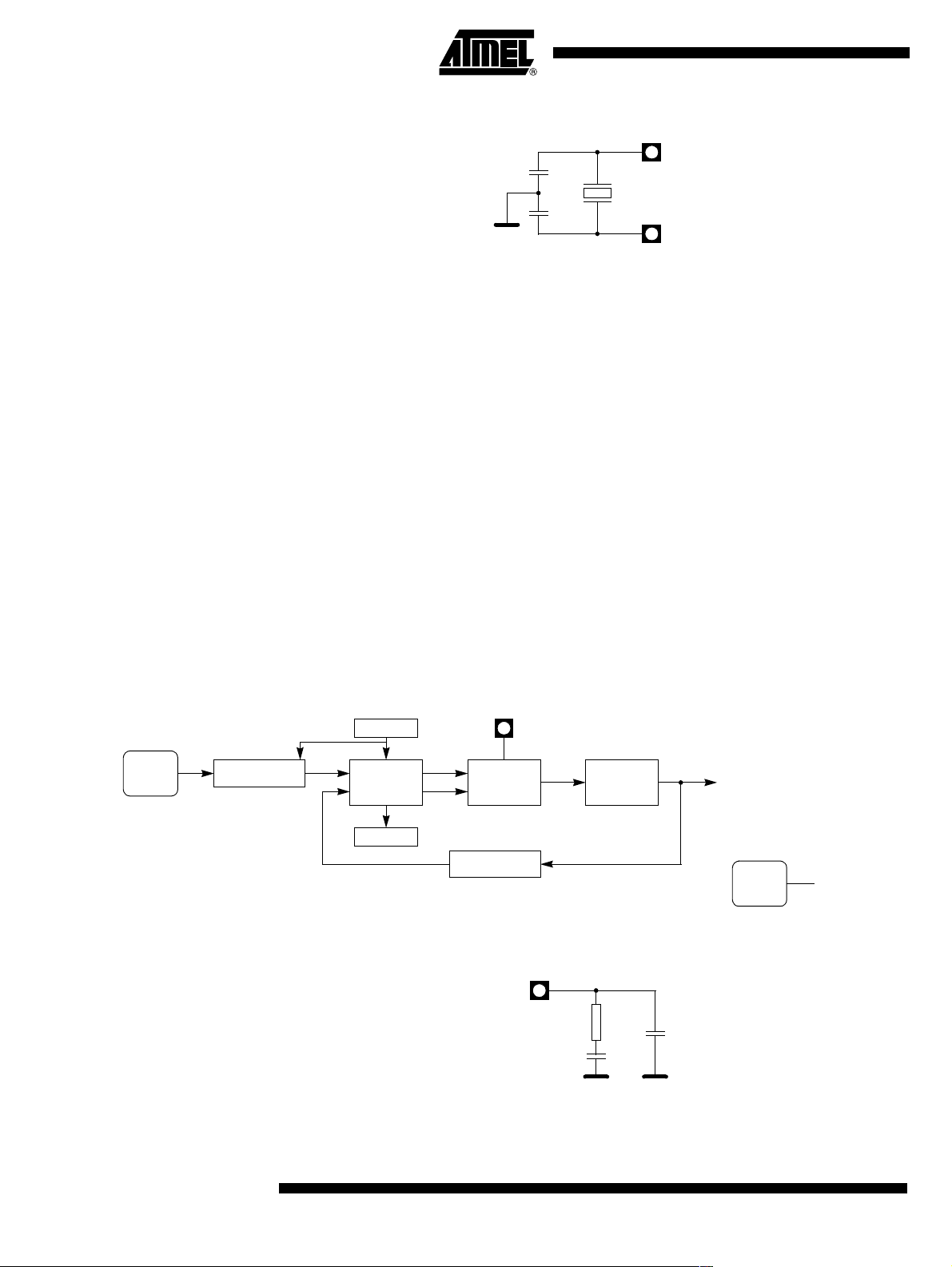

The AT89C5131 X1 and X2 pins are the input and the output of a single-stage on-chip

inverter (see Figure 5) that can be configured with off-chip components as a Pierce

oscillator (see Figure 6). Value of capacitors and crystal characteristics are detailed in

the section “DC Characteristics”.

The clock controller outputs three different clocks as shown in Figure 5:

• a clock for the CPU core

• a clock for the peripherals which is used to generate the Timers, PCA, WD, and Port

sampling clocks

• a clock for the USB controller

These clocks are enabled or disabled depending on the power reduction mode as

detailed in Section “Power Management”, page 145.

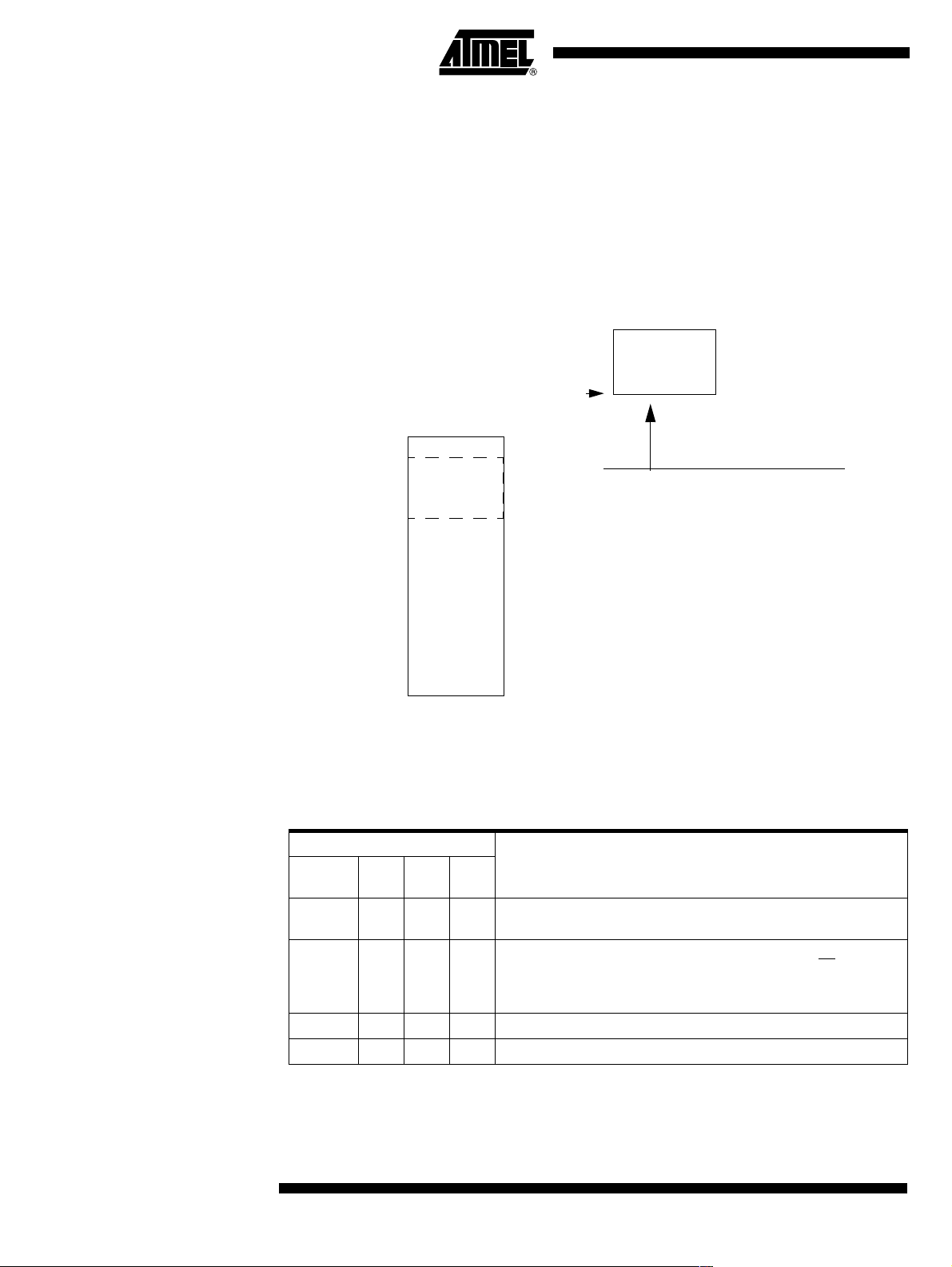

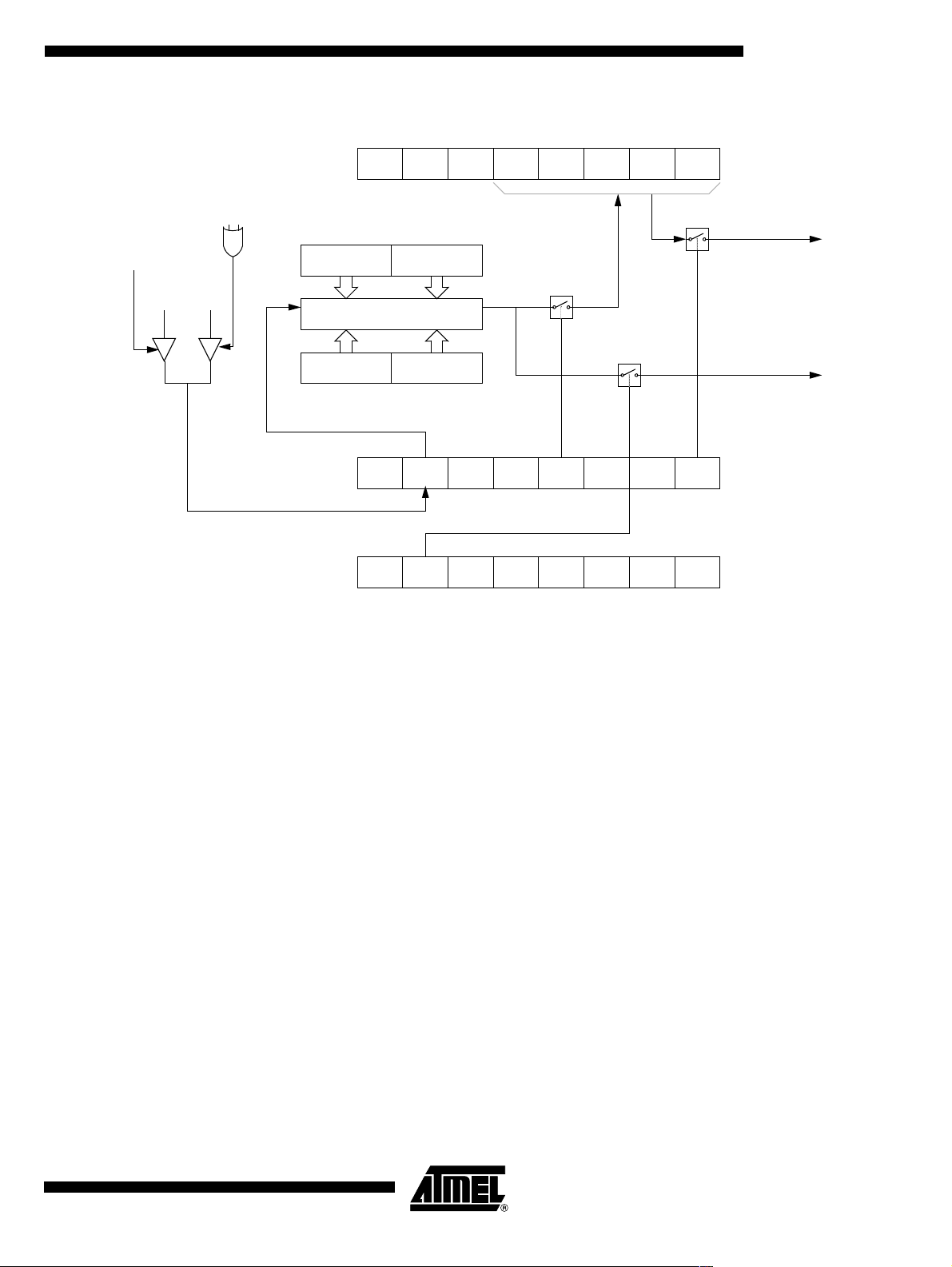

Figure 5. Oscillator Block Diagram

÷ 2

X1

X2

PD

PCON.1

PLL

Oscillator Two clock sources are available for CPU:

• Crystal oscillator on X1 and X2 pins: Up to 32 MHz

In order to optimize the power consumption, the oscillator inverter is inactive when the

PLL output is not selected for the USB device.

0

1

X2

CKCON.0

Peripheral

Clock

CPU Core

Clock

IDL

PCON.0

USB

Clock

4136A–USB–03/03

19

Page 20

Figure 6. Crystal Connection

X1

C1

Q

C2

VSS

X2

PLL

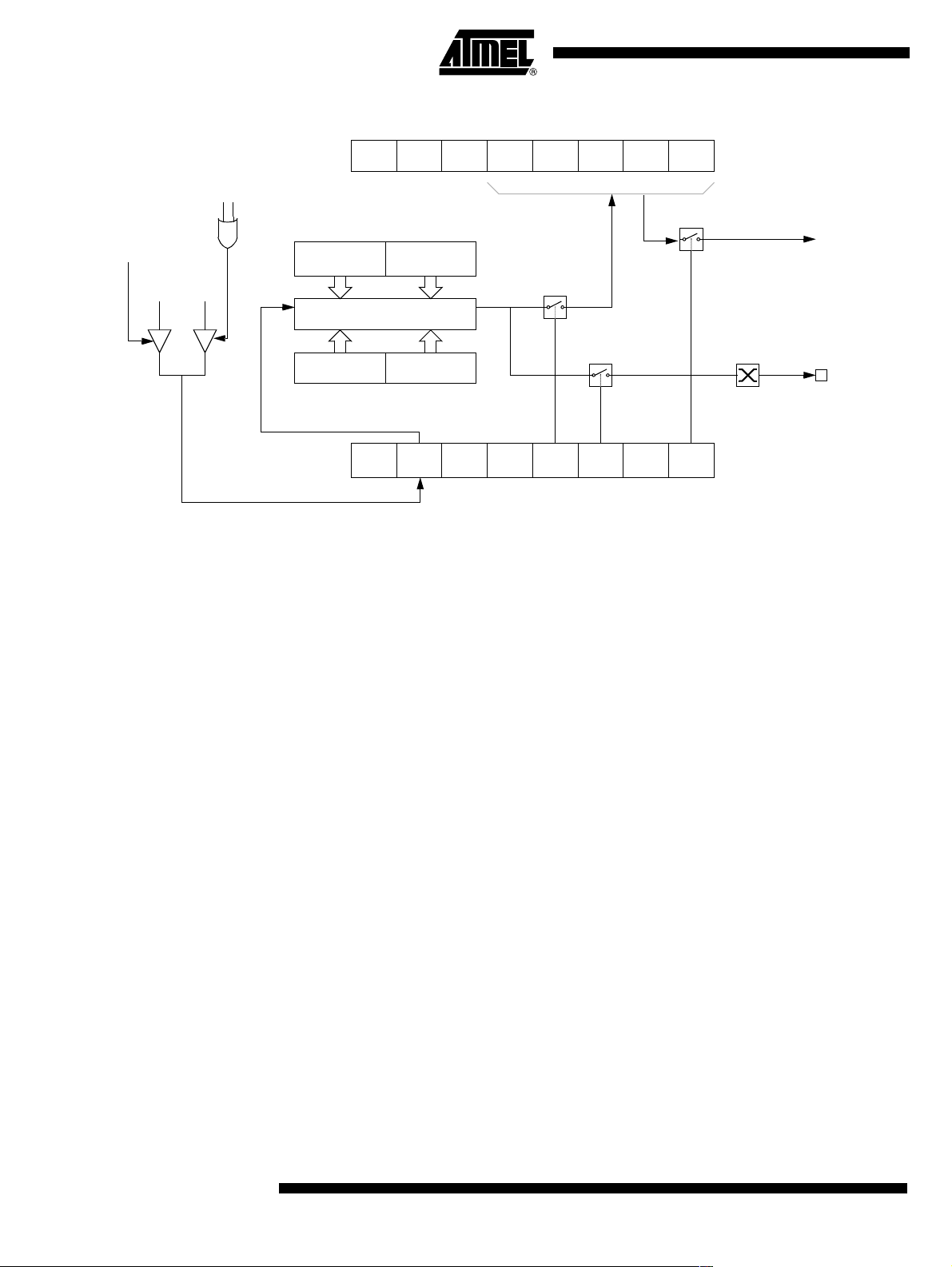

PLL Description The AT89 C513 1 P LL is us ed to gen er ate int ernal hi gh f re que ncy c lo ck ( the USB Cl ock)

synchronized with an external low-frequency (the Perip heral Clock) . The PLL c lock is

used to generate the USB interface clock. Figure 7 shows the internal structure of the

PLL.

The PFLD block is the Phase Frequency Comparator and Lock Detector. This block

makes the comparison between the reference clock coming from the N divider and the

reverse clock coming from the R divider and generates some pulses on the Up or Down

signal dependin g on the edge posi tion of the r everse c lock. The P LLEN bit in PLLCO N

register is used to enab le the c lock gene ratio n. When the PLL is l ocked, th e bit PL OCK

in PLLCON register (see Figure 7) is set.

The CHP block is the Charge Pump that generates the voltage reference for the VCO by

injecting or extracting charges from the external filter connected on PLLF pin (see

Figure 8). Value of the filter components are detailed in the Section “DC

Characteristics”.

The VCO block is the Voltage Controlled Oscillator controlled by the voltage V

duced by the charge pump. It generates a square wave signal: the PLL clock.

Figure 7. PLL Block Diagram and Symbol

OSC

CLOCK

N divider

N3:0

Figure 8. PLL Filter Connection

PLLCON.1

PLLEN

PFLD

PLOCK

PLLCON.0

USBclk

Up

Down

OSCclk R 1+()×

-----------------------------------------------=

PFILT

CHP

R divider

R3:0

N1+

PFILT

Vref

VCO USB Clock

CLOCK

USB Clock Symbol

R

C1

VSS

C2

VSS

USB

REF

pro-

20

The typical values are: R = 100 Ω, C1 = 10 nf, C2 = 2.2 nF.

AT89C5131

4136A–USB–03/03

Page 21

AT89C5131

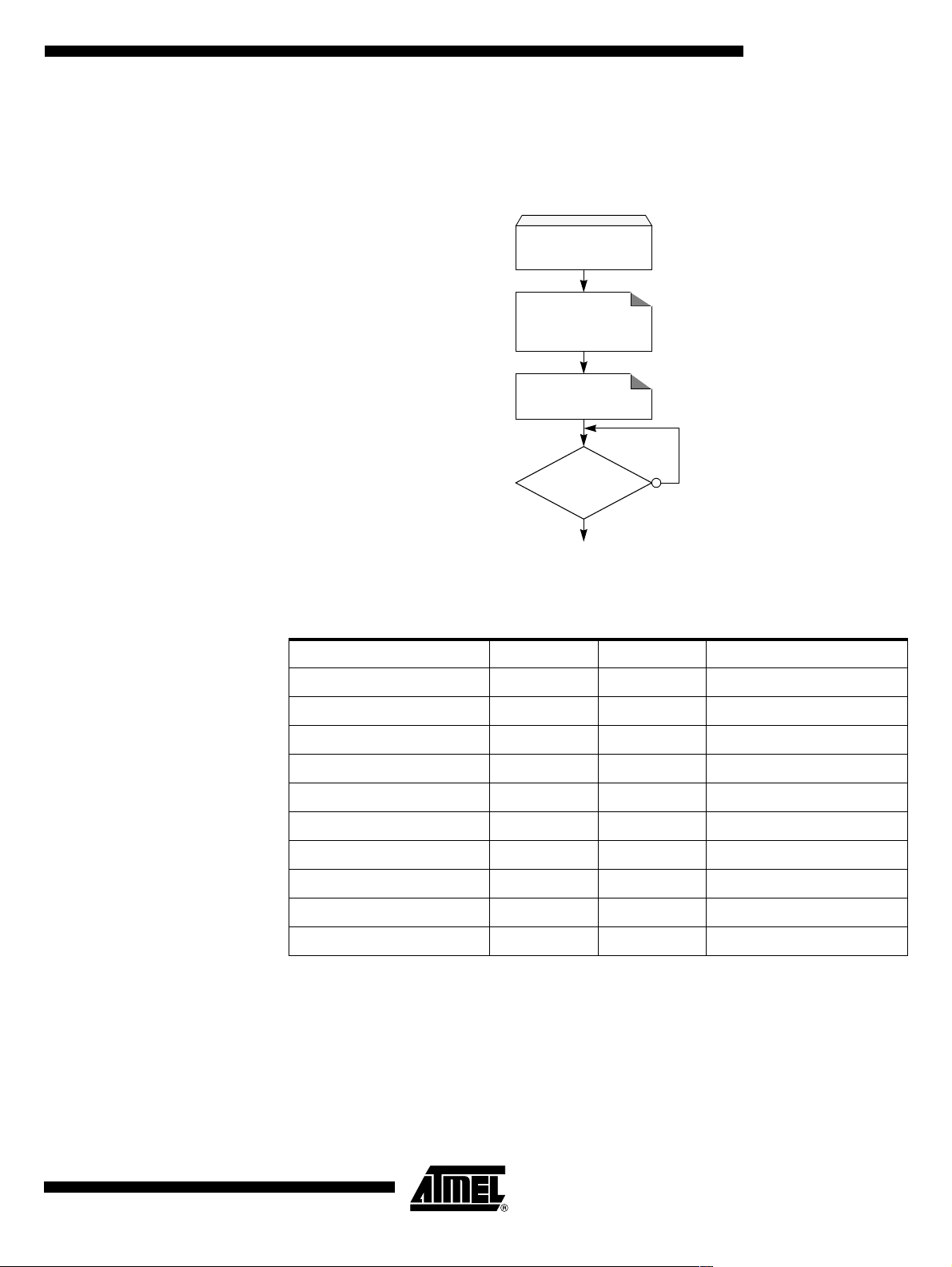

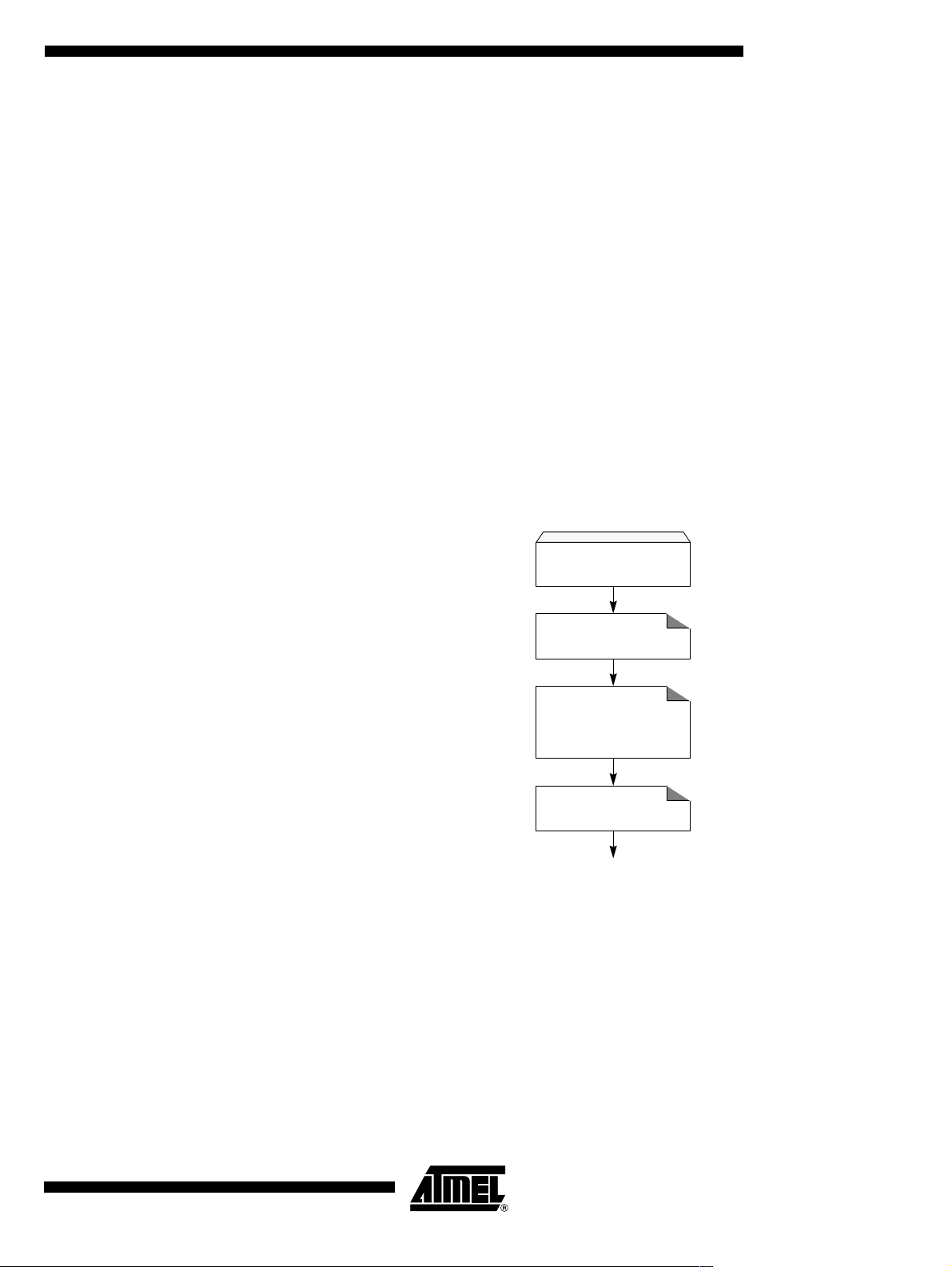

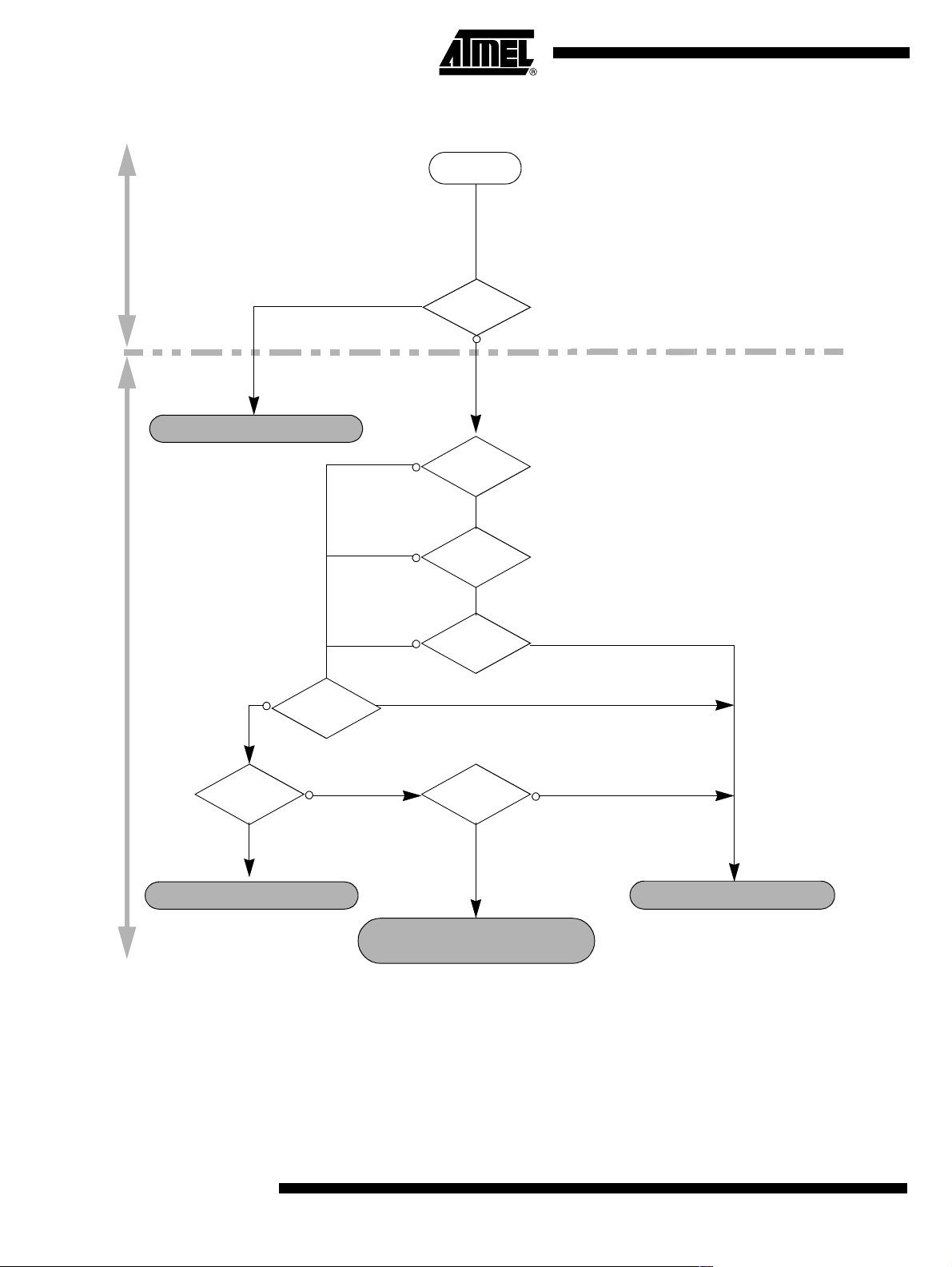

PLL Programming The PLL is progra mmed u sing the flo w sho wn in Figure 9. As s oon as clock gene ratio n

is enabled user must wait until the lock indicator is set to ensure the clock output is

stable.

Figure 9. PLL Programming Flow

PLL

Programming

Configure Dividers

N3:0 = xxxxb

R3:0 = xxxxb

Enable PLL

PLLEN = 1

PLL Locked?

LOCK = 1?

Divider Values To generate a 48 MHz clock using the PLL, the divider values have to be configured fol-

lowing the oscillator frequency. The typical divider values are shown in Table 25.

Table 25. Typical Divider Values

Oscillator Frequency R+1 N+1 PLLDIV

3 MHz 16 1 F0h

6 MHz 8 1 70h

8 MHz 6 1 50h

12 MHz 4 1 30h

16 MHz 3 1 20h

18 MHz 8 3 72h

20 MHz 12 5 B4h

24 MHz 2 1 10h

32 MHz 3 2 21h

40 MHz 12 10 B9h

4136A–USB–03/03

21

Page 22

Registers Table 26. CKCON0 (S:8Fh)

Clock Control Register 0

76543210

- WDX2 PCAX2 SIX2 T2X2 T1X2 T0X2 X2

Bit Number

7-

6WDX2

5PCAX2

4SIX2

3T2X2

2T1X2

Bit

Mnemonic Description

Reserved

The value read from this bit is always 0. Do not set this bit.

Watchdog Clock

This control bit is validated when the CPU clock X2 is set. When X2 is low,

this bit has no effect.

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Programmable Counter Array Clock

This control bit is validated when the CPU clock X2 is set. When X2 is low,

this bit has no effect.

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Enhanced UART Clock (Mode 0 and 2)

This control bit is validated when the CPU clock X2 is set. When X2 is low,

this bit has no effect.

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer2 Clock

This control bit is validated when the CPU clock X2 is set. When X2 is low,

this bit has no effect.

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer1 Clock

This control bit is validated when the CPU clock X2 is set. When X2 is low,

this bit has no effect.

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

22

AT89C5131

Timer0 Clock

This control bit is validated when the CPU clock X2 is set. When X2 is low,

1T0X2

0X2

this bit has no effect.

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

System Clock Control bit

Clear to select 12 clock periods per machine cycle (STD mode, F

F

OSC

Set to select 6 clock periods per machine cycle (X2 mode, F

Reset Value = 0000 0000b

/2).

= F

CPU

PER =

CPU = FPER = FOSC

4136A–USB–03/03

).

Page 23

AT89C5131

Table 27. CKCON1 (S:AFh)

Clock Control Register 1

76543210

-------SPIX2

Bit Number

7-1 -

0 SPIX2

Bit

Mnemonic Description

Reserved

The value read from this bit is always 0. Do not set this bit.

SPI Clock

This control bit is validated when the CPU clock X2 is set. When X2 is low,

this bit has no effect.

Clear to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Reset Value = 0000 0000b

Table 28. PLLCON (S:A3h)

PLL Control Register

76543210

------PLLENPLOCK

Bit

Bit Number

7-3 -

Mnemonic Description

Reserved

The value read from this bit is always 0. Do not set this bit.

2-

Reserved

The value read from this bit is always 0. Do not set this bit.

PLL Enable Bit

1 PLLEN

0PLOCK

Set to enable the PLL.

Clear to disable the PLL.

PLL Lock Indicator

Set by hardware when PLL is locked.

Clear by hardware when PLL is unlocked.

Reset Value = 0000 0000b

Table 29. PLLDIV (S:A4h)

PLL Divider Register

76543210

R3 R2 R1 R0 N3 N2 N1 N0

Bit

Bit Number

7-4 R3:0 PLL R Divider Bits

3-0 N3:0 PLL N Divider Bits

Mnemonic Description

Reset Value = 0000 0000

4136A–USB–03/03

23

Page 24

Dual Data Pointer Register

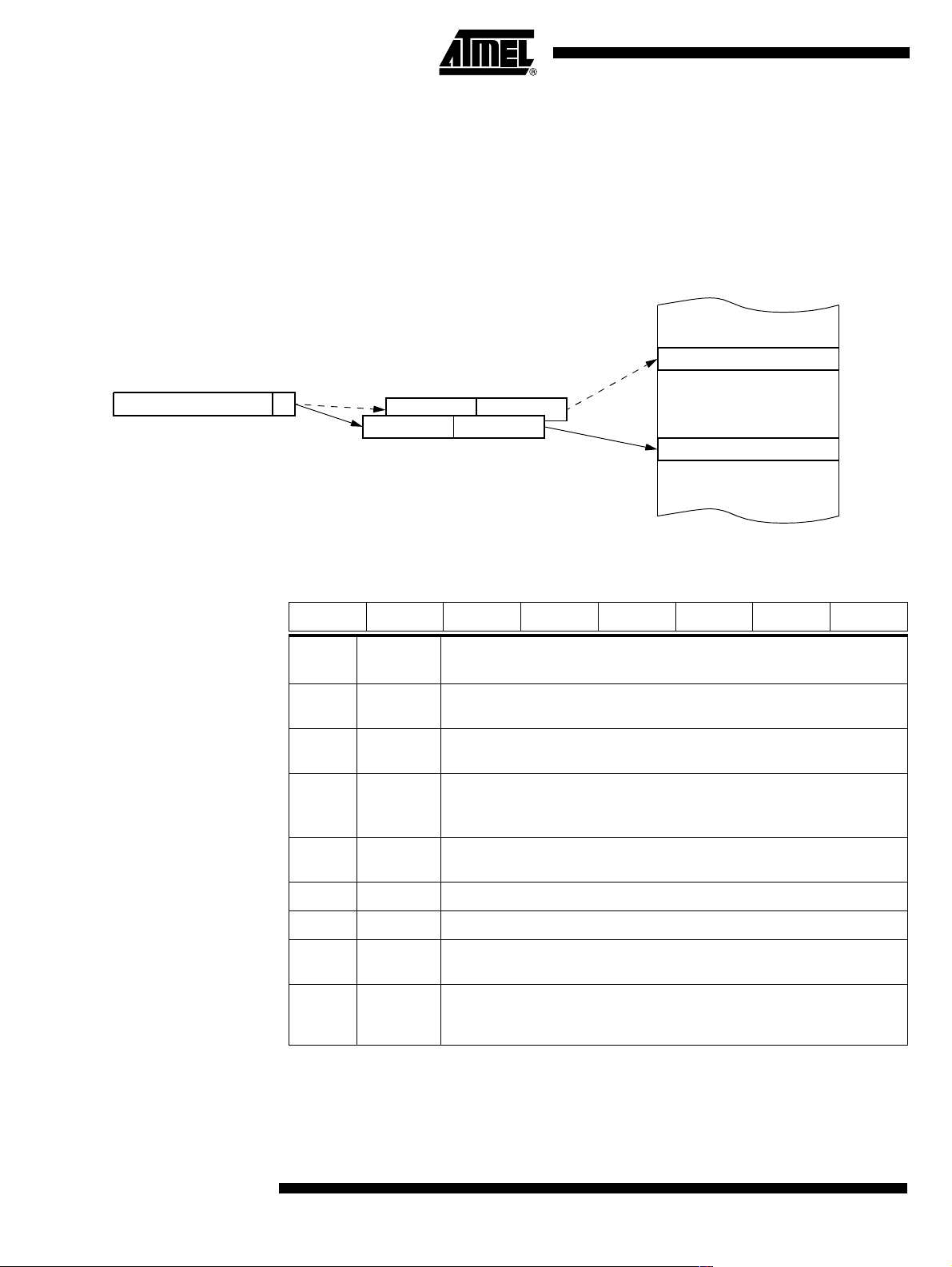

Figure 10. Use of Dual Pointer

AUXR1(A2H)

The additional data pointer can be used to speed up code execution and reduce code

size.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external

memory, and a single bit called DPS = AUXR1.0 (see Table 30) that allows the program

code to switch between them (see Figure 10).

External Data Memory

07

DPS

DPTR1

DPTR0

DPH(83H) DPL(82H)

Table 30. AUXR1 Register

AUXR1- Auxiliary Register 1(0A2h)

76543210

- - ENBOOT - GF3 0 - DPS

Bit

Number

7-

6-

5 ENBOOT

4-

3 GF3 This bit is a general-purpose user flag.

2 0 Always cleared.

1-

0DPS

Bit

Mnemonic Description

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Enable Boot Flash

Cleared to disable boot ROM.

Set to map the boot ROM between F800h - 0FFFFh.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Data Pointer Selection

Cleared to select DPTR0.

Set to select DPTR1.

Reset Value = XXXX XX0X0b

Not bit addressable

24

a. Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

AT89C5131

4136A–USB–03/03

Page 25

AT89C5131

ASSEMBLY LANGUAGE

; Block move using dual data pointers

; Modifies DPTR0, DPTR1, A and PSW

; note: DPS exits opposite of entry state

; unless an extra INC AUXR1 is added

;

00A2 AUXR1 EQU 0A2H

;

0000 909000MOV DPTR,#SOURCE ; address of SOURCE

0003 05A2 INC AUXR1 ; switch data pointers

0005 90A000 MOV DPTR,#DEST ; address of DEST

0008 LOOP:

0008 05A2 INC AUXR1 ; switch data pointers

000A E0 MOVX A,@DPTR ; get a byte from SOURCE

000B A3 INC DPTR ; increment SOURCE address

000C 05A2 INC AUXR1 ; switch data pointers

000E F0 MOVX @DPTR,A ; write the byte to DEST

000F A3 INC DPTR ; increment DEST address

0010 70F6JNZ LOOP ; check for 0 terminator

0012 05A2 INC AUXR1 ; (optional) restore DPS

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1

SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, bu t simply togg les it. In simple routines , such as the block mov e examp le,

only the fact that DPS is togg led in th e pr op er se quen ce matt er s, n ot i ts a ctu al val ue. In

other words, th e block m ove rout ine wor ks the sa me wheth er DPS is ’0’ or ’1’ on entry.

Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in

the opposite state.

4136A–USB–03/03

25

Page 26

Program/Code Memory

The AT89C5131 implement 32 Kbytes of on-ch ip program/code memory. Figure 11

shows the split of internal and external program/code memory spaces depending on the

product.

The Flash memory increa ses EP ROM and ROM func tional ity by in-cir cui t electric al erasure and programming. Thanks to the internal charge pump, the high voltage needed for

programming or erasing Flash ce lls is gene rated on-chip usi ng the standard V

DD

voltage. Thus, the Flash Memory can be programmed using only one voltage and allows Inapplication Softwa re Progr amming c ommonly known as IAP. Ha rdware programm ing

mode is also available using specific programming tool.

Figure 11. Program/Code Memory Organization

FFFFh

32 Kbytes

External Code

8000h

7FFFh1

32 Kbytes

Flash

0000h

Note: If the program executes exclusively from on-chip code memory (not from external mem-

ory), beware of executing code from the upper byte of on-chip memory (7FFFh) and

thereby disrupting I/O Ports 0 and 2 due to external prefetch. Fetching code constant

from this location does not affect Ports 0 and 2.

AT89C5131

External Code Memory Access

Memory Interfac e The external memory interface comprises the external bus (Port 0 and Port 2) as well as

the bus control signals (PSEN

Figure 12 shows the structure of the external address bus. P0 carries address A7:0

while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0. Table 31

describes the external memory interface signals.

Figure 12. External Code Memory Interface Structure

AT89C5131

, and ALE).

P2

ALE

P0

AD7:0

A15:8

Latch

A7:0

Flash

EPROM

A15:8

A7:0

26

D7:0

OEPSEN

AT89C5131

4136A–USB–03/03

Page 27

Table 31. External Data Memory Interface Signals

Signal

Name Type Description

AT89C5131

Alternate

Function

A15:8 O

AD7:0 I/O

ALE O

PSEN

Address Lines

Upper address lines for the external bus.

Address/Data Lines

Multiplexed lower address lines and data for the external memory.

Address Latch Enable

ALE signals indicates that valid address information are available on lines

AD7:0.

Program Store Enable Output

O

This signal is active low during external code fetch or external code read

(MOVC instruction).

P2.7:0

P0.7:0

-

-

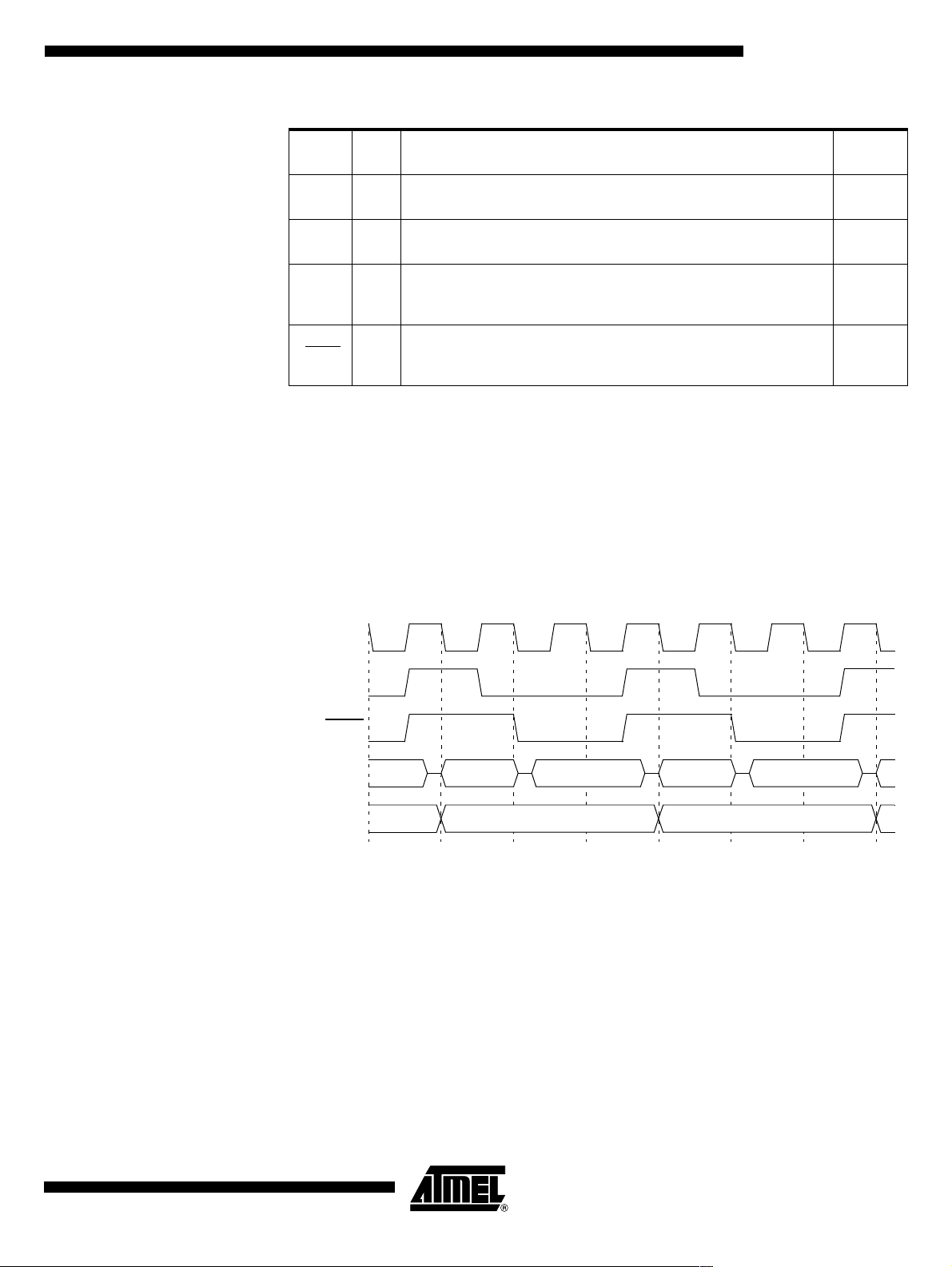

External Bus Cycles This section describes the bus cycles the AT89C5131 executes to fetch code (see

Figure 13) in the external program/code memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator

clock periods in standard mode or 6 oscillator clock periods in X2 mode. For further

information on X2 mode (see the clock Section).

For simplicity, the accompanying figure depicts the bus cycle waveforms in idealized

form and do not provide precise timing information.

Figure 13. External Code Fetch Waveforms

CPU Clock

Flash Memory Architecture

ALE

PSEN

P0

P2

D7:0

PCL

PCHPCH

PCLD7:0 D7:0

PCH

AT89C5131 features two on-chip Flash memories:

• Flash memory FM0:

containing 32 Kbytes of program memory (user space) organized into 128-byte

pages,

• Flash memory FM1:

3 Kbytes for bootloader and Application Programming Interfaces (API).

The FM0 supports both paral lel progra mming and Serial In- System Progr ammi ng (IS P)

whereas FM1 supports on ly parallel pr ogramming by progr ammers. The IS P mode is

detailed in the “In-System Programming” section.

All Read/Write access operations on Flash memory by user application are managed by

a set of API described in the “In-System Program mi ng” section.

4136A–USB–03/03

27

Page 28

Figure 14. Flash Memory Architecture

Hardware Security (1 Byte)

Extra Row (128 Bytes)

Column Latches (128 Bytes)

3 Kbytes

Flash Memory

Boot Space

FM1

FFFFh

F400h

7FFFh

32 Kbytes

Flash Memory

User Space

FM0

FM1 mapped between FFFFh and

F400h when bit ENBOOT is set in

AUXR1 re gister

0000h

FM0 Memory Architecture The Flash memory is made up of 4 blocks (see Figure 14):

1. The memory array (user space) 32 Kbytes

2. The Extra Row

3. The Hardware security bits

4. The column latch registers

User Space This space is composed of a 32 Kbytes Flash memory organized in 256 pages of 128

bytes. It contains the user’s application code.

Extra Row (XRow ) This row is a part of FM0 and has a size of 12 8 bytes . The extra r ow may c ontain info r-

mation for bootloader usage.

Hardware Security Space The hardware security space is a part of FM0 and has a size of 1 byte.

The 4 MSB can be read/written by software. Th e 4 LSB can only be read by softwar e

and written by hardware in parallel mode.

Column Latches The column latches, also part of FM0, have a size of full page (128 bytes).

The column latches are the entrance buffers of the three previous memory locations

(user array, XRow and Hardware security byte).

Overview of FM0 Operations

The CPU interfaces to the Flash memor y through the FCON register and AUX R1

register.

These registers are used to:

• Map the memory spaces in the adressable space

• Launch the programming of the memory spaces

• Get the status of the Flash memory (busy/not busy)

• Select the Flash memory FM0/FM1.

Mapping of the Memory Space By default, the user space is accessed by MOVC instruction for read only. The column

latches space is made accessible by setting the FPS bit in FCON register. Writing is

possible from 0000h to 7FFFh, address bits 6 to 0 are used to select an address within a

page while bits 14 to 7 are used to select the programming address of the page.

Setting this bit takes precedence on the EXTRAM bit in AUXR register.

28

AT89C5131

4136A–USB–03/03

Page 29

AT89C5131

The other memory spaces (user, extra row, hardware security) are made accessible in

the code segment by programming bits FMOD0 and FMOD1 in FCON register in accordance with Table 32. A MOVC instruction is then used for reading these spaces.

Table 32. FM0 Blocks Select Bits

FMOD1 FMO D0 FM0 Adressable Space

0 0 User (0000h-FFFFh)

0 1 Extra Row(FF80h-FFFFh)

1 0 Hardware Security (0000h)

1 1 reserved

Launching Programming FPL3:0 bits in FCON r egist er are us ed to sec ure th e launch o f prog ramming . A spe cific

sequence must be written in these bits to unlock the write protection and to launch the

programming. This sequence i s 5 followed by A. Table 33 summarizes the memor y

spaces to program according to FMOD1:0 bits.

Table 33. Programming Spaces

Write to FCON

OperationFPL3:0 FPS FMOD1 FMOD0

5 X 0 0 No action

User

Extra Row

Security

Space

Reserved

AX00

5 X 0 1 No action

AX01

5 X 1 0 No action

A X 1 0 Write the fuse bits space

5 X 1 1 No action

A X 1 1 No action

Write the column latches in user

space

Write the column latches in extra row

space

The Flash memory enters a busy state as soon as programming is launched. In this

state, the memory is not avail abl e for fetc hi ng code. T hus to avoid any erra tic exe cu tio n

during programming, the CPU enters Idle mode. Exit is automatically performed at the

end of programming.

Note: Interrupts that may oc cur during programming time must be disabled to avoid any spuri-

ous exit of the idle mode.

Status of the Flash Memory The bit FBUSY in FCON register is used to indicate the status of programming.

FBUSY is set when programming is in progress.

Selecting FM0/FM1 The bit ENBOOT in AUXR1 register i s used to ch oose between FM0 and FM1 mappe d

up to F800h.

29

4136A–USB–03/03

Page 30

Loading the Column Latches Any nu mbe r of data from 1 byte to 128 bytes c an be load ed in the co lu mn latches . This

provides the capability to program the whole memory by byte, by page or by any number

of bytes in a page.

When progra mmin g is laun ched, a n aut omati c erase of the loc atio ns load ed in th e col umn latches is fi rst per formed, then pr ogrammi ng is eff ectiv ely done . Thus, n o page or

block erase is needed and only the loaded data are programmed in the corresponding

page.

The following procedure is used to load the column latches and is summarized in

Figure 15:

• Map the column latch space by setting FPS bit.

• Load the DPTR with the address to load.

• Load Accumulator register with the data to load.

• Execute the MOVX @DPTR, A instruction.

• If needed loop the three last instructions until the page is completely loaded.

Figure 15. Column Latches Loading Procedure

Column Latches

Loading

Column Latches Mapping

FPS = 1

Data Load

DPTR = Address

ACC = Data

Exec: MOVX @DPTR, A

Last Byte

to load?

Data memory Mapping

FPS = 0

Programming the Flash Spaces

User The following procedure is used to program the User space and is summarized in

Figure 16:

• Load data in the column latches from address 0000h to 7FFFh

(1)

.

• Disable the interrupts.

• Launch the programming by writing the data sequence 50h followed by A0h in

FCON register.

The end of the programming indicated by the FBUSY flag cleared.

• Enable the interrupts.

Note: 1. The last page address used when loading the column latch is the one used to select

the page programming address.

30

AT89C5131

4136A–USB–03/03

Page 31

AT89C5131

Extra Row The following procedure is used to pr ogra m the Extra Row space and i s summ arized i n

Figure 16:

• Load data in the column latches from address FF80h to FFFFh.

• Disable the interrupts.

• Launch the programming by writing the data sequence 52h followed by A2h in

FCON register.

The end of the programming indicated by the FBUSY flag cleared.

• Enable the interrupts.

Figure 16. Flash and Extra Row Programming Procedure

Flash Spaces

Programming

Column Latches Loading

see Figure 15

Disable IT

EA = 0

Launch Programming

FCON = 5xh

FCON = Axh

FBusy

Cleared?

Erase Mode

FCON = 00h

End Programming

Enable IT

EA = 1

4136A–USB–03/03

31

Page 32

Hardware Security The following procedure is used to program the Hardware Security space and is sum-

marized in Figure 17:

• Set FPS and map Hardware byte (FCON = 0x0C)

• Disable the interrupts.

• Load DPTR at address 0000h.

• Load Accumulator register with the data to load.

• Execute the MOVX @DPTR, A instruction.

• Launch the programming by writing the data sequence 54h followed by A4h in

FCON register.

The end of the programming indicated by the FBusy flag cleared.

• Enable the interrupts.

Figure 17. Hardware Programming Procedure

Flash Spaces

Programming

FCON = 0Ch

Data Load

DPTR = 00h

ACC = Data

Exec: MOVX @DPTR, A

Disable IT

EA = 0

Launch Programming

FCON = 54h

FCON = A4h

FBusy

Cleared?

Erase Mode

FCON = 00h

End Programming

Enable IT

EA = 1

32

AT89C5131

4136A–USB–03/03

Page 33

AT89C5131

Reading the Flash Spaces

User The following procedure is used to read the User space and is summarized in Figure 18:

• Map the User space by writing 00h in FCON register.

• Read one byte in Accumulator by executing MOVC A, @A+DPTR with A = 0 &

DPTR = 0000h to FFFFh.

Extra Row The following procedure is used to read the Extra Row space and is summarized in

Figure 18:

• Map the Extra Row space by writing 02h in FCON register.

• Read one byte in Accumulator by executing MOVC A, @A+DPTR with A = 0 &

DPTR = FF80h to FFFFh.

Hardware Security The followi ng procedure is used to read the Hardwar e Security space and is summ a-

rized in Figure 18:

• Map the Hardware Security space by writing 04h in FCON register.

• Read the byte in Accumulator by executing MOVC A, @A+DPTR with A = 0 &

DPTR = 0000h.

Figure 18. Reading Procedure

Flash Spaces Reading

Flash Spaces Mapping

FCON = 00000xx0b

Data Re ad

DPTR = Address

Exec: MOVC A, @A+DPTR

ACC = 0

Erase Mode

FCON = 00h

4136A–USB–03/03

33

Page 34

Registers Table 34. FCON (S:D1h)

Flash Control Register

76543210

FPL3 FPL2 FPL1 FPL0 FPS FMOD1 FMOD0 FBUSY

Bit Number

7-4 FPL3:0

3FPS

2-1 FMOD1:0

0FBUSY

Bit

Mnemonic Description

Programming Launch Command Bits

Write 5Xh followed by AXh to launch the programming according to FMOD1:0.

(see Table 33.)

Flash Map Program Space

Set to map the column latch space in the data memory space.

Clear to re-map the data memory space.

Flash Mode

See Table 32 or Table 33.

Flash Busy

Set by hardware when programming is in progress.

Clear by hardware when programming is done.

Can not be cleared by software.

Reset Value = 0000 0000b

34

AT89C5131

4136A–USB–03/03

Page 35

AT89C5131

Flash EEPROM Memory

General Description The Flash me mory in crease s EPRO M functi onalit y with in -circu it elect rical erasur e and

programming. It contai ns 32 K bytes of program memor y organi zed in 256 pages of 128

bytes, respectively. This memory is both parallel and serial In- System Programmabl e

(ISP). ISP allows devices to alter their own program memory in the actual end product

under software control. A default serial loader (bootloader) pro gram allows ISP of the

Flash.

The programming does not require 12V external programming voltage. The necessary

high programming voltage is generated on-chip using the standard V

microcontroller.

Features • Flash EEPROM internal program memory.

• Boot vector allows user-provided Flash loader code to reside anywhere in the Flash

memory space. This configuration provides flexibility to the user.

• Default loader in Boot EEPROM allows programming via the serial port without the

need of a user provided loader.

• Up to 64K bytes external program memory if the internal program memory is

disabled (EA = 0).

• Programming and erase voltage with standard 5V or 3.3V V

• Read/Program/Erase:

• Byte-wise read (without wait state).

• Byte or page erase and programming (10 ms).

• Typical programming time (32 Kbytes) in 10 sec.

• Parallel programming with 87C51 compatible hardware interface to programmer.

• Programmable security for the code in the Flash.

• 100K write cycles

• 10 years data retention

supply.

CC

pins of the

CC

Flash Programming and Erasure

4136A–USB–03/03

The 32 Kbytes Flash is prog ramme d by bytes or by page s of 128 by tes. It is not ne cessary to erase a byte or a page before programming. The programming of a byte or a

page includes a self erase before programming.

There are three methods of programming the Flash memory:

1. The on-chip ISP bootloader may be invoked which will use low level routines to

program the pages. The interface used for serial downloading of Flash is the

UART.

2. The Flash may be programmed or erased in the end-user application by calling

low-level routines through a common entr y point in the Boot ROM.

3. The Flash may be programmed using the parallel method by using a conven-

tional EPROM programmer. The parallel programming method used by these

devices is similar to that used by EPROM 87C51 but it is not identical and the

commercially available programmers need to have support for the A T89C5131.

The bootloader and the A ppl icati on P r ogram min g Interface (API) routines ar e lo ca ted i n

the Boot ROM.

35

Page 36

Flash Registers and Memory Map

The AT89C5131 Flash memory uses several registers:

• Hardware registers can only be accessed through the parallel programming modes

which are handled by the parallel programme r.

• Software registers are in a special page of the Flash memory which can be

accessed through the API or with the parallel programming modes. This page,

called “Extra Flash Memory”, is not in the internal Flash program memory

addressing space.

Hardware Registers The only hardware registers of the AT89C5131 is called Hardware Security Byte (HSB).

Table 35. Hardware Security Byte (HSB)

76543210

X2 BLJB OSCON1 OSCON0 - LB2 LB1 LB0

Bit

Number

7X2

6BLJB

5-4 OSCON1-0

3-Reserved

2-0 LB2-0

Bit

Mnemonic Description

X2 Mode

Cleared to force X2 mode (6 clocks per instruction)

Set to force X1 mode, Standard Mode (Default).

Bootloader Jump Bit

Set this bit to sta rt th e user’s application on next reset at address 0000h.

Cleared this bit to start the bootloader at address F400h (default).

Oscillator Control Bits

These two bits are used to control the oscillator in order to reduce consummation.

OSCON

1 1 The oscillator is configured to run from 0 to 32 MHz

1 0 The oscillator is configured to run from 0 to 16 MHz

0 1 The oscillator is configured to run from 0 to 8 MHz

0 0 This configuration shouldn’t be set

User Memory Lock Bits

See Table 36

OSCON0 Description

Bootloader Jump Bit (BLJB) One bit of the HSB, the BLJB bit, is used to force the boot address:

• When this bit is set the boot address is 0000h.

• When this bit is reset the boot address is F400h. By default, this bit is cleared and

the ISP is enabled.

Flash Memory Lock Bits The three lock bits provide different levels of protection for the on-chip code and data,

when programmed as shown in Table 36.

36

AT89C5131

4136A–USB–03/03

Page 37

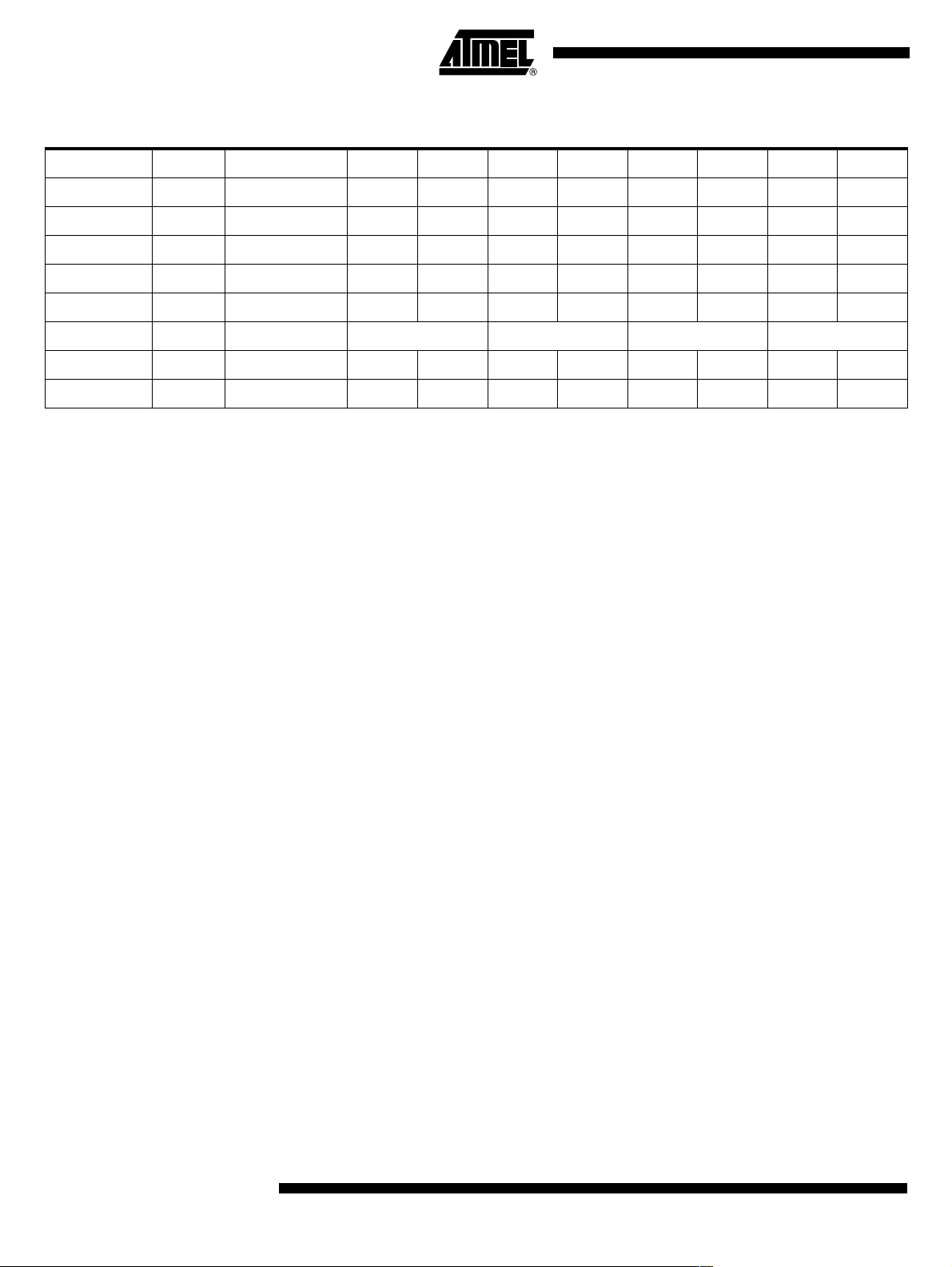

Table 36. Program Lock bits

Program Lock Bit s

1 U U U No program lock features enabled.

2PUU

AT89C5131

Protection DescriptionSecurity level LB0 LB1 LB2

MOVC instruction executed from external

program memory is disabled from fetching code

bytes from any internal memory, EA

and latched on reset, and further parallel

programming of the Flash and of the EEPROM

(boot and Xdata) is disabled. ISP and software

programming with API are still allowed.

is sampled

3XPU

4 X X P Same as 3, also external execution is disabled.

Notes: 1. U: unprogrammed or “one” level.

2. P: programmed or “zero” level.

3. X: don’t care

4. WARNING: Security level 2 and 3 should only be programmed after Flash and code

verification.

Same as 2, also verify through parallel

programming interface is disabled and serial

programming ISP is disabled.

These security bits prote ct the code acces s through the paralle l program ming inte rface.

They are set by default to lev el 4. The code acce ss thr ough the IS P is stil l possib le and

is controlled by the “software security bits” which are stored in the extra Flash memory

accessed by the ISP firmware.

To load a new application with the parallel programmer, a chip erase must be done first.

This will set the HSB in its in activ e stat e and will e rase the Flas h memo ry. The part reference can always be read using Flash parallel programming modes.

Default Values The default value of the HSB provides parts ready to be programmed with ISP:

• BLJB: Cleared to force ISP operation.

• X2: Set to force X1 mode (Standard Mode)

• OSCON1-0: Set to start with 32 MHz oscillator configuration value.

• XRAM: Unprogrammed to valid XRAM

• LB2-0: Security level four to protect the code from a parallel access with maximum

security.

Software Registers Several registers are used, in factory and by parallel programmers, to make copies of

hardware registers con tents . Thes e va lue s are us ed by Atmel ISP (se e Sect ion “In-Sys-

tem Programming (ISP)”).

These registers are in the “Extra Flash Memory” part of the Flash memory. This block is

also called ”XAF” or eXtra Array Flash. They are accessed in the following ways:

• Commands issued by the parallel memory programmer.

• Commands issued by the ISP software.

• Calls of API issued by the application software.

Several software registers are described in Table 37.

37

4136A–USB–03/03

Page 38

Table 37. Software Registers

Mnemonic Description Default value

SBV S oftware Boot Vector FCh –

HSB

BSB Boot Status Byte 0FFh –

SSB S oftware Security Byte FFh –

–

–

–

– Size and Type FBh AT89C5131 16 Kbyte

–

– Revision FFh

Copy of the Hardware

Security Byte

Copy of the Manufacturer

Code

Copy of the Device ID #1:

Family Code

Copy of the Device ID #2:

Memories

Copy of the Device ID #3:

Name

1011 1000b –

58h Atmel

D7h

F7h AT89C5131 32 Kbyte

EFh

C51 X2, Electrically

Erasable

AT89C5131 32 Kbyte,

revision 0

AT89C5131 16 Kbyte,

revision 0

After programming the par t by ISP , the BSB mu st be cl eared (00h) in o rder to al low the

application to boot at 0000h.

The content of the Software Security Byte (SSB) is described in Table 38

and Table 39.

To assure code p rotec ti on f ro m a pa ra ll el ac ce ss , t he H SB mu st al so be at t he r e qui re d

level.

Table 38. Software Security Byte (SSB)

76543210

38

AT89C5131

------LB1LB0

Bit

Number

7-

6-

5-

4-

3-

2-

1-0 LB1-0

Bit

Mnemonic Description

Reserved

Do not clear this bit.

Reserved

Do not clear this bit.

Reserved

Do not clear this bit.

Reserved

Do not clear this bit.

Reserved

Do not clear this bit.

Reserved

Do not clear this bit.

User Memory Lock Bits

See Table 39

4136A–USB–03/03

Page 39

AT89C5131

The two lock bits provide different levels of protection for the on-chip code and data,

when programmed as shown to Table 39.

Table 39. Program Lock Bits of the SSB

Program Lock Bits

Security

Level LB0 LB1

1 U U No program lock features enabled.

2 P U ISP programming of the Flash is disabled.

3 X P Same as 2, also verify through ISP programming interface is disabled.

Notes: 1. U: unprogrammed or "one" level.

2. P: programmed or “zero” level.

3. X: don’t care

4. WARNING: Security level 2 and 3 should only be programmed after Flash and code

verification.

Protection Description

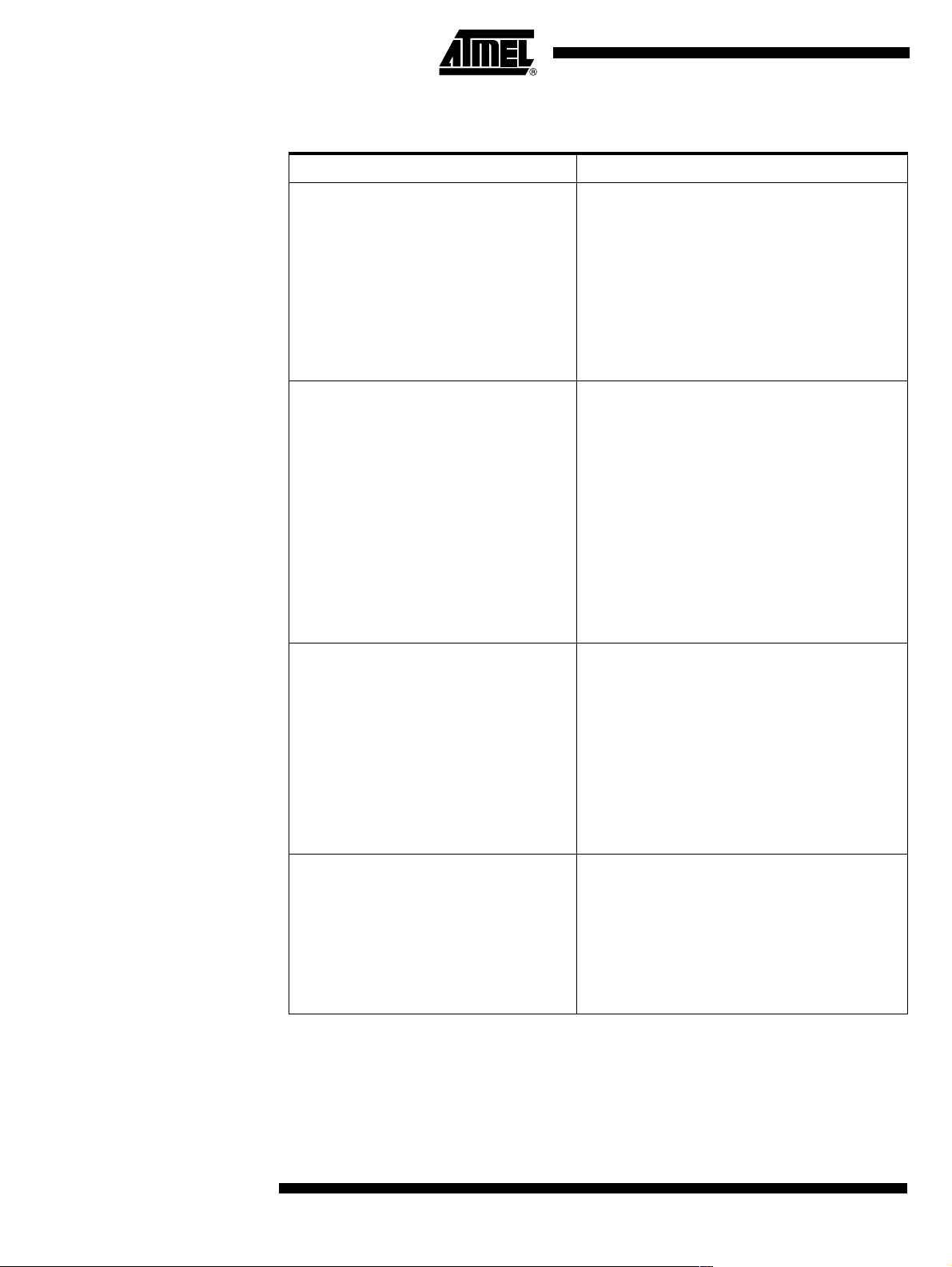

Flash Memory Status AT89C5131 parts are delivered with the ISP boot in the Flash memory. After ISP or par-

allel programming, the possible contents of the Flash memory are summarized in Figure

19:

Figure 19. Flash Memory Possible Contents

7FFFh

AT89C5131

Virgin

Virgin

or

Application

Dedicated

ISP

ApplicationApplication

Virgin

or

Application

Virgin

or

Application

Dedicated

ISP

0000h

Default

After ISP

After ISP

After parallel

programming

After parallel

programming

After parallel

programming

Memory Organization In the AT89C5131, the lowest 16K or 32K of the 64 Kbyte program memory address

space is filled by internal Flash.

When the EA

Bus expansion for accessing program memory from 16K or 32K upward is automatic

since external instruction fetches occur automatically when the program counter

exceeds 3FFFh (16K) or 7FFFh (32K). If the EA

fetches are from external memory. If all storage is on chip, then byte location 3FFFh

(16K) or 7FFFh (32K) should be left vacant to prevent and undesired pre-fetch from

external program memory address 4000h (16K) or 8000h (32K).

4136A–USB–03/03

is pin high, the processor fetches instructions from internal program Flash.

pin is tied low, all program memory

39

Page 40

Boot Process

Boot Flash When the user application programs its own Flash memory, all of the low level details

are handled by a code that is permanently contained in a 3 Kbyte “Boot ROM”. A user

program simply calls the common entry point in the Boot ROM with appropriate parameters to accomplis h the desired operation. Bo ot ROM operati ons includ e: erase bloc k,

program byte or page, verify byte or page, program security lock bit, etc. The Boot ROM

is placed in the program memory space at the top of the address space from F800h to

FFFFh (Figure 20).

Figure 20. Boot ROM Loader Memory Map

Boot Process Secondary

FFF0

F400

FFF0

Entry point for API

ISP start

Entry point for API

40

AT89C5131

F400

The boot process is summariz ed in Fi gur e 21.

ISP start

4136A–USB–03/03

Page 41

Figure 21. Boot Process Flowchart

Hardware

AT89C5131

RESET

BLJB = 1?

APPLICATION PROGRAM

Software

No

BSB = = 00h?

0000h address

bit = = 0?

No

Yes

No

No

No

F800h address

P1_CF = FFh?

Yes

P3_CF = FFh?

Yes

P4_CF = FFh?

SBV < 3Fh?

YesYes

Yes

No

4136A–USB–03/03

APPLICATION PROGRAM

ATMEL BOOTLOADER

CUSTOMER BOOTLOADER

PC = [SBV]00h

41

Page 42

In-System Programming (ISP)

The In-System Programmin g (ISP) is performe d without removi ng the microcontroll er

from the system. The ISP facility consists of a series of internal hardware resources

coupled with internal firmware to facilitate remote programming of the AT89C5131

through the serial port.

The Atmel ISP feature has made in-circuit programming in an embedded application

possible with a minimum of additional expenses in components and circuit board area.

Using In-System

Programming

The ISP function through UART uses four pins: TxD, RxD, V

nector needs to be available to in terfac e the applic ation to an external circuit in order to

use this feature.

The ISP feature allows a wide range of baud rates in the user applicati on. It is also

adaptable to a wide rang e of o scilla tor freq uen cies. T his is acco mplis hed by meas urin g

the bit-time of a single bit in a received character. This information is then used to program the baud rate in term s of timer coun ts based on the os cillator frequency . The ISP

feature requires that an initi al cha racter (a n upperc ase U) be s ent to th e AT89C5 131 to

establish the baud rate. The ISP firmware provides auto-echo of received characters.

Once baud rate initialization has been performed, the ISP firmware will only accept Intel

Hex-type records. Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below:

:NNAAAARRDD..DDCC<crlf>

AT89C5131 will accept up to 16 (10h) data bytes. The “AAAA” string represents the

address of the first byte in the record. If there are zero bytes in the record, this field is

often set to ‘‘0000’’. The “RR” string in dicat es the re cord t ype. A rec ord type of “00” is a

data record. A record type of “01” indicates the end-of-file mark. In this application, additional record types will be added to indicate either commands or data for the ISP feature.

The “DD” string represents the data bytes. The maximum number of data bytes in a

record is limited to 16 (decimal). The “CC” string represents the checksum byte. ISP

commands are summarized in Table 40.

As a record is received by the AT89 C5131, the inf ormation in the rec ord is s tored inte rnally and a checksum calculation is performed and compared to ‘‘CC’’.

, VCC. Only a small con-

SS

42

The operation indicated by the record type is not performed until the entire record has

been received. Should an er r or occ ur in th e checksum, the AT89C51 31 wi ll sen d an “X”

out the serial port indicating a checksum error. If the checksum calculation is found to

match the chec ksu m in the recor d, th en th e c omman d wil l be exec uted. In m ost cases ,

successful reception of the record will be indicated by transmitting a “.” character out the

serial port (displaying the contents of the internal program memory is an exception). In

the case of a Data Record (record type ‘‘00’’), an additional check is made. A “.” character will NOT be sent unless the record checksum matched the calculated checksum and

all of the bytes in the record were successfully programmed. For a data record, an “X”

indicates that the checksum failed to match, and an “R” character indicates that one of

the bytes did not properly program.

Atmel_ISP, a software utility to implement ISP programming with a PC, is available from

Atmel. Please visit our web site www.atmel.com.

AT89C5131

4136A–USB–03/03

Page 43

Table 40. Intel-Hex Records Used by In-System Programming

Record Type Command/Data Function

Data Record

:nnaaaa00dd....ddcc

Where:

Nn = number of bytes (hex) in record

00

01

aaaa = memory address of first byte in record

dd....dd = data bytes

cc = checksum

Example:

:05008000AF5F67F060B6

End of File (EOF), no operation

:xxxxxx01cc

Where:

xxxxxx = required field, but value is a “don’t care”

cc = checksum

Example:

:00000001FF

AT89C5131

02

Specify Oscillator Frequency (Not required, left for Philips compatibility)

:01xxxx02ddcc

Where:

xxxx = required field, but value is a “don’t care”

dd = required field, but value is a “don’t care”

cc = checksum

Example:

:0100000210ED

4136A–USB–03/03

43

Page 44

Table 40. Intel-Hex Records Used by In-System Programming (Continued)

Record Type Command/Data Function

Miscellaneous Write Functions

:nnxxxx03ffssddcc

Where:

nn = number of bytes (hex) in record

xxxx = required field, but value is a “don’t care”

03 = Write Function

ff = subfunction code

ss = selection code

dd = data input (as needed)

cc = checksum

Subfunction Code = 01 (Erase Block)

ff = 01

ss = block number in bits 7:5, Bits 4:0 = zeros

Example:

:0200000301A05A erase block 5

Subfunction Code = 04 (Reset Boot Vector and Status Byte)

ff = 04

ss = don’t care

dd = don’t care

Example:

:020000034500F8 Reset boot vector (FCh) and status byte (FFh)

Subfunction Code = 05 (Program Software Security Bits)

03

ff = 05

ss = 00 program software security bit 1 (Level 2 inhibit writing to Flash)

ss = 01 program software security bit 2 (Level 3 inhibit Flash verify)

ss = 02 program security bit 3 (No effect, left for Philips compatibility; disable external

memory is already set in the default hardware security byte)

Example:

:020000030501F6 program security bit 2

Subfunction Code = 06 (Program Boot Status Byte, Boot Vector, X2 bit, Osc bit or BLJB

fuse bit)

ff = 06

ss = 00 program Boot Status byte

ss = 01 program Software Boot vector

ss = 02 program X2 bit

ss = 03 program Osc bit

ss = 04 program BLJB

Example:

:03000003060100F5 program boot vector with 00

Subfunction Code = 07 (Full chip erase)

ff = 07

ss = don’t care

dd = don’t care

Example:

:03000007F5 program boot vector with 00

44

AT89C5131

4136A–USB–03/03

Page 45

AT89C5131

Table 40. Intel-Hex Records Used by In-System Programming (Continued)

Record Type Command/Data Function

Display Device Data or Blank Check

Record type 04 causes the contents of the entire Flash array to be sent out the serial

port in a formatted display. This display consists of an address and the contents of 16

bytes starting with that address. No display of the device contents will occur if security

bit 2 has been programmed. The dumping of the device data to the serial port is

terminated by the reception of any character.

General Format of Function 04

:05xxxx04sssseeeeffcc

Where:

04

05 = number of bytes (hex) in record

xxxx = required field, but value is a “don’t care”

04 = “Display Device Data or Blank Check” function code

ssss = starting address

eeee = ending address

ff = subfunction

00 = display data

01 = blank check

cc = checksum

Example:

:0500000440004FFF0069 (display 4000–4FFF)

In-application Programming Method

Miscellaneous Read Functions

General Format of Function 05

:02xxxx05ffsscc

Where:

02 = number of bytes (hex) in record

xxxx = required field, but value is a “don’t care”

05 = “Miscellaneous Read” function code

ffss = subfunction and selection code

05

0000 = read copy of the signature byte – manufacturer id (58H)