Page 1

Features

• Clock Controller

– 80C51 core wit h 6 clocks per instructi on

– 8 MHz On-Chip Oscil lator

– PLL for generating clock to supply CPU core, USB and Smart Card Interfaces

– Programmable CPU clock from 500 KHz / X1 to 48 MHz / X1

• Reset Controller

– Power On Reset (POR) featur e avoiding an external reset capacitor

– Power Fail Detector (PFD)

– Watch-Dog Timer

• Power Management

– Two power saving modes : Idle and Power Down

– Four Power Down Wake-u p Sources : Smart Card Detection, Keyboard Interrupt, USB

Resume, External Interrupt

– Input Voltage Range : 3.0V - 5.5V

– Core’s Power Consu mp ti on (Without Smart Card and USB) :

•30 mA Maximum Operating Current @ 48 MHz / X1

•200 μA Maximum Power- down Current @ 5.5V

• Interrupt Controller

– up to 9 interrupt sources

– up to 4 Leve l P rio r ity

• Memory Controller

– Internal Progra m memory :

•up to 32KB of Flash or CRAM or ROM for AT8xC5122

•up to 30KB of ROM for AT83C5123

– Internal Data Me mory : 768 bytes including 256 bytes of data and 512 bytes of XRAM

– Optional : inter nal data E2PROM 512 bytes

• T w o 16-bit Timer/Counters

• USB 2.0 Full Speed Interface

–48 MHz DPLL

– On-Chip 3.3V USB voltage regulator and transcei vers

– Software detach feature

– 7 endpoints programmable with In or out directions and ISO, Bulk or Int errupt Transf ers :

•Endpoint 0: 32 Bytes Bidirectionnal FIFO for Control transfers

•Endpoint s 1,2,3: 8 bytes FIFO

•Endpoint s 4,5: 64 Bytes FIFO

•Endpoint 6: 2*64 byt es FIFO with Pin-Pong feature

• ISO 7816 UART Interface Fully Compliant with EMV, GIE-CB and WHQL Standards

– Programmable ISO clock from 1 MHz to 4.8 MHz

– Card insertion/removal detection wit h automatic deactiva tion sequence

– Programmable Baud Rate Generator from 372 to 11.625 clock pulses

– Synchronous/Asynchronous Protocols T=0 and T=1 with Direct or Inverse Convention

– Automatic character repetition on parity errors

– 32 B it Wa iting Time Count e r

– 16 Bit Guard Time Counter

– Internal Step Up/Down Converter with Programmable Voltage Output:

•VCC = 4.0V to 5.5V, 1.8V -30 mA, 3V- 60 mA and 5V-60 mA

•VCC = 3.0V, 1.8V-30 mA, 3V-30 m A and 5V-30 mA

– Current overload protection

– 6 kV ESD (MIL/STD 833 Class 3) protection on whole Smart Card Interface

• Alternate Smart Card Interface with CLK, IO and RST

• UART Interface with Integrat ed Baud Rate Gener ator (BRG)

• Keyboard interface with up to 20x8 matrix management capability

• Master/Slave SPI Interface

• Four 8 bit Ports, one 6 bit port, one 3-bit port

– Up to Seven LED outputs with 3 lev el programmable current source : 2, 4 and 10 mA

– Two Gene ral Purpose I/O programmable as ext ernal interrupts

– Up to 8 input lines programmable as interrupts

– Up to 30 outp ut lines

C51

Microcontroller

with USB and

Smart Card

Reader

Interfaces

AT83C5122

AT83EC5122

AT85C5122

AT89C5122

AT89C5122DS

AT83C5123

AT83EC5123

Rev. 4202E–SCR–06/06

1

Page 2

AT8xC5122/23

Reference Documents The user must get the following additionnal documents which are not included but which

complete this product datasheet

• Product Errata Sheet

• Bootloader Datasheet

2

4202E–SCR–06/06

Page 3

AT8xC5122/23

Product Description AT8xC5122/23 products are high-performance CMOS derivatives of the 80C51 8-bit

microcontrollers designed for USB smart card reader applications.

The AT8xC5122 is proposed in four versions :

- ROM vers ion w ith or wi thout interna l data E 2PR OM. T he RO M dev ice is on ly fa ctory

programmable.

- CRAM version withou t interna l data E2PR OM. The CRAM devi ce impl ements a vol atile program memory whic h is programmed by means of a n embedded ROMed

bootloader which transfers the code from a remote software programming tool called

FLIP through UART or USB interfaces.

- Flash version without internal data E2PROM. At power-up, the program located in the

flash memory is transferred into the CRAM then executed.

The AT83C5123 is a low pi n count of the AT 8xC5122 and is propos ed in ROM version

with or without internal data E2PROM. The ROM device is only factory programmable.

The AT8xC5122DS is a secure version of the AT8xC5122 on which the external program memory access mode is disabled.

4202E–SCR–06/06

3

Page 4

AT8xC5122/23

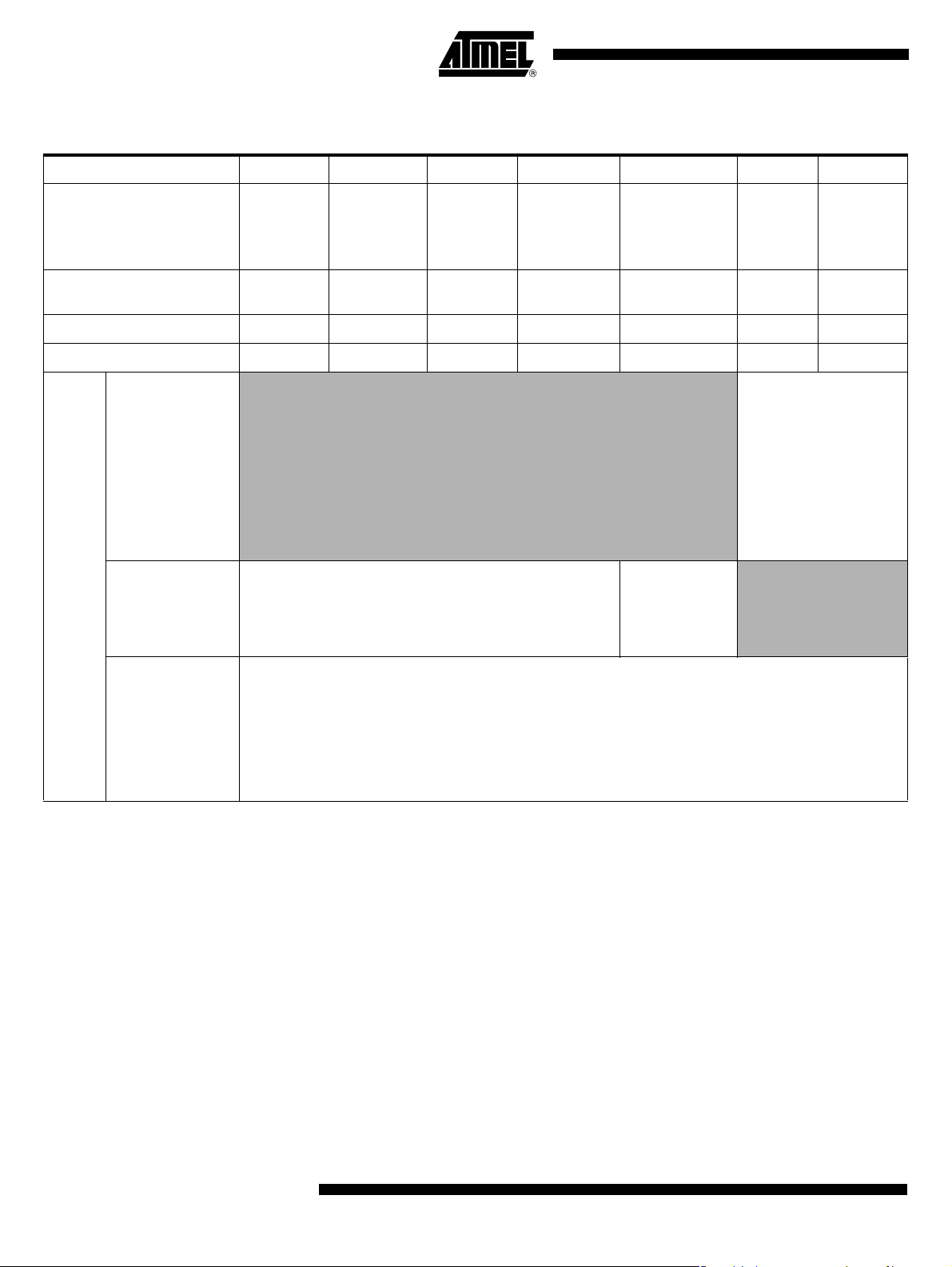

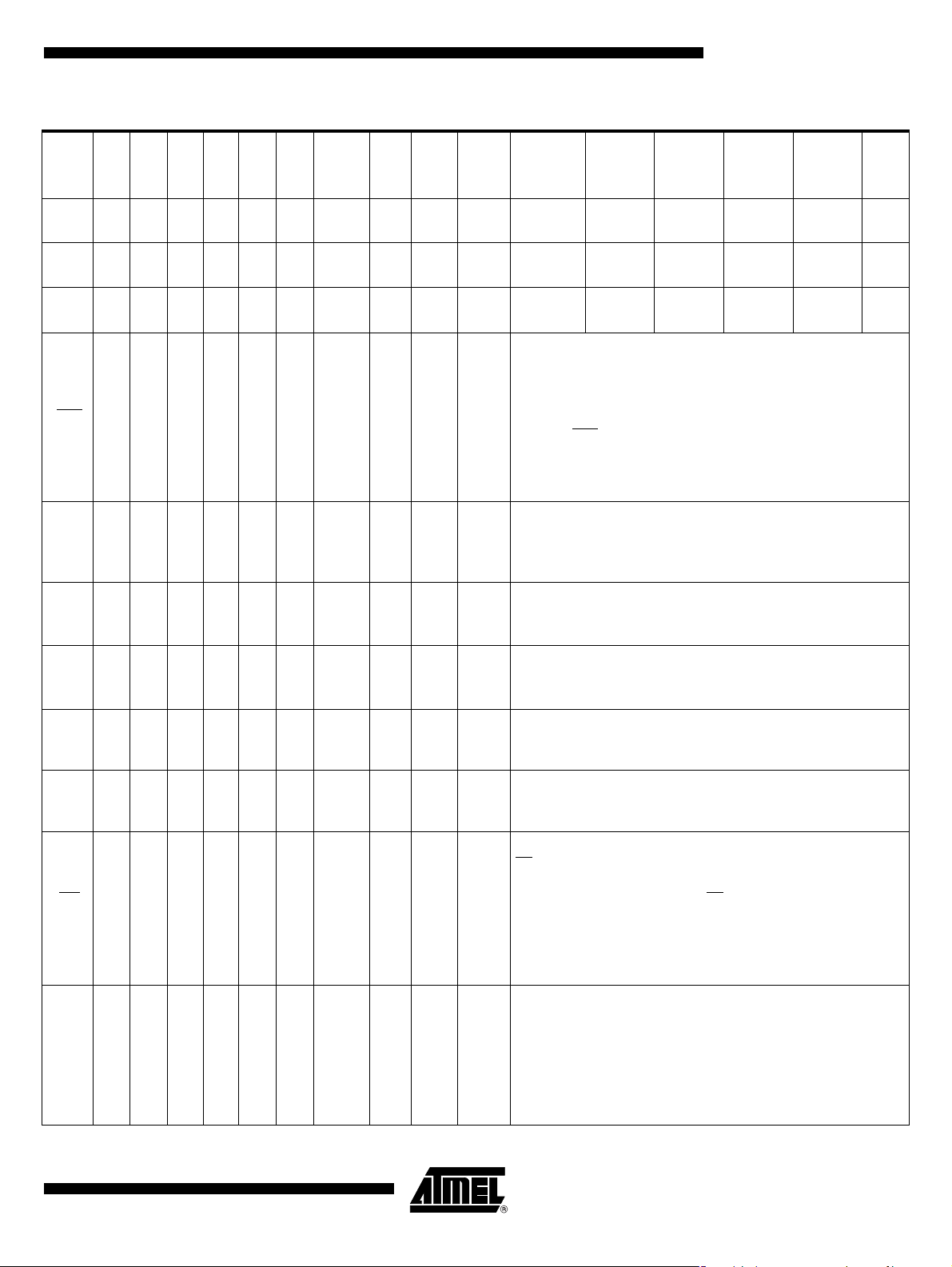

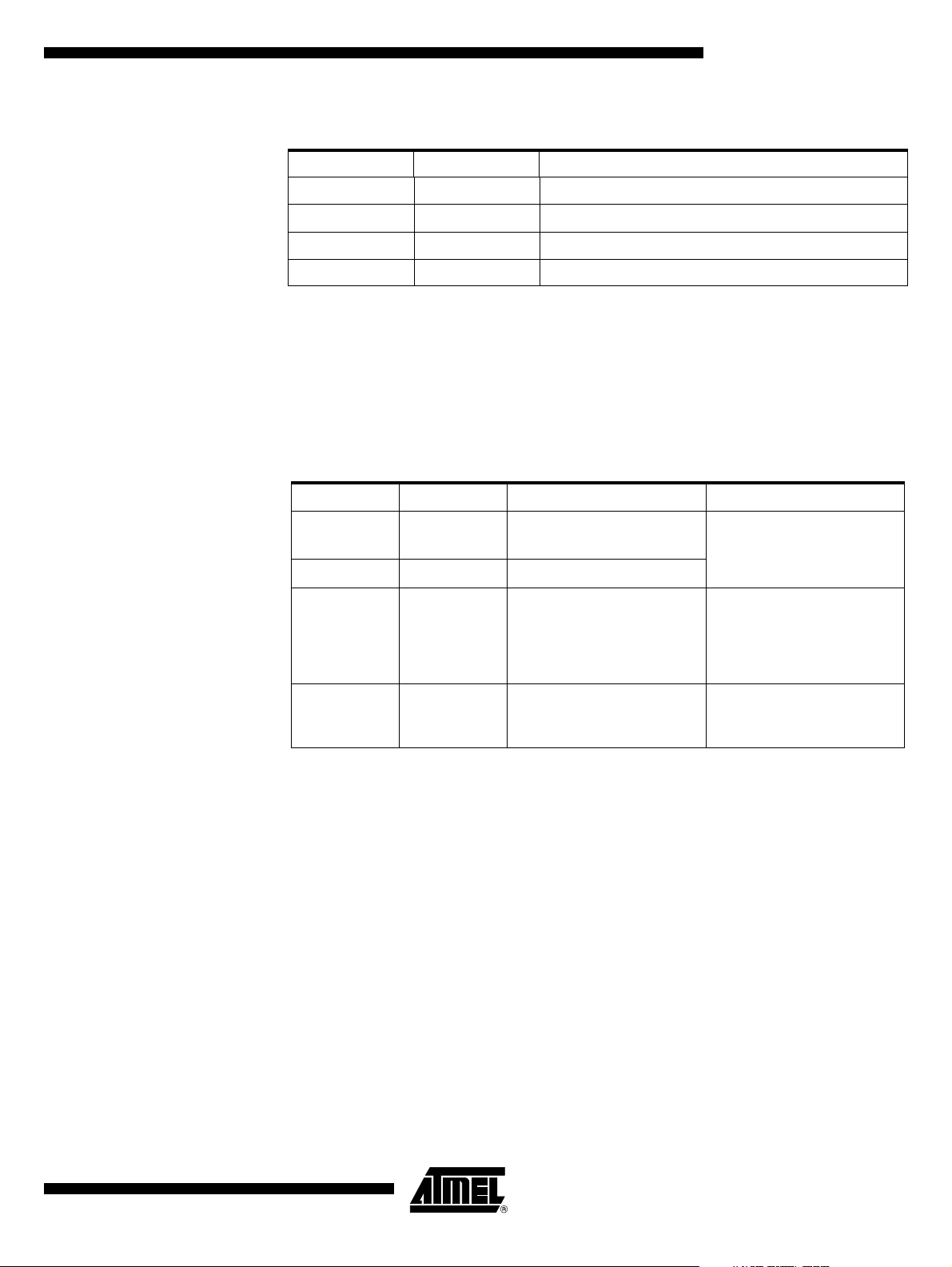

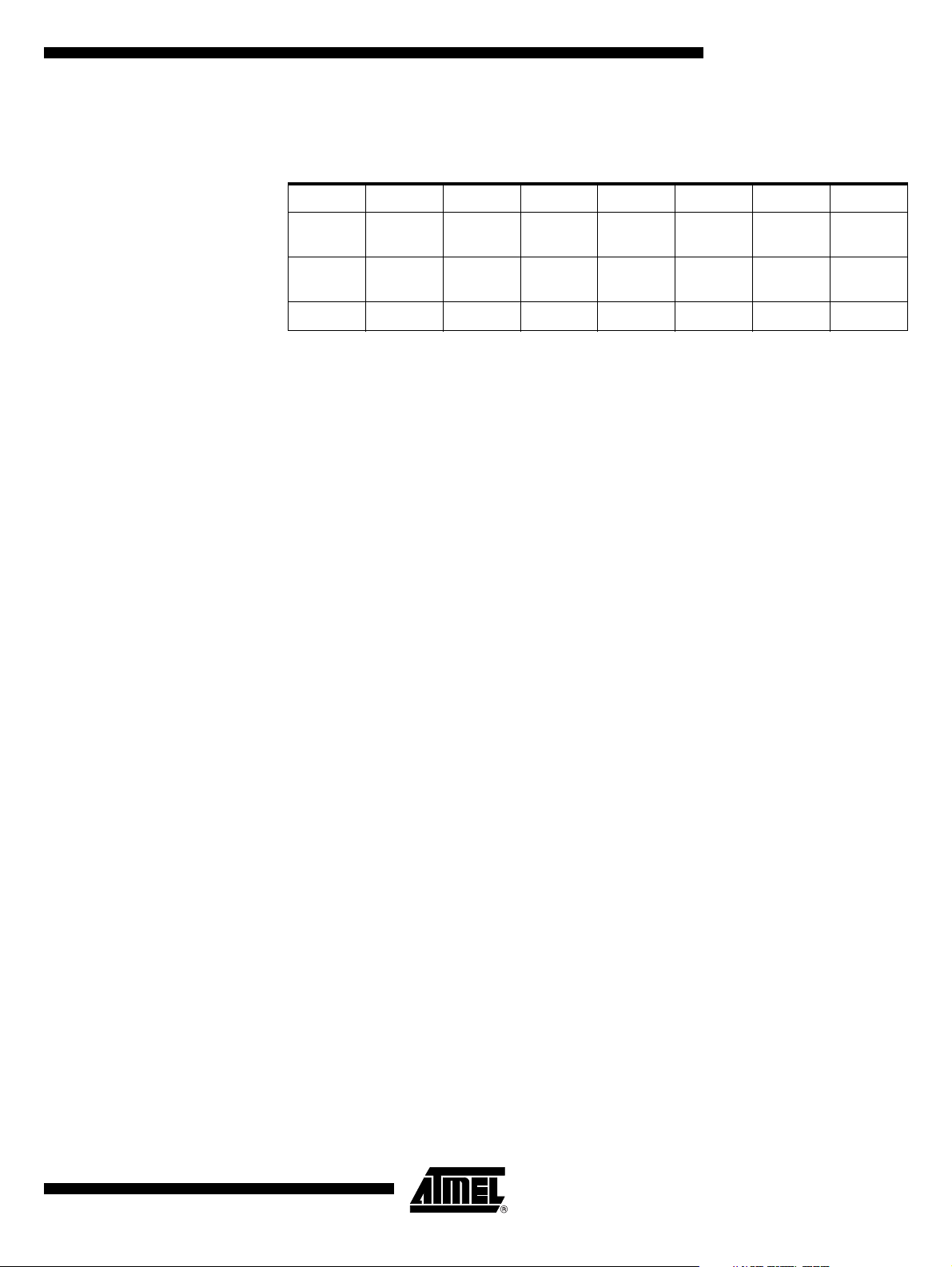

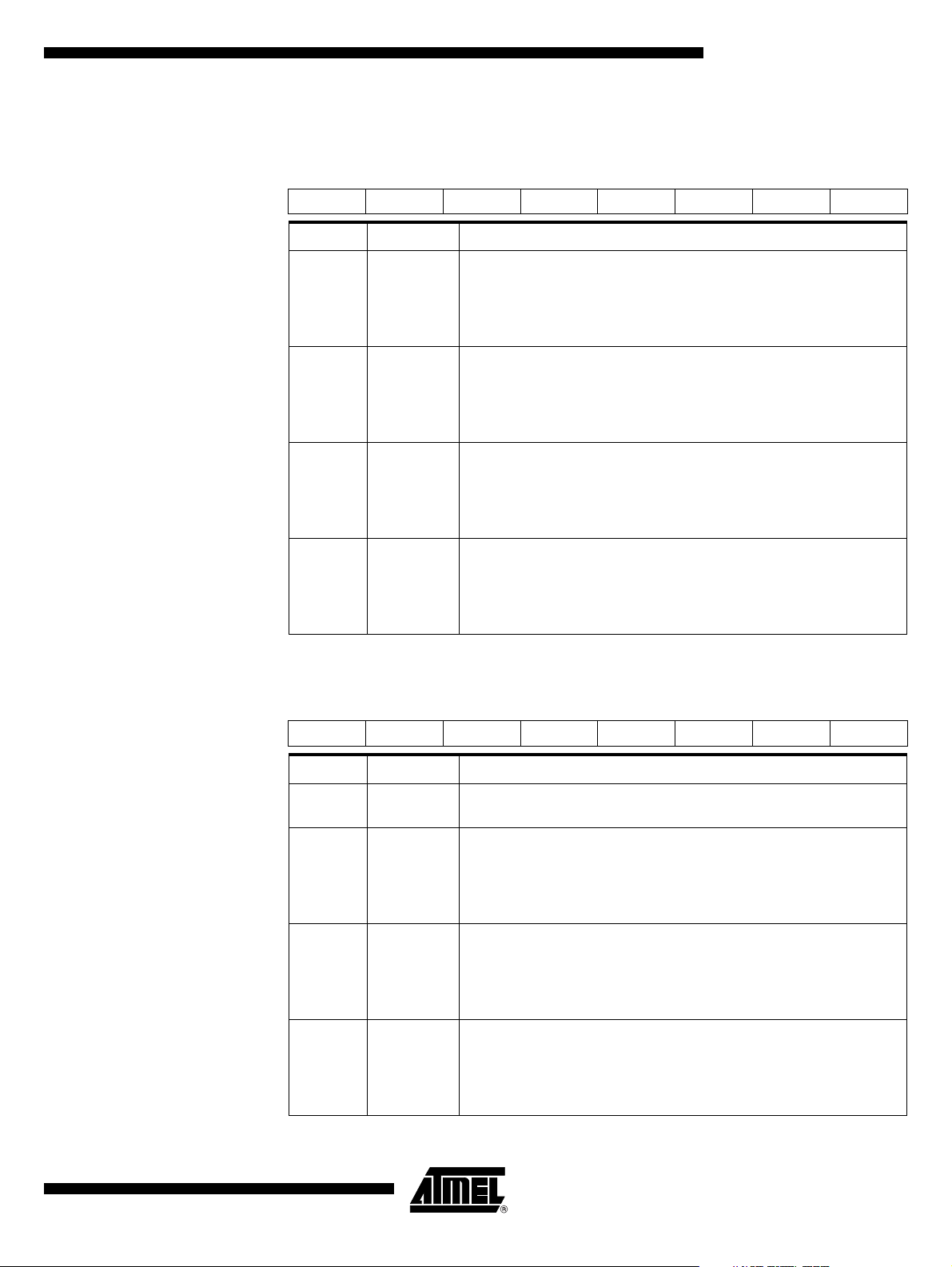

Table 1. Product versions

Features AT83C5122 AT83EC5122 AT85C5122 AT89C5122 AT89C5122DS AT83C5123 AT83EC5123

VQFP64

Packages

Program memory 32KB ROM 30KB ROM 32KB CRAM

Internal Data E2PROM No 512 Bytes No No No No 512 Bytes

Embedded bootloader No No Yes Yes Yes No No

VQFP32,

QFN32

packages

Features

PLCC68,

VQFP64,QFN64

packages

QFN64

PLCC28

Die Form

VQFP64

PLCC28

All features are available

PLCC68

VQFP64

PLCC28

Die Form

VQFP64

QFN64

PLCC28

32KB

E2PROM

VQFP32

VQFP64

QFN64

32KB E2PROM 30KB ROM 30KB ROM

All features are

available

except External

Program Mem ory

Access

QFN32

PLCC28

Die Form

Features not av ailable :

- Keyboard Interface

- Master/Slave SPI

- External Program Memor y

Reduced features :

- Only 12 I/O with up to 4

LED Outputs with

Programmable Current

QFN32

VQFP32

PLCC28

Interface

Access

PLCC28 package

Features not avai lab le :

- Alternate Smart Card Inte rfa ce

- Keyboard Interface

- Master/Slave SPI Interface

- External Program Memory Access

Reduced features :

- Only 7 I/O with up to 4 LED Outputs with Programmable Current

Note: The PLCC28 pinout is common t o AT8xC5122 and AT83C5123 products

4

4202E–SCR–06/06

Page 5

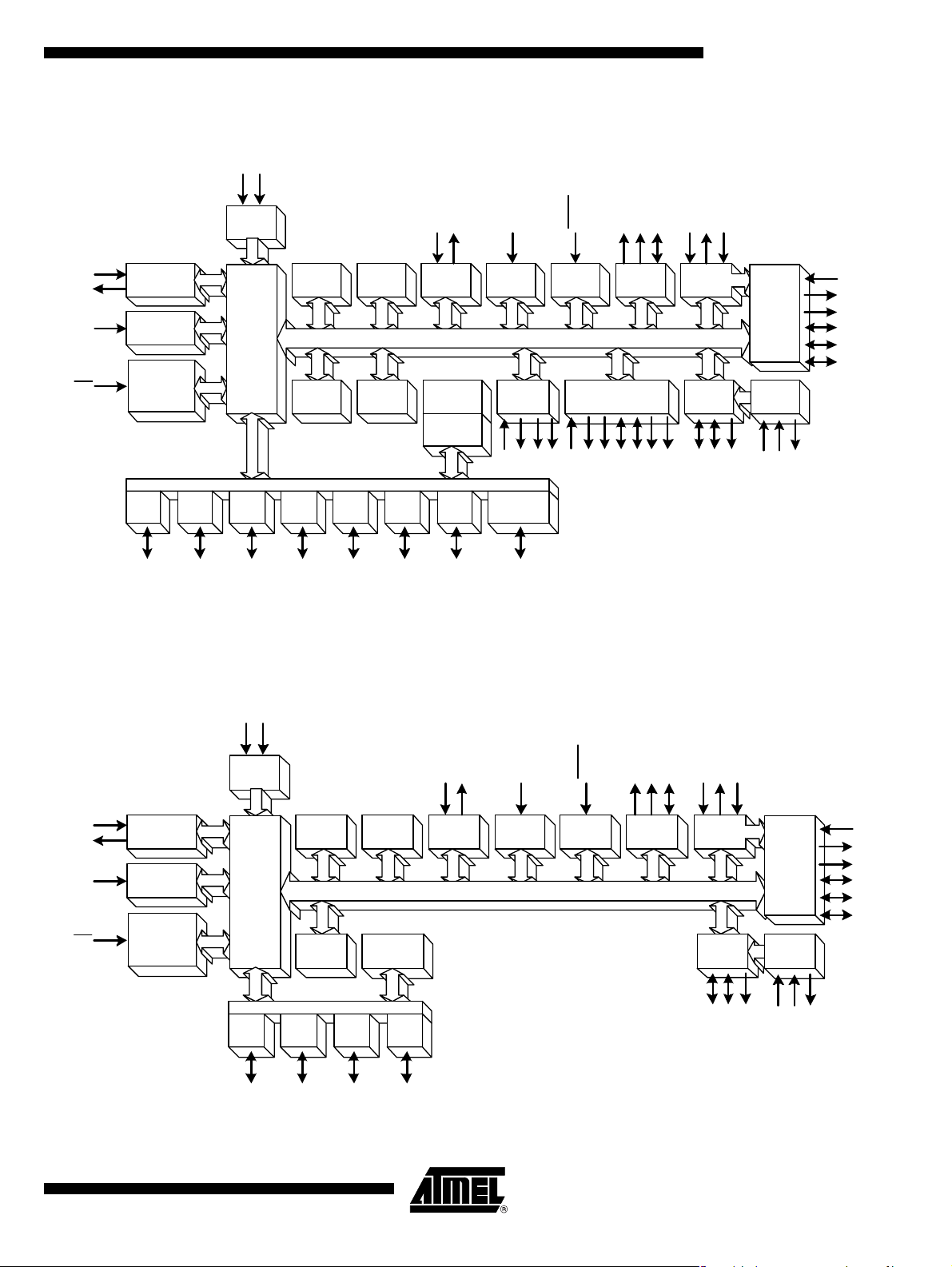

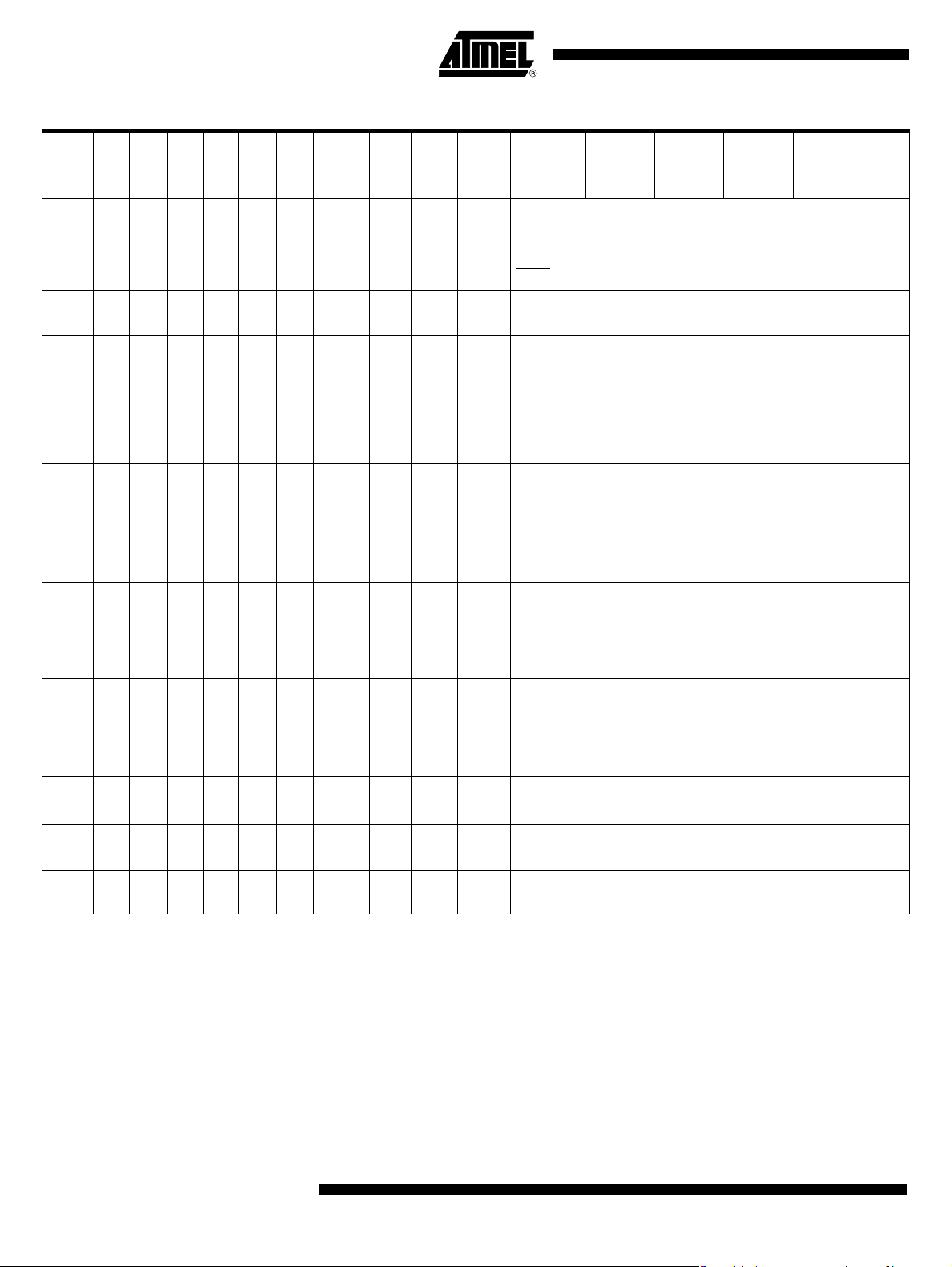

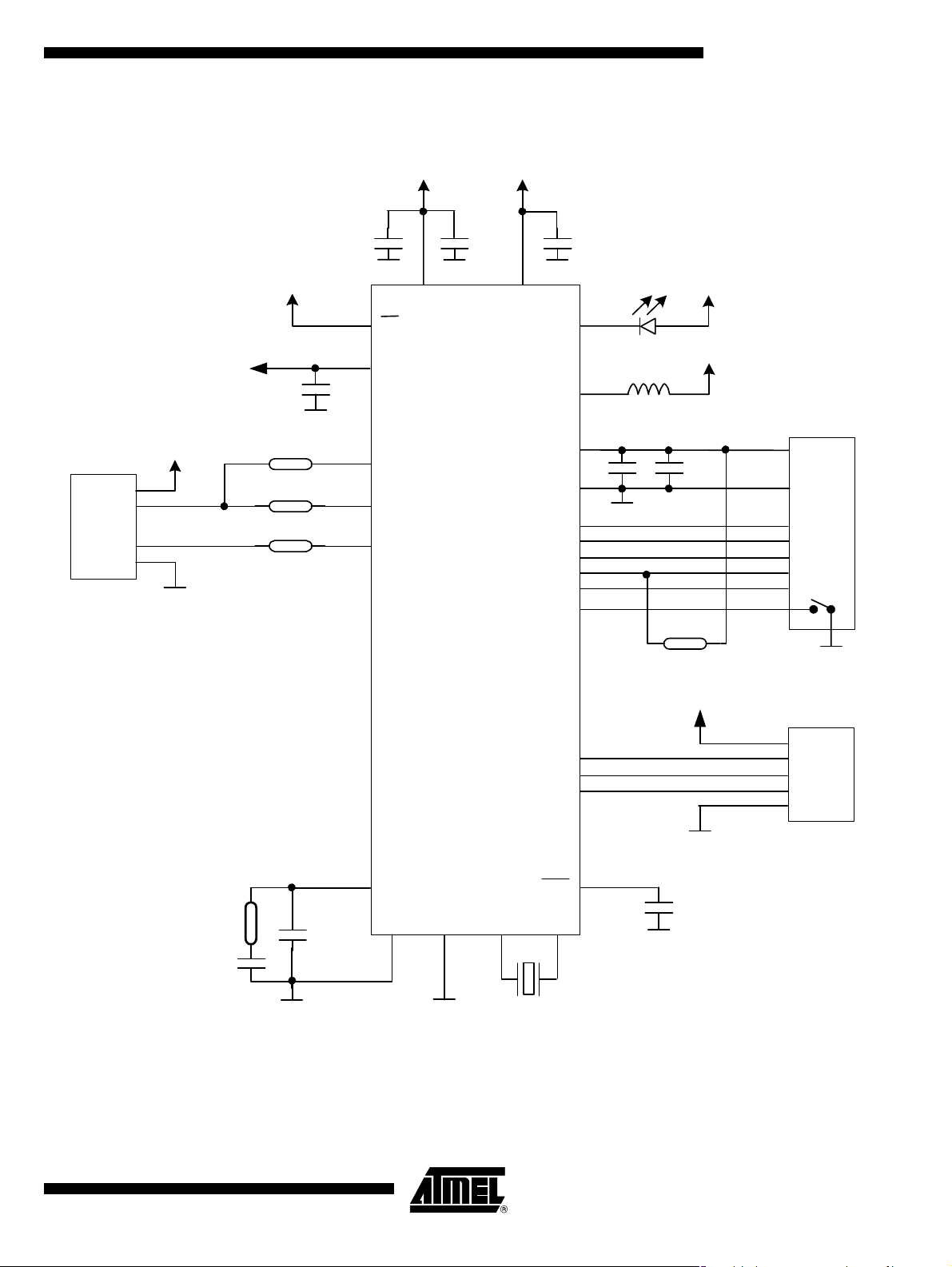

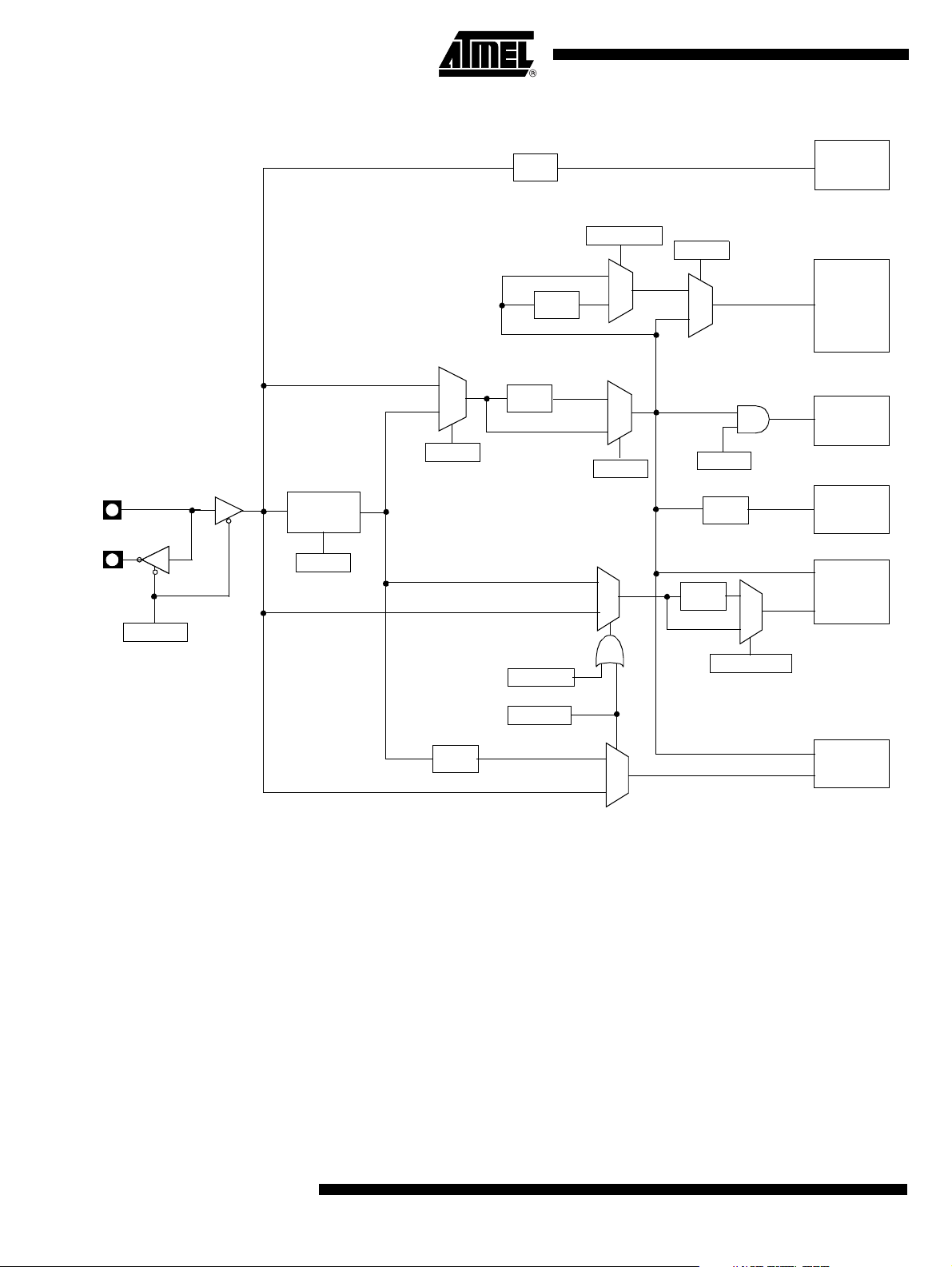

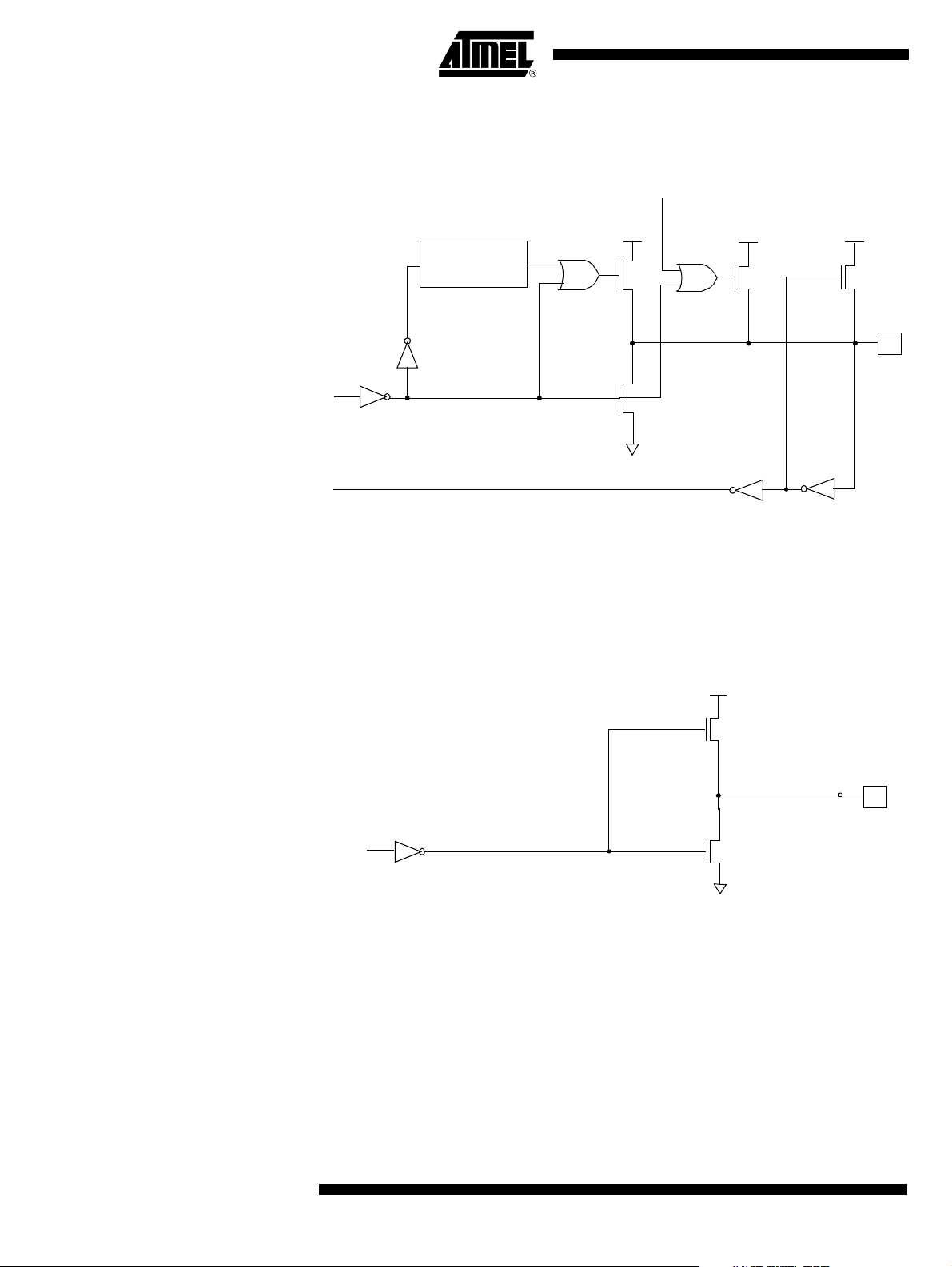

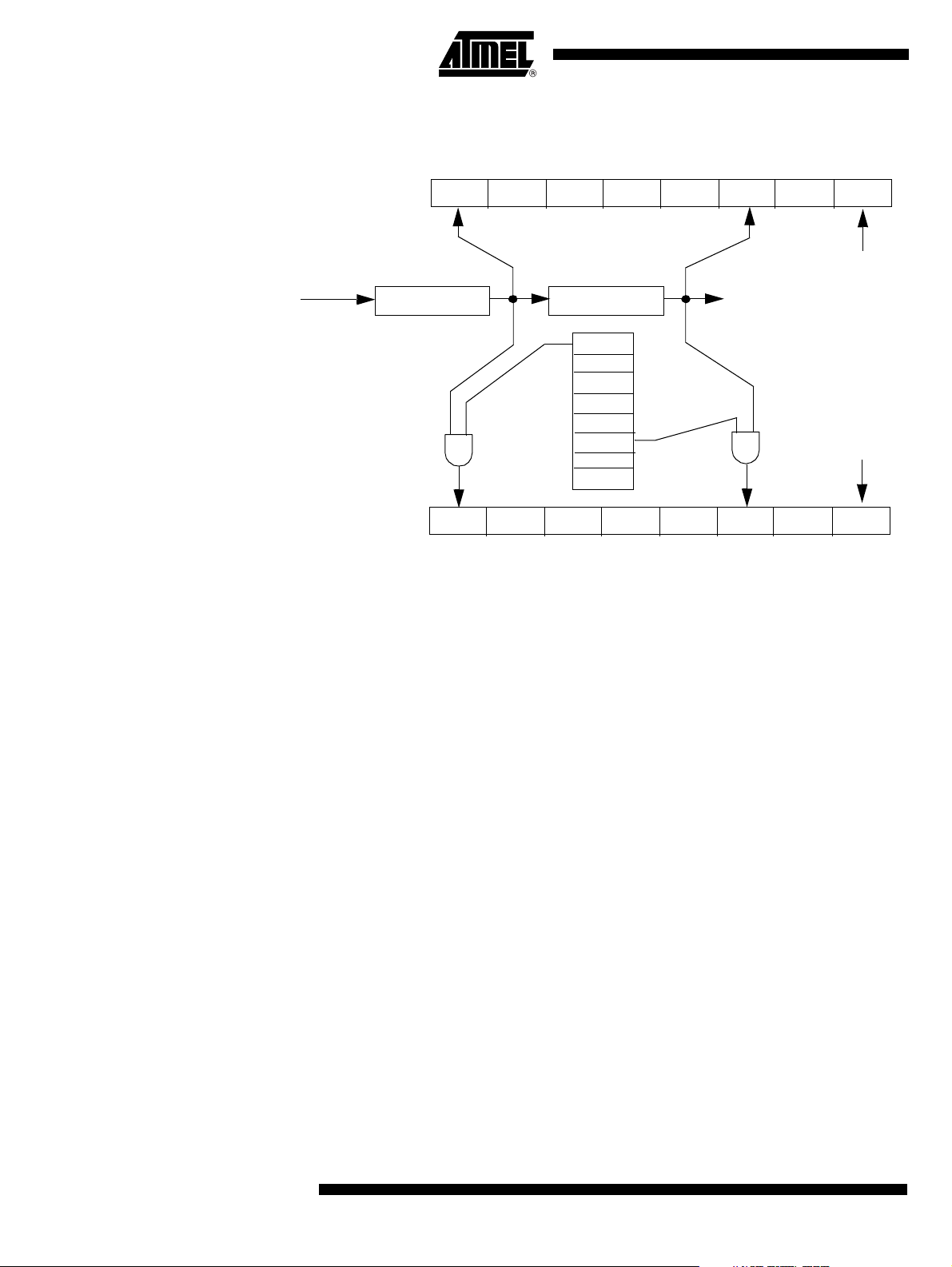

AT8xC5122 Block Diagram

VCC

VSS

AT8xC5122/23

3.3 V

Regulator

XTAL1

XTAL2

RST

8 MHz

Oscillator

PLLPLLF

WATCH-DOG

POR

PFD

RESET

8-BIT

PORT

P0[0-7]

3-BIT

PORT

256 x 8

RAM

80C51 8-BIT CORE

8-BIT

PORT

P1[2,6-7]

P2[0-7]

AT83C5123 Block Diagram

256 x 8

RAM

32K x 8

ROM (1)

Parallel I/O Ports

8-BIT

PORT

P3[0-7]

6-BIT

PORT

512 x 8

XRAM

32K x 8

CRAM (1 )

P4[0-5]

RxD

TxD

UART

Interface

INTERNAL ADDRESS AND DATA BUS

32K x 8

E2PROM (1)

512 x 8

E2PROM (1)

8-BIT

PORT

LED's

P5[0-7]

LED[0-6]

T[0-1]

16-BIT

TIMERS

SPI

Interface

MISO

KBD

Interface

INT[0-1]

Interrupt

Controller

SS

EA

SCK

MOSI

Note 1 : the implementation of these features depends on product versions

KB[0-7]

CRST1

Alternate

Card

External Memory

Controller

ALE

PSEN

AD[0-7]

CCLK1

A[8-15]

LI

CVCC

DC/DC

Converter

USB

Interface

D+

CVSS

ISO 7816

3.3V

Regulator

D-

VREF

AVCC

CIO1

RD

WR

Interface

AVSS

CPRE S

CRST

CCLK

CIO

CC4

CC8

DVCC

XTAL1

XTAL2

RST

8 MHz

Oscillator

PLLPLLF

WATCH-DOG

POR

PFD

RESET

VCC

3.3 V

Regulator

256 x 8

RAM

80C51 8-BIT CORE

3-BIT

PORT

P1[2,6-7]

VSS

Parallel I/O Ports

8-BIT

PORT

256 x 8

RAM

30K x 8

ROM

P3[0-7]

1-BIT

PORT

512 x 8

XRAM

512 x 8

E2PROM (1)

P5.0

LED's

RxD

TxD

UART

Interface

INTERNAL ADDRESS AND DATA BUS

Note 1 : the implementation of these f eatures depends o n pro duct versions

LED[0-3]

T[0-1]

16-BIT

TIMERS

INT[0-1]

Interrupt

Controller

CRST1

CCLK1

Alternate

Card

CIO1

LI

CVCC

DC/DC

Converter

USB

Interface

D+

CVSS

CPRES

CRST

CCL K

ISO 7816

Interface

3.3V

Regulator

D-

VREF

AVSS

AVCC

CIO

CC4

CC8

DVCC

4202E–SCR–06/06

5

Page 6

AT8xC5122/23

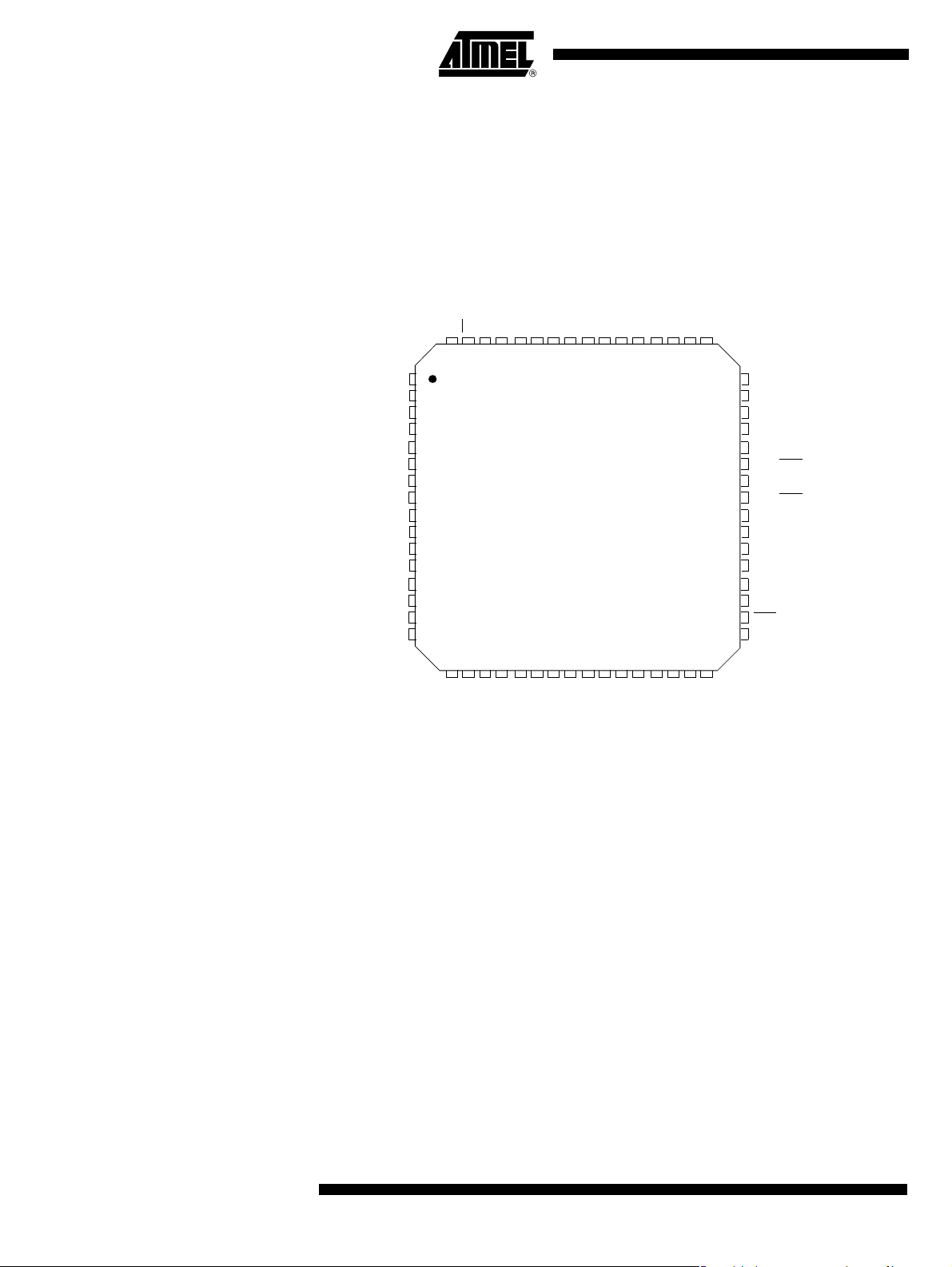

Pinout

High Pin Count Package Description

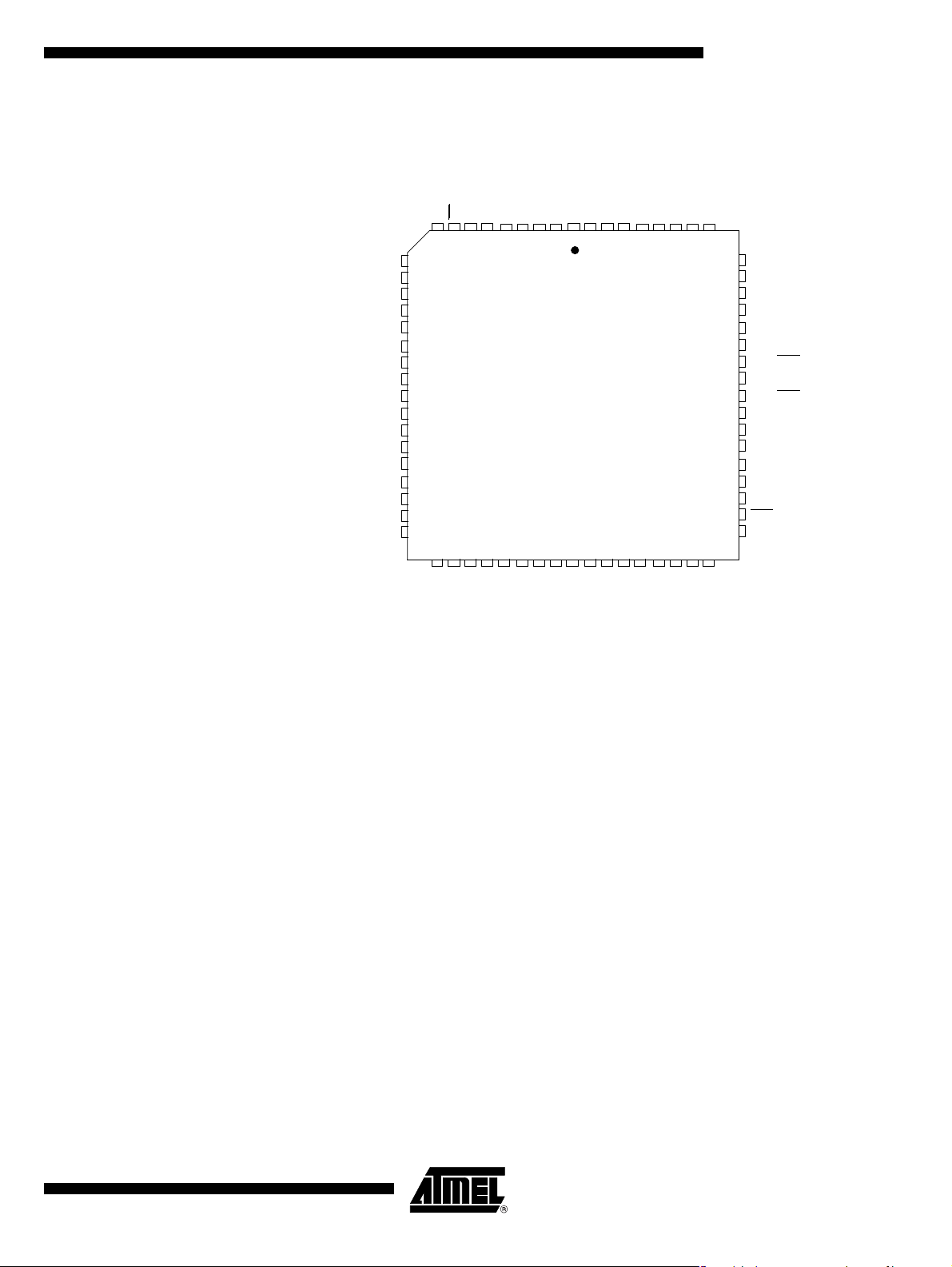

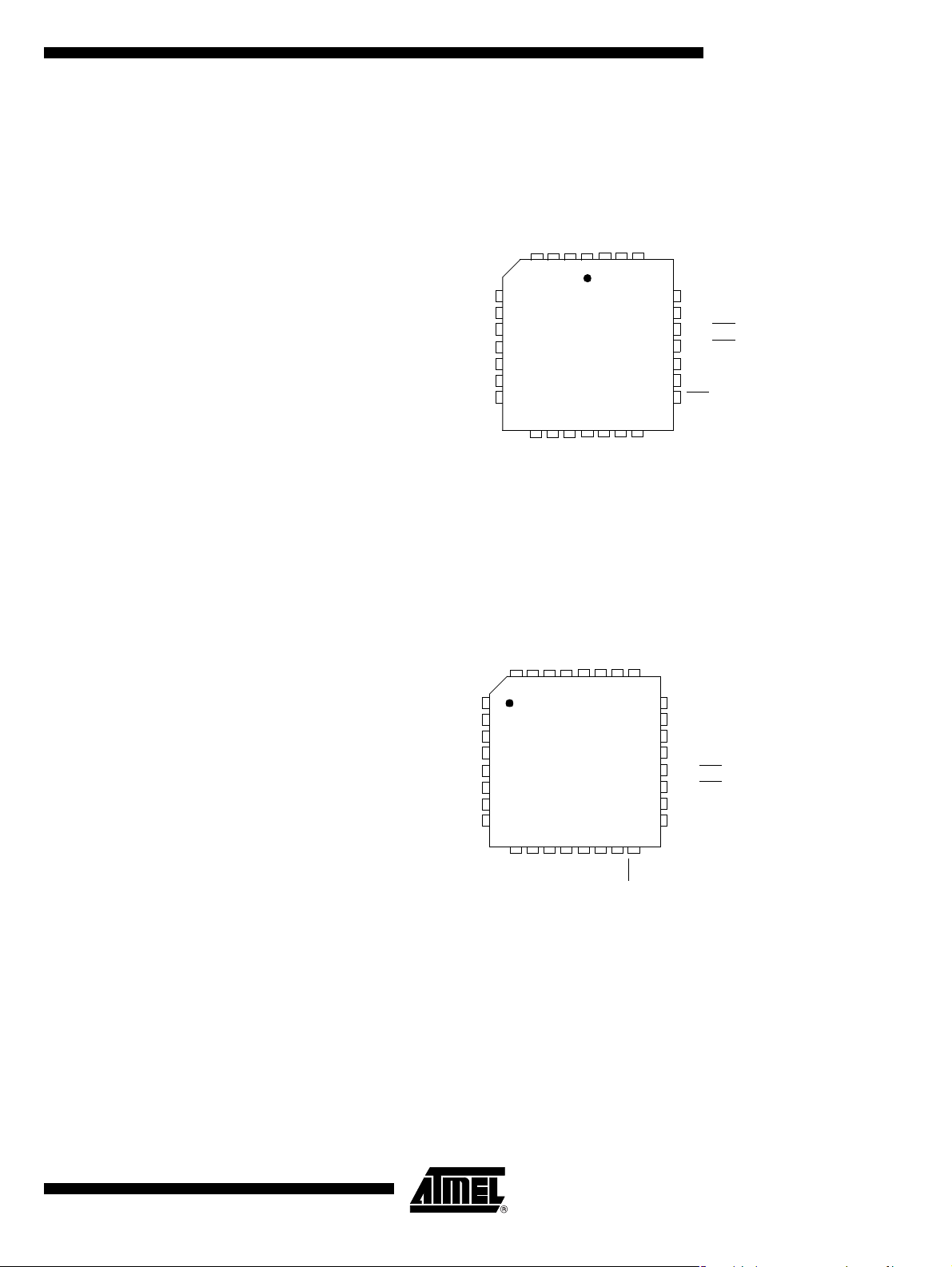

A T8xC5122 version Figure 1. VQFP64 Package Pinout

D+

P1.7/CCLK1

DVCC

P1.2/CPRES

CC8

P5.7/KB7

P5.6/KB6

CRST

P5.5/KB5

P5.4/KB4

CC4

P5.3/KB3

P5.2/KB2

CCLK

P5.1/KB1

P5.0/KB0

PSEN

VSS

CIO

64 52

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

EA

VREF

62 61 60 59 58 63

D-

P2.1/A9

P2.0/A8

57

56 55 54 53

P2.2/A10

VQFP64

AVCC

PLLF

P2.3/A11

51 50

49

P2.6/A14

P3.1/TxD

48

P1.6/SS

47

P2.7/A15

46

P3.0/RxD

45

P3.5/T1/CRST1

44

P3.2/INT0/LED0/CIO1

43

42

P4.0/MISO

P3.3/INT1

41

P4.1/MOSI

40

P3.4/T0/LED1

39

P4.2/SCK

38

P4.3/LED4

37

P3.6/WR/LED2

36

35

P4.4/LED5

34

RST

33

P4.5/LED6

P2.5/A13

P2.4/A12

AVSS

CVCC

30 29 28 27 26 25 24 23 22 21 20 19 18 17

31 32

LI

ALE

VCC

CVSS

P0.7/AD7

P0.6/AD6

P0.5/AD5

P0.4/AD4

P3.7/RD/LED3

P0.3/AD3

P0.2/AD2

P0.1/AD1

P0.0/AD0

XTAL1

XTAL2

6

4202E–SCR–06/06

Page 7

AT8xC5122/23

Figure 2. PLCC68 Package Pinout (for engineering purpose only)

DVCC

P1.2/CPRES

CC8

P5.7/KB7

P5.6/KB6

CRST

P5.5/KB5

P5.4/KB4

CC4

P5.3/KB3

P5.2/KB2

CCLK

P5.1/KB1

P5.0/KB0

PSEN

VSS

NC

P1.7/CCLK1

EA

CIO

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

LI

NC

CVCC

D-

VREF

D+

ALE

VCC

CVSS

P2.2/A10

P2.1/A9

P2.0/A8

AVCC

1686766656463 62 6123456789

PLCC68

35 36 37 38 39 40 41 42 433433323130292827

P0.5/AD5

P0.7/AD7

P0.6/AD6

P0.4/AD4

PLLF

P3.7/RD/LED3

AVSS

P0.3/AD3

P0.2/AD2

P2.3/A11

P2.5/A13

P2.4/A12

P2.6/A14

N/A

N/A

60

P3.1/TxD

59

58

P1.6/SS

P2.7/A15

57

P3.0/RxD

56

55

P3.5/T1/CRST1

54

P3.2/INT0/LED0/CIO1

P4.0/MISO

53

52

P3.3/INT1

P4.1/MOSI

51

P3.4/T0/LED1

50

P4.2/SCK

49

P4.3/LED4

48

P3.6/WR/LED2

47

P4.4/LED5

46

RST

45

P4.5/LED6

44

NC : not connected

XTAL2

P0.1/AD1

XTAT1

P0.0/AD0

N/A : not available

4202E–SCR–06/06

7

Page 8

AT8xC5122/23

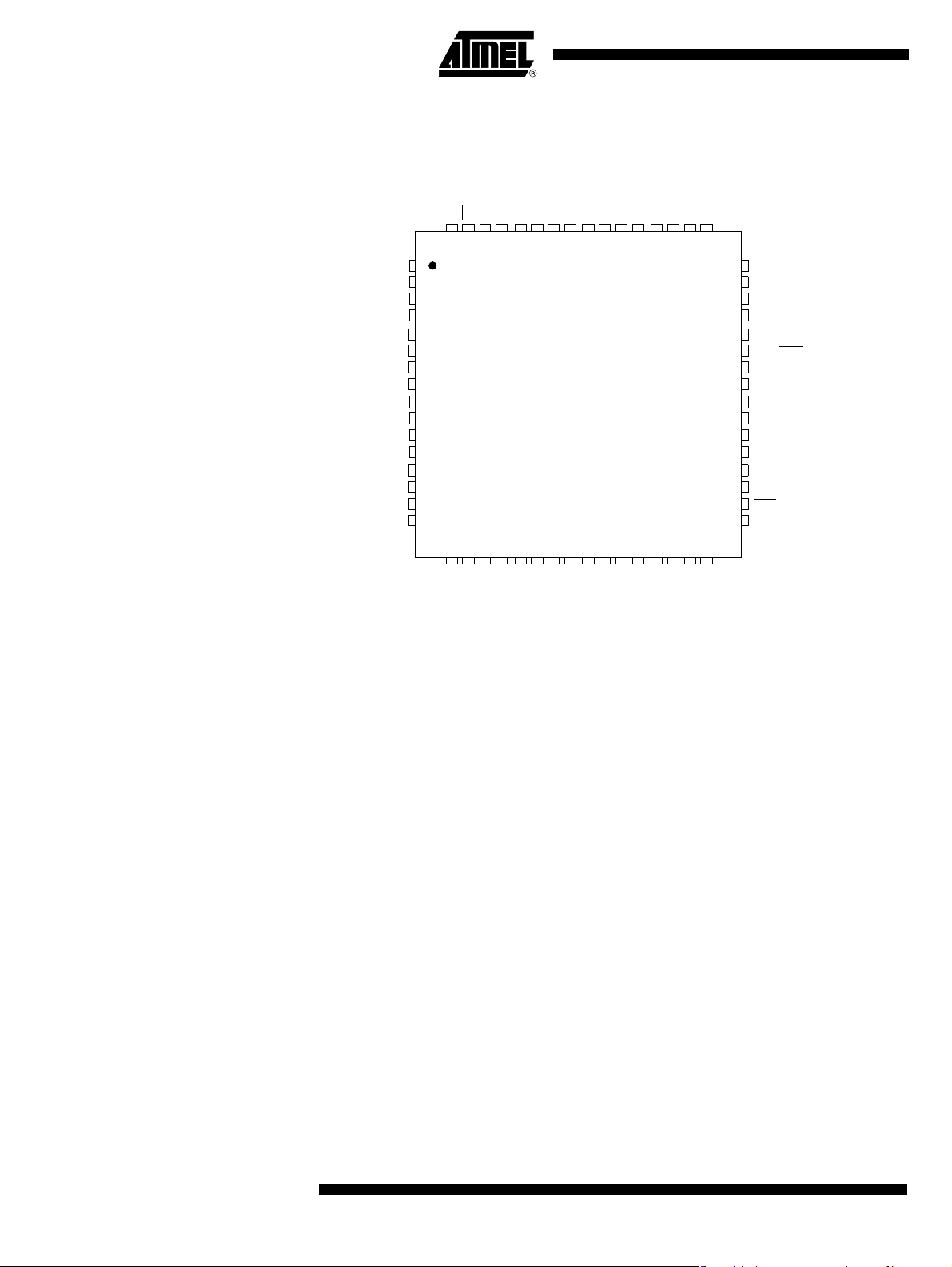

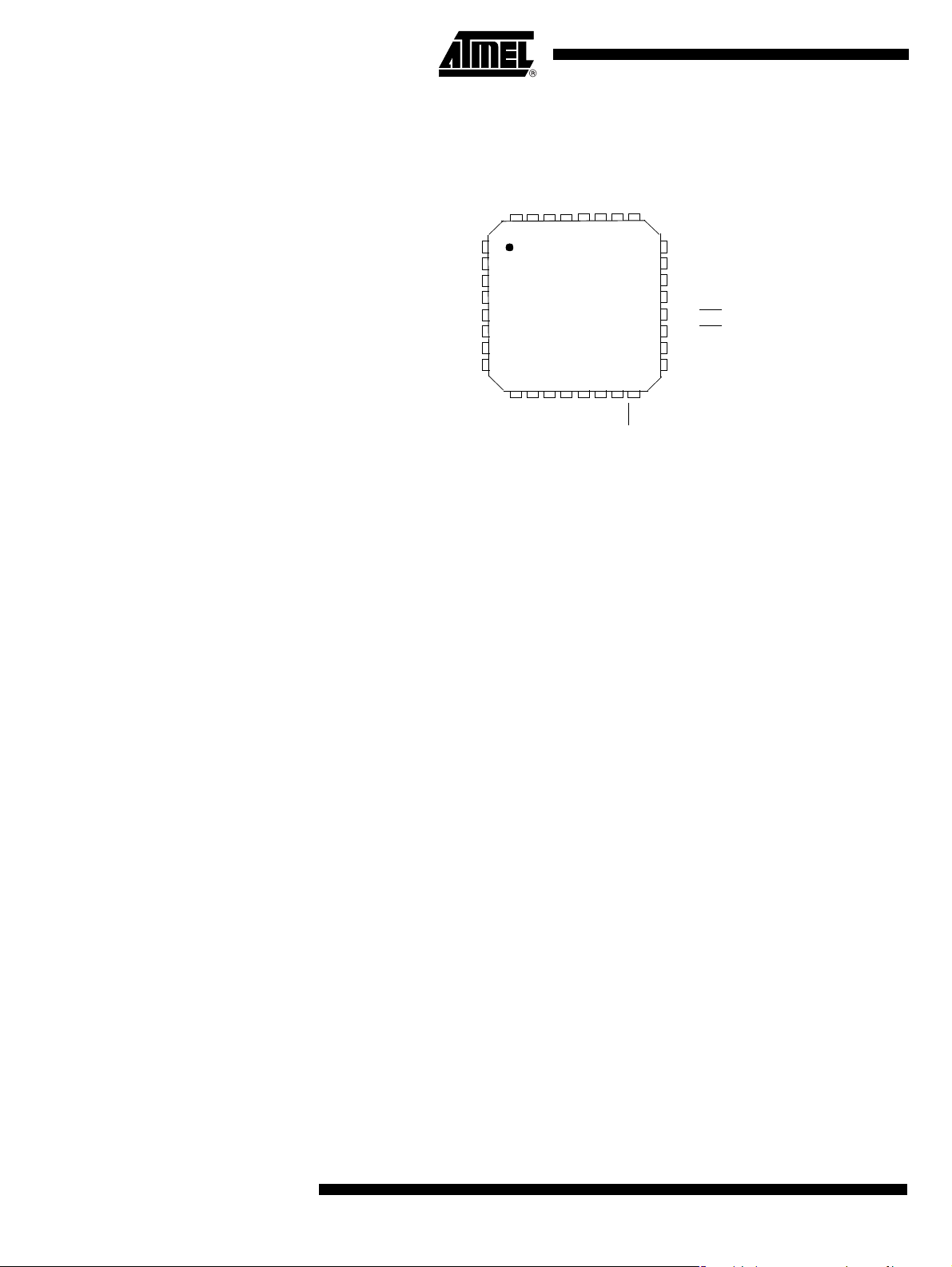

Figure 3. QFN64 Package Pinout

P1.7/CCLK1

DVCC

P1.2/CPRES

CC8

P5.7/KB7

P5.6/KB6

CRST

P5.5/KB5

P5.4/KB4

CC4

P5.3/KB3

P5.2/KB2

CCLK

P5.1/KB1

P5.0/KB0

PSEN

VSS

CIO

64 52

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

EA

VREF

62 61 60 59 58 63

D-

D+

QFN64

P2.1/A9

P2.0/A8

57

56 55 54 53

P2.5/A13

P2.2/A10

AVCC

PLLF

P2.4/A12

AVSS

P2.3/A11

51 50

49

P2.6/A14

P3.1/TxD

48

P1.6/SS

47

P2.7/A15

46

P3.0/RxD

45

P3.5/T1/CRST1

44

P3.2/INT0/LED0/CIO1

43

42

P4.0/MISO

P3.3/INT1

41

P4.1/MOSI

40

P3.4/T0/LED1

39

P4.2/SCK

38

P4.3/LED4

37

P3.6/WR/LED2

36

35

P4.4/LED5

34

RST

33

P4.5/LED6

CVCC

30 29 28 27 26 25 24 23 22 21 20 19 18 17

31 32

LI

ALE

VCC

CVSS

P0.1/AD1

P0.7/AD7

P0.6/AD6

P0.5/AD5

P0.4/AD4

P3.7/RD/LED3

P0.3/AD3

P0.2/AD2

P0.0/AD0

XTAL2

XTAL1

8

4202E–SCR–06/06

Page 9

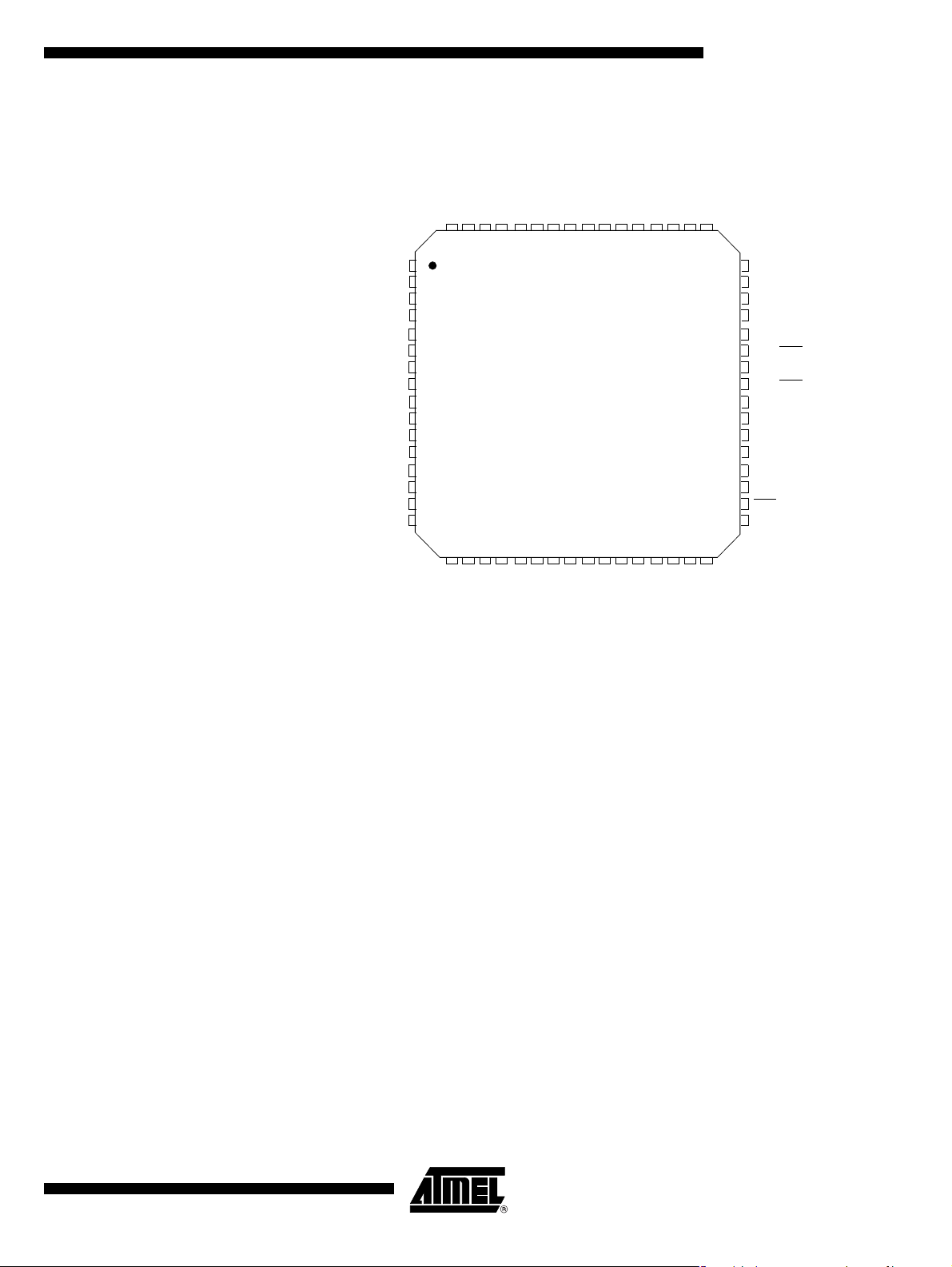

A T89C5122DS version Figure 4. VQFP64 Package Pinout

P1.7/CCLK1

DVCC

P1.2/CPRES

CC8

P5.7/KB7

P5.6/KB6

CRST

P5.5/KB5

P5.4/KB4

CC4

P5.3/KB3

P5.2/KB2

CCLK

P5.1/KB1

P5.0/KB0

PSEN

VSS

CIO

64 52

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

VREF

VCC

D+

62 61 60 59 58 63

P2.2/A10

P2.1/A9

P2.0/A8

D-

57

56 55 54 53

VQFP64

AT8xC5122/23

P2.5/A13

P2.4/A12

AVSS

AVCC

PLLF

P2.3/A11

51 50

49

P2.6/A14

P3.1/TxD

48

P1.6/SS

47

P2.7/A15

46

P3.0/RxD

45

P3.5/T1/CRST1

44

P3.2/INT0/LED0/CIO1

43

42

P4.0/MISO

P3.3/INT1

41

P4.1/MOSI

40

P3.4/T0/LED1

39

P4.2/SCK

38

P4.3/LED4

37

P3.6/WR/LED2

36

35

P4.4/LED5

34

RST

33

P4.5/LED6

CVCC

30 29 28 27 26 25 24 23 22 21 20 19 18 17

31 32

LI

ALE

VCC

CVSS

P0.1/AD1

P0.7/AD7

P0.6/AD6

P0.5/AD5

P0.4/AD4

P3.7/RD/LED3

P0.3/AD3

P0.2/AD2

P0.0/AD0

XTAL2

XTAL1

4202E–SCR–06/06

9

Page 10

AT8xC5122/23

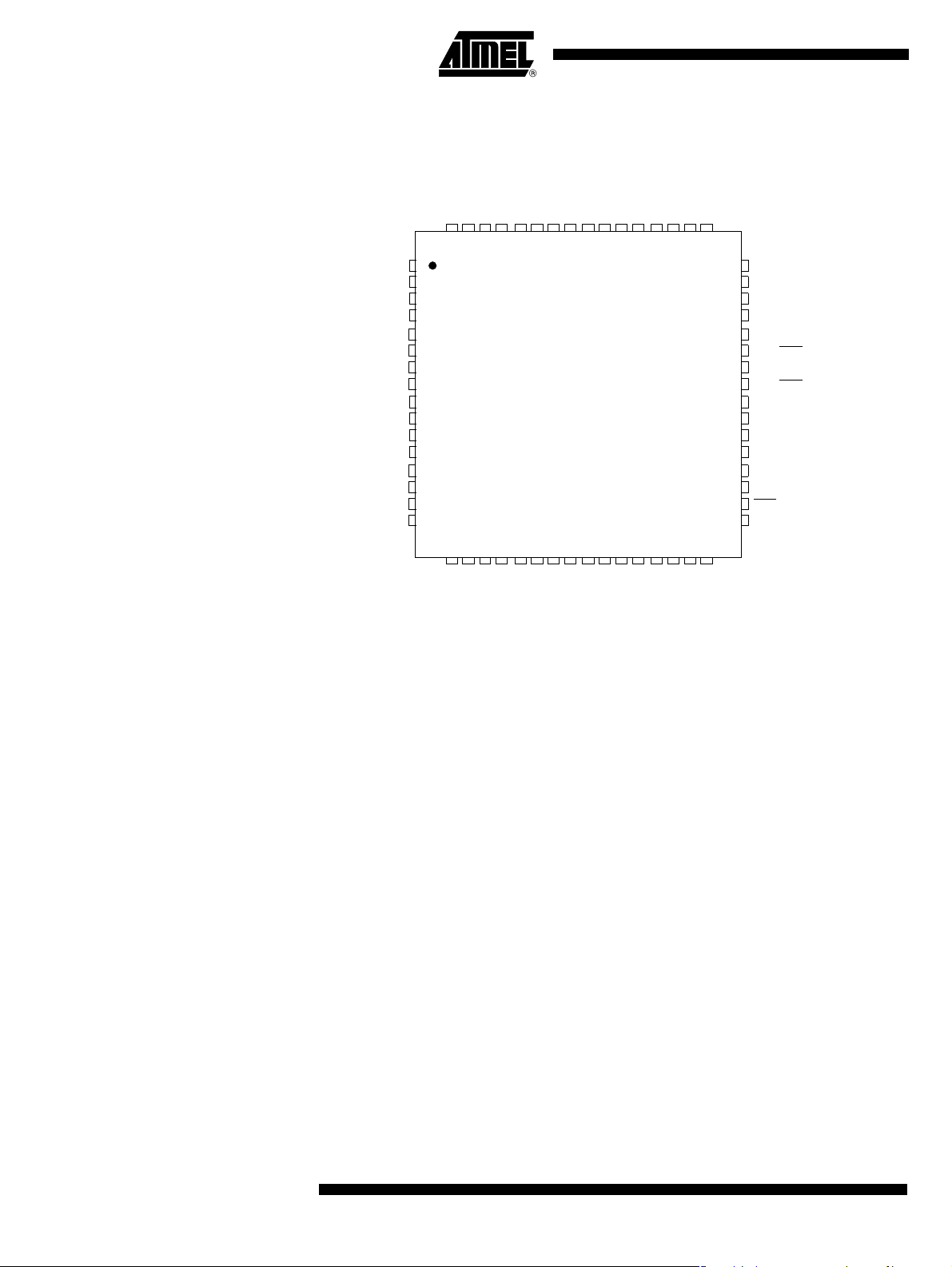

Figure 5. QFN64 Package Pinout

DVCC

P1.2/CPRES

CC8

P5.7/KB7

P5.6/KB6

CRST

P5.5/KB5

P5.4/KB4

CC4

P5.3/KB3

P5.2/KB2

CCLK

P5.1/KB1

P5.0/KB0

PSEN

VSS

VCC

P1.7/CCLK1

CIO

62 61 60 59 58 63

64 52

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

LI

CVSS

CVCC

D-

VREF

D+

ALE

VCC

P0.7/AD7

P2.2/A10

P2.1/A9

P2.0/A8

57

56 55 54 53

QFN64

P0.5/AD5

P0.4/AD4

P0.6/AD6

AVCC

P3.7/RD/LED3

AVSS

PLLF

P2.3/A11

P0.1/AD1

P0.3/AD3

P0.2/AD2

51 50

30 29 28 27 26 25 24 23 22 21 20 19 18 17

49

31 32

XTAL1

P0.0/AD0

P2.6/A14

P3.1/TxD

48

P1.6/SS

47

P2.7/A15

46

P3.0/RxD

45

P3.5/T1/CRST1

44

P3.2/INT0/LED0/CIO1

43

42

P4.0/MISO

P3.3/INT1

41

P4.1/MOSI

40

P3.4/T0/LED1

39

P4.2/SCK

38

P4.3/LED4

37

P3.6/WR/LED2

36

35

P4.4/LED5

34

RST

33

P4.5/LED6

XTAL2

P2.5/A13

P2.4/A12

10

4202E–SCR–06/06

Page 11

Low Pin Count Package Description

AT8xC5122/23

AT8xC5122 and AT83C5123

Figure 6. PLCC28 Package Pinout

versions

DVCC

P1.2/CPRES

CC8

CRST

CC4

CCLK

VSS

5

6

7

8

9

10

11

A T83C5123 version Figure 7. VQFP32 Package Pinout

CIO

D-D+AVCC

VREF

1234282726

PLCC28

15141312 1617 18

LI

VCC

CVSS

CVCC

AVSS

PLLF

P3.1/TxD

25

P3.0/RxD

24

P3.2/INT0/LED0

23

P3.3/INT1

22

P3.4/T0/LED1

21

P3.6/LED2

20

19

RST

XTAL1

XTAL2

P3.7/LED3

DVCC

P1.2/CPRES

CC8

CRST

CC4

CCLK

P5.0

VSS

1

2

3

4

5

6

7

8

CIO

P1.7/CCLK1

VREF

VQFP32

1211109 131415

LI

CVSS

CVCC

D-D+AVCC

28 27 26

VCC

P3.7/LED3

AVSS

PLLF

2529303132

P3.1/TxD

24

P1.6

23

P3.0/RxD

22

P3.5/T1/CRST1

21

P3.2/INT0/LED0/CIO1

20

P3.3/INT1

19

P3.4/T0/LED1

18

P3.6/LED2

17

16

RST

XTAL1

XTAL2

4202E–SCR–06/06

11

Page 12

AT8xC5122/23

Figure 8. QFN32 Package Pinout

DVCC

P1.2/CPRES

CC8

CRST

CC4

CCLK

P5.0

VSS

CIO

P1.7/CCLK1

1

2

3

4

5

6

7

8

LI

CVCC

D-D+AVCC

VREF

28 27 26

QFN32

1211109 131415

VCC

CVSS

P3.7/LED3

AVSS

PLLF

2529303132

P3.1/TxD

24

P1.6

23

P3.0/RxD

22

P3.5/T1/CRST1

21

P3.2/INT0/LED0/CIO1

20

P3.3/INT1

19

P3.4/T0/LED1

18

P3.6/LED2

17

16

RST

XTAL1

XTAL2

12

4202E–SCR–06/06

Page 13

AT8xC5122/23

Pin Descript i on

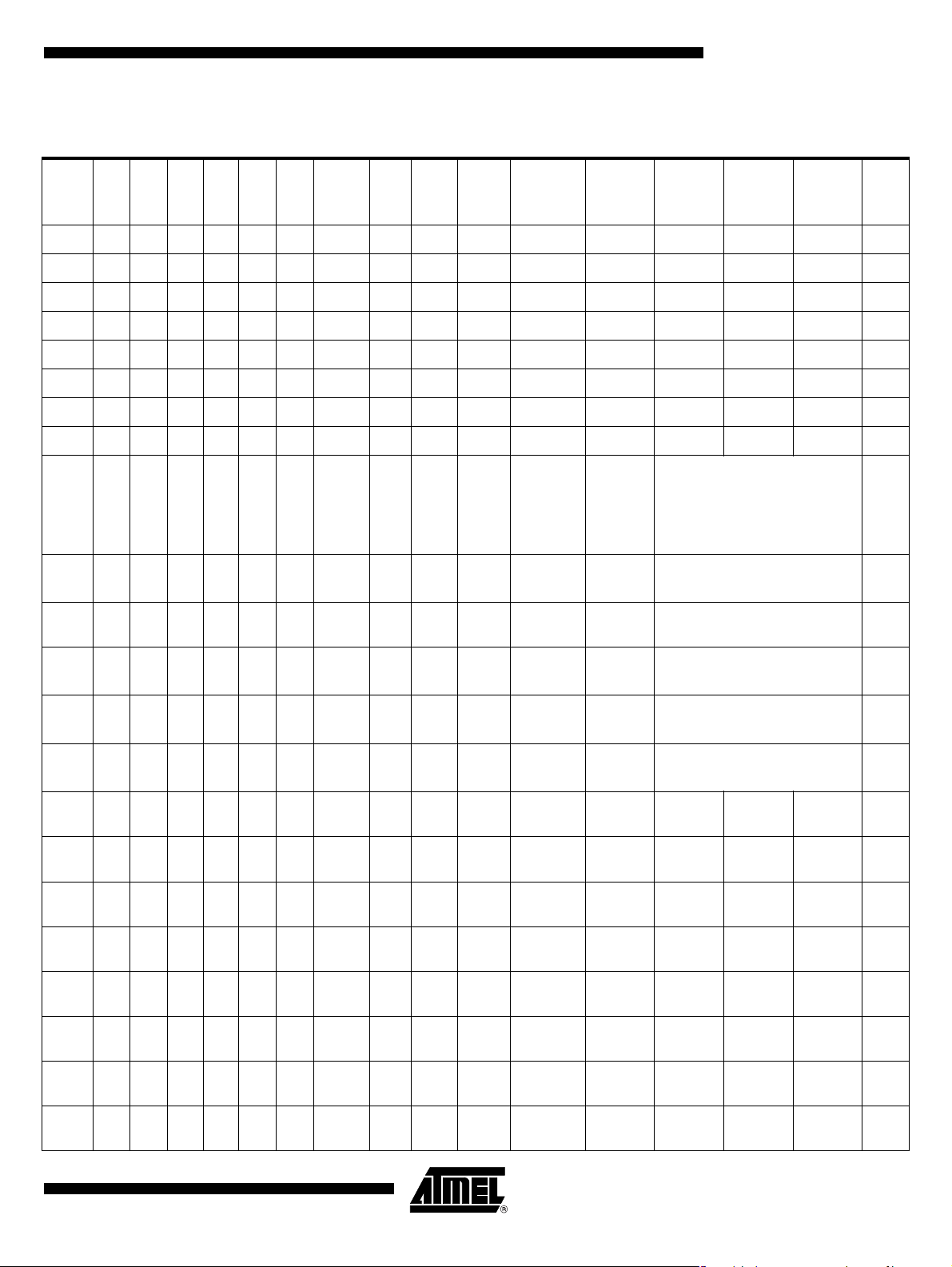

Table 2. Pin Description

Internal

Power

QFN64

Port

P0.0 30 - 41 - 30 - VCC 2KV I/O Float AD0 P0 KB_OUT Push-pull

P0.1 29 - 40 - 29 - VCC 2KV I/O Float AD1 P0 KB_OUT Push-pull

P0.2 28 - 39 - 28 - VCC 2KV I/O Float AD2 P0 KB_OUT Push-pull

P0.3 27 - 38 - 27 - VCC 2KV I/O Float AD3 P0 KB_OUT Push-pull

P0.4 25 - 36 - 25 - VCC 2KV I/O Float AD4 P0 KB_OUT Push-pull

P0.5 24 - 35 - 24 - VCC 2KV I/O Float AD5 P0 KB_OUT Push-pull

P0.6 23 - 34 - 23 - VCC 2KV I/O Float AD6 P0 KB_OUT Push-pull

P0.7 22 - 33 - 22 - VCC 2KV I/O Float AD7 P0 KB_OUT Push-pull

CIO 64 32 9 4 64 32 CVCC 6KV I/O 0 Port51

VQFP64

VQFP32

PLCC68

PLCC28

QFN32

Supply ESD I/O

Reset

Level Alt

Reset

Config Conf 1 Conf 2 Conf 3 Led

CVCC inactive at reset.

ESD tes ted with a 10µF on CVCC

An external pull-up of 10K is

recommended to support ICC’s

with too high internal pull-ups.

CC4 3 3 12 7 3 3 CVCC 6KV I/O 0 Port51

P1.2 2 2 11 6 2 2 VCC 2KV I/O 1 CPRES Port51

CC4 9 5 18 9 9 5 CVCC 6KV I/O 0 Port51

CCLK 12 6 21 10 12 6 CVCC 6KV O 0 Push-pull

CRST 6 4 15 8 6 4 CVCC 6KV O 0 Push-pull

P1.6 47 23 58 - 47 23 VCC 2KV I/O 1 SS Port51

P1.7 62 31 7 - 62 31 VCC 2KV I/O 1 CCLK1 Port51

P2.0 58 - 3 - 58 - VCC 2KV I/O 1 A8 Port51 Push-pull KB_OUT

P2.1 57 - 2 - 57 - VCC 2KV I/O 1 A9 Port51 Push-pull KB_OUT

P2.2 56 - 1 - 56 - VCC 2KV I/O 1 A10 Port51 Push-pull KB_OUT

P2.3 52 - 65 - 52 - VCC 2KV I/O 1 A11 Port51 Push-pull KB_OUT

CVCC inactive at reset

ESD tes ted with a 10µF on CVCC

Weak & medium pull-u p can be

disconnected

CVCC inactive at reset

ESD tes ted with a 10µF on CVCC

CVCC inactive at reset

ESD tes ted with a 10µF on CVCC

CVCC inactive at reset

ESD tes ted with a 10µF on CVCC

Input

WPU

Input

WPU

Input

WPU

Input

WPU

P2.4 51 - 64 - 51 - VCC 2KV I/O 1 A12 Port51 Push-pull KB_OUT

P2.5 50 - 63 - 50 - VCC 2KV I/O 1 A13 Port51 Push-pull KB_OUT

4202E–SCR–06/06

Input

WPU

Input

WPU

13

Page 14

AT8xC5122/23

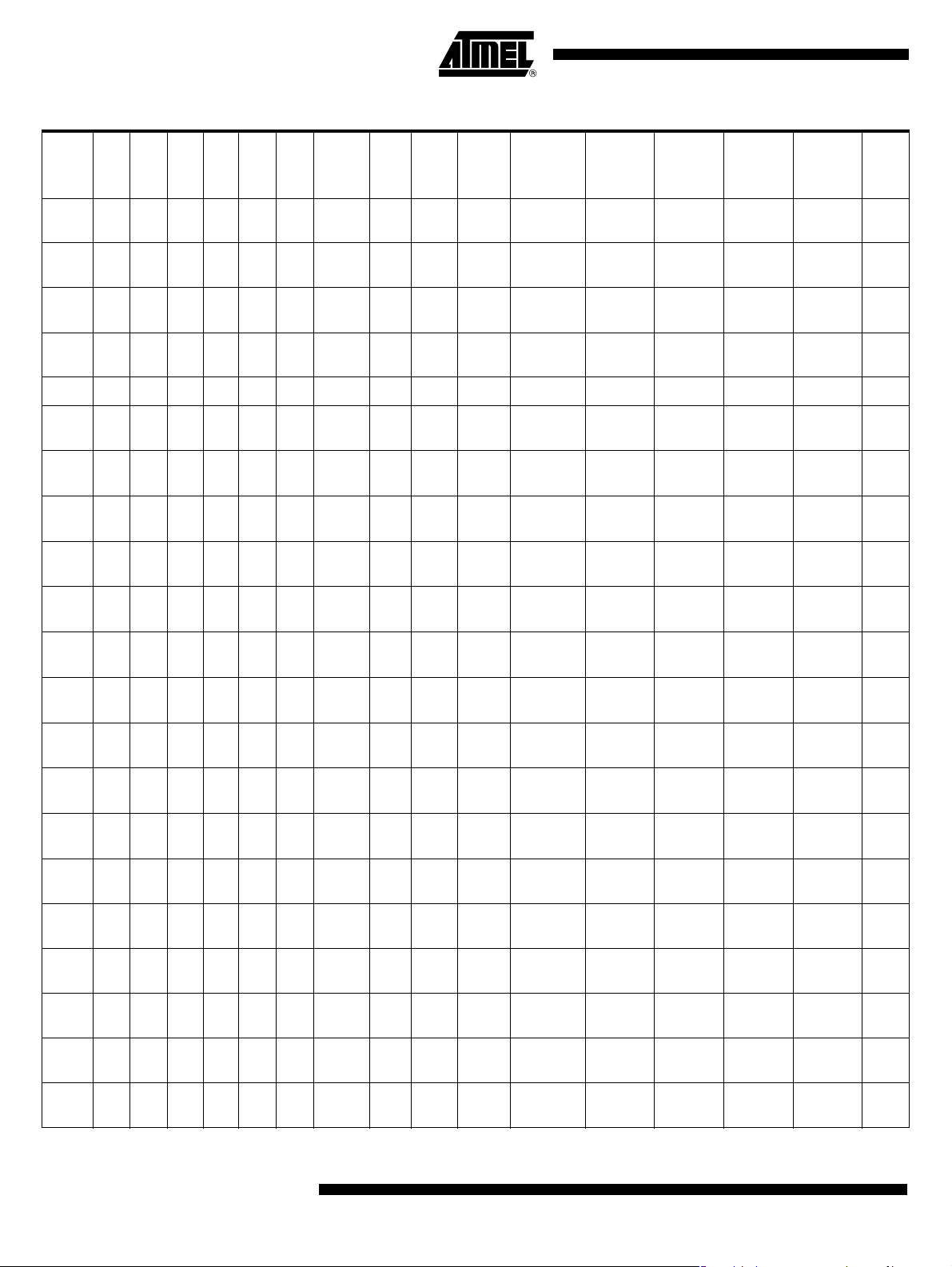

Table 2. Pin Description (Continued)

Port

VQFP64

VQFP32

PLCC68

QFN64

PLCC28

Internal

Power

QFN32

Supply ESD I/O

Reset

Level Alt

Reset

Config Conf 1 Conf 2 Conf 3 Led

P2.6 49 - 62 - 49 - VCC 2KV I/O 1 A14 Port51 Push-pull KB_OUT

P2.7 46 - 57 - 46 - VCC 2KV I/O 1 A15 Port51 Push-pull KB_OUT

P3.0 45 22 56 24 45 22 VCC 2KV I/O 1 RxD Port51 Push-pull KB_OUT

P3.1 48 24 59 25 48 24 VCC 2KV I/O 1 TxD Port51 Push-pull KB_OUT

P3.2 43 20 54 23 43 20 VCC 2KV I/O 1 INT0 Port51 LED0

P3.3 41 19 52 22 41 19 VCC 2KV I/O 1 INT1 Port51 Push-pull KB_OUT

P3.4 39 18 50 21 39 18 VCC 2KV I/O 1 T0 Port51 Push-pull KB_OUT

P3.5 44 21 55 - 44 21 VCC 2KV I/O 1 T1 Port51

P3.6 36 17 47 20 36 17 VCC 2KV I/O 1 WR Port51 LED2

P3.7 26 13 37 16 26 13 VCC 2KV I/O 1 RD Port51 LED3

P4.0 42 - 53 - 42 - VCC 2KV I/O 1 MISO Port51

Input

WPU

Input

WPU

Input

WPU

Input

WPU

Input

WPU

Input

WPU

LED1

P4.1 40 - 51 - 40 - VCC 2KV I/O 1 MOSI Port51

P4.2 38 - 49 - 38 - VCC 2KV I/O 1 SCK Port51

P4.3 37 - 48 - 37 - VCC 2KV I/O 1 Port51 Push-pull KB_OUT

P4.4 35 - 46 - 35 - VCC 2KV I/O 1 Port51 Push-pull KB_OUT

P4.5 33 - 44 - 33 - VCC 2KV I/O 1 Port51 Push-pull KB_OUT

P5.0 14 7 23 - 14 7 VCC 2KV I/O 1 KB0 Port51 Push-pull

P5.1 13 - 22 - 13 - VCC 2KV I/O 1 KB1 Port51 Push-pull

P5.2 11 - 20 - 11 - VCC 2KV I/O 1 KB2 Port51 Push-pull

P5.3 10 - 19 - 10 - VCC 2KV I/O 1 KB3 Port51 Push-pull

P5.4 8 - 17 - 8 - VCC 2KV I/O 1 KB4 Port51 Push-pull

Input

MPU

Input

MPU

Input

MPU

Input

WPD

Input

WPD

Input

MPU

Input

MPU

Input

MPU

Input

WPU

Input

WPU

Input

WPU

Input

WPU

Input

WPU

LED4

LED5

LED6

14

4202E–SCR–06/06

Page 15

Table 2. Pin Description (Continued)

Port

VQFP64

VQFP32

PLCC68

QFN64

PLCC28

Internal

Power

QFN32

Supply ESD I/O

Reset

Level Alt

AT8xC5122/23

Reset

Config Conf 1 Conf 2 Conf 3 Led

P5.5 7 - 16 - 7 - VCC 2KV I/O 1 KB5 Port51 Push-pull

P5.6 5 - 14 - 5 - VCC 2KV I/O 1 KB6 Port51 Push-pull

P5.7 4 - 13 - 4 - VCC 2KV I/O 1 KB7 Port51 Push-pull

Reset Input

The Port pins are driven to their reset conditions when a voltage

is applied, whether or not the oscillator is running.

IL

when the chip is in Idle mode or Power-Down mode

Ω

VREF < 3.6 V

can be connected to D+ through a 1.5 KΩ resistor. The V

RST

V

34 16 45 19 34 16 VCC I/0

D+ 60 29 5 2 60 29 DVCC I/O

D- 59 28 4 1 59 28 DVCC I/O

61 30 6 3 61 30 AVCC O

REF

lower than V

This pin has an internal 10K pull-up resistor which allows the device

to be reset by connecting a capacit or between this pi n and VSS.

Asserting RST

returns the chip to normal operation.

The output is active for at least 12 oscillator periods when an internal

reset occurs.

USB Positive Data Upstream Port

This pin requires an external serial resistor of 27Ω (AT8xC122) or

33Ω (AT83C5123) and a 1.5 K

configuration.

USB Negative Data Upstream Port

This pin requires an external serial resistor of 27Ω (AT8xC122) or

33Ω (AT83C5123)

USB Voltage Reference: 3.0 <

V

REF

voltage is controlled by software.

Input

WPD

Input

WPD

Input

WPD

pull-up to VREF for full speed

Input

WPU

Input

WPU

Input

WPU

REF

XTAL

XTAL

VCC

ALE21-32-21- VCC O

31 14 42 17 31 14 VCC I

1

32 15 43 18 32 15 VCC O

2

EA

/

63 - 8 - 63 - VCC I

Input to the on-chip inverting oscillator amplifier

To use the internal oscillator, a crystal or an external oscillator must

be conn ected to this pin.

Output of the on-chip inverting oscillator amplifier

To use the internal oscillator, a crystal circuit must be connected to

this pin. If an external oscillator is used, leave XTAL2 unconnected.

Exter nal Access Enable (Only AT8xC5122)

must be strapped to ground in order to enable the device to fetch

EA

code from external memory locations 0000h to FFFFh.

If security level 1 is programmed, EA

Warning : EA pin cannot be left floating. If the External Access

Enable mod e i s not u se d, EA pi n mus t b e st rapp ed to V CC . I f this l ast

condition is not met,the MCU may have an unpredictable behaviour.

VCC (Only AT89C5122DS)

Address Latch Enable/Program Pulse: Ou tp ut puls e f or latc hing

the low byte of the address during an access to external memory. In

normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2

mode) t he os cil lat or f r equ enc y, and can be use d fo r ex ter nal t i mi ng or

clocki ng. Note that one ALE pulse is skipped during each access to

external data memory. ALE can be disabled by setting SFR’s

AUXR.0 bit. With this bit set, ALE will be inactive during internal

fetches

will be latched on reset.

4202E–SCR–06/06

15

Page 16

AT8xC5122/23

Table 2. Pin Description (Continued)

Internal

Power

QFN64

Port

PSEN 15 - 24 - 15 - VCC O

VQFP64

VQFP32

PLCC68

PLCC28

QFN32

Supply ESD I/O

Reset

Level Alt

Program Strobe Enable: The read strobe to external program

memory. When executing code from the external program memory,

PSEN

activations are skipped during each access to external data memory.

PSEN

Reset

Config Conf 1 Conf 2 Conf 3 Led

is activated twice each machine cycle, except that two PSEN

is not activated during fetches from internal program memory.

PLLF 54 26 67 27 54 26 AVCC O

AVCC 55 27 68 28 55 27 PWR

VCC201231152012 PWR

LI 18 10 29 13 18 10 PWR

CVCC 17 9 28 12 17 9 PWR

DVCC 1 1 10 5 1 1 PWR

PLL Low Pass Filter input

Receives the RC network of the PLL low pass filter.

Analog Supply Voltage

AVCC is used to supply the internal 3.3V analog regulator which

supplies the i nternal USB driver

Supply Voltage

VCC is used to supply the internal 3.3V digital regulator which

supplies the PLL, CPU core and internal I/O ’s

DC/DC Input

LI supplies the current for the charge pump of the DC/DC converter.

- LI tied directly to VCC : the DC/DC converter must be configured in

regulator mode.

- LI tied to VC C through an ext ernal 10 µH coil : the DC/DC convert er

can be configured either in regulator or in pump mode.

Card Supply Voltage

CVCC is t he ouput of internal DC/DC co nverter w hich supplies the

Smart Card Interface. It must be connected to an external decoupling

capacitor of 10 µF with the lowest ESR as this parameter influences

on the CVCC noise

Digital Supply V olta ge

DVCC is t he output of the internal analog 3.3V regulator whi c h

supplies the USB driver. This pin must be connected to an external

680nF decoupling capacitor if the USB interface is used.

This ou tpu t ca n be use d by th e ap pl ic ati on w ith a max im um of 10 mA.

CVSS 19 11 30 14 19 11 GND

VSS 16 8 25 11 16 8 GND

AVSS 53 25 66 26 53 25 GND

16

DC/DC Ground

CVSS is used to sink high shunt currents from the external coil

Digital Ground

VSS is used to supply the PLL, buffer ring and the digital core

Analog Ground

AVSS is used to supply the USB driver.

4202E–SCR–06/06

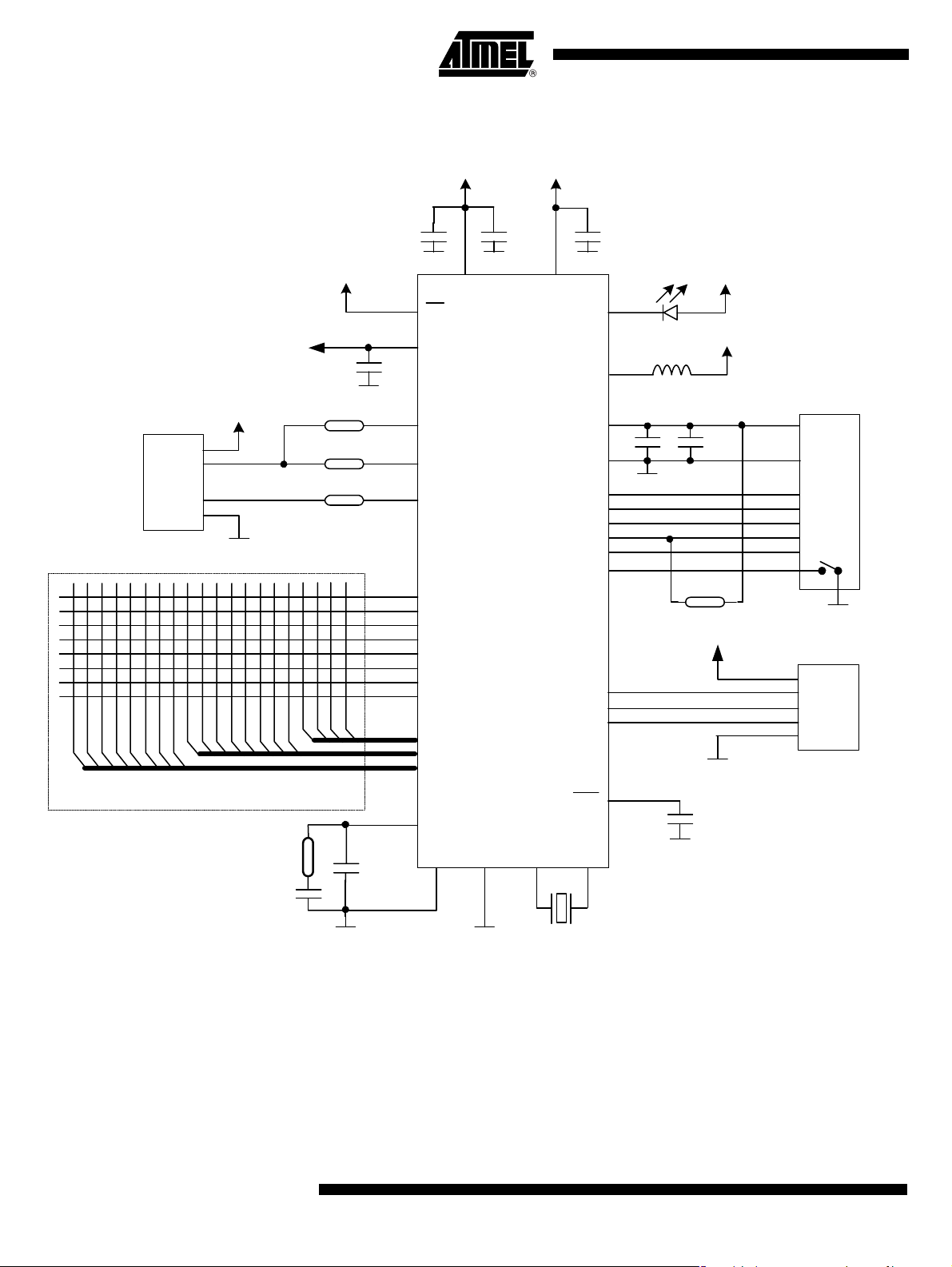

Page 17

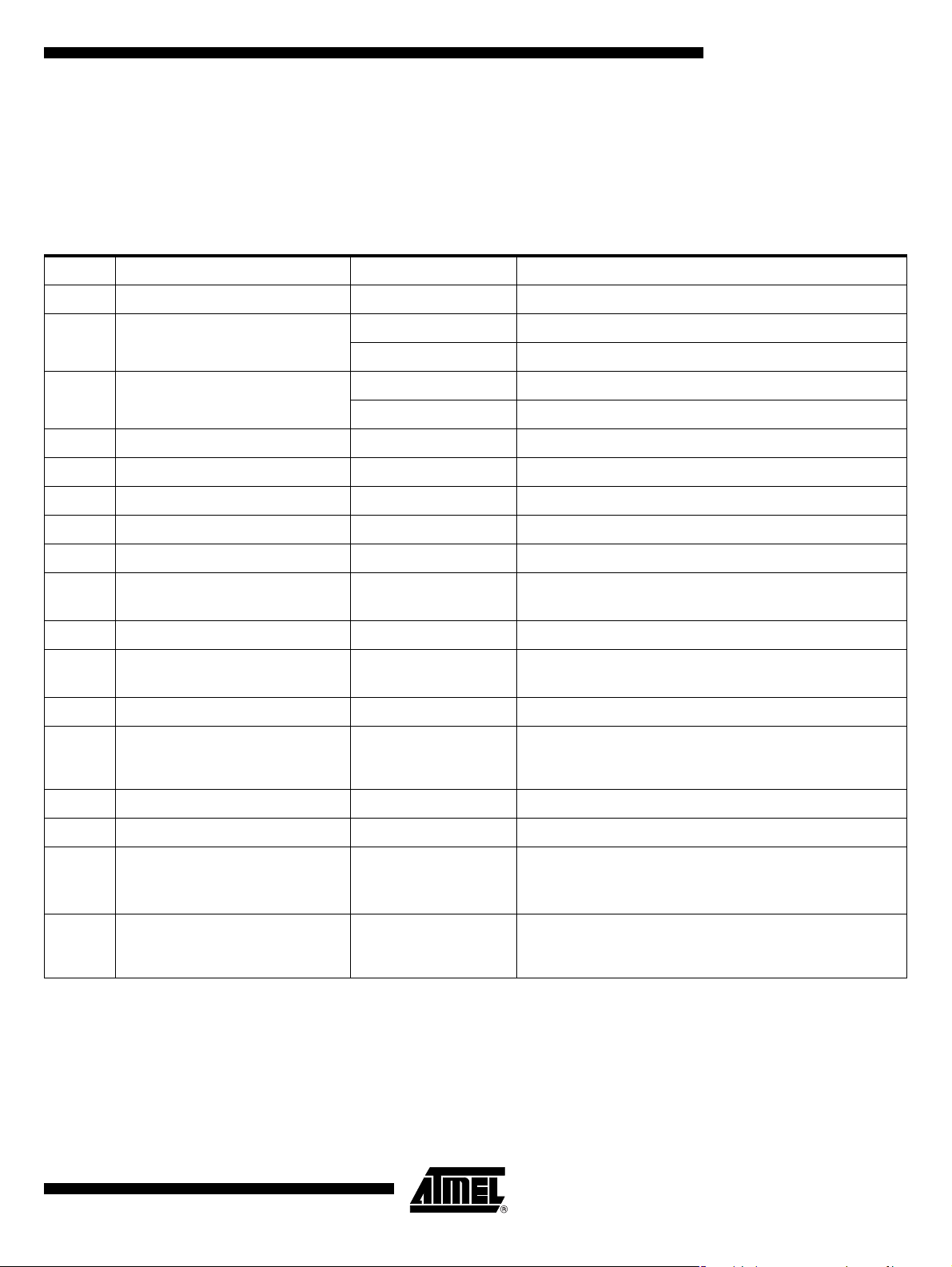

Typical Applications

Recommended External components

All the external components described in the figure and table below must be implemented as close as possible from the microcontroller package.

Table 3. External Components Bill Of Materials

Reference Description Value Comments

R1 USB Full Speed Pull-up 1.5 KΩ +/-10% All product versions

AT8xC5122/23

R2 USB pad serial resistor

R3 USB pad serial resistor

R4 PLL filter resis tor 1.8 KΩ +/-10% All product versions

R5 CIO Pull-up resistor 10 KΩ +/10% All product versions

C1 Power Supply filter capacitor 100 nF +80/-20% All product versions

C2 PLL filter capacitor 33 pF +/-10% All product versions

C3 PLL filter capacitor 150 pF +/-10% All product versions

C4 USB pad decoupling c apacitor 680 nF +/-30%

C5 Smart Card clock filter capacitor 27 pF +/-10% All product versions.

C6 DC/DC Converter decoupling capacitor

C7 DC/DC Converter filter capacitor 100 nF +80/-20% All product versions

C8 Power Supply decoupling capacitor 4.7 µF +/-10%

27 Ω +/-10% For AT8xC 5122 versions

33 Ω +/-10% For AT83C5123 versions

27 Ω +/-10% For AT8xC 5122 versions

33 Ω +/-10% For AT83C5123 versions

All product versions.

If USB interface is not used, this capacitor is optional

10 µF +/-10%

Low ESR

All product versions.

This capacitor does not impact the USB Inrush Current

All products versions

This capacitor impacts the USB Inrush Current. Maximum

application capacitance allowed by the USB standard is 10 µF.

C9 Power Supply filter capacitor 100 nF +80/-20C All product versions

C10 Reset capa citor 10 µF +/-10% Option al capacitor for all produ c t versio ns

L1 DC/DC converter input inductance

Q1 Crystal

10 µH +/- 1 0%

Min rated current : 200 mA

Min rated freq. : 4 MHz

8.0000 Mhz +/- 2500 ppm

max

ESR max : 100 Ω

All product versions.

Qualified component : Murata LQH32CN100K21L

If DC/DC converter is not used at 5V, this inductance is optional.

All product versions

4202E–SCR–06/06

17

Page 18

AT8xC5122/23

USB Keyboard with Smart Card Reader Using the AT8xC5122 and AT89C5122DS Versions

VCC

C9

GND

VCC

EA/VCC (1)

10mA Max

GND

R1

R2

R3

R19

R18

R17

R16

R15

D+

D-

VCC

GND

R14

R13

R12

R11

R10

R09

R08

USB

VBUS

GND

R07

R06

R05

R04

R03

R02

R01

R00

C4

C0

C1

C2

C3

C4

C5

C6

C7

DVCC

VREF

D+

D-

KB0

KB1

KB2

KB3

KB4

KB5

KB6

KB7

P3[0-1,3-4]

P2[0-7]

P0[0-7]

GND

VCC AVCC

C8

VCC

CPRES

CRST1

CCLK1

GND

LEDx

CVCC

CVSS

CRST

CCLK

CC4

CIO

CC8

CIO1

C1

VCC

C7

R5

VCC

VCC

Smart Card

C1

VCC

C5

GND

C2

RST

C3

CLK

C4

C4

C7

I/O

C8

C8

S1

S1

S2

GND

L1

LI

C6

GND

Alternate Card

C1

VCC

C2

RST

C3

CLK

C7

I/O

C5

GND

GND

Keyboard Matrix

Notes :

1 - Pin configuration depends on product versions

18

R4

C3

GND

C2

PLLF

AVSS

VSS

GND

XTAL2XTAL1

Q1

RST

C10

Optional

Capacitor

GND

4202E–SCR–06/06

Page 19

USB Smart Card Reader Using the AT83C5123 Version

AT8xC5122/23

USB

VBUS

D+

GND

D-

VCC

GND

VCC

10mA Max

GND

R1

R2

R3

C4

C9

VCC

GND

EA

DVCC

VREF

D+

D-

GND

VCC AVCC

C8

VCC

CVCC

CPRES

GND

LEDx

CVSS

CRST

CCLK

CC4

CIO

CC8

C1

VCC

VCC

L1

LI

C6

GND

C7

R5

Smart Card

C1

VCC

C5

GND

C2

RST

C3

CLK

C4

C4

C7

I/O

C8

C8

S1

S1

S2

GND

R4

C3

GND

C2

PLLF

AVSS

VSS

GND

CRST1

CCLK1

CIO1

RST

XTAL2XTAL1

Q1

C10

GND

VCC

GND

Optional

Capacitor

Alternate Card

C1

VCC

C2

RST

C3

CLK

C7

I/O

C5

GND

4202E–SCR–06/06

19

Page 20

AT8xC5122/23

Memory Or ga nization The AT8xC5122/23 devices have separated address spaces for Program and Data

Memory, as shown in Figure 13 on page 29, Figure 14 on page 31 and Figure 15 on

page 32. The logical separation of Program and Data memory allows the Data Memory

to be accessed by 8-bi t addresses , which can be more quic kly stored and m anipulate d

by an-bit CPU. Nevertheless, 16-bit Data Memory addresses can also be generated

through the DPTR register.

Program Memory Managament

Depending on the state of EA pin, the MCU fetches the code from internal or external

progr am memory (R OMless mod e )

Warning : the EA pin c an not be lef t flo ating , oth er wise M CU m ay have an unpr ed ictable behaviour.

If EA is strapped to VCC, the MCU fetches the code from the internal program memo ry.

The wa y th e MC U works in this mod e depe nds o n the d evic e ve rsi on. S ee next pa ragraphs for further details.

If the EA is strapped to GND, the MCU fetches the code from external program memory.

This mode is common for all device versions wich supports it. After reset, the CPU

begins the execution from location 0000h. There can be up to 64 KBytes of program

memory. In this mode, the internal program memories are disabled.

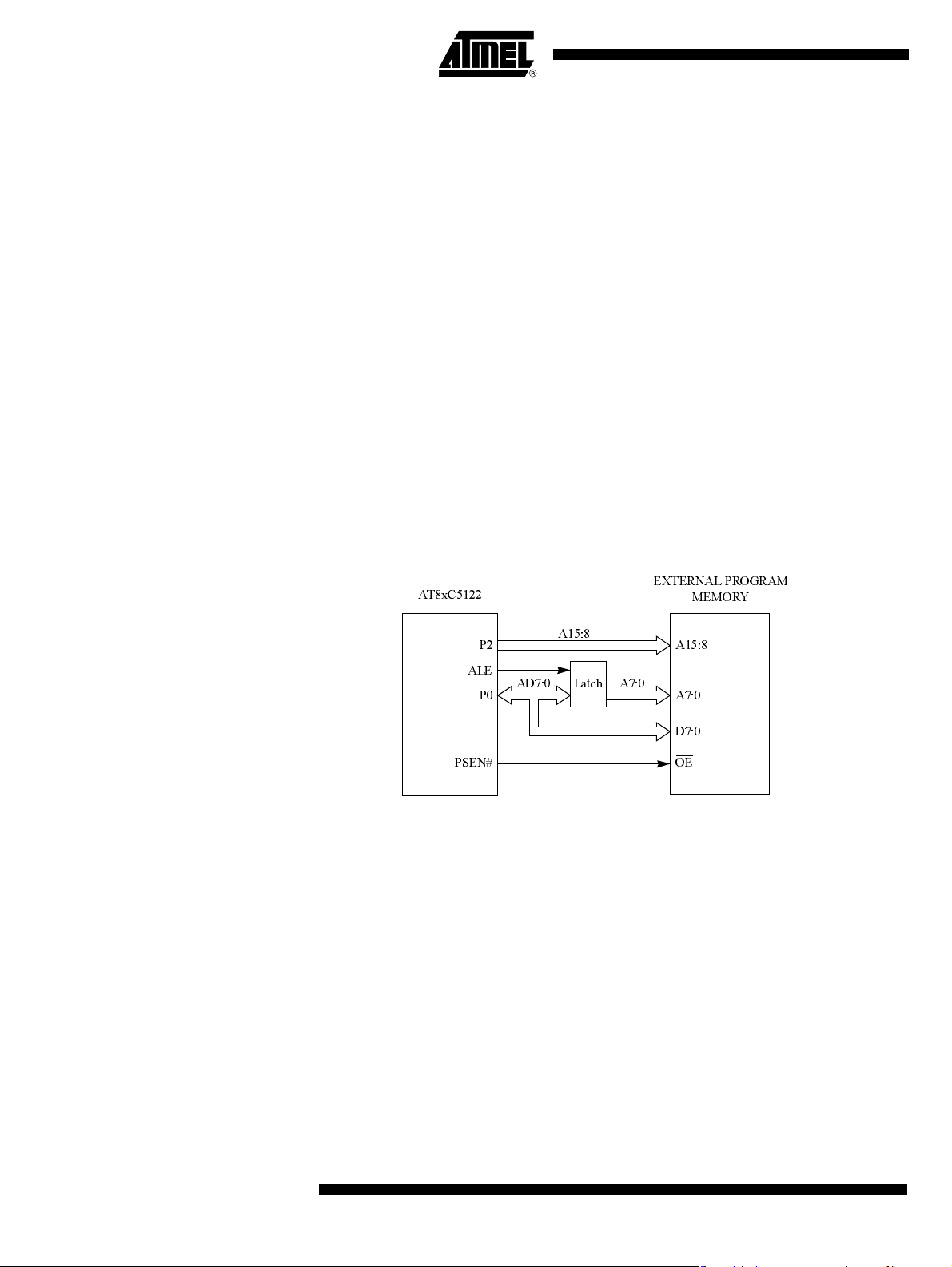

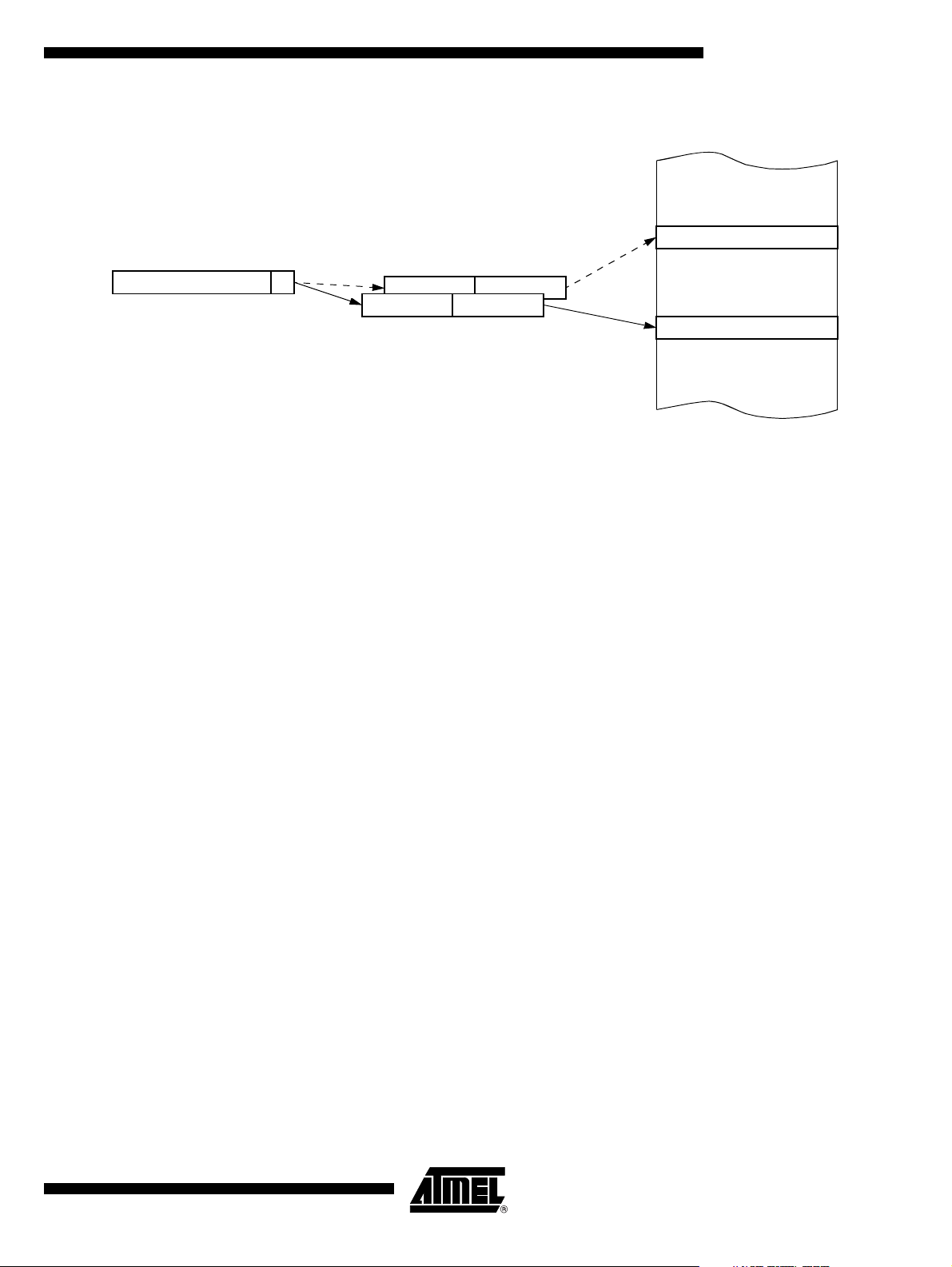

The hardware configuration for external program execution is shown in Figure 9.

Figure 9. Executing from External Program Memory

AT8xC5122

ALE

P2

P0

AD7:0

A15:8

Latch

EXTERNAL PROGRAM

MEMORY

A15:8

A7:0

A7:0

20

D7:0

OEPSEN#

Note that the 16 I/O line s (Ports 0 and 2) are dedicated to bus func tions during ex ternal

Program Mem ory fetches. P ort 0 serves a s a m ultiplexed a ddre ss/dat bus. It em its the

low byte of the Program Counter (PC L) as an add ress, and then go es into a floa t state

awaiting the arrival of the code byte from the Program Mem ory . During the time that the

low byte of the Program Counter is valid on P0, the signal ALE (Address Latch Enable)

clocks the byte into an address latch. Meanwhile, Port 2 emits the high byte of the Program Counter (PCH). Then PSEN strobes the External Program M emory and the code

byte is read into the MCU.

PSEN is not activated and Ports P0 and P2 are not affected during internal program

fetches.

4202E–SCR–06/06

Page 21

AT8xC5122/23

Data Memory Managament

RAM Achitecture The internal RAM is mapped into three separate segments :

All device versions implements :

- 256 Bytes of RAM to increase data parameter handling and high level language usage

- 512 bytes of XRAM (Extended RAM) to store program data.

• The Lower 128 bytes (addresses 00h to 7Fh) are directly and indirectly

addressable.

• The Upper 128 bytes (addresses 80h to FFh) are indirectly addressable only.

• The Special Function Registers (SFRs) (addresses 80h to FFh) are directly

addressable only.

The U pper 12 8 bytes and SF R’s ha ve the same address spac e but ar e phys ically

separated.

When an instruction ac cesses an i nternal location ab ove addres s 7Fh, the CPU knows

whether the ac cess is in the upper 128 b ytes of data RA M or to SFR space by the

addressing mode used in the instruction.

• Instructions that use direct addressing access SFR space. For example: MOV

0A0H, # data, accesses the SFR at location 0A0h (which is P2).

• Instructions that use indirect addressing access the Upper 128 bytes of data RAM.

For example: MOV @R0, # data where R0 contains 0A0h, accesses the data byte

at address 0A0h, rather than P2 (whose address is 0A0h).

The stack pointer (SP) may be locat ed anywhere in the 256 bytes RAM (lowe r and

upper RAM) internal data memory. The stack may not be located in the XRAM.

The M0 bit al lows to st retc h the X RA M ti mings . If M 0 is s et, t he re ad an d w rite pu ls es

are extended from 6 to 30 clock periods. This is useful to access externa l slow

peripherals.

XRAM Achitecture Depending on the state of EXTRAM bit in AUXR register (See Table 5 on p age 24), t he

MCU fetches data from internal or external XRAM.

If EXTRAM=0 (reset condition), the MCU fetches the data from internal XRAM. The size

of internal XRAM is configured by the bit XRS0 in AUXR register (See Table 5 on page

24).

Table 4. XRAM Size Configuration

Address

XRS0 XRAM size

0

1 512 bytes 000h 1FFh

The XRAM logically occupie s the first bytes of external data memory. The bit XRS0 can

be used to hide a part of the available XRAM . This can be use ful if external peripherals

are mapped at addresses already used by the internal XRAM.

The XRAM is indirectly addressed, using the MOVX instruction in combination with any

of the registers R0, R1 of the selected bank or DPTR.

256 Bytes

(Reset condition)

Start End

000h 0FFh

4202E–SCR–06/06

For example, MOVX @R0, # data where R0 contains 0A0H, accesses the XRAM at

address 0A0H rather than external memory.

21

Page 22

AT8xC5122/23

An access to e xternal XRAM m emory locations hig her than the accessi ble size o f the

memory (roll-over feature) will be performed with the M OVX DPTR i nstructions, with P 0

and P2 as data/address busses, WR

and RD as respectively write and read signals.

Accesses above XRAM size can only be done by the use of DPTR.

If EXTRAM=1 the MCU fetches the data from external XRAM Memory. There can be up

to 64 KBytes of external XRAM Memory.

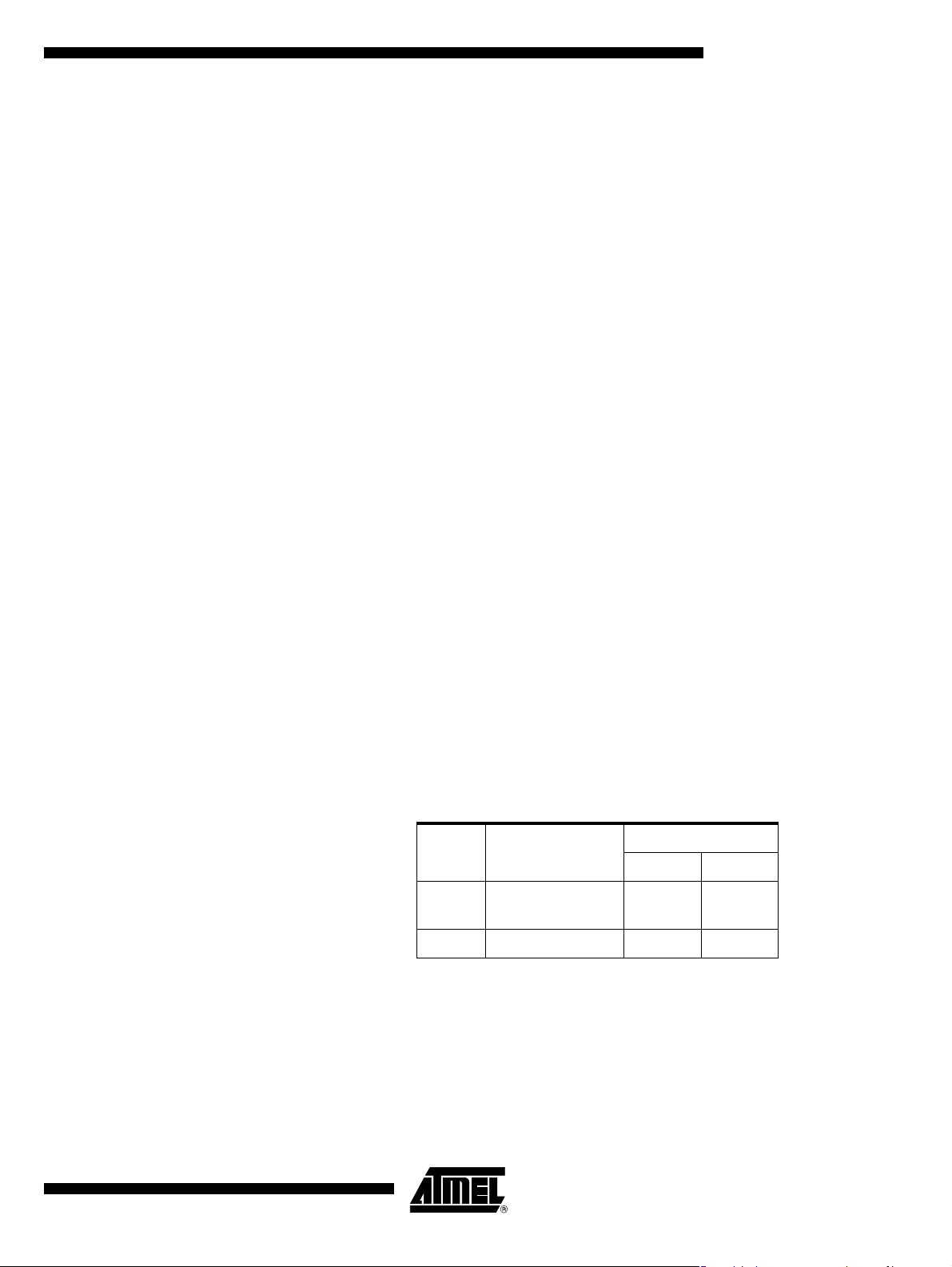

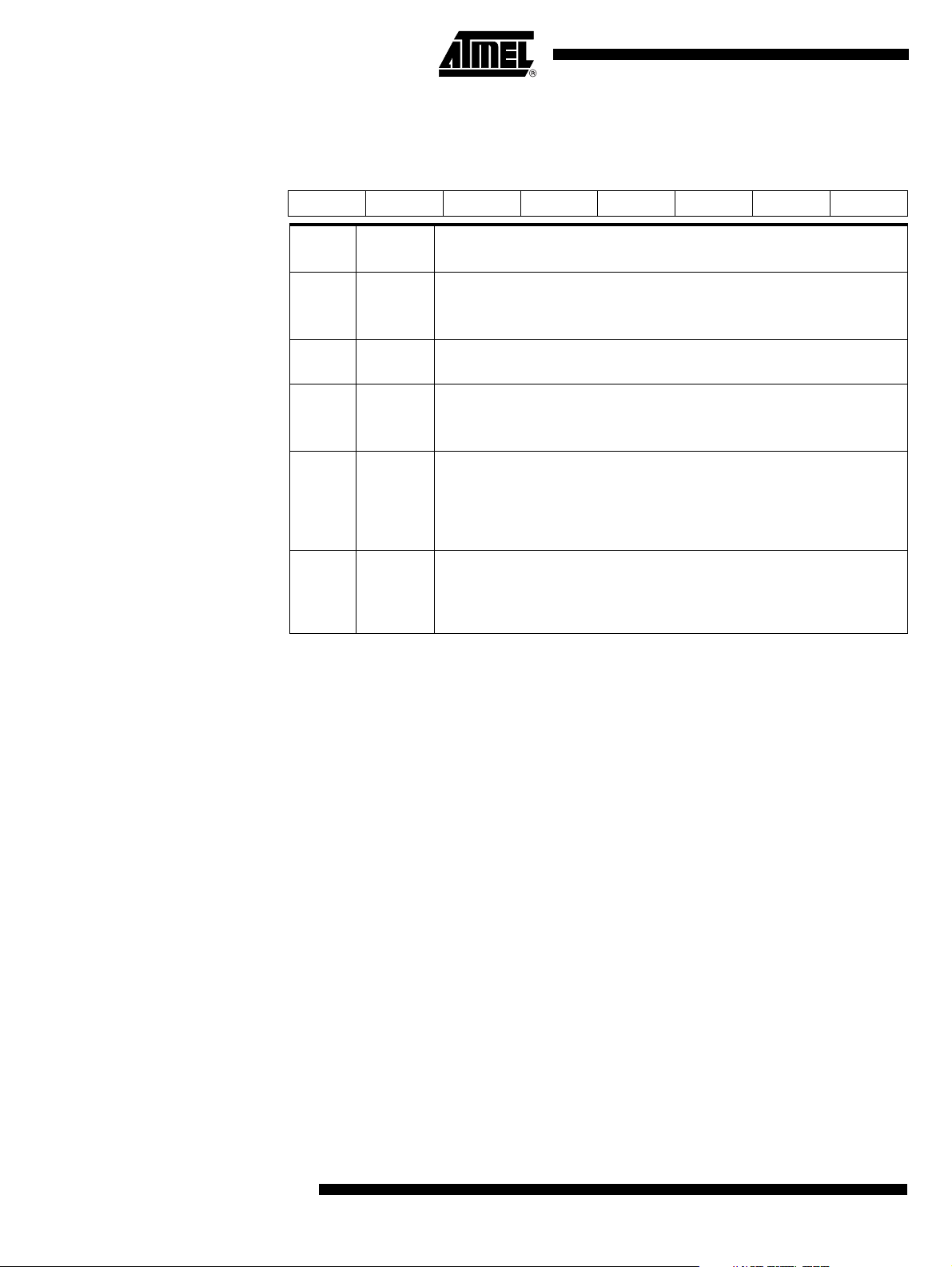

The hardware configuration for external Data Memory Access is shown in Figure 10

Figure 10. Accessing to External XRAM Memory

AT8xC5122/23

EXTER NAL XRAM

MEMORY

AD7:0

A15:8

Latch

A7:0

A15:8

A7:0

D7:0

OERD#

WR

P2

ALE

P0

WR#

MOVX @Ri an d M OVX @DPT R wil l be similar to the standard 80C51. MOVX @ Ri will

provide an eight-bit address multiplexed with data on Port 0 and any output port pins

can be use d to ou tput hi gher ord er addre ss bi ts. Thi s is to p rovide t he ext ernal pagin g

capability. MO VX @DP TR will generate a sixteen -bit addre ss. Po rt 2 outputs the highorder eight address bits (DPH) while Port0 m ultiplexes the low -order eight address bits

(DPL) with data. MOVX @ Ri a nd M OVX @DPTR will generate either read or write signals on W

R and RD.

Ports P0, P2 are not affected and RD, WR signals are not activated during access to

internal XR AM.

Note that external XRAM Memory access is only available on High Pin Count Packages.

External Program Memory and ext ernal XRAM Memory may be combined if desired by

applying the RD and PSEN sig nals t o the in puts o f a n AND gat e and using the ouput of

the gate as the read strobe to the external program/data memory.

Dual Data Pointer Register (DDPTR)

22

RD

STROBE

PSEN

The addi tion al da ta poin ter ca n be u sed t o spe ed up code exe cuti on and reduc e cod e

size.

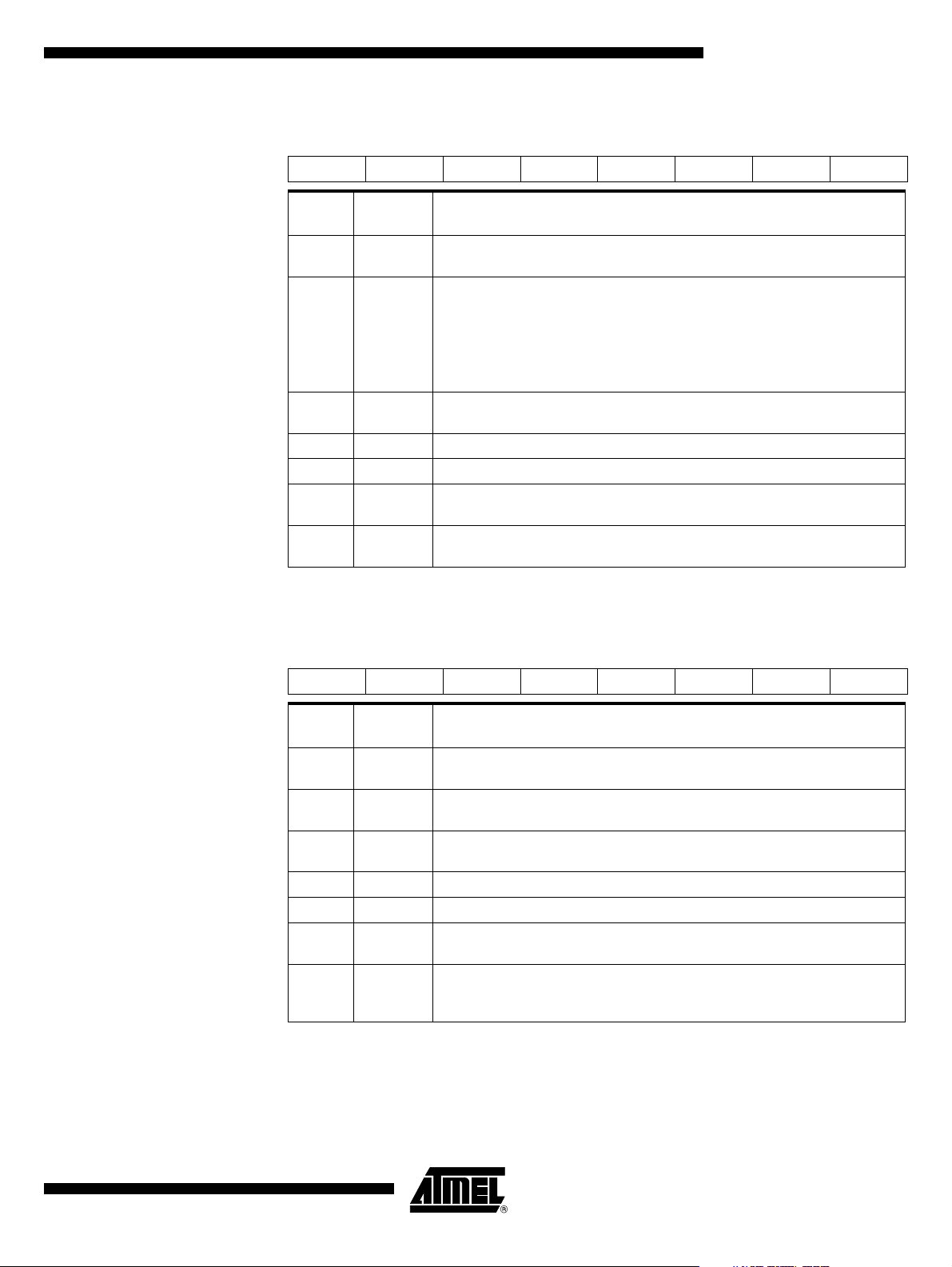

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external

memory, and a single bit called DPS = AUXR1.0 (see Table 7) that allow the program

code to switch between them (Figure 11).

4202E–SCR–06/06

Page 23

Figure 11. Use of Dual Pointer

AUXR1(A2H)

Assembly Language

AT8xC5122/23

External Data Memory

07

DPS

DPH(83H) DPL(82H)

a. Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

; Block move using dual data pointers

; Modifies DPTR0, DPTR1, A and PSW

; note: DPS exits opposite of entry state

; unless an extra INC AUXR1 is added

;

00A2 AUXR1 QU 0A2H

;

0000 909000MOV DPTR,#SOURCE ; address of SOURCE

0003 05A2 INC AUXR1 ; switch data pointers

0005 90A000 MOV DPTR,#DEST ; address of DEST

0008 LOOP:

0008 05A2 INC AUXR1 ; switch data pointers

000A E0 MOVX A,@DPTR ; get a byte from SOURCE

000B A3 INC DPTR ;increment SOURCE address

000C 05A2 INC AUXR1 ; switch data pointers

000E F0 MOVX @DPTR,A ; write the byte to DEST

000F A3 INC DPTR ; increment DEST address

0010 70F6JNZ LOOP ; check for 0 terminator

0012 05A2 INC AUXR1 ; (optional) restore DPS

DPTR1

DPTR0

4202E–SCR–06/06

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1

SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggl es it. In simple rou tines, such as the block move example,

only the fact that DPS is toggled in the proper sequence matters, not its actual value.

For example, the block move routine works the sam e whether DPS is '0' or '1 ' on ent ry.

Observe that witho ut the last ins truction (INC AUXR1), th e routine will exit with DP S in

the opposite state.

23

Page 24

AT8xC5122/23

Registers

Table 5. Auxiliary Register - AUXR (8Eh)

76543210

DPU - - - XRS0 EXTRAM AO

Bit

Number

7DPU

6-3 -

2XRS0

1 EXTRAM

0AO

Bit

Mnemonic Description

Disable weak Pull-up

0 weak pull-up is enabled

1 weak pull-up is disabl ed

Reserved

The value read from this bit is indeterminate. Do not change these bits.

XRAM Size

0 256 bytes (default)

1 512 bytes

EXTRAM bit

Cleared to access internal XRAM using MOVX @ Ri/ @ DPTR.

Set to access external memory.

Programmed by hardware after Power-up regarding Hardware Security Byte

(HSB), default setting , XRAM selected.

ALE Output bit

Cleared , ALE is emitted at a constant rate of 1/6 the o s cillator frequency (or 1/3 if

X2 mode is used)( default).

Set , ALE is active only when a MOVX or MOVC instruction is used.

Reset Value = 0XXX X000b

24

4202E–SCR–06/06

Page 25

AT8xC5122/23

Table 6. Auxiliary Register 1 AUXR1- (0A2h) for AT8xC5122

7 6 5 4 3 2 1 0

--ENBOOT-GF30-DPS

Bit

Number

7 - 6 -

5 ENBOOT

4-

3 GF3 This bit is a general-purpose user flag.

2 0 Always cleared .

1-

0DPS

Bit

Mnemonic Description

Reserved

The valu e re a d from this bit is ind et er m in at e. Do not chang e th es e bits .

Enable Boot ROM (CRAM / E2PROM version only)

Set this bit to map the Boot ROM from 8000h to FFFFh. If the PC increments

beyond 7FFFh address, the code is fetch from int ernal ROM

Clear this bit to disable Bo ot ROM. If the PC increments beyond 7FFF h address,

the code is fetch from external code memory (C51 standard roll over function)

This bit is forced to 1 at reset

Reserved

The value rea d fro m thi s bit is ind et erm in at e. Do no t chang e th is bit.

Reserved

The value rea d fro m thi s bit is ind et erm in at e. Do no t chang e th is bit.

Data Pointer Selection

Cleared to select DPTR0. Set to select DPTR1.

Reset Value = XX1X XX0X0b (Not bit addressable)

Table 7. Auxiliary Register 1 AUXR1- (0A2h) for AT83C5123

7 6 5 4 3 2 1 0

----GF30-DPS

Bit

Number

7 - 6 -

5

4-

3 GF3 This bit is a general-purpose user flag.

2 0 Always cleared .

1-

0DPS

Bit

Mnemonic Description

Reserved

The valu e re a d from this bit is ind et er m in at e. Do not chang e th es e bits .

Reserved

The valu e re a d from this bit is ind et er m in at e. Do not chang e th es e bits .

Reserved

The value rea d fro m thi s bit is ind et erm in at e. Do no t chang e th is bit.

Reserved

The value rea d fro m thi s bit is ind et erm in at e. Do no t chang e th is bit.

Data Pointer Selection

Cleared to select DPTR0.

Set to select DPTR1.

Reset Value = XXXX XX0X0b (Not bit addressable)

4202E–SCR–06/06

25

Page 26

AT8xC5122/23

Table 8. CRAM Configuration Register - RCON (D1h)

76543210

----RPS---

Bit

Number

7 - 4 -

3RPS

2-0 -

Bit

Mnemonic Description

Reset Value = XXXX 0XXXb

AT8xC5122’s CRAM and E2PROM Versions

The AT8xC5122’s CRAM and E2PROM versions implements :

- 32 KB of ROM mapped from 8000 to FFFF in which is embed ded a bootlo ader for In-

System Programming feature

- 32 KB of CRAM (Code RAM) , a volatile program memory mapped from 0000 to 7FFF

In CRAM versions only :

- 512 bytes of E2PROM can be optionally implemented to store permane nt data

Reserved

The value read from this bit is indeterminate. Do not change these bits.

CRAM Memory Mapping Bit

Set to map the CRAM memory during MOVX instructions

Clear to map the XRAM memory during MOVX .

This bit has priority over th e EXTRAM bit.

Reserved

The value read from this bit is indeterminate. Do not change these bits.

In E2PR OM ver sion :

- 32KB of E2PROM are implemented to store permanent code

Warnings :

– so me bytes of user program memory space are reserved for bootloader

configuration. Depending on the configuration, up to 256 bytes of code may

be not available for the user code from 7F00h location. Refer to bootloader

datasheet for further details.

– Port P3.7 may be used by the bootloader as a hardware condition at reset to

select the In-System Programming mode. Once the bootloader has started,

the P3.7 Port is no more used.

26

4202E–SCR–06/06

Page 27

AT8xC5122 Microcontroller

FFFFh

Bootloader

AT8xC5122/23

P3.7

7FFFh

7F00h

7EFFh

0000h

When pin EA =1 and after the reset, the MCU begins the execution of the embedded

bootloade r from loca tion F8 00h of the ROM. T he b ootload er implem ent s an In-Sys tem

Programming (ISP) mode which manages the transfer of the code in the volatile Program Memory (CR A M) .

For CRAM ve rsion, th e code is sup plied b y the ATME L’s FL exible In-system Pro gramming software (FLIP) through USB or UART interface

For E2PROM vers ion, t he code is supplied from the internal cod e E2P ROM or by F LI P.

The s tate of pi n P 3.7 at re set de term ines the code so urc e. I f P3 .7=1 (re set cond ition )

the source is the internal E2PROM and the transfer takes about 1.5 seconds. If P3.7=0

the source is FLIP and the transfer time depends mainly on external conditions not

related to bootloader.

Reserved

User code

4202E–SCR–06/06

Once the code is running in CRAM, the roll-over condition (code fetched beyond

address 7FFFh) depends on the state of ENBOOT bit of AUXR1 register (Table 6 on

page 25).

If ENBOOT=1 (reset condition) the MCU fetche s the code from bootloader ROM. If

ENBOOT=0, the MCU fetches the code from the external Program Memory. In this last

case, PSEN is activated and Ports P0 and P2 are used to emit data and address

signals.

Warning : external Program Memory access is not allowed on Low Pin Count

Packages.

27

Page 28

AT8xC5122/23

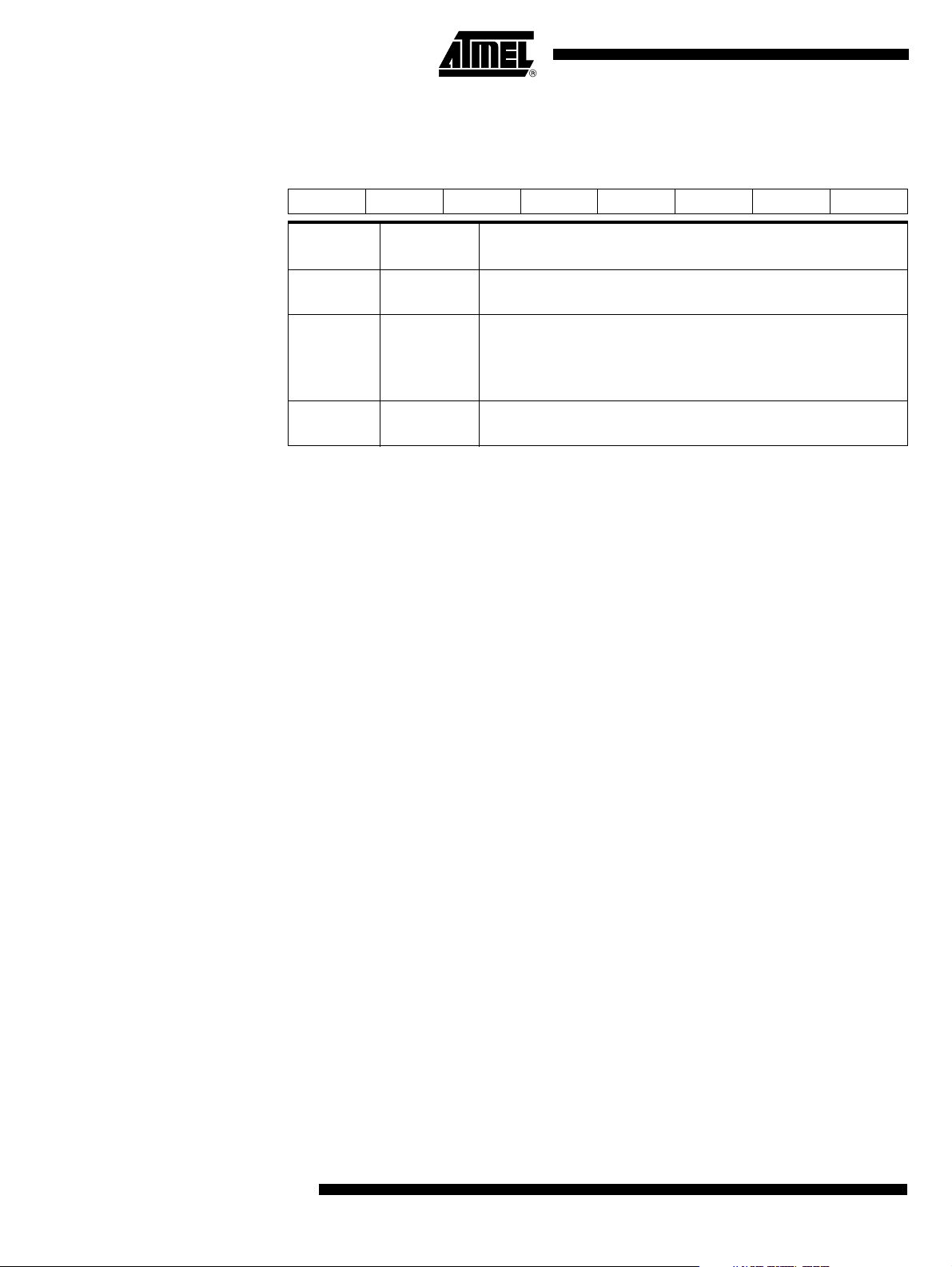

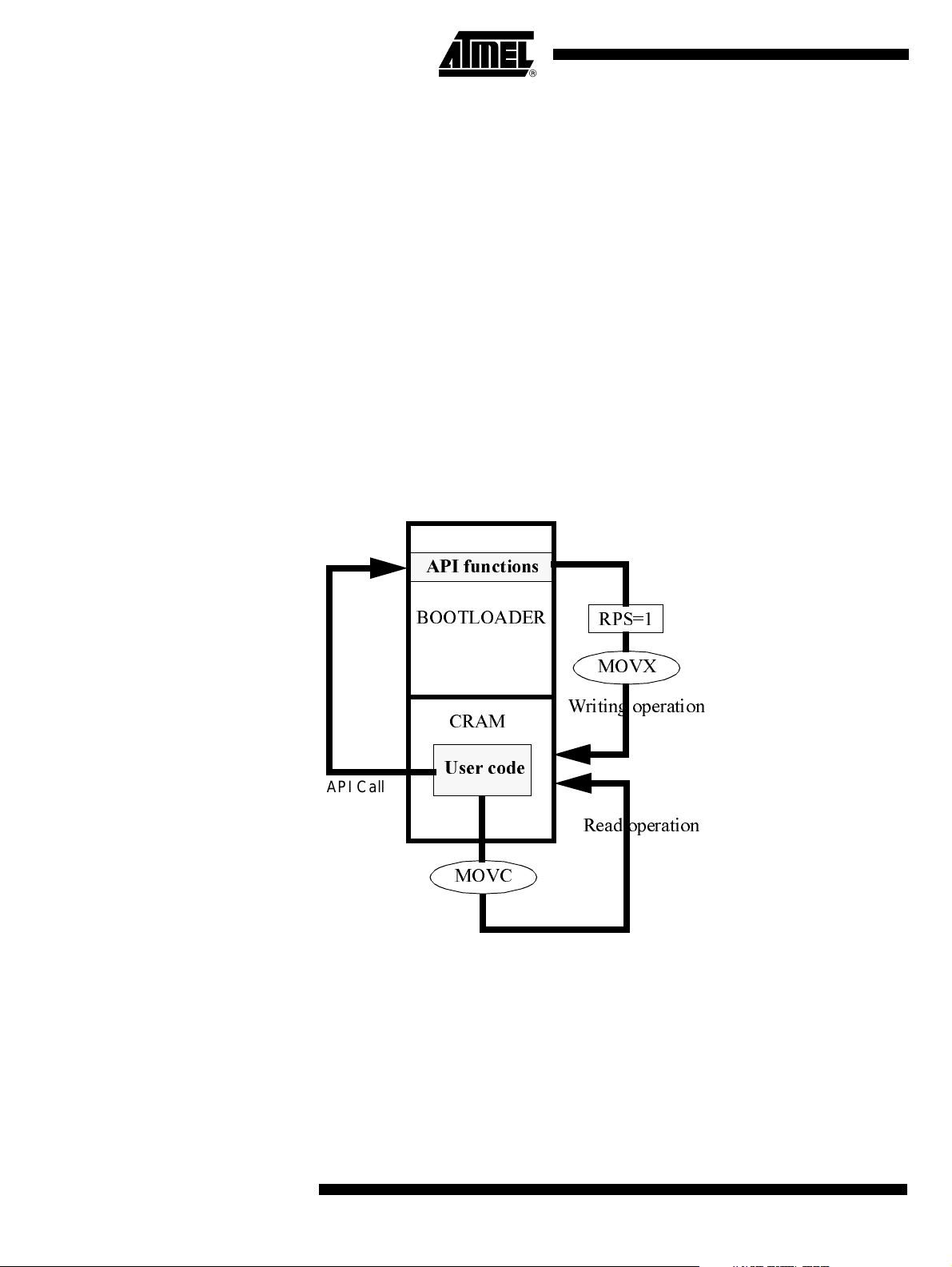

Using CRAM Memory The CRAM is a read / write volatile memory that is mapped in the program memory

space. Then wh en the p ower is sw itched off t he code is l ost and ne eds to be reload at

each power up. In return, the CRAM enabl es a lot of f lexibility in the code dev elopment

as it can be programm ed indefinite ly. The user code runnin g in the CRAM c an perform

read operations in CRAM itself by means of MOVC instructions like any C51 m icrocontroller does. Although the writing operations in CRAM are usually handled by the

bootloader, it is possible for the user code to handle its own writing operations in CRAM

as well. The user co de must c all API functi ons prov ide d by th e bootlo ade r in the R OM

memory. Refer to bootloader datasheet for further details about the use of these API

functions. These API functions use a mechanism provided by the AT8xC5122 microcontroller. When the bit RPS is set in RCON register (Tabl e 8 on page 26), the MOVX

intructions are configured to write in CRAM instead of XRAM m em ory. Ho wever, due t o

C51 architecture, it is not possible for the user c ode to write directly in CRAM when it is

itself running in CRAM. This is why the API functions must be called in order to have the

code executing in ROM while the CRAM is written.

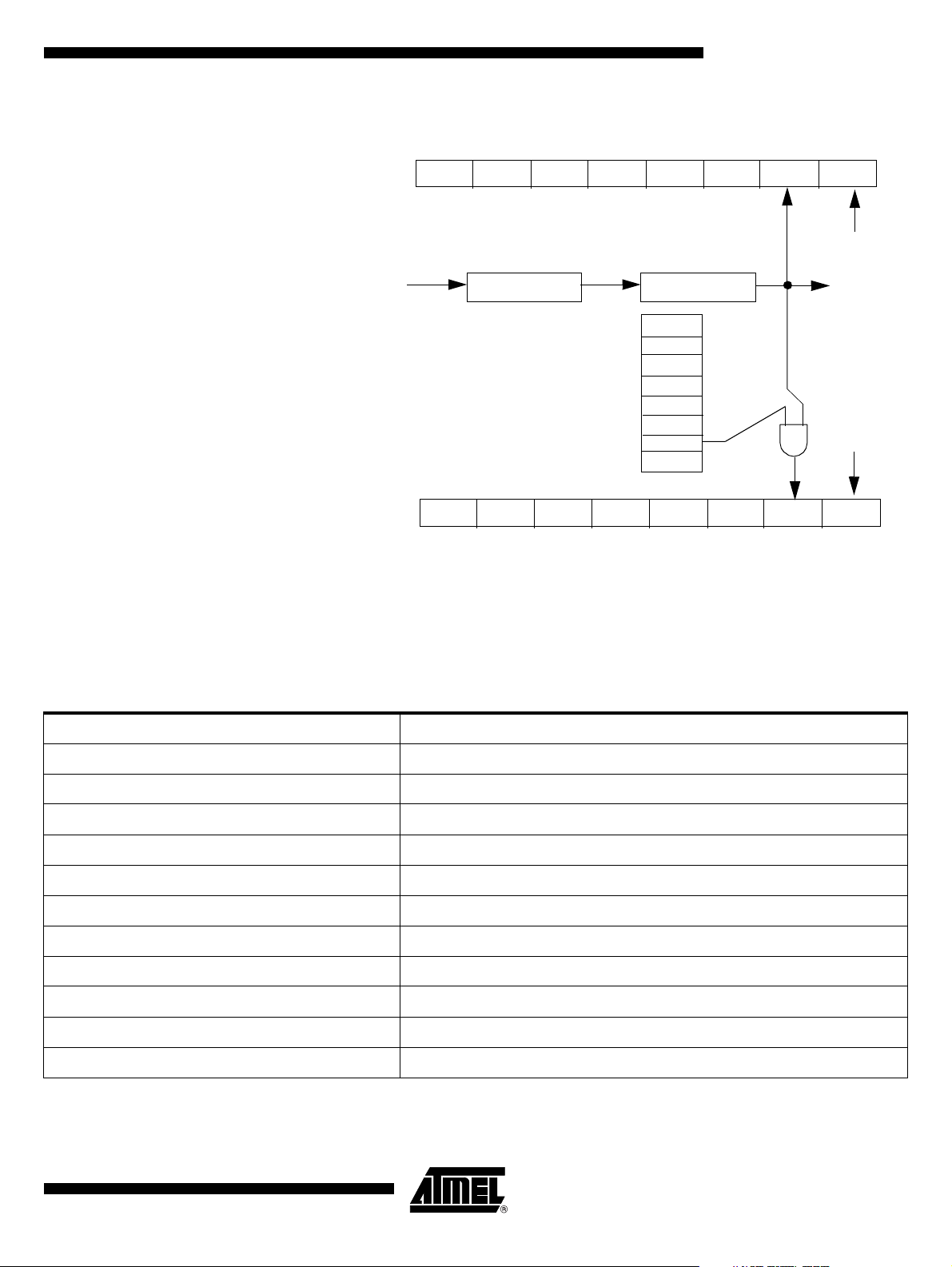

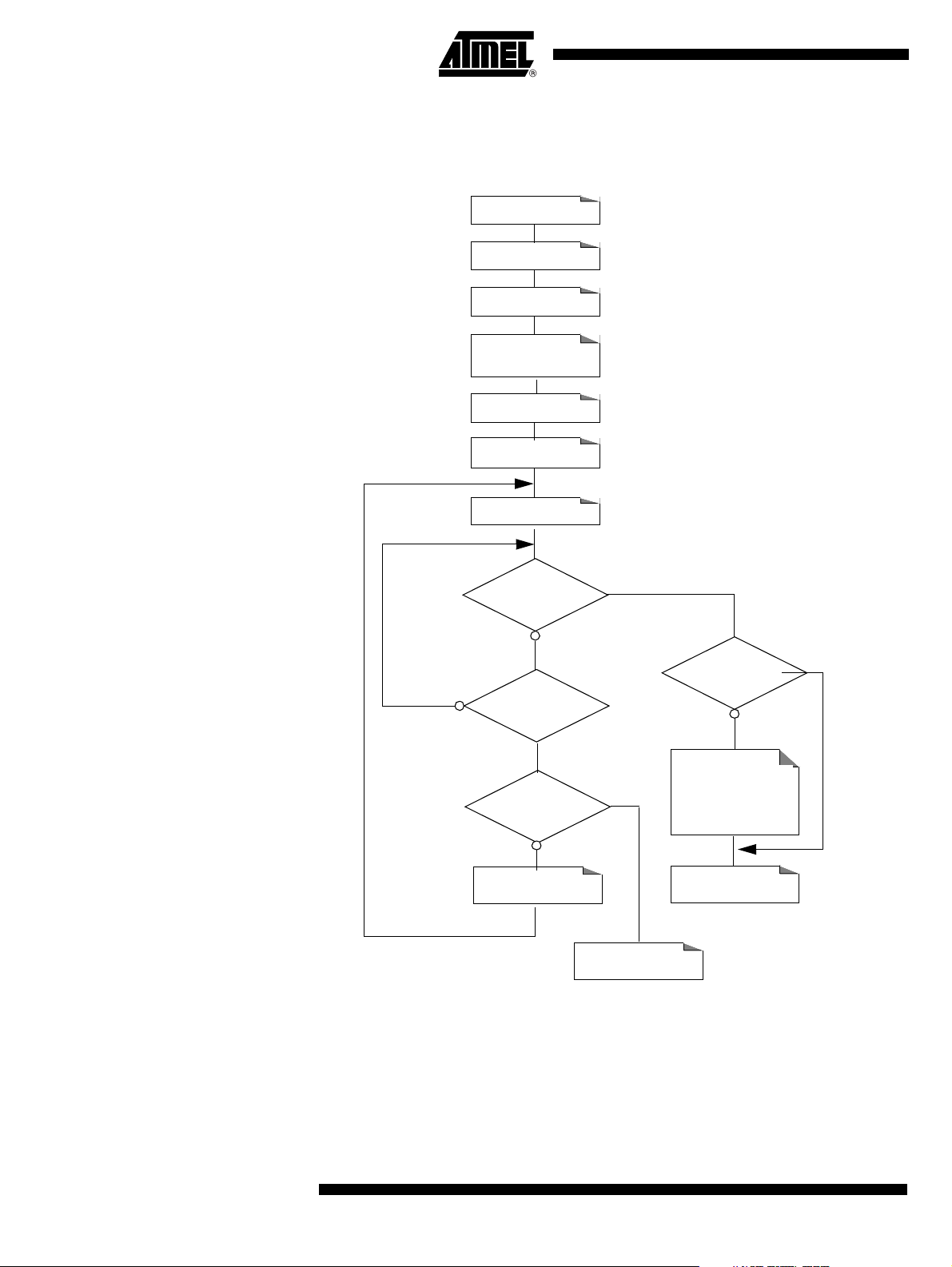

Figure 12. Read / Write Mechanisms in CRAM Memory

API Call

API functions

BOOTLOADER

CRAM

User code

MOVC

RPS=1

MOVX

Writing operation

Read operation

28

4202E–SCR–06/06

Page 29

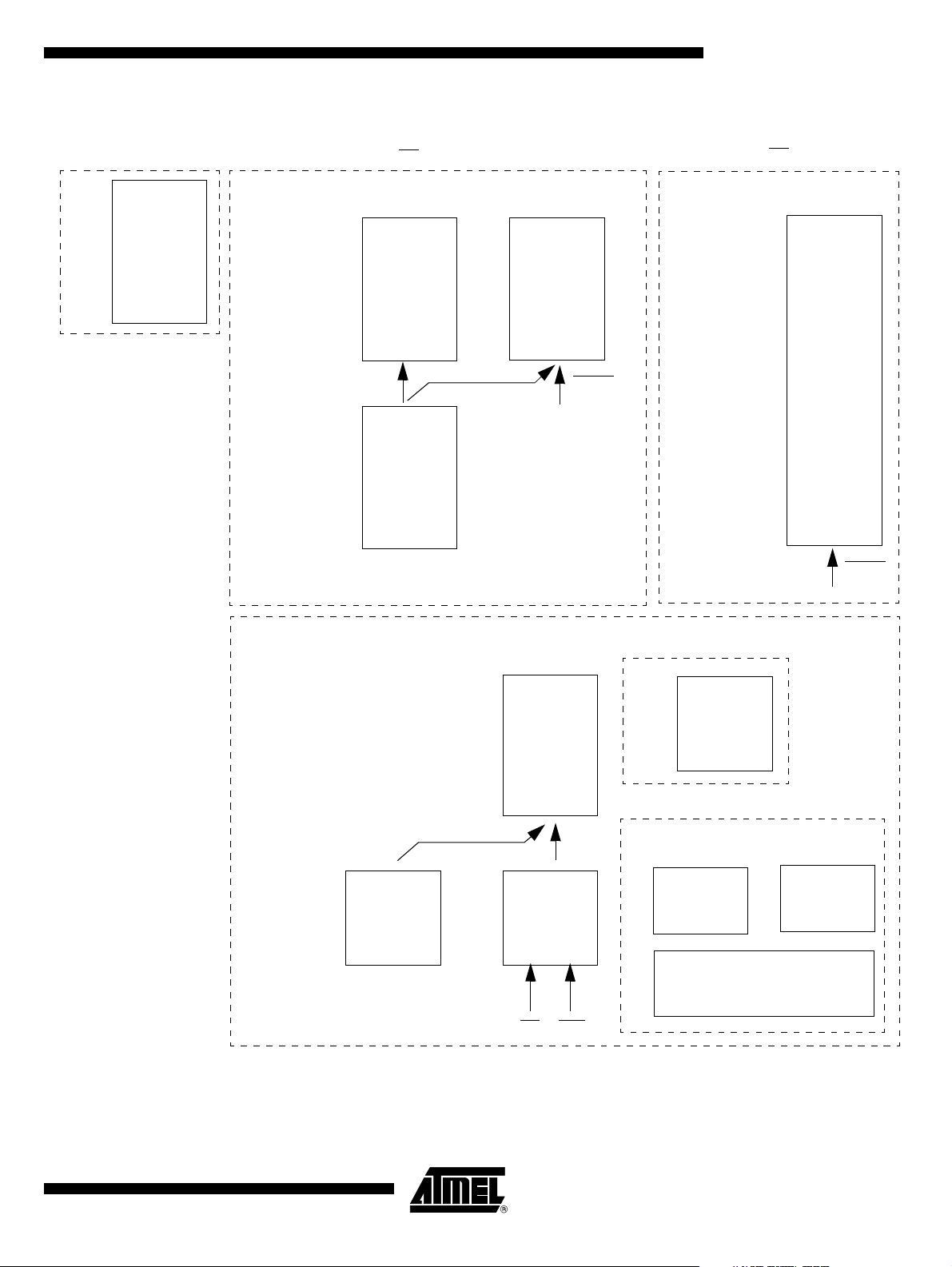

Figure 13. AT8xC5122’s CRAM and E2PROM Versions

AT8xC5122/23

(E2PROM version)

FFFF

32K

INTERNAL

E2PROM

(Read/Write)

8000

PROGRAM

MEMORY

Reset@

FFFF

<F800>

8000

Roll-Over

7FFF

0000

EA = 1

ENBOOT=1

32K

INTERNAL

ROM

(Read Only)

32K

INTERNAL

CRAM

(Read/Write)

FFFF

8000

ENBOOT=0

32K

EXTERNAL

PROGRAM

MEMORY

PSEN

Reset@

EA = 0

EXTERNAL

PROGRAM

MEMORY

<0000>

PSEN

DATA MEMORY

(Read / Write)

01FF

0000

EXTRAM=0

Roll-Over

On-chip

512 bytes

XRAM

FFFF

0200

01FF

0000

EXTRAM=1

EXTERNAL

XRAM

EXTERNAL

XRAM

RD WR

Optional

(applicable only to CRAM version)

01FF

512 Bytes

INTERNAL

E2PROM

0000

On-Chip 256 bytes RAM

Indirect

Addressing

FF

128 Bytes

80

7F

00

Upper

RAM

128 Bytes

Direct

Addressing

FF

SFR

Space

80

Lower

RAM

4202E–SCR–06/06

29

Page 30

AT8xC5122/23

AT8xC5122’s ROM Version

Security Level There are two security levels (applicable to High Pin Count packages only) :

The AT8xC5122’s ROM version implements :

- 32 K of ROM mappe d fro m 0 000h to 7FFFh in which is em bedded the user code. The

ROM device is only factory programmable.

- 512 byte s of E 2P ROM can be op tiona lly imp lem ente d to s tore pe rman en t data. Wi th

this option, the size of ROM is reduced to 30K.

After the rese t, th e MCU b egins t he exe cutio n of the user code fr om lo cation 00 00 h of

the ROM.

Access to external Program Memory is not allowed.

Table 9. Security Level s Des cri ption

Securi ty Level Prote ction description

1 No protection lock enabl ed

MOVC instruction executed from external Program Memory is disabled when fe tching

2

code bytes from internal Program Memory

EA

is sampled and latched on r eset.

External code execution is enabled.

The security level 2 can be used to protect the user code from piracy. This option is configured at factory and must be requested by the customer at order time.

30

4202E–SCR–06/06

Page 31

Figure 14. AT8xC5122’s ROM Version

AT8xC5122/23

PROGRAM MEMORY

(Read only)

7FFF

0000

EA=1

Roll-Over

INTERNAL

32K ROM

EXTRAM=0

FFFF

8000

RESET@

<0000>

EA=0

EXTERNAL

EXTERNAL

PSEN

EXTRAM=1

Optional

DATA MEMORY

(Read / Write)

01FF

0000

On-chip

512 bytes

XRAM

FFFF

0200

Roll-Over

01FF

0000

EXTERNAL

XRAM

EXTERNAL

XRAM

RD WR

01FF

512 Bytes

INTERNAL

E2PROM

0000

On-Chip 256 bytes RAM

Indirect

Addressing

FF

80

7F

00

Upper

128 Bytes

RAM

FF

80

Lower

128 Bytes

RAM

Direct

Addressing

SFR

Space

4202E–SCR–06/06

31

Page 32

AT8xC5122/23

AT83C5123 Version The AT83C5123 device is a low pin count version of the AT8xC5122.

The ROM version implements :

- 30 KB of ROM mapp ed from 0000 t o 77 FF in w hich is em bedded the user co de. Th e

ROM device is only factory programmable.

- 512 bytes of E2PROM can be optionally implemented to store permane nt data

Figure 15. AT83C5123’s Device

7FFF

PROGRAM MEMORY

(Read only)

DATA MEMORY

(Read / Write)

RESET@

<0000>

OPTIONAL

01FF

0000

01FF

0000

INTERNAL

30K ROM

512 Bytes

INTERNAL

E2PROM

On-chip

512 bytes

XRAM

On-Chip 256 bytes RAM

Indirect

Addressing

FF

80

7F

00

Upper

128 Bytes

RAM

FF

80

Lower

128 Bytes

RAM

Direct

Addressing

SFR

Space

32

4202E–SCR–06/06

Page 33

AT8xC5122/23

Special Function Register s (S FR ’s)

Introduction The Special Function Registers (SFRs) of the AT8xC5122/23 can be ranked into the fol-

lowing categories:

• C51 Core Registers: ACC, B, DPH, DPL, PSW, SP

• System Configuration Registers: PCON, CKRL, CKCON0, CKCON1, CKSEL,

PLLCON, PLLDI V, AUXR, AUXR1, RCON

• I/O Port Registers: P0, P1, P2, P3, P4, P5, PMOD1, PMOD2

• Timer Registers: TCON, TH0, TH1, TMOD, TL0, TL1

• Watchdog (WD) Registers: WDTRST, WDTPRG

• Serial I/O Port Registers: SADDR, SADEN, SBUF, SCON

• Baud Rate Generator (BRG) Registers: BRL, BDRCON

• System Interrupt Registers: IE0, IPL0, IPH0, IE1, IPL1, IPH1

• Smart Card Interface (SCI) Registers: SCSR, SCCON/SCETU0, SCI SR/SCETU1,

SCIER/SCIIR, SCIBUF, SCGT0/SC WT0 , SCGT1/SCWT1, SCICR/SC WT2 , SCIC L K

• DC/DC Converter Registers: DCCKPS

• Keyboard Interface Registers: KBE, KBF, KBLS

• Seri a l Port Int erface (SPI) Reg i s ters: SP C ON, SPS TA, SPDAT

• Universal Serial Bus (USB) Registers:USBCON, USBADDR, USBINT, USBIEN,

UEPNUM, UEPCONX, U EPSTAX, UEPRST, UEPINT, UEPIEN, UEPD ATX,

UBYCTX, UFNUML, UFNUMH

• LED Controller Registers: LEDCON0, LEDCON1

4202E–SCR–06/06

33

Page 34

AT8xC5122/23

AT8xC5122 V er sio n

Bit

addressable Not bit addressable

0/8 1 /9 2/A 3/B 4/ C 5/D 6/E 7/F

F8h

F0h

E8h

E0h

UEPINT

0000 0000

B

0000 0000

P5

1111 1111

ACC

0000 0000

LEDCON0

0000 0000

LEDCON1

XX00 0000

UBYCTX

0000 0000

D8h

D0h

PSW

0000 0000

C8h

1

S

C

C0h

R

S

0

B8h

1

S

C

B0h

R

0

S

1

S

C

A8h

R

S

0

P4

1111 1111

IPL0

X000 000

P3

1111 1111

IEN0

0000 0000

RCON

XXXX 0XXX

SCICLK

(1)

0X10 1111

(1)

SCWT3

0000 0000

SADEN

0000 0000

IEN1

XXXX X000

SADDR

0000 0000

UEPIEN

0000 0000

UFNUML

0000 0000

IPL1

00XX 00X0

SCIBUF

XXXX XXXX

SPCON

0001 0100

UFNUMH

0000 0000

IPH1

00XX 00X0

SCSR

X000 1000

UEPCONX

1000 0000

SPSTA

0000 0000

USBCON

0000 0000

SCGT0

0000 1100

SCWT0

1000 0000

SCETU0

0111 0100

SCCON

0000 0000

(1)

(1)

(1)

(1)

UEPRST

0000 0000

SPDAT

1111 1111

USBINT

0000 0000

(1)

SCGT1

XXXX XXX0

(1)

SCWT1

0010 0101

SCETU1

(1)

XXXX X001

(1)

SCISR

10X0 0000

UEPSTAX

0000 0000

USBADDR

1000 0000

USBIEN

0000 0000

(1)

SCICR

0000 0000

SCWT2

0000 0000

(1)

SCIER

0X00 0000

(1)

SCIIR

0X00 0000

UEPDATX

0000 0000

UEPNUM

0000 0000

DCCKPS

0000 0000

IPH0

(1)

X000 0000

A0h

98h

90h

88h

80h

P2

1111 1111

SCON

0000 0000

P1

1111 1111

TCON

0000 0000

P0

1111 1111

34

ISEL

0000 0100

SBUF

XXXX XXXX

(2)

PMOD0

0000 0000

TMOD

0000 0000

SP

0000 0111

Notes: 1. Mapping is done using SCRS bit in SCSR register.

AUXR1

XX1X 0XX0

BRL

0000 0000

TL0

0000 0000

DPL

0000 0000

PLLCON

XXXX X000

BDRCON

XXX0 00 00

TL1

0000 0000

DPH

0000 0000

2. Grey areas : do not write in .

PLLDIV

0000 0000

KBLS

0000 0000

TH0

0000 0000

PMOD1

0000 0000

KBE

0000 0000

TH1

0000 0000

CKSEL

XXXX XXX0

WDTRST

XXXX XXXX

KBF

0000 0000

AUXR

0XXX X000

WDTPRG

XXXX X000

CKRL

XXXX 1111

CKCON0

X0X0 X000

PCON

00X1 0000

4202E–SCR–06/06

Page 35

AT83C5123 V er sio n

Bit

addressable Not bit addressable

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

AT8xC5122/23

F8h

F0h

E8h

E0h

UEPINT

0000 0000

B

0000 0000

P5

XXXX XXX1

ACC

0000 0000

LEDCON0

0000 0000

UBYCTX

0000 0000

D8h

D0h

PSW

0000 0000

C8h

SCWT3

SADEN

IEN1

SADDR

(1)

(1)

UEPIEN

0000 0000

UFNUML

0000 0000

IPL1

X0XX 0XXX

SCIBUF

XXXX XXXX

UFNUMH

0000 0000

IPH1

X0XX 0XXX

SCSR

X000 1000

1

S

C

C0h

R

S

0

B8h

1

S

C

B0h

R

0

S

1

S

C

A8h

R

S

0

P4

11XX XXXX

IPL0

X000 000

P3

1111 1111

IEN0

0000 0000

SCICLK

0X10 1111

0000 0000

0000 0000

X0XX 0XXX

0000 0000

UEPCONX

1000 0000

USBCON

0000 0000

SCGT0

0000 1100

SCWT0

1000 0000

SCETU0

0111 0100

SCCON

0000 0000

(1)

(1)

(1)

(1)

UEPRST

0000 0000

USBINT

0000 0000

(1)

SCGT1

XXXX XXX0

SCWT1

(1)

0010 0101

SCETU1

(1)

XXXX X001

(1)

SCISR

10X0 0000

UEPSTAX

0000 0000

USBADDR

1000 0000

USBIEN

0000 0000

(1)

SCICR

0000 0000

SCWT2

0000 0000

(1)

SCIER

0X00 0000

(1)

SCIIR

0X00 0000

(1)

UEPDATX

0000 0000

UEPNUM

0000 0000

DCCKPS

0000 0000

IPH0

X000 0000

CKCON1

XXXX XXX0

A0h

98h

90h

88h

80h

4202E–SCR–06/06

SCON

0000 0000

P1

1111 1111

TCON

0000 0000

ISEL

0000 0100

SBUF

XXXX XXXX

PMOD0

00XX 0XXX

TMOD

0000 0000

SP

0000 0111

Notes: 1. Mapping is done using SCRS bit in SCSR register.

AUXR1

XXXX 0XX0

BRL

0000 0000

TL0

0000 0000

DPL

0000 0000

PLLCON

XXXX X000

BDRCON

XXX0 0000

TL1

0000 0000

DPH

0000 0000

2. Grey areas : do not write in .

PLLDIV

0000 0000

TH0

0000 0000

PMOD1

XXXX 00XX

TH1

0000 0000

CKSEL

XXXX XXX0

WDTRST

XXXX XXXX

AUXR

0XXX X000

WDTPRG

XXXX X000

CKRL

XXXX 1111

CKCON0

X0X0 X000

PCON

00X1 0000

35

Page 36

AT8xC5122/23

SFR’ s Descr ipt ion

Table 10. C51 Core SFRs

MnemonicAddName 76543210

ACC E0h Accumulator ACC

B F0h B Register B

PSW D0h Program Status Word CY AC F0 RS1 RS0 OV F1 P

SP 81h Stack Pointer SP

DPL 82h

DPH 83h

Data Pointer Low byte (LSB

of DPT R)

Data Pointer High byte

(MSB of DPTR)

DPL

DPH

Ta ble 1 1. Clock SFRs

MnemonicAddName 76 5 43210

PCON 87h Power Controller SMOD1 SMOD0

CKCON0 8Fh Clock Controller 0

WDX2 SIX2 T1X2 T0X2 X2

CKCON1 AFh Clock Controller 1

CKSEL 8 5h Clock Selection

CKRL 97h Clock Reload Register

PLLCON A3h PLL Controller Register

PLLDIV A4h PLL Di vider register R3-0 N3-0

AUXR 8Eh Auxiliary Register 0 DPU

AUXR1 A2h Auxil iary Register 1

RCON

(1)

CRA M me m or y

D1h

Configuration

ENBOOT

POF GF1 GF0 PD IDL

CKREL 3-0

EXT48 PLLEN PLOCK

XRS0 EXTRAM A0

(1)

GF3 DPS

RPS

SPIX2

CKS

Table 12. I/O Port SFRs

Mnemonic Add Name 7 6 5 4 3 2 1 0

(1)

P0

80h Port 0 P0

P1 90h Port 1 P1

(1)

P2

A0h Port 2 P2

P3 B0h Port 3 P3

(1)

P4

C0h Port 4 P4

P5 E8h Por t 5 P5 (only P5.0 for AT8xC5122)

PMOD0 91h Port Mode Register 0 P3C1 P3C0 P2C1

PMOD1 84h Port Mode Register 1 P5HC1

36

Note: 1. Only for AT8xC5122

(1)

P5HC0

(1)

P5MC1

Note: 1. Only for AT8xC5122

(1)

(1)

P2C0

P5MC0

(1)

CPRESRES - P0C1

(1)

P5LC1 P5LC0 P4C1

(1)

(1)

4202E–SCR–06/06

P0C0

P4C0

(1)

(1)

Page 37

AT8xC5122/23

Table 13. Timers SFRs

MnemonicAddName 76543210

TH0 8Ch T imer/Counter 0 High byte TH0

TL0 8Ah Timer/Coun ter 0 Low byt e TL0

TH1 8Dh T imer/Counter 1 High byte TH1

TL1 8Bh Timer/Coun ter 1 Low byt e TL1

TCON 88h

TMOD 89h

Timer/Counter 0 and 1

control

Timer/Counter 0 and 1

Modes

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

GATE1 C/T1# M11 M01 GA TE0 C/T0# M10 M00

Table 14. Watchdog SFRs

MnemonicAddName 76543210

WDTRST A6h Watchdog T imer Reset WDTRST

WDTPRG A7h Watchdog Timer Program

S2-0

Table 15. Serial I/O Ports SFRs

MnemonicAddName 76543210

SCON 98h Serial Control FE/SM0 SM1 SM2 REN TB8 RB8 TI RI

SBUF 99 h Serial Data Bu ffer SBUF

SADEN B9h Slave Address Mask SADEN

SADDR A9h Slave Address SADDR

Table 16. Baud Rate Generator SFRs

MnemonicAddName 76543210

BRL 9Ah Baud Rate Reload BRL

BDRCON 9Bh Baud Rate Control

BRR TBCK RBCK SPD M0SRC

Table 17. Interrupt SFRs

MnemonicAddName 76543210

IEN0 A8h Interrupt Enable Control 0 EA

IEN1 B1h Interrupt Enable Control 1

IPL0 B8h

4202E–SCR–06/06

Interrupt Priority Control

Low 0

EUSB ESCI ESPI

ES ET1 EX1 ET0 EX0

(1)

PSL PT1L PX1L PT0L PX0L

EKB

(1)

37

Page 38

AT8xC5122/23

Table 17. Interrupt SFRs

MnemonicAddName 76543210

IPH0 B7h

IPL1 B2h

IPH1 B3h

ISEL A1h Interrupt Enable Register CPLEV PRESIT RXIT OELEV OEEN PRESEN RXEN

Interrupt Priority Control

High 0

Interrupt Priority Control

Low 1

Interrupt Priority Control

High 1

PSH PT1HPX1HPT0HPX0H

PUSBL PSCIL PSPIL

PUSBH PSCIH PSPIH

(1)

(1)

PKBL

PKBH

(1)

(1)

Note: 1. Only for AT8xC5122

Table 18. SCIB SFRs

MnemonicAddName 76543210

SCGT0 B4h

SCGT1 B5h

SCWT0 B4h

SCWT1 B5h

SCWT2 B6h

Smart Card Transmit Guard

Time Register 0

Smart Card Transmit Guard

Time Register 1

Smart Card Character/ Block

Waiting Time Register 0

Smart Card Character/ Block

Waiting Time Register 1

Smart Card Character/ Block

Waiting Time Register 2

GT7 - 0

GT8

WT7 - 0

WT15-8

WT23-16

SCWT3 C1h

SCICR B6h

SCCON ACh

SCETU0 ACh Smart Card ETU Register 0 ETU7 - 0

SCETU1 ADh Smart Card ETU Register 1 COMP

SCISR ADh

SCIIR AEh

SCIER AEh

SCSR ABh

SCIBUF AAh Smart Card Buffer Register

Smart Card Character/ Block

Waiting Time Register 3

Smart Card Interface Control

Register

Smart Card Interface

Contacts Register

Smart Card UART Interface

Status Register (Read only)

Smart Card UART Interrupt

Identification Register (Read

only)

Smart Card UART Interrupt

Enable Register

Smart Card Selection

Register

RESET CARDDET VCARD1-0 UART WTEN CREP CONV

CLK

SCTBE CARDIN

SCTBI

ESCTBI

BGTEN CREPSEL ALTKPS1-0 SCCLK1 SCRS

Can store a new byte to be transmitted on the I/O pin when SCTBE is set. Bit ordering on the I/O pin

depend s on the convention

Provides the byte receive d from th e I/O pin when SCRI is s et. Bit ordering on the I/O pin depends on

the conv en tion.

CARDC8 CARDC4 CARDIO CARDCLK CARDRST CARDVCC

ICARDOVF VCARDOK SCWTO SCTC SCRC SCPE

ICARDERR VCARDERR

ICARDER EVCARDER ESCWTI ESCTI ESCRI ESCPI

WT31-24

ETU10-8

SCWTI SCTI SCRI SCPI

38

4202E–SCR–06/06

Page 39

AT8xC5122/23

Table 18. SCIB SFRs

MnemonicAddName 76543210

SCICLK C1h

Smart Card Frequency

Prescaler Register

XTSCS

(1)

SCICLK5-0

Note: 1. Only for AT8xC5122

Table 19. DC/DC SFRs

MnemonicAddName 76543210

DCCKPS BFh

DC/DC Converter Reload

Register

MODE OVFADJ BOOST[1-0] DCCKPS3-0

Table 20. Keyboard SFRs

MnemonicAddName 76543210

(1)

KBF

KBE

KBLS

(1)

(1)

9Eh Keyboard Flag Register KBE7 - 0

Keyboard Input Enable

9Dh

Register

Keyboard Level Selector

9Ch

Register

KBF7 - 0

KBLS7 - 0

Note: 1. Only for AT8xC5122

Table 21. SPI SFRs

MnemonicAddName 76543210

(1)

SPCON

C3h Serial Peripheral Control SPR2 SPEN SSDIS MSTR CPOL CPHA SPR1 SPR0

SPSTA

SPDAT

(1)

(1)

Serial Peripheral Status-

C4h

Control

C5h Serial Peripheral Data R7 - 0

SPIF WCOL

MODF

Notes: 1. Only for AT8xC5122

Table 22. USB SFRs

MnemonicAddName 76543210

USBCON BCh USB Global Control USBE SUSPCLK

USBADDR C6h USB Address FEN UADD6-0

USBINT BDh USB Global Interrupt

USBIEN BEh

UEPNUM C7 h USB Endpo int Number

UEPCONX D4 h USB Endpo int X Control EPEN NA KIEN NA KO UT NAK IN DTGL EPDIR E PTYPE1 EPTYPE0

UEPSTAX C Eh USB Endpoint X Status DIR RXOUTB1 STALLRQ TXRDY ST L/CR C RXSETUP RXOUTB0 T XCM P

UEPRST D5h USB Endpoint Reset

UEPINT F8h USB Endpoint Interrup t

USB Global Interrupt

Enable

EP6RST EP5RST EP4RST EP3RST EP2RST EP1RST EP0RST

EP6INT EP5INT EP4INT EP3INT EP2INT EP1INT EP0INT

SDRMWUP

WUPCPU EORINT S OFINT SPINT

EWUPCPU EEORINT ESOFINT ESPINT

DETACH UPRSM RMWUPE CONFG FADDEN

EPNUM3-0

4202E–SCR–06/06

39

Page 40

AT8xC5122/23

Table 22. USB SFRs

MnemonicAddName 76543210

UEPIEN C2h

UEPDATX CFh USB Endpoint X Fifo Data FDAT7 - 0

UBYCTX E2h

UFNUML BAh USB Frame Number Low FNUM7 - 0

UFNUMH BBh USB Frame Number High

USB Endpoint Interrupt

Enable

USB Byte Counter Low

(EPX)

EP6INTE EP5INTE EP4INTE EP3INTE EP2INTE EP1INTE EP0INTE

BYCT6-0

CRCOK CRCERR FNUM10-8

Table 23. LED SFRs

MnemonicAddName 76543210

LEDCON0 F1h LED Control 0 LED3 LED2 LED1 L ED0

LEDCON1

(1)

E1h LED Control 1 LED6 LED5 LED4

Note: 1. Only for AT8xC5122

40

4202E–SCR–06/06

Page 41

AT8xC5122/23

Clock Controller The clock controller is based on an on-chip oscillator feeding an on-chip Phase Lock

Loop (PLL). All the internal clocks to the CPU core and peripherals are generated by this

controller.

On-Chip Oscillator The on-chip oscillator is composed of a single-stage inverter and a parallel feedback

resistor. The XTAL1 and XTAL2 pins are respectively the input and the output of the

inverter, which can be configured with off-chip components as a Pierce oscillator (see

Figure 16).

The on-chip oscillator has been designed and optimized to work with an external 8 MHz

crystal and very few load capacitance. Then external load capacitors are not needed

given that :

– the internal capacitance of the microcontroller and the stray capacitance of

circuit board are enough to ensure a stable oscillation

– a very high accuracy on the oscillation frequency is not needed

The circuit works on its fundamental frequency at 8 MHz.

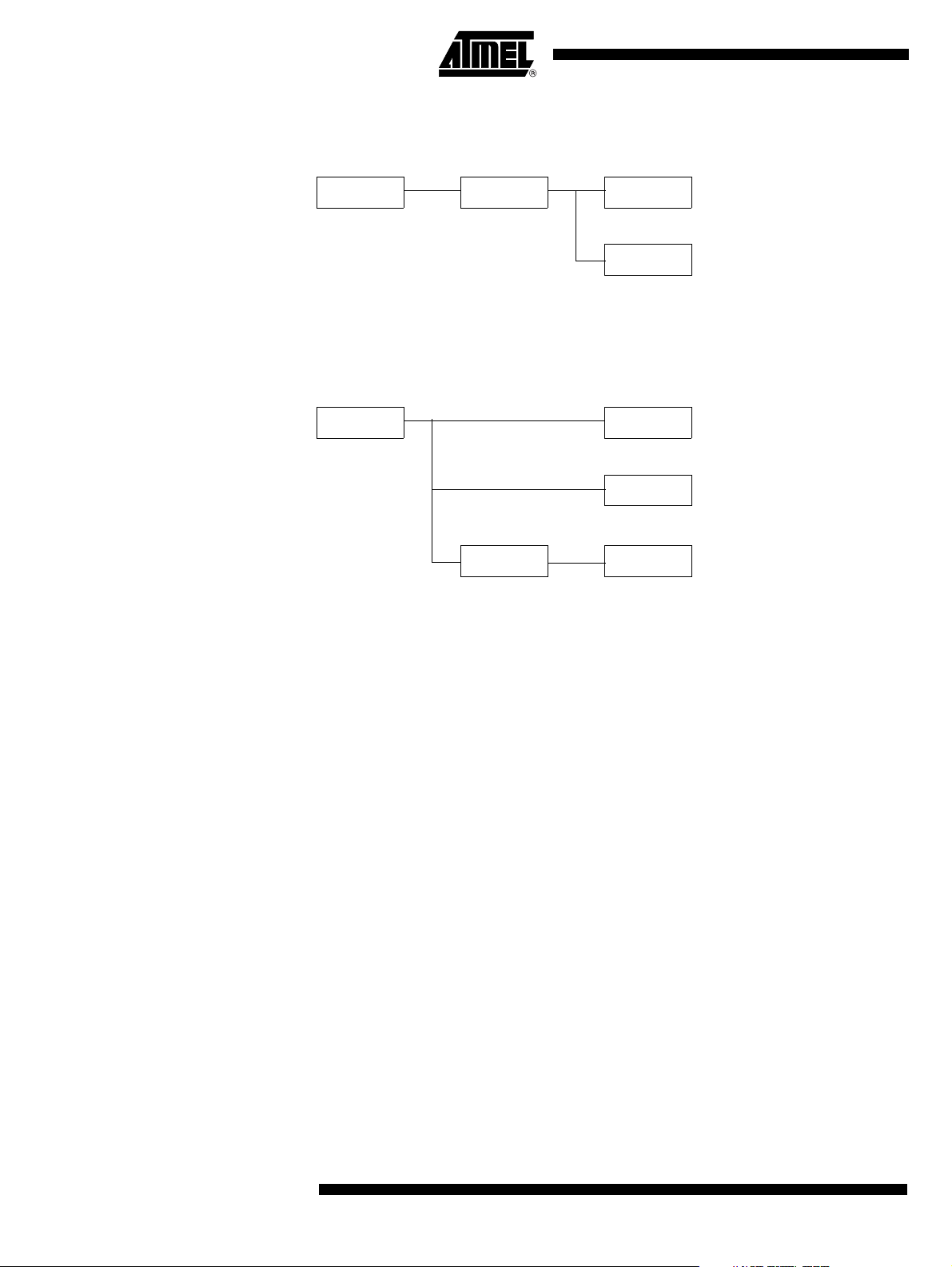

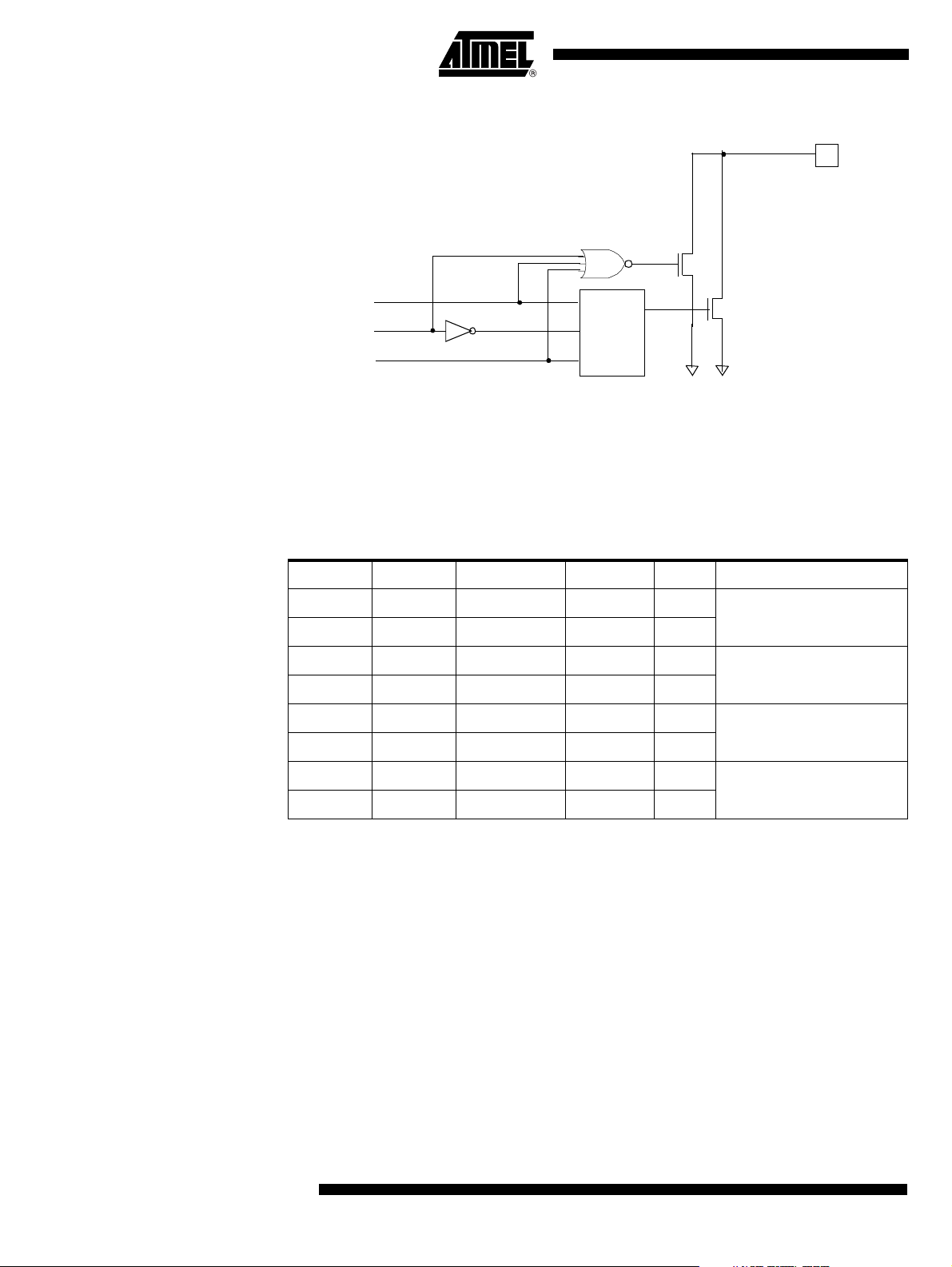

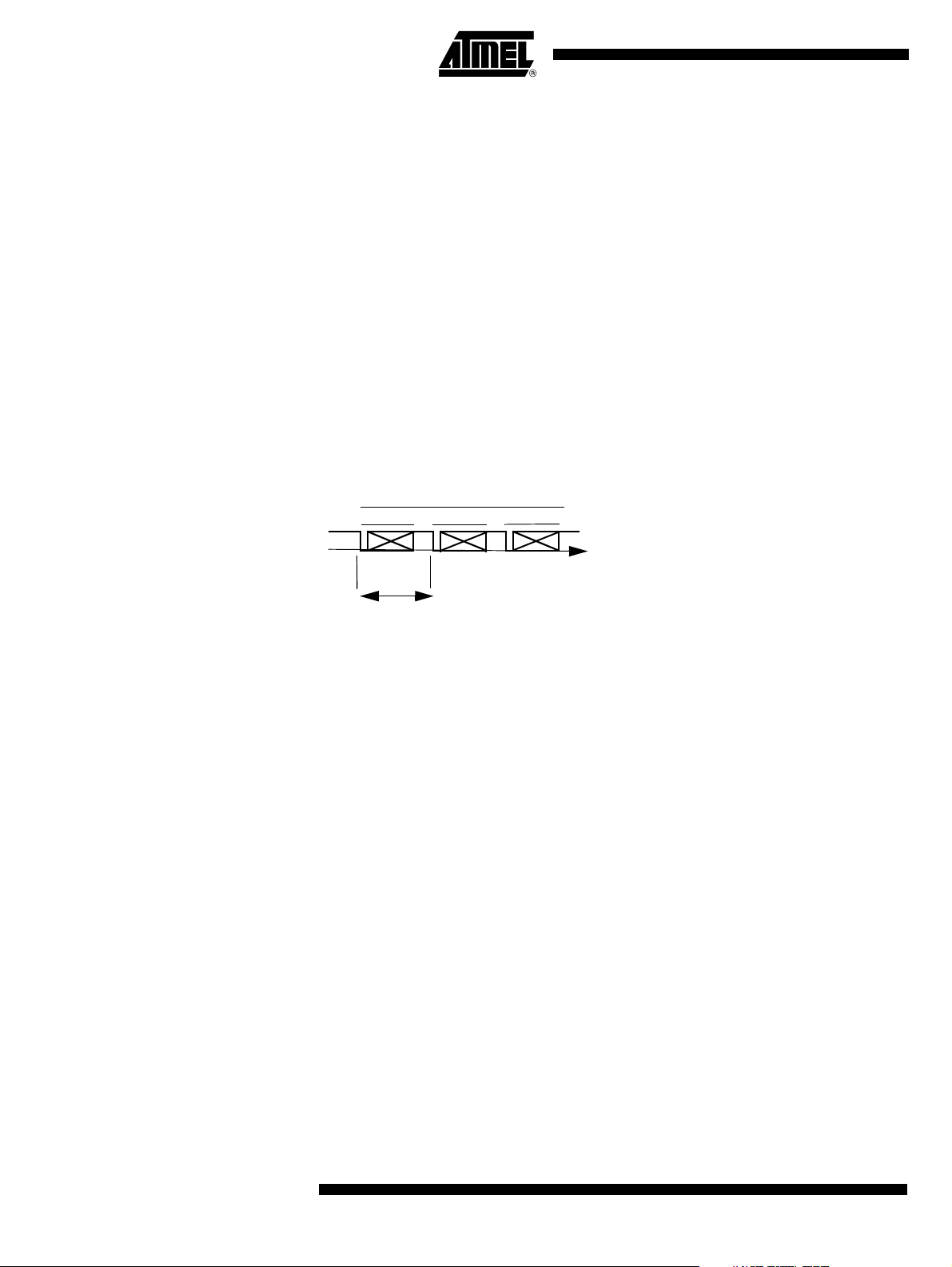

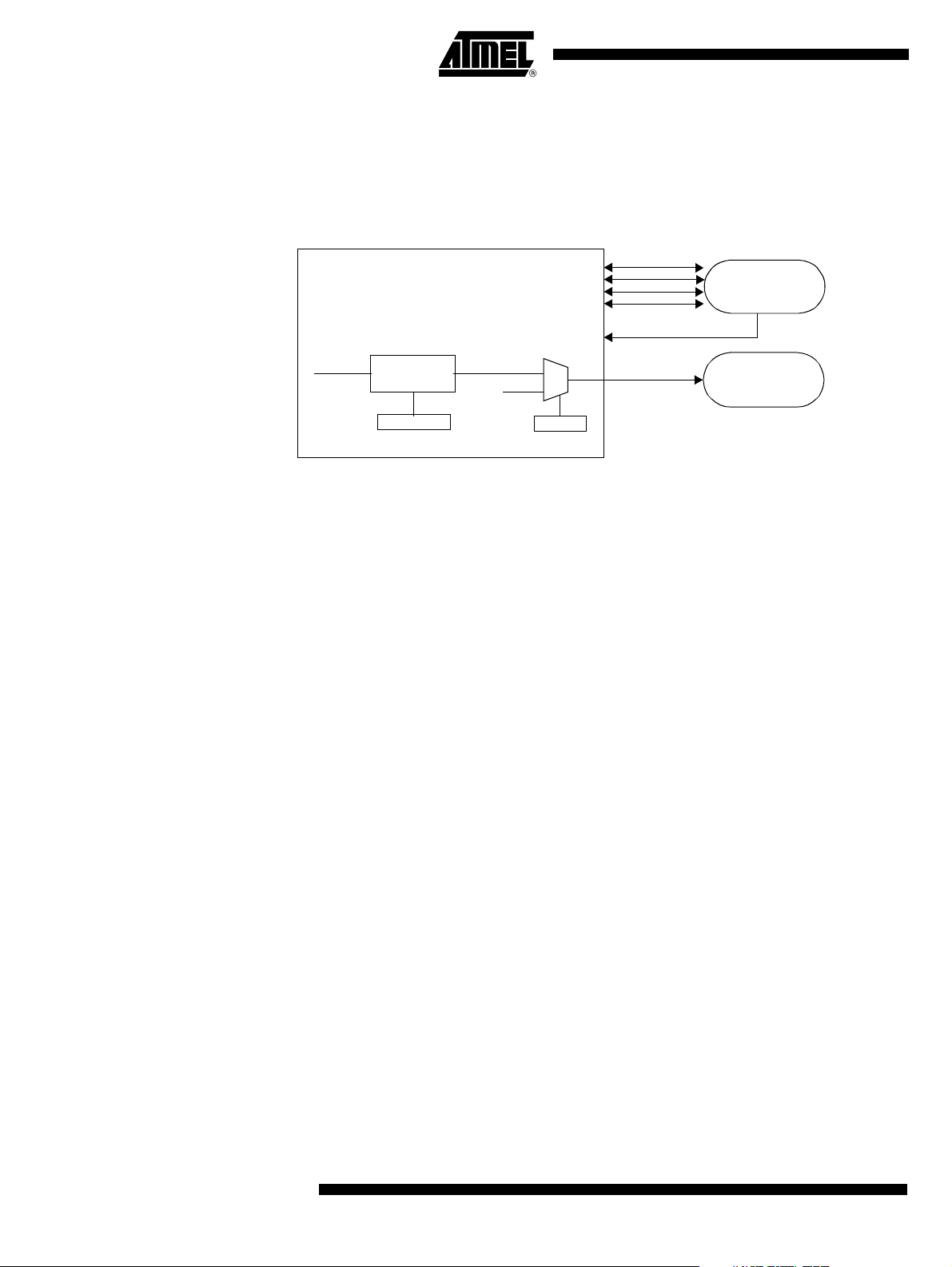

Figure 16. Oscillator Schematic

Microcontroller

To internal

Feedback

Resistor

clock ci rcuitry

XTAL1

C1 C2

C1 and C2 represents the internal capacitance o f the microcontroller and the stray

capacitance of the circuit board. It is recommended to implement the crystal as close as

possible from the microcontroller package.

Quartz Specification The equivalent circuit of a crystal is represented on the figure below :

The Equivalent Serial Resistance R1 must be lower than 100 Ohm.

8 MHz

GND GND

L1 C1 R1

XTAL2

C0

4202E–SCR–06/06

41

Page 42

AT8xC5122/23

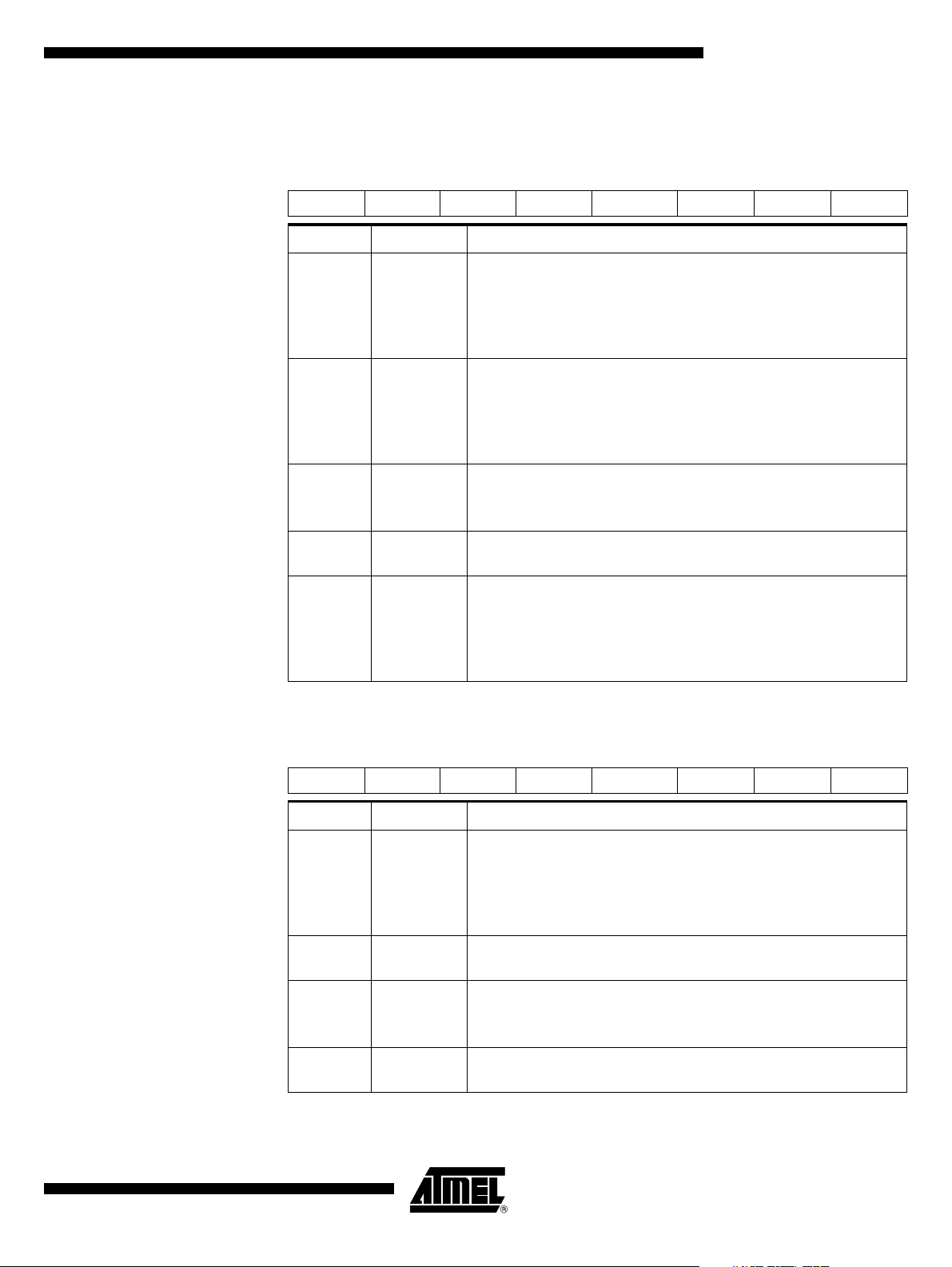

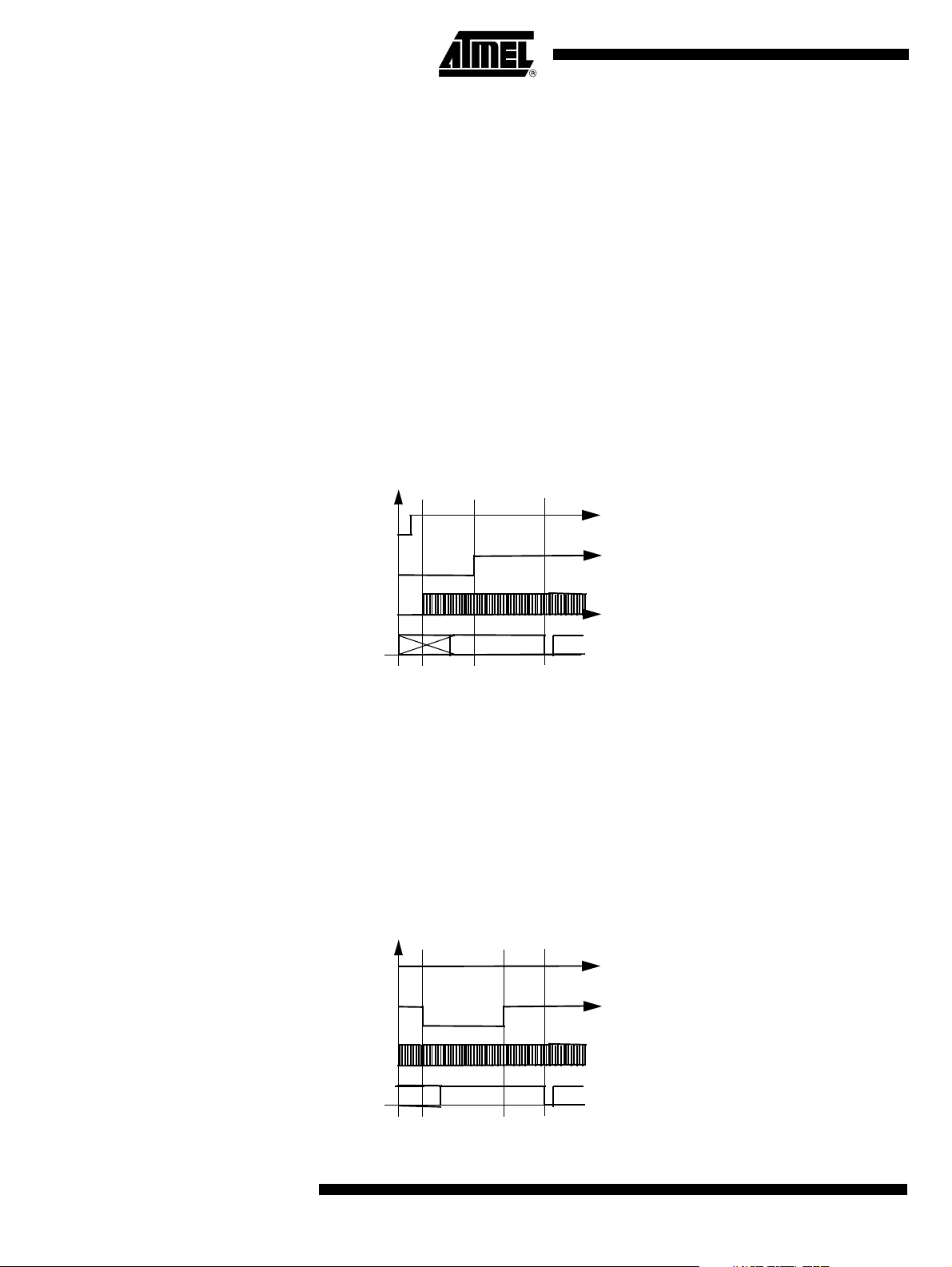

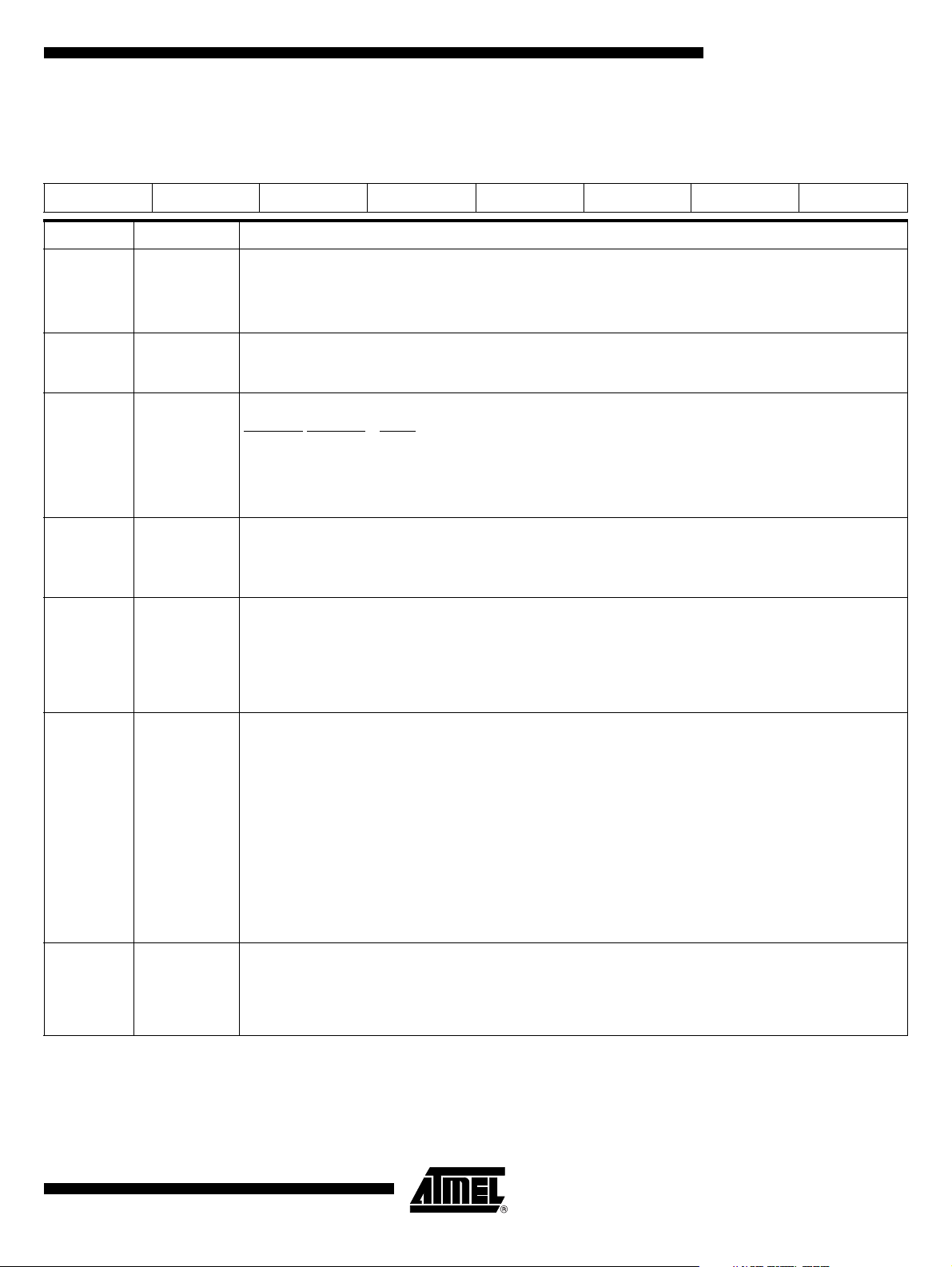

Phase Lock Loop (P LL)

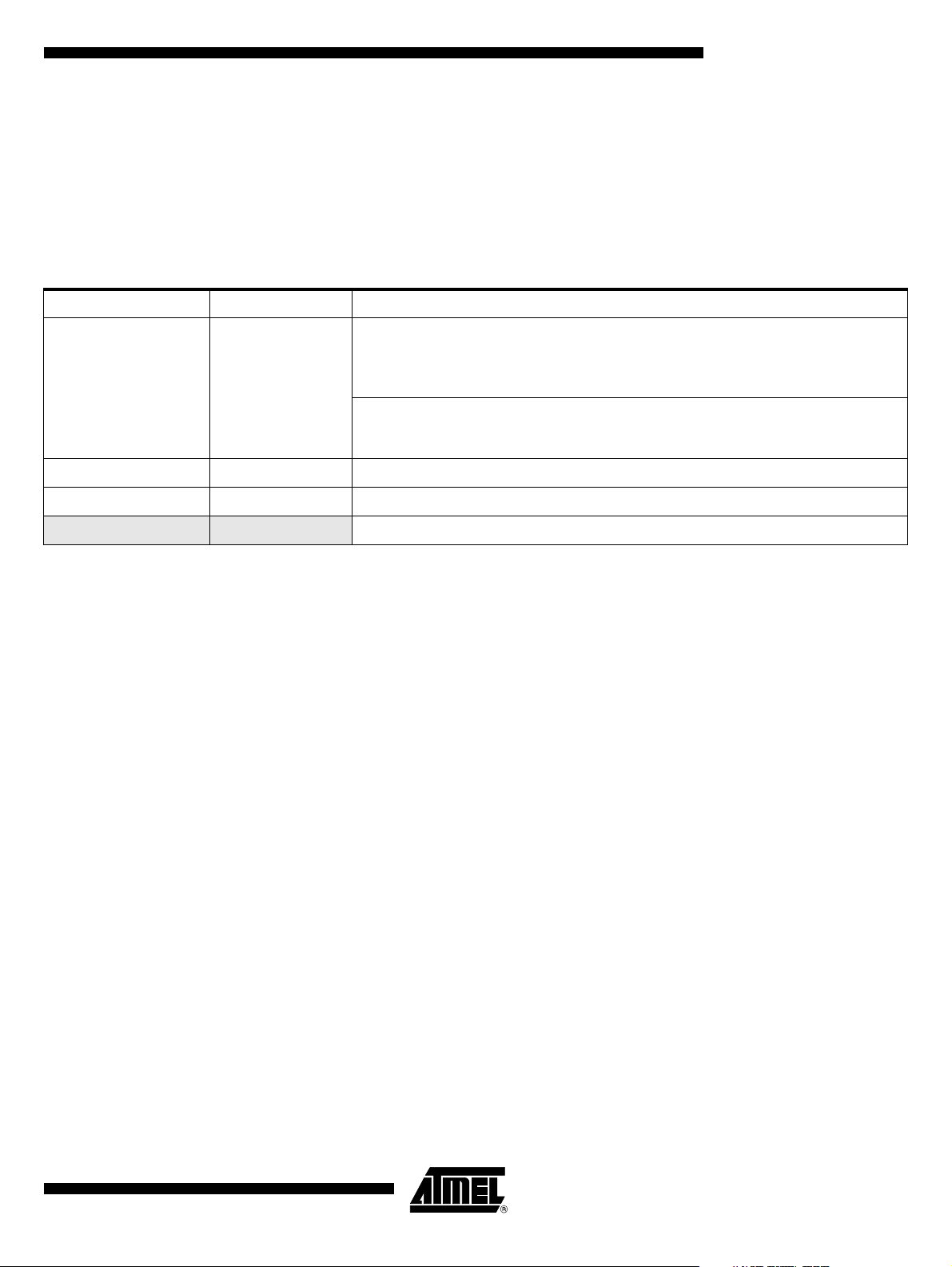

PLL Descrip t io n The AT8xC5122/23’s PLL is used to generate internal high frequency clock synchro-

nized with an external low-frequency. Figure 17 shows the internal structure of the PLL.

The PFLD block is the Phase Frequency Comparator and Lock Detector. This block

makes the com parison betwe en the ref erence clock coming f rom the N divi der and th e

reverse clock coming from the R divider and generates some pulses on the Up or Down

signal depending o n the edge po sition of the reverse clock . The PLLE N bit in PLLCON

register is used to enable the clock generation. When the PLL is locked, the bit PLOCK

in PLLCON register is set.

The CHP block is the Charge Pump that generates the voltage reference for the VCO by

injecting or e xtracting charges from the extern al filter conne cted on P LLF pin (se e

Figur e 18). Va lue of the filter co mponents are deta iled in th e Section “DC

Characteristics”.

CK_XTAL1

The VCO block is the Voltage Controlled Oscillator controlled by the voltage V

REF

produced by th e charge pump . It generates a squ are wave signal: t he PLL clock. Th e

CK_PLL frequency is defined by the follwing formula:

F

CK_PLL

= F

CK_XTAL1

* (R+1) / (N+1)

Figure 17. PLL Block Diagram and Symbol

PLLF

CHP

R divider

R3:0

V

REF

VCO CK_PLL

N Divider

N3:0

PLLCON.1

PLLEN

Up

PFLD

Down

PLOCK

PLLCON.0

Figure 18. PLL Filter V alu e

PLLF

1,8

K

Ω

150 pF

VSS

33 pF

VSS

PLL Program m i ng The PLL must be programmed t o wo rk a t 96 MHz frequency by means of PL LCON a nd

PLLDIV registers. As soon as the PLL is enabled, the firmware must wait for the lock bit

status to ensure that the PLL is ready.

42

4202E–SCR–06/06

Page 43

Figure 19. PLL Programming Flow

PLL

Programming

Configure Divi ders

N3:0=

xxxxb

R3:0= xxxxb

Enable PLL

PLLEN= 1

PLL Locked?

PLOCK= 1?

AT8xC5122/23

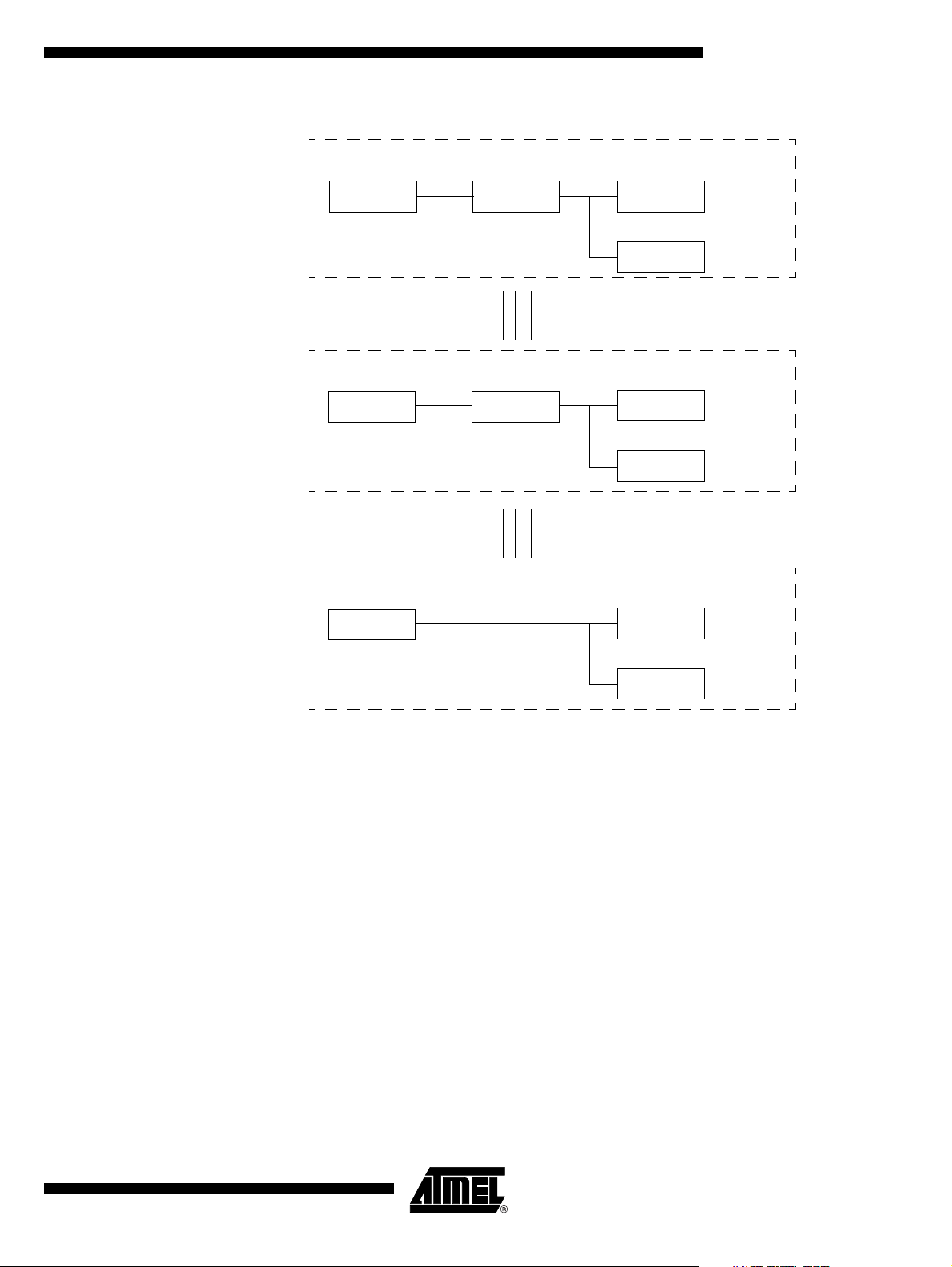

Clock Tree Architecture The clock controller outputs several different clocks as shown in Figure 20:

• a clock for the CPU core

• a clock for the peripherals which is used to generate the timers, watchdog, SPI,

UART, and ports sampling clocks. This divided clock will be used to generate the

alternate card clock.

• a clock for the USB

• a clock for the SCIB controller

• a clock for the DC/DC converter

These clocks are enabled or not depending on th e power redu ction mode as detailed in

Section “Power Management”, page 180.

These clocks are generated using four presacalers defined in the table below:

Prescaler Register Reload Factor Function

PR1 CKRL CKRL[0:3] CPU & Peripheral clocks

PR2 SCICLK SCICLK[0:5] Smart card

PR3 SCSR ALTKPS[0:1] Alternate card

PR4 DCCKPS DCCKPS[3:0] DC/DC

4202E–SCR–06/06

43

Page 44

AT8xC5122/23

I

Figure 20. Clock Tree Diagram

XTAL1

XTAL2

PD

PCON.1

CK_XTAL1

PLL

96 MHz

PLLEN

PLLCON.1

CK_XTAL1

CK_PLL

CK_PLL

0

1

CKS

CKSEL.0

1/2

PR4

DCCKPS[3:0]

1/2

PR1

CKRL[3:0]

CK_PLL

CK_XTAL1

XTSCS

SCICLK.7

EXT48

PLLCON.2

CK_XTAL1

CKCON0.X or

CKCON1.0

PeriphX2

1

0

0

1

X2

CKCON0.0

0

1

0

1

CK_DCDC

DC/DC

Converter

CKCON0.0

X2

Peripherals

CK_T0

1

0

CK_PERIPH

CK_T1

CK_SI

CK_WD

CK_SPI

PERIPH = T0, T1, SI, WD or SP

CK_IDLE

CK_CPU

CPU

IDL

PCON.0

PR3

SCSR[3:2]

PR2

SCICLK[5:0]

SCICLK[5:0]

<48

=48

CK_IDLE

CK_ISO

CK_IDLE

CK_USB

Alternate

Card

SCIB

USB

CPU and Peripheral Clocks Two clocks sources are available for CPU and peripherals:

– on -c h ip o s c illator

– a derivative of the PLL clock.

These clock sources are configured by the PR1 prescaler to generate the CPU core

CK_CPU and the peripheral clocks:

– CK_IDLE fo r alternate card and peripherals registers access

–CK_T0 for Timer 0

–CK_T1 for Timer 1

– C K_SI for th e UART

– CK_WD for the Watchdog Timer

– CK_SPI for SPI

44

4202E–SCR–06/06

Page 45

AT8xC5122/23

The CPU and peripherals clocks frequencies are defined in the table below.

CKS X2 F

00F

01F

10F

11Not allowed

X1 and X2 Modes Use of on - chip osc illator

When the C PU a nd P eri phe rals cl ock s are fe d by the on -chi p os ci lla tor, the C PU an d