Page 1

Features

• AUDIO CODEC

– 100dB Dynamic Range Stereo Audio DAC - 8 to 96 kHz sampling frequency

– 96dB Dynamic Range Stereo Audio ADC - 8 to 96 kHz sampling frequency

– 16 / 32 Ohms headset amplifier with capless operation

• SNR: 97 dB A-Weighted

• THD: -60 dB (16Ohms / 20mW / 3.3V supply)

• Maximum output power: 55mW (16Ohms / 3.3V supply)

– Stereo line inputs, stereo auxiliary inputs

– Stereo microphone inputs with bias generator for electret device

– Low power Analog Bypass mode (Line / Aux in to Headset Out)

– Low power Analog sidetone mode (Microphone in to Headset Out)

– Automatic Audio path control with smooth fade in / fade out operation

2

S port

–I

• Master / Slave Operation

2

S / Left / Right justified modes

•I

• 16 / 18 / 20 / 24 bit operation

• 6x SUPPLY CHANNEL VOLTAGE REGULATORS

– DCDC0:

• 1.85V - 600mA. 0.8 to 3.6V / 50mV step.

• 2 MHz switching buck regulator

• Fast load transient response - PWM / PFM modes.

• Efficiency up to 92%

– DCDC1:

• 1.2V - 600mA. 0.8 to 3.6V / 50mV step.

• 2 MHz switching buck regulator

• Fast load transient response - PWM / PFM modes.

• Efficiency up to 90%

– LDO2: 1V - 300mA. 0.8 to 1.35V / 50mV step - Fast transient response

– LDO3: 3.3V - 200mA. 2.7 to 3.6V / 50mV step - Fast transient response

– LDO4: 3.3V - 200mA. 2.7 to 3.6V / 50mV step - Audio codec supply

– LDO5: 2.5V - 10mA - Backup battery charger and RTC supply

• LOW CONSUMPTION POWER MANAGER

– 2.5V - 5.5V VIN Operation

– 20uA typical consumption OFF mode

– VIN monitor, CPU supplies monitor

– Die temperatue and over-current protections

– Reset and Interrupt generation

– Automatic Voltage Ramping on supply channels for DVS applications

– Standby mode with selectable supplies OFF

• RTC

– Ultra Low power crystal oscillator (<1uA typ.)

– Wake up function with programmable alarm or selectable inputs

• 10-b / 300kS/s ADC with 4 external / 6 int\ernal selectable inputs

• Two-Wire Interface for PMU and Audio controls

• Available in 7.5 x 7.5 x 0.9 mm 64-pin QFN Package

• Applications: Multimedia, Audio + Supply solution for MPU+DDR2 designs.

Power

Management

and Analog

Companions

(PMAAC)

AT73C246

6 Supply

Channel PMU

With Audio

Codec

11050A–PMAAC–07-Apr-10

Page 2

1. Description

The AT73C246 is an integrated high performance Power Management and Audio IC. It is specifically designed for advanced technology application processors with complex and low voltage

supplies targeting audio applications from low to high end. This System-on-Chip allows significant savings in both cost and board area over previous discrete solutions.

Directly operated from a 2.9V to 5.5V input voltage, the PMU generates a set of 4 regulated

power supplies and an associated delayed reset signal. These 4 voltages are built up with 2 high

efficiency DCDC buck converters and 2 low noise LDOs. Featuring ultra fast transient responses

and integrating automatic voltage scaling function, these supplies perfectly fit with modern low

voltage MCU cores and memory supplies (DDR, Flash, ...). An additional 200mA LDO under

software control is provided for auxiliary application functions. The high performances of this

LDO (high PSRR, low noise, fast transient response) makes it ideal for analog front-ends (Audio,

RF...) as well digital peripherals.

Aside from the PMU, the AT73C246 integrates a complete state-of-the art low power audio

codec with headphone amplifier. On the input side, a stereo microphone preamplifier with differential or single ended connection (MICDIFF / MIC) and 2 selectable stereo inputs (LINE / AUX)

are directed to a 96dB Dynamic Range stereo audio ADC through an input mixer. On the output

side a 100dB dynamic range stereo audio DAC drives, through an output mixer, a 60 mW stereo

headphone amplifier which comes along with a VCM buffer. This VCM buffer allows to save two

large on-board coupling capacitors for area constrained applications. Additionally two fully analog paths called bypass and sidetone from line / aux and microphone inputs to headphone

outputs allow to reduce the audio power consumption to minimum when needed.

The PMU is complemented with a low power RTC system including a recharging LDO, a crystal

oscillator and a programmable alarm that is fully integrated in the PMU digital core. Thus, the

RTC function is able to wake up the PMU, i.e the regulated power supplies, at a programmed

instant.

Also, a 10-bit ADC equipped with a 10:1 analog multiplexer is provided to the application to perform voltage measurements.

Finally, to reduce power consumption to minimum, the PMU features a flexible STANDBY mode

where the MCU is placed in reset state with selectable supplies ON, OFF or in low-power mode.

Power consumption in OFF mode is typically 20uA.

2

AT73C246

11050A–PMAAC–07-Apr-10

Page 3

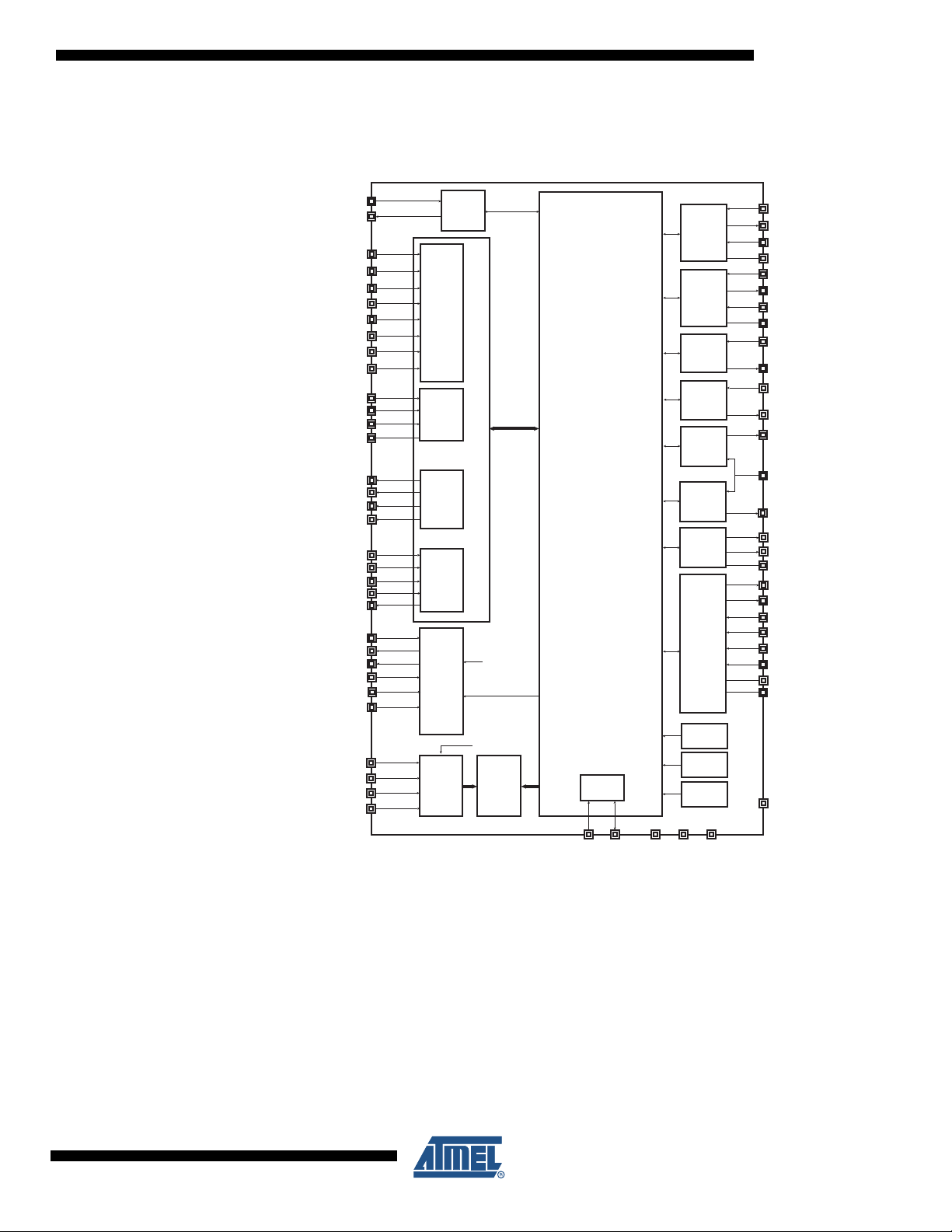

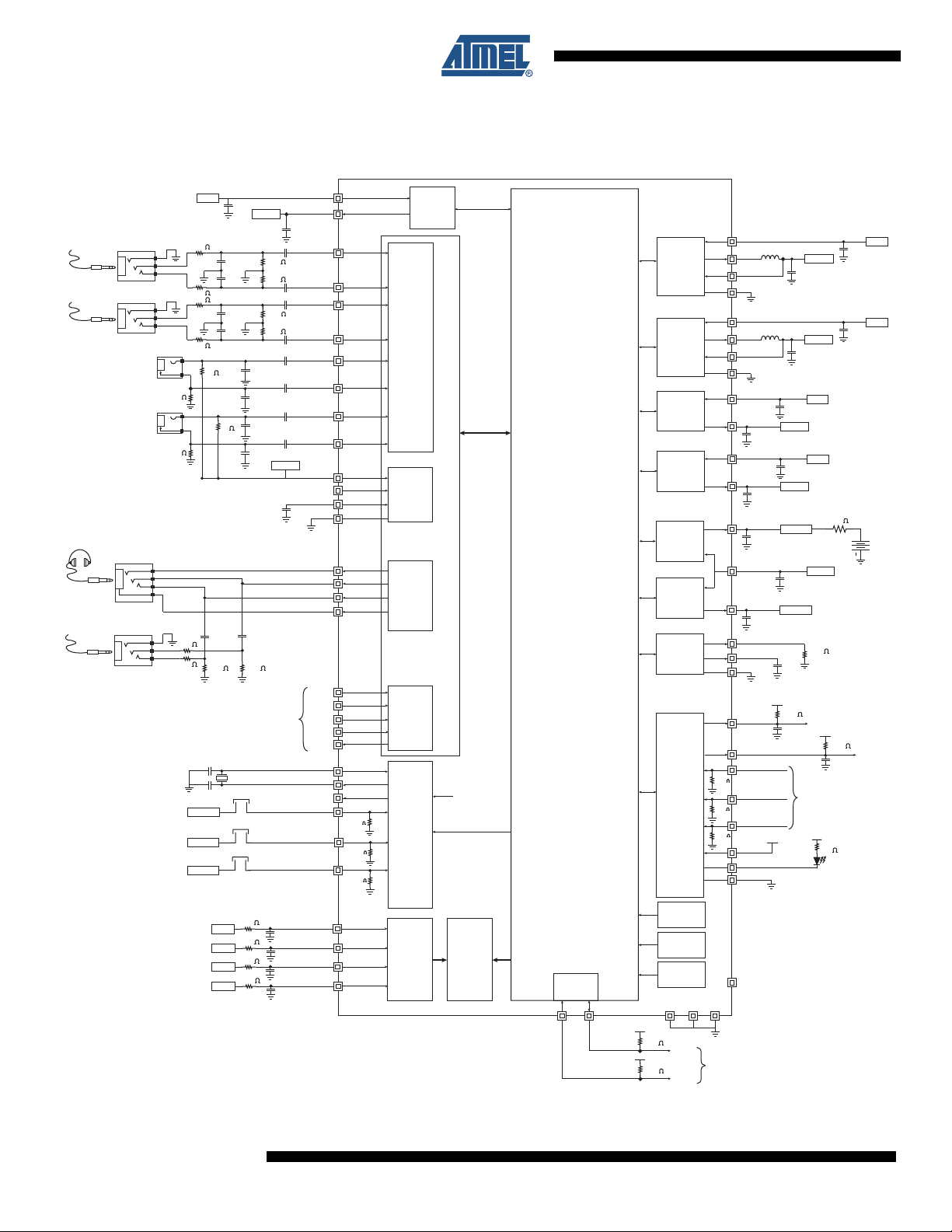

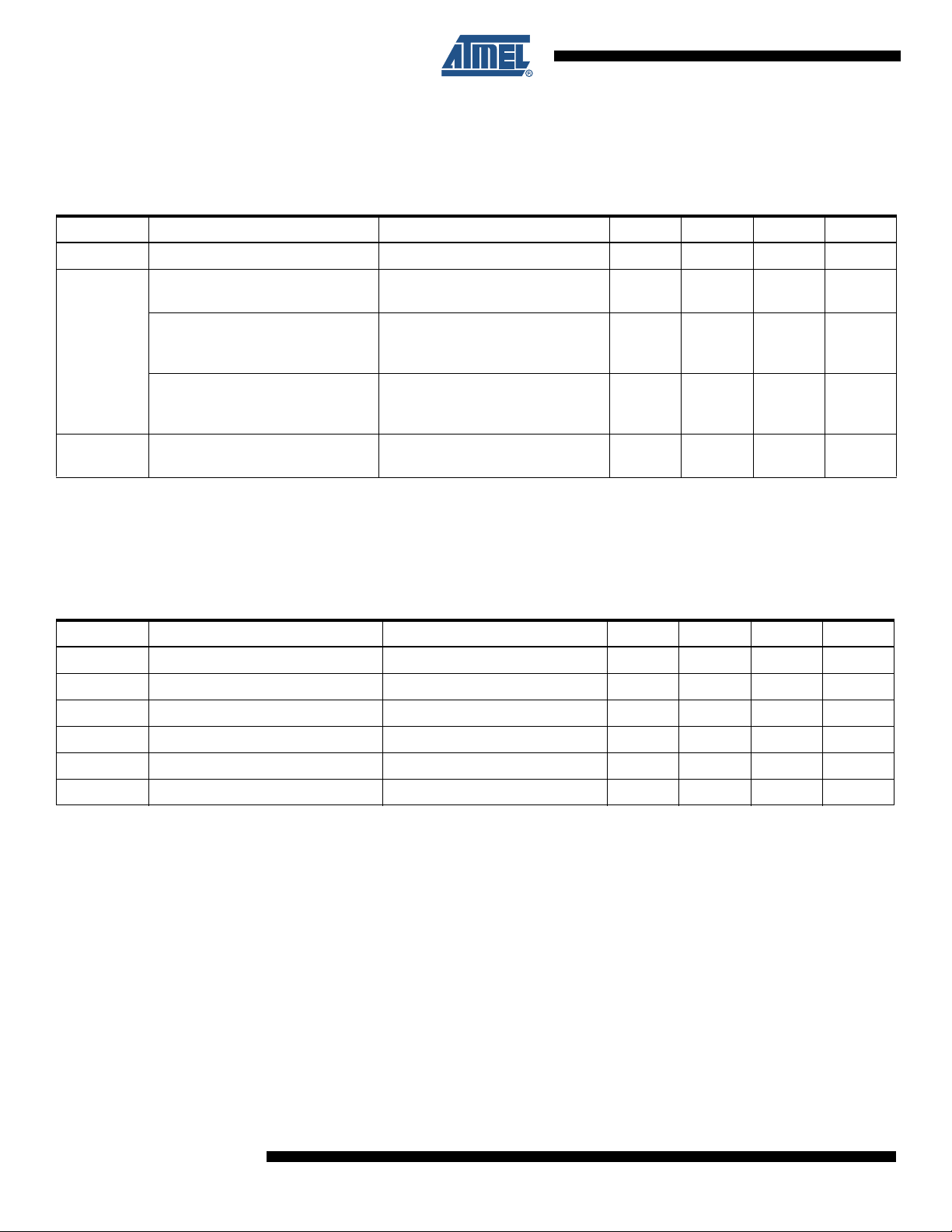

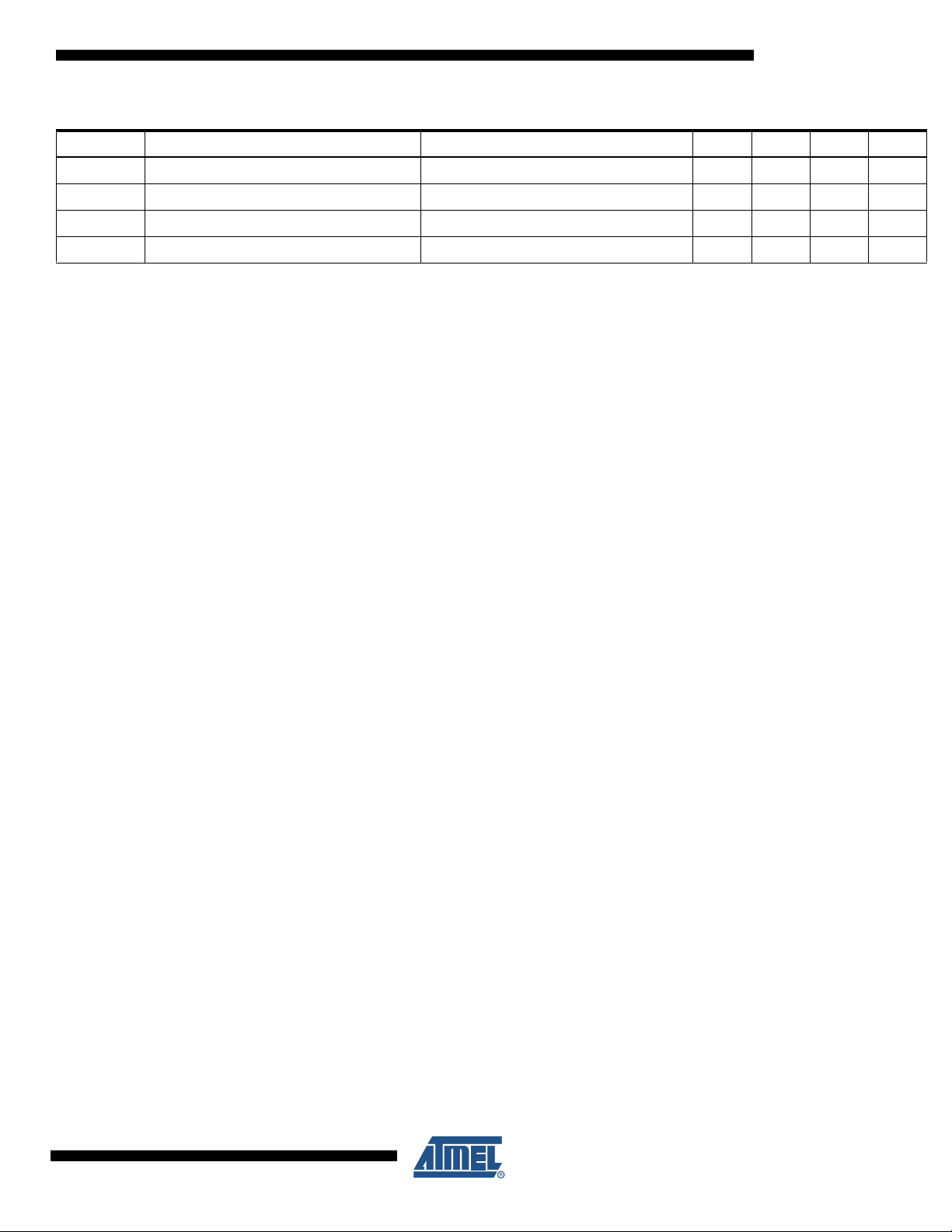

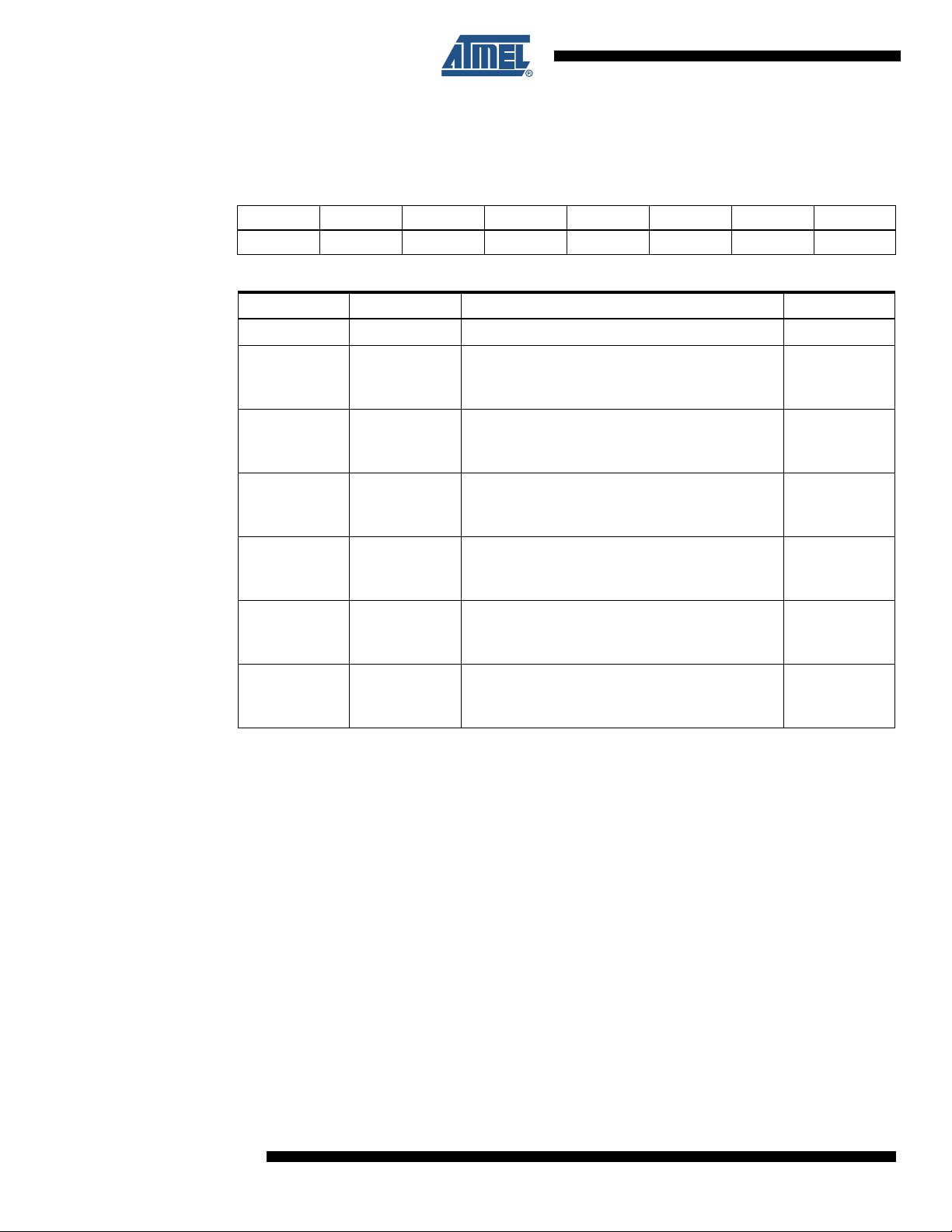

2. Block Diagram

LDO4

3.3V

(CODEC)

AUDIO

CODEC

DIGITAL

CORE

VIN4

VIN0

SW0

VFB0

GND0

BUCK0

1.8V

Max: 600mA

(CORE + MEM)

TWDTWCK

Max: 200mA

VDD4

AVDD

VIN1

SW1

VFB1

GND1

BUCK1

1.2V

Max: 600mA

(CORE)

VIN2

LDO2

1V

Max: 300mA

(CORE)

VDD2

VIN3

LDO3

3.3V

Max: 200mA

(I/O)

VDD3

VINSYS

LDO5

2.5V

Max: 10mA

(BACKUP)

VBACKUP

LDO6

1.8V / 10mA

VDDC

VMID

MICBIAS

AGND

AUDIO

BIAS

LINR

LINL

MICL

AUDIO IN

+ ADC

AUXR

AUXL

HPDET

HPL

HPR

HPVCM

AUDIO OUT

+ DAC

MCLK

LRFS

BCLK

DAI

AUDIO

PORT

DAO

XIN

CLK32K

XOUT

WAKEUP0

RTC +

OSC

PMU

BIAS

REXT

VBG

GNDSYS

ANA0

ANALOG

MUX

ANA1

ANA2

ANA3

10b SAR

ADC

PMU STATE

MACHINES

RSTB

ITB

VPAD

DGND

TWI

DCDC

4MHz RC

OSCILLATOR

WAKEUP1

WAKEUP2

WAKEUP3

HRST

PWREN

VBACKUP

DIE TEMP

SENSOR

SYSTEM

32KHz RC

OSCILLATOR

MICLN

MICR

MICRN

LED

Internal voltages

37

36

28

27

30

29

34

31

33

32

18

35

12

17

13

14

16

15

44

43

42

41

40

63

64

49

62

60

61

3

4

5

6

22 21

26NC47NC48

NC

2

65

45

25

24

23

19

20

11

9

10

8

7

1

39

38

50

51

55

52

54

53

59

56

58

57

NC

46

(Internal

functions)

AT73C246

Figure 2-1. AT73C246 functional block diagram

11050A–PMAAC–07-Apr-10

3

Page 4

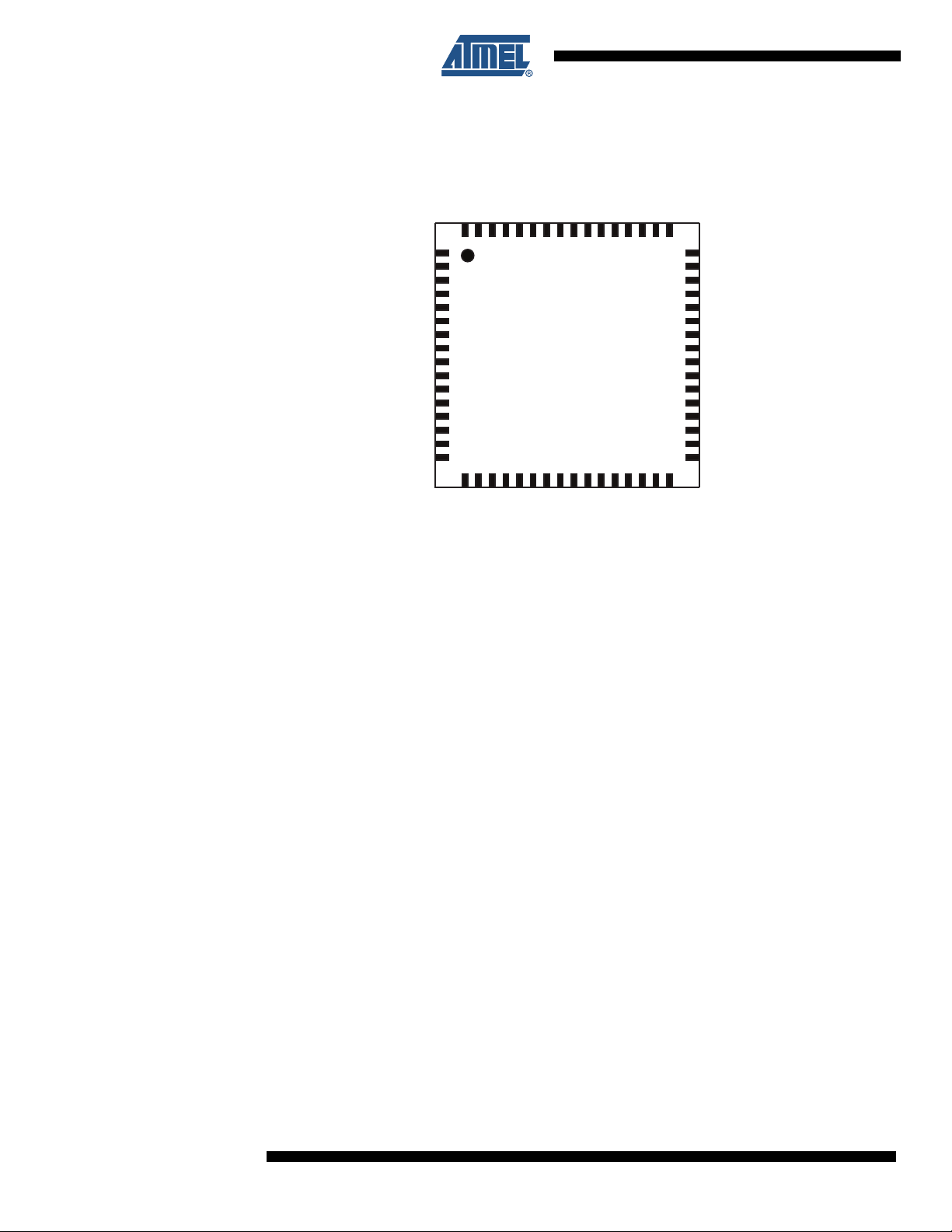

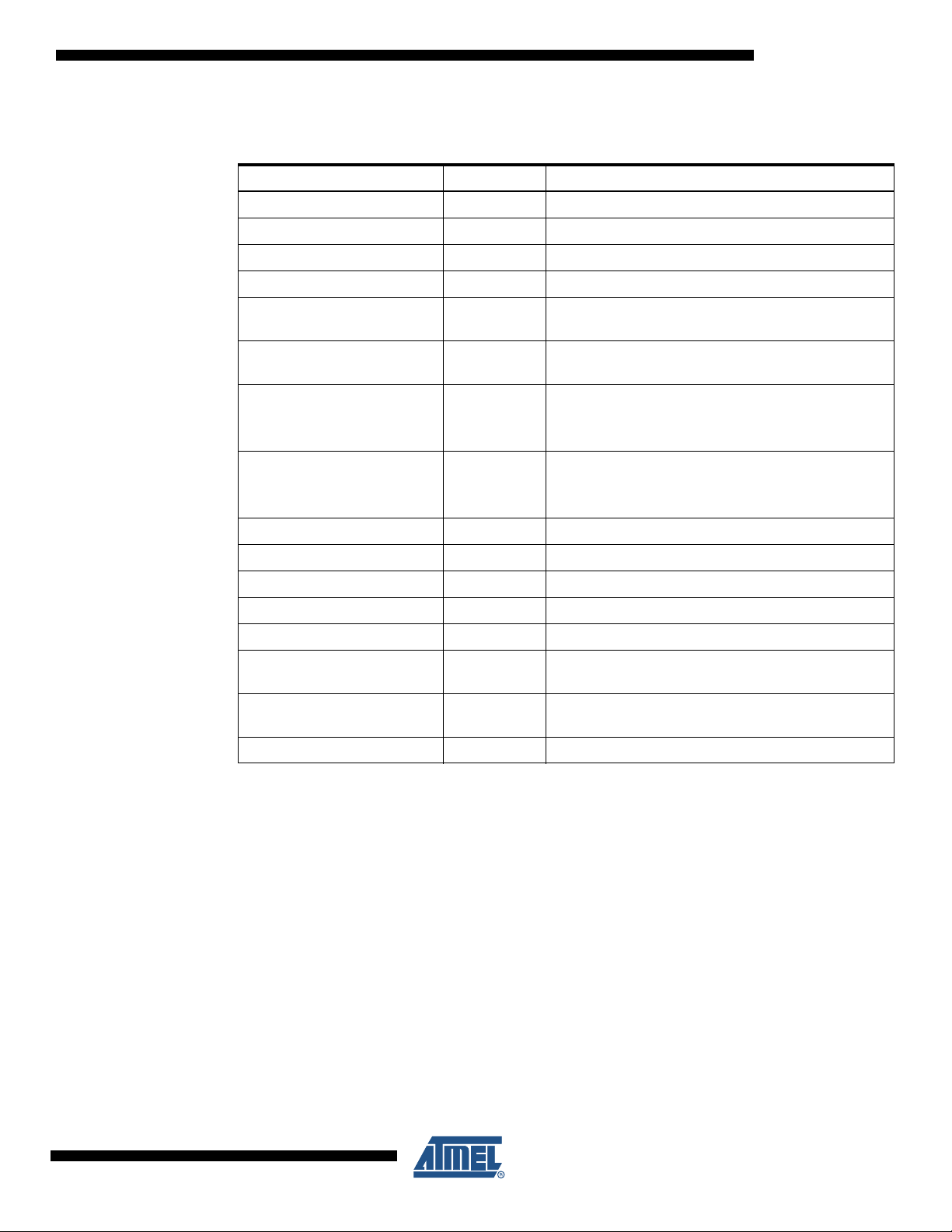

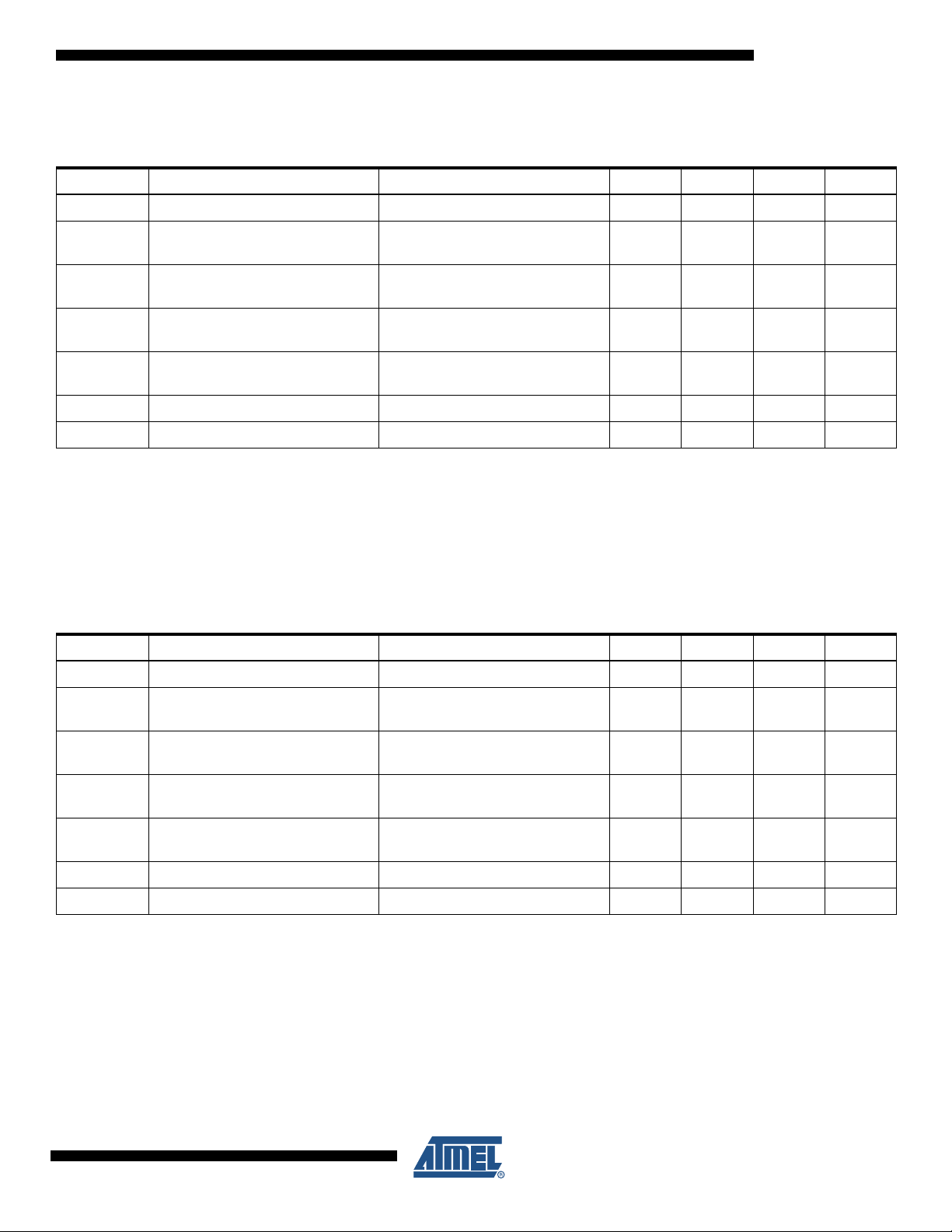

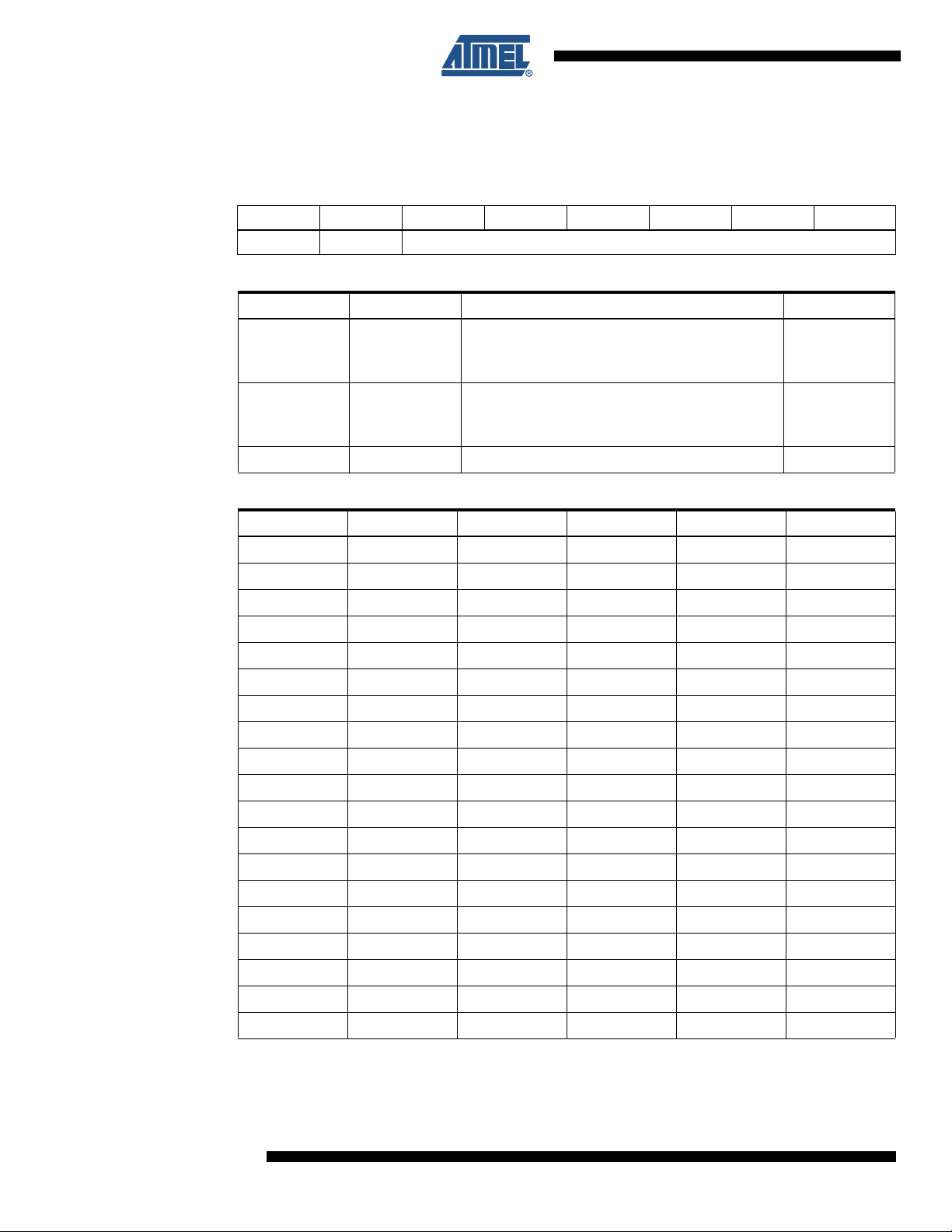

3. Package and Pinout

1

16

17 32

33

48

4964

VBACKUP

LED

ANA0

ANA1

ANA2

ANA3

VINSYS

VDDC

VBG

REXT

GNDSYS

VMID

HPDET

HPR

HPVCM

HPL

AGND

AVDD

ITB

RSTB

TWD

TWCK

WAKEUP1

WAKEUP2

WAKEUP3NCLINR

LINL

AUXR

AUXL

MICLN

MICRN

NC

NC

NC

VPAD

MCLK

LRFS

BCLK

DAI

DAO

VDD3

VIN3

VIN4

VDD4

MICBIAS

MICL

MICR

XOUT

XIN

WAKEUP0

PWREN

HRST

GND0

SW0

VIN0

VFB0

GND1

SW1

VIN1

VFB1

VIN2

VDD2

MCLK32

Figure 3-1. AT73C246 QFN64 package pinout - Top view

4

AT73C246

11050A–PMAAC–07-Apr-10

Page 5

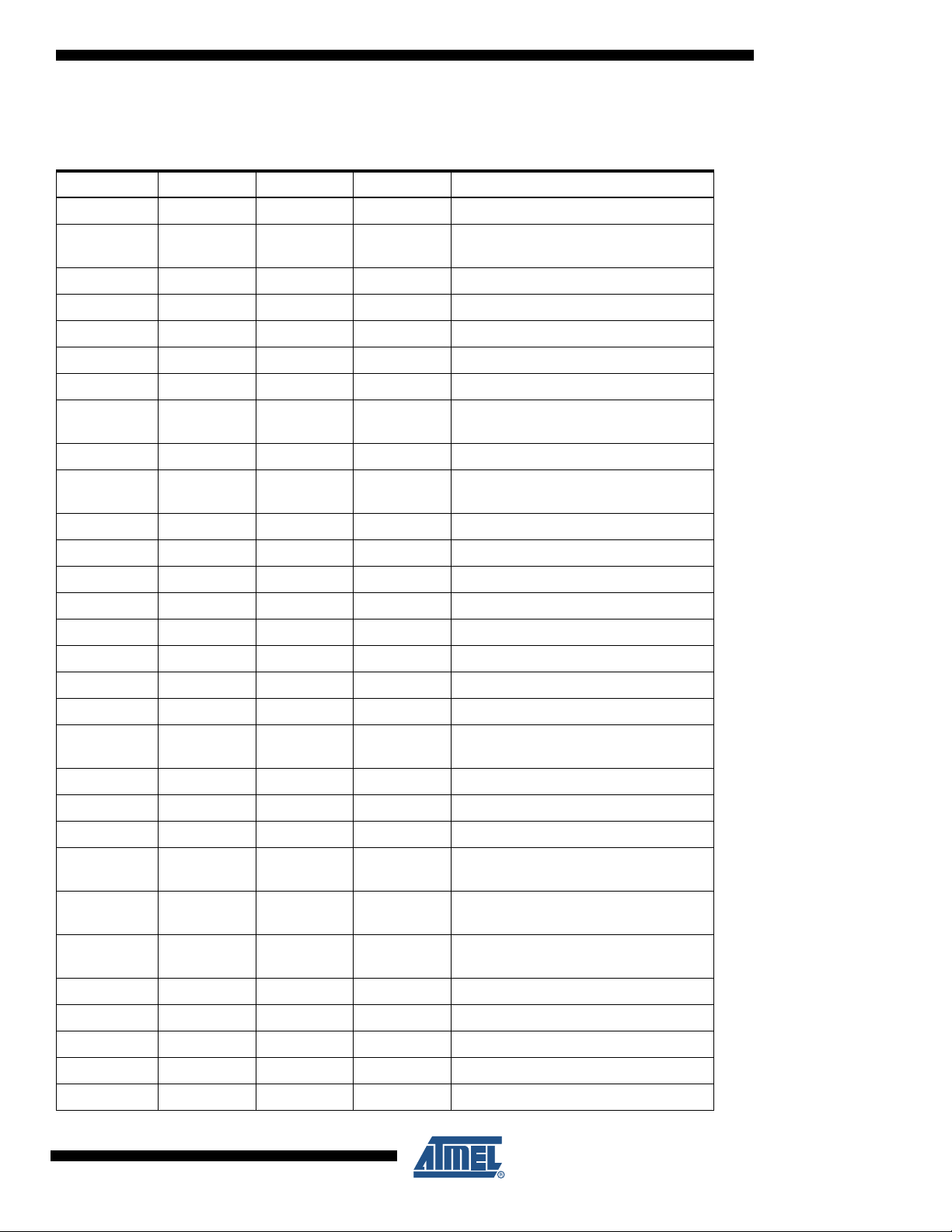

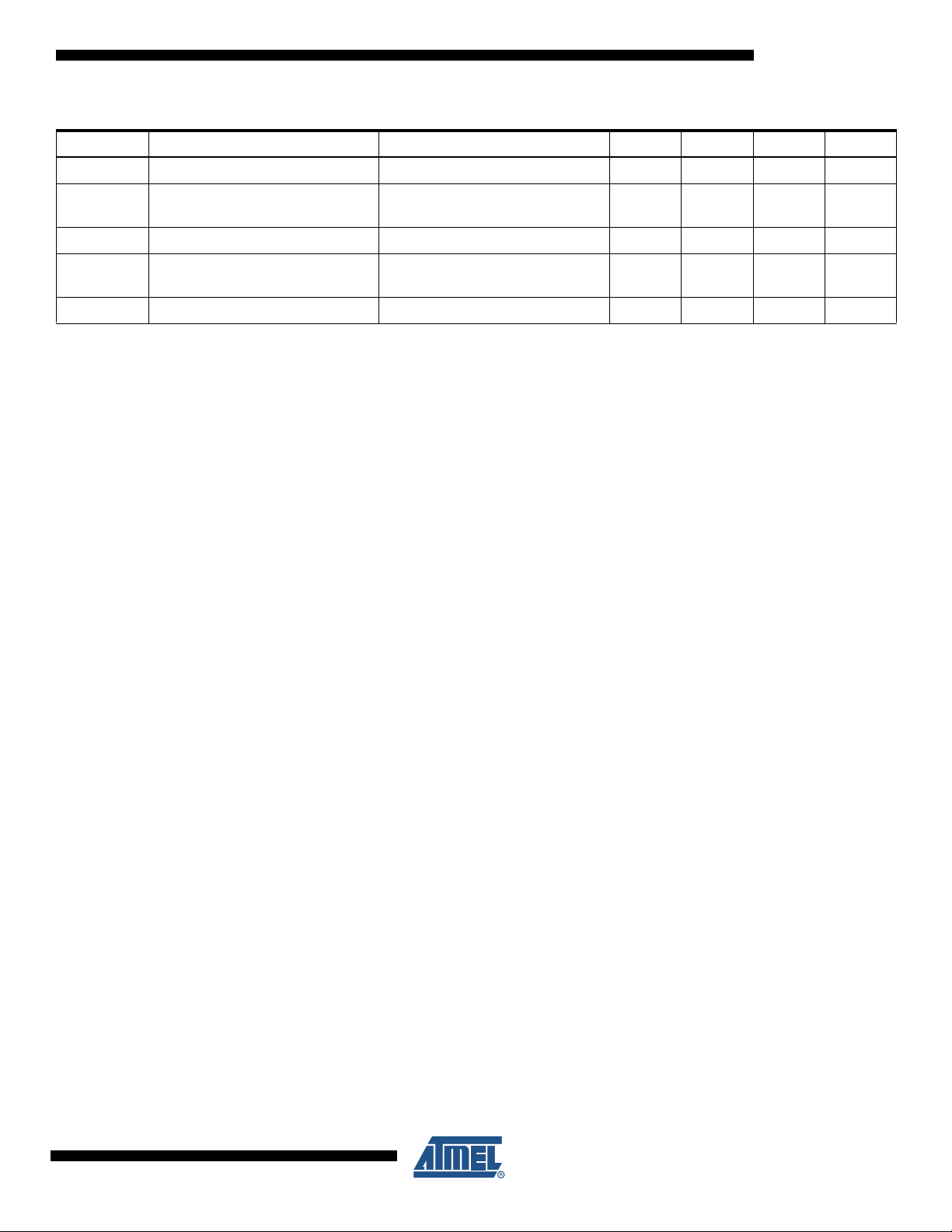

4. Pin Description

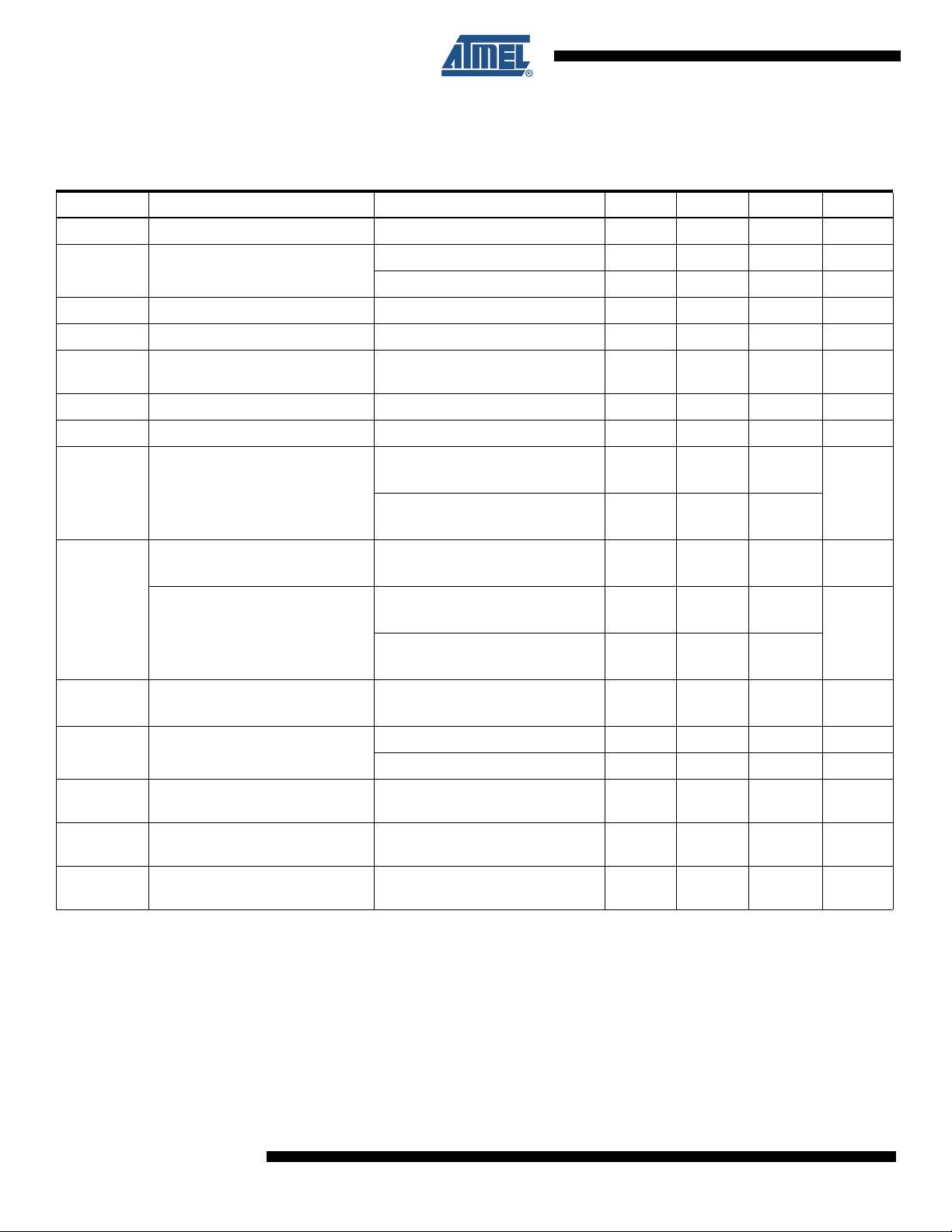

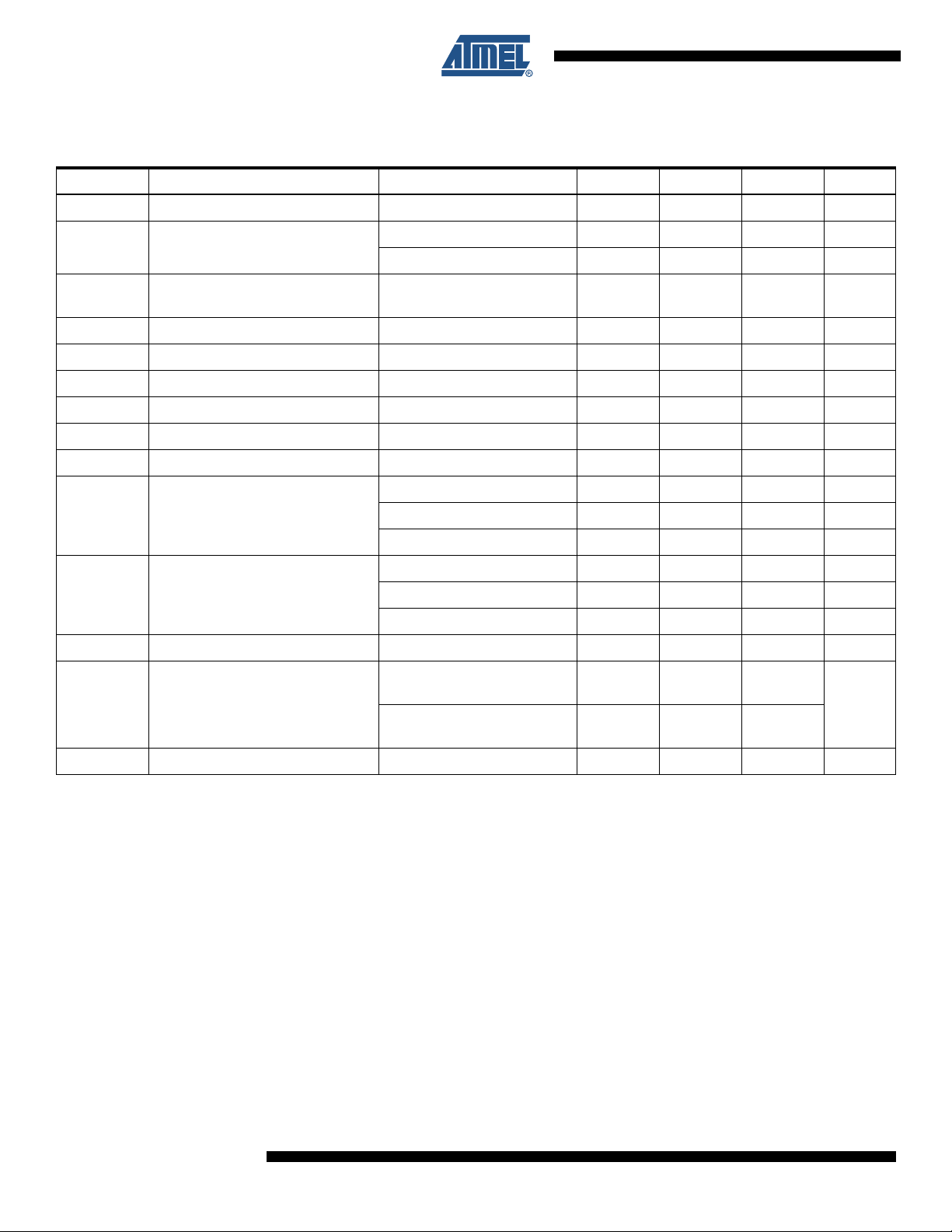

Table 4-1. Pin Description

Pin Name I/O Pin Number Type Function

VBACKUP Output 1 Analog RTC supply

AT73C246

LED Output 2 Digital

ANA0 Input 3 Analog Measurement input 0

ANA1 Input 4 Analog Measurement Input 1

ANA2 Input 5 Analog Measurement Input 2

ANA3 Input 6 Analog Measurement Input 3

VINSYS Input 7 Power PMU core supply

VDDC Output 8 Analog

VBG Output 9 Analog PMU Voltage reference

REXT Output 10 Analog

GNDSYS GND 11 Analog PMU ground

VMID Output 12 Analog Audio Codec Mid-Supply reference

HPDET Input 13 Analog Headset detector

HPR Output 14 Analog Headset output right

HPVCM Output 15 Analog Headset virtual ground output

HPL Output 16 Analog Headset output left

AGND GND 17 Analog Audio Codec ground

AVDD Input 18 Power Audio Codec supply input

Output for blinking led. Leave not

connected if a LED is not wired.

PMU / Audio digital supply. Internal use

only. No resistive load.

Resistor connection for PMU bias

current

ITB Output 19 Digital

RSTB Output 20 Digital CPU reset - Active low - Open drain

TWD Input/Output 21 Digital Two Wire Interface - Data

TWCK Input 22 Digital Two Wire Interface - Clock

WAKEUP1 Input 23 Digital

WAKEUP2 Input 24 Digital

WAKEUP3 Input 25 Digital

NC - 26 - Connect to DGND

LINR Input 27 Analog Audio Line input right

LINL Input 28 Analog Audio Line input left

AUXR Input 29 Analog Audio auxiliary input right

AUXL Input 30 Analog Audio auxiliary input left

11050A–PMAAC–07-Apr-10

Interrupt request - Active low - Opendrain

Wake up 1 Input - VPAD level - 100k

Pull down

Wake up 2 Input - VPAD level - 100k

Pull down

Wake up 3 input - VPAD level - 100k

Pull down

5

Page 6

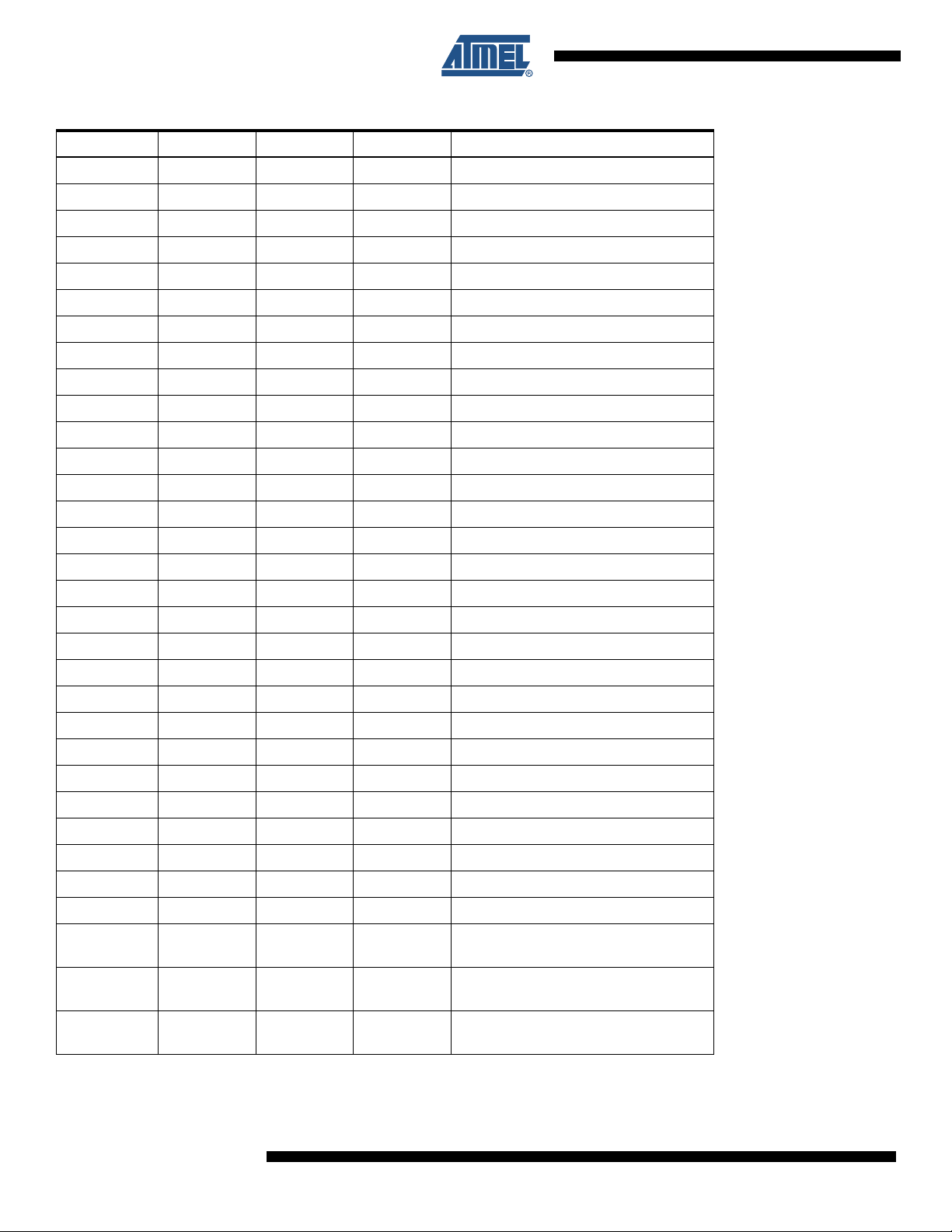

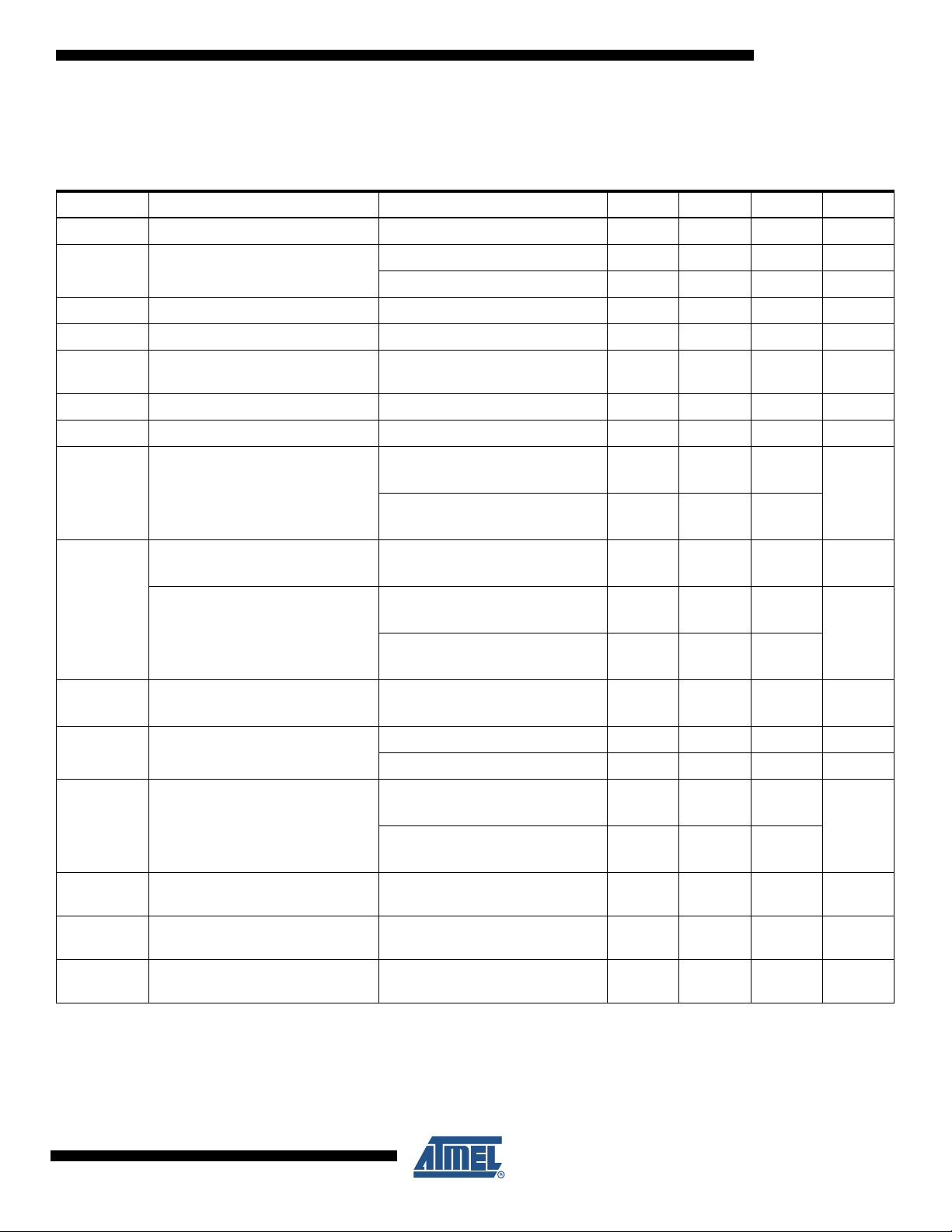

Table 4-1. Pin Description

Pin Name I/O Pin Number Type Function

MICLN Input 31 Analog Audio negative microphone input left

MICRN Input 32 Analog Audio negative microphone input right

MICR Input 33 Analog Audio positive microphone input right

MICL Input 34 Analog Audio positive microphone input left

MICBIAS Output 35 Analog Voltage bias for electret microphone

VDD4 Output 36 Power LDO4 output - 3.3V typ

VIN4 Input 37 Analog LDO4 input

VIN3 Input 38 Power LDO3 input

VDD3 Output 39 Analog LDO3 output - 3.3V typ

DAO Output 40 Digital Digital audio port data output

DAI Input 41 Digital Digital audio port data input

BCLK Input/Output 42 Digital Digital audio port bit clock

LRFS Input/Output 43 Digital Digital audio port left/right clock

MCLK Input 44 Digital Audio codec master clock input

VPAD Input 45 Power PMU I/O ring supply

NC - 46 - Leave open

NC - 47 - Connect to DGND

NC - 48 - Connect to DGND

MCLK32 Output 49 Digital RTC clock output - VPAD level

VDD2 Output 50 Analog LDO2 output

VIN2 Input 51 Power LDO2 input

VFB1 Input 52 Analog DCDC1 Voltage feedback input

VIN1 Input 53 Power DCDC1 power stage supply

SW1 Output 54 Analog DCDC1 power stage output

GND1 Ground 55 Analog DCDC1 power stage ground

VFB0 Input 56 Analog DCDC0 Voltage feedback input

VIN0 Input 57 Analog DCDC0 power stage supply

SW0 Output 58 Analog DCDC0 power stage output

GND0 Ground 59 Analog DCDC0 power stage ground

HRST Input 60 Digital

PWREN Input 61 Digital

WAKEUP0 Input 62 Digital

Hard reset - VBACKUP level - 100k Pull

down

Power on/off - VBACKUP level - 100k

Pull down

Wake up 0 input - VBACKUP level 100k Pull down

6

AT73C246

11050A–PMAAC–07-Apr-10

Page 7

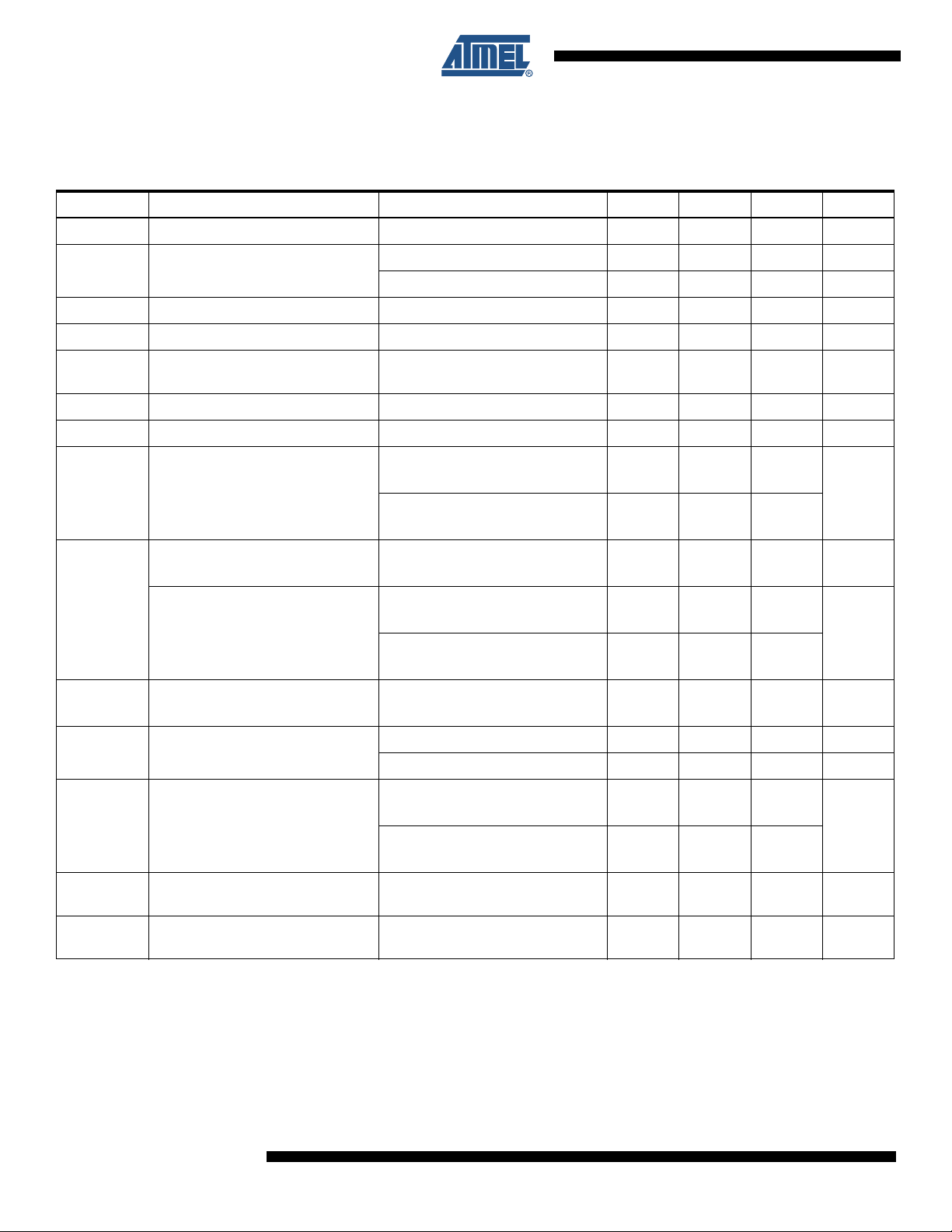

Table 4-1. Pin Description

Pin Name I/O Pin Number Type Function

XIN Input 63 Analog RTC crystal oscillator input

XOUT Output 64 Analog RTC crystal oscillator output

DGND Ground 65 Analog PMU digital ground + Thermal pad.

AT73C246

11050A–PMAAC–07-Apr-10

7

Page 8

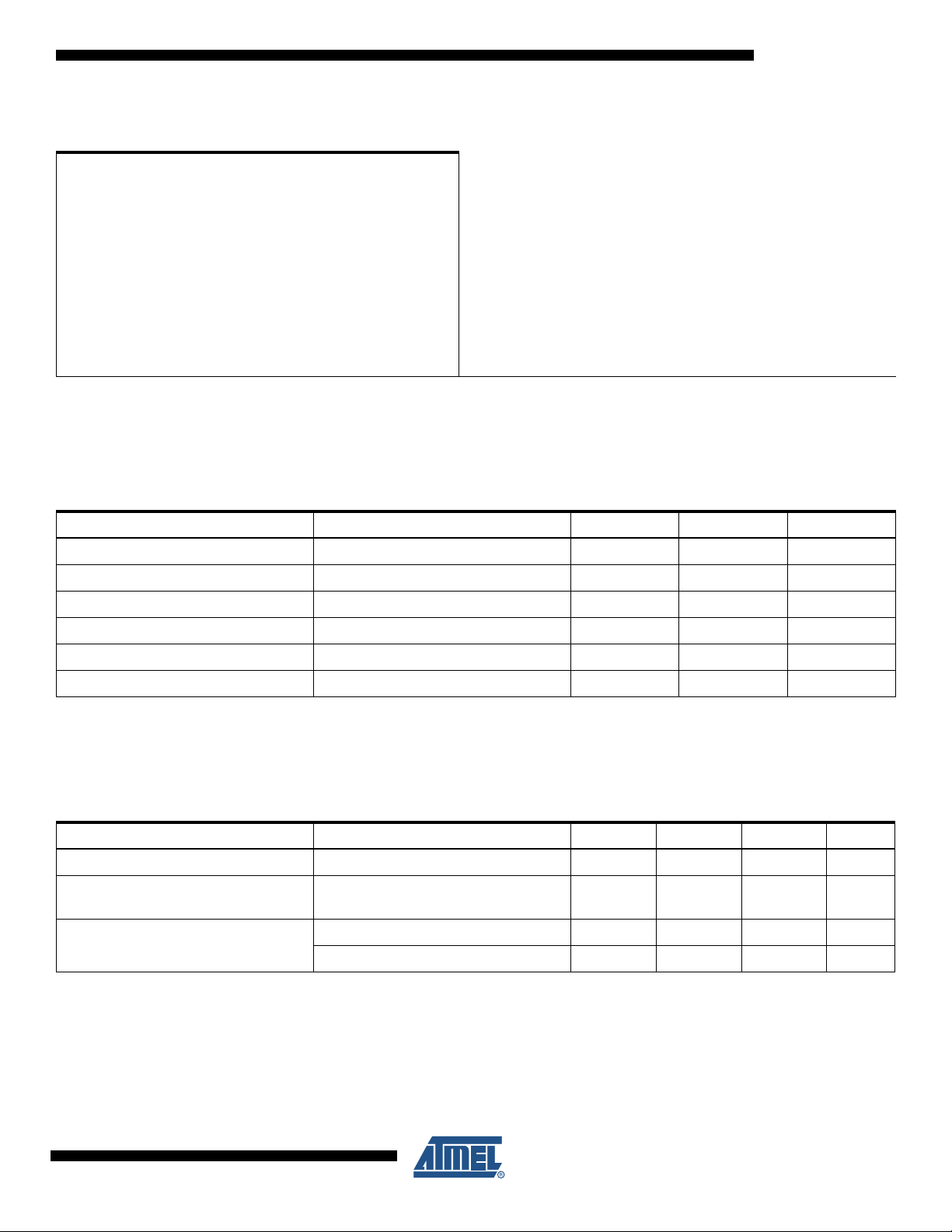

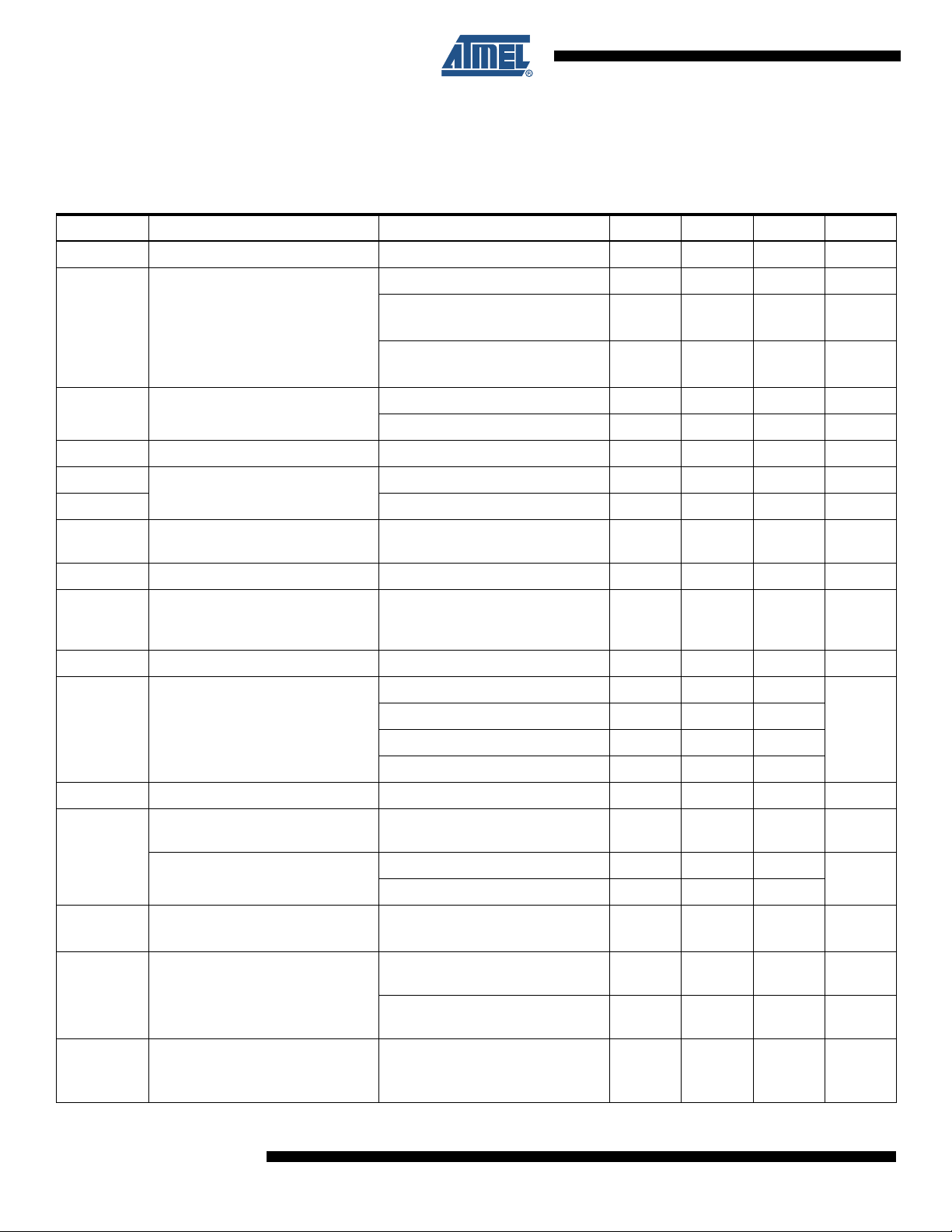

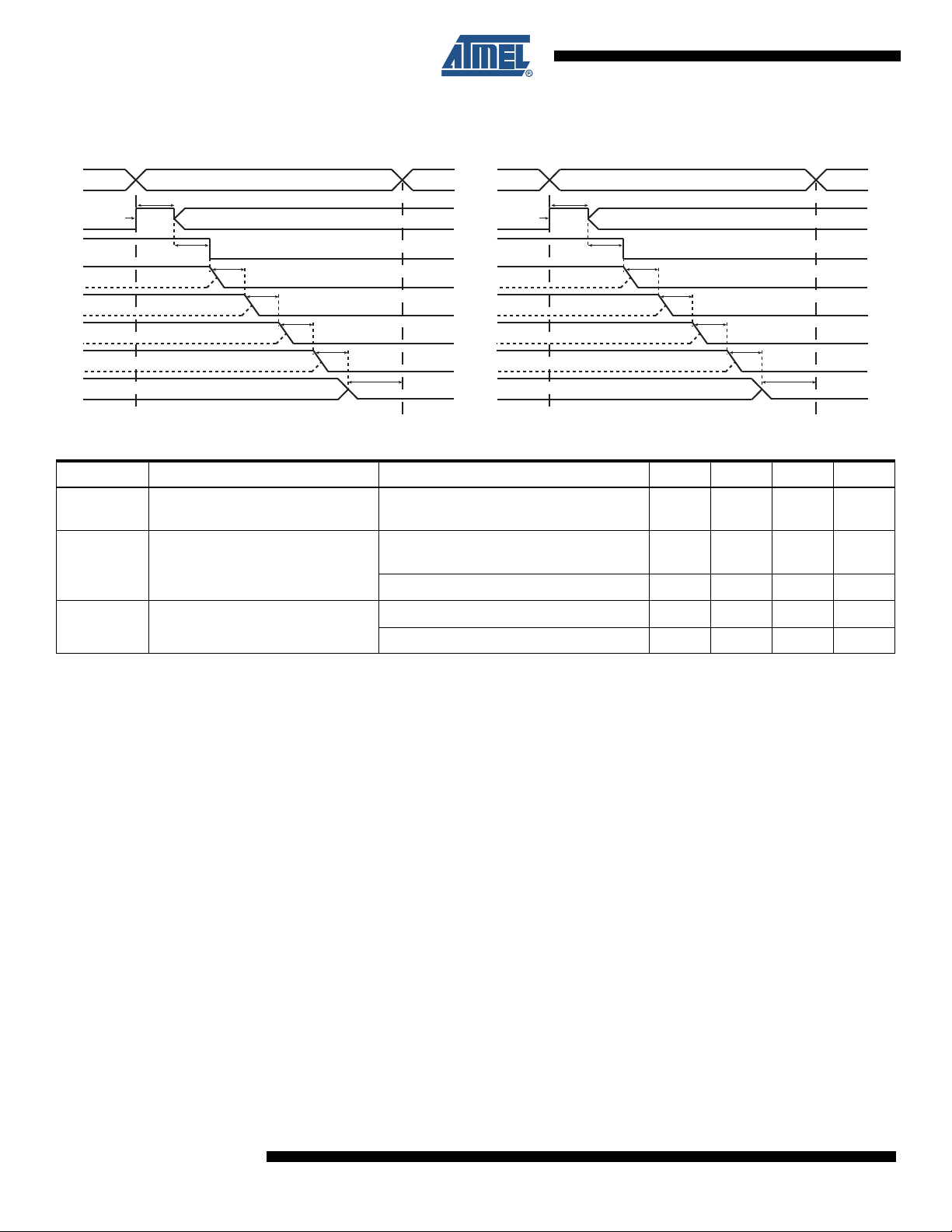

5. Application Block Diagram

1

Figure 5-1. AT73C246 Application Block Diagram

37

1µF

1µF

1µF

1µF

VDD4

I²S

to MCU

3.3µF

C39

3.3µF

C37

3.3µF

C35

3.3µF

C33

C31

C29

C27

C25

AUXL

AUXR

MICL

MICLN

MICR

MICRN

AVDD

MICBIAS

VMID

AGND

HPDET

HPVCM

MCLK

LRFS

BCLK

DAO

XOUT

CLK32K

WAKEUP0

HRST

PWREN

VIN4

LINL

LINR

HPR

36

28

27

30

29

AUDIO IN

34

31

33

32

18

35

12

AUDIO

17

CODEC

13

14

HPL

DAI

XIN

AUDIO OUT

16

15

+DAC

44

43

42

41

40

AUDIO

PORT

63

64

49

62

100K

60

100K

RTC +

61

100K

LINEJACK

J1

AUXJACK

J2

HEADSET 32ohms

J5

LINEOUT

J6

VIN

C42

10µF

VDD4

C41

C40

1nF

C38

1nF

C36

1nF

C34

1nF

R18

2K

PUSHBUTTON

PUSHBUTTON

PUSHBUTTON

10µF

R29

100K

R28

100K

R25

100K

R24

100K

C32

1nF

C30

1nF

C28

1nF

C26

1nF

C23

1µF

C21

3.3µF

R12

100K

X1

S3

S2

S1

100

R30

R31

100

100

R26

R27

100

MIC_L

J3

J4

MIC_R

R22

2K

R23

2K

R19

2K

C22

R14

3.3µF

100

R13

100

100K

R15

C1

9

12

p

C2

0

12p

VBACKUP

VBACKUP

VBACKUP

LDO4

3.3V

Max: 200mA

(CODEC)

+ ADC

BIAS

AUDIO

OSC

VBACKUP

DIGITAL

CORE

BUCK0

1.8V

Max: 600mA

(CORE + MEM)

BUCK1

1.2V

Max: 600mA

(CORE)

LDO2

1V

Max: 300mA

(CORE)

LDO3

3.3V

Max: 200mA

(I/O)

LDO5

2.5V

Max: 10mA

(BACKUP)

LDO6

1.8V / 10mA

(Internal

functions)

PMU

BIAS

PMU STATE

MACHINES

57

VIN0

SW0

VFB0

GND0

VIN1

SW1

VFB1

GND1

VIN2

C6

10µF

VIN3

C8

10µF

C9

2.2µF

VINSYS

C11

2.2µF

REXT

VBG

GNDSYS

RSTB

ITB

WAKEUP1

WAKEUP2

WAKEUP3

VPAD

LED

DGND

L1

2.2µH

L2

2.2µH

VDD0/VDD3

VDD0/VDD3

C2

22µF

C4

22µF

C5

2.2µF

VDD2

C7

10µF

VDD3

VBACKUP

C10

2.2µF

VDDC

C12

22nF

R3

4.7K

C13

10nF

VDD0

VDD1

VDD0

VIN

VINSYS

R2

560k

1%

VDD0/VDD3

From MCU

VIN

D1

R5

470

58

56

59

53

54

52

55

51

50

38

39

1

7

8

10

9

11

20

19

23

100K

24

100K

25

100K

45

2

65

2K

Backup

Battery

R4

4.7K

C14

10nF

VIN

C1

10µF

VIN

C3

10µF

R1

+

BAT

VDD0/VDD3

VDD0/VDD3

DIE TEMP

SENSOR

4MHz RC

OSCILLATOR

SYSTEM

32KHz RC

OSCILLATOR

26 47 48

R6

4.7K

R7

4.7K

DCDC

TWD

TWCK

46

To MCU TWI

NC

R8

ANA_0

ANA_1

ANA_2

ANA_3

100

R9

100

R10

100

R11

100

C15

22nF

C17

22nF

C16

22nF

C18

22nF

ANA0

ANA1

ANA2

ANA3

3

4

5

6

ANALOG

INPUTS

10b SAR

ADC

TWI

22 21

TWDTWCK

8

AT73C246

11050A–PMAAC–07-Apr-10

Page 9

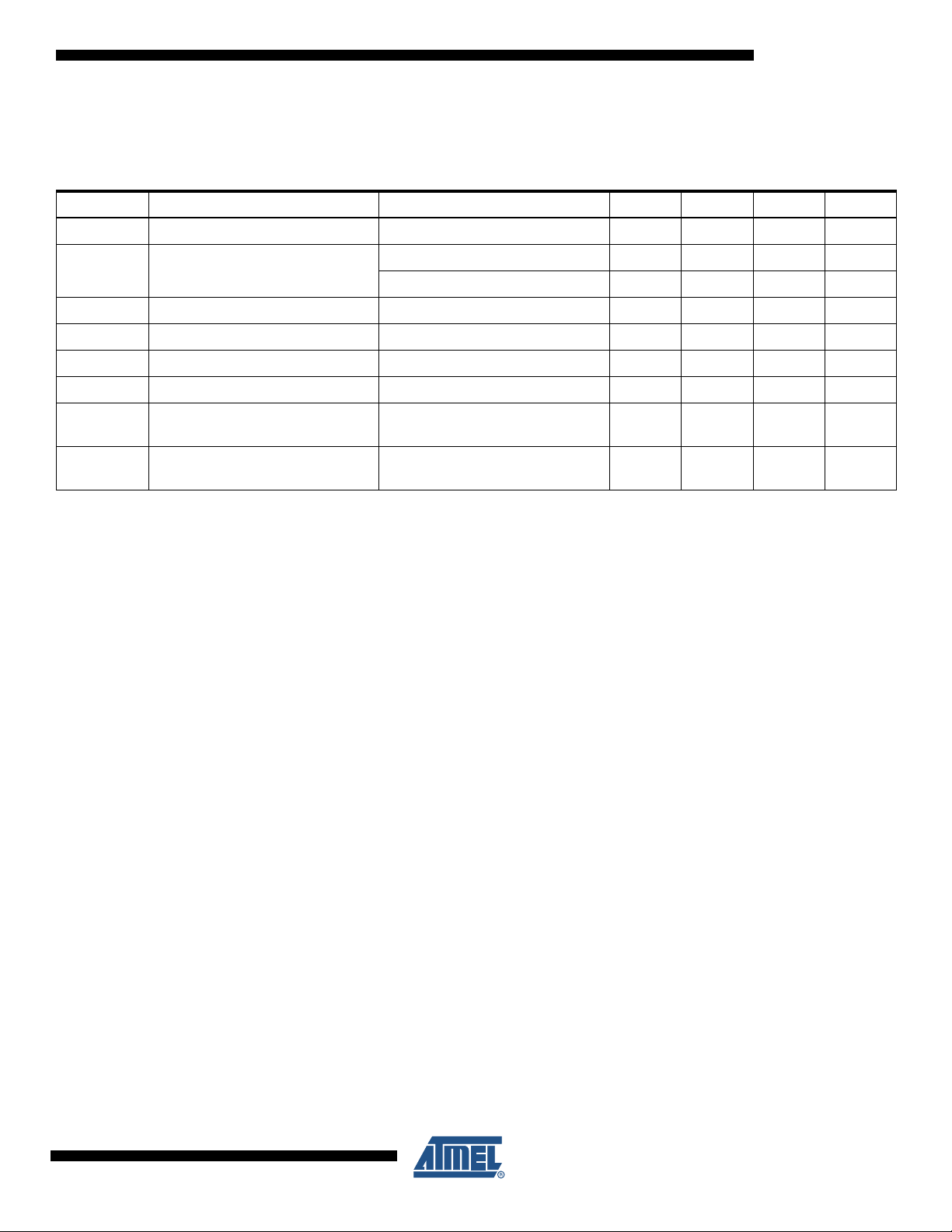

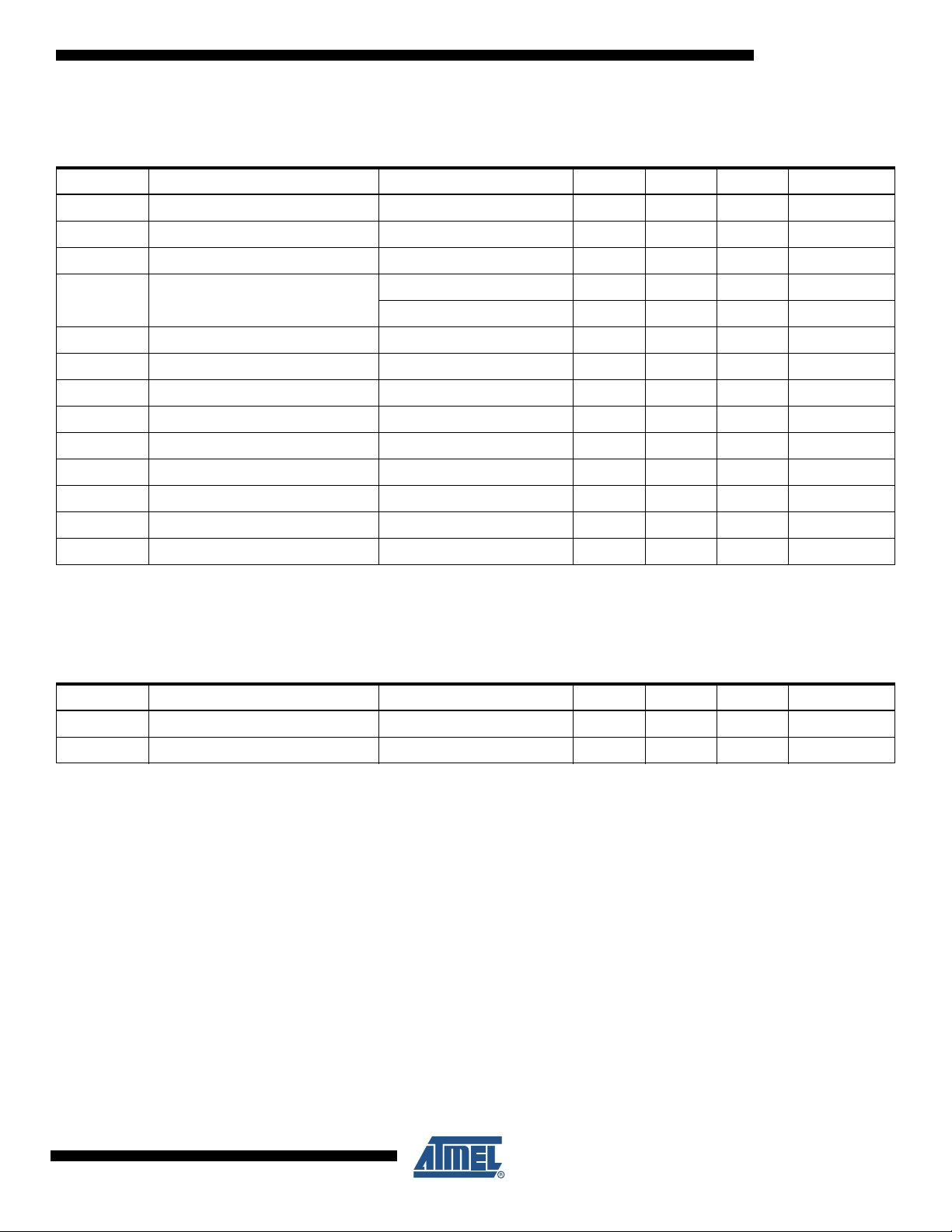

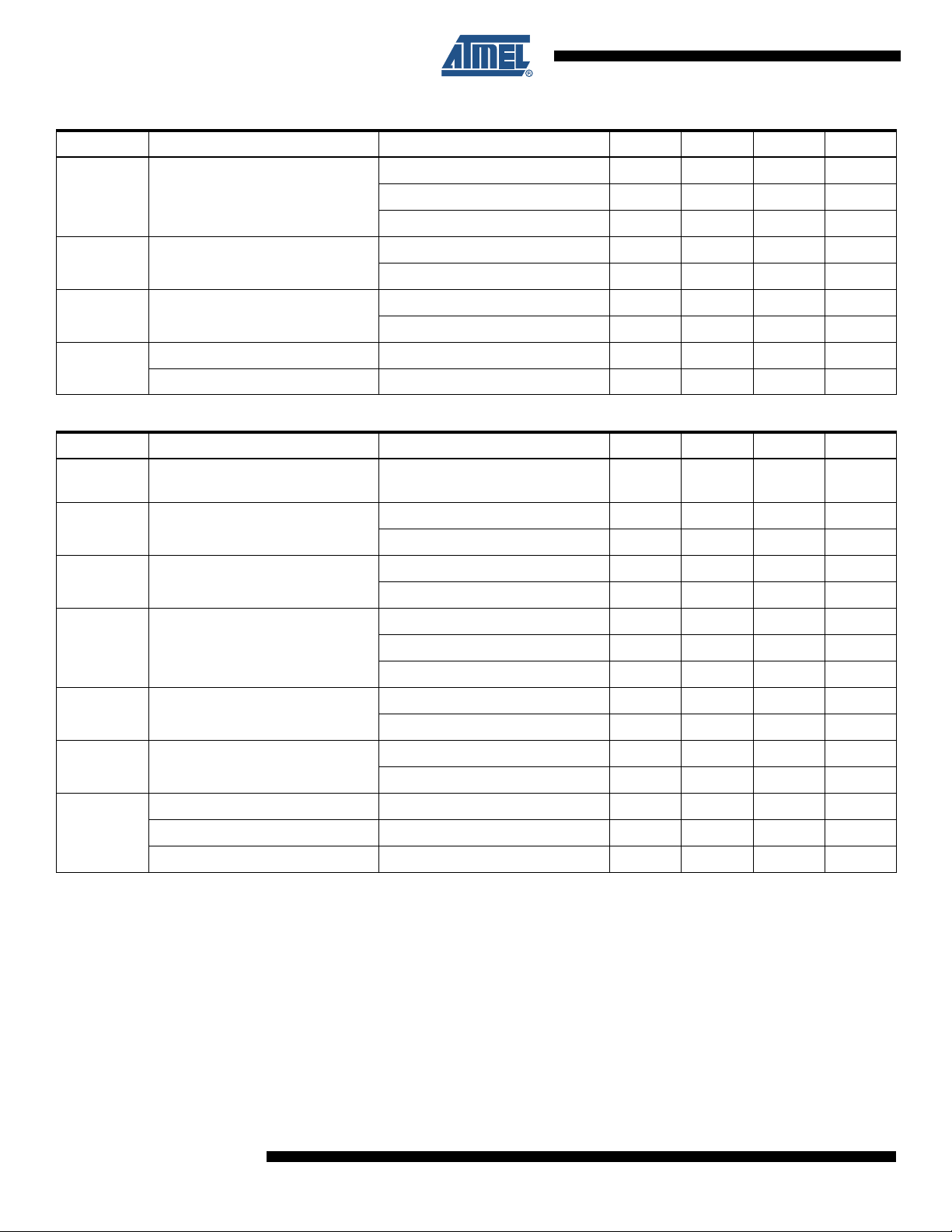

Table 5-1. Typical Application Components Design

Schematic Reference Value Description

R1, R18, R19, R22, R23 2kΩ 5% / 0.063W

R2 560kΩ 1% / 0.063W

R3, R4, R6,R7 4.7kΩ 5% / 0.063W

R5 470Ω 5% / 0.063W

R8, R9, R10, R11, R14, R15,

R26, R27, R30, R31

R12, R13, R24, R25, R28,

R29

100Ω 5% / 0.063W

100kΩ 5% / 0.063W

AT73C246

C1, C3, C6, C7, C8, C10,

C41, C42

C2, C4 22µF

C5, C9, C11 2.2µF X5R / 6.3V

C23, C25, C27, C29, C31 1µF X5R / 6.3V

C13, C14 10nF X5R / 6.3V

C15, C16, C17, C18, C12 22nF X5R / 6.3V

C19, C20 12pF C0G / 25V

C21, C22, C33, C35, C37,

C39

C26, C28, C30, C32, C34,

C36, C38, C40

L1, L2 2.2µH COILCRAFT: LPS3314-222

10µF

3.3µF X5R / 6.3V

1nF X5R

X5R / 6.3V

TDK: C1608X5R0J106MT

MURATA: GRM188R60J106ME47

X5R / 6.3V

TDK: C2012X5R0J226M

MURATA: GRM21BR60J226ME39

11050A–PMAAC–07-Apr-10

9

Page 10

10

AT73C246

11050A–PMAAC–07-Apr-10

Page 11

6. Absolute Maximum Ratings

Table 6-1. Absolute Maximum Ratings

Operating Temperature (Industrial).................-40 C to + 85⋅C

Storage Temperature......................................-55°C to + 150°C

Power Supply Input on V

Power Supply Input on V

INSYS

, A

IN2

, V

IN{0,1,3,4}, VPAD

...................... -0.3V to + 3.6V

VDD

Digital I/O Input Voltage...................................... -0.3V to + 5.5V

All Other Pins.......................................................-0.3V to + 5.5V

.. -0.3V to + 5.5V

AT73C246

(1)

*NOTICE: Stresses beyond those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device.

This is a stress rating only and functional operation of

the device at these or other conditions beyond those

indicated in the operational sections of this specification

is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

ESD (all pins).........................................2 KV HBM / 100V MM

(2)

Notes: 1. Refer to Power Dissipation Rating section

2. According to specifications MIL-883-Method 3015.7 (HBM - Human Body Model) / JESD22 A115 (MM - Machine Model)

7. Recommended Operating Conditions

Table 7-1. Recommended Operating Conditions

Parameter Condition Min Max Units

Operating Ambiant Temperature

Power Supply Input V

Power Supply Input V

Power Supply Input V

Power Supply Input A

Power Supply Input V

Note: 1. Refer to Power Dissipation Rating section

(1)

INSYS

IN{0,1,3,4}

IN2

VDD

PAD

-40 85 °C

2.5 5.5 V

2.9 5.5 V

1.65 3.6 V

2.7 3.6 V

1.75 5.5 V

8. Power Dissipation Ratings

Table 8-1. Recommended Operating Conditions

Parameter Condition Min Typ Max Units

Junction Temperature (Tj) -40 125 °C

(1)

R

THjA

Maximum On-chip Power Dissipation

Note: 1. According to specification JESD51-5

11050A–PMAAC–07-Apr-10

Package thermal junction to ambient

resistance

30 35 °C / W

Ambient temperature = 70°C 1.8 1.6 W

Ambient temperature = 85°C 1.3 1.1 W

11

Page 12

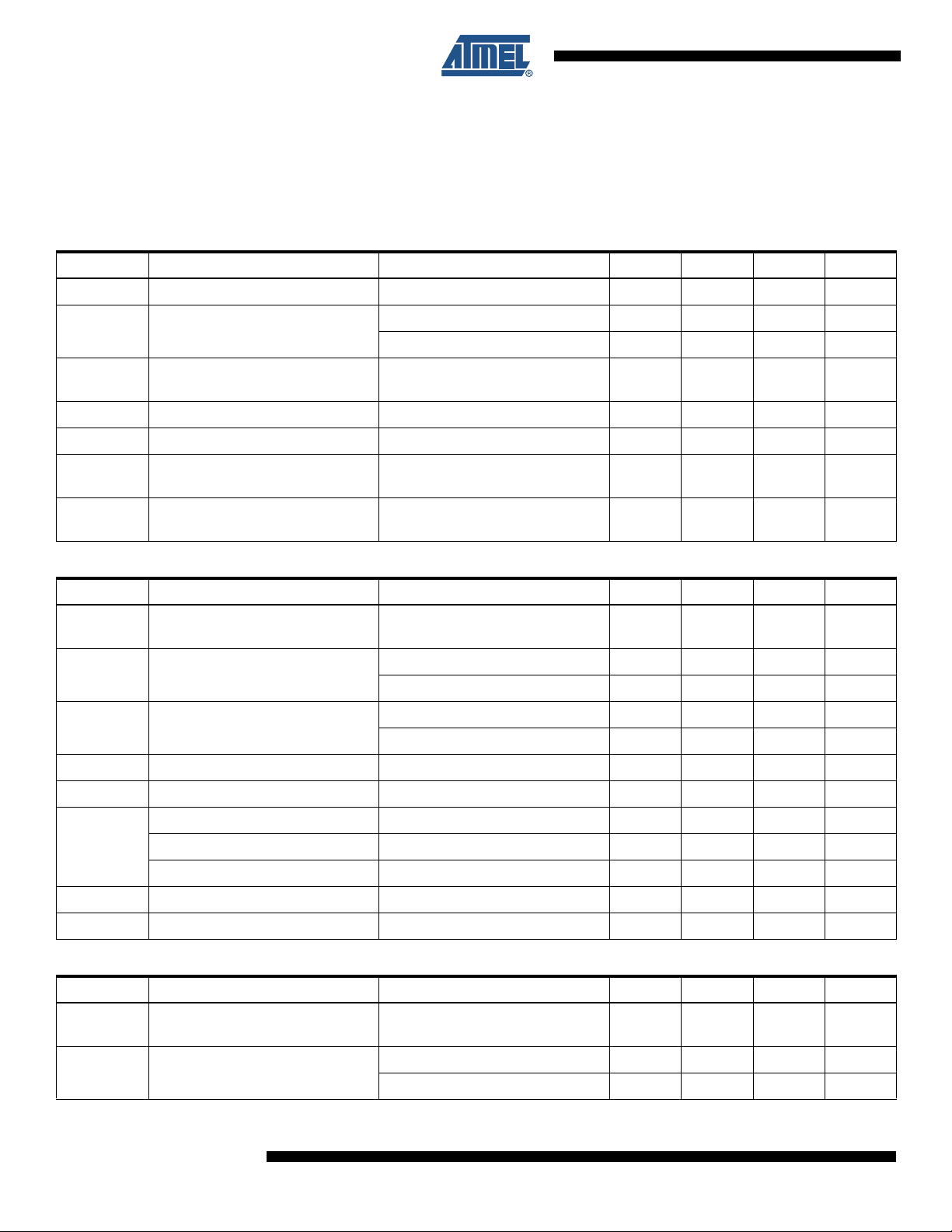

9. PMU Electrical Characteristics

9.1 Current Consumption Versus Modes

Table 9-1. Current Consumption Versus Modes

Symbol Parameter Comments Min Typ Max Units

V

IN

Operating Supply Voltage V

POWERDOWN Mode.

INSYS, VIN{0,1,3,4}

present. 2.9 3.6 5.5 V

All LDOs and DCDC converters

OFF. Audio OFF. RTC running.

-2040µA

All LDOs and DCDC converters

I

DD_VIN

RUN Mode.

running in PWM. Audio OFF. RTC

running.

-715mA

Default setup: DCDC0 ON in low-

STANDBY Mode.

power mode. LDO3 ON. All other

-310500µA

functions OFF.

I

DD_RTC

All Modes.

RTC running. Total current

entering pin V

BACKUP

15µA

9.2 Supply Monitor Thresholds

The following table applies to functional state diagrams of Figure 11-1 “AT73C246 Power Man-

ager Functional State Diagram” on page 25 and Figure 11-2 “AT73C246 Start-up and Shutdown

State Diagram” on page 26.

Table 9-2. Supply Monitor Thresholds

Symbol Parameter Comments Min Typ Max Units

> 3.1V PMU Input 3.1V Rising Threshold 3.070 3.1 3.130 V

V

IN

V

< 2.9V PMU Input 2.9V Falling Threshold 2.870 2.9 2.930 V

IN

> 2.7V PMU Input 2.7V Rising Threshold 2.70 2.75 2.85 V

V

IN

< 2.7V PMU Input 2.7V Falling Threshold 2.60 2.65 2.70 V

V

IN

V

> 1.8V V

BKP

< 1.8V V

V

BKP

Input Rising Threshold 1.80 1.85 1.90 V

BACKUP

Input Falling Threshold 1.70 1.75 1.80 V

BACKUP

12

AT73C246

11050A–PMAAC–07-Apr-10

Page 13

9.3 Digital I/Os DC Characteristics

AT73C246

Table 9-3. V

Referred Digital I/Os

PAD

Symbol Parameter Comments Min Typ Max Units

V

PAD

V

IL

V

IH

V

OH

V

OL

I

O

R

P

Notes: 1. V

Operating Supply Voltage 1.75 3.6 5.5 V

Input Low-Level Voltage -0.3 -

Input High-Level Voltage

Output High-Level Voltage IO max.

0.7 x

V

PAD

0.75 x

V

PAD

-

--V

Output Low-Level Voltage IO max - -

Output Current - - 8 mA

Pull-Up or Pull-Down Resistance When applicable. 70 100 145 kΩ

referred pins ITB, RSTB: open drain outputs. Only VOL and IO parameters are applicable.

PAD

2. V

referred pins WAKEUP1, WAKEUP2, WAKEUP3, MCLK, DAI, TWCK: CMOS inputs. Only VIH and VIL parameters are

PAD

0.3 x

V

PAD

V

PAD

0.3

0.25 x

V

PAD

+

applicable.

3. V

4. V

5. V

referred pins MCLK32K, DAO: CMOS outputs. Only VOL, VOH and IO parameters are applicable.

PAD

referred pin TWD: CMOS input and open drain output. Only VIL, VIH, VOL, IO parameters are applicable.

PAD

referred pins LRFS, BCLK: CMOS BiDir. All parameters applicable

PAD

V

V

V

Table 9-4. V

Referred Digital I/Os

BACKUP

Symbol Parameter Comments Min Typ Max Units

V

BACKUP

V

IL

V

IH

V

OH

V

OL

I

O

R

P

Note: V

Operating Supply Voltage 1.75 2.5 2.65 V

Input Low-Level Voltage -0.3 -

Input High-Level Voltage

Output High-Level Voltage IO max.

0.7 x

V

BACKUP

0.75 x

V

BACKUP

Output Low-Level Voltage IO max - -

-

--V

0.3 x

V

BACKUP

V

BACKUP

+ 0.3

0.25 x

V

BACKUP

Output Current - - 8 mA

Pull-Up or Pull-Down resistance When applicable. 70 100 145 kΩ

referred pins PWREN, HRST, WAKEUP0: CMOS inputs. Only VIL and VIH parameters are applicable.

BACKUP

V

V

V

11050A–PMAAC–07-Apr-10

13

Page 14

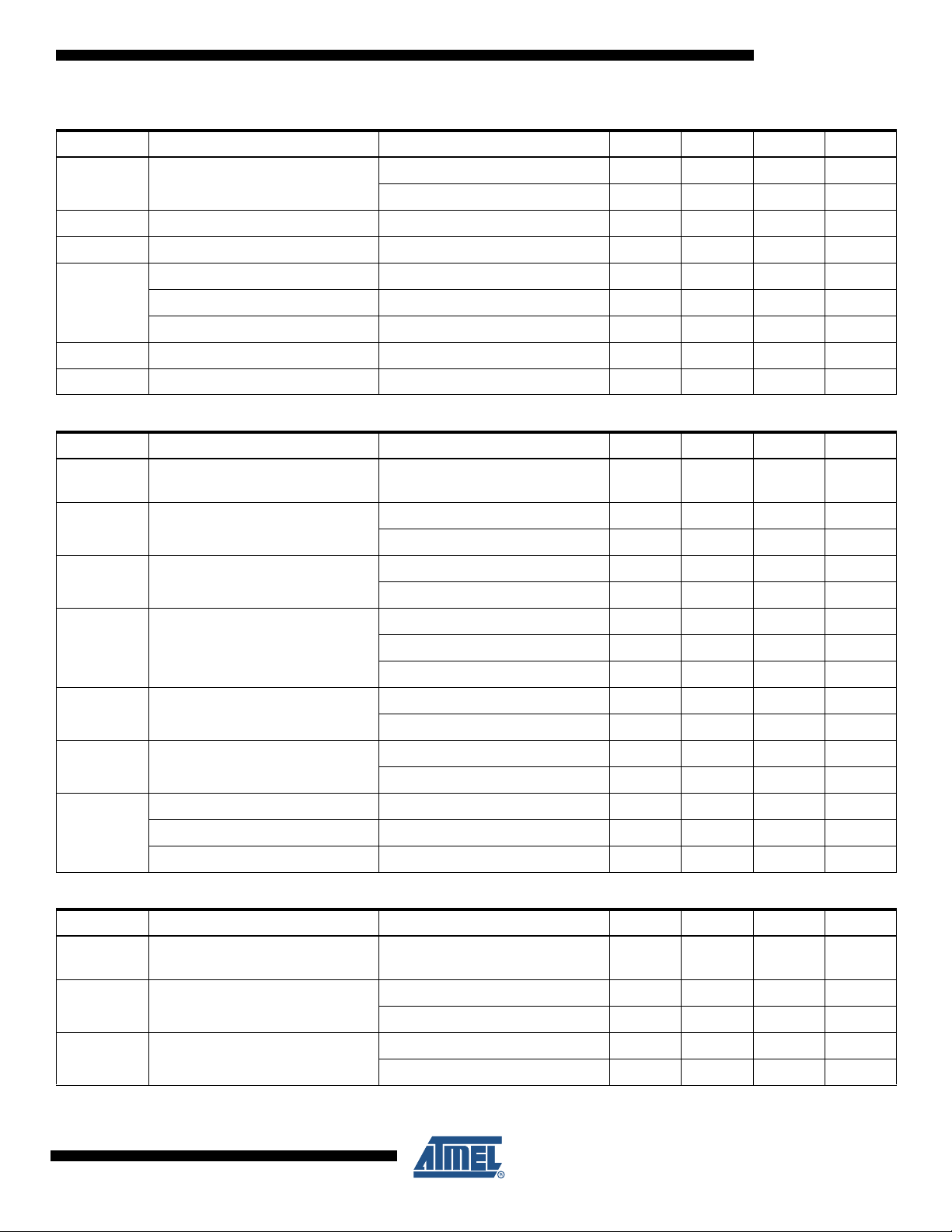

9.4 DCDC0 and DCDC1

Unless otherwise specified: External components L=2.2μH, C

T

= [-40°C ; +125°C].

J

Table 9-5. DCDC0 and DCDC1 Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

V

IN

I

DD

I

O

Operating Supply Voltage V

Supply Current

(1)

Output Current

, V

IN1

and V

IN0

OFF - - 1 µA

PFM operation.

= 1.85V, V

V

DD0

PWM operation.

V

= 1.85V, V

DD0

PFM operation. - - 50 mA

PWM operation. - - 600 mA

=22μF and CIN=10μF. V

OUT

2.9 3.6 5.5 V

INSYS

DD1

DD1

= 1.2V

= 1.2V

-

-

IN{0,1}

> V

DD{0,1}

+ 500mV.

40 80 µA

36.5mA

f

SW

V

DD0

V

DD1

V

DD_RANGE

V

DD_STEP

N

STEP

T

STEP

V

DD_ACC

V

DD_RIPPLE

Switching Frequency PWM operation. 1.8 2 2.2 MHz

Default Output Voltage

Programmable Output Voltage

Range

Output Voltage Steps PFM or PWM operation. 50 mV

Number of Output Steps

Step time With automatic ramping. 260 280 300 µs

DC Output Voltage Accuracy

Ripple Voltage PWM operation. 2 mV

Static Load Regulation

Δ

VDD_IL

Dynamic Load Regulation

Δ

VDD_VIN

Static Line Regulation

Eff Efficiency

I

INRUSH

Inrush Current

V

(2)

DD0

V

DD1

-1.85- V

-1.2- V

PFM or PWM operation. 0.8 3.6 V

In case of direct output voltage

programming. Automatic ramping

4

not active.

PFM; T

PFM; T

PWM; T

PWM; T

PWM operation. I

to I

PWM. IO: 0 to I

PWM. I

V

V

PWM. I

Relative to V

PWM. I

Relative to V

Current from V

(1)

from 0 to 100% V

V

= 25°C ; IO = 0 mA -1.5 2.5

J

= [-40;125°C] ; IO = 0 mA -2 3

J

= 25°C ; IO = 0 mA -1.5 1.5

J

= [-40;125°C] ; IO = 0 mA -2 2

J

ranging from 0

O

OMAX

; 1μs rise time -40

OMAX

: I

O

and V

IN0

= 1.85V, V

DD0

OMAX

OMAX

= 1.85V, V

DD0

to 0 ; 1μs fall time 40

OMAX

from 2.9 to 5.5V

INSYS

= 1.2V

DD1

load. V

input supply.

IN0

load. V

input supply.

IN1

IN(0,1)

DD{0,1}

DD1

= 1.85V.

DD0

= 1.2V.

DD1

and V

= 1.2V

INSYS

25mV

5mV

85 %

78 %

30 200 mA

step /

100µs

%

mV

14

AT73C246

11050A–PMAAC–07-Apr-10

Page 15

AT73C246

Table 9-5. DCDC0 and DCDC1 Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

OCP Over-Current Protection Output current. 1 1.4 1.8 A

T

START

T

PWM

PWRF

C

OUT

DET

Start-up Time

PFM to PWM Settling Time No output load. 10 µs

Power Fail Detector Threshold

Accuracy

Total Capacitive Load At V

Notes: 1. Current consumption without load. One DCDC converter ON, the other one OFF.

2. Default output voltage are set during manufacturing. Please contact Atmel for other default settings.

3. Threshold levels are programmed in register PMU_RST_LVL (0x04)

From OFF to PWM operation.

rising to 95% of final value.

V

DD(0,1)

Overload of the programmed

threshold by 10mV / 5us min

pins. 8 36 µF

FB{0,1}

5ms

(3)

.

-1 - +1 %.V

DD

11050A–PMAAC–07-Apr-10

15

Page 16

9.5 LDO2

Unless otherwise specified: External components C

Table 9-6. LDO2 Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

V

IN

I

DD

I

O

V

DD2

V

DD_RANGE

Operating Supply Voltage V

Supply Current

(1)

Output Current V

Default Output Voltage

(2)

Programmable Output Voltage

Range

OFF - - 1 µA

ON - - 250 µA

=10µF, CIN=10μF, TJ = [-40°C ; +125°C].

OUT

IN2

> V

IN2

+ 500mV. - - 300 mA

DD2

1.65 1.8 3.6 V

-1-V

0.8 1.35 V

V

DD_STEP

T

STEP

V

DD_ACC

Output Voltage Steps 50 mV

Step time With automatic ramping. 570 600 630 µs

DC Output Voltage Accuracy

Static Load Regulation

Δ

VDD_IL

Dynamic Load Regulation

Δ

VDD_VIN

V

DROPOUT

I

INRUSH

T

START

PWRF

DET

Static Line Regulation

Drop Out Voltage

(4)

Inrush Current

Start-up Time

Power Fail Detector Threshold

Accuracy

Notes: 1. Current consumption in V

2. Default output voltage are set during manufacturing. Please contact Atmel for other default settings.

3. Threshold level is programmed in register PMU_RST_LVL (0x04)

4. V

DROPOUT

= V

IN2

- V

when V

DD2

without load.

IN2

= 98% of V

DD2

> V

V

IN2

= 25°C ; IO = 0 mA

T

J

V

IN2

= [-40°C ; 125°C] ; IO = 0 mA

T

J

V

IN2

ranging from 0 to I

I

O

V

IN2

0 to I

I

O:

V

IN2

I

O: IOMAX

I

= 0 mA

O

V

IN2

+ 500mV

DD2

> V

+ 500mV

DD2

> V

+ 500mV

DD2

> V

+ 500mV

DD2

; 1μs rise time

OMAX

> V

+ 500mV

DD2

to 0 ; 1μs fall time

from 1.65 to 3.6V

-1 1

%

-1.5 1.5

0.05 1 %.V

OMAX

-50

mV

50

5mV

IO = 200mA 300 mV

I

= 300mA 450 mV

O

Current from V

final value.

V

OFF and rising to 95% of

DD2

final value. I

Overload of the programmed

threshold by 10mV / 5us min

obtained with V

DD2

from 0 to 95% of

IN2

= 0 mA

O

IN2

> V

(3)

.

DD2

200 500 mA

1ms

-1 - +1 %.V

+ 500mV

DD2

DD2

16

AT73C246

11050A–PMAAC–07-Apr-10

Page 17

AT73C246

9.6 LDO3

Unless otherwise specified: External components C

Table 9-7. LDO3 Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

V

IN

I

DD

I

O

V

DD3

V

DD_RANGE

Operating Supply Voltage V

Supply Current

(1)

Output Current V

Default Output Voltage

(2)

Programmable Output Voltage

Range

=10µF, CIN=10μF, TJ = [-40°C ; +125°C].

OUT

IN3

2.9 3.6 5.5 V

OFF - - 1 µA

ON - - 350 µA

> V

IN3

+ 300mV. - - 200 mA

DD3

-3.3- V

2.7 3.6 V

V

DD_STEP

T

STEP

V

DD_ACC

Output Voltage Steps 50 mV

Step time With automatic ramping. 570 600 630 µs

DC Output Voltage Accuracy

Static Load Regulation

Δ

VDD_IL

Dynamic Load Regulation

Δ

VDD_VIN

V

DROPOUT

Static Line Regulation

Drop Out Voltage

(4)

PSRR Power Supply Rejection Ratio

I

INRUSH

Inrush Current

> V

V

IN3

= 25°C ; IO = 0 mA

T

J

V

IN3

= [-40°C ; 125°C] ; IO = 0 mA

T

J

V

IN3

ranging from 0 to I

I

O

V

IN3

0 to I

I

O:

V

IN3

I

O: IOMAX

V

IN3

V

IN3

+ 300mV

DD3

> V

+ 300mV

DD3

> V

+ 300mV

DD3

> V

+ 300mV

DD3

; 1μs rise time

OMAX

> V

DD3

+ 300mV

to 0 ; 1μs fall time

> V

+ 300mV. IO = 0 mA

DD3

from 2.9 to 5.5V

-1 1

%

-1.5 1.5

0.05 0.5 %.V

OMAX

-40

mV

40

5mV

IO = 10mA 50 mV

I

= 200mA 250 mV

O

V

> V

> V

+ 300mV

DD3

+ 300mV

DD3

from 0 to 95%

IN3

60

dB

50

200 500 mA

IN3

= 1mA. DC to 3kHz.

I

O

V

IN3

= 10mA. DC to 3kHz.

I

O

Current from V

of final value.

DD3

T

START

PWRF

DET

Start-up Time

Power Fail Detector Threshold

Accuracy

Notes: 1. Current consumption in V

2. Default output voltage are set during manufacturing. Please contact Atmel for other default settings.

3. Threshold level is programmed in register PMU_RST_LVL (0x04)

4. V

DROPOUT

11050A–PMAAC–07-Apr-10

= V

IN3

- V

when V

DD3

without load.

IN3

= 98% of V

DD3

V

OFF and rising to 95% of

DD3

final value. I

= 0 mA

O

Overload of the programmed

threshold by 10mV / 5us min

obtained with V

DD3

IN3

> V

(3)

.

DD3

-1 - +1 %.V

+ 300mV

1ms

DD3

17

Page 18

9.7 LDO4

Unless otherwise specified: External components C

Table 9-8. LDO4 Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

V

IN

I

DD

I

O

V

DD4

V

DD_RANGE

Operating Supply Voltage V

Supply Current

(1)

Output Current V

Default Output Voltage

(2)

Programmable Output Voltage

Range

=10µF, CIN=10μF, TJ = [-40°C ; +125°C].

OUT

IN4

2.9 3.6 5.5 V

OFF - - 1 µA

ON - - 350 µA

> V

IN4

+ 300mV. - - 200 mA

DD4

-3.3- V

2.7 3.6 V

V

DD_STEP

T

STEP

V

DD_ACC

Output Voltage Steps 50 mV

Step time With automatic ramping. 570 600 630 µs

DC Output Voltage Accuracy

Static Load Regulation

Δ

VDD_IL

Dynamic Load Regulation

Δ

VDD_VIN

V

DROPOUT

Static Line Regulation

Drop Out Voltage

(3)

PSRR Power Supply Rejection Ratio

I

INRUSH

Inrush Current

> V

V

IN4

= 25°C ; IO = 0 mA

T

J

V

IN4

= [-40°C ; 125°C] ; IO = 0 mA

T

J

V

IN4

ranging from 0 to I

I

O

V

IN4

0 to I

I

O:

V

IN4

I

O: IOMAX

V

IN4

V

IN4

+ 300mV

DD4

> V

+ 300mV

DD4

> V

+ 300mV

DD4

> V

+ 300mV

DD4

; 1μs rise time

OMAX

> V

DD4

+ 300mV

to 0 ; 1μs fall time

> V

+ 300mV. IO = 0 mA

DD4

from 2.9 to 5.5V

-1 1

%

-1.5 1.5

0.05 0.5 %.V

OMAX

-40

mV

40

5mV

IO = 10mA 50 mV

I

= 200mA 250 mV

O

V

> V

> V

+ 300mV

DD4

+ 300mV

DD4

from 0 to 95%

IN4

60

dB

50

200 500 mA

IN4

= 1mA. DC to 3kHz.

I

O

V

IN4

= 10mA. DC to 3kHz.

I

O

Current from V

of final value.

DD4

T

START

Start-up Time

Notes: 1. Current consumption in V

2. Default output voltage are set during manufacturing. Please contact Atmel for other default settings.

18

3. V

DROPOUT

AT73C246

= V

IN4

- V

when V

DD4

without load.

IN4

= 98% of V

DD4

V

OFF and rising to 95% of

DD4

final value. I

DD4

= 0 mA

O

obtained with V

IN4

> V

+ 300mV

DD4

1ms

11050A–PMAAC–07-Apr-10

Page 19

AT73C246

9.8 LDO5

Unless otherwise specified: External components C

Table 9-9. LDO5 Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

V

IN

I

DD

I

O

V

BACKUP

Δ

VDD_VIN

Δ

VDD_VIN

I

INRUSH

T

START

Note: 1. Current consumption in V

Operating Supply Voltage V

Supply Current

(1)

Output Current - - 10 mA

Output Voltage Accuracy 2.42 2.5 2.58 V

Static Line Regulation V

Static Line Regulation V

Inrush Current

Start-up Time

without plugged backup battery

INSYS

=2.2µF, CIN=10μF, TJ = [-40°C ; +125°C].

OUT

INSYS

2.7 3.6 5.5 V

OFF - - 1 µA

ON - - 7 µA

from 2.7 to 5.5V 3 10 mV

INSYS

=3.6V, IO from 0 to I

INSYS

Current from V

T

START(MAX)

V

BACKUP

. V

OFF and rising to 95% of

final value.

INSYS

BACKUP

OMAX

from 0 to

= 2.5V

10 15 mV

180 350 mA

1ms

11050A–PMAAC–07-Apr-10

19

Page 20

9.9 Measurement Bridge and 10-bit ADC

Table 9-10. Measurement Bridge and 10-bit ADC Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

V

IN

I

DD

V

REF

Operating Supply Voltage

Supply Current

Reference Voltage

INL Integral Non Linearity End Point Method -2 - +2 LSB

DNL Differential Non Linearity End Point Method -1 - +1 LSB

Offset Offset Error -2 +2 LSB

GAIN Gain Error -2 +2 LSB

F

S

T

ACQ

V

MEAS

ATT

R

IN_NOM

R

IN_TEMP

C

IN

MEAS

Sampling Rate 300 kS/s

Track and Hold Acquisition Time 500 ns

Measured Input Voltage Range

Measured Input Scaling Factor

ANA{0,1,2,3} Input resistance Tj = 25C 96 120 144 kΩ

RIN deviation with temperature

ANA{0,1,2,3} Input capacitance 15 pF

Notes: 1. The 10-bit ADC is supplied from the regulated V

2. Please refer to Atmel Data Converter Terminology literature

(1)

V

INSYS

2.9 3.6 5.5 V

OFF - - 1 µA

ON - - 2 mA

Internally connected to

VDDC pin.

External inputs ANA{0,1,2,3} 0.4 V

V

DD{0,1,2,3,4}

V

INSYS

inputs 0.4 4 V

input 0.4 5.5 V

1.75 1.8 1.85 V

INSYS

External inputs ANA{0,1,2,3} -1% 0.25 +1% V/V

V

DD{0,1,2,3,4,5}

V

INSYS

T

[-40 ; +25]. Relative to

J

R

IN_NOM

TJ [25 ; 125]. Relative to

R

IN_NOM

inputs -1% 0.4 +1% V/V

input -1% 0.25 +1% V/V

+ 20

-16

voltage (1.8V) which is generated from V

DDC

INSYS

.

V

%

20

AT73C246

11050A–PMAAC–07-Apr-10

Page 21

AT73C246

9.10 RTC Crystal Oscillator

Table 9-11. RTC Crystal Oscillator Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

V

IN

Operating Supply Voltage V

BACKUP

Freq Frequency with crystal - 32.768 - kHz

Duty Duty Cycle 40 50 60 %

I

DD

T

V

V

R

ON

XIN

XOUT

F

Supply Current

(1)

Star tup Time CL= 12pF - 1000 1500 ms

Level Sinus Wave on XIN 250 300 mVpp

Vpp On XOUT 300 mVpp

Internal Resistor between xin and xout 10 MΩ

OFF - - 5 nA

ON - - 1.5 µA

Drift Accuracy @25°C, +/- 20ppm 1.5 mn/month

Esr Equivalent Series Resistance Rs Crystal @ 32.768kHz 50 100 kΩ

C

M

C

SHUNT

C

LOAD

Note: 1. Current consumption in V

Motional Capacitance Crystal @ 32.768kHz 0.6 3 fF

Shunt Capacitance Crystal @ 32.768kHz 0.6 2 pF

Load Capacitance Crystal @ 32.768kHz 6 12.5 pF

with crystal. In case of crystal not present on-board, back-up batteries or supercapacitors,

BACKUP

must be avoided.

1.75 2.5 2.65 V

9.11 Die Temperature Sensor

Table 9-12. Die Temperature Sensor Electrical Characteristics

Symbol Parameter Comments Min Typ Max Units

T

SHUTDOWN

T

RESTART

130°C Shutdown Threshold 135 145 155 °C

110°C Restart Threshold 105 115 125 °C

11050A–PMAAC–07-Apr-10

21

Page 22

10. Audio Codec Electrical Characteristics

Unless otherwise specified: AVDD = 3.3V, TA = 25C, MCLK = 12.288MHz, FS = 48kHz. Master mode and 24-bit operation

2

on I

S port. All gains set to 0dB, audio effects are off. Noise measurements are made in the [20Hz-20kHz] band using the

A-Weighting filter. Distortion measurements are made from the 2

Input sources have an internal impedance of 50 Ohms. Audio Path without mixing capability.

Table 10-1. Audio Codec Bias

Symbol Parameter Comments Min Typ Max Units

AVDD Operating Supply Voltage 2.7 3.3 3.6 V

nd

to the 5th harmonic products of a 997Hz input sinewave.

I

DD

V

MID

T

MID_ON

T

MID_OFF

V

MICBIAS

R

MICBIAS

Supply Current

STANDBY 1 mA

Mid-Supply Reference Voltage -1%

Time to charge V

Time to discharge V

Microphone Bias Reference

Voltage

Microphone Bias Reference

Voltage Internal Resistance

capacitor From 0 to 95% of final value 350 ms/μF

MID

capacitor From 0 to 95% of final value 700 ms/μF

MID

No load. AVDD V

1.5 1.9 2.3 kΩ

AVDD /

2

+1% V

Table 10-2. Line Record Path: Line or Auxiliary Input to ADC Output

Symbol Parameter Comments Min Typ Max Units

OFF 20 µA

V

FS

Full Scale Input Voltage

SNR Signal-to-Noise Ratio

(1)

(2)

Corresponds to 0dBFs digital

output signal.

AVDD = 3.3V 85 96 - dB

AVDD = 2.7V 82 93 - dB

DR Dynamic Range

(3)

AVDD = 3.3V 85 96 - dB

AVDD = 2.7V 82 93 - dB

THD Total Harmonic Distortion -1dBFS digital output - -80 -74 dB

XTALK Left / Right Channel separation

(5)

80 90 - dB

Programmable Gain Range -34 0 12 dB

G

LINE

R

IN

C

IN

Gain Step Size - 1 - dB

Mute Attenuation

(6)

80 - - dB

Input Resistance 5.9 7 8.1 kΩ

Input Capacitance - - 10 pF

AVDD /

3.3

V

RMS

Table 10-3. Microphone Record Path: Microphone Input to ADC Output

Symbol Parameter Comments Min Typ Max Units

V

FS

Full Scale Input Voltage

SNR Signal-to-Noise Ratio

22

AT73C246

(1)

Corresponds to 0dBFs digital

output signal.

(2)

AVDD = 3.3V 85 96 - dB

AVDD = 2.7V 82 93 - dB

AVDD /

3.3

V

11050A–PMAAC–07-Apr-10

RMS

Page 23

AT73C246

Table 10-3. Microphone Record Path: Microphone Input to ADC Output

Symbol Parameter Comments Min Typ Max Units

DR Dynamic Range

(3)

THD Total Harmonic Distortion -1dBFS digital output - -84 -74 dB

XTALK Left / Right Channel separation

Programmable Gain Range 0 - 46 dB

G

LINE

Gain Step Size - 1 - dB

Mute Attenuation

(6)

AVDD = 3.3V 85 96 - dB

AVDD = 2.7V 82 93 - dB

(5)

80 90 - dB

80 - - dB

R

IN

C

IN

Input Resistance 0dB gain 8.4 12 15.6 kΩ

Input Capacitance - - 10 pF

Table 10-4. Playback Path: DAC Input to Headphone Output

Symbol Parameter Comments Min Typ Max Units

V

FS

Full Scale Output Voltage

SNR Signal-to-Noise Ratio

DR Dynamic Range

(3)

(1)

(2)

THD Total Harmonic Distortion

P

O

Output Power

XTALK Left / Right Channel Separation

Programmable Gain Range -77 - +6 dB

G

HS

Gain Step Size - 1 - dB

Mute Attenuation

(6)

0dBFs digital input signal.

AVDD = 3.3V 92 97 - dB

AVDD = 2.7V 89 94 - dB

AVDD = 3.3V 92 97 - dB

AVDD = 2.7V 89 94 - dB

0dBFs input - 10kΩ load - -88 -80 dB

20mW output - 32Ω load - -65 -60 dB

20mW output - 16Ω load - -60 -55 dB

32Ω load - THD < -40dB or 1% 30 mW

16Ω load - THD < -40dB or 1% 50 mW

10kΩ AC coupled load 90 dB

(5)

16Ω DC coupled load 60 dB

80 - - dB

AVDD /

3.3

V

RMS

Table 10-5. Analog Bypass Path: Line / Auxiliary Input to Headphone Output

Symbol Parameter Comments Min Typ Max Units

V

FS

Full Scale Output Voltage

SNR Signal-to-Noise Ratio

DR Dynamic Range

11050A–PMAAC–07-Apr-10

(3)

(1)

(2)

AVDD = 3.3V 92 97 - dB

AVDD = 2.7V 89 94 - dB

AVDD = 3.3V 92 97 - dB

AVDD = 2.7V 89 94 - dB

AVDD /

3.3

V

RMS

23

Page 24

Table 10-5. Analog Bypass Path: Line / Auxiliary Input to Headphone Output

Symbol Parameter Comments Min Typ Max Units

0dBFs input - 10kΩ load - -88 -80 dB

THD Total Harmonic Distortion

P

O

Output Power

XTALK Left / Right Channel Separation

20mW output - 32Ω load - -65 -60 dB

20mW output - 16Ω load - -60 -55 dB

32Ω load - THD < -40dB or 1% 30 mW

16Ω load - THD < -40dB or 1% 50 mW

10kΩ AC coupled load 90 dB

(5)

16Ω DC coupled load 60 dB

G

BYP

Mute Attenuation

(6)

80 - - dB

Table 10-6. Analog Sidetone Path: Microphone Input to Headphone Output

Symbol Parameter Comments Min Typ Max Units

Bypass Gain -1 0 +1 dB

V

FS

Full Scale Output Voltage

SNR Signal-to-Noise Ratio

(1)

(2)

AVDD = 3.3V 92 97 - dB

AVDD = 2.7V 89 94 - dB

DR Dynamic Range

(3)

AVDD = 3.3V 92 97 - dB

AVDD = 2.7V 89 94 - dB

0dBFs input - 10kΩ load - -88 -80 dB

THD Total Harmonic Distortion

20mW output - 32Ω load - -65 -60 dB

20mW output - 16Ω load - -60 -55 dB

32Ω load - THD < -40dB or 1% 30 mW

P

O

XTALK Left / Right Channel Separation

Output Power

16Ω load - THD < -40dB or 1% 50 mW

10kΩ AC coupled load 90 dB

(5)

16Ω DC coupled load 60 dB

Programmable Gain Range -30 - 0 dB

G

SIDETONE

Gain Steps 2.5 3 3.5 dB

Mute Attenuation

(6)

Notes: 1. Full Scale: A linear extrapolation to 0dBFS of the measured level at -10dBFS.

2. Signal-to-Noise Ratio: The ratio of the RMS value of a 997Hz full scale sine wave to the RMS value of output noise with no

signal applied. Device is not muted.

3. Dynamic Range: According to AES17-1991 (Audio Engineering Society) and EIAJ CP-307 (Electronic Industries Association of Japan), an extrapolation to 0dBFS input signal of the THD+N ratio measurement at -60dBFS. As an example, if

THD+N @ -60dBFS = -36dB, then DR = 96dB.

4. Total Harmonic Distortion + Noise Ratio: The ratio of the RMS sum of the noise and the distortion components to the RMS

value of the signal.

5. XTALK: Attenuation measurement from one channel to the other one. Measurement is performed by stimulated one channel

with a 997Hz / -10dBFS sinewave and leaving the other channel unstimulated.

6. Mute Attenuation: Attenuation measurement of a -10dBFS / 997Hz input signal when concerned gain is set to mute.

80 - - dB

AVDD /

3.3

V

RMS

24

AT73C246

11050A–PMAAC–07-Apr-10

Page 25

11. PMU Functional Description

POWERDOWN

(all supplies OFF)

RSTB = 0

HRST

(all supplies OFF)

RSTB = 0

TWI Reset

STANDBY

(selected supplies ON)

RSTB = 0

RUN

(all supplies ON)

RSTB = 1

POWER-OFF or POWER-FAIL

EVENT

POWER-ON EVENT &

Vin > 3.1V

HRST_POWERDOWN

EVENT

HRST_RUN

EVENT

HRST

EVENT

WAKEUP

EVENT

STANDBY

EVENT

HRST

EVENT

HRST

EVENT

STANDBY-OUT or POWER-FAIL

EVENT

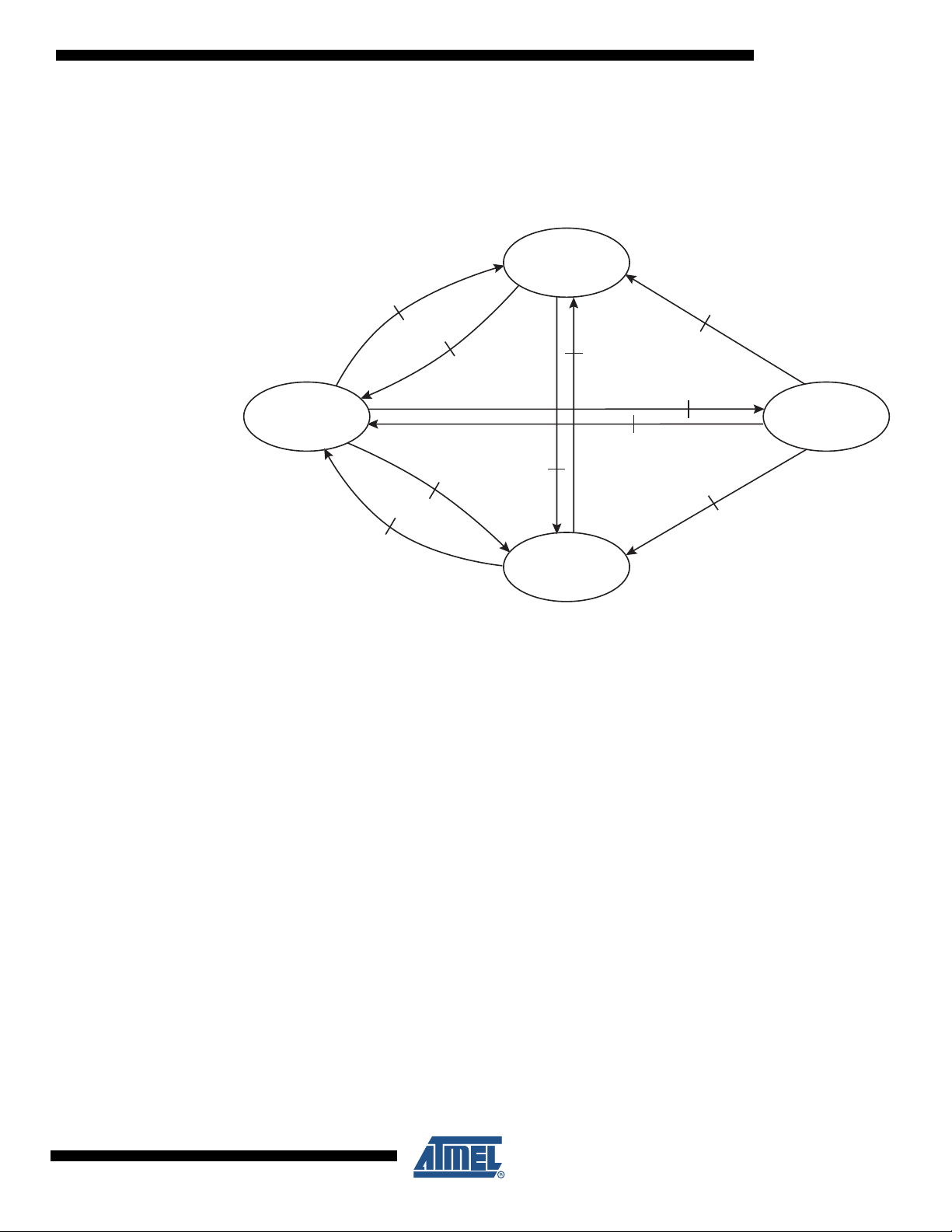

11.1 Power Manager State Diagram

Figure 11-1. AT73C246 Power Manager Functional State Diagram

AT73C246

AT73C246 is placed in POWERDOWN state at VINSYS rising following the PMU startup state

diagram described in Figure 11-2 on page 26. From this POWERDOWN state, normal CPU supplies startup is achieved through validation of one of the POWER-ON events. From this state,

the PMU may be placed in STANDBY state (e.g.: during CPU sleep periods) upon software

request (STANDBY event). PMU wake-up is achieved if one of the WAKEUP events is detected.

The PMU returns to the POWERDOWN state as soon as a POWER-OFF event is detected. A

special HRST (Hard-Reset) state is provided to ensure complete stop and restart of the CPU

supplies in case of a software crash. Moreover, die temperature and VDD

supervised and may generate a POWER-FAIL event in case of out-of-specification detection.

{0,1,2,3}

supplies are

11050A–PMAAC–07-Apr-10

25

Page 26

11.2 PMU Startup and Shutdown State Diagram

Start : V

INSYS

Monitor &

V

DDC

= 1.8V.

PMU_RSTN = 0

AUDIO_RSTN = 0

V

INSYS

< 2.7V

or

V

DDC

_KO

Vin > 2V

VINSYS > 2.7V &

V

DDC

_OK

PMU_RSTN = 1

AUDIO_RSTN = 1

1

READ

CONFIG

V

BACKUP

< 1.8V

RTC_RSTN = 0

1

START

LDO5

(BACKUP)

V

BACKUP

> 1.8V

RTC_RSTN = 1

POWER

DOWN

V

BACKUP

> 1.8V

START

LDO5

(BACKUP)

V

BACKUP

> 1.8V

V

INSYS

< 2.7V

OFF

LDO5

(BACKUP)

1

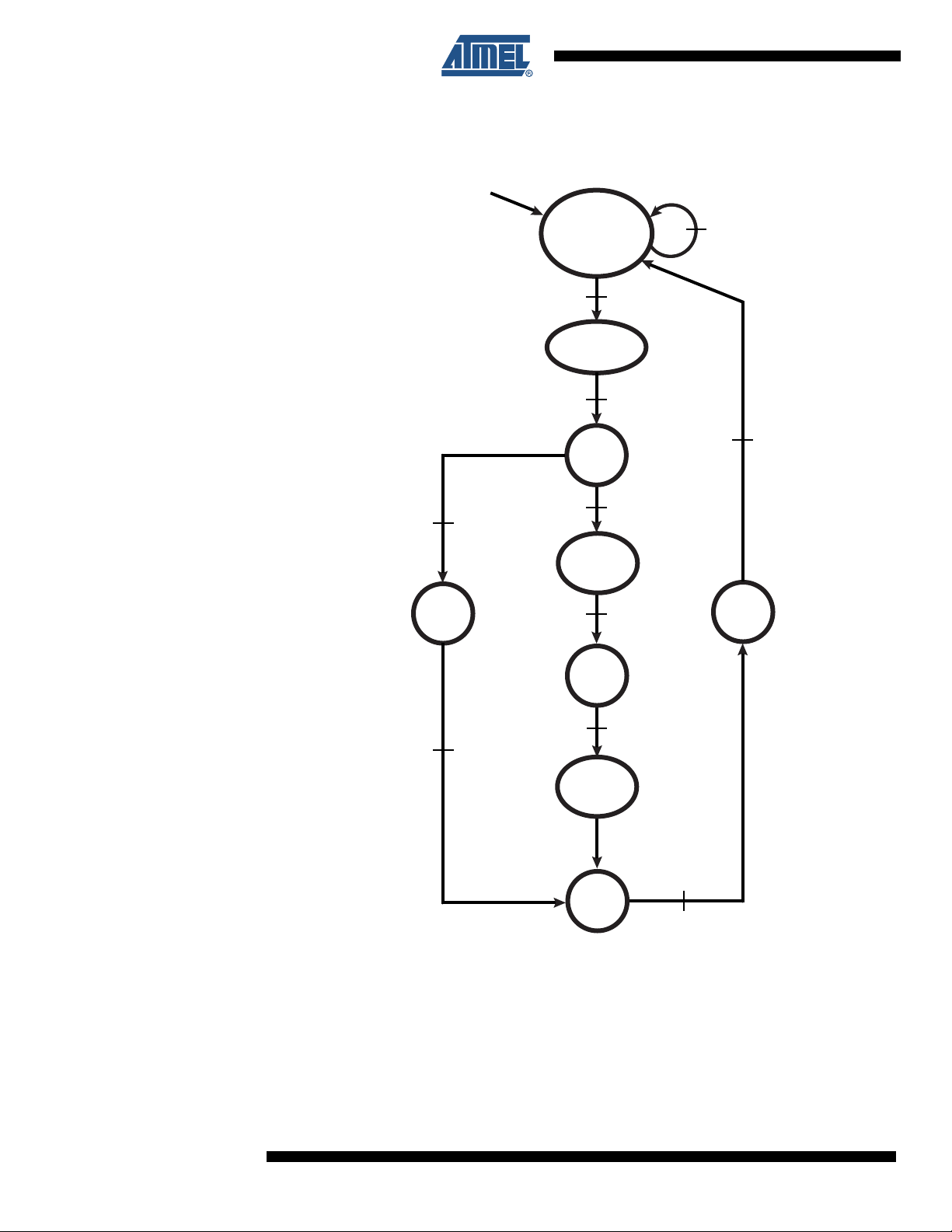

Figure 11-2. AT73C246 Start-up and Shutdown State Diagram

The start-up of the AT73C246 follows the flow diagram of Figure 11-2 and aims at placing the

power manager in the POWERDOWN state.

When V

•An internal V

rises above 2V:

INSYS

INSYS

monitor starts and holds the internal PMU_RSTN and AUDIO_RSTN

signals to 0, thus forcing a complete reset of AT73C246. The PMU digital core supply voltage

26

AT73C246

11050A–PMAAC–07-Apr-10

Page 27

(V

= 1.8V) is started. During this PMU reset, the ‘LED’ pin is driven to VINSYS (LED is

DDC

OFF).

• When V

is ready and V

DDC

INSYS

released, thus enabling the PMU digital core functions.

• Before starting the LDO5 (RTC supply), V

1.8V, the RTC function is resetted. In case of V

function.

• At this step, the power manager is placed in POWERDOWN state.

11.3 Power Manager Conditional Transitions

11.3.1 POWER-ON EVENTS

POWER-ON EVENTS are validated if all these listed conditions are true:

AT73C246

> 2.7V, the internal reset signals previously mentioned are

voltage is monitored and if it is lower than

BACKUP

> 1.8V, no reset is issued on the RTC

BACKUP

•V

INSYS

• AT73C246 internal junction temperature Tj < 110°C

• PWREN pin is high for more than 100ms (see Table 11-1 on page 28).

Note: PWREN pin, with internal 100k pull-down resistor, is active high (V

11.3.2 POWER-OFF EVENTS

POWER-OFF EVENTS are validated if one of these listed conditions is true:

•V

INSYS

• PWREN pin goes from low to high state and high state is held for more than 5s (see Table

11-1 on page 28).

• Software request: bit 0 (OFF) of register 0x00 (PMU_MODES) is written to 1.

11.3.3 POWER-FAIL EVENTS

POWER-FAIL EVENTS are validated if one of these listed conditions is true:

• AT73C246 internal junction temperature Tj > 130°C

• Any internal power fail detection signal coming from any CPU power supply (V

V

DD2

Note: In case of PWREN pin hard wired high (V

> 3.1V

level). It is possible to

hard wire the PWREN pin to V

quently, using the software POWER-OFF EVENT (described in Section 11.3.2) will lead to going

back to the RUN state just after the POWERDOWN STATE.

to always activate RUN state when V

BACKUP

BACKUP

> 3.1V. Conse-

INSYS

< 2.9V.

, V

DD1

,

DD0

, V

) goes from low to high level.

DD3

level), the POWER-FAIL EVENTS will lead to the

POWERDOWN state without possibility to go to the RUN state. The power manager will be able to

reach the RUN state only after an HRST event. This prevents the power manager from oscillating

between RUN and POWERDOWN states in case of permanent failure on CPU supplies.

BACKUP

11.3.4 STANDBY EVENT

STANDBY EVENT is validated if the following condition is true:

• Software request: bit 1 (STANDBY) of register 0x00 (PMU_MODES) is written to 1.

11.3.5 STANDBY-OUT EVENT

STANDBY-OUT EVENT is validated if the following condition is true:

•V

INSYS

11050A–PMAAC–07-Apr-10

< 2.9V.

27

Page 28

11.3.6 WAKEUP EVENTS

WAKEUP EVENTS are validated if one of the listed condition is true:

• WAKEUP0 pin goes from low to high state and WAKEUP0 bit is set to ‘1’ (see Table 11-1) in

• WAKEUP1 pin goes from low to high state and WAKEUP1 bit is set to ‘1’ (see Table 11-1) in

• WAKEUP2 pin goes from low to high state and WAKEUP2 bit is set to ‘1’ (see Table 11-1) in

• WAKEUP3 pin goes from low to high state and WAKEUP3 bit is set to ‘1’ (see Table 11-1) in

• PWREN pin goes from low to high state and high state is held for more than 10ms (see Table

• An RTC alarm occurs and RTC bit is set to ‘1’ in register 0x01 (PMU_WAKEUP_EVENTS).

Notes: 1. WAKEUP0 and PWREN pins must be driven with V

11.3.7 HRST EVENT

HRST EVENT is validated if the following condition is true:

• HRST pin goes from low to high state and high state is held for more than 1s (see Table 11-

register 0x01 (PMU_WAKEUP_EVENTS).

register 0x01 (PMU_WAKEUP_EVENTS).

register 0x01 (PMU_WAKEUP_EVENTS).

register 0x01 (PMU_WAKEUP_EVENTS).

11-1) and PWREN bit is set to ‘1’ in register 0x01 (PMU_WAKEUP_EVENTS).

level, WAKEUP{1,2,3} pins must be

BACKUP

driven with V

2. If any WAKEUP EVENT is triggered while AT73C246 is going from RUN to STANDBY state,

STANDBY state is then first reached before WAKEUP EVENT is taken into account.

PAD

level.

1).

11.3.8 HRST RUN EVENTS

HRST RUN EVENTS are validated if all these listed conditions are true:

• HRST pin is at low level for more than 10ms (see Table 11-1).

•V

INSYS

> 3.1V

• AT73C246 internal junction temperature Tj < 110°C

Note: In case of 110°C < Tj < 130°C, HRST state is maintained. The self cooling down of the die will lead

to Tj < 110°C, thus exit of HRST state.

11.3.9 HRST POWERDOWN EVENTS

HRST POWERDOWN EVENTS are validated if all of these listed conditions are true:

• HRST pin is at low level for more than 10ms.

•V

< 3.1V or AT73C246 internal junction temperature Tj >130°C

INSYS

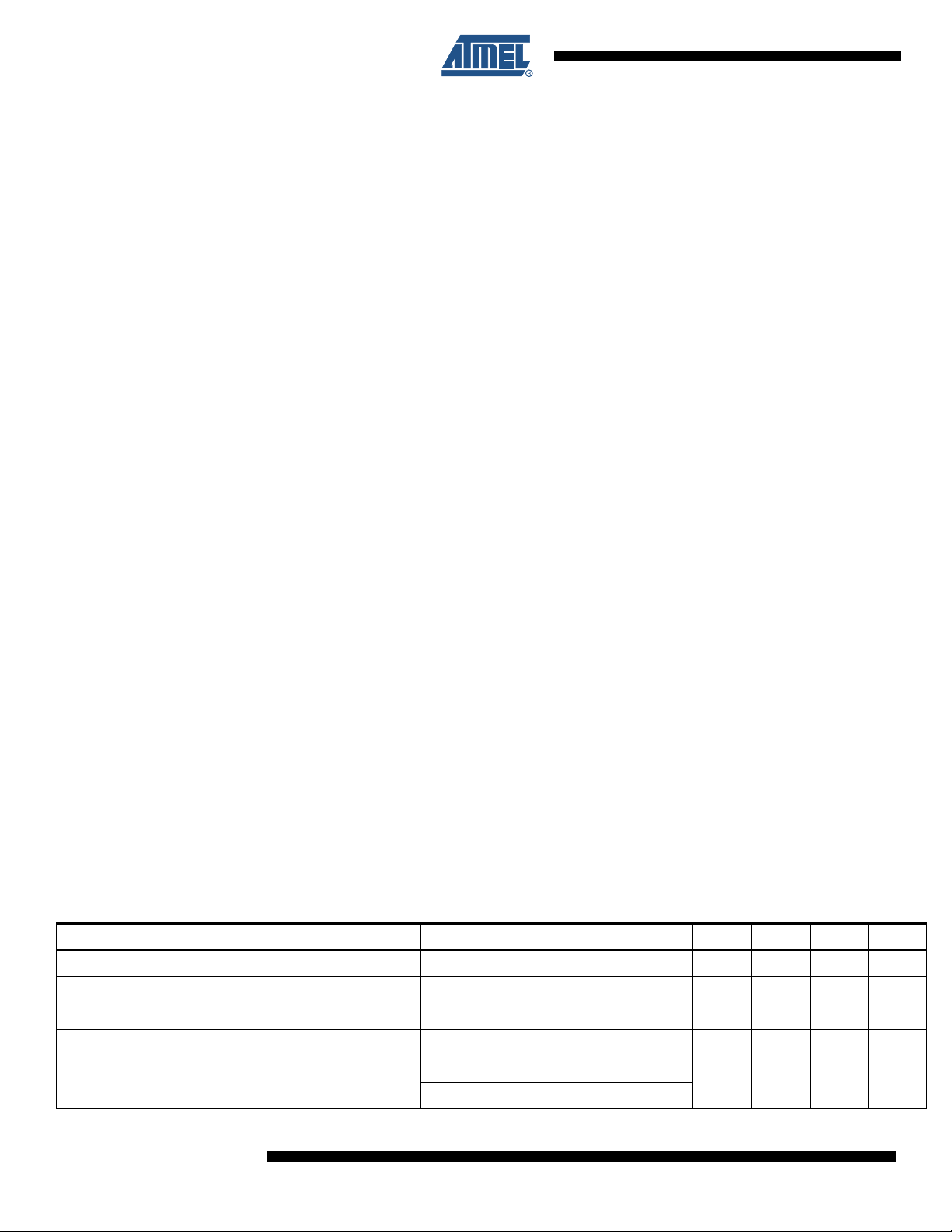

Table 11 - 1 . EVENTS Timing Table

Pin Parameter Comments Min Typ Max Units

PWREN Pin at V

PWREN Pin at V

PWREN Pin at V

HRST Pin at V

HRST Pin at GND Level. Debouncing Time.

Level. Debouncing Time. Pin used as POWER-ON event 95 100 105 ms

BACKUP

Level. Debouncing Time. Pin used as POWER-OFF event 4.75 5 5.25 sec

BACKUP

Level. Debouncing Time. Pin used as WAKEUP event 9.5 10 10.5 ms

BACKUP

Level. Debouncing Time. Pin used as HRST event 0.95 1 1.05 sec

BACKUP

Pin used as HRST RUN event

Pin used as HRST POWERDOWN event

9.5 10 10.5 ms

28

AT73C246

11050A–PMAAC–07-Apr-10

Page 29

AT73C246

Table 11 - 1 . EVENTS Timing Table

Pin Parameter Comments Min Typ Max Units

WAKEUP0 Pin pulsed to V

WAKEUP1 Pin pulsed to V

WAKEUP2 Pin pulsed to V

WAKEUP3 Pin pulsed to V

11.4 Power Manager State Description

AT73C246 ICs are available with 2 factory programmed power sequences. The following timing

diagrams refer to “SEQUENCE A” and “SEQUENCE B” programmed ICs as defined in section

17. “Ordering Information” on page 154. See also the structure of register “VERSION (0x7F)”.

11.4.1 POWERDOWN STATE

When AT73C246 is in POWERDOWN state:

Level. Pulse Width. Pin used as WAKEUP event 5 - - ns

BACKUP

Level. Pulse Width. Pin used as WAKEUP event 5 - - ns

PAD

Level. Pulse Width. Pin used as WAKEUP event 5 - - ns

PAD

Level. Pulse Width. Pin used as WAKEUP event 5 - - ns

PAD

• Only V

supply is active. VDD

BACKUP

{0,1,2,3,4}

power supplies are OFF.

• Audio function is OFF.

• ADC function is OFF.

• RSTB pin is held low.

• Led pin is set as input with internal 120k pull-up resistor to VINSYS.

• TWI registers are reset to default value.

When the POWERDOWN state is reached from the RUN state, the CPU power supplies are

switched off sequentially as described in Figure 11-3 on page 30.

11050A–PMAAC–07-Apr-10

29

Page 30

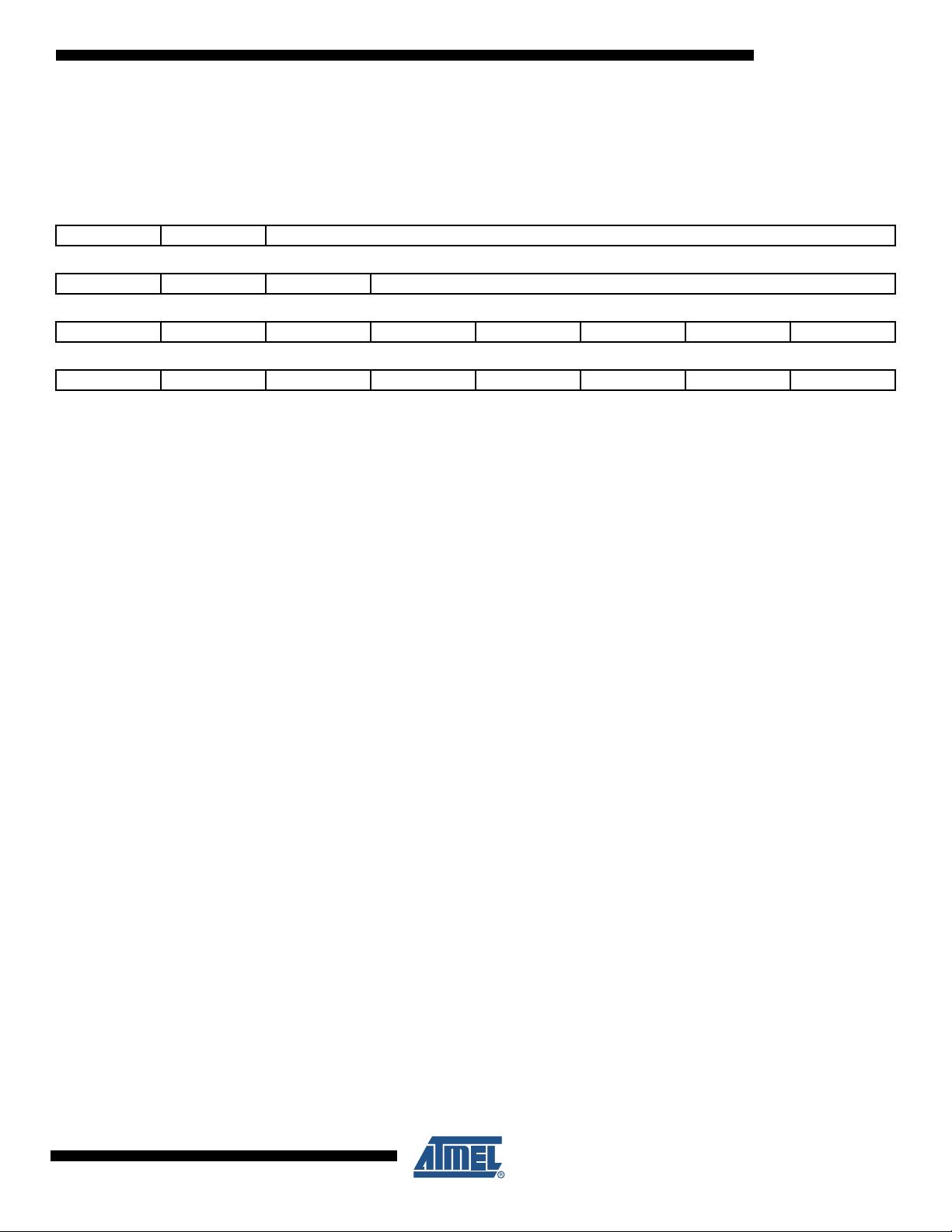

Figure 11-3. AT73C246 - RUN to POWERDOWN state Supplies Shutdown timing diagram.

RUN

STATE

SUPPLIES SHUTDOWN

POWEROFF

EVENT

POWERDOWN

STATE

T

PWRDOWN

T

OFF_AUDIO

T

OFF_VDD3

V

DD3

(3.3V)

V

DD1

(1.2V)

V

DD2

(1V)

3.3V

1.2V

1V

RSTB

V

DD0

(1.85V)

T

OFF_VDD1

T

OFF_VDD0

T

OFF_VDD2

V

DD4

(CODEC)

T

OFF_VDD4

1.85V

RUN

STATE

SUPPLIES SHUTDOWN

POWEROFF

EVENT

POWERDOWN

STATE

T

PWRDOWN

T

OFF_AUDIO

T

OFF_VDD2

V

DD2

(1V)

V

DD1

(1.2V)

V

DD3

(3.3V)

1V

1.2V

3.3V

RSTB

V

DD0

(1.85V)

T

OFF_VDD1

T

OFF_VDD0

T

OFF_VDD3

V

DD4

(CODEC)

T

OFF_VDD4

1.85V

SEQUENCE A SEQUENCE B

Table 11 - 2 . RUN to POWERDOWN state timing table

Symbol Parameter Comments Min Typ Max Units

T

PWRDOWN

POWERDOWN Event detection

time

Audio CODEC is OFF or Power Fail

T

OFF_AUDIO

Audio CODEC Shutdown Time

Occurs

Audio CODEC is ON 486 512 538 ms

VDDx is OFF in RUN state

T

OFF_VDDx

VDDx SHUTDOWN Time

VDDx is ON in RUN state

(1)

Note: 1. VDDx activity during RUN state is set by Bit7 of register VDDx_CTRL.

58 62 66 µs

58 62 66 µs

(1)

58 62 66 µs

4.8 5.2 5.4 ms

30

AT73C246

11050A–PMAAC–07-Apr-10

Page 31

When the POWERDOWN state is reached from the STANDBY state, the CPU power supplies

STANDBY

STATE

SUPPLIES SHUTDOWN

STANDBY_OUT

EVENT

POWERDOWN

STATE

T

STBY_OUT

T

OFF_VDD2

V

DD2

(1V)

V

DD0

(1.85V)

V

DD3

(3.3V)

1V

1.2V

RSTB

V

DD1

(1.2V)

T

OFF_VDD1

1.85V

T

OFF_VDD0

3.3V

T

OFF_VDD3

V

DD4

(CODEC)

T

OFF_VDD4

STANDBY

STATE

SUPPLIES SHUTDOWN

STANDBY_OUT

EVENT

POWERDOWN

STATE

T

STBY_OUT

T

OFF_VDD3

V

DD3

(3.3V)

V

DD0

(1.85V)

V

DD2

(1V)

3.3V

1.2V

RSTB

V

DD1

(1.2V)

T

OFF_VDD1

1.85V

T

OFF_VDD0

1V

T

OFF_VDD2

V

DD4

(CODEC)

T

OFF_VDD4

SEQUENCE A SEQUENCE B

are switched off sequentially as described in Figure 11-4.

Figure 11-4. AT73C246 - STANDBY to POWERDOWN state Supplies Shutdown timing diagram.

Table 11 - 3 . STANDBY to POWERDOWN state timing table

AT73C246

Symbol Parameter Comments Min Typ Max Units

T

STBY_OUT

T

OFF_VDDx

T

OFF_VDD4

STANDBY OUT Event

detection time

VDDx SHUTDOWN Time

VDD4 SHUTDOWN Time

VDDx is OFF during STANDBY state

VDDx is ON during STANDBY state

VDD4 is OFF in RUN state

VDD4 is ON in RUN state

(2)

(2)

(1)

(1)

95 100 105 µs

58 62 66 µs

4.8 5.2 5.4 ms

58 62 66 µs

4.8 5.2 5.4 ms

Notes: 1. VDDx activity during STANDBY state is set by register PMU_STANDBY_SUPPLIES.

2. VDD4 activity during RUN state is set by Bit7 of register VDD4_CTRL.

11.4.2 RUN STATE

When AT73C246 is in RUN state:

•VDD

{0,1,2,3,5}

power supplies are ON.

• RSTB pin is released.

• PMU functions are under software control (LDO4, AUDIO CODEC, ADC Controller)

• Led pin is driven according to register PMU_LED (0x0B).

11050A–PMAAC–07-Apr-10

31

Page 32

When RUN state is reached from the POWERDOWN state, the power supplies are sequentially

POWERDOWN

STATE

SUPPLIES START UP

T

ON_SYS

RUN STATE

VDD3 (3.3V)

T

ON_VDD3

VDD0 (1.85V)

T

ON_VDD0

VDD1 (1.2V)

TON_VDD1

VDD2 (1V)

3.3V

1.85V

1.2V

1V

T

ON_VDD2

RSTB

VPAD LEVEL

T

RESET

PWREN

EVENT

SEQUENCE A SEQUENCE B

POWERDOWN

STATE

SUPPLIES START UP

T

ON_SYS

RUN STATE

VDD2 (1V)

T

ON_VDD2

VDD0 (1.85V)

T

ON_VDD0

VDD1 (1.2V)

TON_VDD1

VDD3 (3.3V)

1V

1.85V

1.2V

3.3V

TON_VDD3

RSTB

VPAD LEVEL

T

RESET

PWREN

EVENT

started-up according to the Figure 11-5

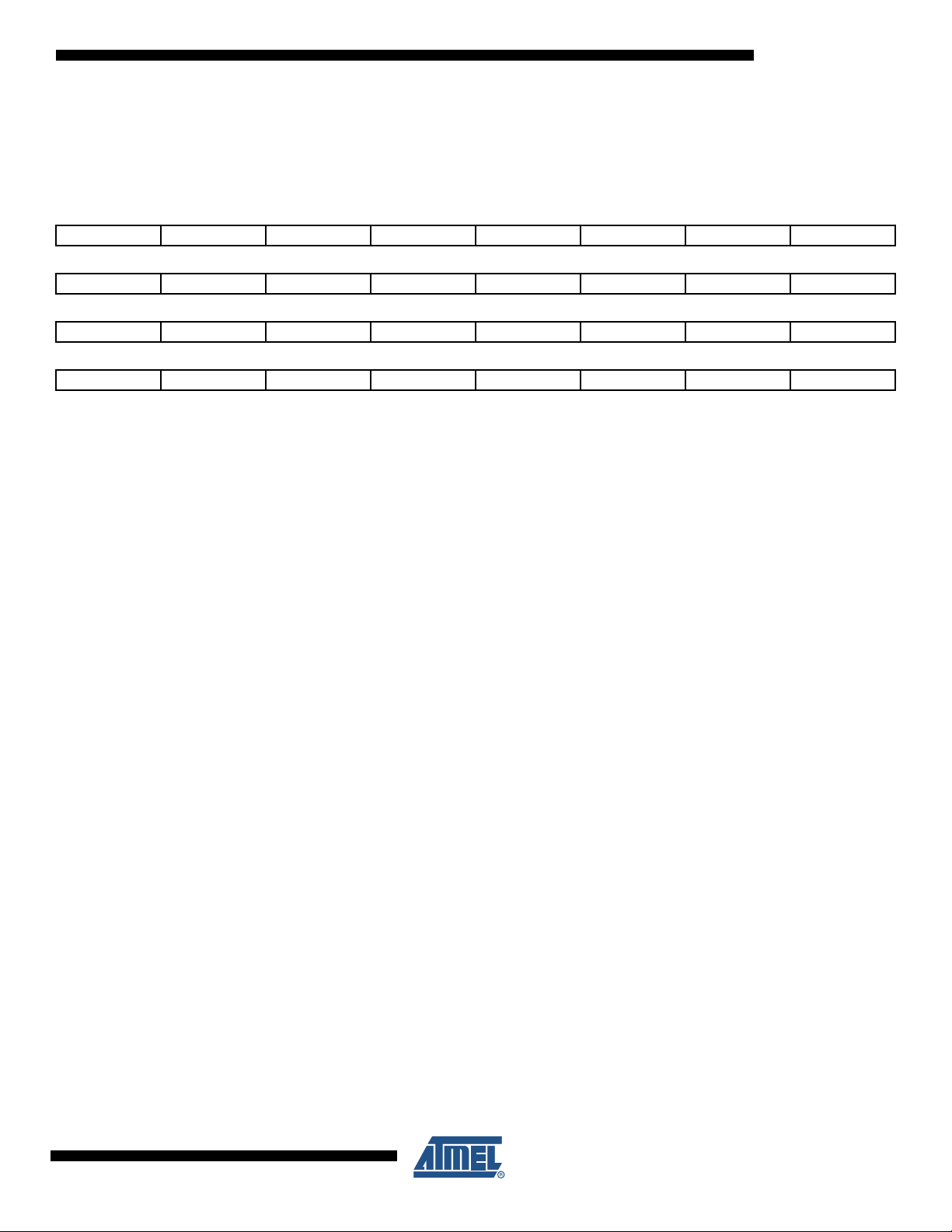

Figure 11-5. AT73C246 - POWERDOWN to RUN state Supplies Start-Up timing diagram..

Table 11 - 4 . POWERDOWN to RUN state timing table

Symbol Parameter Comments Min Typ Max Units

T

ON_SYS

T

ON_VDD0

T

ON_VDD1

T

ON_VDD2

T

ON_VDD3

T

RESET

POWER-ON Event Detection Time 1.7 1.8 1.9 ms

VDD0 Start-up Time 5 5.3 5.6 ms

VDD1 Start-up Time 5 5.3 5.6 ms

VDD2 Start-up Time 5.2 5.5 5.8 ms

VDD3 Start-up Time 5.2 5.5 5.8 ms

All Regulators ON To RSTB High 30.4 32 33.6 ms

32

AT73C246

11050A–PMAAC–07-Apr-10

Page 33

When RUN state is reached from the STANDBY state, the power supplies are sequentially

SEQUENCE A SEQUENCE B

STANDBY

STAT E

SUPPLIES START UP

TON_SYS

RUN STATE

WAKEUP

EVENT

V

DD3

(3.3V)

TON_VDD3

TON_VDD0

TON_VDD1

V

DD2

(1V)

3.3V

1.85V

1.2V

1V

TON_VDD2

RSTB

VPAD LEVEL

TRESET

V

DD3

ON

or OFF

STANDBY

STAT E

SUPPLIES START UP

TON_SYS

RUN STATE

WAKEUP

EVENT

V

DD2

(1V)

TON_VDD2

TON_VDD0

TON_VDD1

V

DD3

(3.3V)

1V

1.85V

1.2V

3.3V

TON_VDD3

RSTB

VPAD LEVEL

TRESET

V

DD3

ON

or OFF

V

DD0

(1.85V)

V

DD1

(1.2V)

PFM

TPFM

PFM

V

DD0

(1.85V)

V

DD1

(1.2V)

PFM

TPFM

PFM

PWM

V

DD0

PWM

V

DD1

PWM

V

DD0

PWM

V

DD1

started-up according to the Figure 11-6.

Figure 11-6. AT73C246 - STANDBY to RUN state Supplies Start-Up timing diagram.

Table 11 - 5 . STANDBY to RUN state timing table

AT73C246

Symbol Parameter Comments Min Typ Max Units

T

ON_SYS

T

PFM

T

ON_VDDx

T

RESET

Start-up Time

PFM/PWM Switching

time

VDDx Start-up Time

All Regulators ON To

RSTB High

Time from validated WAKEUP event (end of debounce

time when applicable) to VDD2 or VDD3 power on.

Time from validated WAKEUP event (end of debounce

time when applicable) to PFM/PWM switching if

applicable.

VDDx is OFF during STANDBY state

VDDx is ON during STANDBY state

(1)

(1)

Note: 1. VDDx activity during STANDBY state is set by register PMU_STANDBY_SUPPLIES.

11.4.3 STANDBY STATE

When AT73C246 is in STANDBY state:

•V

BACKUP

•VDD

is ON.

are ON or OFF according to the status in register 0x03

{0,1,2,3}

(PMU_STANDBY_SUPPLIES)

•VDD

is ON or OFF according to the status in register 0x0A (VDD4_CTRL)

4

• Audio function is OFF

• ADC function is ON or OFF according to the status in register 0x30 (ADC_CTRL)

• RSTB pin is forced to ground.

• TWI pins are ignored to prevent TWI registers from corruption

• Led pin is driven according to register PMU_LED (0x0B)

To reach the STANDBY state, the appropriate power supplies are shut down as described in the

Figure 11-7 on page 34.

11050A–PMAAC–07-Apr-10

810 900 990 µs

420 470 520 µs

5.2 5.4 5.7 ms

58 62 66 µs

30.4 32 33.6 ms

33

Page 34

Figure 11-7. AT73C246 - RUN to STANDBY state Supplies Shutdown timing diagram.

RUN

STATE

SUPPLIES SHUTDOWN

STANDBY

EVENT

STANDBY

STATE

T

STANDBY

T

OFF_AUDIO

T

OFF_VDD2

T

WAIT +

V

DD2

(1V)

V

DD3

(3.3V)

1V

1.2V

1.85V

3.3V

RSTB

T

OFF_VDD1

T

OFF_VDD0

T

OFF_VDD3

1.85V

(V

DD3

ON

or OFF

)

SEQUENCE A SEQUENCE B

RUN

STAT E

SUPPLIES SHUTDOWN

STANDBY

EVENT

STANDBY

STATE

T

STANDBY

T

OFF_AUDIO

T

OFF_VDD3

T

WAIT +

V

DD3

(3.3V)

V

DD2

(1V)

3.3V

1.2V

1.85V

1V

RSTB

T

OFF_VDD1

T

OFF_VDD0

T

OFF_VDD2

1.85V

(V

DD3

ON

or OFF

)

V

DD1

(1.2V)

V

DD0

(1.85V)

TPWM

PWM

PWM

V

DD1

(1.2V)

V

DD0

(1.85V)

TPWM

PWM

PWM

PFM

V

DD0

PFM

V

DD1

PFM

V

DD0

PFM

V

DD1

Table 11 - 6 . RUN to STANDBY state timing table

Symbol Parameter Comments Min Typ Max Units

T

STANDBY

T

PWM

T

WAIT

T

OFF_AUDIO

T

OFF_VDDx

T

ON_VDDx

STANDBY Event

Detection Time

PFM/PWM Switching

time

WAKEUP Event

Detection Window

Audio CODEC

Shutdown Time

VDDx SHUTDOWN

Time

VDDx STARTUP Time

Time from validated WAKEUP event (end of debounce

time when applicable) to PFM/PWM switching if

applicable.

If a WAKEUP event occurs in this window the PMU

automatically restart at the end of the STANDBY

process.

Audio CODEC is ON 486 512 538 ms

Audio CODEC is OFF 58 62 66 µs

VDDx is OFF during both STANBY

VDDx is OFF during STANBY state

VDDx is ON during RUN state

(2)

.

VDDx is ON during STANBY state

VDDx is OFF during RUN state

(2)

.

VDDx is ON during both STANBY

(1)

and RUN

(1)

.

(1)

.

(1)

and RUN

(2)

states. 58 62 66 µs

(2)

states. 58 62 66 µs

Note: 1. VDDx activity during STANDBY state is set by register PMU_STANDBY_SUPPLIES.

2. VDDx activity during RUN state is set by Bit7 of register VDDx_CTRL.

11.4.4 HRST STATE

HRST state is a transition state used to restart the CPU:

150 160 170 µs

460 500 540 µs

150 160 170 µs

4.8 5.2 5.4 ms

4.8 5.2 5.4 ms

34

•VDD

{0,1,2,3,4}

are switched off according to figure Figure 11-8 on page 35 depending on the

previous state

AT73C246

•VDD

• RSTB pin is forced to ground

is ON

5

11050A–PMAAC–07-Apr-10

Page 35

AT73C246

RUN / STANDBY /

POWERDOWN

STAT E

SUPPLIES SHUTDOWN

HRST_EVENT

EVENT

HRST

STATE

T

HRST

T

OFF_VDD3

T

OFF_AUDIO

V

DD3

(3.3V)

V

DD1

(1.2V)

V

DD2

(1V)

3.3V

1.2V

1.85V

1V

RSTB

V

DD0

(1.85V)

T

OFF_VDD1

T

OFF_VDD0

T

OFF_VDD2

PMU FUNCTIONS

(LDO4, ADC, LED,...)

T

OFF_PMU

RUN / STANDBY /

POWERDOWN

STATE

SUPPLIES SHUTDOWN

HRST_EVENT

EVENT

HRST

STATE

T

HRST

T

OFF_VDD2

T

OFF_AUDIO

V

DD2

(1V)

V

DD1

(1.2V)

V

DD3

(3.3V)

1V

1.2V

1.85V

3.3V

RSTB

V

DD0

(1.85V)

T

OFF_VDD1

T

OFF_VDD0

T

OFF_VDD3

PMU FUNCTIONS

(LDO4, ADC, LED,...)

T

OFF_PMU

SEQUENCE A SEQUENCE B

Figure 11-8. AT73C246 - HRST state Supplies Shutdown timing diagram.

Table 11 - 7 . HRST state timing table from RUN STATE

Symbol Parameter Comments Min Typ Max Units

T

HRST

T

OFF_AUDIO

T

OFF_VDDx

T

OFF_PMU

HRST Event Detection Time 58 62 66 µs

Audio CODEC is ON 486 512 538 ms

Audio CODEC Shutdown Time

Audio CODEC is OFF 58 62 66 µs

VDDx SHUTDOWN Time

VDDx is OFF in RUN state

VDDx is ON in RUN state

(1)

(1)

58 62 66 µs

4.8 5.2 5.4 ms

PMU Functions Shutdown Time 1.4 1.5 1.6 ms

Note: 1. VDDx activity during RUN state is set by Bit7 of register VDDx_CTRL

Table 11 - 8 . HRST state timing table from STANDBY STATE

Symbol Parameter Comments Min Typ Max Units

T

HRST

T

OFF_AUDIO

T

OFF_VDDx

T

OFF_VDD4

T

OFF_PMU

Notes: 1. VDDx activity during STANDBY state is set by register PMU_STANDBY_SUPPLIES.

11050A–PMAAC–07-Apr-10

HRST Event Detection

Time

Audio CODEC Shutdown

Time

VDDx SHUTDOWN Time

VDD4 SHUTDOWN Time

Audio CODEC is ON 486 512 538 ms

Audio CODEC is OFF 58 62 66 µs

VDDx is OFF during STANDBY state

VDDx is ON during STANDBY state

VDD4 is OFF in RUN state

VDD4 is ON in RUN state

(2)

(2)

(1)

(1)

PMU Functions Shutdown

Time

2. VDD4 activity during RUN state is set by Bit7 of register VDD4_CTRL.

58 62 66 µs

58 62 66 µs

4.8 5.2 5.4 ms

58 62 66 µs

4.8 5.2 5.4 ms

1.4 1.5 1.6 ms

35

Page 36

11.5 DCDC0 and DCDC1 Functional Description

DCDC0 and DCDC1 are 2 identical high performance synchronous step-down (buck) converters. They feature:

• 2 control modes: PFM and PWM,

• A soft start circuit,

• A software programmable output voltage between 0.8 and 3.6V with automatic ramping for

DVS application,

• An Over-Current-Protection circuit,

• A 180 degree out of phase operating mode.

11.5.1 PFM and PWM Control Modes

Pulse Frequency Modulation control is an hysteretic control of the output voltage. It is specially

intended for light loads (< 50mA typ). In this mode, the DCDC converter exhibits a very low quiescent current (< 50

operation in this mode is not fixed but proportional to the load current.

Pulse Width Modulation control is a fixed frequency, variable duty cycle control of the DCDC

converter. It has a fast and precise feedback loop specially intended to handle hard loads and

low output ripple voltage.

At start-up, DCDC0 and DCDC1 operate in PWM mode. This way, high load at CPU boot are

properly handled. Through software control in registers VDD0_CTRL (0x06) and VDD1_CTRL

(0x07), the user may enter the low-power mode (PFM) when the application consumption is

reduced.

µA) thus achieving very high efficiency at light loads. The frequency of

11.5.2 Soft-start Circuit

DCDC0 and DCDC1 feature a soft start circuit to prevent high input current while charging the

output capacitor from 0V to the default output voltage. Typically, the in-rush current at start-up

(with no load) is limited to 30 mA.

11.5.3 Output Voltage Programming

DCDC0 and DCDC1 output voltages can be managed through software control in registers

VDD0_CTRL (0x06) and VDD1_CTRL (0x07). 50mV steps are provided from 0.8V to 3.6V. It is

recommended to use the automatic ramping function in register PMU_SUPPLY_CTRL (0x04) to

achieve smooth operation. When the DVS_VDD

are ramped from the current value to the final value in 50mV / 280us steps. For users who intend

to disable the DVS_VDD

At power up, DCDC0 and DCDC1 default output voltages are respectively 1.85V and 1.20V. For

different default output voltages, please contact Atmel.

11.5.4 180

° Out-of-phase Operation

DCDC0 and DCDC1 can be operated in-phase or at 180

tion bit in register PMU_SUPPLY_CTRL (0x04). When operated in phase both converters will

start charging their inductor at the same time. When operated at 180

charge start time will be shifted by half a 2MHz clock delay (= 250ns) from one converter to the

other. This latter scheme tends to average the input current of both DCDC converters.

bit is active (default mode), output voltages

{0,1}

bit, a maximum of 4 steps (= 200mV) per 100us is allowed.

{0,1}

° out-of-phase according to the selec-

° out-of-phase, the inductor

36

AT73C246

11050A–PMAAC–07-Apr-10

Page 37

11.6 LDO2 Functional Description

LDO2 is a linear voltage regulator intended to supply CPU core voltages in the range 0.8V to

1.35V. Its maximum input voltage is 3.6V. Thus, it must not be wired to the VIN plane with VINSYS, VIN0, VIN1, VIN3 and VIN4 if VIN is above 3.6V. Considering its low-output voltage and

for the sake of efficiency and power dissipation, the user may connect it at the output of DCDC0.

This LDO features:

• A soft start circuit,

• A software programmable output voltage between 0.8 and 1.35V with automatic ramping for

DVS application.

11.6.1 Soft-start Circuit

LDO2 features a soft start circuit to prevent high input current while charging the output capacitor from 0V to the default output voltage. This soft start circuit limits the input current during 5ms

(+/-5%) at startup to 200mA in typical conditions. After this delay, LDO2 recovers full current

capability.

11.6.2 Output Voltage Programming

LDO2 output voltage can be managed through software control in register VDD2_CTRL (0x08).

50mV steps are provided from 0.8V to 1.35V. It is recommended to use the automatic ramping

function in register PMU_SUPPLY_CTRL (0x04) to achieve smooth operation. When the

DVS_VDD2 bit is active (default mode), output voltages are ramped from the current value to

the final value in 50mV / 600us steps.

AT73C246

At power up, LDO2 default output voltage is 1V. For different default output voltage, please contact Atmel.

11.7 LDO3 and LDO4 Functional Description