Page 1

5

4

3

2

1

BOM MARK

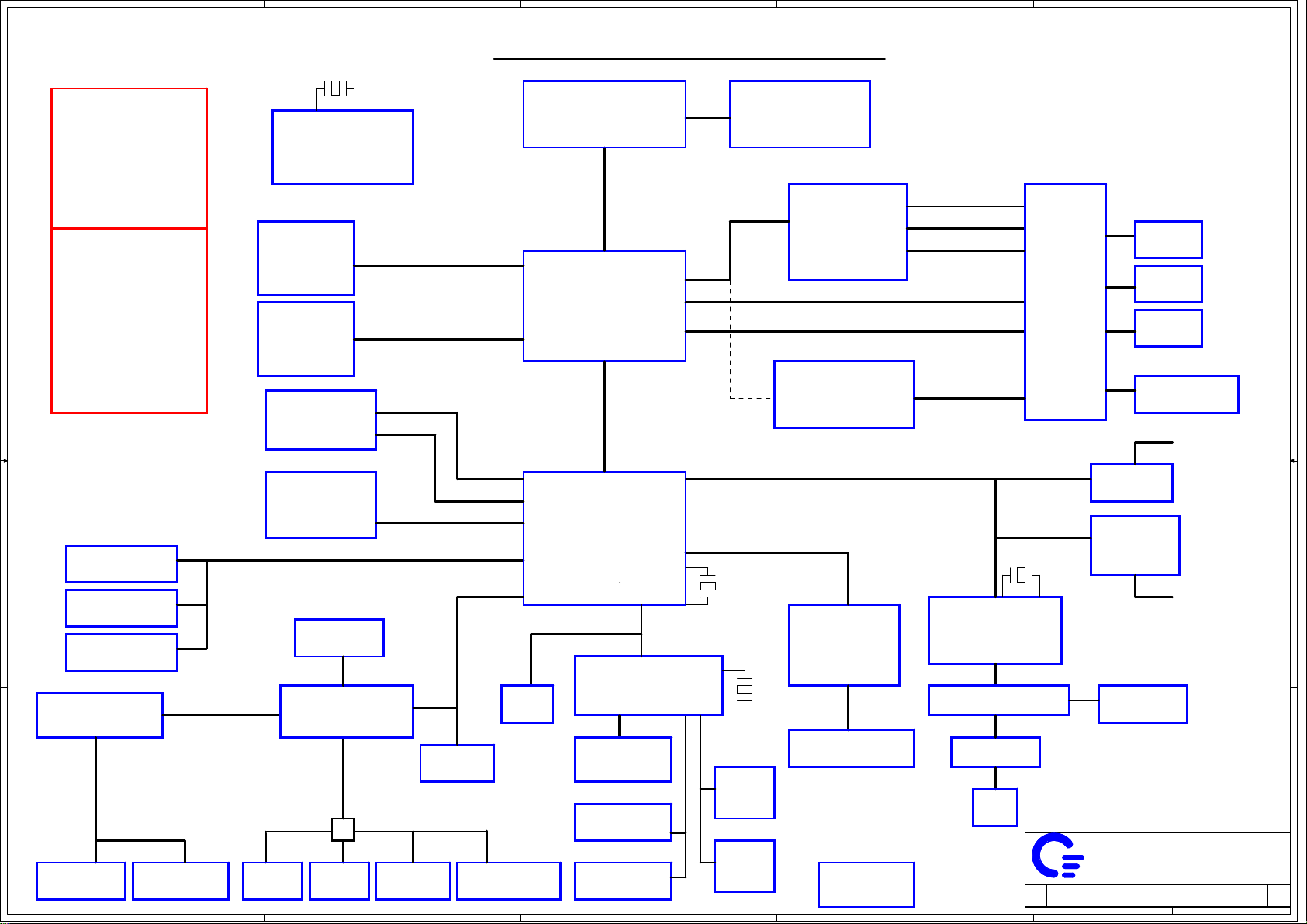

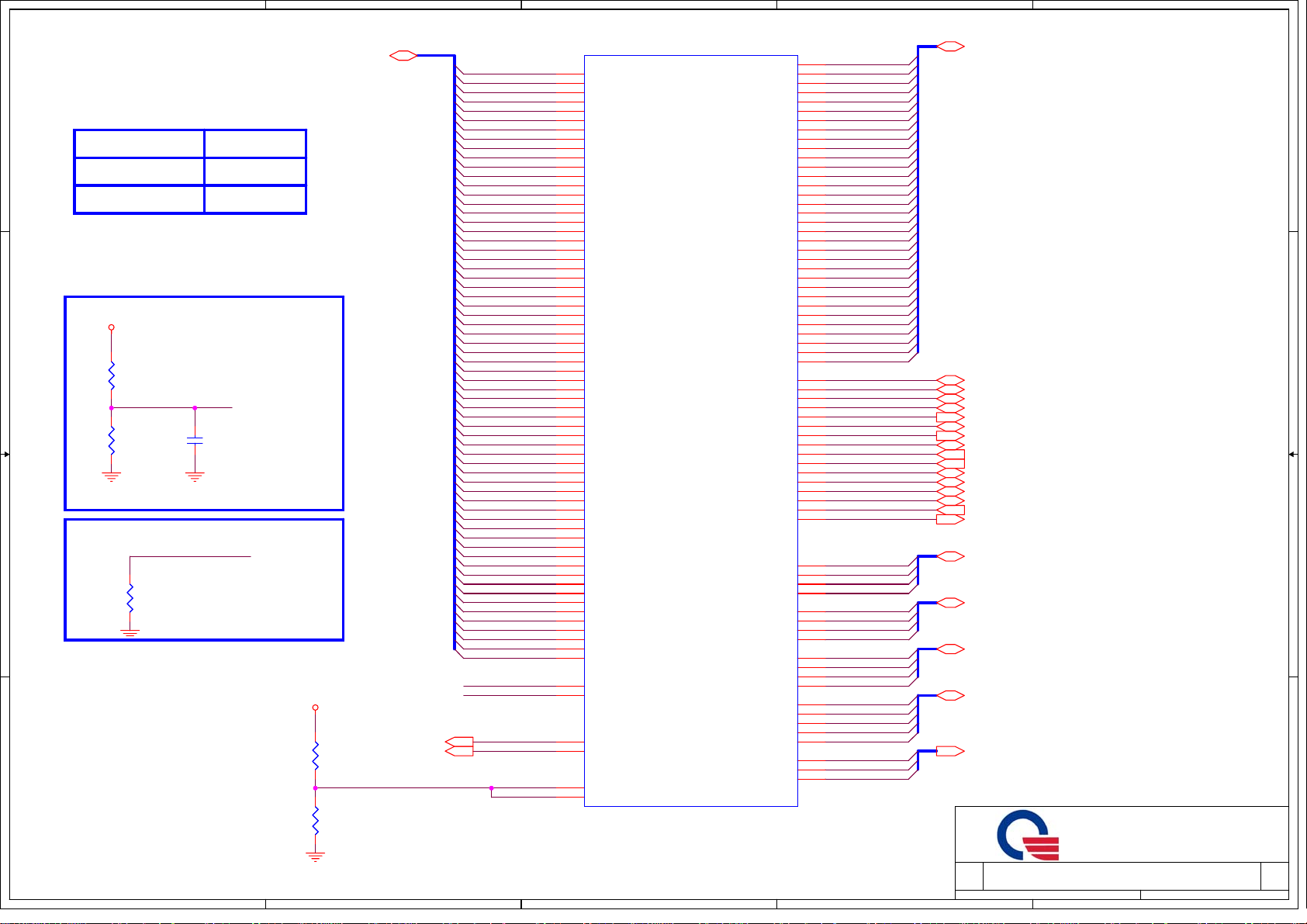

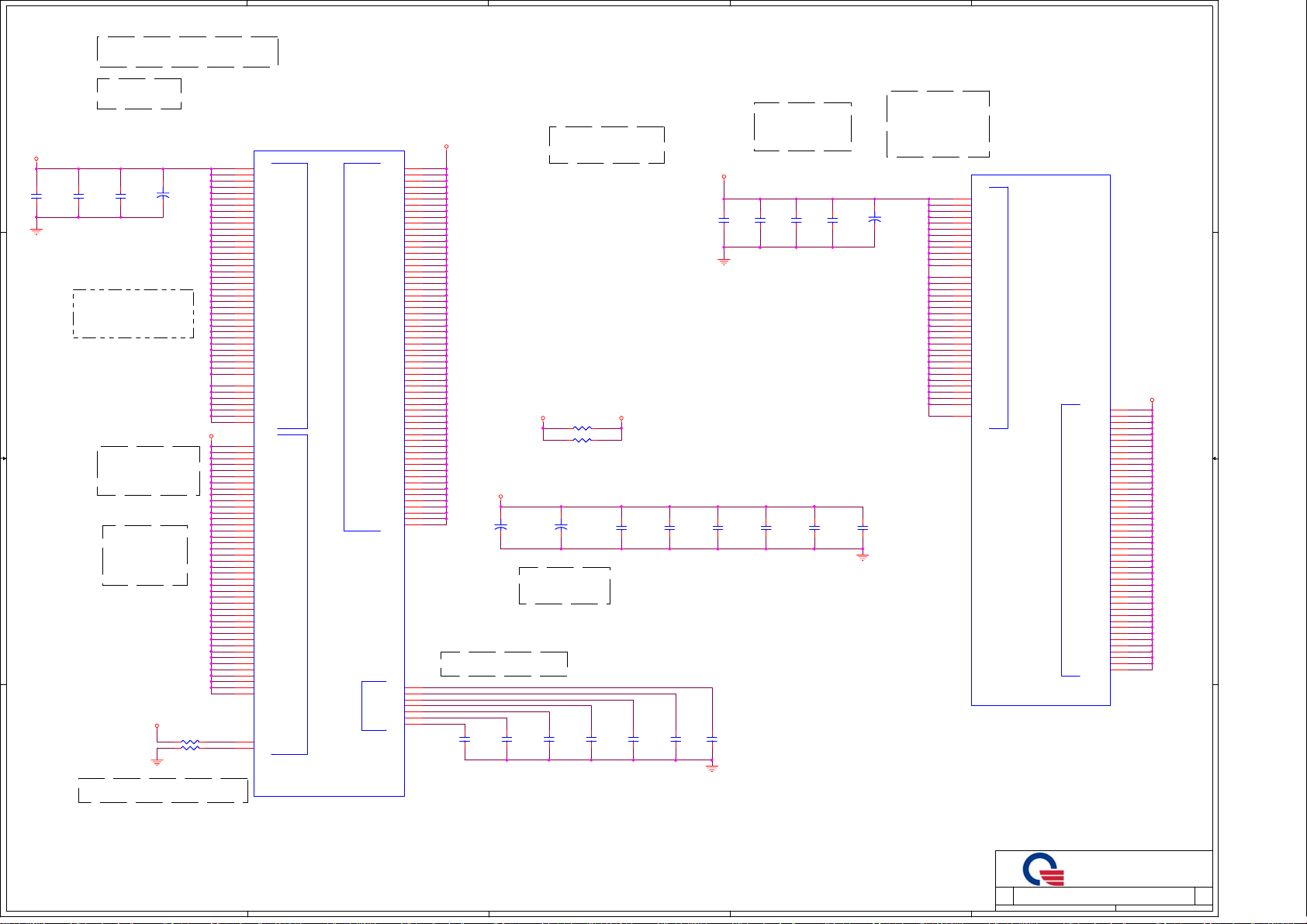

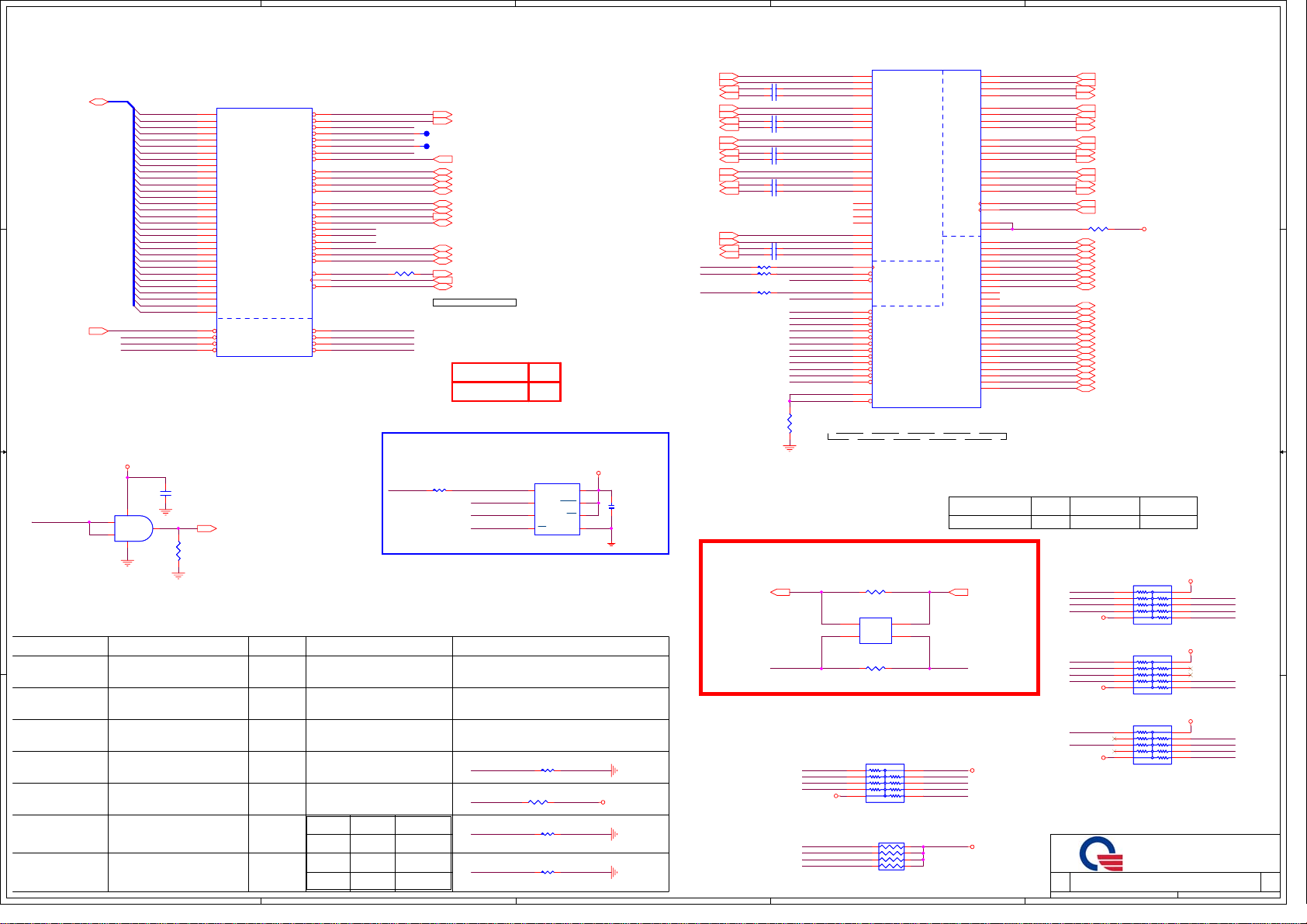

ZY2 SYSTEM BLOCK DIAGRAM

X'TAL

P16

P17

14.318MHZ

P2

Dual Channel DDR2

667/800 MHz

Dual Channel DDR3

667/800 MHz

Penryn 479

uFCPGA

FSB

NB

Cantiga

PM965

P5,P6,P7,P8,P9,P10,P11

P3,P4

667/800/1067 Mhz

X4 DMI interface

要打

要打

要打

要打

要打

要打

要打

要打

要打

要打

要打

要打

要打

要打

要打

要打

要打

CLOCK GENERATOR

ICS: ICS9LPRS365BGLFT

SELGO: SLG8SP512K05

DDRII

SO-DIMM 0

SO-DIMM 1

DDRIII

SO-DIMM 0

SO-DIMM 1

E@ EXT VGA

D D

C C

268@ AUDIO 268

D@ DOCK

D2@ DDR2

SP@ 特殊(EXT VGA OR DDR2)

LC@ LOW COST

ED2@ EXT VGA & DDR2

CB@ CARDBUS

NSF@ Non ASF

I@ INT VGA

888@ AUDIO 888

D3@ DDR3

ND@ NON DOCK

NLC@ NON LOW COST

TPM@ INT TPM

ID2@ INT VGA & DDR2

ED3@ EXT VGA & DDR3

ID3@ INT VGA & DDR3

ASF@ ASF

NCB@ NON CARDBUS

HDD (SATA)*2

LOW COST

1. MINI CARD 1 SLOT

2. NON DOCK

3. NON CARDBUS

4. NON ASF

5. NON HDMI

ODD (SATA)

Bluetooth

B B

USB4 P22

USB Port x 4

USB0~3

CCD

P25

P19USB7

Int MIC

P25

P25

P27

SATA0

SATA1

SATA4

USB 2.0

Azalia

SB

ICH9M

P12,P13,P14,P15

LPC

X'TAL

32.768KHZ

EC (WPC8769LDG)

Azalia Audio

SPDIF

P28

Controller

ALC268 & 888

Connector

P28

P27

MDC 1.5

MIC Jack

P28

4

P27

Audio Amplifier

A A

Speaker

P27 & 28

Phone Jack Line in

5

P28P28

TPM

P23

SUBWOOFER

P28

SPI ROM

Touch Pad

K/B COON.

P32

P32

P32

P32

3

CPU

Thermal Sensor

PCIE

MXM-NB8P-GS

( nVidia )

VRAM 256M

VRAM 512M

LVDS

RGB

DVI Level Shift IC

PI3VDP411LSZDE

Page:20

PCI-Express

PCI Bus

Cardreader

Controller

OZ601T

X'TAL

32.768K

Media Card Reader

VR

P27

CIR

P32

P3

P18

P29

P29

Fan Header

EXT_LVDS

EXT_CRT

EXT_DVI

INT_LVDS

INT_CRT

INT_DVI

BROADCOM

10/100/1G LAN

SWITCH CIRCUIT

Transformer

P31

2

5764M

RJ45

P22

CRT

Page:19

SWITCH

CIRCUIT

PCIE-1

New Card

PCIE-4

PCIE-6

X'TAL

25M

P21

Page:22

P22

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Mini Card /

WLAN / TV

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT : ZY2 & ZY6

PROJECT : ZY2 & ZY6

Block Diagram

Block Diagram

Block Diagram

LVDS

Page:19

HDMI

Page:20

DOCKING/DVI

Page: 31

USB5

P23

P23

USB6

DOCK/LAN

Page: 33

1

140Tuesday, April 08, 2008

140Tuesday, April 08, 2008

140Tuesday, April 08, 2008

1A

1A

1A

of

of

of

Page 2

5

4

3

2

1

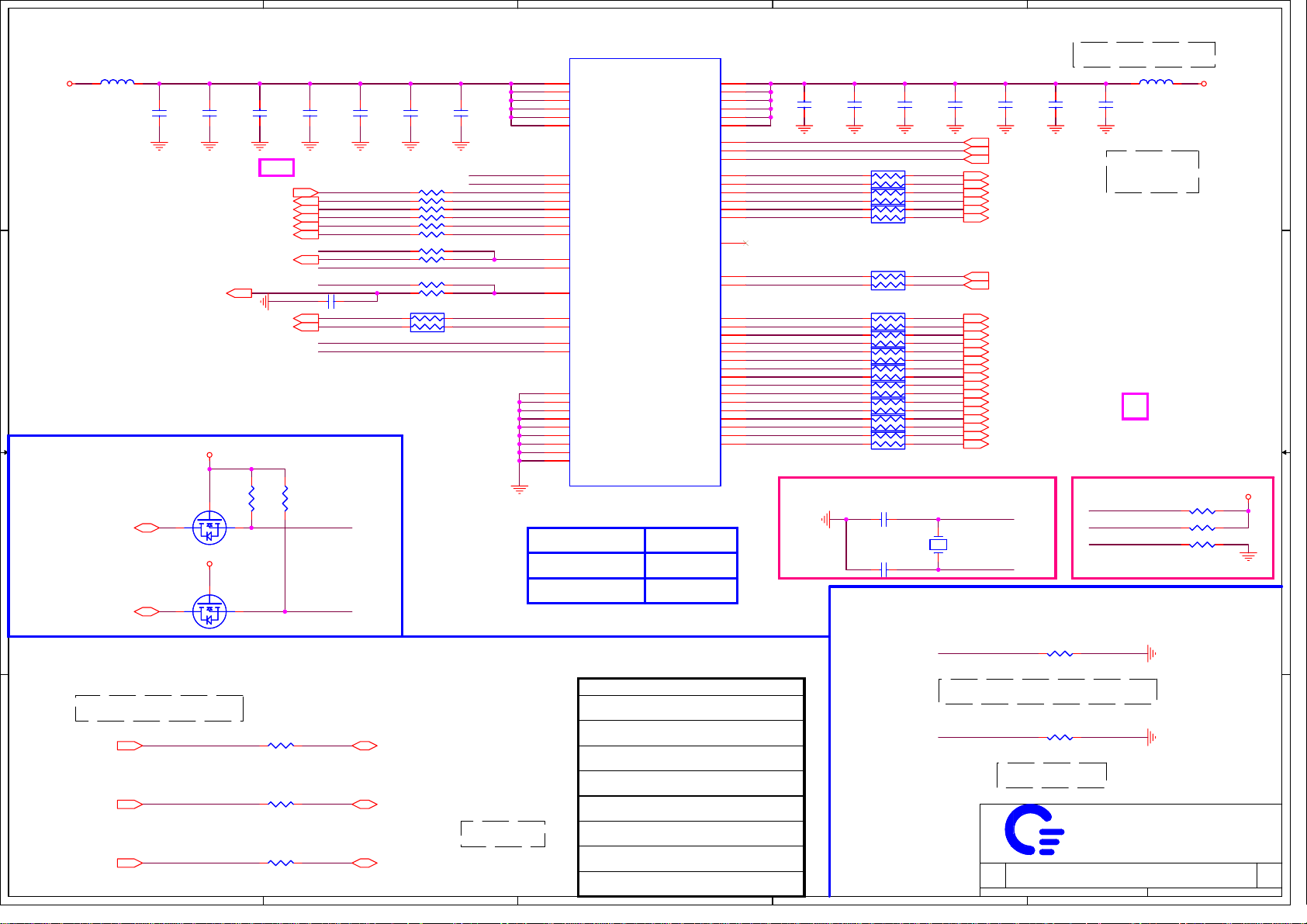

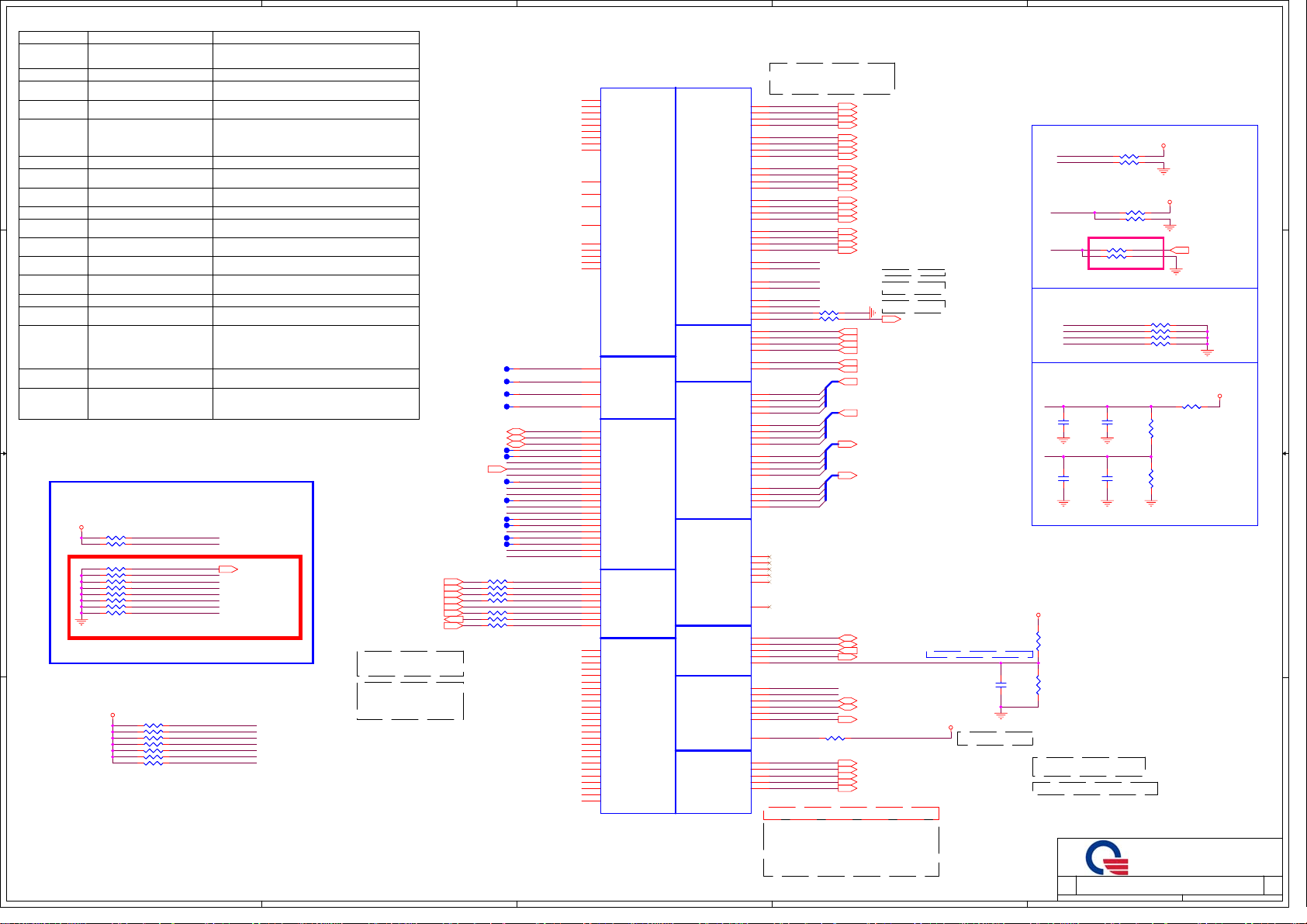

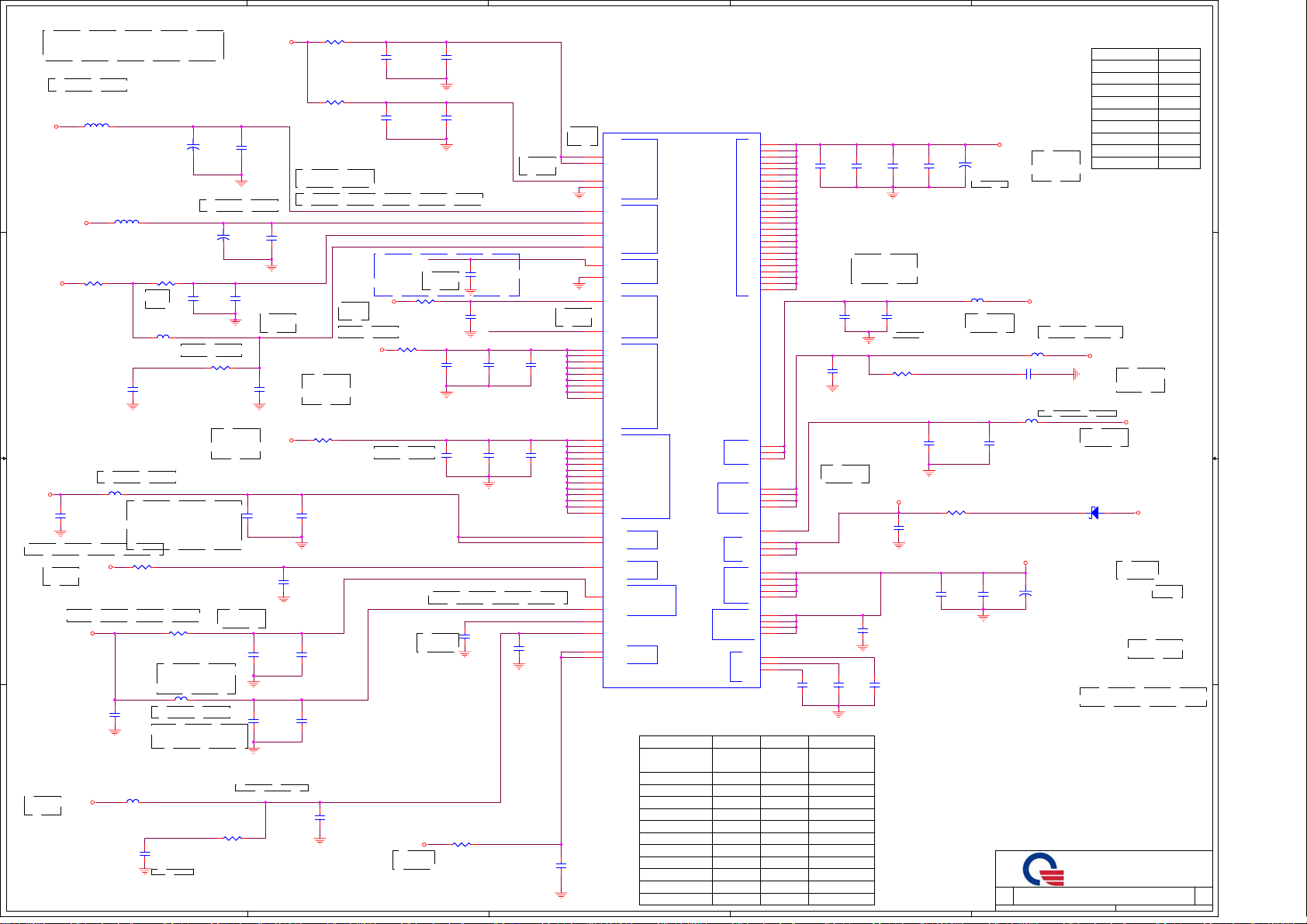

Clock Generator

U25

U25

R255 BKP1608HS181-TR255 BKP1608HS181-T

+3V +1.05V

C257

C215

C219

C216

C216

.1U/10V_4

D D

.1U/10V_4

C219

.1U/10V_4

.1U/10V_4

C215

.1U/10V_4

.1U/10V_4

C257

.1U/10V_4

.1U/10V_4

R254 Change from 33 to 475

SATACLKREQ#<14>

NEW_CLKREQ#<29>

PCLK_DEBUG<23>

PCLK_591<32>

PCLK_PCM<27>

PCLK_ICH<13>

CLKUSB_48<14>

14M_ICH<14>

CLK_DREFCLK<6>

CLK_DREFCLK#<6>

C C

+3V

PCLK_ICH

CPU_BSEL0

MCH_BSEL1

CPU_BSEL2

CGCLK_SMB

CGDAT_SMB

Clock Gen I2C

R237

R237

R243

10K_4

10K_4

R243

10K_4

10K_4

CGDAT_SMB

Q26

Q26

RHU002N06

RHU002N06

PDAT_SMB<14,16,20,21,23,29>

2

3

1

+3V_CLK

C262

C262

.1U/10V_4

.1U/10V_4

R246 475/F_4R246 475/F_4

R254 475/F_4R254 475/F_4

R253 33_4R253 33_4

R252 33_4R252 33_4

R264 33_4R264 33_4

R263 33_4R263 33_4

R258 2.2K_4R258 2.2K_4

R261 33_4R261 33_4

R230 10K_4R230 10K_4

C209*30P/50V_4 C209*30P/50V_4

R229 33_4R229 33_4

RP16 I@0X2RP16 I@0X2

4

2

C260

C260

.1U/10V_4

.1U/10V_4

3

1

C263

C263

10U/6.3V_6

10U/6.3V_6

CG_XOUT

CG_XIN

SATACLKREQ#_R

NEW_CLKREQ#_R

PCLK_MINI_R

PCLK_591_R

PCLK_PCM_R

PCLK_ICH_R

FSA

DREFCLK_R

DREFCLK#_R

FSC

2

VDD_PCI

9

VDD_48

16

VDD_PLL3

39

VDD_SRC

55

VDD_CPU

61

VDD_REF

59

XTAL_OUT

60

XTAL_IN

1

PCI_0/CLKREQ_A#

3

PCI_1/CLKREQ_B#

4

PCI_2

5

PCI_3

6

^PCI_4/LCDCLK_SEL

7

PCIF_5/ITP_EN

10

USB_48MHz/FS_A

57

FS_B/TEST_MODE

62

REF/FS_C/TEST_SEL

13

SRC_0/DOT_96

14

SRC_0#/DOT_96#

64

SCL

63

SDA

8

VSS_PCI

11

VSS_48

15

VSS_I/O

19

VSS_PLL3

23

VSS_SRC_1

29

VSS_SRC_2

42

VSS_SRC_3

52

VSS_CPU

58

VSS_REF

SLG8SP512

SLG8SP512

VDD_I/O

VDD_PLL3_I/O

VDD_SRC_I/O_1

VDD_SRC_I/O_2

VDD_SRC_I/O_3

VDD_CPU_I/O

CPU_STOP#

PCI_STOP#

CKPWRGD/PD#

CPU_0

CPU_0#

CPU_1_MCH

CPU_1_MCH#

SRC_8/CPU_ITP

SRC_8#/CPU_ITP#

LCDCLK/27M

LCDCLK#/27M_SS

SRC_2

SRC_2#

SRC_3/CLKREQ_C#

SRC_3#/CLKREQ_D#

SRC_7/CLKREQ_F#

SRC_7#/CLKREQ_E#

SRC_11/CLKREQ_H#

SRC_11#/CLKREQ_G#

SRC_4

SRC_4#

SRC_6

SRC_6#

SRC_9

SRC_9#

SRC_10

SRC_10#

12

20

26

36

45

49

37

38

56

54

53

51

50

47

46

48

NC

17

18

21

22

24

25

27

28

41

40

44

43

30

31

34

35

33

32

C272

C272

10U/6.3V_6

10U/6.3V_6

CLK_CPU_BCLK_R

CLK_CPU_BCLK#_R

CLK_MCH_BCLK_R

CLK_MCH_BCLK#_R

CLK_PCIE_CARD_R

CLK_PCIE_CARD#_R

CLK_DREFSSCLK_R

CLK_DREFSSCLK#_R

CLK_PCIE_SATA_R

CLK_PCIE_SATA#_R

CLK_PCIE_LAN_R

CLK_PCIE_LAN#_R

CLK_PCIE_NEW_C_R

CLK_PCIE_NEW_C#_R

CLK_PCIE_ICH_R

CLK_PCIE_ICH#_R

PECLK_VGA_R

PECLK_VGA#_R

CLK_PCIE_MINI1_R

CLK_PCIE_MINI1#_R

CLK_PCIE_3GPLL_R

CLK_PCIE_3GPLL#_R

CLK_PCIE_TV_R

CLK_PCIE_TV#_R

Rev:C Change C 205 & C204 P/N to CH03306JB04

QCI P/N

B B

PCLK_SMB<14,16,20,21,23,29>

Q27

Q27

RHU002N06

RHU002N06

3

+3V

2

1

CGCLK_SMB

ICS9LPRS365BGLFT

AL8SP512K05

ALPRS365K13

+1V05_CLK

C265

C213

C213

.1U/10V_4

.1U/10V_4

RP13 0X2_4RP13 0X2_4

1

3

RP12 0X2_4RP12 0X2_4

1

3

RP11 0X2_4RP11 0X2_4

1

3

RP15 I@0X2RP15 I@0X2

3

1

RP18 0X2_4RP18 0X2_4

3

1

RP17 0X2_4RP17 0X2_4

3

1

RP20 0X2_4RP20 0X2_4

3

1

RP9 0X2_4RP9 0X2_4

1

3

RP10 E@0X2RP10 E@0X2

1

3

RP19 0X2_4RP19 0X2_4

3

1

RP8 0X2_4RP8 0X2_4

3

1

RP14 0X2_4RP14 0X2_4

1

3

C205 33P/50V_4C205 33P/50V_4

C204 33P/50V_4C204 33P/50V_4

C265

.1U/10V_4

.1U/10V_4

2

4

2

4

2

4

4

2

4

2

4

2

4

2

2

4

2

4

4

2

4

2

2

4

Strap table

C214

C214

.1U/10V_4

.1U/10V_4

Y8

Y8

14.318MHz

14.318MHz

CG_XIN

CG_XOUT

C212

C212

.1U/10V_4

.1U/10V_4

PM_STPCPU# <14>

PM_STPPCI# <14>

CK_PWRGD <14>

CLK_CPU_BCLK <3>

CLK_CPU_BCLK# <3>

CLK_MCH_BCLK <5>

CLK_MCH_BCLK# <5>

CLK_PCIE_CARD <28>

CLK_PCIE_CARD# <28>

CLK_DREFSSCLK <6>

CLK_DREFSSCLK# <6>

CLK_PCIE_SATA <12>

CLK_PCIE_SATA# <12>

CLK_PCIE_LAN <21>

CLK_PCIE_LAN# <21>

CLK_PCIE_NEW_C <29>

CLK_PCIE_NEW_C# <29>

CLK_PCIE_ICH <13>

CLK_PCIE_ICH# <13>

CLK_MXM <18>

CLK_MXM# <18>

CLK_PCIE_MINI1 <23>

CLK_PCIE_MINI1# <23>

CLK_PCIE_3GPLL <6>

CLK_PCIE_3GPLL# <6>

CLK_PCIE_TV <23>

CLK_PCIE_TV# <23>

CLK VDD power range 1.05V~3.3V

C261

C261

.1U/10V_4

.1U/10V_4

C267

C267

.1U/10V_4

.1U/10V_4

Pin 56 : It acts as a

level sensitive strobe

to latch the FS pins

and other multiplexed

inputs.

Rev:B Swap SRC9 & SRC4

SATACLKREQ#_R

NEW_CLKREQ#_R

PCLK_MINI_R

Rev:B for vendor requestSLG8SP512

R219BKP1608HS181-T R219BKP1608HS181-T

+3V

R475 10K_4R475 10K_4

R531 10K_4R531 10K_4

R532 10K_4R532 10K_4

CPU Clock select

BSEL Frequency Select Table

FSC FSB FSA Frequency

Pin 10/57/62 : For Pin CPU frequency selection

CPU_BSEL0<3>

A A

CPU_BSEL1<3>

CPU_BSEL2<3>

5

R262 0_4R262 0_4

R226 0_4R226 0_4

R231 0_4R231 0_4

MCH_BSEL0 <6>

MCH_BSEL1 <6>

CRB Rev0.7 : 110(CBA)

MCH_BSEL2 <6>

4

0

0

0

1

0

1

0

1

1

1

1

0

1

0

0

1

1

0

01

1

1

0

3

266Mhz0

133Mhz

166Mhz

200Mhz

400Mhz

Reserved

100Mhz

333Mhz

2

PCLK_PCM_R

Pin 6 : For Pin 13/14 and 17/18 selection

0 = LCDCLK & DOT96 for internal graphic controller support

1 = 27M & 27M_SS &SRC_0 for external graphic controller support

PCLK_ICH_R

R260 10K_4R260 10K_4

R259 10K_4R259 10K_4

Pin 7 : For Pin 46/47 selection

1 = CPU_ITP

0 = SRC_8

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT : ZY2 & ZY6

PROJECT : ZY2 & ZY6

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CLOCK GENERATOR CK505 W/REGULATOR

CLOCK GENERATOR CK505 W/REGULATOR

CLOCK GENERATOR CK505 W/REGULATOR

Date: Sheet

Date: Sheet

Date: Sheet

240Tuesday, April 08, 2008

240Tuesday, April 08, 2008

240Tuesday, April 08, 2008

of

of

1

of

1A

1A

1A

Page 3

5

4

3

2

1

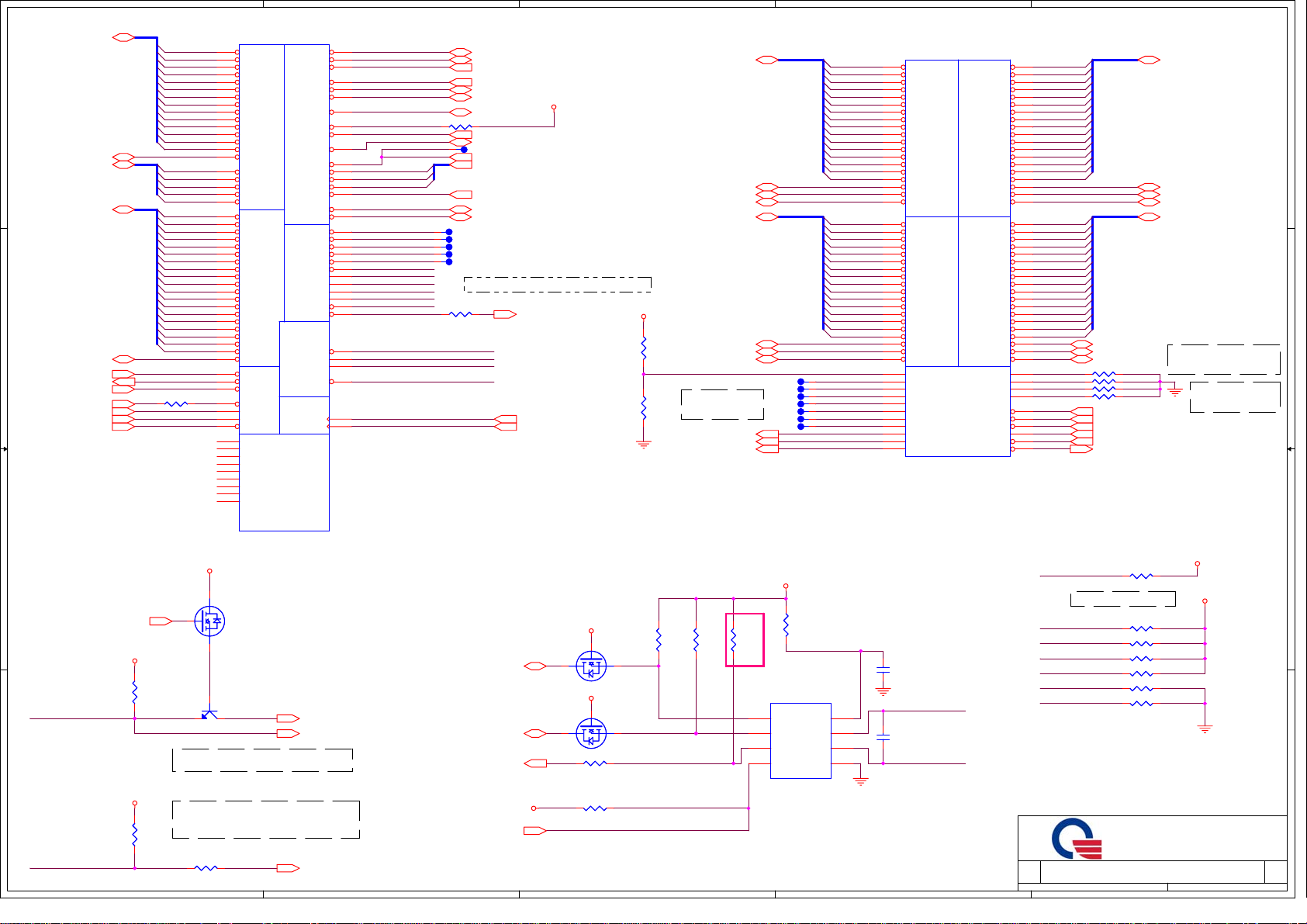

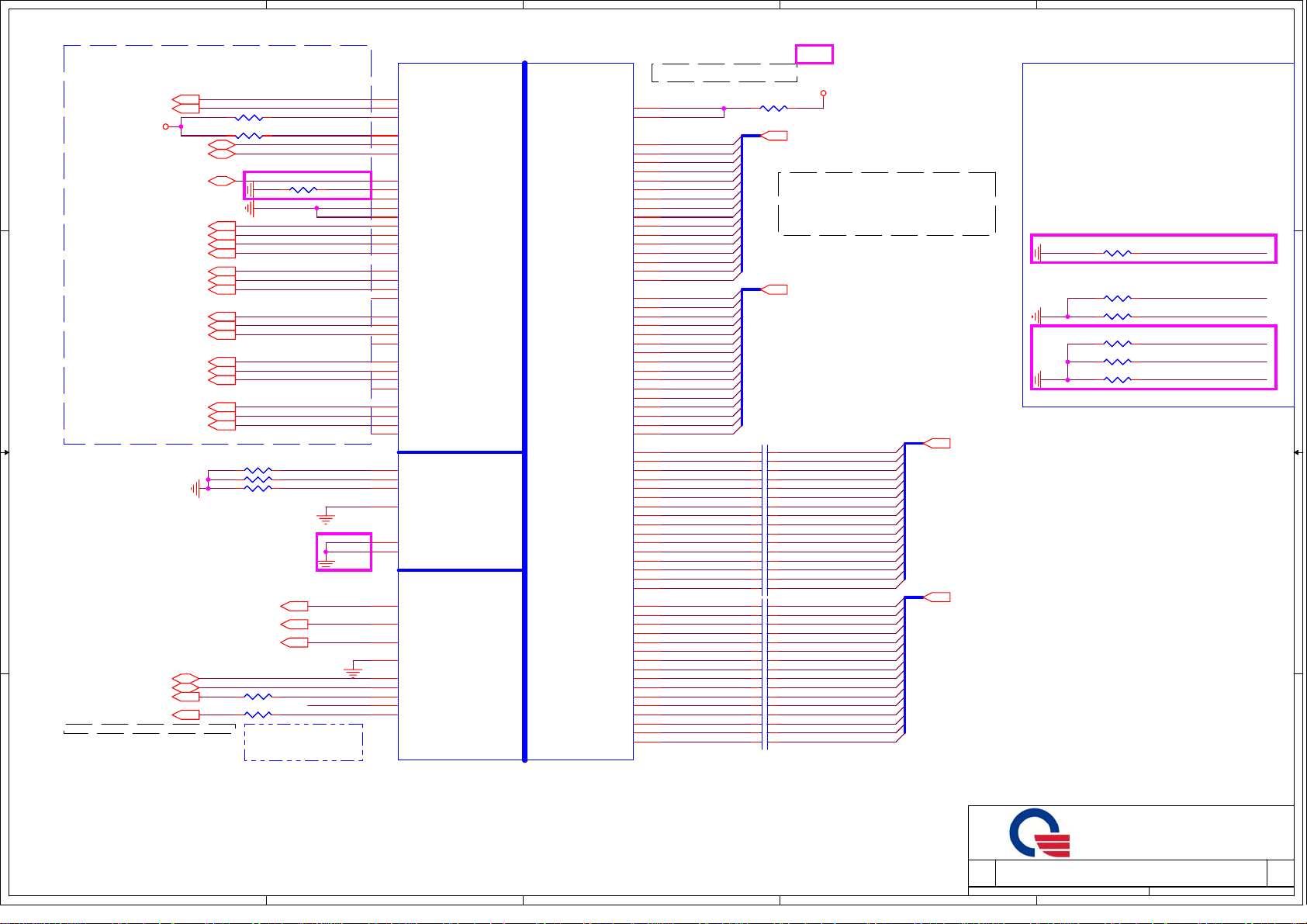

H_A#[3..16]<5>

D D

H_ADSTB#0<5>

H_REQ#[0..4]<5>

H_A#[17..35]<5>

C C

H_ADSTB#1<5>

H_A20M#<12>

H_FERR#<12>

H_IGNNE#<12>

H_STPCLK#<12>

H_INTR<12>

H_NMI<12>

H_SMI#<12>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

R494 0_4R494 0_4

AA4

AB2

AA3

D22

W6

W2

W5

W3

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

K3

H2

K2

J3

L1

Y2

U5

R3

U4

Y5

U1

R4

T5

T3

Y4

U2

V4

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

D2

D3

F6

U40A

U40A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

ADDR GROUP_0

ADDR GROUP_0

ADDR GROUP_1

ADDR GROUP_1

THERMAL

THERMAL

ICH

ICH

THERMTRIP#

RESERVED

RESERVED

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

PROCHOT#

THERMDA

THERMDC

H CLK

H CLK

BCLK[0]

BCLK[1]

U40B

AD26

AF26

E22

F24

E26

G22

F23

G25

E25

E23

K24

G24

H22

F26

K22

H23

H26

H25

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

C23

D25

C24

AF1

A26

B22

B23

C21

J24

J23

J26

C3

U40B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

BSEL[0]

BSEL[1]

BSEL[2]

Penryn

Penryn

DATA GRP 0

DATA GRP 0

MISC

MISC

DATA GRP 1

DATA GRP 1

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

R500 27.4/F_6R500 27.4/F_6

COMP1

R501 54.9/F_4R501 54.9/F_4

COMP2

R144 27.4/F_6R144 27.4/F_6

COMP3

R147 54.9/F_4R147 54.9/F_4

H_D#[32..47]

H_D#[48..63]

H_DSTBN#3 <5>

H_DSTBP#3 <5>

H_DINV#3 <5>

ICH_DPRSTP# <6,12,35>

H_DPSLP# <12>

H_DPWR# <5>

H_PWRGD <12>

H_CPUSLP# <5>

PSI# <35>

H_D#[32..47] <5>

H_DSTBN#2 <5>

H_DSTBP#2 <5>

H_DINV#2 <5>

H_D#[48..63] <5>

Layout note:

comp0,2: Zo=27.4ohm, L<0.5"

comp1,3: Zo=55ohm, L<0.5"

Layout note:

DPRSTP# , Daisy Chain

(SB>Power>NB>CPU)

H1

E2

G5

H5

F21

E1

F1

H_IERR#

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

XDP_BPM#0

AD4

XDP_BPM#1

AD3

XDP_BPM#2

AD1

XDP_BPM#3

AC4

XDP_BPM#4

AC2

XDP_BPM#5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

TDI

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

H_PROCHOT#_D

H_THERMDA

H_THERMDC

PM_THRMTRIP#

R162 56.2/F_4R162 56.2/F_4

H_RS#0

H_RS#1

H_RS#2

R491 0_4R491 0_4

H_ADS# <5>

H_BNR# <5>

H_BPRI# <5>

H_DEFER# <5>

H_DRDY# <5>

H_DBSY# <5>

H_BREQ# <5>

H_INIT# <12>

H_LOCK# <5>

T16T16

H_CPURST# <5>

H_RS#[0..2] <5>

H_TRDY# <5>

H_HIT# <5>

H_HITM# <5>

T10T10

T15T15

T13T13

T11T11

T14T14

Connect it to CPU DBR# is for ITP debug port

or CPU interposer (like ICE) to reset the system

+1.05V

SYS_RST# <14>

CLK_CPU_BCLK <2>

CLK_CPU_BCLK# <2>

+1.05V

R113

R113

1K/F_4

1K/F_4

R115

R115

2K/F_6

2K/F_6

H_D#[0..15]<5>

H_DSTBN#0<5>

H_DSTBP#0<5>

H_DINV#0<5>

H_D#[16..31]<5>

H_DSTBN#1<5>

H_DSTBP#1<5>

H_DINV#1<5>

Layout note:

H_GTLREF: Zo=55 ohm

L<0.5", 2/3*VCCP+-2%

CPU_BSEL0<2>

CPU_BSEL1<2>

CPU_BSEL2<2>

H_D#[0..15]

H_D#[16..31]

T18T18

T17T17

T19T19

T72T72

T12T12

T70T70

T71T71

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_GTLREF

CPU_TEST1

CPU_TEST2

CPU_TEST3

CPU_TEST4

CPU_TEST5

CPU_TEST6

CPU_TEST7

Penryn

Penryn

Thermal Trip

B B

DELAY_VR_PWRGOOD<6,14,32,35>

+1.05V

R495

R495

56.2/F_4

+1.05V

56.2/F_4

R163

R163

56_4

56_4

5

PM_THRMTRIP#

A A

Processor hot

H_PROCHOT#_D

+1.05V

3

Q41

Q41

2

FDV301N

FDV301N

1

2

Q40

Q40

MMBT3904

MMBT3904

1 3

No use Thermal trip CPU side still PU 56ohm.

Use Thermal trip can share PU at SB side

No use PROCHOT CPU side still PU 56ohm.

Use PROCHOT to optional receiver CPU side PU

68ohm and through isolat 2.2K ohm to receiver

side

R164 *0_4R164 *0_4

SYS_SHDN# <34,38>

PM_THRMTRIP# <6,12>

H_PROCHOT# <35>

CPU Thermal monitor

2ND_MBCLK<32>

2ND_MBDATA<32>

THERM_ALERT#<14,18>

CPUFAN#_ON<31>

4

R540

R540

10K_4

10K_4

+3V

U39

U39

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

G780

G780

ADDRESS: 98H

R490

R490

200_6

200_6

VCC

DXP

DXN

GND

LM86VCC

1

2

3

5

C552

C552

.1U/10V_4

.1U/10V_4

H_THERMDA

C551

C551

100P/X7R/50V_4

100P/X7R/50V_4

H_THERMDC

2

Rev:B Add R540

+3V

Q39

Q39

2

RHU002N06

RHU002N06

3

3

R465 *0_4R465 *0_4

+5V

R493 *10K_4R493 *10K_4

1

+3V

Q38

Q38

2

RHU002N06

RHU002N06

1

R466

R466

10K_4

10K_4

CPUFAN#_ON

3

R467

R467

10K_4

10K_4

XDP PU/PD

XDP_DBRESET#

XDP_TDO

XDP_TDI

XDP_TMS

XDP_BPM#5

XDP_TCK

XDP_TRST#

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CPU Host Bus

CPU Host Bus

CPU Host Bus

Date: Sheet

Date: Sheet

Date: Sheet

R492 *1K_4R492 *1K_4

XDP_DBRESET# and XDP_TDO

reserve for XDP

R128 *54.9/F_4R128 *54.9/F_4

R149 54.9/F_4R149 54.9/F_4

R131 54.9/F_4R131 54.9/F_4

R121 54.9/F_4R121 54.9/F_4

R127 54.9/F_4R127 54.9/F_4

R124 54.9/F_4R124 54.9/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

+3V

+1.05V

ZY2 & ZY6

ZY2 & ZY6

ZY2 & ZY6

340Tuesday, April 08, 2008

340Tuesday, April 08, 2008

340Tuesday, April 08, 2008

of

of

of

1A

1A

1A

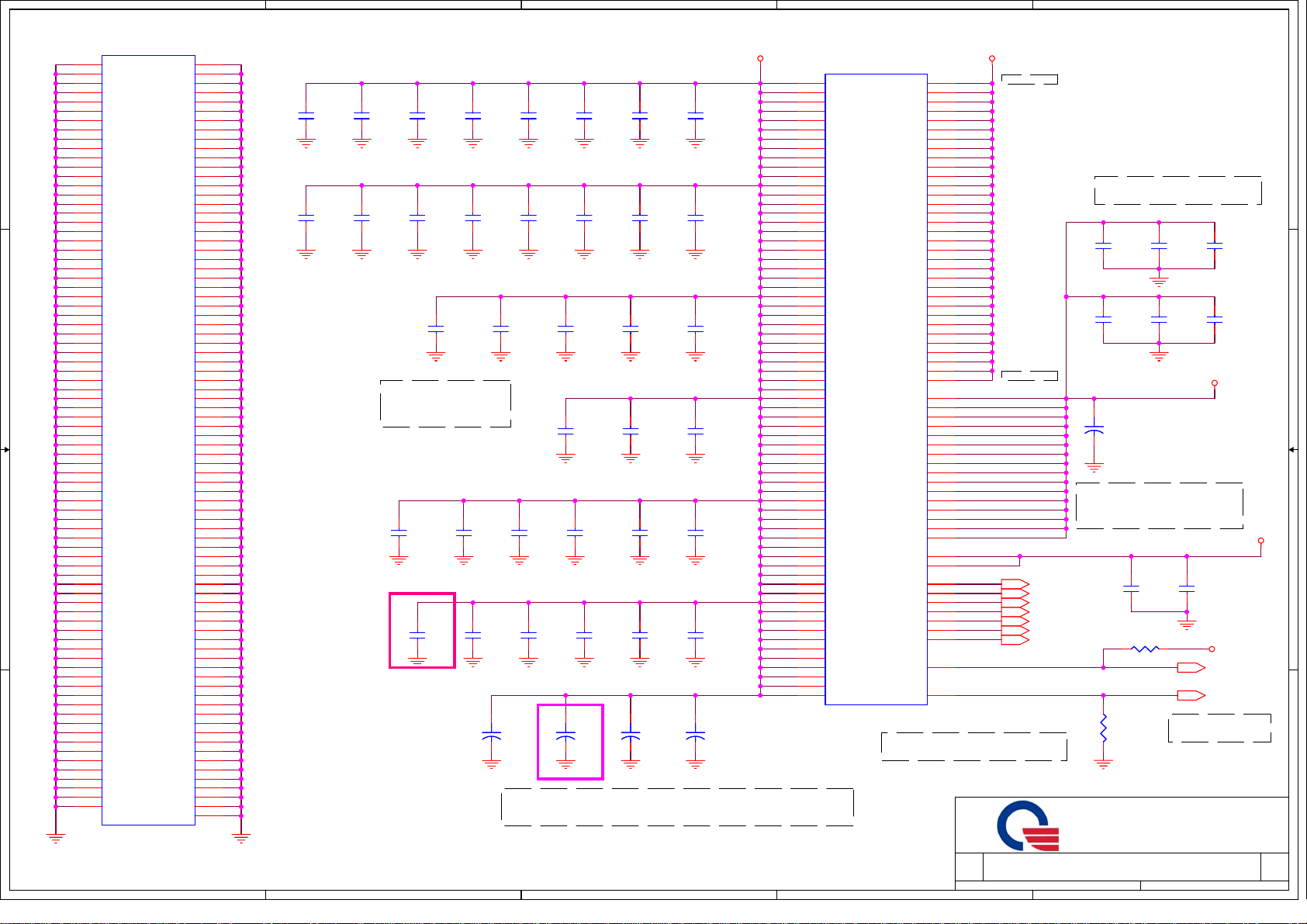

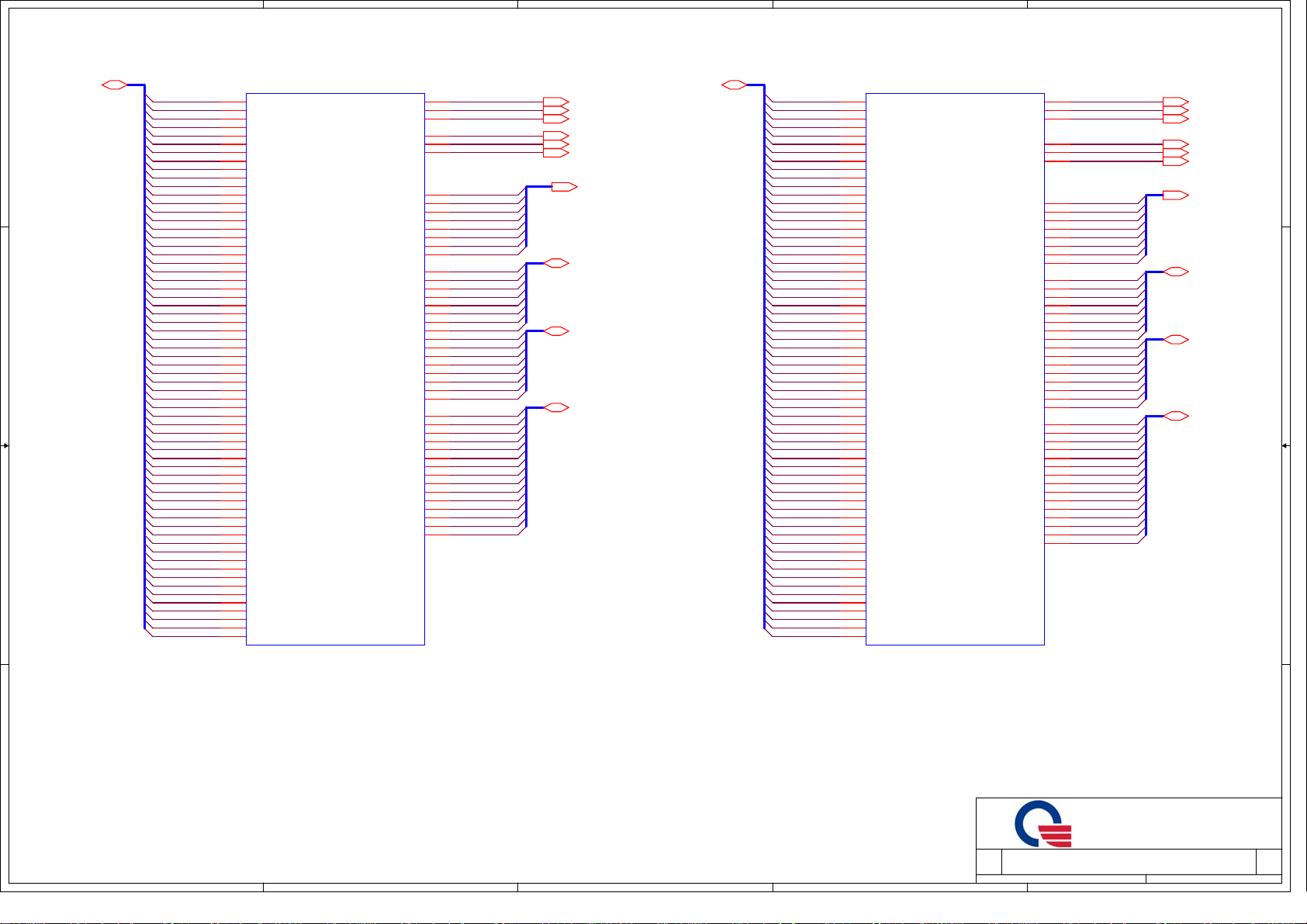

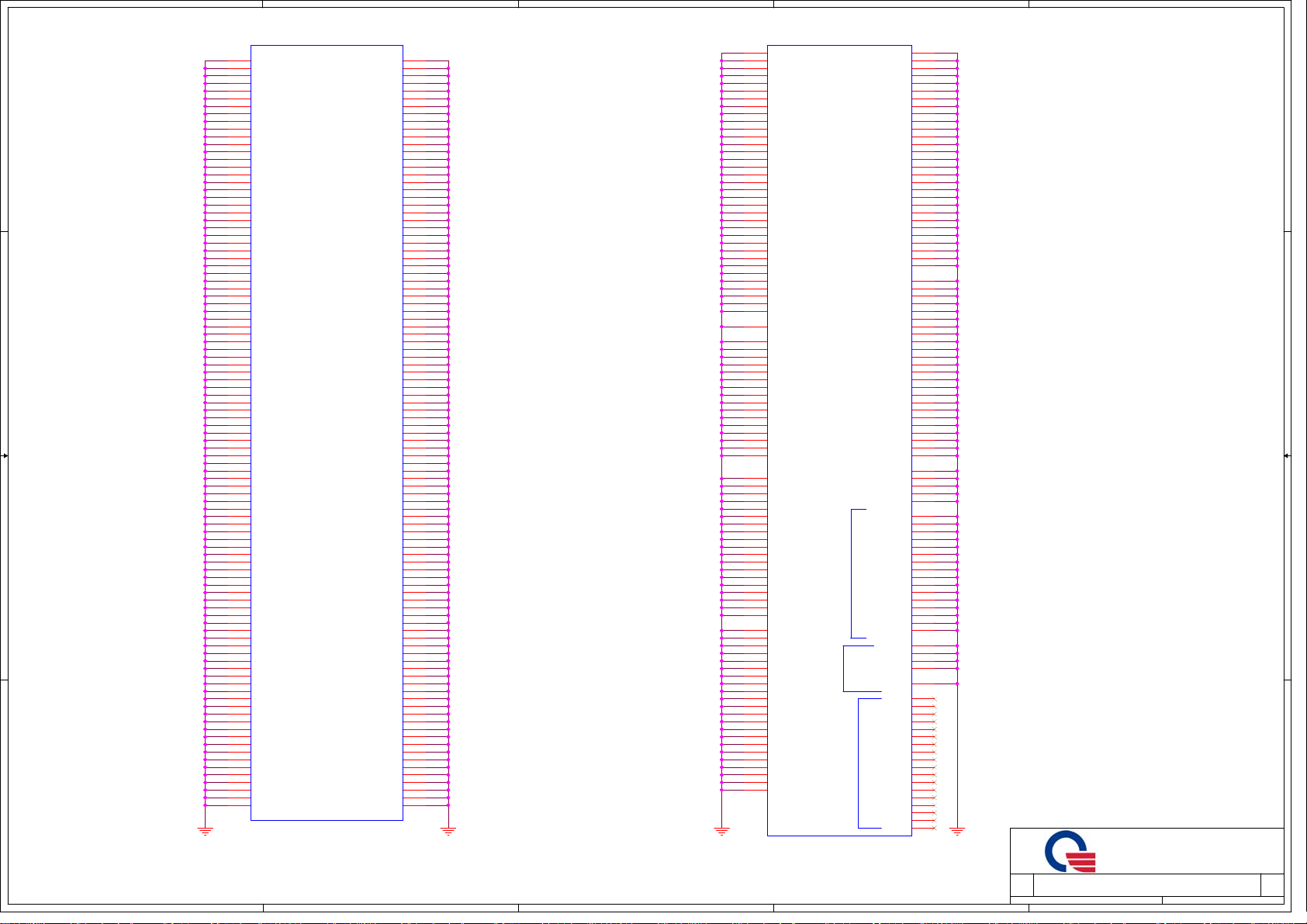

Page 4

5

4

3

2

1

U40D

U40D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

D D

C C

B B

A A

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Penryn

Penryn

5

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

.

.

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

C557

C557

*10U/6.3V_8

*10U/6.3V_8

C565

C565

10U/6.3V_8

10U/6.3V_8

C156

C156

10U/6.3V_8

10U/6.3V_8

C573

C573

*10U/6.3V_8

*10U/6.3V_8

C154

C154

10U/6.3V_8

10U/6.3V_8

C572

C572

10U/6.3V_8

10U/6.3V_8

C140

C140

*10U/6.3V_8

*10U/6.3V_8

Layout Note:

Place these parts

reference to Intel demo

board.

C158

C158

*10U/6.3V_8

*10U/6.3V_8

C563

C563

10U/6.3V_8

10U/6.3V_8

10/12 :Modify BOM

4

C558

C155

C155

*10U/6.3V_8

*10U/6.3V_8

C571

C571

*10U/6.3V_8

*10U/6.3V_8

C153

C153

*10U/6.3V_8

*10U/6.3V_8

C574

C574

10U/6.3V_8

10U/6.3V_8

C558

10U/6.3V_8

10U/6.3V_8

C553

C553

*10U/6.3V_8

*10U/6.3V_8

C141

C141

*10U/6.3V_8

*10U/6.3V_8

C152

C152

10U/6.3V_8

10U/6.3V_8

C570

C570

10U/6.3V_8

10U/6.3V_8

C80

C80

+

+

*330U/2V_7343

*330U/2V_7343

Montevina platform : Early Reference Board Schematics Feb 2007. Rev 1.0

stuff 22U*34, NC 22U*2

stuff 330U*2, NC330U*2

C568

C568

*10U/6.3V_8

*10U/6.3V_8

C556

C556

10U/6.3V_8

10U/6.3V_8

C139

C139

*10U/6.3V_8

*10U/6.3V_8

C142

C142

*10U/6.3V_8

*10U/6.3V_8

C151

C151

*10U/6.3V_8

*10U/6.3V_8

C569

C569

*10U/6.3V_8

*10U/6.3V_8

C576

C576

+

+

330U/2V_7343

330U/2V_7343

C566

C566

*10U/6.3V_8

*10U/6.3V_8

C119

C119

*10U/6.3V_8

*10U/6.3V_8

C560

C560

10U/6.3V_8

10U/6.3V_8

C120

C120

*10U/6.3V_8

*10U/6.3V_8

C567

C567

10U/6.3V_8

10U/6.3V_8

C554

C554

10U/6.3V_8

10U/6.3V_8

C81

C81

+

+

330U/2V_7343

330U/2V_7343

3

+

+

VCC_CORE VCC_CORE

U40C

U40C

A7

C157

C157

*10U/6.3V_8

*10U/6.3V_8

C559

C559

*10U/6.3V_8

*10U/6.3V_8

C118

C118

10U/6.3V_8

10U/6.3V_8

C121

C121

10U/6.3V_8

10U/6.3V_8

C564

C564

*10U/6.3V_8

*10U/6.3V_8

C555

C555

*10U/6.3V_8

*10U/6.3V_8

C577

C577

*330U/2V_7343

*330U/2V_7343

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A9

B7

B9

C9

D9

E7

E9

F7

F9

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

Penryn

Penryn

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

.

.

VCCA : 2.5A(Supply after VCC Stable)

4.5A(Supply before VCC Stable)

2

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

VCC:38A

VCCP:130mA

H_VID0 <35>

H_VID1 <35>

H_VID2 <35>

H_VID3 <35>

H_VID4 <35>

H_VID5 <35>

H_VID6 <35>

CPU Power

CPU Power

CPU Power

Layout Note:

Inside CPU center cavity in 2 rows

C129

C129

.1U/16V_6

.1U/16V_6

C128

C128

.1U/16V_6

.1U/16V_6

+

+

C575

C575

330U/2.5V_7

330U/2.5V_7

Layout Note:

VCCA CAP closr to Pin

VCCA : 2.5A(Supply after VCC Stable)

4.5A(Supply before VCC Stable)

R84 100/F_6R84 100/F_6

R77

R77

100/F_6

100/F_6

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

C135

C135

.1U/16V_6

.1U/16V_6

C136

C136

.1U/16V_6

.1U/16V_6

C562

C562

.01U/16V_4

.01U/16V_4

Layout Note:

Z0=27.4,PU/PD L<1"

ZY2 & ZY6

ZY2 & ZY6

ZY2 & ZY6

1

+1.05V

C561

C561

10U/6.3V_8

10U/6.3V_8

VCC_CORE

VCCSENSE <35>

VSSSENSE <35>

of

of

of

440Tuesday, April 08, 2008

440Tuesday, April 08, 2008

440Tuesday, April 08, 2008

C147

C147

.1U/16V_6

.1U/16V_6

C148

C148

.1U/16V_6

.1U/16V_6

+1.5V

1A

1A

1A

Page 5

5

4

3

2

1

U38A

H_D#[0..63]<3>

D D

QCI P/N

Intel Cantiga (G)M

Intel Cantiga (P)M

+1.05V

C C

B B

A A

0.3125*VCCP

WIDE(10):SPACING(20) ,

R177

R177

L<0.5"

221/F_4

221/F_4

H_SWING

R175

R175

100/F_4

100/F_4

R464

R464

24.9/F_4

24.9/F_4

2/3*VCCP

WIDE(10):SPACING(20),

L<0.5"

5

AJ0QT620T01

AJ0QT780T03

Capacitor close

C178

C178

to the pin

0.1U/10V_4

0.1U/10V_4

H_RCOMP

WIDE(10):SPACING(20) ,

L<0.5"

+1.05V

R484

R484

1K/F_4

1K/F_4

R482

R482

2K/F_4

2K/F_4

H_CPURST#<3>

4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_AVREF

U38A

F2

H_D#_0

G8

H_D#_1

F8

H_D#_2

E6

H_D#_3

G2

H_D#_4

H6

H_D#_5

H2

H_D#_6

F6

H_D#_7

D4

H_D#_8

H3

H_D#_9

M9

H_D#_10

M11

H_D#_11

J1

H_D#_12

J2

H_D#_13

N12

H_D#_14

J6

H_D#_15

P2

H_D#_16

L2

H_D#_17

R2

H_D#_18

N9

H_D#_19

L6

H_D#_20

M5

H_D#_21

J3

H_D#_22

N2

H_D#_23

R1

H_D#_24

N5

H_D#_25

N6

H_D#_26

P13

H_D#_27

N8

H_D#_28

L7

H_D#_29

N10

H_D#_30

M3

H_D#_31

Y3

H_D#_32

AD14

H_D#_33

Y6

H_D#_34

Y10

H_D#_35

Y12

H_D#_36

Y14

H_D#_37

Y7

H_D#_38

W2

H_D#_39

AA8

H_D#_40

Y9

H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

C5

H_SWING

E3

H_RCOMP

C12

H_CPURST#

E11

H_CPUSLP#

A11

H_AVREF

B11

H_DVREF

SP@CANTIGA_1p2

SP@CANTIGA_1p2

3

H_ADSTB#_0

H_ADSTB#_1

HOST

HOST

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

2

H_A#[3..35] <3>

H_ADS# <3>

H_ADSTB#0 <3>

H_ADSTB#1 <3>

H_BNR# <3>

H_BPRI# <3>

H_BREQ# <3>

H_DEFER# <3>

H_DBSY# <3>

CLK_MCH_BCLK <2>

CLK_MCH_BCLK# <2>

H_DPWR# <3>

H_DRDY# <3>

H_HIT# <3>

H_HITM# <3>

H_LOCK# <3>

H_TRDY# <3>

H_DINV#[3..0] <3>

H_DSTBN#[3..0] <3>

H_DSTBP#[3..0] <3>

H_REQ#[0..4] <3>

H_RS#[0..2] <3>H_CPUSLP#<3>

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GMCH HOST

GMCH HOST

GMCH HOST

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

ZY2 & ZY6

ZY2 & ZY6

ZY2 & ZY6

of

of

of

540Tuesday, April 08, 2008

540Tuesday, April 08, 2008

540Tuesday, April 08, 2008

1

1A

1A

1A

Page 6

5

4

3

2

1

Strap table

Pin Name Strap description

CFG[2:0]

CFG[4:3]

CFG5

CFG6

D D

CFG7

CFG8

CFG9

CFG10

FSB Frequency Select

Reserved

DMI X2 Select

iTPM Host Interface

ME TLS Confidentiality

Reserved

PCIE Graphics Lane Reversal

PCIE Loopback enable

ReservedCFG11

CFG12

CFG13

CFG[15:14]

CFG16

CFG[18:17]

CFG19

C C

CFG20

ALLZ

XOR

Reserved

FSB Dynamic ODT

Reserved

DMI Lane Reversal

Digital Display Port

(SDVO/DP/iHDMI)

Concurrent with PCIE

SDVO_CTRLDATA SDVO Present

DDPC_CTRLDATA Digital Display Present

Strap pin

+3V

R477 *4.02K/F_4R477 *4.02K/F_4

R478 *4.02K/F_4R478 *4.02K/F_4

B B

A A

R207 TPM@2.21K/F_4R207 TPM@2.21K/F_4

R479 *4.02K/F_4R479 *4.02K/F_4

R196 *4.02K/F_4R196 *4.02K/F_4

R487 *4.02K/F_4R487 *4.02K/F_4

R488 *4.02K/F_4R488 *4.02K/F_4

R222 *4.02K/F_4R222 *4.02K/F_4

R216 *4.02K/F_4R216 *4.02K/F_4

R200 *4.02K/F_4R200 *4.02K/F_4

REV: E Modify TPM (R207)

+3V

R184 I@2.21K/F_4R184 I@2.21K/F_4

R188 I@2.21K/F_4R188 I@2.21K/F_4

R206 *2.21K/F_4R206 *2.21K/F_4

R217 *2.21K/F_4R217 *2.21K/F_4

R481 10K_4R481 10K_4

R485 10K_4R485 10K_4

R209 10K_4R209 10K_4

5

Configuration

000= FSB 1066MHz

010 = FSB 800MHz

011 = FSB 667MHz

0 = DMI X2

1 = DMI X4(Default)

0 = iTPM Host Interface is enabled

1 = iTPM Host Interface is disabled(Default)

0 = AMT Firmware will use TLS cipher suite

with no confidentiality

1 = AMT Firmware will use TLS cipher suite

with confidentiality(Default)

0 = Reverse Lanes

1 = Normal operation(Default)

0 = Enabled

1 = Disabled (Default)

0 = ALLZ mode enable

1 = disable(Default)

0 = XOR mode enable

1 = disable(Default)

0 = Dynamic ODT disable

1 = Dynamic ODT Enable(Default)

0 = Normal (Default)

1 = Lanes Reversed

0 = Only Digital Display port (SDVO/DP/iHDMI)

or PCIE is operational (Default)

1 = Digital Display port (SDVO/DP/iHDMI) and

PCIE are operating simultaneously via PEG

port

0 = No SDVO/HDMI Device Present(Default)

1 = SDVO/HDMI Device present

0 = Digital display(HDMI/DP) device

absent(Default)

1 = Digital display(HDMI/DP) device present

MCH_CFG_19

MCH_CFG_20

MCH_CFG_5

MCH_CFG_7

MCH_CFG_9

MCH_CFG_10

MCH_CFG_12

MCH_CFG_13

MCH_CFG_16

MCH_CFG_6_R <13>

SDVO_CTRLDATA

SDVO_CTRLCLK

DDPC_DDCDATA

DDPC_CTRLCLK

CLK_MCH_OE#

PM_EXTTS#0

PM_EXTTS#1

MCH_CFG_6<13>

PM_SYNC#<14>

ICH_DPRSTP#<3,12,35>

PM_EXTTS#0<16,17>

PM_EXTTS#1<16,17>

DELAY_VR_PWRGOOD<3,14,32,35>

PLT_RST#<13>

PM_THRMTRIP#<3,12>

PM_DPRSLPVR<14,35>

No use Thermal trip NB side can

NC.(NB has ODT)

PM_DPRSTP#

The Daisy chain topology should

be routed from ICH9M to IMVP ,

then to (G)MCH and CPU, in that

order.

4

T30T30

T28T28

T31T31

T29T29

MCH_BSEL0<2>

MCH_BSEL1<2>

MCH_BSEL2<2>

T25T25

T27T27

T21T21

T24T24

T26T26

T20T20

T22T22

T23T23

R213 0_4R213 0_4

R483 0_4R483 0_4

R470 0_4R470 0_4

R212 0_4R212 0_4

R247 100/F_4R247 100/F_4

R221 *0_4R221 *0_4

R218 0_4R218 0_4

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

PM_SYNC#_R

ICH_DPRSTP#_R

PM_EXTTS#0_1_EC_R

TS#DIMM0_1_R

RST_IN#_MCH

THRMTRIP#_R

DPRSLPVR_R

U38B

U38B

M36

RSVD1

N36

RSVD2

R33

RSVD3

T33

RSVD4

AH9

RSVD5

AH10

RSVD6

AH12

RSVD7

AH13

RSVD8

K12

RSVD9

T24

RSVD14

B31

RSVD15

M1

RSVD17

AY21

RSVD20

B2

RSVD21

BG23

RSVD22

BF23

RSVD23

BH18

RSVD24

BF18

RSVD25

AL34

ME_JTAG_TCK

AK34

ME_JTAG_TDI

AN35

ME_JTAG_TDO

AM35

ME_JTAG_TMS

T25

CFG_0

R25

CFG_1

P25

CFG_2

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

C23

CFG_9

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

CFG_16

H21

CFG_17

P29

CFG_18

R28

CFG_19

T28

CFG_20

R29

PM_SYNC#

B7

PM_DPRSTP#

N33

PM_EXT_TS#_0

P32

PM_EXT_TS#_1

AT40

PWROK

AT11

RSTIN#

T20

THERMTRIP#

R32

DPRSLPVR

BG48

NC_1

BF48

NC_2

BD48

NC_3

BC48

NC_4

BH47

NC_5

BG47

NC_6

BE47

NC_7

BH46

NC_8

BF46

NC_9

BG45

NC_10

BH44

NC_11

BH43

NC_12

BH6

NC_13

BH5

NC_14

BG4

NC_15

BH3

NC_16

BF3

NC_17

BH2

NC_18

BG2

NC_19

BE2

NC_20

BG1

NC_21

BF1

NC_22

BD1

NC_23

BC1

NC_24

F1

NC_25

SP@CANTIGA_1p2

SP@CANTIGA_1p2

3

CFG

CFG

PM

PM

NC

NC

SM_VREF.Default use voltage divider

for poor layout cause +SMDDR_VREF not

meet spec.And Intel circuit PU/PD is

1K,But Check list PU/PD is 10K.

AP24

SA_CK_0

AT21

SA_CK_1

AV24

SB_CK_0

AU20

SB_CK_1

AR24

SA_CK#_0

AR21

SA_CK#_1

AU24

SB_CK#_0

AV20

SB_CK#_1

BC28

SA_CKE_0

AY28

SA_CKE_1

AY36

SB_CKE_0

RSVD

RSVD

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_DRAMRST#

DPLL_REF_CLK

DDR CLK/ CONTROL/COMPENSATION

DDR CLK/ CONTROL/COMPENSATION

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

ME JTAG

ME JTAG

CLK

CLK

DMI

DMI

GRAPHICS VID

GRAPHICS VID

MEHDA

MEHDA

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

MISC

MISC

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_VREF

SM_PWROK

SM_REXT

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

CLKREQ#

ICH_SYNC#

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

BB36

BA17

AY16

AV16

AR13

BD17

AY17

BF15

AY13

BG22

BH21

BF28

BH28

AV42

AR36

BF17

BC36

B38

A38

E41

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

AH34

N28

M28

G36

E36

K36

H36

B12

B28

B30

B29

C29

A28

M_CLK0

M_CLK1

M_CLK2

M_CLK3

M_CLK#0

M_CLK#1

M_CLK#2

M_CLK#3

M_RCOMP

M_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

R256 499/F_4R256 499/F_4

R257 D3@0_4R257 D3@0_4

CLK_DREFCLK

CLK_DREFCLK#

CLK_DREFSSCLK

CLK_DREFSSCLK#

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

MCH_CLVREF_R

DDPC_CTRLCLK

DDPC_DDCDATA

CLK_MCH_OE#

TSATN#

R180 56_4R180 56_4

HDA_BIT_CLK_HDMI

HDA_RST#_HDMI

HDA_SDIN_HDMI

HDA_SDOUT_HDMI

HDA_SYNC_HDMI

Impact ICH9M VCCHDA and VCCSUSHDA supply 1.5V/3.3V

NOTE:

If (G)MCH's HD Audio signals are connected to ICH9M

for iHDMI, VCCHDA and VCCSUSHDA on ICH9M should be

only on 1.5V. These power pins on ICH9M can be

supplied with 3.3V if and only if (G)MCH's HDA is not

connected to ICH9M. Consequently, only 1.5V

audio/modem codecs can be used on the platform.

M_CLK0 <16,17>

M_CLK1 <16,17>

M_CLK2 <16,17>

M_CLK3 <16,17>

M_CLK#0 <16,17>

M_CLK#1 <16,17>

M_CLK#2 <16,17>

M_CLK#3 <16,17>

M_CKE0 <16,17>

M_CKE1 <16,17>

M_CKE2 <16,17>

M_CKE3 <16,17>

M_CS#0 <16,17>

M_CS#1 <16,17>

M_CS#2 <16,17>

M_CS#3 <16,17>

M_ODT0 <16,17>

M_ODT1 <16,17>

M_ODT2 <16,17>

M_ODT3 <16,17>

SM_VREF=0.5*VCC_SM

SM_PWROK only for

DDR3.DDR2 PD only

SM_DRAMRST# only

for DDR3.DDR2 NC.

DDR3_DRAMRST# <17>

CLK_DREFCLK <2>

CLK_DREFCLK# <2>

CLK_DREFSSCLK <2>

CLK_DREFSSCLK# <2>

CLK_PCIE_3GPLL <2>

CLK_PCIE_3GPLL# <2>

DMI_TXN[3:0] <13>

DMI_TXP[3:0] <13>

DMI_RXN[3:0] <13>

DMI_RXP[3:0] <13>

CL_CLK0 <14>

CL_DATA0 <14>

MPWROK <14,32>

CL_RST#0 <14>

SDVO_CTRLCLK <20>

SDVO_CTRLDATA <20>

MCH_ICH_SYNC# <14>

HDA_BIT_CLK_HDMI <12>

HDA_RST#_HDMI <12>

HDA_SDIN_HDMI <12>

HDA_SDOUT_HDMI <12>

HDA_SYNC_HDMI <12>

2

Check list note : CL_REF=0.35VNB Thermal trip pin

+1.05V

C207

C207

0.1U/10V_4

0.1U/10V_4

DDPC_CTRL for HDMI port C

SDVO_CTRL for HDMI port B

If HDMI not support

HDA --> NC

VCC_HDA-->GND

Differential signal-->NC

M_RCOMP

R458 80.6/F_4R458 80.6/F_4

M_RCOMP#

R457 80.6/F_4R457 80.6/F_4

SM_VREF

SM_PWROK

R251 D3@10K/F_4R251 D3@10K/F_4

R248 10K/F_4R248 10K/F_4

INTEL FAE Suggest PD for Ext graphics

CLK_DREFCLK#

CLK_DREFCLK

CLK_DREFSSCLK#

CLK_DREFSSCLK

SM_RCOMP_VOH

C516

C516

2.2U/6V_6

2.2U/6V_6

SM_RCOMP_VOL

SM_RCOMP_VOL

C514

C514

2.2U/6V_6

2.2U/6V_6

+1.05V

R224

R224

1K/F_4

1K/F_4

R233

R233

511/F_4

511/F_4

<Checklist ver0.8>

If TSATN# is not used, then it must be terminated

with a 56-Ω pull-up resistor to VCCP.

<Pin out check issue>

Cantiga EDS 0.7 change Ball B12 to TSATN# from TSATN

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GMCH DMI

GMCH DMI

GMCH DMI

Date: Sheet of

Date: Sheet of

Date: Sheet of

+VDR_SUS

R250 10K/F_4R250 10K/F_4

R249 10K/F_4R249 10K/F_4

+VDR_SUS

HWPG_VDR <32,37>

R174 E@0_4R174 E@0_4

R182 E@0_4R182 E@0_4

R193 E@0_4R193 E@0_4

R183 E@0_4R183 E@0_4

C517

C517

R453

R453

0.01U/16V_4

0.01U/16V_4

3.01K/F_4

3.01K/F_4

R452

R452

C515

C515

1K/F_4

1K/F_4

0.01U/16V_4

0.01U/16V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

+VDR_SUS

R4541K/F_4 R4541K/F_4

ZY2 & ZY6

ZY2 & ZY6

ZY2 & ZY6

1A

1A

640Tuesday, April 08, 2008

640Tuesday, April 08, 2008

640Tuesday, April 08, 2008

1A

Page 7

5

4

3

2

1

U38C

IV&EV Dis/Enable setting

If LVDS no use,all signal can NC

L_BKLT_CTRL<19>

D D

INT_LVDS_BLON<19>

+3V

INT_LVDS_EDIDCLK<19>

INT_LVDS_EDIDDATA<19>

INT_LVDS_DIGON<19>

10/15: R178 Change to I@

INT_TXLCLKOUT-<18>

INT_TXLCLKOUT+<18>

INT_TXUCLKOUT-<18>

INT_TXUCLKOUT+<18>

INT_TXLOUT0-<18>

INT_TXLOUT1-<18>

INT_TXLOUT2-<18>

INT_TXLOUT0+<18>

INT_TXLOUT1+<18>

C C

INT_TXLOUT2+<18>

INT_TXUOUT0-<18>

INT_TXUOUT1-<18>

INT_TXUOUT2-<18>

INT_TXUOUT0+<18>

INT_TXUOUT1+<18>

INT_TXUOUT2+<18>

IV&EV Dis/Enable setting

Note :REV B: remove R475

& R471 short to GND

B B

INT_CRT_DDCCLK<18>

INT_CRT_DDCDAT<18>

INT_HSYNC<18>

HSYNC/VSYNC serial R place close to NB

A A

INT_VSYNC<18>

R203 I@10K_4R203 I@10K_4

R469 I@10K_4R469 I@10K_4

R178 I@2.37K/F_4R178 I@2.37K/F_4

INT_TXLCLKOUTINT_TXLCLKOUT+

INT_TXUCLKOUTINT_TXUCLKOUT+

INT_TXLOUT0INT_TXLOUT1INT_TXLOUT2-

INT_TXLOUT0+

INT_TXLOUT1+

INT_TXLOUT2+

INT_TXUOUT0INT_TXUOUT1INT_TXUOUT2-

INT_TXUOUT0+

INT_TXUOUT1+

INT_TXUOUT2+

R189 75_4R189 75_4

R195 75_4R195 75_4

R205 75_4R205 75_4

INT_CRT_BLU<18>

INT_CRT_GRN<18>

INT_CRT_RED<18>

R473 I@30.1_4R473 I@30.1_4

R474 I@30.1_4R474 I@30.1_4

CRTIREF pull down

for Teenah 1.3k ohm/F

for cantiga 1.02k ohm/F

L_CTRL_CLK

L_CTRL_DATA

INT_TV_COMP

INT_TV_Y/G

INT_TV_C/R

INT_CRT_BLU

INT_CRT_GRN

INT_CRT_RED

HSYNC_G

CRTIREF

VSYNC_G

U38C

L32

L_BKLT_CTRL

G32

L_BKLT_EN

M32

L_CTRL_CLK

M33

L_CTRL_DATA

K33

L_DDC_CLK

J33

L_DDC_DATA

M29

L_VDD_EN

C44

LVDS_IBG

B43

LVDS_VBG

E37

LVDS_VREFH

E38

LVDS_VREFL

C41

LVDSA_CLK#

C40

LVDSA_CLK

B37

LVDSB_CLK#

A37

LVDSB_CLK

H47

LVDSA_DATA#_0

E46

LVDSA_DATA#_1

G40

LVDSA_DATA#_2

A40

LVDSA_DATA#_3

H48

LVDSA_DATA_0

D45

LVDSA_DATA_1

F40

LVDSA_DATA_2

B40

LVDSA_DATA_3

A41

LVDSB_DATA#_0

H38

LVDSB_DATA#_1

G37

LVDSB_DATA#_2

J37

LVDSB_DATA#_3

B42

LVDSB_DATA_0

G38

LVDSB_DATA_1

F37

LVDSB_DATA_2

K37

LVDSB_DATA_3

F25

TVA_DAC

H25

TVB_DAC

K25

TVC_DAC

H24

TV_RTN

C31

TV_DCONSEL_0

E32

TV_DCONSEL_1

E28

CRT_BLUE

G28

CRT_GREEN

J28

CRT_RED

G29

CRT_IRTN

H32

CRT_DDC_CLK

J32

CRT_DDC_DATA

J29

CRT_HSYNC

E29

CRT_TVO_IREF

L29

CRT_VSYNC

SP@CANTIGA_1p2

SP@CANTIGA_1p2

L<0.5" , If PCIE not support

still connect to +VCC_PEG

EXP_A_COMPX

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

LVDS

LVDS

TV

TV

VGA

VGA

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

T37

T36

H44

J46

L44

L40

N41

P48

N44

T43

U43

Y43

Y48

Y36

AA43

AD37

AC47

AD39

H43

J44

L43

L41

N40

P47

N43

T42

U42

Y42

W47

Y37

AA42

AD36

AC48

AD40

J41

M46

M47

M40

M42

R48

N38

T40

U37

U40

Y40

AA46

AA37

AA40

AD43

AC46

J42

L46

M48

M39

M43

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

C_PEG_TXN0

C_PEG_TXN1

C_PEG_TXN2

C_PEG_TXN3

C_PEG_TXN4

C_PEG_TXN5

C_PEG_TXN6

C_PEG_TXN7

C_PEG_TXN8

C_PEG_TXN9

C_PEG_TXN10

C_PEG_TXN11

C_PEG_TXN12

C_PEG_TXN13

C_PEG_TXN14

C_PEG_TXN15

C_PEG_TXP0

C_PEG_TXP1

C_PEG_TXP2

C_PEG_TXP3

C_PEG_TXP4

C_PEG_TXP5

C_PEG_TXP6

C_PEG_TXP7

C_PEG_TXP8

C_PEG_TXP9

C_PEG_TXP10

C_PEG_TXP11

C_PEG_TXP12

C_PEG_TXP13

C_PEG_TXP14

C_PEG_TXP15

R215 49.9/F_4R215 49.9/F_4

C189 .1U/10V_4C189 .1U/10V_4

C196 .1U/10V_4C196 .1U/10V_4

C197 .1U/10V_4C197 .1U/10V_4

C208 .1U/10V_4C208 .1U/10V_4

C218 E@.1U/10V_4C218 E@.1U/10V_4

C228 E@.1U/10V_4C228 E@.1U/10V_4

C233 E@.1U/10V_4C233 E@.1U/10V_4

C242 E@.1U/10V_4C242 E@.1U/10V_4

C249 E@.1U/10V_4C249 E@.1U/10V_4

C250 E@.1U/10V_4C250 E@.1U/10V_4

C252 E@.1U/10V_4C252 E@.1U/10V_4

C264 E@.1U/10V_4C264 E@.1U/10V_4

C269 E@.1U/10V_4C269 E@.1U/10V_4

C270 E@.1U/10V_4C270 E@.1U/10V_4

C274 E@.1U/10V_4C274 E@.1U/10V_4

C276 E@.1U/10V_4C276 E@.1U/10V_4

C188 .1U/10V_4C188 .1U/10V_4

C194 .1U/10V_4C194 .1U/10V_4

C195 .1U/10V_4C195 .1U/10V_4

C206 .1U/10V_4C206 .1U/10V_4

C220 E@.1U/10V_4C220 E@.1U/10V_4

C224 E@.1U/10V_4C224 E@.1U/10V_4

C230 E@.1U/10V_4C230 E@.1U/10V_4

C236 E@.1U/10V_4C236 E@.1U/10V_4

C245 E@.1U/10V_4C245 E@.1U/10V_4

C251 E@.1U/10V_4C251 E@.1U/10V_4

C254 E@.1U/10V_4C254 E@.1U/10V_4

C256 E@.1U/10V_4C256 E@.1U/10V_4

C259 E@.1U/10V_4C259 E@.1U/10V_4

C271 E@.1U/10V_4C271 E@.1U/10V_4

C275 E@.1U/10V_4C275 E@.1U/10V_4

C277 E@.1U/10V_4C277 E@.1U/10V_4

PEG_RXN[15:0] <18>

Can support reversal routing.If CFG9=1, PCI

Express is normal operation. If CFG9=0,

then PEG_TXP0 becomes PEG_TXP15, PEG_TXP1

becomes PEG_TXP14, PEG_TXP2 becomes

PEG_TXP13, etc. similarly for PEG_RXP[15:0]

and PEG_RXN[15:0]

PEG_RXP[15:0] <18>

Rev: B Change P/N

+1.05V

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

IV&EV Dis/Enable setting

<5/31>Montevina_Schematics_Checklist_Rev0_8

a)For TVOUT Disabled, TV_DCONSEL[1:0] Connect to GND. But

design guide Rev0.7 show NC.What is correct.

b)For CRT DAC Disable, CRT_DDC_CLK, CRT_DDC_DATA .

CRT_HSYNC, CRT_VSYNCThese signals should be connected to

GND. But design guide Rev0.7 show NC, Intel suggest follow

Design guide.

PEG_TXN[15:0] <18>

PEG_TXP[15:0] <18>

<check list>

For EV@

Connect to GND

CRT R/G/B

HSYNC/VSYNC

CRTIREF

R181 SP@0 & 1.02K/F_4R181 SP@0 & 1.02K/F_4

<check list>

For IV@

Connect to 150ohm

CRT R/G/B

Connect to 1.02Kohm

CRTIREF

CRTIREF

11/28: Change R181 1.02K ohm P/N

R472 E@0_4R472 E@0_4

R468 E@0_4R468 E@0_4

R186 SP@150_4R186 SP@150_4

R190 SP@150_4R190 SP@150_4

R197 SP@150_4R197 SP@150_4

HSYNC_G

VSYNC_G

INT_CRT_BLU

INT_CRT_GRN

INT_CRT_RED

10/15: Change to SP@

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GMCH VGA

GMCH VGA

GMCH VGA

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :

ZY2 & ZY6

ZY2 & ZY6

ZY2 & ZY6

of

of

of

740Tuesday, April 08, 2008

740Tuesday, April 08, 2008

740Tuesday, April 08, 2008

1

1A

1A

1A

Page 8

5

4

3

2

1

M_A_DQ[63:0]<16,17>

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

U38D

U38D

AJ38

AJ41

AN38

AM38

AJ36

AJ40

AM44

AM42

AN43

AN44

AU40

AT38

AN41

AN39

AU44

AU42

AV39

AY44

BA40

BD43

AV41

AY43

BB41

BC40

AY37

BD38

AV37

AT36

AY38

BB38

AV36

AW36

BD13

AU11

BC11

BA12

AU13

AV13

BD12

BC12

BB9

BA9

AU10

AV9

BA11

BD9

AY8

BA6

AV5

AV7

AT9

AN8

AU5

AU6

AT5

AN10

AM11

AM5

AJ9

AJ8

AN12

AM13

AJ11

AJ12

SP@CANTIGA_1p2

SP@CANTIGA_1p2

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

BD21

SA_BS_0

BG18

SA_BS_1

AT25

SA_BS_2

BB20

SA_RAS#

BD20

SA_CAS#

AY20

SA_WE#

AM37

SA_DM_0

AT41

SA_DM_1

AY41

SA_DM_2

AU39

SA_DM_3

BB12

SA_DM_4

AY6

SA_DM_5

AT7

SA_DM_6

AJ5

SA_DM_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

AJ44

AT44

BA43

BC37

AW12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW24

BC21

BG26

BH26

BH17

AY25

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_BS0 <16,17>

M_A_BS1 <16,17>

M_A_BS2 <16,17>

M_A_RAS# <16,17>

M_A_CAS# <16,17>

M_A_WE# <16,17>

M_A_DM[7:0] <16,17>

M_A_DQS[7:0] <16,17>

M_A_DQS#[7:0] <16,17>

M_A_A[14:0] <16,17>

M_B_DQ[63:0]<16,17>

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

U38E

U38E

AK47

SB_DQ_0

AH46

SB_DQ_1

AP47

SB_DQ_2

AP46

SB_DQ_3

AJ46

SB_DQ_4

AJ48

SB_DQ_5

AM48

SB_DQ_6

AP48

SB_DQ_7

AU47

SB_DQ_8

AU46

SB_DQ_9

BA48

SB_DQ_10

AY48

SB_DQ_11

AT47

SB_DQ_12

AR47

SB_DQ_13

BA47

SB_DQ_14

BC47

SB_DQ_15

BC46

SB_DQ_16

BC44

SB_DQ_17

BG43

SB_DQ_18

BF43

SB_DQ_19

BE45

SB_DQ_20

BC41

SB_DQ_21

BF40

SB_DQ_22

BF41

SB_DQ_23

BG38

SB_DQ_24

BF38

SB_DQ_25

BH35

SB_DQ_26

BG35

SB_DQ_27

BH40

SB_DQ_28

BG39

SB_DQ_29

BG34

SB_DQ_30

BH34

SB_DQ_31

BH14

SB_DQ_32

BG12

SB_DQ_33

BH11

SB_DQ_34

BG8

SB_DQ_35

BH12

SB_DQ_36

BF11

SB_DQ_37

BF8

SB_DQ_38

BG7

SB_DQ_39

BC5

SB_DQ_40

BC6

SB_DQ_41

AY3

SB_DQ_42

AY1

SB_DQ_43

BF6

SB_DQ_44

BF5

SB_DQ_45

BA1

SB_DQ_46

BD3

SB_DQ_47

AV2

SB_DQ_48

AU3

SB_DQ_49

AR3

SB_DQ_50

AN2

SB_DQ_51

AY2

SB_DQ_52

AV1

SB_DQ_53

AP3

SB_DQ_54

AR1

SB_DQ_55

AL1

SB_DQ_56

AL2

SB_DQ_57

AJ1

SB_DQ_58

AH1

SB_DQ_59

AM2

SB_DQ_60

AM3

SB_DQ_61

AH3

SB_DQ_62

AJ3

SB_DQ_63

SP@CANTIGA_1p2

SP@CANTIGA_1p2

BC16

SB_BS_0

BB17

SB_BS_1

BB33

SB_BS_2

AU17

SB_RAS#

BG16

SB_CAS#

BF14

SB_WE#

AM47

SB_DM_0

AY47

SB_DM_1

BD40

SB_DM_2

BF35

SB_DM_3

BG11

SB_DM_4

BA3

SB_DM_5

AP1

SB_DM_6

AK2

SB_DM_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

AL47

AV48

BG41

BG37

BH9

BB2

AU1

AN6

AL46

AV47

BH41

BH37

BG9

BC2

AT2

AN5

AV17

BA25

BC25

AU25

AW25

BB28

AU28

AW28

AT33

BD33

BB16

AW33

AY33

BH15

AU33

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_BS0 <16,17>

M_B_BS1 <16,17>

M_B_BS2 <16,17>

M_B_RAS# <16,17>

M_B_CAS# <16,17>

M_B_WE# <16,17>

M_B_DM[7:0] <16,17>

M_B_DQS[7:0] <16,17>

M_B_DQS#[7:0] <16,17>

M_B_A[14:0] <16,17>

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GMCH DDRII

GMCH DDRII

GMCH DDRII

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :

ZY2 & ZY6

ZY2 & ZY6

ZY2 & ZY6

840Tuesday, April 08, 2008

840Tuesday, April 08, 2008

840Tuesday, April 08, 2008

1

1A

1A

1A

of

of

of

Page 9

5

Power consumption reference to Intel

644135 Cantiga chipset EDS Volume1.

Section 10

GM TDP 10.5~12W

GS TDP 7~8W

PM TDP 7W

D D

U38G

+VDR_SUS

+

+

C244

C519

C519

22U/6V_8

22U/6V_8

Place on the edga

VCC_SM(1.8V)

DDR2(800M)

3000mA_S0 , 1mA_S3

DDR2(667M) : 2600mA_S0

DDR3(1067M) : 4140mA_S0

C C

B B

C244

C521

C521

0.1U/10V_4

0.1U/10V_4

22U/6V_8

22U/6V_8

1.05V

Graphics core

VCC_AXG

VCC_AXG_NCTF

6326.84mA

Voltage regulator is

shared between the

Graphics Core Rail,

VCCA_HPLL, VCCA_MPLL,

VCCA_PEG_PLLVCCD_PEG_PLL,

VCCA_SM_CK, VCCA_DPLLA,

VCCA_DPLLB, VCCD_HPLL,

VCCA_SM, VCC_AXF

C518

C518

330U/2.5V_7

330U/2.5V_7

+1.05V_AXG

R242 I@10/F_4R242 I@10/F_4

R238 I@10/F_4R238 I@10/F_4

+1.05V_AXG

AP33

AN33

BH32

BG32

BF32

BD32

BC32

BB32

BA32

AY32

AW32

AV32

AU32

AT32

AR32

AP32

AN32

BH31

BG31

BF31

BG30

BH29

BG29

BF29

BD29

BC29

BB29

BA29

AY29

AW29

AV29

AU29

AT29

AR29

AP29

BA36

BB24

BD16

BB21

AW16

AW13

AT13

AE25

AB25

AA25

AE24

AC24

AA24

AE23

AC23

AB23

AA23

AJ21

AG21

AE21

AC21

AA21

AH20

AF20

AE20

AC20

AB20

AA20

AM15

AL15

AE15

AJ15

AH15

AG15

AF15

AB15

AA15

AN14

AM14

AJ14

AH14

Y26

Y24

Y21

T17

T16

Y15

V15

U15

U14

T14

U38G

VCC_SM_1