Page 1

5

4

3

2

1

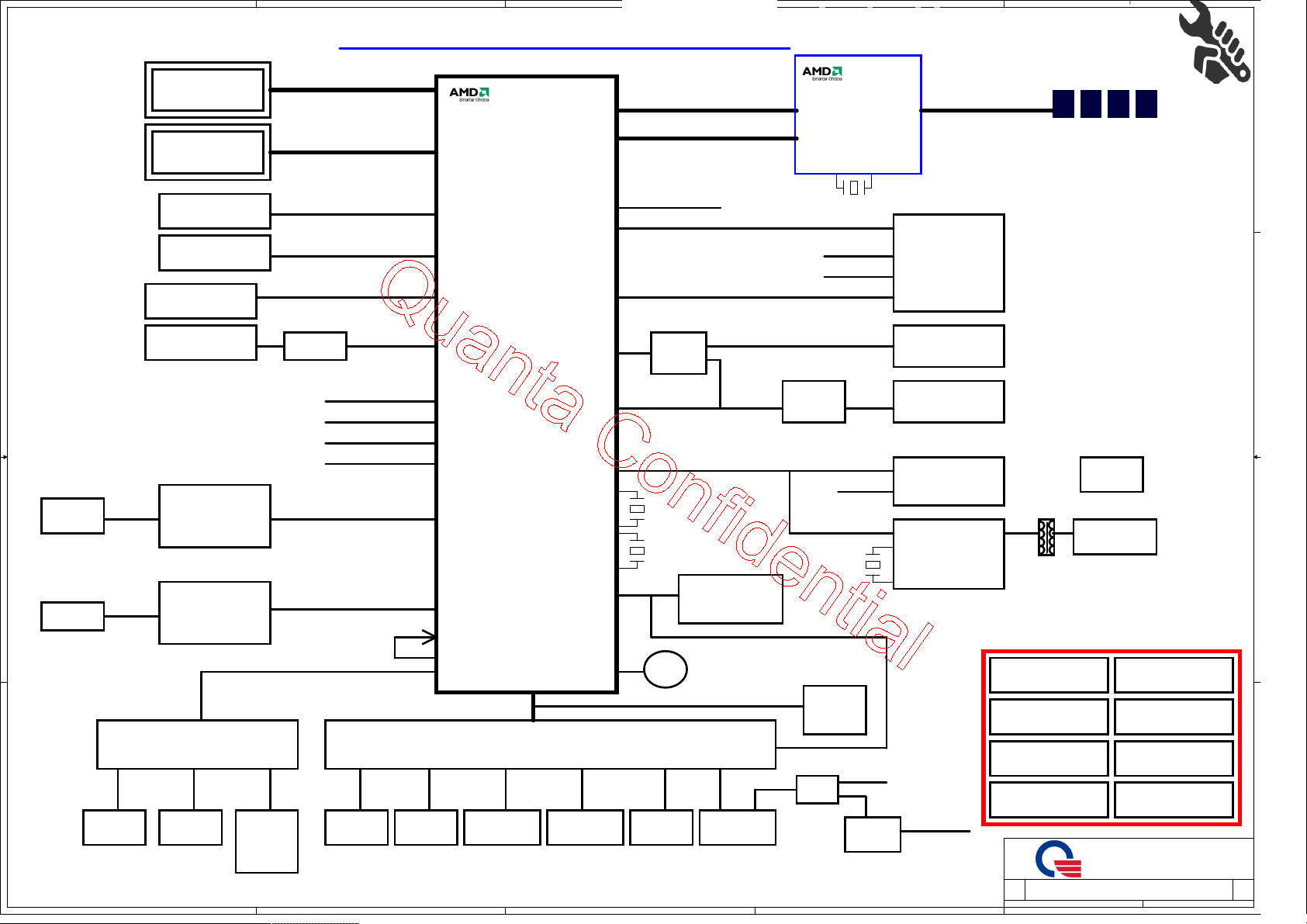

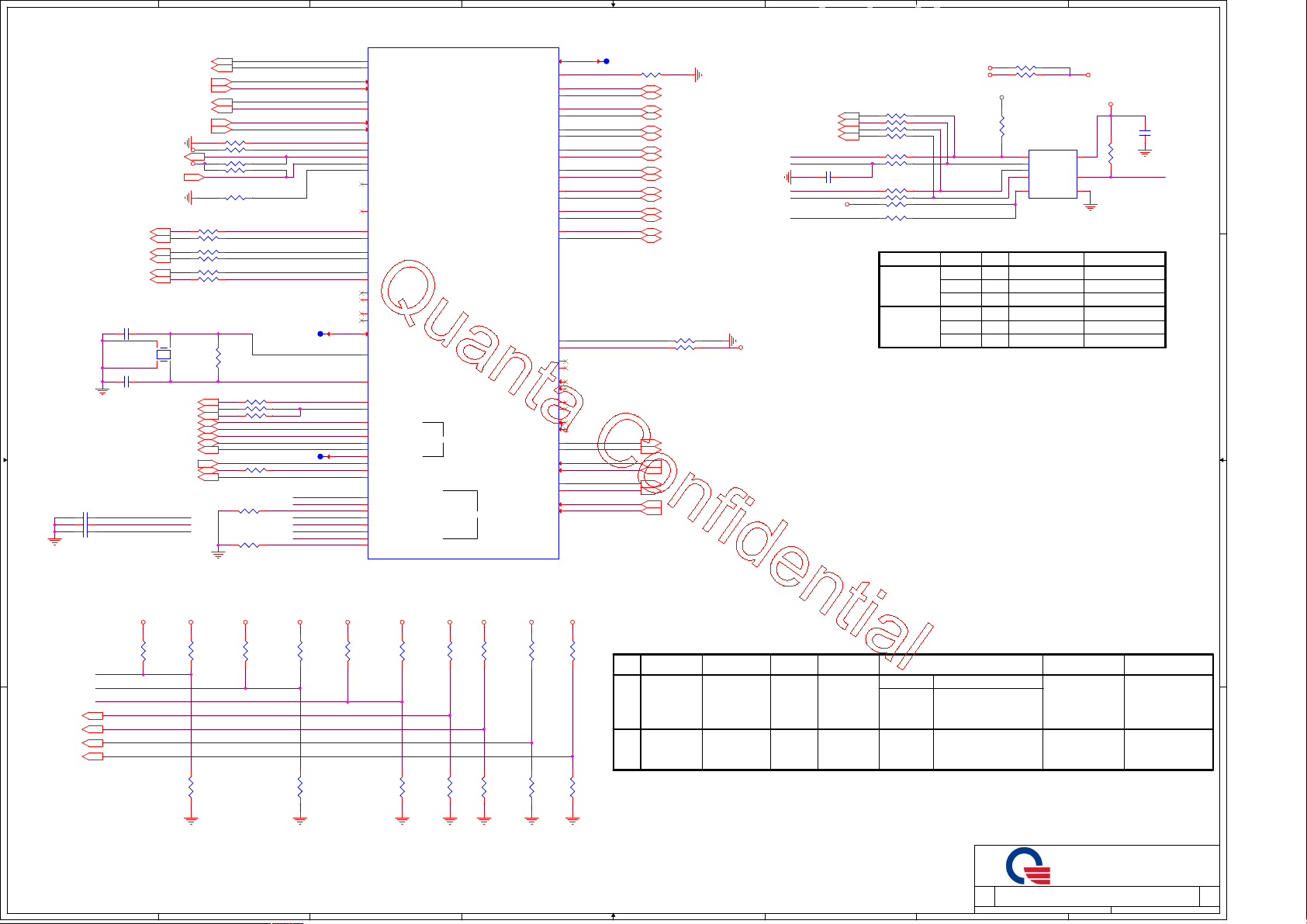

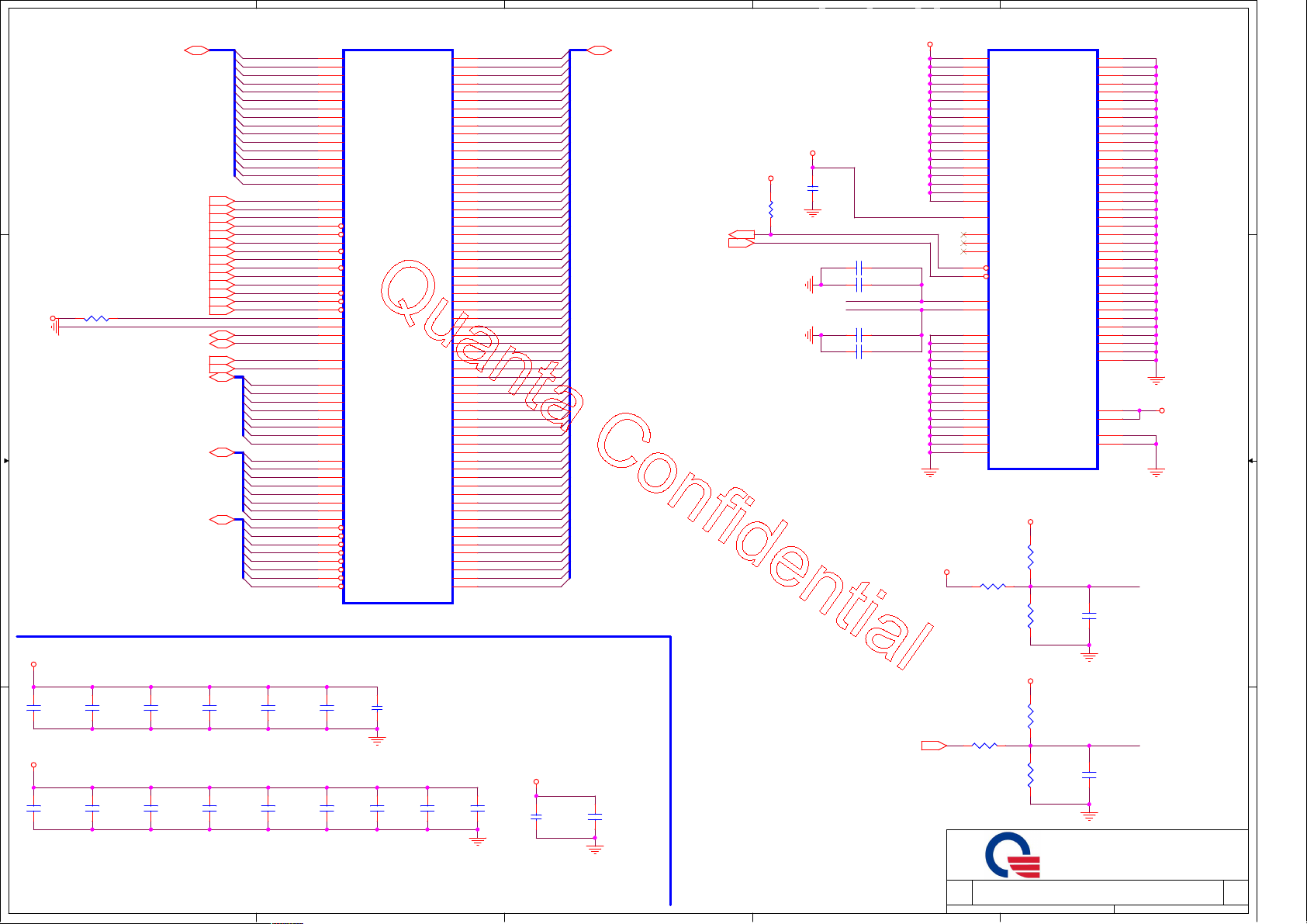

ZRZ/ZRZL BLOCK DIAGRAM

DDRIII-SODIMM1

P9

D D

DDRIII-SODIMM2

P10

SATA - HDD

SATA - ODD

USB3 Con.

C C

USB3 Con.

P24

P24

P25

P25 P25

Cardreader

CR Con.

P25

B B

USB2 DB

RTS5170-GRT

IO Board

Connector

P25

P25

Azalia

Channel A (CZ)

Channel B

USB Charger

USB2-1 (CCD)

USB2-2 (Touchpad)(CZ-L)

USB2-4 (M.2)

USB2-3 (Touch Screen)

SATA 0

SATA 1

USB3 - 3

USB2 - 7

USB3 - 2

USB2 - 6

USB2-3

USB2-0

FP4

TDP:15W

IMC

CARRIZO(15h)

60h-6Fh

CARRIZO-L(16h)

30h-3Fh

SATA0

SATA1

USB3.0

APU

BGA 968

USB2.0

P2,3,4,5,6,7,8

CLK

HDA

LPC

PEG

TX/RX

DP0

DP1

DP2

GPP

SPI

RTC

PCIE 0~3

PCIE 4~7 (CZ)

I2C-0 (Touc hpad)(CZ)

I2C-1 (Touc h Screen)( CZ)I2C

DP0

PS8339B

DP1

DP DeMUX

P18

DP2

X'TAL

32.768KHz

X'TAL 48MHz

SPI ROM 8M

CZ:1.8V / CZ-L:3.3V

BATT

P7

P6

GEO GPU

Channel

Meso XT 25W

Exo XT 25W

S3 23mm X 23mm

P11,12,13,14,15 P16

X'TAL

27.0MHz

eDP/TS/CCD Con.

USB2-2 (Touch)

USB2-5 (CCD)

P17

HDMI Con.

P18

DP to VGA

IT6516

P19

GPP1

USB2-4

GPP0

CRT Con.

M.2

WLAN+BT

w/ Debug

P19

P21

LAN

X'TAL

25MHz

RTL8111H

P20

VRAM DDR3-128Mb*16*4 = 1GB

VRAM DDR3-256Mb*16*4 = 2GB

CZ@ :CARRIZO

CZL@ :CARRIZO-L

SP@ :special part

UBT@ :USB TS

I2CT@ :I2C TS(only CZ reserve)

EV@ :GPU

Maso@ :Maso GPU

Exo@ :Exo GPU

EV_SP@:GPU special part

TPM@ :TPM

TPM_I@:SLB9655TT1.2

TPM_N@:NPCT650AAAWX

GS@ :G-sensor

HDT@ : Debug

KBL@ :KB Backlight

IOAC@ :IOAC

NIOAC@:non-IOAC

BQ24737

Batery Charger

VRAM

Reset Button

RJ45 Con.

ISL62771

CPU CORE / VDDNB

P30

P20

P34,35

TPM

NPCT650

0ohm

option

P23

I2C-0 (CZ)

CY7C65211

USB to I2C

(CZ-L)

2

USB2-1 (CZ-L)

TYPE1 : CZ

TYPE2 : CZL

AUDIO CODEC

ALC25 5-CG

A A

Phone

Jack

Speaker DMIC

P22

5

P22

P22 P30

Knowles

NeoMEMS

P22

LED

P26

K/B Con.

4

K/B BL Con.

P28 P17 P28 P27

IT8987E/BX

P28

EC

HALL SENSOR

FAN Con.

(DAC)

3

PS/2

Touch Pad

Con.

TPS51225

3V/5V

RT8237

0.95V

G5316

+1.5V_SUS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

RT8068

1.8V

P31

ISL62771

VGPU CORE

P32

RT8068

GPU_POWER / VDDC_GFX

P33

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZRZ

ZRZ

ZRZ

141Wednesday, March 18, 2015

141Wednesday, March 18, 2015

1

141Wednesday, March 18, 2015

P36

P37

P38

1A

1A

1A

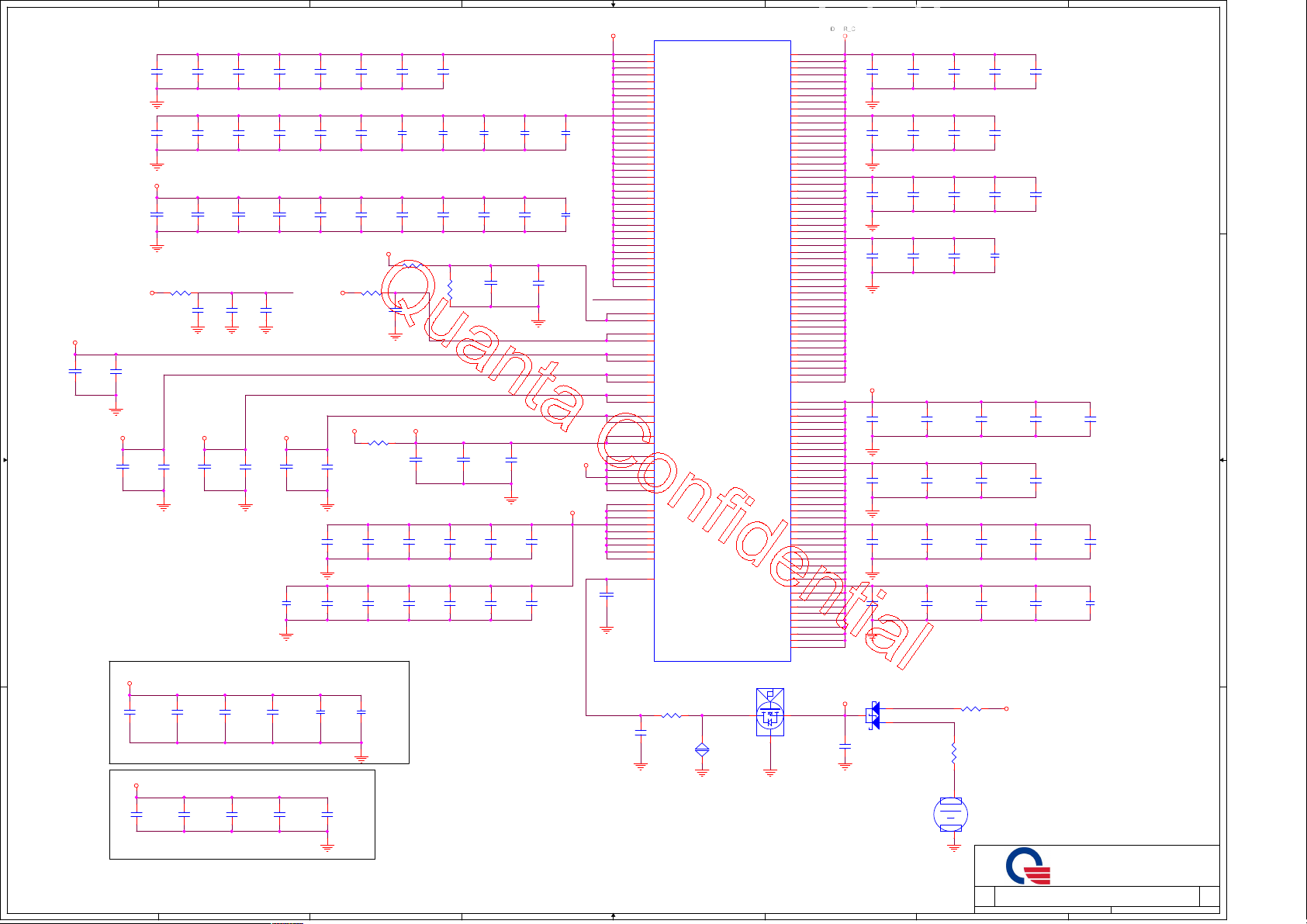

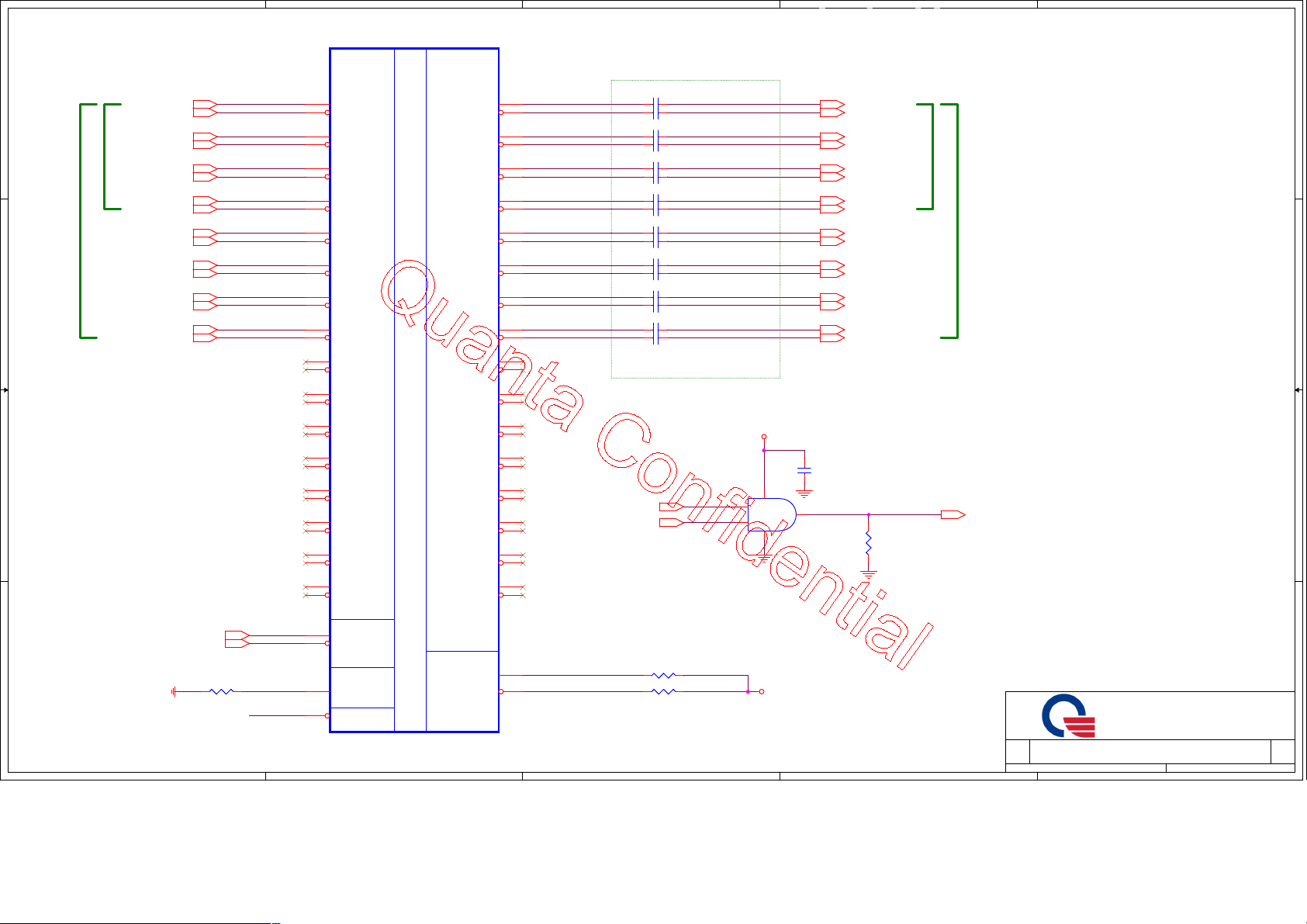

Page 2

1

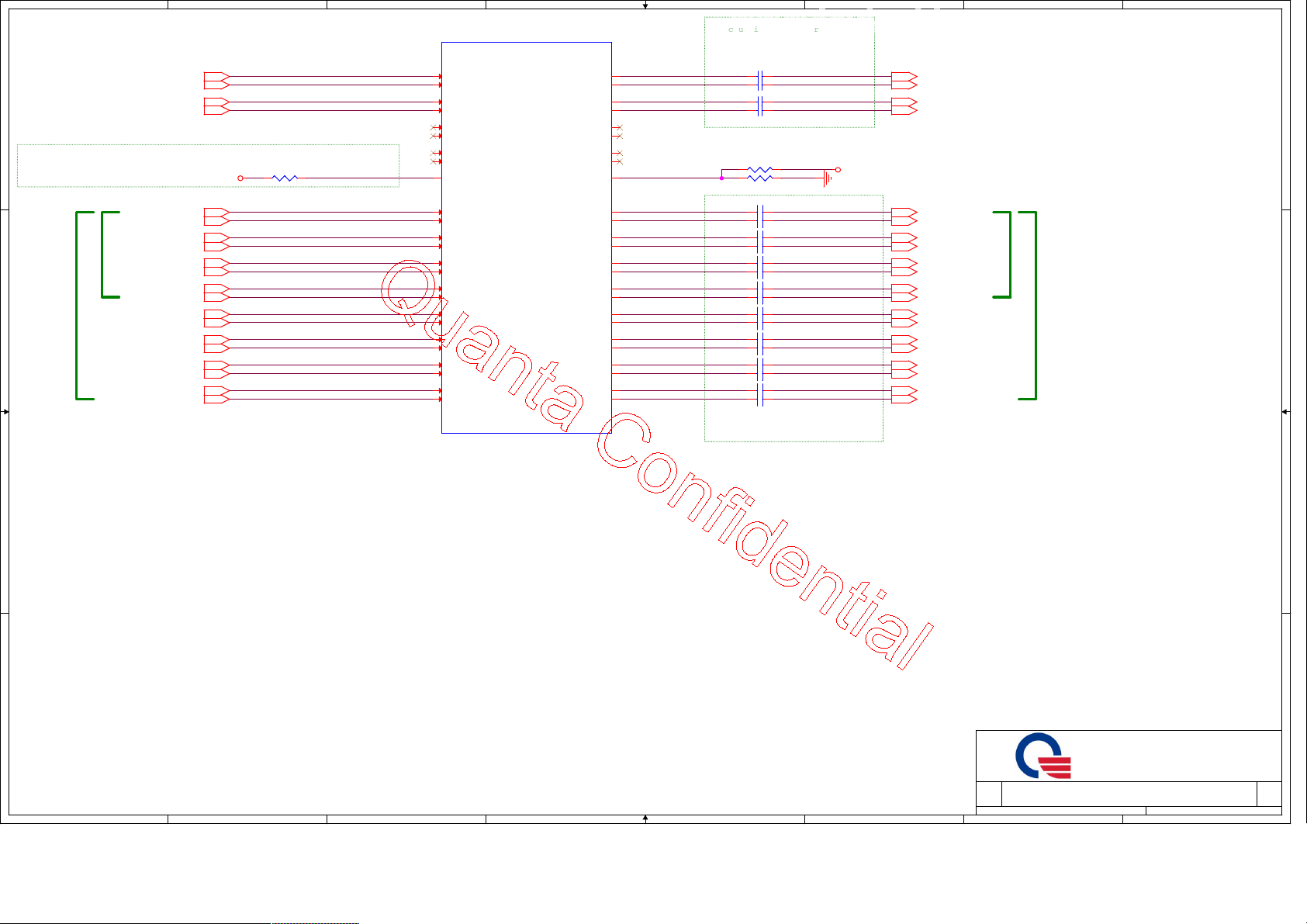

(CPU)

LAN

A A

1.05V VDDP only for CZ with DDR-2133 memory

If running DDR-1866 or slower memory,

Platform VDDP should be set to 0.95V

WLAN

PCIE_RXP0[20]

PCIE_RXN0[20]

PCIE_RXP1[21]

PCIE_RXN1[21]

VDDP_0.95V

2

CZ: (196R_CS11962FB00)

CZL:(1.69K_CS21692FB01)

R399 SP@196/F_4

3

U10

P_GPP_RXP[ 0]

U9

P_GPP_RXN[ 0]

T6

P_GPP_RXP[ 1]

T5

P_GPP_RXN[ 1]

T9

P_GPP_RXP[ 2]

T8

P_GPP_RXN[ 2]

P7

P_GPP_RXP[ 3]

P6

P_GPP_RXN[ 3]

P_TX_ZVDD_09 5 P_RX_ZVDD_095

U7

P_ZVDDP

U28B

PCIE

4

P_GPP_TXP[0 ]

P_GPP_TXN[0 ]

P_GPP_TXP[1 ]

P_GPP_TXN[1 ]

P_GPP_TXP[2 ]

P_GPP_TXN[2 ]

P_GPP_TXP[3 ]

P_GPP_TXN[3 ]

P_ZVSS/ P_RX_ZVD DP

R1

R2

R4

R3

N1

N2

N4

N3

U6

PCIE_TXP0_C

PCIE_TXN0_C

PCIE_TXP1_C

PCIE_TXN1_C

5

AC-coupling capactior

CZ :Gen3 (220nF) CH4222K9B04

CZL:Gen1/2 (100nF) CH4103K1B08

Current device no Gen3

C558 0.1U/16V/X7R_4

C557 0.1U/16V/X7R_4

C544 0.1U/16V/X7R_4

C543 0.1U/16V/X7R_4

R400 CZL@1K/F_4

R401 CZ@196/F_4

VDDP_0.95V

6

PCIE_TXP0 [20]

PCIE_TXN0 [20]

PCIE_TXP1 [21]

PCIE_TXN1 [21]

LAN

WLAN

7

8

P10

L10

P9

N6

N5

N9

N8

L7

L6

L9

K6

K5

K9

K8

J7

J6

P_GFX_R XP[0]

P_GFX_R XN[0]

P_GFX_R XP[1]

P_GFX_R XN[1]

P_GFX_R XP[2]

P_GFX_R XN[2]

P_GFX_R XP[3]

P_GFX_R XN[3]

P_GFX_R XP[4]

P_GFX_R XN[4]

P_GFX_R XP[5]

P_GFX_R XN[5]

P_GFX_R XP[6]

P_GFX_R XN[6]

P_GFX_R XP[7]

P_GFX_R XN[7]

FP4 REV 0.93

SP@FP4

PEG_RXP0[11]

PEG_RXN0[11]

PEG_RXP1[11]

PEG_RXN1[11]

PEG_RXP2[11]

PEG_RXN2[11]

PEG_RXP3[11]

X4 : CARRIZO-L (G EN2)

B B

C C

X8 : CARRIZO (GEN3 )

PEG_RXN3[11]

PEG_RXP4[11]

PEG_RXN4[11]

PEG_RXP5[11]

PEG_RXN5[11]

PEG_RXP6[11]

PEG_RXN6[11]

PEG_RXP7[11]

PEG_RXN7[11]

P_GFX_TXP[ 0]

P_GFX_TXN[ 0]

P_GFX_TXP[ 1]

P_GFX_TXN[ 1]

P_GFX_TXP[ 2]

P_GFX_TXN[ 2]

P_GFX_TXP[ 3]

P_GFX_TXN[ 3]

P_GFX_TXP[ 4]

P_GFX_TXN[ 4]

P_GFX_TXP[ 5]

P_GFX_TXN[ 5]

P_GFX_TXP[ 6]

P_GFX_TXN[ 6]

P_GFX_TXP[ 7]

P_GFX_TXN[ 7]

M2

PEG_TXP0_C

M1

PEG_TXN0_C

L1

PEG_TXP1_C

L2

PEG_TXN1_C

L4

PEG_TXP2_C

L3

PEG_TXN2_C

J1

PEG_TXP3_C

J2

PEG_TXN3_C

J4

PEG_TXP4_C

J3

PEG_TXN4_C

H2

PEG_TXP5_C

H1

PEG_TXN5_C

G1

PEG_TXP6_C

G2

PEG_TXN6_C

G4

PEG_TXP7_C

G3

PEG_TXN7_C

C559 EV_SP@0.22u/10V_4

C560 EV_SP@0.22u/10V_4

C546 EV_SP@0.22u/10V_4

C545 EV_SP@0.22u/10V_4

C561 EV_SP@0.22u/10V_4

C562 EV_SP@0.22u/10V_4

C548 EV_SP@0.22u/10V_4

C547 EV_SP@0.22u/10V_4

C563 EV_SP@0.22u/10V_4

C564 EV_SP@0.22u/10V_4

C550 EV_SP@0.22u/10V_4

C549 EV_SP@0.22u/10V_4

C565 EV_SP@0.22u/10V_4

C566 EV_SP@0.22u/10V_4

C551 EV_SP@0.22u/10V_4

C552 EV_SP@0.22u/10V_4

AC-coupling capactior

CZ-8Lane :Gen3(220nF) CH4222K9B04

CZL-4Lane:Gen1/2(100nF) CH4103K1B08

PEG_TXP0 [11]

PEG_TXN0 [11]

PEG_TXP1 [11]

PEG_TXN1 [11]

PEG_TXP2 [11]

PEG_TXN2 [11]

PEG_TXP3 [11]

PEG_TXN3 [11]

PEG_TXP4 [11]

PEG_TXN4 [11]

PEG_TXP5 [11]

PEG_TXN5 [11]

PEG_TXP6 [11]

PEG_TXN6 [11]

PEG_TXP7 [11]

PEG_TXN7 [11]

X4 : CARRIZO-L (G EN2)

X8 : CARRIZO (GEN3 )

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

FP4 PCIE I/F(1/7)

FP4 PCIE I/F(1/7)

FP4 PCIE I/F(1/7)

Date: Sheet of

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

PROJECT :

7

ZRZ

ZRZ

ZRZ

1A

1A

1A

241Friday, March 06, 2015

241Friday, March 06, 2015

241Friday, March 06, 2015

8

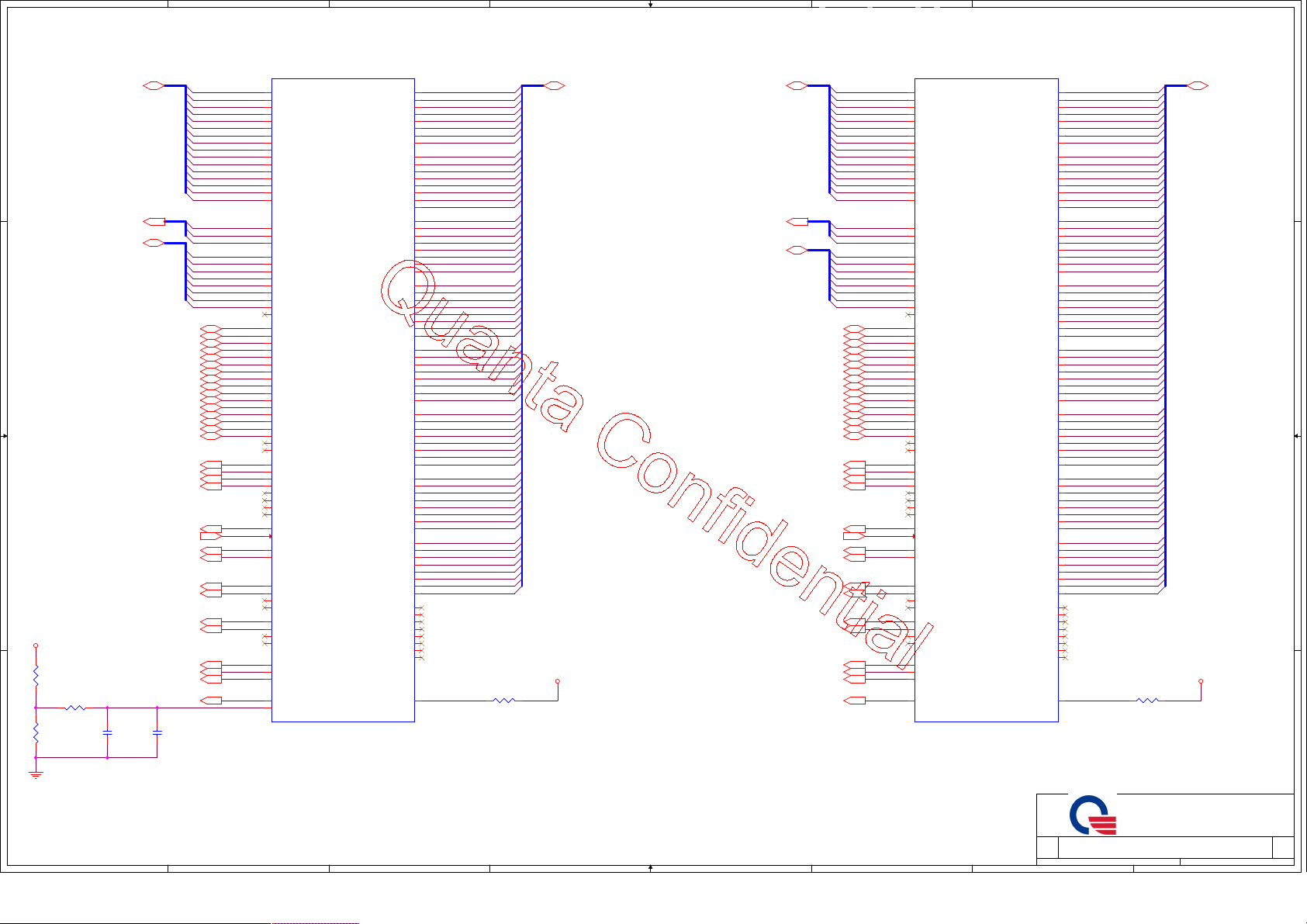

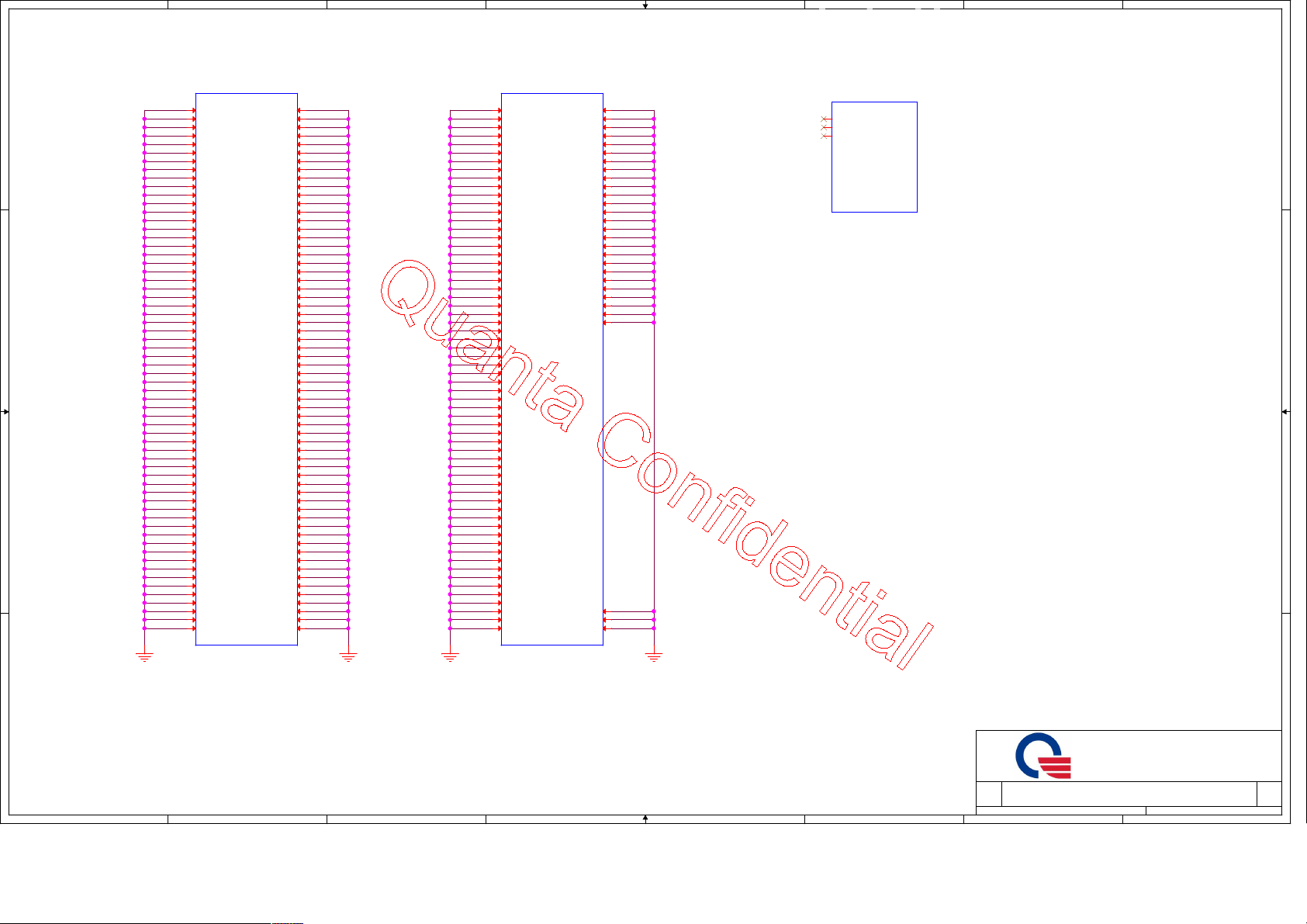

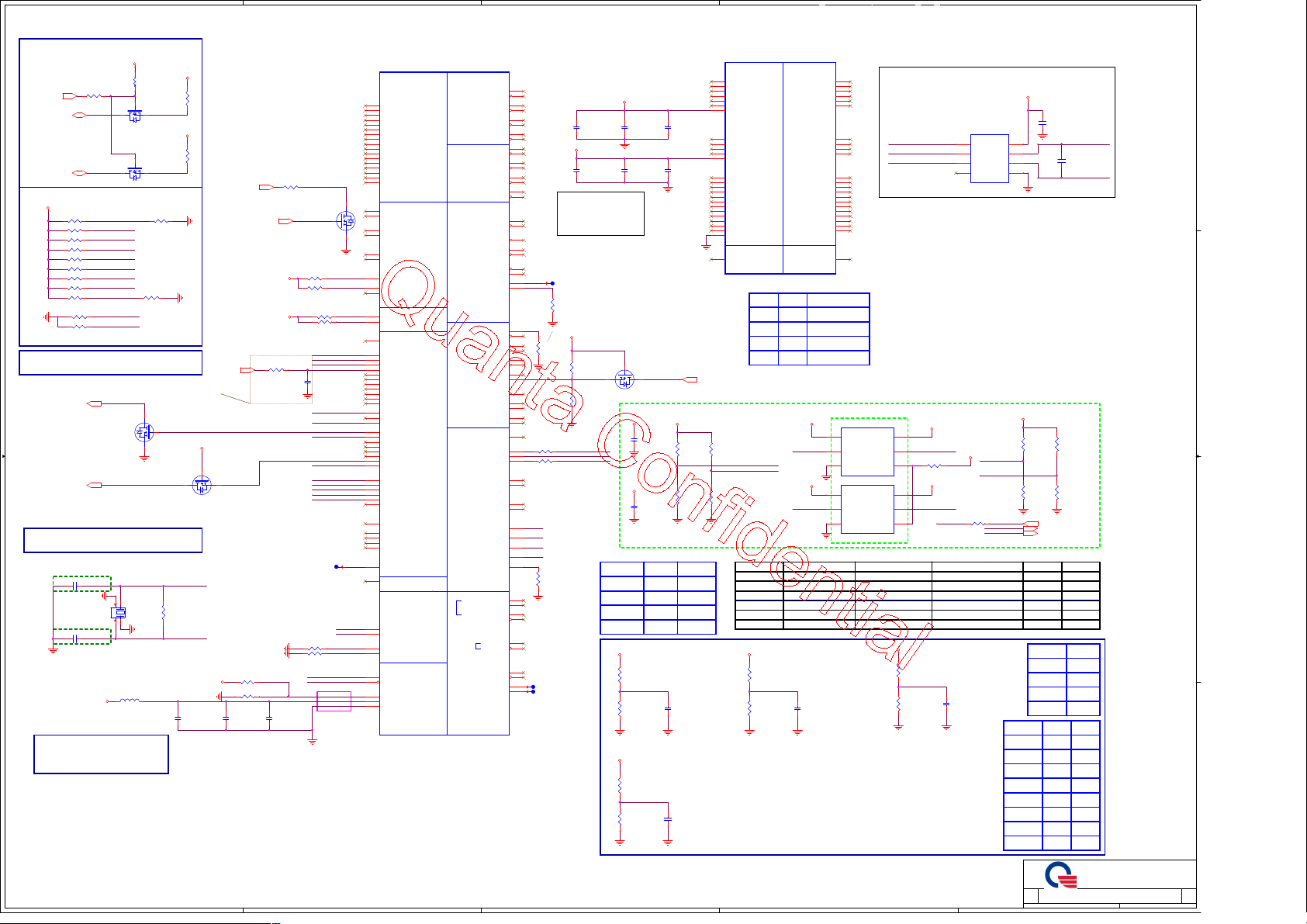

Page 3

1

2

3

4

5

6

7

8

(CPU)

Channel A:CZ ONLY

AE28

M_A_A0

M_A_A1

M_A_A2

A A

M_A_BS#[2..0][9]

M_A_DM[7..0][9]

B B

C C

+1.5VSUS

R521

1K/F_4

R522 *short_4

R523

1K/F_4

D D

C606

0.1u/16V_4

PLACE CLOSE TO APU

M_A_DQS0[9]

M_A_DQS#0[9]

M_A_DQS1[9]

M_A_DQS#1[9]

M_A_DQS2[9]

M_A_DQS#2[9]

M_A_DQS3[9]

M_A_DQS#3[9]

M_A_DQS4[9]

M_A_DQS#4[9]

M_A_DQS5[9]

M_A_DQS#5[9]

M_A_DQS6[9]

M_A_DQS#6[9]

M_A_DQS7[9]

M_A_DQS#7[9]

M_A_CLK0[9]

M_A_CLK0#[9]

M_A_CLK1[9]

M_A_CLK1#[9]

M_A_RESET#[9]

M_A_EVENT#[9]

M_A_CKE0[9]

M_A_CKE1[9]

M_A_ODT0[9]

M_A_ODT1[9]

M_A_CS#0[9]

M_A_CS#1[9]

M_A_RAS#[9]

M_A_CAS#[9]

M_A_WE#[9]

M_A_VRFDQ[9] M_B_VRFDQ[1 0]

M_VREF

C607

1000P/50V_4

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

MA_ADD[0]

Y27

MA_ADD[1]

Y29

MA_ADD[2]

Y26

MA_ADD[3]

W28

MA_ADD[4]

W29

MA_ADD[5]

W26

MA_ADD[6]

U29

MA_ADD[7]

W25

MA_ADD[8]

U26

MA_ADD[9]

AG29

MA_ADD[10]

U27

MA_ADD[11]

T28

MA_ADD[12]

AK26

MA_ADD[13]

T26

MA_ADD[14]/MA_BG[1]

T25

MA_ADD[15]/MA_ACT_L

AG26

MA_BANK[0]

AG27

MA_BANK[1]

T29

MA_BANK[2]/MA_BG[0]

E19

MA_DM[0]

D21

MA_DM[1]

K21

MA_DM[2]

F29

MA_DM[3]

AP28

MA_DM[4]

AV26

MA_DM[5]

AR22

MA_DM[6]

BC22

MA_DM[7]

K29

MA_DM[8]

H19

MA_DQS_H[0]

G19

MA_DQS_L[0]

B22

MA_DQS_H[1]

A22

MA_DQS_L[1]

F23

MA_DQS_H[2]

E23

MA_DQS_L[2]

G27

MA_DQS_H[3]

F27

MA_DQS_L[3]

AP25

MA_DQS_H[4]

AP26

MA_DQS_L[4]

AW27

MA_DQS_H[5]

AV27

MA_DQS_L[5]

AV22

MA_DQS_H[6]

AU22

MA_DQS_L[6]

BA21

MA_DQS_H[7]

AY21

MA_DQS_L[7]

L27

MA_DQS_H[8]

L26

MA_DQS_L[8]

AE25

MA_CLK_H[0]

AE26

MA_CLK_L[0]

AD26

MA_CLK_H[1]

AD27

MA_CLK_L[1]

AB28

MA_CLK_H[2]

AB29

MA_CLK_L[2]

AB25

MA_CLK_H[3]

AB26

MA_CLK_L[3]

N29

MA_RESET_L

AE29

MA_EVENT_L

P27

MA_CKE 0

P29

MA_CKE 1

AK27

MA0_ODT[0]

AL26

MA0_ODT[1]

AH25

MA1_ODT[0]

AL25

MA1_ODT[1]

AH26

MA0_CS_L[0]

AL29

MA0_CS_L[1]

AH29

MA1_CS_L[0]

AL28

MA1_CS_L[1]

AG24

MA_RAS_L/MA_RAS_L_ADD[16]

AK29

MA_CAS_L/MA_CAS_L_ADD[15]

AH28

MA_WE_L/MA_WE_L_ADD[1 4]

B19

MA_VREFDQ

T32

M_VREF

U28A

MEMORY A

FP4 REV 0.93

SP@FP4

MA_DATA[0]

MA_DATA[1]

MA_DATA[2]

MA_DATA[3]

MA_DATA[4]

MA_DATA[5]

MA_DATA[6]

MA_DATA[7]

MA_DATA[8]

MA_DATA[9]

MA_DATA[10]

MA_DATA[11]

MA_DATA[12]

MA_DATA[13]

MA_DATA[14]

MA_DATA[15]

MA_DATA[16]

MA_DATA[17]

MA_DATA[18]

MA_DATA[19]

MA_DATA[20]

MA_DATA[21]

MA_DATA[22]

MA_DATA[23]

MA_DATA[24]

MA_DATA[25]

MA_DATA[26]

MA_DATA[27]

MA_DATA[28]

MA_DATA[29]

MA_DATA[30]

MA_DATA[31]

MA_DATA[32]

MA_DATA[33]

MA_DATA[34]

MA_DATA[35]

MA_DATA[36]

MA_DATA[37]

MA_DATA[38]

MA_DATA[39]

MA_DATA[40]

MA_DATA[41]

MA_DATA[42]

MA_DATA[43]

MA_DATA[44]

MA_DATA[45]

MA_DATA[46]

MA_DATA[47]

MA_DATA[48]

MA_DATA[49]

MA_DATA[50]

MA_DATA[51]

MA_DATA[52]

MA_DATA[53]

MA_DATA[54]

MA_DATA[55]

MA_DATA[56]

MA_DATA[57]

MA_DATA[58]

MA_DATA[59]

MA_DATA[60]

MA_DATA[61]

MA_DATA[62]

MA_DATA[63]

MA_CHECK[0]

MA_CHECK[1]

MA_CHECK[2]

MA_CHECK[3]

MA_CHECK[4]

MA_CHECK[5]

MA_CHECK[6]

MA_CHECK[7]

MA_ZVDDIO_MEM_S

H17

J17

F20

H20

E17

F17

K18

E20

A21

C21

C23

D23

B20

B21

B23

A23

G22

H22

E25

G25

J20

E22

H23

J23

F26

E27

J26

J27

H25

E26

G28

G29

AN26

AP29

AR26

AP24

AN29

AN27

AR29

AR27

AU26

AV29

AU25

AW25

AU29

AU28

AW26

AT25

AV23

AW23

AV20

AW20

AR23

AT23

AR20

AT20

BB23

BB22

BB20

AY19

BA23

BC23

BC21

BB21

K26

K28

N26

N28

J29

K25

L29

N25

AD29

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

MA_ZVDDIO

R124 CZ@39.2/F_4

+1.5VSUS

M_A_DQ[0..63] [9]

U28I

AG31

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_BS#[2..0][10]

M_B_DM[7..0][10]

M_B_DQS0[10]

M_B_DQS#0[1 0]

M_B_DQS1[10]

M_B_DQS#1[1 0]

M_B_DQS2[10]

M_B_DQS#2[1 0]

M_B_DQS3[10]

M_B_DQS#3[1 0]

M_B_DQS4[10]

M_B_DQS#4[1 0]

M_B_DQS5[10]

M_B_DQS#5[1 0]

M_B_DQS6[10]

M_B_DQS#6[1 0]

M_B_DQS7[10]

M_B_DQS#7[1 0]

M_B_CLK0[10]

M_B_CLK0#[10]

M_B_CLK1[10]

M_B_CLK1#[10]

M_B_RESET#[10]

M_B_EVENT#[10]

M_B_CKE0[10]

M_B_CKE1[10]

M_B_ODT0[10]

M_B_ODT1[10]

M_B_CS#0[10]

M_B_CS#1[10]

M_B_RAS#[10]

M_B_CAS#[10]

M_B_WE#[10]

M_B_BS#0

M_B_BS#1

M_B_BS#2

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

MB_ADD[0]

AC30

MB_ADD[1]

AC31

MB_ADD[2]

AB32

MB_ADD[3]

AA32

MB_ADD[4]

AA33

MB_ADD[5]

AA31

MB_ADD[6]

Y33

MB_ADD[7]

AA30

MB_ADD[8]

W32

MB_ADD[9]

AG32

MB_ADD[10]

Y32

MB_ADD[11]

W33

MB_ADD[12]

AL31

MB_ADD[13]

W30

MB_ADD[14]/MB_BG[1]

V32

MB_ADD[15]/MB_ACT_L

AH32

MB_BANK[0]

AG33

MB_BANK[1]

W31

MB_BANK[2]/MB_BG[0]

D25

MB_DM[0]

D29

MB_DM[1]

E33

MB_DM[2]

J33

MB_DM[3]

AR30

MB_DM[4]

AW30

MB_DM[5]

BC30

MB_DM[6]

BC26

MB_DM[7]

N33

MB_DM[8]

B26

MB_DQS_H[0]

A26

MB_DQS_L[0]

B30

MB_DQS_H[1]

A30

MB_DQS_L[1]

F32

MB_DQS_H[2]

E32

MB_DQS_L[2]

K32

MB_DQS_H[3]

J32

MB_DQS_L[3]

AR32

MB_DQS_H[4]

AR33

MB_DQS_L[4]

AW32

MB_DQS_H[5]

AW33

MB_DQS_L[5]

BA29

MB_DQS_H[6]

AY29

MB_DQS_L[6]

BA25

MB_DQS_H[7]

AY25

MB_DQS_L[7]

P32

MB_DQS_H[8]

N32

MB_DQS_L[8]

AE33

MB_CLK_H[0]

AE32

MB_CLK_L[0]

AE30

MB_CLK_H[1]

AE31

MB_CLK_L[1]

AD32

MB_CLK_H[2]

AD33

MB_CLK_L[2]

AC33

MB_CLK_H[3]

AC32

MB_CLK_L[3]

T33

MB_RESET_L

AG30

MB_EVENT_L

U32

MB_CKE 0

U33

MB_CKE 1

AL30

MB0_ODT[0]

AM32

MB0_ODT[1]

AJ32

MB1_ODT[0]

AM33

MB1_ODT[1]

AJ33

MB0_CS_L[0]

AL32

MB0_CS_L[1]

AJ30

MB1_CS_L[0]

AL33

MB1_CS_L[1]

AH33

MB_RAS_L/MB_RAS_L_ADD[16]

AK32

MB_CAS_L/MB_CAS_L_ADD[15]

AJ31

MB_WE_L/MB_WE_L_ADD[1 4]

A19

MB_VREFDQ

MEMORY B

FP4 REV 0.93

SP@FP4

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

MB_CHECK[0]

MB_CHECK[1]

MB_CHECK[2]

MB_CHECK[3]

MB_CHECK[4]

MB_CHECK[5]

MB_CHECK[6]

MB_CHECK[7]

MB_ZVDDIO_MEM_S

A25

C25

C27

D27

B24

B25

B27

A27

A29

C29

B32

D32

B28

B29

A31

C31

E30

E31

G33

G32

C33

D33

G30

G31

J30

J31

L33

L32

H32

H33

L30

L31

AN31

AP32

AT32

AU32

AN33

AN32

AR31

AT33

AU30

AV32

BA33

AY32

AU33

AU31

AW31

AY33

BC31

BB30

BB28

AY27

BB32

BA31

BC29

BB29

BB27

BB26

BB24

AY23

BA27

BC27

BC25

BB25

N30

N31

R33

R32

M32

M33

R30

R31

AF32

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

MB_ZVDDIO

R515 39.2/F_4

M_B_DQ[0..63] [10]M_A_A[15:0][9] M_B_A[15:0][10]

+1.5VSUS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FP4 DDR3 I/F(2/7)

FP4 DDR3 I/F(2/7)

FP4 DDR3 I/F(2/7)

Date: Sheet of

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

7

PROJECT :

ZRZ

ZRZ

ZRZ

1A

1A

341Friday, March 06, 2015

341Friday, March 06, 2015

341Friday, March 06, 2015

8

1A

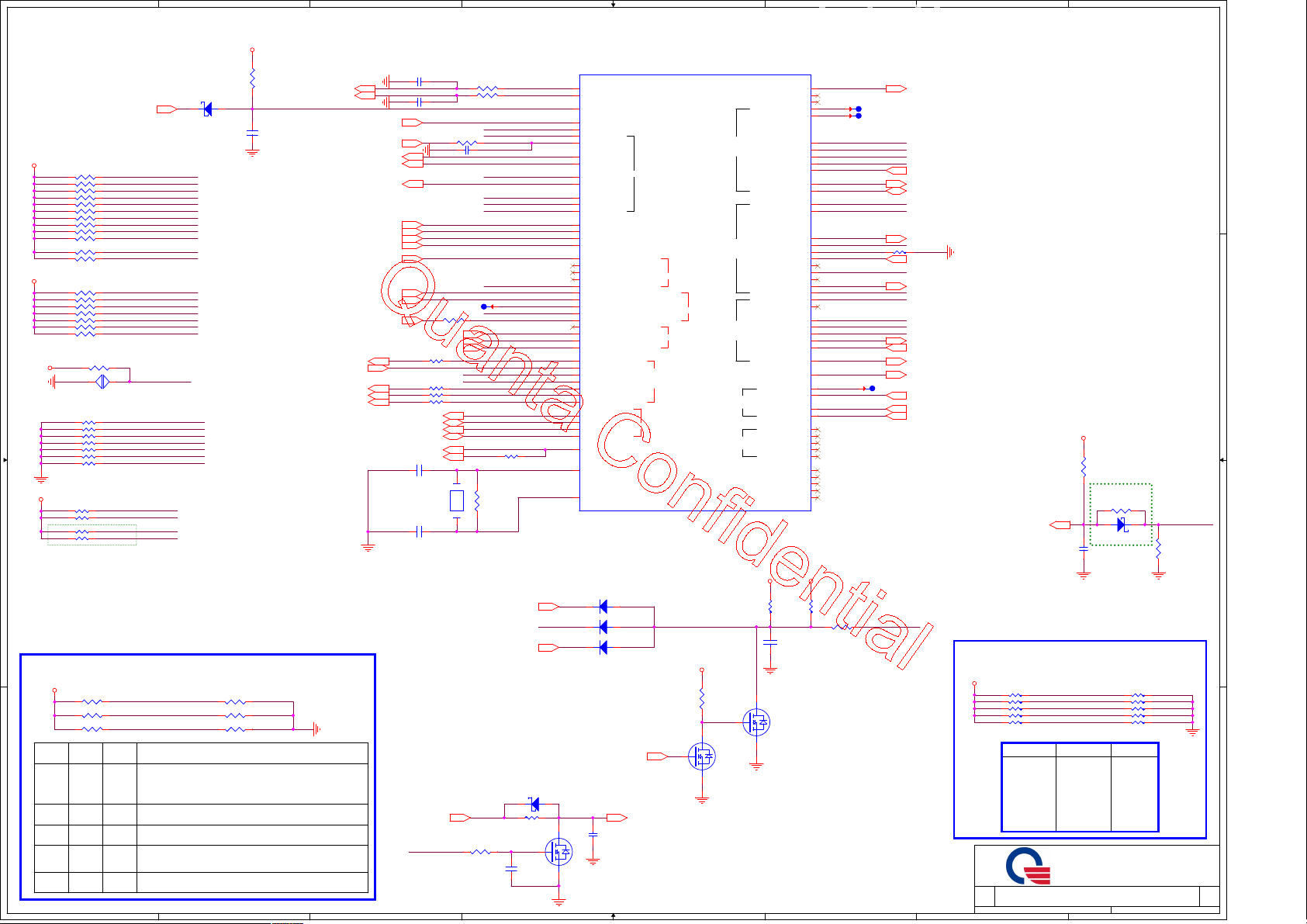

Page 4

1

(CPU)

VDD_18

R496 300_4

R439 300_4

A A

APU_PWRGD

APU_RST#

Serial VID

VDD_18 VDD_18

R465

*1K_4

B B

R464

*220_4

VFIX MODE

R491

R459

*1K_4

R458

*220_4

R460

*2.2K_4

*1K_4

APU_SVC

APU_SVD

APU_PWRGD_SVID_ REG

R490

*220_4

VID Override table (VDD)

SVDSVC

0

0

0

Boot Voltage

1.1V

1.0V

1100.9V

11

0.8V

R471

*CZ@1K_4

R470

*CZ@220_4

2

R479

*CZ@1K_4

R478

*CZ@220_4

R472

*CZ@1K_4

GFX_SVTAPU_SVT

GFX_SVC

GFX_SVD

APU_PWRGD_SVID_ REG[34,35]

3

DP2_TX0[19]

DP2_TX0#[19]

DP2_TX1[19]

DP2_TX1#[19]

MUX_TX0[18]

MUX_TX0#[18]

MUX_TX1[18]

DP DEMUX

eDP

APU_SVT[34]

APU_SVC[34]

APU_SVD[34]

GFX_SVT[35]

GFX_SVC[35]

GFX_SVD[35]

C589

*27p/50V_4

FOR DEBUG, PLACE THESE CAPS CLOSE TO APU

MUX_TX1#[18]

MUX_TX2[18]

MUX_TX2#[18]

MUX_TX3[18]

MUX_TX3#[18]

EDP_TX0[17]

EDP_TX0#[17]

EDP_TX1[17]

EDP_TX1#[17]

*APU_SVT & GFX_SVT need 0R in power side

Note: Place resistor for SVT on VRM side (Power side)

R461 *short_4

R457 *short_4

R467 *shortCZ@0_4

R469 *shortCZ@0_4

R489 *short_4

APU_PWRGD_D

R492 HDT@0_2

APU_PWRGD

APU_RST#

C572

*27p/50V_4

4

Soldermask open ings for all bottom side vias/TPs under FP4

B6

DP2_TXP[0]

A6

DP2_TXN[0]

D7

DP2_TXP[1]

C7

DP2_TXN[1]

A7

DP2_TXP[2]

B7

DP2_TXN[2]

D9

DP2_TXP[3]

C9

DP2_TXN[3]

A2

DP1_TXP[0]

A3

DP1_TXN[0]

B4

DP1_TXP[1]

A4

DP1_TXN[1]

D5

DP1_TXP[2]

C5

DP1_TXN[2]

A5

DP1_TXP[3]

B5

DP1_TXN[3]

E2

DP0_TXP[0]

E1

DP0_TXN[0]

E3

DP0_TXP[1]

E4

DP0_TXN[1]

D1

DP0_TXP[2]

D2

DP0_TXN[2]

C1

DP0_TXP[3]

B1

DP0_TXN[3]

C15

SVT0

APU_SVC_R

APU_SVD_R

GFX_SVC_R

GFX_SVD_R

APU_SIC

APU_SID

APU_RST#

APU_PWRGD

APU_PROCHOT#

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST# APU_VSS_SENSE

APU_DBRDY

APU_DBREQ#

D17

SVC0

D19

SVD0

B15

SVT1

B16

SVC1

A18

SVD1

CZL:3V_S0

B18

SIC

CZL:3V_S0

C17

SID

D15

RESET_L

C19

PWROK

A15

PROCHOT_L

B17

ALERT_L

H15

TDI

H14

TDO

D13

TCK

G15

TMS

J14

TRST_L

C13

DBRDY

A11

DBREQ_L

DISPLAY/SVI2/JTAG/TEST

DP2 : CZ only

CZ:1.8_S0

U28C

CZ:1.8_S0 CZL:3V_S0

(XX,PD)

(XX,PD)

CZ:1.8_S0 CZL:3V_S0

CZL:3V_S0

CZL:3V_S0

FP4 REV 0.93

SP@FP4

DP_ZVSS

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP2_AUXP

DP2_AUXN

DP2_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP0_AUXP

DP0_AUXN

DP0_HPD

RSVD_1

TEMPIN0

TEMPIN1

TEMPIN2

TEMPINRETURN

TEST410

TEST411

TEST28_H

TEST28_L

DP_STEREOSYNC/TEST36

VDDCR_GF X_SE NSE

VDDCR_NB_ SENSE

VDDCR_CP U_SENS E

VDDP_SE NSE

VSS_SENS E

5

TEST10

TEST14

TEST15

TEST16

TEST17

TEST11

TEST18

TEST19

TEST31

TEST37

A9

DP_ZVSS

B9

DP_AUX_ZVSS

G5

G6

APU_DIGON

F11

APU_BLPWM

H9

G9

E9

F7

E7

F5

F8

E8

G8

K24

RSVD

E15

APU_TEMPIN0

E14

APU_TEMPIN1

E12

APU_TEMPIN2

F14

APU_TEMPRETURN

AK24

APU_TEST410

AL24

APU_TEST411

P24

APU_TEST4

TEST4

N24

APU_TEST5

TEST5

AN24

TEST6

AB8

TEST9

Y9

B10

APU_TEST14

D11

APU_TEST15

A10

APU_TEST16

C11

APU_TEST17

B11

APU_TEST11

A14

APU_TEST18

B14

APU_TEST19

A13

APU_TEST28_H

B13

APU_TEST28_L

P26

APU_TEST31

E11

DP_STEREOSYNC

A17

H11

J12

G12

AY18

H12

6

R437 2K/F_4

R436 150/F_4

APU_DISP_BLEN [17,29]

DP2_AUX [19]

DP2_AUX# [19]

DP2_HPD [1 9]

MUX_AUX [18]

MUX_AUX# [18]

MUX_HPD [18]

EDP_AUX [17]

EDP_AUX# [17]

EDP_HPD [17]

TP12

TP40

TP5

TP4

TP8

TP7

TP10

TP9

R435 *1K/F_4

TP36

R434 *1K/F_4

R446 *1K/F_4

R447 *1K/F_4

R445 1K/F_4

R444 1K/F_4

TP39

TP38

R483 *1K/F_4

TP46

TP37

TP32

TP43

R440 *short_4

R443 *shortCZ@0_4

R506 *0_4

CRB CLOSE TO APU

R482 *1K/F_4

+3V

R448 *0_4

R146 *39.2/J_4

R145 *39.2/J_4

R452 1K/F_4

R453 *1K/F_4

APU_VDDGFX_RUN_FB_ H [35]

APU_VDDNB_RUN_FB_H [34]

APU_VDD_RUN_FB_H [34]

APU_VDDP_RUN_FB_H [32]

APU_VDD_RUN_FB_L [34]

APU_VDDGFX_RUN_FB_ L [35]

APU_VDDP_RUN_FB_L [32]

33S0_18S0

CZ : 1.8V

CZL : 3.3V

APU_BLPWM

APU_DIGON

CZ : 1.8V

CZL : 3.3V

VDD_18

33S0_18S0

VDD_18

7

+3V

33S0_18S0

R426

2

10K_4

LCD 3.3V

1

3

Q37

PJA138K

R410*short_ 4

EN:>1.5V

DP2_AUX

R646 *CZ@100K_4

R647 *CZ@100K_4

DP2_AUX#

M_TEST CON NECTIO N TBD

PU ->enable HDMI video/audi o

PD->Disable HDMI audio

(APU_VDD_RUN_FB_L = APU_VDDNB_RUN_FB_L)

8

APU_DISP_PWM [ 17]

APU_DISP_ON [17]

+3V

33S0_18S0

HDT(Hardware Debug Tool ) Connector

C C

U29

APU_RST#

APU_PWRGD_D APU_PWROK_BUF

1

1A

2

GND

3

2A

HDT@SN74LVC2G07DCKR

VDD_18 VDD_18 VDD_18

R520

HDT@1K/F_4

APU_TRST#

C613

D D

HDT@0.01u/50V_4

R519 HDT@33_4

R518 HDT@10K_4

R517 HDT@10K_4

R516 HDT@10K_4

HDT_TRST# APU_PWROK_BUF

PLACE HDT+ HEADER ON TOP

CN8

1

CPU_VDDIO

3

GND

5

GND

7

GND

9

CPU_TRST_L

11

CPU_DBRDY3

13

CPU_DBRDY2

15

CPU_DBRDY1

17

GND

19

CPU_VDDIO

*HDT@HDT

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TDO

CPU_PWROK_BUF

CPU_RST_L_BUF

CPU_DBRDY0

CPU_DBREQ_L

CPU_PLLTEST0

CPU_PLLTEST1

2

APU_TCK

4

APU_TMS

6

HDT_APU_TDI

8

APU_TDO

10

12

APU_RST_L_BUF

14

APU_DBRDY

16

HDT_DBREQ#

18

APU_TEST19

20

APU_TEST18

R544 HDT@0_4

R539 HDT@33_4

*HDT@0.01u/5 0V_4

C624

VCC

6

1Y

5

4

2Y

VDD_18

C614

HDT@0.1U/16V/X7R_4

APU_RST_L_BUF

R533 HDT@1K/F_4

R532 HDT@1K/F_4

APU_TDI

R543

R542 HDT@1K/F_4

R541 HDT@1K/F_4

APU_DBREQ#

R540 HDT@1K/F_4

C623

HDT@0.01u/50V_4

HDT@1K/F_4

CORE_PWM_PROCHOT#[29,30,34,35]

THERM_ALERT#[28]

3V_S0

5V_S0

(G991 Internal PU)

SMBUS (Internal Thermal sensor)

2ND_MBCLK[12,29]

3V_S5

(PU in EC side )

2ND_MBDATA[12,29]

R494

10K_4

33S0_18S0

Q40

5

43

APU_PROCHOT#

2

6

1

APU_ALERT#

VDD_18

+3V

R502 1K/F_4

R508 1K/F_4

R497 1K/F_4

R493 1K/F_4

R512 CZ@0_4

R505 CZL@0_4

APU_SIC

APU_SID

APU_ALERT#

APU_PROCHOT#

33S0_18S0

PJT138K

Q42

5

43

APU_SIC

2

6

1

APU_SID

PJT138K

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FP4 DISPLAY/MISC(3/7)

FP4 DISPLAY/MISC(3/7)

FP4 DISPLAY/MISC(3/7)

Date: Sheet of

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

7

PROJECT :

ZRZ

ZRZ

ZRZ

1A

1A

441Friday, March 06, 2015

441Friday, March 06, 2015

441Friday, March 06, 2015

8

1A

Page 5

1

2

3

4

5

6

7

8

(CPU)

VDD_18_S5

R382

22K_4

PCIE_WAKE#

SCL1

SDA1

LR_LED_L

S0A3

DNBSWON#

USB_OC1#

USB_OC2#

USB_OC3#

AGPIO4

AGPIO8

AGPIO40

CLK_SCLK

CLK_SDATA

CLK_REQ3

PCIE_REQ_GPU#_R

AGPIO64

AGPIO66

AGPIO69

I2C_SCL_TP

I2C_SDA_TP

I2C_SCL_TS

I2C_SDA_TS

D29 RB500V-40

10ms RC-delay (PU,PU)

C526

1u/10V_4

A A

+3V_S5

+3V

B B

+3V_S5

VDD_18

CZ :12C Touch interface:2.2K(CS22202JB18)

USB interface:10k(CS31002FB26)

C C

CZL:NC

PCH_RSMRST#[29]

R392 NIOAC@10K/F_4

R81 CZL@10K_4

R79 CZL@10K_4

R78 10K/F_4

R80 10K/F_4

R77 10K/F_4

R389 10K/F_4

R396 10K/F_4

R664 10K/F_4

R93 CZL@10K/F_4

R85 CZ@10K/F_4

R86 CZ@10K/F_4

R476 2.2K_4

R466 2.2K_4

R477 CZ@10K/F_4

R473 CZ@10K/F_4

R498 CZL@10K/F_4

R504 CZL@10K/F_4

R500 CZ@10K/F_4

R386 *10K/F_4

J1

1 2

*SHORT_ PAD

R674 CZ@1K_4

R430 CZ@1K_4

R675 CZ@1K_4

R676 CZ@1K_4

R432 *10K/F_4

R105 CZ@10K/F_4

R111 CZ@10K/F_4

R449 CZ@2.2K_4

R455 CZ@2.2K_4

R425 SP@10K_4

R420 SP@10K_4

SYS_RST# internal

40K pull up

SYS_RST#

ACZ_RST#_R

ACZ_BCLK_R

ACZ_SYNC_R

ACZ_SDOUT_R

PCH_AZ_CODEC_SDIN0

AZ_SDIN1

AZ_SDIN2

PLTRST#[21,23,29]

PCIERST#[11,17,20,21]

PCIE_LAN_WAKE#[12,20,21]

APU_S5_MUX_CTRL[39]

PCIE_REQ_LAN#[20]

PCIE_CLKREQ_WL AN#[21]

PCIE_REQ_GPU#[12]

PCH_AZ_CODEC_BITCLK[22]

PCH_AZ_CODEC_SDIN0[22]

PCH_AZ_CODEC_RST#[22]

PCH_AZ_CODEC_SYNC[22 ]

PCH_AZ_CODEC_SDOUT[22]

C573 150P/50V_4

C569 150P/50V_4

DNBSWON#[29]

SUSB#[29]

SUSC#[29]

KBRST#[29]

SIO_A20GATE[29]

SIO_EXT_SCI#[29]

SIO_EXT_SMI#[2 9]

ACPRESENT[30] ACCEL_INTA [23]

R441 33_4

R431 33_4

R433 33_4

R438 33_4

I2C_SCL_TP[27]

I2C_SDA_TP[27 ]

I2C_SCL_TS[17]

I2C_SDA_TS[17 ]

RTC_CLK[6]

SUS_CLK[21]

32.768KHZ

R450 33_4

R419 33_4

R390 *short_4

C534 *EV@100P/50V_4

TP69

R474 *EV@0_4

USB_OC1#[25]

USB_OC2#[25]

USB_OC3#[25]

C56818p/50V_4

Y4

C56722P/50V_4

12

ACZ_BCLK_R

AZ_SDIN1

AZ_SDIN2

ACZ_RST#_R

ACZ_SYNC_R

ACZ_SDOUT_R

R666 *33_4

R409

20M_4

PCH_RSMRST#_R

SYS_PWRGD

SYS_RST#

PCIE_WAKE#

S0A3

APU_TEST0

APU_TEST1

APU_TEST2

LR_LED_L

CLK_REQ3

PCIE_REQ_GPU#_R

LPC_RST#_R

PCIE_RST#

32K_X1

32K_X2

BB12

AY15

BC19

BB13

BC15

BB17

BC17

BB18

BB16

BB10

AN7

AE4

AE1

BC9

AF2

AG2

AK7

AH5

AE8

AH8

AH6

AK8

AE3

AD7

AG3

AD5

AL8

AN8

AE2

AH9

AG1

AH2

AL9

AU6

AR8

AP6

AR5

AU9

AT9

AR7

BB9

BB7

BC7

AG7

AT1

AT2

3V_S5? S0?

LPC_RST_L

3V_S5

PCIE_RST_L/EGPIO26

1.8V_S5

RSMRST_L

3V_S5

PWR_BTN_L/AGPIO0

CZ:3V_S0 CZL:1.8V_S0

PWR_GOOD

SYS_RESET_L/AGPIO1

WAKE_L/AGPIO2

SLP_S3_L

SLP_S5_L

3V_S5

S0A3_GPIO/AGPIO10

CZ ONLY

S5_MUX_CTRL/EGPIO42

(,PD)

TEST0

(,PD)

TEST1/TMS

(,PD)

TEST2

ESPI_RESET_L/KBRST_L/AGPIO129

GA20IN/AGPIO126

LPC_PME_L/AGPIO22

LPC_SMI_L/AGPIO86

AC_PRES /USB_ OC4_L /IR_ RX0/AG PIO23

IR_TX0/USB_OC5_L/AGPIO13

IR_TX1/USB_OC6_L/AGPIO14

IR_RX1/AGPIO15

IR_LED_L/LLB_L/AGPIO12

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

CLK_REQ1_L/AGPIO115

CLK_REQ2_L/AGPIO116

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

CLK_REQG_L/OSCIN/EGPIO132

USB_OC 0_L/ TRST_ L/AGP IO1 6

USB_OC 1_L/ TDI/ AGPIO 17

USB_OC 2_L/ TCK/ AGPIO1 8

USB_OC 3_L/ TDO/ AGPIO2 4

AZ_BITC LK/I2 S_BC LK_M IC

AZ_SDIN0 /I2S _DATA_M IC[0 ]

AZ_SDIN1 /I2S _LR_ PLAYB ACK

AZ_SDIN2 /I2S _DATA_M IC[1 ]

AZ_RST_ L/I2 S_LR _MIC

AZ_SYNC/ I2S_ BCLK _PLAY BACK

AZ_SDOUT/ I2S_ DATA_PL AYBACK

I2C0_SCL/EGPIO145

I2C0_SDA/EGPIO146

CZ:1.8V_S0 CZL:3V

I2C1_SCL/EGPIO147

I2C1_SDA/EGPIO148

3V_S5

(PU,)

RTCCLK

X32K_X1

X32K_X2

(,PD)

SYS PWRGD

SYS_RST#[6]

PWROK_EC[29]

D9 *1N4148WS

D8 *1N4148WS

D10 1N4148WS

Test mode setting (Follow AMD's suggestion)

+3V_S5

NC,no i nstall by defa ult

R87 *2.2K_4

R83 *1K_4

R383 *2.2K_4

TEST2 TEST1 TEST0 Description

0

00

D D

0

0

0

1

1

TMS

1TMS

1

APU_TEST0

APU_TEST1

APU_TEST2

FCH TAP accessible from APU when TAPEN is asserted

FCH JTAG pins are overloaded for multiple

functions, in this configuration the FCH JTAG are

used as non-JTAG pins

1

Reserved

Reserved

X

FCH JTAG multi-function pins are configured as

JTAG pins, in this configuration the FCH TAP

0

can be accessed from FCH JTAG pins

Use on ATE only

1

Yuba JTAG enabled

R88 15K_4

R384 15K_4

2

HWPG[29]

D30 *CZ@RB500V-40

R480 CZ@47K_4

3

Q38

VDDGFX_PD

3

R488 CZ@10K/F_4

2

C578

CZ@1000P/50V_4

4

CZ@2N7002K

1

C577

*CZ@1U/10V_4

VDDGFX_EN [35]VRON[29,34]

(CZ,CZL)

U28D

ACPI/SD /AZ/GP IO/RT C/I2C /UART/MI SC

(PU,PU)

(PU,PU)

(PU,PU)

(PD,PU)

3V_S0

(PU,PU)

3V_S0

(PU,PU)

3V_S5

(PU,PU)

3V_S0

(PU,PU)

(PU,PU)

CZ ONLY

(PU,)

(PU,PU)

3V_S5

(PU,PU)

(PU,PU)

(,PU)

(PU,PU)

(PU,PU)

3V_S0

(PU,)

(PU,PU)

(PU,PU)

(PU,PU)

(PU,PU)

FP4 REV 0.93

SP@FP4

+3V_S5

(,PU)

(,PU)

CZ:3V_S5 CZL:3V_S0

1.8V_S0

1.8V_S0

1.8V_S0

(,PU)

3V_S5

(,PD)

(,PD)

S5

(,PD)

CZ:1.8V_S0 CZL:1.8V_S5

CZ:1.8V_S0 CZL:1.8V_S5

3

2

1

5

(PD,PU)

3V_S0

3V_S0

CZ:3V_S5 CZL:3V_S0

(PD,PU)

(PD,PU)

(PD,PU)

(PD,PU)

(PD,PU)

(PD,)

(PU,)

(PU,)

(PU,)

(PU,)

(PD,PU)

(PD,PU)

(PD,PU)

(PD,)

(PD,)

(PU,PU)

(PU,PU)

(PU,)

(PU,)

R206

100K_4

SD0_PWR_CTRL/AGPIO102

3.3V_S0

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SDA1/I2C3_SDA/AGPIO20

(PU,PU)

(PD,)

3.3V_S5

(PD,PU)

(PD,PU)

(PD,PU)

(PD,PU)

(PD,PU)

3.3V_S0

AGPIO71 /SGPI O_DATAOUT

AGPIO72 /SGPI O_DATAI N

3.3V_S0

1.8V_S0

UART1_CT S_L/ BT_I 2S_ BCLK /EGP IO14 0

UART1_RX D/BT _I2S _SD I/EGP IO1 41

UART1_TX D/BT_ I2S _SDO /EGPI O14 3

UART1_I NTR/BT_ I2S _LRC LK/ AGPIO1 44

3

2

Q22

1

2N7002K

SD0_WP/EGPIO101

SD0_CD/AGPIO25

SD0_CLK/EGPIO95

SD0_CMD/EGPIO96

SD0_DATA0/EGPIO97

SD0_DATA1/EGPIO98

SD0_DATA2/EGPIO99

SD0_DATA3/EGPIO100

SD0_LED/EGPIO93

SCL1/I2C3_SCL/AGPIO19

AGPIO3

AGPIO4

AGPIO5

AGPIO6/ LDT_R ST

AGPIO7/ LDT_P WROK

AGPIO8

AGPIO9

VDDGFX_ PD/AGP IO39

AGPIO40

AGPIO64

AGPIO65

AGPIO66 /SHUTDOW N_L

AGPIO68 /SGPI O_CL K

AGPIO69 /SGPI O_LO AD

SPKR/AGPIO91

BLINK/USB_OC7_L/AGPIO11

GENINT1_L/AGPIO89

GENINT2_L/AGPIO90

FANIN0/AGPIO84

FANOUT0/AGPIO85

UART0_CT S_L/ EGPI O135

UART0_RX D/EG PIO1 36

UART0_RT S_L/ EGPI O137

UART0_TX D/EG PIO1 38

UART0_I NTR/AGP IO13 9

UART1_RT S_L/ EGPI O142

+3V

R189

CZ@4.7K_4

C339

0.22u/10V_4

Q21

2N7002K

BB2

BB5

BC2

BB4

AY5

BC3

BA3

BC5

BA5

BB6

BA15

AY17

AG5

AG4

AL5

AL6

AJ1

AJ3

AH1

AJ4

AK5

AD8

AG8

AW15

AU15

AT15

AU12

AT14

AR14

BC13

BA17

AN5

BB14

BA19

BC18

BB19

AY9

AW8

AV5

AV8

AW9

AV11

AU7

AT11

AR11

AP9

VDD_18

R188

CZL@4.7K_4

R187 *short_4

TP34

TP35

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

SCL1

SDA1

GEVENT2#

AGPIO4

S3_resume

AGPIO8

AGPIO40

AGPIO64

AGPIO66

DGPU_PWREN_A

AGPIO69

6

DGPU_RST_L [1 1]

BOARD_ID4 [17]

CLK_SCLK [9,10,23]

CLK_SDATA [9,10,23]

R84 10K_4

PCH_ODD_EN [24]

ODD_PLUGIN# [24]

SPKR [22]

AGPIO11 [6]

TP6

PE_PWRGD [38]

APU_TP_INT# [17]

APU_I2C_INT# [27]

SYS_PWRGDSUSB#

GEVENT2# [6]

VDDGFX_PD [29]

+3V

R116

*EV@100K/F_6

CZ : mount R659

CZL: mount D2

R659 EV_SP@0_4

DGPU_PWREN[38]

BOARD ID

+3V

ZYV

BOARD_ID4 Depend on cable => always PU, PD DNI

Touch cable PIN2 => NC

non-Touch cable PIN2 => GND

R109 SP@10K_4

R104 SP@10K_4

R106 SP@10K_4

R107 IOAC@10K_4R90 15K_4

R4 10K_4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

GPIO

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FP4 GPIO/AZ/I2C/SD/UARTS(4/7)

FP4 GPIO/AZ/I2C/SD/UARTS(4/7)

FP4 GPIO/AZ/I2C/SD/UARTS(4/7)

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

dTPM

dGPU

non-G sensor

IOAC non-IOAC

Touch

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

High

D2

EV_SP@RB500V-40

C193

EV@0.1u/16V_4

DGPU_PWREN_A

R644

*EV@1M_4

R110 SP@10K_4

R103 SP@10K_4

R102 SP@10K_4

R99 NIOAC@10K_4

R5 *10K_4

Low

iTPM

UMA

G sensor

non-Touch

ZRZ

ZRZ

ZRZ

541Wednesday, March 18, 2015

541Wednesday, March 18, 2015

541Wednesday, March 18, 2015

8

1A

1A

1A

Page 6

1

2

3

4

5

6

7

8

(CPU)

AU3

SATA_TXP0[24]

HDD

H:SSD

L:ODD

CLK_PCIE_VGAP[11]

CLK_PCIE_VGAN[11]

CLK_PCIE_LANP[20]

CLK_PCIE_LANN[20]

CLK_PCIE_WLANP[21]

CLK_PCIE_WLANN[21]

EMI reserve

ODD

C530 6p/50V_4

C529 6p/50V_4

A A

B B

C574 *15P/50V_4

C575 *15P/50V_4

C576 *15P/50V_4

C C

SATA_TXN0[24]

SATA_RXN0[24]

SATA_RXP0[24]

SATA_TXP1[24]

SATA_TXN1[24]

SATA_RXN1[24]

SATA_RXP1[24]

R413 1K/F_4

VDDP_0.95V

DEVSLP_HDD[24]

DEVSLP_ODD[24]

DEVSLP_ODD PU in ODD connector side

2

Y2

48MHz

4

CLK_PCI_775[29]

PCLK_TPM[23]

CLK_LPC_DEBUG[21]

LPC_LAD0[21,23,29]

LPC_LAD1[21,23,29]

LPC_LAD2[21,23,29]

LPC_LAD3[21,23,29]

LPC_LFRAME#[21,23,29]

SERIRQ[23,29]

LPC_CLKRUN#[23,29]

LPCPD#[23]

CLK_LPC_DEBUG

PCLK_TPM

CLK_PCI_775

R412 1K/F_4

R114 CZ@10K/F_4

+3V

R115 *CZ@10K/F_4

R507 10K/F_4

R404 *shortEV@0_4

R405 *shortEV@0_4

R394 *short_4

R395 *short_4

R398 *short_4

R397 *short_4

13

R388

1M_4

R462 22_4

R456 22_4

R451 22_4

R442 *short_4

R112 CZ@10K/F_4

R117 CZ@10K/F_4

SATA_ZVSS

SATA_ZVDD

DEVSLP_HDD

DEVSLP_ODD

CLK_PCIE_VGAP_C

CLK_PCIE_VGAN_C

CLK_PCIE_LANP_R

CLK_PCIE_LANN_R

CLK_PCIE_WLANP_C

CLK_PCIE_WLANN_C

TP3

48M_X1

48M_X2

LPCCLK0

LPCCLK1

TP33

LPC_CLKRUN#_R

SPI_CLK

SPI_CS#

SPI_SO

SPI_SI

SPI_WP

SPI_HOLD#

SATA_TX0P

AU4

SATA_TX0N

AV1

SATA_RX0N

AV2

SATA_RX0P

AY2

SATA_TX1P

AY1

SATA_TX1N

AW4

SATA_RX1N

AW3

SATA_RX1P

AW1

SATA_ZVSS

AW2

SATA_ZVDDP

AT17

DEVSLP[0]/EGPIO67

AT12

DEVSLP[1]/EGPIO70

BB15

SATA_ACT_L/AGPIO130

AU2

SATA_X1

AU1

SATA_X2

U4

GFX_CLKP

U3

GFX_CLKN

U1

GPP_CLK0P

U2

GPP_CLK0N

W4

GPP_CLK1P

W3

GPP_CLK1N

W1

GPP_CLK2P

W2

GPP_CLK2N

Y2

GPP_CLK3P

Y1

GPP_CLK3N

BC10

X25M_48M_OSC

T2

X48M_X1

T1

X48M_X2

AW14

LPCCLK0/EGPIO74

AY13

LPCCLK1/EGPIO75

BB11

LAD0

BA11

LAD1

AY11

LAD2

BA13

LAD3

AV14

LFRAME_L

BA1

ESPI_ALERT_L/LDRQ0_L

BC14

SERIRQ/AGPIO87

BC11

LPC_CLKRUN_L/AGPIO88

AE9

LPC_PD_L/AGPIO21

BC6

SPI_CLK/ESPI_CLK/EGPIO117

BB8

SPI_CS1_L/EGPIO118

AW7

SPI_CS2_L/ESPI_CS_L/EGPIO119

BA9

SPI_DI/ESPI_DATA/EGPIO120

AY7

SPI_DO/EGPIO121

AW11

SPI_WP_L/EGPIO122

BA7

SPI_HOLD_L/EGPIO133

AW12

SPI_TPM_CS_L/AGPIO76

1.8V_S0

1.8V_S0

CZ:3V_S0 CZL:3V_S5

CZ:3V_S0 CZL:3V_S5

CZ:3V_S0 CZL:3V_S5

CZ:3V_S0 CZL:3V_S5

U28E

CLK/SATA/USB/SPI/LPC

3V_S0

3V_S0

3V_S0

(PD,)

(PD,)

(PD,)

(PD,)

(PD,)

(PD,)

3V_S0

(PU,PU)

3V_S0

(,PU)

3V_S5

(PD,)

CZ:1.8V_S0 CZL:1.8V_S5

(PD,)

(PD,)

(PD,)

CZ:3V_S0 CZL:3V_S5

FP4 REV 0.93

SP@FP4

(PD,)

USBCLK /25 M_48 M_OSC

USB_ZVS S

USB_HSD 0P

USB_HSD 0N

USB_HSD 1P

USB_HSD 1N

USB_HSD 2P

USB_HSD 2N

USB_HSD 3P

USB_HSD 3N

USB_HSD 4P

USB_HSD 4N

USB_HSD 5P

USB_HSD 5N

USB_HSD 6P

USB_HSD 6N

USB_HSD 7P

USB_HSD 7N

USB_SS _ZVS S

USB_SS _ZVDD P

USB_SS _0TX P

USB_SS _0TX N

USB_SS _0RX P

USB_SS _0RX N

USB_SS _1TX P

USB_SS _1TX N

USB_SS _1RX P

USB_SS _1RX N

USB_SS _2TX P

USB_SS _2TX N

USB_SS _2RX P

USB_SS _2RX N

USB_SS _3TX P

USB_SS _3TX N

USB_SS _3RX P

USB_SS _3RX N

(PD,)

AP8

AP5

AR2

AR1

AR3

AR4

AN2

AN1

AN3

AN4

AM1

AM2

AL2

AL1

AL3

AL4

AK2

AJ2

AD2

AD1

AA3

AA4

W9

W8

AA2

AA1

W5

W6

AC1

AC2

Y6

Y7

AC4

AC3

AB5

AB6

USB_ZVSS

TP2

R414 11.8K/F_4

USBSS_CALP

USBSS_CALN

Port0 & Port1 : CZ ONLY

USBP0+ [25]

USBP0- [25]

USBP1+ [27]

USBP1- [27]

USBP2+ [17]

USBP2- [17]

USBP3+ [25]

USBP3- [25]

USBP4+ [21]

USBP4- [21]

USBP5+ [17]

USBP5- [17]

USBP6+ [25]

USBP6- [25]

USBP7+ [25]

USBP7- [25]

R408 1K/F_4

R407 1K/F_4

USB30_TX2+ [25]

USB30_TX2- [25]

USB30_RX2+ [25]

USB30_RX2- [25]

USB30_TX3+ [25]

USB30_TX3- [25]

USB30_RX3+ [25]

USB30_RX3- [25]

DB

Touch Pad

Touch Panel

Card reader

WLAN/BT

CCD

USB3 (Charger)

USB3

VDDP_0.95V_S5

VDD_18

+3V_S5

route SPI bus as daisy chain

SPI IMPEDANCE 50-55R, <4''

SPI_CS[29]

SPI_SCK[29]

SPI_SDI[29]

SPI_SDO[29]

SPI_CS# SPI_CS_A

SPI_CLK

C570 *22P/50V_4

SPI_SI

SPI_SO SPI_SDO_A

33S5_18S0

SPI_WP

R486 CZL@0_4

R422 CZL@0_4

R423 CZL@0_4

R487 CZL@0_4

R484 33_4

R418 33_4

SPI EMI

R424 33_4

R485 33_4

R454 10K/F_4

R463 *short_4

SPI_SCK_A

SPI_SDI_A

SPI_WP_R

SP@ socket P/N: DFHS08FS023 only for A-TEST

SPI ROM

CARRIZO-L

3.3V

CARRIZO

1.8V

Vender Size Quanta P/N

EON

WND

EON

R416 CZ@0_4

R411 CZL@0_4

33S5_18S0

R415

10K/F_4

U27

1

CE#

6

SCK

5

SI

2

SO

3

WP#

SP@W25Q64FW SSIG

AKE3EFP0N07

8M

AKE2EZN0Q00

8M

AKE3EZN0Q01

8M

AKE5EZN0N00

8M

AKE5EG-0Q00 GD25LQ64CSIGRGGD

8M

8M

VDD

HOLD#

VSS

33S5_18S0

33S5_18S0

8

R417

10K/F_4

7

4

Vender P/N

W25Q64FVSSIQWND

GD25B64CSIGRGGD

EN25QH64-104HIP

W25Q64FWSSIG

C571

0.1u/16V_4

SPI_HOLD#

STRAPS PINS

+3V_S5

+3V_S5+3V_S5+3V+3V+3V +3V_S5+3V_S5 +3V_S5 +3V_S5

R92

R95

*CZL@10K_4

LPCCLK0

LPCCLK1

LPC_LFRAME#

RTC_CLK[5]

GEVENT2#[5]

SYS_RST#[5]

AGPIO11[5]

D D

1

R108

*CZ@10K_4

R97

2k_4

2

R96

CZL@10K_4

R101

CZ@10K_4

R100

*2k_4

R531

CZL@10K_4

R475

CZ@10K_4

R468

*2k_4

3

R82

10K_4

R76

*2k_4

*CZ@10K_4

R91

2k_4

R387

10K_4

R385

*2k_4

4

R94

10K_4

R98

*2k_4

LPC_CLK0 LFRAME#

BOOT Fail Timer

PU

ENABLE

LPC_CLK1

Internal CLKGEN

DEFAULT

PD

BOOT Fail Timer

DISABLE

External CLKGEN

DEFAULT

5

SPI ROM

DEFAULT

LPC ROM

RTC_CLK

Coin battery

is on board.

DEFAULT

Coin battery

is not on board.

6

GEVENT2# (AGPIO3)

CZ-L

1.8V SPI ROM

3.3V SPI ROM

DEFAULT

Int pull-up

Int pull-upInt pull-up

SYS_RST#

CZ

Enhanced Reset logic

(faster resume from S5)

normal reset mode

DEFAULT DEFAULT

Default to

Traditional Reset logic

short reset mode

DEFAULT

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FP4 SATA/USB/LPC/SPI(5/7)

FP4 SATA/USB/LPC/SPI(5/7)

FP4 SATA/USB/LPC/SPI(5/7)

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

PROJECT :

Int pull-up

AGPIO11(BLINK)

LDT_RST#/LDT_PWRGD

output to APU

LDT_RST#/LDT_PWRGD

output to Pads

ZRZ

ZRZ

ZRZ

641Friday, March 06, 2015

641Friday, March 06, 2015

641Friday, March 06, 2015

8

1A

1A

1A

Page 7

1

(CPU)

C215

22u/6.3V_6

A A

VDD_18

B B

C207

10u/6.3V_6

C C

+1.5VSUS

D D

C219

0.22u/10V_4

VDDP_0.95V

C583

10u/6.3V_6

R499 *short_4

+1.5V +3V

C195

0.22u/10V_4

C160

C162

0.22u/10V_4

10u/6.3V_6

DECOUPLING BETWEEN PROCESSOR AND DIMMs

ACROSS VDDIO AND VSS SPLI T

C236

0.22u/10V_4

C235

0.22u/10V_4

VDDCR_NB

C148

0.22u/10V_4

2

C209

C210

22u/6.3V_6

22u/6.3V_6

C237

C216

0.22u/10V_4

0.22u/10V_4

C587

C588

10u/6.3V_6

10u/6.3V_6

+VDDIO_AZ

C596

C595

1u/10V_4

1u/10V_4

C191

C192

0.22u/10V_4

10u/6.3V_6

C220

0.22u/10V_4

4x0.22UF (0402)+2x180PF(0402)

C141

0.22u/10V_4

C149

0.22u/10V_4

C217

1u/10V_4

VDDP_0.95V_S5+3V_S5VDD_18_S5

C234

0.22u/10V_4

C211

22u/6.3V_6

C233

0.22u/10V_4

C590

10u/6.3V_6

C167

10u/6.3V_6

C185

180P/50V_4

C152

0.22u/10V_4

C212

22u/6.3V_6

C227

0.22u/10V_4

C226

0.22u/10V_4

R147 *short_4

C168

0.22u/10V_4

C114

0.22u/10V_4

C194

0.22u/10V_4

C306

180P/50V_4

C151

0.22u/10V_4

3

C213

22u/6.3V_6

C225

0.22u/10V_4

C586

0.22u/10V_4

VDDP_0.95V

R69 SP@0_8

C274

10u/6.3V_6

VDDCR_FCH_ALWVDDCR_FCH_S5

R113 *CZ@0_4

C147

0.22u/10V_4

C199

0.22u/10V_4

C221

180P/50V_4

C224

C232

22u/6.3V_6

22u/6.3V_6

C280

C275

180P/50V_4

180P/50V_4

C579

C214

0.22u/10V_4

0.22u/10V_4

CZL UMA tied to VSS.

CZ UMA&DIS and CZL DIS tied to VDDP

C181

CZ@22u/6.3V_6

C106

22U/6.3V_6

C206

0.22u/10V_4

R70

SP@0_4

C175

CZ@22u/6.3V_6

C115

22U/6.3V_6

C208

0.22u/10V_4

200mA

C304

C218

180P/50V_4

180P/50V_4

C581

C580

0.22u/10V_4

0.22u/10V_4

VDDP_GFX

C133

SP@10u/6.3V_6

VDD33

C180

CZ@0.22u/10V_4

Place under APU

C150

22U/6.3V_6

C222

0.22u/10V_4

4

C337

180P/50V_4

C582

180P/50V_4

1.5A

C153

SP@0.22u/10V_4

1.5A

500mA

200mA

800mA

VDDP_0.95V

VDDCR_NB

C109

22U/6.3V_6

C228

0.22u/10V_4

+1.5VSUS

+VDDIO_AZ

200mA

7A

C184

0.22u/10V_4

+1.5V_RTC_R

20MIL

P25

VDDIO_ME M_S3 _1

P28

VDDIO_ME M_S3 _2

T24

VDDIO_ME M_S3 _3

T27

VDDIO_ME M_S3 _4

U25

VDDIO_ME M_S3 _5

U28

VDDIO_ME M_S3 _6

V30

VDDIO_ME M_S3 _7

V33

VDDIO_ME M_S3 _8

W24

VDDIO_ME M_S3 _9

W27

VDDIO_ME M_S3 _10

Y25

VDDIO_ME M_S3 _11

Y28

VDDIO_ME M_S3 _12

Y30

VDDIO_ME M_S3 _13

AB24

VDDIO_ME M_S3 _14

AB27

VDDIO_ME M_S3 _15

AB30

VDDIO_ME M_S3 _16

AB33

VDDIO_ME M_S3 _17

AD25

VDDIO_ME M_S3 _18

AD28

VDDIO_ME M_S3 _19

AD30

VDDIO_ME M_S3 _20

AE24

VDDIO_ME M_S3 _21

AE27

VDDIO_ME M_S3 _22

AF30

VDDIO_ME M_S3 _23

AF33

VDDIO_ME M_S3 _24

AG25

VDDIO_ME M_S3 _25

AG28

VDDIO_ME M_S3 _26

AH24

VDDIO_ME M_S3 _27

AH27

VDDIO_ME M_S3 _28

AH30

VDDIO_ME M_S3 _29

AK25

VDDIO_ME M_S3 _30

AK28

VDDIO_ME M_S3 _31

AK30

VDDIO_ME M_S3 _32

AK33

VDDIO_ME M_S3 _33

AL27

VDDIO_ME M_S3 _34

AM30

VDDIO_ME M_S3 _35

AR19

VDDIO_AUDI O

AE6

VDDP_GF X_2

AE5

VDDP_GF X_1

AP19

VDD_33 _1

AP21

VDD_33 _2

AP16

VDD_18 _1

AP18

VDD_18 _2

AP10

VDD_18 _S5_ 1

AR9

VDD_18 _S5_ 2

AP15

VDD_33 _S5_ 1

AR15

VDD_33 _S5_ 2

AN12

VDDP_S5 _1

AP12

VDDP_S5 _2

AP13

VDDCR_F CH_S5_ 1

AR12

VDDCR_F CH_S5_ 2

AW19

VDDP_6

AU17

VDDP_1

AU19

VDDP_2

AV17

VDDP_3

AV19

VDDP_4

AW17

VDDP_5

AL12

VDDCR_NB_ 1

AL13

VDDCR_NB_ 2

AL15

VDDCR_NB_ 3

AL18

VDDCR_NB_ 4

AL21

VDDCR_NB_ 5

AN13

VDDCR_NB_ 6

AN16

VDDCR_NB_ 7

AN19

VDDCR_NB_ 8

AN22

VDDCR_NB_ 9

AR17

VDDBT_RTC _G

R554 1K/F_4

C636

1u/10V_4

RTC (RTC)

5

12

G1

*SHORT_ PAD

U28F

POWER

FP4 REV 0.93

SP@FP4

+1.5V_RTC

VDDCR_CP U_1

VDDCR_CP U_2

VDDCR_CP U_3

VDDCR_CP U_4

VDDCR_CP U_5

VDDCR_CP U_6

VDDCR_CP U_7

VDDCR_CP U_8

VDDCR_CP U_9

VDDCR_CP U_10

VDDCR_CP U_11

VDDCR_CP U_12

VDDCR_CP U_13

VDDCR_CP U_14

VDDCR_CP U_15

VDDCR_CP U_16

VDDCR_CP U_17

VDDCR_CP U_18

VDDCR_CP U_19

VDDCR_CP U_20

VDDCR_CP U_21

VDDCR_CP U_22

VDDCR_CP U_23

VDDCR_CP U_24

VDDCR_CP U_25

VDDCR_CP U_26

VDDCR_CP U_42

VDDCR_CP U_31

VDDCR_CP U_43

VDDCR_CP U_32

VDDCR_CP U_44

VDDCR_CP U_33

VDDCR_CP U_45

VDDCR_CP U_34

VDDCR_CP U_46

VDDCR_CP U_35

VDDCR_CP U_47

VDDCR_CP U_36

VDDCR_CP U_28

VDDCR_CP U_29

VDDCR_CP U_40

VDDCR_CP U_30

VDDCR_CP U_37

VDDCR_CP U_49

VDDCR_CP U_38

VDDCR_CP U_39

VDDCR_CP U_48

VDDCR_CP U_41

VDDCR_CP U_27

VDDCR_GF X_14

VDDCR_GF X_15

VDDCR_GF X_16

VDDCR_GF X_17

VDDCR_GF X_18

VDDCR_GF X_19

VDDCR_GF X_20

VDDCR_GF X_21

VDDCR_GF X_22

VDDCR_GF X_23

VDDCR_GF X_24

VDDCR_GF X_25

VDDCR_GF X_26

VDDCR_GF X_27

VDDCR_GF X_28

VDDCR_GF X_29

VDDCR_GF X_1

VDDCR_GF X_2

VDDCR_GF X_3

VDDCR_GF X_4

VDDCR_GF X_5

VDDCR_GF X_6

VDDCR_GF X_7

VDDCR_GF X_8

VDDCR_GF X_9

VDDCR_GF X_10

VDDCR_GF X_11

VDDCR_GF X_12

VDDCR_GF X_30

VDDCR_GF X_31

VDDCR_GF X_32

VDDCR_GF X_33

VDDCR_GF X_34

VDDCR_GF X_35

VDDCR_GF X_36

VDDCR_GF X_37

VDDCR_GF X_13

Q47

AP2138N-1.5TRG1

1

2

6

VDDCR_CPU

U8

W7

W12

W15

W18

W21

Y8

Y10

Y13

Y16

Y19

Y22

AB7

AB9

AB12

AB15

AB18

AB21

AD6

AD10

AD13

AD16

AD19

AD22

AE7

AE12

AK9

AG10

AK10

AG13

AK13

AG16

AK16

AG19

AK19

AG22

AK22

AH7

AE18

AE21

AH21

AG6

AH12

AN6

AH15

AH18

AL7

AK6

AE15

L8

L13

L16

L19

L22

N7

N12

N15

N18

N21

P8

P13

P16

P19

P22

T7

F12

F15

G11

G14

J8

J9

J11

K7

K12

K13

K15

K16

T12

T15

T18

T21

U13

U16

U19

U22

K19

VDDCR_GFX

C201

22U/6.3V_6

C188

22U/6.3V_6

C169

0.22u/10V_4

C163

0.22u/10V_4

C205

CZ@22U/6.3V_6

C190

CZ@22U/6.3V_6

C155

CZ@0.22u/10V_4

C173

CZ@0.22u/10V_4

+3VRTC

3

20MIL20MIL

RTC CR2032 Coin Battery

DBV: AHL03003057

VDE: AHL03003003

C639

1u/10V_4

D39

BAT54CW

C202

22U/6.3V_6

C177

22U/6.3V_6

C171

0.22u/10V_4

C164

0.22u/10V_4

Place under APU

+3VPCU_R

+VCCRTC_2

C203

22U/6.3V_6

C178

22U/6.3V_6

C170

0.22u/10V_4

C161

0.22u/10V_4

C182

CZ@22U/6.3V_6

C196

CZ@22U/6.3V_6

C156

CZ@0.22u/10V_4

C174

CZ@0.22u/10V_4

R562 *short_4

20MIL

R563

1K/F_4

+BAT

20MIL

12

CN11

RTC_2032

7

C186

22U/6.3V_6

C179

22U/6.3V_6

C166

0.22u/10V_4

C183

180P/50V_4

C176

CZ@22U/6.3V_6

C204

CZ@22U/6.3V_6

C157

CZ@0.22u/10V_4

C172

CZ@0.22u/10V_4

+3VPCU

C187

22U/6.3V_6

C165

0.22u/10V_4

C154

CZ@22U/6.3V_6

C200

CZ@22U/6.3V_6

C158

CZ@0.22u/10V_4

C197

CZ@0.22u/10V_4

C189

CZ@22U/6.3V_6

C159

CZ@0.22u/10V_4

C198

CZ@180P/50V_4

8

ACROSS VDDNB AND VSS SPLIT

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FP4 POWER(6/7)

FP4 POWER(6/7)

FP4 POWER(6/7)

Date: Sheet of

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

7

PROJECT :

ZRZ

ZRZ

ZRZ

1A

1A

741Wednesday, March 18, 2015

741Wednesday, March 18, 2015

741Wednesday, March 18, 2015

8

1A

Page 8

(CPU)

1

2

3

4

5

6

7

8

U28G

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

GND

FP4 REV 0.93

SP@FP4

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

L28

M4

M30

N10

N13

N16

N19

N22

N27

P1

P2

P4

P5

P12

P15

P18

P21

P30

P33

T4

T10

T13

T16

T19

T22

T30

U5

U12

U15

U18

U21

U24

V1

V2

V4

W10

W13

W16

W19

W22

Y4

Y5

Y12

Y15

Y18

Y21

Y24

AB1

AB2

AB4

AB10

AB13

AB16

AB19

AB22

AD4

AD9

AD12

AD15

AD18

AD21

AD24

AE10

AE13

AE16

AE19

AE22

AF1

AF4

AG9

AG12

AG15

AG18

AG21

AH4

AH10

AH13

AH16

AH19

AH22

AK1

AK4

AK12

AK15

AK18

AL16

AL19

AL22

AM4

AN9

AN10

AN15

AN18

AN21

AN25

AN28

AP1

AP2

AP4

AP7

AP22

AP27

AP30

AP33

AR6

AR25

AR28

AT4

AT19

AT22

AT30

AU5

AU8

AU11

AU14

AU20

AU23

AU27

AV4

AV7

AV9

AV12

AV15

AV25

A A

B B

C C

A12

A16

A20

A24

A28

A32

B12

B33

D10

D12

D14

D16

D18

D20

D22

D24

D26

D28

D30

F19

F22

F25

F30

F33

G17

G20

G23

G26

H30

J15

J19

J22

J25

J28

K10

K22

K27

K30

K33

L12

L15

L18

L21

L25

A8

B2

B8

C3

D4

D6

D8

F1

F2

F4

F9

G7

H4

J5

K1

K2

K4

L5

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

U28H

GND

FP4 REV 0.93

SP@FP4

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_215

VSS_214

AV30

AV33

AW22

AY4

AY6

AY8

AY10

AY12

AY14

AY16

AY20

AY22

AY24

AY26

AY28

AY30

BB1

BB33

BC4

BC8

BC12

BC16

BC20

BC24

BC28

BC32

L24

AL10

AK21

U30

U31

AN30

RSVD_2

RSVD_3

RSVD_4

U28J

FP4 REV 0.93

SP@FP4

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

FP4 GND(7/7)

FP4 GND(7/7)

FP4 GND(7/7)

Date: Sheet of

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

PROJECT :

7

ZRZ

ZRZ

ZRZ

1A

1A

1A

841Friday, March 06, 2015

841Friday, March 06, 2015

841Friday, March 06, 2015

8

Page 9

5

4

3

2

1

SODIMM (SDM)

M_A_A[15:0][3]

D D

M_A_BS#0[3]

M_A_BS#1[3]

M_A_BS#2[3]

M_A_CS#0[3]

M_A_CS#1[3]

M_A_CLK0[3]

M_A_CLK0#[3]

M_A_CLK1[3]

M_A_CLK1#[3]

M_A_CKE0[3]

M_A_CKE1[3]

M_A_CAS#[3]

M_A_RAS#[3]

M_A_WE#[3]

CLK_SCLK[5,10,23]

C C

B B

+1.5VSUS

CLK_SDATA[5,10,23]

M_A_ODT0[3]

M_A_ODT1[3]

M_A_DM[7..0][3]

M_A_DQS[7:0][3]

M_A_DQS#[7:0][3]

Place these Caps near So-Dimm1.

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

JDIM1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

PC2100 DDR3 SDRAM SO-DIMM

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

CZ@DDR3-DIMM1_H=4_REV

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

(204P)

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ3

M_A_DQ1

M_A_DQ0

M_A_DQ7

M_A_DQ2

M_A_DQ8

M_A_DQ9

M_A_DQ11

M_A_DQ10

M_A_DQ12

M_A_DQ13

M_A_DQ15

M_A_DQ14

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQ[63:0] [3]

+3V

+1.5VSUS

M_A_EVENT#[3]

M_A_RESET#[3]

R197

CZ@1K_4

C322

CZ@1U/10V_4

C321 CZ@1000p/50V_4

C320 CZ@0.1u/16V_4

C348 CZ@0.1u/16V_4

C347 CZ@1000p/50V_4

2.48A

+VREF_DQ0

+VREF_CA0

+SMDDR_VREF

+1.5VSUS

R210 *CZ@0_6

3mA

JDIM1B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

CZ@DDR3-DIMM1_H=4_REV

+1.5VSUS

+1.5VSUS

(204P)

PC2100 DDR3 SDRAM SO-DIMM

R209

CZ@1K/F_4

R199

CZ@1K/F_4

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

GND

GND

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

+SMDDR_VTT

203

204

205

206

+VREF_CA0

C349

CZ@0.1u/16V_4

0.25A

C313

CZ@0.1u/16V_4 R176

+1.5VSUS

A A

C341

CZ@0.1u/16V_4

C314

CZ@0.1u/16V_4

C342

CZ@0.1u/16V_4

5

C317

CZ@0.1u/16V_4

C343

CZ@0.1u/16V_4

C318

CZ@0.1u/16V_4

C344

CZ@0.1u/16V_4

C315

CZ@0.1u/16V_4

C345

CZ@0.1u/16V_4

C316

CZ@0.1u/16V_4

C346

CZ@0.1u/16V_4

4

C332

CZ@180P/50V_4

+SMDDR_VTT

C335

CZ@4.7U/6.3V_6

C333

CZ@0.1u/16V_4

3

CZ@1K/F_4

M_A_VRFDQ[3]

2

R175 *CZ@0_6

3mA

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

DDR3 DIMM 1

DDR3 DIMM 1

DDR3 DIMM 1

Date: Sheet of

Date: Sheet of

Date: Sheet of

R177

CZ@1K/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

+VREF_DQ0

C319

CZ@0.1u/16V_4

ZRZ

ZRZ

ZRZ

1

1A

1A

1A

941Wednesday, March 18, 2015

941Wednesday, March 18, 2015

941Wednesday, March 18, 2015

Page 10

5

4

3

2

1

SODIMM (SDM)

M_B_A[15:0][3]

D D

M_B_BS#0[3]

M_B_BS#1[3]

M_B_BS#2[3]

M_B_CS#0[3]

M_B_CS#1[3]

M_B_CLK0[3]

M_B_CLK0#[3]

M_B_CLK1[3]

M_B_CLK1#[3]

M_B_CKE0[3]

M_B_CKE1[3]

M_B_CAS#[3]

M_B_RAS#[3]

R211 4.7K_4

+3V

C C

B B

M_B_WE#[3]

CLK_SCLK[5,9,23]

CLK_SDATA[5,9,23]

M_B_ODT0[3]

M_B_ODT1[3]

M_B_DM[7..0][3]

M_B_DQS[7:0][3]

M_B_DQS#[7:0][3]

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

JDIM2A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13