Page 1

5

4

3

2

1

BOM

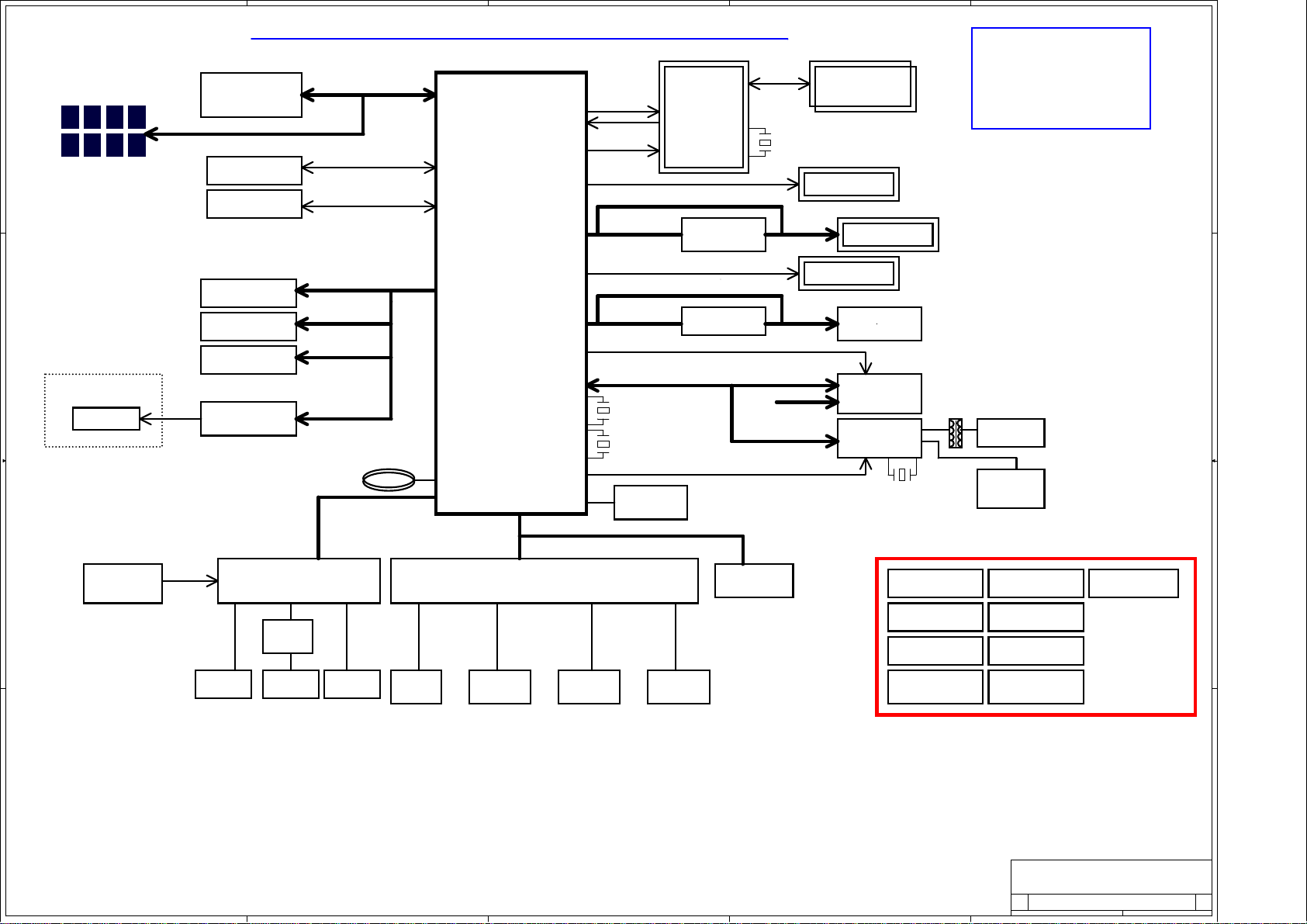

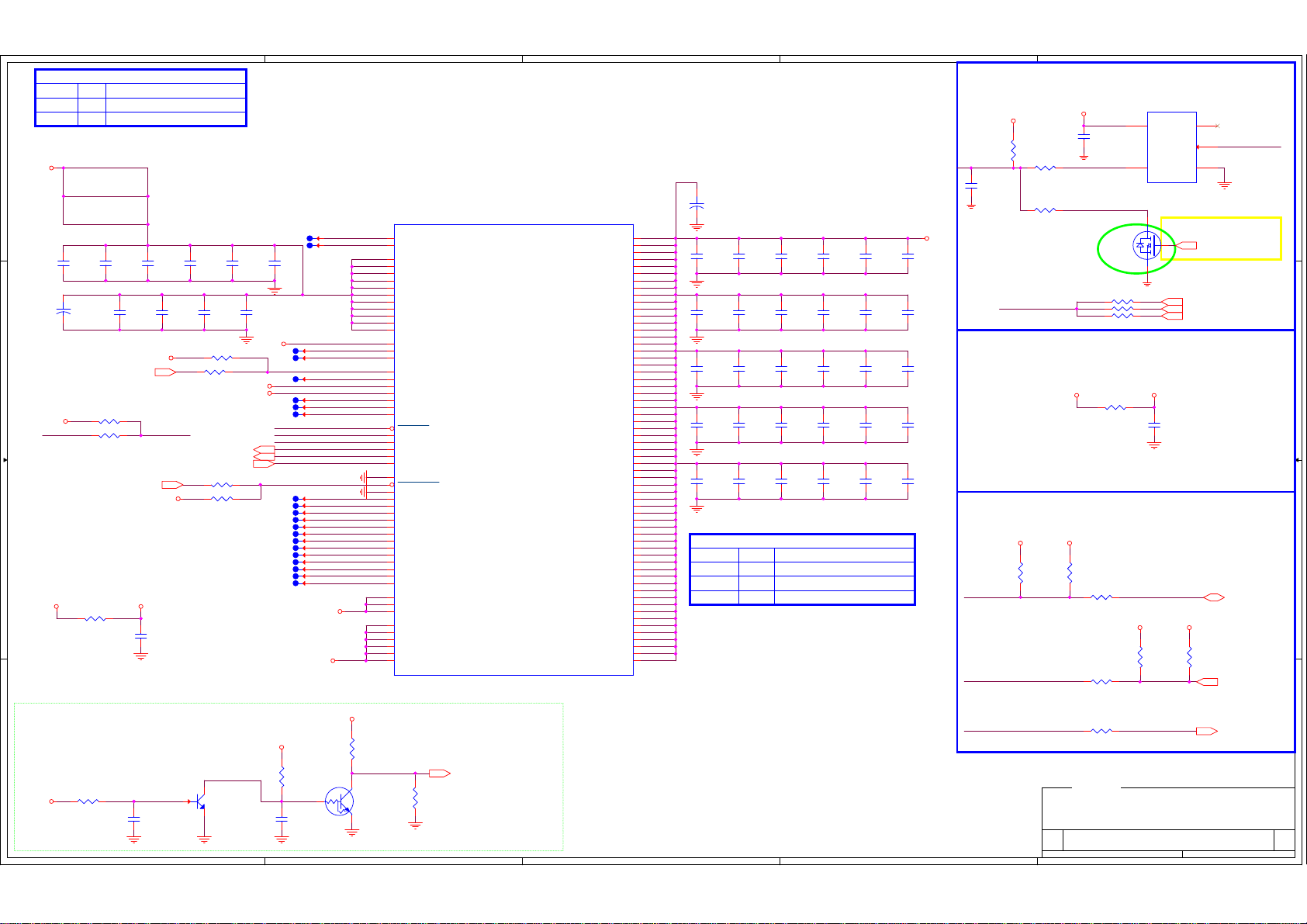

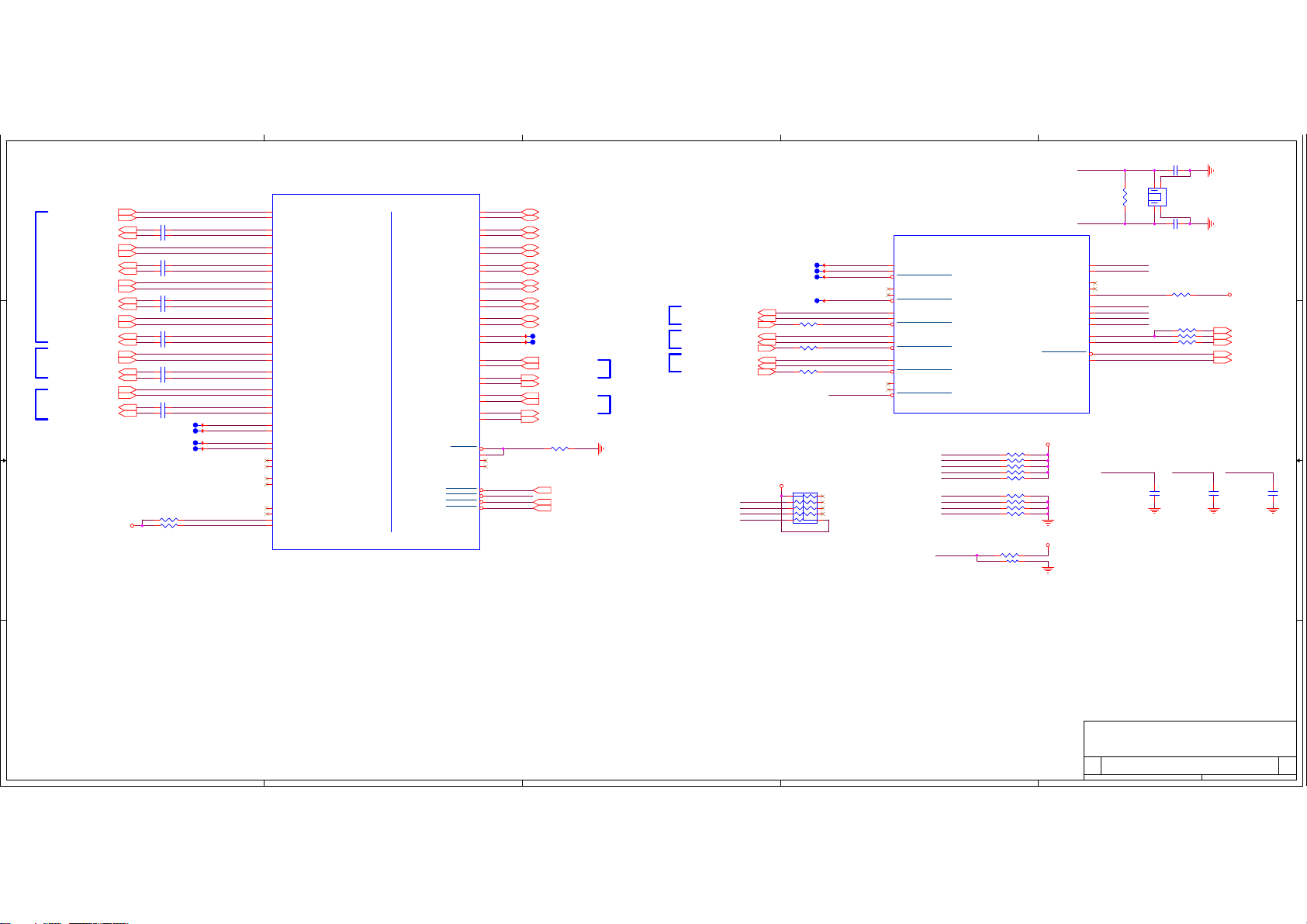

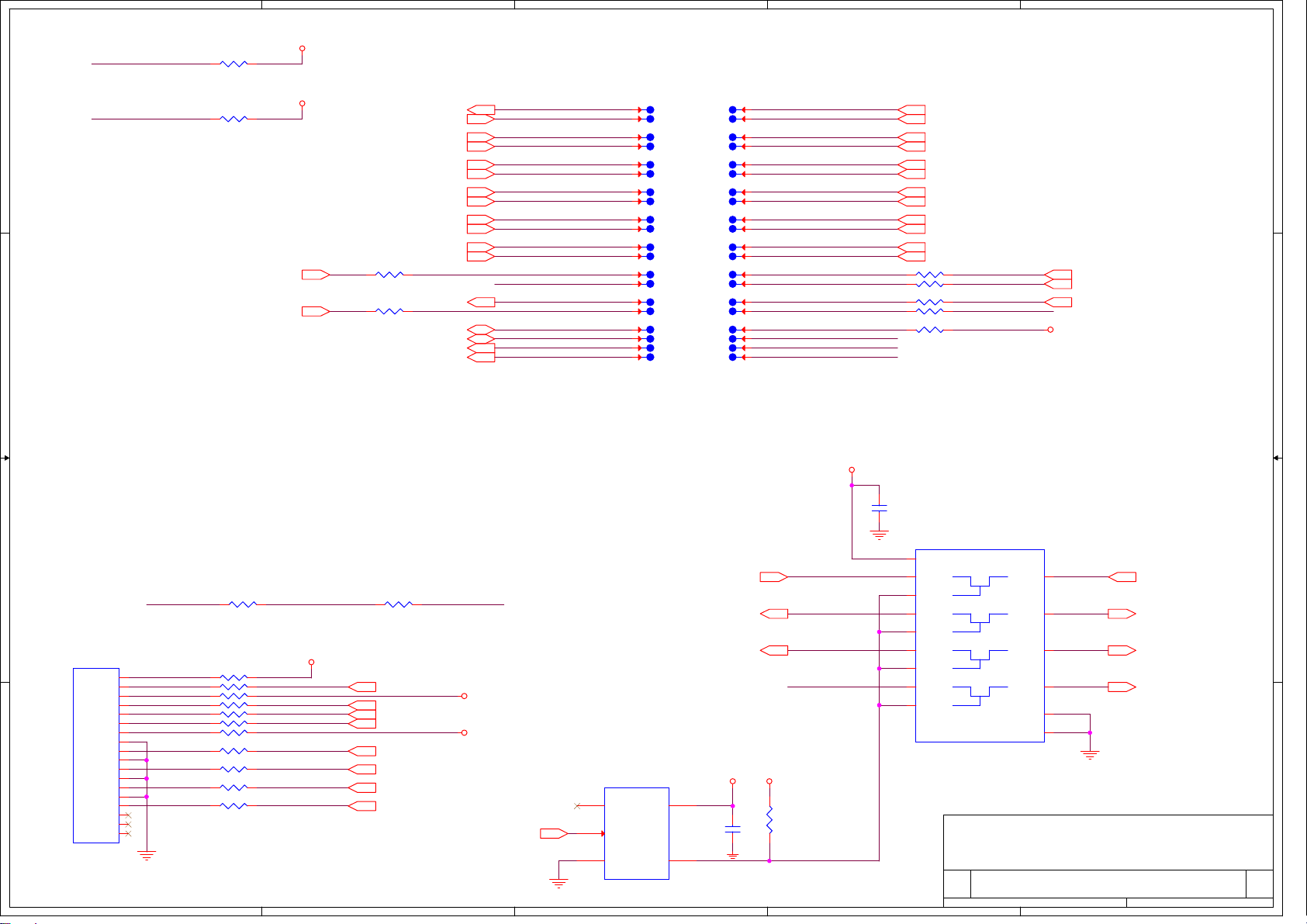

ZRQ_GDDR3 SHB ULT SYSTEM BLOCK DIAGRAM

Dual Channel DDR III

P13

P27

P26

1066/1333/1600 MHZ

SATA0

SATA1

USB2-4

USB2-2

USB2-5

USB2-6

P8

BATTERY

Azalia

Haswell ULT 15W

MCP 1168pins

IMC

DC+GT3

40 mm X 24 mm

SATA

Integrated PCH

USB2.0

RTC

IHDA

LPC

P2~P13

PCI-E x4

TX/RX

CLK

eDP

USB3.0/2.0

CLK

PCI-E x1

CLK

SPI

DP

PCIE-5

EDP

DDI2-Lane0~1

DDI2-Lane2~3

USB3-2/USB2-1

DDI1

USB3-1

USB2-0

X'TAL

32.768KHz

X'TAL 24MHz

SPI ROM

Memory Down

D D

Max. 4G

C C

2Rx16

P14

DDR3L-SODIMM

SATA - HDD

MINI CARD

mSATA SSD

USB2 IO

CCD(Camera)

Touch Screen(option)

P31

P23

P23

I/O board

I/O Board Conn.USB2 IO

P31

GPU

N14P-GV2

N14P-GE2

N14P-GT2

Display

P15~P19

DP Switch

HD3SS2521

USB Charger USB3 Port

SLG55584A

P8

P23

P31

X'TAL 27MHz

PCIE-3

USB2-3

PCIE-4

VRAM

GV2-DDR3

eDP Conn.

Mini DP Conn.

HDMI Conn.

MB side

RTL8411AAR

/RTL8411BAR

P20,P21

P24

P25

MINI CARD

WLAN+BT

10/100/1G

P23

P31

P26

P28

X'TAL 25MHz

IV@ : iGPU

EV@ : Optimus

SW@ : With DP switch

NSW@ : W/O DP switch

TPL@ : Touch screen

KBL@ : Keyboard backlight

TPM@ : TPM

RJ45

P27

Cardreader

CONN. 2in 1

P29

01

P24

EC

IT8587

Image Sensor

P32

TPM(option)

P33

Fan Driver

(PWM Type)

P32

3

P27

2

BQ24737A

Batery Charger

TPS51225

+3V/+5V

TPS51622

+VCCIN

TPS51211

+1.05V_S5/+1.05V

TPS51216

+1.35V_SUS

P34

TPS54318

+1.5V

P35

UP1642

+VGPU_CORE

P38

TPS51211

+1.5V_GFX/1.05V_GFX/3V_GFX

P36

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Thermal Protection

P37

Discharger

P39

P40

P41

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Block Diagram

Block Diagram

Block Diagram

1

ZRQ

ZRQ

ZRQ

1 47Friday, April 12, 2013

1 47Friday, April 12, 2013

1 47Friday, April 12, 2013

P39

3A

3A

3A

B B

DMIC Array

Int. MIC

P30

Combo HP

A A

5

ALC3225

AUDIO CODEC

ALC1001

P30

AMP

P30 P30 P30

P30

Speaker*2Speaker*2

K/B Con.

P32

4

OCH1691WAD

HALL SENSOR

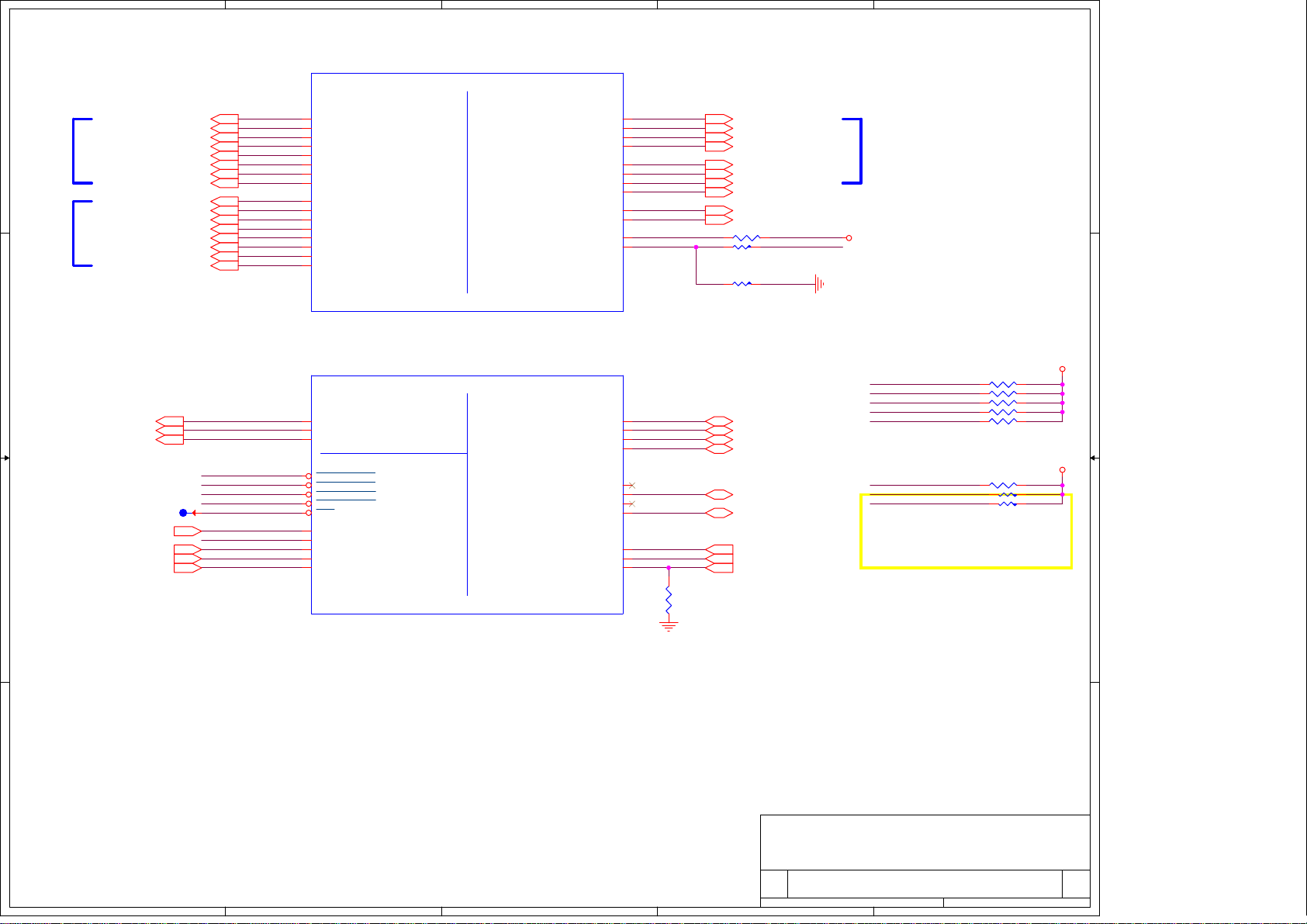

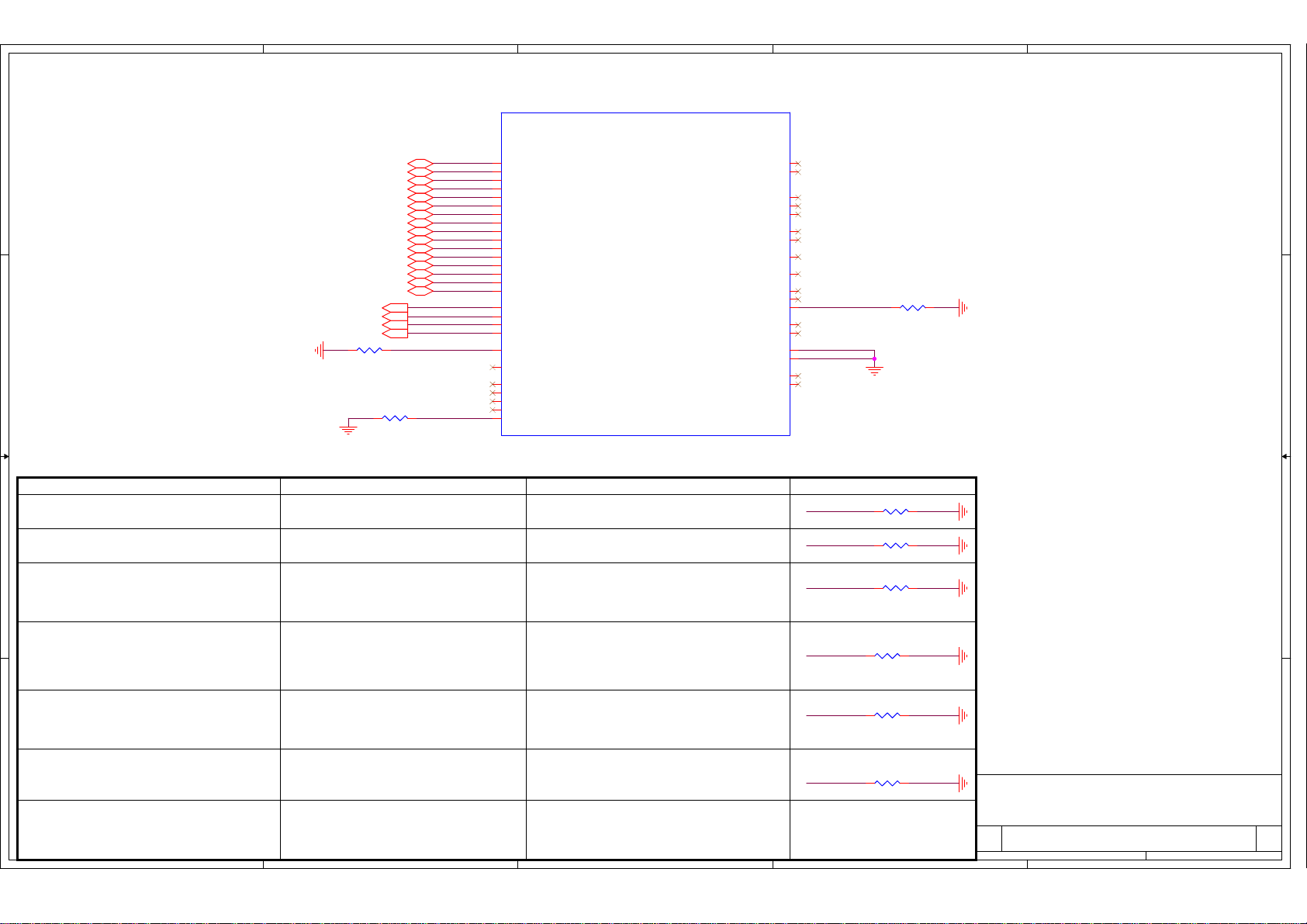

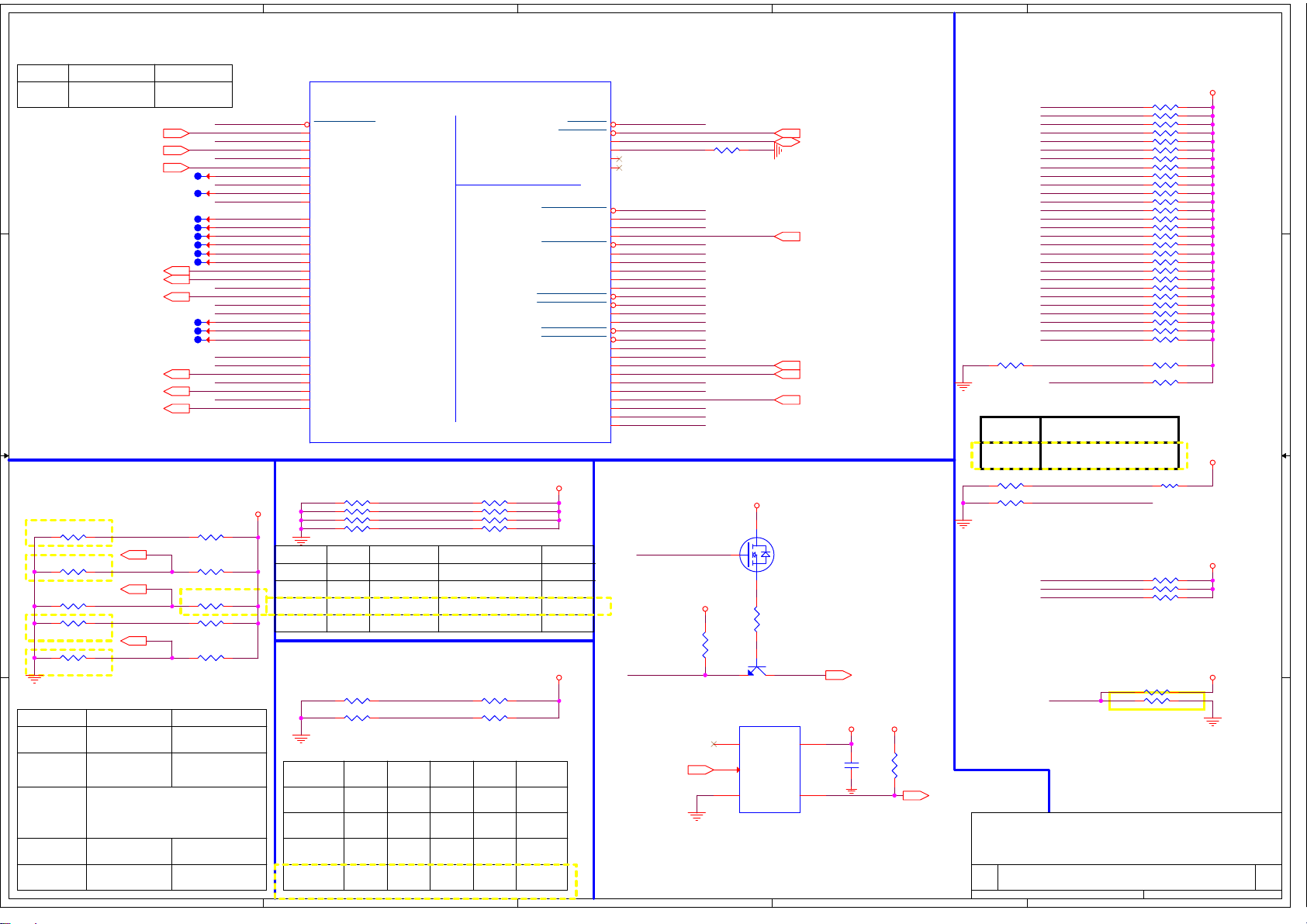

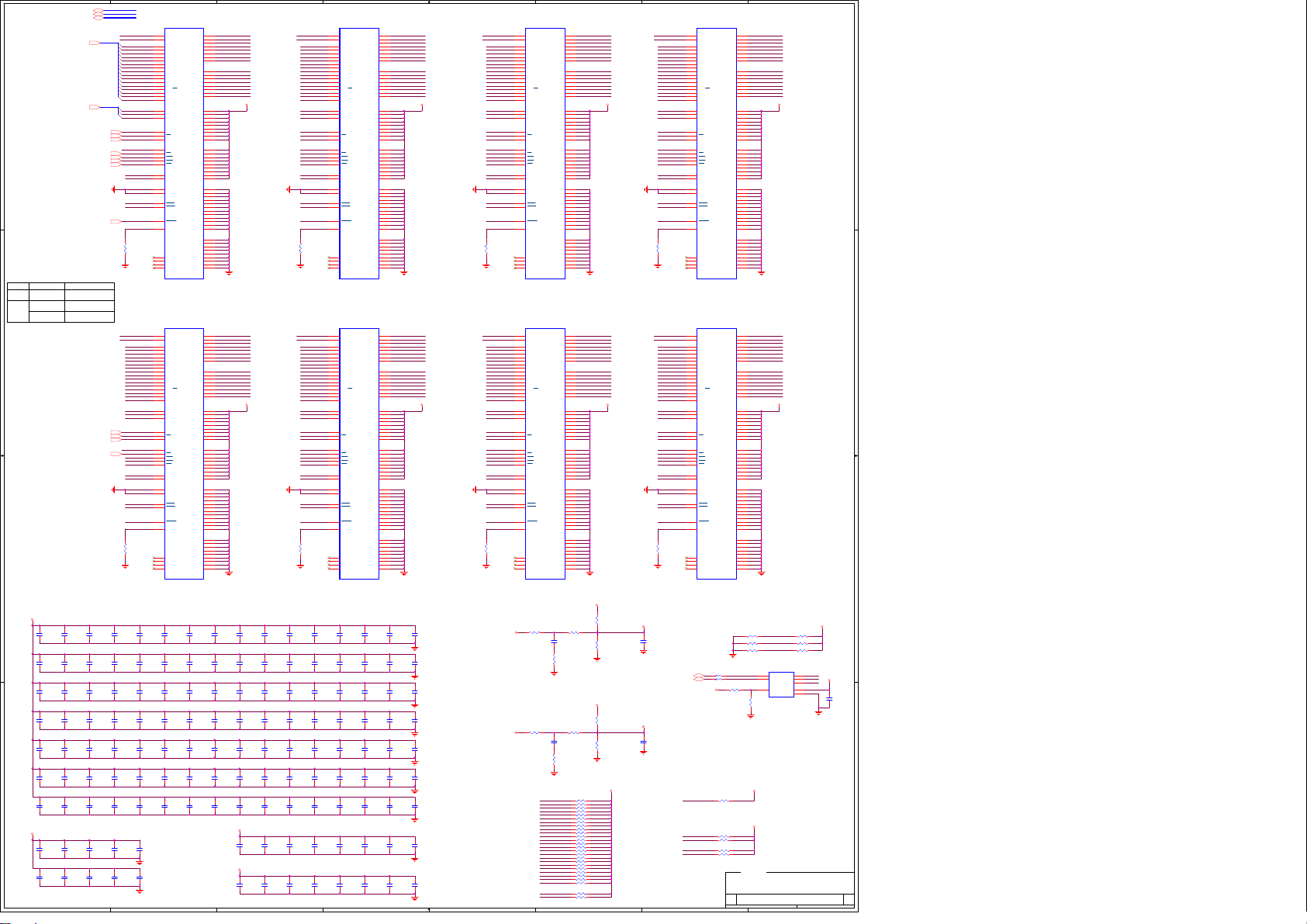

Page 2

5

4

3

2

1

Haswell ULT (DISPLAY,eDP)

U42A

HSW_ULT_DDR3L

02

D D

HDMI

Mini DP

C C

B B

INT_HDMITX2N25

INT_HDMITX2P25

INT_HDMITX1N25

INT_HDMITX1P25

INT_HDMITX0N25

INT_HDMITX0P25

INT_HDMICLK-25

INT_HDMICLK+25

DP2_TXN023

DP2_TXP023

DP2_TXN123

DP2_TXP123

DP2_TXN223

DP2_TXP223

DP2_TXN323

DP2_TXP323

PCH_BRIGHT24

PCH_BLON24

PCH_VDDEN24

TP46

TP_INT_PCH24

BOARD_ID410

BOARD_ID110

BOARD_ID210,32

PCH_BRIGHT

PCH_BLON

PCH_VDDEN

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

PCI_PME#

DGPU_SELECT#

BOARD_ID4

BOARD_ID1

BOARD_ID2

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

AD4

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U42I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

+3V

GPIO55

+3V

GPIO52

+3V

GPIO54

+3V

GPIO51

+3V

GPIO53

eDP SIDEBAND

+3V

+3V

+3V

+3V

+3V_S5

PCIE

1 OF 19

HSW_ULT_DDR3L

9 OF 19

EDPDDI

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

R806

100K_4

EDP_TXN0 24

EDP_TXP0 24

EDP_TXN1 24

EDP_TXP1 24

EDP_TXN2 24

EDP_TXP2 24

EDP_TXN3 24

EDP_TXP3 24

EDP_AUXN 24

EDP_AUXP 24

R149 24.9/F_4

R561 *0_4

R562 *0_4

HDMI_DDCCLK_SW 25

HDMI_DDCDATA_SW 25

DDPC_CTRLCLK 23

DDPC_CTRLDAT 23

INT_DP_AUXDN 23

INT_DP_AUXDP 23

INT_HDMI_HPD 25

DP_HPD_Q 23

EDP_HPD 24

PCH_BRIGHTDP_UTIL

eDP Panel

+VCCIOA_OUT

eDP_RCOMP

Trace length < 100 mils

Trace width = 20 mils

Trace spacing = 25 mils

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

DGPU_SELECT#

TP_INT_PCH

DDPC_CTRLCLK

DDPC_CTRLDAT

DDPB/C_CTRLDATA has an iPD 20K,

When PU at rising edge of

PCH_PWROK, the DDI port will

be detected

R160 10K_4

R635 10K_4

R623 10K_4

R617 10K_4

R601 10K_4

R175 TPL@100K_4

R576 2.2K_4

R575 2.2K_4

+3V

+3V

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

5

4

3

Friday, April 12, 2013

2

PROJECT :

Haswell 3/5 (DDI/eDP)

Haswell 3/5 (DDI/eDP)

Haswell 3/5 (DDI/eDP)

ZRQ

ZRQ

ZRQ

2 47

2 47

2 47

1

3A

3A

3A

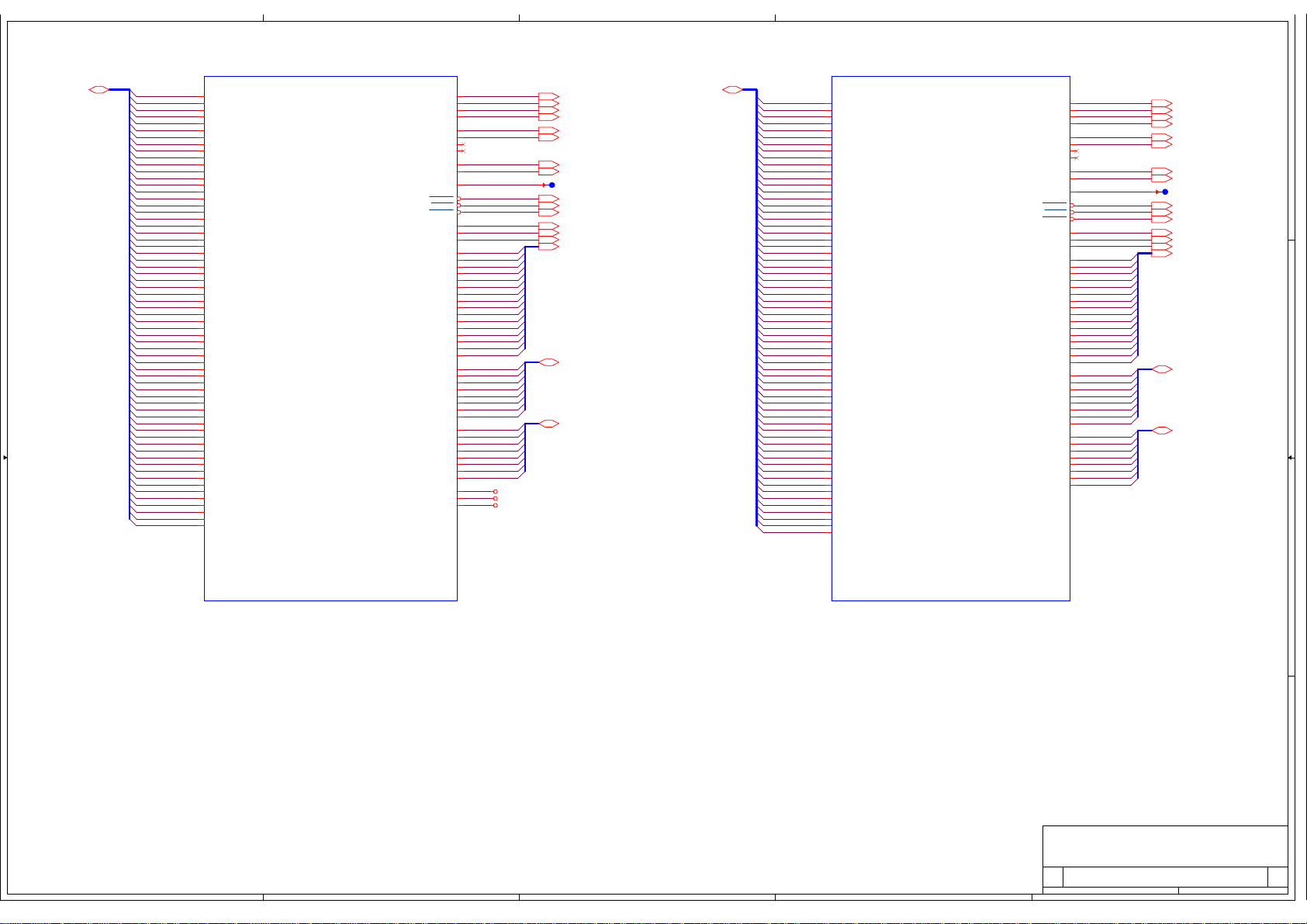

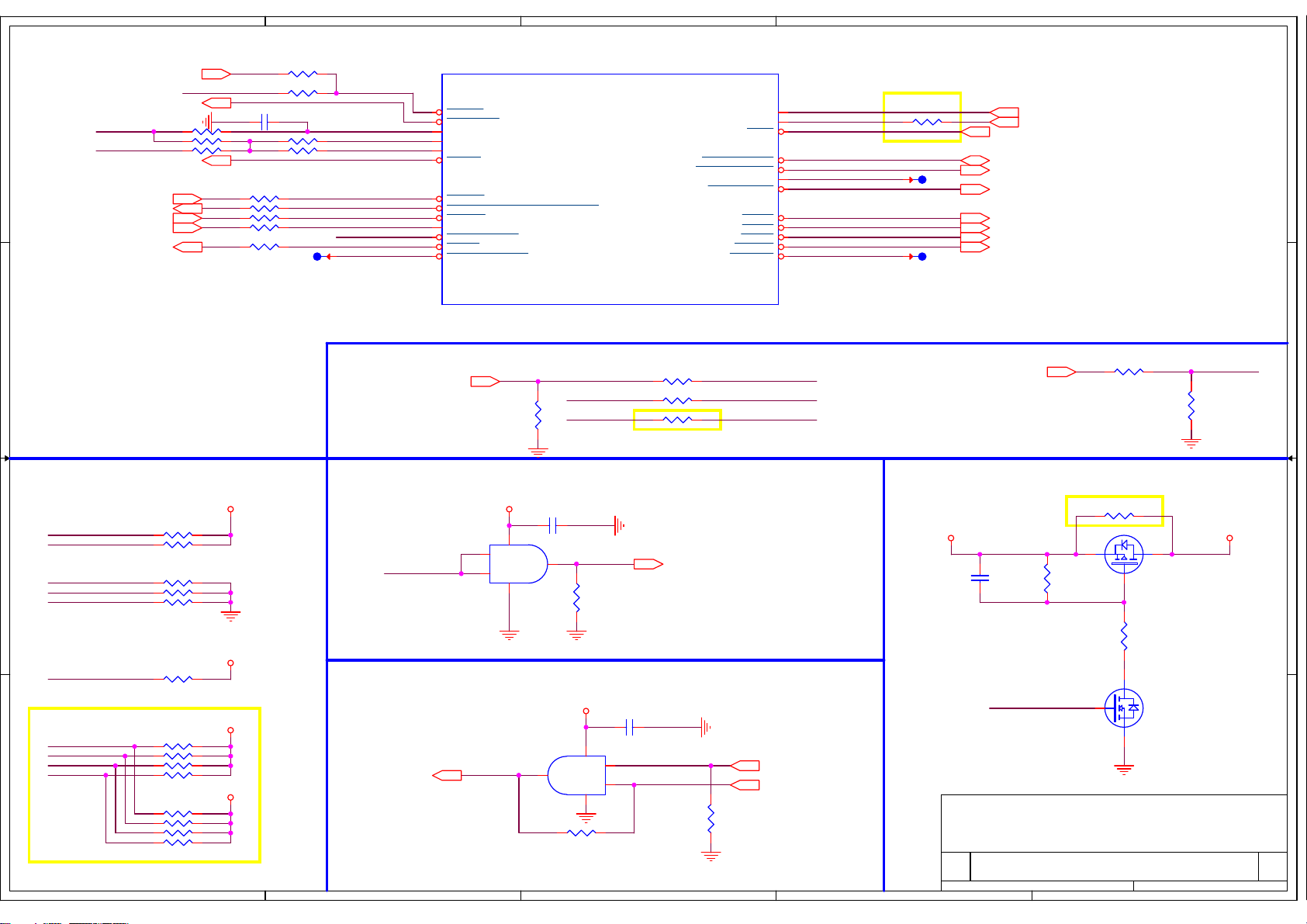

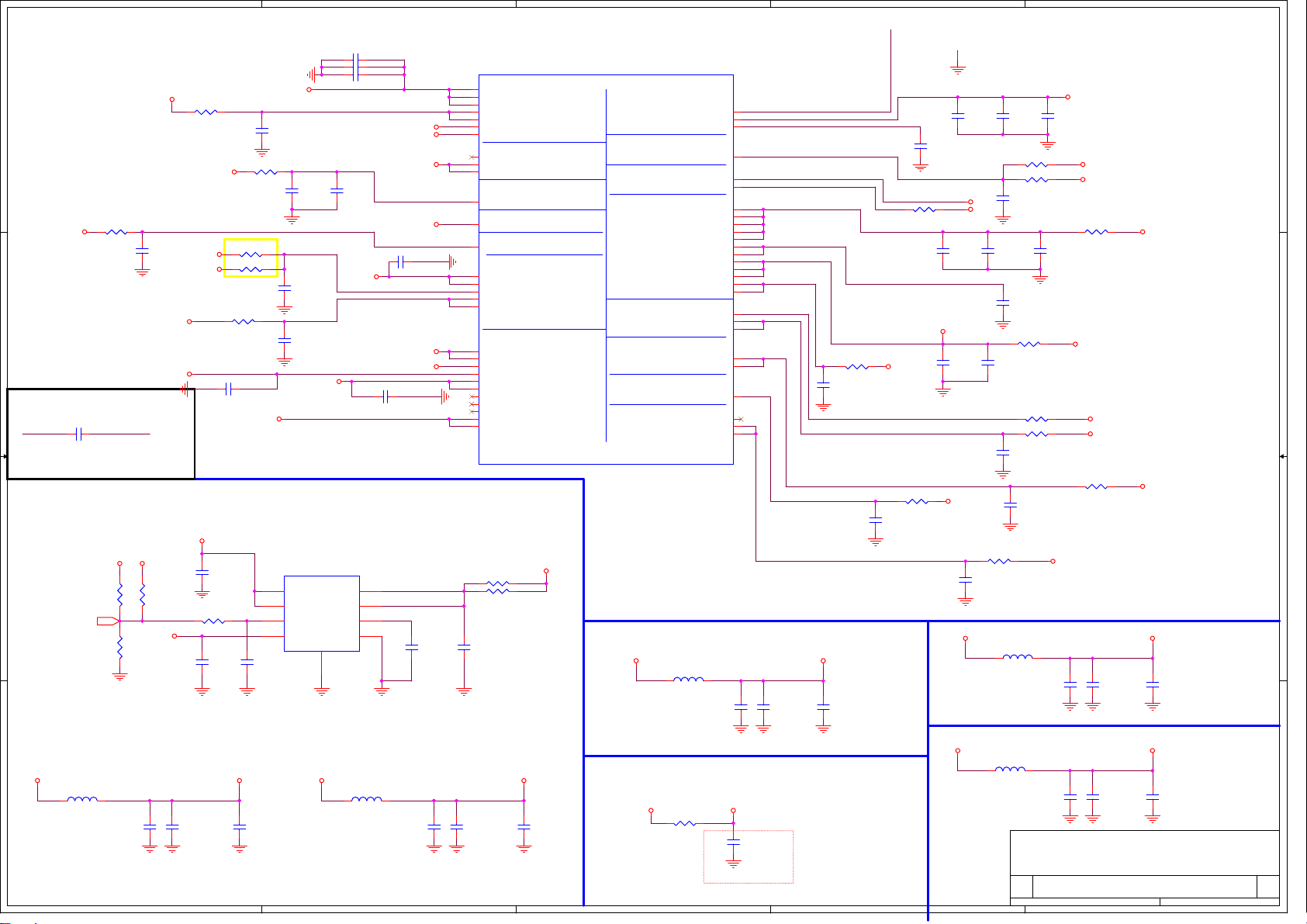

Page 3

5

4

3

Haswell ULT (DDR3L) Haswell Processor (DDR3)

U42C

M_A_DQ[63:0]14

D D

C C

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

+VREF_CA_CPU

+VREFDQ_SA_M3

+VREFDQ_SB_M3

M_A_CLK0# 14

M_A_CLK0 14

M_A_CLK1# 14

M_A_CLK1 14

M_A_CKE0 14

M_A_CKE1 14

M_A_CS#0 14

M_A_CS#1 14

TP60

M_A_RAS# 14

M_A_WE# 14

M_A_CAS# 14

M_A_BS#0 14

M_A_BS#1 14

M_A_BS#2 14

M_A_A[15:0] 14

M_A_DQS#[7:0] 14

M_A_DQS[7:0] 14

U42D

M_B_DQ[63:0]15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_B_ODT0

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_CLK0# 15

M_B_CLK0 15

M_B_CLK1# 15

M_B_CLK1 15

M_B_CKE0 15

M_B_CKE1 15

M_B_CS#0 15

M_B_CS#1 15

TP57

M_B_RAS# 15

M_B_WE# 15

M_B_CAS# 15

M_B_BS#0 15

M_B_BS#1 15

M_B_BS#2 15

M_B_A[15:0] 15

M_B_DQS#[7:0] 15

M_B_DQS[7:0] 15

03

B B

3 OF 19

A A

5

4

3 2 1

4 OF 19

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

PROJECT :

Haswell 2/5 (DDR3 I/F)

Haswell 2/5 (DDR3 I/F)

Haswell 2/5 (DDR3 I/F)

ZRQ

ZRQ

ZRQ

3 47

3 47

3 47

3A

3A

3A

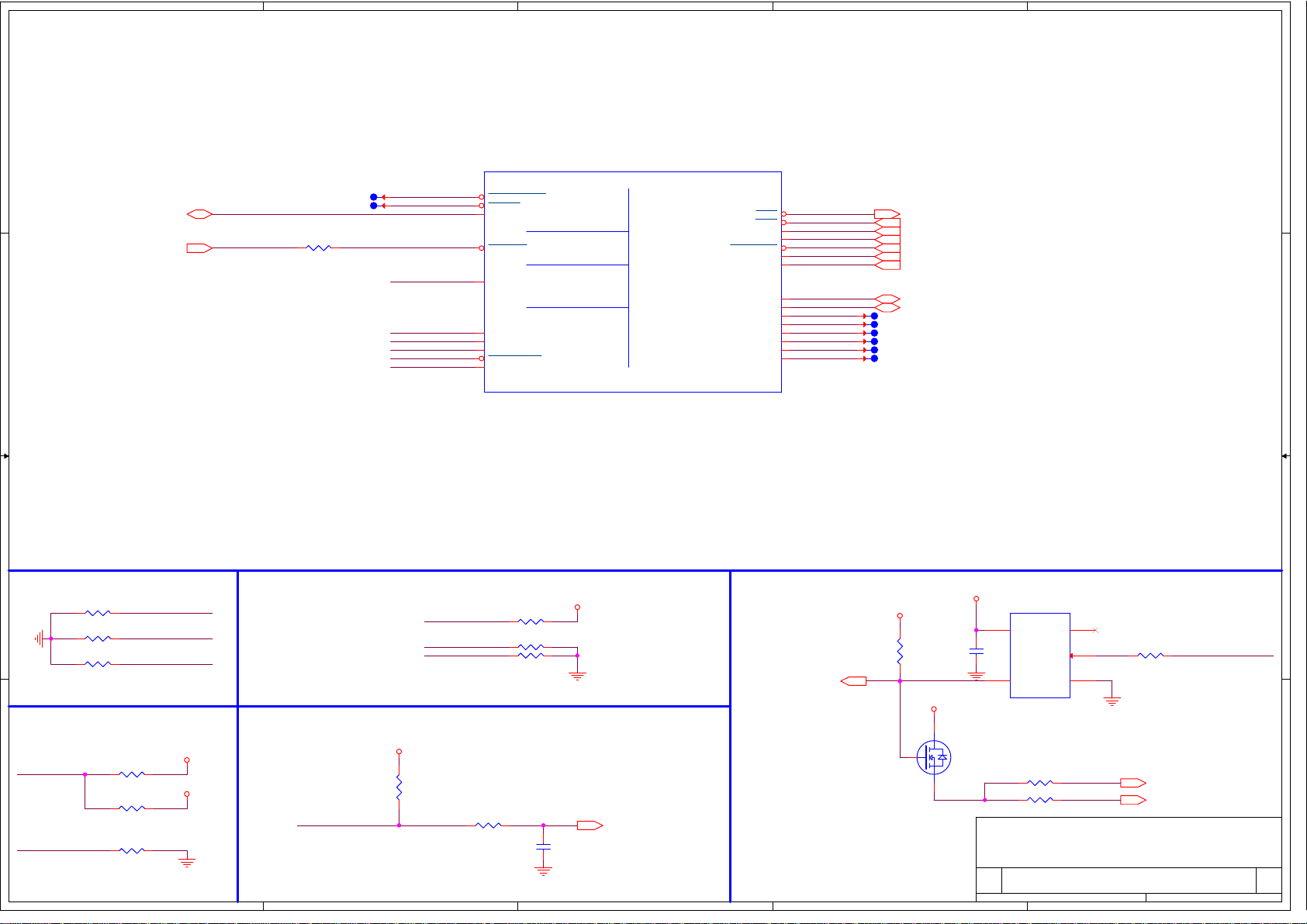

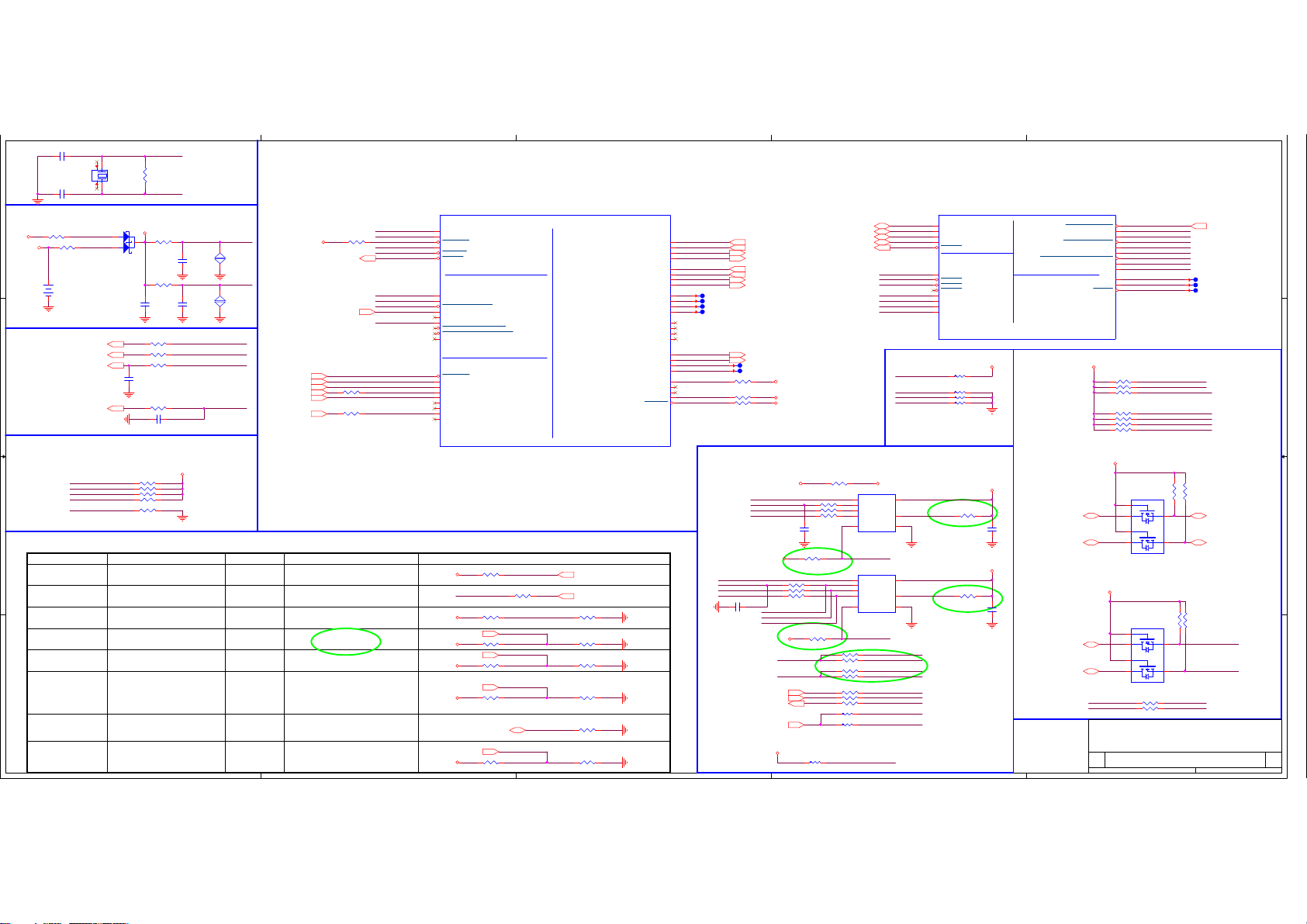

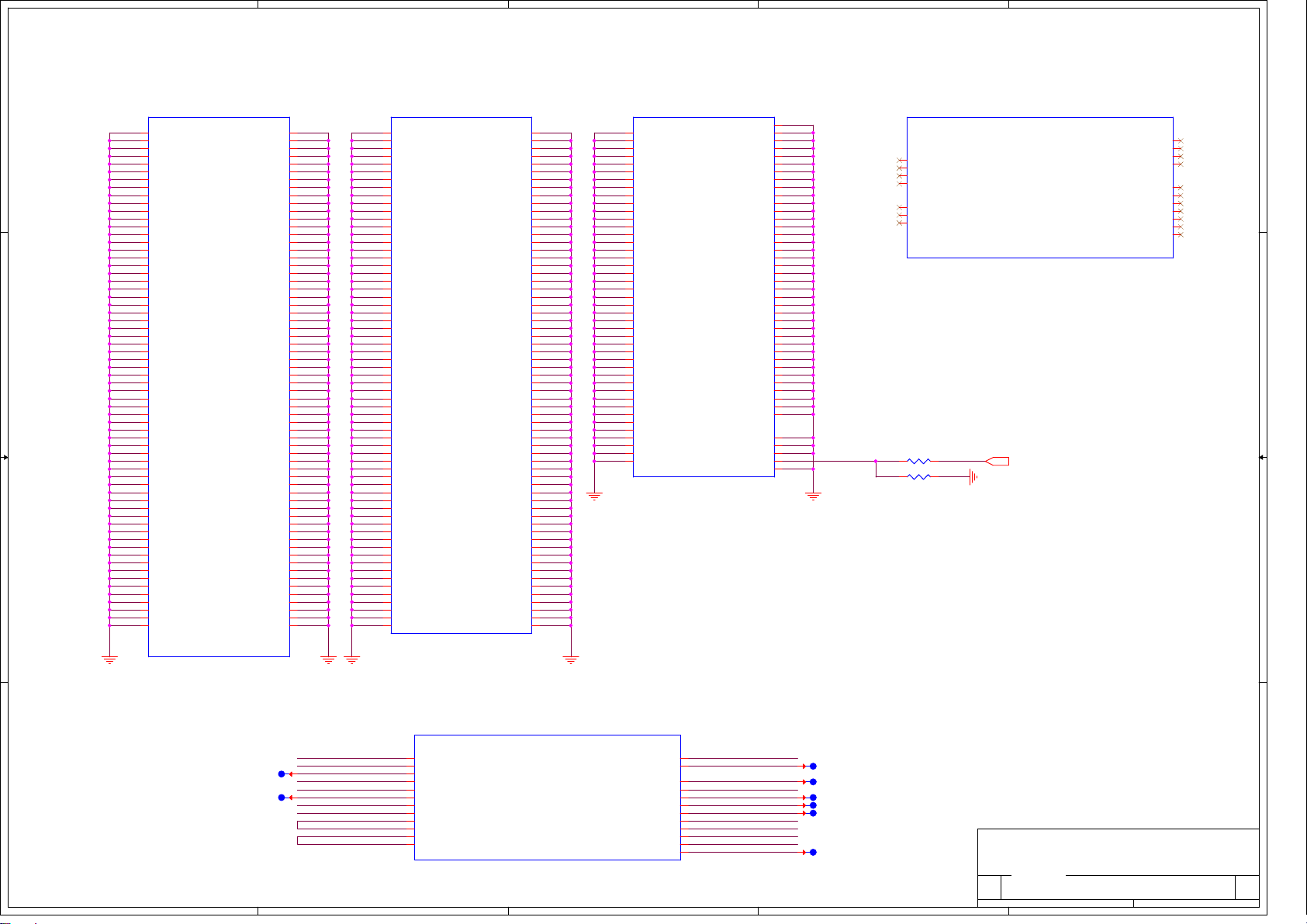

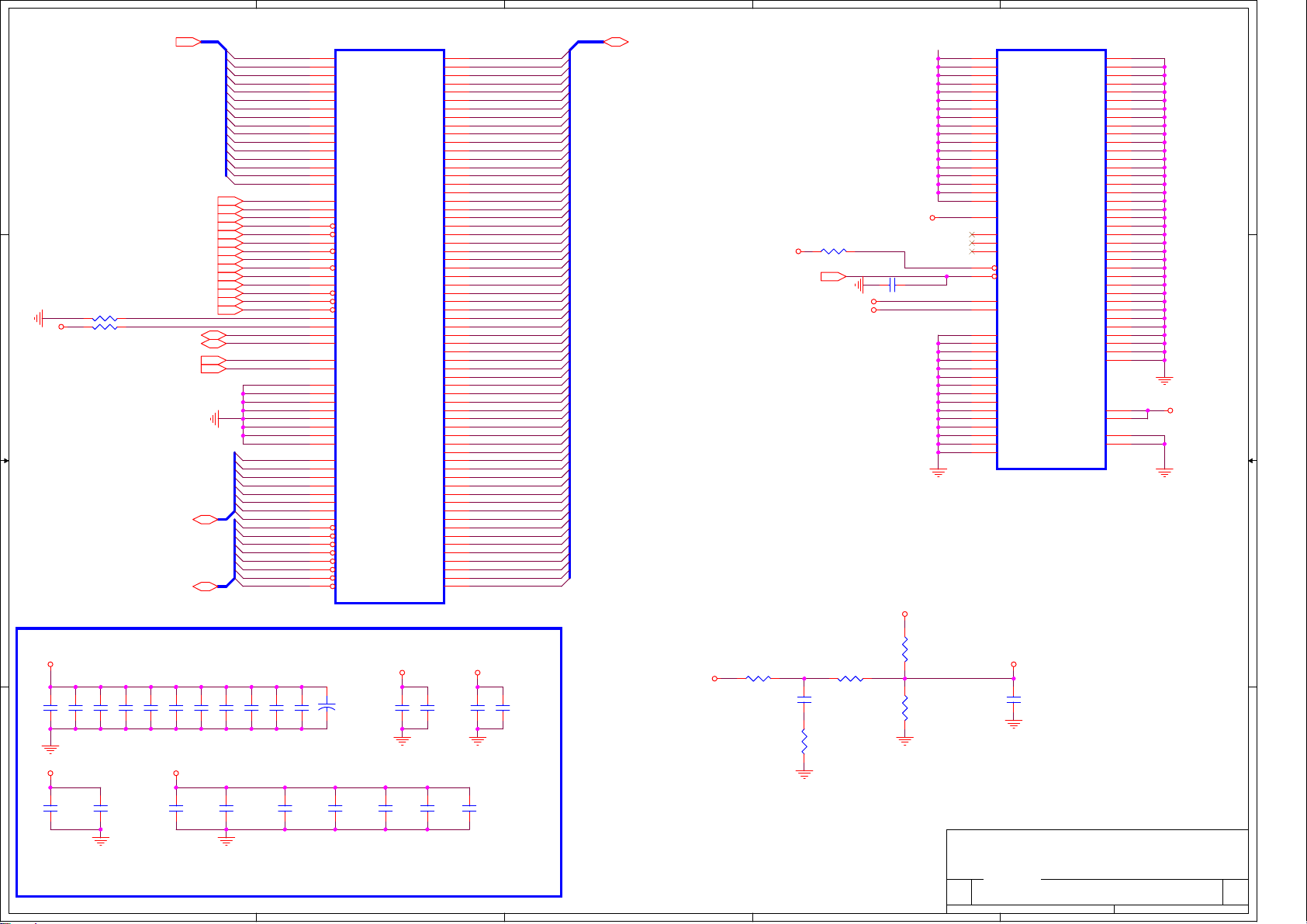

Page 4

5

4

3

2

1

04

H_PECI (50ohm)

Route on microstrip only

D D

C C

Spacing >18 mils

Trace Length: 0.4~6.125 iches

H_PWRGOOD (50ohm)

Trace Length: 1~11.25 inches

CPU_PLTRST# (50ohm)

Trace Length: 10~17 inches

H_PECI33 XDP_PRDY# 13

H_PROCHOT#33,34,38

TP79

TP25

R605 56_4

SM_RCOMP[0:2]

Trace length < 500 mils

Trace width = 12~15 mils

Trace spacing = 20 mils

PROC_DETECT

CATERR#

H_PECI

H_PROCHOT#_RH_PROCHOT#

H_PWRGOOD_R

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

DDR_PG_CTRL

Haswell ULT (SIDEBAND)

THERMAL

DDR3L

DSW

HSW_ULT_DDR3L

MISC

JTAG

PWR

2 OF 19

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

U42B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

XDP_PRDY#

K62

XDP_PREQ#

E60

XDP_TCK0

E61

XDP_TMS_CPU

E59

XDP_TRST#

F63

XDP_TDI_CPU

F62

XDP_TDO_CPU

J60

XDP_BPM#0

H60

XDP_BPM#1

H61

XDP_BPM#2

H62

XDP_BPM#3

K59

XDP_BPM#4

H63

XDP_BPM#5

K60

XDP_BPM#6

J61

XDP_BPM#7CPU_DRAMRST#

XDP_PREQ# 13

XDP_TCK0 8,13

XDP_TMS_CPU 13

XDP_TRST# 8,13

XDP_TDI_CPU 13

XDP_TDO_CPU 13

XDP_BPM#0 13

XDP_BPM#1 13

TP82

TP80

TP23

TP81

TP27

TP24

TCK,TMS

Trace Length < 9000mils

BPM#[0:7]

Trace Length 1~6 inches

Length match < 300 mils

B B

DRAM COMP

R683 200/F_4

R691 120/F_4

R686 100/F_4

PU/PD of CPU

H_PROCHOT#

A A

H_PWRGOOD_R

R613 *62_4

R614 62_4

R569 10K_4

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

5

+VCCIO_OUT

+1.05V_VCCST

DRAMRST

CPU DRAM

CPU_DRAMRST#

+1.35V_SUS

12

4

XDP_TDO_CPU

XDP_TCK0

XDP_TRST#

470_4

R141 51_4

R202 51_4

R690 *51_4

R404 *SHORT_4

+1.05V_VCCST

12

C459

*0.1u/10V_4

DDR3_DRAMRST# 14,15

3

DDR3L ODT GENERATIONXDP PU/PD

+5V_S5

12

R306

220K/F_4

DDR_VTTT_PG_CTRL37

2

0.1u/10V_4

+1.35V_SUS

3

2

1

+1.35V_SUS

U20

5

VCC

12

C271

4

Y

74AUP1G07GW

Q37

2N7002K

R738 66.5/F_4R403

R739 66.5/F_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

1

NC

2

A

GND

Haswell 1/5 (PEG/DMI/FDI)

Haswell 1/5 (PEG/DMI/FDI)

Haswell 1/5 (PEG/DMI/FDI)

R695 *SHORT_4

3

M_B_ODT0_DIMM 15

M_B_ODT1_DIMM 15

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

ZRQ

ZRQ

ZRQ

DDR_PG_CTRL

4 47

4 47

4 47

3A

3A

3A

Page 5

5

VDDQ Output Decoupling Recommendations

330uFx2 7343

22uFx11

10uFx10

D D

+1.35V_SUS

+

C C

+1.05V_VCCST

VRON_CPU IMVP_PWRGD

B B

BOT socket side

5 onTOP, 6 on BOT inside socket cavity

0805

5 onTOP, 5 on BOT inside socket cavity

0805

C258

C259

10u/6.3V_6

10u/6.3V_6

C269

*470u/2V_7343

R190 *SHORT_8

C257

2.2u/6.3V_6

VCC_SENSE38

R566 *10K_4

R567 10K_4

PWR_DEBUG13

+1.05V_VCCST+1.05V

+VCCIN

+1.05V_VCCST

C223

*4.7u/6.3V_6

C261

10u/6.3V_6

C224

2.2u/6.3V_6

+1.35V_CPU 1.4A

+1.35V_CPU

C260

10u/6.3V_6

C256

2.2u/6.3V_6

R583 100/F_4

R587 *SHORT_4

300mA

+VCCIO_OUT

300mA

+VCCIOA_OUT

VCCST_PWRGD13

VRON_CPU38

IMVP_PWRGD10,38

R173 *SHORT_4

R151 150_6

C225

10u/6.3V_6

C227

2.2u/6.3V_6

+VCCIN

C226

10u/6.3V_6

TP28

TP41

TP42

TP43

TP47

TP50

TP30

TP31

TP26

TP85

TP32

TP49

TP51

TP36

TP39

TP37

TP54

TP35

TP34

TP29

TP20

ULT_RVSD_61

ULT_RVSD_62

ULT_RVSD_63

ULT_RVSD_64

VCC_SENSE_R

ULT_RVSD_65

ULT_RVSD_66

ULT_RVSD_67

ULT_RVSD_68

H_CPU_SVIDART#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

VCCST_PWRGD

VRON_CPU

IMVP_PWRGD

PWR_DEBUG_R

ULT_RVSD_69

ULT_RVSD_70

ULT_RVSD_71

ULT_RVSD_72

ULT_RVSD_73

ULT_RVSD_74

ULT_RVSD_75

ULT_RVSD_76

ULT_RVSD_77

ULT_RVSD_78

ULT_RVSD_79

ULT_RVSD_80

ULT_RVSD_81

+1.05V_VCCST

+VCCIN

4

Haswell ULT (POWER)

HSW_ULT_DDR3L

HSW ULT POWER

12 OF 19

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

AC58

AB23

AD23

AA23

AE59

AD60

AD59

AA59

AE60

AC59

AG58

AC22

AE22

AE23

AB57

AD57

AG57

L59

J58

F59

N58

E63

A59

E20

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

U59

V59

C24

C28

C32

U42L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

3

+

C537

*470u/2V_7343

C46

C190

22u/6.3V_8

22u/6.3V_8

C210

C567

22u/6.3V_8

22u/6.3V_8

C562

C167

22u/6.3V_8

22u/6.3V_8

C204

C173

22u/6.3V_8

22u/6.3V_8

C548

C168

*22u/6.3V_8

*22u/6.3V_8

VCC Output Decoupling Recommendations

470uFx4 7343

22uFx8

22uFx11

10uFx11

0805

0805

0805

+VCCIN 32A

C73

C561

22u/6.3V_8

C201

22u/6.3V_8

C169

22u/6.3V_8

C170

22u/6.3V_8

C542

*22u/6.3V_8

C228

22u/6.3V_8

C206

22u/6.3V_8

C165

22u/6.3V_8

C203

22u/6.3V_8

C74

*22u/6.3V_8

22u/6.3V_8

C557

22u/6.3V_8

C45

22u/6.3V_8

C172

22u/6.3V_8

C71

*22u/6.3V_8

TOP socket side

4 on TOP, 4 on BOT near socket edge

TOP, inside socket cavity

BOT, inside socket cavity

2

C75

22u/6.3V_8

C202

22u/6.3V_8

C171

22u/6.3V_8

C205

22u/6.3V_8

C560

*22u/6.3V_8

VCCST PWRGD

VCCST_PWRGD

C582

*0.1u/10V_4

+VCCIN

SVID

H_CPU_SVIDDAT

H_CPU_SVIDART#

+1.05V_VCCST

R551

10K_4

R545 0_4

R582 *0_4

VCCST_PWRGD_EN

Layout note: need routing together

and ALERT need between CLK and DATA.

+VCCIO_OUT

R621

*130/F_4

Place PU resistor

close to CPU

Place PU resistor

close to CPU

CRB is via +1.05V PG

+3V_S5

VCCST_PWRGD_R

HWPG_1.05V_EC

B-stage DNP

+1.05V_VCCST

R618

130/F_4

R625 *SHORT_4

R630 43_4

C584

0.1u/10V_4

R536 *0_8

Q60

2N7002K

R579 *0_4

R544 *0_4

R580 0_4

+VCCIO_OUT+1.05V

+1.05V_VCCST

5

4

1

U38

VCC

Y

74AUP1G07GW

3

1

R640

75_4

1

NC

2

A

3

GND

Reserve from EC

2

HWPG_1.05V_S5 13,33,36

EC_PWROK 7,33

APWORK 7,33

C580

*4.7u/6.3V_6

+VCCIO_OUT

R633

*75_4

05

VCCST_PWRGD_EN

HWPG_1.05V_EC# 33

VR_SVID_DATA 38

VR_SVID_ALERT# 38

HWPG_1.05V for DDR=1.5V

+3V

A A

C487

*1000p/50V_4

2

Q45

1 3

*MMBT3904-7-F

+1.05V

R454 *4.7K_4

5

R451

*4.7K_4

C485

*1000p/50V_4

+3V

R463

*4.7K_4

HWPG_1.05V 33

2

Q46

1 3

*DTC144EU

R453

*100K/F_4

10/30 reserve

DDR=1.5V ,This block POP

4

3

2

H_CPU_SVIDCLK

R641 *SHORT_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

PROJECT :

Haswell 4/5 (POWER)

Haswell 4/5 (POWER)

Haswell 4/5 (POWER)

1

VR_SVID_CLK 38

ZRQ

ZRQ

ZRQ

5 47

5 47

5 47

3A

3A

3A

Page 6

5

4

3

Haswell ULT (CFG,RSVD)

U42S

HSW_ULT_DDR3L

06

D D

NOA_STBN_013

NOA_STBN_113

NOA_STBP_013

NOA_STBP_113

C C

CFG013

CFG113

CFG213

CFG313

CFG48,13

CFG513

CFG613

CFG713

CFG813

CFG913

CFG1013

CFG1113

CFG1213

CFG1313

CFG1413

CFG1513

R177 49.9/F_4

R572 8.2K_4

NOA_STBN_0

NOA_STBN_1

NOA_STBP_0

NOA_STBP_1

CFG_RCOMP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

TD_IREF

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

J20

H18

B12

A5

E1

D1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

TD_IREF

RESERVED

PROC_OPI_RCOMP

19 OF 19

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

OPI_COMP1

R700 49.9/F_4

Processor Strapping

1 0

CFG0

EAR-STALL/NOT STALL RESET SEQUENCE

AFTER PCU PLL IS LOCKED

CFG1

PCH/ PCH LESS MODE SELECTION

B B

CFG3

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

CFG 8

ALLOW THE USE OF NOA ON LOCKED UNITS

(DEFAULT) NORMAL OPERATION; NO STALL

(DEFAULT) NORMAL OPERATION

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED

TO

EMBEDDED DISPLAY PORT

DISABLED(DEFAULT); IN THIS CASE, NOA

WILL BE DISABLED IN LOCKED UNITS AND

ENABLED IN UN-LOCKED UNITS

STALL

PCH-LESS MODE

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS

CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED; NOA WILL BE AVAILABLE

REGARDLESS OF THE LOCKING OF THE UNIT

CFG0

CFG1

CFG3

CFG8

R203 *1K_4

R184 *1K_4

R192 *1K_4

R171 *1K_4

CFG9

NO SVID PROTOCOL CAPABLE VR

CONNECTED

A A

CFG10

SAFE MODE BOOT

5

VRS SUPPORTING SVID PROTOCOL ARE

PRESENT

POWER FEATURES ACTIVATED

DURING RESET

4

NO VR SUPPORTING SVID IS PRESENT. THE

CHIP WILL NOT GENERATE (OR RESPOND TO)

SVID ACTIVITY

POWER FEATURES (ESPECIALLY CLOCK

GATINE ARE NOT ACTIVATED

3 2 1

CFG9

CFG10

R172 *1K_4

R183 *1K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

PROJECT :

Haswell 5/5 (CFG/GND)

Haswell 5/5 (CFG/GND)

Haswell 5/5 (CFG/GND)

ZRQ

ZRQ

ZRQ

6 47

6 47

6 47

3A

3A

3A

Page 7

5

4

3

Haswell ULT PCH (PM)

PCH_SUSACK#33

D D

SYS_PWROK

EC_PWROK

PCH_SUSPWARN#33

DNBSWON#33

ACPRESENT34

PCH_SLP_S0#13,33

RSMRST#33

PCH_SUSPWRACK

SYS_RESET#13

R656 0_4

R555 *0_4

R542 *0_4

PCI_PLTRST#33

R662 *0_4

R658 0_4

C617 *1u/6.3V_4

R705 *0_4

R547 *0_4

R719 *SHORT_4

R659 *0_4

R274 *SHORT_4

R277 *SHORT_4

R653 *SHORT_4

TP55

SUSACK#_R

SUSACK#_R

SYS_RESET#

SYS_PWROK_R

EC_PWROK_R

APWROK_R

PCI_PLTRST#

PCH_RSMRST#

PCH_SUSPWRACK

PCH_PWRBTN#

PCH_ACPRESENT

PCH_BATLOW#

PCH_SLP_S0#_R

PCH_SLP_WLAN#

U42H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

AW6

AV4

AL7

AJ8

AN4

AF3

AM5

+3V_S5

PLTRST

RSMRST

SUSWARN/SUSPWRDNACK/GPIO30

PWRBTN

ACPRESENT/GPIO31

BATLOW/GPIO72

SLP_S0

SLP_WLAN/GPIO29

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

+3V

+3V_S5

+3V_S5

DSW

DSW

DSW

DSW

+3V_S5

DSW

+3V_S5

8 OF 19

DSWVRMEN

DPWROK

DSW

CLKRUN/GPIO32

SUS_STAT/GPIO61

DSW

DSW

DSW

DSW

DSW

WAKE

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

AW7

DSWVREN

AV5

DPWROK_R

AJ5

PCIE_LAN_WAKE#

V5

CLKRUN#

AG4

AE6

PCH_SUSCLK

AP5

PCH_SLP_S5#

AJ6

SUSC#

AT4

SUSB#

AL5

PCH_SLP_A#

AP4

PCH_SLP_SUS#

AJ7

PCH_SLP_LAN#

Deep Sx

R722 *SHORT_4

TP44

TP58

DSWVREN 8

DPWROK 33

PCIE_LAN_WAKE# 26,28

CLKRUN# 27,33

LPCPD# 27

PCH_SLP_S5# 13

SUSC# 13,33

SUSB# 13,33

PCH_SLP_A# 13

PCH_SLP_SUS# 33

07

C C

PCH PM PU/PD

+3V

CLKRUN#

SYS_RESET#

B B

A A

PCH_RSMRST#

SYS_PWROK

DPWROK_R

PCH_SUSPWRACK

PCH_ACPRESENT

PCH_BATLOW#

PCIE_LAN_WAKE#

PCH_PWRBTN#

R176 8.2K_4

R644 10K_4

R707 10K_4

R565 *10K_4

R721 100K/F_4

+3V_S5

R696 10K_4

+3V_S5

R259 *10K_4

R262 *8.2K_4

R264 *10K_4

R261 *10K_4

+3VPCU

R272 10K_4

R275 8.2K_4

R276 1K_4

R273 *10K_4

5

DSW PU

Power Sequence

PCH_PWROK33

R354

100K_4

EC_PWROK SYS_PWROK_R

R353 *SHORT_4

R543 *0_4

R720 *0_4

Non Deep Sx

EC_PWROK_R

DPWROK_RRSMRST#

PLTRST# Buffer Deep Sx Circuit

+3V

PCI_PLTRST#

2

1

3 5

C255 0.1u/10V_4

4

U19

TC7SH08FU

R242

100K_4

PLTRST# 13,16,26,27,28,33

+3V_S5 +3VCC_S5

*0.33u/10V_6

SYSPWOK

+3V_S5

C583 *0.1u/10V_4

2

SYS_PWROK13

4

SYS_PWROK

4

U37

TC7SH08FU

3 5

R556 *0_4

EC_PWROK

1

3 2 1

EC_PWROK 5,33

IMVP_PWRGD_3V 10

R550

10K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

APWORK5,33

R413 0_4

Speed up 250ms to boot up

for EC power on 250 ms

Non Deep Sx

R300 *0_6

1

R302

C282

PCH_SLP_SUS#

100K_4

2

Q35

2N7002K

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LPT 1/6 (DMI/FDI/VGA)

LPT 1/6 (DMI/FDI/VGA)

LPT 1/6 (DMI/FDI/VGA)

2

3

1

Q34

AO3413

R303

*SHORT_6

ZRQ

ZRQ

ZRQ

R414

10K_4

3

7 47

7 47

7 47

APWROK_R

3A

3A

3A

Page 8

RTC Clock 32.768KHz (RTC)

C624 18p/50V_4

C625 18p/50V_4

RTC Circuitry (RTC)

D D

R373 *S HORT_6

+3VPCU

R363 1K _4

+3V_RTC_0

+3V_RTC_[0:2]

Trace width = 20 mils

12

CN14

BAT_CONN

HDA

PCH_AZ_CODEC_RST#30

PCH_AZ_CODEC_SDOUT30

PCH_AZ_CODEC_BITCLK30

C C

PCH_AZ_CODEC_SYNC30

PCH JTAG

JTAG_TCK,JTAG_TMS

Trace Length < 9000mils

XDP_TMS

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

XDP_TCK1

B B

ULT Strapping Table

Pin Name Strap description

GPIO81(SPKR)

HDA_SDO

INTVRMEN

GPIO66

GPIO86

GPIO15

A A

CFG4

DSWVREN

5

Y7

32.768KHZ

D21

BAT54C

RTC_X1

R699

10M_4

RTC_X2

+3V_RTC

Trace width = 30 mils

+3V_RTC

R754

20K/F_4

R750

20K/F_4

C676

1u/6.3V_4

R703 33_ 4

R701 33_ 4

R698 33_ 4

C639

*10p/50V_4

R726 33_ 4

C638 *10p/50V_4

C671

1u/6.3V_4

C670

1u/6.3V_4

23

+3V_RTC_2

+3V_RTC_1

4 1

MP remove(Intel)

R200 51_4

R201 51_4

R216 51_4

R650 *1K_4

R657 *51_4

No reboot on TCO Timer

expiration

Flash Descriptor Security

Override / Intel ME Debug Mode

+1.05V_S5

Integrated 1.05V VRM enable ALWAYS

Top-Block Swap override

Boot BIOS Strap Bit

TLS(Transport layer security)

DP presence strap

Deep Sx well on die VR enable

5

RTC_RST#

12

J6

*JUMP

SRTC_RST#

12

J5

*JUMP

HDA_RST#_R

HDA_SDO_R

HDA_BCLK_R

HDA_SYNC_R

Sampled

PWROK

PWROK

R708 1M_4

+3V_RTC

RTC_RST#13

PCH_AZ_CODEC_SDIN030

XDP_TRST#4,13

XDP_TCK113

XDP_TDI13

XDP_TDO13

XDP_TMS13

XDP_TCK04,13

R215 *S HORT_4

R652 *S HORT_4

Configuration note

0 = Default enable (iPD 20K)

1 =Disable No-Reboot mode

0 = Default can program ME (iPD 20K)

1 =can't program ME

1=Should be always pull-up

0 = Default disable (iPD 20K)

1 = Enable TBS function

0 = Default SPI (iPD 20K)

1 =LPC

0 = Default enable w/o

confidentiality(iPD 20K)

1 =Default enable with

confidentiality

0 = Enable an external display

port is connected to the eDP

1 =disable

1=Should be always pull-up

4

Haswell ULT PCH (RTC/HDA/SATA/SPI)

HSW_ULT_DDR3L

SATA_RN0/PERN6_L3

+3V

+3V

+3V

+3V

SPKR 10,30

ME_WR# 33

R704 *3 30K_4

R577 *1 K_4

R129 *1 K_4

R189 *1 K_4

R193 1K _4

R706 *3 30K_4

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

RTC

AUDIO SATA

JTAG

5 OF 19

SPKR

R702 *S HORT_4 R97 33_4

PCH_INTVRMEN

GPIO66

GPIO86

GPIO15

CFG4

CFG46,13

DSWVREN

RTC_X1

RTC_X2

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BCLK_R

HDA_SYNC_R

HDA_RST#_R

HDA_SDO_R

XDP_TCK1

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

4

U42E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

+3V

+3V_RTC

+3V

+3V

+3V_S5

DSWVREN7

+3V_RTC

R642 *1 K_4

HDA_SDO_R

R717 330 K_4

GPIO6610

R578 *1 K_4

GPIO8610

R136 *1K_4

GPIO1510

R195 8.2K _4

R718 330 K_4

3

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

3

J5

H5

B15

A15

J8

H8

A17

B17

J6

TP19

H6

TP17

B14

TP15

C15

TP13

F5

E5

C17

D17

V1

U1

VGPU_EN

V6

GPIO36

AC1

GPIO37

A12

SATA_IREF

L11

K10

C12

U3

R573 *S HORT_4

SATA_RCOMP

R574 3.01 K/F_4

SATA_LED#

R636 10K _4

SATA_RCOMP

Impedance = 50 ohm

Trace length < 500 mils

Trace spacing = 15 mils

PCH Quad SPI ROM

(Default for WIN8)

3.3K is original and for no

support fast read function

PCH_SPI_CS1#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

C565 *22p/50V_4

SATA_RXN0 27

SATA_RXP0 27

SATA_TXN0 27

SATA_TXP0 27

SATA_RXN1_SSD 26

SATA_RXP1_SSD 2 6

SATA_TXN1_SSD 26

SATA_TXP1_SSD 26

SYS_COM_REQ 23

VGPU_EN 2 0,40

TP33

TP88

+V1.05S_ASATA3PLL

+V1.05S_ASATA3PLL

+3V

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

+3V_PCH_ME

R529 33_4

R521 33_4

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

+3V_PCH_ME

PCH_SPI_CLK_EC33

PCH_SPI_SI_EC33

PCH_SPI_SO_EC33

SPI_CS0#_UR_ME33

+3V_PCH_ME

HDD

mSATA

R145 33_4

R153 33_4

R103 33_4

R106 *1 K_4

R94 *1K _4

PCH_SPI_IO2

PCH_SPI_IO3

R109 10K_4

2

Haswell ULT PCH(LPC,SPI,SMBUS,C-LINK,THERMAL)

LPC_LAD026,27,33

LPC_LAD126,27,33

LPC_LAD226,27,33

LPC_LAD326,27,33

LPC_LFRAME#26,27,33

PCH_SPI_CLK

PCH_SPI_CS1#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

SYS_COM_REQ

VGPU_EN

GPIO36

GPIO37

W25Q32BVSSIG / AKE391P0N00----->4MB

MX25L3206EM2I / AKE39FP0Z02----->4MB

MX25L1606EM2I / AKE38FP0Z01----->2MB

W25Q16BVSSIG / AKE38FP0N01----->2MB

R540 *S HORT_6

C162

*22p/50V_4

R91 33_4

R95 33_4

R146 33_4

R533 33_4

R525 33_4

R520 33_4

R98 33_4

R112 *0_4

R104 0_4

U14

1

CE#

6

SCK

5

SI

2

SO

3

WP#

ROM-2M_ME

SPI_WP_IO2_ME

U34

1

CE#

6

SCK

5

SI

2

SO

3

WP#

ROM-4M_EC

SPI_WP_IO2_EC

SPI_CS0#_UR_ME

+3V_PCH_ME+3V_S5

8

VDD

7

SPI_HOLD_IO3_ME

HOLD#

4

VSS

8

VDD

7

SPI_HOLD_IO3_EC

HOLD#

4

VSS

SPI_WP_IO2_ME

SPI_WP_IO2_EC

SPI_HOLD_IO3_ME

SPI_HOLD_IO3_EC

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_CS0#

PCH_SPI_CS1#

2

R147 *1 K_4

C147

0.1u/10V_4

R534 *1 K_4

C95

0.1u/10V_4

HSW_ULT_DDR3L

LPC

+3V

+3V_PCH_ME

+3V_PCH_ME

+3V_S5

SMBALERT/GPIO11

+3V_S5

+3V_S5

SMBUS

+3V_S5

SML0ALERT/GPIO60

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

C-LINKSPI

SMBus

SML0DATA

SML1ALERT/PCHHOT/GPIO73

SML1CLK/GPIO75

SML1DATA/GPIO74

7 OF 19

+3V_S5

SMBus(PCH)

SMB_PCH_DAT26

SMB_PCH_CLK26

PCH_XDP_WLAN/S5 DDR_TP/S0

SMBus(EC)

2ND_MBCLK19,33

2ND_MBDATA19,33

U42G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

R182 *10K_4

R629 IV@10K_4 R689 10K_4

R168 10K_4

R655 10K_4

reserve for SPI fast read

EC/S5 PCH/S5

1

08

AN2

SMBALERT#

AP2

SMB_PCH_CLK

SMBCLK

AH1

SMB_PCH_DAT

SMBDATA

AL2

SMB0ALERT#

AN1

SMB_ME0_CLK

SML0CLK

AK1

SMB_ME0_DAT

AU4

SMB1ALERT#

AU3

SMB_ME1_CLK

AH3

SMB_ME1_DAT

AF2

CL_CLKPCH_SPI_CS0#

CL_CLK

AD2

CL_DAT

CL_DATA

AF4

CL_RST#

CL_RST

R680 10K_4

R697 10K_4

R285 2.2K_4

R284 2.2K_4

R663 2.2K_4

R661 2.2K_4

+3V_S5

2ND_MBCLK

2ND_MBDATA

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

SMB0ALERT#

SMB1ALERT#

SMBALERT#

SMB_PCH_CLK

SMB_PCH_DAT

SMB_ME0_CLK

SMB_ME0_DAT

+3V

R289

4.7K_4

Q33

5

2

6

2N7002DW

*2.2K_4

Q32

5

2

6

*2N7002DW

R280 0_4

R282 0_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LPT 2/6 (SATA/HDA/SPI)

LPT 2/6 (SATA/HDA/SPI)

LPT 2/6 (SATA/HDA/SPI)

Friday, April 12, 2013

Friday, April 12, 2013

Friday, April 12, 2013

1

43

1

R290

43

1

SMB_ME1_CLK

SMB_ME1_DAT

SMBALERT# 32

TP87

TP86

TP89

R279

4.7K_4

CLK_SDATA 13, 14,15,23,32

CLK_SCLK 13,14,15,23,32

R278

*2.2K_4

SMB_ME1_CLK

SMB_ME1_DAT

ZRQ

ZRQ

ZRQ

8 47

8 47

8 47

3A

3A

3A

Page 9

5

Haswell ULT PCH (PCIE,USB3.0,USB2.0)

U42K

PEG_RX#016

D D

PEG x4

C C

LAN WLAN

B B

PEG_RX01 6

PEG_TX#016

PEG_TX016

PEG_RX#116

PEG_RX11 6

PEG_TX#116

PEG_TX116

PEG_RX#216

PEG_RX21 6

PEG_TX#216

PEG_TX216

PEG_RX#316

PEG_RX31 6

PEG_TX#316

PEG_TX316

PCIE_RX3-_WLAN26

PCIE_RX3+_WLAN26

PCIE_TX3-_WLAN26

PCIE_TX3+_WLAN26

PCIE_RX4-_LAN28

PCIE_RX4+_LAN28

PCIE_TX4-_LAN28

PCIE_TX4+_LAN28

+V1.05S_ AUSB3PLL

C592 EV@0 .22u/10V_ 4

C593 EV@0 .22u/10V_ 4

C572 EV@0 .22u/10V_ 4

C573 EV@0 .22u/10V_ 4

C597 EV@0 .22u/10V_ 4

C598 EV@0 .22u/10V_ 4

C574 EV@0 .22u/10V_ 4

C575 EV@0 .22u/10V_ 4

C587 0.1u /10V_4

C586 0.1u /10V_4

C589 0.1u /10V_4

C588 0.1u /10V_4

TP22

TP21

TP11

TP9

R571 3.01 K/F_4

R570 *SHORT_4

PCIE_RCOMP

PCIE_IREF

F10

PERN5_L0

E10

PERP5_L0

C23

R_PEG_TX# 0

R_PEG_TX0

R_PEG_TX# 1

R_PEG_TX1

R_PEG_TX# 2

R_PEG_TX2

R_PEG_TX# 3

R_PEG_TX3

PCIE_TX3PCIE_TX3+

PCIE_TX4PCIE_TX4+

PCIE_RXN1

PCIE_RXP1

PCIE_TXN1

PCIE_TXP1 USBCOMP

C22

F8

E8

B23

A23

H10

G10

B21

C21

E6

F6

B22

A21

G11

F11

C29

B30

F13

G13

B29

A29

G17

F17

C30

C31

F15

G15

B31

A31

E15

E13

A27

B27

PETN5_L0

PETP5_L0

PERN5_L1

PERP5_L1

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

PERN1/USB3RN3

PERP1/USB3RP3

PETN1/USB3TN3

PETP1/USB3TP3

PERN2/USB3RN4

PERP2/USB3RP4

PETN2/USB3TN4

PETP2/USB3TP4

RSVD

RSVD

PCIE_RCOMP

PCIE_IREF

PCIE USB

+3V_S5

+3V_S5

+3V_S5

+3V_S5

HSW_ULT_DDR3L

4

11 OF 19

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

DSW

USB2N0

DSW

USB2P0

DSW

USB2N1

DSW

USB2P1

DSW

USB2N2

DSW

USB2P2

DSW

USB2N3

DSW

USB2P3

DSW

USB2N4

DSW

USB2P4

DSW

USB2N5

DSW

USB2P5

DSW

USB2N6

DSW

USB2P6

DSW

USB2N7

DSW

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

RSVD

RSVD

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USBP7+

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USBP0- 2 3

USBP0+ 2 3

USBP1- 3 1

USBP1+ 3 1

USBP2- 2 4

USBP2+ 2 4

USBP3- 2 6

USBP3+ 2 6

USBP4- 3 1

USBP4+ 3 1

USBP5- 2 4

USBP5+ 2 4

USBP6- 3 1

USBP6+ 3 1

TP63

TP62

USB3_RXN0 31

USB3_RXP 0 31

USB3_TXN0 31

USB3_TXP0 31

USB3_RXN1 23

USB3_RXP 1 23

USB3_TXN1 23

USB3_TXP1 23

R245 22.6 /F_4

USB_OC0# 31

USB_OC2# 31

USB_OC3# 31

mDP Dongle

MB USB2.0

CCD

BT

MB USB3.0

Touch screen

DB USB2.0

CR

MB USB3.0

mDP Dongle

USBCOMP

Impedance = 50 ohm

Trace length < 500 mils

Trace spacing = 15 mils

MB U3

MB U2

DB U2

3

Haswell ULT PCH (CLOCK)

CLK_PCIE_N0

TP75

CLK_PCIE_P0

TP73

CLK_PCIE_REQ0#

TP84

CLK_PCIE_REQ1#

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

TP106

R639 *SHORT_4

R638 *SHORT_4

R651 *SHORT_4

+3V_S5

RP6

10

9

8

7 4

10K_10P 8R

CLK_PCIE_REQ2#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

CLK_PCIE_REQ5#

1

2

3

56

CLK_PCIE_WLANN26

CLK_PCIE_WLANP26

PCIE_CLKREQ_WLAN#26

CLK_PCIE_LANN28

LAN WLANVGA

CLK_PCIE_LANP28

CLK_PCIE_LAN_REQ#28

CLK_PCIE_VGA#16

CLK_PCIE_VGA16

CLK_PEGA_REQ#16

USB Overcurrent

U42F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

2

HSW_ULT_DDR3L

+3V

+3V

+3V

+3V

+3V

+3V

CLK_PCIE_REQ0#

CLK_PCIE_REQ1#

CLK_PCIE_REQ2#

CLK_PCIE_REQ3#

CLK_PCIE_REQ5#

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLK_PCIE_REQ4#

CLOCK

SIGNALS

6 OF 19

R637 10K_ 4

R645 10K_ 4

R654 10K_ 4

R612 10K_ 4

R634 10K_ 4

R563 10K_ 4

R564 10K_ 4

R258 10K_ 4

R271 10K_ 4

R608 10K_4

R619 *1K_4

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

+3V

+3V

XTAL24_IN

XTAL24_OUT

A25

B25

K21

M21

C26

C35

C34

AK8

AL8

AN15

AP15

B35

A35

R558

1M_4

XTAL24_IN

XTAL24_OUT

ICLK_BIAS

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLK_PCH_PCI3USBP7CLK_PCH_PCI4

C266

*18p/50V _4

1

C590 12 p/50V_4

Y6

24MHz

2 4

1 3

C591 12 p/50V_4

R557 3.01 K/F_4

*18p/50V _4

R257TPM@22_4

R25622_4

R25522_4

C267

09

+V1.05S_ AXCK_LCPLL

PCLK_TPM 2 7

CLK_PCI_LPC 26

CLK_PCI_EC 33

CLK_PCIE_XDPN 13

CLK_PCIE_XDPP 13

PCLK_TPMCLK_PCI_LPCCLK_PCI_EC

C268

*18p/50V _4

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

5

4

3

2

Friday, April 12, 2013

PROJECT :

LPT 3/6 (PCIE/USB/CLK)

LPT 3/6 (PCIE/USB/CLK)

LPT 3/6 (PCIE/USB/CLK)

ZRQ

ZRQ

ZRQ

9 47

9 47

1

9 47

3A

3A

3A

Page 10

5

4

3

Haswell ULT PCH (GPIO,CPU/MISC,NCTF)

High Low

GPIO8

D D

C C

DEVSLP0 for HDD

DEVSLP1 for mSATA

No touch panel Touch panel

GPIO824

GPIO158

DGPU_PWROK20

DGPU_HOLD_RST#16

DGPU_PWR_EN41

MODPHY_EN11

DEVSLP027

DEVSLP126

TP40

TP48

TP53

TP93

TP59

TP61

TP56

TP38

TP91

TP45

TP52

SPKR8,30

BOARD_ID0

GPIO8

LAN_DISABLE#

GPIO15

SKU_ID0

DGPU_PWROK

GPIO24

WK_GPIO27

GPIO28

ODD_PRSNT#

GPIO56

GPIO57

GPIO58

GPIO59

GPIO44

GPIO47

DGPU_HOLD_RST#

DGPU_PWR_EN

DGPU_PW_CTRL#

MODPHY_EN

RAM_ID0

RAM_ID3

GPIO25

GPIO45

GPIO46

RAM_ID1

RAM_ID2

DEVSLP0

BOARD_ID3

DEVSLP1

SKU_ID1

SPKR

Board ID

+3V

R624 10K_4

BOARD_ID12

R606 10K_4

B B

BOARD_ID22,32

R603 *10K_4

R124 10K_4

BOARD_ID42

R600 10K_4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

Low

BOARD_ID0

BOARD_ID1

A A

BOARD_ID2

BOARD_ID3

BOARD_ID4

Enable on

board memory

Pin8 of SYNAPTICS and ELAN are NC

pin. BIOS maybe will use EEPROM

detection. Default is pull high.

Reserved

(Default)

Reserved

(Default)

5

R626 *10K_4

R607 *10K_4

R602 10K_4

R121 *10K_4

R599 *10K_4

High

GDDR5DDR3

Disable on

board memory

Reserved

Reserved

U42J

P1

BMBUSY/GPIO76

AU2

AM7

AD6

AD5

AN5

AD7

AN3

AG6

AP1

AL4

AT5

AK4

AB6

AT3

AH4

AM4

AG5

AG3

AM3

AM2

Y1

T3

U4

Y3

P3

Y2

P2

C4

L2

N5

V2

+3V_S5

GPIO8

LAN_PHY_PWR_CTRL/GPIO12

+3V_S5

GPIO15

+3V

GPIO16

+3V

GPIO17

+3V_S5

GPIO24

DSW

GPIO27

+3V_S5

GPIO28

+3V_S5

GPIO26

+3V_S5

GPIO56

+3V_S5

GPIO57

+3V_S5

GPIO58

+3V_S5

GPIO59

+3V_S5

GPIO44

+3V_S5

GPIO47

+3V

GPIO48

+3V

GPIO49

+3V

GPIO50

HSIOPC/GPIO71

+3V_S5

GPIO13

+3V_S5

GPIO14

DSW

GPIO25

+3V_S5

GPIO45

+3V_S5

GPIO46

+3V_S5

GPIO9

+3V_S5

GPIO10

DEVSLP0/GPIO33

SDIO_POWER_EN/GPIO70

DEVSLP1/GPIO38

DEVSLP2/GPIO39

SPKR/GPIO81

RAM ID

R693 10K_4

R247 *10K_4

R682 10K_4

R688 10K_4

RAM_IDVender Freq.

Hynix

Elpida

0000

0001

Elpida 0010 AKD5JGST404 EDJ4216EFBG-GN-F 1600MHz

SKU ID

R647 IV@10K_4

R139 IV@10K_4

SKU_ID1 SKU_ID0 VGA H/W

UMA Only

dGPU Only

Switchable

(Mux)

Optimize

(Muxless)

0

0

1

1

HSW_ULT_DDR3L

+3V

+3V

+3V

+3V

+3V

+3V

Q PN

GPIO

+3V

RAM_ID0

RAM_ID1

RAM_ID2

RAM_ID3

DSW

10 OF 19

R692 *10K_4

R263 10K_4

R681 *10K_4

R687 *10K_4

Mfr. PN

CPU/

MISC

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

SERIAL IO

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

THRMTRIP

+3V

RCIN/GPIO82

PCH_OPI_RCOMP

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

+3V_S5

AKD5JGETW04 H5TC4G63AFR-PRBA 1600MHz

AKD5JGST400

SKU_ID0

SKU_ID1

0

1

0

1

4

EDJ4216EBBG-DJ-F

R646 EV@10K_4

R143 EV@10K_4

Setup

Signal

Menu

UMA

Hidden

GPU

Hidden

UMA+GPU dGPU/SG UMA boot

UMA

UMA/SG

1333MHz

+3V

UMA boot

GPU boot

UMA boot

D60

THRMTRIP#

V4

SIO_RCIN#

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

IRQ_SERIRQ

OPI_COMP2

SERIRQ

RSVD

RSVD

CPU thermal trip

THRMTRIP#

IMVP_PWRGD5,38

IRQ_SERIRQ

DEVSLP0

DEVSLP1

SIO_RCIN# 33

R132

1K_4

Q18

FDV301N

IRQ_SERIRQ 27,33

GPIO86 8

SIO_EXT_SMI# 33

SIO_EXT_SCI# 33

GPIO66 8

SYS_SHDN# 27,35,39

+1.05V_VCCST

5

12

C767

0.1u/10V_4

4

+3V

R807

10K_4

R648 *100K_4

high UMA Only

low

R628 EV@100K_4

R162 *10K_4

IMVP_PWRGD_3V 7

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

R709 49.9/F_4

GPIO83

GPIO84

GPIO85

GPIO86

GPIO87

GPIO88

GPIO89

GPIO90

GPIO91

GPIO92

GPIO93

GPIO94

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

SIO_EXT_SMI#

SIO_EXT_SCI#

GPIO64

GPIO65

GPIO66

GPIO67

GPIO68

GPIO69

+1.05V_VCCST

3

IMVP_PWRGD_3V

+1.05V_VCCST

3 2 1

2

1

R133

2

1K_4

1 3

Q19 MMBT3904-7-F

U55

NC1VCC

2

A

GND3Y

74AUP1G07GW

SIO_RCIN#

SIO_EXT_SMI#

SIO_EXT_SCI#

GPIO83

GPIO84

GPIO85

GPIO87

GPIO88

GPIO89

GPIO90

GPIO91

GPIO92

GPIO93

GPIO94

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO64

GPIO65

GPIO67

GPIO68

GPIO69

DGPU_PWR_EN

DGPU_HOLD_RST#

GPU power is control by PCH

GPIO (Discrete, SG or Optimize)

DGPU_PW_CTRL#

DGPU_PWROK

LAN_DISABLE#

ODD_PRSNT#

GPIO8

WK_GPIO27

GPIO27 : If not used then use

8.2-kΩ to 10-kΩ pull-down to GND.

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LPT 4/6 (GPIO/MISC)

LPT 4/6 (GPIO/MISC)

LPT 4/6 (GPIO/MISC)

R159 10K_4

R169 *10K_4

R611 *10K_4

R187 10K_4

R135 10K_4

R131 10K_4

R206 10K_4

R150 10K_4

R207 10K_4

R152 10K_4

R208 10K_4

R205 10K_4

R597 10K_4

R594 10K_4

R209 10K_4

R590 10K_4

R588 10K_4

R210 10K_4

R589 10K_4

R595 10K_4

R592 10K_4

R585 10K_4

R586 10K_4

R584 10K_4

R134 10K_4

R130 10K_4

R128 10K_4

R581 10K_4

R649 10K_4

R643 10K_4

R627 IV@1K_4

R260 10K_4

R679 10K_4

R250 *10K_4

R727 10K_4

R728 *10K_4

ZRQ

ZRQ

ZRQ

10

+3V

+3V

+3V_S5

+3VPCU

10 47

10 47

10 47

3A

3A

3A

Page 11

5

4

3

2

1

Haswell ULT PCH (Power)

C577 *1u/6.3V_4

C163 1u/6.3V_4

C175 1u/6.3V_4

+1.05V

25mA

C235

1u/6.3V_4

R179 *SHORT_8

Deep Sx

+3VPCU

+3V_S5

D D

R292 *0_6

+1.05V_S5

Non Deep Sx

+3V

C C

+1.05V

WW15 4/10 Intel VCCDSW3

G3 can't boot issue.

C245

+PCH_VCCDSW+VCCPDSW

0.47u/25V_6

+V1.05DX_MODPHY

R294 *0_6

+1.05V_S5

+1.05V_DCPSUS2

R254*SHORT_6

R253 *0_6

1u/6.3V_4

C164 1u/6.3V_4

+3VCC_S5

1.741A

C181

*1u/6.3V_4

C177

10u/6.3V_6

C238

R165*SHORT_8

+V1.05S_AIDLE

10mA

C166

1u/6.3V_4

+V3.3DX_1.5DX_1.8DX_AUDIO

0.114A

41mA

C174

22u/6.3V_8

+1.05V

63mA

+V1.05S_AUSB3PLL

+V1.05S_ASATA3PLL

+3VCC_S5

+V1.05S_AXCK_DCB

+V1.05S_AXCK_LCPLL

C209 1u/6.3V_4

1.838A

+V1.05S_APLLOPI

+1.05V_DCPSUS3

C270 22u/6.3V_8

+VCCPDSW

+V3.3S_VCCPCORE

B18

B11

Y20

AA21

W21

AH14

AH13

AC9

AA9

AH10

K19

A20

R21

T21

K18

M20

V21

AE20

AE21

K9

L10

M9

N8

P9

J13

V8

W9

J18

J17

U42M

VCCHSIO

VCCHSIO

VCCHSIO

VCC1_05

VCC1_05

VCCUSB3PLL

VCCSATA3PLL

RSVD

VCCAPLL

VCCAPLL

DCPSUS3

VCCHDA

DCPSUS2

VCCSUS3_3

VCCSUS3_3

VCCDSW3_3

VCC3_3

VCC3_3

VCCCLK

VCCCLK

VCCACLKPLL

VCCCLK

VCCCLK

VCCCLK

RSVD

RSVD

RSVD

VCCSUS3_3

VCCSUS3_3

PCH VCCHSIO Power

+1.05V_S5

+3V_S5

R604

100K_4

+3V

R188

*100K_4

R185

*100K_4

+5V_S5

B B

MODPHY_EN10

C607

0.1u/10V_4

12

C601

1u/6.3V_4

R596

*SHORT_4

1 2

12

12

C608

0.047u/25V_4

U40

TPS22965DSGR

1

VIN_01

VIN_022VOUT_01

3

ON

4

VBIAS

VOUT_02

PAD

9

GND

+V1.05DX_MODPHY

8

7

6

CT

5

12

C604

330p/50V_4

R560 *SHORT_8

R559 *SHORT_8

12

C602

0.1u/10V_4

HSIO

USB3

HDA

VRM

GPIO/LPC

LPT LP POWER

HSW_ULT_DDR3L

OPI

13 OF 19

VCCAPLL power

RTC

SPI

CORE

THERMAL SENSOR

SERIAL IO

SUS OSCILLATOR

USB2

VCCSUS3_3

DCPSUSBYP

DCPSUSBYP

L21 2.2uH/210mA_8

*47u/6.3V_8

VCCRTC

DCPRTC

VCCSPI

VCCASW

VCCASW

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCCASW

VCCASW

VCCASW

DCPSUS1

DCPSUS1

VCCTS1_5

VCC3_3

VCC3_3

VCCSDIO

VCCSDIO

DCPSUS4

RSVD

VCC1_05

VCC1_05

C248

AH11

AG10

AE7

Y8

AG14

AG13

J11

H11

H15

AE8

AF22

AG19

AG20

AE9

AF9

AG8

AD10

AD8

J15

K14

K16

U8

T9

AB8

AC20

AG16

AG17

+VCCRTCEXT

+V3.3M_PSPI

PCH_VCC_1_1_21

+V1.05S_CORE_PCH

+1.05V_DCPSUS1

+V1.05S_APLLOPI+1.05V

57mA

C619

*47u/6.3V_8

18mA

+PCH_VCCDSW

+V1.05M_VCCASW

0.109A

R293 *0_6

C212

1u/6.3V_4

+V3.3S_VCCSDIO

+1.05V_DCPSUS4

+V1.05S_VCCUSBCORE

C218

1u/6.3V_4

R194 *SHORT_6

+V1.05M_VCCASW

+1.05V_S5

3mA

1mA

17mA

R291 *0_6

C197

1u/6.3V_4

1u/6.3V_4

+3V_RTC

C231

C643

0.1u/10V_4

C208

0.1u/10V_4

+1.05V

+1.05V

C237

C213

1u/6.3V_4

1u/6.3V_4

0.658A

R217 *SHORT_8

C221

C217

1u/6.3V_4

22u/6.3V_8

+V1.5S_VCCATS

+V3.3S_VCCPTS

+1.05V_S5

R270 *SHORT_8

C236

1u/6.3V_4

+1.05V +V1.05S_AXCK_DCB

L33 2.2uH/210mA_8

C642

0.1u/10V_4

1u/6.3V_4

R220 *SHORT_6

R204 *0_6

C216

0.1u/10V_4

C192

10u/6.3V_6

C233

1u/6.3V_4

R111 *SHORT_6

R107 *SHORT_6

C183

1u/6.3V_4

C194

1u/6.3V_4

+1.05V

C579

47u/6.3V_8

+3V_S5

+3V

R174 *SHORT_8

+1.05V

+1.5V

+3V

R158 *SHORT_6

0.2A

C578

47u/6.3V_8

+1.05V

+3V

C158

1u/6.3V_4

11

+1.05V +V1.05S_AXCK_LCPLL

+V1.05DX_MODPHY +V1.05S_AUSB3PLL +V1.05DX_MODPHY +V1.05S_ASATA3PLL

A A

L18 2.2uH/210mA_8

C88

47u/6.3V_8

C77

47u/6.3V_8

C595

1u/6.3V_4

L17 2.2uH/210mA_8

C89

47u/6.3V_8

42mA41mA

C79

47u/6.3V_8

C596

1u/6.3V_4

PCH HDA Power

+3V_S5

R252 *SHORT_6

11mA

+V3.3DX_1.5DX_1.8DX_AUDIO

C234

0.1u/10V_4

Place close to ball

5

4

3

2

L14 2.2uH/210mA_8

C68

47u/6.3V_8

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

Date: Sheet of

Friday, April 12, 2013

31mA

C76

47u/6.3V_8

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LPT 5/6 (POWER)

LPT 5/6 (POWER)

LPT 5/6 (POWER)

C594

1u/6.3V_4

1

ZRQ

ZRQ

ZRQ

11 47

11 47

11 47

3A

3A

3A

Page 12

5

4

3

2

1

Haswell ULT (GND)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U42O

HSW_ULT_DDR3L

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D50

D51

D53

D54

D55

D57

D59

D62

G18

G22

H13

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

HSW_ULT_DDR3L

U42P

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

VSS

16 OF 19

VSS_SENSE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

VSS_SENSE_R

U42R

AT2

RSVD

AU44

RSVD

AV44

RSVD

D15

RSVD

F22

RSVD

H22

RSVD

J21

RSVD

R591 *SHORT_4

R593 100/F_4

HSW_ULT_DDR3L

D D

C C

B B

A11

A14

A18

A24

A28

A32

A36

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U42N

14 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43