Page 1

1

2

3

4

5

6

7

8

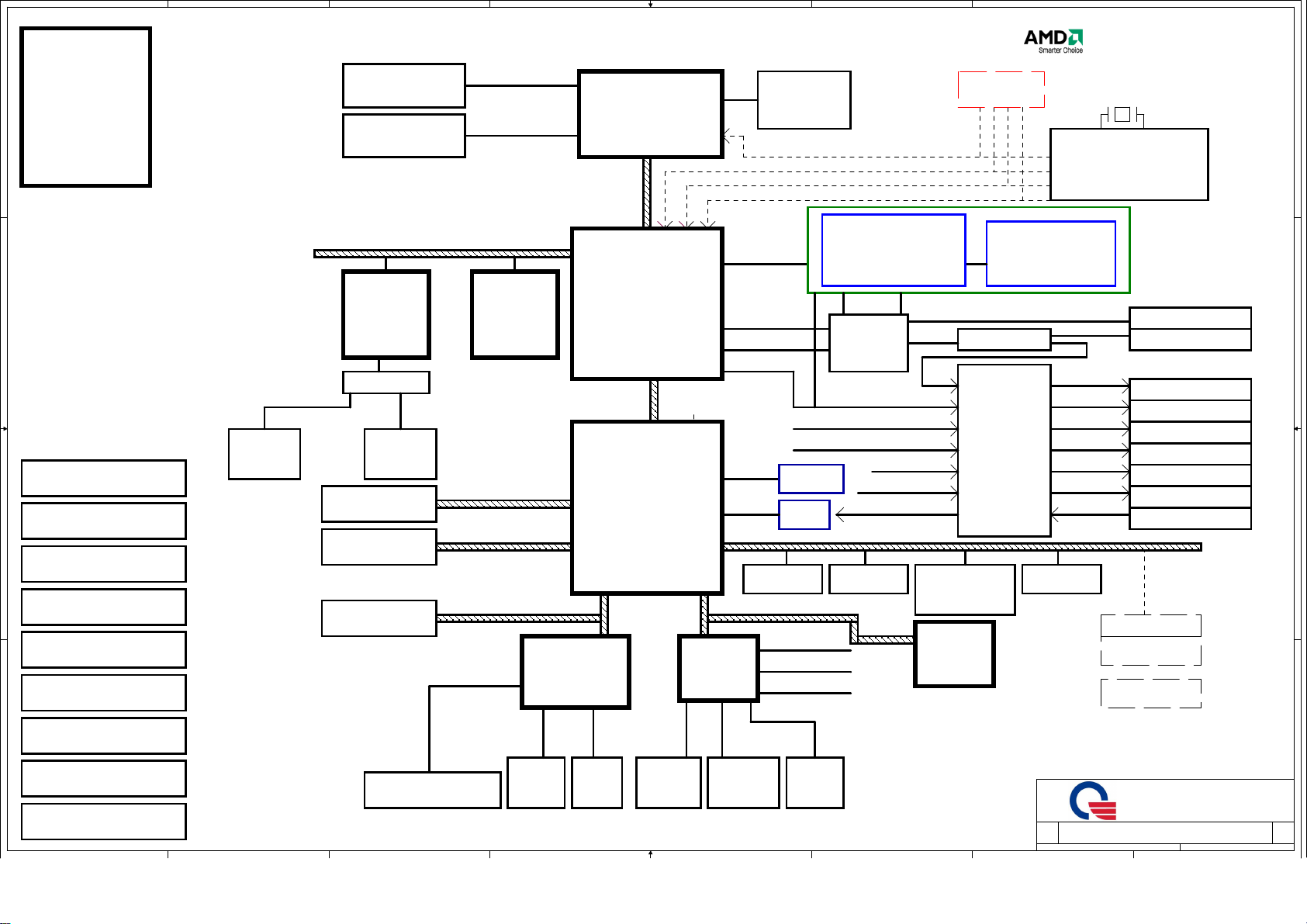

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

A A

LAYER 4 : IN2

LAYER 5 : VCC

LAYER 6 : IN3

LAYER 7 : GND

LAYER 8 : BOT

B B

Lan_PCIE1 Lan_PCIE2

Docking

AMD CPU CORE (ISL6265)

PAGE 39

NB_CORE (UP6111AQDD)

C C

+VGPU_CORE (MAX8792ETD)

PAGE 41

PAGE 43

1.1V (UP6111AQDD)

PAGE 40

1.8V/GPU_Power/+2.5V

PAGE 44

DDR 1.5V(RT8207)

PAGE 42

DDR3-SODIMM1

DDR3-SODIMM2

X1

LAN

BCM 57760

PCIE-LAN

(10/100/1000)

PAGE 27

1 to 2 Switch

SATA - HDD1

SATA - CD-ROM

TPM

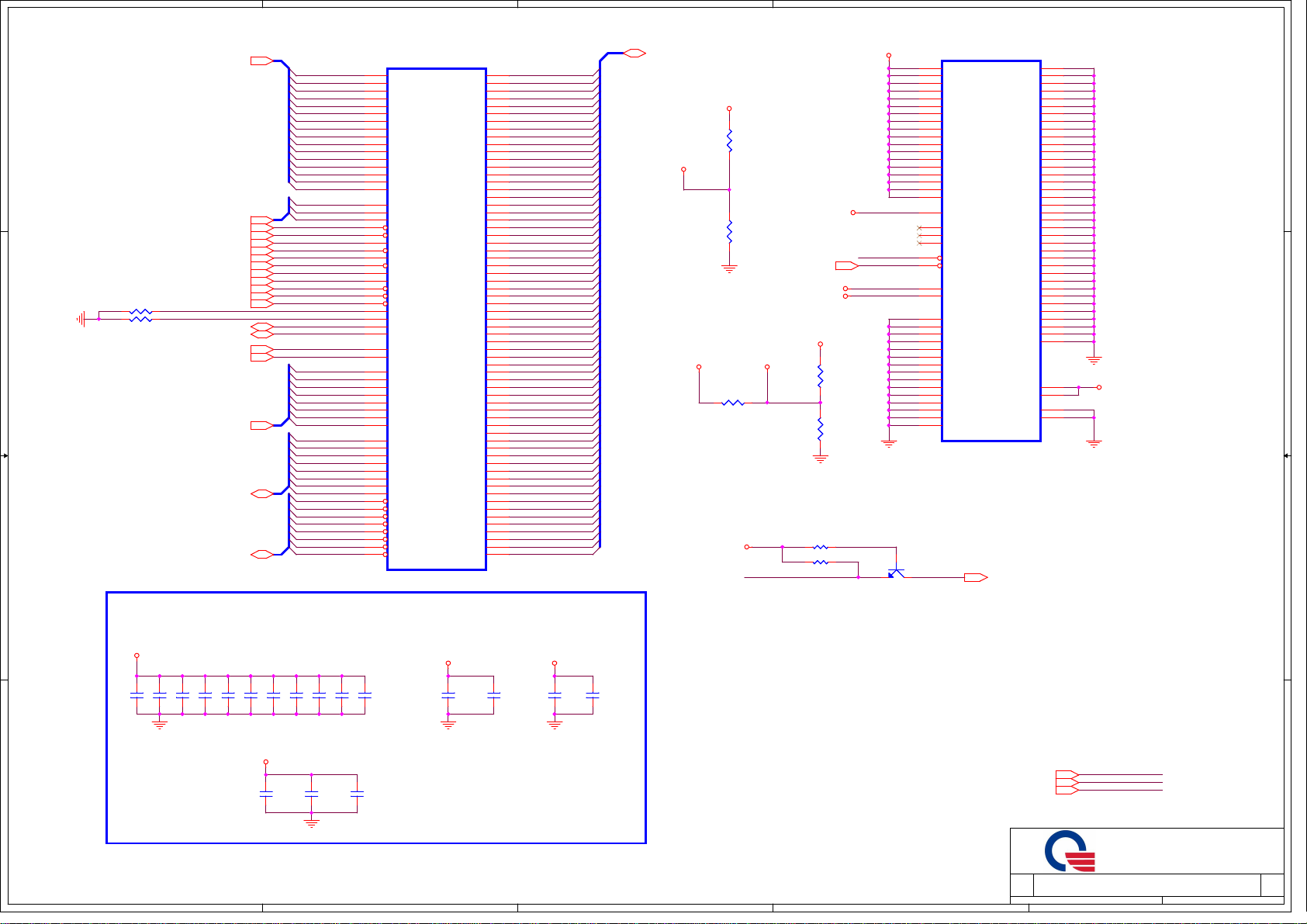

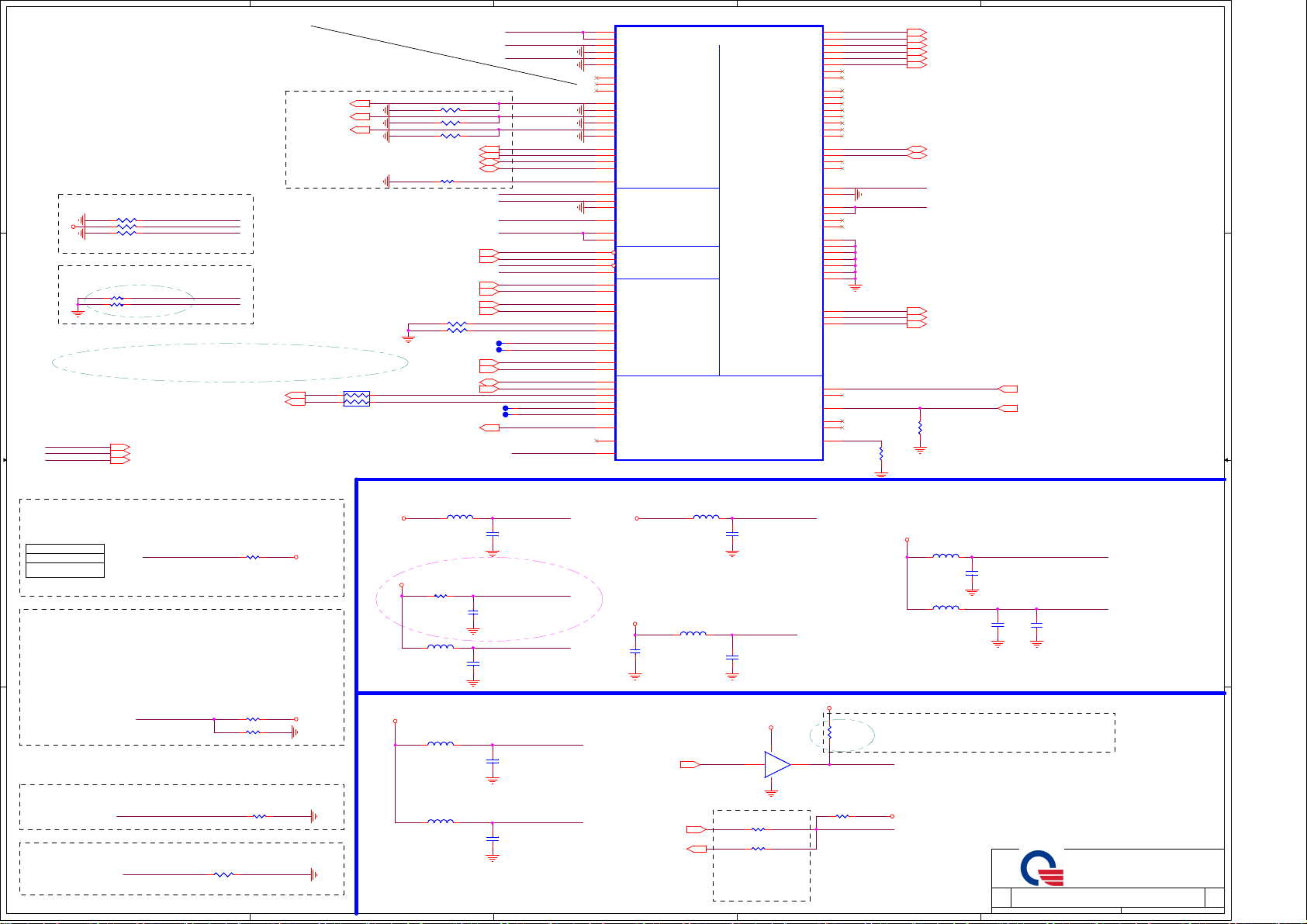

ZRA SYSTEM DIAGRAM

DDR3 channel A

PAGE 7

DDR3 channel B

PAGE 8

AMD Champlain

35mm X 35mm

S1G4 Processor

638P (PGA)45W/35W

PAGE 4,5,6

HT3

PCI-E

Port 0 Port 2

X1

Mini PCI-E

Card

(Wireless LAN)

NORTH BRIDGE

RS880

A12

21mm X 21mm, 528pin BGA

PAGE 28

PAGE 9,10,11,12

ALINK X4

RJ45

PAGE 27

SATA0 150MB

PAGE 29

SATA1 150MB

SOUTH BRIDGE

SB820

21mm X 21mm, 528pin BGA

4.5W(Ext)

4.3W(Int)

PAGE 29 PAGE 13,14,15,16,17

LPC

PAGE 28

Azalia

Winbond KBC

NPCE781L

PAGE 35

Codec

CX20672-11Z

PAGE 30

CPU THERMAL

SENSOR

PCI-Express 16X

LVDS

CRT

DVI

USB2.0

USB2.0

USB2.0

USB2.0 Ports

X1

MIC to Docking

Line out to Docking

Line in from Docking

PAGE 6

CPU_CLK

NBGFX_CLK

NBGPP_CLK

SBLINK_CLK

DVI

USB2.0 x 1

Lan_PCIE1

Finger print

PAGE 32

BT

PAGE 32

PAGE 32

ATI

Madison LP

128-bit M2 Pkg

29mm X 29mm

PAGE 18,19,20,21,22,23

LVDS CRT

MUXs

CRT

(S.G)

MIC to Docking

Line out to Docking

Line in from Docking

Webcam

PAGE 26

PAGE 30

From SB

Option

1 to 2 Switch

Docking

PAGE 36

CardReader

AU6437

PAGE 31

MDC

14.318MHz

CLOCK GEN

ICS9LPRS476AKLFT-->HP

SLG8SP628VTR-->HP

RTM880N-796 -->HP

800MHz

VRAM

DDR3

64MX16X8,128bit

128MX16X8,128 bit

PAGE 24,25

LVDS

CRT

WLAN conn

PAGE 28

PAGE 3

VGA

On board LVDS

On board CRT

CRT connector

DVI connector

USB connector x 3

RJ45 connector

MIC

Line out

Line in

USB BOARD

USB2.0 Ports x3

PAGE 32

Power BOARD

PAGE 33

/ParkMadison

SYSTEM 5V/3V (RT8206)

D D

1V/CPU_VDDR/Discharage

Charger (ISL88731)

1

PAGE 38

PAGE 45

PAGE 37

Keyboard

Touch Pad

2

PAGE 34

PAGE 32 PAGE 34

3

CPU FAN

SPI

PAGE 35

4

Digital MIC AUDIO CONN

(Phone/ MIC)

PAGE 30 PAGE 30

5

Speaker

PAGE 30

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

6

Date: Sheet of

7

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZRA

ZRA

ZRA

1A

1A

1 48Monday, March 29, 2010

1 48Monday, March 29, 2010

1 48Monday, March 29, 2010

8

1A

Page 2

5

4

3

2

1

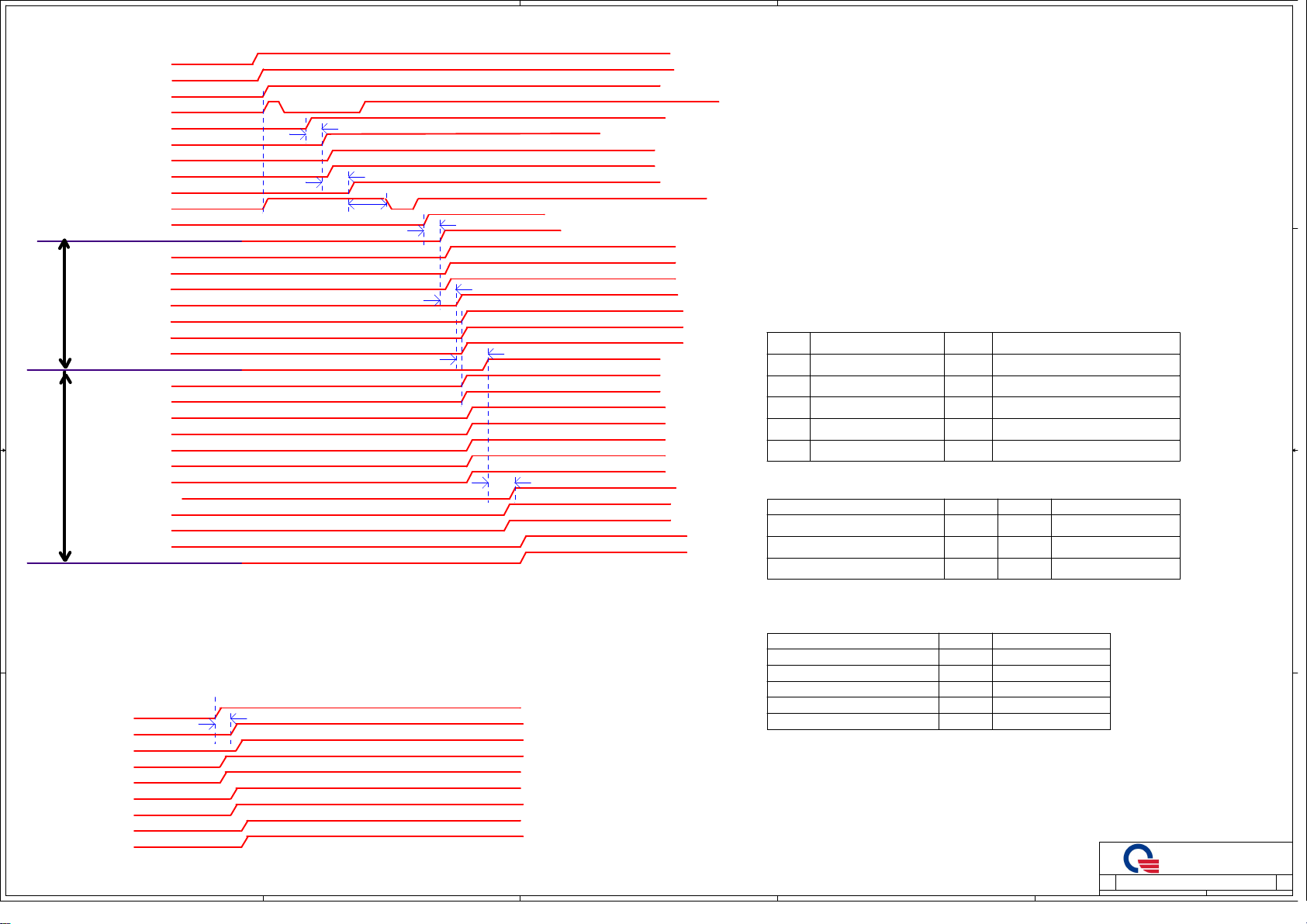

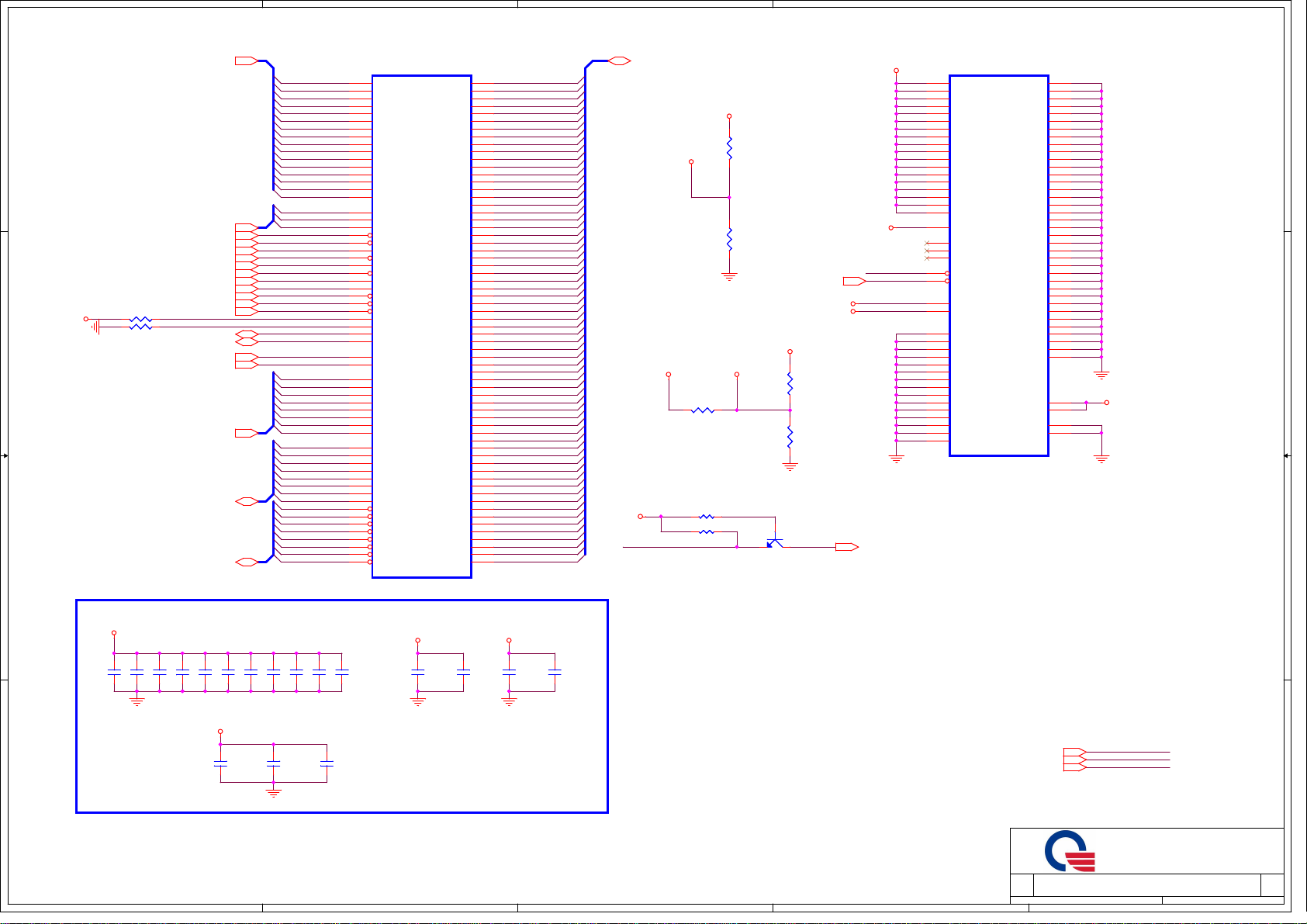

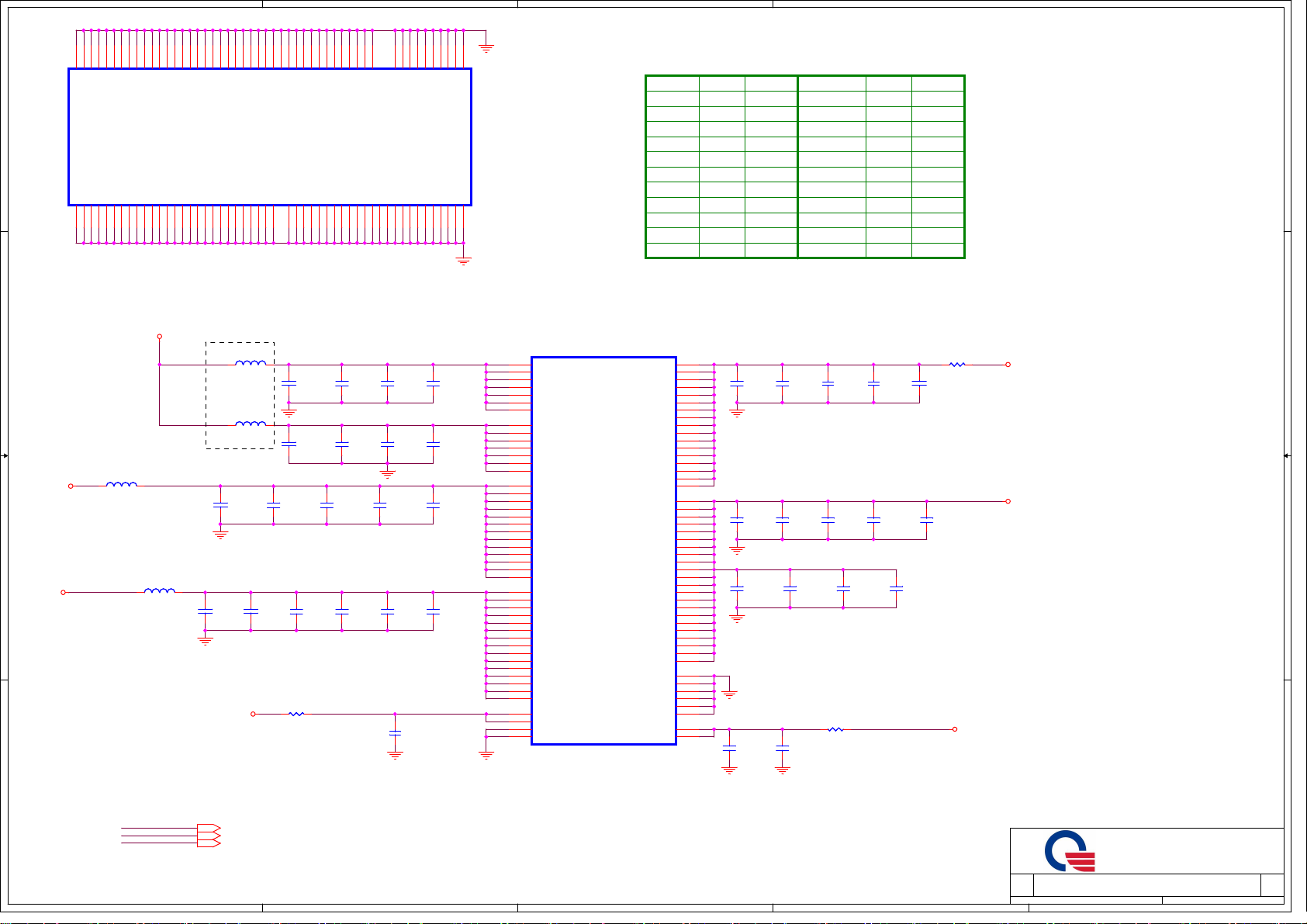

Danube Power On Sequence

From VBAT

From AC,BATT

D D

From EC

UP6111A

From EC SUSON

From EC MAINON

C C

GROUP A

Actv' by +3V

GROUP B

B B

Notice:

1.CPU_LDT_RST# msut be asserted a minimum of 1ms prior to the assertion of CPU_PWRGD

2.CPU_CLKP/N must be within specification a minimum of 1ms prior to the assertion of CPU_PWRGD

3.CPU_PWRGD remains deasserted at least 1ms after both CPU_CLKP/N and all voltages to the processor are within

specification for operation

4.all NB power rails(1.8V/1.2V/1.1V) valid before NB_PWRGD at least 1ms

5.stable input clocks from CLKGEN(HT_REFCLKP/N) to NB before NB_PWRGD at least 1ms

VCCRTC

VIN_SRC

+5VPCU,+3VPCU

NBSWON#From Button

VIN

S5_ON

+5V_S5,+3V_S5,+1.1V_S5

HWPG_1.1VUP6111A

EC_RSMRST#From EC to SB

DNBSWON#From EC to SB

SUSB#, SUSC#From SB to EC

+0.75V_DDR_VTT, +SMDDR_VREF

+1.5VSUS

HWPG_1.5V

+5V, +3V, +1.8V, +1.5V

HWPG_1.8V

+1.1V

VRON

+2.5V

HWPG_2.5V

+VCORE

CPU_VDDNB_CORE

CPU_COREPG

CPU_VDDR

HWPG_0.9V

+NB_CORE_ON

NB_CORE

HWPG_0.95V

SB_PWRGD_IN

NB_PWRGD_IN

EC setting: 5ms

EC setting: 30ms

EC setting: 100ms

EC setting: 10ms

VTERM only will be shut down in S3 mode,

and VTERM for DDR3 SODIMM only

EC setting: 10ms

EC setting: 10ms

RC=~22ms, NB_CORE should not ramp before 1.1V

EC setting: 10ms

SB_PWRGD_IN rise time<50ms

SB_PWRGD to NB_PWRGD:40~42ms

Danube GPU Power Sequence

dGPU_VRONFrom SB

MXM_PWR_EN

2ms

Power on sequence required:

SB800:

1.+3.3V_S5 ramp before +1.1_S5

2.+3.3V ramp before +1.8V

3.+1.8V ramp before +1.1V

4.+3.3V ramp before +1.1V

5.+3.3V_S5 ramping down time>300us

6.All power rails rise time >= 50us, except +3.3V_S5<=40ms

7.100us<=+3.3V_S5 rise time<=40ms

9.VBAT (VCCRTC) must ramp at least 5 seconds before the S5 rails

to allow start time for the internal RTC

(only in SB820M NB_PWRGD signal)

40ms <= SB PWRGOOD to NB_PWRGD delay <= 42ms

RS880:

1.0<(+3.3V)-(+1.8V)<2.1

2.+1.8V ramp before +1.1V

3.+1.1V ramp before CPU_VDDNB_CORE

BOM naming rule

Items Function Name Description

Internal CLK GEN

1

External CLK GEN

2

iGPU IV@

3

4

dGPU

5

iGPU & dGPU notice

SGN@

GN@

SW@

SP@

SB SMBUS Table

CLK GEN RAM Mini Card (WLAN)

(SB_DA0)/(SB_CL0) (+3V)

Power Plane

MOS CKT (Level shift)

V

+3V +3V

X X X*

VV

+3V

*Reserve: There is not SMBUS function in AVL

EC SMBUS Table

CPU thermal SensorBattery

EC775 SDA1 / SCL1 (+3VPCU)

EC775 SDA2 / SCL2 (+3V)

EC775 SDA3 / SCL3 ()

Power Plane +3VPCU

MOS CKT (Level shift)

V

V

+3V

X

X

+3V_D

+VGPU_CORE

A A

PG_GPIO_EN

+1V

PG_1.5V_EN

+1.5V_GPU

+1.8V_GPU

5

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Power Sequence

Power Sequence

Power Sequence

1

ZRA

ZRA

ZRA

2 48Monday, March 29, 2010

2 48Monday, March 29, 2010

2 48Monday, March 29, 2010

1A

1A

1A

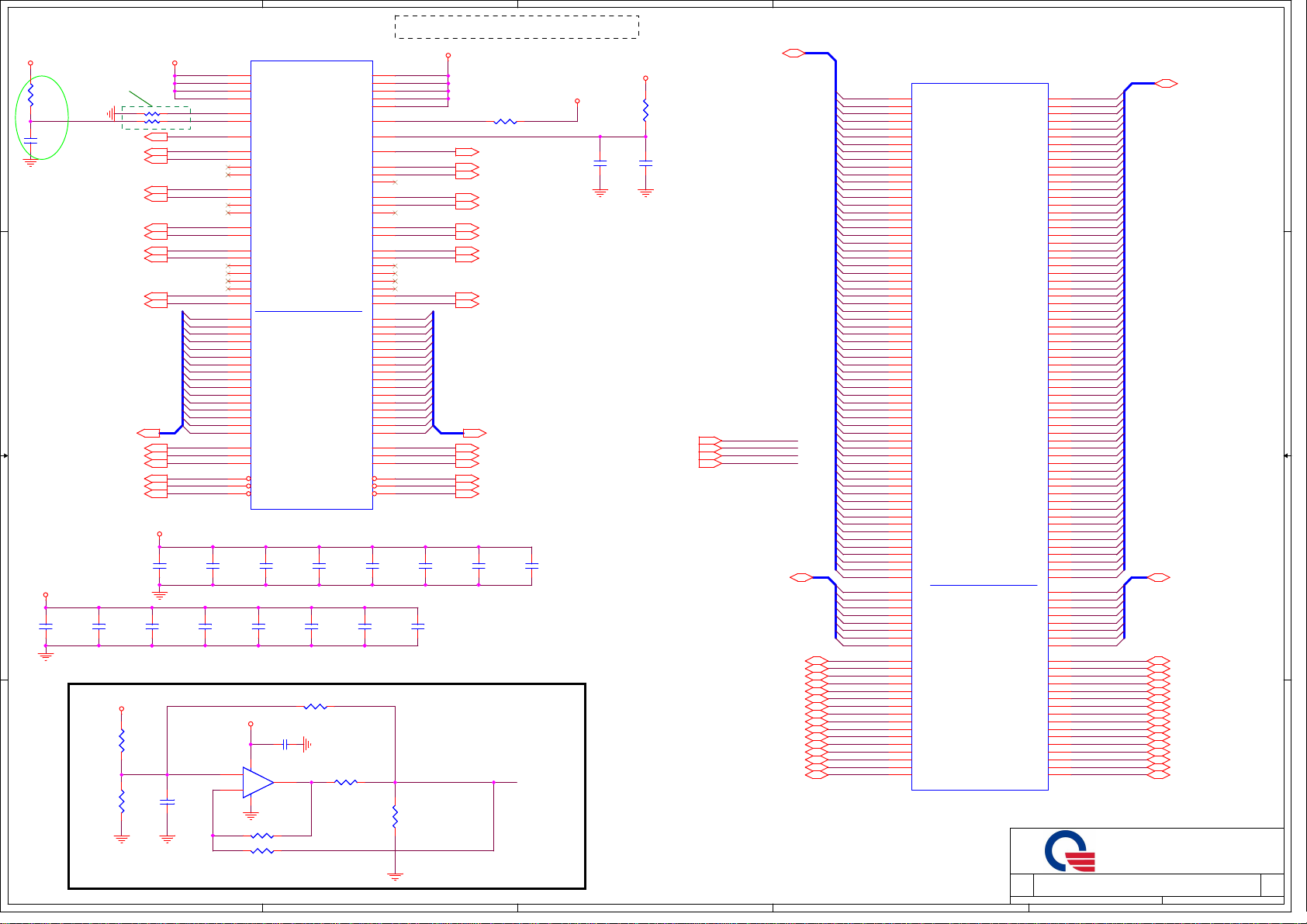

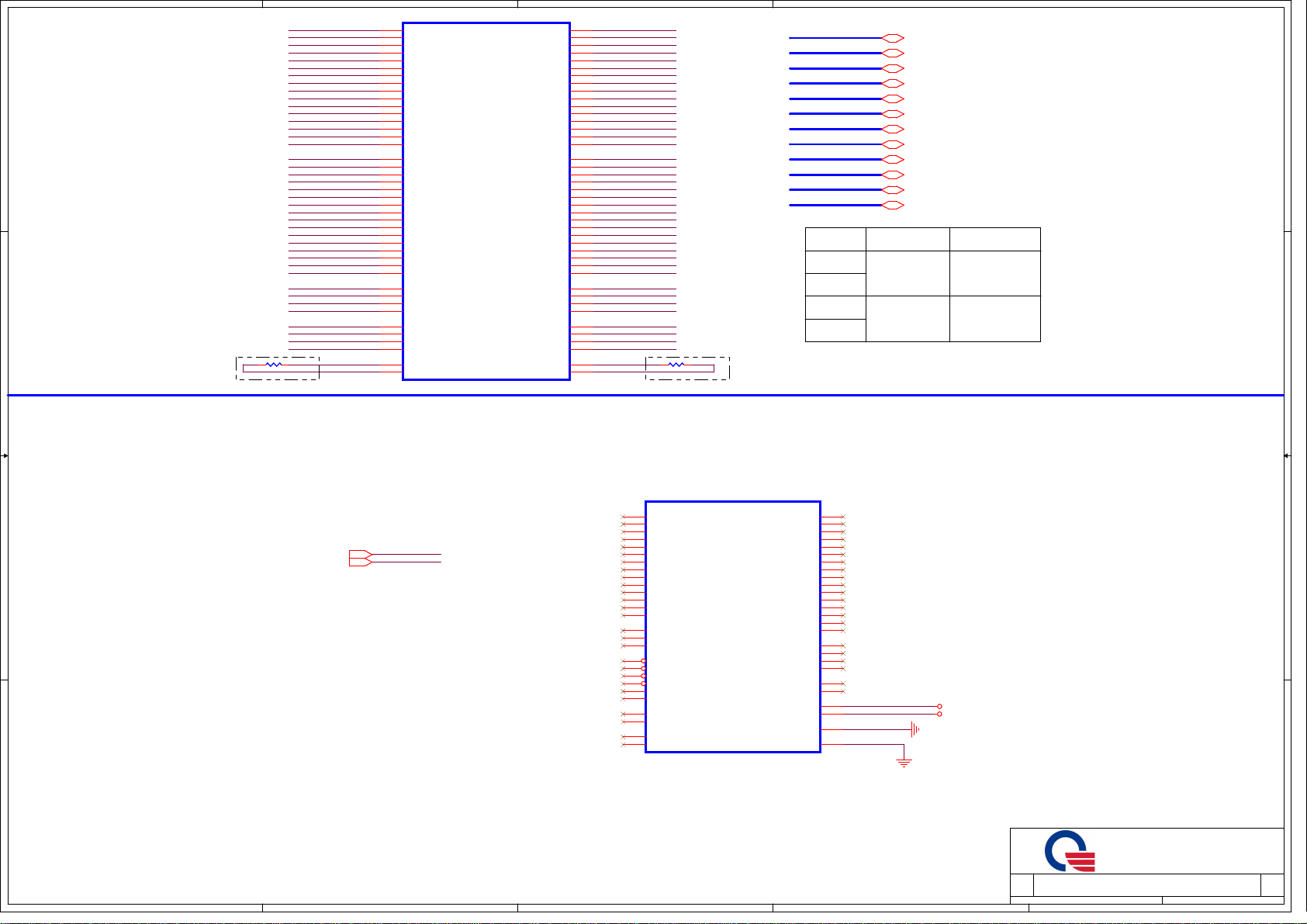

Page 3

5

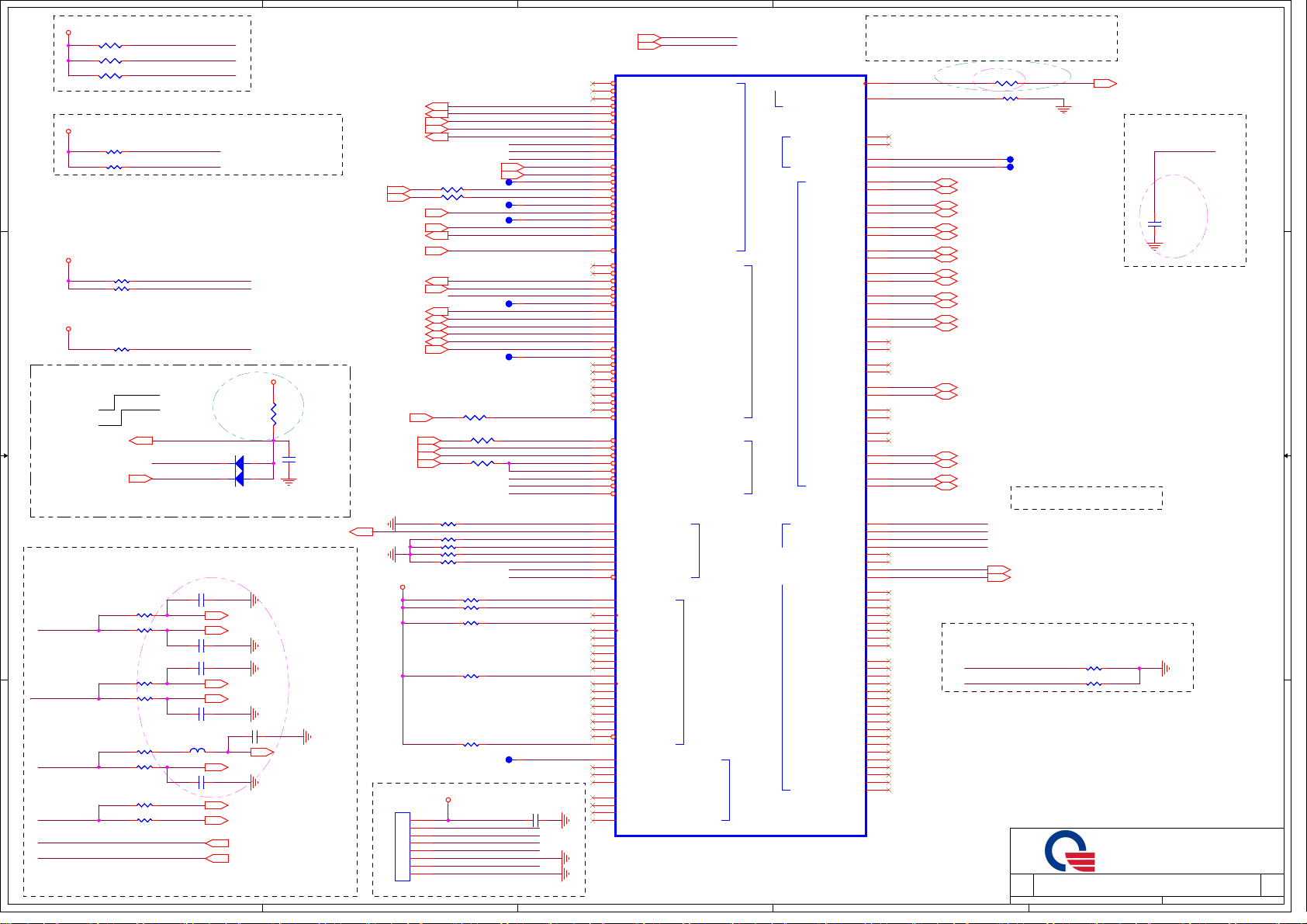

S1G4

+1.1V +1.1V_VLDT

1.1V@1.5A

R486 0_6R486 0_6

R483 0_6R483 0_6

P/N: DG0^8000005

DG0^8000009

DG0^80000013

D D

DG0^80000014

C450 10u/6.3V_8C450 10u/6.3V_8

C746 10u/6.3V_8C746 10u/6.3V_8

C453 0.22u/6.3V_4C453 0.22u/6.3V_4

C314 180P/50V_4C314 180P/50V_4

SI Change from AMD request

HT_CADINP[15..0]8

HT_CADINN[15..0]8

HT_CLKINP[1..0]8

HT_CLKINN[1..0]8

HT_CTLINP[1..0]8

HT_CTLINN[1..0]8

HT_CADOUTP[15..0]8

HT_CADOUTN[15..0]8

HT_CLKOUTP[1..0]8

HT_CLKOUTN[1..0]8

HT_CTLOUTP[1..0]8

C C

HT_CTLOUTN[1..0]8

FOX PZ63826-284R-41F

DG0^8000004 IC SOCKET SMD 638P S1(P1.27,H3.2)

MLX 47296-4131

DG0^8000003 IC SOCKET SMD 638P S1(P1.27,H3.2)

TYC 4-1903401-2

DG0^8000005 IC SOCKET SMD 638P S1(P1.27,H3.2)

HT_CADINP[15..0]

HT_CADINN[15..0]

HT_CLKINP[1..0]

HT_CLKINN[1..0]

HT_CTLINP[1..0]

HT_CTLINN[1..0]

HT_CADOUTP[15..0]

HT_CADOUTN[15..0]

HT_CLKOUTP[1..0]

HT_CLKOUTN[1..0]

HT_CTLOUTP[1..0]

HT_CTLOUTN[1..0]

2.5V@250mA

HT_CADINP0

HT_CADINN0

HT_CADINP1

HT_CADINN1

HT_CADINP2

HT_CADINN2

HT_CADINP3

HT_CADINN3

HT_CADINP4

HT_CADINN4

HT_CADINP5

HT_CADINN5

HT_CADINP6

HT_CADINN6

HT_CADINP7

HT_CADINN7

HT_CADINP8

HT_CADINN8

HT_CADINP9

HT_CADINN9

HT_CADINP10

HT_CADINN10

HT_CADINP11

HT_CADINN11

HT_CADINP12

HT_CADINN12

HT_CADINP13

HT_CADINN13

HT_CADINP14

HT_CADINN14

HT_CADINP15

HT_CADINN15

HT_CLKINP0

HT_CLKINN0

HT_CLKINP1

HT_CLKINN1

HT_CTLINP0

HT_CTLINN0

HT_CTLINP1

HT_CTLINN1

BLM21PG221SN1D(220 100M2A)_8

BLM21PG221SN1D(220 100M2A)_8

+2.5V

C781

C781

4.7u/6.3V_6

4.7u/6.3V_6

+1.1V_VLDT

+1.1V_VLDT

+1.1V_VLDT

+1.1V_VLDT

L44

L44

D1

D2

D3

D4

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

J3

J2

J5

K5

N1

P1

P3

P4

SOCKET_638_PIN

SOCKET_638_PIN

LS0805-100M-N

U30A

U30A

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

4

HT LINK

HT LINK

C483

C483

4.7u/6.3V_6

4.7u/6.3V_6

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

+CPUVDDA

C459

C459

0.22u/6.3V_4

0.22u/6.3V_4

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

W/S= 15 mil/20mil

C463

C463

3300P/50V_4

3300P/50V_4

+1.1V_VLDT

+1.1V_VLDT

+1.1V_VLDT

+1.1V_VLDT

HT_CADOUTP0

HT_CADOUTN0

HT_CADOUTP1

HT_CADOUTN1

HT_CADOUTP2

HT_CADOUTN2

HT_CADOUTP3

HT_CADOUTN3

HT_CADOUTP4

HT_CADOUTN4

HT_CADOUTP5

HT_CADOUTN5

HT_CADOUTP6

HT_CADOUTN6

HT_CADOUTP7

HT_CADOUTN7

HT_CADOUTP8

HT_CADOUTN8

HT_CADOUTP9

HT_CADOUTN9

HT_CADOUTP10

HT_CADOUTN10

HT_CADOUTP11

HT_CADOUTN11

HT_CADOUTP12

HT_CADOUTN12

HT_CADOUTP13

HT_CADOUTN13

HT_CADOUTP14

HT_CADOUTN14

HT_CADOUTP15

HT_CADOUTN15

HT_CLKOUTP0

HT_CLKOUTN0

HT_CLKOUTP1

HT_CLKOUTN1

HT_CTLOUTP0

HT_CTLOUTN0

HT_CTLOUTP1

HT_CTLOUTN1

C469

C469

*10u/6.3V_8

*10u/6.3V_8

C44910u/6.3V_8 C44910u/6.3V_8

C3180.22u/6.3V_4 C3180.22u/6.3V_4

C448180P/50V_4 C448180P/50V_4

+1.5VSUS

B-TEST 0205

SIC5

SID5

ALERT_L5

SideBand Temp sense I2C

3

CPU CLK

CLK_CPU_BCLKP_PR12

CLK_CPU_BCLKN_PR12

Keep trace from resisor to CPU within 0.6"

keep trace from caps to CPU within 1.2"

CLK_CPU_BCLKP_C CLK_CPU_BCLKN_C

CLK_CPU_BCLKP_PR

CLK_CPU_BCLKN_PR

R490

R490

1K_4

1K_4

+1.5VSUS4,5,6,7,15,29,38,41,43,44

+1.5V27,29,41,44

+1.1V8,9,10,11,15,39

+2.5V43

R488

R488

1K_4

1K_4

S1G4

+1.5VSUS

R516 169/F_4R516 169/F_4

R487

R487

1K_4

1K_4

+1.1V_VLDT

+1.5VSUS

C780 3900P/25V_4C780 3900P/25V_4

C779 3900P/25V_4C779 3900P/25V_4

R477 1K_4R477 1K_4

R478 *300_4R478 *300_4

+1.5VSUS

+1.5V

+1.1V

+2.5V

CLK_CPU_BCLKP_PR

CLK_CPU_BCLKN_PR

CPU_LDT_RST#12

CPU_PWRGD12

CPU_LDT_STOP#10,12

R220 44.2/F_4R220 44.2/F_4

R218 44.2/F_4R218 44.2/F_4

CPU_VDD0_FB_H38

CPU_VDD0_FB_L38

CPU_VDD1_FB_H38

CPU_VDD1_FB_L38

R519 510_4R519 510_4

R518 510_4R518 510_4

2

+CPUVDDA

W/S= 15 mil/20mil

+CPUVDDA

+CPUVDDA

CLK_CPU_BCLKP_C

CLK_CPU_BCLKN_C

CPU_LDT_RST#

CPU_PWRGD

CPU_LDT_STOP#

CPU_LDT_REQ#_CPU

CPU_HTREF0

CPU_HTREF1

place them to CPU within 1.5"

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPUTEST23

CPUTEST18

CPUTEST19

CPUTEST25H

CPUTEST25L

place them to CPU within 1.5"

CPUTEST21

CPUTEST20

CPUTEST24

CPUTEST22

CPUTEST12

CPUTEST27

R503 *short_4R503 *short_4

SB check list tide to CPUVDDIO (+1.5VSUS)

CPU_PWRGD

CPU_LDT_RST#

CPU_LDT_STOP#

CPU_LDT_REQ#_CPU

250mA

F8

F9

A9

A8

B7

A7

F10

C6

SIC

AF4

SID

AF5

ALERT_L

AE6

R6

P6

F6

E6

Y6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

G9

E9

E8

AB8

AF7

AE7

AE8

AC8

AF8

TEST9

C2

AA6

A3

A5

B3

B5

C1

U30D

U30D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

SIC

SID

ALERT_L

HT_REF0

HT_REF1

VDD0_FB_H

VDD0_FB_L

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

TEST19

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TEST6

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

SOCKET_638_PIN

SOCKET_638_PIN

VSS

RSVD11

SVC

SVD

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

R514300_4 R514300_4

R509300_4 R509300_4

R243300_4 R243300_4

R505*300_4 R505*300_4

M11

W18

A6

A4

AF6

AC7

AA8

W7

W8

W9

Y9

H6

G6

E10

AE9

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

+1.5V

CPU_SVC_R

CPU_SVD_R

CPU_THERMTRIP_L#

CPU_PROCHOT_L#

CPU_MEMHOT_L#

VDDIO_FB_H

VDDIO_FB_L

CPU_DBREQ#

CPU_TDO

CPUTEST17

CPUTEST16

CPUTEST15

CPUTEST14

CPUTEST29H

CPUTEST29L

1

S1G4

R520 300_4R520 300_4

S1G4

H_THRMDC 5

H_THRMDA 5

VDDIO_FB_H 41

VDDIO_FB_L 41

CPU_VDDNB_FB_H 38

CPU_VDDNB_FB_L 38

T30T30

T29T29

T28T28

T33T33

T72T72

R511

R511

80.6/F_4

80.6/F_4

T73T73

+1.5VSUS

CPU_LDT_REQ# 10

CPU_LDT_RST#

R459

R459

*10K_4

*10K_4

R455 0_4R455 0_4

B-TEST 0205

CNTR_VREF

D25

D25

*BAS316

*BAS316

R460 100K_6R460 100K_6

SYS_SHDN# 18,37,44

CPU_THERMTRIP# 13

+1.5VSUS

+1.5VSUS

CPU_MEMHOT_L#

+3V

R532

R532

4.7K_4

4.7K_4

CPU_LDT_RST_HTPA#

3

Q36

Q36

BSS138_NL/SOT23

BSS138_NL/SOT23

12

G2

G2

*SHORT_PAD1

*SHORT_PAD1

2

1

for debug only

R457 *10K_4R457 *10K_4

S1G4

2

Q32

R464 *1K_4R464 *1K_4

Q32

*MMBT3904

*MMBT3904

13

CPU_MEMHOT# 6,7,12

S1g4 does not support MEMHOT#

4

S1G4

Serial VID

SI Change from AMD request

+1.5VSUS

+1.5V

+1.5VSUS

+1.5V

CPU_SVC_R

CPU_SVD_R

CPU_PWRGD

R530 1K_4R530 1K_4

R526 *1K_4R526 *1K_4

R531 1K_4R531 1K_4

R527 *1K_4R527 *1K_4

R513 *short_4R513 *short_4

R512 *short_4R512 *short_4

R515 *short_4R515 *short_4

R523 *220_4R523 *220_4

R522 *220_4R522 *220_4

R525 *220_4R525 *220_4

HDT Connector

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

+1.5VSUS

CPU_TDO

C484 *0.1u/10V_4C484 *0.1u/10V_4

3

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

KEY

KEY

*HDT_CONN

*HDT_CONN

CN7

CN7

VFIX MODE

VID Override Circuit

SVC SVD Voltage Output

CPU_SVC 38

CPU_SVD 38

CPU_PWRGD_SVID_REG 38

0 0

0

1

1

CPUTEST24

CPUTEST23

CPUTEST20

CPUTEST22

CPUTEST12

CPUTEST15

CPUTEST14

CPUTEST19

CPUTEST18

CPUTEST21

1

0

1

R475 1K_4R475 1K_4

R473 *1K_4R473 *1K_4

R474 1K_4R474 1K_4

R476 1K_4R476 1K_4

R184 1K_4R184 1K_4

R229 1K_4R229 1K_4

R534 1K_4R534 1K_4

R533 1K_4R533 1K_4

R236 1K_4R236 1K_4

R159 1K_4R159 1K_4

1.1V

1.0V

0.9V

0.8V

S1G4

S1G4

Quanta Computer Inc.

Quanta Computer Inc.

25

CPU_LDT_RST_HTPA#

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

S1G4 HT,CTL I/F 1/3

S1G4 HT,CTL I/F 1/3

S1G4 HT,CTL I/F 1/3

ZRA

ZRA

ZRA

3 48Monday, March 29, 2010

3 48Monday, March 29, 2010

3 48Monday, March 29, 2010

1

1A

1A

1A

+1.5VSUS

3

1

2

1 3

Q31

Q31

MMBT3904

MMBT3904

CNTR_VREF 5

Q33

Q33

FDV301N

FDV301N

R461

R461

10K_4

10K_4

R456 *0_4R456 *0_4

CPU_PROCHOT# 12,14

R524 20K/F_4R524 20K/F_4

+3V

B B

CPU_LDT_REQ#_CPU

The RS880 family does not support CLMC architecture

The LDTREQ# connection from the CPU to ALLOW_LDTSTOP

of the Northbridge is no longer required.

A A

+1.5VSUS

R472 300_4R472 300_4

+1.5VSUS

CPU_PROCHOT_L#

Q35 *BSS138_NL/SOT23Q35 *BSS138_NL/SOT23

1

R508 *0_4R508 *0_4

CPU_COREPG16,38,39

CPU_THERMTRIP_L#

R466 *10K_4R466 *10K_4

C778 0.1u/10V_4C778 0.1u/10V_4

R529 34.8K/F_4R529 34.8K/F_4

2

3

+1.5VSUS

R467

R467

1K_4

1K_4

2

Q30

Q30

1 3

*MMBT3904

*MMBT3904

R458 0_4R458 0_4

5

2

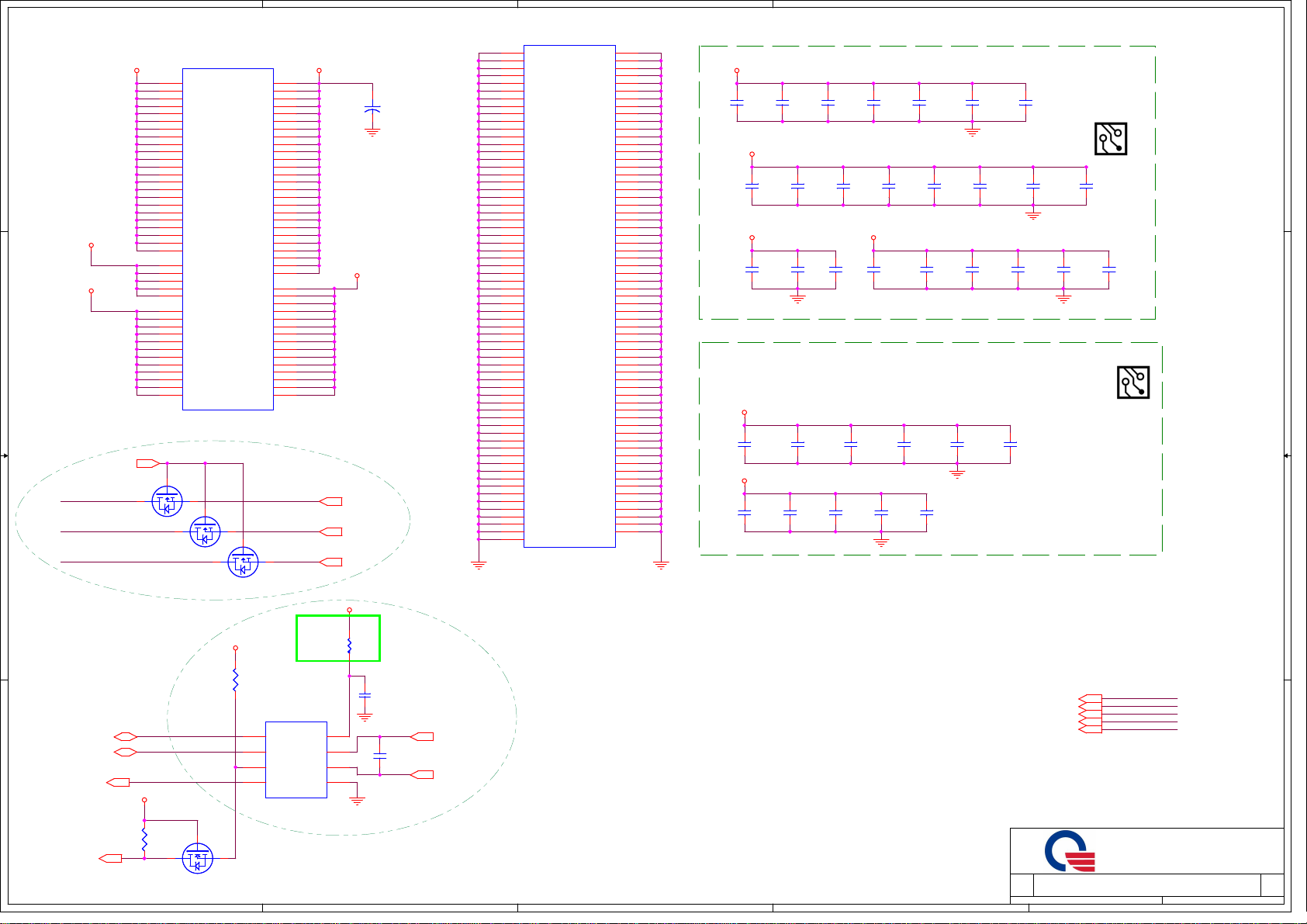

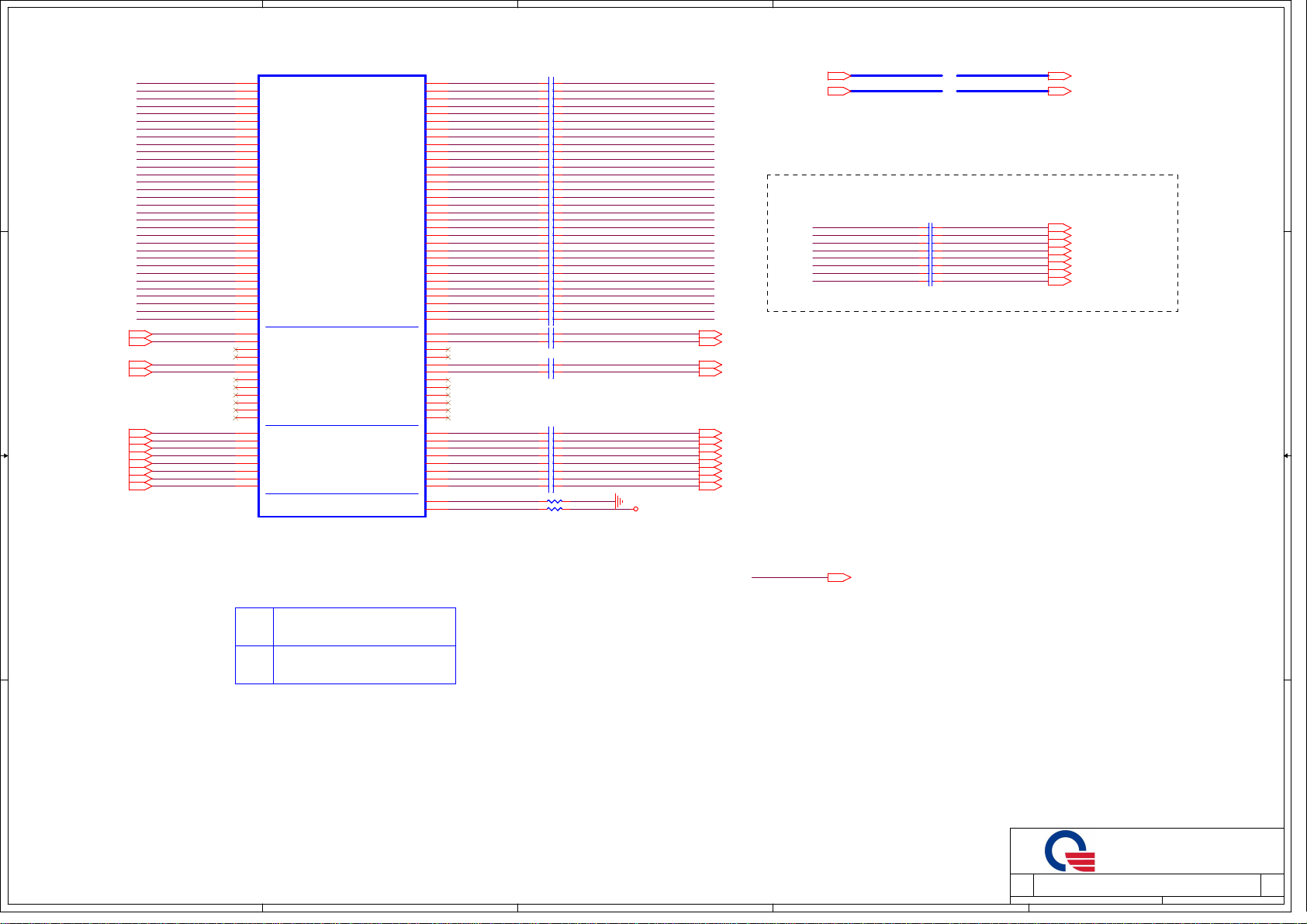

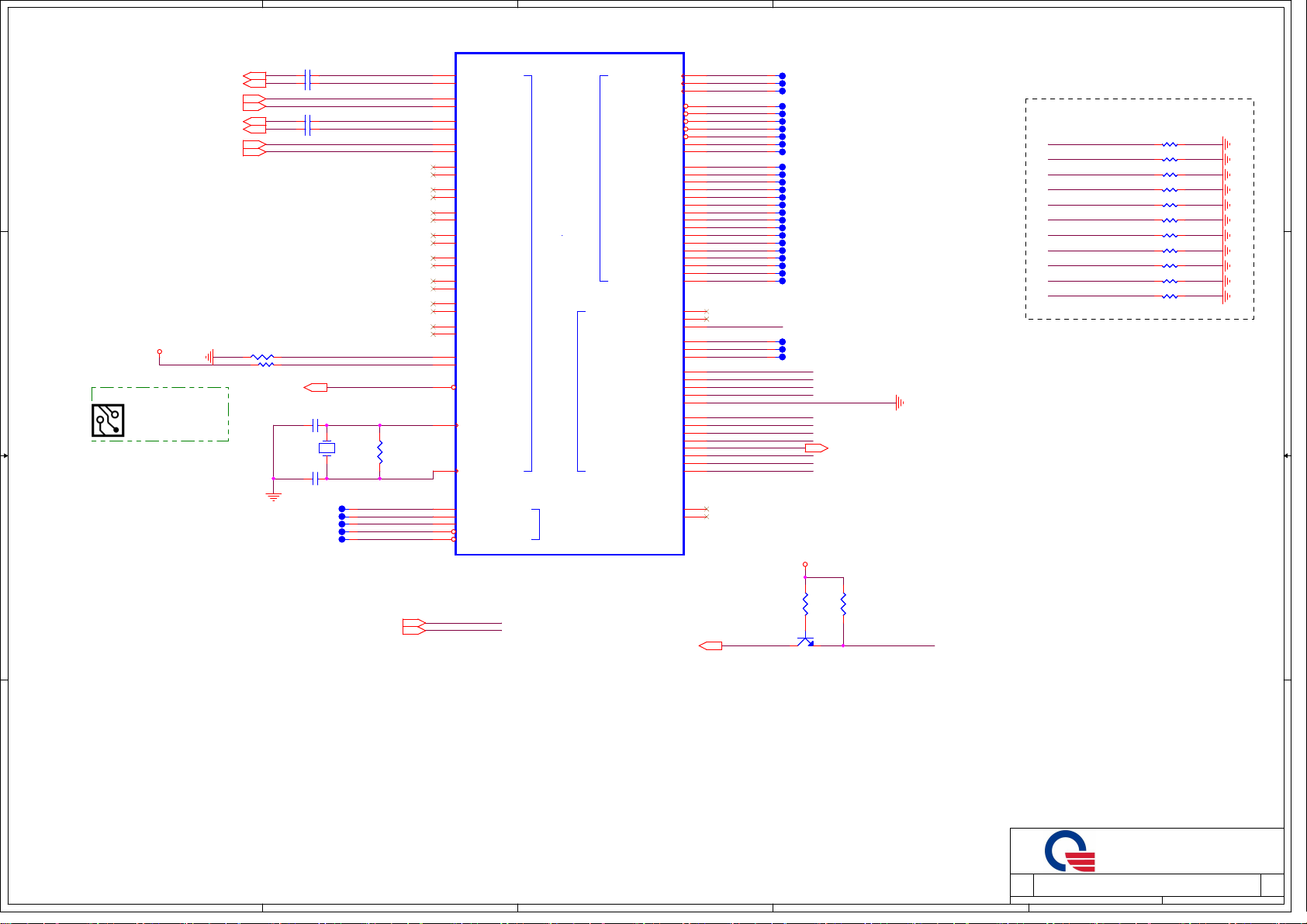

Page 4

A

+1.5VSUS CPU_VDDR

PLACE THEM CLOSE TO

CPU WITHIN 1"

R465

R465

0_4

0_4

4 4

C739

C739

10u/6.3V_8

10u/6.3V_8

S1G4

3 3

2 2

CPU_VDDR

C465

C465

1000P/50V_4

1000P/50V_4

1 1

R480 39.2/F_4R480 39.2/F_4

R479 39.2/F_4R479 39.2/F_4 R182 *0_4R182 *0_4

M_A_RST#6

M_A_ODT06

M_A_ODT16

M_A_CS#06

M_A_CS#16

M_A_CKE06

M_A_CKE16

M_A_CLKP16

M_A_CLKN16

M_A_CLKP26

M_A_CLKN26

M_A_A[0..15]6 M_B_A[0..15] 7

M_A_BANK06

M_A_BANK16

M_A_BANK26

M_A_RAS#6

M_A_CAS#6

M_A_WE#6

CPU_VDDR

C464

C464

1000P/50V_4

1000P/50V_4

+1.5VSUS

R462

R462

1K/F_4

1K/F_4

R469

R469

1K/F_4

1K/F_4

A

C472

C472

4.7u/6.3V_6

4.7u/6.3V_6

C371

C371

1000P/50V_4

1000P/50V_4

C741

C741

*0.47u/10V_4

*0.47u/10V_4

1 2

M_ZP

M_ZN

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

U30B

U30B

D10

VDDR1

MEM:CMD/CTRL/CLK

C10

B10

AD10

AF10

AE10

H16

V22

U21

V19

U19

U20

V20

N19

N20

E16

AA16

P19

P20

N21

M20

N22

M19

M22

M24

K22

R21

K20

V24

K24

K19

R20

R23

R19

T19

T20

J22

J20

F16

Y16

L20

L21

L19

L22

J21

T22

T24

MEM:CMD/CTRL/CLK

VDDR2

VDDR3

VDDR4

MEMZP

MEMZN

MA_RESET_L

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_CKE0

MA_CKE1

MA_CLK_H5

MA_CLK_L5

MA_CLK_H1

MA_CLK_L1

MA_CLK_H7

MA_CLK_L7

MA_CLK_H4

MA_CLK_L4

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_RAS_L

MA_CAS_L

MA_WE_L

SOCKET_638_PIN

SOCKET_638_PIN

Place close to socket

C309

C309

4.7u/6.3V_6

4.7u/6.3V_6

C299

C299

1000P/50V_4

1000P/50V_4

C461

C461

180P/50V_4

180P/50V_4

+3VPCU

52

U27

U27

3

+

+

4

-

-

*OPA343NA/3K

*OPA343NA/3K

R468 *0_4R468 *0_4

R463 *0_4R463 *0_4

C471

C471

4.7u/6.3V_6

4.7u/6.3V_6

R470 0_4R470 0_4

C734

C734

*0.1u/10V_4

*0.1u/10V_4

1

VDDR_SENSE

MEMVREF

MB_RESET_L

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

C305

C305

4.7u/6.3V_6

4.7u/6.3V_6

C470

C470

180P/50V_4

180P/50V_4

R471 *10_4R471 *10_4

VDDR5

VDDR6

VDDR7

VDDR8

VDDR9

B

VDDR=> 0.9V support 1066 / 800 DDR

VDDR= >1.05V support 1333 / 1066 / 800 DDR

CPU_VDDR

VDDR=>1.75A

W10

AC10

AB10

AA10

A10

CPU_VTT_SENSE

Y10

MEMVREF_CPU

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

C306

C306

0.22u/6.3V_4

0.22u/6.3V_4

C468

C468

180P/50V_4

180P/50V_4

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

C308

C308

0.22u/6.3V_4

0.22u/6.3V_4

C460

C460

180P/50V_4

180P/50V_4

M_B_RST# 7

M_B_ODT0 7

M_B_ODT1 7

M_B_CS#0 7

M_B_CS#1 7

M_B_CKE0 7

M_B_CKE1 7

M_B_CLKP1 7

M_B_CLKN1 7

M_B_CLKP2 7

M_B_CLKN2 7

M_B_BANK0 7

M_B_BANK1 7

M_B_BANK2 7

M_B_RAS# 7

M_B_CAS# 7

M_B_WE# 7

C302

C302

0.22u/6.3V_4

0.22u/6.3V_4

Reserved for AMD suggest

MEMVREF_CPU

R481

R481

*10K_4

*10K_4

B

+0.75V_DDR_VTT

C303

C303

0.22u/6.3V_4

0.22u/6.3V_4

+SMDDR_VREF

C369

C369

0.1u/10V_4

0.1u/10V_4

C

+0.75V_DDR_VTT6,7,41

+SMDDR_VREF6,7,41

C

R482

R482

*0_4

*0_4

C367

C367

1000P/50V_4

1000P/50V_4

CPU_VDDR44

+1.5VSUS3,5,6,7,15,29,38,41,43,44

M_B_DQ[0..63]7

+0.75V_DDR_VTT

+SMDDR_VREF

CPU_VDDR

+1.5VSUS

M_B_DM[0..7]7

M_B_DQSP07

M_B_DQSN07

M_B_DQSP17

M_B_DQSN17

M_B_DQSP27

M_B_DQSN27

M_B_DQSP37

M_B_DQSN37

M_B_DQSP47

M_B_DQSN47

M_B_DQSP57

M_B_DQSN57

M_B_DQSP67

M_B_DQSN67

M_B_DQSP77

M_B_DQSN77

D

Processor Memory Interface

U30C

U30C

MEM:DATA

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

AE14

AF14

AF11

AD11

A12

B16

A22

E25

AB26

AE22

AC16

AD12

C12

B12

D16

C16

A24

A23

E26

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

Y11

F26

D

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MEM:DATA

SOCKET_638_PIN

SOCKET_638_PIN

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

M_A_DM[0..7] 6

M_A_DQSP0 6

M_A_DQSN0 6

M_A_DQSP1 6

M_A_DQSN1 6

M_A_DQSP2 6

M_A_DQSN2 6

M_A_DQSP3 6

M_A_DQSN3 6

M_A_DQSP4 6

M_A_DQSN4 6

M_A_DQSP5 6

M_A_DQSN5 6

M_A_DQSP6 6

M_A_DQSN6 6

M_A_DQSP7 6

M_A_DQSN7 6

E

M_A_DQ[0..63] 6

ZRA

ZRA

ZRA

M_A_DQ0

G12

M_A_DQ1

F12

M_A_DQ2

H14

M_A_DQ3

G14

M_A_DQ4

H11

M_A_DQ5

H12

M_A_DQ6

C13

M_A_DQ7

E13

M_A_DQ8

H15

M_A_DQ9

E15

M_A_DQ10

E17

M_A_DQ11

H17

M_A_DQ12

E14

M_A_DQ13

F14

M_A_DQ14

C17

M_A_DQ15

G17

M_A_DQ16

G18

M_A_DQ17

C19

M_A_DQ18

D22

M_A_DQ19

E20

M_A_DQ20

E18

M_A_DQ21

F18

M_A_DQ22

B22

M_A_DQ23

C23

M_A_DQ24

F20

M_A_DQ25

F22

M_A_DQ26

H24

M_A_DQ27

J19

M_A_DQ28

E21

M_A_DQ29

E22

M_A_DQ30

H20

M_A_DQ31

H22

M_A_DQ32

Y24

M_A_DQ33

AB24

M_A_DQ34

AB22

M_A_DQ35

AA21

M_A_DQ36

W22

M_A_DQ37

W21

M_A_DQ38

Y22

M_A_DQ39

AA22

M_A_DQ40

Y20

M_A_DQ41

AA20

M_A_DQ42

AA18

M_A_DQ43

AB18

M_A_DQ44

AB21

M_A_DQ45

AD21

M_A_DQ46

AD19

M_A_DQ47

Y18

M_A_DQ48

AD17

M_A_DQ49

W16

M_A_DQ50

W14

M_A_DQ51

Y14

M_A_DQ52

Y17

M_A_DQ53

AB17

M_A_DQ54

AB15

M_A_DQ55

AD15

M_A_DQ56

AB13

M_A_DQ57

AD13

M_A_DQ58

Y12

M_A_DQ59

W11

M_A_DQ60

AB14

M_A_DQ61

AA14

M_A_DQ62

AB12

M_A_DQ63

AA12

M_A_DM0

E12

M_A_DM1

C15

M_A_DM2

E19

M_A_DM3

F24

M_A_DM4

AC24

M_A_DM5

Y19

M_A_DM6

AB16

M_A_DM7

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

S1G4 DDRIII MEMORY I/F 2/3

S1G4 DDRIII MEMORY I/F 2/3

S1G4 DDRIII MEMORY I/F 2/3

1A

1A

4 48Monday, March 29, 2010

4 48Monday, March 29, 2010

4 48Monday, March 29, 2010

1A

Page 5

5

U30E

U30E

G4

VDD_1

H2

VDD_2

J9

VDD_3

J11

VDD_4

J13

VDD_5

D D

CPU_VDDNB_CORE

3A

+1.5VSUS

C C

CNTR_VREF3

CPU_SMBCLK

BSS138_NL/SOT23

BSS138_NL/SOT23

CPU_SMBDATA

B B

OVT#

J15

K6

K10

K12

K14

L4

L7

L9

L11

L13

L15

M2

M6

M8

M10

N7

N9

N11

K16

M16

P16

T16

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

2

3

BSS138_NL/SOT23

BSS138_NL/SOT23

BSS138_NL/SOT23

BSS138_NL/SOT23

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

SOCKET_638_PIN

SOCKET_638_PIN

Q43

Q43

1

3

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

2

Q42

Q42

1

2

3

+VCORE+VCORE +VCORE

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

Place under CPU bracket side.

+1.5VSUS

B-TEST 0205

Q44

Q44

1

PV modify for design

+3V

PC55

PC55

+

330u/2V_7343

+

330u/2V_7343

1.5V@2A

SIC 3

SID 3

ALERT_L 3

4

U30F

U30F

AA4

AA11

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AB2

AB7

AB9

AD6

AD8

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

H21

H23

B4

B6

B8

B9

D6

D8

D9

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

J4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

SOCKET_638_PIN

SOCKET_638_PIN

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

3

2

1

BOTTOM SIDE DECOUPLING

C389

C389

10u/6.3V_8

10u/6.3V_8

+VCORE

C381

C381

10u/6.3V_8

10u/6.3V_8

CPU_VDDNB_CORE

C382

C382

10u/6.3V_8

10u/6.3V_8

C378

C378

10u/6.3V_8

10u/6.3V_8

10u/6.3V_8

10u/6.3V_8

10u/6.3V_8

10u/6.3V_8

C407

C407

C399

C399

10u/6.3V_8

10u/6.3V_8

C404

C404

C416

C416

10u/6.3V_8

10u/6.3V_8

+1.5VSUS

C390

C390

10u/6.3V_8

10u/6.3V_8

C426

C426

10u/6.3V_8

10u/6.3V_8

10u/6.3V_8

10u/6.3V_8

C427

C427

10u/6.3V_8

10u/6.3V_8

C420

C420

C434

C434

0.22u/6.3V_4

0.22u/6.3V_4

0.22u/6.3V_4

0.22u/6.3V_4

C388

C388

10u/6.3V_8

10u/6.3V_8

C425

C425

C379

C379

0.01u/16V_4

0.01u/16V_4

C435

C435

0.01u/16V_4

0.01u/16V_4

C393

C393

0.22u/6.3V_4

0.22u/6.3V_4

C380

C380

180P/50V_4

180P/50V_4

180P/50V_4

180P/50V_4

C417

C417

0.22u/6.3V_4

0.22u/6.3V_4

C436

C436

C395

C395

0.01u/16V_4

0.01u/16V_4

C396

C396

180P/50V_4

180P/50V_4

C413

C413

180P/50V_4

180P/50V_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.5VSUS

C437

4.7u/6.3V_6

4.7u/6.3V_6

+1.5VSUS

0.22u/6.3V_4

0.22u/6.3V_4

C437

C400

C400

C421

C421

4.7u/6.3V_6

4.7u/6.3V_6

C387

C387

0.22u/6.3V_4

0.22u/6.3V_4

4.7u/6.3V_6

4.7u/6.3V_6

C423

C423

0.01u/16V_4

0.01u/16V_4

C406

C406

4.7u/6.3V_6

4.7u/6.3V_6

C397

C397

0.01u/16V_4

0.01u/16V_4

C414

C414

0.22u/6.3V_4

0.22u/6.3V_4

C431

C431

180P/50V_4

180P/50V_4

C401

C401

C375

C375

0.22u/6.3V_4

0.22u/6.3V_4

PROCESSOR POWER AND GROUND

R536

MSOP

VCC

DXP

DXN

GND

R536

*200/F_6

*200/F_6

1

2

3

5

C782

C782

*0.1U/10V_4

*0.1U/10V_4

C474

C474

*2200P/50V_4

*2200P/50V_4

4

B-TEST 0221

H_THRMDA 3

H_THRMDC 3

+1.5VSUS3,4,6,7,15,29,38,41,43,44

CPU_VDDNB_CORE38

+VCORE38

+3V_S512,13,15,16,26,27,29,32,35,37

+3V3,6,7,10,11,12,13,14,15,16,18,20,25,26,27,29,30,32,33,34,35,37,38,39,40,41,42,43,44

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

S1G4 PWR & GND 3/3

S1G4 PWR & GND 3/3

S1G4 PWR & GND 3/3

+1.5VSUS

CPU_VDDNB_CORE

+VCORE

+3V_S5

+3V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZRA

ZRA

ZRA

5 48Monday, March 29, 2010

5 48Monday, March 29, 2010

5 48Monday, March 29, 2010

1

1A

1A

1A

+3V

R540

R540

*10K_4

*10K_4

U31

CPU_SMBCLK34

CPU_SMBDATA34

OVT#33

A A

PM_THERM#13

CPU_SMBCLK

CPU_SMBDATA

OVT#

+3V

R535

R535

*8.2K_4

*8.2K_4

5

2

3

Q37*2N7002E-LF Q37*2N7002E-LF

U31

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

*G786P8

*G786P8

1

Page 6

5

4

3

2

1

2.48A

+3V

+1.5VSUS

MEMHOT_MA#

2

1 3

CN18B

CN18B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

DDR3_SO-DIMM_SOCKET_1.5V_Standard H=8

DDR3_SO-DIMM_SOCKET_1.5V_Standard H=8

Q26

Q26

*MMBT3904

*MMBT3904

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

(204P)

(204P)

PC2100 DDR3 SDRAM SO-DIMM

PC2100 DDR3 SDRAM SO-DIMM

VTT1

VTT2

GND

GND

CPU_MEMHOT# 3,7,12

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

205

206

+0.75V_DDR_VTT

M_A_A[15:0]4

D D

M_A_BANK[0..2]4

M_A_CS#04

M_A_CS#14

M_A_CLKP14

M_A_CLKN14

M_A_CLKP24

M_A_CLKN24

M_A_CKE04

M_A_CKE14

M_A_CAS#4

M_A_RAS#4

R152 10K_4R152 10K_4

R149 10K_4R149 10K_4

C C

B B

M_A_WE#4

PCLK_SMB7,13,27

PDAT_SMB7,13,27

M_A_ODT04

M_A_ODT14

M_A_DM[7:0]4

M_A_DQSP[7:0]4

M_A_DQSN[7:0]4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BANK0

M_A_BANK1

M_A_BANK2

DIMM0_SA0

DIMM0_SA1

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

CN18A

CN18A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

PC2100 DDR3 SDRAM SO-DIMM

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

PC2100 DDR3 SDRAM SO-DIMM

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

DDR3_SO-DIMM_SOCKET_1.5V_Standard H=8

DDR3_SO-DIMM_SOCKET_1.5V_Standard H=8

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

(204P)

(204P)

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

M_A_DQ1

M_A_DQ0

M_A_DQ3

M_A_DQ2

M_A_DQ5

M_A_DQ4

M_A_DQ7

M_A_DQ6

M_A_DQ9

M_A_DQ8

M_A_DQ15

M_A_DQ14

M_A_DQ12

M_A_DQ13

M_A_DQ11

M_A_DQ10

M_A_DQ21

M_A_DQ17

M_A_DQ23

M_A_DQ18

M_A_DQ20

M_A_DQ16

M_A_DQ19

M_A_DQ22

M_A_DQ24

M_A_DQ25

M_A_DQ30

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ26

M_A_DQ31

M_A_DQ36

M_A_DQ32

M_A_DQ33

M_A_DQ35

M_A_DQ38

M_A_DQ37

M_A_DQ39

M_A_DQ34

M_A_DQ40

M_A_DQ44

M_A_DQ42

M_A_DQ46

M_A_DQ45

M_A_DQ41

M_A_DQ43

M_A_DQ47

M_A_DQ53

M_A_DQ49

M_A_DQ55

M_A_DQ54

M_A_DQ48

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ61

M_A_DQ60

M_A_DQ63

M_A_DQ62

M_A_DQ56

M_A_DQ57

M_A_DQ59

M_A_DQ58

M_A_DQ[63:0] 4

+0.75VSMVREF_SUSA

+SMDDR_VREF

+1.5VSUS

R252

R252

1K/F_4

1K/F_4

R254

R254

1K/F_4

1K/F_4

R199 0_4R199 0_4

+1.5VSUS

+0.75VSMVREF_SUSA

+VREF_CA_A

*2K/F_4

*2K/F_4

*2K/F_4

*2K/F_4

R124 *2.2K_4R124 *2.2K_4

R123 2.2K_4R123 2.2K_4

MEMHOT_MA#

M_A_RST#4

+VREF_CA_A

+1.5VSUS

R198

R198

R195

R195

Place these Caps near So-Dimm0.

+1.5VSUS

C442

C442

C391

C391

C422

C438

C438

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

C432

C432

10u/6.3V_6

10u/6.3V_6

A A

5

C444

C444

10u/6.3V_6

10u/6.3V_6

C411

C411

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

10u/6.3V_6

C402

C402

*0.1u/10V_4

*0.1u/10V_4

+0.75V_DDR_VTT

C287

C287

1u/6.3V_4

1u/6.3V_4

C422

0.1u/10V_4

0.1u/10V_4

C418

C418

0.1u/10V_4

0.1u/10V_4

C403

C403

*0.1u/10V_4

*0.1u/10V_4

C288

C288

1u/6.3V_4

1u/6.3V_4

C394

C394

*0.1u/10V_4

*0.1u/10V_4

C861

C861

10u/6.3V_6

10u/6.3V_6

+VREF_CA_A

C385

C385

0.1u/10V_4

0.1u/10V_4

4

C384

C384

2.2u/6.3V_6

2.2u/6.3V_6

+0.75VSMVREF_SUSA

C492

C492

0.1u/10V_4

0.1u/10V_4

C490

C490

2.2u/6.3V_6

2.2u/6.3V_6

+1.5VSUS3,4,5,7,15,29,38,41,43,44

+3V3,5,7,10,11,12,13,14,15,16,18,20,25,26,27,29,30,32,33,34,35,37,38,39,40,41,42,43,44

+0.75V_DDR_VTT4,7,41

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

+1.5VSUS

+3V

+0.75V_DDR_VTT

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

DDR3 DIMMA-STD

DDR3 DIMMA-STD

DDR3 DIMMA-STD

ZRA

ZRA

ZRA

6 48Monday, March 29, 2010

6 48Monday, March 29, 2010

6 48Monday, March 29, 2010

1

1A

1A

1A

Page 7

5

4

3

2

1

+1.5VSUS

M_B_DQ[63:0] 4

+0.75VSMVREF_SUSB

+SMDDR_VREF

MEMHOT_MB#

+1.5VSUS

+VREF_CA_B

R197 0_4R197 0_4

R126 *2.2K_4R126 *2.2K_4

R125 2.2K_4R125 2.2K_4

R253

R253

1K/F_4

1K/F_4

R255

R255

1K/F_4

1K/F_4

R193

R193

*2K/F_4

*2K/F_4

R192

R192

*2K/F_4

*2K/F_4

1 3

M_B_RST#4

+0.75VSMVREF_SUSB

+VREF_CA_B

+1.5VSUS

2

Q27

Q27

*MMBT3904

*MMBT3904

2.48A

+3V

MEMHOT_MB#

CPU_MEMHOT# 3,6,12

+1.5VSUS

CN19B

CN19B

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

77

NC1

122

NC2

125

NCTEST

198

EVENT#

30

RESET#

1

VREF_DQ

126

VREF_CA

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

PC2100 DDR3 SDRAM SO-DIMM

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

PC2100 DDR3 SDRAM SO-DIMM

25

26

31

32

37

38

43

DDR3_SO-DIMM_SOCKET_1.5V_Standard H=4

DDR3_SO-DIMM_SOCKET_1.5V_Standard H=4

(204P)

(204P)

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

GND

GND

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

203

204

205

206

+0.75V_DDR_VTT

M_B_A[15:0]4

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

D D

M_B_BANK[0..2]4

M_B_CS#04

M_B_CS#14

M_B_CLKP14

M_B_CLKN14

M_B_CLKP24

M_B_CLKN24

M_B_CKE04

M_B_CKE14

M_B_CAS#4

M_B_RAS#4

R151 10K_4R151 10K_4

+3V

R150 10K_4R150 10K_4

C C

B B

M_B_WE#4

PCLK_SMB6,13,27

PDAT_SMB6,13,27

M_B_ODT04

M_B_ODT14

M_B_DM[7:0]4

M_B_DQSP[7:0]4

M_B_DQSN[7:0]4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_BANK0

M_B_BANK1

M_B_BANK2

DIMM1_SA0

DIMM1_SA1

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

CN19A

CN19A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

PC2100 DDR3 SDRAM SO-DIMM

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

PC2100 DDR3 SDRAM SO-DIMM

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

DDR3_SO-DIMM_SOCKET_1.5V_Standard H=4

DDR3_SO-DIMM_SOCKET_1.5V_Standard H=4

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

(204P)

(204P)

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

M_B_DQ1

M_B_DQ0

M_B_DQ3

M_B_DQ2

M_B_DQ4

M_B_DQ5

M_B_DQ7

M_B_DQ6

M_B_DQ9

M_B_DQ13

M_B_DQ11

M_B_DQ10

M_B_DQ12

M_B_DQ8

M_B_DQ14

M_B_DQ15

M_B_DQ17

M_B_DQ16

M_B_DQ19

M_B_DQ18

M_B_DQ21

M_B_DQ20

M_B_DQ22

M_B_DQ23

M_B_DQ29

M_B_DQ25

M_B_DQ27

M_B_DQ26

M_B_DQ28

M_B_DQ24

M_B_DQ31

M_B_DQ30

M_B_DQ33

M_B_DQ32

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ39

M_B_DQ38

M_B_DQ44

M_B_DQ40

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ41

M_B_DQ43

M_B_DQ42

M_B_DQ53

M_B_DQ52

M_B_DQ55

M_B_DQ54

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ60

M_B_DQ61

M_B_DQ58

M_B_DQ59

M_B_DQ57

M_B_DQ56

M_B_DQ62

M_B_DQ63

+1.5VSUS

C443

C443

10u/6.3V_6

10u/6.3V_6

A A

Place these Caps near So-Dimm1.

C405

C405

10u/6.3V_6

10u/6.3V_6

5

C430

C430

10u/6.3V_6

10u/6.3V_6

C445

C445

10u/6.3V_6

10u/6.3V_6

C412

C412

10u/6.3V_6

10u/6.3V_6

+0.75V_DDR_VTT

C433

C433

10u/6.3V_6

10u/6.3V_6

C295

C295

1u/6.3V_4

1u/6.3V_4

C398

C398

0.1u/10V_4

0.1u/10V_4

C440

C440

*0.1u/10V_4

*0.1u/10V_4

C424

C424

*0.1u/10V_4

*0.1u/10V_4

C294

C294

1u/6.3V_4

1u/6.3V_4

C419

C419

0.1u/10V_4

0.1u/10V_4

C415

C415

*0.1u/10V_4

*0.1u/10V_4

C292

C292

10u/6.3V_6

10u/6.3V_6

+VREF_CA_B

4

C386

C386

0.1u/10V_4

0.1u/10V_4

+0.75VSMVREF_SUSB

C383

C383

2.2u/6.3V_6

2.2u/6.3V_6

C491

C491

0.1u/10V_4

0.1u/10V_4

C493

C493

2.2u/6.3V_6

2.2u/6.3V_6

+1.5VSUS3,4,5,6,15,29,38,41,43,44

+3V3,5,6,10,11,12,13,14,15,16,18,20,25,26,27,29,30,32,33,34,35,37,38,39,40,41,42,43,44

+0.75V_DDR_VTT4,6,41

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

+1.5VSUS

+3V

+0.75V_DDR_VTT

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

DDR3 DIMMB-STD

DDR3 DIMMB-STD

DDR3 DIMMB-STD

ZRA

ZRA

ZRA

7 48Monday, March 29, 2010

7 48Monday, March 29, 2010

7 48Monday, March 29, 2010

1

1A

1A

1A

Page 8

5

HT_CADOUTP0

HT_CADOUTN0

HT_CADOUTP1

HT_CADOUTN1

HT_CADOUTP2

HT_CADOUTN2

HT_CADOUTP3

HT_CADOUTN3

HT_CADOUTP4

HT_CADOUTN4

HT_CADOUTP5

HT_CADOUTN5

D D

C C

R186 301/F_4R186 301/F_4 R190 301/F_4R190 301/F_4

HT_CADOUTP6

HT_CADOUTN6

HT_CADOUTP7

HT_CADOUTN7

HT_CADOUTP8

HT_CADOUTN8

HT_CADOUTP9

HT_CADOUTN9

HT_CADOUTP10

HT_CADOUTN10

HT_CADOUTP11

HT_CADOUTN11

HT_CADOUTP12

HT_CADOUTN12

HT_CADOUTP13

HT_CADOUTN13

HT_CADOUTP14

HT_CADOUTN14

HT_CADOUTP15

HT_CADOUTN15

HT_CLKOUTP0

HT_CLKOUTN0

HT_CLKOUTP1

HT_CLKOUTN1

HT_CTLOUTP0

HT_CTLOUTN0

HT_CTLOUTP1

HT_CTLOUTN1

HT_RXCALP HT_TXCALP

HT_RXCALN

AC24

AC25

AB25

AB24

AA24

AA25

W21

W20

AB23

AA22

Y25

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

Y22

Y23

V21

V20

U20

U21

U19

U18

T22

T23

M22

M23

R21

R20

C23

A24

4

U28A

U28A

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS880/RX881

RS880/RX881

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

F21

G21

G20

H21

J20

J21

J18

K17

L19

J19

M19

L18

M21

P21

P18

M18

H24

H25

L21

L20

M24

M25

P19

R18

B24

B25

HT_CADINP0

HT_CADINN0

HT_CADINP1

HT_CADINN1

HT_CADINP2

HT_CADINN2

HT_CADINP3

HT_CADINN3

HT_CADINP4

HT_CADINN4

HT_CADINP5

HT_CADINN5

HT_CADINP6

HT_CADINN6

HT_CADINP7

HT_CADINN7

HT_CADINP8

HT_CADINN8

HT_CADINP9

HT_CADINN9

HT_CADINP10

HT_CADINN10

HT_CADINP11

HT_CADINN11

HT_CADINP12

HT_CADINN12

HT_CADINP13

HT_CADINN13

HT_CADINP14

HT_CADINN14

HT_CADINP15

HT_CADINN15

HT_CLKINP0

HT_CLKINN0

HT_CLKINP1

HT_CLKINN1

HT_CTLINP0

HT_CTLINN0

HT_CTLINP1

HT_CTLINN1

HT_TXCALN

3

HT_CADOUTP[15..0]

HT_CADOUTN[15..0]

HT_CLKOUTP[1..0]

HT_CLKOUTN[1..0]

HT_CTLOUTP[1..0]

HT_CTLOUTN[1..0]

HT_CADINP[15..0]

HT_CADINN[15..0]

HT_CLKINP[1..0]

HT_CLKINN[1..0]

HT_CTLINP[1..0]

HT_CTLINN[1..0]

2

HT_CADOUTP[15..0] 3

HT_CADOUTN[15..0] 3

HT_CLKOUTP[1..0] 3

HT_CLKOUTN[1..0] 3

HT_CTLOUTP[1..0] 3

HT_CTLOUTN[1..0] 3

HT_CADINP[15..0] 3

HT_CADINN[15..0] 3

HT_CLKINP[1..0] 3

HT_CLKINN[1..0] 3

HT_CTLINP[1..0] 3

HT_CTLINN[1..0] 3

1

signals RS880 RX880

HT_TXCALP

HT_TXCALN

HT_RXCALP

HT_RXCALN

Ra

301 ohm 1%

Rb

301 ohm 1%

Ra

1.21k ohm 1%

Rb

1.21k ohm 1%

RbRa

RES CHIP 1.21K 1/16W +-1%(0402)

P/N : CS21212FB18

This block is for UMA only , Discrete can remove all component

U28D

U28D

AB12

MEM_A0(NC)

AE16

MEM_A1(NC)

V11

MEM_A2(NC)

AE15

MEM_A3(NC)

AA12

+1.8V10,11,16,25,38,43,44

B B

A A

5

+1.1V3,9,10,11,15,39

+1.8V

+1.1V

4

AB16

AB14

AD14

AD13

AD15

AC16

AE13

AC14

Y14

AD16

AE17

AD17

W12

Y12

AD18

AB13

AB18

V14

V15

W14

AE12

AD12

RS880/RX881

RS880/RX881

3

MEM_A4(NC)

MEM_A5(NC)

MEM_A6(NC)

MEM_A7(NC)

MEM_A8(NC)

MEM_A9(NC)

MEM_A10(NC)

MEM_A11(NC)

MEM_A12(NC)

MEM_A13(NC)

MEM_BA0(NC)

MEM_BA1(NC)

MEM_BA2(NC)

MEM_RASb(NC)

MEM_CASb(NC)

MEM_WEb(NC)

MEM_CSb(NC)

MEM_CKE(NC)

MEM_ODT(NC)

MEM_CKP(NC)

MEM_CKN(NC)

MEM_COMPP(NC)

MEM_COMPN(NC)

PAR 4 OF 6

PAR 4 OF 6

MEM_DQ0/DVO_VSYNC(NC)

MEM_DQ1/DVO_HSYNC(NC)

MEM_DQ2/DVO_DE(NC)

MEM_DQ3/DVO_D0(NC)

MEM_DQ4(NC)

MEM_DQ5/DVO_D1(NC)

MEM_DQ6/DVO_D2(NC)

MEM_DQ7/DVO_D4(NC)

MEM_DQ8/DVO_D3(NC)

MEM_DQ9/DVO_D5(NC)

MEM_DQ10/DVO_D6(NC)

MEM_DQ11/DVO_D7(NC)

MEM_DQ12(NC)

MEM_DQ13/DVO_D9(NC)

MEM_DQ14/DVO_D10(NC)

MEM_DQ15/DVO_D11(NC)

MEM_DQS0P/DVO_IDCKP(NC)

MEM_DQS0N/DVO_IDCKN(NC)

MEM_DQS1P(NC)

MEM_DQS1N(NC)

MEM_DM0(NC)

MEM_DM1/DVO_D8(NC)

SBD_MEM/DVO_I/F

SBD_MEM/DVO_I/F

IOPLLVDD18(NC)

IOPLLVDD(NC)

IOPLLVSS(NC)

MEM_VREF(NC)

AA18

AA20

AA19

Y19

V17

AA17

AA15

Y15

AC20

AD19

AE22

AC18

AB20

AD22

AC22

AD21

Y17

W18

AD20

AE21

W17

AE19

AE23

AE24

AD23

AE18

IOPLLVDD18 - memory PLL

not applicable to RX881

15mA

+1.8V

26mA

+1.1V

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

RS880M-HT LINK I/F 1/4

RS880M-HT LINK I/F 1/4

RS880M-HT LINK I/F 1/4

ZRA

ZRA

ZRA

8 48Monday, March 29, 2010

8 48Monday, March 29, 2010

8 48Monday, March 29, 2010

1

1A

1A

1A

Page 9

5

4

3

2

1

U28B

PEG_RXP15

PEG_RXN15

PEG_RXP14

PEG_RXN14

PEG_RXP13

D D

PCIE_RX1+26

C C

PCIE_RX1-26

PCIE_RXP227

PCIE_RXN227

A_RXP012

A_RXN012

A_RXP112

A_RXN112

A_RXP212

A_RXN212

A_RXP312

A_RXN312

PEG_RXN13

PEG_RXP12

PEG_RXN12

PEG_RXP11

PEG_RXN11

PEG_RXP10

PEG_RXN10

PEG_RXP9

PEG_RXN9

PEG_RXP8

PEG_RXN8

PEG_RXP7

PEG_RXN7

PEG_RXP6

PEG_RXN6

PEG_RXP5

PEG_RXN5

PEG_RXP4

PEG_RXN4

PEG_RXP3

PEG_RXN3

PEG_RXP2

PEG_RXN2

PEG_RXP1

PEG_RXN1

PEG_RXP0

PEG_RXN0

U28B

D4

C4

A3

B3

C2

C1

E5

F5

G5

G6

H5

H6

J6

J5

J7

J8

L5

L6

M8

L8

P7

M7

P5

M5

R8

P8

R6

R5

P4

P3

T4

T3

AE3

AD4

AE2

AD3

AD1

AD2

V5

W6

U5

U6

U8

U7

AA8

Y8

AA7

Y7

AA5

AA6

W5

Y5

RS880/RX881

RS880/RX881

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

GPP_RX4P

GPP_RX4N

GPP_RX5P

GPP_RX5N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

PART 2 OF 6

PART 2 OF 6

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

PCE_CALRP(PCE_BCALRP)

PCE_CALRN(PCE_BCALRN)

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

PCIE I/F GFX

PCIE I/F GFX

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

A5

B5

A4

B4

C3

B2

D1

D2

E2

E1

F4

F3

F1

F2

H4

H3

H1

H2

J2

J1

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

AC1

AC2

AB4

AB3

AA2

AA1

Y1

Y2

Y4

Y3

V1

V2

AD7

AE7

AE6

AD6

AB6

AC6

AD5

AE5

AC8

AB8

PEG_TXP15_C

PEG_TXN15_C

PEG_TXP14_C

PEG_TXN14_C

PEG_TXP13_C

PEG_TXN13_C

PEG_TXP12_C

PEG_TXN12_C

PEG_TXP11_C

PEG_TXN11_C

PEG_TXP10_C

PEG_TXN10_C

PEG_TXP9_C

PEG_TXN9_C

PEG_TXP8_C

PEG_TXN8_C

PEG_TXP7_C

PEG_TXN7_C

PEG_TXP6_C

PEG_TXN6_C

PEG_TXP5_C

PEG_TXN5_C

PEG_TXP4_C

PEG_TXN4_C

PEG_TXP3_C

PEG_TXN3_C

PEG_TXP2_C

PEG_TXN2_C

PEG_TXP1_C

PEG_TXN1_C

PEG_TXP0_C

PEG_TXN0_C

PCIE_TXP0_C

PCIE_TXN0_C

PCIE_TXP2_C

PCIE_TXN2_C

A_TXP0_C

A_TXN0_C

A_TXP1_C

A_TXN1_C

A_TXP2_C

A_TXN2_C

A_TXP3_C

A_TXN3_C

NB_PCIECALRP

NB_PCIECALRN

C743 SW@0.1u/10V_4C743 SW@0.1u/10V_4

C745 SW@0.1u/10V_4C745 SW@0.1u/10V_4

C737 SW@0.1u/10V_4C737 SW@0.1u/10V_4

C740 SW@0.1u/10V_4C740 SW@0.1u/10V_4

C732 SW@0.1u/10V_4C732 SW@0.1u/10V_4

C735 SW@0.1u/10V_4C735 SW@0.1u/10V_4

C714 SW@0.1u/10V_4C714 SW@0.1u/10V_4

C713 SW@0.1u/10V_4C713 SW@0.1u/10V_4

C716 SW@0.1u/10V_4C716 SW@0.1u/10V_4

C715 SW@0.1u/10V_4C715 SW@0.1u/10V_4