5

4

3

2

1

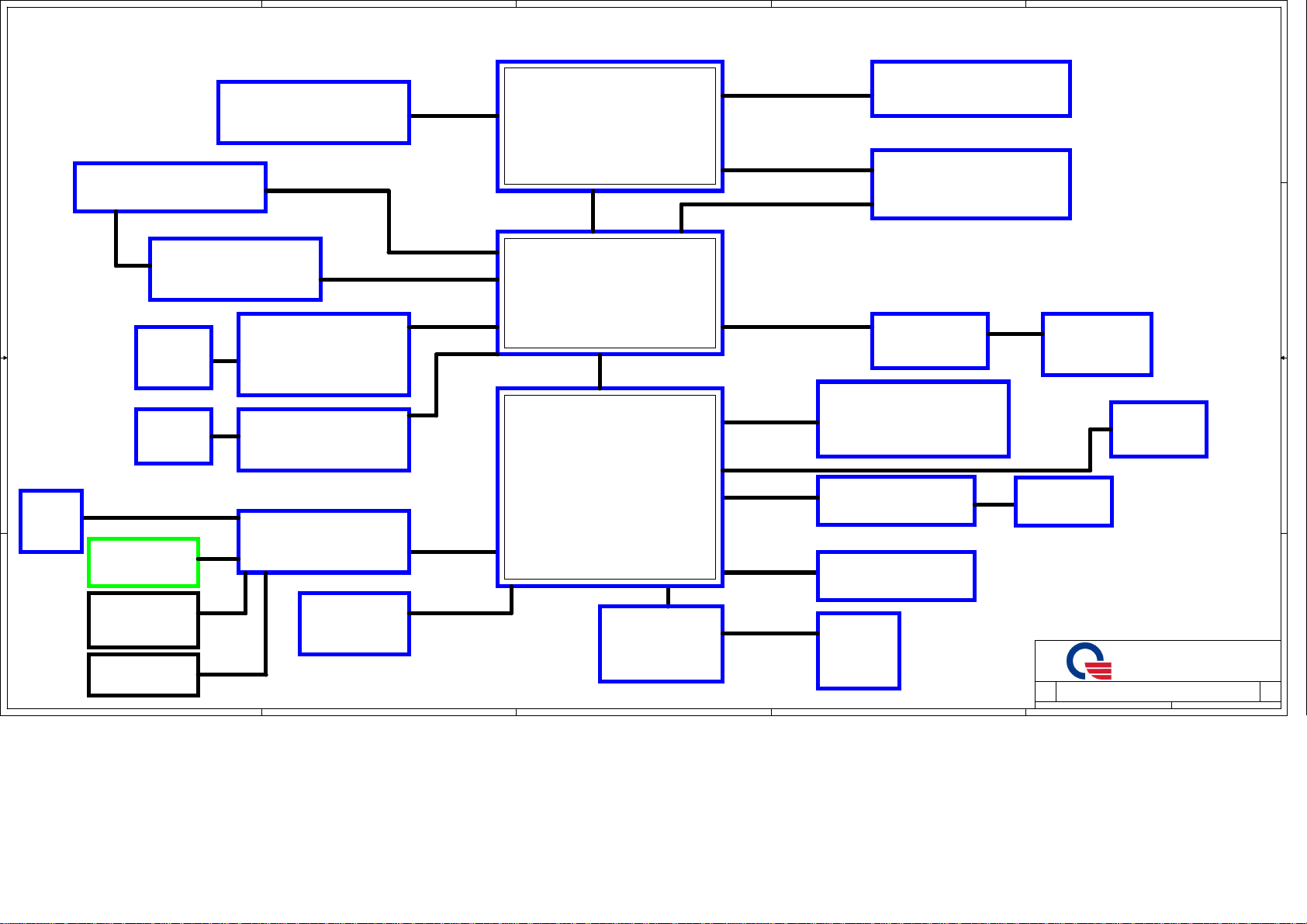

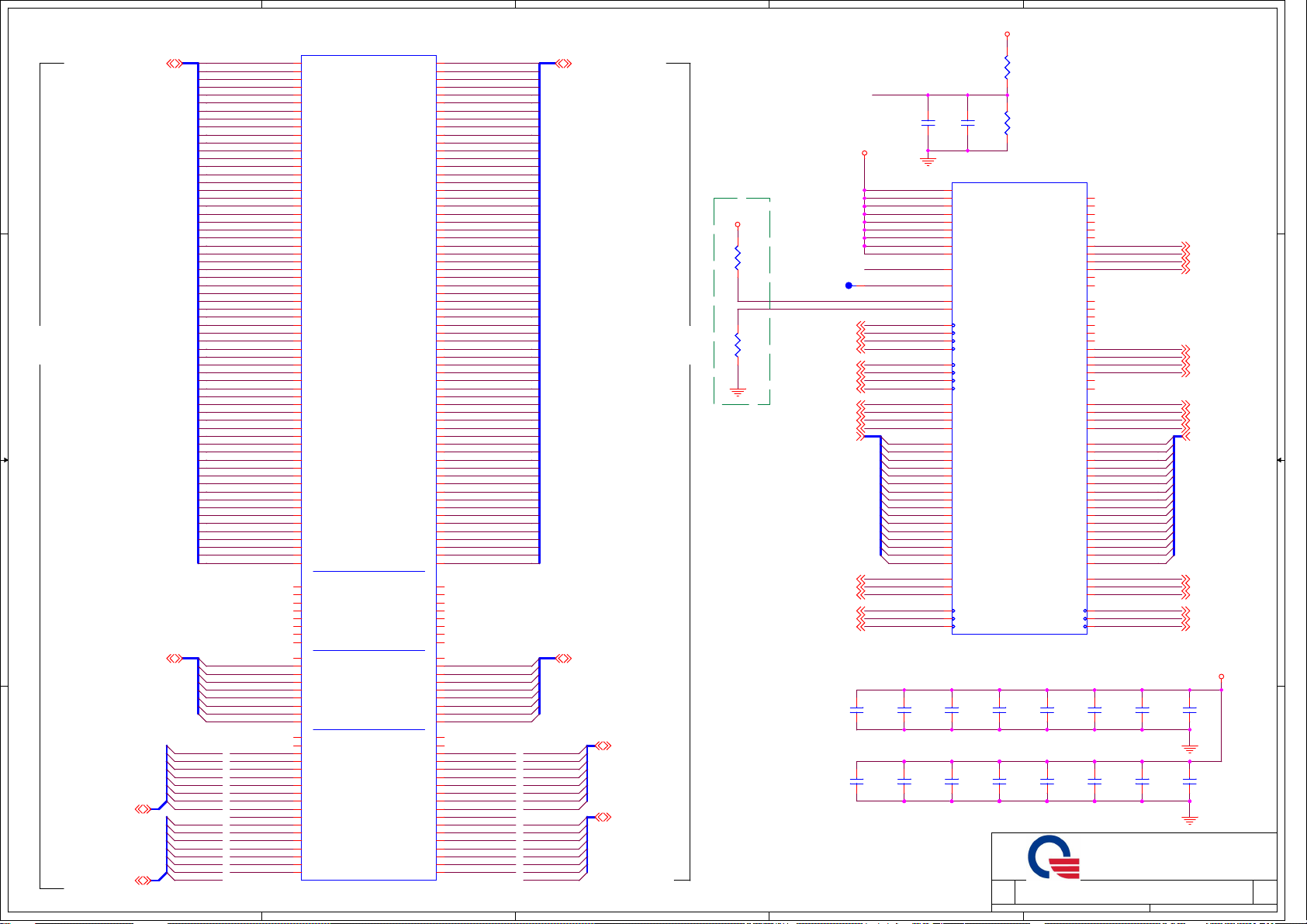

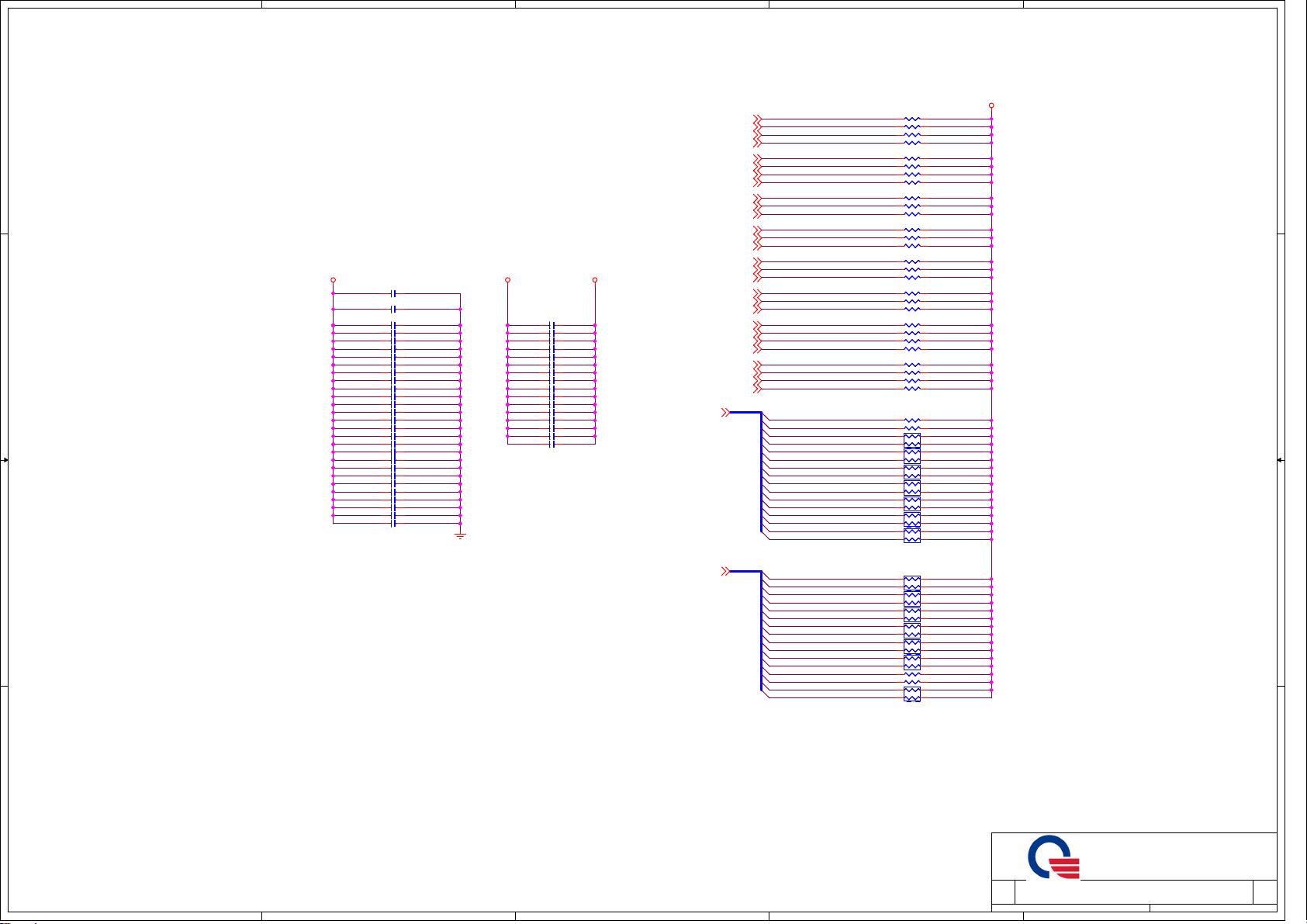

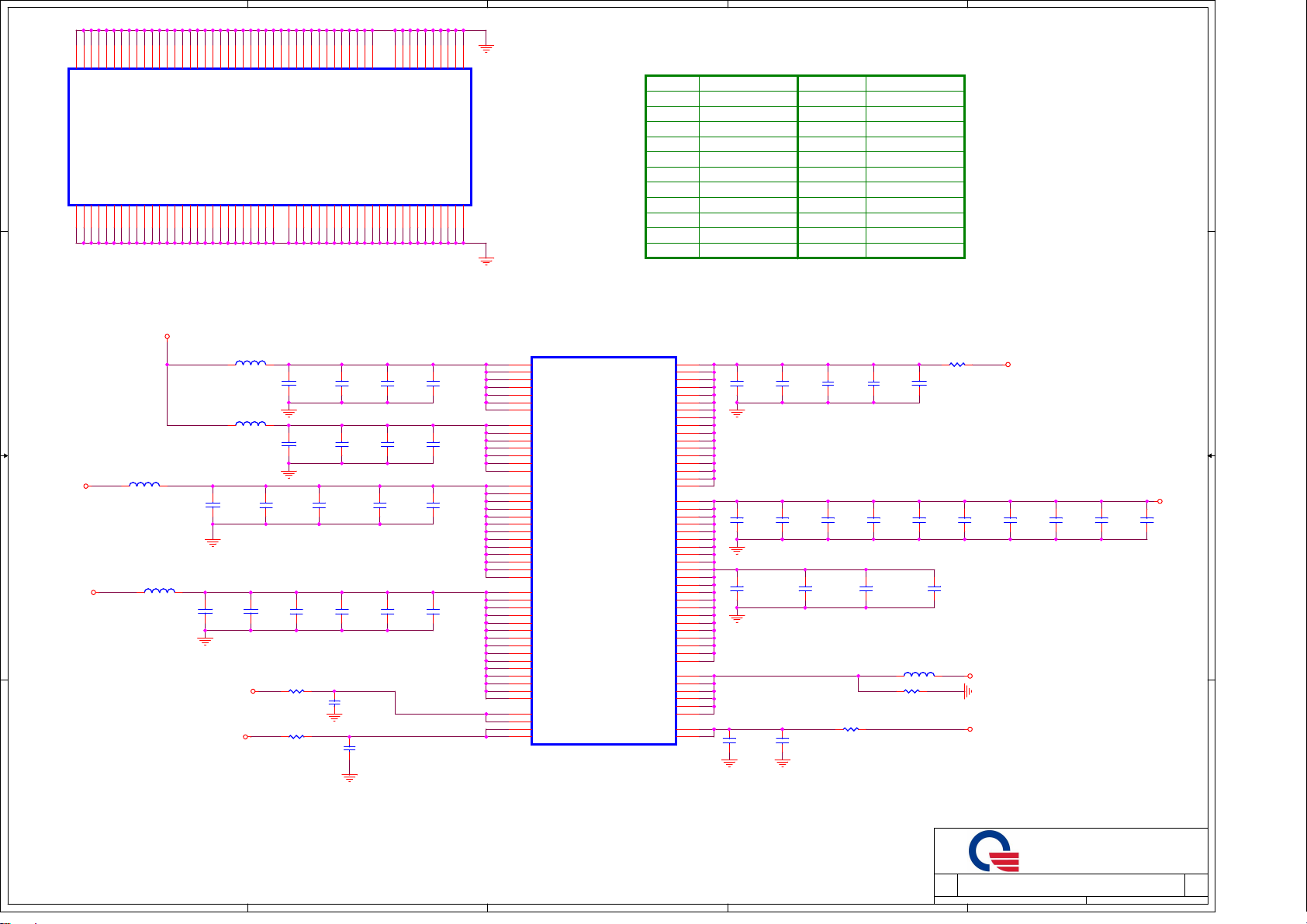

Amazon LCD PC Block Diagram

D D

DDRII X2

page:8

CHA/B

18.5" panel

page:19

AMD AM2

uPGA940

VCORE:+1.196 ~ +0.748

VCCP:+1.1V

VCCA:+1.8V or +1.5V

page:4-7

+/- CPU_CLK

+/- HCLK

HT-LINK

VID[0:6]

LVDS

C C

MXM

MODULE

(MXM3.0)

page:20

10/100

RJ-45

page:25

Ethernet

RTL8103EL

page:24

LVDS

PCIEX16

PCI-E

PCI-E

RS780MN

HOST

LVDS, DMI, DDR CLK

POWER

GND

page:10-13

A_LINK

PCI-E/USB

SATA

B B

6 in 1

page:27

SPK

page:29

LINE OUT

page:23

A A

H/P OUT

page:29

Int. Mic

page:29

5

Card Reader

JR385

page:27

HDA CODEC

ALC269

page:29

USB X2

side USB

page:26

RTC, AC97, SATA, IDE, LPC, CPU

PCI-E, USB, DMI, PCI

SMB, GPIO, CLK

Azalia

USB

4

SB700

page:14-18

ITE8512

page:32

LPC BUS

EC

3

USB

USB

Camera Conn.

USB PORT X4

Rear

SPI

Flash

page:32

CPU VCORE

page:34

Clock Gengerator

page:3

MINI CARD

page:30

HDD, ODD

page:28

page:22

page:26

2

WLAN

Module

Bluetooth

USB

Camera

Module

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

RESERVE

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZN1

ZN1

ZN1

1

1

B

B

1 41Friday, May 08, 2009

1 41Friday, May 08, 2009

1 41Friday, May 08, 2009

B

5

4

3

2

1

2

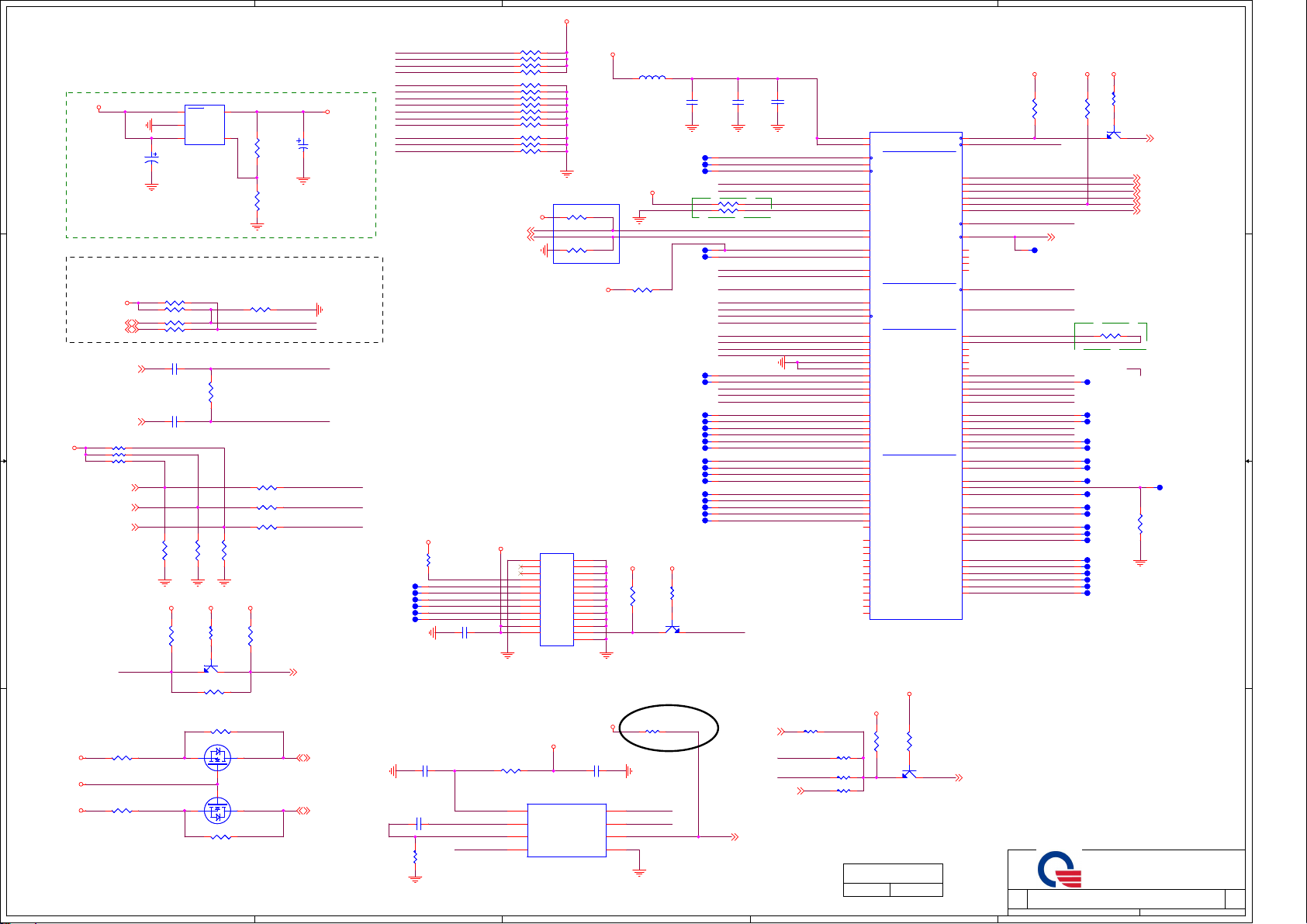

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : VCC

LAYER 3 : IN1

D D

LAYER 4 : IN2

LAYER 5 : GND

LAYER 6 : BOT

C C

B B

Power S0~S2

15VPCU

5VPCU

3VPCU

RVCC3

5VSUS

1.8VSUS

VCC5

VCC3

VCC1.8 1.8V

VCC1.5

VCC1.2 1.2V

CPU_VDDA

NB_CORE

SMDDR_VTERM

CPU_CORE

PS_ON, SLP_S3#, SLP_S5#

Voltage

15V

5V

3V

3V

5V

1.8V SUSON

5V

3V

1.5V

2.5V

1.2V

0.9V

By CPU

+5VALW

RSMRST#

+12V,5V,3.3V

VDRM_PWRGD

VCC_NB_PWRGD

VRM_PWRGD

NB_PWRGD

SB_PWRGD

CPU_PWRGD

PCI_RST#

CPU_RST#

Voltage Rails

V V V V

V

V V V

V

V V

V

V

V

V

V

V

V

V

V

BONEFISH POWER UP SEQUENCE

T1>= 70 ms

V V V

V V

VV

VV

T2

1ms < T2 < 10ms

1ms < T3 < 5ms

S4 S5

T3T1

Ctl SignalS3

VIN

V

VIN

RVCC_ON

V

V

RVCC_ONRVCC1.2 1.2V V

SUSD

MAIND

MAIND

MAIND

MAINON

MAINON

VCC3

VRON

SUSON

VR_ON

From Power Button

From PWM

From EC

From EC

From EC

From SB

From SB to EC

From EC

From AC IN

5VPCU 3VPCU

SYS_HWPG(PCU)

NBSWON#

RVCC_ON

RVCC5

RVCC3

RVCC1.2

RSMRST#

DNBSWON#

PCIE_WAKE#

SUSB#,SUSC#

SUSON

Power On Sequence

>10ms

>100ms

SUSON

3VSUS 1.8VSUS SMDDR_VREF SMDDR_VTERM

From PWM

From EC

HWPG_1.8V (SUS)

MAINON

MAINON

VCC5 VCC3 VCC2.5 VCC1.8 VCC1.5 NB_CORE 1.1V_NB

From PWM

From EC

HWPG_1.5V,HWPG_2.5V,GFXPG(MAIN) HWPG_1.2_NB

VRON

CPU_CORE0, CPU_CORE1, CPU VDDNB_CORE, VCC1.2

From PWM

VRM_PWRGD (CPU)

HWPG

From EC

From SB

From SB

From SB

From SB

ECPWROK

SB_PWRGD

NB_PWRGD

CPU_PWRGD/LDT_PG

PLTRST# PCIRST#

CPU_LDT_RST#

CPU_LDT_STOP#

0ns~30ns

99ms~108ms

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SYSTEM INFORMATION

SYSTEM INFORMATION

SYSTEM INFORMATION

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

ZN1

ZN1

ZN1

2 41Friday, May 08, 2009

2 41Friday, May 08, 2009

1

2 41Friday, May 08, 2009

B

B

B

5

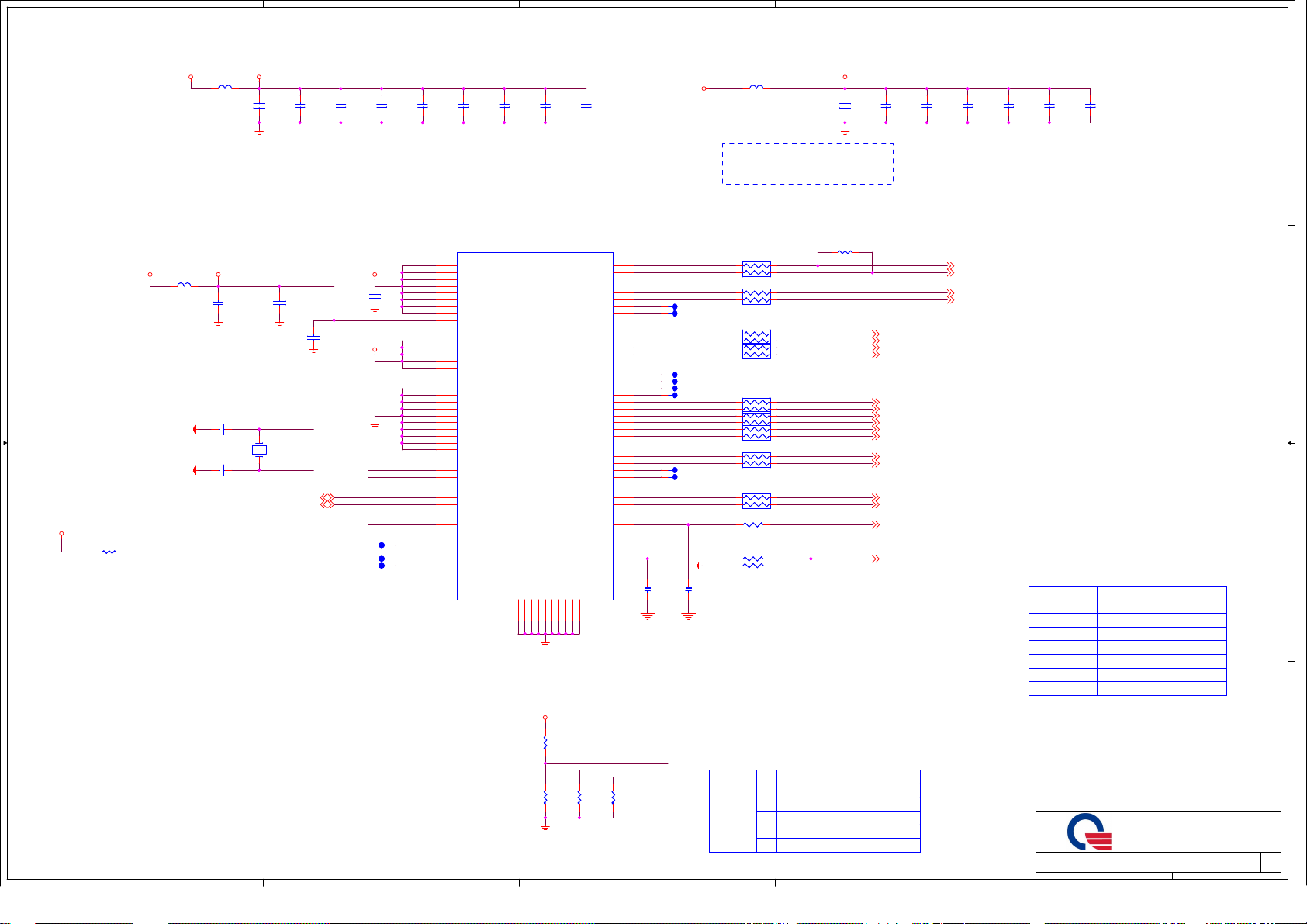

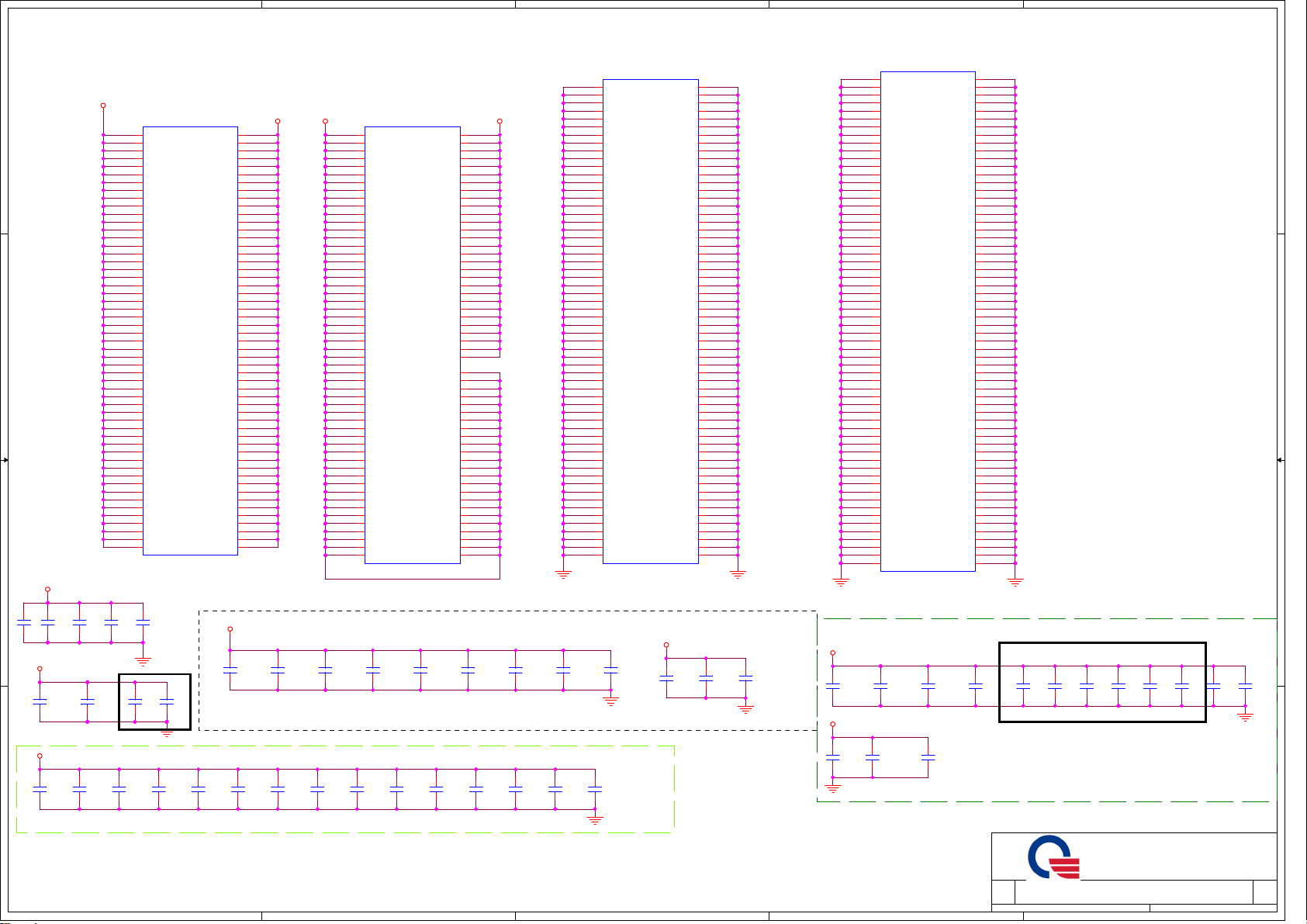

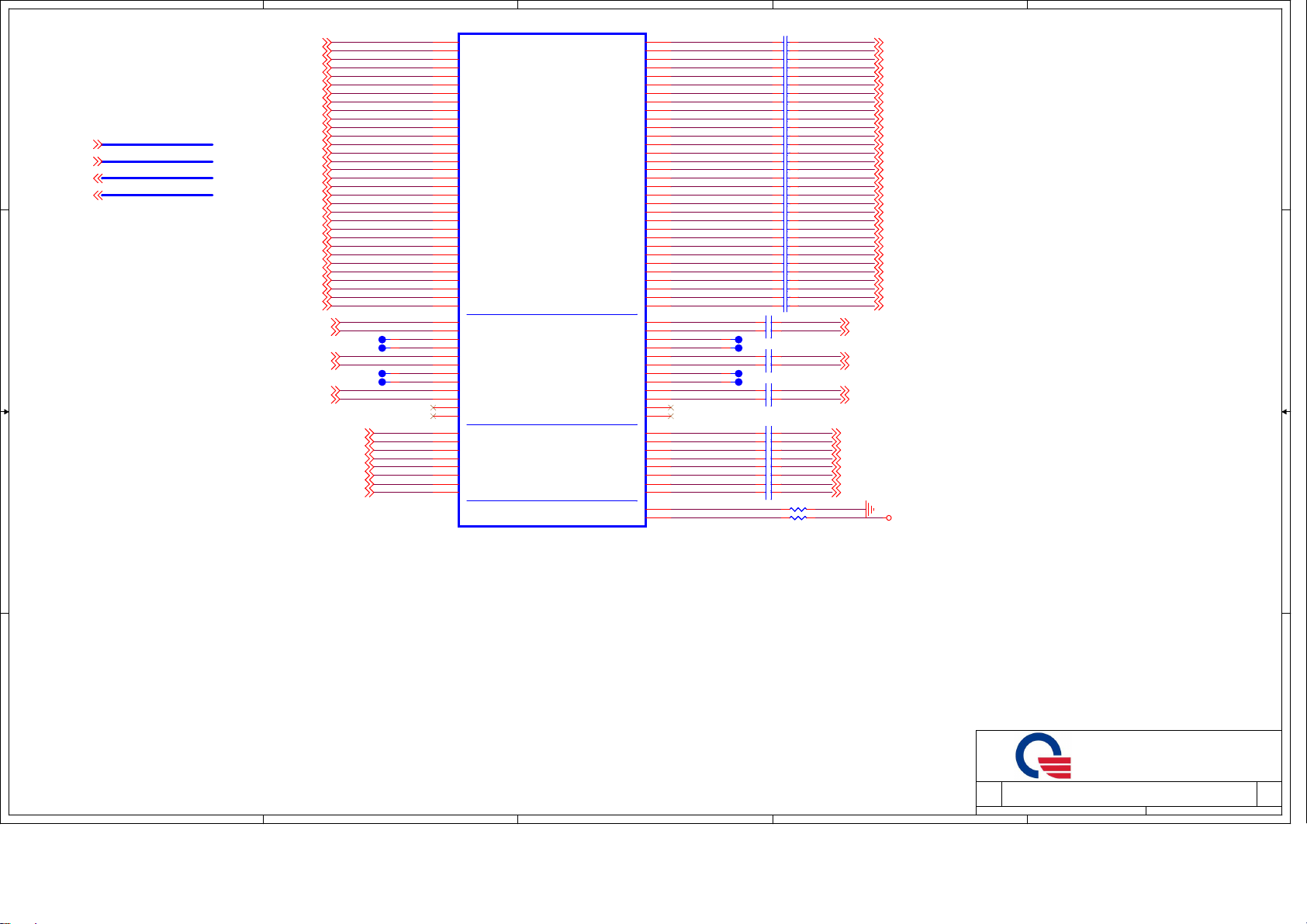

CLK_GEN_SLG8SP628

4

3

2

1

VCC3 CLK_VDD CLK_VDDIO

L26

L26

BK1608HS600

BK1608HS600

22U/6.3V_8

D D

22U/6.3V_8

C252

C252

C260

C260

0.1u/10V_4

0.1u/10V_4

C258

C258

0.1u/10V_4

0.1u/10V_4

C270

C270

0.1u/10V_4

0.1u/10V_4

C275

C275

0.1u/10V_4

0.1u/10V_4

C269

C269

0.1u/10V_4

0.1u/10V_4

C268

C268

0.1u/10V_4

0.1u/10V_4

C276

C276

0.1u/10V_4

0.1u/10V_4

C273

C273

0.1u/10V_4

0.1u/10V_4

VCC1.2

ICS9LPRS480 P/N : ALPRS480000

SLG8SP628

RTM880N-796

U12

U12

4

CLK_VDD_USB

L27

L27

BK1608HS600

BK1608HS600

C C

CLK_VDD

B B

R315 8.2K_4R315 8.2K_4

CLK_PD#

C263

C263

0.1u/10V_4

0.1u/10V_4

C266 33PC266 33P

C264 33PC264 33P

C255

C255

2.2U_0805

2.2U_0805

21

Y2

Y2

14.318MHZ/20P

14.318MHZ/20P

C256

C256

10uF_0805

10uF_0805

CG_XIN

CG_XOUT

PCLK_SMB8,15,19,30

PDAT_SMB8,15,19,30

CLK_VDDVCC3

C250

C250

22U/6.3V_8

22U/6.3V_8

CLK_VDDIO

1 2

CG_XIN

CG_XOUT

CLK_PD#

T80T80

CLKREQ2#

T85T85

T84T84

VDDDOT

16

VDDSRC

26

VDDATIG

35

VDDSB_SRC

40

VDDSATA

48

VDDCPU

55

VDDHTT

56

VDDREF

63

VDD48

11

VDDSRC_IO0

17

VDDSRC_IO1

25

VDDATIG_IO

34

VDDSB_SRC_IO

47

VDDCPU_IO

1

GND48

7

GNDDOT

10

GNDSRC0

18

GNDSRC1

24

GNDATIG

33

GNDSB_SRC

43

GNDSATA

46

GNDCPU

52

GNDHTT

60

GNDREF

61

X1

62

X2

2

SMBCLK

3

SMBDAT

51

PD#

23

CLKREQ0#

45

CLKREQ1#

44

CLKREQ2#

39

CLKREQ3#

38

CLKREQ4#

SLG8SP628

SLG8SP628

P/N : AL8SP628000

P/N : AL000880000

CPUK8_0T

CPUK8_0C

ATIG0T

ATIG0C

ATIG1T

ATIG1C

SB_SRC0T

SB_SRC0C

SB_SRC1T

SB_SRC1C

SRC0T

SRC0C

SRC1T

SRC1C

SRC2T

QFN64

QFN64

TGND065TGND166TGND267TGND368TGND469TGND570TGND671TGND772TGND873TGND9

CLK_VDD

SRC2C

SRC3T

SRC3C

SRC4T

SRC4C

SRC6T/SATAT

SRC6C/SATAC

SRC7T/27M_SS

SRC7C/27M_NS

HTT0T/66M

HTT0C/66M

48MHz_0

REF0/SEL_HTT66

REF1/SEL_SATA

REF2/SEL_27

74

CPUCLKP_R

50

CPUCLKN_R

49

NBGFX_CLKP_R NBGFX_CLKP

30

NBGFX_CLKN_R NBGFX_CLKN

29

28

27

37

36

32

31

22

21

20

19

15

14

13

12

9

8

42

41

6

5

54

53

64

59

58

57

T83T83

T82T82

SBLINK_CLKP_R SBLINK_CLKPSBLINK_CLKP

SBLINK_CLKN_R SBLINK_CLKNSBLINK_CLKN

SBSRC_CLKP_R

SBSRC_CLKN_R

T81T81

T77T77

T79T79

T78T78

CLK_PCIE_MXM_R

CLK_PCIE_MXM#_R

CLK_PCIE_LAN_R CLK_PCIE_LANCLK_PCIE_LAN

CLK_PCIE_JM385_R CLK_PCIE_JM385CLK_PCIE_JM385

CLK_PCIE_JM385#_R CLK_PCIE_JM385#CLK_PCIE_JM385#

T76T76

T75T75

NBHT_REFCLKN_R NBHT_REFCLKNNBHT_REFCLKN

CLK_48M_USB_R

SEL_HTT66

SEL_SATA

C265

C265

C259

C259

*10p/50V_4

*10p/50V_4

*10p/50V_4

*10p/50V_4

L28

L28

BK1608HS600

BK1608HS600

Clock chip has internal serial terminations

for differencial pairs, external resistors are

reserved for debug purpose.

Place within 0.5"

of CLKGEN

RP7 0X2RP7 0X2

RP4 0X2RP4 0X2

RP9 0X2RP9 0X2

RP6

RP6

RP3 0X2RP3 0X2

RP2 0X2RP2 0X2

RP1 0X2RP1 0X2

RP8 0X2RP8 0X2

RP5 0X2RP5 0X2

R177 33_4R177 33_4

R180 158/F_4R180 158/F_4

R181 90.9/F_4R181 90.9/F_4

2

1

4

3

2

1

4

3

2

1

4

3

1

3

1

3

1

3

1

3

1

3

1

3

0X2

0X2

SBSRC_CLKPSBSRC_CLKP

2

SBSRC_CLKNSBSRC_CLKN

4

CLK_PCIE_WLANCLK_PCIE_WLANCLK_PCIE_MINI_R

2

CLK_PCIE_WLAN#CLK_PCIE_WLAN#CLK_PCIE_MINI#_R

4

CLK_MXM

2

CLK_MXM#

4

2

CLK_PCIE_LAN#CLK_PCIE_LAN#CLK_PCIE_LAN#_R

4

2

4

NBHT_REFCLKPNBHT_REFCLKPNBHT_REFCLKP_R

2

4

CLK_48M_USB

Ra

EXT_NB_OSCSEL_27

Rb

R182

R182

*261/F_4

*261/F_4

C272

C272

22U/6.3V_8

22U/6.3V_8

C274

C274

0.1u/10V_4

0.1u/10V_4

CPUCLKP

CPUCLKN

SBLINK_CLKP 12

SBLINK_CLKN 12

SBSRC_CLKP 14

SBSRC_CLKN 14

CLK_PCIE_WLAN 30

CLK_PCIE_WLAN# 30

CLK_MXM 20

CLK_MXM# 20

CLK_PCIE_LAN 24

CLK_PCIE_LAN# 24

CLK_PCIE_JM385 27

CLK_PCIE_JM385# 27

NBHT_REFCLKP 12

NBHT_REFCLKN 12

CLK_48M_USB 15

EXT_NB_OSC 12

C262

C262

0.1u/10V_4

0.1u/10V_4

CPUCLKP 6

CPUCLKN 6

NBGFX_CLKP 12

NBGFX_CLKN 12

C278

C278

C257

C257

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

To CPU

To NB

To NB

100 Mhz

To SB

To Mini PCIE Slot(WLAN)

To MXM MODULE

To LAN Controller

To 6 in 1 Controller

To NB HT BUS

To SB USB

To NB

C277

C277

C267

C267

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

200 Mhz

RS780 for VGA

100 Mhz

100 Mhz

48 Mhz

CLOCK INPUT TABLE

CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK

GPP_REFCLK

GPPSB_REFCLK

RS780

100M DIFF

100M DIFF

14M SE (1.1V)

vref

100M DIFF(IN/OUT)*

NC or 100M DIFF OUTPUT

100M DIFF

R327

R327

*8.2K_4

*8.2K_4

A A

R326

R326

8.2K_4

8.2K_4

5

4

R328

R328

8.2K_4

8.2K_4

SEL_SATA

SEL_HTT66

SEL_27

R316

R316

8.2K_4

8.2K_4

66 MHz 3.3V single ended HTT clock

SEL_HTT66

SEL_SATA

SEL_27

3

1

*0 100 MHz differential HTT clock

100 MHz non-spreading differential SRC clock

1*

0

100 MHz spreading differential SRC clock

27MHz and 27M SS outputs

1

0*

100 MHz SRC clock

* default

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Clock Generator

Clock Generator

Clock Generator

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

ZN1

ZN1

ZN1

1A

1A

3 41Friday, May 08, 2009

3 41Friday, May 08, 2009

3 41Friday, May 08, 2009

1

1A

5

4

3

2

1

4

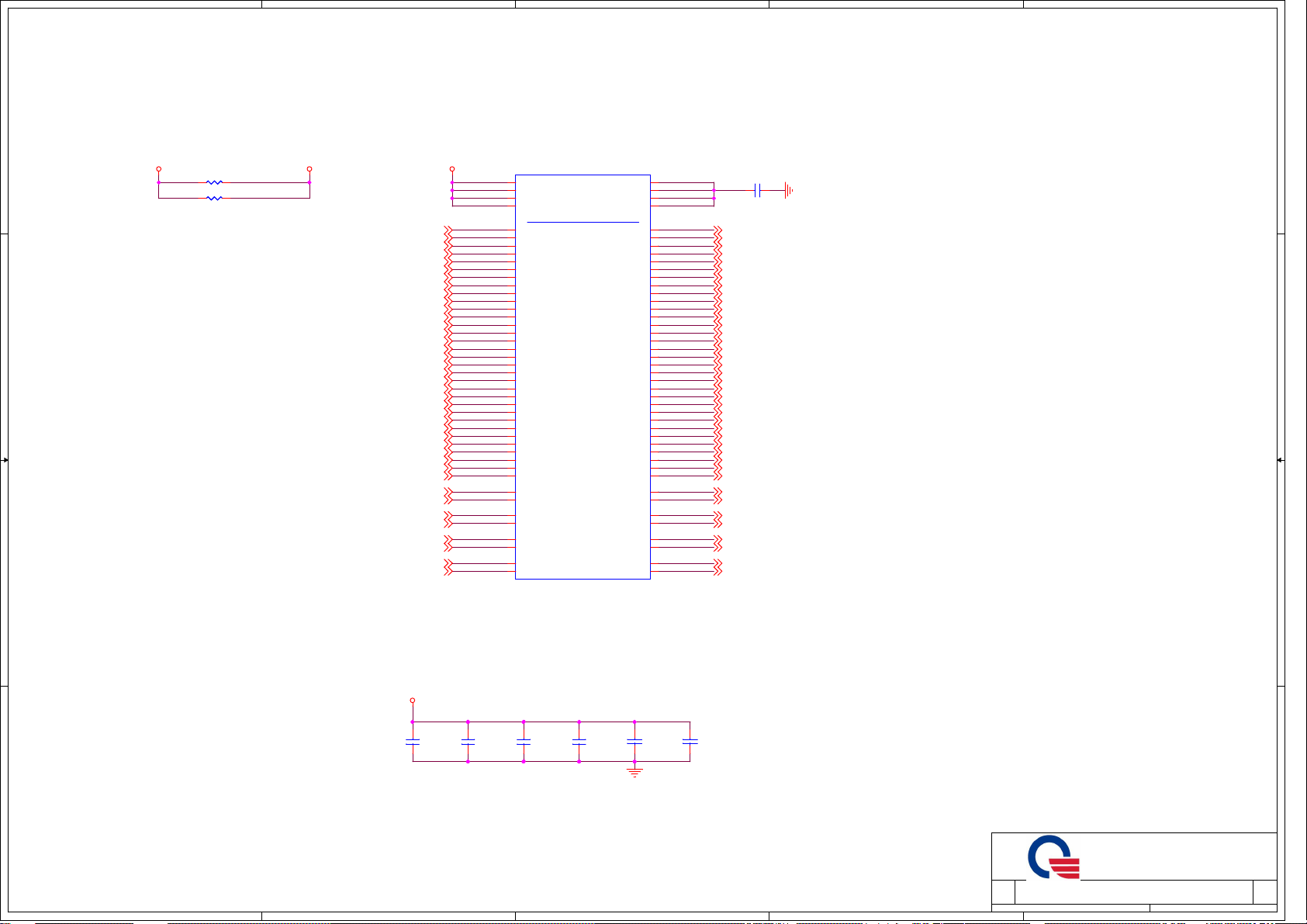

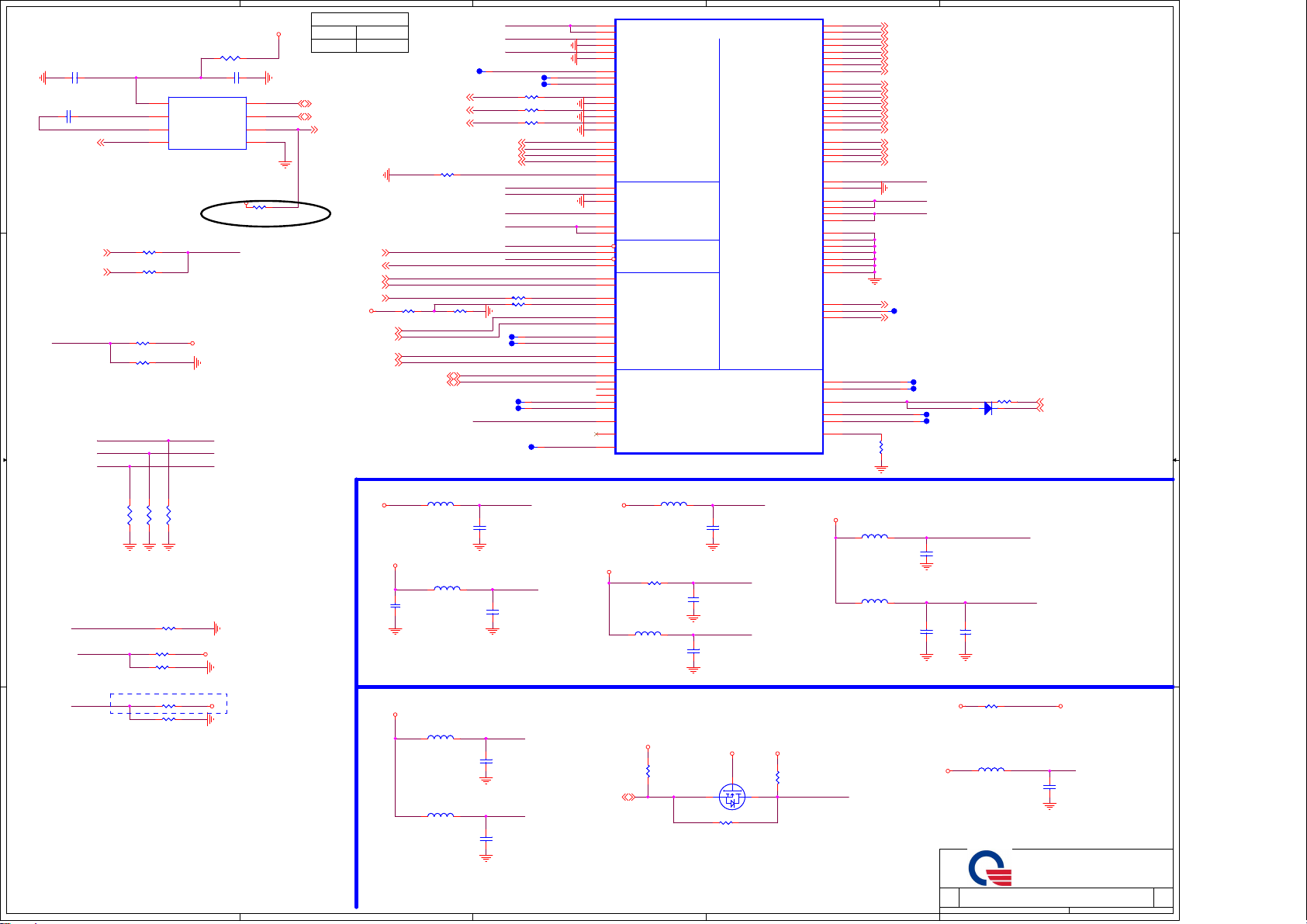

CPU HyperTransport Interface

D D

VCC1.2 VLDT_RUN

R98 *short0805R98 *short0805

R100 *short0805R100 *short0805

C C

B B

VDDLDTRUNCPU is connected to the VDD_LDT_RUN power

supply through the package or on the die. It is only connected

on the board to decoupling near the CPU package.

VLDT_RUN

HT_CADIN15_P10

HT_CADIN15_N10

HT_CADIN14_P10

HT_CADIN14_N10

HT_CADIN13_P10

HT_CADIN13_N10

HT_CADIN12_P10

HT_CADIN12_N10

HT_CADIN11_P10

HT_CADIN11_N10

HT_CADIN10_P10

HT_CADIN10_N10

HT_CADIN9_P10

HT_CADIN9_N10

HT_CADIN8_P10

HT_CADIN8_N10

HT_CADIN7_P10

HT_CADIN7_N10

HT_CADIN6_P10

HT_CADIN6_N10

HT_CADIN5_P10

HT_CADIN5_N10

HT_CADIN4_P10

HT_CADIN4_N10

HT_CADIN3_P10

HT_CADIN3_N10

HT_CADIN2_P10

HT_CADIN2_N10

HT_CADIN1_P10

HT_CADIN1_N10

HT_CADIN0_P10

HT_CADIN0_N10

HT_CLKIN1_P10

HT_CLKIN1_N10

HT_CLKIN0_P10

HT_CLKIN0_N10

HT_CTLIN1_P10

HT_CTLIN1_N10

HT_CTLIN0_P10

HT_CTLIN0_N10

AJ4

AJ3

AJ2

AJ1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

N6

P6

N3

N2

V4

V5

U1

V1

U9A

U9A

VLDT_06

VLDT_05

VLDT_02

VLDT_01

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

Athlon 64 M2

Processor Socket

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

HT LINK

HT LINK

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

VLDT_08

VLDT_07

VLDT_04

VLDT_03

H6

H5

H2

H1

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

C149

C149

4.7U_0603

4.7U_0603

HT_CADOUT15_P 10

HT_CADOUT15_N 10

HT_CADOUT14_P 10

HT_CADOUT14_N 10

HT_CADOUT13_P 10

HT_CADOUT13_N 10

HT_CADOUT12_P 10

HT_CADOUT12_N 10

HT_CADOUT11_P 10

HT_CADOUT11_N 10

HT_CADOUT10_P 10

HT_CADOUT10_N 10

HT_CADOUT9_P 10

HT_CADOUT9_N 10

HT_CADOUT8_P 10

HT_CADOUT8_N 10

HT_CADOUT7_P 10

HT_CADOUT7_N 10

HT_CADOUT6_P 10

HT_CADOUT6_N 10

HT_CADOUT5_P 10

HT_CADOUT5_N 10

HT_CADOUT4_P 10

HT_CADOUT4_N 10

HT_CADOUT3_P 10

HT_CADOUT3_N 10

HT_CADOUT2_P 10

HT_CADOUT2_N 10

HT_CADOUT1_P 10

HT_CADOUT1_N 10

HT_CADOUT0_P 10

HT_CADOUT0_N 10

HT_CLKOUT1_P 10

HT_CLKOUT1_N 10

HT_CLKOUT0_P 10

HT_CLKOUT0_N 10

HT_CTLOUT1_P 10

HT_CTLOUT1_N 10

HT_CTLOUT0_P 10

HT_CTLOUT0_N 10

VLDT_RUN

C147

C147

180P

180P

12

C150

C150

180P

180P

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

AMD AM2 HT I/F

AMD AM2 HT I/F

AMD AM2 HT I/F

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

ZN1

ZN1

ZN1

1A

1A

1A

4 41Friday, May 08, 2009

4 41Friday, May 08, 2009

4 41Friday, May 08, 2009

1

C146

C146

4.7U_0603

4.7U_0603

A A

5

4

C145

C145

4.7U_0603

4.7U_0603

C151

C151

0.22U

0.22U

C148

C148

0.22U

0.22U

12

3

5

U9C

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_DM7

M_B_DM6

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

M_B_DQS7

M_B_DQS#7

M_B_DQS6

M_B_DQS#6

M_B_DQS5

M_B_DQS#5

M_B_DQS4

M_B_DQS#4

M_B_DQS3

M_B_DQS#3

M_B_DQS2

M_B_DQS#2

M_B_DQS1

M_B_DQS#1

M_B_DQS0

M_B_DQS#0

D D

C C

B B

A A

M_B_DQS[0..7]8

M_B_DQS#[0..7]8

5

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

C15

A15

A13

D13

G30

G29

H31

G31

AJ14

AH17

AJ23

AK29

C30

A23

B17

B13

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

F29

F31

F13

K29

K31

L29

L28

J29

J31

J30

U9C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_DM8

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H8

MB_DQS_L8

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

Athlon 64 M2

Processor Socket

DDRII: DATA

DDRII: DATA

4

3

Processor DDR2 Memory Interface

M_A_DQ63

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_DM8

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H8

MA_DQS_L8

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

4

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

K25

J26

G28

G27

L24

K27

H29

H27

J25

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

J28

J27

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

F19

F15

G15

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_A_DM7

M_A_DM6

M_A_DM5M_B_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

To SODIMM socket A (near)To SODIMM socket B (Far)

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQ[0..63] 8M_B_DQ[0..63]8

M_A_DM[0..7] 8M_B_DM[0..7]8

M_A_DQS[0..7] 8

M_A_DQS#[0..7] 8

3

PLACE THEM CLOSE TO

CPU WITHIN 1"

1.8VSUS

R358

R358

39.2F

39.2F

1 2

R363

R363

39.2F

39.2F

1 2

M_A_CS#38,9

M_A_CS#28,9

M_A_CS#18,9

M_A_CS#08,9

M_B_CS#38,9

M_B_CS#28,9

M_B_CS#18,9

M_B_CS#08,9

M_CKE38,9

M_CKE28,9

M_CKE18,9

M_CKE08,9

M_A_A[0..15]8,9

M_A_BS#28,9

M_A_BS#18,9

M_A_BS#08,9

M_A_RAS#8,9

M_A_CAS#8,9

M_A_WE#8,9

0.9V

SMDDR_VTERM

T122T122

M_ZN

M_ZP

C499

C499

4.7U_0603

4.7U_0603

C186

C186

1000P

1000P

2

0.9V

CPU_M_VREF

CPU_M_VREF

VTT_SENSE

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

2

D12

C12

B12

A12

AK12

AJ12

AH12

AG12

AL12

F12

E12

AH11

AJ11

AD27

AA25

AC25

AA24

AE29

AB31

AE30

AC31

M31

M29

L27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

N25

Y27

AA27

AA26

AB25

AB27

C515

C515

4.7U_0603

4.7U_0603

C177

C177

1000P

1000P

C517

C517

0.1U

0.1U

1

1.8VSUS

R351

R351

2K/F

2K/F

C518

C518

R352

R352

1000P

1000P

2K/F

2K/F

U9B

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA1_CS_L1

MA1_CS_L0

MA0_CS_L1

MA0_CS_L0

MB1_CS_L1

MB1_CS_L0

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

U9B

MB1_ODT0

MB0_ODT0

MA1_ODT0

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

C526

C526

0.22U

0.22U

C190

C190

180P

180P

AE20

AE19

G20

G21

V27

W27

AG21

AG20

G19

H19

U27

U26

AL19

AL18

C19

D19

W29

W28

AJ19

AK19

A18

A19

U31

U30

AD31

AD29

AC27

AC28

M_B_A15

N28

M_B_A14

N29

M_B_A13

AE31

M_B_A12

N30

M_B_A11

P29

M_B_A10

AA29

M_B_A9

P31

M_B_A8

R29

M_B_A7

R28

M_B_A6

R31

M_B_A5

R30

M_B_A4

T31

M_B_A3

T29

M_B_A2

U29

M_B_A1

U28

M_B_A0

AA30

N31

AA31

AA28

AB29

AC29

AC30

C521

C524

C524

0.22U

0.22U

C182

C182

180P

180P

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

C521

0.22U

0.22U

C191

C191

180P

180P

1

ZN1

ZN1

ZN1

MA1_CLK_H2

MA1_CLK_L2

MA1_CLK_H1

MA1_CLK_L1

MA1_CLK_H0

MA1_CLK_L0

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MA0_CLK_H0

MA0_CLK_L0

MB1_CLK_H2

MB1_CLK_L2

MB1_CLK_H1

MB1_CLK_L1

MB1_CLK_H0

MB1_CLK_L0

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_CLK_H0

MB0_CLK_L0

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 M2

Processor Socket

C491

C491

4.7U_0603

4.7U_0603

C188

C188

1000P

1000P

C509

C509

4.7U_0603

4.7U_0603

C179

C179

1000P

1000P

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

AMD AM2 DDR II Memory I/F

AMD AM2 DDR II Memory I/F

AMD AM2 DDR II Memory I/F

Date: Sheet of

Date: Sheet of

Date: Sheet of

M_CLKOUT1 8

M_CLKOUT1# 8

M_CLKOUT0 8

M_CLKOUT0# 8

M_CLKOUT4 8

M_CLKOUT4# 8

M_CLKOUT3 8

M_CLKOUT3# 8

M_ODT3 8,9

M_ODT2 8,9

M_ODT1 8,9

M_ODT0 8,9

M_B_A[0..15] 8,9

M_B_BS#2 8,9

M_B_BS#1 8,9

M_B_BS#0 8,9

M_B_RAS# 8,9

M_B_CAS# 8,9

M_B_WE# 8,9

SMDDR_VTERM

C525

C525

0.22U

0.22U

C184

C184

180P

180P

5 41Friday, May 08, 2009

5 41Friday, May 08, 2009

5 41Friday, May 08, 2009

5

1A

1A

1A

5

VCC3

D D

Vout =1.25(1+R1/R2)

= 1.25 (1+20K/20K)

= 2.5V

If AMD SI is not used, the SID pin can be left unconnected and SIC

should have a 300-Ω (±5%) pulldown to VSS.

1.8VSUS

CPU_SIC15

CPU_SID15

C C

CPUCLKP3

CPUCLKN3

CPU_PWRGD14

CPU_LDT_STOP#12,14

CPU_LDT_RST#12,14

VCC3

VCC3

VCC3

R105 300_4R105 300_4

R103 300_4R103 300_4

R102 300_4R102 300_4

H_PROCHOT#

R93 *10KR93 *10K

R95 *10KR95 *10K

5

1.8VSUS

B B

A A

PU10

PU10

1

SHDN

2

GND

3

VIN

G923-330T1UF

G923-330T1UF

PC139

PC139

10U_0805

10U_0805

R114 *300R114 *300

R137 *300R137 *300

R130 *0R130 *0

R115 *0R115 *0

C166 3900PC166 3900P

C163 3900PC163 3900P

R104

R104

*680

*680

1.8VSUS

R362

R362

300

300

THMDAT

1

THMCLK

1

VO

SET

R107

R107

*680

*680

1.8VSUS

2

1 3

*MMBT3904

*MMBT3904

Q27

Q27

R372 0R372 0

R96 0R96 0

R384 0R384 0

4

5

CPU_SIC_R

CPU_SID_R

R134

R134

169_0603F

169_0603F

R106

R106

*680

*680

R361

R361

*10K

*10K

Q29

Q29

*2N7002E-LF

*2N7002E-LF

2

2

Q30

Q30

*2N7002E-LF

*2N7002E-LF

PR150

PR150

20K_0603F

20K_0603F

PR149

PR149

20K_0603F

20K_0603F

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

R110 0R110 0

R111 0R111 0

R109 0R109 0

VCC3

R370

R370

*4.7K

*4.7K

MBDATA

3

MBCLK

3

0.2A

R135300 R135300

2.5V

PC149

PC149

100U/6.3V/3528

100U/6.3V/3528

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_HT_RESET#

CPU_PROCHOT# 14

MBDATA 12,32

MBCLK 12,32

CPU_VDDA

4

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

1.8VSUS

R97

R97

300_4

300_4

CPU_DBREQ#

CPU_DBRDY

T66T66

T127T127

CPU_TCK

CPU_TMS

T136T136

CPU_TDI

T129T129

T128T128

CPU_TRST#

CPU_TDO

T123T123

C144 *0.1U/10V_4C144 *0.1U/10V_4

CPU Thermal

Senser

C567 0.1UC567 0.1U

C128 2200P_0603C128 2200P_0603

R88

R88

*0_4

*0_4

4

1.8VSUS

R381 *300R381 *300

R113 300R113 300

R112 1K/FR112 1K/F

R140 510/FR140 510/F

R142 300R142 300

R139 *300R139 *300

R141 *300R141 *300

R144 *300R144 *300

R143 *300R143 *300

R375 *300R375 *300

R108 *300R108 *300

R371 510/FR371 510/F

R369 300R369 300

R374 300R374 300

close to CPU

CPU_CORE

COREFB+V34

COREFB-34

HDT Connector

1.8VSUS

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

R385 200_6R385 200_6

H_THERMDA

H_THERMDC

SYS_SHDN#1

23 24

U6

U6

1

2

3

4

G781-1

G781-1

MSOP8-4_9-65

MSOP8-4_9-65

KEY

KEY

CN10

CN10

*HDT CONN

*HDT CONN

VCC

DXP

DXN

-OVT

25

VCC3

sub-address:9Ah

SMDATA

PR3110/F PR3110/F

PR3010/F PR3010/F

1.8VSUS

C564

C564

*0.1U

*0.1U

SMCLK

-ALT

GND

CPU_VDDA

3

L51 40ohm_600mAL51 40ohm_600mA

VLDT_RUN

R145 *0R145 *0

VCC3

R82

R82

*4.7K

*4.7K

VCC3

THMCLKTHERM_VCC

8

THMDAT

7

THERM_ALERT#

6

5

3

1.8VSUS

2

*MMBT3904

*MMBT3904

Q15

Q15

1K/F_4

1K/F_4

R448

R448

VDDA_RUN

C541

C541

4.7U_0603

4.7U_0603

CPU_HT_RESET#

T67T67

CPU_ALL_PWROK

T130T130

CPU_LDTSTOP#

T135T135

CPU_SIC_R

CPU_SID_R

R379 44.2FR379 44.2F

R380 44.2FR380 44.2F

place them to CPU within 1"

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_H

T125T125

CPU_VDDIO_SUS_FB_L

T124T124

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

T61T61

CPU_TEST16_BP2

T133T133

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_TEST07_ANALOG_T

T65T65

CPU_TEST6_DIECRACKMON

T142T142

H_THERMDC

T132T132

H_THERMDA

T137T137

CPU_TEST3_GATE0

T138T138

CPU_TEST2_DRAIN0

T140T140

T107T107

T101T101

T94T94

T97T97

CPU_RSVD_MA0_CLK3_P

T100T100

CPU_RSVD_MA0_CLK3_N

T103T103

T98T98

CPU_RSVD_MB0_CLK3_P

T99T99

CPU_RSVD_MB0_CLK3_N

T108T108

R81

R81

*10K

*10K

CPU_HT_RESET#

13

2

ATHLON Control and Debug

12

C543

C543

C544

C544

0.22U

0.22U

3300pF

3300pF

U9D

U9D

C10

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HT_REF1

HT_REF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

R390

R390

10K

10K

1 3

MMBT3904

MMBT3904

2

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

DBREQ_L

TEST29_H

TEST29_L

TEST28_H

TEST28_L

MISC

MISC

VCC3

R77

R77

300

300

2

Q14

Q14

98 (CPU)

NB_SHDN#112

MXM_THERM#20,32

THERM_ALERT# 15

CPU_HTREF1

CPU_HTREF0

R790R79

CPU_THERMTRIP#

SYS_SHDN#1

D10

C7

C9

D8

AL6

AK6

V8

V7

G2

G1

AK11

AL11

A8

B8

B6

AL9

AH10

AJ10

AL10

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

L25

L26

L31

L30

W26

W25

AE27

U24

V24

AE28

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

0

R780R78

0

R3870R387

0

R80*0R80

*0

SMBUS SLAVE ADDRESS

G781

AMD NPT M2 SOCKET

Processor Socket

VCC3

VID5

VID4

VID3

VID2

VID1

VID0

PSI_L

NC#1

NC#2

NC#3

NC#4

NC#5

NC#6

NC#7

NC#8

TEST24

TEST23

TEST22

TEST21

TEST20

TEST27

TEST26

TEST10

TEST8

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

TDO

1

Add component to BOM

Vender suggest

1.8VSUS

H_THERMTRIP#

AK7

H_PROCHOT#

AL7

D2

D1

C1

E3

E2

E1

CPU_PRESENT#

AL3

F1

H3

H4

H20

H21

CPU_DBREQ#

A5

CPU_TDO

AK10

CPU_TEST29_H_FBCLKOUT_P

C11

CPU_TEST29_L_FBCLKOUT_N

D11

AE7

AD19

AE8

AD18

CPU_TEST24_SCANCLK1

AK8

CPU_TEST23_TSTUPD

AH8

CPU_TEST22_SCANSHIFTEN

AJ9

CPU_TEST21_SCANEN

AL8

CPU_TEST20_SCANCLK2

AJ8

CPU_TEST28_H_PLLCHRZ_P

J10

CPU_TEST28_L_PLLCHRZ_N

H9

CPU_TEST27_SINGLECHAIN

AK9

CPU_TEST26_BURNIN#

AK5

CPU_TEST10_ANALOGOUT

G7

CPU_TEST08_DIG_T

D4

CPU_MA_RESET#

E20

CPU_MB_RESET#

B19

AL4

AK4

AK3

CPU_RSVD_VIDSTRB1

F2

CPU_RSVD_VIDSTRB0

F3

CPU_VDDNB_FB_H

G4

CPU_VDDNB_FB_L

G3

CPU_CORE_TYPE

G5

Y31

Y30

AG31

V31

W31

AF31

SYS_SHDN# 38

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

1.8VSUS 1.8VSUS

R376

R376

10K

R373

R373

300

300

PSI# 34

T59T59

PLACE IT CLOSE TO CPU WITHIN 1"

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

AMD AM2 CTRL & DEBUG

AMD AM2 CTRL & DEBUG

AMD AM2 CTRL & DEBUG

10K

R101

R101

300

300

2

1 3

MMBT3904

MMBT3904

Q28

Q28

PSI_L is a Power Status Indicator

signal. This signal is asserted when

the processor is in a low powerstate.

PSI_L should be connected to the power

supply controller, if the controller

supports “skipmode, or diode emulation

mode”. PSI_L is asserted by the

processor during the C3 and S1 states.

R368 80.6FR368 80.6F

T139T139

T126T126

T131T131

T134T134

T64T64

T115T115

T119T119

T143T143

T144T144

T58T58

T57T57

T62T62

T63T63

T60T60

T92T92

T96T96

T91T91

T90T90

T95T95

T93T93

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

CPU_THERMTRIP# 15

VID5 34

VID4 34

VID3 34

VID2 34

VID1 34

VID0 34

T141T141

R3830R383

0

ZN1

ZN1

ZN1

6 41Friday, May 08, 2009

6 41Friday, May 08, 2009

6 41Friday, May 08, 2009

6

1A

1A

1A

5

4

3

2

1

PROCESSOR POWER AND GROUND

U9H

U9G

U9G

A3

VSS1

A7

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

A11

AA4

AA5

AA7

AA9

AB2

AB3

AB8

A9

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

Athlon 64 M2

Processor Socket

6090022000_4

6090022000_4

GND1

GND1

CPU_CORE

Y29

Y28

Y26

Y24

V30

V28

V26

V25

T30

T28

T26

T24

P30

P28

P26

P24

M30

M28

M26

M24

AF30

AD30

AD28

AD26

AC24

AB30

AB28

AB26

AB24

Y23

W22

V23

U22

T23

R22

P23

P21

N22

N20

M23

M21

L22

L20

AF11

AE12

AD23

AD11

AC22

AC20

AC18

AC16

AC14

AC12

1.8VSUS

CPU_CORE

R12

R14

R16

R18

R20

T11

T13

T15

T17

T19

T21

U10

U12

U14

U16

U18

U20

V11

V13

V15

V17

V19

V21

W10

W12

W14

W16

W18

W20

Y11

Y13

Y15

Y21

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

U9F

U9F

VDD107

VDD108

VDD109

VDD110

VDD111

T2

VDD112

T3

VDD113

T7

VDD114

T9

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

U8

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

V9

VDD129

VDD130

VDD131

VDD132

VDD133

VDD134

VDD135

W4

VDD136

W5

VDD137

W8

VDD138

VDD139

VDD140

VDD141

VDD142

VDD143

VDD144

Y2

VDD145

Y3

VDD146

Y7

VDD147

Y9

VDD148

VDD149

VDD150

VDD151

VDD152

VDD153

VDD154

VDD155

VDD156

VDD157

VDD158

VDD159

VDD160

POWER2

POWER2

VDDIO28

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

VDDIO12

VDDIO11

VDDIO10

VDDIO9

VDDIO

VDDIO8

VDDIO7

VDDIO6

VDDIO5

VDDIO4

VDDIO3

VDDIO2

VDDIO1

VDD184

VDD183

VDD182

VDD181

VDD180

VDD179

VDD178

VDD177

VDD176

VDD175

VDD174

VDD173

VDD172

VDD171

VDD170

VDD169

VDD168

VDD167

VDD166

VDD165

VDD164

VDD163

VDD162

VDD161

U9E

E10

F11

G10

G12

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AC4

AC5

AC8

AC10

AD2

AD3

AD7

AD9

AE10

AF7

AF9

AG4

AG5

AG7

AH2

AH3

H11

H23

A4

A6

B5

B7

C6

C8

D7

D9

E8

F9

B3

C2

C4

D3

D5

E4

E6

F5

F7

G6

G8

H7

U9E

VDD1

VDD2

VDD29

VDD30

VDD33

VDD34

VDD37

VDD38

VDD41

VDD42

VDD45

VDD46

VDD49

VDD50

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD31

VDD32

VDD35

VDD36

VDD39

VDD40

VDD43

VDD44

VDD47

VDD48

VDD51

VDD52

VDD53

Athlon 64 M2

Processor Socket

POWER1

POWER1

D D

C C

B B

CPU_CORE

VDD106

VDD105

VDD104

VDD103

VDD102

VDD101

VDD100

VDD99

VDD98

VDD97

VDD96

VDD95

VDD94

VDD93

VDD92

VDD91

VDD90

VDD89

VDD88

VDD87

VDD86

VDD85

VDD84

VDD83

VDD82

VDD81

VDD80

VDD79

VDD78

VDD77

VDD76

VDD75

VDD74

VDD73

VDD72

VDD71

VDD70

VDD69

VDD68

VDD67

VDD66

VDD65

VDD64

VDD63

VDD62

VDD61

VDD60

VDD59

VDD58

VDD57

VDD56

VDD55

VDD54

CPU_CORE

R10

R8

R5

R4

P19

P17

P15

P13

P11

P9

P7

N18

N16

N14

N12

N10

N8

M19

M17

M15

M13

M11

M9

M7

M3

M2

L18

L16

L14

Y19

Y17

L12

L10

L8

L5

L4

K23

K21

K19

K17

K15

K13

K11

K9

K7

J24

J22

J20

J18

J16

J14

J12

J8

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

H10

H8

G11

G9

F30

F28

F26

F24

F22

F20

F18

F16

F14

F4

E11

D30

D28

D26

D24

D22

D20

D18

D16

D14

C3

B30

B28

B26

B24

B22

B20

B18

B16

B14

B11

B9

B4

AL5

AK30

AK28

AK26

AK24

AK22

AK20

Y16

Y14

AK18

AK16

AK14

AK2

AH30

AH28

AH26

AH24

AH22

AH20

AH18

AH16

AH14

AG11

T22

T20

T18

T16

T14

T12

T10

R23

R21

R19

R17

R15

R13

R11

P22

P20

P18

P16

P14

P12

P10

N23

N21

N19

N17

Y18

K22

K20

K18

K16

K14

K12

K10

H30

H28

H26

H24

H22

H18

H16

H14

H12

T8

R9

R7

P8

P3

P2

K8

K3

K2

J23

J21

J19

J17

J15

J13

J11

J9

J7

J5

J4

U9H

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS163

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

6090022000_4

6090022000_4

U4

VSS184

U5

VSS185

U7

VSS186

U9

VSS187

U11

VSS188

U13

VSS189

U15

VSS190

U17

VSS191

U19

VSS192

U21

VSS193

U23

VSS194

V2

VSS195

V3

VSS196

V10

VSS197

V12

VSS198

V14

VSS199

V16

VSS200

V18

VSS201

V20

VSS202

V22

VSS203

W9

VSS204

W11

VSS205

W13

VSS206

W15

VSS207

W17

VSS208

W19

VSS209

W21

VSS210

W23

VSS211

Y8

VSS212

Y10

VSS213

GND2

GND2

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

Y12

W7

Y20

Y22

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

7

BOTTOMSIDE DECOUPLING

C561

C561

0.22U

0.22U

1.8VSUS

22U/6.3V_8

22U/6.3V_8

C426

C426

C559

C559

0.22U

0.22U

C556

C556

0.22U

0.22U

C427

C427

22U/6.3V_8

22U/6.3V_8

C557

C557

0.01U

0.01U

C459

C459

0.22U

0.22U

C560

C560

180P

180P

C432

C432

0.22U

0.22U

CPU_CORE

C547

C547

10U_0603

10U_0603

C548

C548

10U_0603

10U_0603

C546

C546

10U_0603

10U_0603

C549

C549

10U_0603

10U_0603

C550

C550

10U_0603

10U_0603

C551

C551

10U_0603

10U_0603

CPU_CORE

C553

C552

C552

10U_0603

10U_0603 C154

C554

C554

10U_0603

10U_0603

C553

10U_0603

10U_0603

C154

*22U/6.3V_8

*22U/6.3V_8

C153

C153

C152

*22U/6.3V_8

*22U/6.3V_8 C434

C152

*22U/6.3V_8

*22U/6.3V_8

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

1.8VSUS

C429

C429

4.7U_0603

4.7U_0603

C434

0.22U

0.22U

C456

C456

0.22U

0.22U

C453

C453

0.22U

0.22U

C460

C460

0.22U

0.22U

C462

C462

0.22U

0.22U

1.8VSUS

C428

C428

4.7U_0603

4.7U_0603

C431

C431

4.7U_0603

4.7U_0603

C430

C430

4.7U_0603

4.7U_0603

C438

C438

0.22U

0.22U

C442

C442

0.01U

0.01U

C450

C450

180P

180P

CPU_CORE

C481

C507

C504

C504

C507

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C506

C527

C527

C528

C531

C531

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

A A

C528

22U/6.3V_8

22U/6.3V_8

5

22U/6.3V_8

22U/6.3V_8

C532

C532

C506

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C508

C508

C479

C479

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

4

C480

C480

C481

22U/6.3V_8

22U/6.3V_8

C482

C482

22U/6.3V_8

22U/6.3V_8

C485

C485

22U/6.3V_8

22U/6.3V_8

C530

C530

22U/6.3V_8

22U/6.3V_8

C503

C503

22U/6.3V_8

22U/6.3V_8

3

C439

C439

0.01U

0.01U

C443

C443

180P

180P

C454

C454

180P

180P

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

AMD AM2 PWR & GND

AMD AM2 PWR & GND

AMD AM2 PWR & GND

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

ZN1

ZN1

ZN1

1A

1A

1A

7 41Friday, May 08, 2009

7 41Friday, May 08, 2009

7 41Friday, May 08, 2009

1

5

1.8VSUS

4

3

1.8VSUS

2

1

8

103

111

104

112

117

VDD7

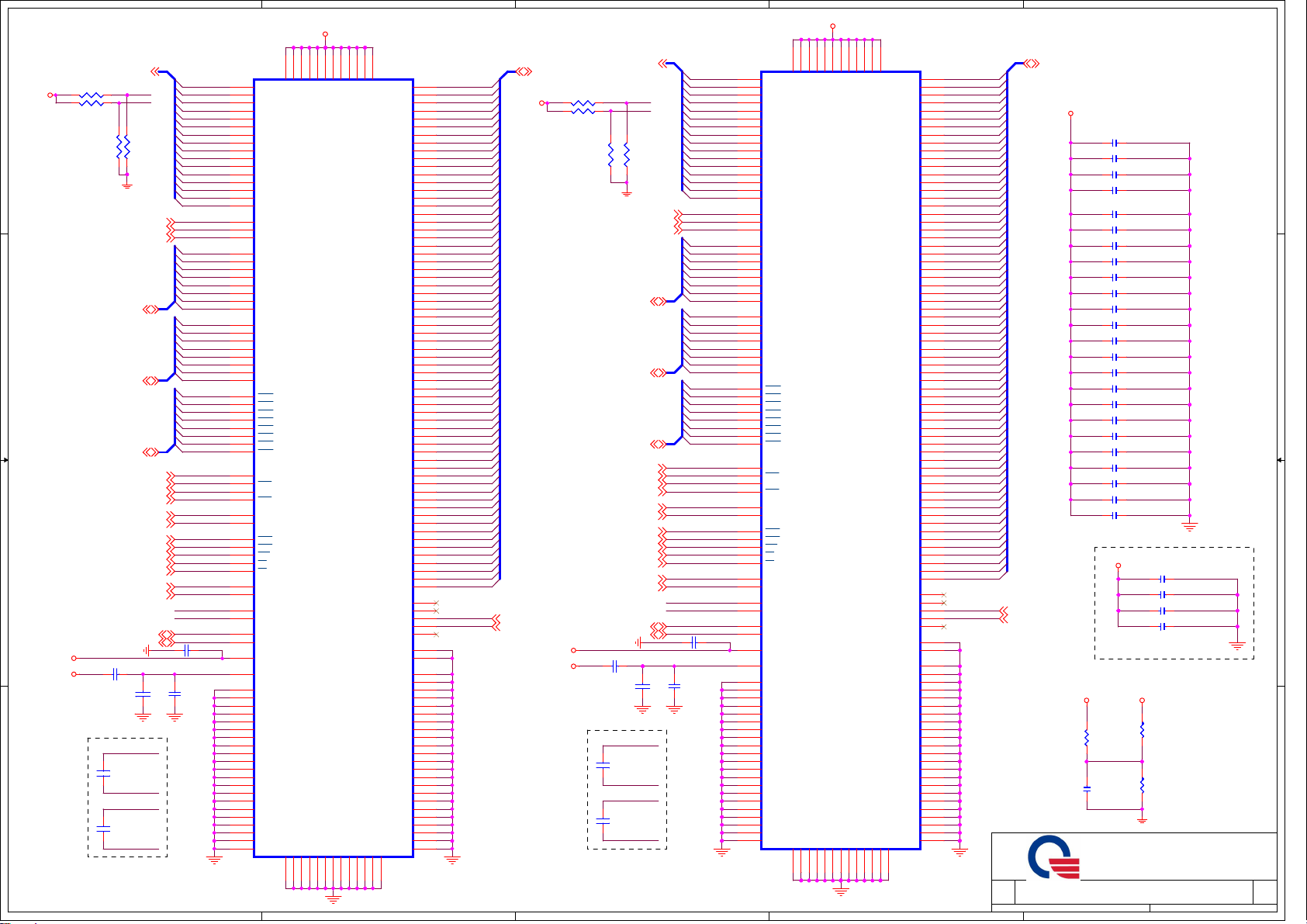

SO-DIMM

SO-DIMM

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

VDD8

VDD9

VSS30

VSS29

122

121

118

CN21

CN21

DQ0

DQ1

DQ2

VDD10

VDD11

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

GuidePin

GuidePin

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

132

128

127

DDRII_SODIMM_H_11

DDRII_SODIMM_H_11

2

M_B_DQ4

5

M_B_DQ1

7

M_B_DQ2

17

M_B_DQ3

19

M_B_DQ5

4

M_B_DQ0

6

M_B_DQ6

14

M_B_DQ7

16

M_B_DQ8

23

M_B_DQ9

25

M_B_DQ10

35

M_B_DQ15

37

M_B_DQ12

20

M_B_DQ13

22

M_B_DQ14

36

M_B_DQ11

38

M_B_DQ20

43

M_B_DQ16

45

M_B_DQ19

55

M_B_DQ23

57

M_B_DQ21

44

M_B_DQ17

46

M_B_DQ18

56

M_B_DQ22

58

M_B_DQ29

61

M_B_DQ28

63

M_B_DQ26

73

M_B_DQ27

75

M_B_DQ24

62

M_B_DQ25

64

M_B_DQ30

74

M_B_DQ31

76

M_B_DQ33

123

M_B_DQ36

125

M_B_DQ39

135

M_B_DQ35

137

M_B_DQ32

124

M_B_DQ37

126

M_B_DQ34

134

M_B_DQ38

136

M_B_DQ40

141

M_B_DQ41

143

M_B_DQ46

151

M_B_DQ43

153

M_B_DQ44

140

M_B_DQ45

142

M_B_DQ47

152

M_B_DQ42

154

M_B_DQ53

157

M_B_DQ49

159

M_B_DQ55

173

M_B_DQ54

175

M_B_DQ48

158

M_B_DQ52

160

M_B_DQ50

174

M_B_DQ51

176

M_B_DQ60

179

M_B_DQ57

181

M_B_DQ62

189

M_B_DQ59

191

M_B_DQ61

180

M_B_DQ56

182

M_B_DQ63

192

M_B_DQ58

194

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

103

111

104

112

117

VDD7

SO-DIMM

SO-DIMM

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

121

VDD8

VDD9

VSS30

VSS29

122

118

CN22

CN22

DQ0

DQ1

DQ2

VDD10

VDD11

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

GuidePin

GuidePin

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

132

128

127

DDRII_SODIMM_H_6.5

DDRII_SODIMM_H_6.5

4

M_A_DQ0

5

M_A_DQ1

7

M_A_DQ2

17

M_A_DQ3

19

M_A_DQ5

4

M_A_DQ4

6

M_A_DQ7

14

M_A_DQ6

16

M_A_DQ12

23

M_A_DQ8

25

M_A_DQ10

35

M_A_DQ14

37

M_A_DQ13

20

M_A_DQ9

22

M_A_DQ15

36

M_A_DQ11

38

M_A_DQ21

43

M_A_DQ17

45

M_A_DQ19

55

M_A_DQ18

57

M_A_DQ20

44

M_A_DQ16

46

M_A_DQ22

56

M_A_DQ23

58

M_A_DQ29

61

M_A_DQ28

63

M_A_DQ31

73

M_A_DQ30

75

M_A_DQ25

62

M_A_DQ24

64

M_A_DQ27

74

M_A_DQ26

76

M_A_DQ36

123

M_A_DQ32

125

M_A_DQ38

135

M_A_DQ35

137

M_A_DQ33

124

M_A_DQ37

126

M_A_DQ34

134

M_A_DQ39

136

M_A_DQ40

141

M_A_DQ41

143

M_A_DQ42

151

M_A_DQ46

153

M_A_DQ44

140

M_A_DQ45

142

M_A_DQ43

152

M_A_DQ47

154

M_A_DQ49

157

M_A_DQ53

159

M_A_DQ55

173

M_A_DQ51

175

M_A_DQ52

158

M_A_DQ48

160

M_A_DQ50

174

M_A_DQ54

176

M_A_DQ56

179

M_A_DQ61

181

M_A_DQ58

189

M_A_DQ59

191

M_A_DQ57

180

M_A_DQ60

182

M_A_DQ62

192

M_A_DQ63

194

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

M_A_A[0..15]5,9

R273 *4.7KR273 *4.7K

VCC3

R259 *4.7KR259 *4.7K

D D

SA_A : 00

M_A_DM[0..7]5

C C

M_A_DQS[0..7]5

M_A_DQS#[0..7]5

B B

VCC3

1.8VSUS

A A

SA0_A

SA1_A

12

12

R2720 R2720

M_A_BS#05,9

M_A_BS#15,9

M_A_BS#25,9

M_CLKOUT05

M_CLKOUT0#5

M_CLKOUT15

M_CLKOUT1#5

M_CKE05,9

M_CKE15,9

M_A_RAS#5,9

M_A_CAS#5,9

M_A_WE#5,9

M_A_CS#05,9

M_A_CS#15,9

M_ODT05,9

M_ODT15,9

PDAT_SMB3,15,19,30

PCLK_SMB3,15,19,30

C383 0.1UC383 0.1U

C367

C367

2.2U_0805

2.2U_0805

M_CLKOUT0

C436

C436

1.5P

1.5P

M_CLKOUT0#

M_CLKOUT1

C437

C437

1.5P

1.5P

M_CLKOUT1#

R2810 R2810

1 2

5

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_CLKOUT0

M_CLKOUT0#

M_CLKOUT1

M_CLKOUT1#

SA1_A

C361 0.1UC361 0.1U

MVREF_DIM

C370

C370

0.1U

0.1U

102

A0

101

A1

1

2

3

8

9

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

(H=6.5)

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

59

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

M_A_DQ[0..63] 5

R313 4.7KR313 4.7K

VCC3

R309 *4.7KR309 *4.7K

SA_B : 10

M_A_CS#2 5,9

M_A_CS#3 5,9

VCC3

1.8VSUS

M_B_A[0..15]5,9

12

R3080 R3080

M_B_DM[0..7]5

M_B_DQS[0..7]5

M_B_DQS#[0..7]5

M_CLKOUT35

M_CLKOUT3#5

M_CLKOUT45

M_CLKOUT4#5

M_CKE25,9

M_CKE35,9

M_B_RAS#5,9

M_B_CAS#5,9

M_B_WE#5,9

M_B_CS#05,9

M_B_CS#15,9

M_ODT25,9

M_ODT35,9

PDAT_SMB3,15,19,30

PCLK_SMB3,15,19,30

C411 0.1UC411 0.1U

C395

C395

2.2U_0805

2.2U_0805

M_CLKOUT3

C435

C435

1.5P

1.5P

M_CLKOUT3#

M_CLKOUT4

C441

C441

1.5P

1.5P

M_CLKOUT4#

SA0_B

SA1_B

12

R312*0 R312*0

M_B_BS#05,9

M_B_BS#15,9

M_B_BS#25,9

1 2

3

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_CLKOUT3

M_CLKOUT3#

M_CLKOUT4

M_CLKOUT4#

SA0_B

SA1_BSA0_A

C394 0.1UC394 0.1U

MVREF_DIM

C402

C402

0.1U

0.1U

102

A0

101

A1

1

2

3

8

9

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

(H=11)

59

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

M_B_DQ[0..63] 5

1.8VSUS

M_B_CS#2 5,9

M_B_CS#3 5,9

DDR_VREF

DDRII SODIMM x2

DDRII SODIMM x2

DDRII SODIMM x2

*10U_0805C415 *10U_0805C415

*10U_0805C371 *10U_0805C371

10U_0805C321 10U_0805C321

10U_0805C373 10U_0805C373

0.1UC416 0.1UC416

0.1UC376 0.1UC376

0.1UC377 0.1UC377

0.1UC417 0.1UC417

0.1UC378 0.1UC378

0.1UC421 0.1UC421

0.1UC423 0.1UC423

0.1UC418 0.1UC418

0.1UC380 0.1UC380

0.1UC419 0.1UC419

0.1UC374 0.1UC374

0.1UC375 0.1UC375

0.1UC379 0.1UC379

0.1UC381 0.1UC381

0.1UC382 0.1UC382

0.1UC327 0.1UC327

0.1UC328 0.1UC328

0.1UC322 0.1UC322

0.1UC323 0.1UC323

0.1UC325 0.1UC325

1.8VSUS

*0.1UC422 *0.1UC422

*0.1UC420 *0.1UC420

*0.1UC324 *0.1UC324

*0.1UC326 *0.1UC326

For EMI

1.8VSUS

R256

R261*0R261

*0

MVREF_DIM

C352

C352

*1U

*1U

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

R256

1K/F

1K/F

0.9V

R274

R274

1K/F

1K/F

1

ZN1

ZN1

ZN1

8 41Friday, May 08, 2009

8 41Friday, May 08, 2009

8 41Friday, May 08, 2009

1A

1A

1A

5

4

3

2

1

9

SMDDR_VTERM

D D

0.9V

SMDDR_VTERM

10U_0805C372 10U_0805C372

*10U_0805C414 *10U_0805C414

0.1UC399 0.1UC399

0.1UC398 0.1UC398

0.1UC397 0.1UC397

C C

0.1UC389 0.1UC389

0.1UC386 0.1UC386

0.1UC396 0.1UC396

0.1UC385 0.1UC385

0.1UC346 0.1UC346

0.1UC362 0.1UC362

*0.1UC390 *0.1UC390 0.1UC409 0.1UC409

*0.1UC401 *0.1UC401

0.1UC400 0.1UC400

0.1UC391 0.1UC391

0.1UC388 0.1UC388

0.1UC412 0.1UC412

0.1UC351 0.1UC351

*0.1UC413 *0.1UC413

0.1UC387 0.1UC387

0.1UC363 0.1UC363

0.1UC364 0.1UC364

*0.1UC365 *0.1UC365

0.1UC366 0.1UC366

0.1UC347 0.1UC347

0.1UC348 0.1UC348

*0.1UC349 *0.1UC349

0.1UC350 0.1UC350

1.8VSUS

0.9V

SMDDR_VTERM

0.1UC404 0.1UC404

0.1UC403 0.1UC403

0.1UC332 0.1UC332

0.1UC337 0.1UC337

0.1UC410 0.1UC410

0.1UC405 0.1UC405

0.1UC406 0.1UC406

0.1UC407 0.1UC407

0.1UC408 0.1UC408

0.1UC331 0.1UC331

0.1UC338 0.1UC338

0.1UC333 0.1UC333

0.1UC334 0.1UC334

0.1UC335 0.1UC335

0.1UC336 0.1UC336

M_CKE05,8

M_CKE15,8

M_CKE25,8

M_CKE35,8

M_ODT05,8

M_ODT15,8

M_ODT25,8

M_ODT35,8

M_A_BS#05,8

M_A_BS#15,8

M_A_BS#25,8

M_A_WE#5,8

M_A_CAS#5,8

M_A_RAS#5,8

M_B_BS#05,8

M_B_BS#15,8

M_B_BS#25,8

M_B_WE#5,8

M_B_CAS#5,8

M_B_RAS#5,8

M_A_CS#05,8

M_A_CS#15,8

M_A_CS#25,8

M_A_CS#35,8

M_B_CS#05,8

M_B_CS#15,8

M_B_CS#25,8

M_B_CS#35,8

M_A_A[0..15]5,8

M_A_A13

M_A_A10

M_A_A0

M_A_A2

M_A_A4

M_A_A6

M_A_A7

M_A_A11

M_A_A12

M_A_A9

M_A_A3

M_A_A1

M_A_A8

M_A_A5

M_A_A14

M_A_A15

R288 47_4R288 47_4

R265 47_4R265 47_4

R317 47_4R317 47_4

R310 47_4R310 47_4

R268 47_4R268 47_4

R296 47_4R296 47_4

R304 47_4R304 47_4

R325 47_4R325 47_4

R293 47_4R293 47_4

R266 47_4R266 47_4

R290 47_4R290 47_4

R292 47_4R292 47_4

R295 47_4R295 47_4

R267 47_4R267 47_4

R322 47_4R322 47_4

R302 47_4R302 47_4

R319 47_4R319 47_4

R321 47_4R321 47_4

R323 47_4R323 47_4

R303 47_4R303 47_4

R269 47_4R269 47_4

R294 47_4R294 47_4

R289 47_4R289 47_4

R271 47_4R271 47_4

R305 47_4R305 47_4

R324 47_4R324 47_4

R318 47_4R318 47_4

R307 47_4R307 47_4

R270 47_4R270 47_4

R291 47_4R291 47_4

RP16 0404-47X2RP16 0404-47X2

1 2

3 4

RP15 0404-47X2RP15 0404-47X2

1 2

3 4

RP14 0404-47X2RP14 0404-47X2

1 2

3 4

RP17 0404-47X2RP17 0404-47X2

1 2

3 4

RP19 0404-47X2RP19 0404-47X2

1 2

3 4

RP18 0404-47X2RP18 0404-47X2

1 2