Page 1

1

2

3

4

5

6

7

8

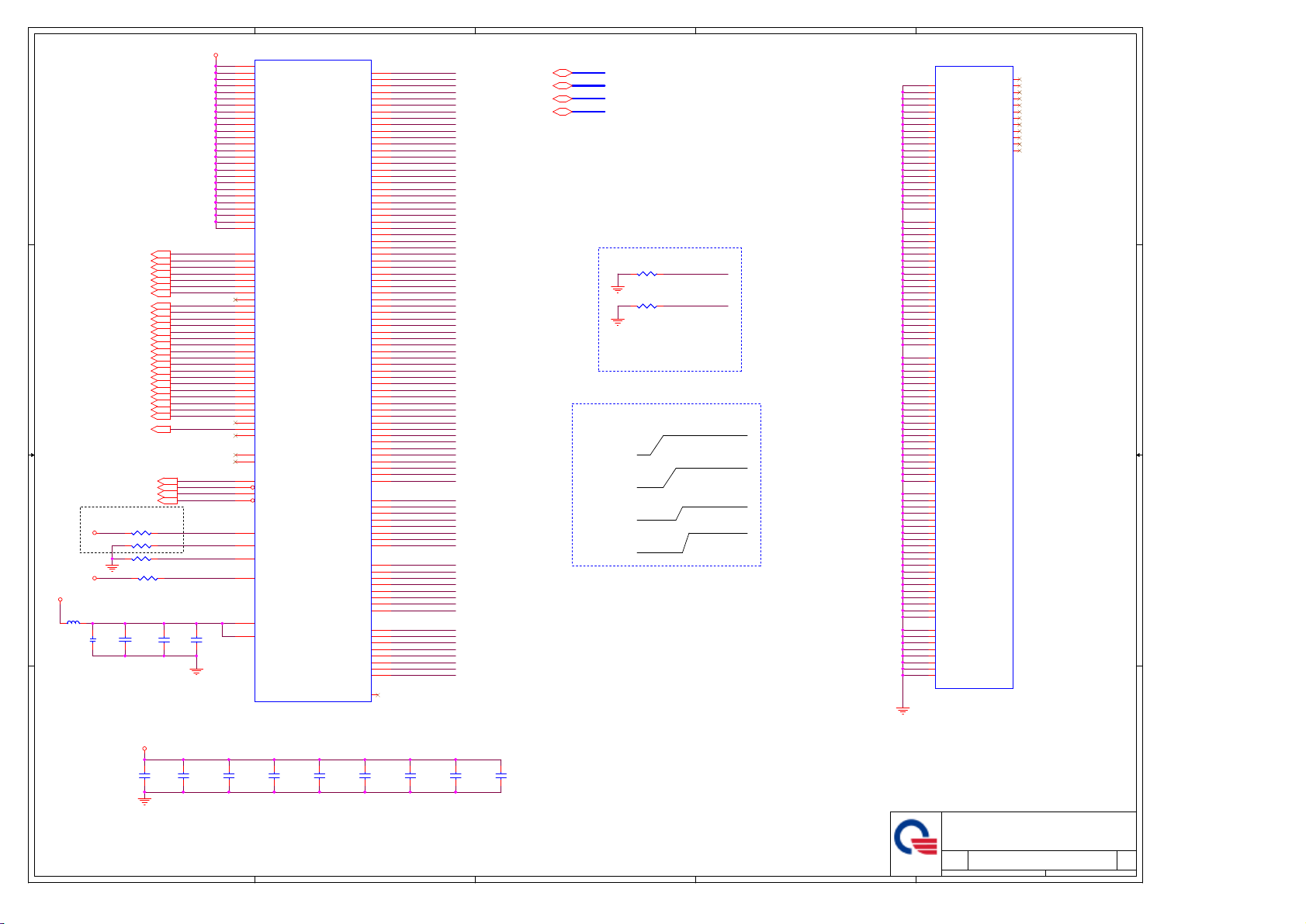

PCB STACK UP

6L

UMA CO-LAY DIS

LAYER 1 : TOP

AA

LAYER 2 : SGND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : VCC

LAYER 6 : BOT

BB

SYSTEM CHARGER(ISL6251AHAZ-T)

SYSTEM POWER ISL6237IRZ-T

DDR II SMDDR_VTERM

CC

1.8V/1.8VSUS(TPS51116REGR)

VCCP +1.5V AND GMCH

1.05V(RT8204)

CPU CORE ISL6266A

PAGE 31

PAGE 32

PAGE 36

PAGE 33

PAGE 34

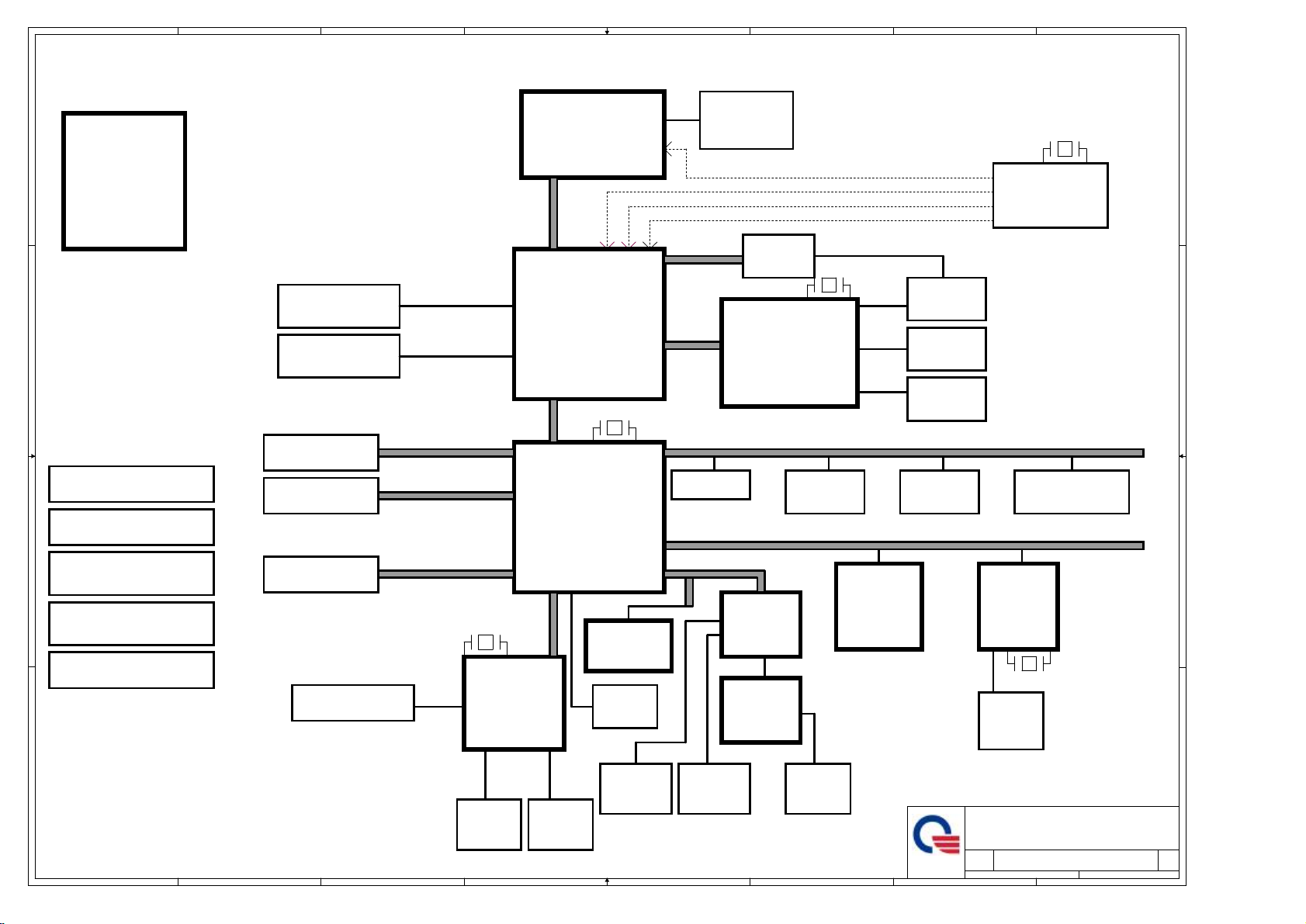

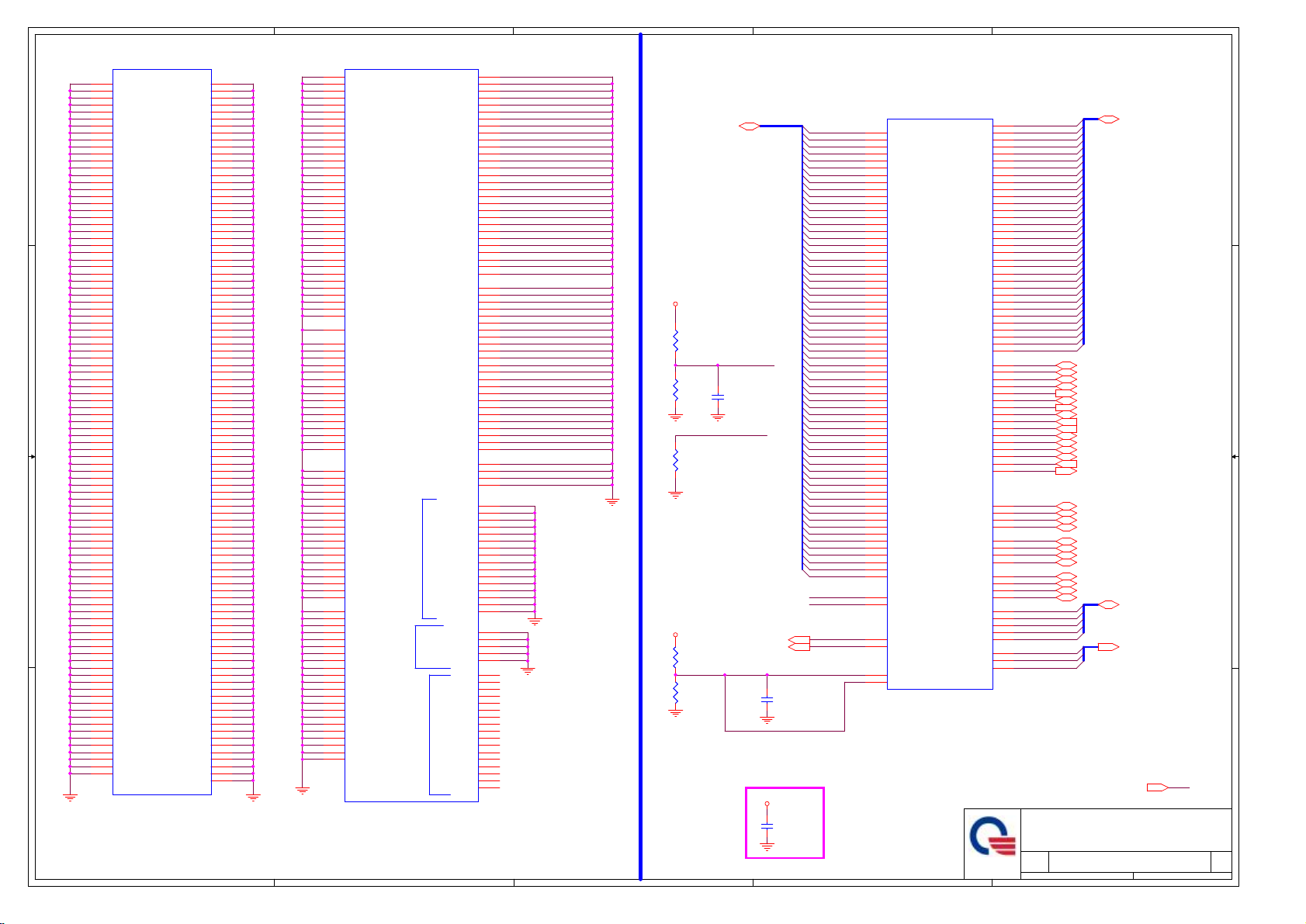

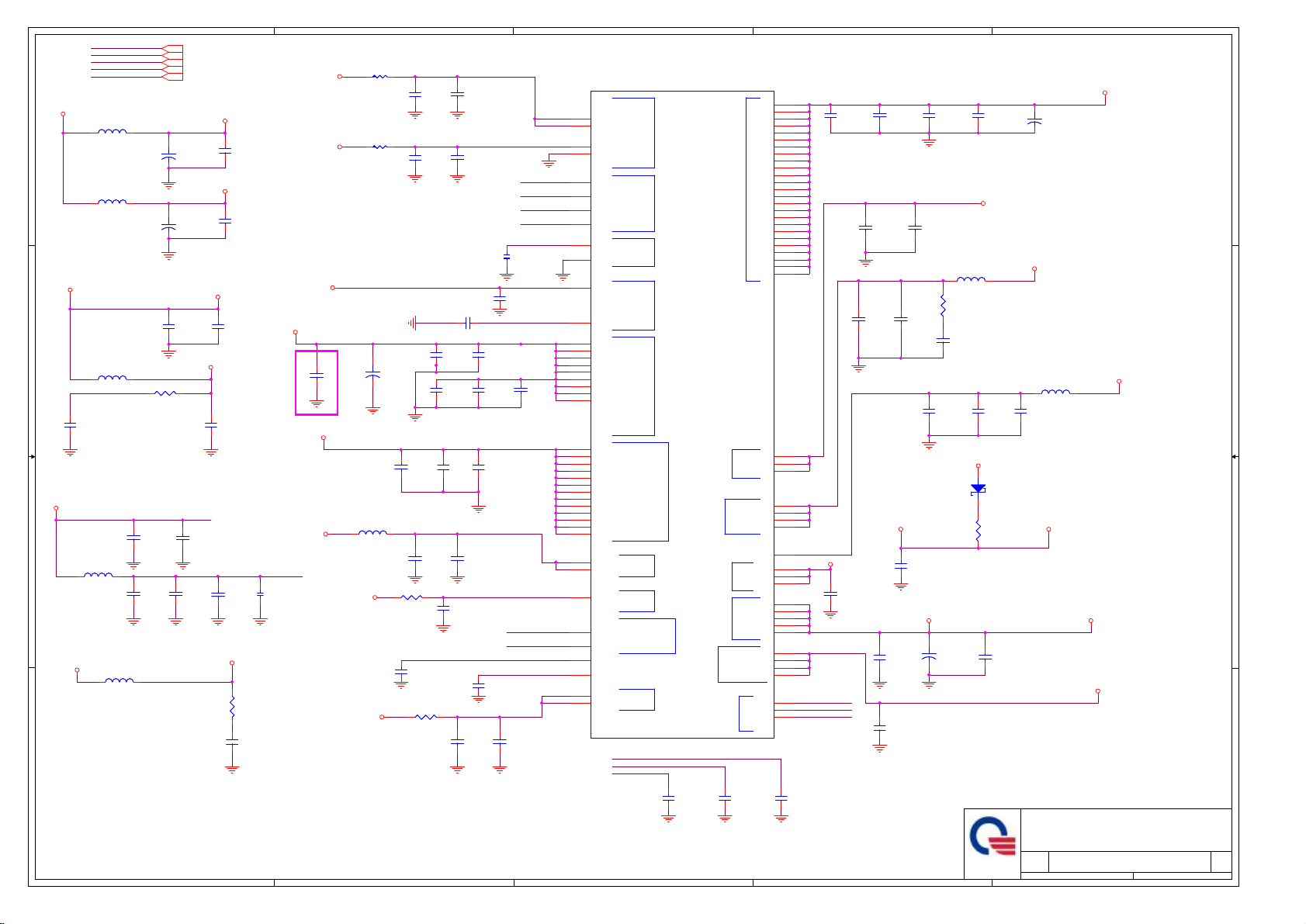

Tango/Ballet BLOCK DIAGRAM

PCI-Express

16X

USB2.0

0,8,9

PAGE 26

X3

PCI-E

Azalia

CPU THERMAL

SENSOR

PAGE 4

Level Shift

PAGE 18

nVIDIA

NB10M-GE2-S

PAGE 12~16

NBSRCCLK, NBSRCCLK#

Analog

IDT92HP75B2

PAGE 24

AUDIO

Amplifier

TPA6017

PAGE 25

CLK_CPU_BCLK,CLK_CPU_BCLK#

CLK_MCH_BCLK,CLK_MCH_BCLK#

DREFCLK,DREFCLK#

DREFSSCLK,DREFSSCLK#

27MHz

64 Bit

533p

5

BlueToothUSB2.0 Ports

(Option)(Option)

PAGE 26

DDRII-SODIMM1

PAGE 10

DDRII-SODIMM2

PAGE 10

SATA - HDD

PAGE 26

SATA - CD-ROM

PAGE 26

E-SATA

PAGE 26

Keyboard

Touch Pad

PAGE 29

PAGE 29

FSB 667/800/1066

DDRII 667/800 MHz

DDRII 667/800 MHz

DMI LINK

SATA0 150MB

SATA1 150MB

SATA5 150MB

32.768KHz

ENE KBC

KB3926 C0/D2

CPU

Penryn

478P (uPGA)/35W

NORTH BRIDGE

Cantiga

PAGE 5~9

SOUTH BRIDGE

ICH-9M

PAGE 19~22

LPC

PAGE31

PAGE 3,4

32.768KHz

MDC CONN

(Option)

PAGE 28

SPI for

HDCP

PAGE 20

HDMI CON

(Option)

PAGE 18

CRT

PAGE18

Dual Link

LCD CONN

PAGE 17

3

Webcam

PAGE 17

X1X1

Mini PCI-E

Card

(Wireless LAN)

PAGE 30

14.318MHz

CLOCK GEN

ALPRS355B MLF64PIN

PAGE 2

Card Reader

RTS5159

(Option)

LAN

Realtek

PCIE-LAN

RTL8103EL

(10/100 LAN)

PAGE 27

25MHz

RJ45

PAGE 27

01

6

PAGE 23

DD

GMT G9931P1U

FAN

PAGE 26

1

2

3

SPI

PAGE 29

4

Audio Jacks microphone

(Phone/ MIC)

PAGE 24PAGE 24

5

Jack to

Speaker

PAGE 25

6

PROJECT : OP6/7

PROJECT : OP6/7

PROJECT : OP6/7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

NB5

NB5

NB5

Date:Sheet of

Date:Sheet of

Date:Sheet of

7

Block Diagram

Block Diagram

Block Diagram

A

A

137Tuesday, January 20, 2009

137Tuesday, January 20, 2009

137Tuesday, January 20, 2009

8

A

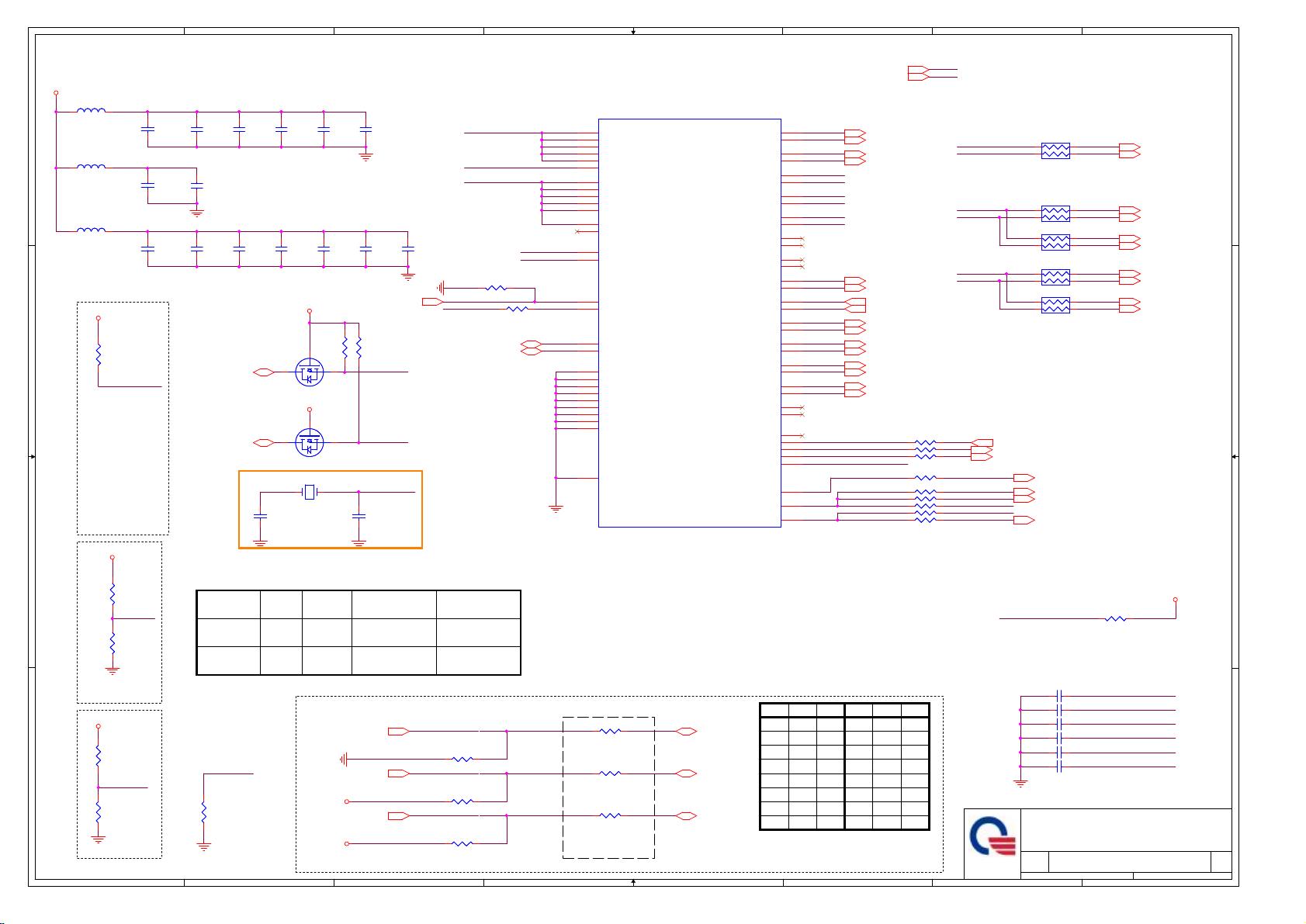

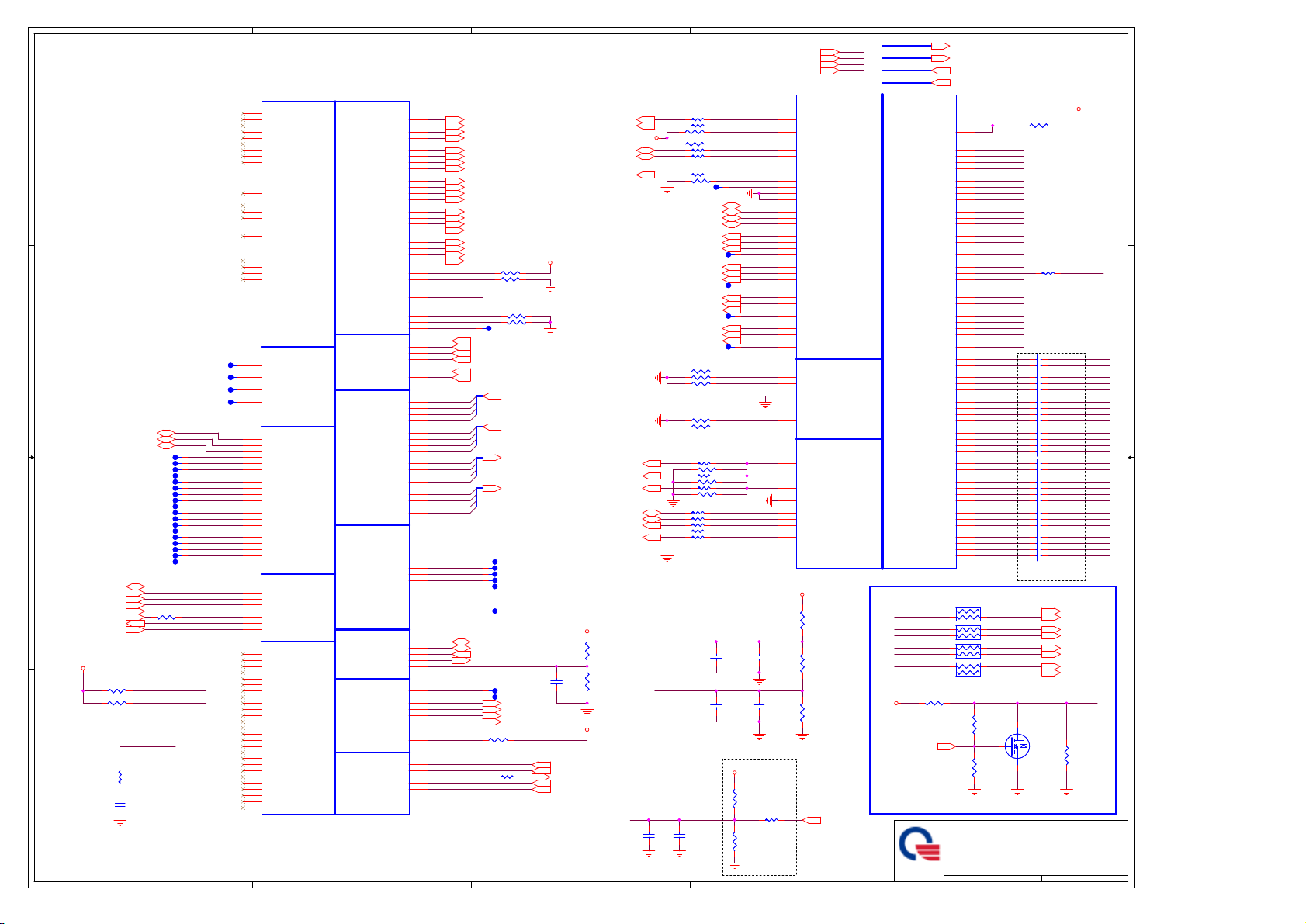

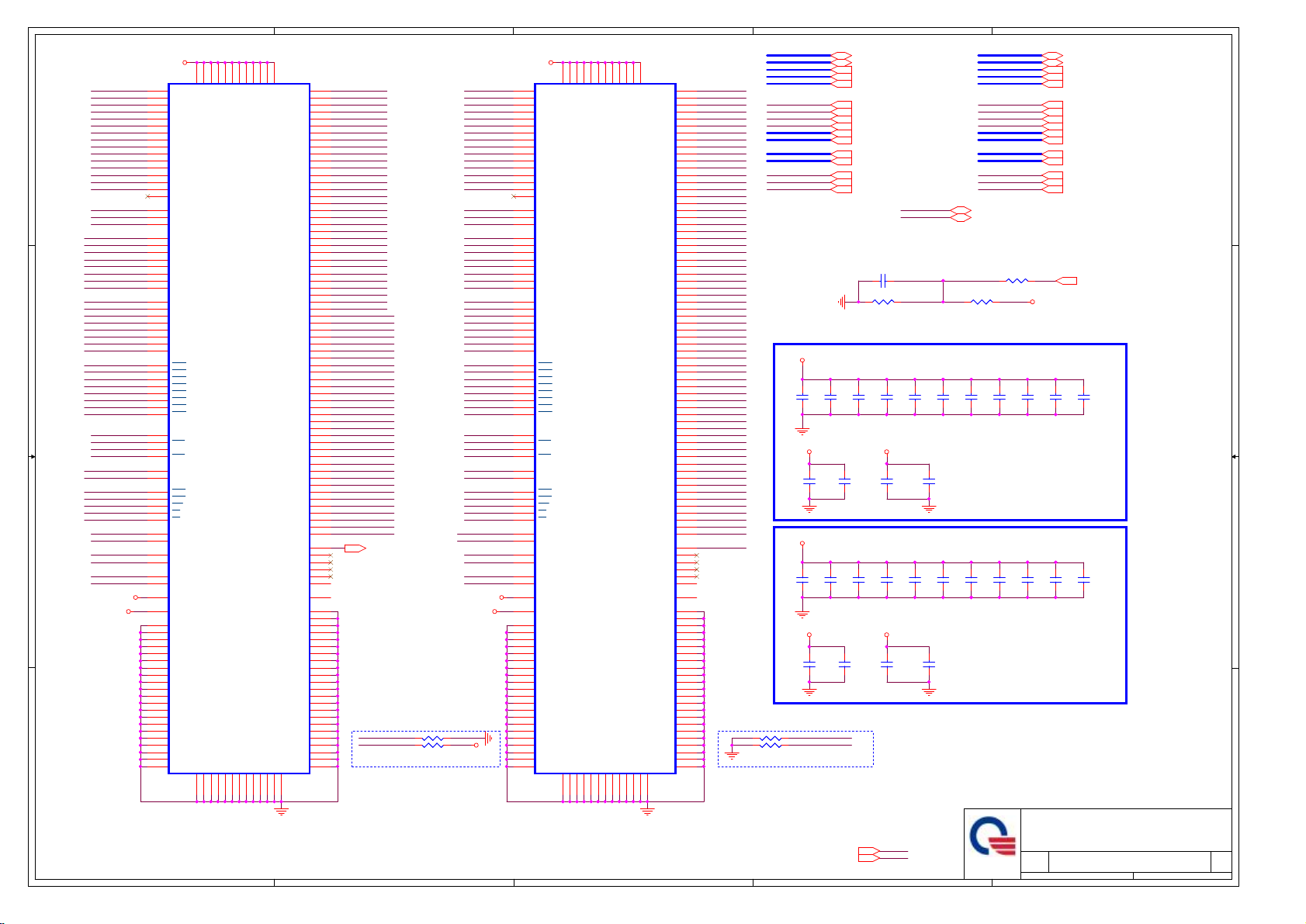

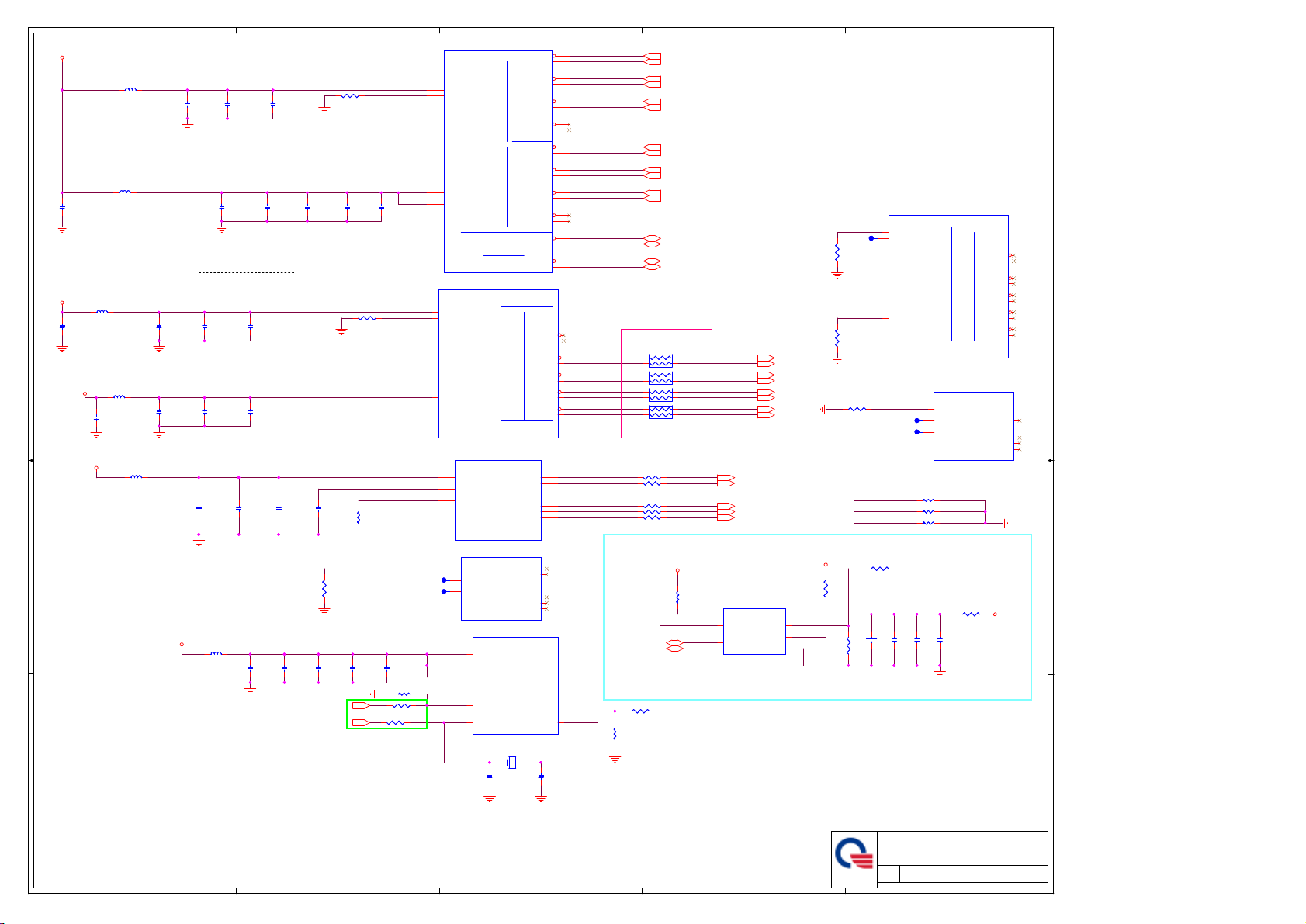

Page 2

1

+3V

L38

L38

1 2

HCB1608KF-181T15

HCB1608KF-181T15

AA

L42

L42

1 2

HCB1608KF-181T15

HCB1608KF-181T15

10U/6.3V_8

10U/6.3V_8

L43

L43

1 2

HCB1608KF-181T15

HCB1608KF-181T15

10U/6.3V_8

10U/6.3V_8

+3V

BB

CC

R279

R279

10K_4

10K_4

1 2

0=overclocking

of CPU and

SRC Allowed

1 = overclocking

of CPU and SRC

not Allowed

+3V

C542

C542

C554

C554

TME

C513

C513

10U/6.3V_8

10U/6.3V_8

+3V_CK_CPU

C562

C562

.1U/10V_4

.1U/10V_4

C530

C530

.1U/10V_4

.1U/10V_4

C549

C549

.1U/10V_4

.1U/10V_4

+3V_CK_MAIN

PDAT_SMB[21]

PCLK_SMB[21]

2

C511

C511

.1U/10V_4

.1U/10V_4

+3V_CK_MAIN2

C561

C561

.1U/10V_4

.1U/10V_4

2N7002

2N7002

2N7002

2N7002

CG_XIN

12

C507

C507

33P/50V_4

33P/50V_4

C509

C509

.1U/10V_4

.1U/10V_4

C529

C529

.1U/10V_4

.1U/10V_4

Q15

Q15

3

Q16

Q16

3

+3V

2

+3V

2

Y3

Y3

1 2

14.318MHZ

14.318MHZ

10K_4

10K_4

C541

C541

.1U/10V_4

.1U/10V_4

C566

C566

.1U/10V_4

.1U/10V_4

R297

R297

1

1

12

C508

C508

.1U/10V_4

.1U/10V_4

C547

C547

.1U/10V_4

.1U/10V_4

R296

R296

10K_4

10K_4

CGDAT_SMB

CGCLK_SMB

CG_XOUT

C512

C512

33P/50V_4

33P/50V_4

3

C539

C539

.1U/10V_4

.1U/10V_4

CK_PWG[21]

DB:Change from 27P to 33P(TXC suggestion)

CPU_BSEL1

+3V_CK_MAIN

+3V_CK_CPU

+3V_CK_MAIN2

R317*100K/F_4 R317*100K/F_4

R3122.2K_4R3122.2K_4

CGCLK_SMB[10,11,30]

CGDAT_SMB[10,11,30]

CG_XIN

CG_XOUT

4

U21

U21

23

VDDPLL3

16

VDD48

9

VDDPCI

CK505

VDDREF

VDDSRC

VDDCPU

VDD96I/O

VDDPLL3I/O

VDDSRCI/O

VDDSRCI/O

VDDSRCI/O

VDDCPU_IO

NC

X1

X2

CK_PWRGD/PD#

FSLB/TEST_MODE

SCLK

SDATA

GND

GND

GND48

GNDCPU

GNDPCI

GNDREF

GNDSRC

GNDSRC

GNDSRC

EPAD

CK505

4

46

62

19

27

33

43

52

56

55

3

2

63

FSB

64

7

6

22

26

18

59

15

1

30

36

49

65

5

CPUT2_ITP/SRCT8

CPUC2_ITP/SRCC8

DOTT_96/SRCT0

DOTC_96/SRCC0

27MHz_Nonss/SRCCLK1/SE1

27Mhz_ss/SRCCLC1/SE2

SRCCLKT2/SATACL

SRCCLKC2/SATACL

SRCCLKT3/CR#_C

SRCCLKC3/CR#_D

CPU_STOP#

SRCCLKT7/CR#_F

SRCCLKC7/CR#_E

SRCCLKT10

SRCCLKC10

SRCCLKT11/CR#_H

SRCCLKC11/CR#_G

PCICLK0/CR#_A

PCICLK1/CR#_B

PCICLK2/TME

PCICLK4/27_SELECT

PCI_F5/ITP_EN

USB_48MHZ/FSLA

FSLC/TST_SL/REF

ICS9LPRS355BKLF MLF64

ICS9LPRS355BKLF MLF64

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

SRCCLKT4

SRCCLKC4

PCI_STOP#

SRCCLKT6

SRCCLKC6

SRCCLKT9

SRCCLKC9

PCICLK3

61

60

58

57

54

53

20

21

24

25

28

29

31

32

34

35

45

44

48

47

51

50

37

38

41

42

40

39

8

R_CLK_MCH_OE#

10

11

12

13

14

17

5

SRC8

SRC8#

SRC0

SRC0#

SRC1

SRC1#

TME

R_PCLK_KBC

27M_SEL

6

+3V[4,6,9,10,11,12,14,15,17,18,19,20,21,22,24,25,26,27,28,29,30,33,34,37]

+1.05V[3,4,5,6,8,9,19,22,33,34]

CLK_CPU_BCLK[3]

CLK_CPU_BCLK#[3]

CLK_MCH_BCLK[5]

CLK_MCH_BCLK#[5]

CLK_PCIE_3GPLL[6]

CLK_PCIE_3GPLL#[6]

PM_STPPCI#[21]

PM_STPCPU#[21]

CLK_PCIE_ICH[20]

CLK_PCIE_ICH#[20]

CLK_PCIE_WLAN[30]

CLK_PCIE_WLAN#[30]

CLK_PCIE_LAN[27]

CLK_PCIE_LAN#[27]

CLK_PCIE_SATA[19]

CLK_PCIE_SATA#[19]

R280475/F_4R280475/F_4

R27633_4R27633_4

R28833_4R28833_4

ITP_EN

R28533_4R28533_4

R30822_4R30822_4

R30322_4R30322_4

FSA

R3152.2K_4R3152.2K_4

FSC

R28910K_4R28910K_4

FSLC

R29833_4R29833_4

SRC8

SRC8#

SRC0

SRC0#

SRC1

SRC1#

CPU_BSEL0

CPU_BSEL2

7

RP494P2R-0RP494P2R-0

4

2

int

RP47*4P2R-0RP47*4P2R-0

4

2

discrete

2

4

RP484P2R-0RP484P2R-0

int

RP50*4P2R-0RP50*4P2R-0

2

4

2

4

RP514P2R-33RP514P2R-33

discrete

CLK_MCH_OE#[6]

PCLK_DEBUG[30]

PCLK_KBC[29]

PCLK_ICH[20]

CLK_48M_USB[21]

CLK_48M_CR[23]

CLK_14M_ICH[21]

8

02

3

1

3

1

1

3

1

3

1

3

CLK_CPU_ITP[3]

CLK_CPU_ITP#[3]

DREFCLK[6]

DREFCLK#[6]

CLK_PCIE_VGA[12]

CLK_PCIE_VGA#[12]

DREFSSCLK[6]

DREFSSCLK#[6]

27M_NONSS[14]

27M_SS[14]

QFN64CK505

R293

R293

des

10K_4

10K_4

1 2

27M_SEL

R299

R299

int

*10K_4

*10K_4

1 2

0=UMA

1 = External VGA

+3V

*10K/F_4

*10K/F_4

R291

R291

DD

1 2

ITP_EN

10K_4

10K_4

R292

R292

1 2

Enable ITP CLK

1

27M_SEL

PIN13

0=UMA

1 = External

VGA

R_PCLK_KBC

R283

R283

*10K/F_4

*10K/F_4

1 2

PIN20

DOT96T

PIN21

PIN24

SRCT1/LCDT_100DOT96C

PIN25

SRCT1/LCDT_100

SRCT0SRCC027Mout-NSS27Mout-SS

CPU Clock select

CPU_BSEL0[3]

R314*1K/F_4R314*1K/F_4

CPU_BSEL1[3] MCH_BSEL1[6]

+1.05V

CPU_BSEL2[3] MCH_BSEL2[6]

+1.05V

2

R322*1K/F_4R322*1K/F_4

R281*1K/F_4R281*1K/F_4

3

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

R321*0_4/SR321*0_4/S

R316*0_4/SR316*0_4/S

R278*0_4/SR278*0_4/S

1K to NB only when

XDP is implement.No

XDP can use 0 ohm

4

Realtek

MCH_BSEL0[6]

SLG8SP513VTRSilego

RTM875N-606-VD-GR

FSCFSB

1330

0

0

0

00

1

1

1

5

AL8SP513000

AL000875000

FSACPUSRCPCI

1100

10

1

1

1

0

0

0 33

0

1

0

1

1

133

166

200

266

333

400

RSVD

100

100

100

100

100

100

100

100

6

CLK_MCH_OE#

33

33

33

33

R27710K_4R27710K_4

C501*33P/50V_4C501*33P/50V_4

C503*27P/50V_4C503*27P/50V_4

C495*33P/50V_4C495*33P/50V_4

C518*10P/50V_4C518*10P/50V_4

C514*10P/50V_4C514*10P/50V_4

C506*33P/50V_4C506*33P/50V_4

for EMI

PCLK_KBC

PCLK_ICH

PCLK_DEBUG

CLK_48M_USB

CLK_48M_CR

CLK_14M_ICH

33

33

NB5

NB5

NB5

7

PROJECT : OP6/7

PROJECT : OP6/7

PROJECT : OP6/7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

Date:Sheet of

Date:Sheet of

Date:Sheet of

Clock Generator

Clock Generator

Clock Generator

+3V

12

SI

SI

237Tuesday, January 20, 2009

237Tuesday, January 20, 2009

237Tuesday, January 20, 2009

8

SI

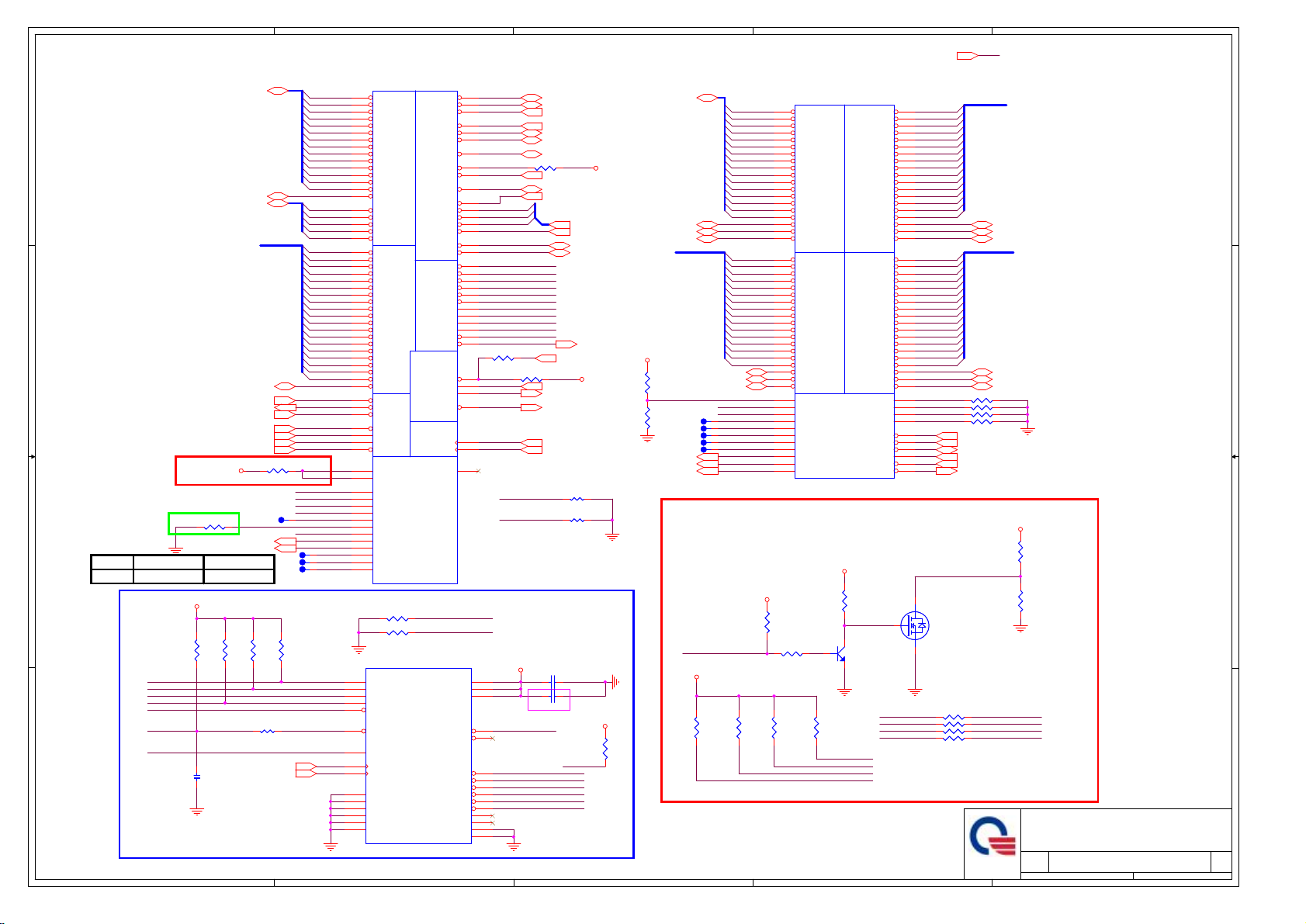

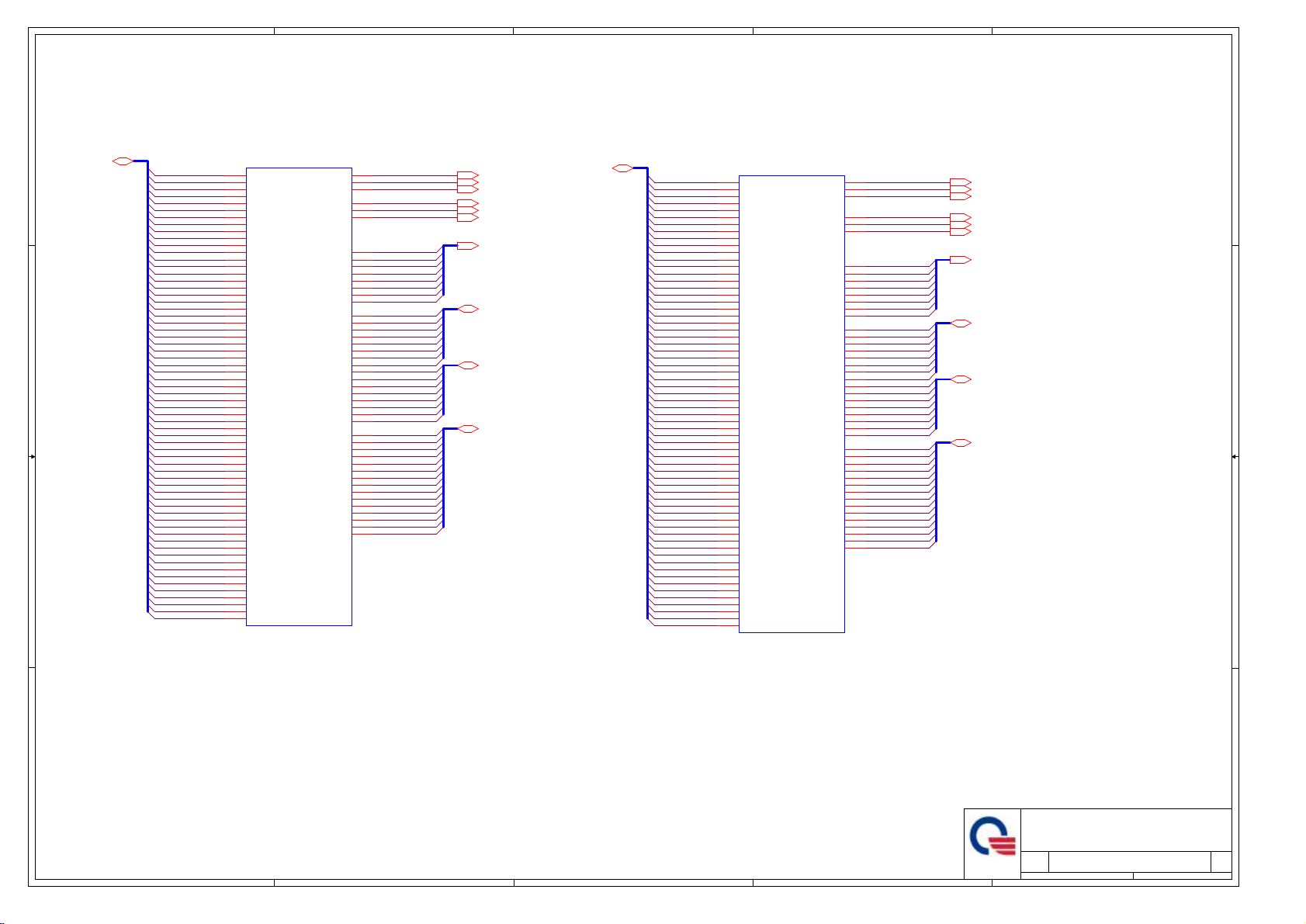

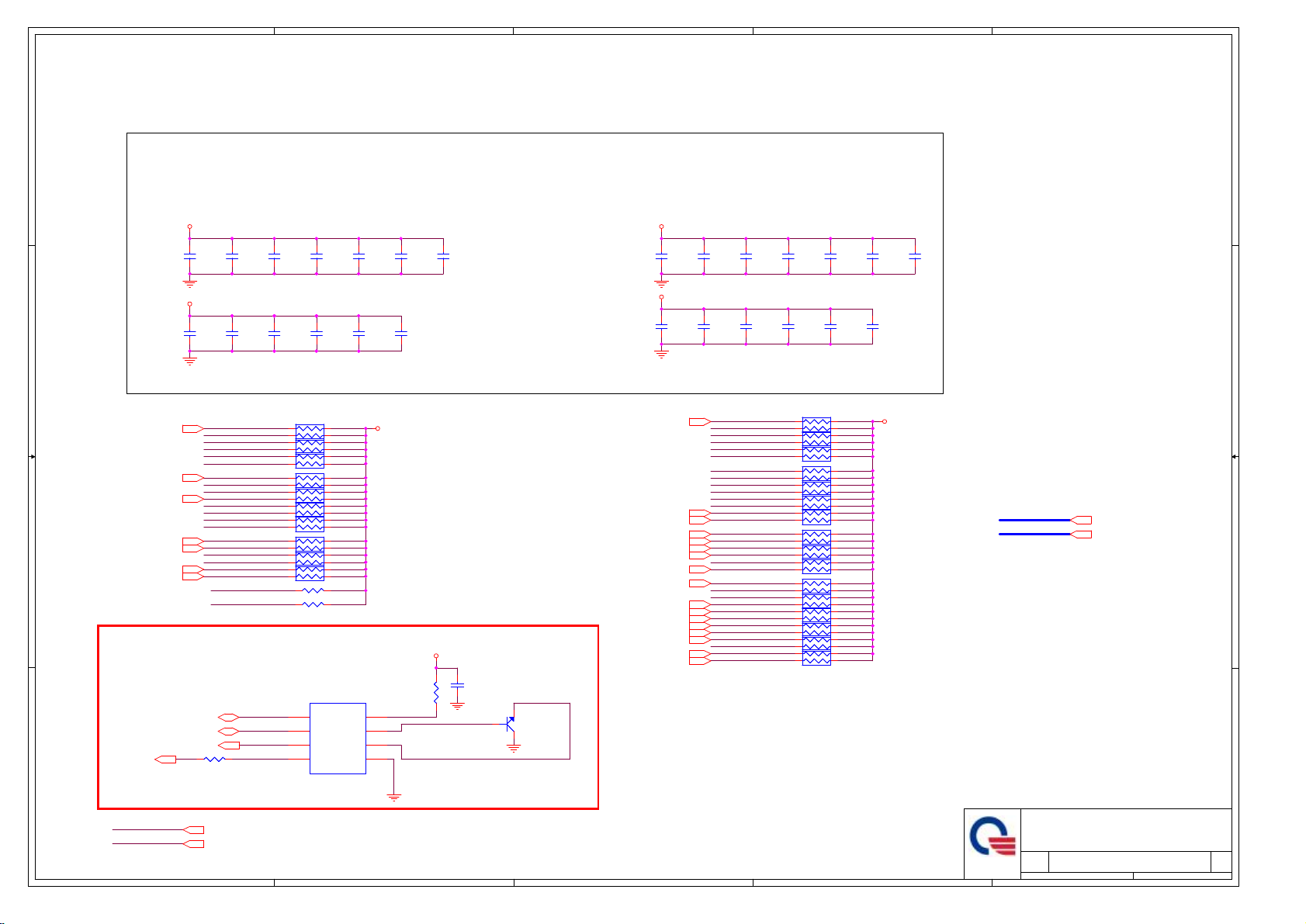

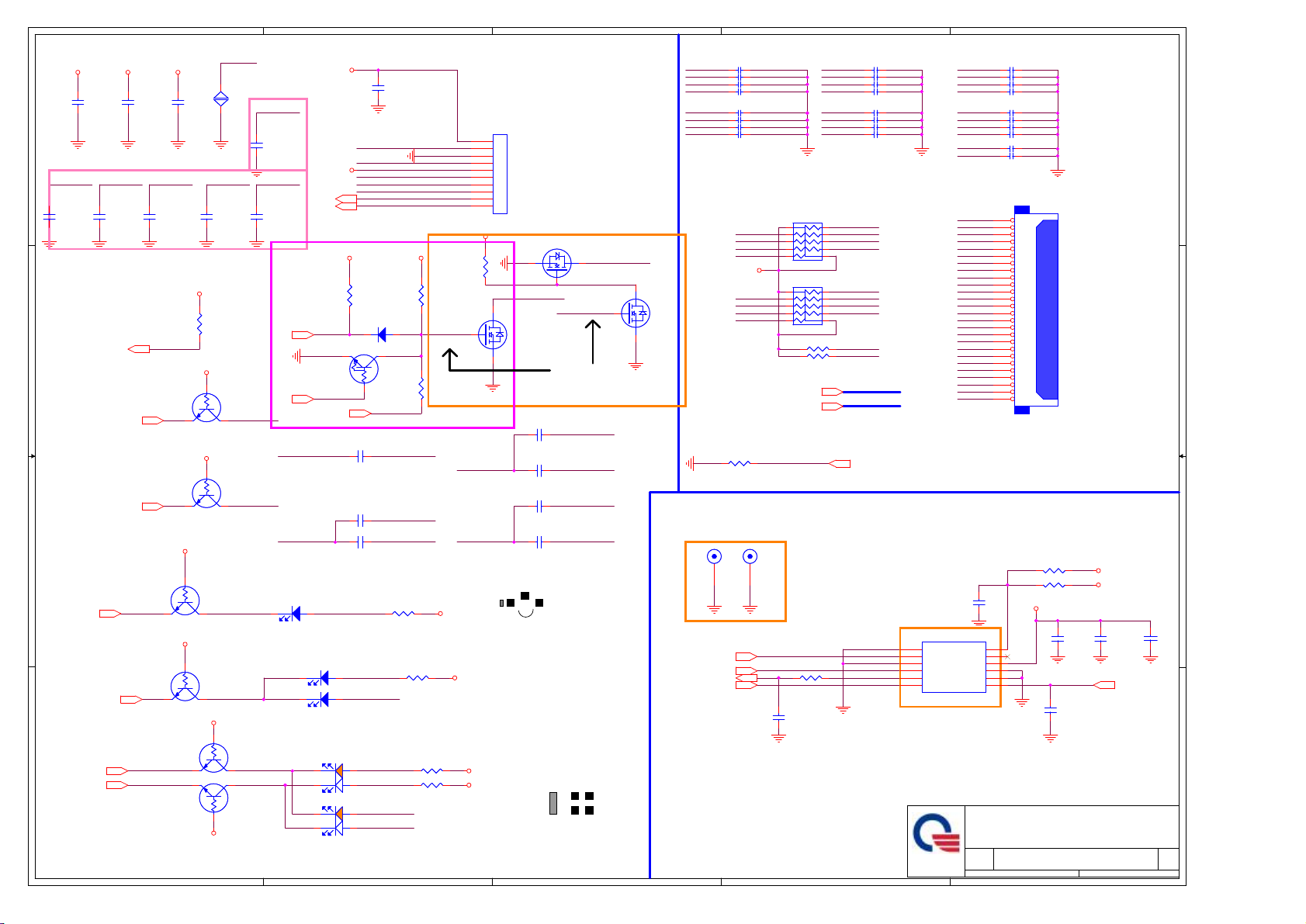

Page 3

5

H_A#[35:3][5]

DD

H_ADSTB#0[5]

H_REQ#[4:0][5]

H_A#[35:3]

CC

H_ADSTB#1[5]

H_A20M#[19]

H_FERR#[19]

H_IGNNE#[19]

H_STPCLK#[19]

H_INTR[19]

H_NMI[19]

+1.05V

H_SMI#[19]

R174*51/F_4R174*51/F_4

For QC CPU

PV Stage:Change to short pad

H_THERMDA2[4]

H_THERMDC2[4]

0_4*0_4

R30

R30

*54.9/F_4

*54.9/F_4

R29*1K/F_4R29*1K/F_4

CLK_CPU_ITP#[2]

CLK_CPU_ITP[2]

TP5TP5

R23

R23

54.9/F_4

54.9/F_4

R28*0_4/SR28*0_4/S

BB

AA

MODEL UT5 Quad CoreUT3 Dual Core

R28

+1.05V

R170

R170

*51/F_4

*51/F_4

ITP_TDI

ITP_TMS

ITP_TCK

ITP_TDO

ITP_TRST#

H_CPURST#

ITP_TCK

C169

C169

*100P/50V_4

*100P/50V_4

5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

ITP_BPM1#0

ITP_BPM1#1

ITP_BPM1#2

ITP_BPM1#3

GTLREF_CTL

H_GTLREF2

H_THERMDA2

H_THERMDC2

TP2TP2

TP1TP1

TP3TP3

Populate ITP700Flex for bringup

R20

R20

54.9/F_4

54.9/F_4

ITP_RST#

4

U34A

U34A

J4

A[3]#

L5

ADDR GROUP 0 ADDR GROUP 1

ADDR GROUP 0 ADDR GROUP 1

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

Quard Core Only

Quard Core Only

F6

TDI_1/RSV

D3

TDO_2/RSV

N5

BMP_1#[0]/RSV

M4

BMP_1#[1]/RSV

B2

BMP_1#[2]/RSV

AE8

BMP_1#[3]/VSS

D8

DCLKPH_1/VSS

F8

ACLKPH_1/VSS

D22

GTLREF_2/RSV

T2

THRMDA_1/RSV

V3

THRMDC_1/RSV

AA8

HFPLL_1/VSS

AC8

SPARE_1[4]/VSS

AA7

BR1#/VCC

Penryn Ball-out Rev 1a

Penryn Ball-out Rev 1a

R3154.9/F_4R3154.9/F_4

R3254.9/F_4R3254.9/F_4

JITP1

JITP1

1

TDI

2

TMS

5

TCK

7

TDO

3

TRST#

12

RESET#

11

FBO

8

BCLKN

9

BCLKP

10

GND0

14

GND1

16

GND2

18

GND3

20

GND4

22

GND5

*ITP700Flex

*ITP700Flex

4

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

CONTROL XDP/ITP SIGNALS

CONTROL XDP/ITP SIGNALS

IERR#

INIT#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

ICH

ICH

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

RSVD[06]

TDI

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

GND_0

GND_1

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

D21

A24

B25

C7

A22

A21

D2

ITP_TCK

ITP_TRST#

VTT0

VTT1

VTAP

DBR#

DBA#

NC0

NC1

H_IERR#

R13849.9/F_4R13849.9/F_4

H_RS#0

H_RS#1

H_RS#2

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

R61*0_4R61*0_4

R12968_4R12968_4

CPU_TEST2

CPU_TEST1

+1.05V

27

28

26

SYS_RST#

25

24

ITP_BPM#0

23

ITP_BPM#1

21

ITP_BPM#2

19

ITP_BPM#3

17

ITP_BPM#4

15

ITP_BPM#5

13

4

6

29

30

H_ADS#[5]

H_BNR#[5]

H_BPRI#[5]

H_DEFER#[5]

H_DRDY#[5]

H_DBSY#[5]

HBREQ#0[5]

H_INIT#[19]

H_LOCK#[5]

H_CPURST#[5]

H_RS#[2:0][5]

H_TRDY#[5]

H_HIT#[5]

H_HITM#[5]

SYS_RST#[21]

H_PROCHOT#[34]

+1.05V

H_THERMDA[4]

H_THERMDC[4]

PM_THRMTRIP#[6,19]

CLK_CPU_BCLK[2]

CLK_CPU_BCLK#[2]

R141*1K/F_4R141*1K/F_4

R151*1K/F_4R151*1K/F_4

C21*.1U/10V_4C21*.1U/10V_4

C19.1U/10V_4C19.1U/10V_4

EMI add

ITP_BPM#5

+1.05V

+1.05V

R175

R175

*51/F_4

*51/F_4

3

3

+1.05V

H_DSTBN#0[5]

H_DSTBP#0[5]

R543

R543

1K/F_4

1K/F_4

R542

R542

2K/F_4

2K/F_4

CPU_BSEL0[2]

CPU_BSEL1[2]

CPU_BSEL2[2]

H_D#[63:0][5]

H_DINV#0[5]

H_D#[63:0]

TP7TP7

TP61TP61

TP62TP62

TP63TP63

TP8TP8

H_DSTBN#1[5]

H_DSTBP#1[5]

H_DINV#1[5]

H_GTLREF

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

CPU_TEST1

CPU_TEST2

CPU_TEST3

CPU_TEST4

CPU_TEST5

CPU_TEST6

CPU_TEST7

U34B

U34B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

C3

TEST7

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Penryn Ball-out Rev 1a

Penryn Ball-out Rev 1a

For QC Support

Don't install for DCChange to +5V

+1.05V

R177

R177

*10K/F_4

GTLREF_CTL

+1.05V

R36

R36

*51/F_4

*51/F_4

*10K/F_4

R35

R35

*51/F_4

*51/F_4

R180

R180

*10K/F_4

*10K/F_4

R34

R34

*51/F_4

*51/F_4

DATA GRP 0

DATA GRP 0

DATA GRP 1

DATA GRP 1

MISC

MISC

+5V

2

R33

R33

*51/F_4

*51/F_4

ITP_BPM1#0

ITP_BPM1#1

ITP_BPM1#2

ITP_BPM1#3

2

+1.05V[2,4,5,6,8,9,19,22,33,34]

H_D#32

Y22

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

DATA GRP 2

DATA GRP 2

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

DATA GRP 3

DATA GRP 3

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

R185

R185

*100K/F_4

*100K/F_4

Q11

Q11

*MMBT3904-7-F

*MMBT3904-7-F

1 3

ITP_BPM1#0 ITP_BPM#0

ITP_BPM1#1 ITP_BPM#1

ITP_BPM1#2 ITP_BPM#2

ITP_BPM1#3 ITP_BPM#3

2

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

3

2

1

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

H_GTLREF2

Q10

Q10

*2N7002

*2N7002

BSS138

R24*0_4R24*0_4

R25*0_4R25*0_4

R26*0_4R26*0_4

R27*0_4R27*0_4

H_D#[63:0]

H_DSTBN#2[5]

H_DSTBP#2[5]

H_DINV#2[5]

H_D#[63:0]

H_DSTBN#3[5]

H_DSTBP#3[5]

H_DINV#3[5]

R55124.9/F_4R55124.9/F_4

R54949.9/F_4R54949.9/F_4

R5124.9/F_4R5124.9/F_4

R5449.9/F_4R5449.9/F_4

H_DPRSTP#[6,19,34]

H_DPSLP#[19]

H_DPWR#[5]

H_PWRGD[19]

H_CPUSLP#[5]

PM_PSI#[34]

NB5

NB5

NB5

1

03

+1.05V

R150

R150

*1K/F_4

*1K/F_4

R154

R154

*2K/F_4

*2K/F_4

PROJECT : OP6/7

PROJECT : OP6/7

PROJECT : OP6/7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

Date:Sheet of

Date:Sheet of

Date:Sheet of

Penryn 1/2

Penryn 1/2

Penryn 1/2

337Tuesday, January 20, 2009

337Tuesday, January 20, 2009

1

337Tuesday, January 20, 2009

SI

SI

SI

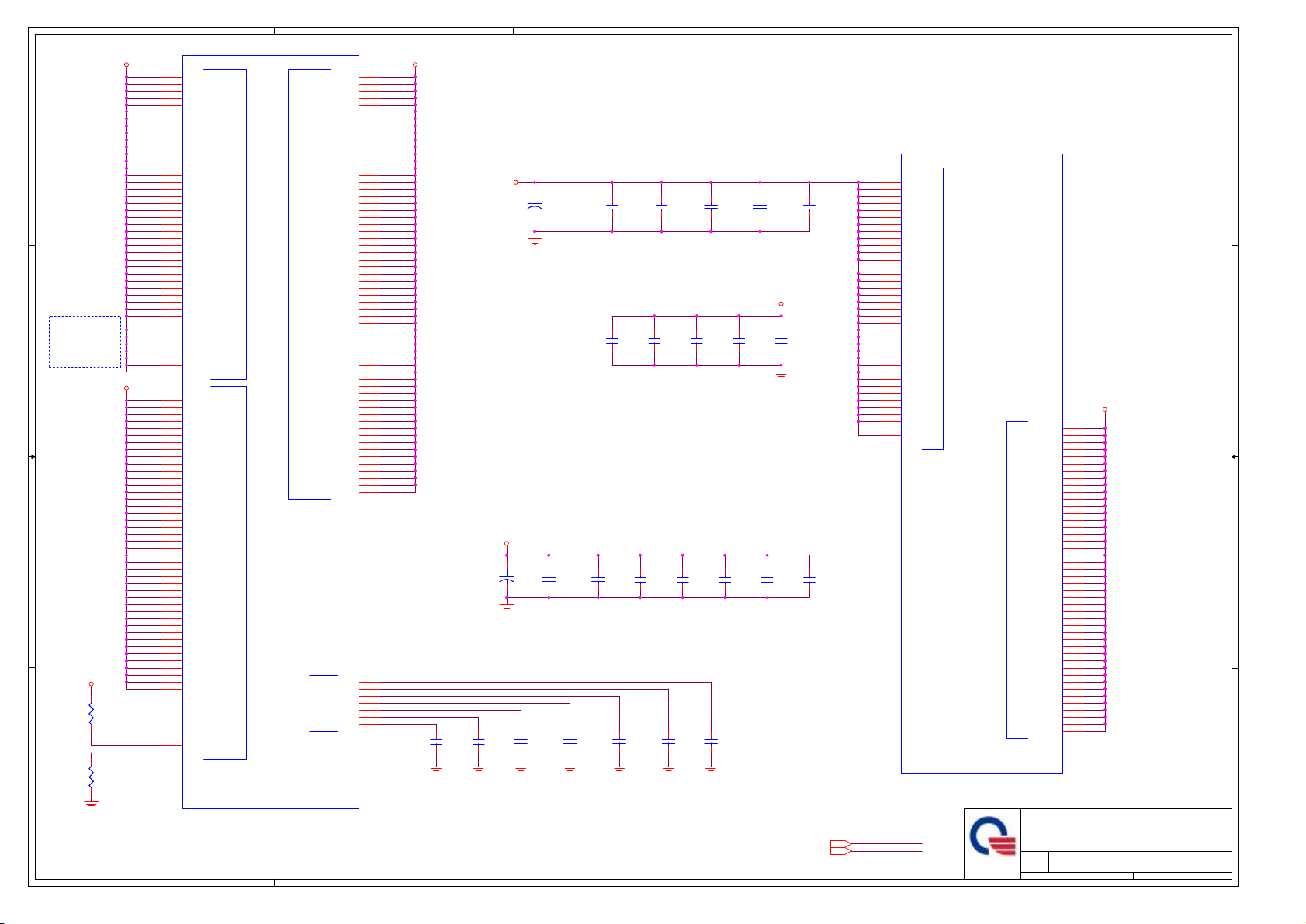

Page 4

5

+VCORE

C206

C206

C66

C66

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

C67

C67

22U/6.3V_8

22U/6.3V_8

C205

C205

22U/6.3V_8

22U/6.3V_8

C31

C31

22U/6.3V_8

22U/6.3V_8

C207

C207

22U/6.3V_8

22U/6.3V_8

C28

C28

22U/6.3V_8

22U/6.3V_8

C68

C68

22U/6.3V_8

22U/6.3V_8

C99

C99

22U/6.3V_8

22U/6.3V_8

C70

C70

.1U/10V_4

.1U/10V_4

U11*EMC-1403U11*EMC-1403

VCC

SCLK

DP1

SDA

DN1

ALERT#

DP2

OVERT#

GND6DN2

22U/6.3V_8

C98

C98

22U/6.3V_8

22U/6.3V_8

C93

C93

22U/6.3V_8

22U/6.3V_8

C30

C30

22U/6.3V_8

22U/6.3V_8

C208

C208

22U/6.3V_8

22U/6.3V_8

C29

C29

22U/6.3V_8

22U/6.3V_8

C64

C64

22U/6.3V_8

22U/6.3V_8

C95

C95

22U/6.3V_8

22U/6.3V_8

C39

C39

.1U/10V_4

.1U/10V_4

1

2

3

4

5

DD

CC

+1.05V

C72

C72

.1U/10V_4

.1U/10V_4

BB

MBCLK2

MBDATA2

SYS_SHDN-1#

PM_THRM_R#

10

9

8

7

C201

C201

22U/6.3V_8

22U/6.3V_8

C63

C63

22U/6.3V_8

22U/6.3V_8

C97

C97

22U/6.3V_8

22U/6.3V_8

C33

C92

C92

22U/6.3V_8

22U/6.3V_8

C26

C26

22U/6.3V_8

22U/6.3V_8

C69

C69

22U/6.3V_8

22U/6.3V_8

C203

C203

22U/6.3V_8

22U/6.3V_8

C32

C32

22U/6.3V_8

22U/6.3V_8

C61

C61

.1U/10V_4

.1U/10V_4

LM86VCC

H_THERMDA

H_THERMDC

C204

C204

22U/6.3V_8

22U/6.3V_8

C62

C62

22U/6.3V_8

22U/6.3V_8

C96

C96

22U/6.3V_8

22U/6.3V_8

C27

C27

22U/6.3V_8

22U/6.3V_8

C65

C65

22U/6.3V_8

22U/6.3V_8

C202

C202

22U/6.3V_8

22U/6.3V_8

C94

C94

22U/6.3V_8

22U/6.3V_8

C75

C75

.1U/10V_4

.1U/10V_4

C176

C176

*100P/50V_4

*100P/50V_4

C45

C45

.1U/10V_4

.1U/10V_4

H_THERMDA2[3]

H_THERMDC2[3]

For QC

R132

R132

10K_4

10K_4

MBCLK2[15,29]

MBDATA2[15,29]

AA

5

R131

R131

10K_4

10K_4

MBCLK2

MBDATA2

4

PM_THRM_R#

4

+VCORE +VCORE

+3V

R613

R613

*0_4/S

*0_4/S

LM86VCC

R161

R161

10K_4

10K_4

U9

U9

8

7

6

4

EMC1402-1-ACZL-TR

EMC1402-1-ACZL-TR

ADDRESS: 98H

SCLK

SDA

ALERT#

OVERT#

U34C

U34C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Penryn Ball-out Rev 1a

Penryn Ball-out Rev 1a

25mils

VCC

DXP

DXN

GND

VCCSENSE

VSSSENSE

1

2

3

5

R611*0_6/S R611*0_6/S

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

.

.

C811

C811

.1U/10V_4

.1U/10V_4

C158

C158

100P/50V_4

100P/50V_4

PM_THRM#[21]

3

+1.05V

R46

R46

100/F_4

100/F_4

+VCORE

H_THERMDA[3]

H_THERMDC[3]

SYS_SHDN-1#

3

C107

C107

10U/6.3V_8

10U/6.3V_8

C807

C807

.01U/16V_4

.01U/16V_4

R48

R48

100/F_4

100/F_4

+1.5V

CPU_VID0[34]

CPU_VID1[34]

CPU_VID2[34]

CPU_VID3[34]

CPU_VID4[34]

CPU_VID5[34]

CPU_VID6[34]

VCCSENSE[34]

VSSSENSE[34]

R121*0_4R121*0_4

R120*0_4/SR120*0_4/S

Q8

Q8

MMBT3904-7-F

MMBT3904-7-F

2

1 3

C803

C803

10U/6.3V_8

10U/6.3V_8

D8

D8

*RB501V-40

*RB501V-40

2 1

D9

D9

2 1

RB501V-40

RB501V-40

R11810K_4R11810K_4

D10

D10

2 1

*RB501V-40

*RB501V-40

2

SYS_SHDN#[31,32]

3920_RST#[29,31]

ECPWROK[6,21,29]

+3V

VGA_OVT#[15]

2

+3V[2,6,9,10,11,12,14,15,17,18,19,20,21,22,24,25,26,27,28,29,30,33,34,37]

+1.05V[2,3,5,6,8,9,19,22,33,34]

+1.5V[9,19,20,22,28,30,33,37]

+VCORE[34]

U34D

U34D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Penryn Ball-out Rev 1a

Penryn Ball-out Rev 1a

1

P6

VSS[082]

P21

VSS[083]

P24

VSS[084]

R2

VSS[085]

R5

VSS[086]

R22

VSS[087]

R25

VSS[088]

T1

VSS[089]

T4

VSS[090]

T23

VSS[091]

T26

VSS[092]

U3

VSS[093]

U6

VSS[094]

U21

VSS[095]

U24

VSS[096]

V2

VSS[097]

V5

VSS[098]

V22

VSS[099]

V25

VSS[100]

W1

VSS[101]

W4

VSS[102]

W23

VSS[103]

W26

VSS[104]

Y3

VSS[105]

Y6

VSS[106]

Y21

VSS[107]

Y24

VSS[108]

AA2

VSS[109]

AA5

VSS[110]

AA11

VSS[112]

AA14

VSS[113]

AA16

VSS[114]

AA19

VSS[115]

AA22

VSS[116]

AA25

VSS[117]

AB1

VSS[118]

AB4

VSS[119]

AB8

VSS[120]

AB11

VSS[121]

AB13

VSS[122]

AB16

VSS[123]

AB19

VSS[124]

AB23

VSS[125]

AB26

VSS[126]

AC3

VSS[127]

AC6

VSS[128]

AC11

VSS[130]

AC14

VSS[131]

AC16

VSS[132]

AC19

VSS[133]

AC21

VSS[134]

AC24

VSS[135]

AD2

VSS[136]

AD5

VSS[137]

AD8

VSS[138]

AD11

VSS[139]

AD13

VSS[140]

AD16

VSS[141]

AD19

VSS[142]

AD22

VSS[143]

AD25

VSS[144]

AE1

VSS[145]

AE4

VSS[146]

AE11

VSS[148]

AE14

VSS[149]

AE16

VSS[150]

AE19

VSS[151]

AE23

VSS[152]

AE26

VSS[153]

A2

VSS[154]

AF6

VSS[155]

AF8

VSS[156]

AF11

VSS[157]

AF13

VSS[158]

AF16

VSS[159]

AF19

VSS[160]

AF21

VSS[161]

A25

AF25

VSS[163]

.

.

PROJECT : OP6/7

PROJECT : OP6/7

PROJECT : OP6/7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

NB5

NB5

NB5

Date:Sheet of

Date:Sheet of

Date:Sheet of

Penryn & TH Monitor 2/2

Penryn & TH Monitor 2/2

Penryn & TH Monitor 2/2

1

04

437Tuesday, January 20, 2009

437Tuesday, January 20, 2009

437Tuesday, January 20, 2009

SI

SI

SI

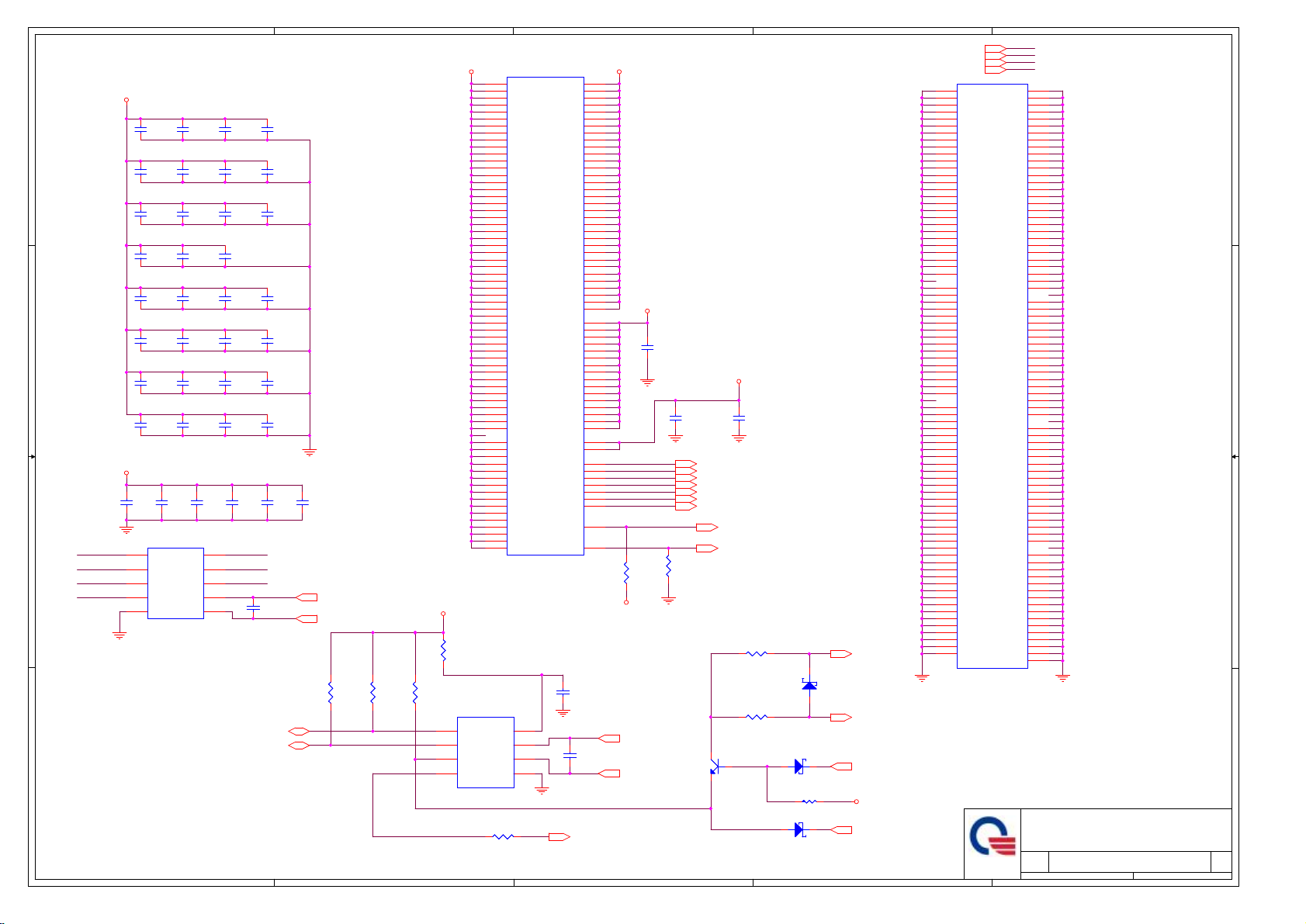

Page 5

5

U40J

U40I

U40I

AU48

VSS_1

AR48

VSS_2

AL48

VSS_3

BB47

VSS_4

AW47

VSS_5

AN47

VSS_6

AJ47

VSS_7

AF47

VSS_8

AD47

DD

CC

BB

AA

AB47

BD46

BA46

AY46

AV46

AR46

AM46

BF44

AH44

AD44

AA44

BC43

AV43

AU43

AM43

BG42

AY42

AT42

AN42

AJ42

AE42

BD41

AU41

AM41

AH41

AD41

AA41

BG40

BB40

AV40

AN40

AT39

AM39

AJ39

AE39

BH38

BC38

BA38

AU38

AH38

AD38

AA38

BF37

BB37

AW37

AT37

AN37

AJ37

BG36

BD36

AK15

AU36

Y47

T47

N47

L47

G47

V46

R46

P46

H46

F46

Y44

U44

T44

M44

F44

J43

C43

N42

L42

Y41

U41

T41

M41

G41

B41

H40

E40

N39

L39

B39

Y38

U38

T38

J38

F38

C38

H37

C37

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

CANTIGA_GM

CANTIGA_GM

VSS

VSS

5

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

AM36

AE36

P36

L36

J36

F36

B36

AH35

AA35

Y35

U35

T35

BF34

AM34

AJ34

AF34

AE34

W34

B34

A34

BG33

BC33

BA33

AV33

AR33

AL33

AH33

AB33

P33

L33

H33

N32

K32

F32

C32

A31

AN29

T29

N29

K29

H29

F29

A29

BG28

BD28

BA28

AV28

AT28

AR28

AJ28

AG28

AE28

AB28

Y28

P28

K28

H28

F28

C28

BF26

AH26

AF26

AB26

AA26

C26

B26

BH25

BD25

BB25

AV25

AR25

AJ25

AC25

Y25

N25

L25

J25

G25

E25

BF24

AD12

AY24

AT24

AJ24

AH24

AF24

AB24

R24

L24

K24

J24

G24

F24

E24

BH23

AG23

Y23

B23

A23

AJ6

BG21

AW21

AU21

AP21

AN21

AH21

AF21

AB21

BC20

BA20

AW20

AT20

AJ20

AG20

BG19

BG17

BC17

AW17

AT17

BA16

AU16

AN16

BG15

AC15

W15

BG14

AA14

BG13

BC13

BA13

AN13

AJ13

AE13

BF12

AV12

AT12

AM12

AA12

BD11

BB11

AY11

AN11

AH11

BG10

AV10

AT10

AJ10

AE10

AA10

M10

BC9

AN9

AM9

AD9

BH8

R21

M21

G21

Y20

N20

K20

F20

C20

A20

A18

R17

M17

H17

C17

N16

K16

G16

E16

A15

C14

N13

G13

E13

A12

Y11

N11

G11

C11

BF9

BB8

AV8

AT8

L12

J21

L13

J12

G9

B9

U40J

CANTIGA_GM

CANTIGA_GM

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_235

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

4

VSS

VSS

4

VSS NCTF

VSS NCTF

VSS SCB

VSS SCB

NC

NC

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

VSS_NCTF_15

VSS_NCTF_16

VSS_SCB_1

VSS_SCB_2

VSS_SCB_3

VSS_SCB_4

VSS_SCB_5

NC_26

NC_27

NC_28

NC_29

NC_30

NC_31

NC_32

NC_33

NC_34

NC_35

NC_36

NC_37

NC_38

NC_39

NC_40

NC_41

NC_42

AH8

Y8

L8

E8

B8

AY7

AU7

AN7

AJ7

AE7

AA7

N7

J7

BG6

BD6

AV6

AT6

AM6

M6

C6

BA5

AH5

AD5

Y5

L5

J5

H5

F5

BE4

BC3

AV3

AL3

R3

P3

F3

BA2

AW2

AU2

AR2

AP2

AJ2

AH2

AF2

AE2

AD2

AC2

Y2

M2

K2

AM1

AA1

P1

H1

U24

U28

U25

U29

AF32

AB32

V32

AJ30

AM29

AF29

AB29

U26

U23

AL20

V20

AC19

AL17

AJ17

AA17

U17

BH48

BH1

A48

C1

A3

E1

D2

C3

B4

A5

A6

A43

A44

B45

C46

D47

B47

A46

F48

E48

C48

B48

3

2

1

05

U40A

AD14

AA13

AA11

AD11

AD10

AD13

AE12

AE14

AE11

M11

AD8

AD3

AD7

AC1

AC3

AG2

AD6

M9

N12

M5

P13

N10

M3

Y10

Y12

Y14

W2

AA8

AA9

AE9

AA2

AA3

AF3

AE3

AE8

C12

E11

A11

B11

2

F2

G8

F8

E6

G2

H6

H2

F6

D4

H3

J1

J2

J6

P2

L2

R2

N9

L6

J3

N2

R1

N5

N6

N8

L7

Y3

Y6

Y7

Y9

C5

E3

U40A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CANTIGA_GM

CANTIGA_GM

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

HOST

HOST

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_D#[63:0][3]

+1.05V

R621

R621

221/F_4

221/F_4

H_SWING

R622

R622

C837

C837

100/F_4

100/F_4

.1U/10V_4

.1U/10V_4

H_RCOMP

R196

R196

24.9/F_4

24.9/F_4

+1.05V

R199

R199

1K/F_4

1K/F_4

R198

R198

2K/F_4

2K/F_4

3

H_CPURST#[3]

H_CPUSLP#[3] H_RS#[2:0][3]

C844

C844

.1U/10V_4

.1U/10V_4

+1.05V

C1025

C1025

.1U/10V_4

.1U/10V_4

EMI add

H_AVREF

H_AVREF

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_A#3

A14

H_A#4

C15

H_A#5

F16

H_A#6

H13

H_A#7

C18

H_A#8

M16

H_A#9

J13

H_A#10

P16

H_A#11

R16

H_A#12

N17

H_A#13

M13

H_A#14

E17

H_A#15

P17

H_A#16

F17

H_A#17

G20

H_A#18

B19

H_A#19

J16

H_A#20

E20

H_A#21

H16

H_A#22

J20

H_A#23

L17

H_A#24

A17

H_A#25

B17

H_A#26

L16

H_A#27

C21

H_A#28

J17

H_A#29

H20

H_A#30

B18

H_A#31

K17

H_A#32

B20

H_A#33

F21

H_A#34

K21

H_A#35

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

H_REQ#0

B15

H_REQ#1

K13

H_REQ#2

F13

H_REQ#3

B13

H_REQ#4

B14

H_RS#0

B6

H_RS#1

F12

H_RS#2

C8

PROJECT : OP6/7

PROJECT : OP6/7

PROJECT : OP6/7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

NB5

NB5

NB5

Date:Sheet of

Date:Sheet of

Date:Sheet of

Cantiga Host & VSS 1/5

Cantiga Host & VSS 1/5

Cantiga Host & VSS 1/5

H_A#[35:3][3]

H_ADS#[3]

H_ADSTB#0[3]

H_ADSTB#1[3]

H_BNR#[3]

H_BPRI#[3]

HBREQ#0[3]

H_DEFER#[3]

H_DBSY#[3]

CLK_MCH_BCLK[2]

CLK_MCH_BCLK#[2]

H_DPWR#[3]

H_DRDY#[3]

H_HIT#[3]

H_HITM#[3]

H_LOCK#[3]

H_TRDY#[3]

H_DINV#0[3]

H_DINV#1[3]

H_DINV#2[3]

H_DINV#3[3]

H_DSTBN#0[3]

H_DSTBN#1[3]

H_DSTBN#2[3]

H_DSTBN#3[3]

H_DSTBP#0[3]

H_DSTBP#1[3]

H_DSTBP#2[3]

H_DSTBP#3[3]

H_REQ#[4:0][3]

+1.05V[2,3,4,6,8,9,19,22,33,34]

1

SI

SI

537Tuesday, January 20, 2009

537Tuesday, January 20, 2009

537Tuesday, January 20, 2009

SI

Page 6

5

MCH_CFG_5 DMIx2 selection

Low: DMIx2

High: DMIx4 (Default)

MCH_CFG_16 FSB Dynamic ODT

Low: Dynamic ODT disabled

High: Dynamic ODT enabled (Default)

MCH_CFG_9 PCI Express Graphic Lane

Low: Reverse Lane

DD

High: Normal operation(Default)

MCH_CFG_19 DMI Lane Reversal

Low: Normal (Default)

High: Lane Reserved

MCH_CFG_6 iTPM Host Interface

Low: iTPM Host Interface enabled

High: iTPM Host Interface disabled (Default)

MCH_CFG_7 Intel (R) Management Engine Crypto

Low: Intel (R) Management Engine Crypto

TLS cipher suite with no confidentiality

High: Intel (R) Management Engine Crypto

TLS cipher suite with no confidentiality (Default)

MCH_CFG_10 PCIe Lookback Enable

Low: Enabled

High: Disabled (Default)

MCH_CFG_12/13 XOR/ALLZ/CLOCK Un-gating

MCH_CFG_13MCH_CFG_12

00

1

0

CC

11

BB

PM_SYNC#[21]

H_DPRSTP#[3,19,34]

PM_EXTTS#0[10,11]

PM_EXTTS#1[11]

DELAY_VR_PWRGOOD[21,34]

PLT_RST-R#[12,20]

PM_THRMTRIP#[3,19]

DPRSLPVR[21,34]

+3V

R23510K_4R23510K_4

R23010K_4R23010K_4

AA

Configuration

Reserved

XOR Mode enabled

0

All-Z Mode enabled

1

Normal operation (Default)

MCH_BSEL0[2]

MCH_BSEL1[2]

MCH_BSEL2[2]

TP23TP23

TP64TP64

TP20TP20

TP22TP22

TP14TP14

TP12TP12

TP19TP19

TP18TP18

TP13TP13

TP15TP15

TP17TP17

TP25TP25

TP21TP21

TP24TP24

R201100/F_4R201100/F_4

PM_EXTTS#1

ACZ_BITCLK_MCH

R634

R634

*33_4

*33_4

C874

C874

*33P/50V_4

*33P/50V_4

5

TP9TP9

TP16TP16

TP11TP11

TP10TP10

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

PM_EXTTS#0

PM_EXTTS#1

RST_IN#_MCH

TP32TP32

TP29TP29

TP28TP28

AH10

AH12

AH13

AY21

BG23

BF23

BH18

BF18

AL34

AK34

AN35

AM35

AT40

AT11

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

M36

N36

R33

T33

AH9

K12

T24

B31

B2

M1

T25

R25

P25

P20

P24

C25

N24

M24

E21

C23

C24

N21

P21

T21

R20

M20

L21

H21

P29

R28

T28

R29

B7

N33

P32

T20

R32

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

F1

A47

U40B

U40B

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD14

RSVD15

RSVD16

RSVD17

RSVD20

RSVD22

RSVD23

RSVD24

RSVD25

ME_JTAG_TCK

ME_JTAG_TDI

ME_JTAG_TDO

ME_JTAG_TMS

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_SYNC#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

NC_26

CANTIGA_GM

CANTIGA_GM

CFGRSVD

CFGRSVD

NC

NC

ME JTAG

ME JTAG

PM

PM

4

SA_CK_0

SA_CK_1

SB_CK_0

SB_CK_1

SA_CK#_0

SA_CK#_1

SB_CK#_0

SB_CK#_1

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DDR CLK/ CONTROL/COMPENSATION

DDR CLK/ CONTROL/COMPENSATION

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

CLK

CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI

DMI

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

GRAPHICS VID

GRAPHICS VID

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

MEHDA

MEHDA

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

MISC

MISC

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

4

AP24

AT21

AV24

AU20

AR24

AR21

AU24

AV20

BC28

AY28

AY36

BB36

BA17

AY16

AV16

AR13

BD17

AY17

BF15

AY13

SM_RCOMP

BG22

SM_RCOMP#

BH21

SM_RCOMP_VOH

BF28

SM_RCOMP_VOL

BH28

+0.9VSMVREF_MCH

AV42

SW_PWROK_NB

AR36

SM_REXT

BF17

TP_SM_DRAMRST#

BC36

B38

A38

E41

F41

F43

E43

DMI_TXN0

AE41

DMI_TXN1

AE37

DMI_TXN2

AE47

DMI_TXN3

AH39

DMI_TXP0

AE40

DMI_TXP1

AE38

DMI_TXP2

AE48

DMI_TXP3

AH40

DMI_RXN0

AE35

DMI_RXN1

AE43

DMI_RXN2

AE46

DMI_RXN3

AH42

DMI_RXP0

AD35

DMI_RXP1

AE44

DMI_RXP2

AF46

DMI_RXP3

AH43

GFXVR_VID_0

B33

GFXVR_VID_1

B32

GFXVR_VID_2

G33

GFXVR_VID_3

F33

GFXVR_VID_4

E33

GFXVR_EN

C34

AH37

AH36

AN36

AJ35

AH34

DDPC_CTRLCLK

N28

DDPPC_CTRLDATA

M28

G36

E36

K36

H36

MCH_TSATN

B12

B28

B30

ACZ_SDIN3_MCH

B29

C29

A28

M_A_CLK0[10]

M_A_CLK1[10]

M_B_CLK0[10]

M_B_CLK1[10]

M_A_CLK0#[10]

M_A_CLK1#[10]

M_B_CLK0#[10]

M_B_CLK1#[10]

M_A_CKE0[10,11]

M_A_CKE1[10,11]

M_B_CKE0[10,11]

M_B_CKE1[10,11]

M_A_CS#0[10,11]

M_A_CS#1[10,11]

M_B_CS#0[10,11]

M_B_CS#1[10,11]

M_A_ODT0[10,11]

M_A_ODT1[10,11]

M_B_ODT0[10,11]

M_B_ODT1[10,11]

R21980.6/F_4R21980.6/F_4

R20980.6/F_4R20980.6/F_4

R23710K_4R23710K_4

R207499/F_4R207499/F_4

TP34TP34

DREFCLK[2]

DREFCLK#[2]

DREFSSCLK[2]

DREFSSCLK#[2]

CLK_PCIE_3GPLL[2]

CLK_PCIE_3GPLL#[2]

DMI_TXN[3:0][20]

DMI_TXP[3:0][20]

DMI_RXN[3:0][20]

DMI_RXP[3:0][20]

TP66TP66

TP65TP65

TP33TP33

TP31TP31

TP30TP30

TP67TP67

CL_CLK0[21]

CL_DATA0[21]

ECPWROK[4,21,29]

CL_RST#0[21]

TP27TP27

TP26TP26

SDVO_CLK[18]

SDVO_DATA[18]

CLK_MCH_OE#[2]

MCH_ICH_SYNC#[21]

R20056.2/F_4R20056.2/F_4

R6380_4R6380_4

+1.8VSUS

MCH_CLVREF

3

+1.05V

R257

R257

1K/F_4

1K/F_4

0.35 V

R258

R258

C451

C451

499/F_4

499/F_4

.1U/10V_4

.1U/10V_4

+1.05V

ACZ_BITCLK_MCH[19]

ACZ_RST#_MCH[19]

ACZ_SDIN3[19]

ACZ_SDOUT_MCH[19]

ACZ_SYNC_MCH[19]

3

2

+3V[2,4,9,10,11,12,14,15,17,18,19,20,21,22,24,25,26,27,28,29,30,33,34,37]

+1.8VSUS[8,9,10,28,33,36]

+1.05V[2,3,4,5,8,9,19,22,33,34]

+1.05V_PEG[2,3,4,5,8,9,19,22,33,34]

U40C

U40C

TP70TP70

LA_CLK#[17]

LA_CLK[17]

LB_CLK#[17]

LB_CLK[17]

LA_DATAN0[17]

LA_DATAN1[17]

LA_DATAN2[17]

LA_DATAP0[17]

LA_DATAP1[17]

LA_DATAP2[17]

LB_DATAN0[17]

LB_DATAN1[17]

LB_DATAN2[17]

LB_DATAP0[17]

LB_DATAP1[17]

LB_DATAP2[17]

C425

C425

470P/50V_4

470P/50V_4

TP69TP69

TP68TP68

TP35TP35

TP37TP37

.01U/16V_4

.01U/16V_4

.01U/16V_4

.01U/16V_4

DPST_PWM_INT

LVDS_BLON_INT

L_CTRL_CLK

L_CTRL_DATA

EDIDCLK_INT

EDIDDATA_INT

DISP_ON_INT

LVDS_IBG

LVDS_VBG

LA_DATAN3

LA_DATAP3

LB_DATAN3

LB_DATAP3

TV_DCONSEL0

TV_DCONSEL1

DDCCLK_INT

DDCDATA_INT

HSYNC_INT

CRTIREF

VSYNC_INT

C363

C363

C386

C386

+1.8VSUS

R253

R253

*1K/F_4

*1K/F_4

R254*0_4/SR254*0_4/S

R251

R251

*1K/F_4

*1K/F_4

CRT_B_1

CRT_G_1

CRT_R_1

L32

G32

M32

M33

K33

J33

M29

C44

B43

E37

E38

C41

C40

B37

A37

H47

E46

G40

A40

H48

D45

F40

B40

A41

H38

G37

J37

B42

G38

F37

K37

F25

H25

K25

H24

C31

E32

E28

G28

J28

G29

H32

J32

J29

E29

L29

C356

C356

2.2U/6.3V_6

2.2U/6.3V_6

C373

C373

2.2U/6.3V_6

2.2U/6.3V_6

L_BKLT_CTRL

L_BKLT_EN

L_CTRL_CLK

L_CTRL_DATA

L_DDC_CLK

L_DDC_DATA

L_VDD_EN

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSB_CLK#

LVDSB_CLK

LVDSA_DATA#_0

LVDSA_DATA#_1

LVDSA_DATA#_2

LVDSA_DATA#_3

LVDSA_DATA_0

LVDSA_DATA_1

LVDSA_DATA_2

LVDSA_DATA_3

LVDSB_DATA#_0

LVDSB_DATA#_1

LVDSB_DATA#_2

LVDSB_DATA#_3

LVDSB_DATA_0

LVDSB_DATA_1

LVDSB_DATA_2

LVDSB_DATA_3

TVA_DAC

TVB_DAC

TVC_DAC

TV_RTN

TV_DCONSEL_0

TV_DCONSEL_1

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_IRTN

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_TVO_IREF

CRT_VSYNC

CANTIGA_GM

CANTIGA_GM

+1.8VSUS

R225

R225

1K/F_4

1K/F_4

12

R222

R222

3.01K/F_4

3.01K/F_4

R218

R218

1K/F_4

1K/F_4

+0.9VSMVREF[10,36]

DPST_PWM[15,17]

LVDS_BLON[15,17]

EDIDCLK[14,15,17]

EDIDDATA[14,15,17]

DISP_ON[15,17]

CRT_B[14,18]

CRT_G[14,18]

CRT_R[14,18]

DDCCLK[15,18]

DDCDATA[15,18]

HSYNC_COM[14,18]

VSYNC_COM[14,18]

R636*0_4R636*0_4

R227*0_4R227*0_4

R229*10K/F_4R229*10K/F_4

+3V

R236*10K/F_4R236*10K/F_4

R640*0_4R640*0_4

R239*0_4R239*0_4

R637*0_4R637*0_4

R646*2.37K/F_4R646*2.37K/F_4

R211*75/F_4R211*75/F_4

R213*75/F_4R213*75/F_4

R212*75/F_4R212*75/F_4

R626*0_4R626*0_4

R628*0_4R628*0_4

R166*0_4R166*0_4

R215*150/F_4R215*150/F_4

R171*0_4R171*0_4

R179*0_4R179*0_4

R217*150/F_4R217*150/F_4

R228*0_4R228*0_4

R216*33_4R216*33_4

R630*1.02K/F_4R630*1.02K/F_4

R220*33_4R220*33_4

SM_RCOMP_VOH

SM_RCOMP_VOLPM_EXTTS#0

+0.9VSMVREF_MCH

C426

C426

.1U/10V_4

.1U/10V_4

HP SVTP TEST

2

PEG_TX#[15:0]

PEG_TX[15:0]

PEG_RX#[15:0]

PEG_RX[15:0]

LVDS

LVDS

TV

TV

VGA

VGA

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_10

PEG_TX#_11

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

PEG_TX#[15:0][12]

PEG_TX[15:0][12]

PEG_RX#[15:0][12]

PEG_RX[15:0][12]

T37

T36

H44

J46

L44

L40

N41

P48

N44

T43

U43

Y43

Y48

Y36

AA43

AD37

AC47

AD39

H43

J44

L43

L41

N40

P47

N43

T42

U42

Y42

W47

Y37

AA42

AD36

AC48

AD40

J41

M46

M47

M40

M42

R48

N38

T40

U37

U40

Y40

AA46

AA37

AA40

AD43

AC46

J42

L46

M48

M39

M43

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

For UMA HDMI Function

PEG_TX0

RP58*4P2R-0RP58*4P2R-0

2

4

RP59*4P2R-0RP59*4P2R-0

2

4

RP60*4P2R-0RP60*4P2R-0

2

4

RP61*4P2R-0RP61*4P2R-0

2

4

R552*20K/F_4R552*20K/F_4

+3V

PEG_TX#0

PEG_TX1

PEG_TX#1

PEG_TX2

PEG_TX#2

PEG_TX3

PEG_TX#3

HDMI_HPD_CON[18]

HPD# Inverting Level Shifting Circuit

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Custom

Custom

Custom

NB5

NB5

NB5

Date:Sheet of

Date:Sheet of

Date:Sheet of

1

06

+1.05V_PEG

PEG_COMP

R24149.9/F_4R24149.9/F_4

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

C_PEG_TX#0

C_PEG_TX#1

C_PEG_TX#2

C_PEG_TX#3

C_PEG_TX#4

C_PEG_TX#5

C_PEG_TX#6

C_PEG_TX#7

C_PEG_TX#8

C_PEG_TX#9

C_PEG_TX#10

C_PEG_TX#11

C_PEG_TX#12

C_PEG_TX#13

C_PEG_TX#14

C_PEG_TX#15

C_PEG_TX0

C_PEG_TX1

C_PEG_TX2

C_PEG_TX3

C_PEG_TX4

C_PEG_TX5

C_PEG_TX6

C_PEG_TX7

C_PEG_TX8

C_PEG_TX9

C_PEG_TX10

C_PEG_TX11

C_PEG_TX12

C_PEG_TX13

C_PEG_TX14

C_PEG_TX15

1

3

1

3

1

3

1

3

R631

R631

*0_4

*0_4

R558

R558

*100K/F_4

*100K/F_4

PROJECT : OP6/7

PROJECT : OP6/7

PROJECT : OP6/7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Cantiga DMI/DISP 2/5

Cantiga DMI/DISP 2/5

Cantiga DMI/DISP 2/5

2

int

int

R182

R182

*0_4

*0_4

C416.1U/10V_4C416.1U/10V_4

C423.1U/10V_4C423.1U/10V_4TP36TP36

C440.1U/10V_4C440.1U/10V_4

C431.1U/10V_4C431.1U/10V_4

C435.1U/10V_4C435.1U/10V_4

C437.1U/10V_4C437.1U/10V_4

C446.1U/10V_4C446.1U/10V_4

C455.1U/10V_4C455.1U/10V_4

C457.1U/10V_4C457.1U/10V_4

C447.1U/10V_4C447.1U/10V_4

C473.1U/10V_4C473.1U/10V_4

C465.1U/10V_4C465.1U/10V_4

C469.1U/10V_4C469.1U/10V_4

C433.1U/10V_4C433.1U/10V_4

C466.1U/10V_4C466.1U/10V_4

C470.1U/10V_4C470.1U/10V_4

C419.1U/10V_4C419.1U/10V_4

C418.1U/10V_4C418.1U/10V_4

C430.1U/10V_4C430.1U/10V_4

C424.1U/10V_4C424.1U/10V_4R221*150/F_4R221*150/F_4

C444.1U/10V_4C444.1U/10V_4

C445.1U/10V_4C445.1U/10V_4

C438.1U/10V_4C438.1U/10V_4

C453.1U/10V_4C453.1U/10V_4

C464.1U/10V_4C464.1U/10V_4R226*0_4R226*0_4

C439.1U/10V_4C439.1U/10V_4

C462.1U/10V_4C462.1U/10V_4

C458.1U/10V_4C458.1U/10V_4

C468.1U/10V_4C468.1U/10V_4

C432.1U/10V_4C432.1U/10V_4

C467.1U/10V_4C467.1U/10V_4

C471.1U/10V_4C471.1U/10V_4

dis

HDMI_HPD#

3

Q31

Q31

*2N7002

*2N7002

1

1

HDMI_HPD#

IN_D2[18]

IN_D2#[18]

IN_D1[18]

IN_D1#[18]

IN_D0[18]

IN_D0#[18]

IN_CLK[18]

IN_CLK#[18]

Level: 0.9V

637Tuesday, January 20, 2009

637Tuesday, January 20, 2009

637Tuesday, January 20, 2009

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

R550

R550

*7.5K/F_4

*7.5K/F_4

SI

SI

SI

Page 7

5

4

3

2

1

07

DD

M_A_DQ[63:0][10]

CC

BB

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AJ38

AJ41

AN38

AM38

AJ36

AJ40

AM44

AM42

AN43

AN44

AU40

AT38

AN41

AN39

AU44

AU42

AV39

AY44

BA40

BD43

AV41

AY43

BB41

BC40

AY37

BD38

AV37

AT36

AY38

BB38

AV36

AW36

BD13

AU11

BC11

BA12

AU13

AV13

BD12

BC12

AU10

BA11

BD9

AN8

AU5

AU6

AN10

AM11

AM5

AN12

AM13

AJ11

AJ12

BB9

BA9

AV9

AY8

BA6

AV5

AV7

AT9

AT5

AJ9

AJ8

U40D

U40D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

CANTIGA_GM

CANTIGA_GM

SA_BS_0

SA_BS_1

SA_BS_2

SA_RAS#

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_WE#

BD21

BG18

AT25

BB20

BD20

AY20

AM37

AT41

AY41

AU39

BB12

AY6

AT7

AJ5

AJ44

AT44

BA43

BC37

AW12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW24

BC21

BG26

BH26

BH17

AY25

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_BS#0[10,11]

M_A_BS#1[10,11]

M_A_BS#2[10,11]

M_A_RAS#[10,11]

M_A_CAS#[10,11]

M_A_WE#[10,11]

M_A_DM[7:0][10]

M_A_DQS[7:0][10]

M_A_DQS#[7:0][10]

M_A_A[14:0][10,11]

M_B_DQ[63:0][10]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25