Page 1

8

7

6

5

4

3

2

1

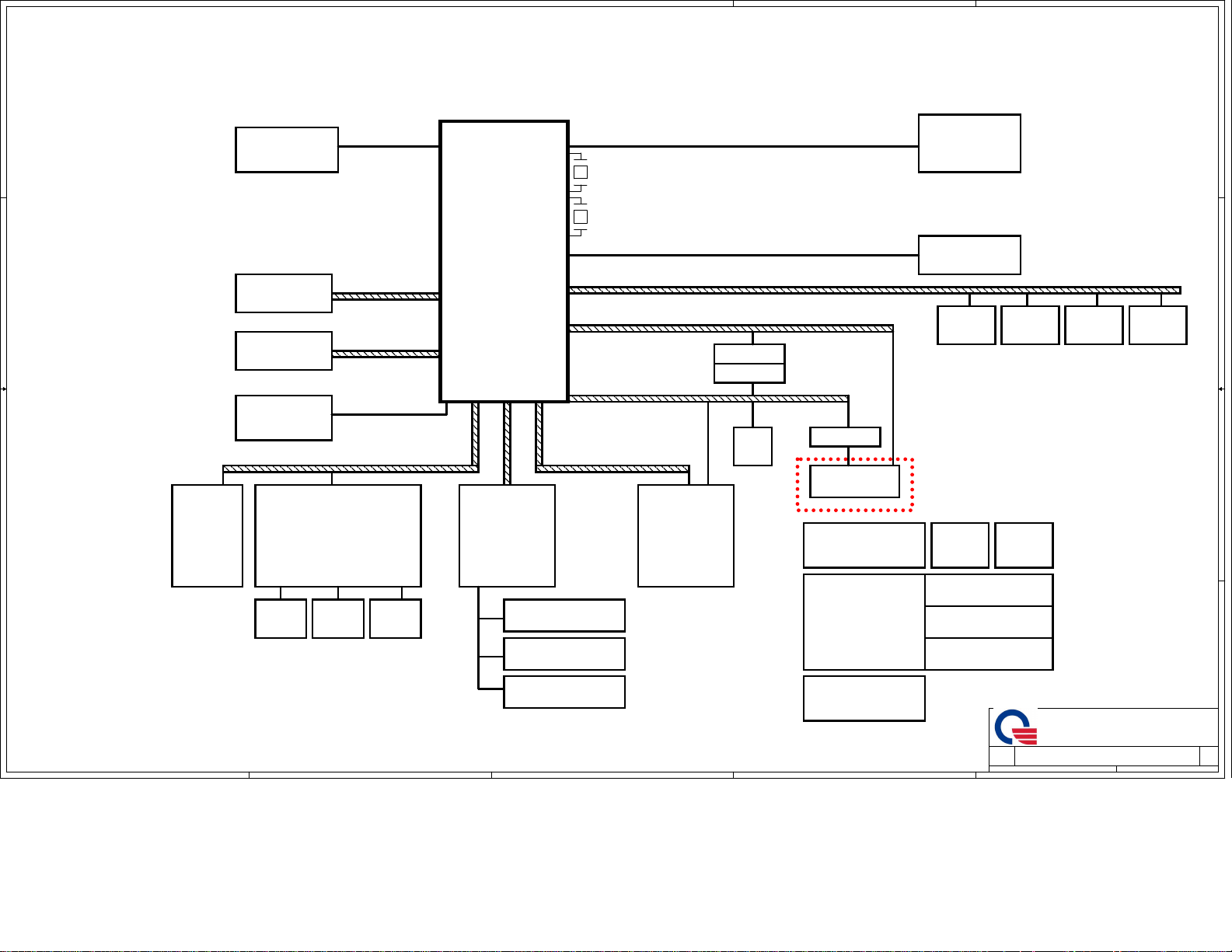

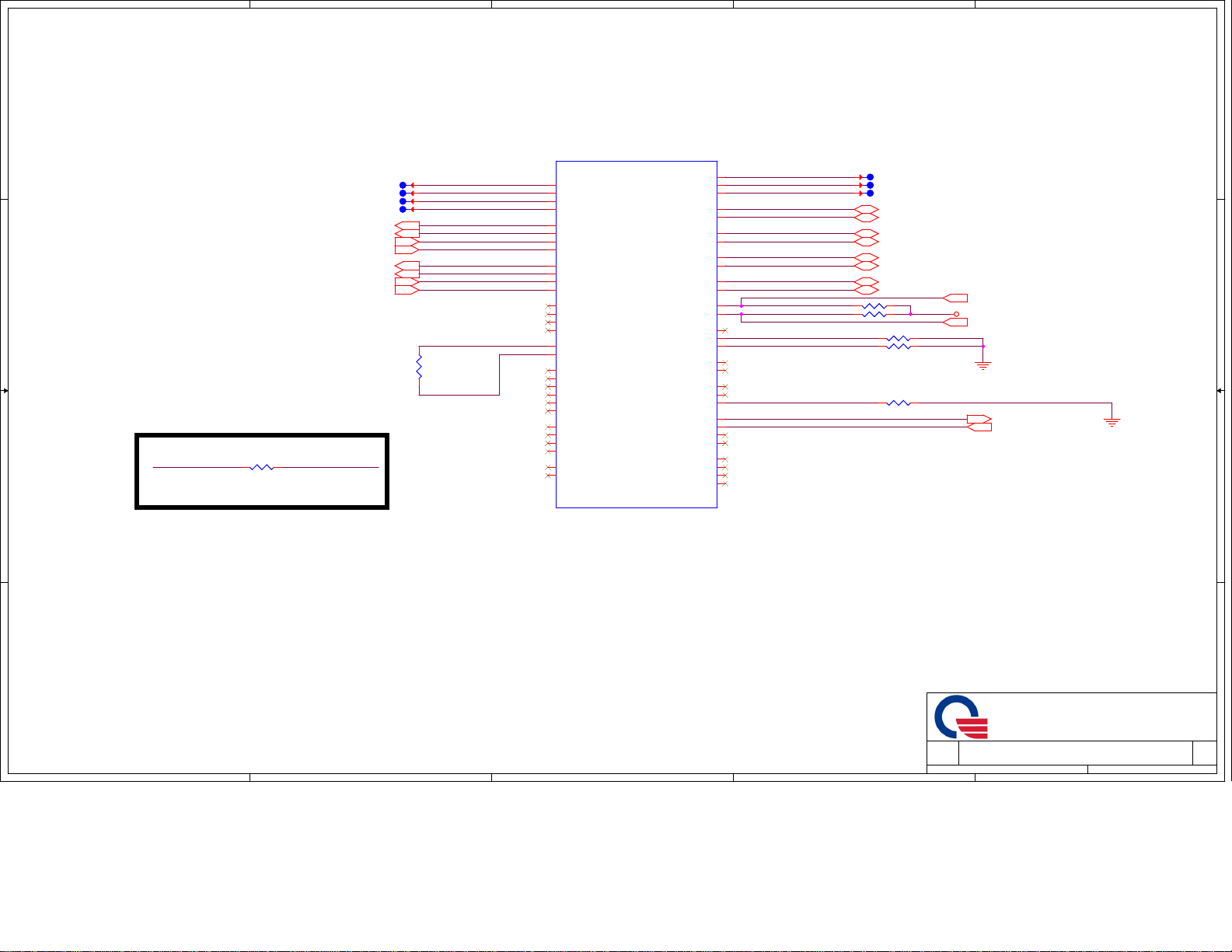

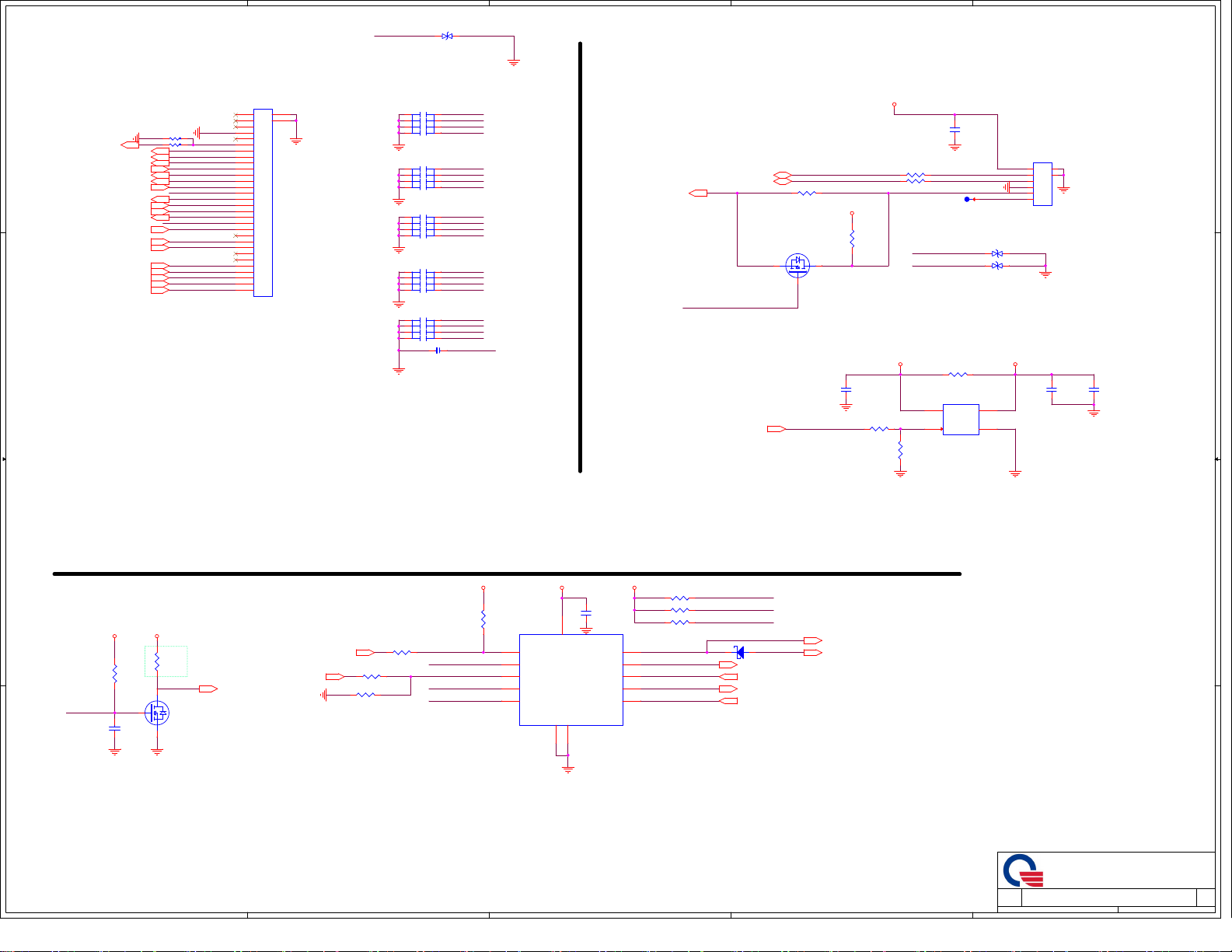

1. Schematic Page Description :

01

Origins Schematic Ver :

D D

SoC I2C table

Function

NA

PMIC

Channel

I2C0

I2C1

Read

Write

0x?

0x? 0x?

I2C4Audio codec

Track Pad I2C5

EC

I2C6

EC SMBus/I2C table

C C

Function

Battery/charger

NA

PCH

NA I2C2

Thermal I2C3

Channel

SMB0

SMB1

I2C1

Address

Current sensor address

USB3/2 port mapping

B B

USB3 Port No#

USB3P0

USB3P1

USB3P2

USB3P3

Usage

NA

I/O

I/O

NA

USB2 Port No# Usage

USB2P0

USB2P1

USB2P2

USB2P3

USB2P4

NA

I/O(3.0)

I/O(3.0)

CCD

BT

Function

+VBATA 0x47

+V5A 0x43

+V3P3A

+V1P8A 0x49

Channel

0x4B

0x46+V1P05A

Function Channel

+VCC_OUT 0x40

+VGG 0x44

0x45+VNN

+VDDQ_OUT 0x41

PCIe port mapping

PCIe port No#

PCIe_0

A A

PCIe_1

PCIe_2

PCIe_3

8

Usage

NA

NA

WLAN

NA

PCIe CLK# Usage

PCIe_CLK0

PCIe_CLK1

PCIe_CLK2

PCIe_CLK3

7

NA

NA

WLAN

NA

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

6

5

4

3

Date: Sheet of

2

Quanta Computer Inc.

Sch Page description

Sch Page description

Sch Page description

Tuesday, April 12, 2016 411

Tuesday, April 12, 2016 411

Tuesday, April 12, 2016 411

1A

1A

1A

1

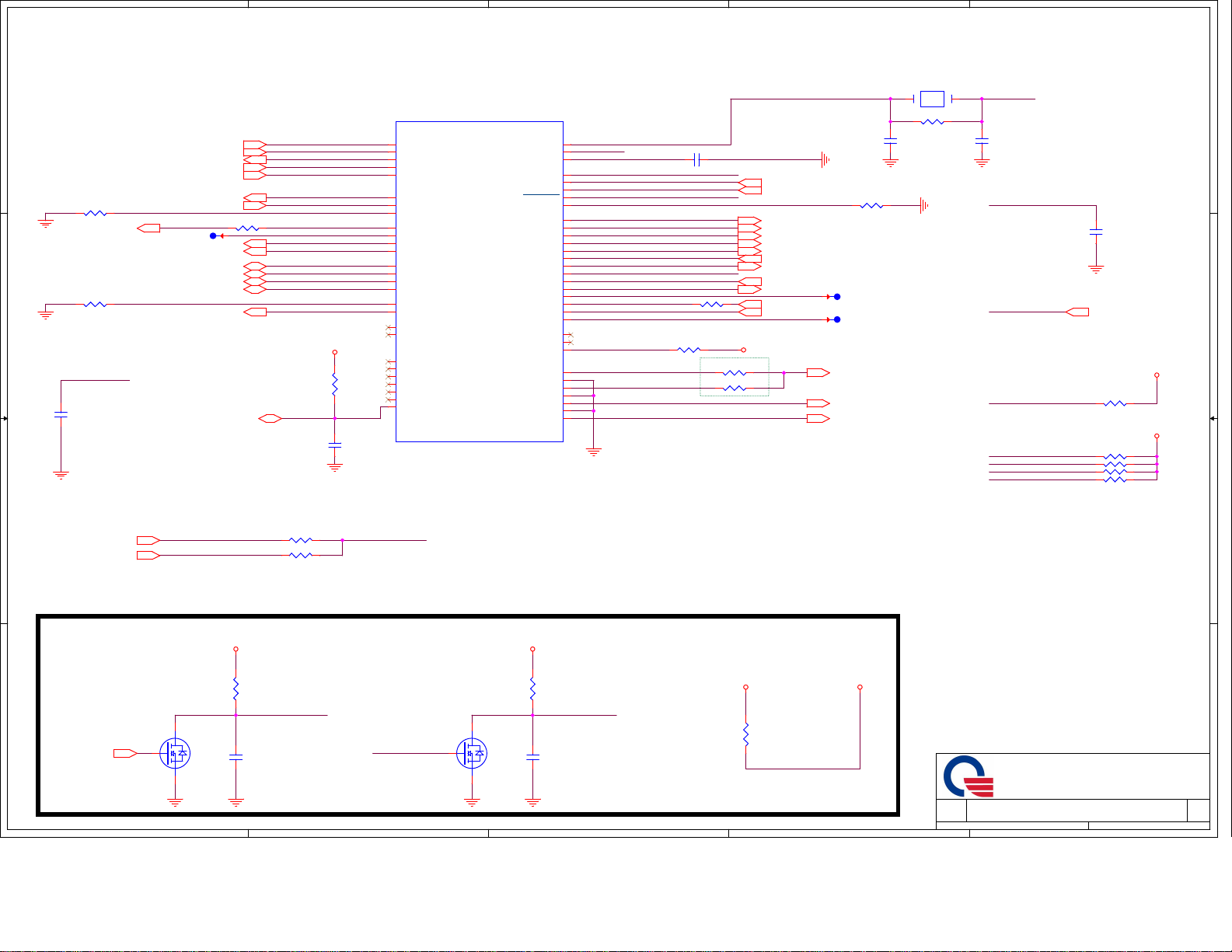

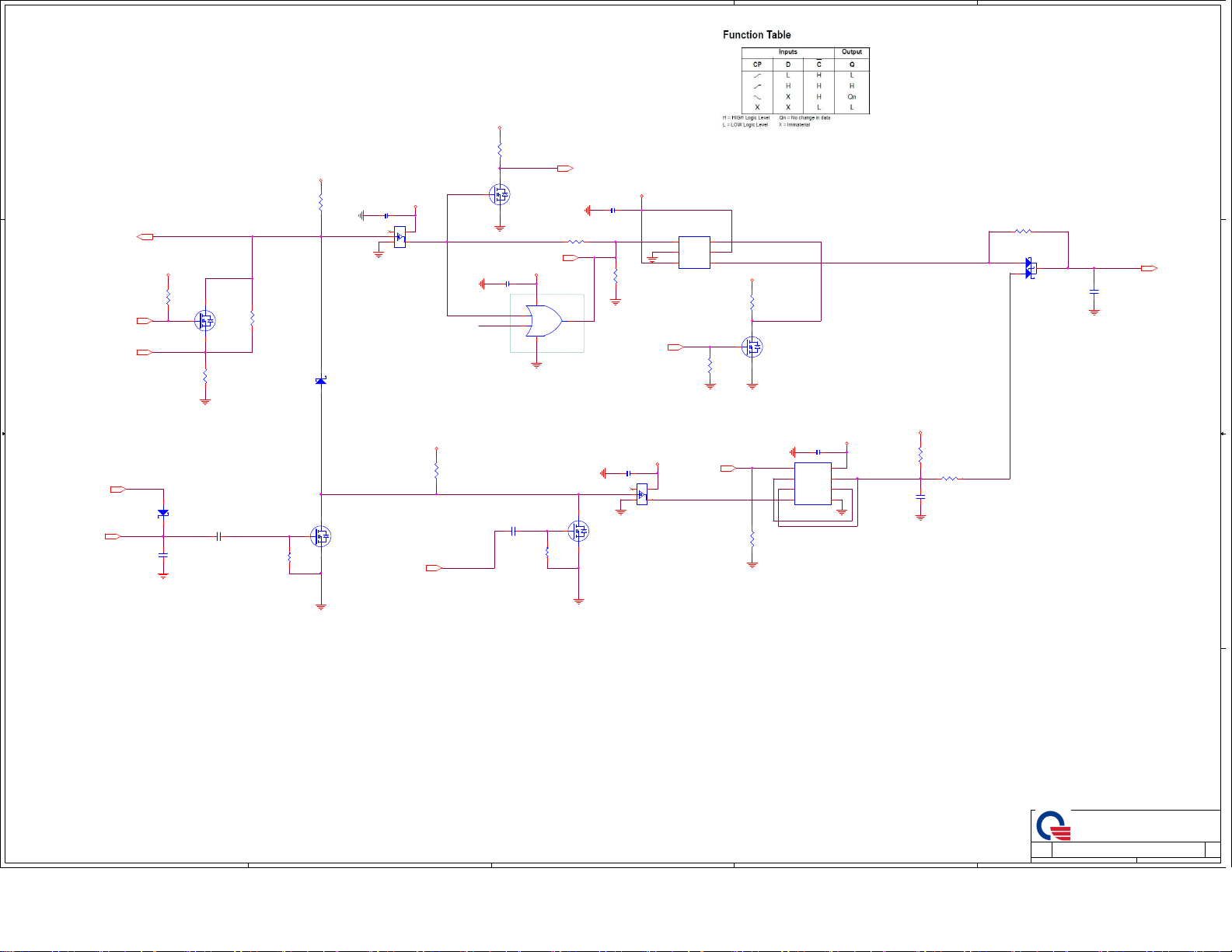

Page 2

5

www.schematic-x.blogspot.com

4

3

2

1

NL6D Chromebook

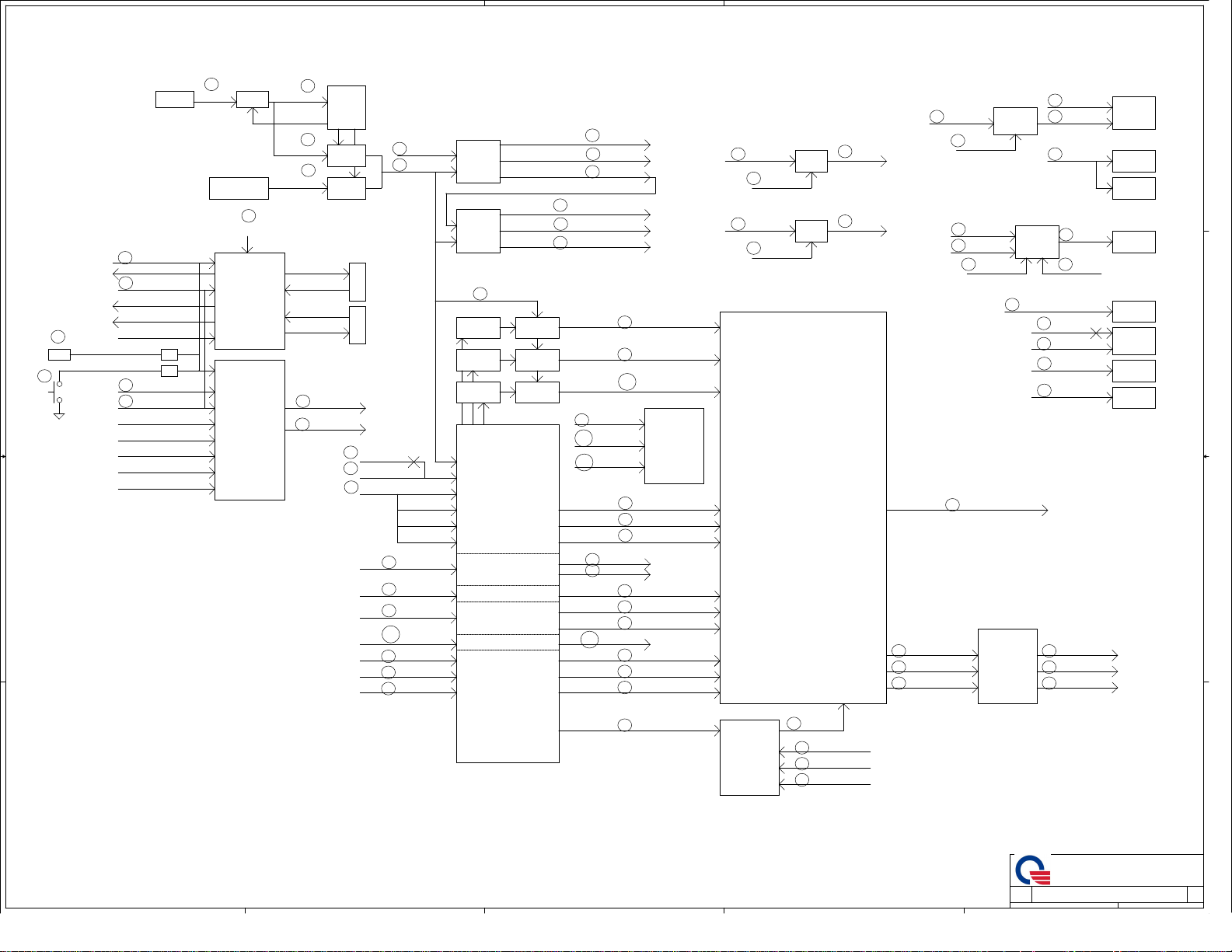

Intel Braswell Platform Block Diagram

D D

LPDDR3

Memory down 4Pcs

2 Channel

eMMC 5.0

C C

16G/32G

MMC

LPDDR3

Intel Braswell

Power : TDP 6 Watt

Package : FCBGA 1170

Size : 25 x 27 (mm)

DDI 1

32.768KHz

PAGE 6

19.2 Mhz

PAGE 6

DDI 2

I2C Interface

USB 3.0 Interface

SD Card

1.8V BIOS+TXE

SPI ROM(64Mb)

W25Q64FWSSIG

SD Card 3.0

SPI Interface

Int

I2S+I2C(PORT1)

Port0/3

USB 2.0 Interface

Port0

X2 LANES

Port4

Port2

USB3.0 Port x 1

Charger

SN1408009RTER

Port2

Port3

CCD

Port1

Charger

SN1408009RTER

Port1

LCD Conn

HDMI Conn

Port1

PMIC

Port4 Port5

Audio Codec

ALC5650

Track Pad

Port6

KBC

MEC1322

PCIE Gen 2 x 1 LaneLPC Interface

B B

TPM

SLB9655TT1.2

FW4.32GOOG

KBC

MEC1322-LZY

Audio Codec

REALTEK

ALC5650

Port2

NGFF M.2 2230-E

USB port3

WLAN / BT Combo

Package : DQFN132

Size : 11 x 11 (mm)

SMB0

Battery

SMB3

Thermal IC

Keyboard

Package : QFN-48

Size : 6 x 6 (mm)

Speaker

PCIE CLK PORT 2

TMP432

Combo Jack

Headphone + MIC

A A

DMIC

5

4

3

USB3.0 Port x 1

Daughter Board

BQ24770

NVDC Battery Charger

PMIC RT5067

+VNN

+V1P05A

+V1P8A

+V1P8U

+V1P8S

+V3P3A_PRIM

+V1P15S

+V1P24A

+VDDQ_VTT

Thermal Protection

Discharger

2

RT7291

+V5A

RT9610/CSD87381P

RT9610/CSD87381P

RT9610/CSD87381P

RT7290

+V3P3A

+VCC

+VGG

+VDDQ

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Quanta Computer Inc.

Block Diagram

Block Diagram

Block Diagram

1

1A

1A

2 41Tuesday, April 12, 2016

2 41Tuesday, April 12, 2016

2 41Tuesday, April 12, 2016

1A

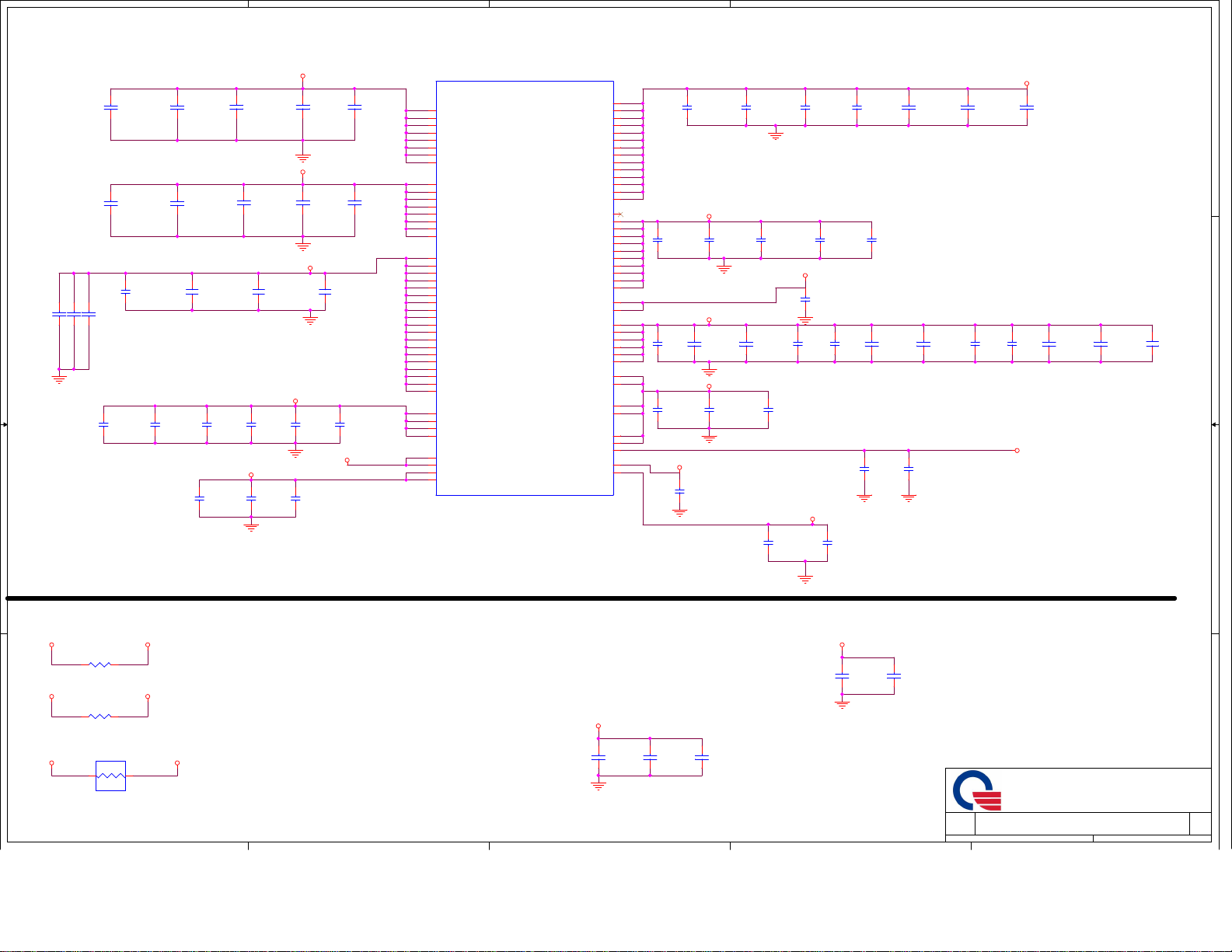

Page 3

5

4

3

2

1

03

D D

C C

B B

A A

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Power Sequence

Power Sequence

Power Sequence

1

3 41Tuesday, April 12, 2016

3 41Tuesday, April 12, 2016

3 41Tuesday, April 12, 2016

1A

1A

1A

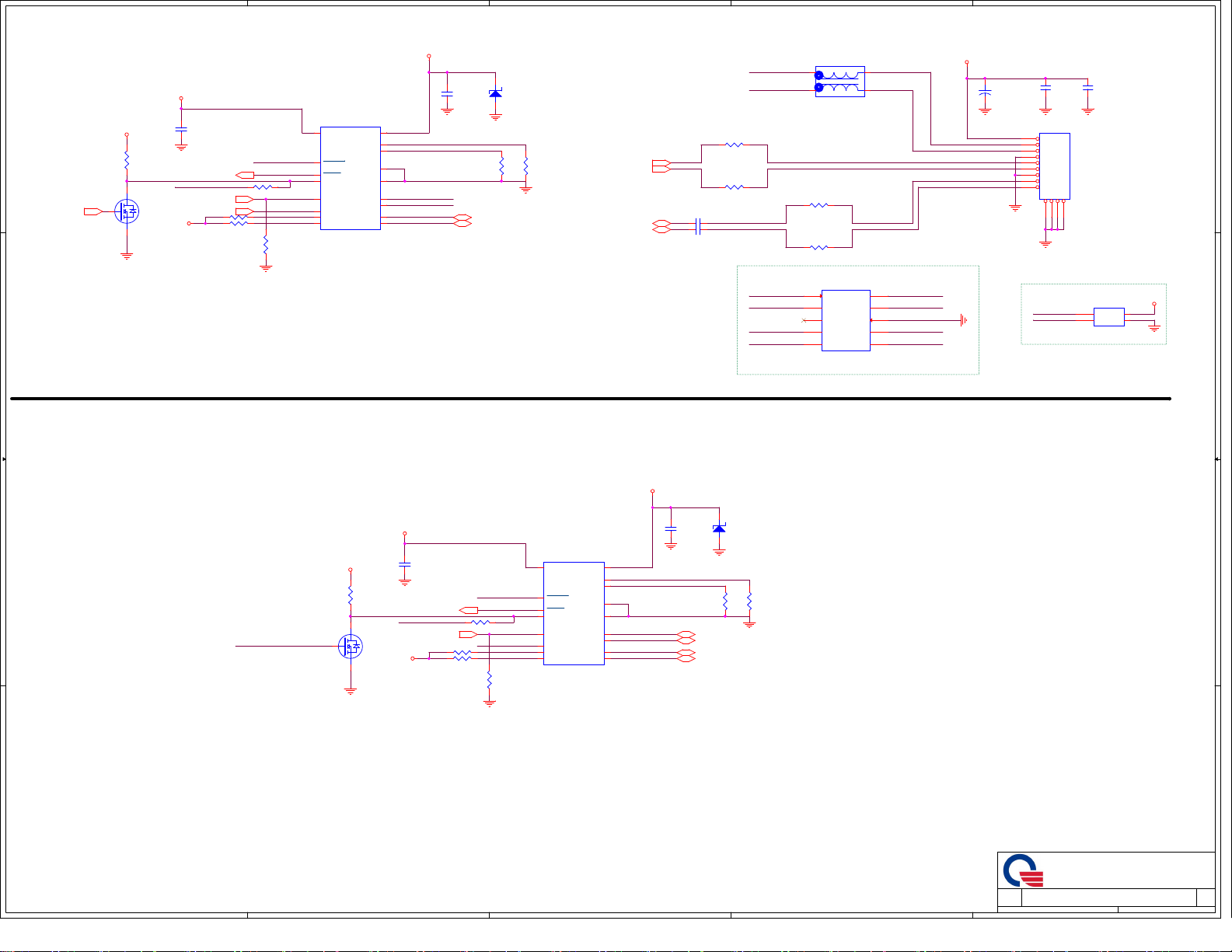

Page 4

1

2

3

4

5

6

7

8

04

A A

B B

C C

D D

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

1

2

3

4

5

6

Date: Sheet of

7

SMBUS_I2C

SMBUS_I2C

SMBUS_I2C

8

1A

1A

1A

4 41Tuesday, April 12, 2016

4 41Tuesday, April 12, 2016

4 41Tuesday, April 12, 2016

Page 5

5

4

3

2

1

05

1

+VDC_IN

Adapter

D D

PWR_BTN_L

13

BATT_ENABLE

BC_ACOK

2

EC_RST#

EC_IN_RW

EC_ENTERING_RW

RKB

R

EC_ACIN

3

BC_ACOK2

LID_OPEN_OUT1_L

STARTUP_LATCH_SET(EC)

SMC_SHUTDOWN(EC)

EC_HIB_L

PWR_BTN_SELECT(EC)

13

13

KB_PWR_BTN_L

DEBUG_PWR_BTN_L

C C

B B

MOSFET

Battery Pack

2a

+VRTC

HOLELESS RESET

SLG4K4350

EC HIB Logic

1a

+VCHGR_VIN

1a

+VCHGR_VIN

1

+VBATT

KB_ROW02_SW

KB_COL02_SW

KB_ROW02

KB_COL02KBEC

V5A_EN4

SMC_ONOFF_N

14

Charger

MOSFET

MOSFET

6a

6a

5

V5A_EN

4

+VBATA

2

V3P3A_PWRGD

PMIC_EN

+V5A

+VNN_VIN

+V1P05A_VIN

+V1P8A_VIN

+V1P8A

9

+V3P3A +V3P3A_PRIME

6

+V1P8A

9

16a

+VDDQ +VDDQ_VTT

SLP_S0IX#

17

SLP_S4

15

SLP_S3

16

+V5A VR +V5A

RT7291B V5A_PWRGD

2a

+V3P3A_LDO/+VRTC

+V3P3A VR +V3P3A

RT7290A V3P3A_PWRGD

+VBATA

2

+VCC PWM

RT9610

+VGG PWM

RT9610

+VDDQ PWM

RT9610

PWM1

PWM2

PWM6

PMIC

DRV_EN1

DRV_EN2

DRV_EN6

VSYS

PMIC_EN

VCC

VIN3

VIN4

VIN5

V3P3_VIN

VIN_LDO

VDDQ_LDO_IN

RT5067

1. +VCC

2. +VGG

3. +VNN

4. +V1P05A

5. +V1P8A

6. +VDDQ

MOSFET

CSD87381P

MOSFET

CSD87381P

MOSFET

CSD87381P

6

6a

16

16a

16b

16b

2a

5

5a

16

16

+V5A_LDO

19

18

16a

+V1P8U

+VDDQ

+VDDQ_VTT

7

8

9

+V1P8U

+V1P8SVIN_1P8_SW

11

16

10

17

20

21

+VCC

+VGG

+VDDQ

LPDDR3

+VNN

+V1P05A

+V1P8A

+V1P15S

+V1P24A

DDR3_DRAM_PWROK

DDR3_VCCA_PWROK

COREPWROK

+V5A5

16

SLP_S3D

6

+V3P3A +V3P3S

16

SLP_S3D

MOSFET

MOSFET

17

17

SoC

Intel Braswell

eDP

Switch IC

?

6 +V3P3A

PLTRST

22

PCH_DISP_ON

+V1P8A9

?

VSDIO_EN

LVT

SD

Switch IC

6 +V3P3A (+V3P3A-WIFI)

17

11

6 +V3P3A

6 +V3P3A

+V5S +V5A5

PMU_SLP_S0IX#

17

PMU_SLP_S4

15

PMU_SLP_S3

16

+VBATA2

+V3P3DX_EDP?6 +V3P3A

+VSDIO?

?

VSDIO_SEL

+V3P3S

+V3P3A_PRIME

SLP_S0IX#

17

SLP_S4

15

SLP_S3

16

EDP LCD

USB Port

KB LIGHT

SD Card

WIFI/BT

TPM

Track Pad

Thermal

RSMRST_N_PWRGD

12

EC

A A

5

4

3

17

15

16

RSMRST#13

SLP_S0IX#

SLP_S4

SLP_S3

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

BSW PWR TREE

BSW PWR TREE

BSW PWR TREE

1

5 41Tuesday, April 12, 2016

5 41Tuesday, April 12, 2016

5 41Tuesday, April 12, 2016

1A

1A

1A

Page 6

5

4

3

2

1

SoC (CPU)

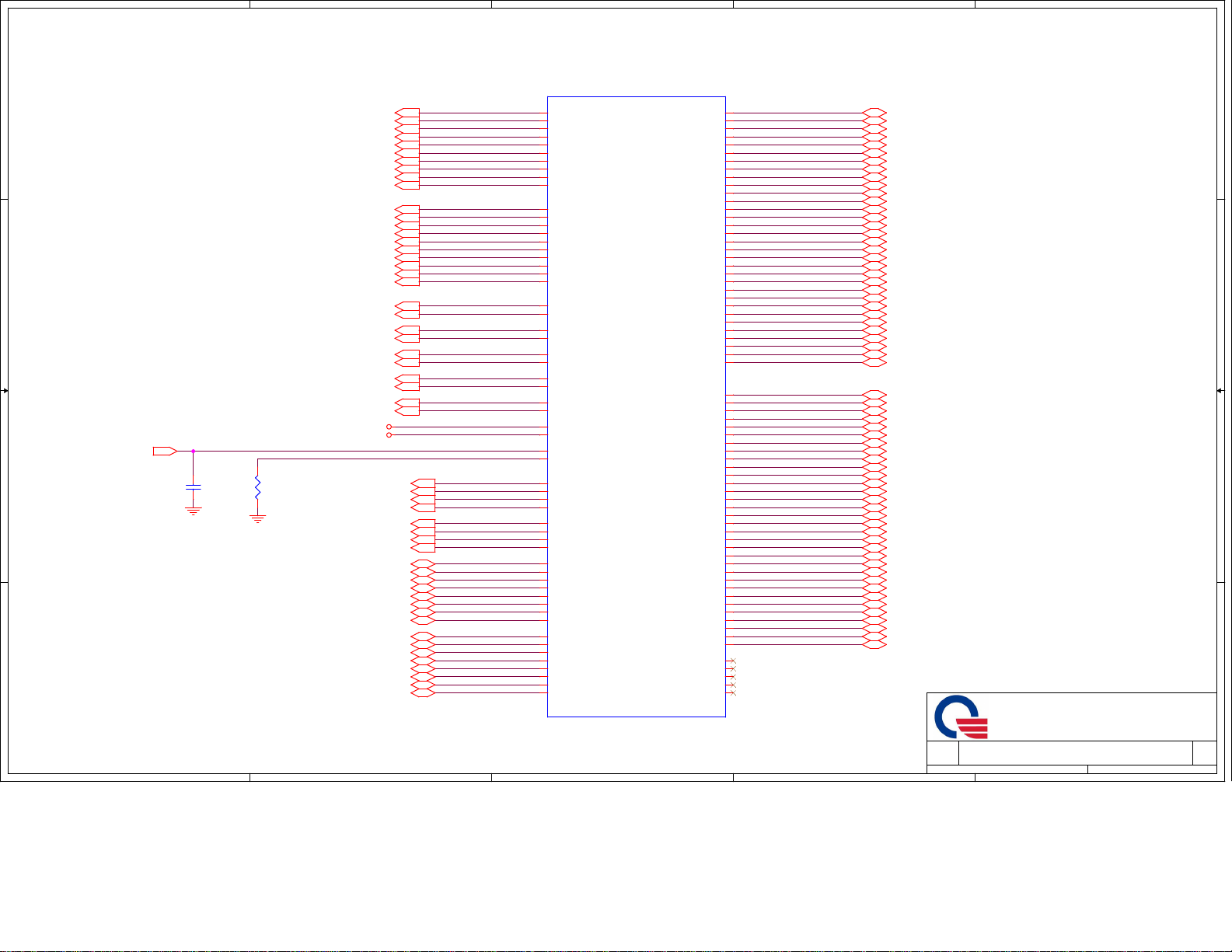

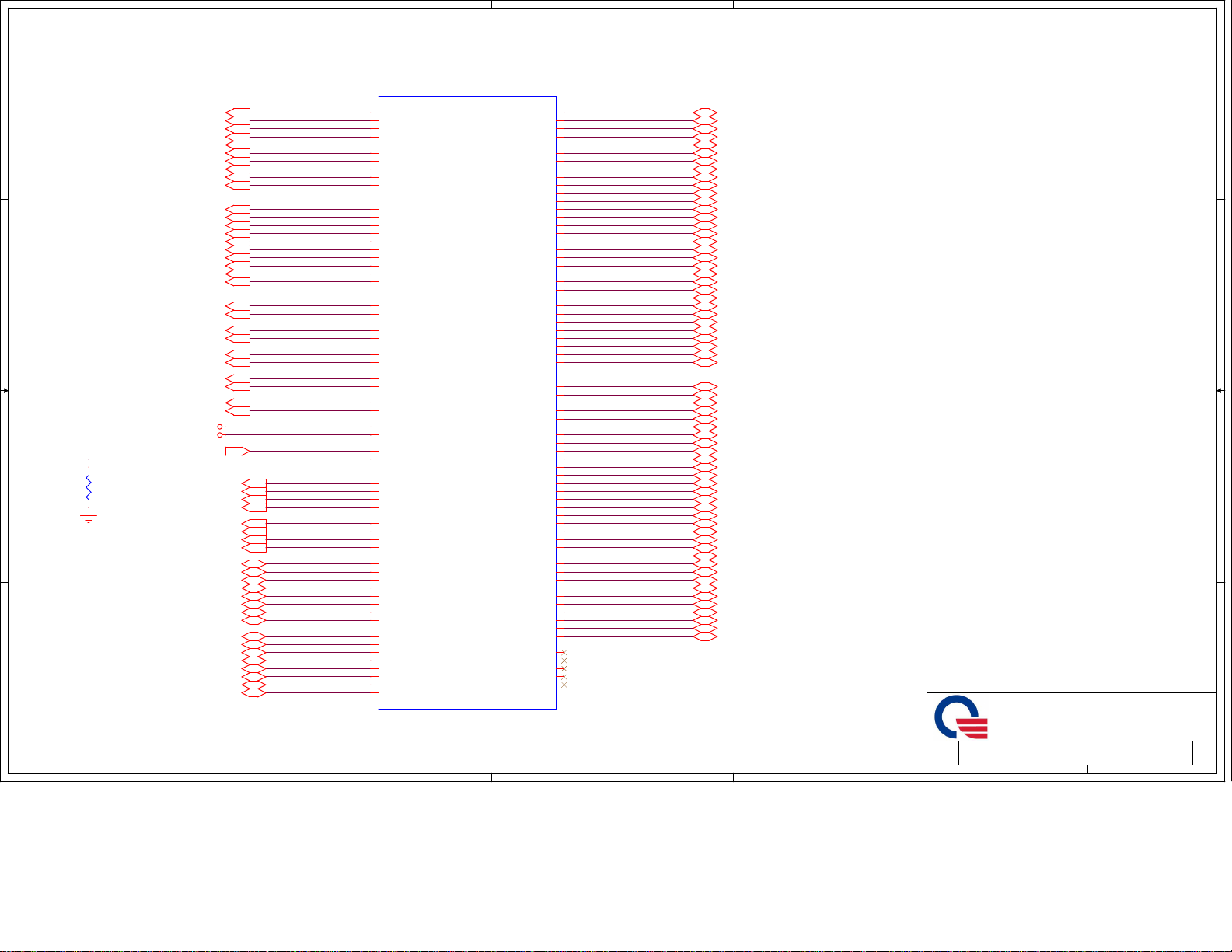

BRASWELL SOC - MEMORY LPDDR3 CHANNEL A

06

BSW_MCP_EDS

D D

C C

DDR3_DRAM_PWROK[39]

CA

B B

PLACE CA CAP NEAR SOC

A A

5

C234

0.1U/16V_4

R403

182/F_4

M0_B_A9[17]

M0_B_A8[17]

M0_B_A7[17]

M0_B_A6[17]

M0_B_A5[17]

M0_B_A4[17]

M0_B_A3[17]

M0_B_A2[17]

M0_B_A1[17]

M0_B_A0[17]

M0_A_A9[17]

M0_A_A8[17]

M0_A_A7[17]

M0_A_A6[17]

M0_A_A5[17]

M0_A_A4[17]

M0_A_A3[17]

M0_A_A2[17]

M0_A_A1[17]

M0_A_A0[17]

M0_CS1_N[17]

M0_CS0_N[17]

M0_CKE1[17]

M0_CKE0[17]

M0_B_CLKP0[17]

M0_B_CLKN0[17]

M0_A_CLKP0[17]

M0_A_CLKN0[17]

M0_B_ODT[17]

M0_A_ODT[17]

+VREFCA0_R

+VREFDQ0_R

M0_B_DM3[17]

M0_B_DM2[17]

M0_B_DM1[17]

M0_B_DM0[17]

M0_A_DM3[17]

M0_A_DM2[17]

M0_A_DM1[17]

M0_A_DM0[17]

M0_B_DQSP3[17]

M0_B_DQSN3[17]

M0_B_DQSP2[17]

M0_B_DQSN2[17]

M0_B_DQSP1[17]

M0_B_DQSN1[17]

M0_B_DQSP0[17]

M0_B_DQSN0[17]

M0_A_DQSP3[17]

M0_A_DQSN3[17]

M0_A_DQSP2[17]

M0_A_DQSN2[17]

M0_A_DQSP1[17]

M0_A_DQSN1[17]

M0_A_DQSP0[17]

M0_A_DQSN0[17]

4

M0_B_A9

M0_B_A8

M0_B_A7

M0_B_A6

M0_B_A5

M0_B_A4

M0_B_A3

M0_B_A2

M0_B_A1

M0_B_A0

M0_A_A9

M0_A_A8

M0_A_A7

M0_A_A6

M0_A_A5

M0_A_A4

M0_A_A3

M0_A_A2

M0_A_A1

M0_A_A0

M0_CS1_N

M0_CS0_N

M0_CKE1

M0_CKE0

M0_B_CLKP0

M0_B_CLKN0

M0_A_CLKP0

M0_A_CLKN0

M0_B_ODT

M0_A_ODT

DDR3_DRAM_PWROK

DDR3_M0_RCOMPPD

M0_B_DM3

M0_B_DM2

M0_B_DM1

M0_B_DM0

M0_A_DM3

M0_A_DM2

M0_A_DM1

M0_A_DM0

M0_B_DQSP3

M0_B_DQSN3

M0_B_DQSP2

M0_B_DQSN2

M0_B_DQSP1

M0_B_DQSN1

M0_B_DQSP0

M0_B_DQSN0

M0_A_DQSP3

M0_A_DQSN3

M0_A_DQSP2

M0_A_DQSN2

M0_A_DQSP1

M0_A_DQSN1

M0_A_DQSP0

M0_A_DQSN0

U17A

BG45

LPDDR3_M0_CA9_B

BH46

LPDDR3_M0_CA8_B

BA40

LPDDR3_M0_CA7_B

BD47

LPDDR3_M0_CA6_B

BD49

LPDDR3_M0_CA5_B

BJ45

LPDDR3_M0_CA4_B

BB49

LPDDR3_M0_CA3_B

BE46

LPDDR3_M0_CA2_B

BF48

LPDDR3_M0_CA1_B

BE52

LPDDR3_M0_CA0_B

BF44

LPDDR3_M0_CA9_A

BD44

LPDDR3_M0_CA8_A

AY40

LPDDR3_M0_CA7_A

BB46

LPDDR3_M0_CA6_A

BH48

LPDDR3_M0_CA5_A

BD42

LPDDR3_M0_CA4_A

BH47

LPDDR3_M0_CA3_A

BJ48

LPDDR3_M0_CA2_A

BC42

LPDDR3_M0_CA1_A

BB47

LPDDR3_M0_CA0_A

AU38

LPDDR3_M0_CSB1

AY38

LPDDR3_M0_CSB0

AY42

LPDDR3_M0_CKE1_A

BB44

LPDDR3_M0_CKE0_A

BD38

LPDDR3_M0_CK_P_B

BF38

LPDDR3_M0_CK_N_B

BD40

LPDDR3_M0_CK_P_A

BF40

LPDDR3_M0_CK_N_A

BA38

LPDDR3_M0_ODT_B

AV36

LPDDR3_M0_ODT_A

AT28

DDR3_M0_OCAVREF

AU28

DDR3_M0_ODQVREF

AV28

DDR3_DRAM_PWROK

BA28

DDR3_M0_RCOMP

BH30

LPDDR3_M0_DM3_B

BG41

LPDDR3_M0_DM2_B

BD32

LPDDR3_M0_DM1_B

AY36

LPDDR3_M0_DM0_B

AP44

LPDDR3_M0_DM3_A

AT48

LPDDR3_M0_DM2_A

BA53

LPDDR3_M0_DM1_A

AP52

LPDDR3_M0_DM0_A

BH32

LPDDR3_M0_DQS3_B

BG31

LPDDR3_M0_DQSB3_B

BH40

LPDDR3_M0_DQS2_B

BG39

LPDDR3_M0_DQSB2_B

BC30

LPDDR3_M0_DQS1_B

BC32

LPDDR3_M0_DQSB1_B

AT32

LPDDR3_M0_DQS0_B

AT34

LPDDR3_M0_DQSB0_B

AT42

LPDDR3_M0_DQS3_A

AT41

LPDDR3_M0_DQSB3_A

AV47

LPDDR3_M0_DQS2_A

AV48

LPDDR3_M0_DQSB2_A

AY52

LPDDR3_M0_DQS1_A

BA51

LPDDR3_M0_DQSB1_A

AM52

LPDDR3_M0_DQS0_A

AM51

LPDDR3_M0_DQSB0_A

BSW_MCP_EDS

?

DDR0

3

LPDDR3_M0_DQ31_B

LPDDR3_M0_DQ30_B

LPDDR3_M0_DQ29_B

LPDDR3_M0_DQ28_B

LPDDR3_M0_DQ27_B

LPDDR3_M0_DQ26_B

LPDDR3_M0_DQ25_B

LPDDR3_M0_DQ24_B

LPDDR3_M0_DQ23_B

LPDDR3_M0_DQ22_B

LPDDR3_M0_DQ21_B

LPDDR3_M0_DQ20_B

LPDDR3_M0_DQ19_B

LPDDR3_M0_DQ18_B

LPDDR3_M0_DQ17_B

LPDDR3_M0_DQ16_B

LPDDR3_M0_DQ15_B

LPDDR3_M0_DQ14_B

LPDDR3_M0_DQ13_B

LPDDR3_M0_DQ12_B

LPDDR3_M0_DQ11_B

LPDDR3_M0_DQ10_B

LPDDR3_M0_DQ9_B

LPDDR3_M0_DQ8_B

LPDDR3_M0_DQ7_B

LPDDR3_M0_DQ6_B

LPDDR3_M0_DQ5_B

LPDDR3_M0_DQ4_B

LPDDR3_M0_DQ3_B

LPDDR3_M0_DQ2_B

LPDDR3_M0_DQ1_B

LPDDR3_M0_DQ0_B

LPDDR3_M0_DQ31_A

LPDDR3_M0_DQ30_A

LPDDR3_M0_DQ29_A

LPDDR3_M0_DQ28_A

LPDDR3_M0_DQ27_A

LPDDR3_M0_DQ26_A

LPDDR3_M0_DQ25_A

LPDDR3_M0_DQ24_A

LPDDR3_M0_DQ23_A

LPDDR3_M0_DQ22_A

LPDDR3_M0_DQ21_A

LPDDR3_M0_DQ20_A

LPDDR3_M0_DQ19_A

LPDDR3_M0_DQ18_A

LPDDR3_M0_DQ17_A

LPDDR3_M0_DQ16_A

LPDDR3_M0_DQ15_A

LPDDR3_M0_DQ14_A

LPDDR3_M0_DQ13_A

LPDDR3_M0_DQ12_A

LPDDR3_M0_DQ11_A

LPDDR3_M0_DQ10_A

LPDDR3_M0_DQ9_A

LPDDR3_M0_DQ8_A

LPDDR3_M0_DQ7_A

LPDDR3_M0_DQ6_A

LPDDR3_M0_DQ5_A

LPDDR3_M0_DQ4_A

LPDDR3_M0_DQ3_A

LPDDR3_M0_DQ2_A

LPDDR3_M0_DQ1_A

LPDDR3_M0_DQ0_A

RSVD1

RSVD2

NC1

NC2

NC3

BG29

BG33

BG28

BH34

BJ33

BG32

BH28

BJ29

BH38

BJ37

BG43

BH36

BG37

BH42

BJ41

BG42

BD28

BD30

BC34

BD34

BA34

BF30

BA32

BF34

BD36

AV34

AV32

AU32

BF36

AU34

BA36

BC36

AP40

AT40

AV41

AP42

AT38

AP41

AV42

AT44

AT47

AT50

AV50

AP47

AV45

AP48

AY50

AY48

BC53

AW51

BB51

BC52

BD52

AW53

AV52

AV51

AT52

AR51

AP51

AL51

AK52

AK51

AR53

AL53

AT30

AU30

BA42

BF52

BH44

?1 OF 13REV = 1

M0_B_DQ31

M0_B_DQ30

M0_B_DQ29

M0_B_DQ28

M0_B_DQ27

M0_B_DQ26

M0_B_DQ25

M0_B_DQ24

M0_B_DQ23

M0_B_DQ22

M0_B_DQ21

M0_B_DQ20

M0_B_DQ19

M0_B_DQ18

M0_B_DQ17

M0_B_DQ16

M0_B_DQ15

M0_B_DQ14

M0_B_DQ13

M0_B_DQ12

M0_B_DQ11

M0_B_DQ10

M0_B_DQ9

M0_B_DQ8

M0_B_DQ7

M0_B_DQ6

M0_B_DQ5

M0_B_DQ4

M0_B_DQ3

M0_B_DQ2

M0_B_DQ1

M0_B_DQ0

M0_A_DQ31

M0_A_DQ30

M0_A_DQ29

M0_A_DQ28

M0_A_DQ27

M0_A_DQ26

M0_A_DQ25

M0_A_DQ24

M0_A_DQ23

M0_A_DQ22

M0_A_DQ21

M0_A_DQ20

M0_A_DQ19

M0_A_DQ18

M0_A_DQ17

M0_A_DQ16

M0_A_DQ15

M0_A_DQ14

M0_A_DQ13

M0_A_DQ12

M0_A_DQ11

M0_A_DQ10

M0_A_DQ9

M0_A_DQ8

M0_A_DQ7

M0_A_DQ6

M0_A_DQ5

M0_A_DQ4

M0_A_DQ3

M0_A_DQ2

M0_A_DQ1

M0_A_DQ0

2

M0_B_DQ31 [17]

M0_B_DQ30 [17]

M0_B_DQ29 [17]

M0_B_DQ28 [17]

M0_B_DQ27 [17]

M0_B_DQ26 [17]

M0_B_DQ25 [17]

M0_B_DQ24 [17]

M0_B_DQ23 [17]

M0_B_DQ22 [17]

M0_B_DQ21 [17]

M0_B_DQ20 [17]

M0_B_DQ19 [17]

M0_B_DQ18 [17]

M0_B_DQ17 [17]

M0_B_DQ16 [17]

M0_B_DQ15 [17]

M0_B_DQ14 [17]

M0_B_DQ13 [17]

M0_B_DQ12 [17]

M0_B_DQ11 [17]

M0_B_DQ10 [17]

M0_B_DQ9 [17]

M0_B_DQ8 [17]

M0_B_DQ7 [17]

M0_B_DQ6 [17]

M0_B_DQ5 [17]

M0_B_DQ4 [17]

M0_B_DQ3 [17]

M0_B_DQ2 [17]

M0_B_DQ1 [17]

M0_B_DQ0 [17]

M0_A_DQ31 [17]

M0_A_DQ30 [17]

M0_A_DQ29 [17]

M0_A_DQ28 [17]

M0_A_DQ27 [17]

M0_A_DQ26 [17]

M0_A_DQ25 [17]

M0_A_DQ24 [17]

M0_A_DQ23 [17]

M0_A_DQ22 [17]

M0_A_DQ21 [17]

M0_A_DQ20 [17]

M0_A_DQ19 [17]

M0_A_DQ18 [17]

M0_A_DQ17 [17]

M0_A_DQ16 [17]

M0_A_DQ15 [17]

M0_A_DQ14 [17]

M0_A_DQ13 [17]

M0_A_DQ12 [17]

M0_A_DQ11 [17]

M0_A_DQ10 [17]

M0_A_DQ9 [17]

M0_A_DQ8 [17]

M0_A_DQ7 [17]

M0_A_DQ6 [17]

M0_A_DQ5 [17]

M0_A_DQ4 [17]

M0_A_DQ3 [17]

M0_A_DQ2 [17]

M0_A_DQ1 [17]

M0_A_DQ0 [17]

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

BSW 1/10 (DDRA)

BSW 1/10 (DDRA)

BSW 1/10 (DDRA)

Tuesday, April 12, 2016 416

Tuesday, April 12, 2016 416

Tuesday, April 12, 2016 416

1

1A

1A

1A

Page 7

5

4

3

2

1

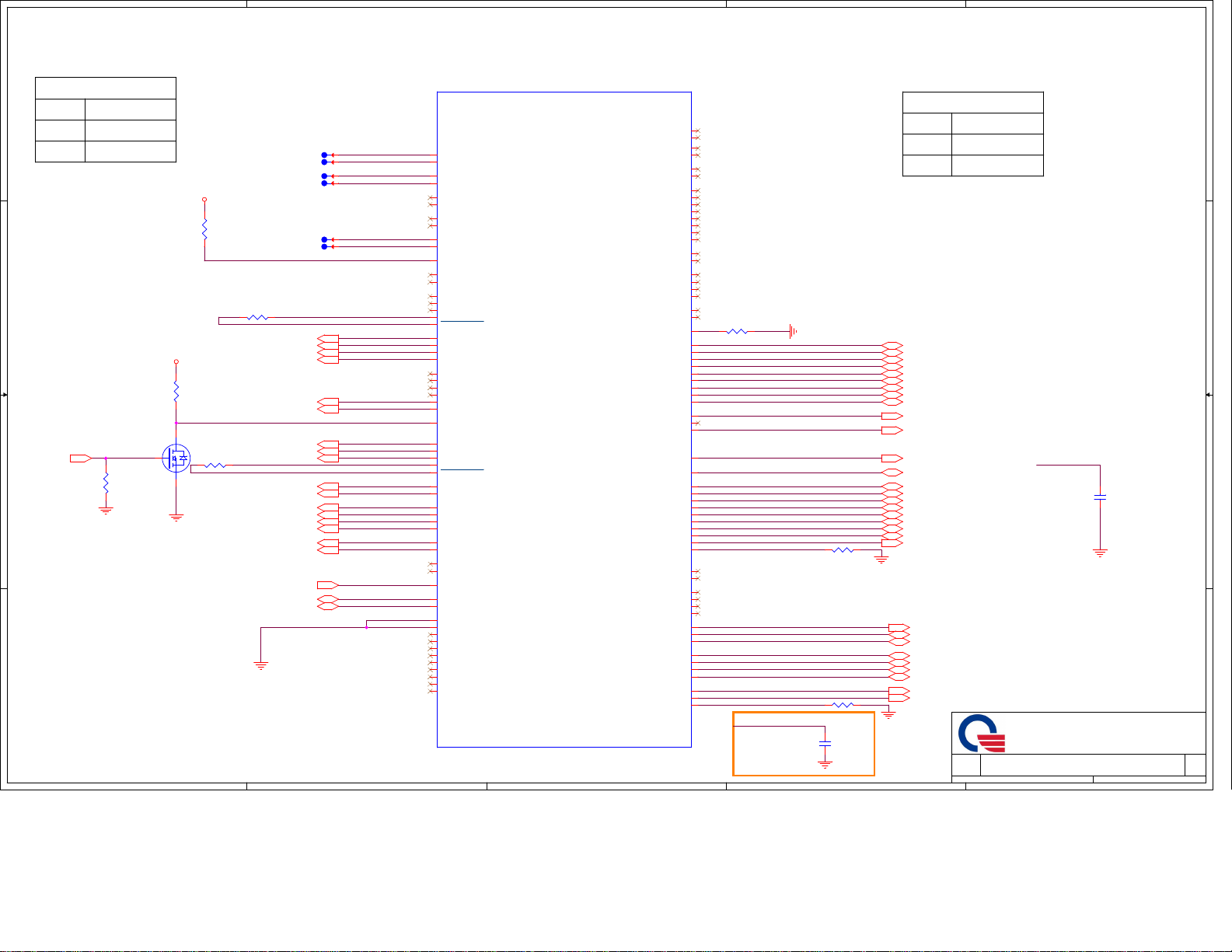

BRASWELL - MEMORY LPDDR3 CHANNEL B

SoC (CPU)

D D

C C

R399

B B

A A

182/F_4

5

DDR3_VCCA_PWROK[39]

M1_B_A9[18]

M1_B_A8[18]

M1_B_A7[18]

M1_B_A6[18]

M1_B_A5[18]

M1_B_A4[18]

M1_B_A3[18]

M1_B_A2[18]

M1_B_A1[18]

M1_B_A0[18]

M1_A_A9[18]

M1_A_A8[18]

M1_A_A7[18]

M1_A_A6[18]

M1_A_A5[18]

M1_A_A4[18]

M1_A_A3[18]

M1_A_A2[18]

M1_A_A1[18]

M1_A_A0[18]

M1_CS1_N[18]

M1_CS0_N[18]

M1_CKE1[18]

M1_CKE0[18]

M1_B_CLKP0[18]

M1_B_CLKN0[18]

M1_A_CLKP0[18]

M1_A_CLKN0[18]

M1_B_ODT[18]

M1_A_ODT[18]

+VREFCA1_R

+VREFDQ1_R

M1_B_DM3[18]

M1_B_DM2[18]

M1_B_DM1[18]

M1_B_DM0[18]

M1_A_DM3[18]

M1_A_DM2[18]

M1_A_DM1[18]

M1_A_DM0[18]

M1_B_DQSP3[18]

M1_B_DQSN3[18]

M1_B_DQSP2[18]

M1_B_DQSN2[18]

M1_B_DQSP1[18]

M1_B_DQSN1[18]

M1_B_DQSP0[18]

M1_B_DQSN0[18]

M1_A_DQSP3[18]

M1_A_DQSN3[18]

M1_A_DQSP2[18]

M1_A_DQSN2[18]

M1_A_DQSP1[18]

M1_A_DQSN1[18]

M1_A_DQSP0[18]

M1_A_DQSN0[18]

M1_B_A9

M1_B_A8

M1_B_A7

M1_B_A6

M1_B_A5

M1_B_A4

M1_B_A3

M1_B_A2

M1_B_A1

M1_B_A0

M1_A_A9

M1_A_A8

M1_A_A7

M1_A_A6

M1_A_A5

M1_A_A4

M1_A_A3

M1_A_A2

M1_A_A1

M1_A_A0

M1_CS1_N

M1_CS0_N

M1_CKE1

M1_CKE0

M1_B_CLKP0

M1_B_CLKN0

M1_A_CLKP0

M1_A_CLKN0

M1_B_ODT

M1_A_ODT

DDR3_VCCA_PWROK

DDR3_M1_RCOMPPD

M1_B_DM3

M1_B_DM2

M1_B_DM1

M1_B_DM0

M1_A_DM3

M1_A_DM2

M1_A_DM1

M1_A_DM0

M1_B_DQSP3

M1_B_DQSN3

M1_B_DQSP2

M1_B_DQSN2

M1_B_DQSP1

M1_B_DQSN1

M1_B_DQSP0

M1_B_DQSN0

M1_A_DQSP3

M1_A_DQSN3

M1_A_DQSP2

M1_A_DQSN2

M1_A_DQSP1

M1_A_DQSN1

M1_A_DQSP0

M1_A_DQSN0

U17B

BF10

LPDDR3_M1_CA9_B

BD10

LPDDR3_M1_CA8_B

AY14

LPDDR3_M1_CA7_B

BB8

LPDDR3_M1_CA6_B

BH6

LPDDR3_M1_CA5_B

BD12

LPDDR3_M1_CA4_B

BH7

LPDDR3_M1_CA3_B

BJ6

LPDDR3_M1_CA2_B

BC12

LPDDR3_M1_CA1_B

BB7

LPDDR3_M1_CA0_B

BG9

LPDDR3_M1_CA9_A

BH8

LPDDR3_M1_CA8_A

BA14

LPDDR3_M1_CA7_A

BD7

LPDDR3_M1_CA6_A

BD5

LPDDR3_M1_CA5_A

BJ9

LPDDR3_M1_CA4_A

BB5

LPDDR3_M1_CA3_A

BE8

LPDDR3_M1_CA2_A

BF6

LPDDR3_M1_CA1_A

BE2

LPDDR3_M1_CA0_A

AU16

LPDDR3_M1_CSB1

AY16

LPDDR3_M1_CSB0

AY12

LPDDR3_M1_CKE1_B

BB10

LPDDR3_M1_CKE0_B

BD14

LPDDR3_M1_CK_P_B

BF14

LPDDR3_M1_CK_N_B

BD16

LPDDR3_M1_CK_P_A

BF16

LPDDR3_M1_CK_N_A

AV18

LPDDR3_M1_ODT_B

BA16

LPDDR3_M1_ODT_A

AT26

DDR3_M1_OCAVREF

AU26

DDR3_M1_ODQVREF

AV26

DDR3_VCCA_PW ROK

BA26

DDR3_M1_RCOMP

AT6

LPDDR3_M1_DM3_B

AP10

LPDDR3_M1_DM2_B

AP2

LPDDR3_M1_DM1_B

BA1

LPDDR3_M1_DM0_B

BG13

LPDDR3_M1_DM3_A

BH24

LPDDR3_M1_DM2_A

AY18

LPDDR3_M1_DM1_A

BD22

LPDDR3_M1_DM0_A

AV7

LPDDR3_M1_DQS3_B

AV6

LPDDR3_M1_DQSB3_B

AT12

LPDDR3_M1_DQS2_B

AT13

LPDDR3_M1_DQSB2_B

AM2

LPDDR3_M1_DQS1_B

AM3

LPDDR3_M1_DQSB1_B

AY2

LPDDR3_M1_DQS0_B

BA3

LPDDR3_M1_DQSB0_B

BH14

LPDDR3_M1_DQS3_A

BG15

LPDDR3_M1_DQSB3_A

BH22

LPDDR3_M1_DQS2_A

BG23

LPDDR3_M1_DQSB2_A

AT22

LPDDR3_M1_DQS1_A

AT20

LPDDR3_M1_DQSB1_A

BC24

LPDDR3_M1_DQS0_A

BC22

LPDDR3_M1_DQSB0_A

BSW_MCP_EDS

REV = 1

4

BSW_MCP_EDS

?

LPDDR3_M1_DQ31_B

LPDDR3_M1_DQ30_B

DDR1

LPDDR3_M1_DQ29_B

LPDDR3_M1_DQ28_B

LPDDR3_M1_DQ27_B

LPDDR3_M1_DQ26_B

LPDDR3_M1_DQ25_B

LPDDR3_M1_DQ24_B

LPDDR3_M1_DQ23_B

LPDDR3_M1_DQ22_B

LPDDR3_M1_DQ21_B

LPDDR3_M1_DQ20_B

LPDDR3_M1_DQ19_B

LPDDR3_M1_DQ18_B

LPDDR3_M1_DQ17_B

LPDDR3_M1_DQ16_B

LPDDR3_M1_DQ15_B

LPDDR3_M1_DQ14_B

LPDDR3_M1_DQ13_B

LPDDR3_M1_DQ12_B

LPDDR3_M1_DQ11_B

LPDDR3_M1_DQ10_B

LPDDR3_M1_DQ9_B

LPDDR3_M1_DQ8_B

LPDDR3_M1_DQ7_B

LPDDR3_M1_DQ6_B

LPDDR3_M1_DQ5_B

LPDDR3_M1_DQ4_B

LPDDR3_M1_DQ3_B

LPDDR3_M1_DQ2_B

LPDDR3_M1_DQ1_B

LPDDR3_M1_DQ0_B

LPDDR3_M1_DQ31_A

LPDDR3_M1_DQ30_A

LPDDR3_M1_DQ29_A

LPDDR3_M1_DQ28_A

LPDDR3_M1_DQ27_A

LPDDR3_M1_DQ26_A

LPDDR3_M1_DQ25_A

LPDDR3_M1_DQ24_A

LPDDR3_M1_DQ23_A

LPDDR3_M1_DQ22_A

LPDDR3_M1_DQ21_A

LPDDR3_M1_DQ20_A

LPDDR3_M1_DQ19_A

LPDDR3_M1_DQ18_A

LPDDR3_M1_DQ17_A

LPDDR3_M1_DQ16_A

LPDDR3_M1_DQ15_A

LPDDR3_M1_DQ14_A

LPDDR3_M1_DQ13_A

LPDDR3_M1_DQ12_A

LPDDR3_M1_DQ11_A

LPDDR3_M1_DQ10_A

LPDDR3_M1_DQ9_A

LPDDR3_M1_DQ8_A

LPDDR3_M1_DQ7_A

LPDDR3_M1_DQ6_A

LPDDR3_M1_DQ5_A

LPDDR3_M1_DQ4_A

LPDDR3_M1_DQ3_A

LPDDR3_M1_DQ2_A

LPDDR3_M1_DQ1_A

LPDDR3_M1_DQ0_A

2 OF 13

RSVD3

RSVD4

NC4

NC5

NC6

07

AY6

AY4

AP6

AV9

AP7

AV4

AT4

AT7

AT10

AV12

AP13

AT16

AP12

AV13

AT14

AP14

AL1

AR1

AK3

AK2

AL3

AP3

AR3

AT2

AV3

AV2

AW1

BD2

BC2

BB3

AW3

BC1

BG12

BJ13

BH12

BG17

BH18

BG11

BJ17

BH16

BJ25

BH26

BG22

BJ21

BH20

BG26

BG21

BG25

BC18

BA18

AU20

BF18

AU22

AV22

AV20

BD18

BF20

BA22

BF24

BA20

BD20

BC20

BD24

BD26

AT24

AU24

BA12

BF2

BH10

?

3

M1_B_DQ31

M1_B_DQ30

M1_B_DQ29

M1_B_DQ28

M1_B_DQ27

M1_B_DQ26

M1_B_DQ25

M1_B_DQ24

M1_B_DQ23

M1_B_DQ22

M1_B_DQ21

M1_B_DQ20

M1_B_DQ19

M1_B_DQ18

M1_B_DQ17

M1_B_DQ16

M1_B_DQ15

M1_B_DQ14

M1_B_DQ13

M1_B_DQ12

M1_B_DQ11

M1_B_DQ10

M1_B_DQ9

M1_B_DQ8

M1_B_DQ7

M1_B_DQ6

M1_B_DQ5

M1_B_DQ4

M1_B_DQ3

M1_B_DQ2

M1_B_DQ1

M1_B_DQ0

M1_A_DQ31

M1_A_DQ30

M1_A_DQ29

M1_A_DQ28

M1_A_DQ27

M1_A_DQ26

M1_A_DQ25

M1_A_DQ24

M1_A_DQ23

M1_A_DQ22

M1_A_DQ21

M1_A_DQ20

M1_A_DQ19

M1_A_DQ18

M1_A_DQ17

M1_A_DQ16

M1_A_DQ15

M1_A_DQ14

M1_A_DQ13

M1_A_DQ12

M1_A_DQ11

M1_A_DQ10

M1_A_DQ9

M1_A_DQ8

M1_A_DQ7

M1_A_DQ6

M1_A_DQ5

M1_A_DQ4

M1_A_DQ3

M1_A_DQ2

M1_A_DQ1

M1_A_DQ0

M1_B_DQ31 [18]

M1_B_DQ30 [18]

M1_B_DQ29 [18]

M1_B_DQ28 [18]

M1_B_DQ27 [18]

M1_B_DQ26 [18]

M1_B_DQ25 [18]

M1_B_DQ24 [18]

M1_B_DQ23 [18]

M1_B_DQ22 [18]

M1_B_DQ21 [18]

M1_B_DQ20 [18]

M1_B_DQ19 [18]

M1_B_DQ18 [18]

M1_B_DQ17 [18]

M1_B_DQ16 [18]

M1_B_DQ15 [18]

M1_B_DQ14 [18]

M1_B_DQ13 [18]

M1_B_DQ12 [18]

M1_B_DQ11 [18]

M1_B_DQ10 [18]

M1_B_DQ9 [18]

M1_B_DQ8 [18]

M1_B_DQ7 [18]

M1_B_DQ6 [18]

M1_B_DQ5 [18]

M1_B_DQ4 [18]

M1_B_DQ3 [18]

M1_B_DQ2 [18]

M1_B_DQ1 [18]

M1_B_DQ0 [18]

M1_A_DQ31 [18]

M1_A_DQ30 [18]

M1_A_DQ29 [18]

M1_A_DQ28 [18]

M1_A_DQ27 [18]

M1_A_DQ26 [18]

M1_A_DQ25 [18]

M1_A_DQ24 [18]

M1_A_DQ23 [18]

M1_A_DQ22 [18]

M1_A_DQ21 [18]

M1_A_DQ20 [18]

M1_A_DQ19 [18]

M1_A_DQ18 [18]

M1_A_DQ17 [18]

M1_A_DQ16 [18]

M1_A_DQ15 [18]

M1_A_DQ14 [18]

M1_A_DQ13 [18]

M1_A_DQ12 [18]

M1_A_DQ11 [18]

M1_A_DQ10 [18]

M1_A_DQ9 [18]

M1_A_DQ8 [18]

M1_A_DQ7 [18]

M1_A_DQ6 [18]

M1_A_DQ5 [18]

M1_A_DQ4 [18]

M1_A_DQ3 [18]

M1_A_DQ2 [18]

M1_A_DQ1 [18]

M1_A_DQ0 [18]

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

BSW 2/10 (DDRB)

BSW 2/10 (DDRB)

BSW 2/10 (DDRB)

Tuesday, April 12, 2016 417

Tuesday, April 12, 2016 417

Tuesday, April 12, 2016 417

1

1A

1A

1A

Page 8

5

4

3

2

1

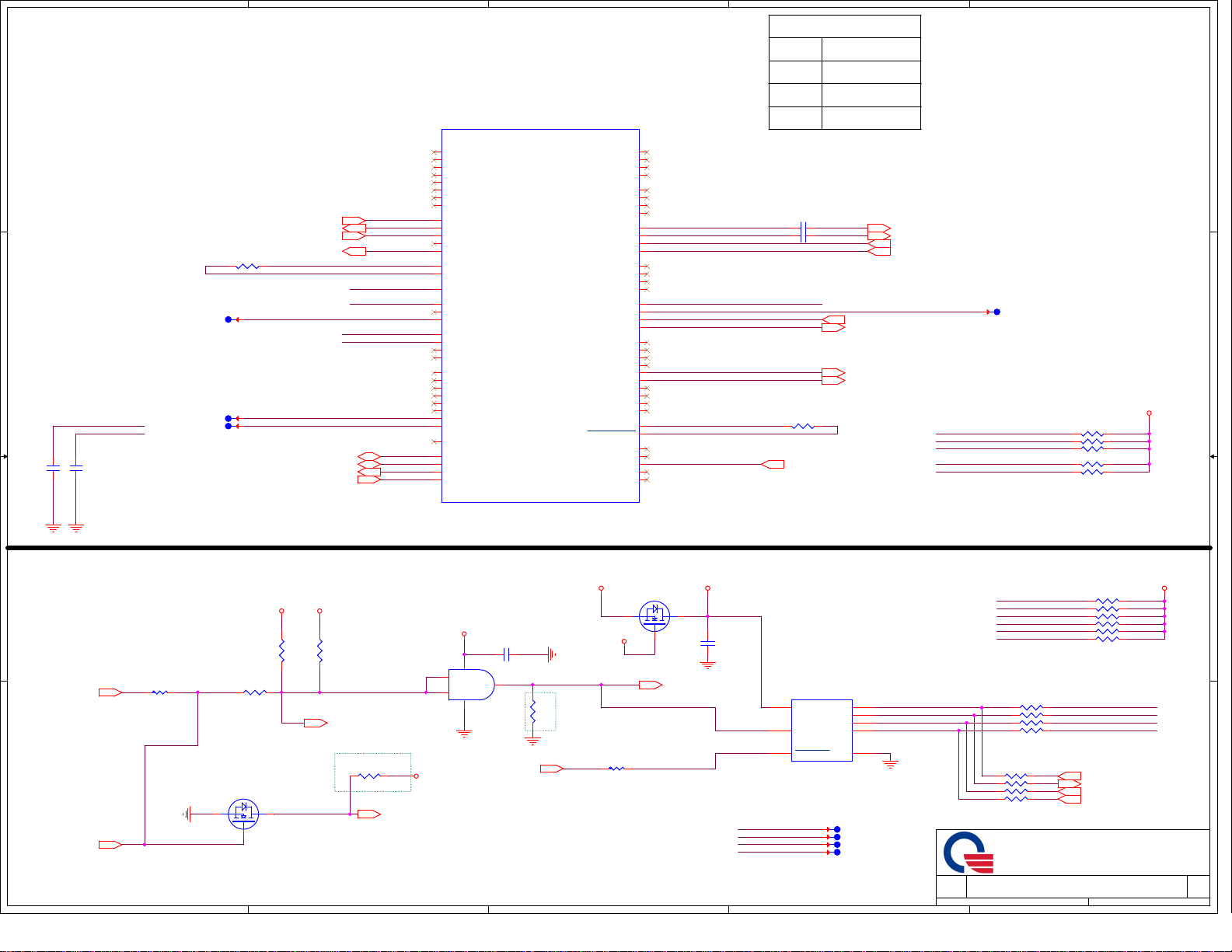

BRASWELL SOC - DISPLAY, XDP, EMMC, SD

SoC (CPU)

?

DDI0

DDI1

DDI2

BSW_MCP_EDS

3 OF 13

SDMMC1

SDMMC2

SDMMC3

3

RSVD15

RSVD12

RSVD14

RSVD13

MCSI_1_CLKP

MCSI_1_CLKN

MCSI_1_DP_0

MCSI_1_DN_0

MCSI_1_DP_1

MCSI_1_DN_1

MCSI_1_DP_2

MCSI_1_DN_2

MCSI_1_DP_3

MCSI_1_DN_3

MCSI and Camera interface

MCSI_2_CLKP

MCSI_2_CLKN

MCSI_2_DP_0

MCSI_2_DN_0

MCSI_2_DP_1

MCSI_2_DN_1

RSVD17

RSVD16

MCSI_COMP

GP_CAMERASB00

GP_CAMERASB01

GP_CAMERASB02

GP_CAMERASB03

GP_CAMERASB04

GP_CAMERASB05

GP_CAMERASB06

GP_CAMERASB07

GP_CAMERASB08

GP_CAMERASB09

GP_CAMERASB10

GP_CAMERASB11

SDMMC1_CLK

SDMMC1_CMD

SDMMC1_D0

SDMMC1_D1

SDMMC1_D2

SDMMC1_D3_CD_B

MMC1_D4_SD_WE

MMC1_D5

MMC1_D6

MMC1_D7

MMC1_RCLK

SDMMC1_RCOMP

SDMMC2_CLK

SDMMC2_CMD

SDMMC2_D0

SDMMC2_D1

SDMMC2_D2

SDMMC2_D3_CD_B

SDMMC3_CLK

SDMMC3_CMD

SDMMC3_CD_B

SDMMC3_D0

SDMMC3_D1

SDMMC3_D2

SDMMC3_D3

SDMMC3_1P8_EN

SDMMC3_PWR_EN_B

SDMMC3_RCOMP

M44

K44

K48

K47

T44

T45

Y47

Y48

V45

V47

V50

V48

T41

T42

P50

P48

P47

P45

M48

M47

T50

T48

P44

AB41

AB45

AB44

AC53

AB51

AB52

AA51

AB40

Y44

Y42

Y41

V40

M7

P6

M6

M4

P9

P7

T6

T7

T10

T12

T13

P13

K10

K9

M12

M10

K7

K6

F2

D2

K3

J1

J3

H3

G2

K2

L3

P12

?

R637 150/F_4

TP_RSVD_STRAP2

EMMC_CLK

EMMC_CMD

EMMC_D0

EMMC_D1

EMMC_D2

EMMC_D3

EMMC_D4

EMMC_D5

EMMC_D6

EMMC_D7

EMMC_RCOMP

SD3_CLK

SDIO3_RCOMP

SD3_CLK

Q

R453 100/F_4

R452 80.6/F_4

C106

*33P/50V_4

2

SD MAPPING

SDMMC1

SDMMC2

SDMMC3

OBSDATA_C0 [16]

OBSDATA_C1 [16]

OBSDATA_C2 [16]

OBSDATA_C3 [16]

OBSDATA_D0 [16]

OBSDATA_D1 [16]

OBSDATA_D2 [16]

OBSDATA_D3 [16]

OBSFN_C0 [16,23]

SDMMC3_1P8_EN [41]

SDMMC3_PWR_EN_N [19,41]

EMMC

NC

SD card

TP_RSVD_STRAP1 [23]

TP_RSVD_STRAP2 [23]

EMMC_CLK [19]

EMMC_CMD [19]

EMMC_D0 [19]

EMMC_D1 [19]

EMMC_D2 [19]

EMMC_D3 [19]

EMMC_D4 [19]

EMMC_D5 [19]

EMMC_D6 [19]

EMMC_D7 [19]

EMMC_RCLK [19]

SD3_CLK [19]

SD3_CMD [19]

SD3_CD# [19,21]

SD3_D0 [19]

SD3_D1 [19]

SD3_D2 [19]

SD3_D3 [19]

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, April 12, 2016 418

Date: Sheet of

Tuesday, April 12, 2016 418

Date: Sheet of

Tuesday, April 12, 2016 418

EMMC_CLK

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

BSW 3/10 (DDI,SD,EMMC)

BSW 3/10 (DDI,SD,EMMC)

BSW 3/10 (DDI,SD,EMMC)

DISPLAY MAPPING

D D

DDI0

DDI1

DDI2

C C

EDP_HPD[20]

B B

A A

NA

eDP

HDMI

EDP_HPD

R105

100K/F_4

5

2

Q14

2N7002K

+V1P8A

3

1

R124

10K_4

+V1P8A

R155

*10K_4

R459 402/F_4

R458 402/F_4

TP80

TP79

TP72

TP74

TP75

TP76

EDP_TXP0_DP[20]

EDP_TXN0_DN[20]

EDP_TXP1_DP[20]

EDP_TXN1_DN[20]

EDP_AUXP_DP[20]

EDP_AUXN_DN[20]

EDP_BKLTEN[35]

EDP_BKLTCTL[35]

EDP_VDDEN[41]

INT_HDMITX2P_DP[22]

INT_HDMITX2N_DN[22]

INT_HDMITX1P_DP[22]

INT_HDMITX1N_DN[22]

INT_HDMITX0P_DP[22]

INT_HDMITX0N_DN[22]

INT_HDMICLK_DP[22]

INT_HDMICLK_DN[22]

INT_HDMI_HPD[22]

HDMI_DDCCLK_SW[22]

HDMI_DDCDATA_SW[22]

DP_USB_C_HPD

DDI0_PLLOBS_DP

DDI0_PLLOBS_DN

EDP_HPD_L

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

DDI1_PLLOBS_DP

DDI1_PLLOBS_DN

INT_HDMI_HPD

HDMI_DDCCLK_SW

HDMI_DDCDATA_SW

4

U17C

D50

DDI0_TXP_0

C51

DDI0_TXN_0

H49

DDI0_TXP_1

H50

DDI0_TXN_1

F53

DDI0_TXP_2

F52

DDI0_TXN_2

G53

DDI0_TXP_3

G52

DDI0_TXN_3

H47

DDI0_AUXP

H46

DDI0_AUXN

W51

HV_DDI0_HPD

Y51

HV_DDI0_DDC_SCL

Y52

HV_DDI0_DDC_SDA

V52

PANEL0_BKLTEN

V51

PANEL0_BKLTCTL

W53

PANEL0_VDDEN

F38

DDI0_PLLOBS_P

G38

DDI0_PLLOBS

J51

DDI1_TXP_0

H51

DDI1_TXN_0

K51

DDI1_TXP_1

K52

DDI1_TXN_1

L53

DDI1_TXP_2

L51

DDI1_TXN_2

M52

DDI1_TXP_3

M51

DDI1_TXN_3

M42

DDI1_AUXP

K42

DDI1_AUXN

R51

HV_DDI1_HPD

P51

PANEL1_BKLTEN

P52

PANEL1_BKLTCTL

R53

PANEL1_VDDEN

F47

DDI1_PLLOBS_P

F49

DDI1_PLLOBS

F40

DDI2_TXP_0

G40

DDI2_TXN_0

J40

DDI2_TXP_1

K40

DDI2_TXN_1

F42

DDI2_TXP_2

G42

DDI2_TXN_2

D44

DDI2_TXP_3

F44

DDI2_TXN_3

D48

DDI2_AUXP

C49

DDI2_AUXN

U51

HV_DDI2_HPD

T51

HV_DDI2_DDC_SCL

T52

HV_DDI2_DDC_SDA

B53

RSVD6

A52

RSVD3

E52

RSVD9

D52

RSVD8

B50

RSVD5

B49

RSVD4

E53

RSVD10

C53

RSVD7

A51

RSVD2

A49

RSVD1

G44

RSVD11

BSW_MCP_EDS

REV = 1

NC's

1

08

C293 *22p/50V_4

1A

1A

1A

Page 9

5

4

3

2

1

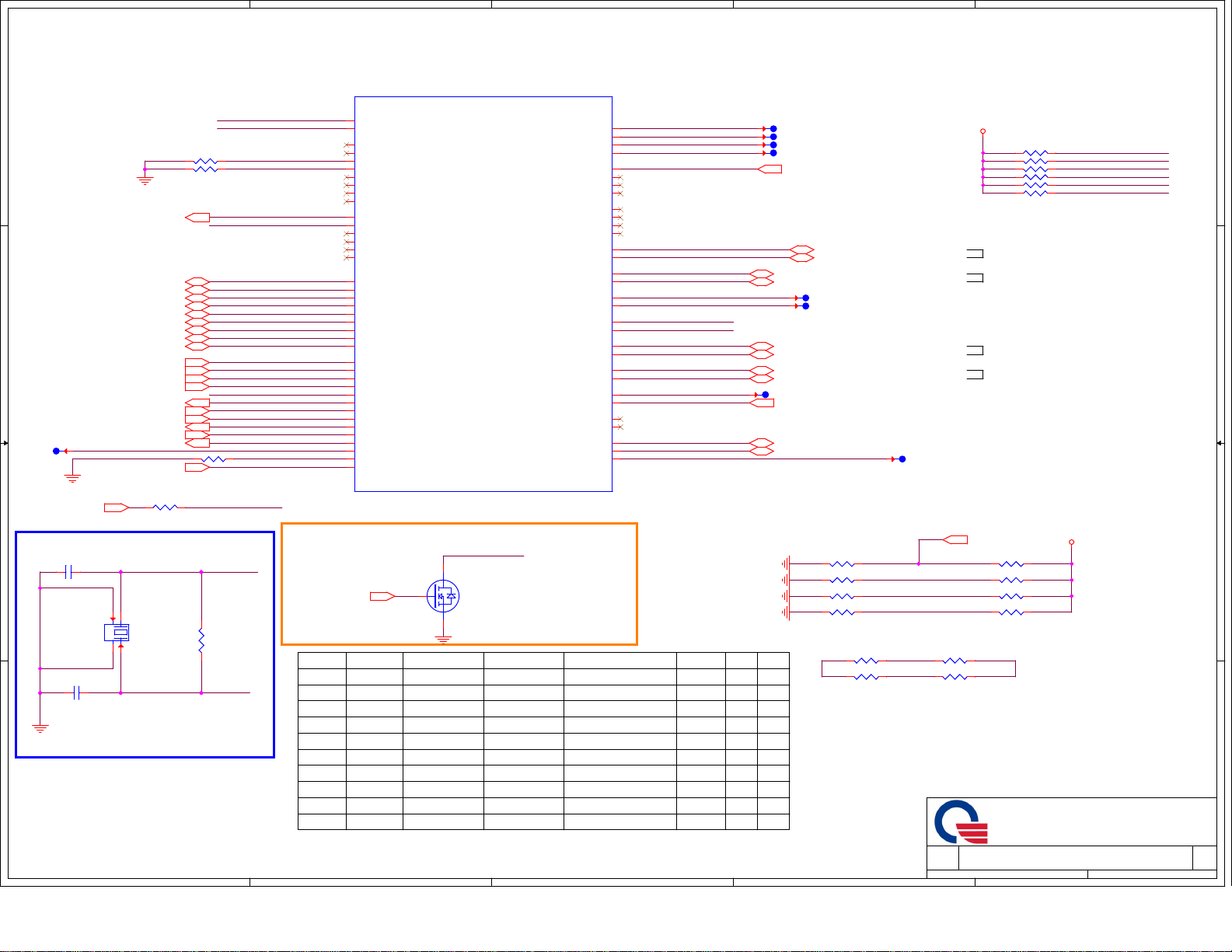

PCIe MAPPING

BSW SOC - SATA, PCIe, SPI, I2S

SoC (CPU)

D D

EC_IN_RW_Q[35]

WIFI_DISABLE#[35]

TOUCH_INT#[35]

R451 402/F_4

TP68

C C

TP70

TP69

C315 *22p/50V_4

I2S_LRCLK_R

I2S_BCLK_R

C323 *22p/50V_4

RAMID0[10]

MIC_PRESENT_L_SOC

AUDIO_SWITCH_INT_N

I2S_BCLK_R[26]

I2S_LRCLK_R[26]

I2S_DOUT_R[26]

I2S_DIN_R[26]

EC_IN_RW_Q

TOUCH_INT#

RAMID0

SATA_RCOMP_DP

SATA_RCOMP_DN

FAST_SPI_CLK

FAST_SPI_CS0

LTE_DISABLE#

FAST_SPI_D0

FAST_SPI_D1

U17D

C31

SATA_TXP0

B30

SATA_TXN0

N28

SATA_RXP0

M28

SATA_RXN0

C29

SATA_TXP1

A29

SATA_TXN1

J28

SATA_RXP1

K28

SATA_RXN1

AH3

SATA_LEDN

AH2

SATA_GP0

AG3

SATA_GP1

AG1

SATA_GP2

AF3

SATA_GP3/SATA_DEVSLP1

N30

SATA_RCOMP_P

M30

SATA_RCOMP_N

W3

FST_SPI_CLK

V4

FST_SPI_CS0_B

V6

FST_SPI_CS1_B

V7

FST_SPI_CS2_B

V2

FST_SPI_D0

V3

FST_SPI_D1

U1

FST_SPI_D2

U3

FST_SPI_D3

AF13

MF_HDA_RSTB

AD6

MF_HDA_SDI1

AD9

MF_HDA_CLK

AD7

MF_HDA_SDI0

AF12

MF_HDA_SYNC

AF14

MF_HDA_SDO

AB9

MF_HDA_DOCKENB

AB7

MF_HDA_DOCKRSTB

H4

SPKR

AK9

GP_SSP_2_CLK

AK10

GP_SSP_2_FS

AK12

GP_SSP_2_TXD

AK13

GP_SSP_2_RXD

BSW_MCP_EDS

REV = 1

BSW_MCP_EDS

SATA

FAST SPI

AUDIO

?

4 OF 13

PCIE_TXP0

PCIE_TXN0

PCIE_RXP0

PCIE_RXN0

PCIE_TXP1

PCIE_TXN1

PCIE_RXP1

PCIE_RXN1

PCIE_TXP2

PCIe

PCIE_TXN2

PCIE_RXP2

PCIE_RXN2

PCIE_TXP3

PCIE_TXN3

PCIE_RXP3

PCIE_RXN3

PCIE_CLKREQ0B

PCIE_CLKREQ1B

PCIE_CLKREQ2B

PCIE_CLKREQ3B

CLK_DIFF_P_0

CLK_DIFF_N_0

CLK_DIFF_P_1

CLK_DIFF_N_1

CLK_DIFF_P_2

CLK_DIFF_N_2

CLK_DIFF_P_3

CLK_DIFF_N_3

RSVD_C16

RSVD_B16

PCIE_RCOMP_P

SATA_RCOMP

SPI1_CLK

SPI1_CS0_B

SPI

SPI1_CS1_B

SPI1_MISO

SPI1_MOSI

C24

B24

G20

J20

A25

C25

D20

F20

B26

C26

D22

F22

A27

C27

G24

J24

AM10

AM12

AK14

AM14

A21

C21

C19

B20

C18

B18

C17

A17

C16

B16

D26

F26

V14

Y13

Y12

V13

V12

?

PCIE_TX2_WLAN_C_DP

PCIE_TX2_WLAN_C_DN

PCIE_RX2_WLAN_DP

PCIE_RX2_WLAN_DN

PCIE_CLKREQ_IMAGE#

LTE_WAKE#

PCIE_CLKREQ_WLAN#

AUDIO_CODEC_IRQ

SOC_PCIE_COMP_DP

SOC_PCIE_COMN_DN

PMIC_IRQ_N

PCIE0

PCIE1

PCIE2

NC

NC

WIFI (StP)

PCIE3 NC

C108 0.1U/16V_4

C107 0.1U/16V_4

R460 402/F_4

PMIC_IRQ_N [39]

PCIE_TX2_WLAN_DP [24]

PCIE_TX2_WLAN_DN [24]

PCIE_RX2_WLAN_DP [24]

PCIE_RX2_WLAN_DN [24]

PCIE_CLKREQ_WLAN# [24]

AUDIO_CODEC_IRQ [26]

CLK_PCIE_WLANP_DP [24]

CLK_PCIE_WLANN_DN [24]

Q

WLAN

TP55

WLAN

PCIE_CLKREQ_IMAGE#

PCIE_CLKREQ_WLAN#

EC_IN_RW_Q

AUDIO_CODEC_IRQ

LTE_WAKE#

R406 *10K_4

R261 *10K_4

R374 10K_4

R416 10K_4

R409 10K_4

09

+V1P8A

B B

BIOS ROM(CPU)

+V1P8A_ME +V3P3A_EC

+V1P8A_ME

R16

R4

100K_4

*100K_4

SPI_WP_ME

GPIO_SPI_WP[21]

R2 *0_4S

R3 *0_4S

3.3V

SPI_WP_ME_ROM_Q

From debug header

SPI_WP_ME_ROM_Q [30]

Q1

A A

SPI_WP_ME[27]

PJA138K

1

3

PCH_SPI_WP_D

2

R17 1K_4

+V1P8A

PCH_SPI_WP_D [10]

to SoC

From Screw

5

4

C1 0.1U/16V_4

2

1

U1

3 5

NL17SZ08DFT2G

SPI_HOLD#_BIOS[21]

4

From debug header

+V1P8A +V1P8A_ME

1

+V3P3A

SOC_SPI_WP#

R18

100K_4

R299 *0_4

3

Q8

PJA138K

2

SOC_SPI_WP# [34]

SOC_SPI_HOLD#

FAST_SPI_CS0

3

C13

0.1U/16V_4

SOC_SPI_WP#

SOC_SPI_HOLD#

SOC_SPI_MOSI_R

SOC_SPI_MISO_R

SOC_SPI_CLK_R

R19 3.3K/F_4

R272 *3.3K/F_4

R315 3.3K/F_4

R301 *3.3K/F_4

R279 *3.3K/F_4

R314 *3.3K/F_4

SPI NOR FLASH

U7

8

VCC

3

WP#

SOC_SPI_HOLD#

SOC_SPI_MOSI_R

SOC_SPI_MISO_R

SOC_SPI_CS#_R

SOC_SPI_CLK_R

SPI_HOLD7GND

SPI_FLASH_W25Q64FWSSIG

For ICT, place on TOP side

SPI_SI

SPI_SO

CS#

SPI_SCK

TP6

TP1

TP2

TP7

2

5

SOC_SPI_MOSI_R

2

SOC_SPI_MISO_R

1

SOC_SPI_CS#_R

6

SOC_SPI_CLK_RSOC_SPI_WP#

4

R292 10_4

R270 10_4

R258 10_4

R298 10_4

R284 0_4

R287 0_4

R273 0_4

R290 0_4

GD_SPI_SI_R [21]

GD_SPI_SO_R [21]

GD_SPI_CS0#_R [21]

GD_SPI_CLK_R [21]

CAD note: Place near to SPI flash

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

BSW 4/10 (PCIE/SATA/SPI)

BSW 4/10 (PCIE/SATA/SPI)

BSW 4/10 (PCIE/SATA/SPI)

Tuesday, April 12, 2016 419

Tuesday, April 12, 2016 419

Tuesday, April 12, 2016 419

1

FAST_SPI_D0

FAST_SPI_D1

FAST_SPI_CS0

FAST_SPI_CLK

+V1P8A_ME

1A

1A

1A

Page 10

5

4

3

2

1

SoC (CPU)

D D

C C

TP28

19.2MHz X'tal

B B

C116 22p/50V_4

A A

BRASWELL - I2C, XDP, SM BUS

AJACK_PRESENT_SOC[35]

SOC_KBC_SMI[23]

C111 22p/50V_4

19.2MHz crystal

I2S_MCLK_R[26]

XDP_GPIO_DFX0[16]

XDP_GPIO_DFX1[16]

XDP_GPIO_DFX2[16]

XDP_GPIO_DFX3[16]

XDP_GPIO_DFX4[16]

XDP_GPIO_DFX5[16]

XDP_GPIO_DFX6[16]

XDP_GPIO_DFX7[16]

XDP_GPIO_DFX8[16]

SOC_WAKE_SCI_N[23,34]

MUX_AUD_INT1#[23,35]

EC_SMI_L[23,34]

KBD_IRQ#[23,34]

EC_KBD_ALERT_SOC[23]

SOC_RUNTIME_SCI[16,23]

TRACKPAD_INT#[23,29]

NFC_FW_RESET#[23]

TP_RSVD_STRAP3[23]

NFC_PWR_MANAGE[23]

R100 *0_4S

1

2

Y1

19.2MHZ +-30PPM

4

3

5

XTAL19_2_IN

XTAL19_2_OUT

R444 2.49K/F_4

R448 49.9/F_4

I2S_MCLK_R

RAMID2

DFX_SUS_DBG_STRAP

EC_KBD_ALERT_SOC

SIM_DET_C

R139 100/F_4

SOC_GPIO_RCOMP

AJACK_PRESENT_SOC

pullup at level shifter side

DFX_SUS_DBG_STRAP

XTAL19_2_OUT

R168

200K/F_4

XTAL19_2_IN

U17E

P24

OSCIN

M22

OSCOUT

J26

RSVD13

N26

RSVD17

ICLK_ICOMP

ICLK_RCOMP

P20

ICLKICOMP

N20

ICLKRCOMP

P26

RSVD18

K26

RSVD14

M26

RSVD16

AH45

RSVD1

A9

MF_PLT_CLK0

C9

MF_PLT_CLK1

B8

MF_PLT_CLK2

B7

MF_PLT_CLK3

B5

MF_PLT_CLK4

B4

MF_PLT_CLK5

AM40

GPIO_DFX0

AM41

GPIO_DFX1

AM44

GPIO_DFX2

AM45

GPIO_DFX3

AM47

GPIO_DFX4

AK48

GPIO_DFX5

AM48

GPIO_DFX6

AK41

GPIO_DFX7

AK42

GPIO_DFX8

AD51

GPIO_SUS0

AD52

GPIO_SUS1

AH50

GPIO_SUS2

AH48

GPIO_SUS3

AH51

GPIO_SUS4

AH52

GPIO_SUS5

AG51

GPIO_SUS6

AG53

GPIO_SUS7

AF52

SEC_GPIO_SUS9

AF51

SEC_GPIO_SUS8

AE51

SEC_GPIO_SUS10

AC51

SEC_GPIO_SUS11

AH40

GPIO0_RCOMP

Y3

GPIO_ALERT

BSW_MCP_EDS

REV = 1

0312 added KBD_ALERT pin to notify SoC to lock ME FW

Keep reserving this feature in DVT build

EC_KBD_ALERT[30]

Vender RAM_ID[2..0]

RAM_ID3

0 (1-CH)

Hynix

Micron

Samsung

Micron

Samsung AKD5QWST508 K4E8E304EE-EGCF 1866MHz

0 (1-CH) 2GB

0 (1-CH)

0 (1-CH)

1 (2-CH) 000

Hynix

Micron

Samsung

Micron

1 (2-CH)

1 (2-CH)

4

BSW_MCP_EDS

iCLK

PLTFM CLK's

GPIO_DFX

GPIO_SUS

EC_KBD_ALERT_SOC

3

2

Q13

PJA138K

1

000 1866MHzSamsung K4E8E304EE-EGCF

001

010

011

100

001

010

011

100

?

RESERVED ISH GPIOs - RSVD for type C GPIOs

C11

B10

F12

F10

D12

E8

C7

D6

J12

F7

J14

L13

AK6

AH7

AF6

AH6

AF9

AF7

AE4

AD2

AC1

AD3

AB2

AC3

AA1

AB3

AA3

Y2

AM6

AM7

AM9

3

TP_HOST_DETECT

TP_DEVICE_DETECT

TP_POL_DETECT

TP_WAKE_ALERT#

I2C_1_SCL

I2C_1_SDA

I2C_NFC_SCL

I2C_NFC_SDA

RAMID1

RAMID3

I2C_6_SCL

SDCARD_WP

SMB_SOC_CLK

SMB_SOC_DATA

TP_GPIO_2_SOC

Freq.Mfr. PNQ PN Size

1866MHz

1866MHz

1866MHz

1866MHz

1866MHz

1866MHz

1866MHz

1866MHz

RSVD3

RSVD2

RSVD9

RESERVED

I2C

SMBUS

5 OF 13

RSVD8

RSVD5

RSVD7

RSVD4

RSVD6

RSVD11

RSVD10

RSVD12

RSVD15

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

I2C3_SCL

I2C3_SDA

I2C4_SCL

I2C4_SDA

I2C5_SCL

I2C5_SDA

I2C6_SCL

I2C6_SDA

RSVD_AA3

RSVD_Y2

MF_SMB_CLK

MF_SMB_DATA

MF_SMB_ALERTB

?

AKD5QWST508

AKD5RW0TW53

AKD5QWSTL01 4Gb

AKD5QWST521 K4E8E324EB-EGCF

H9CCNNN8GTMLAR-NUD

MT52L256M32D1PF-107

WT:B

AKD5QWWT401 EDF8132A3MA-JD-F-R

AKD5RW0TW53

AKD5QWSTL01

AKD5QWST521 K4E8E324EB-EGCF

H9CCNNN8GTMLAR-NUD

MT52L256M32D1PF-107

WT:B

AKD5QWWT401 EDF8132A3MA-JD-F-R

TP40

TP35

TP77

TP78

I2C_1_SCL [39]

I2C_1_SDA [39]

I2C_4_SCL [35]

I2C_4_SDA [35]

I2C_5_SCL [35]

I2C_5_SDA [35]

TP30

SDCARD_WP [19]

SMB_SOC_CLK [35]

SMB_SOC_DATA [35]

RAMID

Total

Size

4Gb

2GB

4Gb0 (1-CH)

2GB

4Gb

2GB

4Gb

2GB

4Gb

4GB

4GB

4Gb1 (2-CH)

4GB

4Gb1 (2-CH)

4Gb

4GB

4Gb

4GB

PCH_SPI_WP_D [9]

I2C_0_SCL_R [35]

I2C_0_SDA_R [35]

TP64

TP65

R400 10K_4

R441 10K_4

R162 10K_4

R445 10K_4

Samsung Hynix

R527 *10K_4

R534 *10K_4

Micron

2

+V1P8A

R115 4.7K_4

R68 *10K_4

R61 *10K_4

R489 2.2K_4

R486 2.2K_4

R156 4.7K_4

SOC_WAKE_SCI_N

KBD_IRQ#

EC_SMI_L

I2C_1_SCL

I2C_1_SDA

SDCARD_WP

Touch panel

PMIC

Audio

Level shifter is stuffed for Audio codec and MIC switch

Track pad

Level shifter is stuffed

Level shifter of Track Pad INT is stuffed

TP60

RAMID0 [9]

RAMID0

RAMID1

RAMID2

RAMID3

R526 *10K_4

R533 *10K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

R401 *10K_4

R447 *10K_4

R166 *10K_4

R446 *10K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

BSW 5/10 (I2C/DFX/GPIO)

BSW 5/10 (I2C/DFX/GPIO)

BSW 5/10 (I2C/DFX/GPIO)

Tuesday, April 12, 2016 4110

Tuesday, April 12, 2016 4110

Tuesday, April 12, 2016 4110

+V1P8A

For BOM, place BOT side

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

1

10

1A

1A

1A

Page 11

5

4

3

2

1

BRASWELL - USB INTERFACE

SoC (CPU)

D D

BSW_MCP_EDS

U17F

TP36

TP37

TP73

TP81

USB3_TXP1_DP[27]

USB3_TXN1_DN[27]

USB3_RXP1_DP[27]

USB3_RXN1_DN[27]

USB3_TXP2_DP[28]

USB3_TXN2_DN[28]

USB3_RXP2_DP[28] USBP4_DP [24]

C C

SOC_UART_TX SOC_UART_RX

B B

R1 *0_4

Un-Stuff for Test Only

USB3_RXN2_DN[28]

USB3_OBSP_DP

R461

402/F_4

USB3_OBSN_DN

B32

C32

F28

D28

A33

C33

F30

D30

C34

B34

G32

C35

A35

G34

D34

F34

C37

A37

F36

D36

M34

M32

C38

B38

G36

N34

P34

J32

J34

J36

REV = 1

USB3_TXP0

USB3_TXN0

USB3_RXP0

USB3_RXN0

USB3_TXP1

USB3_TXN1

USB3_RXP1

USB3_RXN1

USB3_TXP2

USB3_TXN2

USB3_RXP2

USB3_RXN2

USB3_TXP3

USB3_TXN3

USB3_RXP3

USB3_RXN3

USB3_RCOMP_P

USB3_OBSN

RSVD4

RSVD1

RSVD7

RSVD6

RSVD11

RSVD10

RSVD5

RSVD2

RSVD8

RSVD9

RSVD12

RSVD13

BSW_MCP_EDS

?

USB3.0

USB_HSIC_0_STROBE

USB_HSIC_0_DATA

HSICUART

USB_HSIC_1_STROBE

USB_HSIC_1_DATA

USB_HSIC_RCOMP

RESERVED

6 OF 13

USB_OTG_ID

USB_DP0

USB_DN0

USB_DP1

USB_DN1

USB_DP2

USB_DN2

USB_DP3

USB_DN3

USB_DP4

USB_DN4

USB_OC1_B

USB2.0

USB_OC0_B

USB_RCOMP1

USB_VBUSSNS

USB_RCOMP

UART1_TXD

UART1_RXD

UART1_CTS_B

UART1_RTS_B

UART2_TXD

UART2_RXD

UART2_CTS_B

UART2_RTS_B

B48

C42

B42

C43

B44

C41

A41

C45

A45

B40

C40

P16

P14

B46

B47

A48

M36

N36

K38

M38

N38

AD10

AD12

AD13

AD14

Y6

Y7

V9

V10

?

TP_USB_OTG_ID

USBP0_DP

USBP0_DN

USB_OC1#

USB_OC0#

USB_VBUSSNS

USB_RCOMP

USB_HSIC_RCOMP

SOC_UART_TX

SOC_UART_RX

TP33

TP39

TP38

USBP1_DP [28]

USBP1_DN [28]

USBP2_DP [28]

USBP2_DN [28]

USBP3_DP [20]

USBP3_DN [20]

R316 10K_4

R428 10K_4

USBP4_DN [24]

R158 10K_4

R157 113/F_4

R450 *49.9/F_4

11

USB3.0_2

USB3.0_1

CCD

BT

USB_OC1# [28,34]

+V1P8A

USB_OC0# [28,34]

SOC_UART_TX [21]

SOC_UART_RX [21]

A A

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

BSW 6/10 (USB)

BSW 6/10 (USB)

BSW 6/10 (USB)

Tuesday, April 12, 2016 4111

Tuesday, April 12, 2016 4111

Tuesday, April 12, 2016 4111

1

1A

1A

1A

Page 12

5

4

3

2

1

C115

0.1U/16V_4

12

+V1P8S

+V1P8A

BRASWELL - JTAG, LPC, THERMAL, PMU

SoC (CPU)

D D

XDP_H_TCK[16]

XDP_H_TDI[16]

XDP_H_TDO[16]

XDP_H_TMS[16]

XDP_H_TRST#[16]

XDP_H_PRDY_N[16]

R455 10K_4

CLK_PCI_EC[27,30]

R449 100/F_4 R500 *0_4S

C C

CLK_PCI_EC

C297 *22p/50V_4

XDP_H_PREQ_N[16]

CLK_PCI_EC

TP32

LPC_CLKRUN_L[30]

LPC_LFRAME#[27,30]

ILB_SERIRQ[34]

R457 10_4

LPC_LAD0[27,30]

LPC_LAD1[27,30]

LPC_LAD2[27,30]

LPC_LAD3[27,30]

PROCHOT#[21,30]

PLACE 'CC' CAP NEAR SOC

RSVD_M13

CLK_PCI_EC_SOC

TP_L_CLKOUT1

RCOMP_LPC_HVT

ILB_SERIRQ

+V1P8A

PROCHOT#

CC

R48

20K_4

C49

0.1U/16V_4

AF42

AD47

AF40

AD48

AB48

AD45

AF41

M13

P28

P30

AF50

AF48

AF44

AF45

AD50

P2

R3

T3

P3

M3

M2

N3

N1

T4

T2

H5

H7

REV = 1

U17G

TCK

TDI

TDO

TMS

TRST_B

CX_PRDY_B

CX_PREQ_B

RSVD5

MF_LPC_CLKOUT0

MF_LPC_CLKOUT1

LPC_CLKRUNB

LPC_FRAMEB

MF_LPC_AD0

MF_LPC_AD1

MF_LPC_AD2

MF_LPC_AD3

LPC_HVT_RCOMP

ILB_SERIRQ

RSVD_H5

RSVD_H7

RSVD6

RSVD7

RSVD4

RSVD3

RSVD1

RSVD2

PROCHOT_B

BSW_MCP_EDS

BSW_MCP_EDS

JTAG/ITP

Reserved

?

BRTCX1_PAD

RTC_EXTPAD

RTC

COREPW ROK

SUSPWRDNACK

SUS_STAT_B

PMU_SUSCLK

PMU_SLP_S4_B

PMU_SLP_S3_B

PMU_RESETBUTTON_B

PMU

LPC

PMU_PLTRST_B

PMU_BATLOW_B

PMU_AC_PRESENT

PMU_SLP_S0IX_B

PMU_SLP_LAN_B

PMU_WAKE_B

PMU_PW RBTN_B

PMU_WAKE_LAN_B

PWM

SVID

SVID0_ALERT_B

CORE_VCC0_SENSE

CORE_VSS0_SENSE

CORE_VCC1_SENSE

CORE_VSS1_SENSE

Voltage sense

DDI_VGG_SENSE

UNCORE_VSS_SENSE2

UNCORE_VSS_SENSE1

7 OF 13

RTCX2_PAD

SRTCRST_B

RSMRST_B

RTC_TEST

RSVD_VSS

SVID0_CLK

SVID0_DATA

M18

K18

F16

D18

G16

F18

J16

G18

AE3

D14

C15

C12

B14

AF2

F14

C14

C13

A13

B12

N16

M16

P18

AD42

AD41

AD40

AG32

AJ32

AD29

AF27

AD24

AD22

AC27

?

RTC_X1

RTC_X2

BRTC_EXTPAD

SRTCRST#

CORE_PWROK_R

SOC_RSMRST#

SOC_RTEST#

RSVD_VSS_G18

PMC_SUSPWRDNACK

PMC_SUS_STAT#

PMC_SUSCLK0

SLP_S4#

SLP_S3#

SOC_REST_BTN#

SOC_PLTRST#

PMC_BATLOW#

ACPRESENT

SLP_S0IX#

TP_SOC_SLP_LAN#

SOC_PMC_WAKE#

SOC_PWRBTN#

TP_PMU_WAKE_LAN_B

SVID_ALERT#

+VCORE_VCC0_SENSEP_DP

+VCORE_VCC1_SENSEP_DP

R56 100K_4

C302 0.1U/16V_4

CORE_PWROK_R [16,30,39]

SOC_RSMRST# [16,34]

PMC_SUSPWRDNACK [34]

PMC_SUS_STAT# [34]

PMC_SUSCLK0 [35]

SLP_S4# [34,39]

SLP_S3# [34,39,41]

SOC_REST_BTN# [16,21,34]

SOC_PLTRST# [16,19,34]

ACPRESENT [35]

SLP_S0IX# [34,39]

PCH_WAKE_L [34]

SOC_PWRBTN# [34]

+V1P05A_R_SOC

R96 0_4

R95 0_4

SENSEP and SENSEN differential routing

RTC 32.768KHz X'tal

Y2 32.768KHZ

1 2

R169 10M_4

C117

15P/50V_4

R160 10K/F_4

TP34

TP71

+VCC_SENSEP_DP [39]

+VGG_SENSEP_DP [39]

+VNN_SENSEP [39]

RTC_X2

C114

15P/50V_4

PLACE 'CB' CAP NEAR SOC

CORE_PWROK_R

CB

O_1.8VA

SOC_PMC_WAKE# [35]

SOC_REST_BTN#

PMC_SUSPWRDNACK

SOC_PMC_WAKE#

ACPRESENT

PMC_BATLOW#

R487 *10K_4

R443 10K_4

R499 10K_4

R163 2.2K_4

R466 10K_4

B B

VBATA_VR_HOT_N[37]

TEMP_ALERT#[33]

TEMP_ALERT#

RTC Circuitry(RTC)

R60 *0_4S

R53 *0_4S

+VRTC +VRTC

PROCHOT#VBATA_VR_HOT_N

RTC CIRCUIT

R476

20K_4

A A

EC_STRAP_GPIO1[30]

3

2

Q50

2N7002K

1

5

SRTCRST# SOC_RTEST#

C314

1u/6.3V_4

EC_STRAP_GPIO1

4

3

2

Q49

2N7002K

1

R482

20K_4

C313

1u/6.3V_4

R484

*0_6S

Imax support up to 100uA

Estimate 1.5mW Ploss at Imax

3

+VRTC+V3P3A_LDO

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

BSW 7/10 (JTAG/LPC//PMU)

BSW 7/10 (JTAG/LPC//PMU)

BSW 7/10 (JTAG/LPC//PMU)

Tuesday, April 12, 2016 4112

Tuesday, April 12, 2016 4112

Tuesday, April 12, 2016 4112

1

1A

1A

1A

Page 13

5

4

3

2

1

SoC (CPU)

D D

C C

PLACE THESE CAPS CLOSE TO

AK30, AK35, AK38 AND AM29

PLACE THESE CAPS CLOSE TO

AM19 AND AK21

B B

BRASWELL - POWER 1

+VCC

C241

1U/10V_4

C88

22uF/6.3V_6

C91

22uF/6.3V_6

C90

22uF/6.3V_6

C89

22uF/6.3V_6

C269 22uF/6.3V_6

C261 22uF/6.3V_6

C266

C272 22uF/6.3V_6

1U/10V_4

C251

1U/10V_4

C254

10u/6.3V_4

C246

1U/10V_4

C83

1U/10V_4

C244

4.7U/6.3V_4

+V1P15A

C257

4.7U/6.3V_4

C252

10u/6.3V_4

C247

1U/10V_4

C248

1U/10V_4

+VCC

+V1P15A

+VGG

C78

1U/10V_4

C82

C264

4.7U/6.3V_4

C256

4.7U/6.3V_4

1U/10V_4

C253

10u/6.3V_4

C77

1U/10V_4

+V1P15A

C265

4.7U/6.3V_4

C263

4.7U/6.3V_4

U17H

AF36

CORE_VCC1_S0IX3

AG33

CORE_VCC1_S0IX7

AG35

CORE_VCC1_S0IX8

AG36

CORE_VCC1_S0IX9

AG38

CORE_VCC1_S0IX10

AJ33

CORE_VCC1_S0IX14

AJ36

CORE_VCC1_S0IX15

AJ38

CORE_VCC1_S0IX16

AF30

CORE_VCC1_S0IX2

AG27

CORE_VCC1_S0IX4

AG29

CORE_VCC1_S0IX5

AG30

CORE_VCC1_S0IX6

AJ27

CORE_VCC1_S0IX11

AJ29

CORE_VCC1_S0IX12

AJ30

CORE_VCC1_S0IX13

AF29

CORE_VCC1_S0IX1

AD16

DDI_VGG_S0IX1

AD18

DDI_VGG_S0IX2

AD19

DDI_VGG_S0IX3

AF16

DDI_VGG_S0IX4

AF18

DDI_VGG_S0IX5

AF19

DDI_VGG_S0IX6

AF21

DDI_VGG_S0IX7

AF22

DDI_VGG_S0IX8

AJ19

DDI_VGG_S0IX15

AG16

DDI_VGG_S0IX9

AG18

DDI_VGG_S0IX10

AG19

DDI_VGG_S0IX11

AG21

DDI_VGG_S0IX12

AG22

DDI_VGG_S0IX13

AG24

DDI_VGG_S0IX14

AJ21

DDI_VGG_S0IX16

AJ22

DDI_VGG_S0IX17

AJ24

DDI_VGG_S0IX18

AK24

DDI_VGG_S0IX19

AK30

CORE_V1P15_S0IX1

AK35

CORE_V1P15_S0IX2

AK36

CORE_V1P15_S0IX3

AM29

CORE_V1P15_S0IX4

AK33

FUSE_V1P15_S0IX2

AJ35

FUSE_V1P15_S0IX1

AM19

VCCSRAMGEN_1P152

AK21

VCCSRAMGEN_1P151

BSW_MCP_EDS

REV = 1

?

BSW_MCP_EDS

UNCORE_VNN_S41

UNCORE_VNN_S42

UNCORE_VNN_S43

UNCORE_VNN_S44

UNCORE_VNN_S45

UNCORE_VNN_S46

UNCORE_VNN_S47

UNCORE_VNN_S48

UNCORE_VNN_S49

UNCORE_VNN_S410

UNCORE_VNN_S411

UNCORE_VNN_S412

UNCORE_VNN_S413

UNCORE_VNN_S414

VCCSRAMSOCIUN_1P056

VCCSRAMSOCIUN_1P051

VCCSRAMSOCIUN_1P052

VCCSRAMSOCIUN_1P053

VCCSRAMSOCIUN_1P054

VCCSRAMSOCIUN_1P055

VCCSRAMSOCIUN_1P057

VCCSRAMSOCIUN_1P058

VCCSRAMSOCIUN_1P059

VCCSRAMSOCIUN_1P0510

ICLK_GND_OFF2

iCLKDDRPCIeSATAUSBFUSE

ICLK_GND_OFF1

DDR_V1P05A_G31

DDR_V1P05A_G34

DDR_V1P05A_G32

DDR_V1P05A_G35

DDR_V1P05A_G36

DDR_V1P05A_G33

PCIE_V1P05A_G31

PCIE_V1P05A_G32

SATA_V1P05A_G32

SATA_V1P05A_G31

USB3_V1P05A_G32

USB3_V1P05A_G31

USBSSIC_V1P05A_G3

FUSE3_V1P05A_G5

FUSE_V1P05A_G3

8 OF 13

RSVD1

PLACE THESE CAPS CLOSE TO

AA18, AA19, AA21, AA22, AA24, AA25,

AC18, AC19, AC21, AC22, AC24, AC25,

AD25 AND AD27

AA18

AA19

AA21

AA22

AA24

AA25

AC18

AC19

AC21

AC22

AC24

AC25

AD25

AD27

AA30

V33

AA32

AA33

AA35

AA36

AC32

Y30

Y32

Y33

Y35

V19

V18

AM21

AM33

AM22

AN22

AN32

AM32

V22

V24

U24

U22

V27

U27

V29

N18

U19

?

C280

1U/10V_4

+V1P05A_R_SOC

C312

1U/10V_4

+V1P05A_R_SOC

C233

1U/10V_4

+V1P05A_R_SOC

C306

1U/10V_4

+V1P05A_R_SOC

C120

1U/10V_4

C76

22uF/6.3V_6

C281

1U/10V_4

C278

C112

1U/10V_4

C273

1U/10V_4

C79

22uF/6.3V_6

PLACE THIS

CAP CLOSE TO

N18

C283

1U/10V_4

PLACE THESE CAPS CLOSE TO

V33, AA32, AA33, AA35, AA36,

AC32, Y30, Y32, Y33 AND Y35

1U/10V_4

+V1P05A_R_SOC

C286

1U/10V_4

C230

1U/10V_4

C295

1U/10V_4

+V1P05A_R_SOC

C289

1U/10V_4

C271

C288

1U/10V_4

1U/10V_4

C113

1U/10V_4

C101

22uF/6.3V_6

C100

22uF/6.3V_6

PLACE THIS CAP CLOSE TO V19 AND V18

PLACE THESE CAPS CLOSE TO

AM21, AM33, AM22, AN22, AN32

AND AM32

C229

1U/10V_4

C225

22uF/6.3V_6

C226

22uF/6.3V_6

C232

1U/10V_4

C231

0305 added 4x1uF,4x22uF,1x10uF on DDR_V1P05A

PLACE THESE CAPS CLOSE TO

V22, V24, U24, U22, V27 AND U27

C307

C308

1U/10V_4

1U/10V_4

PLACE THESE CAPS CLOSE TO U19

C294

1U/10V_4

+VNN

C102

22uF/6.3V_6

1U/10V_4

+V1P05A_R_SOC

13

C227

22uF/6.3V_6

C310

22uF/6.3V_6

C224

10u/6.3V_6

R173

*0.002_1206_S

5

+VCCSFRPLLDDR_1P24_1P35

+VCCCLKDDR_1P24_1P35

+V1P05A_R_SOC

C311

*22uF/6.3V_6

+V1P05A_R_SOC

C98

22uF/6.3V_6

CAD NOTE: PLACE CLOSE TO PIN AM21,

AM33, AM22, AN22, AN32 AND AM32 POWER PLANE

4

3

C99

22uF/6.3V_6

C119

22uF/6.3V_6

DUMMY CAPS. TO BE DELETED IN NEXT REVISION

2

C309

*22uF/6.3V_6

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Quanta Computer Inc.

BSW 8/10 (Power 1)

BSW 8/10 (Power 1)

BSW 8/10 (Power 1)

Tuesday, April 12, 2016 4113

Tuesday, April 12, 2016 4113

Tuesday, April 12, 2016 4113

1

1A

1A

1A

+VDDQ

R348 *0_6S

+VDDQ

R350 *0_6S

A A

+V1P05A +V1P05A_R_SOC

1 2

Page 14

5

SoC (CPU)

PLACE THESE CAPS

CLOSE TO AM25

+VCCCLKDDR_1P24_1P35

D D

PLACE THESE CAPS

CLOSE TO THE

DDR_VDDQ_G_ PINS

PLACE THESE CAPS

CLOSE TO E1 AND E2

C C

C211

22uF/6.3V_6

C31

22uF/6.3V_6

PLACE THESE CAPS

CLOSE TO G1

PLACE THESE CAPS

CLOSE TO AH4 AND AF4

+V1P8A_R_SOC

C287

1U/10V_4

PLACE THESE CAPS

CLOSE TO Y18

BRASWELL - POWER 2

PLACE THESE CAPS CLOSE TO AN27

+VCCSFRPLLDDR_1P24_1P35

C210

22uF/6.3V_6

C29

22uF/6.3V_6

+VCCPADCF3SI0_1P8_3P3

C103

1U/10V_4

C260

1U/10V_4

+V1P8A_R_SOC

C290

1U/10V_4

C239

1U/10V_4

C34

22uF/6.3V_6

C292

1U/10V_4

PLACE THESE CAPS

CLOSE TO AD33, AK18,

AF33 AND AK19

C301

1U/10V_4

C94

1U/10V_4

C35

22uF/6.3V_6

C240

1U/10V_4

+VDDQ

+VCCPADCF1SI0_1P8_3P3

+VCCCFIOAZA_1P80

4

U17I

AN27

DDRSFR_VDDQ_G_S4

AM25

DDR_VDDQ_G_S42

BE1

DDR_VDDQ_G_S416

BE53

DDR_VDDQ_G_S419

BJ2

DDR_VDDQ_G_S426

BJ3

DDR_VDDQ_G_S427

BJ49

DDR_VDDQ_G_S428

BJ5

DDR_VDDQ_G_S429

BH50

DDR_VDDQ_G_S425

BH5

DDR_VDDQ_G_S424

BH49

DDR_VDDQ_G_S423

BH4

DDR_VDDQ_G_S422

BE3

DDR_VDDQ_G_S417

BG51

DDR_VDDQ_G_S421

BG3

DDR_VDDQ_G_S420

BJ51

DDR_VDDQ_G_S430

BJ52

DDR_VDDQ_G_S431

AY10

DDR_VDDQ_G_S414

AY44

DDR_VDDQ_G_S415

AV44

DDR_VDDQ_G_S413

AV10

DDR_VDDQ_G_S410

BE51

DDR_VDDQ_G_S418

AV38

DDR_VDDQ_G_S412

AV16

DDR_VDDQ_G_S411

AU36

DDR_VDDQ_G_S49

AU18

DDR_VDDQ_G_S48

AN36

DDR_VDDQ_G_S47

AN35

DDR_VDDQ_G_S46

AN19

DDR_VDDQ_G_S45

AN18

DDR_VDDQ_G_S44

AM36

DDR_VDDQ_G_S43

AM18

DDR_VDDQ_G_S41

E1

SDIO_V3P3A_V1P8A_G31

E2

SDIO_V3P3A_V1P8A_G32

G1

SDIO_V3P3A_V1P8A_G33

AH4

VCCCFIOAZA_1P802

AF4

VCCCFIOAZA_1P801

Y18

GPIO_V1P8A_G35

AD33

GPIO_V1P8A_G31

AK18

GPIO_V1P8A_G33

AF33

GPIO_V1P8A_G32

AK19

GPIO_V1P8A_G34

BSW_MCP_EDS

REV = 1

?

BSW_MCP_EDS

DDR

9 OF 13

DDI_VDDQ_G31

DDI_VDDQ_G32

MIPI_V1P2A_G32

MIPI_V1P2A_G31

ICLK_VSFR_G32

ICLK_VSFR_G31

CORE_VSFR_G35

CORE_VSFR_G36

CORE_VSFR_G31

CORE_VSFR_G34

CORE_VSFR_G32

CORE_VSFR_G33

CORE_VSFR_G31_AC36

USBHSIC_V1P2A_G3

USB_VDDQ_G32

USB_VDDQ_G33

USB_VDDQ_G31

USBRTCFUSE

USBSSIC_V1P2A_G3

USB_V1P8A_G3

USB_V3P3A_G32

USB_V3P3A_G31

RTC_V3P3RTC_G52

RTC_V3P3RTC_G51

RTC_V3P3A_G51

RTC_V3P3A_G52

FUSE_V1P8A_G3

FUSE1_V1P05A_G4

FUSE0_V1P05A_G3

RSVD_VSS

RSVD1

RSVD2

3

+V1P24A_MIPI_SOC

+V1P24A_R_SOC

PLACE THESE CAPS

CLOSE TO Y27 & Y25

C284

V36

Y36

T40

P40

Y27

Y25

P38

V30

AC30

AF35

AD35

AD38

AC36

M41

U35

V35

H44

P41

AA29

C23

B22

C5

B6

D4

E3

+V1P8A_R_SOC

U16

H10

G10

A3

RSVD_VSS_A3

K20

M20

?

1U/10V_4

+V1P24A_R_SOC

C285

1U/10V_4

+V1P24A_SSIC_HSIC_SOC

+V1P24A_SSIC_HSIC_SOC

+VCCRTCSUS_3P3

+V1P05A_R_SOC

R159

10K_4

PLACE THESE CAPS

CLOSE TO P38, V30 & AC30

C270

1U/10V_4

+V1P24A_R_SOC

C303

1U/10V_4

+VCCUSB2_3P3

+VCCRTC_3P3

C110

1U/10V_4

C304

1U/10V_4

C296

1U/10V_4

+V1P24A_R_SOC

+V1P24A_R_SOC

C277

1U/10V_4

C105

1U/10V_4

2

C291

1U/10V_4

+V1P24A_R_SOC

C279

PLACE THESE CAPS

1U/10V_4

CLOSE TO V36 & Y36

R454 *0_6S

PLACE THESE CAPS

CLOSE TO AF35, AD35, AD38 & AC36

C274

1U/10V_4

R463 *0_6S

C299

C300

1U/10V_4

1U/10V_4

+V1P8A_R_SOC

C96

1U/10V_4

+V1P24A_R_SOC

C282

1U/10V_4

1

14

+V1P24A_R_SOC

PLACE THESE CAPS

CLOSE TO THEIR PINS

B B

+V3P3A_PRIME

R464 *0_6S

PLACE CAPS NEAR SOC

+VRTC

R167 *0_6S

A A

+V1P8A

R456 *0_6S

5

+VCCRTCSUS_3P3

+VCCRTC_3P3

+V1P8A_R_SOC

C305

0.1U/16V_4

C109

0.1U/16V_4

+V1P24A

PLACE THIS CAP

CLOSE TO U16

+V1P24A_R_SOC

R164 *0_6S

+V1P8A_R_SOC +V1P05A_R_SOC

C298

1U/10V_4

4

PLACE THIS CAP

CLOSE TO G10 & H10

C118

1U/10V_4

R465 *0_6S

SD3 IO SUPPLY

+V3P3A_PRIME

R462 *0_6S

LPC IO SUPPLY

+V1P8A +VCCCFIOAZA_1P80

R404 *0_6S

AUDIO IO SUPPLY

R161 *0_6S

3

+VCCPADCF3SI0_1P8_3P3+VSDIO

+VCCPADCF1SI0_1P8_3P3

+VCCUSB2_3P3+V3P3A_PRIME

PROJECT : NL6D

PROJECT : NL6D

PROJECT : NL6D

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Quanta Computer Inc.

BSW 9/10 (Power 2)

BSW 9/10 (Power 2)

BSW 9/10 (Power 2)

Tuesday, April 12, 2016 4114

Tuesday, April 12, 2016 4114

Tuesday, April 12, 2016 4114

1

1A

1A

1A

Page 15

5

4

3

2

1

SoC (CPU)

BRASWELL - GND

15

BSW_MCP_EDS

VSS5

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS103

VSS84

VSS102

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

VSS60

VSS59

VSS58

VSS56

VSS55

VSS54

VSS53

VSS6

VSS57

BSW_MCP_EDS

Power-VSS

?

11 OF 13

VSS61

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS4

VSS3

VSS2

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS1

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS29

VSS28

VSS27

VSS26

VSS25

VSS24

VSS23

VSS22

VSS21

VSS20

VSS19

VSS18

VSS17

VSS16

VSS15

VSS14

VSS13

VSS12

VSS11

VSS10

VSS9

VSS8

VSS7

U17L

AY9

AY28

AY26

AY24

AY22

AY20

AW35

AW27

AW19

AM13

AK29

AK22

AV40

AV35

AV30

AV27

AV24

AV19

AV14

AJ18

AU53

AU51

AU3

AU1

AT9

AT51

AT45

AT36

AT35

AT3

AT27

AT19

AT18

AP9

AP50

AP45

AP4

AN9

AN8

AN6

AN53

AN51

AN5

AN49

AN48

AN46

AN45

AN43

AN42

AN40

AN38

?

AN33

AF24

N53

N51

N32

N24

N22

M40

M35

M27

AW13

M19

M14

M45

M50

P32

P27

P22

P19

K45

L35

L27

L19

K50

T47

K36

K34

K32

K30

K24

K22

K16

K14

K12

E46

H35

H27

H19

V25

M9

L1

K4

J53

J38

J35

J30

J27

J22

J19

J18

H8

REV = 1

AN21

BG30

BG27

BG24

BG20

BG19

BG18

BG16

BG14

BF42

BF32

BF28

BF27

BF26

BF22

BF12

BE35

BE19

C20

BD53

BG7

BD35

BD27

BD19

BD1

BC44

BC40

BC38

BC28

BC26

BC16

BC14

BC10

BB35

BB27

BB19

BA35

BA30

BA27

BA24

BA19

B36

B28

AY7

AY51

AY47

AY34

AY32

AY30

AY3

AN30

AY45

U17K

REV = 1

D D

C C

B B

AN3

AN29

AN25

AN24

AN16

AN14

AN12

AN11

AN1

AM50

AM42

AM4

AM38

AM35

AH44

AM30

AM27

U25

P10

AM16

AD4

AK7

AK50

AK47

AK45

AK44

AK40

AK4

AK38

AK32

AK27

AK25

AM24

AK16

AJ53

AJ51

AJ25

AJ16

AH9

AH47

AH42

AH41

AH14

AH13

AH12

AH10

AG25

AF47

U17J

AJ3

AJ1

REV = 1

BSW_MCP_EDS

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS60

VSS84

VSS83

VSS100

VSS99

VSS81

VSS31

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS82

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

VSS61

VSS59

VSS58

VSS57

VSS56

VSS55

VSS54

VSS53

VSS52

BSW_MCP_EDS

Power-VSS

?

10 OF 13

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS30

VSS23

VSS29

VSS28

VSS27

VSS26

VSS25

VSS24

VSS22

VSS21

VSS20

VSS19

VSS18

VSS17

VSS16

VSS15

VSS14

VSS13

VSS12

VSS11

VSS10

VSS9

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

AF38

AF32

AF25

AF10

AE9

AE8

AE6

AE53

AE50

AE48

AE46

AE45

AE43

AE42

AE40

AE14

AE12

AE11

AE1

AD44

AD36

AC29

AD32

AD30

AD21

AC38

AC35

AC33

AC16

AB6

AB50

AB47

AB42

AB4

AB14

AB13

AB12

AB10

AA53

AA38

AA27

AA16

A47

A43

A39

A31

A23

A19

A15

A11

?

BSW_MCP_EDS

VSS2

VSS99

VSS98

VSS97

VSS96

VSS1

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS77

VSS87

VSS86

VSS85

VSS3

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS100

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS88

VSS64

VSS63

VSS62

VSS61

VSS60

VSS59

VSS58

VSS57

VSS40

VSS56

VSS55

VSS54

VSS89

VSS101

BSW_MCP_EDS

Power-VSS

?

12 OF 13

VSS102

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS65

VSS29

VSS28

VSS27

VSS26

VSS25

VSS24

VSS23

VSS4

VSS22

VSS21

VSS20

VSS19

VSS18

VSS17

VSS16

VSS15

VSS14

VSS13

VSS12

VSS11

VSS10

VSS9

VSS8

VSS7

VSS6

VSS5

Y24

G30

G28

G26

G22

G14

G12

F5

F35

F32

F27

F24

F19

E51

E35

E19

D42

D40

D38

D32

D27

D24

D16

D10

J42

C47

C39

C36

C30

C3

C28

C22

AW41

BJ7

BJ47

BJ43

BJ39

BJ35

BJ31

BJ27

BJ23

BJ19

BJ15

BJ11

BG5

BG49

BG40

BG38

BG36

BG35

BG34

?

BH53

BH52

BH2

BH1

BG53

BG1

M24

BF50

BB50

BG47

B52

BF4

BB4

Y50

Y45

Y40

Y38

Y29

Y22

Y21

Y19

Y16

Y14

Y10

L41

P36

U17M

F1

C1

B2

A6

A5

A7

Y9

Y4

P4

REV = 1

BSW_MCP_EDS

Power-VSS

VSS_NCTF18

VSS_NCTF17

VSS_NCTF16

VSS15

VSS_NCTF14

VSS_NCTF13

VSS_NCTF12

VSS_NCTF10