Page 1

5

www.schematic-x.blogspot.com

4

3

2

1

NL6

01

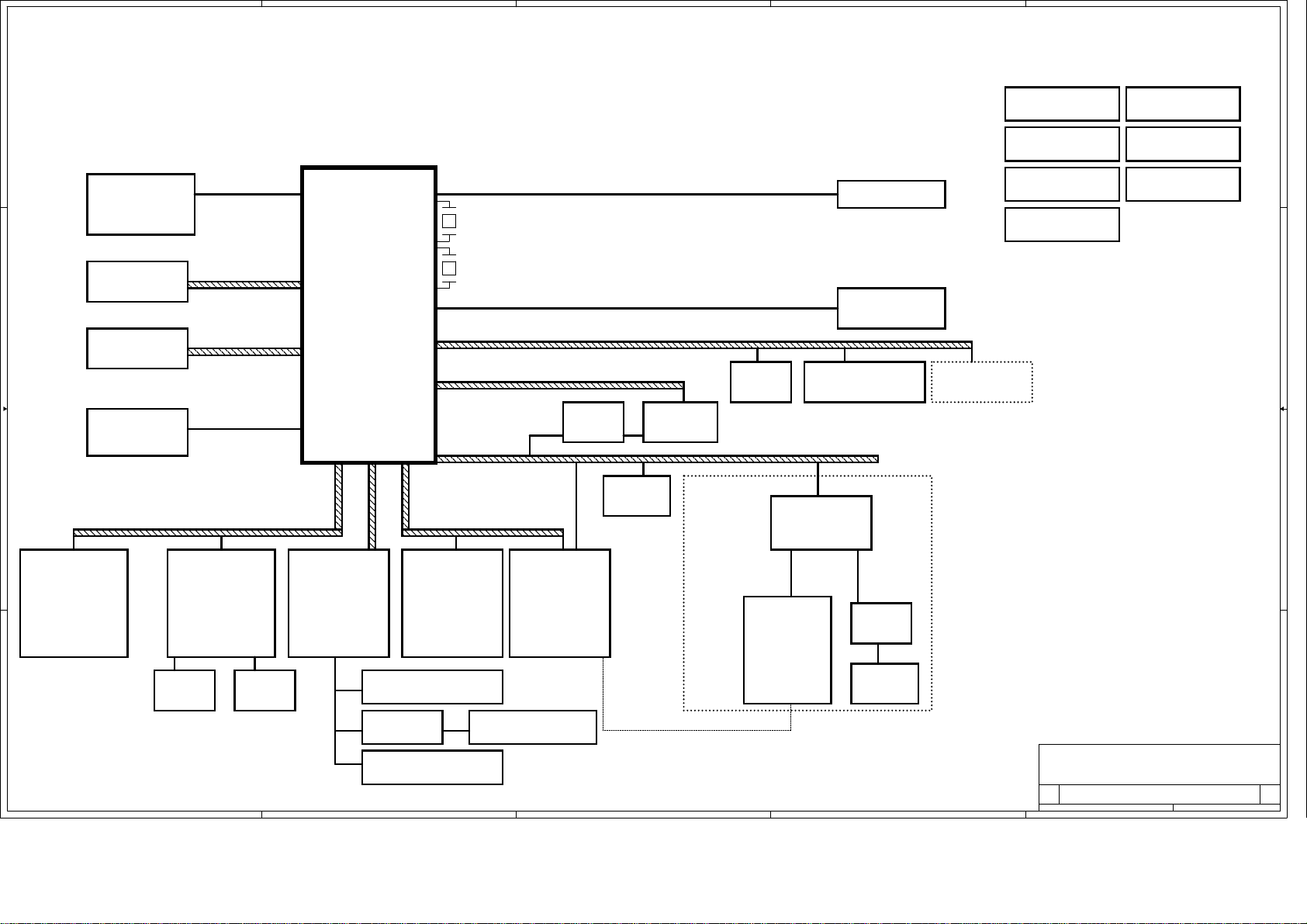

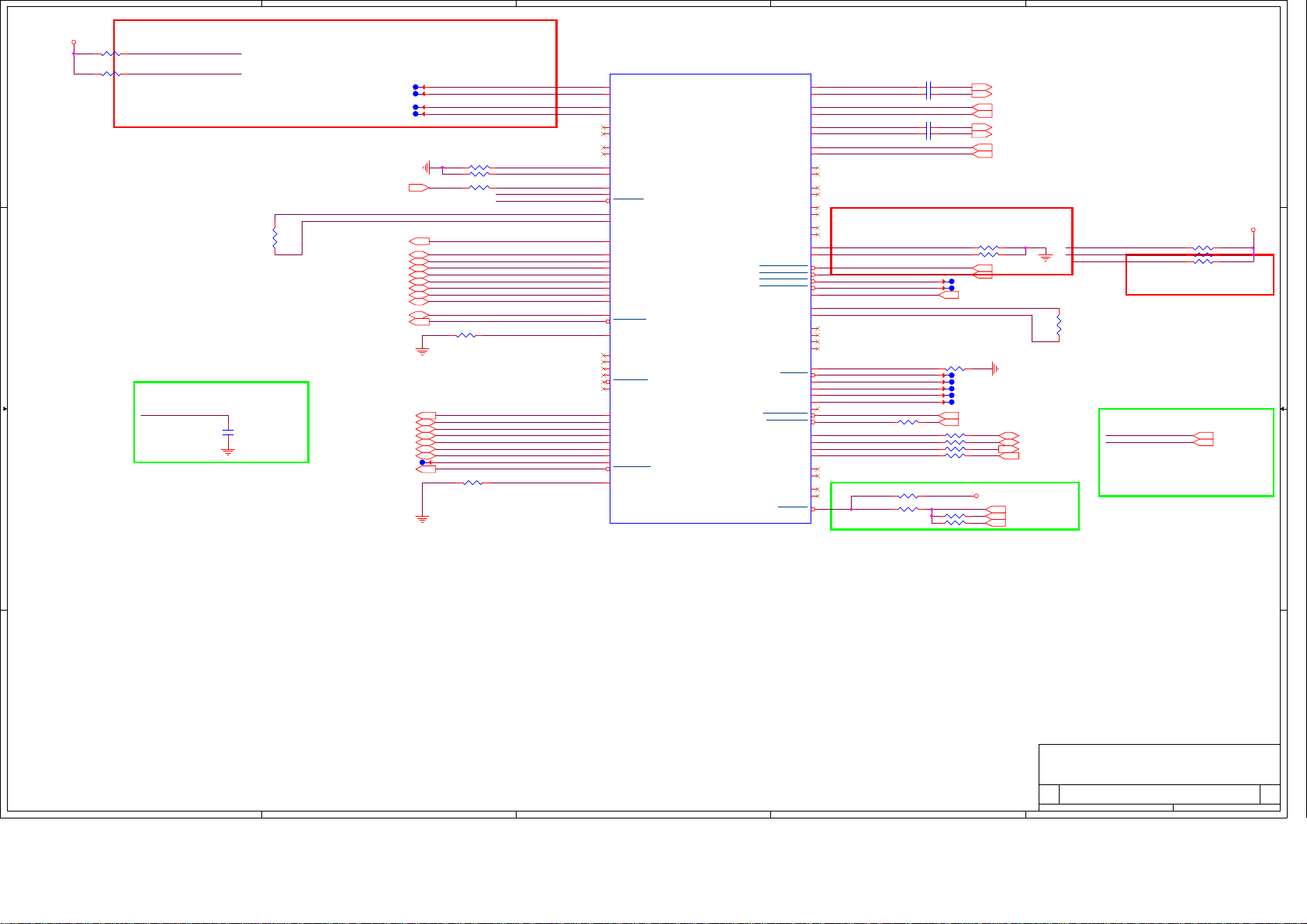

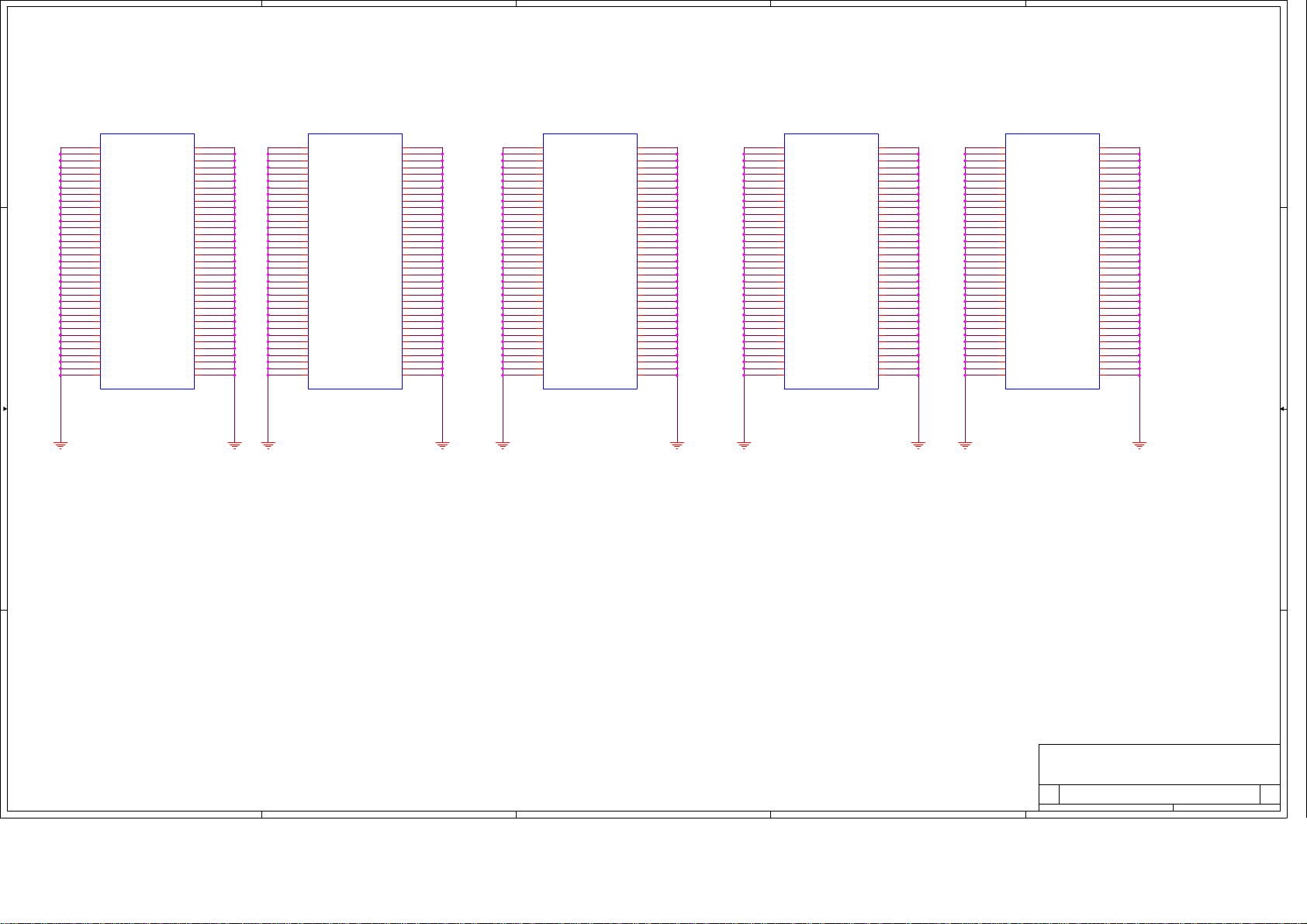

Intel Bay Trail-M Platform Block Diagram

D D

DDR3L 1333

Memory down

DDR3L

2 Channel 1Rx16

PAGE 11,12

eMMC

SDIN8DE2-16G

MMC

PAGE 21

C C

SD card

SDIO

PAGE 16

1.8V BIOS+TXE

SPI ROM(64Mb)

W25Q64FWSSIG

SPI Interface

PAGE 6

B B

TPM

SLB9655TT1.2

FW4.32GOOG

TI KBC

TM4E1G31H6ZRB

Package : BGA-157

Size : 9.1 x 9.1 (mm)

PAGE 22

Thermal IC

PAGE 27

Keyboard

TMP432A

A A

PAGE 26

5

PAGE 26

SKUA QC N2930

Up to 1.83 GHz SR1SG(FCBGA) P/N: AJ0QG9UUT01

SKUB DC N2830

Up to 2.17 GHz SR1SG(FCBGA) P/N: AJ0QG9VUT01

DDI 1

32.768KHz

Intel Bay Trail-M

Power : TDP 7.5 Watt

Package : FCBGA 1170

Size : 25 x 27 (mm)

Int

Audio Codec

MAX98090

Package : TQFN-40

Size : 5 x 5 (mm)

PAGE 24

Speaker

MIC SW

TS3A225E

DMIC

PAGE 2~10

I2S+I2C(PORT1)

PCIE Gen 2 x 1 LaneLPC Interface

M.2 LGA 1216-S3

PAGE 24

CCD Integrated

4

PAGE 6

25 Mhz

PAGE 6

DDI 0

I2C Interface

USB 3.0 Interface

USB 2.0 Interface

Port1 Port0

Video Codec

PAGE 20

PAGE 24

Combo Jack

Headphone + MIC

PAGE 24

X4 LANES

USB Charger

Port0

TPS2546

PAGE 25

Port3

NGFF M.2 2230-E

WLAN / BT Combo

PCIE CLK PORT 0PCIE CLK PORT 1

PAGE 20

PAGE 24

Port0

USB3.0 Port x 1

Port2

CCD

PAGE 17

LTE UART COEXISTENCE

3

PAGE 25

Daughter Board

PAGE 16

eDP

PAGE 17

HDMI Conn PAGE 19

Track Pad

PAGE 26 PAGE ?

ALS

ILS29035

CCD Integrated

Port1

USB Hub

PAGE 17

GL852G-OHG12

USB Hub -2

NGFF M.2 3042-B

USB Hub -1

USB Charger

TPS2546

LTE

USB2.0 Port x 1

2

Port5Port4Port0

Touch Screen

MXT1664S

In touch panel PCBA

BQ24715

Batery Charger

NB670/NB671

PP3300_DSW/PP5000

ISL95833HRTZ-T

+VCC_CORE/+VCC_GFX

Discharger

BOM value option:

CHB@-==>DDR Single channel or dual channel

EDP@ =>4 Lane eDP

TS@ =>Touch screen

SX@ => S0IX

NSX@=> Non S0ix

VC@ =>Video codec

LTE@ => LTE

GD@ =>Google debug

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

TPS51216

PP1350

TLV62150ARGTR

PP1050_PCH

TLV62130ARGTR

PP1000_PCH_S5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Intel Block Diagram

Intel Block Diagram

Intel Block Diagram

NL6

NL6

NL6

1

1A

1A

1A

411

411

411

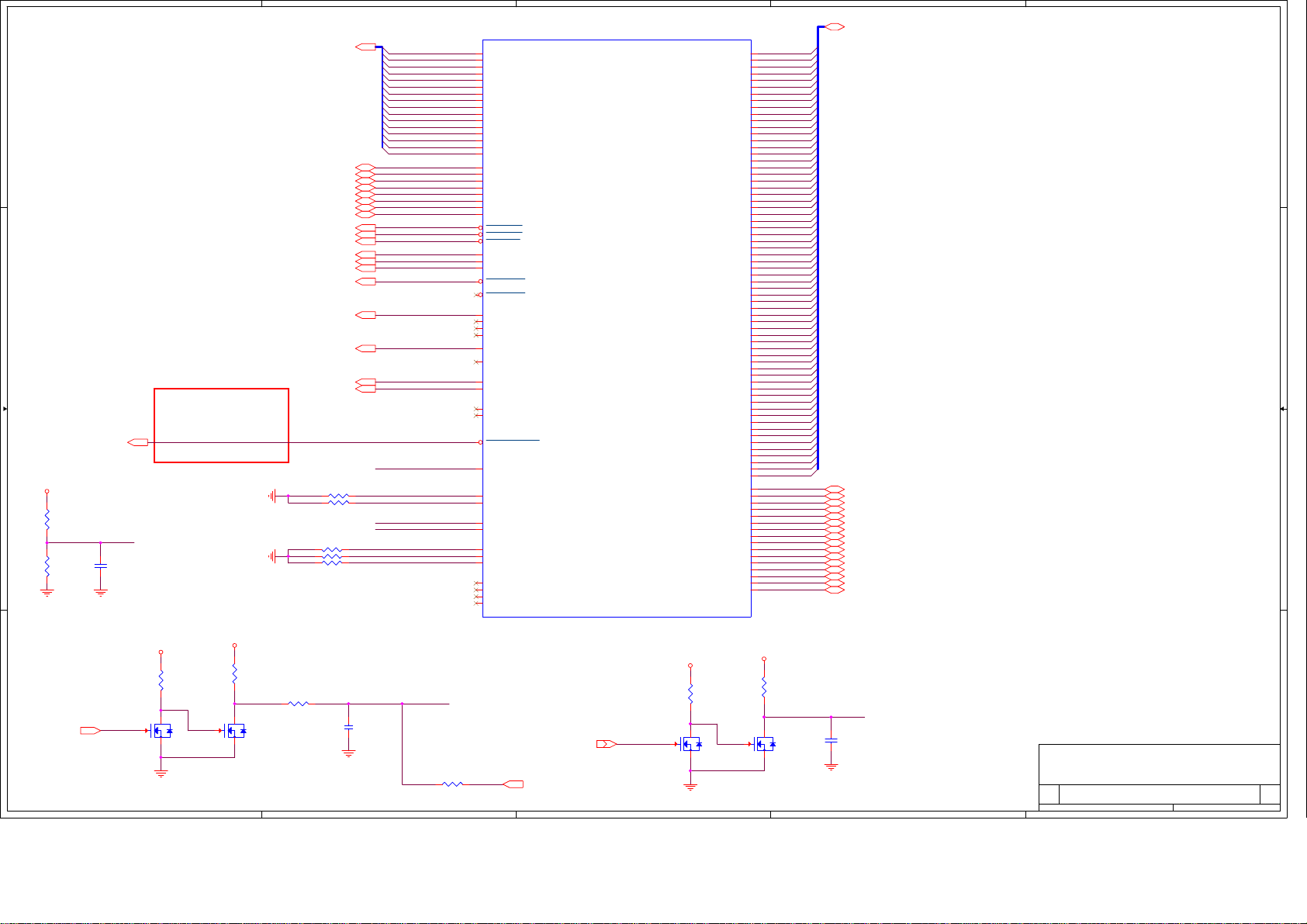

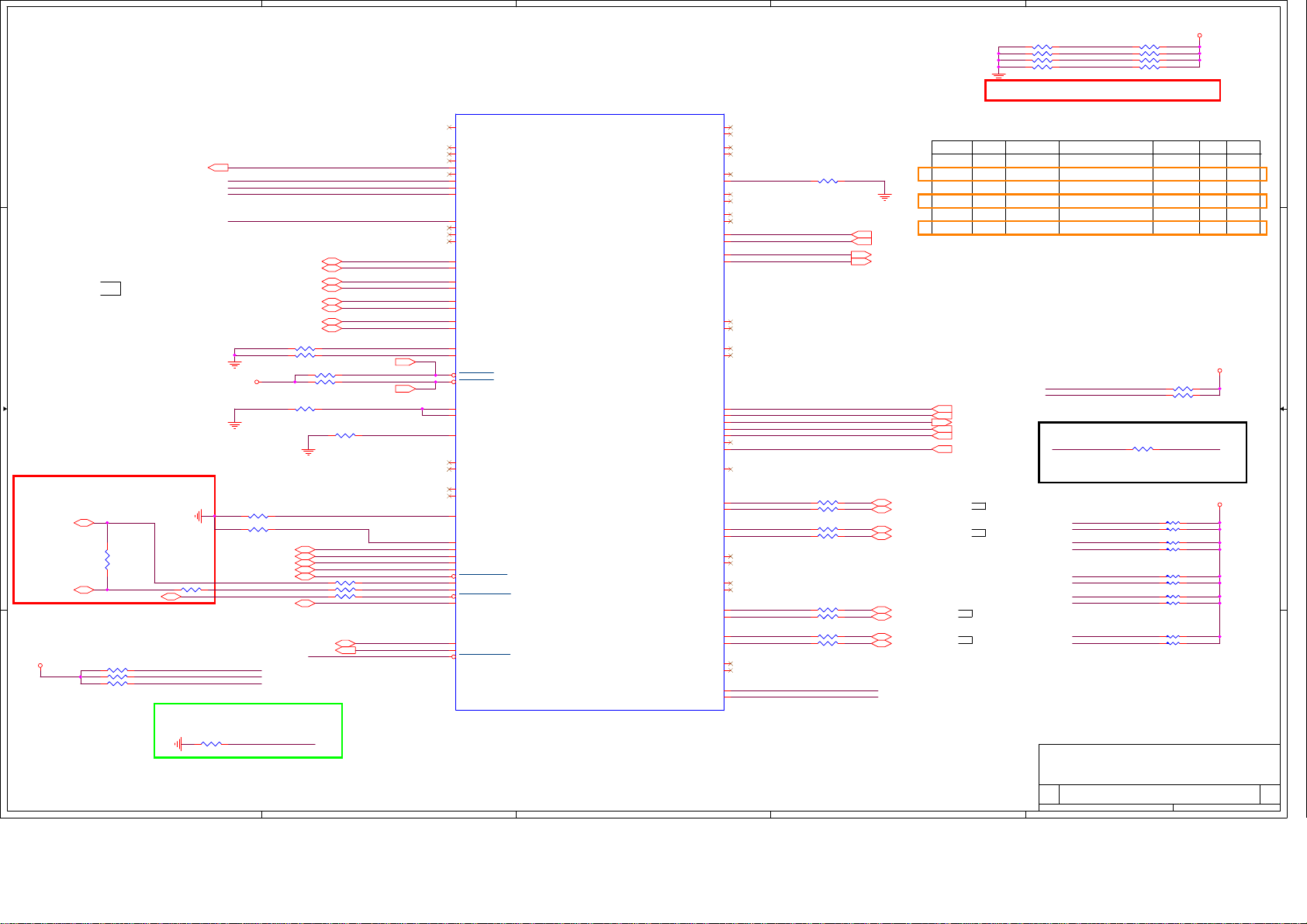

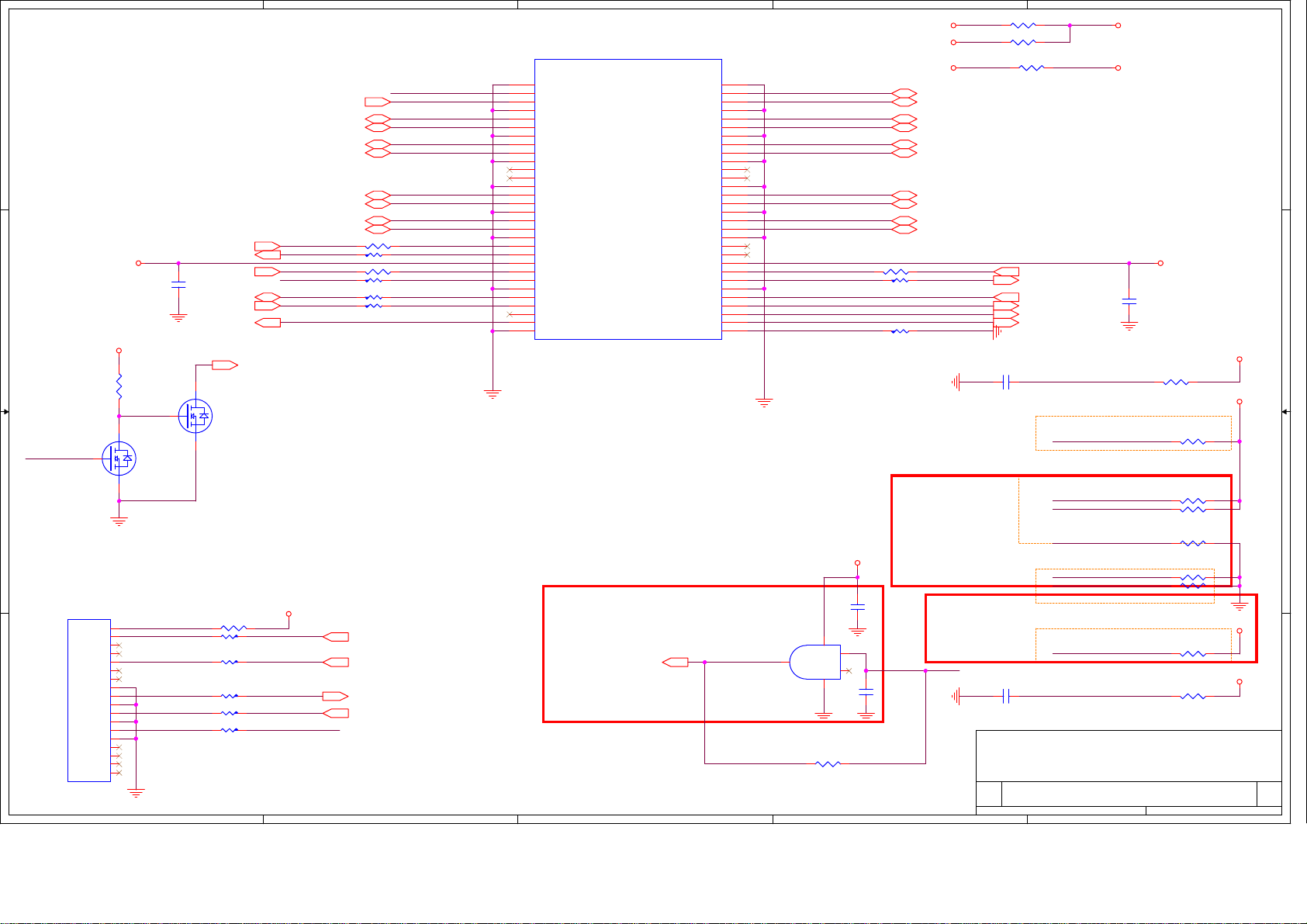

Page 2

5

M_A_A[15:0](12)

D D

M_A_DM0(12)

M_A_DM1(12)

M_A_DM2(12)

M_A_DM3(12)

M_A_DM4(12)

M_A_DM5(12)

M_A_DM6(12)

M_A_DM7(12)

M_A_RAS#(12)

M_A_CAS#(12)

M_A_WE#(12)

M_A_BS0(12)

M_A_BS1(12)

M_A_BS2(12)

M_A_CS#0(12)

C C

1023 unstuff R28 by

Intel request

1121 remove R28,R25,C35

M_A_DRAMRST#(12)

PP1350

B B

A A

R344

4.7K/F_4

CPU_VREF

R348

4.7K/F_4

GND GND

SLP_S4#(6,11,14)

C242

0.1U/10V_4

SLP_S4#

PP3300_PCH_S5

R151

4.7K_4

DRM_PWOK_C1

34

5

Q40A

PJ4N3KDW

GND

5

R195

10K_4

2

PP1350

GND

GND

DRAM_PWROK

61

Q40B

PJ4N3KDW

M_A_CKE0(12)

M_A_ODT0(12)

M_A_CLKP0(12)

M_A_CLKN0(12)

R23 23.2/F_4

R19 29.4/F_4

R18 162/F_4

R178 0_4

R15 100K/F_4

R16 100K/F_4

GND

4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_RAS#

M_A_CAS#

M_A_WE#

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CS#0

M_A_CKE0

M_A_ODT0

M_A_CLKP0

M_A_CLKN0

M_A_DRAMRST#

CPU_VREF

ICLK_DRAM_TERMN_0

ICLK_DRAM_TERMN_1

SOC_DRAM_PWROK

SOC_VCCA_PWROK

DRAM_RCOMP0

DRAM_RCOMP1

DRAM_RCOMP2

SOC_DRAM_PWROK

C102

*1u/10V_4

4

R191 0_4

U14A

K45

DRAM0_MA_00

H47

DRAM0_MA_11

L41

DRAM0_MA_22

H44

DRAM0_MA_33

H50

DRAM0_MA_44

G53

DRAM0_MA_55

H49

DRAM0_MA_66

D50

DRAM0_MA_77

G52

DRAM0_MA_88

E52

DRAM0_MA_99

K48

DRAM0_MA_1010

E51

DRAM0_MA_1111

F47

DRAM0_MA_1212

J51

DRAM0_MA_1313

B49

DRAM0_MA_1414

B50

DRAM0_MA_1515

G36

DRAM0_DM_00

B36

DRAM0_DM_11

F38

DRAM0_DM_22

B42

DRAM0_DM_33

P51

DRAM0_DM_44

V42

DRAM0_DM_55

Y50

DRAM0_DM_66

Y52

DRAM0_DM_77

M45

DRAM0_RAS

M44

DRAM0_CAS

H51

DRAM0_WE

K47

DRAM0_BS_00

K44

DRAM0_BS_11

D52

DRAM0_BS_22

P44

DRAM0_CS_0

P45

DRAM0_CS_2

C47

DRAM0_CKE_00

D48

RESERVED_D48

F44

DRAM0_CKE_22

E46

RESERVED_E46

T41

DRAM0_ODT_0

P42

DRAM0_ODT_2

M50

DRAM0_CKP_0

M48

DRAM0_CKN_0

P50

DRAM0_CKP_2

P48

DRAM0_CKN_2

P41

DRAM0_DRAMRST

AF44

DRAM_VREF

AH42

ICLK_DRAM_TERMN

AF42

ICLK_DRAM_TERMN_AF42

AD42

DRAM_VDD_S4_PWROK

AB42

DRAM_CORE_PWROK

AD44

DRAM_RCOMP_00

AF45

DRAM_RCOMP_11

AD45

DRAM_RCOMP_22

AF40

RESERVED_AF40

AF41

RESERVED_AF41

AD40

RESERVED_AD40

AD41

RESERVED_AD41

VLV_M_D/BGA

REV = 1.15

+1.35V_SUS

+1.35V_SUS

ph

EC_PWROK(27)

PP1350_PGOOD (31)

?

VLV_M_D

1 OF 13

EC_PWROK

3

3

DRAM0_DQ09_C32

DRAM0_DQ_1010

DRAM0_DQ_1111

DRAM0_DQ_1212

DRAM0_DQ_1313

DRAM0_DQ_1414

DRAM0_DQ_1515

DRAM0_DQ_1616

DRAM0_DQ_1717

DRAM0_DQ_1818

DRAM0_DQ_1919

DRAM0_DQ_2020

DRAM0_DQ_2121

DRAM0_DQ_2222

DRAM0_DQ_2323

DRAM0_DQ_2424

DRAM0_DQ_2525

DRAM0_DQ_2626

DRAM0_DQ_2727

DRAM0_DQ_2828

DRAM0_DQ_2929

DRAM0_DQ_3030

DRAM0_DQ_3131

DRAM0_DQ_3232

DRAM0_DQ_3333

DRAM0_DQ_3434

DRAM0_DQ_3535

DRAM0_DQ_3636

DRAM0_DQ_3737

DRAM0_DQ_3838

DRAM0_DQ_3939

DRAM0_DQ_4040

DRAM0_DQ_4141

DRAM0_DQ_4242

DRAM0_DQ_4343

DRAM0_DQ_4444

DRAM0_DQ_4545

DRAM0_DQ_4646

DRAM0_DQ_4747

DRAM0_DQ_4848

DRAM0_DQ_4949

DRAM0_DQ_5050

DRAM0_DQ_5151

DRAM0_DQ_5252

DRAM0_DQ_5353

DRAM0_DQ_5454

DRAM0_DQ_5555

DRAM0_DQ_5656

DRAM0_DQ_5757

DRAM0_DQ_5858

DRAM0_DQ_5959

DRAM0_DQ_6060

DRAM0_DQ_6161

DRAM0_DQ_6262

DRAM0_DQ_6363

DRAM0_DQSP_00

DRAM0_DQSN_00

DRAM0_DQSP_11

DRAM0_DQSN_11

DRAM0_DQSP_22

DRAM0_DQSN_22

DRAM0_DQSP_33

DRAM0_DQSN_33

DRAM0_DQSP_44

DRAM0_DQSN_44

DRAM0_DQSP_55

DRAM0_DQSN_55

DRAM0_DQSP_66

DRAM0_DQSN_66

DRAM0_DQSP_77

DRAM0_DQSN_77

PP3300_PCH_S5

4.7K_4

DRM_PWOK_C2

34

5

Q28A

PJ4N3KDW

GND

DRAM0_DQ_00

DRAM0_DQ_11

DRAM0_DQ_22

DRAM0_DQ_33

DRAM0_DQ_44

DRAM0_DQ_55

DRAM0_DQ_66

DRAM0_DQ_77

DRAM0_DQ_88

R205

10K_4R147

?

PP1350

2

M36

J36

P40

M40

P36

N36

K40

K42

B32

C32

C36

A37

C33

A33

C37

B38

F36

G38

F42

J42

G40

C38

G44

D42

A41

C41

A45

B46

C40

B40

B48

B47

K52

K51

T52

T51

L51

L53

R51

R53

T47

T45

Y40

V41

T48

T50

Y42

AB40

V45

V47

AD48

AD50

V48

V50

AB44

Y45

V52

W51

AC53

AC51

W53

Y51

AD52

AD51

J38

K38

C35

B34

D40

F40

B44

C43

N53

M52

T42

T44

Y47

Y48

AB52

AA51

61

PJ4N3KDW

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQSP0

M_A_DQSN0

M_A_DQSP1

M_A_DQSN1

M_A_DQSP2

M_A_DQSN2

M_A_DQSP3

M_A_DQSN3

M_A_DQSP4

M_A_DQSN4

M_A_DQSP5

M_A_DQSN5

M_A_DQSP6

M_A_DQSN6

M_A_DQSP7

M_A_DQSN7

Q28B

M_A_DQ[63:0] (12)

M_A_DQSP0 (12)

M_A_DQSN0 (12)

M_A_DQSP1 (12)

M_A_DQSN1 (12)

M_A_DQSP2 (12)

M_A_DQSN2 (12)

M_A_DQSP3 (12)

M_A_DQSN3 (12)

M_A_DQSP4 (12)

M_A_DQSN4 (12)

M_A_DQSP5 (12)

M_A_DQSN5 (12)

M_A_DQSP6 (12)

M_A_DQSN6 (12)

M_A_DQSP7 (12)

M_A_DQSN7 (12)

SOC_VCCA_PWROK

C90

*0.1U/10V_4

GND

1128 place C90 to close SoC ball

2

1

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

2

Friday, April 25, 2014

PROJECT :

Valley 1/9 (DDRA)

Valley 1/9 (DDRA)

Valley 1/9 (DDRA)

NL6

NL6

NL6

1A

1A

1A

412

412

1

412

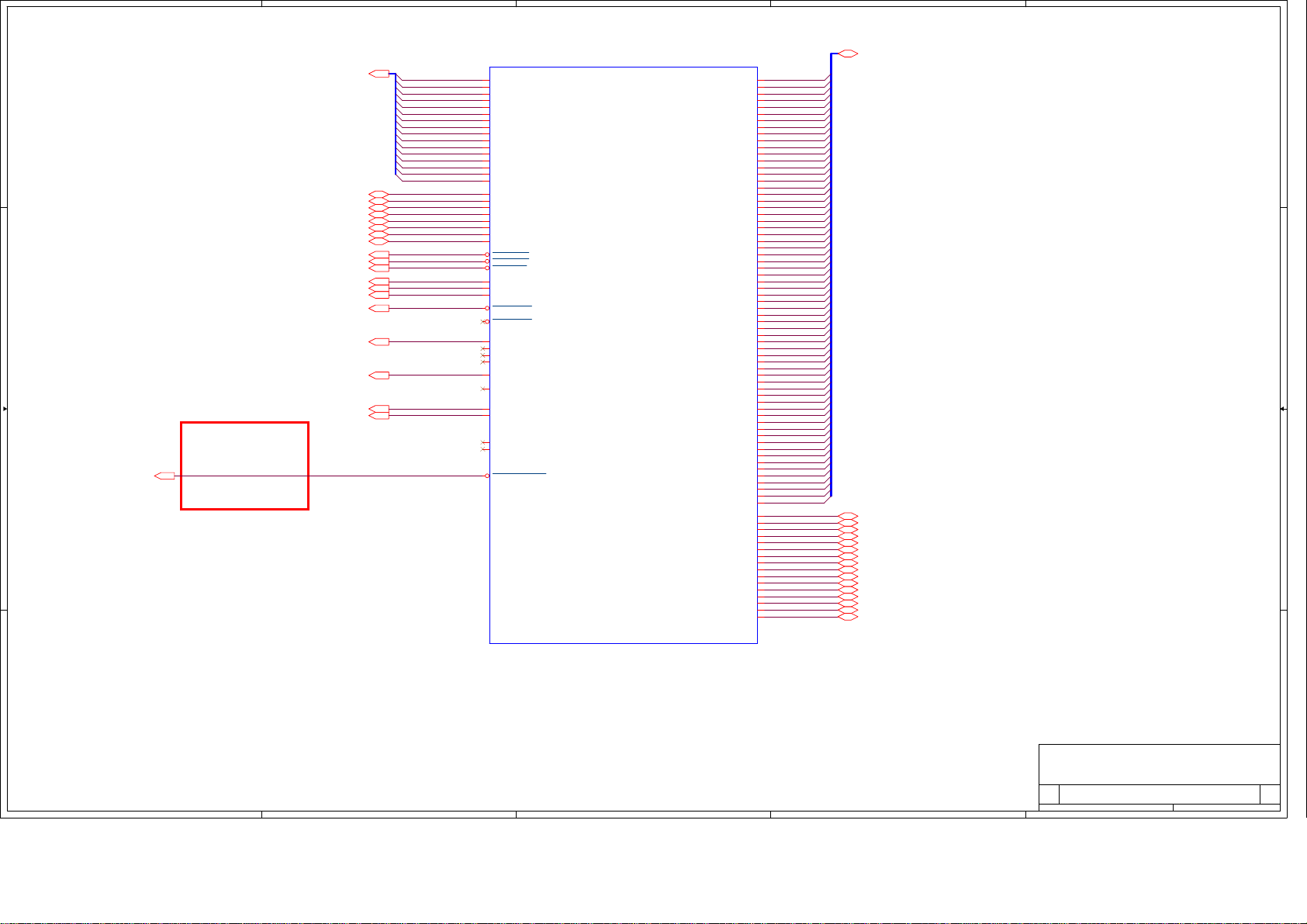

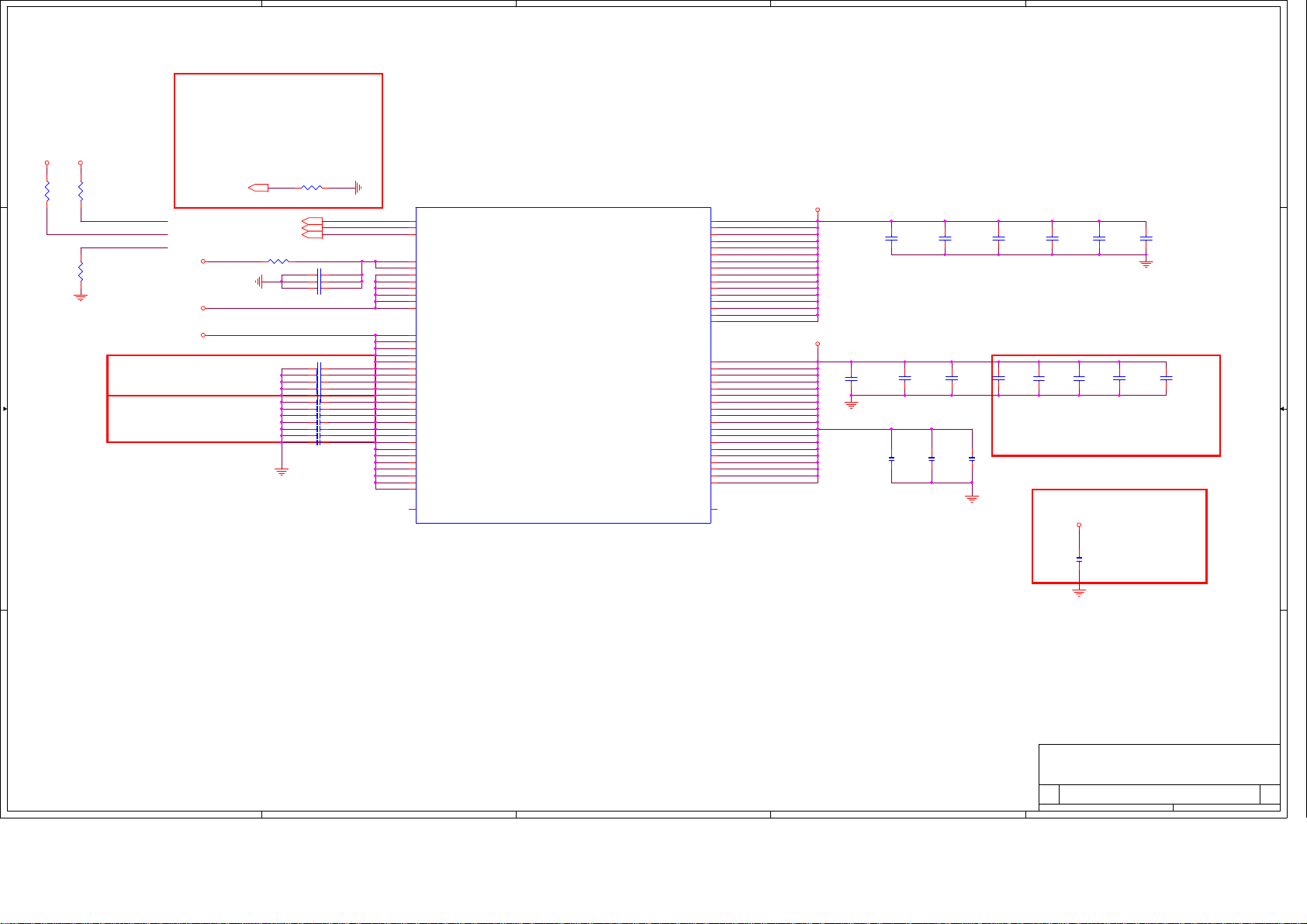

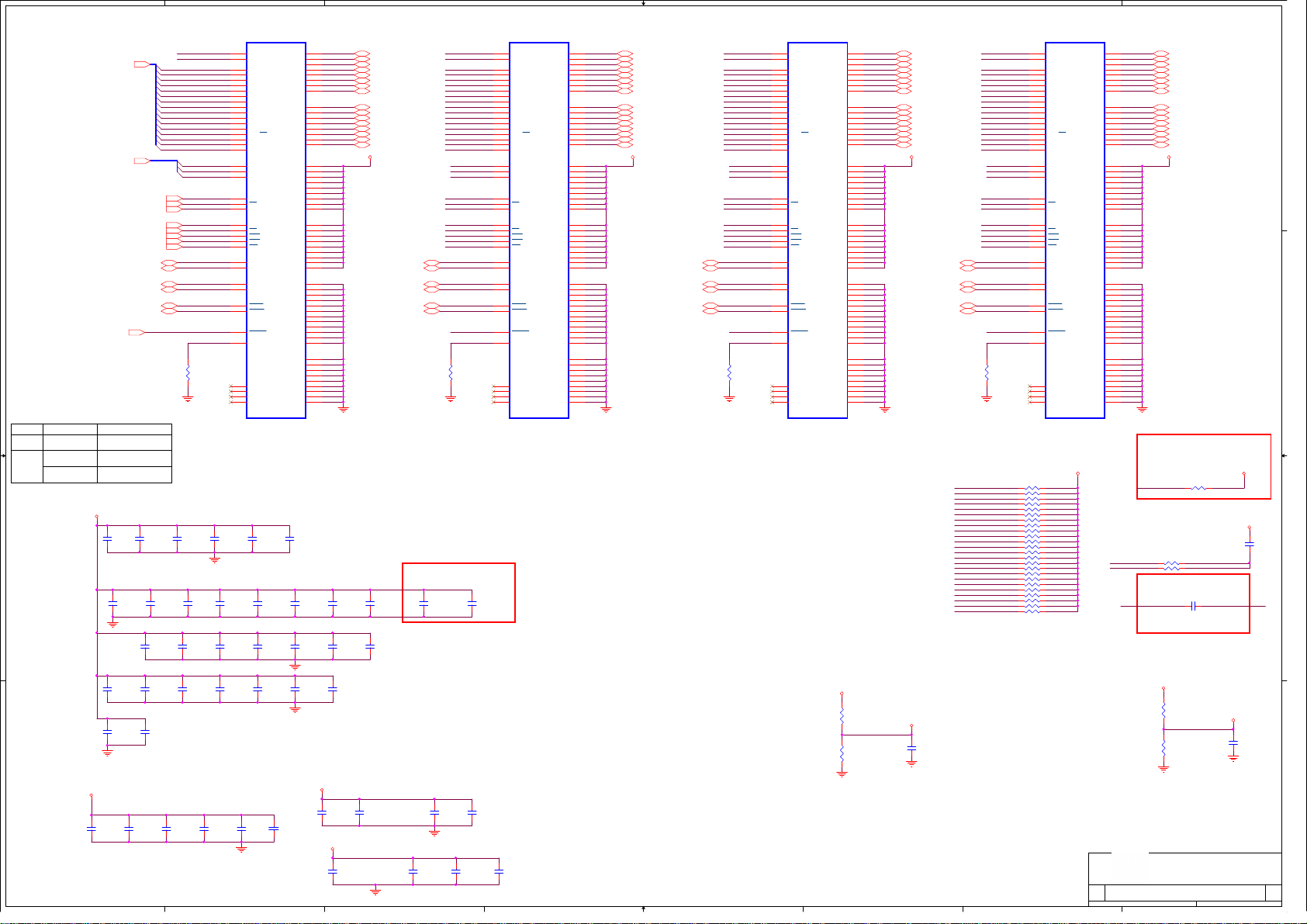

Page 3

5

4

3

2

1

?

VLV_M_D

2 OF 13

DRAM1_DQ_00

DRAM1_DQ_11

DRAM1_DQ_22

DRAM1_DQ_33

DRAM1_DQ_44

DRAM1_DQ_55

DRAM1_DQ_66

DRAM1_DQ_77

DRAM1_DQ_88

DRAM1_DQ_99

DRAM1_DQ_1010

DRAM1_DQ_1111

DRAM1_DQ_1212

DRAM1_DQ_1313

DRAM1_DQ_1414

DRAM1_DQ_1515

DRAM1_DQ_1616

DRAM1_DQ_1717

DRAM1_DQ_1818

DRAM1_DQ_1919

DRAM1_DQ_2020

DRAM1_DQ_2121

DRAM1_DQ_2222

DRAM1_DQ_2323

DRAM1_DQ_2424

DRAM1_DQ_2525

DRAM1_DQ_2626

DRAM1_DQ_2727

DRAM1_DQ_2828

DRAM1_DQ_2929

DRAM1_DQ_3030

DRAM1_DQ_3131

DRAM1_DQ_3232

DRAM1_DQ_3333

DRAM1_DQ_3434

DRAM1_DQ_3535

DRAM1_DQ_3636

DRAM1_DQ_3737

DRAM1_DQ_3838

DRAM1_DQ_3939

DRAM1_DQ_4040

DRAM1_DQ_4141

DRAM1_DQ_4242

DRAM1_DQ_4343

DRAM1_DQ_4444

DRAM1_DQ_4545

DRAM1_DQ_4646

DRAM1_DQ_4747

DRAM1_DQ_4848

DRAM1_DQ_4949

DRAM1_DQ_5050

DRAM1_DQ_5151

DRAM1_DQ_5252

DRAM1_DQ_5353

DRAM1_DQ_5454

DRAM1_DQ_5555

DRAM1_DQ_5656

DRAM1_DQ_5757

DRAM1_DQ_5858

DRAM1_DQ_5959

DRAM1_DQ_6060

DRAM1_DQ_6161

DRAM1_DQ_6262

DRAM1_DQ_6363

DRAM1_DQSP_00

DRAM1_DQSN_00

DRAM1_DQSP_11

DRAM1_DQSN_11

DRAM1_DQSP_22

DRAM1_DQSN_22

DRAM1_DQSP_33

DRAM1_DQSN_33

DRAM1_DQSP_44

DRAM1_DQSN_44

DRAM1_DQSP_55

DRAM1_DQSN_55

DRAM1_DQSP_66

DRAM1_DQSN_66

DRAM1_DQSP_77

DRAM1_DQSN_77

?REV = 1.15

BG38

BC40

BA42

BD42

BC38

BD36

BF42

BC44

BH32

BG32

BG36

BJ37

BG33

BJ33

BG37

BH38

AU36

AT36

AV40

AT40

BA36

AV36

AY42

AY40

BJ41

BG41

BJ45

BH46

BG40

BH40

BH48

BH47

AY52

AY51

AP52

AP51

AW51

AW53

AR51

AR53

AP47

AP45

AK40

AM41

AP48

AP50

AK42

AH40

AM45

AM47

AF48

AF50

AM48

AM50

AH44

AK45

AM52

AL51

AG53

AG51

AL53

AK51

AF52

AF51

BF40

BD40

BG35

BH34

BA38

AY38

BH44

BG43

AU53

AV52

AP42

AP44

AK47

AK48

AH52

AJ51

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQSP0

M_B_DQSN0

M_B_DQSP1

M_B_DQSN1

M_B_DQSP2

M_B_DQSN2

M_B_DQSP3

M_B_DQSN3

M_B_DQSP4

M_B_DQSN4

M_B_DQSP5

M_B_DQSN5

M_B_DQSP6

M_B_DQSN6

M_B_DQSP7

M_B_DQSN7

M_B_A[15:0](13)

D D

M_B_DM0(13)

M_B_DM1(13)

M_B_DM2(13)

M_B_DM3(13)

M_B_DM4(13)

M_B_DM5(13)

M_B_DM6(13)

M_B_DM7(13)

M_B_RAS#(13)

M_B_CAS#(13)

M_B_WE#(13)

M_B_BS0(13)

M_B_BS1(13)

M_B_BS2(13)

C C

1023 unstuff R29 by

Intel request

M_B_CS#0(13)

M_B_CKE0(13)

M_B_ODT0(13)

M_B_CLKP0(13)

M_B_CLKN0(13)

1121 remove R29,R26,C36

M_B_DRAMRST#(13)

B B

M_B_A0 M_B_DQ0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_RAS#

M_B_CAS#

M_B_WE#

M_B_BS0

M_B_BS1

M_B_BS2

M_B_CS#0

M_B_CKE0

M_B_ODT0

M_B_CLKP0

M_B_CLKN0

M_B_DRAMRST#

AY45

BB47

AW41

BB44

BB50

BC53

BB49

BF50

BC52

BE52

AY48

BE51

BD47

BA51

BH49

BH50

BD38

BH36

BC36

BH42

AT51

AM42

AK50

AK52

AV45

AV44

BB51

AY47

AY44

BF52

AT44

AT45

BG47

BE46

BD44

BF48

AP41

AT42

AV50

AV48

AT50

AT48

AT41

U14B

DRAM1_MA_00

DRAM1_MA_11

DRAM1_MA_22

DRAM1_MA_33

DRAM1_MA_44

DRAM1_MA_55

DRAM1_MA_66

DRAM1_MA_77

DRAM1_MA_88

DRAM1_MA_99

DRAM1_MA_1010

DRAM1_MA_1111

DRAM1_MA_1212

DRAM1_MA_1313

DRAM1_MA_1414

DRAM1_MA_1515

DRAM1_DM_00

DRAM1_DM_11

DRAM1_DM_22

DRAM1_DM_33

DRAM1_DM_44

DRAM1_DM_55

DRAM1_DM_66

DRAM1_DM_77

DRAM1_RAS

DRAM1_CAS

DRAM1_WE

DRAM1_BS_00

DRAM1_BS_11

DRAM1_BS_22

DRAM1_CS_0

DRAM1_CS_2

DRAM1_CKE_00

RESERVED_BE46

DRAM1_CKE_22

RESERVED_BF48

DRAM1_ODT_0

DRAM1_ODT_2

DRAM1_CKP_0

DRAM1_CKN_0

DRAM1_CKP_2

DRAM1_CKN_2

DRAM1_DRAMRST

VLV_M_D/BGA

M_B_DQ[63:0] (13)

M_B_DQSP0 (13)

M_B_DQSN0 (13)

M_B_DQSP1 (13)

M_B_DQSN1 (13)

M_B_DQSP2 (13)

M_B_DQSN2 (13)

M_B_DQSP3 (13)

M_B_DQSN3 (13)

M_B_DQSP4 (13)

M_B_DQSN4 (13)

M_B_DQSP5 (13)

M_B_DQSN5 (13)

M_B_DQSP6 (13)

M_B_DQSN6 (13)

M_B_DQSP7 (13)

M_B_DQSN7 (13)

3

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

5

4

3

2

Friday, April 25, 2014

PROJECT :

Valley 2/9 (DDRB)

Valley 2/9 (DDRB)

Valley 2/9 (DDRB)

NL6

NL6

NL6

1A

1A

1A

413

413

1

413

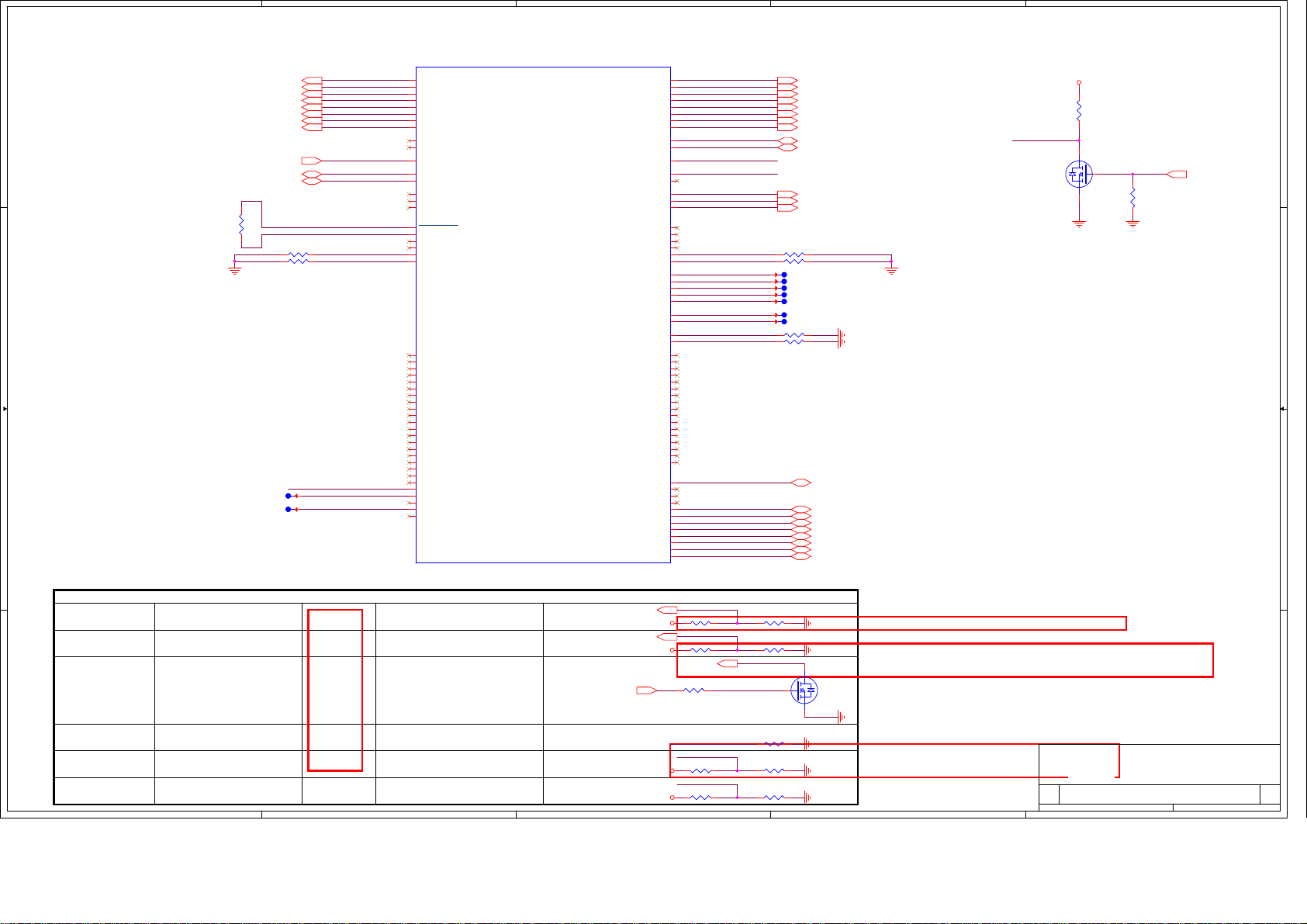

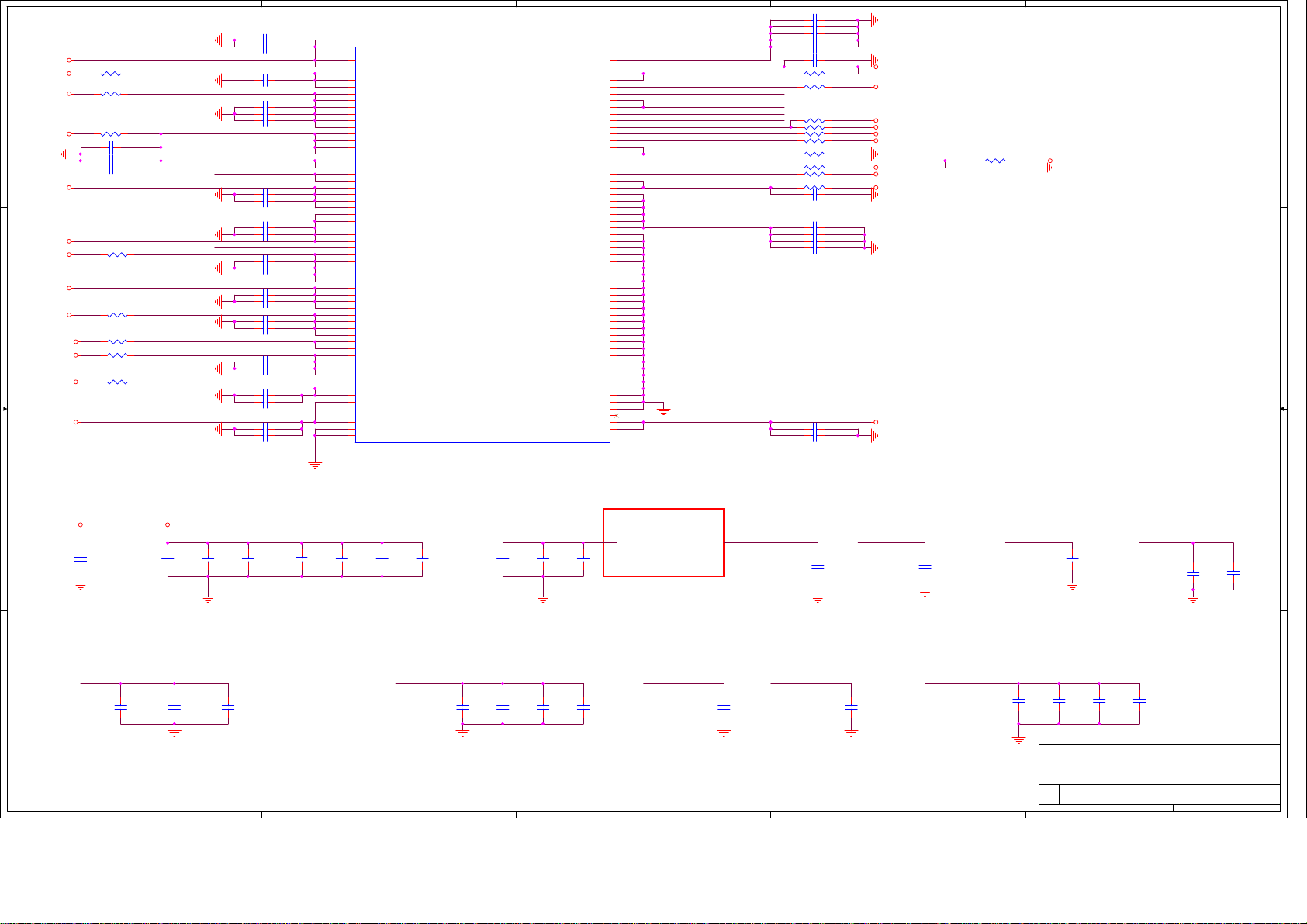

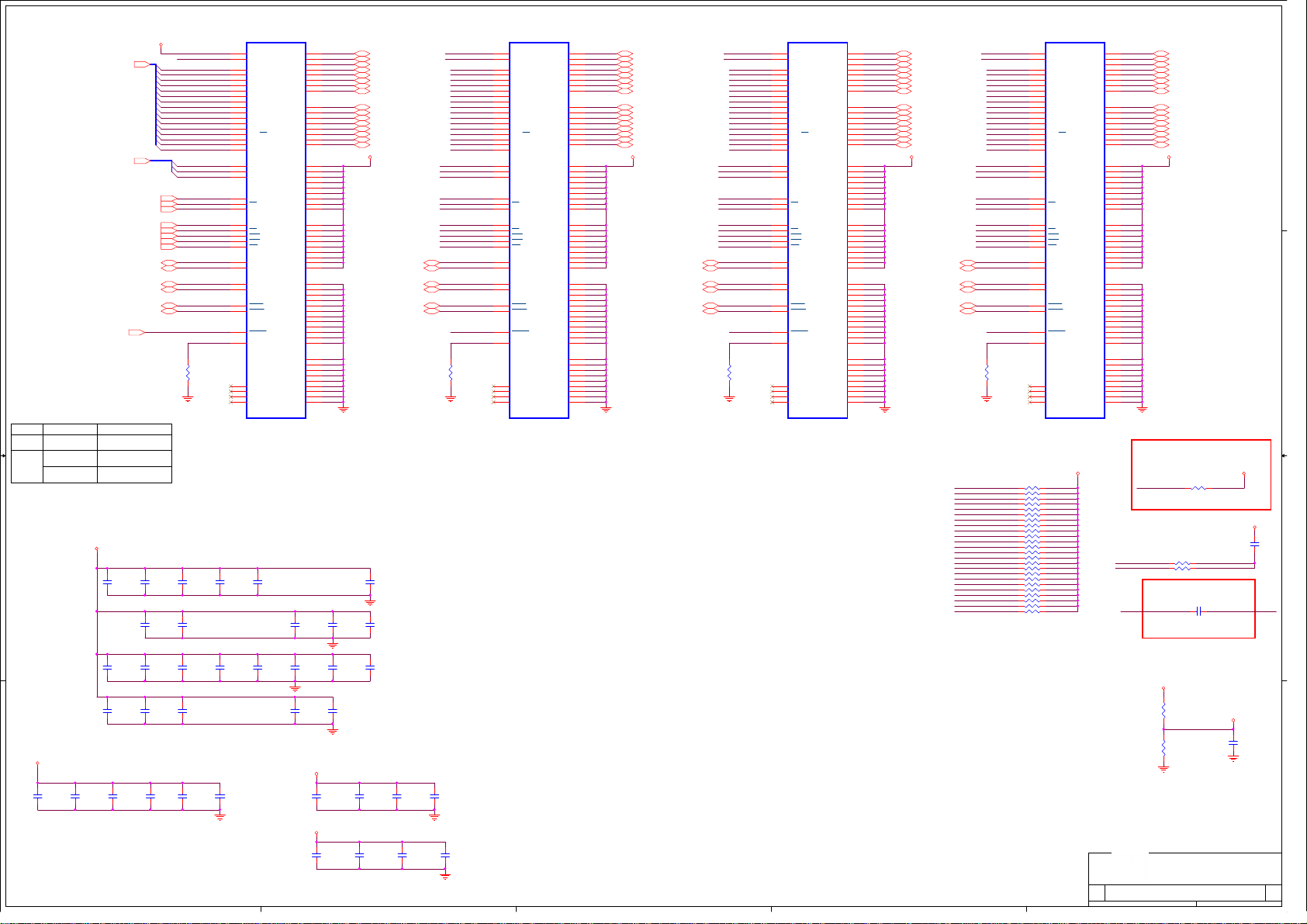

Page 4

5

4

3

2

1

U14C

INT_HDMITX2P(19) EDP_TXP0 (17)

INT_HDMITX2N(19)

INT_HDMITX1P(19)

INT_HDMITX1N(19)

D D

C C

B B

INT_HDMITX0P(19)

INT_HDMITX0N(19)

INT_HDMICLK+(19)

INT_HDMICLK-(19)

INT_HDMI_HPD(19)

HDMI_DDCDATA_SW(19)

HDMI_DDCCLK_SW(19)

R442

402/F_4

R184 *0_4_S

R183 *0_4_S

GND GND

TP5

TP4

INT_HDMITX2P

INT_HDMITX2N

INT_HDMITX1P

INT_HDMITX1N

INT_HDMITX0P

INT_HDMITX0N

INT_HDMICLK+

INT_HDMICLK-

INT_HDMI_HPD

HDMI_DDCDATA_SW

HDMI_DDCCLK_SW

SOC_DDIO_RCOMP

SOC_DDIO_RCOMP_P

SOC_PIN_AM3

SOC_PIN_AM2

GPIO_NC13

GPIO_NC14

INTD_DSI_TE

BTM Strapping Table

Pin Name Strap description

GPIO_SO_SC_56

LPE_I2S2_FRM

GPIO_SO_SC_65

A A

DDI0_DDCDATA

DDI1_DDCDATA

Top Swap (A16 Override)

BIOS Boot Selection

ecurity Flash Descriptors

S

DDI0 Detect

DDI1 Detect

Sampled

PWROK

PWROK

PWROK

PWROK

PWROK

AV3

AV2

AT2

AT3

AR3

AR1

AP3

AP2

AL3

AL1

D27

C26

C28

B28

C27

B26

AK13

AK12

AM14

AM13

AM3

AM2

T2

T3

AB3

AB2

Y3

Y2

W3

W1

V2

V3

R3

R1

AD6

AD4

AB9

AB7

Y4

Y6

V4

V6

A29

C29

AB14

B30

C30

0 = Top address bit is unchanged

+1.0V_SX

DDI0_TXP_0

+1.0V_SX

DDI0_TXN_0

+1.0V_SX

DDI0_TXP_1

+1.0V_SX

DDI0_TXN_1

+1.0V_SX

DDI0_TXP_2

+1.0V_SX

DDI0_TXN_2

+

VLV_M_D/BGA

REV = 1.15

1.0V_SX

+1.0V_SX

+1.0V_SX

+1.0V_SX

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

DDI0_TXP_3

DDI0_TXN_3

DDI0_AUXP

DDI0_AUXN

DDI0_HPD

DDI0_DDCDATA

DDI0_DDCCLK

DDI0_VDDEN

DDI0_BKLTEN

DDI0_BKLTCTL

DDI0_RCOMP

DDI0_RCOMP_P

RESERVED_AM14

RESERVED_AM13

VSS_AM3

VSS_AM2

RESERVED_T2

RESERVED_T3

RESERVED_AB3

RESERVED_AB2

RESERVED_Y3

RESERVED_Y2

RESERVED_W3

RESERVED_W1

RESERVED_V2

RESERVED_V3

RESERVED_R3

RESERVED_R1

RESERVED_AD6

RESERVED_AD4

RESERVED_AB9

RESERVED_AB7

RESERVED_Y4

RESERVED_Y6

RESERVED_V4

RESERVED_V6

GPIO_S0_NC13

GPIO_S0_NC14_C29

RESERVED_AB14

GPIO_S0_NC12

RESERVED_C30

Configuration Note

1 = Top address bit is inverted

0 = LPC

1 = SPI

0 = Override

1 = Normal operation

0 = DDI0 not detected

1 = DDI0 detected

0 = DDI0 not detected

1 = DDI0 detected

GPIO_SO_NC_13

5

4

?

VLV_M_D

+1.0V_SX

+1.0V_SX

+1.8V

+1.8V

DDI1_DDCDATA

+1.8V

DDI1_DDCCLK

+1.8V

+1.8V

DDI1_BKLTEN

+1.8V

DDI1_BKLTCTL

RESERVED_AH14

RESERVED_AH13

RESERVED_AF14

RESERVED_AF13

VGA_DDCCLK

VGA_DDCDATA

RESERVED_T7

RESERVED_T9

RESERVED_AB13

RESERVED_AB12

RESERVED_Y12

RESERVED_Y13

RESERVED_V10

RESERVED_V9

RESERVED_T12

RESERVED_T10

RESERVED_V14

RESERVED_V13

RESERVED_T14

RESERVED_T13

RESERVED_T6

RESERVED_T4

RESERVED_P14

RESERVED_K34

GPIO_S0_NC26

GPIO_S0_NC25

GPIO_S0_NC24

GPIO_S0_NC23

GPIO_S0_NC22

GPIO_S0_NC21

GPIO_S0_NC20

GPIO_S0_NC18

GPIO_S0_NC17

GPIO_S0_NC16

3 OF 13

GPIO_S0_NC15

GPIO_S0_SC_56(7)

I2S_LRCLK(5)

SOC_OVERRIDE#(27)

Pull up +1.8V at HDMI side

AG3

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_TXP_2

DDI1_TXN_2

DDI1_TXP_3

DDI1_TXN_3

DDI1_AUXP

DDI1_AUXN

DDI1_HPD

DDI1_VDDEN

VSS_AH3

VSS_AH2

VGA_RED

VGA_BLUE

VGA_GREEN

VGA_IREF

VGA_IRTN

VGA_HSYNC

VGA_VSYNC

?

PP1800_PCH GND

R58 *0_4_S

HDMI_DDCDATA_SW

PP1800_PCH GND

PP1800_PCH GND

3

EDP_TXP0

AG1

EDP_TXN0

AF3

EDP_TXP1

AF2

EDP_TXN1

AD3

EDP_TXP2

AD2

EDP_TXN2

AC3

EDP_TXP3

AC1

EDP_TXN3

AK3

EDP_AUXP

AK2

EDP_AUXN

K30

EDP_HPD_L

P30

DDI1_DDCDATA

G30

N30

SOC_DISP_ON_C

J30

SOC_EDP_BLON_C

M30

SOC_DPST_PWM_C

AH14

AH13

AF14

AF13

AH3

SOC_PIN_AH3

AH2

BA3

AY2

BA1

AW1

AY3

BD2

BF2

BC1

BC2

T7

T9

AB13

AB12

Y12

Y13

V10

V9

T12

T10

V14

V13

T14

T13

T6

T4

P14

K34

D32

N32

J34

K28

F28

F32

D34

J28

D28

M32

F34

GPIO_S0_SC_56

R128 *10K_4

I2S_LRCLK

R372 10K_4

I2S_DOUT(5)

DDI1_DDCDATA

R386 2.2K_4 R388 *10K_4

GPIO_NC13

R62 *10K_4

R452 *0_4_S

SOC_PIN_AH2

R457 *0_4_S

CRT_R

CRT_B

CRT_G

SOC_VGA_IREF

SOC_VGA_IRTN

CRT_HSYNC

CRT_VSYNC

VGA_DDCCLK

VGA_DDCDATA

XDP_GPIO_S0_NC19

XDP_GPIO_S0_NC23

XDP_GPIO_S0_NC22

XDP_GPIO_S0_NC21

XDP_GPIO_S0_NC20

XDP_GPIO_S0_NC18

XDP_GPIO_S0_NC17

XDP_GPIO_S0_NC16

XDP_GPIO_S0_NC15

R434 *10K_4

R369 *10K_4

I2S_DOUT

SOC_OVERRIDE_NM

R76 *10K_4

R63 10K_4

EDP_TXN0 (17)

EDP_TXP1 (17)

EDP_TXN1 (17)

EDP_TXP2 (17)

EDP_TXN2 (17)

EDP_TXP3 (17)

EDP_TXN3 (17)

EDP_AUXP (17)

EDP_AUXN (17)

SOC_DISP_ON_C (15)

SOC_EDP_BLON_C (15)

SOC_DPST_PWM_C (15)

TP19

TP20

TP16

TP17

TP22

TP49

TP48

R180 *0_4_S

R197 *0_4_S

3

2

1

XDP_GPIO_S0_NC19 (11)

XDP_GPIO_S0_NC23 (11)

XDP_GPIO_S0_NC22 (11)

XDP_GPIO_S0_NC21 (11)

XDP_GPIO_S0_NC20 (11)

XDP_GPIO_S0_NC18 (11)

XDP_GPIO_S0_NC17 (11)

XDP_GPIO_S0_NC16 (11)

XDP_GPIO_S0_NC15 (11)

GNDPP1800_PCH

Q6

2N7002K

GND

1029 unstuff R128, using SoC internal PU

029 unstuff R372, using SoC internal PU

1

1115 stuff R372, system can't boot if un-stuff R372 on

proto1.5 board, need intel double confirm before proto2

GND

1029 unstuff R386, using SoC internal PU

1115 stuff R386, it is required for eDP to be detected

HPD output high

SOC active Low

2

PP1800_PCH

R146

10K_4

EDP_HPD_L

3

2

Q32

2N7002K

GND GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

EDP_HPD

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Valley 3/9 (Display)

Valley 3/9 (Display)

Valley 3/9 (Display)

R459

100K/F_4

EDP_HPD (17)

NL6

NL6

NL6

1

4

1A

1A

1A

414

414

414

Page 5

5

4

3

2

1

PP1800_PCH

R215 *10K_4

R198 *10K_4

D D

C C

SATA_DEVSLP_C

SATA_LED_R_N

1025 Delete complete SSD(connector and caps), unstuf

and add test points on SATA signals

TP34

TP36

TP37

TP38

R409 49.9/F_4

GND

R131 *0_4_S

R139 *0_4_S

R204 *0_4_S

R408

402/F_4

GND

SOC_KBC_SCI(14)

EMMC_CLK(21)

EMMC_D0(21)

EMMC_D1(21)

EMMC_D2(21)

EMMC_D3(21)

EMMC_D4(21)

EMMC_D5(21)

EMMC_D6(21)

EMMC_D7(21)

EMMC_CMD(21)

EMMC_RST#(21)

0217 reserve C377 on SD CLK for EMI

SD3_CLK

C377

*33P/50V_4

B B

SD3_CLK(16)

SD3_D1(16)

SD3_D2(16)

SD3_D3(16)

SD3_CD#(16,18)

SD3_CMD(16)

TP23

SDIO3_PWR_EN#(16)

SD3_CLK

SD3_D0

SD3_D1

SD3_D2

SD3_D3

SD3_CD#

SD3_CMD

SDMMC3_1P8_EN

SDIO3_PWR_EN#

R403 49.9/F_4

GND

f R215

SATA_TXP0_SSD

SATA_TXN0_SSD

SATA_RXP0_SSD

SATA_RXN0_SSD

ICLK_SATA_TERMP

ICLK_SATA_TERMN

SATA_GP0

SATA_DEVSLP_C

SATA_LED_R_N

SATA_RCOMP_DP

SATA_RCOMP_DN

EMMC_CLK

EMMC_D0

EMMC_D1

EMMC_D2

EMMC_D3

EMMC_D4

EMMC_D5

EMMC_D6

EMMC_D7

EMMC_CMD

EMMC_RST#

EMMC_RCOMP

SDIO3_RCOMP

U14D

BF6

SATA_TXP_0

BG7

SATA_TXN_0

AU16

SATA_RXP_0

AV16

SATA_RXN_0

BD10

SATA_TXP1

BF10

SATA_TXN_1

AY16

SATA_RXP_1

BA16

SATA_RXN_1

BB10

ICLK_SATA_TERMP

BC10

ICLK_SATA_TERMN

BA12

SATA_GP0

AY14

SATA_GP1

AY12

SATA_LED

AU18

SATA_RCOMP_P_AU18

AT18

SATA_RCOMP_N_AT18

AT22

MMC1_CLK

AV20

MMC1_D0

AU22

MMC1_D1

AV22

MMC1_D2

AT20

MMC1_D3

AY24

MMC1_D4

AU26

MMC1_D5

AT26

MMC1_D6

AU20

MMC1_D7

AV26

MMC1_CMD

BA24

MMC1_RST

AY18

MMC1_RCOMP

BA18

SD2_CLK

AY20

SD2_D0

BD20

SD2_D1

BA20

SD2_D2

BD18

SD2_D3_CD

BC18

SD2_CMD

AY26

SD3_CLK

AT28

SD3_D0

BD26

SD3_D1

AU28

SD3_D2

BA26

SD3_D3

BC24

SD3_CD#

AV28

SD3_CMD

BF22

SD3_1P8EN

BD22

SD3_PWREN

BF26

SD3_RCOMP

V

LV_M_D/BGA

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V

+1.8V/+3.3V

REV = 1.15

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

?

VLV_M_D

+1.0V

+1.0V

+1.8V

+1.8V

+1.8V

+1.8V

PCIE_RCOMP_P_AP14_AP14

PCIE_RCOMP_N_AP13_AP13

+1.8V/1.5V

+1.8V/1.5V

+1.8V/1.5V

+1.8V/1.5V

+1.8V/1.5V

+1.8V/1.5V

+1.8V/1.5V+1.8V/+3.3V

+1.8V/1.5V

+1.8V

4 OF 13

+1.8V

RESERVED_AV10

HDA_LPE_RCOMP

LPE_I2S2_DATAOUT

LPE_I2S2_DATAIN

+1.0V

PCIE_TXP_0

PCIE_TXN_0

PCIE_RXP_0

PCIE_RXN_0

PCIE_TXP_1

PCIE_TXN_1

PCIE_RXP_1

PCIE_RXN_1

PCIE_TXP_2

PCIE_TXN_2

PCIE_RXP_2

PCIE_RXN_2

PCIE_TXP_3

PCIE_TXN_3

PCIE_RXP_3

PCIE_RXN_3

VSS_BB7

VSS_BB5

PCIE_CLKREQ_0

PCIE_CLKREQ_1

PCIE_CLKREQ_2

PCIE_CLKREQ_3

SD3_WP_BD5

RESERVED_BB4

RESERVED_BB3

RESERVED_AV9

HDA_RST

HDA_SYNC

HDA_CLK

HDA_SDO

HDA_SDI0

HDA_SDI1

HDA_DOCKRST

HDA_DOCKEN

LPE_I2S2_CLK

LPE_I2S2_FRM

RESERVED_P34

RESERVED_N34

RESERVED_AK9

RESERVED_AK7

PROCHOT

AY7

PCIE_TX0+_WLAN_C

AY6

PCIE_TX0-_WLAN_C

AT14

PCIE_RX0+_WLAN

AT13

PCIE_RX0-_WLAN

AV6

PCIE_TX1+_IMAGE_C

AV4

PCIE_TX1-_IMAGE_C

AT10

PCIE_RX1+_IMAGE

AT9

PCIE_RX1-_IMAGE

AT7

AT6

AP12

AP10

AP6

AP4

1213 swap CLKREQ_WLAN and CLKREQ_IMAGE for

AP9

CLKREQ and CLK pins are aligned

AP7

BB7

VSS_BB7

BB5

VSS_BB5

BG3

PCIE_CLKREQ_WLAN#

BD7

PCIE_CLKREQ_IMAGE#

BG5

PCIE_CLKREQ_LAN#

BE3

PCIE_CLKREQ3#

BD5

SD3_WP

AP14

SOC_PCIE_COMP

AP13

SOC_PCIE_COMN

BB4

BB3

AV10

AV9

BF20

HDA_RCOMP

BG22

ACZ_RST#

BH20

ACZ_SYNC

BJ21

ACZ_BCLK

BG20

ACZ_SDOUT

BG19

PCH_AZ_CODEC_SDIN0

BG21

BH18

DET_TRIGGER

BG18

HDA_DOCKEN#

BF28

I2S_BCLK

BA30

I2S_LRCLK

BC30

I2S_DOUT

BD28

I2S_DIN

P34

N34

AK9

AK7

C24

SOC_PROCHOT#

?

C336 0.1U/10V_4

C341 0.1U/10V_4

C322 0.1U/10V_4

C328 0.1U/10V_4

R123 *0_4_S

R96 71.5/F_4

R103 *0_4_S

R455 *0_4_S

R462 *0_4_S

TP18

TP15

SD3_WP (16)

R410 49.9/F_4

TP6

TP10

TP7

TP8

TP9

DET_TRIGGER (24)

AJACK_MICPRES_L (24)SD3_D0(16)

R383 *0_4_S

R375 *0_4_S

R381 *0_4_S

R379 *0_4_S

H_PROCHOT#

R414 *0_4_S

R553 *0_4

1021 un-stuff R553

PCIE_TX0+_WLAN (20)

PCIE_TX0-_WLAN (20)

PCIE_RX0+_WLAN (20)

PCIE_RX0-_WLAN (20)

PCIE_TX1+_IMAGE (20)

PCIE_TX1-_IMAGE (20)

PCIE_RX1+_IMAGE (20)

PCIE_RX1-_IMAGE (20)

PCIE_CLKREQ_WLAN# (20)

PCIE_CLKREQ_IMAGE# (20)

GND

I2S_BCLK_R (24)

I2S_LRCLK_R (24)

I2S_DOUT_R (24)

I2S_DIN_R (24)

PP1000_PCH

H_PROCHOT# (18,27,33)

IMVP7_PROCHOT# (28)

ALERT# (23)

GND

PCIE_CLKREQ_IMAGE#

PCIE_CLKREQ_WLAN#

I2S_DOUT

R431

402/F_4

5

PP1800_PCH

R152 10K_4

R148 10K_4

R364 *10K_4

1029 unstuff R364,

using SoC internal PU

0 = LPC

1 = SPI

I2S_LRCLK

I2S_DOUT

Security Flash Descriptors

0 = Override

1 = Normal Operation

Need check to see if MOSFET

isolation needed or not

I2S_LRCLK (4)

I2S_DOUT (4)

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

5

4

3

2

Friday, April 25, 2014

PROJECT :

Valley 4/9 (SD/PCIE/SATA)

Valley 4/9 (SD/PCIE/SATA)

Valley 4/9 (SD/PCIE/SATA)

NL6

NL6

NL6

1A

1A

1A

415

415

1

415

Page 6

C105 12P/50V_4

GND

GND

C106 12P/50V_4

1121 by X'tal vender suggestion,

D D

change C105/C106 from 15pF to 12pF

PP1800_PCH

C C

PP1800_PCH_S5

1025 add level shifter for

LTE SUSCLK

B B

XTAL25_OUT

1

2

Y3

25MHZ +-10PPM

4

3

XTAL25_IN

1031 remove R417, PRDY should

be direct connection between

SoC and XDP by intel request

1128 add a connection and name to

KBD_IRQ#, besides add pulled high resistor

R150 10K_4

R117 *10K_4

R108 10K_4

R122 10K_4

R111 10K_4

5

R188

1M_4

SOC_JTAG2_TDO

PCH_WAKE#

TRACKPAD_INT#

TOUCH_INT#

XTAL25_IN

XTAL25_OUT

R466 4.02K/F_4

R467 47.5/F_4

GND

CLK_PCIE_WLANN(20)

CLK_PCIE_WLANP(20)

CLK_PCIE_IMAGEN(20)

CLK_PCIE_IMAGEP(20)

I2S_MCLK(24)

KBD_IRQ#(27)

SRT_CRST#(11)

XDP_H_TCK(11)

XDP_H_TRST#(11)

XDP_H_TMS(11)

XDP_H_TDI(11)

XDP_H_TDO(11)

XDP_H_PRDY#(11)

XDP_H_PREQ#_C(11)

MUX_AUD_INT1#(24)

R107 *0_4_S

R424 *0_4_S

WIFI_DISABLE#(15)

GND

PCH_WAKE_L(27)

TRACKPAD_INT#(26)

TOUCH_INT#(15)

LTE_WAKE#(15)

PMC_SUSCLK1(15)

SOC_KBC_SMI(14)

ICLK_ICOMP

ICLK_RCOMP

CLK_PCIE_WLANN

CLK_PCIE_WLANP

CLK_PCIE_IMAGEN

CLK_PCIE_IMAGEP

I2S_MCLK

KBD_IRQ#KBD_IRQ#

SRT_CRST#

XDP_H_TCK

XDP_H_TRST#

XDP_H_TMS

XDP_H_TDI

XDP_H_TDO

XDP_H_PRDY#

XDP_H_PREQ#_C

SOC_SPI_CS#

SOC_SPI_MISO

SOC_SPI_MOSI

SOC_SPI_CLK

PCH_WAKE#

TRACKPAD_INT#

TOUCH_INT#

LTE_WAKE#

SOC_JTAG2_TDO

PMC_SUSCLK1

PCH_SPI_WP_D

SOC_GPOI7

MUX_AUD_INT1#

WIFI_DISABLE#

R402 49.9/F_4

RTC Clock 32.768KHz

RTC Circuitry(RTC)

PP3300_RTC

A A

R116 *0_6_S

30mils

+3V_RTC

R138

20K/F_4

R130

20K/F_4

C85

1u/6.3V_4

GND

5

GND

GND

C89

1u/6.3V_4

C84

1u/6.3V_4

SOC_RTEST#

SRT_CRST#

4

SOC_GPIO_RCOMP

RTC_X1

R161

10M_4

RTC_X2

4

AH12

AH10

AD14

AD13

AD10

AD12

AM10

AT34

AD9

AF6

AF4

AF9

AF7

AK4

AK6

AM4

AM6

AM9

BH7

BH5

BH4

BH8

BH6

BJ9

C12

D14

G12

F14

F12

G16

D18

F16

C23

C21

B22

A21

C22

B18

B16

C18

A17

C17

C16

B14

C15

C13

A13

C19

N26

U14E

ICLK_OSCIN

ICLK_OSCOUT

RESERVED_AD9

ICLK_ICOMP

ICLK_RCOMP

RESERVED_AD10

RESERVED_AD12

PCIE_CLKN_00

PCIE_CLKP_00

PCIE_CLKN_11

PCIE_CLKP_11

PCIE_CLKN_22

PCIE_CLKP_22

PCIE_CLKN_33

PCIE_CLKP_33

RESERVED_AM10

RESERVED_AM9

PMC_PLT_CLK_00

PMC_PLT_CLK_11

PMC_PLT_CLK_22

PMC_PLT_CLK_33

PMC_PLT_CLK_44

PMC_PLT_CLK_55

ILB_RTC_RST

TAP_TCK

TAP_TRST

TAP_TMS

TAP_TDI

TAP_TDO

TAP_PRDY

TAP_PREQ

RESERVED

PCU_SPI_CS_00

PCU_SPI_CS_11

PCU_SPI_MISO

PCU_SPI_MOSI

PCU_SPI_CLK

GPIO_S5_0

GPIO_S5_1

GPIO_S5_2

GPIO_S5_3

GPIO_S5_4

GPIO_S5_5

GPIO_S5_6

GPIO_S5_7

GPIO_S5_8

GPIO_S5_9

GPIO_S5_10

GPIO_RCOMP

VLV_M_D/BGA

REV = 1.15

12

Y2

32.768KHZ

?

VLV_M_D

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V

+1.8V_S5

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V_S5

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5 +1.0V

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

SPI ROM needs power in S3/S5 for the TXE (Trusted execution engine).

C9115P/50V_4

C9215P/50V_4

GND

+3V_RTC

+3V_RTC

+3V_RTC

5 OF 13

PP1800_PCH

PP1800_PCH_S5

+1.0V

+1.0V

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V_S5

+1.8V

+1.8V

+1.8V

+1.8V

R158 *0_6

R157 *0_6_S

PP3300_PCH_S5

3

SIO_UART1_RXD

SIO_UART1_TXD

SIO_UART1_RTS

SIO_UART1_CTS

SIO_UART2_RXD

SIO_UART2_TXD

SIO_UART2_RTS

SIO_UART2_CTS

PMC_SUSPWRDNACK

PMC_SUSCLK0_G24

PMC_SLP_S0IX

PMC_SLP_S4

PMC_SLP_S3

GPIO_S514_J20

PMC_ACPRESENT

PMC_WAKE_PCIE_0

PMC_BATLOW

PMC_PWRBTN

PMC_RSTBTN

PMC_PLTRST

GPIO_S517_J24

PMC_SUS_STAT

ILB_RTC_TEST

PMC_RSMRST

PMC_CORE_PWROK

ILB_RTC_X1

ILB_RTC_X2

ILB_RTC_EXTPAD

SVID_ALERT

SVID_DATA

SVID_CLK

SIO_PWM_00

SIO_PWM_11

GPIO_S5_22

GPIO_S5_23

GPIO_S5_24

GPIO_S5_25

GPIO_S5_26

GPIO_S5_27

GPIO_S5_28

GPIO_S5_29

GPIO_S5_30

SIO_SPI_CS

SIO_SPI_MISO

SIO_SPI_MOSI

SIO_SPI_CLK

1

PP1800_PCH_S5

SPI_WP_ME

SPI_HOLD_ME

3

AU34

AV34

BA34

AY34

BF34

BD34

BD32

BF32

D26

G24

F18

F22

D22

J20

D20

F26

K26

J26

BG9

F20

J24

G18

C11

B10

B7

C9

A9

B8

B24

A25

C25

AU32

AT32

K24

N24

M20

J18

M18

K18

K20

M22

M24

AV32

BA28

AY28

AY30

Q29 PJA138K

2

R136 10K_4

ALS_INT#

TOUCH_INT_L_DX

SIO_UART2_RXD

SIO_UART2_TXD

PMC_SUSPWRDNACK

PMC_SUSCLK0

SLP_S0IX#

SLP_S4#

SLP_S3#

ACPRESENT

SOC_PMC_WAKE#

PMC_BATLOW#

SOC_PWRBTN#

SOC_REST_BTN#

SOC_PLTRST#

PMC_SUS_STAT#

SOC_RTEST#

SOC_RSMRST#

CORE_PWROK

RTC_X1

RTC_X2

BRTC_EXTPAD

SVID_ALERT#_SOC

SVID_DATA_SOC

SVID_CLK_SOC

SIO_PWM1

XDP_GPIO_DFX0

XDP_GPIO_DFX1

XDP_GPIO_DFX2

XDP_GPIO_DFX3

XDP_GPIO_DFX4

XDP_GPIO_DFX5

XDP_GPIO_DFX6

XDP_GPIO_DFX7

XDP_GPIO_DFX8

SIO_SPI_CS#

SIO_SPI_MISO

SIO_SPI_MOSI

SIO_SPI_CLK

PP1800_PCH_ME

3

PCH_SPI_WP_D

R133 0_4

R513 0_4

1

2

2

ALS_INT# (17)

TOUCH_INT_L_DX (15)

TP31

TP33

PMC_SUSPWRDNACK (14)

PMC_SUSCLK0 (15)

SLP_S0IX# (14)

SLP_S4# (2,11,14)

SLP_S3# (11,14)

ACPRESENT (15)

SOC_PMC_WAKE# (15)

SOC_PWRBTN# (11,14)

SOC_REST_BTN# (11,18)

SUS STAT OUTPUT PORT

R448 *0_4_S

C101 0.1U/10V_4

R90 20/F_4

R84 16.9/F_4

R81 0_4

0206 Disconnect SPI SIO I/F

TP67

TP68

TP69

TP70

R488 *3.3K/F_4

R500 3.3K/F_4

near SPI ROM as possible

Q272N7002K

3

PCH_SPI_WP_D

SPI_WP_ME

SOC_PLTRST# (11,14)

PMC_SUS_STAT# (14)

SOC_RTEST# (11)

SOC_RSMRST# (11,14)

CORE_PWROK_R (11,27)

SPEC 512177 INPUT PORT

VR_SVID_ALERT#

VR_SVID_DATA

VR_SVID_CLK

TP32

XDP_GPIO_DFX0 (11)

XDP_GPIO_DFX1 (11)

XDP_GPIO_DFX2 (11)

XDP_GPIO_DFX3 (11)

XDP_GPIO_DFX4 (11)

XDP_GPIO_DFX5 (11)

XDP_GPIO_DFX6 (11)

XDP_GPIO_DFX7 (11)

XDP_GPIO_DFX8 (11)

PP1800_PCH_ME

C355

0.1U/10V_4

GND

SPI_WP_ME_ROM

SPI_HOLD_ME

PP1800_PCH_ME

GPIO_SPI_WP (18)

SPI_HOLD#_BIOS (18)

To PCH

PCH_SPI_WP_D connect to GPIO58 at GRB

SPI_WP_ME (25,27)

2

GND

VR_SVID_ALERT# (33)

VR_SVID_DATA (33)

VR_SVID_CLK (33)

SPI_WP_ME

U22

8

VCC

Default PD

3

WP#

SPI_HOLD7GND

SPI_FLASH

soic8-7_9-1_27

AKE5EZN0N00

IC FLASH (8P) W25Q64FWSSIG (SOIC)

R501 3.3K/F_4

To debug header

From Screw/EC

O_1.8VA

SPI_SI

SPI_SO

CS#

SPI_SCK

SOC_SPI_CS#

1

PP1800_PCH_S5

PMC_SUSPWRDNACK

SOC_PMC_WAKE#

ACPRESENT

PMC_BATLOW#

SOC_REST_BTN#

TOUCH_INT_L_DX

ALS_INT#

9/6 Add EC_RCIN_L for warm boot,

EC side is OD type

SOC_REST_BTN#

R165 *0_4_S

5

2

1

6

4

SPI_WP_ME_ROM_Q

SOC_SPI_MOSI_R

SOC_SPI_MISO_R

SOC_SPI_CS#_R

SOC_SPI_CLK_R

GND

SPI NOR FLASH

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet

R413 10K_4

R412 10K_4

R397 *2.2K_4

R399 10K_4

R441 10K_4

R363 10K_4

R418 10K_4

DATA, CLK CLOSE TO VR

VR_SVID_DATA

VR_SVID_ALERT#

VR_SVID_CLK

R468 *0_4_S

LAYOUT CLOSE TO SPI ROM

3.3V

R472 22/F_4

R487 22/F_4

R503 22/F_4

R480 22/F_4

LAYOUT CLOSE TO SPI ROM

R471 0_4

R479 0_4

R470 0_4

R481 0_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Valley 5/9 (SPI/GPIO/CLK)

Valley 5/9 (SPI/GPIO/CLK)

Valley 5/9 (SPI/GPIO/CLK)

PP1000_PCH

R374

73.2/F_4

PP1800_PCH_ME

C115 0.1u/10V_4

2

1

U1974LVC1G34

3 5

1

PP1800_PCH

ALERT Close to SOC

EC_REST_L (27)

4

SOC_SPI_MOSI

SOC_SPI_MISO

SOC_SPI_CS#

SOC_SPI_CLK

PCH_SPI_SO_R (18)

PCH_SPI_CS0#_R (18)

NL6

NL6

NL6

R88

73.2/F_4

PCH_SPI_SI_R (18)

PCH_SPI_CLK_R (18)

6

R360

73.2/F_4

SPI_WP_ME_ROM

R179

100K_4

of

416

416

416

1A

1A

1A

Page 7

5

D D

LTE_DISABLE#(15)

M

HUB PORT 1

HUB PORT 2

C C

USB2.0

LTE

B USB3.0

HUB1

CCD

BT

GND

PP1800_PCH_S5

GND

1101 add option BOM R446,R449 for

EC CLK for power saving by Intel

request

B B

PCLK_TPM(22)

R446

*0_4

CLK_PCI_EC(27)

PP1800_PCH

A A

LPC_CLKRUN_L(27)

R120 2.2K_4

R125 2.2K_4

R141 2.2K_4

5

GND

R449 *0_4_S

0217 reserve R483 for CLKRUN# disable

GND

SMB_SOC_DATA

SMB_SOC_CLK

SMB_SOC_ALERTB

R483 *0_4

R185 45.3/F_4

R415 49.9/F_4

USBP0+(25)

USBP0-(25)

USBP1+(23)

USBP1-(23)

USBP2+(17)

USBP2-(17)

USBP3+(20)

USBP3-(20)

R437 1K/F_4

R425 1K/F_4

R97 10K_4

R189 10K_4

R443 45.3/F_4

R436 *0_4

GND

LPC_LAD0(22,27)

LPC_LAD1(22,27)

LPC_LAD2(22,27)

LPC_LAD3(22,27)

LPC_LFRAME#(22,27)

CLK_PCI_EC_R SOC_CLKOUT_1

LPC_CLKRUN_L

SOC_SERIRQ(14)

SOC_CLKRUN#

R115 22/F_4

R112 22/F_4

R109 0_4 R392 TS@4.7K_4

SMB_SOC_DATA(11)

SMB_SOC_CLK(11)

LTE_DISABLE#

RAM_ID0

RAM_ID1

RAM_ID2

RAM_ID3

ICLK_USB_TERMN_0

ICLK_USB_TERMN_1

USB_OC0#(14,25)

USB_OC0#

USB_OC1#

USB_OC1#(14,23)

USB_RCOMP

USB_PLL_MON

USB_HSIC_RCOMP

LPC_RCOMP

LPC_LAD0

LPC_LAD1

LPC_LAD2

LPC_LAD3

LPC_LFRAME#

SOC_CLKOUT_0

SOC_CLKRUN#

SOC_SERIRQ

SMB_SOC_DATA

SMB_SOC_CLK

SMB_SOC_ALERTB

4

U14F

G2

GPIO_S5_31

M3

GPIO_S5_32

L1

GPIO_S5_33

K2

GPIO_S5_34

K3

GPIO_S5_35

M2

GPIO_S5_36

N3

GPIO_S5_37

P2

GPIO_S5_38

L3

GPIO_S5_39

J3

GPIO_S5_40

P3

GPIO_S5_41

H3

GPIO_S5_42

B12

GPIO_S5_43

M16

USB_DP0

K16

USB_DN0

J14

USB_DP1

G14

USB_DN1

K12

USB_DP2

J12

USB_DN2

K10

USB_DP3

H10

USB_DN3

D10

ICLK_USB_TERMN_D10

F10

ICLK_USB_TERMN

C20

USB_OC_00

B20

USB_OC_11

D6

USB_RCOMPO

C7

USB_RCOMPI

M13

USB_PLL_MON

B4

USB_HSIC0_DATA

B5

USB_HSIC0_STROBE

E2

USB_HSIC1_DATA

D2

USB_HSIC1_STROBE

A7

USB_HSIC_RCOMP

BF18

LPC_RCOMP

BH16

ILB_LPC_AD_00

BJ17

ILB_LPC_AD_11

BJ13

ILB_LPC_AD_22

BG14

ILB_LPC_AD_33

BG17

ILB_LPC_FRAME

BG15

ILB_LPC_CLK_00

BH14

ILB_LPC_CLK_11

BG16

ILB_LPC_CLKRUN

BG13

ILB_LPC_SERIRQ

BG12

PCU_SMB_DATA

BH10

PCU_SMB_CLK

BG11

PCU_SMB_ALERT

VLV_M_D/BGA

4

REV = 1.15

+1.8V_S5

+1.8V_S5

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V/+3.3V

+1.8V

+1.8V

+1.8V

+1.8V

?

VLV_M_D

6 OF 13

3

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

3

RESERVED_M10

RESERVED_M9

RESERVED_P7

RESERVED_P6

RESERVED_M7

USB3_REXT0

RESERVED_P10

RESERVED_P12

RESERVED_M4

RESERVED_M6

USB3_RXP0

USB3_RXN0

USB3_TXP0

USB3_TXN0

RESERVED_H8

RESERVED_H7

RESERVED_H5

RESERVED_H4

GPIO_S0_SC_55

GPIO_S0_SC_56

GPIO_S0_SC_57

GPIO_S0_SC_58

GPIO_S0_SC_59

GPIO_S0_SC_60

GPIO_S0_SC_61

ILB_8254_SPKR

SIO_I2C0_DATA

SIO_I2C0_CLK

SIO_I2C1_DATA

SIO_I2C1_CLK

SIO_I2C2_DATA

SIO_I2C2_CLK

SIO_I2C3_DATA

SIO_I2C3_CLK

SIO_I2C4_DATA

SIO_I2C4_CLK

SIO_I2C5_DATA

SIO_I2C5_CLK

SIO_I2C6_DATA

SIO_I2C6_CLK

GPIO_S0_SC_092

GPIO_S0_SC_093

2

RAM ID

RAM_ID0

R186 *1K_4

R187 1K_4

R196 1K_4

R212 *1K_4

0220 reserve placeholder R212,R218

f

or additional RAM ID

M10

M9

P7

P6

M7

M12

USB3_P0_REXT

P10

P12

M4

M6

D4

E3

K6

K7

H8

H7

H5

H4

BD12

BC12

BD14

BC14

BF14

BD16

BC16

BH12

BH22

BG23

BG24

BH24

BG25

BJ25

BG26

BH26

BF27

BG27

BH28

BG28

BJ29

BG29

BH30

BG30

?

R440 1.24K/F_4

GND

USB3_RXP0

USB3_RXN0

USB3_TXP0

USB3_TXN0

TRACKPAD_INT_DX

GPIO_S0_SC_56

SOC_UART_TX

SIM_DET_C

EC_IN_RW_C

SOC_UART_RX SOC_UART_TX SOC_UART_RX

I2C_0_SDA_C

R102 22/F_4

I2C_0_SCL_C

R95 22/F_4

I2C_1_SDA_C

R89 22/F_4

I2C_1_SCL_C

R83 22/F_4

I2C_4_SDA_C

R79 22/F_4

I2C_4_SCL_C

R75 22/F_4

I2C_5_SDA_C

R71 TS@22/F_4

I2C_5_SCL_C

R65 TS@22/F_4

I2C_NFC_SDA

I2C_NFC_SCL

USB3_RXP0 (25)

USB3_RXN0 (25)

USB3_TXP0 (25)

USB3_TXN0 (25)

I2C_0_SDA_R (15)

I2C_0_SCL_R (15)

I2C_1_SDA_R (24)

I2C_1_SCL_R (24)

I2C_4_SDA (17)

I2C_4_SCL (17)

I2C_5_SDA (17)

I2C_5_SCL (17)

220 R392,R389,R71,R65 need always to be stuffed even if w/o TS SKU

0

2

RAM_IDVender Freq.

Micron

Hynix

001

AKD5JGSTL02

AKD5JGETW00

Q PN Mfr. PN

MT41K256M16HA-125:E

H5TC4G63AFR-PBA

Micron 010 MT41K128M16JT-125:KAKD5DGSTL02

AKD5MG0TW02

AKD5JGSTL02

101

AKD5JGETW00

TRACKPAD_INT_DX (26)

GPIO_S0_SC_56 (4)

SOC_UART_TX (18)

SIM_DET_C (15)

EC_IN_RW_C (15)

SOC_UART_RX (18)

H5TC2G63FFR-PBAHynix 011

MT41K256M16HA-125:E

H5TC4G63AFR-PBAHynix

Proto1/1.5 stage use H2G & H4G

1212 add new RAMID 101 for single channel SKU

SIM_DET_C

TRACKPAD_INT_DX

Touch pad

udio Codec

A

Light sensor

Touch panel

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

R202 1K_4

RAM_ID1

R203 *1K_4

RAM_ID2

R192 *1K_4

RAM_ID3

R218 *1K_4

R420

*0_4

Un-Stuff for Test Only

I2C_0_SDA_R

I2C_0_SCL_R

I2C_1_SDA_R

I2C_1_SCL_R

I2C_4_SDA

I2C_4_SCL

I2C_5_SDA

I2C_5_SCL

I2C_NFC_SDA

I2C_NFC_SCL

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Valley 6/9 (USB/LPC/I2C)

Valley 6/9 (USB/LPC/I2C)

Valley 6/9 (USB/LPC/I2C)

1

PP1800_PCH_S5

1600MHz000

1600MHz

1600MHz

1600MHz

1600MHzMicron 100

1600MHz

PP1800_PCH

R422 10K_4

R433 10K_4

PP1800_PCH

R438 4.7K_4

R432 4.7K_4

R421 4.7K_4

R416 4.7K_4

R398 4.7K_4

R394 4.7K_4

R389 TS@4.7K_4

R368 *4.7K_4

R367 *4.7K_4

NL6

NL6

NL6

1

Size

4Gb

4Gb

2Gb

2Gb

4Gb

4Gb

7

Total

Size

4GB

4GB

2GB

2GB

2GB

2GB

1A

1A

1A

417

417

417

Page 8

5

4

3

2

1

8

1031 for layout suggestion by

intel, VSS_AXG_SENSE didn't

D D

+VCC_CORE

+VCC_GFX

connect to VSS_SENSE, will

connect the GND via near

VCC_AXG_SENSE

1031 for layout, add 0hm between

GND and VSS_AXG_SENSE

R373

R458

100/F_4

100/F_4

VCC_SENSE

VSS_SENSE

R382

100/F_4

C C

B B

GND

1030 for core power, change

C271,C281,C280,C278,C273 to 10uF

1206 change C271,C273,C280 to

0603 22uF for ACLL issue

1204 for z-height issue, change

C72,C75,C81 to 0.85mm cap

VSS_AXG_SENSE(33)

PP1350

PP1350

+VCC_CORE

R385 *0_4_S

VCC_SENSE(33)

VCC_AXG_SENSE(33)

VSS_SENSE(33)

R343 *0_4_S

GND

GND

VCC_SENSE

VCC_AXG_SENSE

VSS_SENSEVCC_AXG_SENSE

PP1350_VSM

C231 1U/6.3V_4

C251 1U/6.3V_4

C38 0.1U/10V_4

C271 22u/6.3V_6

C281 10u/6.3V_4

C280 22u/6.3V_6

C278 10u/6.3V_4

C273 22u/6.3V_6

C72 22u/6.3V_8

C83 22u/6.3V_8

C75 22u/6.3V_8

C81 22u/6.3V_8

C79 22u/6.3V_8

C80 22u/6.3V_8

C76 22u/6.3V_8

GND

U14G

P28

CORE_VCC_SENSE_P28

BB8

UNCORE_VNN_SENSE

N28

CORE_VSS_SENSE_N28

AD38

DRAM_VDD_S4_AD38

AF38

DRAM_VDD_S4_AF38

A48

DRAM_VDD_S4

AK38

DRAM_VDD_S4_AK38

AM38

DRAM_VDD_S4_AM38

AV41

DRAM_VDD_S4_AV41

AV42

DRAM_VDD_S4_AV42

BB46

DRAM_VDD_S4_BB46

AA27

CORE_VCC_S0IX_AA27

AA29

CORE_VCC_S0IX_AA29

AA30

CORE_VCC_S0IX_AA30

AC27

CORE_VCC_S0IX_AC27

AC29

CORE_VCC_S0IX_AC29

AC30

CORE_VCC_S0IX_AC30

AD27

CORE_VCC_S0IX_AD27

AD29

CORE_VCC_S0IX_AD29

AD30

CORE_VCC_S0IX_AD30

AF27

CORE_VCC_S0IX_AF27

AF29

CORE_VCC_S0IX_AF29

AG27

CORE_VCC_S0IX_AG27

AG29

CORE_VCC_S0IX_AG29

AG30

CORE_VCC_S0IX_AG30

P26

CORE_VCC_S0IX_P26

P27

CORE_VCC_S0IX_P27

U27

CORE_VCC_S0IX_U27

U29

CORE_VCC_S0IX_U29

V27

CORE_VCC_S0IX_V27

V29

CORE_VCC_S0IX_V29

V30

CORE_VCC_S0IX_V30

Y27

CORE_VCC_S0IX_Y27

Y29

CORE_VCC_S0IX_Y29

Y30

CORE_VCC_S0IX_Y30

AF30

TP_CORE_V1P05_S4

VLV_M_D/BGA

REV = 1.15

?

VLV_M_D

7 OF 13

DRAM_VDD_S4_BD49

DRAM_VDD_S4_BD52

DRAM_VDD_S4_BD53

DRAM_VDD_S4_BF44

DRAM_VDD_S4_BG51

DRAM_VDD_S4_BJ48

DRAM_VDD_S4_C51

DRAM_VDD_S4_D44

DRAM_VDD_S4_F49

DRAM_VDD_S4_F52

DRAM_VDD_S4_F53

DRAM_VDD_S4_H46

DRAM_VDD_S4_M41

DRAM_VDD_S4_M42

DRAM_VDD_S4_V38

DRAM_VDD_S4_Y38

UNCORE_VNN_S3_AA24

UNCORE_VNN_S3_AC22

UNCORE_VNN_S3_AC24

UNCORE_VNN_S3_AD22

UNCORE_VNN_S3_AD24

UNCORE_VNN_S3_AF22

UNCORE_VNN_S3_AF24

UNCORE_VNN_S3_AG22

UNCORE_VNN_S3_AG24

UNCORE_VNN_S3_AJ22

UNCORE_VNN_S3_AJ24

UNCORE_VNN_S3_AK22

UNCORE_VNN_S3_AK24

UNCORE_VNN_S3_AK25

UNCORE_VNN_S3_AK27

UNCORE_VNN_S3_AK29

UNCORE_VNN_S3_AK30

UNCORE_VNN_S3_AK32

UNCORE_VNN_S3_AM22

TP2_CORE_VCC_S0IX

1031 remove TP44 and TP35 for GND vias adding

BD49

BD52

BD53

BF44

BG51

BJ48

C51

D44

F49

F52

F53

H46

M41

M42

V38

Y38

AA24

AC22

AC24

AD22

AD24

AF22

AF24

AG22

AG24

AJ22

AJ24

AK22

AK24

AK25

AK27

AK29

AK30

AK32

AM22

AA22

PP1350

+VCC_GFX

GND

C69

10U/6.3V_6

C235

1U/6.3V_4

C63

22u/6.3V_8

C65

10U/6.3V_6

C240

1U/6.3V_4

C70

22u/6.3V_8

C236

1U/6.3V_4

C68

10U/6.3V_6

C266

22u/6.3V_6

1030 for Gfx power, change C266,C289,C290

to 10uF and add 2 caps 10uF

1206 change C266,C311,C315 to

0603 22uF for ACLL issue

C64

22u/6.3V_8

C237

1U/6.3V_4

C289

10u/6.3V_4

1030 change C60 power netname

for layout

+VCC_GFX

C290

10u/6.3V_4

C60

22u/6.3V_8

C238

1U/6.3V_4

C311

22u/6.3V_6

1U/6.3V_4

GND

C239

C315

22u/6.3V_6

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

5

4

3

2

Date: Sheet

PROJECT :

Valley 7/9 (Power 1)

Valley 7/9 (Power 1)

Valley 7/9 (Power 1)

NL6

NL6

NL6

1A

1A

1A

of

418

418

1

418

Page 9

5

C299 1U/6.3V_4

GND

C329 1U/6.3V_4

PP1000_PCH

PP1000_PCH_SX

PP1000_PCH_SX

D D

PP1000_PCH_SX

PP1000_PCH

PP1000_PCH

PP1000_PCH_SX

PP1000_PCH

C C

PP1000_PCH_S5

PP1050_PCH

PP1350_PCH_SX

PP1350_PCH

PP1350_PCH

GND

R378 *0_4_S

R380 *0_4_S

R430 *0_4_S

C295 1U/6.3V_4

C306 1U/6.3V_4

C314 1U/6.3V_4

R54 *0_4_S

R456 *0_4_S

R354 *0_8_S

R384 *0_8_S

R193 *0_6_S

DARM_V1P0_S0IX_PWR_A

GND

DARM_V1P0_S0IX_PWR

GND

DDI_V1P0_S0IX

USB3_V1P0_G3

VIS_V1P0_S0IX_PW

GND

GND

CORE_V1P05

VIS_V1P0_S0IX_PW

GND

GND

USB3_V1P0_G3

GND

CORE_V1P05

UNCORE_V1P35_S0IX

GND

VGA_V1P35_S3

UNCORE_V1P35_S0IX

GND

GND

C256 1U/6.3V_4

C258 1U/6.3V_4

C255 1U/6.3V_4

C254 1U/6.3V_4

C338 0.01U/25V_4

C305 1U/6.3V_4

C308 1U/6.3V_4

C287 1U/6.3V_4

C286 1U/6.3V_4

C284 1U/6.3V_4

C313 1U/6.3V_4

C279 1U/6.3V_4

C334 1U/6.3V_4

C324 1U/6.3V_4

C262 1U/6.3V_4

C259 1U/6.3V_4

C297 1U/6.3V_4

C253 1U/6.3V_4

C339 1U/6.3V_4

C349 1U/6.3V_4

GND

AD35

AF35

AF36

AA36

AJ36

AK35

AK36

AK19

AK21

AJ18

AM16

AN29

AN30

AF16

AF18

AM21

AN21

AN18

AN19

AA33

AF21

AG21

AN25

AC32

AA25

AG32

AF19

AG19

AJ19

AG18

AN16

V32

BJ6

Y35

Y36

U22

V22

Y18

G1

V24

Y22

Y24

M14

U18

U19

Y19

Y32

U36

V36

BD1

U16

4

U14H

SVID_V1P0_S3_V32

VGA_V1P0_S3_BJ6

DRAM_V1P0_S0IX_AD35

DRAM_V1P0_S0IX_AF35

DRAM_V1P0_S0IX_AF36

DRAM_V1P0_S0IX_AA36

DRAM_V1P0_S0IX_AJ36

DRAM_V1P0_S0IX_AK35

DRAM_V1P0_S0IX_AK36

DRAM_V1P0_S0IX_Y35

DRAM_V1P0_S0IX_Y36

DDI_V1P0_S0IX_AK19

DDI_V1P0_S0IX_AK21

DDI_V1P0_S0IX_AJ18

DDI_V1P0_S0IX_AM16

UNCORE_V1P0_G3_U22

UNCORE_V1P0_G3_V22

VIS_V1P0_S0IX_AN29

VIS_V1P0_S0IX_AN30

UNCORE_V1P0_S3_AF16

UNCORE_V1P0_S3_AF18

UNCORE_V1P0_S3_Y18

UNCORE_V1P0_S3_G1

PCIE_V1P0_S3_AM21

PCIE_V1P0_S3_AN21

PCIE_GBE_SATA_V1P0_S3_AN18

SATA_V1P0_S3_AN19

CORE_V1P05_S3_AA33

UNCORE_V1P0_S0IX_AF21

UNCORE_V1P0_S0IX_AG21

VIS_V1P0_S0IX_V24

VIS_V1P0_S0IX_Y22

VIS_V1P0_S0IX_Y24

USB_V1P0_S3_M14

USB_V1P0_S3_U18

USB_V1P0_S3_U19

GPIO_V1P0_S3_AN25

USB3_V1P0_G3_Y19

C3

USB3_V1P0_G3_C3

C5

UNCORE_V1P0_G3_C5

B6

UNCORE_V1P0_G3_B6

CORE_V1P05_S3_AC32

CORE_V1P05_S3_Y32

UNCORE_V1P35_S0IX_F4_U36

UNCORE_V1P35_S0IX_F5_AA25

UNCORE_V1P35_S0IX_F2_AG32

UNCORE_V1P35_S0IX_F3_V36

VGA_V1P35_S3_F1_BD1

UNCORE_V1P35_S0IX_F6

UNCORE_V1P35_S0IX_F1_AG19

ICLK_V1P35_S3_F1_AJ19

ICLK_V1P35_S3_F2

VSSA_AN16

USB_VSSA_U16

REV = 1.15

VLV_M_D/BGA

?

VLV_M_D

8 OF 13

DRAM_V1P35_S0IX_F1_AD36

HDA_LPE_V1P5V1P8_S3_AM32

UNCORE_V1P8_S3_AM30

UNCORE_V1P8_S3_AN32

LPC_V1P8V3P3_S3_AM27

UNCORE_V1P8_G3_U24

USB_V3P3_G3_N18

USB_V3P3_G3_P18

UNCORE_V1P8_S3_U38

VGA_V3P3_S3_AN24

PCU_V1P8_G3_V25

3V_S5

PCU_V3P3_G3_N22

SD3_V1P8V3P3_S3_AN27

VSS_AD16

USB_HSIC_V1P24_G3_V18

VSS_AD18

UNCORE_V1P8_G3_AA18

RTC_VCC_P22

USB_V1P8_G3_N20

PMU_V1P8_G3_U25

CORE_V1P05_S3_AF33

CORE_V1P05_S3_AG33

CORE_V1P05_S3_AG35

CORE_V1P05_S3_U33

CORE_V1P05_S3_U35

CORE_V1P05_S3_V33

VSS_A3_A3

VSS_A49_A49

VSS_A5_A5

VSS_A51_A51

VSS_A52_A52

VSS_A6_A6

VSS_B2_B2

VSS_B52_B52

VSS_B53_B53

VSS_BE1_BE1

VSS_BE53_BE53

VSS_BG1_BG1

VSS_BG53_BG53

VSS_BH1_BH1

VSS_BH2_BH2

VSS_BH52_BH52

VSS_BH53_BH53

VSS_BJ2_BJ2

VSS_BJ3_BJ3

VSS_BJ5_BJ5

VSS_BJ49_BJ49

VSS_BJ51_BJ51

VSS_BJ52_BJ52

VSS_C1_C1

VSS_C53_C53

VSS_E1_E1

VSS_E53_E53

RESERVED_F1

PCIE_V1P0_S3_AK18

PCIE_V1P0_S3_AM18

3

AD36

AM32

AM30

AN32

AM27

U24

N18

P18

U38

AN24

V25

N22

AN27

AD16

AD18

V18

AA18

P22

N20

U25

AF33

AG33

AG35

U33

U35

V33

A3

A49

A5

A51

A52

A6

B2

B52

B53

BE1

BE53

BG1

BG53

BH1

BH2

BH52

BH53

BJ2

BJ3

BJ5

BJ49

BJ51

BJ52

C1

C53

E1

E53

F1

AK18

AM18

?

GND

UNCORE_V1P35_S0IX

UNCORE_V1P8_AN32_PWR

LPC_V3P3_PWR

V1P8_S5_PWR

PCU_V3P3_G3_PWR

UNCORE_V1P8_AN32_PWR

LPC_V3P3_PWR

PCU_V1P8_G3_V25

PCU_V3P3_G3_PWR

+VSDIO

VSS_AD18_AD16_PWR

USB_HSIC_V1P24_G3

V1P8_AA18_PEW

RTC_VCC_P22_PWR

V1P8_S5_PWR

CORE_V1P05

C263 1U/6.3V_4

C248 1U/6.3V_4

C260 1U/6.3V_4

C247 1U/6.3V_4

C268 1U/6.3V_4

C249 1U/6.3V_4

R395 *0_4_S

R114 *0_4_S

R555 *0_6_S

R554 *0_6

R407 *0_4_S

R121 *0_4_S

R464 *0_4_S

R453 *0_4_S

R110 *0_4_S

R400 *0_4_S

C270 1U/6.3V_4

C267 1u/6.3V_4

C264 1u/6.3V_4

C261 1u/6.3V_4

C265 0.47u/6.3V_4

C291 1U/6.3V_4

C304 1U/6.3V_4

2

GND

GND

PP1800_PCH

PP3300_PCH

PP1800_PCH_S5

PP1800_PCH

PP3300_PCH_S5

PP3300_PCH

GND

PP1800_PCH_S5

+3V_RTC

PP1800_PCH_S5

GND

GND

PP1000_PCH

GND

R460 *0_4_S

C346 1U/6.3V_4

PP1000_PCH_S5

GND

1

9

B B

A A

PP1350_PCH

GND

C296

1U/6.3V_4

PP1000_PCH

VIS_V1P0_S0IX_PW

22U/6.3V_8

GND

5

1031 remove C285

USB3_V1P0_G3 LPC_V3P3_PWR

C288

C303

1U/6.3V_4

C59

22U/6.3V_8

GND

C300

1U/6.3V_4 C307

0.01U/25V_4

C61

22U/6.3V_8

C301

1U/6.3V_4

C298

1U/6.3V_4

C276

1U/6.3V_4

C309

1U/6.3V_4

C277

1U/6.3V_4

GND

C323

1U/6.3V_4

C272

1U/6.3V_4

C292

0.01U/25V_4

C275

0.01U/25V_4

3

C337

C269

1U/6.3V_4 C332

1U/6.3V_4

V1P8_S5_PWR RTC_VCC_P22_PWR

GND

4

GND

C74

*1U/6.3V_4

V1P8_AA18_PEW

1U/6.3V_4

GND

VSS_AD18_AD16_PWR

GND

+VSDIO

C350

*1U/6.3V_4

PCU_V3P3_G3_PWR

C302

1U/6.3V_4

GND

UNCORE_V1P8_AN32_PWR

C283

1U/6.3V_4

GND

2

1U/6.3V_4

GND

C274

C282

1U/6.3V_4

1U/6.3V_4C62

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet

PROJECT :

Valley 8/9 (Power 2)

Valley 8/9 (Power 2)

Valley 8/9 (Power 2)

C252

1U/6.3V_4

1

GND

NL6

NL6

NL6

C293

1U/6.3V_4

of

C294

0.1U/10V_4

419

419

419

1A

1A

1A

Page 10

5

4

3

2

1

10

D D

?

U14I

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VLV_M_D/BGA

VLV_M_D

9 OF 13

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

AC36

AC38

AD19

AD21

AD25

AD32

AD33

AD47

AD7

AE1

AE11

AE12

AE14

AE3

AE4

AE40

AE42

AE43

AE45

AE46

AE48

AE50

AE51

AE53

AE6

AE8

AE9

AF10

AF12

AF25

AF32

AF47

AG16

AG25

AG36

?

AG38

AH41

AH45

AJ16

AJ21

AJ25

AJ27

AJ29

AJ30

AJ32

AJ33

AJ35

AJ38

AJ53

AK10

AK14

AK16

AK33

AK41

AK44

AM12

AM19

AM24

AM25

AM29

AM33

AM35

AM36

AM40

AH4

AH7

AH9

AJ1

AJ3

M28

REV = 1.15

A11

A15

A19

A23

A27

A31

A35

A39

A43

A47

AA1

AA16

AA19

AA21

AA3

AA32

AA35

AA38

AA53

AB10

AB4

AB41

AB45

AB47

C C

AB48

AB50

AB51

AC16

AC18

AC19

AC21

AC25

AC33

AC35

AB6

REV = 1.15

U14J

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VLV_M_D/BGA

?

VLV_M_D

10 OF 13

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

AH47

AH48

AH50

AH51

AH6

AM44

AM51

AM7

AN1

AN11

AN12

AN14

AN22

AN3

AN33

AN35

AN36

AN38

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN5

AN51

AN53

AN6

AN8

AN9

AP40

AT12

AT16

AT19

?

AT24

AT27

AT30

AT35

AT38

AT47

AT52

AU24

AU30

AU38

AU51

AV12

AV13

AV14

AV18

AV19

AV24

AV27

AV30

AV35

AV38

AV47

AV51

AW13

AW19

AW27

AW3

AW35

AY10

AY22

AY32

AT4

AU1

AU3

AV7

REV = 1.15

U14K

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VLV_M_D/BGA

?

VLV_M_D

11 OF 13

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

?

U14L

AY36

AY4

AY50

AY9

BA14

BA19

BA22

BA27

BA32

BA35

BA40

BA53

BB19

BB27

BB35

BC20

BC22

BC26

BC28

BC32

BC34

BC42

BD19

BD24

BD27

BD30

BD35

BE19

BE2

BE35

BE8

BF12

BF16

BF24

BF38

?

BF30

BF36

BG31

BG34

BG39

BG42

BG45

BG49

BJ11

BJ15

BJ19

BJ23

BJ27

BJ31

BJ35

BJ39

BJ43

BJ47

BF4

BJ7

C14

C31

C34

C39

C42

C45

C49

D12

D16

D24

D30

D36

D38

E19

E35

REV = 1.15

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VLV_M_D/BGA

VLV_M_D

12 OF 13

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

E8

F19

F2

F24

F27

F30

F35

F5

F7

G10

G20

G22

G26

G28

G32

G34

G42

H19

H27

H35

J1

J16

J19

J22

J27

J32

J35

J40

J53

K14

K22

K32

K36

K4

K50

?

K9

L13

L19

L27

L35

M19

M26

M27

M34

M35

M38

M47

M51

N1

N16

N38

N51

P13

P16

P19

P20

P24

P32

P35

P38

P4

P47

P52

P9

T40

U1

U11

U12

U14

U21

U14M

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS290

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS301

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS314

VSS315

VLV_M_D/BGA

REV = 1.15

?

VLV_M_D

13 OF 13

VSS316

VSS317

VSS318

VSS319

VSS320

VSS321

VSS322

VSS323

VSS324

VSS325

VSS326

VSS327

VSS328

VSS329

VSS330

VSS331

VSS332

VSS333

VSS334

VSS335

VSS336

VSS337

VSS338

VSS339

VSS340

VSS341

VSS342

VSS343

VSS344

VSS345

VSS346

VSS347

VSS348

VSS349

VSS350

U3

U30

U32

U40

U42

U43

U45

U46

U48

U49

U5

U51

U53

U6

U8

U9

V12

V16

V19

V21

V35

V40

V44

V51

V7

Y10

Y14

Y16

Y21

Y25

Y33

Y41

Y44

Y7

Y9

?

B B

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

Friday, April 25, 2014

Date: Sheet of

5

4

3

2

Friday, April 25, 2014

PROJECT :

Valley 9/9 (GND)

Valley 9/9 (GND)

Valley 9/9 (GND)

NL6

NL6

NL6

1A

1A

1A

4110

4110

1

4110

Page 11

5

INTEL Debug Port

D D

SOC_RSMRST#(6,14)

C199

*2N7002K

Q54

PCH_PWRBTN_L(14,27)

CORE_PWROK_R(6,27)

SMB_SOC_DATA(7)

SMB_SOC_CLK(7)

XDP_H_TCK(6)

SOC_RTEST# (6)

3

2

*2N7002K

Q55

1

PP1800_XDP_AB PP1800_XDP_CD

*0.1u/10V_4

C C

PP3300_PCH_S5

R528

100K_4

3

XDP_RTEST_L

B B

2

1

APS

CN14

A A

*ACES_88511-180N

1

APS1

1

2

PMC_SLP_S3#

2

3

3

4

4

5

5

6

6

7

7

8

8

9

ILB_RTC_RST#

9

10

10

11

12

13

14

15

16

17

18

PMC_PWRBTN#

PMC_RSTBTN#

5

11

12

13

14

15

16

17

18

R502 *0_6

R512 *0_4

R511 *0_4

R510 *0_4

R509 *0_4

R508 *0_4

XDP_H_PRDY#(6)

XDP_GPIO_DFX1(6)

XDP_GPIO_DFX2(6)

XDP_GPIO_DFX3(6)