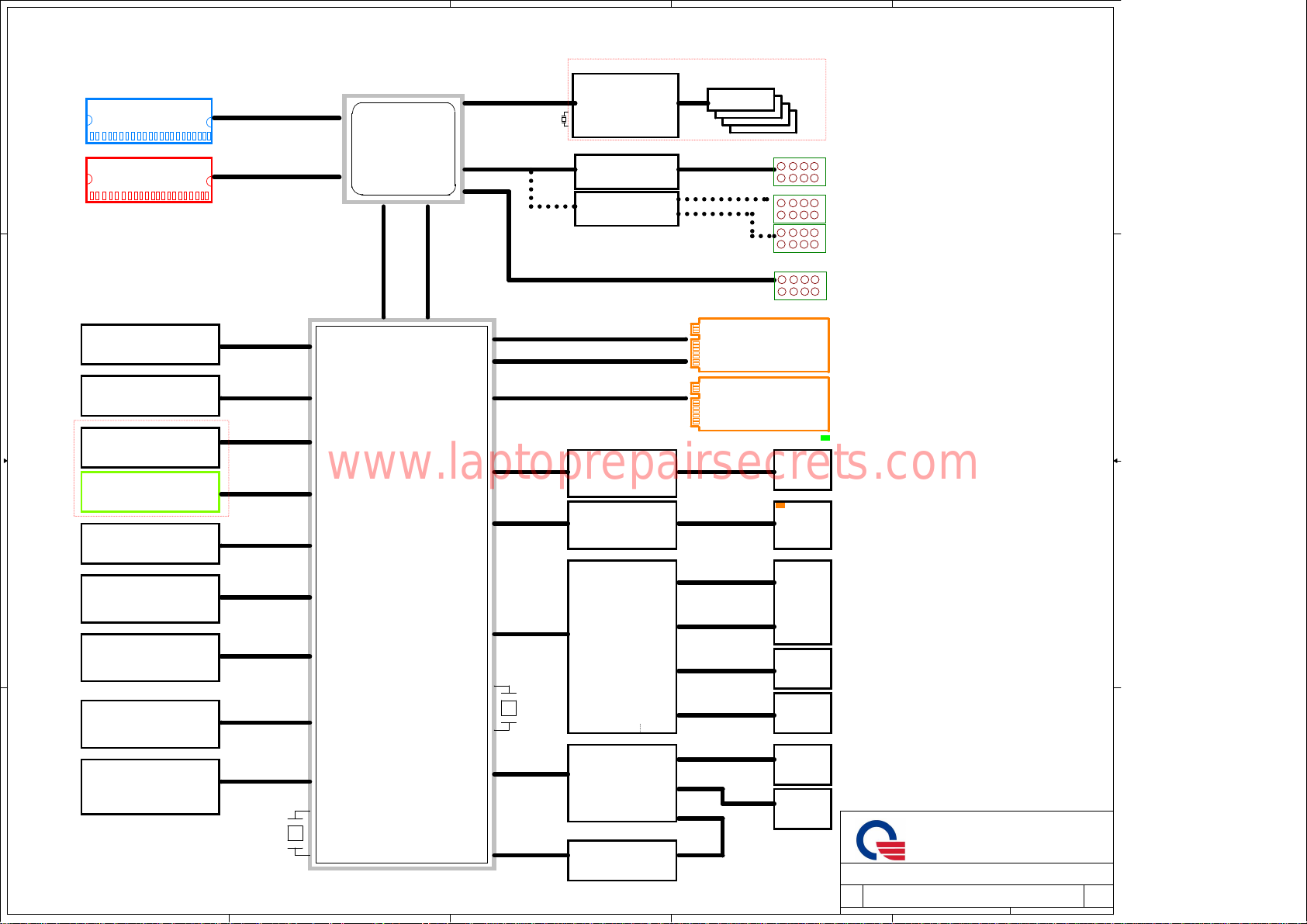

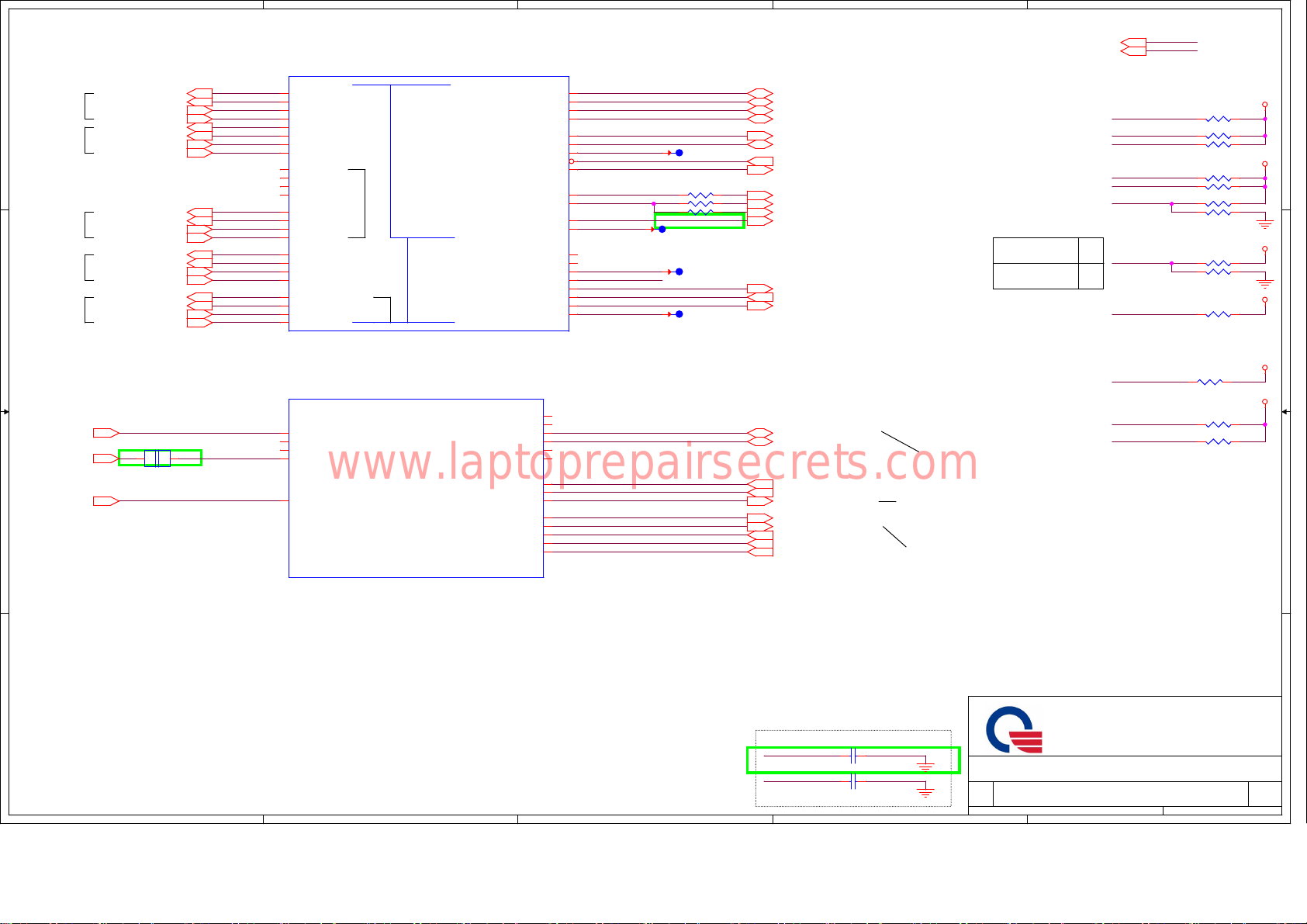

QUANTA N83 Schematics

5

www.laptoprepairsecrets.com

4

3

2

1

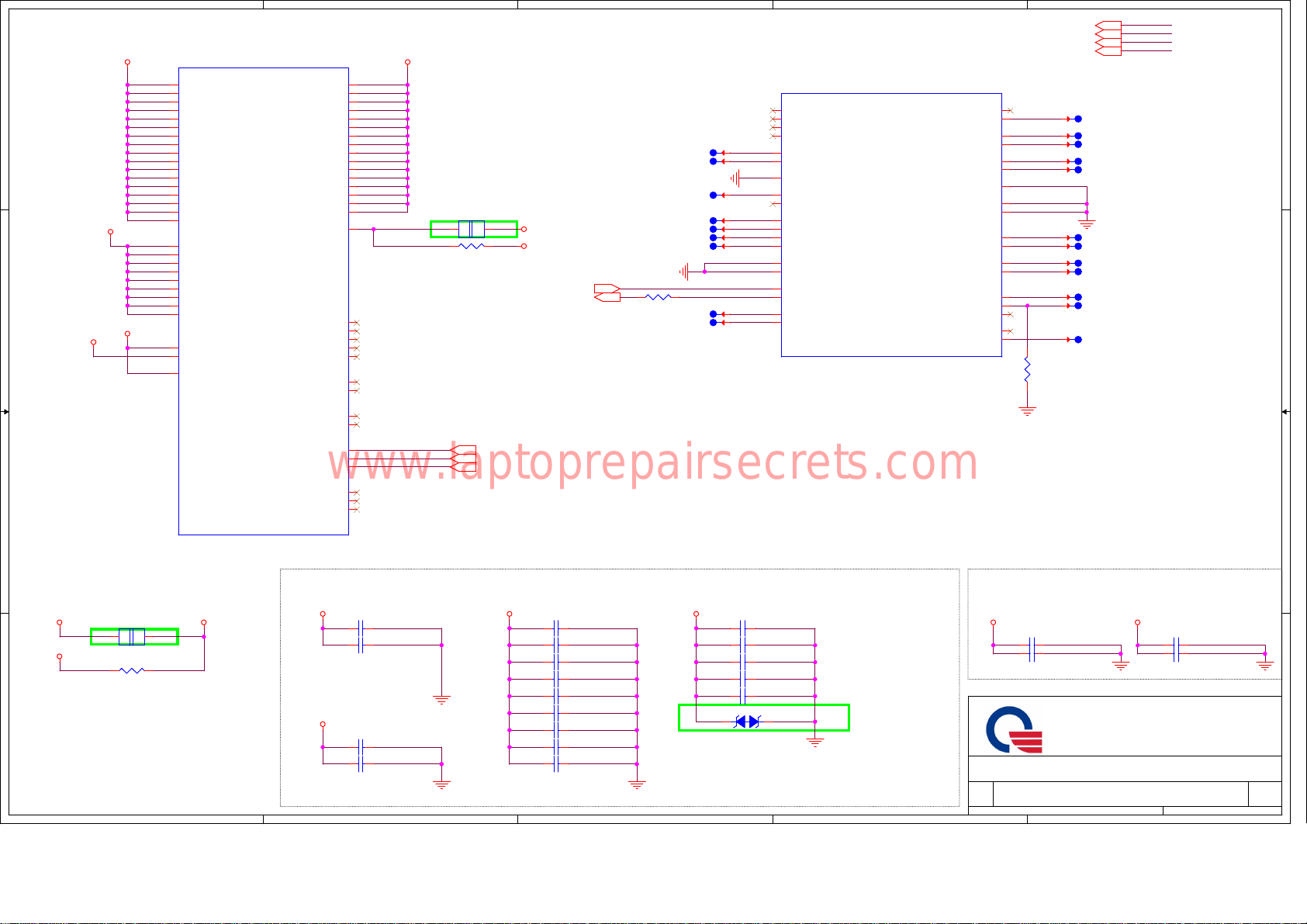

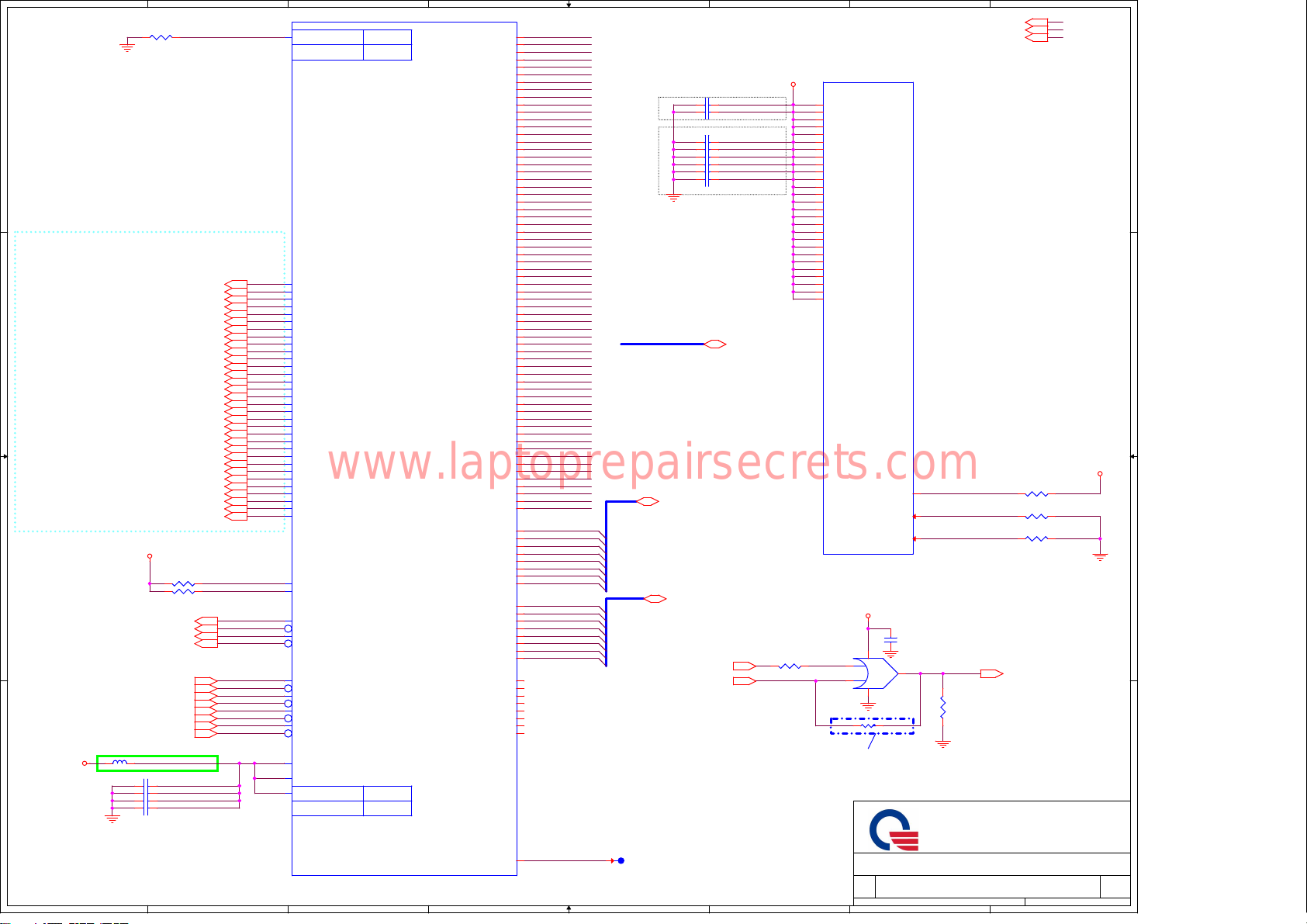

HP Saipan System Block Diagram

-G PCA Only

LGA1151 socket

DDR4-SODIMM CH. A

D D

Page14

DDR4 2133 MT/s

CPU

Skylake-S

DDR4-SODIMM CH. B

C C

3.5" SATA HDD

Page15

Page35

SATA ODD

Page35

IR/HD

WEBCAM

Falcon Cliffs CAM

10pin CONN

Touch Contl.

B B

Page31

Page31

Page31

USB 2.0 x2

( External)

Page32

USB 3.0 x2

( External)

(1 port with fast Charging)

Page32

USB3.0 TYPE-C

( External)

Page33

TPM

A A

Infineon

SLB9670

Page37

CONFIDENTIAL

5

DDR4 2133 MT/s

SATA Gen3

SATA Gen2

USB 2.0

USB 3.0

USB 2.0

USB 2.0

USB 3.0

USB 3.0 x2

SPI

25MHZ XTAL

Up to 35W

Page3~8

FDI

DMI

Skylake PCH-H

(100 Series)

4

Page10~13

PEGx8

eDP

HDMI

USB 2.0

PCIe

SATA

PCIe

PCIe

Azalia

32.768KHz

LPC

SPI

NV

N16S-GMR-AIO

27 MHz

Page16~20

eDP to LVDS

QHD Bridge

Card Reader

RTS5239-R

Gigabit LAN

RTL8161GSH

Audio Codec

Realtek

ALC3252

EC

IT8987E

SPI ROM

64Mbit

3

2GB VRAM x4

Page21

LVDS(2ch)

Page22

Page24

LVDS(2ch) CONN 30PIN

HDMI IN CONN 20PIN

M.2 Slot

WLAN+BT Combo

Page34

M.2 Slot

SSD SATA

Page29

Page28 Page28

Cabled

Cabled

Cabled

Page27

I2C

Page30

Page12

SPI

Page35

CR Slot

Page29

RJ45

Int Spkr

Page27

Combo

Jack

Page27

DMIC

Page27

Converter

Connector

Page52

FAN

Page36

2

Page23

Page25

Page26

HP Restricted Secret

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Project:

Project:

Title

Title

Title

System Block Diagram

System Block Diagram

System Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

--

--

--

Page Modified: Sheet of

Page Modified: Sheet of

Page Modified: Sheet of

Project:

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

01

161Thursday, December 17, 2015

161Thursday, December 17, 2015

161Thursday, December 17, 2015

A

A

A

5

WWW.AliSaler.Com

www.laptoprepairsecrets.com

4

3

2

1

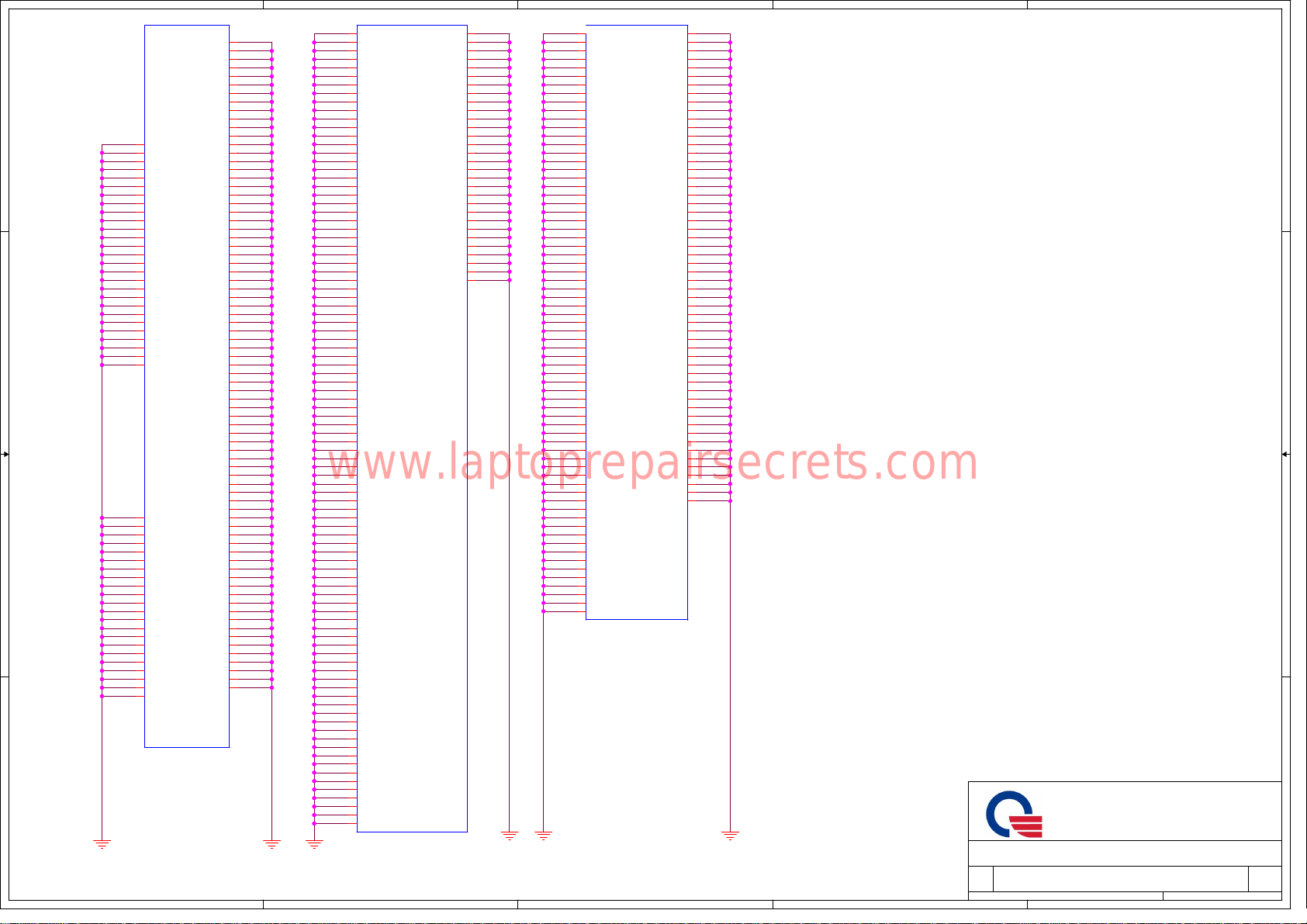

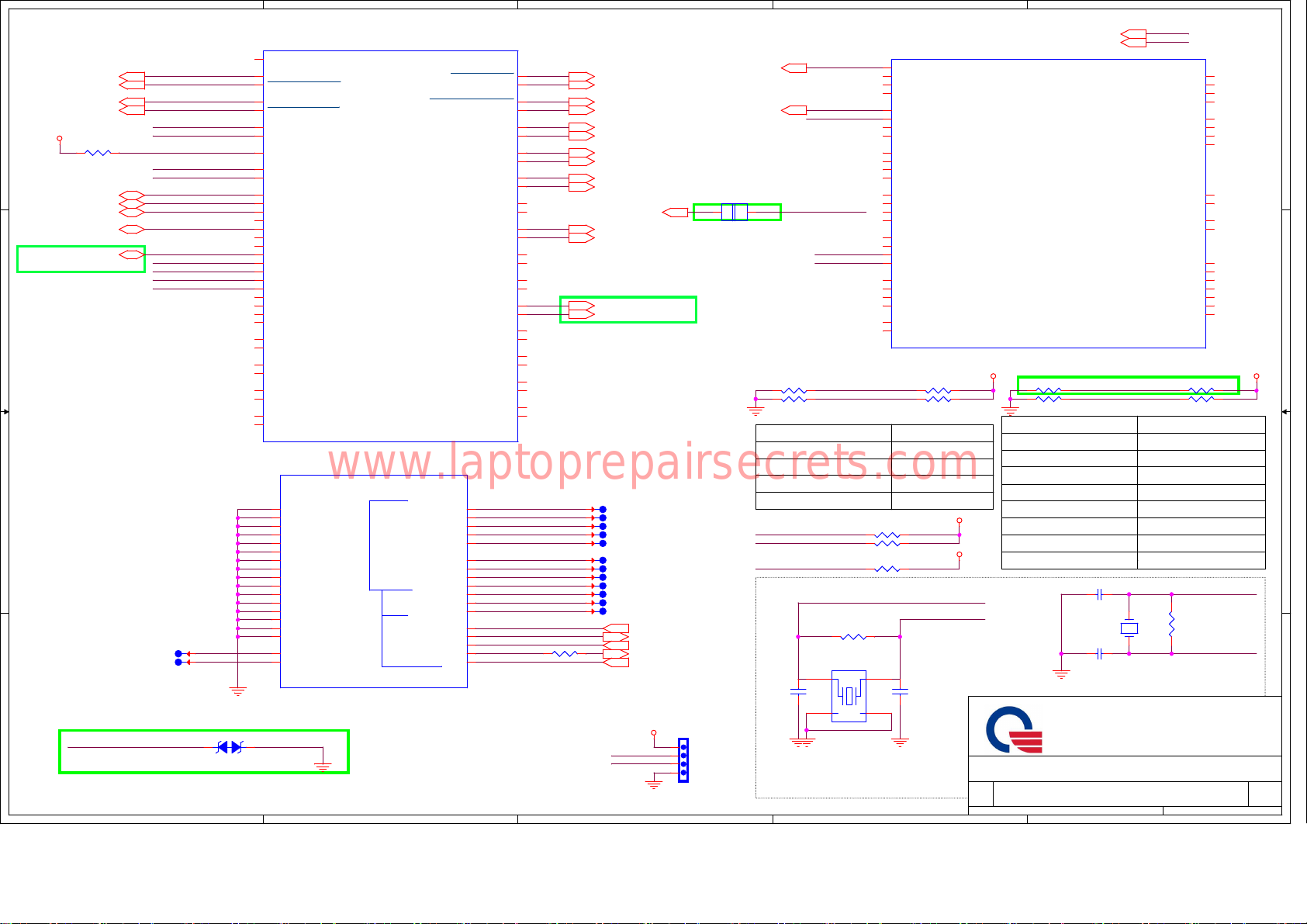

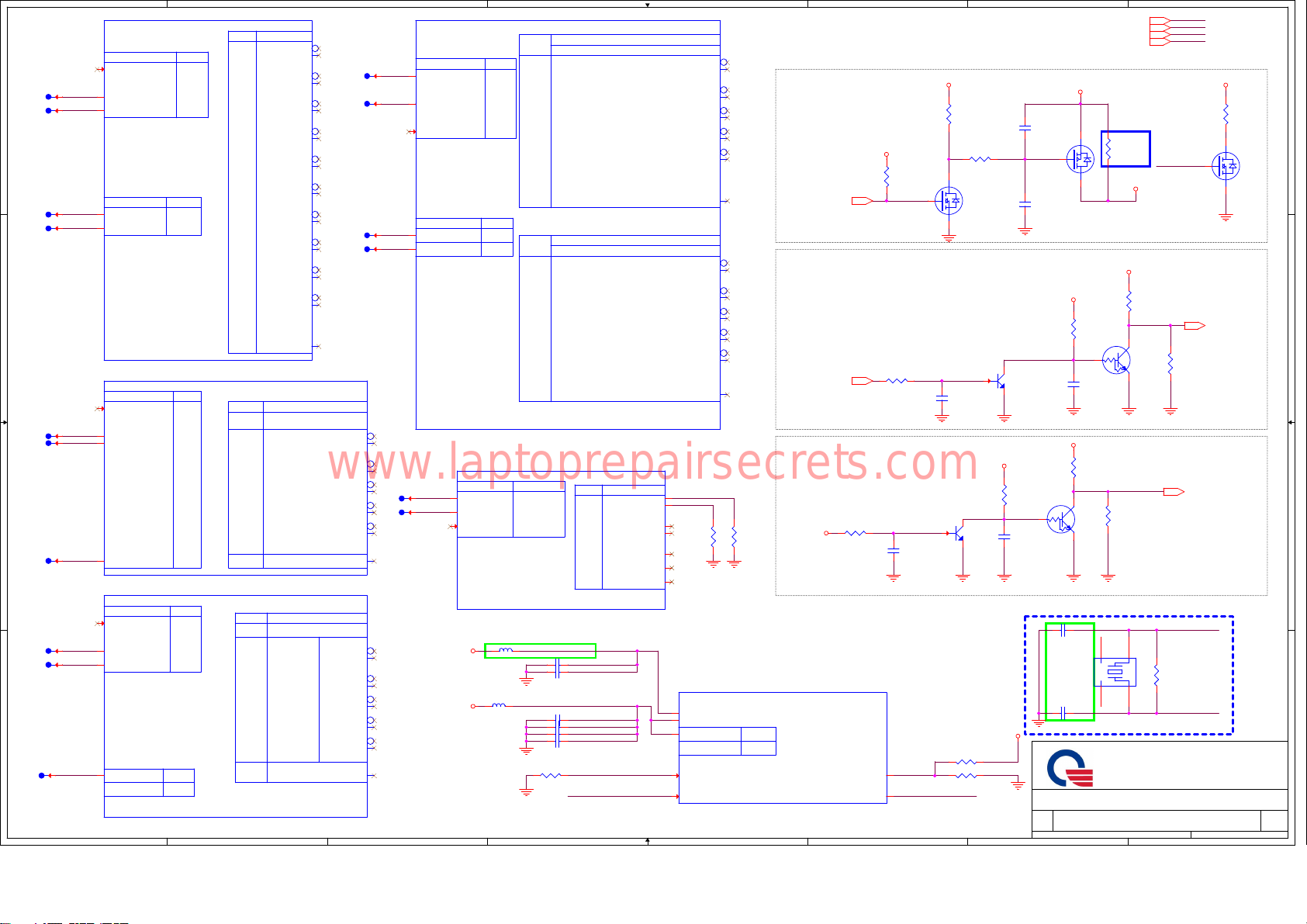

Voltage Rails

Voltage

+RTC_VCC 3V

+VIN

+5V_ALW

D D

+3V_AUX ON ON ON ON ON OFF LDO

+5V_S5

+3V_S5

+1.8V_S5

+1V_S5 1.0V

+VCCST_VCCPLL

+VDDQ

SMDDR_VTERM

+5V

+3V

+12V 12V MAIN_ON1

C C

+VCCGT

+3.3V_VGA 3.3V

+1.05V_VGA

+VGA_CORE

+VCCCORE

19V

5V

3.3V+3V_ALW

3.3V

3.3V

1.8V

1.0V

1.35V

0.75V

5V

3V

0.95V PG_MAINOFF+VCCIO

1.05V+VCCSA

0.65~1.3V

1.05V

0.8~1.15V

1.35V+1.35V_VGA

0.65~1.3V

ON ON ON ON ON ON

ON ON ON ON ON

ON ON ON ON ON

ON ON ON ON ON

ON ON ON ON OFF OFF

ON ON ON ON

ON ON ON ON

ON ON ON ON OFF OFF

OFF OFF OFFON OFFON S3_ON

ON

ON

OFF

ON OFFOFFOFFOFF OFF

ON OFFOFFOFF OFFOFF

ON OFF OFF OFF OFF

ON OFF OFF OFF OFFOFF

ON OFF OFF OFF OFFOFF

ON OFF OFF OFF OFFOFF

ON OFF OFF OFF OFF OFF

ON OFF OFF OFF OFF OFF

ON OFF OFF OFF OFF OFF

ON OFF OFF OFF OFF OFF

OFF OFF OFFON OFF

OFF OFF OFFON OFF

OFF OFF OFFON OFF MAIN_ON1

PCUPower Rail S0 Ctl SignalS3 S4 S5

OFF

OFF

G3

ON

ON

ON

OFF

OFF

Adapter in

Int. LDO

Int. LDO

S5_ON5V

S5_ON

S5_ON

PG_+1.8V_S5

S3_ON

DDR_VTT_CNTL

MAIN_ON1

PG_+VCCIO

VR_ON

EN_+3.3V_VGA

PG_+3.3V_MAIN

PG_+3.3V_MAIN

EN_+1.35V_VGA

VR_ON

02

RTC Batt, PCH , EC

LED

EC

System

PCH, USB, 3D WebCAM, Touch Panel, USB Charger

PCH, XDP, SPI flash ROM,NGFF LAN

PCH, XDP, NGFF LAN

PCH

CPU, PCH, XDP

DDR4, CPU DDR4 I/O

DDR4

HDD, O DD,Audio AMP,P anel VCC,F AN

PCH, Audio, Card Reader, TPM, FHD CAM

3.5" HDD

CPU

CPU

CPU

dGPU

dCPU

dGPU

dGPU, VRAM

CPU

Schematic “Value” Definition

Intel Platform Saipan-G and Saipan-U

B B

By Value

format

XX

*XX

PROTO@XX

MP@XX

DIS@xx

UMA@xx Install UMA

A A

QHD@xx QHD panel

FHD@xx FHD panel

Description Auto BOM

Control

Install

Non-Install

Install in

Pre-production only

Install in MP only

Install Discrete

(DGPU) only

V

V

V

V

V

V

VVV

VVV

DB/SI/PV Stage

UMA

Discrete

N16S GPU

VV

VV

V

V

UMA

VV

VV

V

VV

VV

MP

Discrete

N16S GPU

V

***Board ID and VRAM ID by manual control

5

4

3

ALL STAGE

QHD

PANEL

V

FHD

PANEL

HP Restricted Secret

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

V

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Page Modified: Sheet of

Page Modified: Sheet of

Page Modified: Sheet of

Project:

Project:

Project:

Power States & Value Definition

Power States & Value Definition

Power States & Value Definition

--

--

--

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

A

A

A

261Thursday, December 17, 2015

261Thursday, December 17, 2015

261Thursday, December 17, 2015

5

www.laptoprepairsecrets.com

4

3

2

1

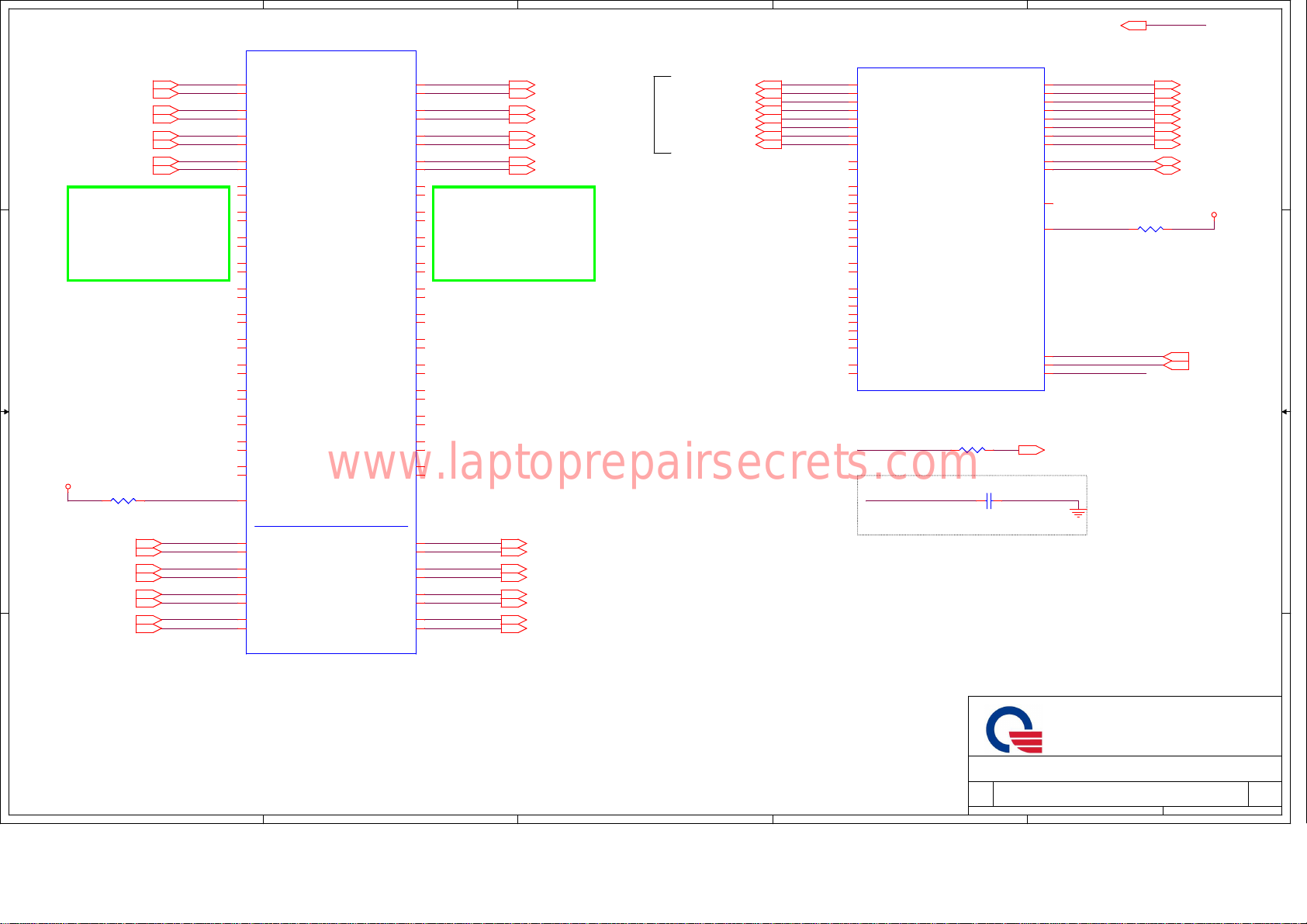

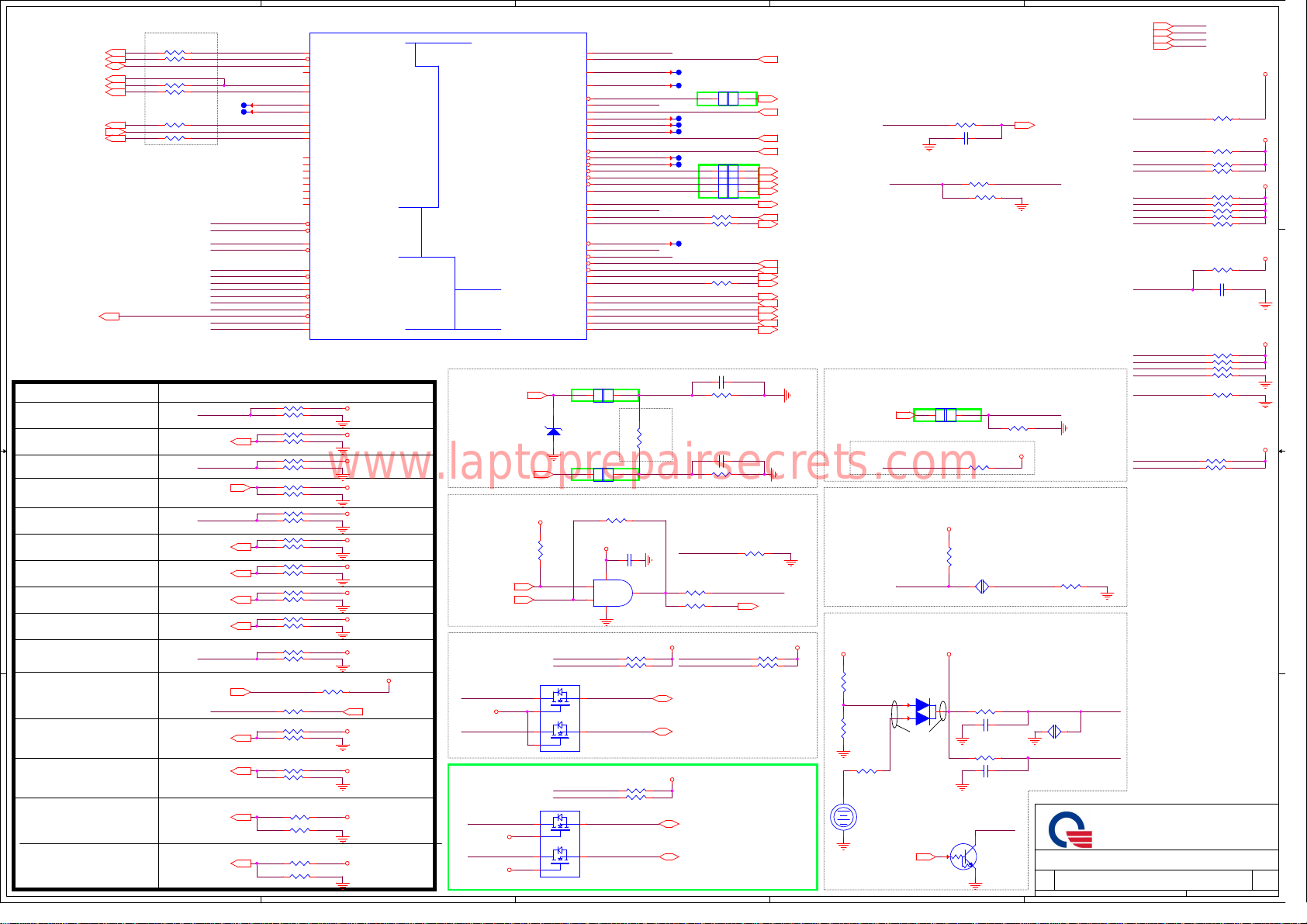

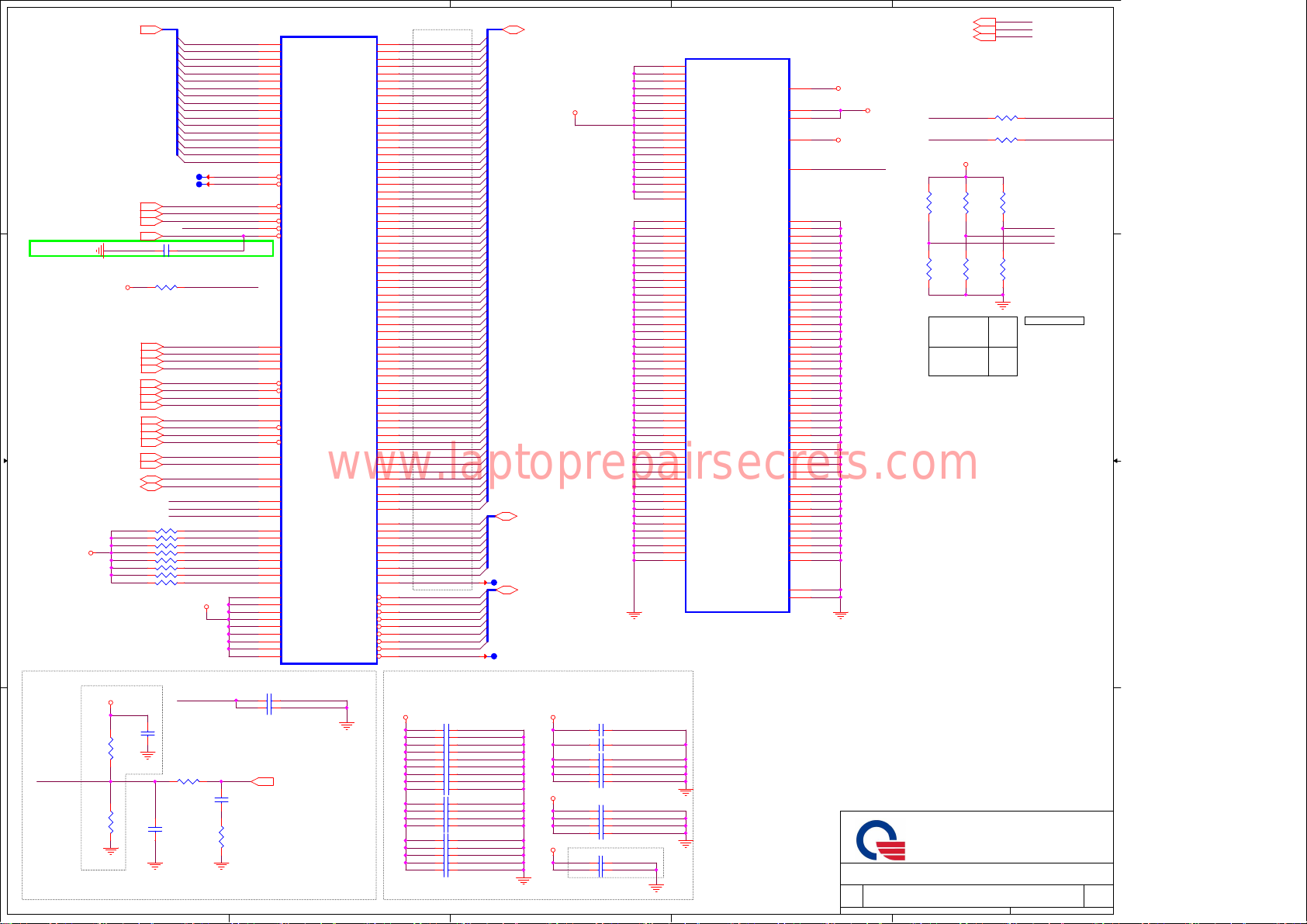

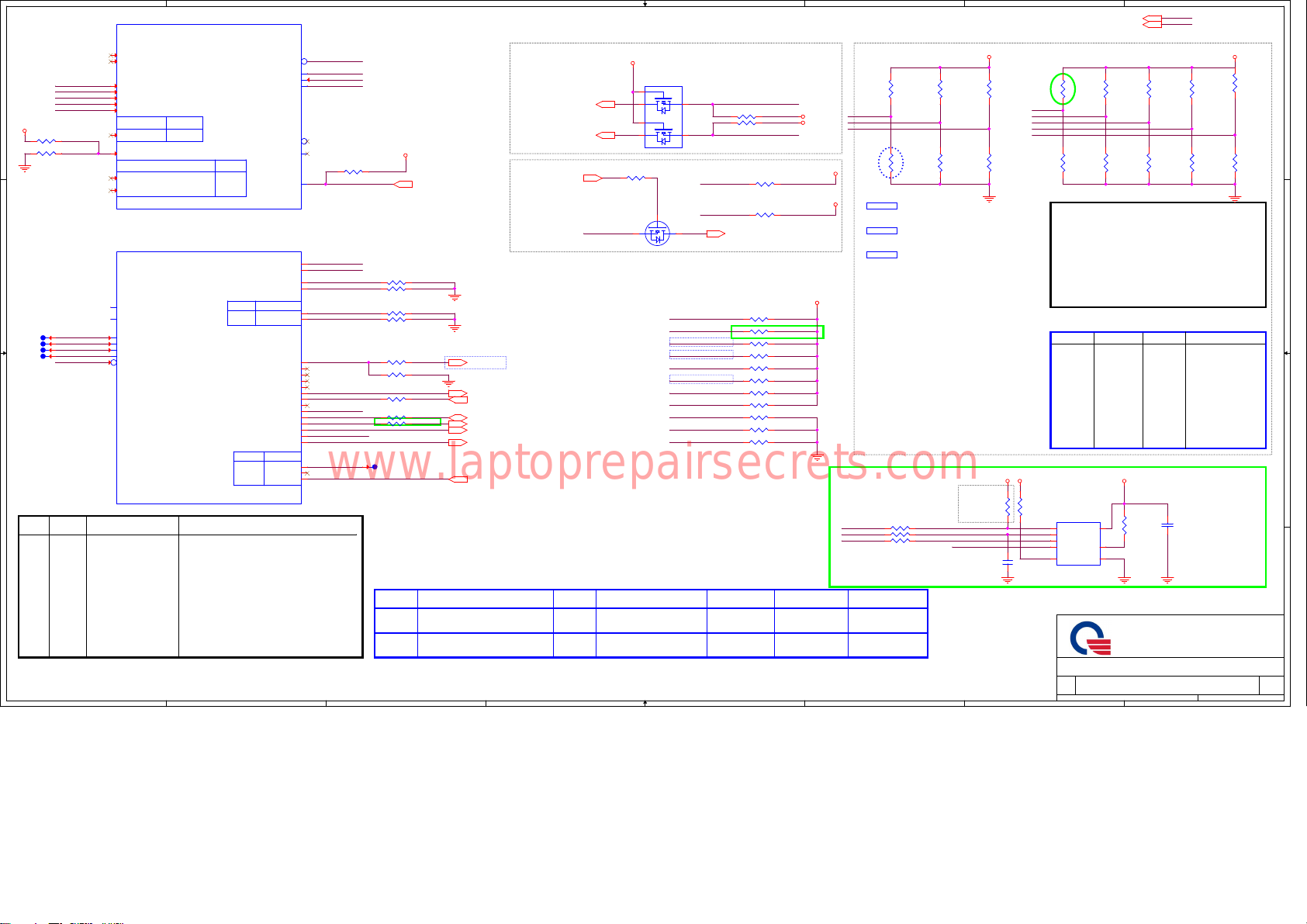

?

M_A_DQ[63:0](14)

D D

C C

B B

A A

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

5

J1A

AE38

DDR0_DQ[0]

AE37

DDR0_DQ[1]

AG38

DDR0_DQ[2]

AG37

DDR0_DQ[3]

AE39

DDR0_DQ[4]

AE40

DDR0_DQ[5]

AG39

DDR0_DQ[6]

AG40

DDR0_DQ[7]

AJ38

DDR0_DQ[8]

AJ37

DDR0_DQ[9]

AL38

DDR0_DQ[10]

AL37

DDR0_DQ[11]

AJ40

DDR0_DQ[12]

AJ39

DDR0_DQ[13]

AL39

DDR0_DQ[14]

AL40

DDR0_DQ[15]

AN38

DDR0_DQ[16]/DDR0_DQ[32]

AN40

DDR0_DQ[17]/DDR0_DQ[33]

AR38

DDR0_DQ[18]/DDR0_DQ[34]

AR37

DDR0_DQ[19]/DDR0_DQ[35]

AN39

DDR0_DQ[20]/DDR0_DQ[36]

AN37

DDR0_DQ[21]/DDR0_DQ[37]

AR39

DDR0_DQ[22]/DDR0_DQ[38]

AR40

DDR0_DQ[23]/DDR0_DQ[39]

AW37

DDR0_DQ[24]/DDR0_DQ[40]

AU38

DDR0_DQ[25]/DDR0_DQ[41]

AV35

DDR0_DQ[26]/DDR0_DQ[42]

AW35

DDR0_DQ[27]/DDR0_DQ[43]

AU37

DDR0_DQ[28]/DDR0_DQ[44]

AV37

DDR0_DQ[29]/DDR0_DQ[45]

AT35

DDR0_DQ[30]/DDR0_DQ[46]

AU35

DDR0_DQ[31]/DDR0_DQ[47]

AY8

DDR0_DQ[32]/DDR1_DQ[0]

AW8

DDR0_DQ[33]/DDR1_DQ[1]

AV6

DDR0_DQ[34]/DDR1_DQ[2]

AU6

DDR0_DQ[35]/DDR1_DQ[3]

AU8

DDR0_DQ[36]/DDR1_DQ[4]

AV8

DDR0_DQ[37]/DDR1_DQ[5]

AW6

DDR0_DQ[38]/DDR1_DQ[6]

AY6

DDR0_DQ[39]/DDR1_DQ[7]

AY4

DDR0_DQ[40]/DDR1_DQ[8]

AV4

DDR0_DQ[41]/DDR1_DQ[9]

AT1

DDR0_DQ[42]/DDR1_DQ[10]

AT2

DDR0_DQ[43]/DDR1_DQ[11]

AV3

DDR0_DQ[44]/DDR1_DQ[12]

AW4

DDR0_DQ[45]/DDR1_DQ[13]

AT4

DDR0_DQ[46]/DDR1_DQ[14]

AT3

DDR0_DQ[47]/DDR1_DQ[15]

AP2

DDR0_DQ[48]/DDR1_DQ[32]

AM4

DDR0_DQ[49]/DDR1_DQ[33]

AP3

DDR0_DQ[50]/DDR1_DQ[34]

AM3

DDR0_DQ[51]/DDR1_DQ[35]

AP4

DDR0_DQ[52]/DDR1_DQ[36]

AM2

DDR0_DQ[53]/DDR1_DQ[37]

AP1

DDR0_DQ[54]/DDR1_DQ[38]

AM1

DDR0_DQ[55]/DDR1_DQ[39]

AK3

DDR0_DQ[56]/DDR1_DQ[40]

AH1

DDR0_DQ[57]/DDR1_DQ[41]

AK4

DDR0_DQ[58]/DDR1_DQ[42]

AH2

DDR0_DQ[59]/DDR1_DQ[43]

AH4

DDR0_DQ[60]/DDR1_DQ[44]

AK2

DDR0_DQ[61]/DDR1_DQ[45]

AH3

DDR0_DQ[62]/DDR1_DQ[46]

AK1

DDR0_DQ[63]/DDR1_DQ[47]

AU33

DDR0_ECC[0]

AT33

DDR0_ECC[1]

AW33

DDR0_ECC[2]

AV31

DDR0_ECC[3]

AU31

DDR0_ECC[4]

AV33

DDR0_ECC[5]

AW31

DDR0_ECC[6]

AY31

DDR0_ECC[7]

DDR CHANNEL A

SKL_S_CPU_LGA

SKL_S_CPU

LGA1151

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

1 OF 12

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKP[1]

DDR0_CKN[1]

DDR0_CKP[2]

DDR0_CKN[2]

DDR0_CKP[3]

DDR0_CKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

4

AW18

AV18

AW17

AY17

AW16

AV16

AT16

AU16

AY24

AW24

AV24

AV25

AW12

AU11

AV13

AV10

AW11

AU14

AU12

AY10

AY13

M_A_BA#0

AV15

M_A_BA#1

AW23

M_A_BG#0

AW13

M_A_A16

AV14

M_A_A14

AY11

M_A_A15

AW15

M_A_A0

AU18

M_A_A1

AU17

M_A_A2

AV19

M_A_A3

AT19

M_A_A4

AU20

M_A_A5

AV20

M_A_A6

AU21

M_A_A7

AT20

M_A_A8

AT22

M_A_A9

AY14

M_A_A10

AU22

M_A_A11

AV22

M_A_A12

AV12

M_A_A13

AV23

AU24

AY15

AT23

AF39

M_A_DQSN0

AK39

M_A_DQSN1

AP39

M_A_DQSN2

AU36

M_A_DQSN3

AW7

M_A_DQSN4

AU3

M_A_DQSN5

AN3

M_A_DQSN6

AJ3

M_A_DQSN7

AF38

M_A_DQSP0

AK38

M_A_DQSP1

AP38

M_A_DQSP2

AV36

M_A_DQSP3

AV7

M_A_DQSP4

AU2

M_A_DQSP5

AN2

M_A_DQSP6

AJ2

M_A_DQSP7

AV32

M_A_DQSP8

AU32

M_A_DQSN8

DDR4 SO-DIMM FOR DQS[7:0] ONLY

?REV = 1.2

M_A_CLKP0 (14)

M_A_CLKN0 (14)

M_A_CLKP1 (14)

M_A_CLKN1 (14)

M_A_CKE0

M_A_CKE1

M_A_CS#0 (14)

M_A_CS#1 (14)

M_A_ODT0 (14)

M_A_ODT1 (14)

M_A_BA#[1..0] (14)

M_A_BG#0 (14)

M_A_A[16:0] (14)

M_A_BG#1 (14)

M_A_ACT# (14)

M_A_PARITY (14)

M_A_ALERT# (14)

M_A_DQSN[7:0] (14)

M_A_DQSP[7:0] (14)

TP7

TP8 TP72

M_B_DQ[63:0](15)

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

(14)

(14)

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

J1B

AD34

DDR1_DQ[0]/DDR0_DQ[16]

AD35

DDR1_DQ[1]/DDR0_DQ[17]

AG35

DDR1_DQ[2]/DDR0_DQ[18]

AH35

DDR1_DQ[3]/DDR0_DQ[19]

AE35

DDR1_DQ[4]/DDR0_DQ[20]

AE34

DDR1_DQ[5]/DDR0_DQ[21]

AG34

DDR1_DQ[6]/DDR0_DQ[22]

AH34

DDR1_DQ[7]/DDR0_DQ[23]

AK35

DDR1_DQ[8]/DDR0_DQ[24]

AL35

DDR1_DQ[9]/DDR0_DQ[25]

AK32

DDR1_DQ[10]/DDR0_DQ[26]

AL32

DDR1_DQ[11]/DDR0_DQ[27]

AK34

DDR1_DQ[12]/DDR0_DQ[28]

AL34

DDR1_DQ[13]/DDR0_DQ[29]

AK31

DDR1_DQ[14]/DDR0_DQ[30]

AL31

DDR1_DQ[15]/DDR0_DQ[31]

AP35

DDR1_DQ[16]/DDR0_DQ[48]

AN35

DDR1_DQ[17]/DDR0_DQ[49]

AN32

DDR1_DQ[18]/DDR0_DQ[50]

AP32

DDR1_DQ[19]/DDR0_DQ[51]

AN34

DDR1_DQ[20]/DDR0_DQ[52]

AP34

DDR1_DQ[21]/DDR0_DQ[53]

AN31

DDR1_DQ[22]/DDR0_DQ[54]

AP31

DDR1_DQ[23]/DDR0_DQ[55]

AL29

DDR1_DQ[24]/DDR0_DQ[56]

AM29

DDR1_DQ[25]/DDR0_DQ[57]

AP29

DDR1_DQ[26]/DDR0_DQ[58]

AR29

DDR1_DQ[27]/DDR0_DQ[59]

AM28

DDR1_DQ[28]/DDR0_DQ[60]

AL28

DDR1_DQ[29]/DDR0_DQ[61]

AR28

DDR1_DQ[30]/DDR0_DQ[62]

AP28

DDR1_DQ[31]/DDR0_DQ[63]

AR12

DDR1_DQ[32]/DDR1_DQ[16]

AP12

DDR1_DQ[33]/DDR1_DQ[17]

AM13

DDR1_DQ[34]/DDR1_DQ[18]

AL13

DDR1_DQ[35]/DDR1_DQ[19]

AR13

DDR1_DQ[36]/DDR1_DQ[20]

AP13

DDR1_DQ[37]/DDR1_DQ[21]

AM12

DDR1_DQ[38]/DDR1_DQ[22]

AL12

DDR1_DQ[39]/DDR1_DQ[23]

AP10

DDR1_DQ[40]/DDR1_DQ[24]

AR10

DDR1_DQ[41]/DDR1_DQ[25]

AR7

DDR1_DQ[42]/DDR1_DQ[26]

AP7

DDR1_DQ[43]/DDR1_DQ[27]

AR9

DDR1_DQ[44]/DDR1_DQ[28]

AP9

DDR1_DQ[45]/DDR1_DQ[29]

AR6

DDR1_DQ[46]/DDR1_DQ[30]

AP6

DDR1_DQ[47]/DDR1_DQ[31]

AM10

DDR1_DQ[48]

AL10

DDR1_DQ[49]

AM7

DDR1_DQ[50]

AL7

DDR1_DQ[51]

AM9

DDR1_DQ[52]

AL9

DDR1_DQ[53]

AM6

DDR1_DQ[54]

AL6

DDR1_DQ[55]

AJ6

DDR1_DQ[56]

AJ7

DDR1_DQ[57]

AE6

DDR1_DQ[58]

AF7

DDR1_DQ[59]

AH7

DDR1_DQ[60]

AH6

DDR1_DQ[61]

AE7

DDR1_DQ[62]

AF6

DDR1_DQ[63]

AR25

DDR1_ECC[0]

AR26

DDR1_ECC[1]

AM26

DDR1_ECC[2]

AM25

DDR1_ECC[3]

AP26

DDR1_ECC[4]

AP25

DDR1_ECC[5]

AL25

DDR1_ECC[6]

AL26

DDR1_ECC[7]

SKL_S_CPU_LGA

DDR CHANNEL B

?

SKL_S_CPU

LGA1151

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

2 OF 12

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKP[1]

DDR1_CKN[1]

DDR1_CKP[2]

DDR1_CKN[2]

DDR1_CKP[3]

DDR1_CKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

REV = 1.2

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AY29

AV29

AW29

AU29

AP17

AN15

AN17

AM15

AM16

AL16

AP15

AL15

AN18

M_B_A16

AL17

M_B_A14

AP16

M_B_A15

AL18

M_B_BA#0

AM18

M_B_BA#1

AW28

M_B_BG#0

AL19

M_B_A0

AL22

M_B_A1

AM22

M_B_A2

AM23

M_B_A3

AP23

M_B_A4

AL23

M_B_A5

AW26

M_B_A6

AY26

M_B_A7

AU26

M_B_A8

AW27

M_B_A9

AP18

M_B_A10

AU27

M_B_A11

AV27

M_B_A12

AR15

M_B_A13

AY28

AU28

AL20

AY25

AF34

M_B_DQSN0

AK33

M_B_DQSN1

AN33

M_B_DQSN2

AN29

M_B_DQSN3

AN13

M_B_DQSN4

AR8

M_B_DQSN5

AM8

M_B_DQSN6

AG6

M_B_DQSN7

AF35

M_B_DQSP0

AL33

M_B_DQSP1

AP33

M_B_DQSP2

AN28

M_B_DQSP3

AN12

M_B_DQSP4

AP8

M_B_DQSP5

AL8

M_B_DQSP6

AG7

M_B_DQSP7

AN25

M_B_DQSP8

AN26

M_B_DQSN8

DDR4 SO-DIMM FOR DQS[7:0] ONLY

AB40

AC40

DIMM_DQ_CPU_VREF_A

AC39

?

TP71

HP Restricted Secret

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Project:

Project:

Title

Title

Title

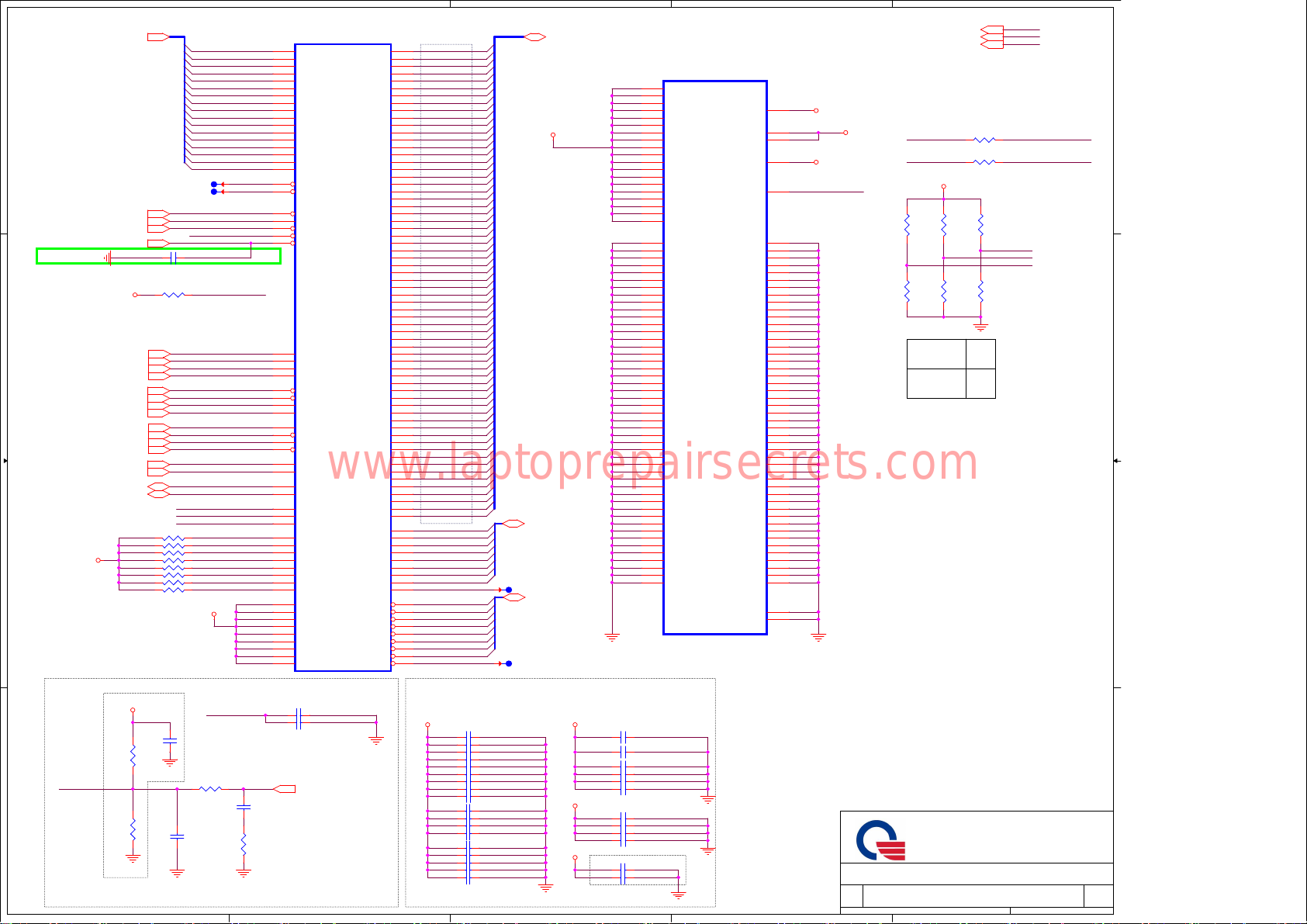

CPU_PEG/DISPLAY

CPU_PEG/DISPLAY

CPU_PEG/DISPLAY

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

--

--

--

Page Modified: Sheet of

Page Modified: Sheet of

3

2

Page Modified: Sheet of

Project:

DIMM_CA_CPU_VREF_A (14)

TP68

DIMM_DQ_CPU_VREF_B (15)

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

03

M_B_CLKP0 (15)

M_B_CLKN0 (15)

M_B_CLKP1 (15)

M_B_CLKN1 (15)

M_B_CKE0 (15)

M_B_CKE1 (15)

M_B_CS#0 (15)

M_B_CS#1 (15)

M_B_ODT0 (15)

M_B_ODT1 (15)

M_B_A[16:14](15)

M_B_BA#[1..0] (15)

M_B_BG#0 (15)

M_B_A[13:0] (15)

M_B_BG#1 (15)

M_B_ACT# (15)

M_B_PARITY (15)

M_B_ALERT# (15)

M_B_DQSN[7:0] (15)

M_B_DQSP[7:0] (15)

361Thursday, December 1 7, 2015

361Thursday, December 1 7, 2015

361Thursday, December 1 7, 2015

A

A

A

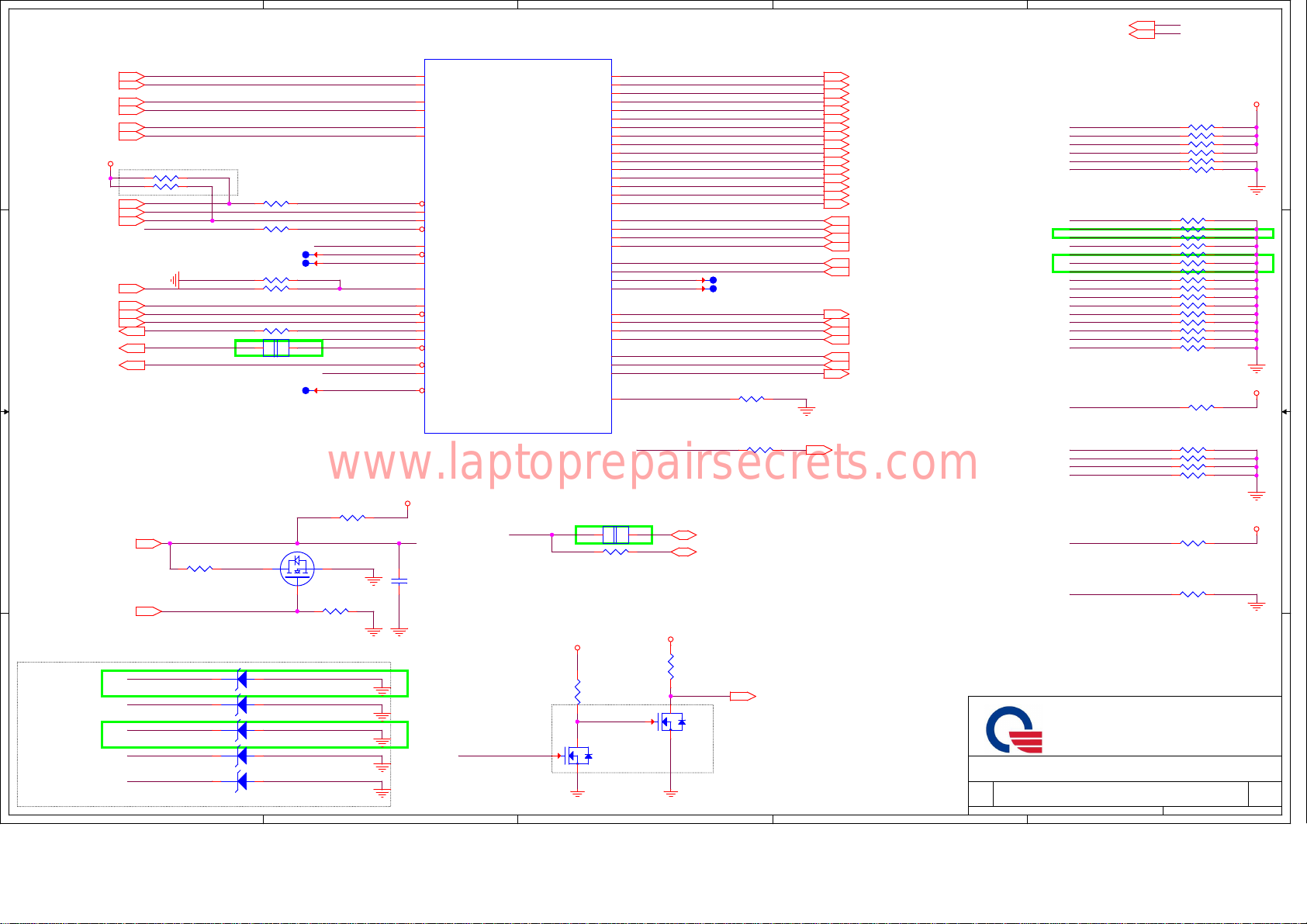

5

www.laptoprepairsecrets.com

J1C

PEG_RXP0(16)

PEG_RXN0(16)

D D

PEG_RXP1(16)

PEG_RXN1(16)

PEG_RXP2(16)

PEG_RXN2(16)

PEG_RXP3(16)

PEG_RXN3(16)

EC-DB-E02 EC-DB-E02

C C

PEG_RCOMP

Trace length < 400 mils

Trace w idth = 12 mils

Trace spacing = 15 mils

+VCCIO

R57 24.9/F_4

B B

PLACE INSIDE CPU CAVITY

DMI_PCH_CPU_RXP0(10)

DMI_PCH_CPU_RXN0(10)

DMI_PCH_CPU_RXP1(10)

DMI_PCH_CPU_RXN1(10)

DMI_PCH_CPU_RXP2(10)

DMI_PCH_CPU_RXN2(10)

DMI_PCH_CPU_RXP3(10)

DMI_PCH_CPU_RXN3(10)

PEG_RCOMP

B8

PEG_RXP[0]

B7

PEG_RXN[0]

C7

PEG_RXP[1]

C6

PEG_RXN[1]

D6

PEG_RXP[2]

D5

PEG_RXN[2]

E5

PEG_RXP[3]

E4

PEG_RXN[3]

F6

PEG_RXP[4]

F5

PEG_RXN[4]

G5

PEG_RXP[5]

G4

PEG_RXN[5]

H6

PEG_RXP[6]

H5

PEG_RXN[6]

J5

PEG_RXP[7]

J4

PEG_RXN[7]

K6

PEG_RXP[8]

K5

PEG_RXN[8]

L5

PEG_RXP[9]

L4

PEG_RXN[9]

M6

PEG_RXP[10]

M5

PEG_RXN[10]

N5

PEG_RXP[11]

N4

PEG_RXN[11]

P6

PEG_RXP[12]

P5

PEG_RXN[12]

R5

PEG_RXP[13]

R4

PEG_RXN[13]

T6

PEG_RXP[14]

T5

PEG_RXN[14]

U5

PEG_RXP[15]

U4

PEG_RXN[15]

L7

PEG_RCOMP

Y3

DMI_RXP[0]

Y4

DMI_RXN[0]

AA4

DMI_RXP[1]

AA5

DMI_RXN[1]

AB4

DMI_RXP[2]

AB3

DMI_RXN[2]

AC4

DMI_RXP[3]

AC5

DMI_RXN[3]

SKL_S_CPU_LGA

SKL_S_CPU

LGA1151

3 OF 12

4

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

REV = 1.2

3

?

A5

A6

B4

B5

C3

C4

D2

D3

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

L1

L2

M2

M3

N1

N2

P2

P3

R2

R1

T2

T3

AC2

AC1

AD3

AD2

AE2

AE1

AF2

AF3

?

PEG_TXP0 (16)

PEG_TXN0 (16)

PEG_TXP1 (16)

PEG_TXN1 (16)

PEG_TXP2 (16)

PEG_TXN2 (16)

PEG_TXP3 (16)

PEG_TXN3 (16)

DMI_CPU_PCH_TXP0 (10)

DMI_CPU_PCH_TXN0 (10)

DMI_CPU_PCH_TXP1 (10)

DMI_CPU_PCH_TXN1 (10)

DMI_CPU_PCH_TXP2 (10)

DMI_CPU_PCH_TXN2 (10)

DMI_CPU_PCH_TXP3 (10)

DMI_CPU_PCH_TXN3 (10)

HDMI

HDMI_TX2P(26)

HDMI_TX2N(26)

HDMI_TX1P(26)

HDMI_TX1N(26)

HDMI_TX0P(26)

HDMI_TX0N(26)

HDMI_CLKP(26)

HDMI_CLKN(26)

C21

D21

D22

E22

B23

A23

C23

D23

B13

C13

B18

A18

D18

E18

C19

D19

D20

E20

A12

B12

B14

A14

C15

B15

B16

A16

C17

B17

B11

C11

2

J1D

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI1_AUXP

DDI1_AUXN

DDI2_TXP[0]

DDI2_TXN[0]

DDI2_TXP[1]

DDI2_TXN[1]

DDI2_TXP[2]

DDI2_TXN[2]

DDI2_TXP[3]

DDI2_TXN[3]

DDI2_AUXP

DDI2_AUXN

DDI3_TXP[0]

DDI3_TXN[0]

DDI3_TXP[1]

DDI3_TXN[1]

DDI3_TXP[2]

DDI3_TXN[2]

DDI3_TXP[3]

DDI3_TXN[3]

DDI3_AUXP

DDI3_AUXN

SKL_S_CPU_LGA

AUD_CPU_SDI_R

EMI reserved

AUD_CPU_BCLK

?

SKL_S_CPU

LGA1151

4 OF 12

R121 20/1%_4

C96 *10p/50V/NPO_4

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

+VCCIO(7,38,42,47)

E10

D10

D9

C9

H10

G10

G9

F9

D12

E12

D14

M9

EDP_COMP

V3

AUD_CPU_BCLK

V2

U1

AUD_CPU_SDI_R

?REV = 1.2

AUD_CPU_SDI (9 )

1

04

DDID_TXDP0 (22)

DDID_TXDN0 (22)

DDID_TXDP1 (22)

DDID_TXDN1 (22)

DDID_TXDN2 (24)

DDID_TXDP2 (24)

DDID_TXDN3 (24)

DDID_TXDP3 (24)

EDP_AUXP (22)

EDP_AUXN (22)

+VCCIO

R59 24.9/F_4

Place inside CPU cavity

AUD_CPU_BCLK (9)

AUD_CPU_SDO (9)

HP Restricted Secret

A A

Title

Title

Title

CPU_PEG/DISPLAY

CPU_PEG/DISPLAY

CPU_PEG/DISPLAY

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

--

--

--

Page Modified: Sheet of

Page Modified: Sheet of

5

4

3

2

Page Modified: Sheet of

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Project:

Project:

Project:

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

461Thursday, December 17, 2015

461Thursday, December 17, 2015

461Thursday, December 17, 2015

A

A

A

5

www.laptoprepairsecrets.com

CLK_DMI_100M_P(12)

CLK_DMI_100M_N(12)

CLK_PCIBCLK_P(12)

CLK_PCIBCLK_N(12)

D D

CLK_24MHZ_P(12)

CLK_24MHZ_N(12)

+VCCST_VCCPLL

R4 56/1%_4

R12 100/1%_4

H_VIDALERT#(48)

H_VIDSCK(48)

H_VIDSOUT(48)

VCCST_PWR GD(9,38)

C C

B B

H_PWRGD(9,38)

H_PM_SYNC(10)

H_PM_DOWN(10)

PCH_THERMTR IP#(10)

H_SKTOCC#(11)

H_PROHOT#

VR_HOT#(39,48)

EC_PROCHOT(30)

EC-DB2-E02

A A

EMI

ESD

VR_HOT#

EC-DB-E01

R13 100/1%_4

DG: 75<Rec<200

H_THERMTRIP#

H_PWRGD

H_PREQ#

H_TRST#

CPU_RESET#

Near CPU

R11 220_4

R10 100/1%_4

TP67

TP66

R119 2.8K/F_4

R122 6.04K/F_4

R577 20/1%_4

R76 SP_4

TP90

R5 75/1%_4

3

EC_PRHOT_S

Q2

2N7002K/60V/0.3A

2

R14 100k/5%_4

D7 TVS_AZ5125-01H

D26 *TVS_AZ5125-01H

D6 TVS_AZ5125-01H

D25 *TVS_AZ5125-01H

D28 *TVS_AZ5125-01H

H_VIDALERT#_R

H_VIDSCK

H_VIDSOUT

H_PROCHOT#

DDR_VTT_CNTL_R

FM_OPC_ZVM_N

RSCD_AC37

H_PWRGD

H_PM_DOWN_R

H_PECI

H_THERMTRIP#

SKL_CNL

H_CATERR#

1

Near CPU

5

4

?

J1E

W5

BCLKP

W4

BCLKN

W1

PCI_BCLKP

W2

PCI_BCLKN

K9

CLK24P

J9

CLK24N

E39

VIDALERT#

E38

VIDSCK

E40

VIDSOUT

C39

PROCHOT#

AC36

DDR_VTT_CNTL

AC38

ZVM#

AC37

RSVD_AC37

H_VCCST_PWRGD

U2

VCCST_PWR GD

F8

PROCPWRGD

E7

RESET#

E8

PM_SYNC

D8

PM_DOWN

G7

PECI

D11

THERMTRIP#

AB35

SKTOCC#

AB36

PROC_SELECT#

D13

CATERR#

SKL_S_CPU_LGA

+VCCST_VCCPLL

VR_HOT# PCH_THERMTR IP#

C8

1000P/50V_4

4

SKL_S_CPU

LGA1151

5 OF 12

H_PECI

H_PECI

DDR_VTT_CNTL

+VDDQ level

DDR_VTT_CNTL_R

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST #

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

EC-DB2-E01

R552 SP_4

R559 *0/5%_4

+3V_S5

R1

10k/5%_4

DDR_VTT_CNTL_G

34

5

Q1A

H15

F15

F16

H16

F19

H18

G21

H20

G16

E16

F17

H17

G20

F20

F21

H19

F14

E14

F18

G18

D16

D17

G14

H14

H13

G12

F13

F11

F12

B9

B10

M11

?REV = 1.2

3

PD_TEST_CPU _0

PD_TEST_CPU _1

PD_TEST_CPU _2

PD_TEST_CPU _3

PD_TEST_CPU _4

PD_TEST_CPU _5

PD_TEST_CPU _6

PD_TEST_CPU _7

PD_TEST_CPU _8

PD_TEST_CPU _9

PD_TEST_CPU _10

PD_TEST_CPU _11

PD_TEST_CPU _12

PD_TEST_CPU _13

PD_TEST_CPU _14

PD_TEST_CPU _15

SKL_PCUSTB_0_D P

SKL_PCUSTB_0_D N

SKL_PCUSTB_1_D P

SKL_PCUSTB_1_D N

SKL_XDP_BPM2

SKL_XDP_BPM3

CFG_RCOMP

PD_TEST_CPU _3

EC_PECI (3 0)

PCH_PECI (10)

+3V_S5

R2

10k/5%_4

61

2

Q1B

PJ4N3KDW/3 0V_0.1A-SC70

3

TP88

TP87

R51 49.9/F_4

R491 1K_4

DDR_VTT_CNTL (41)

2

PD_TEST_CPU _0 (38)

PD_TEST_CPU _1 (38)

PD_TEST_CPU _2 (38)

PD_TEST_CPU _3 (38)

PD_TEST_CPU _4 (38)

PD_TEST_CPU _5 (38)

PD_TEST_CPU _6 (38)

PD_TEST_CPU _7 (38)

PD_TEST_CPU _8 (38)

PD_TEST_CPU _9 (38)

PD_TEST_CPU _10 (38)

PD_TEST_CPU _11 (38)

PD_TEST_CPU _12 (38)

PD_TEST_CPU _13 (38)

PD_TEST_CPU _14 (38)

PD_TEST_CPU _15 (38)

SKL_PCUSTB_0_D P (38)

SKL_PCUSTB_0_D N (38 )

SKL_PCUSTB_1_D P (38)

SKL_PCUSTB_1_D N (38 )

SKL_XDP_BPM_0 (38)

SKL_XDP_BPM_1 (38)

H_TDO (38)CPU_RESET#(10,38)

H_TDI (38)

H_TMS (38)

H_TCK (38)

H_TRST# (12,38)

H_PREQ# (38)

H_PRDY# (38)

XDP_PCUDEBUG_3 (38)

2

+VCCST_VCCPLL(7,9,38,46,47,48)

+VCCIO(4,7,38,42,47)

BK: FOLLOW CRB v1.0

H_PREQ#

H_TMS

H_TDO

H_TDI

H_TRST#

H_TCK

H_TCK TERMINATION PLACE NEAR CPU WITHIN

1.1 INCH

BK: FOLLOW CRB 1.1

Check pcie reverse

EC-DB-E02

EC-DB-E03

PD_TEST_CPU _0

PD_TEST_CPU _1

PD_TEST_CPU _2

PD_TEST_CPU _3

PD_TEST_CPU _4

PD_TEST_CPU _5

PD_TEST_CPU _6

PD_TEST_CPU _7

PD_TEST_CPU _8

PD_TEST_CPU _9

PD_TEST_CPU _10

PD_TEST_CPU _11

PD_TEST_CPU _12

PD_TEST_CPU _13

PD_TEST_CPU _14

PD_TEST_CPU _15

Unstuff R461 & R462 for SPT-H

SKL_CNL

SKL_PCUSTB_0_D P

SKL_PCUSTB_0_D N

SKL_PCUSTB_1_D P

SKL_PCUSTB_1_D N

BK: CRB --> NO THESE , NEED CONFIRM

CRB: Close to SPT-H

H_PWRGD

HP Restricted Secret

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Project:

Project:

Title

Title

Title

CPU MISC

CPU MISC

CPU MISC

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

--

--

--

Page Modified: Sheet of

Page Modified: Sheet of

Page Modified: Sheet of

Project:

1

+VCCST_VCCPLL

R77 *51/F_4

R550 *51/F_4

R540 *51/F_4

R539 *51/F_4

R545 *51/F_4

R61 51/F_4

R492 *1K_4

R484 *1K_4

R489 *1K_4

R496 *1K_4

R511 1K_4

R506 *1K_4

R514 *1K_4

R515 *1K_4

R488 *1K_4

R487 *1K_4

R494 *1K_4

R495 *1K_4

R518 *1K_4

R519 *1K_4

R526 *1K_4

R523 *1K_4

R6 *10k/5%_4

R483 *1K_4

R481 *1K_4

R499 *1K_4

R503 *1K_4

R75 1k/5%_4

R564 *10k/5%_4

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

05

+3V_S5

+VCCST_VCCPLL

A

A

A

561Thursday, December 17, 2015

561Thursday, December 17, 2015

561Thursday, December 17, 2015

5

www.laptoprepairsecrets.com

A25

A26

A27

A28

A29

A30

B25

B27

B29

B31

B32

B33

B34

B35

B36

B37

C25

C26

C27

C28

C29

C30

C32

C34

C36

D25

D27

D29

D31

D32

D33

D34

D35

D36

E24

E25

E26

E27

E28

E29

E30

E32

E34

E36

F23

F24

F25

F27

F29

F31

G30

G32

H22

H23

H25

H27

H29

H31

AJ11

AJ13

AJ15

AJ17

AJ19

AJ21

SKL_S_CPU_LGA

J1G

SKL_S_CPU

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

LGA1151

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

R8 *0/5%_4

R7 100/1%_4

R9 100/1%_4

7 OF 12

+VCCCPRE:

Icc ( max ) : 66A

Icc ( PS2) : 35A

+VCCCORE +VCCCORE

Decoupling Capacitors

D D

+VCCCORE

EC-DB2-E03

+

PC329 DIS@330u /2V_7343

+

PC330 *DIS@330u /2V_7343

Place caps at top

socket edge

+VCCCORE

C45 22U

C323 22U

C50 22U

C329 22U

C51 22U

C C

B B

A A

C360 22U

C44 22U

C362 22U

C56 22U

C42 22U

C61 22U

C58 22U

Place all above caps on

top side of CPU cavity

+VCCCORE

C43 22U

C68 22U

C57 22U

C63 22U

C59 22U

C350 22U

C46 22U

C341 22U

C60 22U

C371 22U

Place all below caps

on bottom side near

CPU socket

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

VCCCORE_SENSE

VSSCORE_SENSE

DG: Near CPU

5

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_SENSE

VSS_SENSE

REV = 1.2

VSSCORE_SENSEVCCCORE_SENSE

4

?

4

H32

J21

F32

F33

F34

G23

G24

G25

G26

G27

G28

G29

J22

J23

J24

J25

J26

J27

J28

J29

J30

J31

K16

K18

K20

K21

K23

K25

K27

K29

K31

L14

L15

L16

L17

L18

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

M13

M14

M16

M18

M20

M22

M24

M26

M28

M30

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

C38

D38

?

+VCCCORE

+VCCCPRE:

Icc ( max ) : 40A

Icc ( PS2) : 32A

VCCCORE_SENSE (48)

VSSCORE_SENSE (48)

+VCCGT

3

AA34

VCCGT

AA35

VCCGT

AA36

VCCGT

AA37

VCCGT

AA38

VCCGT

AB33

VCCGT

AB34

VCCGT

G36

VCCGT

G37

VCCGT

G38

VCCGT

G39

VCCGT

G40

VCCGT

H36

VCCGT

H38

VCCGT

H40

VCCGT

J36

VCCGT

J37

VCCGT

J38

VCCGT

J39

VCCGT

J40

VCCGT

K36

VCCGT

K38

VCCGT

K40

VCCGT

L34

VCCGT

L35

VCCGT

L36

VCCGT

L37

VCCGT

L38

VCCGT

L39

VCCGT

L40

VCCGT

M33

VCCGT

M34

VCCGT

M36

VCCGT

M38

VCCGT

M40

VCCGT

N34

VCCGT

N35

VCCGT

N36

VCCGT

N37

VCCGT

N38

VCCGT

N39

VCCGT

N40

VCCGT

P33

VCCGT

P34

VCCGT

P36

VCCGT

P38

VCCGT

P40

VCCGT

R34

VCCGT

R35

VCCGT

R36

VCCGT

R37

VCCGT

R38

VCCGT

R39

VCCGT

R40

VCCGT

T33

VCCGT

T34

VCCGT

T36

VCCGT

T38

VCCGT

T40

VCCGT

U34

VCCGT

U35

VCCGT

U36

VCCGT

U37

VCCGT

U38

VCCGT

U39

VCCGT

U40

VCCGT

V33

VCCGT

V34

VCCGT

V36

VCCGT

V38

VCCGT

V40

VCCGT

W34

VCCGT

W35

VCCGT

W36

VCCGT

W37

VCCGT

W38

VCCGT

Y33

VCCGT

Y34

VCCGT

Y36

VCCGT

Y38

VCCGT

SKL_S_CPU_LGA

3

J1H

SKL_S_CPU

LGA1151

VCCGT_SENSE

VSSGT_SENSE

VCCGTX_SENSE

VSSGTX_SENSE

8 OF 12

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

REV = 1.2??

F35

G34

G35

H33

H34

J33

J35

K32

K34

L31

L33

M32

F39

F38

F37

F36

2

Decoupling Capacitors

+VCCGT

C327 47u/6.3V_8

C26 47u/6.3V_8

C36 47u/6.3V_8

C347 47u/6.3V_8

C318 47u/6.3V_8

C35 47u/6.3V_8

C336 47u/6.3V_8

Place caps on top side

socket cavity

+VCCGT

C335 47u/6.3V_8

C348 47u/6.3V_8

C32 47u/6.3V_8

C337 47u/6.3V_8

C326 47u/6.3V_8

C325 47u/6.3V_8

C27 47u/6.3V_8

C28 47u/6.3V_8

C37 47u/6.3V_8

Place caps on backside

under socket cavity

+VCCGT

C30 47u/6.3V_8

C31 47u/6.3V_8

C320 47u/6.3V_8

C319 47u/6.3V_8

VCCGT_SENSE (48 )

VSSGT_SENSE (48)

2

HP Restricted Secret

Title

Title

Title

CPU POWER

CPU POWER

CPU POWER

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

--

--

--

Page Modified: Sheet of

Page Modified: Sheet of

Page Modified: Sheet of

1

+VCCCORE(7,47,48,49)

+VCCGT(47,48,50)

06

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Project:

Project:

Project:

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

661Thursday, December 17, 2015

661Thursday, December 17, 2015

661Thursday, December 17, 2015

A

A

A

5

www.laptoprepairsecrets.com

+VCCSA

+VCCSA:

Icc ( max ) :11A

D D

+VCCIO

+VCCIO:

Icc ( max ) :5.31A

C C

VCCST:

Icc ( max ) :0.1A

B B

+VCCST_VCCPLL

+VCCFUSEPRG

AA7

AB6

AB7

AB8

AC7

AC8

N7

P7

R7

T7

U7

Y6

Y7

Y8

W7

V7

AA6

AK11

AK14

AK24

AJ23

M8

P8

T8

U8

W8

V5

V6

V4

SKL_S_CPU_LGA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCST

VCCST

VCCPLL

SKL_S_CPU

LGA1151

VCC_OPC_1P8

VCC_OPC_1P8

VCCSA_SENSE

VCCIO_SENSE

VSS_SAIO_SENSE

VCCOPC_SENSE

VCCEOPIO_SENSE

VSSOPC_EOPIO_SENSE

9 OF 12

REV = 1.2 ?

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCCPLL_OC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCEOPIO

VCCEOPIO

?J1I

4

+VDDQ

AT18

AT21

AU13

AU15

AU19

AU23

AV11

AV17

AV21

AW10

AW14

AW25

AY12

AY16

AY18

AY23

AJ9

+VCCPLL_OC_R

+VCCPCC_OC:

Icc ( max ) :0.11A

AJ30

AJ27

AJ28

AJ29

AK27

AJ25

AJ26

AB37

AB38

AD5

AF4

AE4

AK21

AJ24

AK22

+VDDQ:

Icc ( max ) :2.5A

EC-DB-E01

R549 SP_4

R544 *0_4

+VDDQ

+VCCPLL_OC

PCH_2_CPU_T RIGGER(12)

CPU_2_PCH_TRIGGER(12)

VCCSA_SENSE (44)

VCCIO_SENSE (42)

VSS_SA_IO_SENSE ( 42,44)

3

TP14

TP13

TP85

TP75

TP1

TP73

TP2

R86 20/1%_4

TP83

TP91

H_AV1

H_AW2

H_K10

H_J17

H_B39

H_J19

H_C40

PROC_TRIGOUT

H_L12

H_K12

J8

RSVD_TP

J7

RSVD_TP

L8

RSVD_TP

K8

RSVD_TP

AV1

RSVD_TP

AW2

RSVD_TP

H8

VSS

K10

RSVD

L10

RSVD

J17

RSVD

B39

RSVD

J19

RSVD

C40

RSVD

G8

VSS

AY3

VSS

D1

PROC_TRIGIN

B3

PROC_TRIGOUT

L12

RSVD

K12

RSVD

SKL_S_CPU_LGA

2

+VCCSA(44,47)

+VDDQ(9,14,15,41,46,47,55)

+VCCIO(4,38,42,47)

+VCCST_VCCPLL(5,9,38,46,47,48)

J1J

SKL_S_CPU

LGA1151

10 OF 12

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

VSS

VSS

VSS

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

REV = 1.2??

H11

H12

AW38

AV39

AU39

AU40

AT15

AR23

AR22

J15

J14

AU9

AU10

J13

K13

J11

D15

K11

H_H12

H_AW38

H_AV39

H_AU39

H_AU40

H_J15

H_J14

H_AU9

H_AU10

H_J13

H_K13

H_K11

TP86

TP5

TP6

TP4

TP3

TP74

TP89

TP12

TP11

TP81

TP80

TP84

R533

*560/F_4

CRB 1.1: remove

1

07

Decoupling Capacitors

EC-DB-E01

+VCCCORE

A A

R556 SP_4

R557 *0/5%_4

+VCCFUSEPRG+VCCST_VCCPLL

5

+VCCSA

C67 22U

C66 22U

Place all caps

inside CPU socket

cavity top ;

+VCCST_VCCPLL

C444 22U

C442 1U

X5R

Place caps at

top socket edge

0603X5R

0603X5R

0603X5R

0402

6.3V

6.3V

6.3V

6.3V

4

+VCCIO

C416 22U

C417 22U

C415 22U

C39 22U

C64 22U

C65 22U

C411 0.1U

X7R

C412 0.1U

X7R

C352 0.1U

X7R

Place all caps

inside CPU socket

cavity top

0603X5R

0603X5R

0603X5R

0603X5R

0603X5R

0603X5R

0402

0402

0402

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

16V

16V

16V

+VDDQ

C367 22U

C338 22U

C353 22U

C394 22U

C54 *22U

1 2

D47 *TVL040201SP0

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

6.3V

0603X5R

ESD

Place cap in socket edge top

3

2

RF

+VCCPLL_OC +VDDQ

C282 *6.8p/50V/NPO_4

C97 *6.8p/50V/NPO_4

C284 *6.8p/50V/NPO_4

C283 *6.8p/50V/NPO_4

HP Restricted Secret

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Project:

Project:

Title

Title

Title

CPU POWER/RSVD

CPU POWER/RSVD

CPU POWER/RSVD

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

--

--

--

Page Modified: Sheet of

Page Modified: Sheet of

Page Modified: Sheet of

Project:

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

A

A

A

761Thursday, December 17, 2015

761Thursday, December 17, 2015

761Thursday, December 17, 2015

5

www.laptoprepairsecrets.com

J1F

SKL_S_CPU

D D

A7

VSS

AC34

VSS

AC35

VSS

AC6

VSS

AD1

VSS

AD33

VSS

AD36

VSS

AD37

VSS

AD38

VSS

AD39

VSS

AD4

VSS

AD40

VSS

AD6

VSS

AD7

VSS

AD8

VSS

AE3

VSS

AE33

VSS

AE36

VSS

AE5

VSS

AE8

VSS

AF1

VSS

AF33

VSS

AF36

VSS

AF37

VSS

C C

B B

A A

AF40

VSS

AF5

VSS

AF8

VSS

AJ31

VSS

AJ32

VSS

AJ33

VSS

AJ34

VSS

AJ35

VSS

AJ36

VSS

AJ4

VSS

AJ5

VSS

AJ8

VSS

AK10

VSS

AK12

VSS

AK13

VSS

AK15

VSS

AK16

VSS

AK17

VSS

AK18

VSS

AK19

VSS

AK20

VSS

AK23

VSS

AK25

VSS

AK26

VSS

AK28

VSS

SKL_S_CPU_LGA

5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

LGA1151

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

6 OF 12

REV = 1.2 ?

?

AK29

AK30

AK36

AK37

AK40

AK5

AK6

AK7

AK8

AK9

AL1

AL11

AL14

AL2

AL21

AL24

AL27

AL3

AL30

AL36

AL4

AL5

AM11

AM14

AM17

AM19

AM24

AM27

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AM37

AM38

AM39

AM40

AM5

AN1

AN10

AN11

AN14

AN16

AN19

AN22

AN23

AN24

AN27

AN30

AN36

AN4

AN5

AN6

AN7

AN8

AN9

AP11

AP14

AP24

AP27

AP30

AP36

AP37

AP40

AP5

AR1

AR11

AR14

AR16

AR17

AR18

AR19

AR2

AR20

AR21

AB5

AC3

AC33

AB39

AA8

A17

A11

AA33

AA3

A24

A13

A15

AG1

AH8

AJ1

AH40

AH5

AH39

AH38

AH37

AH36

AG8

AH33

AG5

AG4

AG36

AG33

AG3

AG2

AR30

AR3

AR27

AT10

H30

AV38

AV9

L11

K30

K28

K26

K24

H28

AT30

AT25

AT14

AR33

AU1

AT9

AT28

AT32

AY9

AW9

AW5

AW30

AW3

AV5

AV34

AV30

AV28

AV26

AV2

AU7

AU5

AU30

AT7

AT6

AT5

AT40

AT39

AT36

AT24

AT17

AT13

AT12

AT11

AR5

AR4

AR36

AR35

AR34

AR32

AR31

C20

C22

C35

C33

C31

C24

C2

A4

H7

L6

L9

B6

4

J1K

SKL_S_CPU

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

LGA1151

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_NCTF

VSS_NCTF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL_S_CPU_LGA

4

?

VSS_NCTF

11 of 12

?

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

REV = 1.2

C37

J16

D40

K35

K37

K33

H37

C10

D24

D37

B30

B26

B24

AY7

AY5

AY30

AY27

AW36

AW34

AW32

C12

C14

C16

C18

C5

C8

D26

D28

D30

D4

J1L

G13

G17

G15

G3

G6

H1

H21

H24

H26

H39

H4

H9

J18

J20

J3

J6

K1

K14

K17

K22

U3

T37

T35

R33

P4

P39

P37

P1

N33

M39

M37

M29

M25

M27

M23

M21

M19

M15

M17

M10

M12

M1

L32

L3

L13

K7

K4

K39

AU25

AU34

AU4

AT38

AT37

AT34

AT31

AT29

AT27

AT26

AR24

V35

U6

V1

V37

V39

AT8

W3

Y35

W6

Y37

SKL_S_CPU_LGA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL_S_CPU

LGA1151

3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_NCTF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

12 of 12

REV = 1.2

3

2

?

D39

D7

E11

E13

E17

E15

E19

E21

E23

E3

E31

E33

E37

E35

E6

E9

F1

F22

F10

F26

F28

F30

F40

F4

F7

G11

G19

G22

G31

G33

H35

J10

J12

J32

J34

K15

K19

B38

U33

T4

T1

R6

R8

R3

P35

N8

N6

N3

M4

M7

M35

B28

T39

V8

W33

Y5

?

1

08

HP Restricted Secret

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Project:

Project:

Title

Title

Title

CPU GND

CPU GND

CPU GND

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

--

--

--

Page Modified: Sheet of

Page Modified: Sheet of

2

Page Modified: Sheet of

Project:

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

A

A

A

861Thursday, December 17, 2015

861Thursday, December 17, 2015

861Thursday, December 17, 2015

5

www.laptoprepairsecrets.com

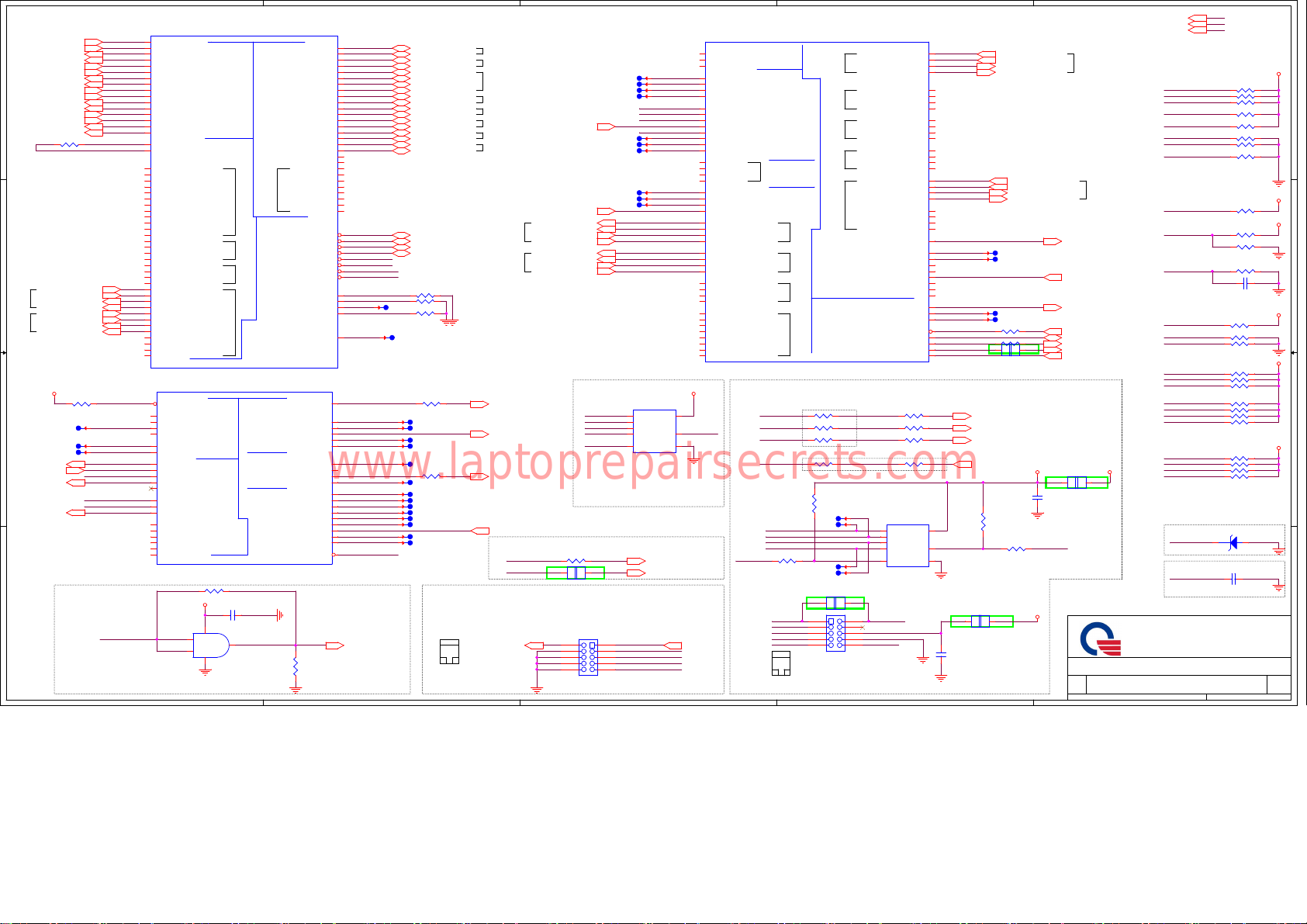

U41D

PCH_BD1

PCH_BE2

BA9

HDA_BCLK

BD8

HDA_RST#

BE7

HDA_SDI0

BC8

HDA_SDI1

BB7

HDA_SDO

BD9

HDA_SYNC

BD1

RSVD_BD1

BE2

RSVD_BE2

AM1

DISPA_SDO

AN2

DISPA_SDI

AM2

DISPA_BCLK

AL42

GPP_D8/SSP0_SCLK

AN42

GPP_D7/SSP0_RXD

AM43

GPP_D6/SSP0_TXD

AJ33

GPP_D5/SSP0_SFRM

AH44

GPP_D20/DMIC_DATA0

AJ35

GPP_D19/DMIC_CLK0

AJ38

GPP_D18/DMIC_DATA1

AJ42

GPP_D17/DMIC_CLK1

BC10

RTCRST#

BB10

SRTCRST#

AW11

PCH_PWROK

BA11

RSMRST#

AV11

DSW_PWROK

BB41

GPP_C2/SMBALERT#

AW44

GPP_C0/SMBCLK

BB43

GPP_C1/SMBDATA

BA40

GPP_C5/SML0ALERT#

AY44

GPP_C3/SML0CLK

BB39

GPP_C4/SML0DATA

AT27

GPP_B23/SML1ALERT#/PCHHOT#

AW42

GPP_C6/SML1CLK

AW45

GPP_C7/SML1DATA

SPT_PCH_DT/SKT

HDA_BCLK(27)

HDA_RST#(27)

HDA_SDIN(27)

HDA_SDOUT_R(10)

HDA_SDOUT(27)

HDA_SYNC(27)

D D

C C

AUD_CPU_SDO(4)

AUD_CPU_SDI(4)

AUD_CPU_BCLK(4)

PCHHOT#(30)

R326 22/5%_4

R778 22/5%_4

R327 22/5%_4

R779 22/5%_4

R787 33/J_4

R774 33/J_4

Near PCH

Note: RESET# is not

required for the

ALC3252.

HDA_BCLK_R

HDA_RST#_R

HDA_SDIN

HDA_SDOUT_R

HDA_SYNC_R

TP141

TP138

AUD_CPU_SDO_R

AUD_CPU_SCLK_R

PCH_RTCRST#

PCH_SRTCRST#

PCH_PWROK

PCH_RSMRST#

PCH_DPWROK

SMB_ALT#

SMB_CLK_RESUME

SMB_DAT_RESUME

GPP_C_5

SML0_CLK

SML0_DAT

PCHHOT#

SMB1_CLK

SMB1_DAT

Strap Pin Table

Configuration

"Top swap" m ode

0 = Disable, Default (Int ernal pull-down)

1 = Enable

"No-Reboot" mo de

0 = Disable, Default (Int ernal pull-down)

1 = Enable

Intel ME Crypto TLS cipher suite.

0 = Disable, Default (Internal pull-down)

1 = Enable

BOOT SELECT STRAP

0 = SPI, Default (Internal pull-down)

1 = LPC

ESPI/LPC SELECT STRAP ( for EC )

0 = LPC ( Default, int. pull-down )

1 = ESPI

BOOT HALT

0 = Enable

1 = PCH has Internal weak pull-up

B B

JTAG ODT

0 = Enable

1 = PCH has Internal weak pull-up

CONSENT STRAP

0 = Consent strap is enabled

1 = PCH has Internal weak pull-up

PERSONALITY STRAP

0 = Enable

1 = PCH has Internal weak pull-up

0 = PCH has Internal weak pull-down

1 = EXI boot stall by pass is enabled

SECRUITY MEASURES.

0 = Enable, Defualt (Internal weak

pull-down)

1 = Disable. Flash Descriptor Securit y

overrided, pull up for debug only.

ESPI FLASH SHARING MODE

0 = Master (Internal weak pull-down)

1 = Slave

DFX TEST MODE

XTAL input is single ended if sampled l ow

else di fferenti al

A A

TEST SETUP MENU

0 = Test setup menu enabled

1 = Disabled (Default)

SV ADVANCE MENU TABLE

0 = SV ADVANCE MENU

1 = Normal Menu (Default)

Note

SPKR

LPSS_GSPI0_MOSI(12)

SMB_ALT#

LPSS_GSPI1_MOSI(12)

GPP_C_5

SPI_MOSI(10,37,38)

SPI_MISO(10,37)

SPI_IO2(10,38)

SPI_IO3(10)

150K PU NEEDED TO DISABLE EXI BOOT STALL BYPASS

PCHHOT#

HDA_SDO(10)

HDA_SDOUT_R

GPP_H_12(10)

VISACH2_D3(10)

TEST_SETUP_MENU(11)

SV_ADVANCE_GP48(10)

5

R729 *4. 7K/F_4

R736 *20 k/5%_4

R726 *4.7K/ F_4

R725 *1k/ 5%_4

R176 *4. 7K/F_4

R175 *20 k/5%_4

R222 *4. 7K/F_4

R223 *20 k/5%_4

R676 *4.7K/ F_4

R675 20k/ 5%_4

R720 1k/ 5%_4

R721 *4. 7K/F_4

R719 *20 k/5%_4

R718 *4. 7K/F_4

R730 *20 k/5%_4

R727 *1. 2k/5%_4

R701 *20k/5%_4

R694 *4.7k/5%_4

R224 150k/1%_4

R225 *20k/5%_4

R319 1K/J_4

HDA_SDO

R586 1K/J_4

R685 *4. 7K/F_4

R684 *20 k/5%_4

R655 *4. 7K/F_4

R669 *20 k/5%_4

R146 10K/J_4

R159 *0/ 5%_4

R645 20k/ 5%_4

R644 *0/ 5%_4

4

SPT-H_PCH

(Primary)

AUDIO

(Primary)

(RTC)

(RTC)

(RTC)

REV = 1.3

+3V

+3V

+3V_S5

+3V_S5

+3V_S5

+3V_S5_SPI

+3V_S5_SPI

+3V_S5_SPI

+3V_S5_SPI

pull down is needed for

pre-ES1/ES1 samples.

+3V_S5

+DVDDIO_AUDIO

EN_OVERRIDE (30)

+3V_S5

+3V_S5

+3V

+3V

SMBUS

CRB 1.0

4

BMBUSY#

PCH_LPC_CLKRUN#

LANPHYPC

SLP_WLAN#

DDR4_DRAMRST_N_R

VRALERTB_PU

TP_DETECT#

GPP_B_1

GPP_B_0

GPP_B_11

PCH_SYSPWROK

PCH_WAKE#

SLP_A#

SLP_LAN#

PM_SLP_S0_R#

PM_SLP_S3_R#

PM_SLP_S4#

PM_SLP_S5_R#

PCH_SUSCLK

BATLOW#

PCH_SUSACK#

PCH_SUSPWRACK

LAN_WAKE#

GPD1

PM_SLP_SUS#_N

SYS_RST#

SPKR

PCH_PROCPWRGD

PCH_JTAG_TMS

PCH_JTAG_TDO

PCH_JTAG_TDI

+3V_S5

C598

0.1u/16V/X7R_4

U42

3 5

TC7SH08FU

R178 1k/5%_4

R168 1k/5%_4

R163 1k/5%_4

R162 1k/5%_4

SMBCLK0_EC

SMBDATA0_EC

3

TP56

EC-DB2-E01

TP53

R761 SP_4

TP36

TP119

TP38

EC-DB2-E01

TP135

TP44

R735 SP_4

R316 SP_4

R307 SP_4

R748 *0/5%_4

R751 *0/5%_4 R320 10K/J_4

TP137

R773 30/1%_4

C191 0.1u/16V/ X7R_4

PCH_RSMRST#

R321

*0_4

PCH_DPWROK

4

3

R309 47k/5%_4

CRB v1.1: R2039 -> 47kohm

Stuff R2043 and don't stuff R2048 if

not supporting Deep SX..

C192 *0.01u/50V/ X7R_4

R323 100k/5%_4

PCH_PWROK_R

BK: DG

PCH_PWROK

R765 10K/J_4

R763 249/1%_4

R759 249/1%_4

+3V_S5 +3V

SMBCLK_PCH_MAIN

SMBDATA_PCH_MAIN

SMBCLK_PCH_MAIN (14,15,38)

SMBDATA_PCH_MAIN (14,15,38)

+3V_S5

SMBCLK0_EC/SMBDATA0_EC:

SMBCLK0_EC (30)

SMBDATA0_EC (30)

PCH_PWROK

R199 1k/5%_4

R197 1k/5%_4

PCH_LPC_CLKRUN# (30)

DDR4_DRAMRST# (14,15)

TP_DETECT# (31)

PCH_SYSPWROK (38)

PCH_WAKE# (28,34,35)

PM_SLP_S0# (30)

PM_SLP_S3# (30)

PM_SLP_S4# (30)

PM_SLP_S5# (30)

PCH_SUSCLK (34,35)

EC_SUSACK# (30)

EC_SUSPWRACK (30)

EC_PWBTN_OUT# (30,38)

SYS_RST# (38)

SPKR (27)

H_PWRGD (5,38)

ITP_PMODE (38)

PCH_JTAGX (38)

PCH_JTAG_TMS (38)

PCH_JTAG_TDO (38)

PCH_JTAG_TDI (38)

PCH_JTAG_TCK (38)

VCCST_PWRGD (5,38)

PCH_SYSPWROK

(Be asserted after both PWROK and VR_READY assertion)

EC_SYS_PWROK(30)

RTC circuit

R27

1.5k/1%_4

VCC_RTC_S

R26

45.3k/1%_4

R25 1K_4

BT_+

12

+-

?

GPP_B1

GPP_B0

GPP_B11

SYS_PWROK

WAKE#

SLP_LAN#

SLP_SUS#

SYS_RESET#

ITP_PMODE

JTAGX

JTAG_TMS

JTAG_TDO

JTAG_TDI

JTAG_TCK

EC-DB1-E01

*TVS AZ5125-01 H.R7G

BB17

AW22

AR15

AV13

BC14

BD23

AL27

AR27

N44

AN24

AY1

BC13

BC15

AV15

BC26

AW15

BD15

BA13

AN15

BD13

BB19

BD19

BD11

BB15

BB13

AT13

AW1

BD26

AM3

AT2

AR3

AR2

AP1

AP2

AN3

?

R328 SP_4

GPP_A12/BMBUSY#/ISH_GP6/SX_EXIT_HOLDOFF#

GPP_A8/CLKRUN#

GPD11/LANPHYPC

(DSW)

(DSW)

GPD9/SLP_WLAN#

(DSW)

(Primary)

GPP_B2/VRALERT#

GPP_G17/ADR_COMPLETE

DRAM_RESET#

(Primary)

(DSW)

(DSW)

(DSW)

(Primary)

(DSW)

(DSW)

(DSW)

(DSW)

(DSW)

(Primary)

GPP_A13/SUSWARN#/SUSPWRDNACK

(DSW)

(DSW)

(DSW)

JTAG

4 OF 12

GPD6/SLP_A#

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

GPD8/SUSCLK

GPD0/BATLOW#

GPP_A15/SUSACK#

GPD2/LAN_WAKE#

GPD1/ACPRESENT

GPD3/PWRBTN#

GPP_B14/SPKR

PROCPWRGD

RSMRST# & DSW_PWROK

EC_RSMRST#(30,38)

D8

Near PCH

EC-DB1-E01

+3V

R769

10K/J_4

R329 SP_4

R762 *0/J_4

2

1

EC_DPWROK(30)

PCH_PWROK PCH SYSTEM RESET

VR_READY(30,48)

EC_PWROK(30)

VR_EADY to EC delay--> EC_PWROK

SYSTEM SMBUS

MEMORY,XDP

CRB: DIMM, PEG slot,

power thermal sensor?

SMB_CLK_RESUME

+3V

SMB_DAT_RESUME

SYSTEM SMBUS

EC-DB1-E04

SMB1_CLK

+3V

SMB1_DAT

+3V

Q7

6

2

5

Q55

6

2

5

SMB_CLK_RESUME

SMB_DAT_RESUME

1

SMBCLK_PCH_MAIN

43

SMBDATA_PCH_MAIN

2N7002DW/60V/0.115A

SMB1_CLK

SMB1_DAT

1

43

2N7002DW/60V/0.115A

2

PM_SLP_SUS#

PM_SLP_SUS#_N

To EC ??

PCH_SUSPWRACK PCH_SUSACK#

BOM Note:

EMPTY R2029 FOR USB WAKE S4/S5

DESIGN NOTE:

STUFF R3030 FOR NON-DEEP SX

EC-DB1-E01

R785 SP_4

BK: CRB

PCH_SYSPWROK

D1

BAT54C

1

2

20MIL

BT_-

BT1

CONNDIPHOUSING2P

CLEAR CMOS

CLR_CMOS(30)

2

R767 10k/5%_4

C597 *0.1u/16V/ X7R_4

R752 *0/J_4

R755 *1k/5%_4

R789 1K/J_4

+3V

R343

2.2K/J_4

JP2

1 2

SHORT PAD

+3V_RTC+3V_AUX

R27/R26

CRB: 30.1k 1%

Check list: 20k

20MIL

3

R29 20K/F_4

C40 1u/10V/X5R_4

R28 20K/F_4

C48 1u/10V/X5R_4

PCH_RTCRST#

2

PDTC144EU

Q5

1 3

1

+3V_PCH_VCCDSW(13)

+3V_S5(5,10,11,12,13,23,25,28,30,32,34,37,38,39,41,42, 43,45,46,47,54,55)

+3V(10,11,12,13,14,15,16,17,18, 19,22,24,25,26,27,28,29,30,31,34,35,36,38,42,44,46,47,48,53,54,55)

+VCCST_VCCPLL(5,7,38,46,47,48)

PM_SLP_SUS# (30)

PCH_SYSPWROK

R780 *10K/J_4

+3V

SYS_RST#_GSYS_RST#

R342 1K/J_4

JP1

12

SHORT PAD

PCH_RTCRST#

PCH_SRTCRST#

VRALERTB_PU

BMBUSY#

TP_DETECT#

PCH_LPC_CLKRUN#

PCH_WAKE#

BATLOW#

GPD1

LAN_WAKE#

EC_PWBTN_OUT#

DDR4_DRAMRST#

PCH_JTAG_TDO

PCH_JTAG_TDI

PCH_JTAG_TMS

PCH_JTAG_TCK

PCH_SUSCLK

CRB: for

LPT-H

SML0_CLK

SML0_DAT

HP Restricted Secret

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Project:

Project:

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Page Modified: Sheet of

Page Modified: Sheet of

Page Modified: Sheet of

Project:

PCH_HDA/SMBUS/MISC

PCH_HDA/SMBUS/MISC

PCH_HDA/SMBUS/MISC

--

--

--

HP-SAIPAN

HP-SAIPAN

HP-SAIPAN

1

09

+3V_S5

R747 10K/J_4

R756 *10K/J_4

R731 10K/J_4

R227 8.2k/5%_4

+3V_PCH_VCCDSW

BK

R764 1K/J_4

R766 10K/J_4

R758 *10K/J_4

R770 4.7K/F_4

R760 470/5%_4

C595 *0.1u/16V/ X7R_4

DG: NEAR DIMM

+VCCST_VCCPLL

R790 51/F_4

R782 51/F_4

R783 51/F_4

R295 *51/5%_4

R304 *1.5K/F_4

R177 1k/5%_4

R179 1k/5%_4

961Thursday, December 17, 2015

961Thursday, December 17, 2015

961Thursday, December 17, 2015

+VDDQ

+3V_S5

+3V

A

A

A

5

www.laptoprepairsecrets.com

?

REV = 1.3

REV = 1.3

R753 *0/J_4

+3V

C588 0.1U

10%

2

1

3 5

SPT-H_PCH

DMI

PCIe/USB 3

(H110)

(H110)

LAN,PCIe

(H110)

(H110)

2 OF 12

SPT-H_PCH

1 OF 12

4

U40

TC7SH08FUSSOP-5P

N/A

LAN

PCIe

?

0402 X7R

USB 2.0

N/A

(H110)

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_F15/USB2_OCB_4

GPP_F16/USB2_OCB_5

GPP_F17/USB2_OCB_6

GPP_F18/USB2_OCB_7

USB2_VBUSSENSE

GPP_B13/PLTRST#

GPP_G16/GSXCLK

GPP_G12/GSXDOUT

GPP_G13/GSXSLOAD

GPP_G14/GSXDIN

GPP_G15/GSXSRESET#

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

GPP_H18/SML4ALERT#

GPP_H17/SML4DATA

GPP_H16/SML4CLK

GPP_H15/SML3ALERT#

GPP_H14/SML3DATA

GPP_H13/SML3CLK

GPP_H12/SML2ALERT#

GPP_H11/SML2DATA

GPP_H10/SML2CLK

INTRUD ER#

16V

AF5

USB2N_1

AG7

USB2P_1

AD5

USB2N_2

AD7

USB2P_2

AG8

USB2N_3

AG10

USB2P_3

AE1

USB2N_4

AE2

USB2P_4

AC2

USB2N_5

AC3

USB2P_5

AF2

USB2N_6

AF3

USB2P_6

AB3

USB2N_7

AB2

USB2P_7

AL8

USB2N_8

AL7

USB2P_8

AA1

USB2N_9

AA2

USB2P_9

AJ8

USB2N_10

AJ7

USB2P_10

W2

USB2N_11

W3

USB2P_11

AD3

USB2N_12

AD2

USB2P_12

V2

USB2N_13

V1

USB2P_13

AJ11

USB2N_14

AJ13

USB2P_14

AD43

AD42

AD39

AC44

Y43

Y41

W44

W43

AG3

USB2_COMP

AD10

AB13

RSVD_AB13

AG2

USB2_ID

BD14

GPD7/RSVD

USB2_COMP

Trace length < 500 m ils

Trace impedance 50 ohm

No longer tha n 450 mils to r esistor

Trace spacing is 15 m ils

?

BB27

P43

R39

R36

R42

R41

AF41

AE44

BC23

BD24

BC36

BE34

BD39

BB36

BA35

BC35

BD35

AW35

BD34

BE11

?

CRB:

NFC

PLTRST_PEG_SLOTS_N

USBHUB_RST_N

TPM

R741

100K/F_4

U41B

PCH_RCOMPN

PCH_RCOMPP

PME_N

TP_PCH_AF17

TP_FPF_VREF

TP_FPF_MON

SPI_MOSI

SPI_MISO

SPI_CS0#

SPI_CLK

SPI_IO2_R

SPI_IO3_R

L27

DMI_RXN0

N27

DMI_RXP0

C27

DMI_TXN0

B27

DMI_TXP0

E24

DMI_RXN1

G24

DMI_RXP1

B28

DMI_TXN1

A28

DMI_TXP1

G27

DMI_RXN2

E26

DMI_RXP2

B29

DMI_TXN2

C29

DMI_TXP2

L29

DMI_RXN3

K29

DMI_RXP3

B30

DMI_TXN3

A30

DMI_TXP3

B18

PCIE_RCOMPN

C17

PCIE_RCOMPP

H15

PCIE1_RXN/USB3_7_RXN

G15

PCIE1_RXP/USB3_7_RXP

A16

PCIE1_TXN/USB3_7_T XN

B16

PCIE1_TXP/USB3_7_TXP

B19

PCIE2_TXN/USB3_8_T XN

C19

PCIE2_TXP/USB3_8_TXP

E17

PCIE2_RXN/USB3_8_RXN

G17

PCIE2_RXP/USB3_8_RXP

L17

PCIE3_RXN/USB3_9_RXN

K17

PCIE3_RXP/USB3_9_RXP

B20

PCIE3_TXN/USB3_9_T XN

C20

PCIE3_TXP/USB3_9_TXP

E20

PCIE4_RXN/USB3_10_RXN

G19

PCIE4_RXP/USB3_10_RXP

B21

PCIE4_TXN/USB3_10_T XN

A21

PCIE4_TXP/USB3_10_T XP

K19

PCIE5_RXN

L19

PCIE5_RXP

D22

PCIE5_TXN

C22

PCIE5_TXP

G22

PCIE6_RXN

E22

PCIE6_RXP

B22

PCIE6_TXN

A23

PCIE6_TXP

L22

PCIE7_RXN

K22

PCIE7_RXP

C23

PCIE7_TXN

B23

PCIE7_TXP

K24

PCIE8_RXN

L24

PCIE8_RXP

C24

PCIE8_TXN

B24

PCIE8_TXP

SPT_PCH_DT/SKT

U41A

BD17

GPP_A11/PME#

AG15

RSVD_AG15

AG14

RSVD_AG14

AF17

RSVD_AF17

AE17

RSVD_AE17

AR19

TP5

AN17

TP4

BB29

SPI0_MOSI

BE30

SPI0_MISO

BD31

SPI0_CS0#

BC31

SPI0_CLK

AW31

SPI0_CS1#

BC29

SPI0_IO2

BD30

SPI0_IO3

AT31

SPI0_CS2#

AN36

GPP_D1/SPI1_CLK

AL39

GPP_D0/SPI1_CS#

AN41

GPP_D3/SPI1_MOSI

AN38

GPP_D2/SPI1_MISO

AH43

GPP_D22/SPI1_IO3

AG44

GPP_D21/SPI1_IO2

SPT_PCH_DT/SKT

DMI_CPU_PCH_TXN0(4)

DMI_CPU_PCH_TXP0(4)

DMI_PCH_CPU_RXN0(4)

DMI_PCH_CPU_RXP0(4)

DMI_CPU_PCH_TXN1(4)

DMI_CPU_PCH_TXP1(4)

DMI_PCH_CPU_RXN1(4)

DMI_PCH_CPU_RXP1(4)

DMI_CPU_PCH_TXN2(4)

D D

DMI_CPU_PCH_TXP2(4)

DMI_PCH_CPU_RXN2(4)

DMI_PCH_CPU_RXP2(4)

DMI_CPU_PCH_TXN3(4)

DMI_CPU_PCH_TXP3(4)

DMI_PCH_CPU_RXN3(4)

DMI_PCH_CPU_RXP3(4)

R744 100/F_4

C C

PCIE_WLAN_RX_N(34)

WLAN

Card

Reader

B B

PCIE_WLAN_RX_P(34)

PCIE_WLAN_TX_N(34)

PCIE_WLAN_TX_P(34)

PCIE_CR_RX_N(29)

PCIE_CR_RX_P(29)

PCIE_CR_TX_N(29)

PCIE_CR_TX_P(29)

+VCCPGPPA

TP48

TP45

TP42

SPI_MOSI(9,37,38)

SPI_MISO(9,37)

SPI_CLK(37)

SPI_CS2#(37)

R754 10K/J_4

EC-SI-xx remove TP

Platform Reset

A A

PLTRST_N

5

4

USB_OC_0#

USB_OC_1#

USB_OC_2#

VISACH2_D3

USB_OC_4#

USB_OC_5#

USB_OC_6#

USB_OC_7#

PCH_USB_COMP

PCH_USB_SS

PCH_AB13

PCH_USB_ID

PCH_BD14

PLTRST_N_R

GPP_G_16

GPP_G_12

CAM_ON

IR_ON

GPP_G_15

PCH_GPP_E_3

BT_RF_OFF_R

GPP_B_4

GPP_H_18

GPP_H_17

GPP_H_16

GPP_H_15

GPP_H_14

GPP_H_13

GPP_H_12

GPP_H_11

GPP_H_10

INTRUDER#

PLTRST_N_BUF (16,24,34,35)

R775 113/F_4

R318 1K_4

TP49

R776 1K_4

TP136

R733 30/1%_4

R745 1k/5%_4

4

USB2_USB3P_1N (32)

USB2_USB3P_1P (32)

USB2_USB3P_2N (32)

USB2_USB3P_2P (32)

USB2_USB2P_3N (32)

USB2_USB2P_3P (32)

USB2_USB2P_4N (32)

USB2_USB2P_4P (32)

USB2_IR_5N (31)

USB2_IR_5P (31)

USB2_TYPC_6N (33)

USB2_TYPC_6P (33)

USB2_WLAN_7N (34)

USB2_WLAN_7P (34)

USB2_TCH_8N (31)

USB2_TCH_8P (31)

USB2_CAM_9N (31)

USB2_CAM_9P (31)

USB_OC_0# (32)

USB_OC_1# (32)

USB_OC_2# (32)

VISACH2_D3 (9)

TP125

TP25