Page 1

5

4

3

2

1

01

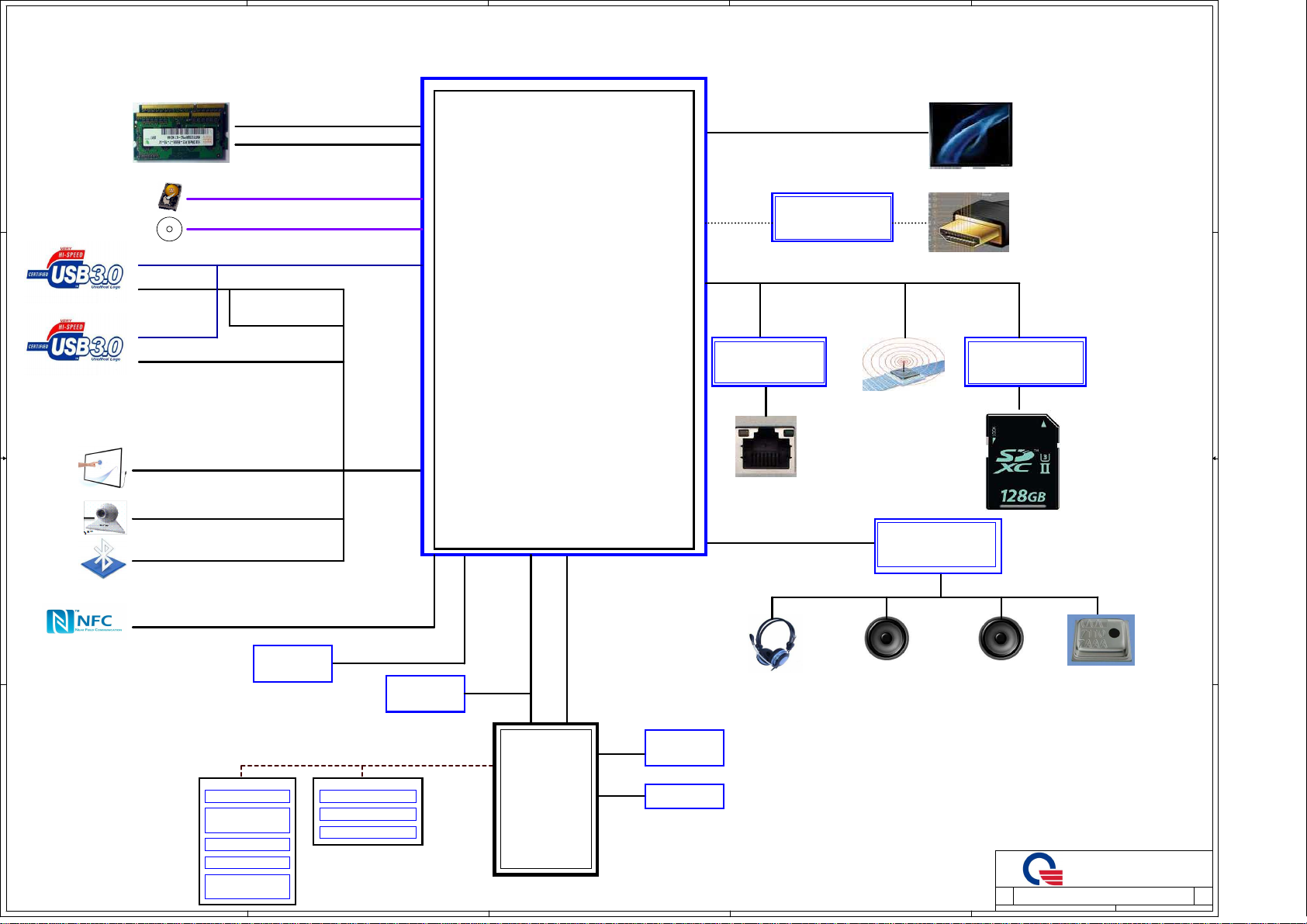

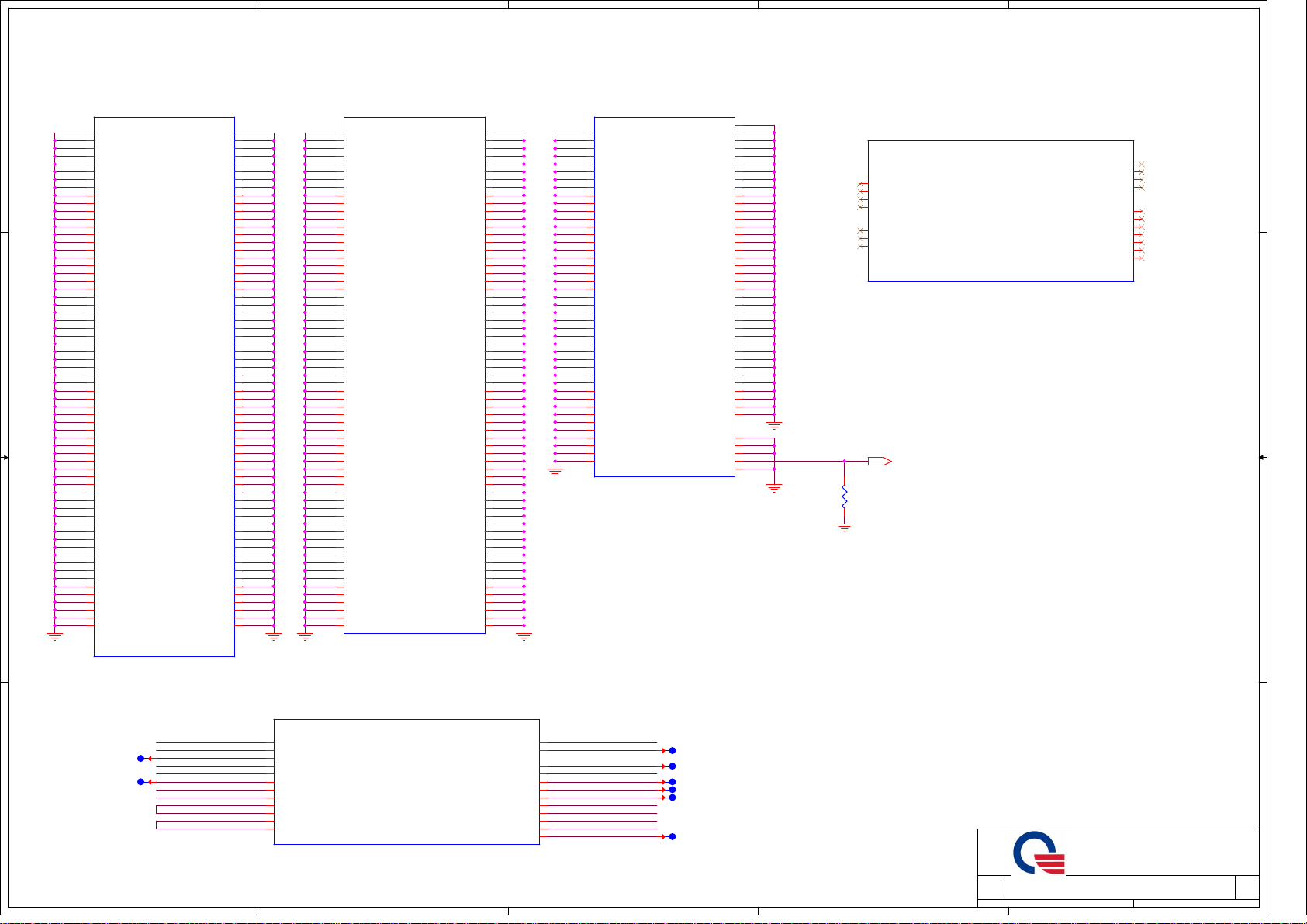

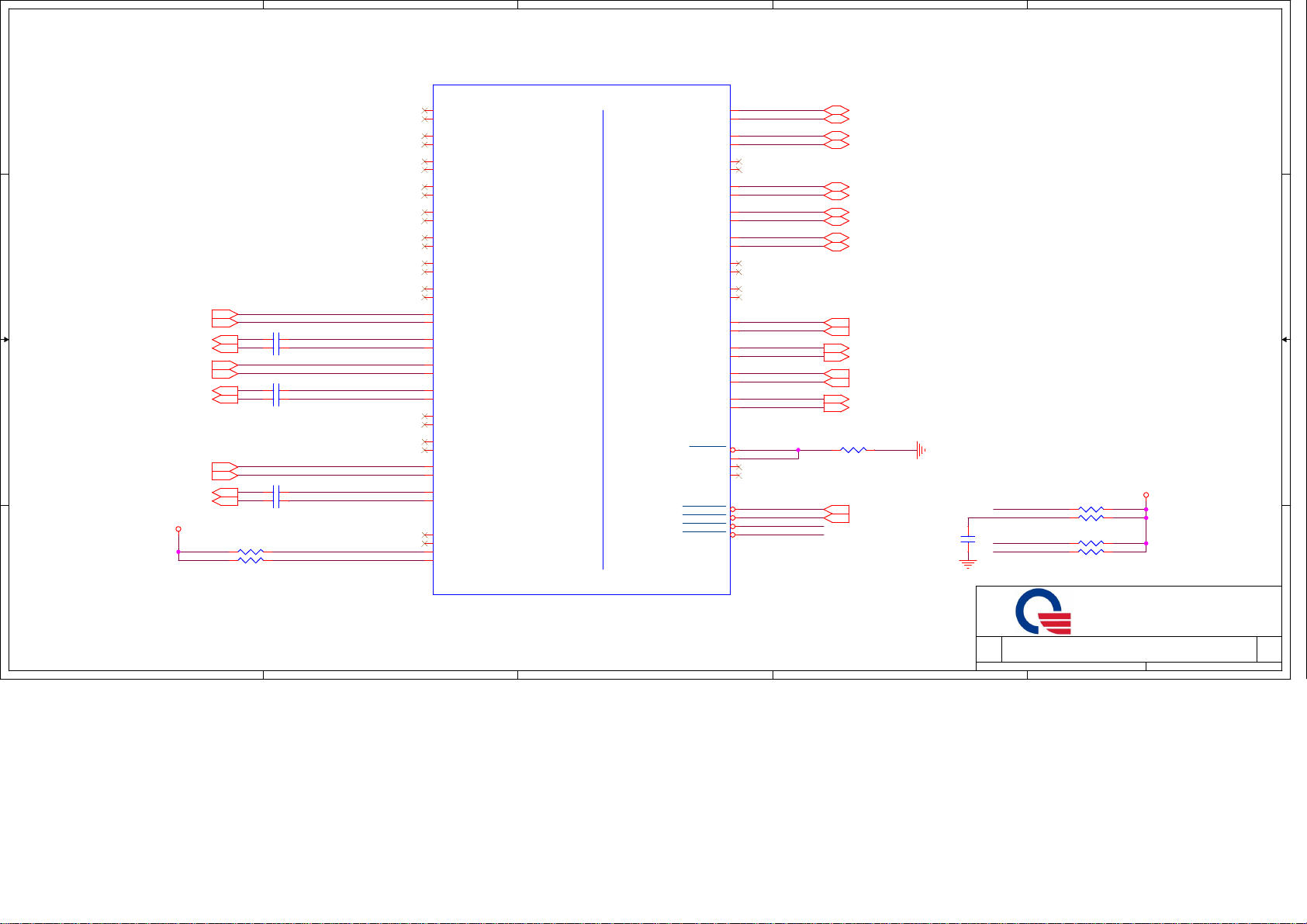

MY6 BLOCK DIAGRAM

PS8201A

P28

15.6" eDP

(1920x1080)

P17

PCIE3

PCI-Express Gen2

Card Reader

OZ777FJ2-B

P24

P19

P17

PCI-Express Gen1

PCIE2

P25

D D

CH-A SO-DIMM

CH-B SO-DIMM

P15~P16

2.5" HDD

ODD

USB3-PORT1

USB2-PORT0

P27

P20

USB Charger

USB3-PORT2

C C

USB2-PORT1

P26

DDR3L-1600

DDR3L-1600

SATA1

SATA2

USB 3.0

Intel

Haswell ULT

Broadwell ULT

+

eDP

HDMI

PCIE

PCI-Express Gen2

PCIE 4

Giga-LAN

RTL8111G

Level shifter

Lynx Point-LP

WLAN

Touch Screen

CAMERA

BT

B B

P19

P30

P24

PORT3

PORT4

PORT5

USB 2.0

BGA1168

(40mm X 24mm)

P3~P14

RJ45

HD-AUDIO

Audio CODEC

ALC286S-VC1

P21

SD-XC/UHS-II

NFC

P23

SPI ROM

8MB

P11

Power button/B

LEDs

A A

5

Power LED

Wireless

device LED

SATA LED

Battery LED

SD Card

Access LED

SMBUS

SPI

TPM 2.0

SLB9665

Buttons

Power SW

VOLUME SW Up

VOLUME SW Dw

4

P18

LPC

EC

ITE8528

P29

PECI

2W + 2W SPK

DMIC on Web Camera

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

PROJECT :

Block Diagram

Block Diagram

Block Diagram

MY6

MY6

MY6

1 46

1 46

1

1 46

H

H

H

SPI

D/A

3

SPI ROM

1MB

FAN

P29

P31

Headset

2

Page 2

1

2

3

4

5

6

7

8

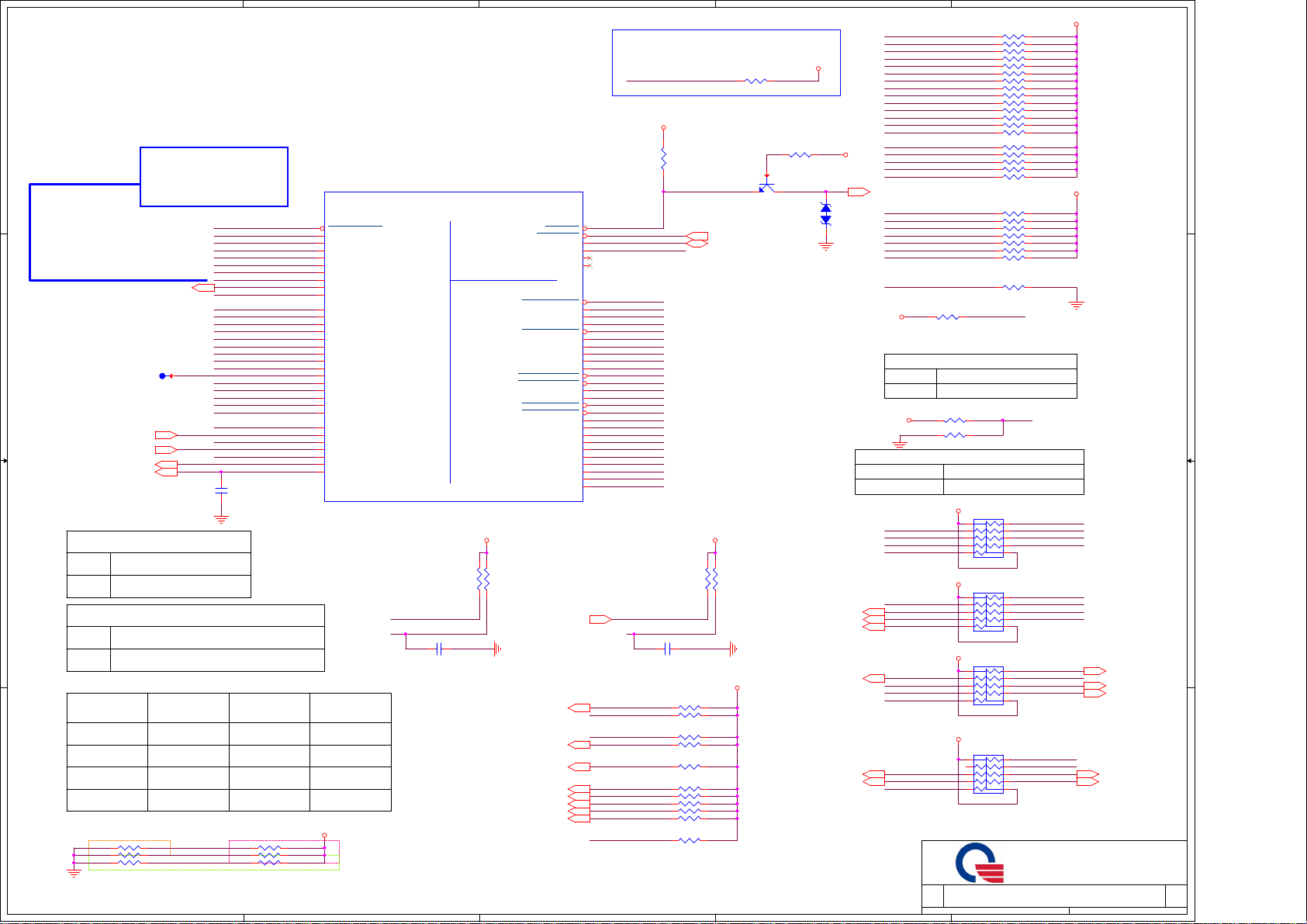

Table of Contents

PAGE DESCRIPTION

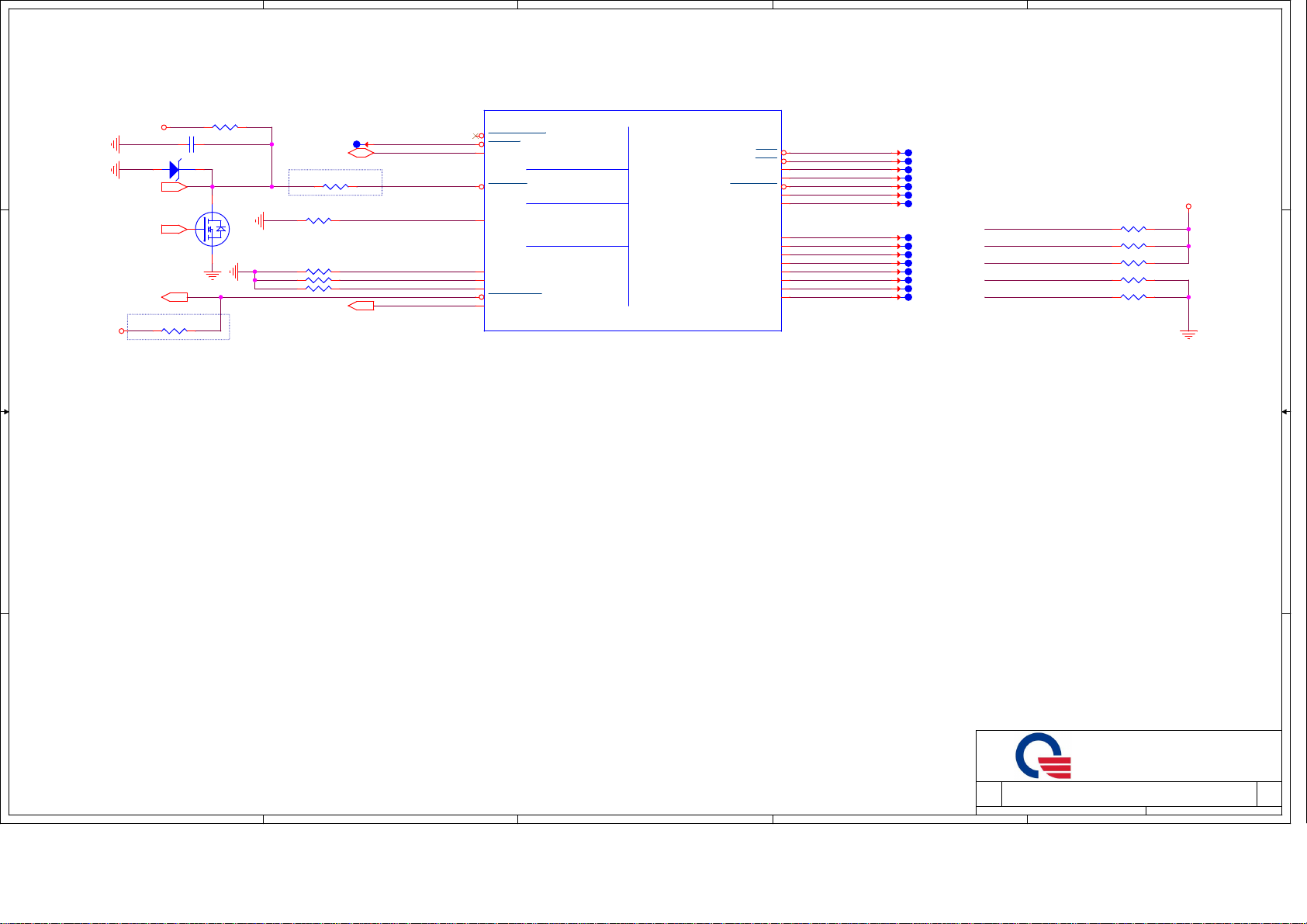

01

Schematic Block Diagram

02

Front Page

HSW MCP(Display/eDp)

03

HSW MCP(Memory)

04

HSW MCP(Gnd/Daisy/Rsvd)

05

A A

06

HSW MCP(CFG)

07

HSW MCP(Sideband/XDP)

08

HSW MCP(Power)

09

HSW PCH(RTC/HDA/SATA)

10

HSW PCH(PCIE/USB)

11

HSW PCH(CLK/LPC/SPI/SMB)

12

HSW PCH(GPIO/LPIO/MISC)

HSW PCH(Power Management)

13

14

HSW PCH(Power)

15

DDR3 SODIMM-0

16

DDR3 SODIMM-1

17

HDMI

18

TPM

19

B B

C C

Panel Control/Touch

20

HDD/ODD

21

AUDIO(ALC286S-VC1)

22

EMI

23

NFC

24

MINI PCIE(WLAN/BT)

25

Card Reader(OZ777FJ2-B)

26

USB 3.0 CONN

27

USB3.0 Conenctor/Charge

28

RTL8111G

EC(IT8528)

29

LED/Camera

30

FAN/NUT

31

CPU Core (ISL95813HRZ)ULT

32

POWER 3VS5&5VS5(TPS51427A)

33

Power +1.35V_SUS/DDR_VTTERM

34

Power +1.05V/+1.5V

35

36

Power Thermal Protection

37

Power AD IN

38

PWR Charger (OZ8682)

39

Discharger

40

Load SW

41

Clock Distribution

42

Power Sequence

43

Power Tree

SMBUS Address

44

RESET MAP

45

Change List

46

Power S0

+5VPCU

+3VPCU

3V_WLAN

5V_S5

3V_S5

+1.35V_SUS

+0.675V_DDR_VTT 0.675V S3_ON

DDR_VTTREF V0.675V

+1.05V 1.05V

1.5V_S0

5V_S0 5V 15V_S0_ON1

3V_S0

+VCC_CORE BY VID

Note1 : Deoend on WOL

F/W List

Location

BIOS/ME

EC

U2

U25

Voltage Rails

Voltage

5V

3.3V

3.3V

5V

3.3V

1.35V

1.5V

5V5V_S3

3.3V

Update method

Flash tool in Windows

Flash tool in Windows

V

V

V 15V_WLAN_ON

V V

V V

V

V

V

V

V

V

V

V

V

S3

V

V

Note1 Note1 Note1

V

V

V

Resister tolerance:

F :+/- 1%, (example:69.8K/F_4)

others are +/- 5%, (example:69.8K_4)

Capacitor tolerance:

X7R:+/- 10%

X5R: +/- 10%

Y5V: +80%~-20%

others are +/- 5%

S4

V

V

V

V

V

V

+5VPCU_6686

(TPS51427ARHBR)

+5VPCU_6686

(TPS51427ARHBR)

Ctl SignalS5

15V_LAN_ON3V_LAN 3.3V V Note1 Note1 Note1

15V_S5_ON

15V_S5_ON

S3_ON

S3_ON

S0_ON_2

S0_ON_1

15V_S3_ON

15V_S0_ON1

VRON

PCB STACK UP

6L

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : VCC

LAYER 6 : BOT

02

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

1

2

3

4

5

6

Wednesday, November 05, 2014

7

PROJECT :

Frontpage

Frontpage

Frontpage

MY6

MY6

MY6

2 46

2 46

2 46

8

H

H

H

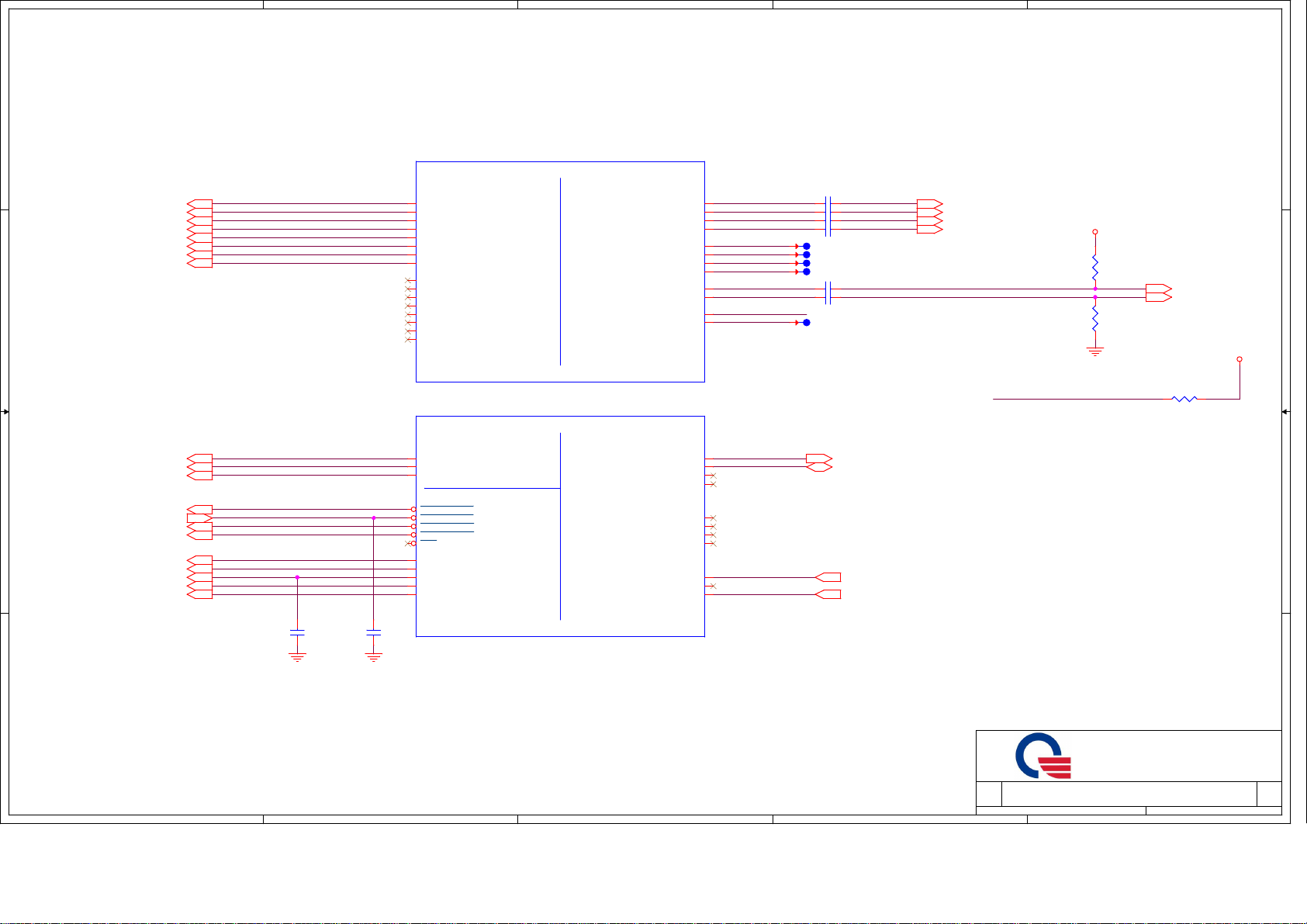

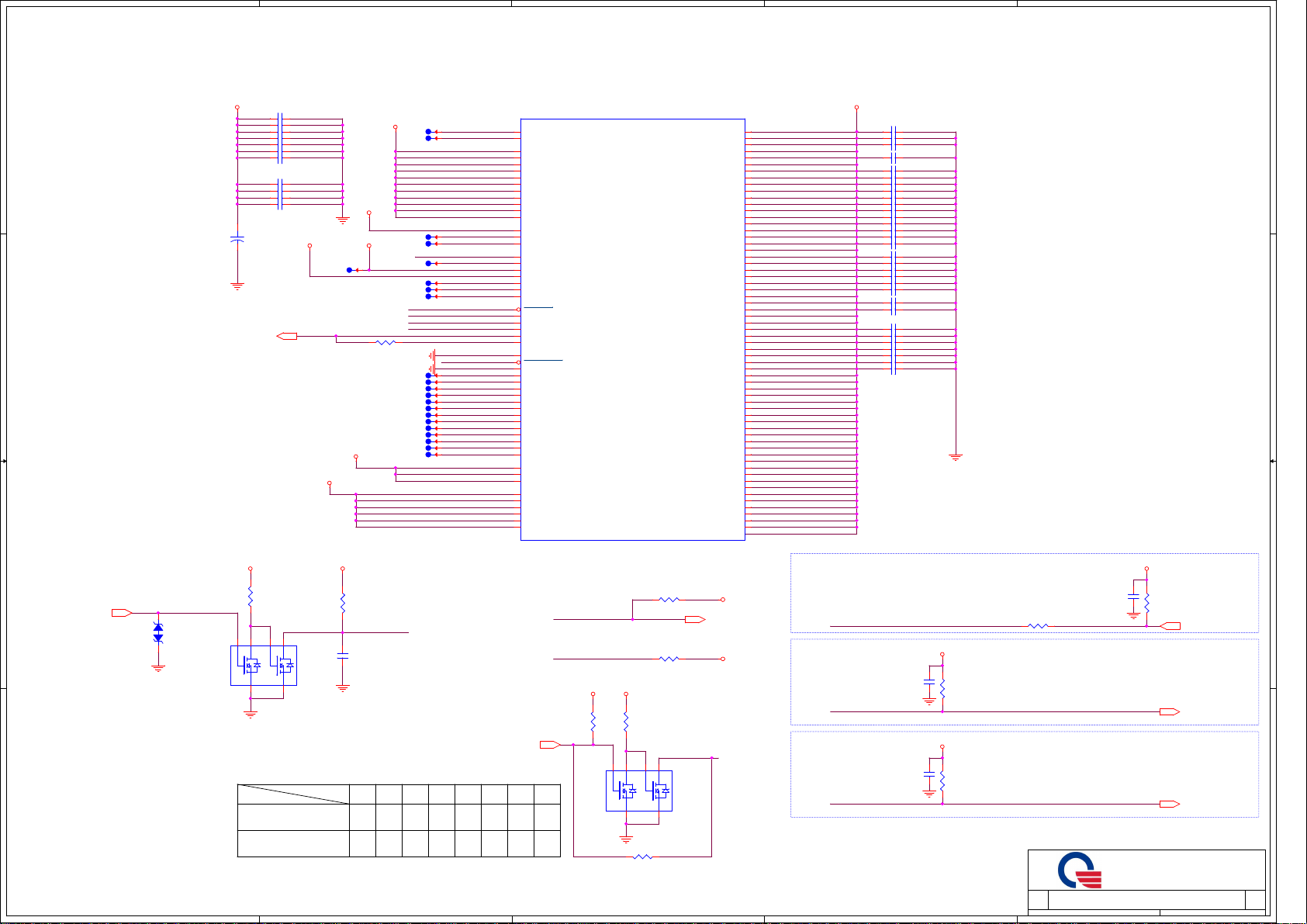

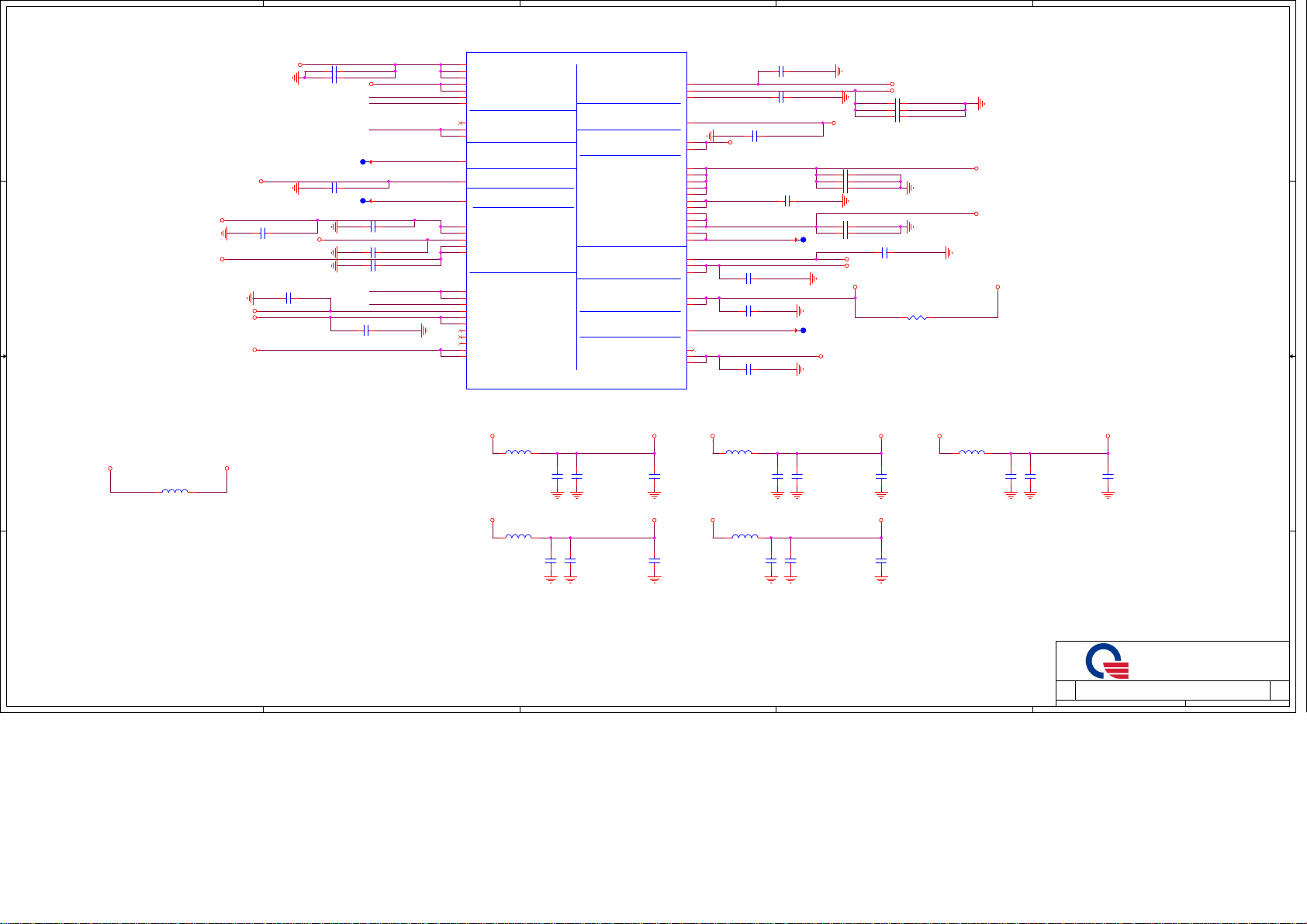

Page 3

5

4

3

2

1

03

D D

Haswell ULT (DISPLAY)

PCIE

HSW_ULT_DDR3L

1 OF 19

HSW_ULT_DDR3L

9 OF 19

EDPDDI

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_TXN0_C

EDP_TXP0_C

EDP_TXN1_C

EDP_TXP1_C

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN_C

EDP_AUXP_C

EDP_COMP

DP_UTIL

C4 0.1U/10V/X5R_4

C5 0.1U/10V/X5R_4

C6 0.1U/10V/X5R_4

C8 0.1U/10V/X5R_4

TP1

TP2

TP3

TP4

C13 0.1U/10V/X5R_4

C14 0.1U/10V/X5R_4

TP130

INT_HDMI_SCL (17)

INT_HDMI_SDA (17)

INT_HDMI_HPD_Q (17)

EDP_HPD (19,29)

EDP_TXN0 (19)

EDP_TXP0 (19)

EDP_TXN1 (19)

EDP_TXP1 (19)

3V_S0

R498

*100K_4

1 2

R497

*100K_4

1 2

EDP_COMP

EDP_COMP MUST PU VCCIOA_OUT

EDP_AUXN (19)

EDP_AUXP (19)

R1 24.9/F_4

+VCCIOA_OUT

U1A

INT_HDMI_TXDN2(17)

INT_HDMI_TXDP2(17)

INT_HDMI_TXDN1(17)

INT_HDMI_TXDP1(17)

INT_HDMI_TXDN0(17)

INT_HDMI_TXDP0(17)

INT_HDMI_TXCN(17)

INT_HDMI_TXCP(17)

C C

EDP_BKLCTL(19)

EDP_BKLEN(19,29)

EDP_ENVDD(19,29)

B B

PCH_GPIO77(12)

EC_A20GATE(12,29)

PCH_GPIO79(12)

PCH_GPIO80(12)

GPIO55(12)

GPIO52(12)

CR_WAKE#(12,25)

PCH_GPIO51(12)

PCH_GPIO53(12)

EDP_BKLCTL

EDP_BKLEN

EDP_ENVDD

PCH_GPIO77

EC_A20GATE

PCH_GPIO79

PCH_GPIO80

GPIO55

GPIO52

CR_WAKE#

PCH_GPIO51

PCH_GPIO53

C488

*0.1U/10V/X7R_4

2

*0.1U/10V/X7R_4

1

C491

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

8

B

A9

C6

U6

P4

N4

N2

A

D4

U7

L1

L3

R5

L4

2

1

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U1I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

eDP SIDEBAND

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

5

4

3

2

Wednesday, November 05, 2014

PROJECT :

HSW MCP(Display/eDP)

HSW MCP(Display/eDP)

HSW MCP(Display/eDP)

1

MY6

MY6

MY6

3 46

3 46

3 46

H

H

H

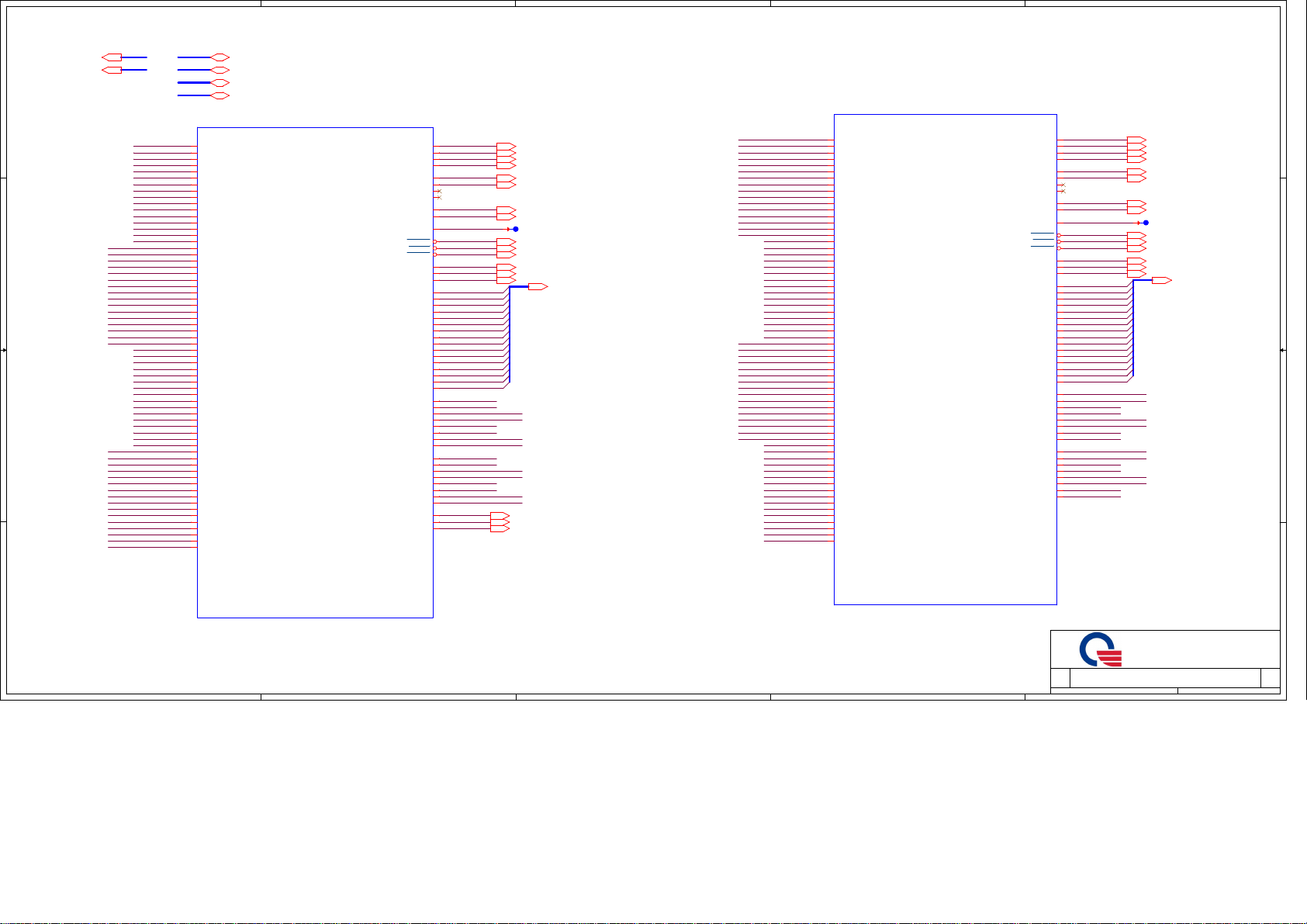

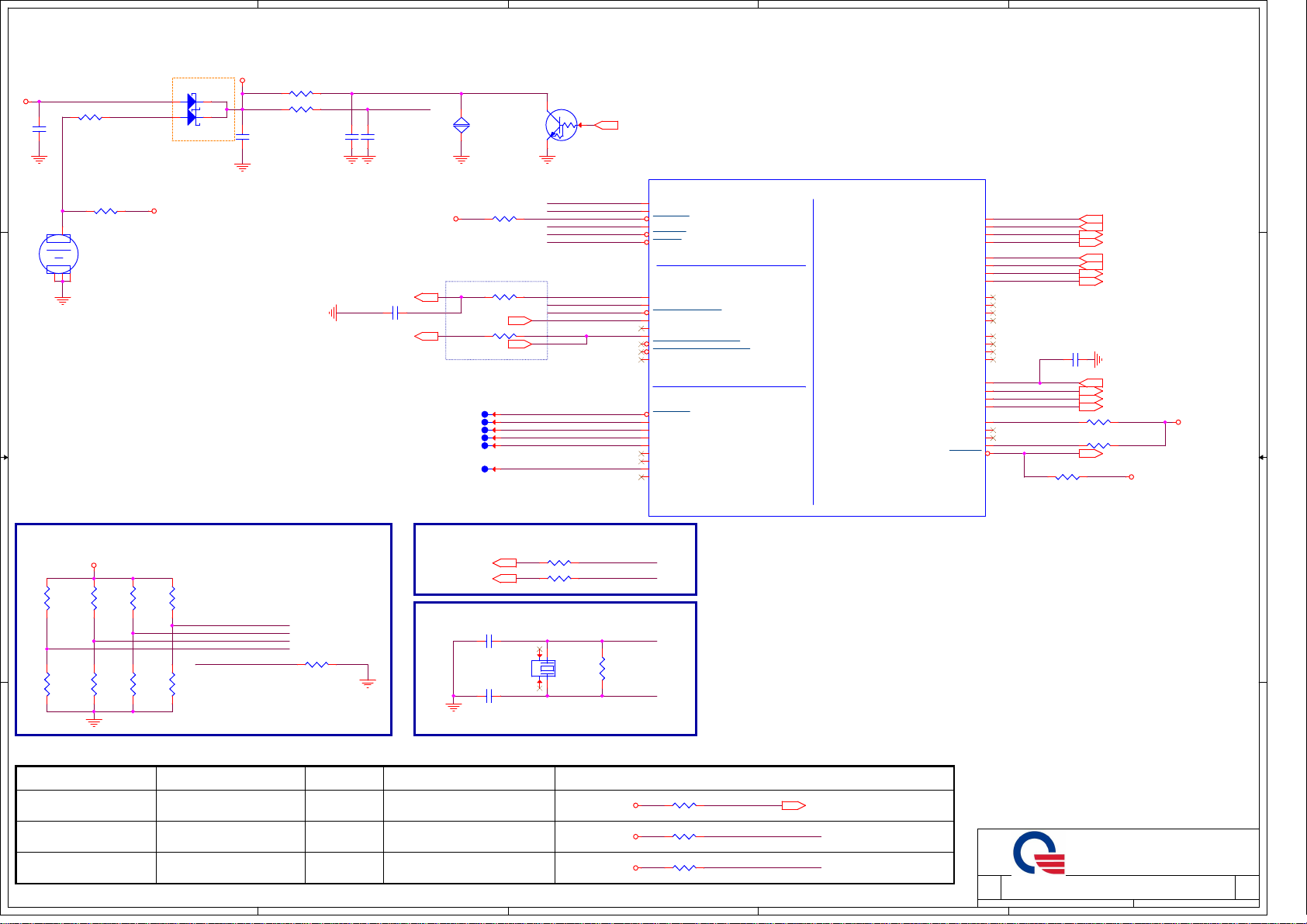

Page 4

5

4

3

2

1

Haswell ULT (DDR3L Interleaved PIN)

M_A_DQ[63:0](15)

M_B_DQ[63:0](16)

D D

AH63

M_A_DQ0

AH62

M_A_DQ1

AK63

M_A_DQ2

AK62

M_A_DQ3

AH61

M_A_DQ4

AH60

M_A_DQ5

AK61

M_A_DQ6

AK60

M_A_DQ7

AM63

M_A_DQ8

AM62

M_A_DQ9

AP63

M_A_DQ10

AP62

M_A_DQ11

AM61

M_A_DQ12

AM60

M_A_DQ13

AP61

M_A_DQ14

AP60

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

M_B_DQ0

M_B_DQ1

M_B_DQ2

C C

B B

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

U1C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

M_A_DQSN[7:0] (15)

M_A_DQSP[7:0] (15)

M_B_DQSN[7:0] (16)

M_B_DQSP[7:0] (16)

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_CLKN0

M_A_CLKP0

M_A_CLKN1

M_A_CLKP1

M_A_CKE0

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_ODT0_CPU

M_A_RAS#

M_A_WE#

M_A_CAS#

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQSN0

M_A_DQSN1

M_B_DQSN0

M_B_DQSN1

M_A_DQSN2

M_A_DQSN3

M_B_DQSN2

M_B_DQSN3

M_A_DQSP0

M_A_DQSP1

M_B_DQSP0

M_B_DQSP1

M_A_DQSP2

M_A_DQSP3

M_B_DQSP2

M_B_DQSP3

M_A_CLKN0 (15)

M_A_CLKP0 (15)

M_A_CLKN1 (15)

M_A_CLKP1 (15)

M_A_CKE0 (15)

M_A_CKE1 (15)

M_A_CS#0 (15)

M_A_CS#1 (15)

TP5

M_A_RAS# (15)

M_A_WE# (15)

M_A_CAS# (15)

M_A_BS#0 (15)

M_A_BS#1 (15)

M_A_BS#2 (15)

M_A_A[15:0] (15)

SM_VREF_CA (16)

SM_VREF_DQ0 (15)

SM_VREF_DQ1 (16)

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

U1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_B_CLKN0

M_B_CLKP0

M_B_CLKN1

M_B_CLKP1

M_B_CKE0

M_B_CKE1

M_B_CS#0

M_B_CS#1

M_B_ODT0_CPU

M_B_RAS#

M_B_WE#

M_B_CAS#

M_B_BS#0

M_B_BS#1

M_B_BS#2

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_A_DQSN4

M_A_DQSN5

M_B_DQSN4

M_B_DQSN5

M_A_DQSN6

M_A_DQSN7

M_B_DQSN6

M_B_DQSN7

M_A_DQSP4

M_A_DQSP5

M_B_DQSP4

M_B_DQSP5

M_A_DQSP6

M_A_DQSP7

M_B_DQSP6

M_B_DQSP7

M_B_CLKN0 (16)

M_B_CLKP0 (16)

M_B_CLKN1 (16)

M_B_CLKP1 (16)

M_B_CKE0 (16)

M_B_CKE1 (16)

M_B_CS#0 (16)

M_B_CS#1 (16)

TP6

M_B_RAS# (16)

M_B_WE# (16)

M_B_CAS# (16)

M_B_BS#0 (16)

M_B_BS#1 (16)

M_B_BS#2 (16)

M_B_A[15:0] (16)

04

A A

5

3 OF 19

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

4

3

4 OF 19

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

2

Wednesday, November 05, 2014

PROJECT :

HSW MCP(Memory)

HSW MCP(Memory)

HSW MCP(Memory)

MY6

MY6

MY6

H

H

4 46

4 46

1

4 46

H

Page 5

5

4

3

2

1

Haswell ULT (GND)

05

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U1O

HSW_ULT_DDR3L

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D50

D51

D53

D54

D55

D57

D59

D62

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

G18

G22

H13

D5

D8

G3

G5

G6

G8

HSW_ULT_DDR3L

D D

C C

B B

A11

A14

A18

A24

A28

A32

A36

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG1 1

AG2 1

AG2 3

AG6 0

AG6 1

AG6 2

AG6 3

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U1N

14 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U1P

HSW_ULT_DDR3L

16 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_SENSE

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M2 2

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

AU44

AV44

AT2

D15

F22

H22

J21

R3

100/F_4

U1R

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSS_SENSE (32)

HSW_ULT_DDR3L

18 OF 19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

U1Q

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

5

TP_DC_TEST_AY60

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_B2

DC_TEST_A3_B3

DC_TEST_A61_B61

DC_TEST_B62_B63

DC_TEST_C1_C2

TP8

TP10

A A

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61

DAISY_CHAIN_NCTF_AY61

AY62

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B61

DAISY_CHAIN_NCTF_B61

B62

DAISY_CHAIN_NCTF_B62

B63

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

HSW_ULT_DDR3L

17 OF 19

4

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW1

DAISY_CHAIN_NCTF_AW2

DAISY_CHAIN_NCTF_AW3

DAISY_CHAIN_NCTF_AW61

DAISY_CHAIN_NCTF_AW62

DAISY_CHAIN_NCTF_AW63

A3

A4

A60

A61

A62

AV1

AW1

AW2

AW3

AW61

AW62

AW63

DC_TEST_A3_B3

TP_DC_TEST_A4

TP_DC_TEST_A60

DC_TEST_A61_B61

TP_DC_TEST_A62

TP_DC_TEST_AV1

TP_DC_TEST_AW1

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_AW63

3

TP7

TP9

TP11

TP12

TP13

TP14

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

2

Wednesday, November 05, 2014

PROJECT :

HSW MCP(GND/RSVD)

HSW MCP(GND/RSVD)

HSW MCP(GND/RSVD)

1

MY6

MY6

MY6

5 46

5 46

5 46

H

H

H

Page 6

5

4

3

2

1

U1S

HSW_ULT_DDR3L

06

TP15

TP18

TP20

TP16

D D

C C

TP21

TP23

TP25

TP27

TP28

TP30

TP32

TP33

TP35

TP36

TP37

TP38

TP40

TP41

TP42

R5 49.9/F_4

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

NOA_STBN_0

NOA_STBN_1

NOA_STBP_0

NOA_STBP_1

NOA_RCOMP

TD_IREF

R6

8.2K/F_4

AC60

AC62

AC63

AA63

AA60

AA62

AA61

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

U63

U62

V63

H18

B12

A5

E1

D1

J20

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

TD_IREF

RESERVED

PROC_OPI_RCOMP

19 OF 19

Processor Strapping

1 0

CFG[2:0]

Reserved configuration lane.

(DEFAULT) NORMAL OPERATION; NO STALL STALL

(DEFAULT) NORMAL OPERATION PCH-LESS MODE

CFG0

CFG1

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

R7 *1K_4

R8 *1K_4

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

MCP_RSVD_19

MCP_RSVD_20

MCP_RSVD_21

MCP_RSVD_22

MCP_RSVD_23

MCP_RSVD_24

MCP_RSVD_25

MCP_RSVD_26

PROC_OPI_COMP

TP17

TP19

TP22

TP24

TP26

TP29

TP31

TP34

R4 49.9/F_4TP39

CFG[3]

MSR Privacy Bit Feature

B B

A A

CFG[4]

DISPLAY PORT PRESENCE STRAP

CFG[19:5]

Reserved configuration lanes.

5

CFG 8

ALLOW THE USE OF NOA

ON LOCKED UNITS

CFG9

NO SVID PROTOCOL

CAPABLE VR CONNECTED

CFG10

SAFE

MODE

BOOT

(DEFAULT) Debug Capability is determined by

IA32_Debug_Interface_MSR (0xC80) bit[0] setting

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO

EMBEDDED DISPLAY PORT

DISABLED(DEFAULT); IN THIS CASE,

NOA WILL BE DISABLED IN LOCKED

UNITS AND ENABLED IN UN-LOCKED

UNITS

VRS SUPPORTING SVID PROTOCOL ARE

PRESENT

POWER FEATURES ACTIVATED

DURING RESET

4

IA32_Debug_Interface_MSR (0xC80) bit[0] default setting

overridden

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

NO VR SUPPORTING SVID IS PRESENT. THE

CHIP WILL NOT GENERATE (OR RESPOND TO)

SVID ACTIVITY

POWER FEATURES (ESPECIALLY CLOCK

GATINE ARE NOT ACTIVATED

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

3

CFG3

R9 *1K_4

CFG4

R10 1K_4

CFG8

R11 *1K_4

CFG9

R12 *1K_4

CFG10

R13 *1K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

2

Wednesday, November 05, 2014

PROJECT :

HSW MCP(CFG)

HSW MCP(CFG)

HSW MCP(CFG)

1

MY6

MY6

MY6

6 46

6 46

6 46

H

H

H

Page 7

5

4

3

2

1

07

DSW

MISC

THERMAL

PWR

DDR3L

HSW_ULT_DDR3L

JTAG

2 OF 19

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

XDP_PRDY_N

XDP_PREQ_N

XDP_TCK0

XDP_TMS_CPU

XDP_TRST_CPU_N

XDP_TDI_CPU

XDP_TDO_CPU

XDP_BPM0_R

XDP_BPM1_R

XDP_BPM2_R

XDP_BPM3_R

XDP_BPM4_R

XDP_BPM5_R

XDP_BPM6_R

XDP_BPM7_R

TP44

TP45

TP46

TP47

TP48

TP49

TP50

TP51

TP52

TP53

TP54

TP55

TP56

TP57

TP58

XDP_TDO_CPU

XDP_TDI_CPU

XDP_TMS_CPU

XDP_TCK0

XDP_TRST_CPU_N

+1.05V

R17 51/F_4

R18 *51_4

R19 *51_4

R22 51/F_4

R24 51/F_4

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

U1B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

D D

C C

+1.35V_SUS

+1.05V

*TVS DIODE

D1

H_PROCHOT#(32)

H_PROCHOT_EC(29)

SM_DRAMRST#(16)

R14 62_4

C15 *47P/50V/NPO_4

2 1

2

R177 470/F_4

12

3

Q1

NX7002AKW(SOT323)

1

TP43

PECI_EC_R(29)

R15 56_4

Close to CPU

R16 10K_4

R20 200/F_4

R21 121/F_4

1 2

R23 100/F_4

DDR_PG_CTRL(15)

CATERR#

CPU_PROCHOT#

H_CPUPWRGD

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST#

DDR_PG_CTRL

Close to CN_DDR1

B B

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

5

4

3

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

PROJECT :

PROJECT :

PROJECT :

HSW MCP(Sideband)

HSW MCP(Sideband)

HSW MCP(Sideband)

1

MY6

MY6

MY6

7 46

7 46

7 46

H

H

H

Page 8

5

4

3

2

1

08

CPU VDDQ

TP64

+VCC_CORE

+1.05V3V_S5

+VCC_CORE

+VCCIO_OUT

+1.05V

R32

10K_4

VCCST_PWRGD

C53

*0.1u/10V/X5R_4

O O O

X X X

Haswell ULT 15W : 4.2A

+1.35V_SUS

TP59

MCP_RSVD_61

MCP_RSVD_62

TP60

MCP_RSVD_63

TP61

MCP_RSVD_64

TP62

VCC_SENSE

TP63

MCP_RSVD_65

TP65

MCP_RSVD_66

MCP_RSVD_67

TP66

TP67

MCP_RSVD_68

H_CPU_SVIDALRT_N

VR_SVID_CLK

VR_SVID_DATA

VCCST_PWRGD

TP68

TP69

TP70

TP71

TP72

TP73

TP74

TP75

TP76

TP77

TP78

TP79

TP80

VR_READY

FIVR_EN_BUF

MCP_RSVD_69

MCP_RSVD_70

MCP_RSVD_71

MCP_RSVD_72

MCP_RSVD_73

MCP_RSVD_74

MCP_RSVD_75

MCP_RSVD_76

MCP_RSVD_77

MCP_RSVD_78

MCP_RSVD_79

MCP_RSVD_80

MCP_RSVD_81

R25 1.5K_4

VCCST (0.1A)

R582

X

O

4

R583

O

X

R584 Q68

+1.35V_SUS

C336 10P/50V/C0G_4

D D

C C

B B

EC_PWROK(13,29)

A A

6X10UF MLCC

4X2.2UF MLCC

D36

*PESD5V0U1BB

1 2

NX7002AKS

C16 10u/6.3V/X5R_6

C17 10u/6.3V/X5R_6

C18 10u/6.3V/X5R_6

C19 10u/6.3V/X5R_6

C20 10u/6.3V/X5R_6

C21 10u/6.3V/X5R_6

C23 2.2u/6.3V/X5R_4

C32 2.2u/6.3V/X5R_4

C24 2.2u/6.3V/X5R_4

C26 2.2u/6.3V/X5R_4

12

+

C493

H_VR_ENABLE_MCP(32)

VR_EN(1.05V): Output to disable VR in C10

VR_Ready(1.05v):

5

Q2

Type R33 R34 Q3

+VCCIOA_OUT

*330U/2.5V/3528/ESR=9_KEN

R31

100K_4

6

2

1

4 3

Location

IMVP_PWRGD(3V)

IMVP_PWRGD(1.05V)

5

Haswell ULT MCP(POWER)

VCC_SENSE

FIVR_EN_BUF

HSW_ULT_DDR3L

R33

100K_4

Q3

NX7002AKS

HSW ULT POW ER

12 OF 19

3V_S53V_S0

R34

100K_4

5

4 3

R582 *0_4

L59

J58

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

F59

N58

AC58

E63

AB23

A59

E20

AD23

AA23

AE59

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

AD60

AD59

AA59

AE60

AC59

AG58

U59

V59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

IMVP_PWRGD(29,32)

X X

O O

U1L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

PR12

X

O

R26 100/F_4

R29 150/F_4

VR_READY

6

2

1

3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

+VCC_CORE

VCC_SENSE (32)

+1.05V

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

CPU VCC

Haswell ULT 15W : 32A

+VCC_CORE

SVID ALERT

H_CPU_SVIDALRT_N

SVID DATA

VR_SVID_DATA

SVID CLK

VR_SVID_CLK

C337 10P/50V/C0G_4

C27 22u/6.3V/X5R_6

C28 22u/6.3V/X5R_6

C29 22u/6.3V/X5R_6

C30 22u/6.3V/X5R_6

C22 22u/6.3V/X5R_6

C31 22u/6.3V/X5R_6

C33 22u/6.3V/X5R_6

C25 22u/6.3V/X5R_6

C34 22u/6.3V/X5R_6

C35 22u/6.3V/X5R_6

C36 22u/6.3V/X5R_6

C37 22u/6.3V/X5R_6

C38 22u/6.3V/X5R_6

C39 22u/6.3V/X5R_6

C40 22u/6.3V/X5R_6

C41 22u/6.3V/X5R_6

C42 22u/6.3V/X5R_6

C43 22u/6.3V/X5R_6

C44 22u/6.3V/X5R_6

C45 22u/6.3V/X5R_6

C46 22u/6.3V/X5R_6

C47 22u/6.3V/X5R_6

C48 22u/6.3V/X5R_6

C49 *22u/6.3V/X5R_6

C50 *22u/6.3V/X5R_6

C51 *22u/6.3V/X5R_6

C477 *22u/6.3V/X5R_6

C478 *22u/6.3V/X5R_6

C476 *22u/6.3V/X5R_6

C479 *22u/6.3V/X5R_6

+1.05V

2

C33 3

0.1U/10V/X7R_4

0.1U/10V/X7R_4

1

+1.05V

2

C33 4

1

2

23 X 22UF(0805 MLCC)

close to CPU

R28 43_4

12

close to CPU

R30

130_4

Close to CPU

R35

*54.9_4

+1.05V

2

C52

0.1U/10V/X7R_4

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

Size Doc ument Num ber R ev

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Wednesday, November 05, 2014

Dat e: Sheet o f

Wednesday, November 05, 2014

Dat e: Sheet o f

Wednesday, November 05, 2014

R27

1

75/F_4

VR_SVID_ALERT# (32)

VR_SVID_DATA (32)

VR_SVID_CLK (32)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

HSW MCP(Power)

HSW MCP(Power)

HSW MCP(Power)

MY6

MY6

MY6

8 46

8 46

1

8 46

H

H

H

Page 9

5

4

3

2

1

RTC Circuitry(RTC)

ES2-22

+3V_RTC_[0:2]

+3VPCU

D D

C C

Trace width = 20 mils

R38 1K_4

1

C515

0.1U/10V/X7R_4

2

R540 1K_4

1

CN1

85204-0200L

324

+3V_RTC_1

RTC_3V

D43 RB500V-40

D44 RB500V-40

+3V_RTC

1u/10V/X5R_4

20MIL

R36 20K/F_4

R37 20K/F_4

C54

1u/10V/X5R_4

C55

RTC_RST#

SRTC_RST#

C56

1u/10V/X5R_4

+3V_RTC

HDA_BITCLK(21)

C361 *33P/50V/_4

HDA_SDOUT(21)

12

J1

*SHORT_ PAD1

R42 1M_4

Close to CPU

R44 33_4

HDA_SDIN0(21)

R45 33_4

HDA_SDOUT_C(29)

TP81

TP83

TP84

TP85

TP86

2

Q62

*DDTC144EUA-7-F

1 3

RTC_X1

RTC_X2

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BITCLK_C

HDA_SYNC_C

HDA_RST#_C

HDA_SDOUT_C

PCH_XDP_TRST_CPU_N

PCH_XDP_TCK1

PCH_XDP_TDI

PCH_JTAG_TDO

PCH_XDP_TMS

PCH_JTAGX

Haswell ULT (RTC, HDA, JTAG, SATA)

CLR_CMOS (29)

U1E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

HSW_ULT_DDR3L

RTC

AUDIO SAT A

JTAG

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

+3V

+3V

+3V

+3V

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

C490 0.1U/10V/X7R_4

SATA_IREF

SATA_RCOMP

R328 10K

SATA_RXN0 (20)

SATA_RXP0 (20)

SATA_TXN0 (20)

SATA_TXP0 (20)

SATA_RXN1 (20)

SATA_RXP1 (20)

SATA_TXN1 (20)

SATA_TXP1 (20)

12

EC_EXT_SMI# (12,29)

GPIO35 (12)

GPIO36 (12)

GPIO37 (12)

R535 *0/short_4TP82

1 2

R46 3.01K/F_4

SATA_ACT# (30)

3V_S0

09

HDD

ODD

+V1.05S_ASATA3PLL

5 OF 19

PCH JTAG Debug (CLG)

R49

*210/F_4

R55

*100/F_4

3V_S5

R50

*210/F_4

R56

*100/F_4

R51

*210/F_4

R57

*100/F_4

R52

*210/F_4

FB ID: Q-00078

PCH_JTAG_TDO

PCH_XDP_TMS

PCH_XDP_TDI

PCH_JTAGX

PCH_XDP_TCK1

R58

*100/F_4

R53 *51/F_4

B B

HDA_SYNC(21)

HDA_RST#(21)

Close to CPU

C57 15P/50V/_4

C58 15P/50V/_4

R47 33_4

R48 33_4

23

Y1

32.768KHZ

4 1

HDA_SYNC_C

HDA_RST#_C

RTC_X1

R54

10M_4

RTC_X2

PCH Strap Table

Pin Name Strap description

A A

SPKR

HDA_SDO

INTVRMEN

No reboot mode setting PWROK

Flash Descriptor Security

Override / Intel ME Debug Mode

Integrated 1.05V VRM enable ALWAYS

5

Sampled

PWROK

Configuration note

0 = Default (weak pull-down 20K)

1 = Setting to No-Reboot mode

0 = Security Effect (Int PD)

1 = Can be Override

Should be always pull-up

4

3V_S0

3V_S5

+3V_RTC

R59 *1K_4

R60 *1K_4

R61 330K_4

3

HDA_SDOUT_C

PCH_INTVRMEN

ACZ_SPKR (12)

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

2

Wednesday, November 05, 2014

PROJECT :

HSW PCH(RTC/HDA/SATA)

HSW PCH(RTC/HDA/SATA)

HSW PCH(RTC/HDA/SATA)

1

MY6

MY6

MY6

9 46

9 46

9 46

H

H

H

Page 10

5

4

3

2

1

Haswell ULT (PCIE,USB)

10

HSW_ULT_DDR3L

PCIE USB

+3V_S5

+3V_S5

+3V_S5

+3V_S5

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

RSVD

RSVD

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB_BIAS

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USBP0- (27)

USBP0+ (27)

USBP1- (26)

USBP1+ (26)

USBP3- (19)

USBP3+ (19)

USBP4- (30)

USBP4+ (30)

USBP5- (24)

USBP5+ (24)

USB30_RX1- (27)

USB30_RX1+ (27)

USB30_TX1- (27)

USB30_TX1+ (27)

USB30_RX2- (26)

USB30_RX2+ (26)

USB30_TX2- (26)

USB30_TX2+ (26)

R62 22.6/F_4

USB_OC0# (27)

USB_OC1# (26)

C489

*0.1U/10V/X7R_4

USB3.0 Port 1 with Charge

USB3.0 Port 2

Touch Screen (Full Speed)

CAMERA

BT

USB3.0 Port 1

USB3.0 Port 2

2

1

USB_OC3#

USB_OC1#

USB_OC2#

USB_OC0#

R63 10K_4

R64 10K_4

R65 10K_4

R67 10K_4

3V_S5

D D

C C

PCIE_RXN3(24)

WiFi/BT

LAN

B B

Card Reader

PCIE_RXP3(24)

PCIE_TXN3(24)

PCIE_TXP3(24)

PCIE_RXN4(28)

PCIE_RXP4(28)

PCIE_TXN4(28)

PCIE_TXP4(28)

PCIE_RXN2(25)

PCIE_RXP2(25)

PCIE_TXN2(25)

PCIE_TXP2(25)

+V1.05S_AUSB3PLL

R66 3.01K/F_4

R536 *0/short_4

C59 0.1u/10V/X5R_4

C60 0.1u/10V/X5R_4

C462 0.1u/10V/X5R_4

C463 0.1u/10V/X5R_4

C61 0.1u/10V/X5R_4

C62 0.1u/10V/X5R_4

1 2

PCIE_TXN3_C

PCIE_TXP3_C

PCIE_TXN4_C

PCIE_TXP4_C

PCIE_TXN2_C

PCIE_TXP2_C

PCIE_RCOMP

PCIE_IREF

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD

E13

RSVD

A27

PCIE_RCOMP

B27

PCIE_IREF

U1K

A A

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

5

4

11 OF 19

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

3

2

Wednesday, November 05, 2014

PROJECT :

HSW PCH(PCIE/USB)

HSW PCH(PCIE/USB)

HSW PCH(PCIE/USB)

1

MY6

MY6

MY6

10 46

10 46

10 46

H

H

H

Page 11

5

4

3

2

1

R556

1K_4

C484

*12p/50V_4

11

3V_S5

NFC_CLK (23)

NFC_DAT (23)

Haswell ULT (CLK)

C63 12P/50V/_4

4

R68

1M_4

SPD

NFC

TP119

TP120

TP121

3

1

2

C64 12P/50V/_4

C65

*10/u/6.3V/X5R_6

C66

15p/50V_4

SML1CLK (29)

SML1DATA (29)

C486

*12p/50V_4

Y2

24MHz

+V1.05S_AXCK_LCPLL

C67

15p/50V_4

EC

SMB_NFC_CLK

SMB_NFC_DAT

C487

*12p/50V_4

CLKOUT_LPC_0 (29)

PCLK_DEBUG (24)

PCLK_TPM (18)

C351

*15p/50V_4

R102

100K_4

3V_S0

NFC-IRQ (23)

3V_S0

NX7002AKS

5

2

6

Q65

TESTLOW_0

TESTLOW_1

TESTLOW_2

TESTLOW_3

Do not short

the testlow pins together.

PCH_SMB0_ALERT#

PCH_SMB_ALERT#

SMB_NFC_CLK

SMB_NFC_DAT

R342 10K_4

R343 10K_4

R344 10K_4

R345 10K_4

R72 10K_4

R74 10K_4

R76 499_4

R77 499_4

Normal Mode -> 2.2K ohm

Fast Mode -> 499 ohm

Close to CON7

3V_S0

R557

1K_4

43

1

C485

*12p/50V_4

U1F

D D

PCIE_CLK_REQ0#(12)

CLK_PCIE_CRDN(25)

Card Reader

WiFi/BT

LAN

C C

CLK_PCIE_CRDP(25)

PCIE_CLK_REQ1#(12,25)

CLK_PCIE_WIFIN(24)

CLK_PCIE_WIFIP(24)

PCIE_CLK_REQ2#(12,24)

CLK_PCIE_LANN(28)

CLK_PCIE_LANP(28)

PCIE_CLK_REQ3#(12,28)

PCIE_CLK_REQ4#(12)

PCIE_CLK_REQ5#(12)

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

HSW_ULT_DDR3L

+3V

+3V

+3V

+3V

+3V

+3V

CLOCK

SIGNALS

6 OF 19

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

A25

XTAL24_IN

B25

XTAL24_OUT

K21

M2 1

C26

DIFFCLK_BIASREF

C35

TESTLOW_0

C34

TESTLOW_1

AK8

TESTLOW_2

AL8

TESTLOW_3

AN15

LPC_CLK_0

AP15

LPC_CLK_1

B35

TP87

A35

TP88

1 2

R69 3.01K/F_4

1 2

R70 22_4

1 2

R71 22_4

1 2

R73 *22_4

Close to CPU

Haswell ULT (LPC/SPI/SMB/CLINK)

U1G

LPC_LAD0(18,24,29)

LPC_LAD1(18,24,29)

LPC_LAD2(18,24,29)

LPC_LAD3(18,24,29)

LPC_LFRAME#(18,24,29)

B B

R565 33_4

R566 33_4

R567 33_4

R568 33_4

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

AU14

AW12

AY12

AW11

AV12

AA3

AC2

AA2

AA4

AF1

Y7

Y4

Y6

LAD0

LAD1

LAD2

LAD3

LFRAME

SPI_CLK

SPI_CS0

SPI_CS1

SPI_CS2

SPI_MOSI

SPI_MISO

SPI_IO2

SPI_IO3

SPI FLASH

3V_S5

C338*10P/50V_4N

3V_S5

3V_S5

HSW_ULT_DDR3L

LPC

SMBUS

+3V_S5

+3V_S5

+3V_S5

C-LINKSPI

+3V_S5

+3V_S5

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML1ALERT/PCHHOT/GPIO73

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

7 OF 19

CL_CLK

CL_DATA

CL_RST

AN2

PCH_SMB_ALERT#

AP2

R_PCH_SCLK

AH1

R_PCH_SDATA

AL2

PCH_SMB0_ALERT#

AN1

SMB_NFC_CLK

AK1

SMB_NFC_DAT

AU4

NFC-IRQ

AU3

AH3

AF2

AD2

AF4

3V_S5

SMBus/Pull-up(CLG)

R78

Close to CPU

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_IO2

A A

5VPGD(29,33)

SPI_WP#(12,29)

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

R82 15_4

R81 15_4

R83 15_4

R85 15_4

R86 0_4

R87 *0_4

5

10K_4

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_WP#

C339*22P/50V_4N

C340*10P/50V_4N

C341*10P/50V_4N

R79

1K_4

1

CE#

6

SCK

5

SI

2

SO

3

WP#

U2

W25Q64FVSSIQ

VDD

HOLD#

VSS

R354

R356

4.7K_4

C70

*12p/50V_4

3V_S0

NX7002AKS

5

2

6

Q5

43

1

C71

*12p/50V_4

2

8

7

PCH_SPI_HOLD#PCH_SPI_SO

4

C68

0.1u/10V/X5R_4

4

R80

1K_4

R84 15_4

Close to CPU

PCH_SPI_IO3

R_PCH_SCLK

R_PCH_SDATA

3

4.7K_4

C69

*12p/50V_4

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

R355

4.7K_4

R357

4.7K_4

PCH_SCLK (15,16)

PCH_SDATA (15,16)

C72

*12p/50V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

PROJECT :

HSW PCH(CLK/LPC/SPI/SMB)

HSW PCH(CLK/LPC/SPI/SMB)

HSW PCH(CLK/LPC/SPI/SMB)

1

MY6

MY6

MY6

11 46

11 46

11 46

H

H

H

Page 12

5

D D

GPIO27

With Intel LAN:

Connect to LANWAKE# pin on the LAN

Without Intel LAN:

Used to wake event from DSx

GPIO76

GPIO8

GPIO12

GPIO15

GPIO16

GPIO17

GPIO24

SIO_WAKE_GPIO27#

NFC_RST#(23)

C C

TP92

SIO_EXT_SCI#(29)

NFC_DWL_REQ(23)

SPI_WP#(11,29)

ACZ_SPKR(9)

NFC_RST#

GPIO26

GPIO56

GPIO57

GPIO58

GPIO59

GPIO44

GPIO47

BOARD_ID0

BOARD_ID1

BOARD_ID2

GPIO71

GPIO13

GPIO14

GPIO25

GPIO45

GPIO46

GPIO9

SIO_EXT_SCI#

GPIO33

NFC_DWL_REQ

GPIO38

GPIO39

C73

*100p/50V/X7R_4

AU 2

AM 7

AD 6

AD 5

AN 5

AD 7

AN 3

AG 6

AH 4

AM 4

AG5

AG 3

AM 3

AM 2

P1

Y1

T3

AP 1

AL 4

AT 5

AK 4

AB 6

U4

Y3

P3

Y2

AT 3

P2

C4

L2

N5

V2

No Reboot Strap(GPIO81)

B B

NC

PU

Default

EN

TLS CONFIDENTIALITY STRAP(GPIO15)

NC

PU

Default

EN

BOARD_ID0 BOARD_ID1 BOARD_ID2

ES1

1

ES2

PP

A A

MRT

0 1

0 0 0

ES2-25 PP-09

R127 10K_4

R129 10K_4

R131 10K_4

BOARD_ID0

BOARD_ID1

BOARD_ID2

1 1

10 1

0

R128 *10K_4

R130 *10K_4

R132 *10K_4

3V_S0

MRT-02

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

5

4

3

Hasswell ULT(GPIO,LPIO,MISC)

+3V

+3V

+3V

+3V

+3V

+3V

CLK_TP_SIO_L

GP IO

HSW_ULT_DDR3L

DSW

+3V

10 OF 19

3V_S0 3V_S0

R350

10K_4

C74 *12p/50V_4

CPU/

MI S C

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

SERIAL IO

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

R351

10K_4

PCIE_CLK_REQ4#(11)

EC_EXT_SMI#(9,29)

PCIE_CLK_REQ0#(11)

PCIE_CLK_REQ1#(11,25)

PCIE_CLK_REQ2#(11,24)

PCIE_CLK_REQ3#(11,28)

PCIE_CLK_REQ5#(11)

THRMTRIP

+3V

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

NFC_DETECT#(23)

GPIO37(9)

D60

PCH_THRMTRIP#

V4

T4

AW 1 5

AF 2 0

AB 2 1

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

PCIE_CLK_REQ4#

GPIO39

GPIO76

EC_EXT_SMI#

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

PCIE_CLK_REQ5#

GPIO16

3

U1J

BMBUSY/GPIO76

+3V_S5

GPIO8

LAN_PHY_PWR_CTRL/GPIO12

+3V_S5

GPIO15

+3V

GPIO16

+3V

GPIO17

+3V_S5

GPIO24

DSW

GPIO27

+3V_S5

GPIO28

+3V_S5

GPIO26

+3V_S5

GPIO56

+3V_S5

GPIO57

+3V_S5

GPIO58

+3V_S5

GPIO59

+3V_S5

GPIO44

+3V_S5

GPIO47

+3V

GPIO48

+3V

GPIO49

+3V

GPIO50

HSIOPC/GPIO71

+3V_S5

GPIO13

+3V_S5

GPIO14

DSW

GPIO25

+3V_S5

GPIO45

+3V_S5

GPIO46

+3V_S5

GPIO9

+3V_S5

GPIO10

DEVSLP0/GPIO33

SDIO_POWER_EN/GPIO70

DEVSLP1/GPIO38

DEVSLP2/GPIO39

SPKR/GPIO81

4

GPIO27

SIO_WAKE_GPIO27#

+1.05V

EC_RCIN#

IRQ_SERIRQ

PCH_OPIRCOMP

GPIO83

GPIO84

GPIO85

BBS

GPIO87

GPIO88

GPIO89

GPIO90

GPIO91

GPIO92

GPIO93

GPIO94

GPIO0

GPIO1

GPIO2

GPIO3

I2C0_SDA

I2C0_SCL

NFC_DETECT#

CLK_TP_SIO_L

GPIO64

GPIO65

GPIO66

GPIO67

GPIO68

GPIO69

NFC_DETECT#

I2C0_SDAI2C0_SCL

C75 *12p/50V_4

R346 10K_4

R347 10K_4

R348 10K_4

R349 10K_4

R120 10K_4

R121 10K_4

R122 10K_4

R123 10K_4

R124 10K_4

R125 10K_4

R126 10K_4

Deep Sx

R103

1K_4

R352

10K_4

R94 10K_4

1 3

EC_RCIN# (29)

IRQ_SERIRQ (18,29)

R353

10K_4

3V_S0

3V_S5

R105 1K_4

2

Q7

PMBT3904

PCH_GPIO53(3)

PCH_GPIO79(3)

2

GPIO Pull-up/Pull-down(CLG)

+1.05V

SHDN# (33,36)

D38

*PESD5V0U1BB

1 2

3V_S0

+V3.3S_1.8S_LPSS_SDIO

R119

R119_NC

CR_WAKE#(3,25)

GPIO52(3)

GPIO36(9)

GPIO55(3)

2

1

GPIO58

GPIO47

GPIO13

SIO_EXT_SCI#

GPIO24

GPIO25

GPIO26

GPIO15

GPIO12

GPIO8

GPIO56

GPIO45

GPIO9

GPIO46

GPIO59

GPIO44

NFC_RST#

GPIO14

GPIO57

EC_RCIN#

IRQ_SERIRQ

GPIO84

GPIO88

GPIO89

GPIO71

NFC_DWL_REQ

PCH_OPIRCOMP

R118 *1K_4

R88 10K_4

R89 10K_4

R90 10K_4

R91 10K_4

R92 10K_4

R93 10K_4

R561 10K_4

R95 *10K_4

R96 10K_4

R97 10K_4

R98 10K_4

R99 10K_4

R100 10K_4

R101 10K_4

R104 10K_4

R106 10K_4

R107 *10K_4

R108 10K_4

R109 10K_4

R110 10K_4

R111 10K_4

R112 10K_4

R113 10K_4

R114 10K_4

R115 10K_4

R116 10K_4

R117 49.9/F_4

BBS

3V_S5

3V_S0

Internal PD(BIOS strap)

GPIO86 (BBS)

PUPDLPC

SPI (Default IPD)

R119 *1K_4

R563 *1K_4

GPIO66

Internal PD

GPIO66

ENABLE

DISABLE(Default)

3V_S0

RP7

10

1

GPIO1

GPIO94

GPIO69

GPIO64

GPIO38

GPIO85

GPIO92

GPIO0

GPIO17

9

8

7 4

10K_x8

3V_S0

RP10

10

9

8

7 4

10K_x8

3V_S0

RP11

10

9

8

7 4

10K_x8

3V_S0

RP14

10

9

8

7 4

10K_x8

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

GPIO68

2

GPIO67

3

GPIO65

GPIO3

56

1

GPIO90

2

GPIO2

3

GPIO91

GPIO93

56

1

2

GPIO33

3

56

1

GPIO83

2

GPIO87

3

56

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

HSW PCH(GPIO/MISC)

HSW PCH(GPIO/MISC)

HSW PCH(GPIO/MISC)

MY6

MY6

MY6

1

12

PCH_GPIO80 (3)

EC_A20GATE (3,29)

GPIO35 (9)

PCH_GPIO51 (3)

PCH_GPIO77 (3)

12 46

12 46

12 46

H

H

H

Page 13

5

4

3

2

1

Haswell ULT (SYSTEM POWER MANAGEMENT)

DSWVRMEN

DPWROK

WAKE

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

R152

1 2

RSMRST#_R

C76 100P/50V_4

AW7

1 2

AV5

R139 *0/short_4

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

SLP_LAN#

TP98

TP99

TP100

TP101

PLTRST#

D4

*TVS DIODE

2 1

12

DSWVRMEN

PCIE_WAKE#

CLKRUN#

SUS_STAT#

SUS_CLK

SLP_S5#_R

MRT-03

RSMRST#SYS_RESET#

TP93

TP122

TP94

SLP_S4# (13,29)

SLP_S3# (13,29)

SLP_A# (13,29)

SLP_SUS# (13,29)

TP96

SLP_S4# (13,29)

SLP_S3# (13,29)

SLP_A# (13,29)

SLP_SUS# (13,29)

RSMRST# (29)

PCIE_WAKE# (24,28)

1 2

R141 *0/short_4

SLP_S5# (29)

D D

1 2

SUSACK#(29)

FB ID: Q-00106

SUSPWRDNACK#

SYS_PWROK(29)

EC_PWROK(8,29)

EC_APWROK(29)

SUSPWRDNACK#(29)

DNBSWON#(29)

AC_PRESENT(29)

C C

B B

R133 *0_4

MRT-03

1 2

R134 *0/short_4

BUF_PLT_RST#(18,19,23,24,25,28,29)

SUSACK#_R

SYS_PWROK

EC_PWROK

EC_APWROK

PLTRST#

RSMRST#_R

SUSPWRDNACK#

DNBSWON#

AC_PRESENT

PM_BATLOW#

TP95

TP97

1 2

R549 0_4

U1H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

1

C79

2

*100P/_4

1 2

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

DSW

DSW

DSW

8 OF 19

1 2

R146 *0_4

3V_S5

TC7SH08FU

U3

4

R151

*100K_4

+3V_S5

2

1

3 5

+3V

+3V_S5

+3V_S5

DSW

1

2

DSW

DSW

DSW

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

DSW

DSW

DSW

DSW

DSW

C78

0.1u/10V/X5R_4

C80

100K_4

*100P/_4

PCH Pull-high/low(CLG)

PCIE_WAKE#

SUSPWRDNACK#

AC_PRESENT

PM_BATLOW#

CLKRUN#

SYS_RESET#

RSMRST#

EC_APWROK

SYS_PWROK

EC_PWROK

R135 1K_4

R136 *10K_4

R137 10K_4

R138 10K_4

R143 8.2K_4

R144 10K_4

R145 10K_4

D3 *TVS DIODE

C516

0.1u/10V/X5R_4

DSWVRMEN

21

R147 10K_4

R148 100K_4

R149 10K_4

C509

0.1u/10V/X5R_4

+3V_RTC

R153

330K_4

13

3V_S5

3V_S0

On Die DSW VR Enable

High = Enable (Default)

Low = Disable

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

5

4

3

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

Date: Sheet of

Wednesday, November 05, 2014

PROJECT :

HSW PCH(Power Management)

HSW PCH(Power Management)

HSW PCH(Power Management)

1

MY6

MY6

MY6

13 46

13 46

13 46

H

H

H

Page 14

5

4

3

2

1

Haswell ULT PCH(POWER)

HSIO

USB3

HDA

VRM

GPIO/LPC

LPT LP POWER

HSW_ULT_DDR3L

OPI

13 OF 19

RTC

SPI

CORE

THERMAL SENSOR

SERIAL IO

SUS OSCILLATOR

USB2

VCCSUS3_3

VCCRTC

DCPRTC

VCCSPI

VCCASW

VCCASW

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCC1_05

DCPSUSBYP

DCPSUSBYP

VCCASW

VCCASW

VCCASW

DCPSUS1

DCPSUS1

VCCTS1_5

VCC3_3

VCC3_3

VCCSDIO

VCCSDIO

DCPSUS4

RSVD

VCC1_05

VCC1_05

AH11

AG10

AE7

+VCCRTCEXT

Y8

C88 0.1u/10V/X5R_4

AG14

+1.05V

AG13

J11

H11

H15

AE8

AF22

AG19

DCPSUSBYP

AG20

AE9

AF9

AG8

AD10

AD8

+V1.05V_SUS

J15

K14

K16

U8

T9

AB8

AC20

AG16

AG17

1 2

C101 0.1u/10V/X5R_4

C103 1u/10V/X5R_4

+V1.05V_SUS_AOSCSUS

C105 1u/10V/X5R_4

C82 1u/10V/X5R_4

1 2

C84 0.1u/10V/X5R_4

1 2

C93 1u/10V/X5R_4

3V_S5

C89 1u/10V/X5R_4

C90 1u/10V/X5R_4

C95 1u/10V/X5R_4

C97 22u/6.3V/X5R_6C96 10/u/6.3V/X5R_6

TP104

1.5V_S0

3V_S0

+V3.3S_1.8S_LPSS_SDIO

TP105

+1.05V

3V_S5

+3V_RTC

C85 1u/10V/X5R_4

1 2

C86 0.1u/10V/X5R_4

1 2

C87 0.1u/10V/X5R_4

1 2

C99 0.1u/10V/X5R_4

R154 *short_0_4

VCCSUS3

129mA

3V_S0

VCC1_05

2.6A

VCCASW

473mA

+1.05V

+1.05V

12

U1M

AA21

AH14

AH13

AH10

AE20

AE21

W21

AC9

AA9

K19

A20

R21

K18

M2 0

L10

B18

B

Y20

J13

W9

J18

J17

T21

V21

K9

M9

N8

P9

11

V8

VCCHSIO

VCCHSIO

VCCHSIO

VCC1_05

VCC1_05

VCCUSB3PLL

VCCSATA3PLL

RSVD

VCCAPLL

VCCAPLL

DCPSUS3

VCCHDA

DCPSUS2

VCCSUS3_3

VCCSUS3_3

VCCDSW3_3

VCC3_3

VCC3_3

VCCCLK

VCCCLK

VCCACLKPLL

VCCCLK

VCCCLK

VCCCLK

RSVD

RSVD

RSVD

VCCSUS3_3

VCCSUS3_3

VCCHSIO

1.84A

D D

3V_S5

C C

3V_S0

+1.05V

+1.05V

3V_S5

+V1.05DX_MODPHY

3V_S5

C102 1u/10V/X5R_4

C81 1u/10V/X5R_4

C83 1u/10V/X5R_4

VCCUSB3PLL

VCCSATA3PLL

54mA

C91 0.1u/10V/X5R_4 C92 10/u/6.3V/X5R_6

3V_S5

+V1.05DX_MODPHY

+1.05V

+V1.05S_AUSB3PLL

+V1.05S_ASATA3PLL

+V1.05S_APLLOPI

+1.05V_SUS_USB3

TP102

+1.05V_SUS_USB2-HDA

TP103

C94 0.1u/10V/X5R_4

C98 1u/10V/X5R_4

C100 10/u/6.3V/X5R_6

+V1.05S_AXCK_DCB

+V1.05S_AXCK_LCPLL

C104 1u/10V/X5R_4

12

14

B B

A A

+V1.05DX_MODPHY

+1.05V

1.95A

5

+V1.05DX_MODPHY

L39

80/5A

4

+V1.05DX_MODPHY

L1

2.2uH_8

C106

47u/6.3V/X5R_8

+V1.05DX_MODPHY

L4

2.2uH_8

C115

47u/6.3V/X5R_8