Page 1

1

bios-fix.com

2

3

4

5

6

7

8

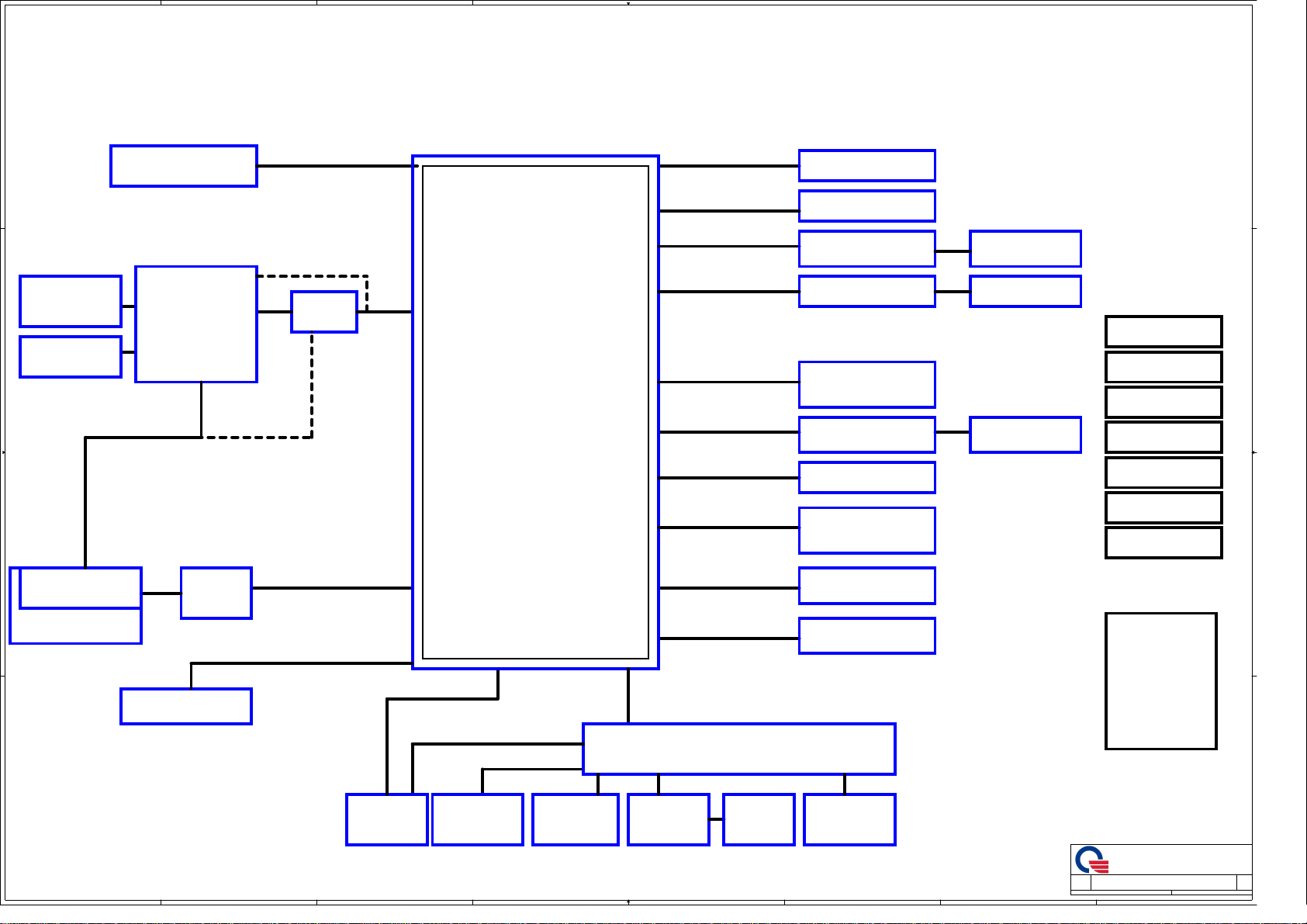

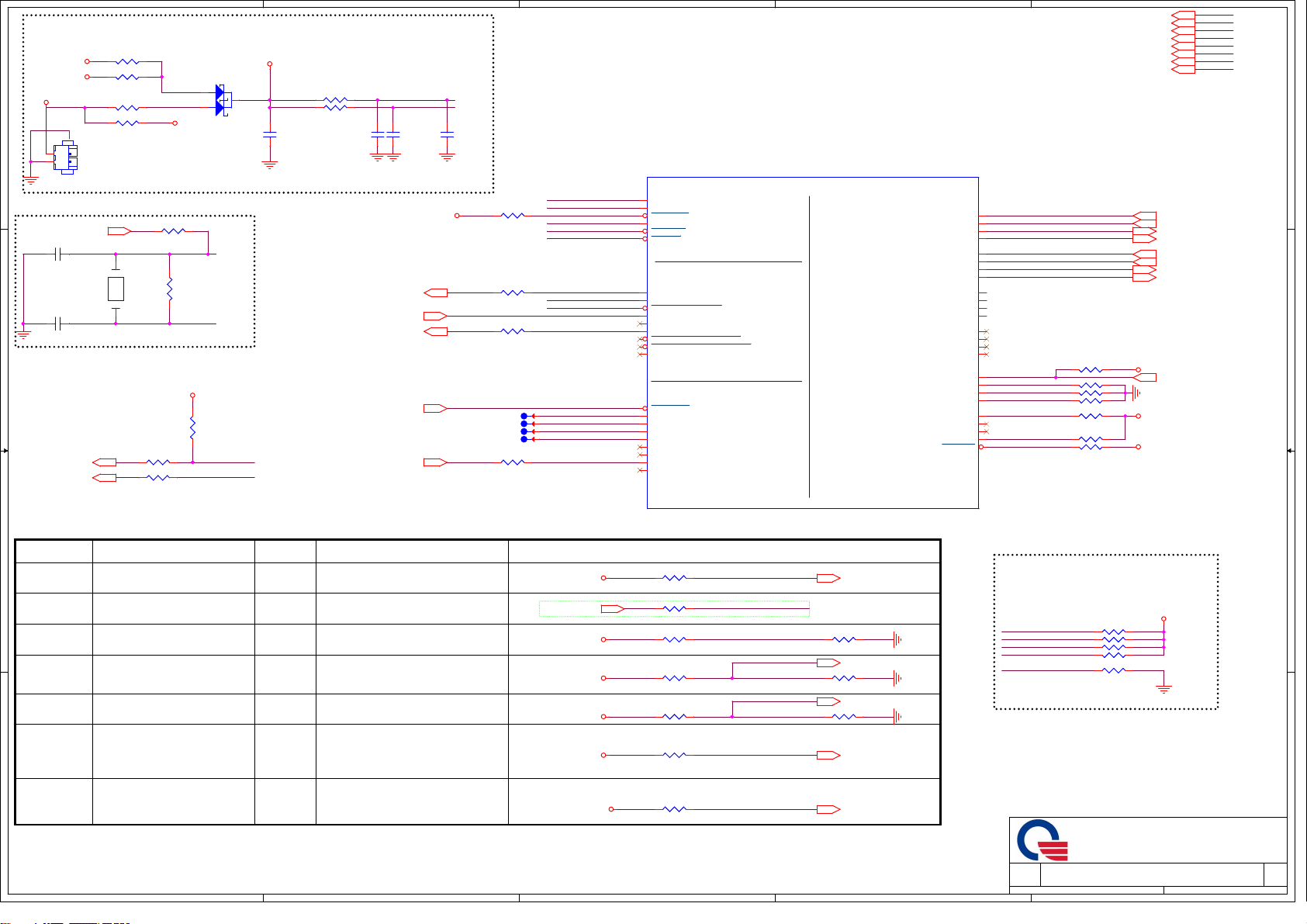

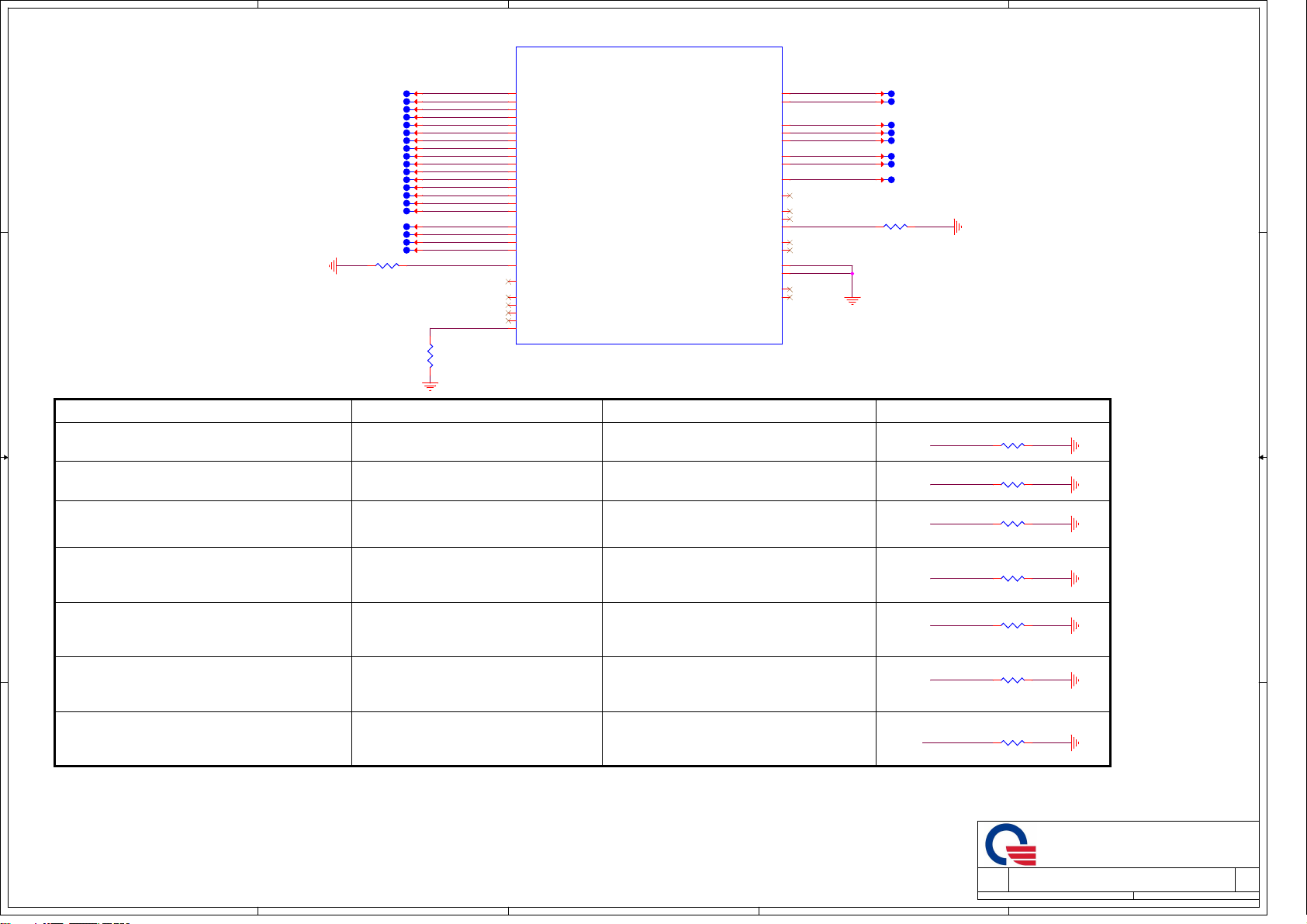

LZ5 13" UMA

1

INTEL SHARK BAY ULT ONE CHIP PLATFORM

A A

DDR3L SODIMM1

HP/Mic Audio

Combo Jack

B B

Internal SPK

PAGE 17

PAGE 17 & 23

AUDIO CODEC

ALC283

DDR3L CHA 1600MT/s

PAGE 14

DSP

HDA

ALC5505

PAGE 17

HDA

PAGE 18

Intel Shark Bay

Digital Mic

Haswell ULT 15W

1168 pin

DC+GT2/DC+GT3

C C

Digital Mic

Camera

Conn

Camera module

PAGE 15

PAGE 15

SPI Flash (8MB)

D D

1

USB2.0 (480Mb/s)

SPI (Dual/Quad mode)

PAGE 7

2

T/P

40 mm x 24 mm

SMBus

PS2

SCAN MATRIX

Int. KB +

KB Backlit

3

PAGE 2~13

EC

IT8587(128K-byte embedded flash)

CPU H/W

Thermal

4

eDP x4 (5.4Gb/s)

HDMI (2.97Gb/s)

PCIE Gen1.1 (2.5Gb/s)

SATA Gen3 (6Gb/s)

SATA Gen3 (6Gb/s)

PCIE Gen2 (5Gb/s)

USB 2.0

USB 2.0

USB 2.0

USB3.0 (6Gb/s)/

USB2.0 (480Mb/s)

LPC BUS

SMBus

Battery

5

Charger

PAGE 31PAGE 31PAGE 27PAGE 25PAGE 25

eDP Conn

HDMI Conn

PAGE 15

PAGE 16

Card Reader

RTS5227E

NGFF SLOT

PAGE 23 PAGE 23

PAGE 20

2.5" HDD /

SSD Module

Mini PCIe Slot

USB 2.0 PORT X 1

USB 2.0

+ USB Charger X 1

Touch Panel

USB 3.0 PORT X 1

Accelerometer

PAGE 19

PAGE 21

PAGE 23

PAGE 23

PAGE 15

PAGE 22

PAGE 24

PAGE 26

6

2 in 1 Socket

SD/MMC

mSATA SSD

PAGE 21

ModuleWLAN

PAGE 21

7

+VCHGR

3V/5V ALW

+1.35V_DDR

+1.05V_SUS

+1.5V

CPU_CORE

+3.3V_DSW

PAGE 31

PAGE 30

PAGE 32

PAGE 33

PAGE 34

PAGE 35

PAGE 30

PCB STACK UP 8L

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : SVCC

LAYER 6 : IN3

LAYER 7 : SGND1

LAYER 8 : BOT

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet

Date: Sheet

System Block Diagram

System Block Diagram

System Block Diagram

8

of

of

137Wednesday, F ebruary 2 7, 2013

137Wednesday, F ebruary 2 7, 2013

137Wednesday, F ebruary 2 7, 2013

1A

1A

1A

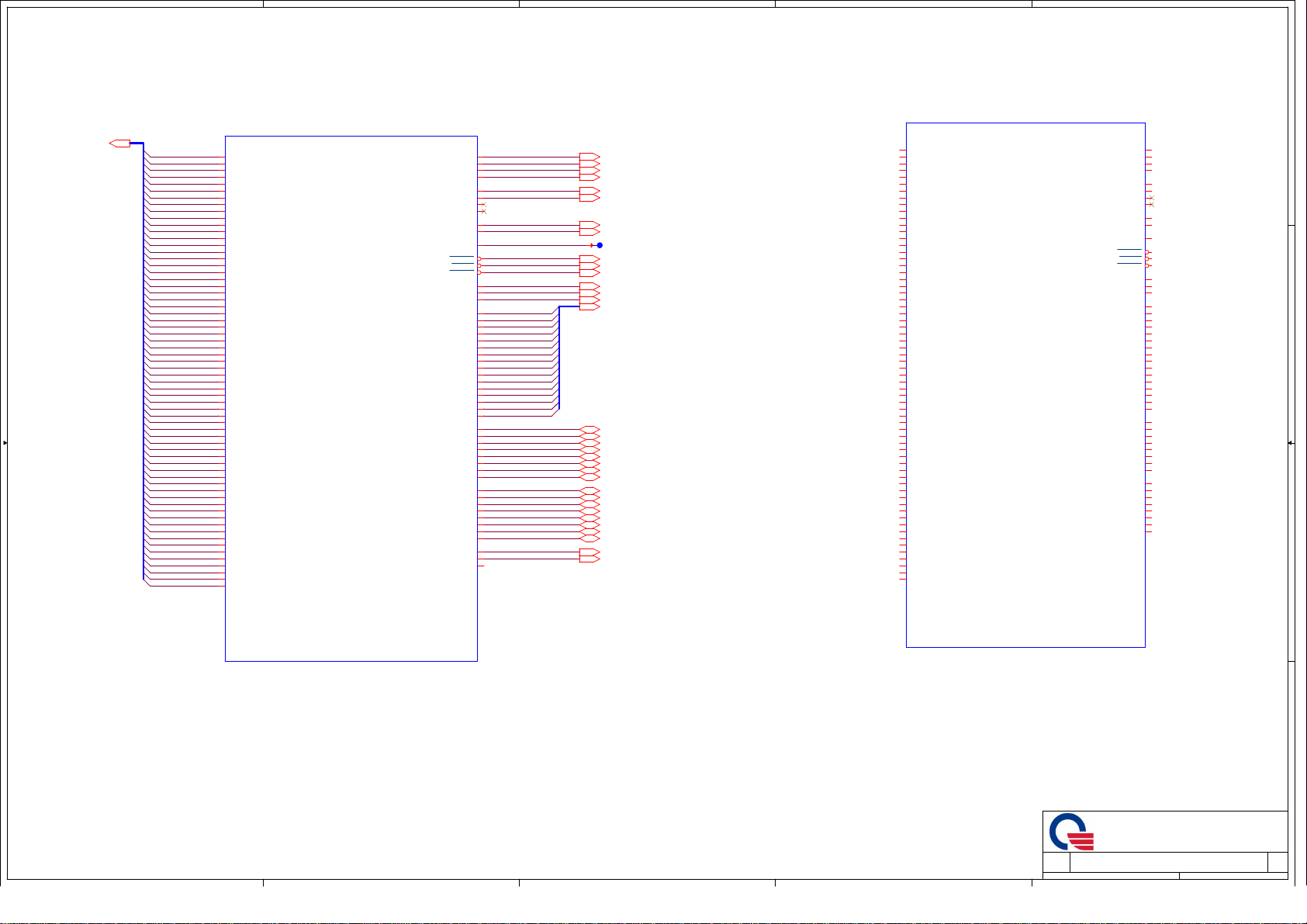

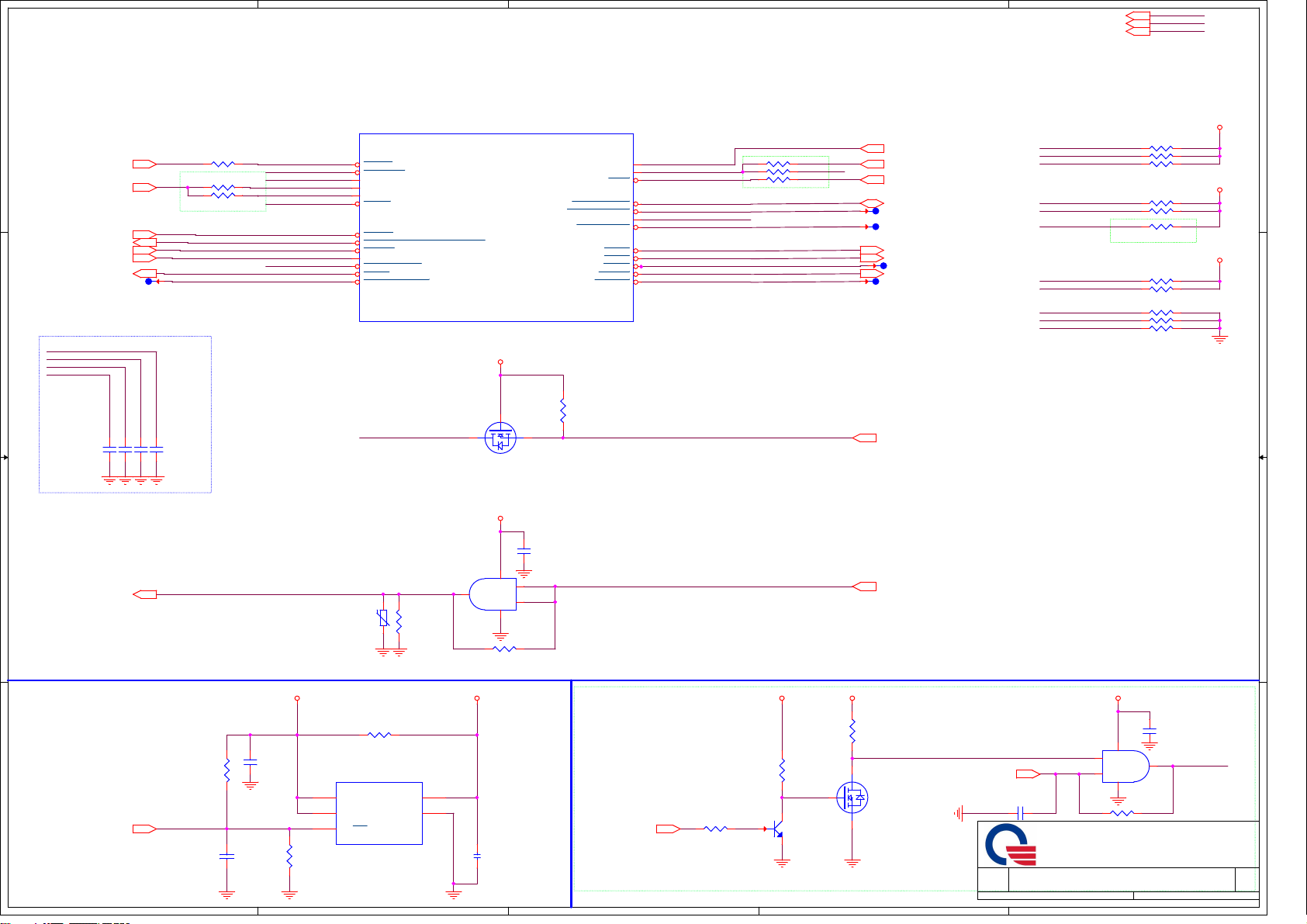

Page 2

5

bios-fix.com

4

3

2

+VCCIOA_OUT9

+3.3V_RUN4,6,7,8,12,14,15,16,17,19,20,21,23,24,25,26,27,30,35,36,37

1

2

D D

Haswell ULT (DISPLAY)

PCIE

HSW_ULT_DDR3L

1 OF 19

HSW_ULT_DDR3L

9 OF 19

EDPDDI

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_COMP

INT_HDMI_HPD

EDP_HPD

R274 *0_4

R282 *0_4

R287 *0_4_S

R288

100K_4

+VCCIOA_OUT

EDP_TXN0 15

EDP_TXP0 15

EDP_TXN1 15

EDP_TXP1 15

T50

T49

T52

T51

EDP_AUXN 15

EDP_AUXP 15

LCD_PWMDP_UTIL

HDMI_SCL 16

HDMI_SDA 16

EDP_HP 15

EC-A13

EDP_COMP

PCH_GPIO78

PCH_GPIO79

PCH_GPIO80

TOUCH_PA NEL_ID#INT_HDMI_TXP0

INT_HDMI_HPD

R289

1M_4

R312 10K_4

R36 10K_4

R304 10K_4

R302 10K_4

R306 10K_4

+3.3V_RUN+3.3V_RUN

2

1

Q26

2N7002K-T1-E3

R32 24.9/F_4

3

R268

20K/F_4

+3.3V_RUN

HDMI_HPD 16

U28A

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

INT. HDMI

HDMI_TX2-_C16

HDMI_TX2+_C16

HDMI_TX1-_C16

HDMI_TX1+_C16

MPCIE_RST_N21

EC-A13

TOUCH_PA NEL_ID#15

HDMI_TX0-_C16

HDMI_TX0+_C16

HDMI_CLK-_C16

HDMI_CLK+_C16

LCD_PWM15

PANEL_BKEN15

ENVDD15

PCH_GPIO554

PCH_GPIO544

PCH_GPIO514

C C

B B

C308 0.1U/10V/X5R_4

C307 0.1U/10V/X5R_4

C311 0.1U/10V/X5R_4

C312 0.1U/10V/X5R_4

C305 0.1U/10V/X5R_4

C306 0.1U/10V/X5R_4

C309 0.1U/10V/X5R_4

C310 0.1U/10V/X5R_4

T70

T3

T64

INT_HDMI_TXN0

INT_HDMI_TXN1 PCH_GPIO53

INT_HDMI_TXP1

INT_HDMI_TXN2

INT_HDMI_TXP2

INT_HDMI_TXCN

INT_HDMI_TXCP

LCD_PWM

PCH_GPIO78

PCH_GPIO79

PCH_GPIO80

TOUCH_PA NEL_ID#

PCH_GPIO53

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

AD4

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U28I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

eDP SIDEBAND

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

A A

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

5

Size Document Number Rev

Date: Sheet

Wednesday, February 27, 2013 2 37

Date: Sheet

Wednesday, February 27, 2013 2 37

Date: Sheet

4

3

2

Wednesday, February 27, 2013 2 37

Haswell ULT 1/12

Haswell ULT 1/12

Haswell ULT 1/12

1

of

of

of

1A

1A

1A

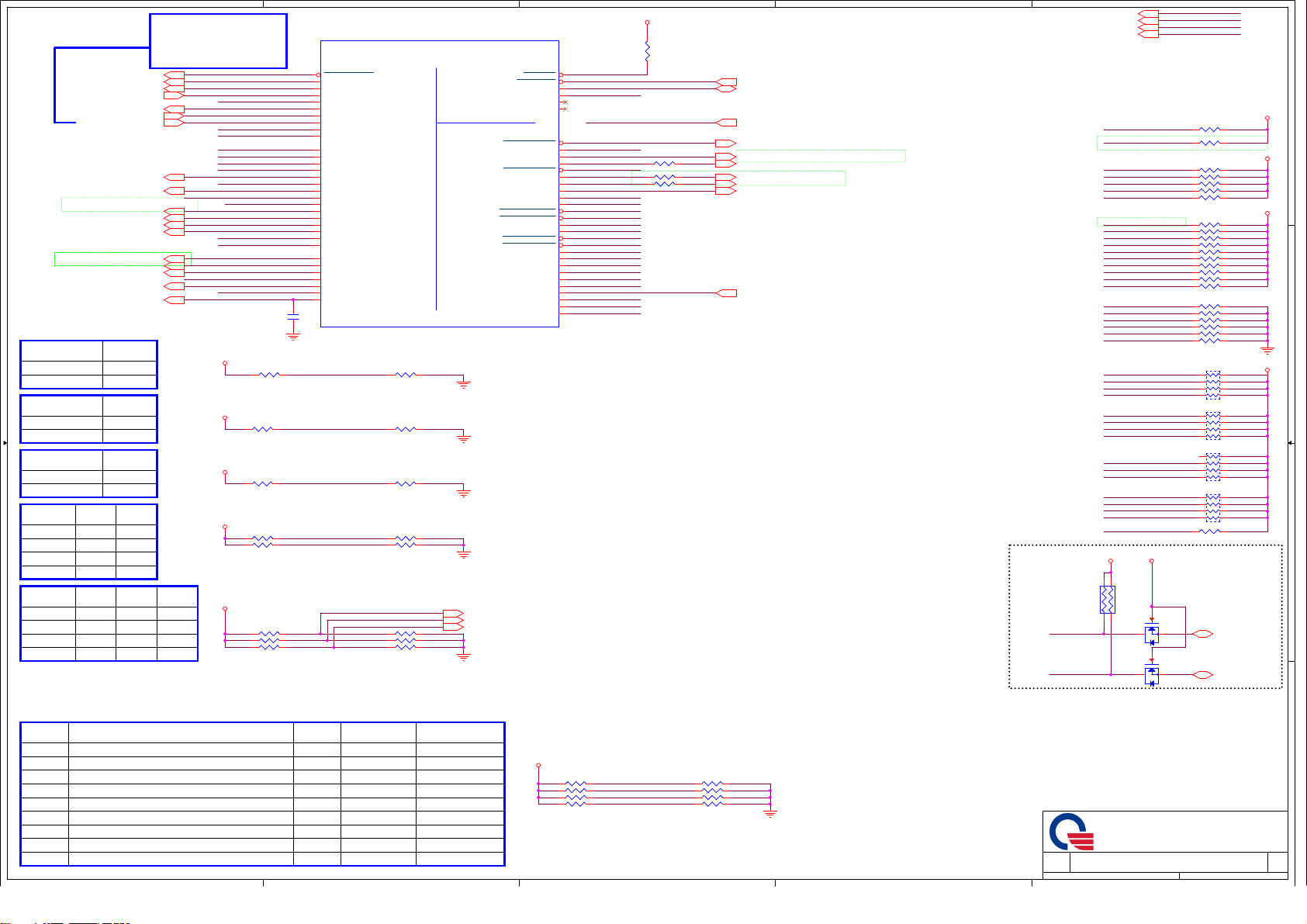

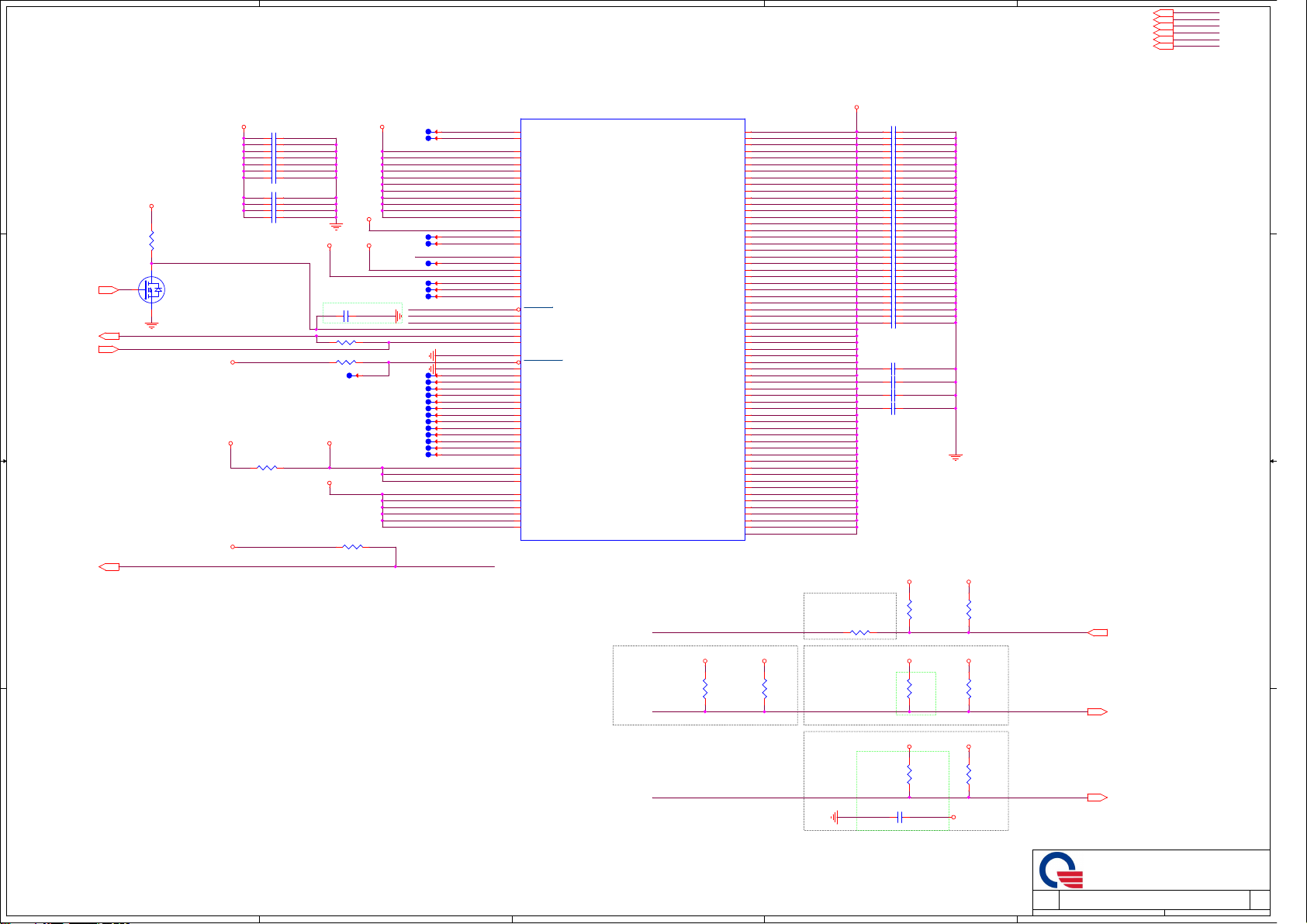

Page 3

5

bios-fix.com

4

3

2

1

3

D D

C C

B B

Haswell ULT (DDR3L)

M_A_DQ[63:0]14

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

U28C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_ODT0_CPU

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CLKN0 14

M_A_CLKP0 14

M_A_CLKN1 14

M_A_CLKP1 14

M_A_CKE0 14

M_A_CKE1 14

M_A_CS#0 14

M_A_CS#1 14

T31

M_A_RAS# 14

M_A_WE# 14

M_A_CAS# 14

M_A_BS#0 14

M_A_BS#1 14

M_A_BS#2 14

M_A_A[15:0] 14

M_A_DQSN0 14

M_A_DQSN1 14

M_A_DQSN2 14

M_A_DQSN3 14

M_A_DQSN4 14

M_A_DQSN5 14

M_A_DQSN6 14

M_A_DQSN7 14

M_A_DQSP0 14

M_A_DQSP1 14

M_A_DQSP2 14

M_A_DQSP3 14

M_A_DQSP4 14

M_A_DQSP5 14

M_A_DQSP6 14

M_A_DQSP7 14

SM_VREF_CA 14

SM_VREF_DQ0 14

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

U28D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

3 OF 19

A A

5

4

3

2

4 OF 19

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Quanta Computer Inc.

Haswell ULT 2/12

Haswell ULT 2/12

Wednesday, February 27, 2013 3 37

Wednesday, February 27, 2013 3 37

Wednesday, February 27, 2013 3 37

Haswell ULT 2/12

1

1A

1A

1A

of

of

of

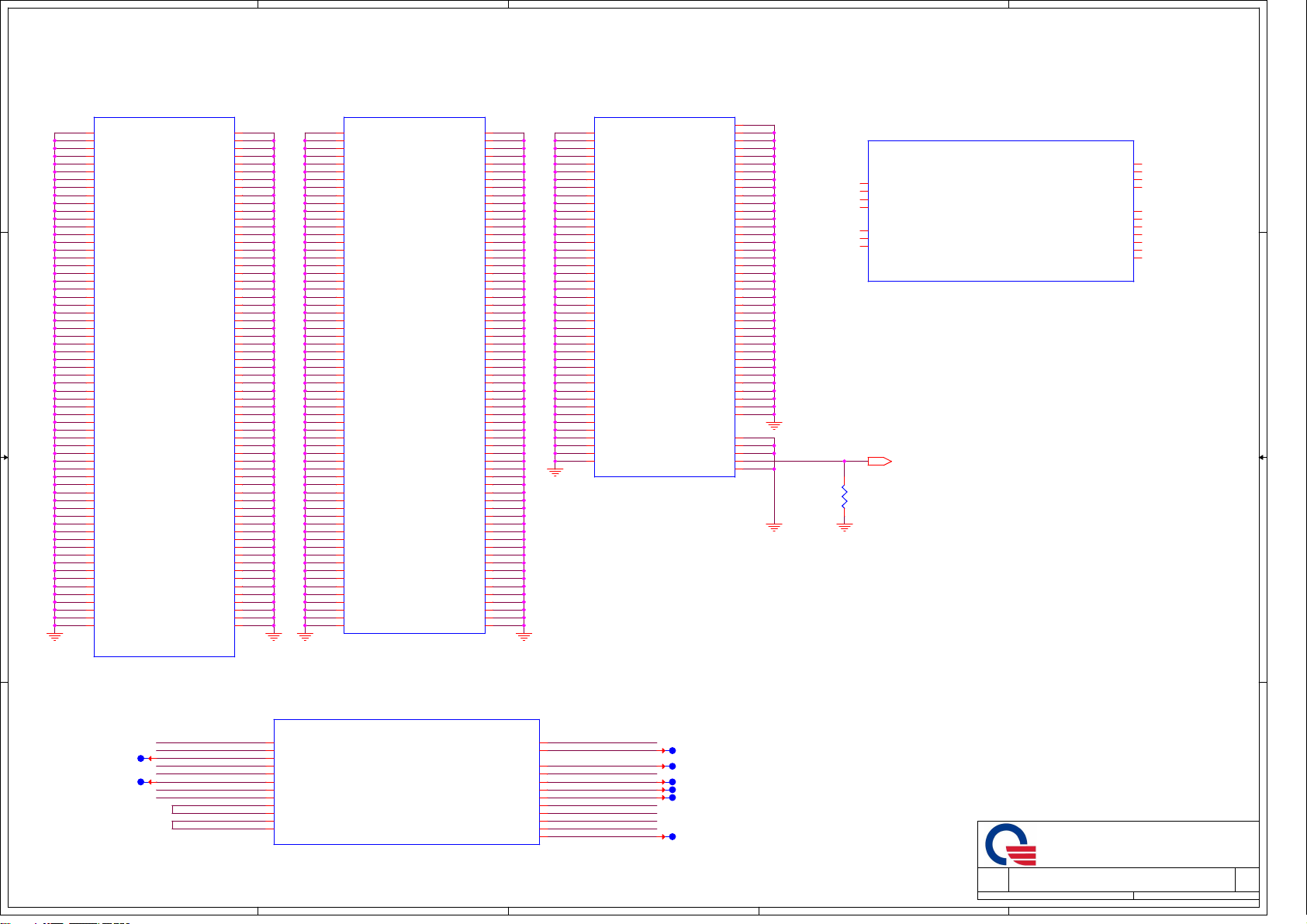

Page 4

5

bios-fix.com

GPIO27

With Intel LAN:

Connect to LANWAKE# pin on the LAN

Without Intel LAN:

Used to wake event from DSx

AUDIO_+3.3V_EN17

USB_ON23

AUDIO_DSP_EN_DS317

GPIO156

DCR15

D D

EC-A13

B.1221

C C

Thunderbolt ID

Supported

Not Supported

Audio DSP ID

Supported

Not Supported

DGPU SELECT

Supported

Not Supported

Model ID

LZ5-UMA

LZ9-UMA

B B

LZ9A-DIS

LZA

Board ID

SDV

SIV

SIT

NGFF_SSD_PRESENT#20

SIO_WAKE_SCI#21,24

AUDIO_DSP_EN17

LCD_BK_OFF15

MODPHY_EN12,33

USB3_P0_EN22

WLAN_ON/OFF#21

CCD_EN15

BT_RADIO_DIS#21

SIO_EXT_SCI#24

DEVSLP020

DEVSLP119

ACZ_SPKR6,17

GPIO84

0

1

GPIO47

0

1

GPIO39

0

1

GPIO45

GPIO46

00

0

1

0

1

11

GPIO51

GPIO54

GPIO55

111

11 0

10 1

SVT

USB_ON

AUDIO_DSP_EN_DS3

GPIO16

DCR

NGFF_SSD_PRESENT#

SIO_WAKE_SCI#

GPIO28

GPIO26

GPIO56

GPIO57

GPIO58

GPIO59

GPIO47

GFXPG

TOUCH_PANEL_ INTR#

USB3_P0_EN

WLAN_ON/OFF#

GPIO45

GPIO46

BT_RADIO_DIS#

SIO_EXT_SCI#

DEVSLP0

VR_TT#

DEVSLP1

GPIO39

*100P/50V/NP O_4

+3.3V_RUN

R33 10K_4

+3.3V_DEEP_SUS

R56 *NON_10K_4

+3.3V_RUN

R34 10 K_4

+3.3V_DEEP_SUS

R334 *10K_4

R335 *10K_4

+3.3V_RUN

R35 10 K_4

R307 *10K_4

R45 10 K_4

Hasswell ULT(GPIO,LPIO,MISC)

U28J

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTR L/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

EC15

SPKR/GPIO81

GPIO84

GPIO47

GPIO39

GPIO45

GPIO46

4

+3V

+3V_S5

+3V_S5

+3V

+3V

+3V_S5

DSW

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V

+3V

+3V

+3V

+3V_S5

+3V_S5

DSW

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V

+3V

+3V

+3V

R594 *10K_4

R53 DSP_10K_4

R587 *10K_4

R333 10K_4

R331 10K_4

R395 *10K_4

R396 10K_4

R397 *10K_4

HSW_ULT_DDR3L

DSW

GPIO

+3V

10 OF 19

+3V

+3V

+3V

CPU/

MISC

+3V

GSPI0_CS/GPIO83

+3V

GSPI0_CLK/GPIO84

+3V

GSPI0_MISO/GPIO85

+3V

GSPI0_MOSI/GPIO86

+3V

GSPI1_CS/GPIO87

+3V

GSPI1_CLK/GPIO88

+3V

GSPI1_MISO/GPIO89

+3V

GSPI_MOSI/GPIO90

+3V

UART0_RXD/GPIO91

+3V

UART0_TXD/GPIO92

UART0_RTS/GPIO93

SERIAL IO

UART0_CTS/GPIO94

+3V

UART1_RXD/GPIO0

+3V

UART1_TXD/GPIO1

+3V

UART1_RST/GPIO2

+3V

UART1_CTS/GPIO3

+3V

+3V

+3V

+3V

+3V

+3V

SDIO_CMD/GPIO65

+3V

+3V

+3V

+3V

PCH_GPIO51 2

PCH_GPIO54 2

PCH_GPIO55 2

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD

RSVD

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

D60

PCH_THRMTRIP#

V4

SIO_RCIN#

T4

IRQ_SERIRQ

AW15

PCH_OPIRCOMP

AF20

AB21

BBS

R6

NGFF_WLAN_PWR_ EN

L6

GPIO84

N6

TOUCH_FING ER_EN

L8

BBS

R7

GPIO87

L5

TP_EN1

N7

TP_EN2

K2

SATA1_PWR_EN

J1

GPIO91

K3

GPIO92

J2

DGPU_HOLD_RST#

G1

GPIO94

K4

GPIO0

G2

GPIO1

J3

GPIO2

J4

GPIO3

F2

I2C0_SDA_L

F3

I2C0_SCL_L

G4

DAT_TP_SIO_L

F1

CLK_TP_SIO_L

E3

GPIO64

F4

GPIO65

D3

E4

GPIO67

C3

GPIO68

E2

GPIO69

3

+V1.05S_VCCST

R31

1K_4

R30 *0_4

R398 *0_4

R399 *0_4

SIO_RCIN# 24

IRQ_SERIRQ 21,24

BBS 6

NGFF_WLAN_PWR_ EN 21

TOUCH_FING ER_EN 15

NGFF_SATA_SSD_PWREN 20

TOUCHPAD_EN 25

TOUCHPANEL_EN 15

SATA1_PWR_EN 19

GPIO66 6

EC-A02

EC-A07

2

+V1.05S_VCCST9,13

+3.3V_DEEP_SUS5,6,7,8,12,14,28

+3.3V_RUN2,6,7,8,12,14,15,16,17,19,20,21,23,24,25,26,27,30,35,36,37

+3.3V_DSW6,8,12,17,21,23,25,31,34,36

1

4

GPIO Pull-up/Pull-down(CLG)

+3.3V_DSW

+3.3V_DEEP_SUS

+3.3V_RUN

+3.3V_RUN

2

4

6

8

2

4

6

8

2

4

6

8

2

4

6

8

I2C0_SCL 1 8

I2C0_SDA 18

EC-A15

EC-A13

RP9

10K

I2C0_SCL_L

Audio DSP

I2C0_SDA_L

SIO_WAKE_SCI#

AUDIO_DSP_EN_DS3

SIO_EXT_SCI#

NGFF_SSD_PRESENT#

WLAN_ON/OFF#

GPIO28

BT_RADIO_DIS#

TOUCH_PANEL_ INTR#

GPIO16

SIO_RCIN#

IRQ_SERIRQ

DCR

VR_TT#

DEVSLP1

DEVSLP0

GFXPG

GPIO87

USB_ON

USB3_P0_EN

NGFF_WLAN_PWR_ EN

GPIO26

PCH_OPIRCOMP

SATA1_PWR_EN

TOUCH_FING ER_EN

GPIO0

DAT_TP_SIO_L

GPIO92

GPIO65

GPIO67

GPIO69

GPIO64

GPIO3

GPIO2

GPIO91

DGPU_HOLD_RST#

GPIO1

GPIO94

CLK_TP_SIO_L

GPIO68

+3.3V_RUN

2

4

1

3

+3.3V_RUN

5

3 4

2

6 1

R128 10K_4

R105 *10K_4

R346 10K_4

R63 10K_4

R340 10K_4

R64 10K_4

R117 10K_4

R313 10K_4

R325 10K_4

R50 10K_4

R42 10K_4

R43 *10K_4

R286 10K_4

R301 *10K_4

R303 *10K_4

R329 10K_4

R621 10K_4

R209 100K_4

R352 100K_4

R44 *100K_4

R348 100K_4

R361 49.9/F_4

R622 100K_4

RN1 10K

RN2 10K

RN4 10K

RN3 10K

R285 10K_4

Q27A

DSP_2N7002DW

Q27B

DSP_2N7002DW

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

DDR3L Memory Down ID Table

Default

Samsung

A A

Micron

ELPIDA

SK hynix

Samsung

Micron

ELPIDA

SK hynix

Description

K4B8G1646B-MYK0 (B/4Gb/35nm/DDP)

MT41K512M16TNA-125:E(V80A/4Gb/30nm/DDP)

EDJ8416E6MB-GN-F(F/4Gb/30nm/DDP)

K4B4G1646B-HYK0(B/4Gb/35nm)

MT41K256M16HA-125:E(V80A/4Gb/30nm)

EDJ4216EFBG-GN-F(F/4Gb/30nm)

H5TC4G63AFR-PBA(D/4Gb/29nm)

5

, LZ5 don't support DDR3L Memory Down

Size

8Gb x 16

8Gb x 16

8Gb x 16

8Gb x 16

4Gb x 16

4Gb x 16

4Gb x 16

4Gb x 16

Quanta P/NVendor

AKD5FGET500

AKD5FGSTL00

AKD5FGST402

AKD5PGET500

AKD5JGSTL02

AKD5JGST403

AKD5JGETW00

4

GPIO[56,57,58,59]

1111

1110

1101

1100

XXXX

1011

1010

1001

1000

+3.3V_DEEP_SUS

R70 10K_4

R351 10K_4

R345 10K_4

R114 10K_4

GPIO56

GPIO57

GPIO58

GPIO59

3

R68 *10K_4

R350 *10K_4

R343 *10K_4

R110 *10K_4

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Quanta Computer Inc.

Haswell ULT 3/12

Haswell ULT 3/12

Haswell ULT 3/12

Wednesday, February 27, 2013 4 37

Wednesday, February 27, 2013 4 37

Wednesday, February 27, 2013 4 37

1

of

of

of

1A

1A

1A

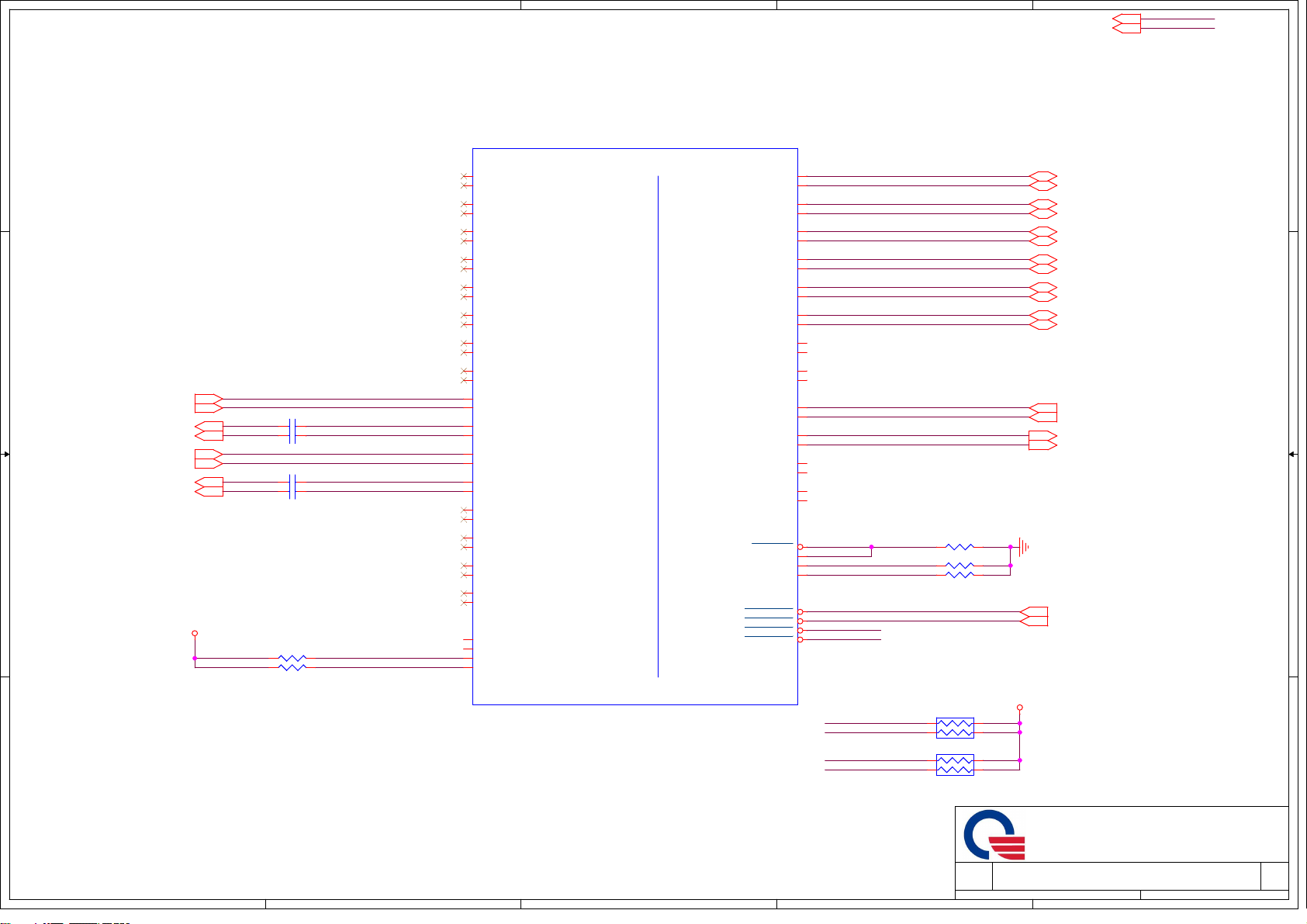

Page 5

5

bios-fix.com

4

3

2

+3.3V_DEEP_SUS4,6,7,8,12,14,28

+V1.05S_AUSB3PLL12

1

5

Haswell ULT (PCIE,USB)

D D

U28K

HSW_ULT_DDR3L

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

C C

PCIE_RXN321

WiFi/BT NGFF

Card Reader

B B

PCIE_RXP321

PCIE_TXN321

PCIE_TXP321

PCIE_RXN423

PCIE_RXP423

PCIE_TXN423

PCIE_TXP423

+V1.05S_AUSB3PLL

C323 0.1U/10V/X5R_4

C324 0.1U/10V/X5R_4

C321 0.1U/10V/X5R_4

C322 0.1U/10V/X5R_4

R281 3K/F_4

R280 0_4

PCIE_TXN3_C

PCIE_TXP3_C

PCIE_TXN4_C

PCIE_TXP4_C

PCIE_RCOMP

PCIE_IREF

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD

E13

RSVD

A27

PCIE_RCOMP

B27

PCIE_IREF

PCIE USB

+3V_S5

+3V_S5

+3V_S5

+3V_S5

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

RSVD

RSVD

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB_BIAS

USBPLLMON_N

USBPLLMON_P

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

R73 22.6/F_4

R100 49.9/F_4

R99 49.9/F_4

USB-_TPanel 15

USB+_TPanel 15

USBP1- 22

USBP1+ 22

USBP2- 23

USBP2+ 23

USBP3- 23

USBP3+ 23

USBP4- 15

USBP4+ 15

USBP5- 21

USBP5+ 21

USB30_RX1- 22

USB30_RX1+ 22

USB30_TX1- 22

USB30_TX1+ 22

USB_OC0# 22

USB_OC1# 23

Touch Panel

USB3.0 Port 1 (CN7)

USB2.0 Port 1

USB2.0 Port 2

CAMERA

WLAN / BT NGFF

USB3.0 Port 1 (CN7)

11 OF 19

USB_OC1#

USB_OC3#

USB_OC2#

USB_OC0#

A A

5

4

3

2

RP3 10K

4

2

RP2 10K

4

2

+3.3V_DEEP_SUS

3

1

3

1

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Haswell ULT 4/12

Haswell ULT 4/12

Haswell ULT 4/12

Wednesday, February 27, 2013 5 37

Wednesday, February 27, 2013 5 37

Wednesday, February 27, 2013 5 37

1

of

of

of

1A

1A

1A

Page 6

5

bios-fix.com

RTC Power trace width 20mils.

D9

BAT54C

R360

*1K_4

HDA_SYNC_C

HDA_RST#_C

+RTC_CELL

R369 20K/F_4

R377 20K/F_4

C340

1U/6.3V_4

1U/6.3V_4

+3V_RTC_0

BT1

4

2

1

R223 *0_6

R222 0_6

R212 1K_4

R214 *1M_4

RTC BATTERY

12

Y4

32.768KHZ

R365 33_4

R376 33_4

+3V_RTC_2

+3V_RTC_1

RTC_VCC_L

R375 *0_4

RTC_X1

R364

10M_4

RTC_X2

+3.3V_DEEP_SUS

+3.3V_DSW

+3.3V_ALW2

+3V_RTC_0

D D

PCH_RTC_X128

C339 18P/50V/_4

C332 18P/50V/_4

C C

HDA_SYNC17,18

HDA_RST#17,18

C336

4

RTC_RST#

SRTC_RST#

C335

1U/6.3V_4

+RTC_CELL

HDA_BITCLK17,18

HDA_SDIN017,18

HDA_SDOUT17,18

XDP_TRST_CPU_N13

XDP_TCK013

SC11

*AVLC 5S 02 100

R367 1M_4

R378 33_4

R372 33_4

T88

T84

T87

T85

R40 *0_4_S

RTC_X1

RTC_X2

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BITCLK_C

HDA_SYNC_C

HDA_RST#_C

HDA_SDOUT_C

XDP_TCK1

XDP_TDI

PCH_JTAG_TDO

XDP_TMS

PCH_JTAGX

3

2

Haswell ULT (RTC, HDA, JTAG, SATA)

U28E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

HSW_ULT_DDR3L

RTC

AUDIO SATA

JTAG

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

+3V

SATA0GP/GPIO34

+3V

SATA1GP/GPIO35

+3V

SATA2GP/GPIO36

+3V

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

GPIO35

GPIO36

GPIO37

SATA_IREF

SATA_RCOMP

+3.3V_DEEP_SUS4,5,7,8,12,14,28

+V3.3S_1.8S_LPSS_SDIO12

+V1.05S_ASATA3PLL12

R322 10K_4

R315 10K_4

R47 10K_4

R328 10K_4

R279 0_4

R291 3K/F_4

R318 10K_4

1

+3.3V_ALW215,17,24,25,28,30,31

+3.3V_DSW4,8,12,17,21,23,25,31,34,36

+3V_RTC_028

+RTC_CELL12,24,28

+3.3V_RUN2,4,7,8,12,14,15,16,17,19,20,21,23,24,25,26,27,30,35,36,37

SATA_RXN0 20

SATA_RXP0 20

SATA_RXN1 19

SATA_RXP1 19

+3.3V_RUN

SMC_EXTSMI_N 24

+V1.05S_ASATA3PLL

+3.3V_RUN

SATA_TXN0 20

SATA_TXP0 20

SATA_TXN1 19

SATA_TXP1 19

6

mSATA

HDD

5 OF 19

PCH Strap Table

Pin Name

B B

SPKR

HDA_SDO

INTVRMEN

GPIO66

GPIO86

GPIO15

A A

DSWVREN

Strap description

No reboot mode setting PWROK

Flash Desc riptor Sec urity

Override / Intel ME Debug Mode

Integrated 1.05V VRM enable ALWAYS

Top-Block Swap override

BBS(Boot BIOS Strap Bit)

TLS(Transport layer security)

Deep Sx well on die DSW VR enable

5

Sampled

PWROK

Configuration Note

0 = Default (weak pull-down 20K)

1 = Setting to No-Reboot mode

0 = Security Effect (Int PD)

1 = Can be Override

Should be always pull-up

0 = Default disable (iPD 20K)

1 = Enable TBS function

0 = Default SPI (iPD 20K)

1 =LPC

0 = Default enable w/o

confidentiality(iPD 20K)

1 =Default enable with

confidentiality

1=Should be alw ays pull-up

4

+3.3V_RUN

ME_WR#24

+RTC_CELL

+V3.3S_1.8S_LPSS_SDIO

+3.3V_RUN

+3.3V_DEEP_SUS

+RTC_CELL

R321 *1K_4

R371 1K_4

R370 330K_4

R283 *1K_4

R59 *10K_4

R368 330K_4

3

HDA_SDOUT_C

PCH_INTVRMEN

ACZ_SPKR 4,17

EC-A21

R359 *330K_4

GPIO66 4

R284 *1K_4

BBS 4

R29 *1K_4R28 *1K_4

GPIO15 4

DSWVRMEN 8

PCH JTAG Debug (CLG)

MP remove(Intel)

+1.05V_RUN

XDP_TMS

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

XDP_TCK1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

R332 51_4

R330 51_4

R338 51_4

R41 *1K_4

R342 *51_4

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Haswell ULT 5/12

Haswell ULT 5/12

Haswell ULT 5/12

Wednesday, February 27, 2013 6 37

Wednesday, February 27, 2013 6 37

Wednesday, February 27, 2013 6 37

1

of

of

of

1A

1A

1A

Page 7

5

bios-fix.com

D D

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

WiFi/BT(NGFF)

Card Reader

C C

CLK_PCIE_WIFIN21

CLK_PCIE_WIFIP21

PCIE_CLK_REQ2#21

CLK_PCIE_CRDN23

CLK_PCIE_CRDP23

PCIE_CLK_REQ3#23

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

Haswell ULT (LPC/SPI/SMB/CLINK)

LPC_LAD021,24

LPC_LAD121,24

LPC_LAD221,24

LPC_LAD321,24

LPC_LFRAME#21,24

RC1 *1.6P/50V_4

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

B B

EC-A16

8512_SI24

8512_SO24

8512_SCK24

8512_SCE#24

8512_SI

8512_SO

8512_SCK

8512_SCE#

For EC(IT8587 e-flash) load code from BIOS flash ROM

RC3 *1.6P/50V_4

A A

5

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

R157 *10K_4

R188 *10K_4

R163 *0_4_S

R185 *0_4_S

R162 *0_4_S

R198 *0_4_S

EC-A16

R193 15

R150 15

R145 15

R183 15

R176 15

4

Haswell ULT (CLK)

HSW_ULT_DDR3L

+3V

+3V

+3V

+3V

+3V

+3V

HSW_ULT_DDR3L

LPC

+3V_S5

+3V_S5

+3V_S5

PCH_SPI_VCC

R172

10K_4

U16

1

CE#

6

SCK

5

SI

2

SO

3

WP#

W25Q64FVSSIQ

SPI FLASH

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO1 8

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO1 9

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO2 0

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO2 1

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO2 2

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO2 3

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

U28F

U28G

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_CLK_R

PCH_SPI_CS0#_R

PCH_SPI_CS0#_R

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

4

CLOCK

SIGNALS

6 OF 19

+3V_S5

SMBUS

+3V_S5

SML1ALERT/PCHHOT/GPIO7 3

C-LINKSPI

7 OF 19

8

VDD

7

HOLD#

4

VSS

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

R160 *0_4_S

R165 *0_4RC4 *1.6P/50V_4

R161

10K_4

R156 15

C181

0.1U/10V/X5R_4

3

A25

XTAL24_IN

B25

XTAL24_OUT

K21

M21

C26

C35

TESTLOW_0

C34

TESTLOW_1

AK8

TESTLOW_2

AL8

TESTLOW_3

AN15

LPC_CLK_0

AP15

LPC_CLK_1

B35

A35

AN2

PCH_SMB_ALERT#

AP2

SMBCLK

AH1

SMBDATA

AL2

CARDREADER_EN

AN1

SML0CLK

AK1

SML0DATA

AU4

GPIO73

AU3

SMB_CLK_ME1

AH3

SMB_DATA_ME1

AF2

AD2

AF4

+3.3V_DEEP_SUS

PCH_SPI_IO3

3

+3.3V_RUN

R275 *0_4

C317

4

3

R292

1M_4

1

2

C316

R276 3K/F_4

R108 22_4

R97 22_4

C127

*10P/50V _4

T32

12P/50V_4

Y3

24MHz

12P/50V_4

2

PCH_XTAL24_IN 28

+V1.05S_AXCK_LCPLL

CLKOUT_LPC_0 24

PCLK_DEBUG 21

CARDREADER_EN 23

2

1

+3.3V_RUN2,4,6,8,12,14,15,16,17,19,20,21,23,24,25,26,27,30,35,36,37

+3.3V_DEEP_SUS4,5,6,8,12,14,28

+1.05V_RUN6,9,12,28,33,37

+V1.05S_AXCK_LCPLL12

7

RP8 10K

2

TESTLOW_1

TESTLOW_0

TESTLOW_2

TESTLOW_3

Do not short

the testlow pins together.

PCIE_CLK_REQ2#

PCIE_CLK_REQ1#

PCIE_CLK_REQ0#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

PCH_SMB_ALERT#

SMBCLK

SMBDATA

GPIO73

SML0CLK

SML0DATA

SMB_DATA_ME1

SMB_CLK_ME1

CARDREADER_EN

SMBus/Pull-up(CLG)

SMBCLK

SMBDATA

SMB_CLK_ME1

SMB_DATA_ME1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Wednesday, February 27, 2013 7 37

Date: Sheet

Wednesday, February 27, 2013 7 37

Date: Sheet

Wednesday, February 27, 2013 7 37

+3.3V_RUN

Q5A

2N7002DW

3 4

Q5B

2N7002DW

6 1

+3.3V_DEEP_SUS

Q6A

2N7002DW

Q6B

2N7002DW

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Haswell ULT 6/12

Haswell ULT 6/12

Haswell ULT 6/12

1

3

RP7 10K

1

3

RN5 10K

1

3

5

7

RP1 10K

1

3

R79 10K_4

RP4 2.2KX2

1

3

R354 10K_4

R349 2.2K_4

R341 2.2K_4

RP5 2.2KX2

1

3

R256 100K_4

2

4

5

1

3

2

5

34

2

61

1

4

2

4

+3.3V_RUN

2

4

6

8

2

4

+3.3V_DEEP_SUS

2

4

2

4

RP6

2.2KX2

PCH_SCLK 14,25

PCH_SDATA 14,25

MBCLK_THRM 24

MBDATA_THRM 24

of

of

of

1A

1A

1A

Page 8

5

bios-fix.com

4

3

2

+3.3V_DSW4,6,12,17,21,23,25,31,34,36

+3.3V_RUN2,4,6,7,12,14,15,16,17,19,20,21,23,24,25,26,27,30,35,36,37

+3.3V_DEEP_SUS4,5,6,7,12,14,28

1

Haswell ULT (SYSTEM POWER MANAGEMENT)

8

PCH Pull-high/low(CLG)

D D

SUSACK#24

EC-A17

EC_PWROK17,24

RSMRST#24

SUSWARN#24

SIO_PWRBTN#24

AC_PRESENT24

SLP_S0#24

TP6

C C

B B

SYS_PWROK

RSMRST#

PLTRST#

EC_PWROK

ESD

BUF_PLT_RST#20,21

SC3 *AVLC 5S 02 100

SC12 *AVLC 5S 02 100

SC13 *AVLC 5S 02 100

R379 0_4

R380 0_4

SC10 *AVLC 5S 02 100

SUSACK#_R

SYS_RESET#

SYS_PWROK

PCH_PWROK

PCH_APWROK

PLTRST#

RSMRST#

SUSWARN#

SIO_PWRBTN#

AC_PRESENT

PM_BATLOW#

U28H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/ GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPI O72

AF3

SLP_S0

AM5

SLP_WLAN/GPI O29

PM_BATLOW#

*EGA-040 2

RV3

R78

100K_4

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

+3V_S5

DSW

DSW

DSW

8 OF 19

+3.3V_DEEP_SUS

2

3

+3.3V_DEEP_SUS

U8

*TC7SH0 8FU

4

3 5

R74 *0_4_S

+3V_S5

+3V_S5

Q28

2N7002

2

1

DSW

+3V

CLKRUN/GPIO32

SUS_STAT/GPIO61

1

C97

*0.1U/10V /X7R_4

DSWVRMEN

DPWROK

WAKE

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

R353

*10K_4

AW7

AV5

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

DPWROK_R

PCIE_WAKE#_R

CLKRUN#

SUSCLK

SIO_SLP_A#

SIO_SLP_LAN#

EC-A04

R366 0_4R339 0_4

R356 *0_4

R84 *0_4_S

PLTRST#

RSMRST#

DSWVRMEN 6

DPWROK 24

PCIE_WAKE# 21

CLKRUN# 24

T97

T96

SLP_S4# 24

SIO_SLP_S3# 24

T95

SLP_SUS# 24

TP5

PM_BATLOW_N 24

PLTRST# 23

SIO_PWRBTN#

SUSWARN#

SUSCLK

AC_PRESENT

PM_BATLOW#

PCIE_WAKE#_R

CLKRUN#

SYS_RESET#

RSMRST#

SYS_PWROK

DPWROK_R

R118 *10K_4

R116 10K_4

R66 10K_4

R101 10K_4

R347 10K_4

R80 1K_4

EC-A29

R317 10K_4

R327 10K_4

R358 10K_4

R337 10K_4

R357 100K_4

+3.3V_DEEP_SUS

+3.3V_DSW

+3.3V_RUN

For DS3

R107 *0_6

R120

*100K_4

A A

SLP_SUS_ON_GPG224

5

C141

1U/6.3V_4

C140

*10P/50V _4

R119

*100K_4

U12

5

IN

4

IN

3

ON/OFF

IC(5P ) G52 43AT1 1U

GND

4

+3.3V_DEEP_SUS+3.3V_DSW +3.3V_DEEP_SUS

System PWR_OK(CLG)

EC-A18

1

OUT

2

R611 *4.7K_4

C135

0.1U/10V_4

IMVP _PWR GD9,35

3

+3.3V_DEEP_SUS +3.3V_RUN

2

R609

*10K_4

Q43

1 3

*MMBT39 04-7-F

3

2

1

R608

*10K_4

Q50

*2N7002

U32

*TC7SH0 8FU

IMVP _PWR GD_3 V

SYS_PWROK_EC24

SC33*AVLC 5S 0 2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Wednesday, February 27, 2013 8 37

Date: Sheet

Wednesday, February 27, 2013 8 37

Date: Sheet

2

Wednesday, February 27, 2013 8 37

2

1

R610 0_4

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Haswell ULT 7/12

Haswell ULT 7/12

Haswell ULT 7/12

3 5

1

C566

*0.1U/10V /X7R_4

4

SYS_PWROK

1A

1A

1A

of

of

of

Page 9

5

bios-fix.com

VCCST_PWRGD_L

+V1.05S_VCCST

+VCCIN

+V_VDDQ_VR

+1.05V_RUN

R54 *0_12_S

C79 10U/6.3V/X5R_6

C82 10U/6.3V/X5R_6

C81 10U/6.3V/X5R_6

C80 10U/6.3V/X5R_6

C161 10U/6. 3V/X5R_6

C91 10U/6.3V/X5R_6

C156 2.2U/ 6.3V/X5R_4

C188 2.2U/ 6.3V/X5R_4

C186 2.2U/ 6.3V/X5R_4

C189 2.2U/ 6.3V/X5R_4

+VCCIOA_OUT

+V1.05S_VCCST

EC-A19

C326 *0.1U/10V/X 5R_4

R290 10K_4

R39 150_6

T4

+VCCIN

R293 100/F _4

D D

6X10UF MLCC

4X2.2UF MLCC

+V1.05S_VCCST

R277

10K_4

3

Q4

2N7002

VCCST_PWRGD#24

H_VR_ENABLE_MCP35

C C

IMVP_PWRGD8,35

2

1

+V1.05S_VCCST

B B

VCCSENSE35

4

CPU VDDQ

Haswell ULT 15W : 4.2A

+V_VDDQ_VR

T11

T7

+VCCIN

+VCCIO_OUT

T13

T26

T19

T20

T18

T28

T65

T9

T14

T10

T12

T27

T29

T25

T86

T24

T30

T15

T16

MCP_RSVD _61

MCP_RSVD _62

MCP_RSVD _63

MCP_RSVD _64

VCCSENSE

MCP_RSVD _65

MCP_RSVD _66

MCP_RSVD _67

MCP_RSVD _68

H_CPU_SVIDALRT_N

VR_SVID_CLK

VR_SVID_DATA

FIVR_EN_BUF

MCP_RSVD _69

MCP_RSVD _70

MCP_RSVD _71

MCP_RSVD _72

MCP_RSVD _73

MCP_RSVD _74

MCP_RSVD _75

MCP_RSVD _76

MCP_RSVD _77

MCP_RSVD _78

MCP_RSVD _79

MCP_RSVD _80

MCP_RSVD _81

VCCSENSE

3

Haswell ULT MCP(POWER)

HSW_ULT_DDR3L

HSW ULT POWER

12 OF 19

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

AC58

AB23

AD23

AA23

AE59

AD60

AD59

AA59

AE60

AC59

AG58

AC22

AE22

AE23

AB57

AD57

AG57

L59

J58

F59

N58

E63

A59

E20

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

U59

V59

C24

C28

C32

U28L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

2

CPU VCC

Haswell ULT 15W : 32A

+VCCIN

C71 22U/6.3V/X5R_6

C76 22U/6.3V/X5R_6

C37 22U/6.3V/X5R_6

C50 22U/6.3V/X5R_6

C59 22U/6.3V/X5R_6

C51 22U/6.3V/X5R_6

C46 22U/6.3V/X5R_6

C34 22U/6.3V/X5R_6C160 10U/6. 3V/X5R_6

C52 22U/6.3V/X5R_6

C38 22U/6.3V/X5R_6

C60 22U/6.3V/X5R_6

C53 22U/6.3V/X5R_6

C32 22U/6.3V/X5R_6

C47 22U/6.3V/X5R_6

C67 22U/6.3V/X5R_6

C66 22U/6.3V/X5R_6

C43 22U/6.3V/X5R_6

C39 22U/6.3V/X5R_6

C35 22U/6.3V/X5R_6

C64 22U/6.3V/X5R_6

C36 22U/6.3V/X5R_6

C55 22U/6.3V/X5R_6

C61 22U/6.3V/X5R_6

C48 22U/6.3V/X5R_6

C33 22U/6.3V/X5R_6

C62 22U/6.3V/X5R_6

C63 22U/6.3V/X5R_6

C65 22U/6.3V/X5R_6

C49 22U/6.3V/X5R_6

C54 22U/6.3V/X5R_6

1 2

C89 1 00P/50VX7R_4

C87 1 00P/50VX7R_4

1 2

C45 1 00P/50VX7R_4

1 2

1 2

C44 1 00P/50VX7R_4

+V1.05S_VCCST

23 X 22UF(MLCC)

+VCCIO_OUT

1

+VCCIN35

+V1.05S_VCCST4,13

+V_VDDQ_VR14,32,37

+VCCIO_OUT13

+1.05V_RUN6,12,28,33,37

+VCCIOA_OUT2

9

SVID ALERT

H_CPU_SVIDALRT_N

SVID DATA

close to CPU

VR_SVID_DATA

R308

130_4

close to CPU

R309 43_4

+VCCIO_OUT+V1.05S_VCCST

close to VR

R305

*130_4

R310

75_4

+V1.05S_VCCST

R49

130_4

EC-A03

+V1.05S_VCCST

EC-A03

SVID CLK

A A

5

4

VR_SVID_CLK

3

close to VR

C567 0.1U/10V_4

2

R52

54.9_4

R311

*75_4

+VCCIO_OUT

R48

*130_4

+VCCIO_OUT

+V1.05S_VCCST

R51

*54.9_4

VR_SVID_ALERT# 35

VR_SVID_DATA 35

VR_SVID_CLK 35

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Quanta Computer Inc.

Haswell ULT 8/12

Haswell ULT 8/12

Haswell ULT 8/12

Wednesday, February 27, 2013 9 37

Wednesday, February 27, 2013 9 37

Wednesday, February 27, 2013 9 37

1

of

of

of

1A

1A

1A

Page 10

5

bios-fix.com

Haswell ULT (GND)

4

3

2

1

10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U28O

HSW_ULT_DDR3L

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D50

D51

D53

D54

D55

D57

D59

D62

E11

E17

G18

G22

H13

HSW_ULT_DDR3L

U28P

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D8

VSS

VSS

VSS

F20

VSS

F26

VSS

F30

VSS

F34

VSS

F38

VSS

F42

VSS

F46

VSS

F50

VSS

F54

VSS

F58

VSS

F61

VSS

VSS

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

VSS

16 OF 19

VSS_SENSE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

AU44

AV44

AT2

D15

F22

H22

J21

R295

100/F_4

U28R

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSSSENSE 35

HSW_ULT_DDR3L

18 OF 19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

HSW_ULT_DDR3L

D D

C C

B B

A11

A14

A18

A24

A28

A32

A36

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U28N

14 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

U28Q

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

5

TP_DC_TEST_AY60

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_B2

DC_TEST_A3_B3

DC_TEST_A61_B61

DC_TEST_B62_B63

DC_TEST_C1_C2

T94

T44

A A

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61

DAISY_CHAIN_NCTF_AY61

AY62

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B61

DAISY_CHAIN_NCTF_B61

B62

DAISY_CHAIN_NCTF_B62

B63

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

HSW_ULT_DDR3L

17 OF 19

4

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW 1

DAISY_CHAIN_NCTF_AW 2

DAISY_CHAIN_NCTF_AW 3

DAISY_CHAIN_NCTF_AW 61

DAISY_CHAIN_NCTF_AW 62

DAISY_CHAIN_NCTF_AW 63

A3

A4

A60

A61

A62

AV1

AW1

AW2

AW3

AW61

AW62

AW63

DC_TEST_A3_B3

TP_DC_TEST_A4

TP_DC_TEST_A60

DC_TEST_A61_B61

TP_DC_TEST_A62

TP_DC_TEST_AV1

TP_DC_TEST_AW1

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_AW63

3

T45

T43

T41

T92

T91

T93

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Wednesday, February 27, 2013 10 37

Date: Sheet

Wednesday, February 27, 2013 10 37

Date: Sheet

2

Wednesday, February 27, 2013 10 37

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Haswell ULT 9/12

Haswell ULT 9/12

Haswell ULT 9/12

1

1A

1A

1A

of

of

of

Page 11

5

bios-fix.com

4

3

2

1

U28S

HSW_ULT_DDR3L

11

T83

T80

T81

T79

D D

C C

T23

T78

T22

T77

T76

T74

T21

T68

T69

T67

T17

T82 R362 49.9/F_4

T72

T75

T71

R314 49.9/F_4

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

NOA_STBN_0

NOA_STBN_1

NOA_STBP_0

NOA_STBP_1

NOA_RCOMP

TD_IREF

R26

8.2K

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

AA62

U63

AA61

U62

V63

H18

B12

T63

T62

T61

T60

A5

E1

D1

J20

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

TD_IREF

RESERVED

PROC_OPI_RCOMP

19 OF 19

Processor Strapping

1 0

CFG0

EAR-STALL/NOT STALL RESET SEQUENCE

AFTER PCU PLL IS LOCKED

CFG1

PCH/ PCH LESS MODE SELECTION

(DEFAULT) NORMAL OPERATION; NO STALL STALL

(DEFAULT) NORMAL OPERATION PCH-LESS MODE

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

PROC_OPI_COMP

AV62

D58

P22

N21

P20

R20

T90

T89

T2

T1

T46

T48

T47

T66T73

CFG0

R326 *1K_4

CFG1

R323 *1K_4

CFG3

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

B B

A A

CFG4

DISPLAY PORT PRESENCE STRAP

CFG 8

ALLOW THE USE OF NOA ON LOCKED UNITS

CFG9

NO SVID PROTOCOL CAPABLE VR CONNECTED

CFG10

SAFE MODE BOOT

5

DISABLED

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO

EMBEDDED DISPLAY PORT

DISABLED(DEFAULT); IN THIS CASE,

NOA WILL BE DISABLED IN LOCKED

UNITS AND ENABLED IN UN-LOCKED

UNITS

VRS SUPPORTING SVID PROTOCOL ARE

PRESENT

POWER FEATURES ACTIVATED

DURING RESET

4

ENABLED

SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED; NOA WILL BE AVAILABLE

REGARDLESS OF THE LOCKING OF THE UNIT

NO VR SUPPORTING SVID IS PRESENT. THE

CHIP WILL NOT GENERATE (OR RESPOND TO)

SVID ACTIVITY

POWER FEATURES (ESPECIALLY CLOCK

GATINE ARE NOT ACTIVATED

3

CFG3

R320 *1K_4

CFG4

R65 1K_4

CFG8

R319 *1K_4

CFG9

R316 *1K_4

CFG10

R61 *1K_4

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Haswell ULT 10/12

Haswell ULT 10/12

Haswell ULT 10/12

Wednesday, February 27, 2013 11 37

Wednesday, February 27, 2013 11 37

Wednesday, February 27, 2013 11 37

1

of

of

of

1A

1A

1A

Page 12

5

bios-fix.com

4

3

2

+3.3V_DEEP_SUS4,5,6,7,8,14,28

+1.05V_RUN6,9,28,33,37

+1.5V_RUN17,21,34,37

+3.3V_RUN2,4,6,7,8,14,15,16,17,19,20,21,23,24,25,26,27,30,35,36,37

+3.3V_DSW4,6,8,17,21,23,25,31,34,36

+15V_ALW31,36

+V1.05S_AXCK_LCPLL7

+V1.05S_AUSB3PLL5

+V1.05S_ASATA3PLL6

1

+5V_ALW14,17,20,22,23,31,32,33,36,37

12

Haswell ULT PCH(POWER)

D D

U28M

AA21

W21

AH14

AH13

AH10

AE20

AE21

L10

B18

B11

Y20

J13

AC9

AA9

W9

J18

K19

A20

J17

R21

T21

K18

M20

V21

K9

M9

N8

P9

V8

VCCHSIO

VCCHSIO

VCCHSIO

VCC1_05

VCC1_05

VCCUSB3PLL

VCCSATA3PLL

RSVD

VCCAPLL

VCCAPLL

DCPSUS3

VCCHDA

DCPSUS2

VCCSUS3_3

VCCSUS3_3

VCCDSW3_3

VCC3_3

VCC3_3

VCCCLK

VCCCLK

VCCACLKPLL

VCCCLK

VCCCLK

VCCCLK

RSVD

RSVD

RSVD

VCCSUS3_3

VCCSUS3_3

+V1.05DX_MODPHY

VCCHSIO

+V1.05DX_MODPHY

1.838A

1.741A

+V3.3DX_1.5DX_AUDIO+3.3V_DEEP_SUS

R75 *0_6

+1.5V_RUN

R71 *0_6_S

11mA

C C

+1.05V_RUN

10mA

+V3.3DX_1.5DX_AUDIO

25mA

+3.3V_DEEP_SUS

0.114A

+3.3V_DSW

41mA

+3.3V_RUN

+1.05V_RUN

+1.05V_RUN

63mA

+3.3V_DEEP_SUS

TP1

TP4

R109 *0_8_S

R115 *0_6_S

R24 *0_8_S

R23 *0_6_S

R111 *0_4_S

C22 1U/6.3V_4

C28 1U/6.3V_4

VCCUSB3PLL

VCCSATA3PLL

54mA

C27 *1U/6.3V_4

C83 1U/6.3V_4

C84 *1U/6.3V_4

C118 22U/6.3V_8

C129 1U/6.3V_4

C23 22U/6.3V_8

C26 1U/6.3V_4

C20 1U/6.3V_4

+V1.05DX_MODPHY

+V1.05S_AUSB3PLL

+V1.05S_ASATA3PLL

+V1.05S_APLLOPI

+V1.05A_VCCUSB3SUS

+V1.05A_USB2SUS

+V3.3A_PSUS

VCCDSW

+V3.3S_PCORE

+V1.05S_AXCK_DCB

+V1.05S_AXCK_LCPLL

+V1.05S_SSCF100

+V3.3A_PSUS

+V1.05DX_MODPHY

B B

HSW_ULT_DDR3L

HSIO

OPI

USB3

HDA

VRM

GPIO/LPC

LPT LP POWER

L17 2.2uH_6

C303

47U/6.3V_8

13 OF 19

RTC

SPI

CORE

THERMAL SENSOR

SERIAL IO

SUS OSCILLATOR

USB2

C314

10U/6.3V/X5R_6

VCCSUS3_3

VCCRTC

DCPRTC

VCCSPI

VCCASW

VCCASW

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCC1_05

DCPSUSBYP

DCPSUSBYP

VCCASW

VCCASW

VCCASW

DCPSUS1

DCPSUS1

VCCTS1_5

VCC3_3

VCC3_3

VCCSDIO

VCCSDIO

DCPSUS4

RSVD

VCC1_05

VCC1_05

+V1.05S_AUSB3PLL

C327

1U/6.3V_4

AH11

AG10

AE7

Y8

AG14

AG13

J11

H11

H15

AE8

AF22

AG19

AG20

AE9

AF9

AG8

AD10

AD8

J15

K14

K16

U8

T9

AB8

AC20

AG16

AG17

EC-A08

+3V_VCCPSUS_P

+VCCRTCEXT

C74 0.1U/10V/X5R_4

VCCSPI_ PCH

+V1.05S_CORE_PCH

+V1.05M_ASW

+V1.05A_SUS_PCH

+V3.3S_PTS

+V1.05A_AOSCSUS

+V1.05S_DUSB

+1.05V_RUN

L2 2.2uH_6

+V3.3S_1.8S_LPSS_SDIO

C56

47U/6.3V_8

C57

10U/6.3V/X5R_6

C119 1U/6.3V_4

C249 1U/6.3V_4

C341 0.1U/10V/X5R_4

C128 0.1U/10V/X5R_4

C69 0.1U/10V/X5R_4

C41 1U/6.3V_4

C42 1U/6.3V_4

C88 10U/6.3V/X5R_6

C85 1U/6.3V_4

C73 1U/6.3V_4

C68 22U/6.3V_8

C72 *1U/6.3V_4

C21 0.1U/10V/X5R_4

C313 1U/6.3V_4

C70 1U/6.3V_4

C86 1U/6.3V_4

+V1.05S_APLLOPI

C58

1U/6.3V_4

+1.05V_RUN

L18 2.2uH_6

R98 *0_4_S

R60 *0_4_S

R58 *0_4

R62 *0_12_S

R46 *0_12_S

R27 *0_4_S

R273 *0_6_S

R55 *0_8_S

C304

47U/6.3V_8

+3.3V_DEEP_SUS

+RTC_CELL

+3.3V_DEEP_SUS

+3.3V_RUN

+1.05V_RUN

+1.05V_RUN

+1.05V_RUN

TP3

+1.5V_RUN

+3.3V_RUN

+3.3V_RUN

TP2

+1.05V_RUN

+V1.05S_AXCK_LCPLL

C315

10U/6.3V/X5R_6

VCCSUS3

129mA

18mA

VCC1_05

2.6A

VCCASW

0.658A

0.109A

3mA

1mA

17mA

C328

1U/6.3V_4

+V1.05DX_MODPHY

+3.3V_RUN

R272

100K_4

Q24B

MODPHY_EN4,33

A A

R271

*100K_4

2

2N7002DW

5

+15V_ALW

R267

10K_4

2

Q21

ME2303T1

3 1

R263 330_4

R261 330_4

3

Q22

61

2

2N7002

1

+1.05V_RUN

EC-A28

0.022U/25V_4

4

Q23

TPCC8067

5 2

4

C299

2N7002DW

+V1.05DX_MODPHY

1

3

Q24A

5

+V1.05DX_MODPHY

L16 2.2uH_6

C302

47U/6.3V_8

R270

100_4

34

C320

10U/6.3V/X5R_6

3

+V1.05S_ASATA3PLL

C325

1U/6.3V_4

+1.05V_RUN

L1 2.2uH_6

47U/6.3V_8

+V1.05S_AXCK_DCB

C19

C18

10U/6.3V/X5R_6

C40

1U/6.3V_4

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

2

Date: Sheet of

Quanta Computer Inc.

Haswell ULT 11/12

Haswell ULT 11/12

Haswell ULT 11/12

Wednesday, February 27, 2013 12 37

Wednesday, February 27, 2013 12 37

Wednesday, February 27, 2013 12 37

1

of

1A

1A

1A

Page 13

5

bios-fix.com

4

3

2

+V1.05S_VCCST4,9

+VCCIO_OUT9

1

13

D D

DSW

MISC

THERMAL

PWR

DDR3L

HSW_ULT_DDR3L

JTAG

2 OF 19

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

SC2 *AVLC 5S 02 100

XDP_PRDY_N

XDP_PREQ_N

XDP_TMS_CPU

XDP_TDI_CPU

XDP_TDO_CPU

XDP_BPM0_R

XDP_BPM1_R

XDP_BPM2_R

XDP_BPM3_R

XDP_BPM4_R

XDP_BPM5_R

XDP_BPM6_R

XDP_BPM7_R

XDP_TDO_CPU

XDP_TDI_CPU

XDP_TMS_CPU

XDP_TCK0

XDP_TRST_CPU_N

T60

T62

T53

T54

T57

T6

T55

T58

T59

T61

T56

T8

T5

XDP_TCK0 6

XDP_TRST_CPU_N 6

+V1.05S_VCCST

R297 51

R296 *51

R294 *51

R38 51

R37 *51

U28B

PROC_DETECT#

T42

PECI_EC_R24

+VCCIO_OUT

IMVP7_PROCHO T#24,30,35

C C

B B

+V1.05S_VCCST

SM_DRAMRST#14

DDR_PG_CTRL14

R298 *62_4

R300 62_4

T63

R299 56_4

R278 10K_4

SC9 *AVLC 5S 02 100

R95 200_4

R94 120_4

R93 100_4

CATERR#

H_PROCHOT#

H_CPUPWRGD

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST#

DDR_PG_CTRL

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

A A

PROJECT : LZ5

PROJECT : LZ5

PROJECT : LZ5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Num ber Rev

Size Document Num ber Rev

5

Size Document Num ber Rev

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

Haswell ULT 12/12

Haswell ULT 12/12

Haswell ULT 12/12

Wednesday, February 27, 2013 13 37

Wednesday, February 27, 2013 13 37

Wednesday, February 27, 2013 13 37

1

of

of

of

1A

1A

1A

Page 14

5

bios-fix.com

M_A_A[15:0]3

D D

M_A_BS#03

M_A_BS#13

M_A_BS#23

M_A_CS#03

M_A_CS#13

M_A_CLKP03

M_A_CLKN03

M_A_CLKP13

M_A_CLKN13

M_A_CKE03

M_A_CKE13

M_A_CAS#3

M_A_RAS#3

M_A_WE#3

PCH_SCLK7,25

PCH_SDATA7,25

C C

M_A_DQSP03

M_A_DQSP13

M_A_DQSP23

M_A_DQSP33

M_A_DQSP43

M_A_DQSP53

M_A_DQSP73

M_A_DQSP63

M_A_DQSN03

M_A_DQSN13

M_A_DQSN23

M_A_DQSN33

M_A_DQSN43

M_A_DQSN53

M_A_DQSN73

M_A_DQSN63

B B

A A

DDR3L SODIMM ODT DENERATION

DDR_PG_CTRL13

EC_SLP_S4#24,32,37

R152 10K_4

R155 10K_4

5

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

DIMM0_SA0

DIMM0_SA1

PCH_SCLK

PCH_SDATA

M_A_ODT0

M_A_ODT1

M_A_DM1

M_A_DM2

2

74AUP1G07GW

CN10A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

CK0#

102

CK1

104

CK1#

73

CKE0

74

CKE1

115

CAS#

110

RAS#

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

ODT0

120

ODT1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3-DIMM0_H=4_STD

ddr-c-201 3289-204p

DGMK4000004

IC SOCKET D DR3 SODIMM(204P ,H4.0,STD)

+V_VDDQ_VR

U10

R104

100K_4

5

5

4

+5V_ALW

34

NC1VCC

A

GND3Y

Q7A

2N7002DW

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17