Page 1

1

2

3

4

5

6

7

8

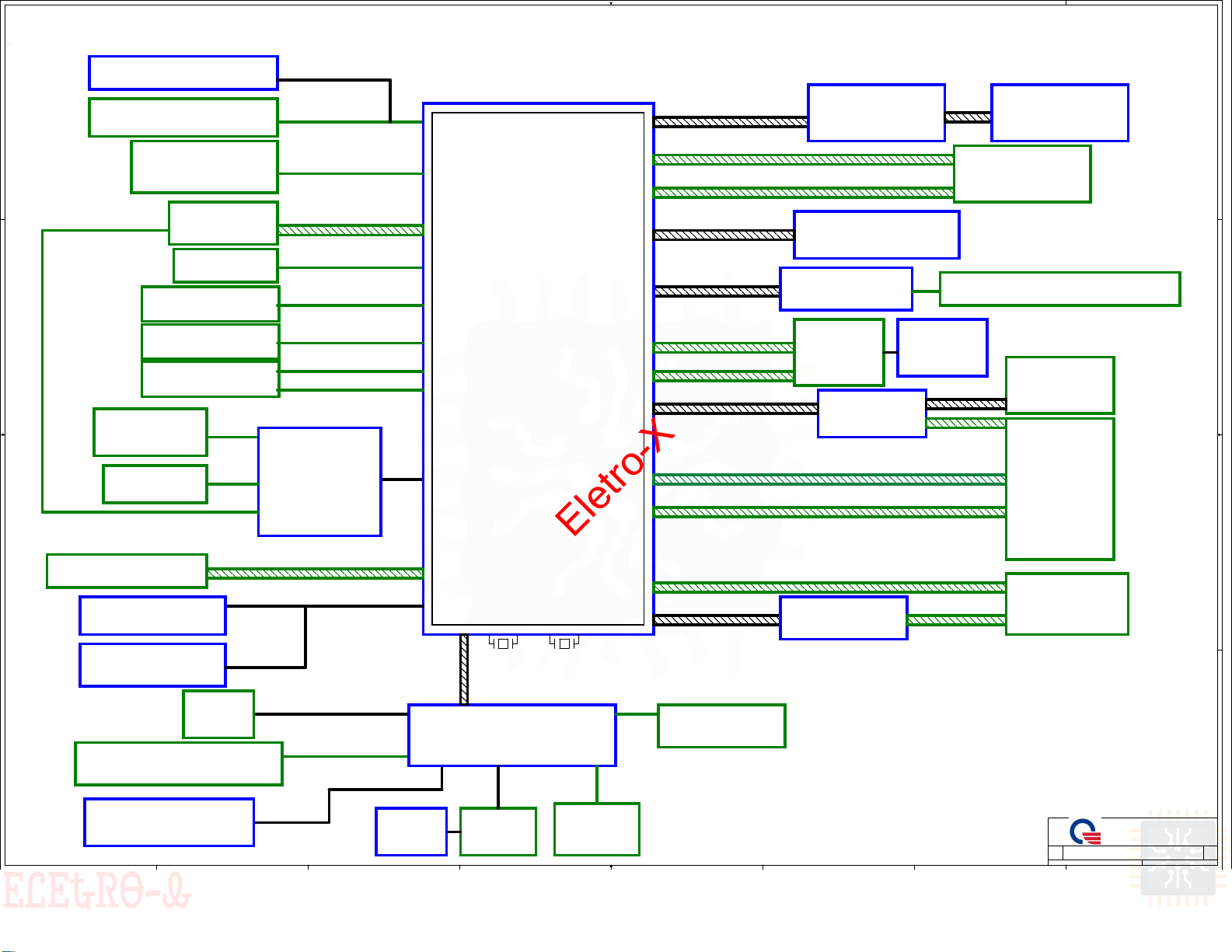

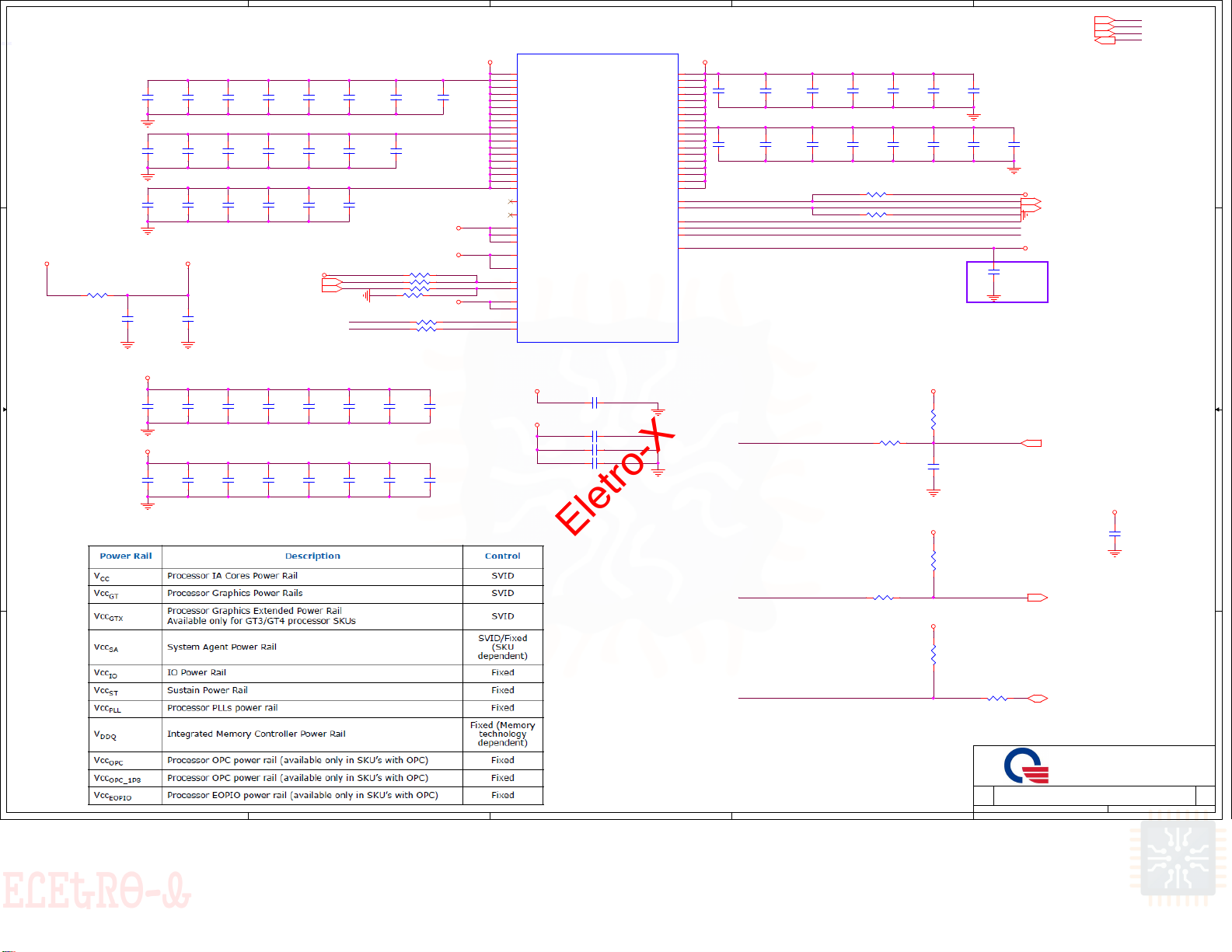

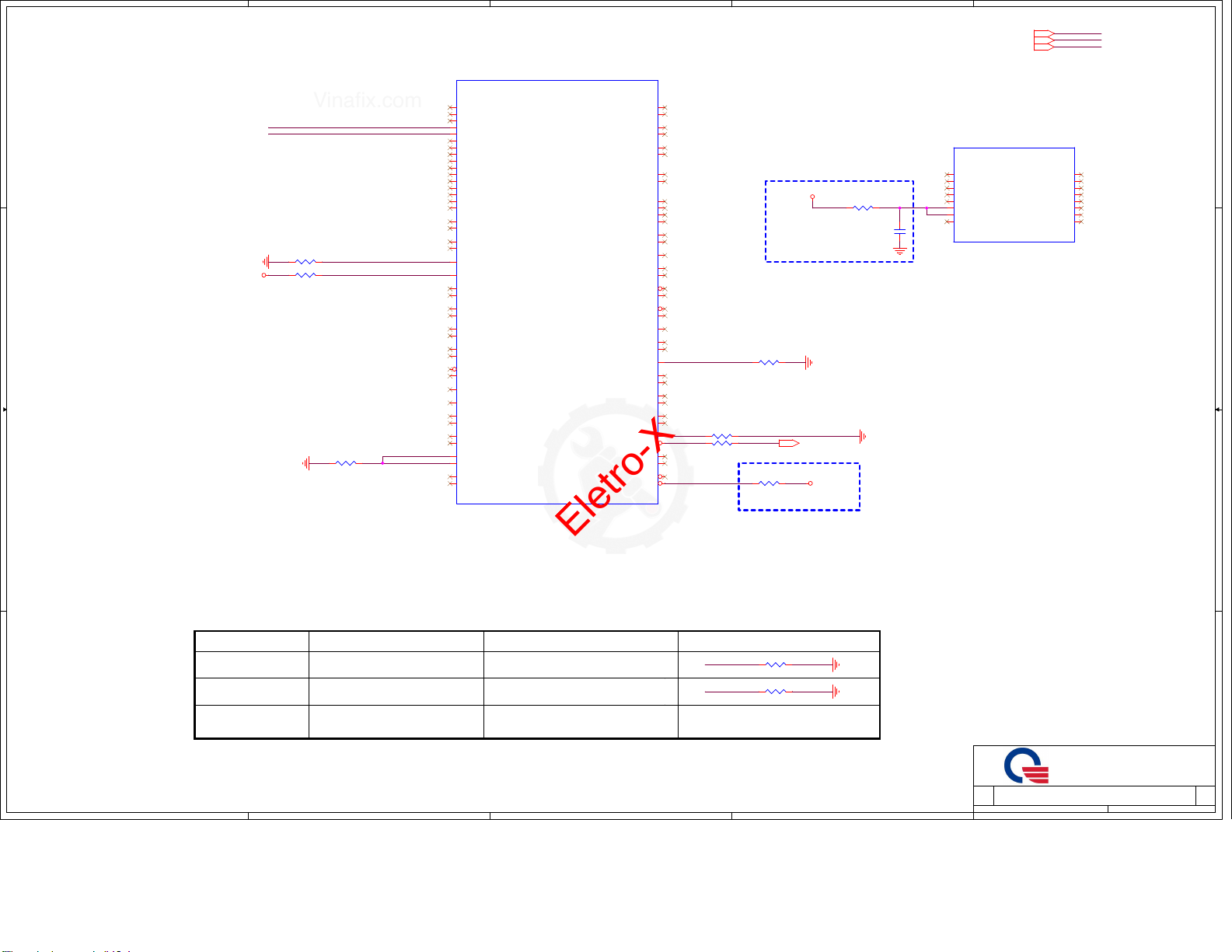

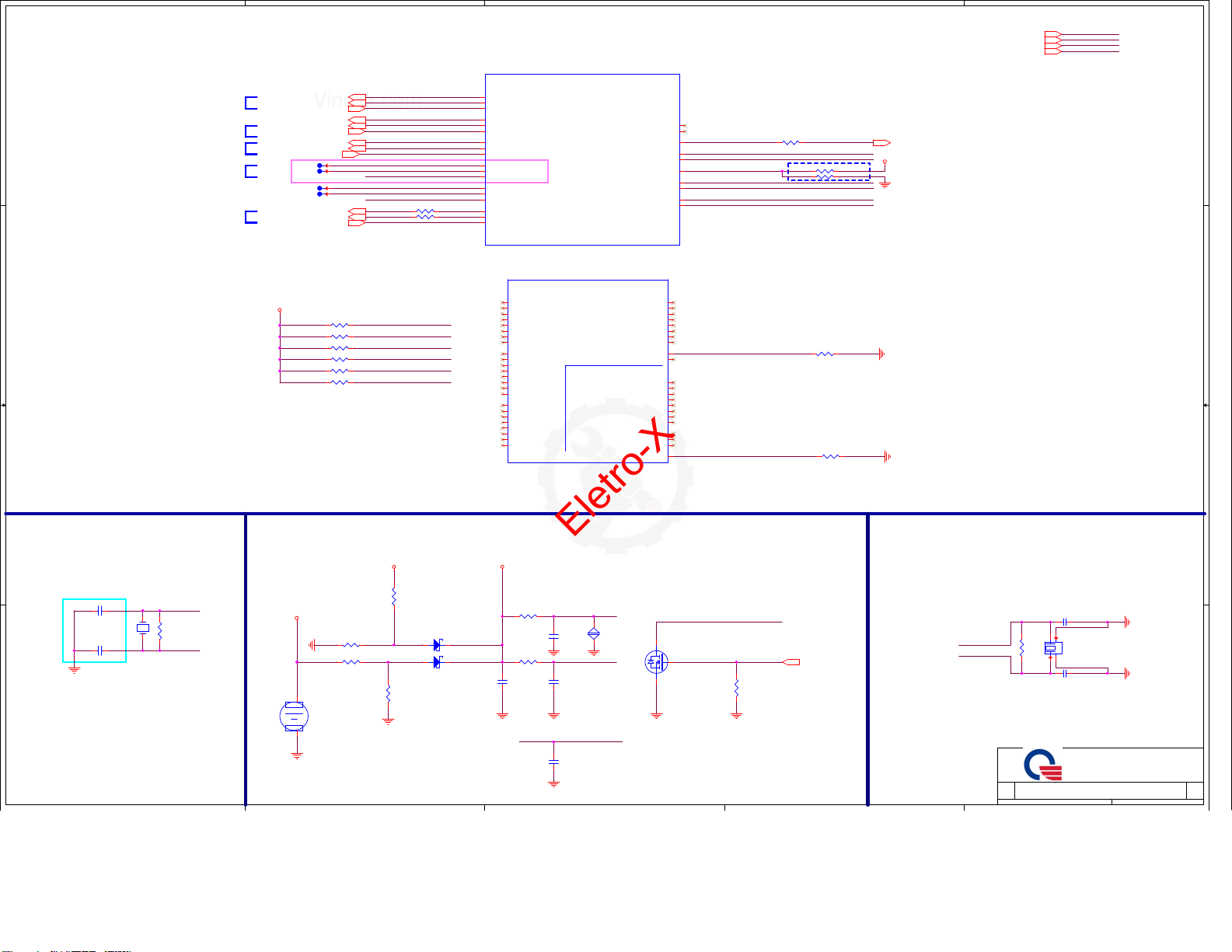

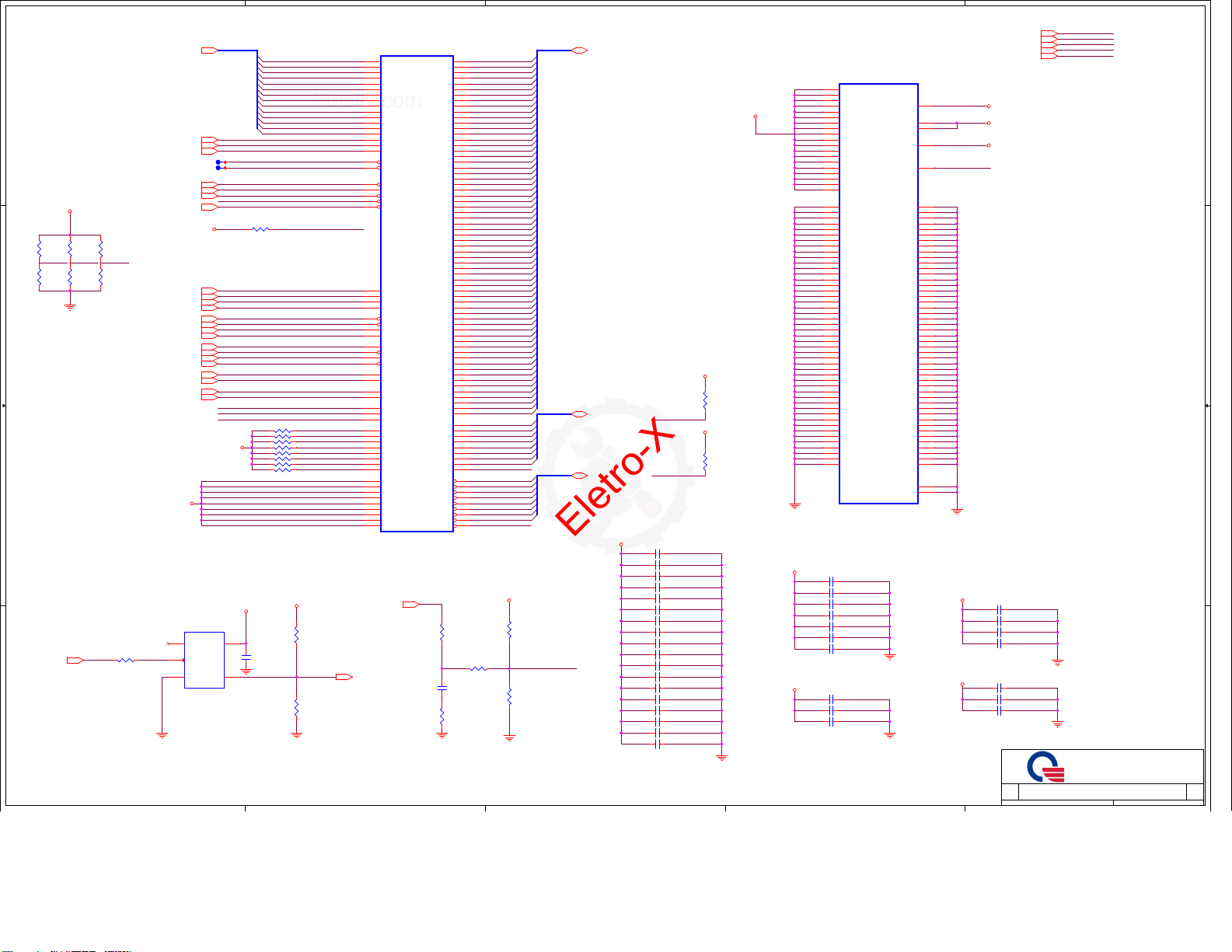

Intel Skylake-U Platform Block Diagram (Windows)

01

DDR4 Memory Down MA

A A

DDR4 SO-DIMM X1 MB

1866-2133 MT/s

PCIE Gen3*4

AMD dGPU

R16M-M1-30

S3

eDP Conn(30pin)

FHD support

HD Camera

eDP 2 Lanes

USB2.0 (480Mb/s)

DMIC

HDMI Conn

HDD

B B

ODD

HDMI (1.65Gb/s)

SATA Gen3 (6Gb/s)

SATA Gen3 (6Gb/s)

Skylake-U SoC

SATA Gen3 (6Gb/s)

M.2 NGFF SSD

PCIE Gen3 * 4

Intel

15W

BGA 1356

Size : 42x24(mm)

HP/Mic Audio

HDA

USB3.0 (5Gb/s)*2

USB2.0 (480Mb/s)*2

PCIE Gen2 *1(5Gb/s)

USB2.0 (480Mb/s)

USB2.0 (480Mb/s)

PCIE Gen2 (5Gb/s)

DP 4 Lanes

1G Ethernet

RTL8111H

Card Reader

RTS5170

4-in-1(SD/SDHC/SDXC/MMC) CONN

NGFF Slot WLAN+BT

Module

M.2 2230

DP SW

PS8338B

VRAM DDR3L

2Gb/4Gb *4

USB 3.0 Port*2

DP to VGA

RTD2166-CG

Combo Jack

AUDIO CODEC

Speaker L/R

ALC3240

USB3.0 (5Gb/s)

USB2.0 (480Mb/s)

Lenovo

Onelink+

Connector

C C

USB2.0 (480Mb/s)

Finger print Sensor

USB2.0 (480Mb/s)

SPI

SPI Flash(16MB)

W25Q128FWSSIG

USB2.0 (480Mb/s)

AOU5 Charger

TPS2546RTER

(Cable

Docking)

USB 2.0 Port*2

24MHz

SMBus

32.768KHz

Synaptics

4

T/P

PS/2

Hall Sensor

EM-1791

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

6

7

Date: Sheet of

PROJECT :

RV310 Block Diagram

RV310 Block Diagram

RV310 Block Diagram

LV6

LV6

LV6

8

1A

1A

1A

1 61Friday, March 11, 2016

1 61Friday, March 11, 2016

1 61Friday, March 11, 2016

TPM 1.2

ST33HTPM2E32AAB9

K/B

D D

Thermal Sensor

( 1local +2 remote)

W83773G

SCAN MATRIX

SMBus

WRST#

CPU PTC Circuit

Place near CPU

1

2

3

LPC

EC(ITE)

IT8886

BatteryCharger

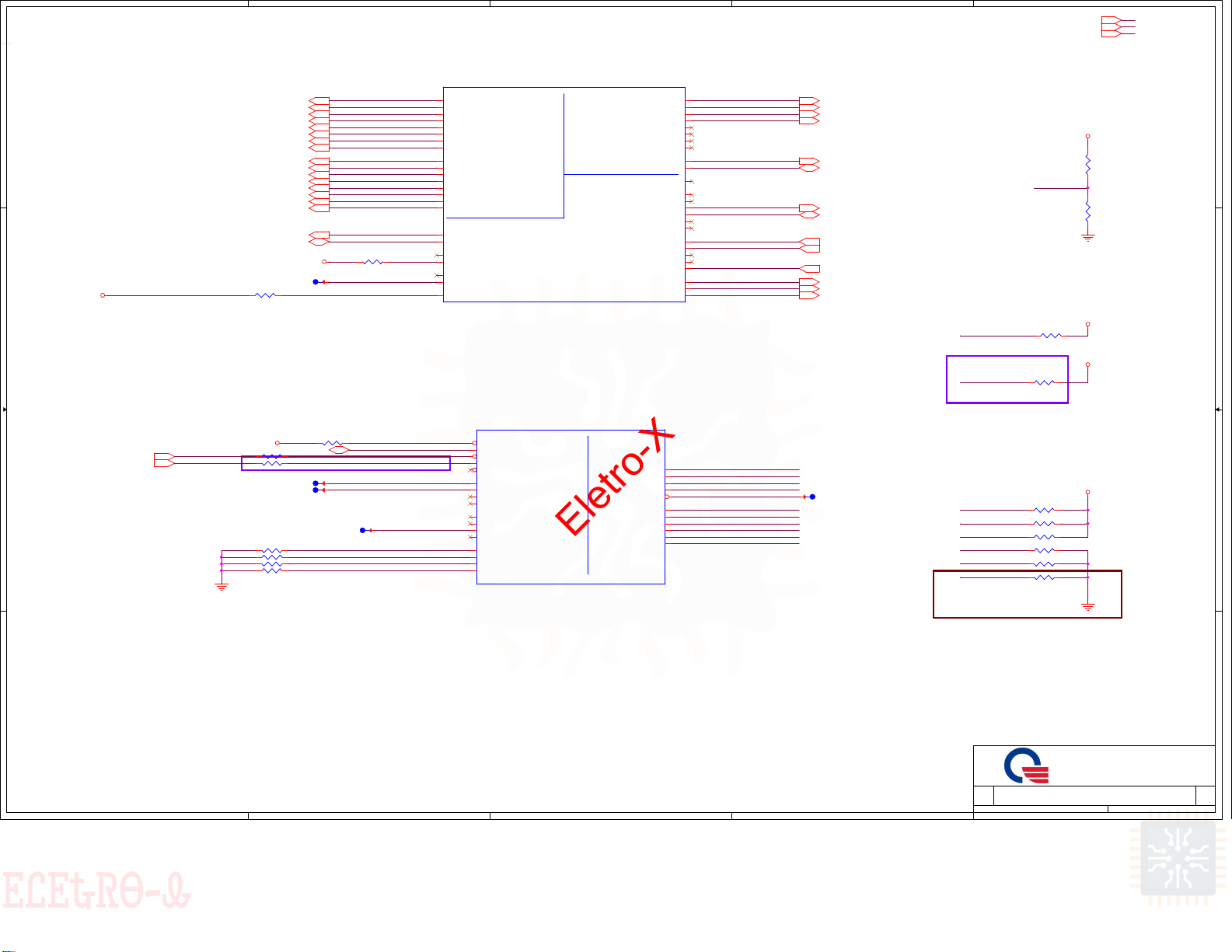

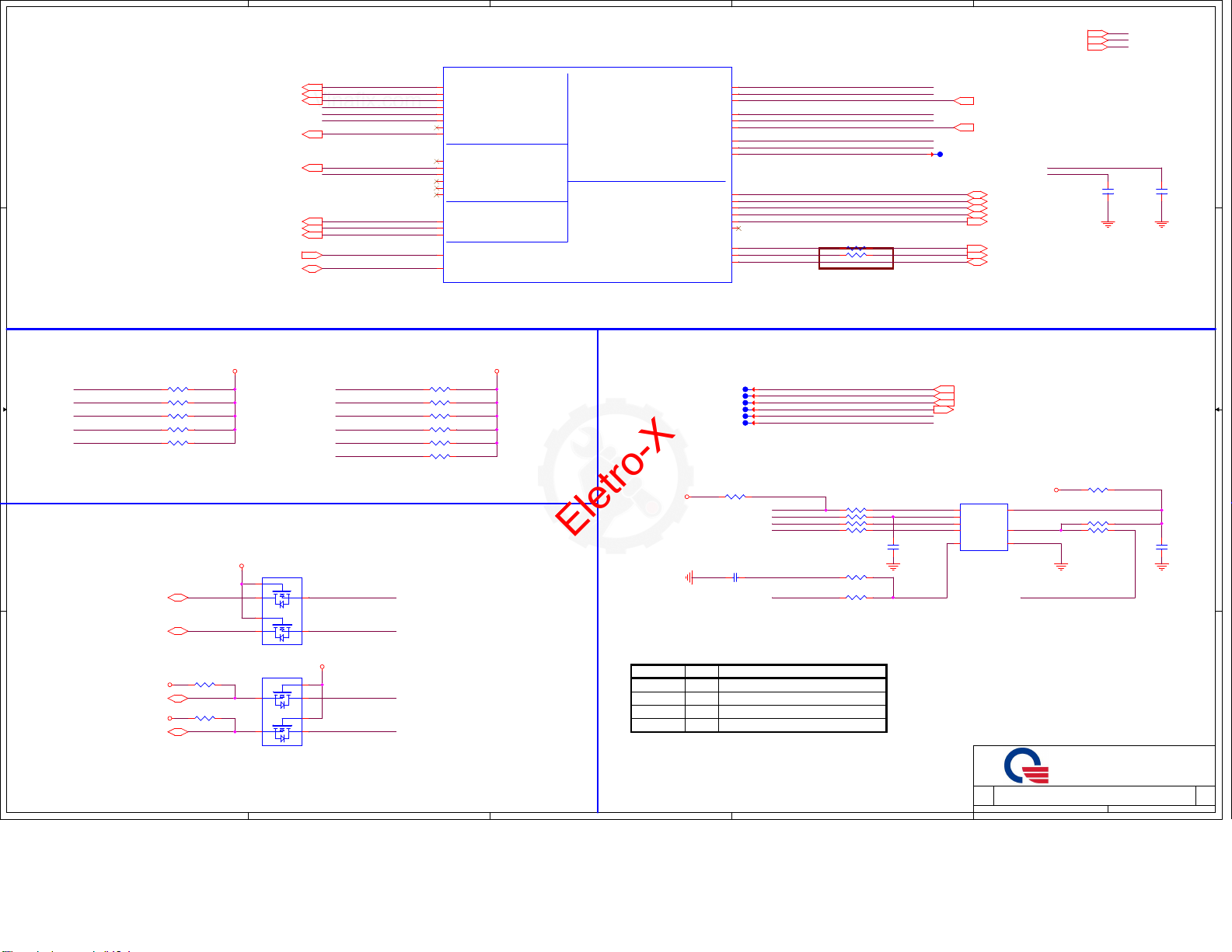

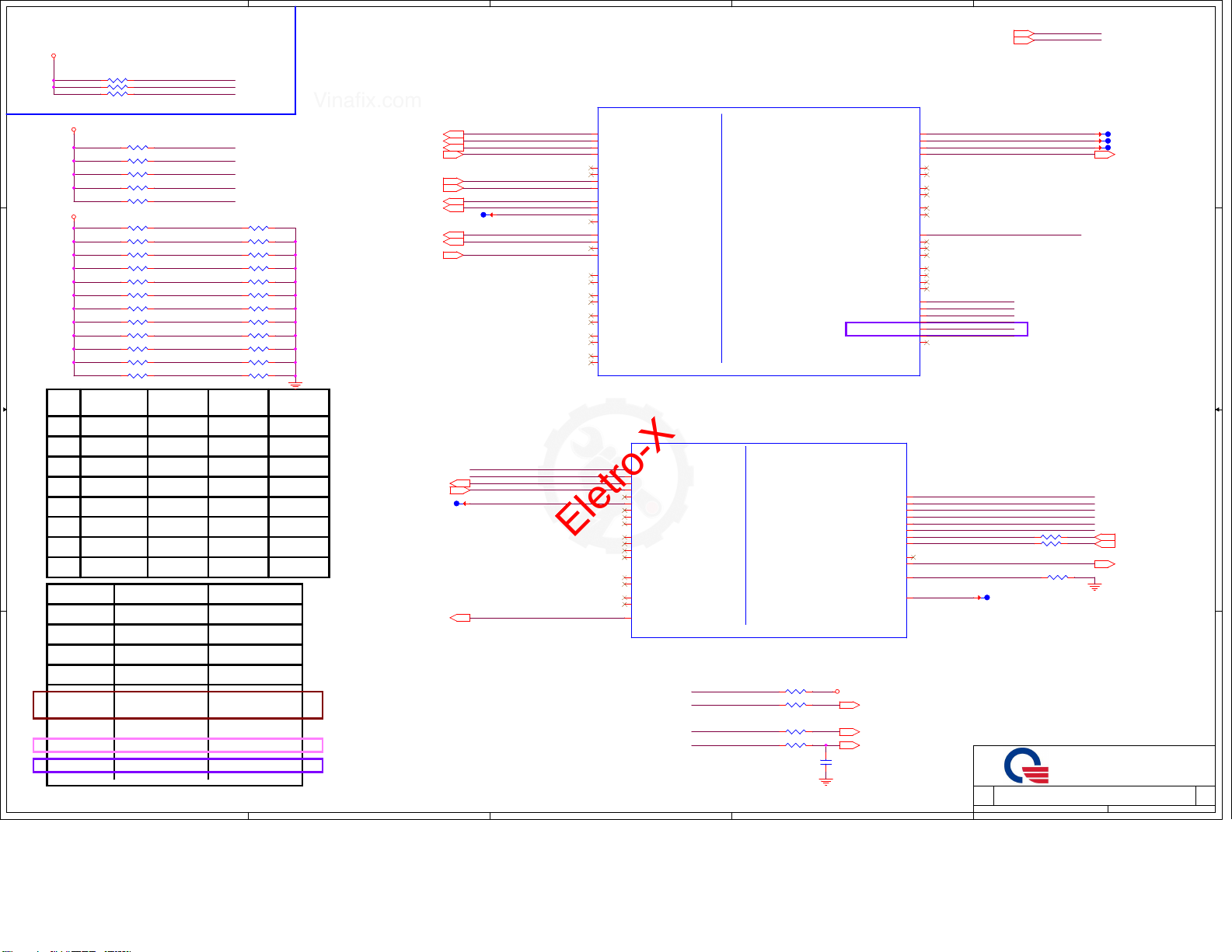

Page 2

5

IN_D2#{26}

D D

HDMI

DOCK DP

+VCCIO

C C

eDP_COMPIO and ICOMPO signals should be shorted near

balls and routed with typical impedance <25 mohms

IN_D2{26}

IN_D1#{26}

IN_D1{26}

IN_D0#{26}

IN_D0{26}

IN_CLK#{26}

IN_CLK{26}

DOCK_DDI2_TXN0{40}

DOCK_DDI2_TXP0{40}

DOCK_DDI2_TXN1{40}

DOCK_DDI2_TXP1{40}

DOCK_DDI2_TXN2{40}

DOCK_DDI2_TXP2{40}

DOCK_DDI2_TXN3{40}

DOCK_DDI2_TXP3{40}

SDVO_CLK{26}

SDVO_DATA{26}

R175 24.9/F_4

+3V

TP7

4

IN_D2#

IN_D2

IN_D1#

IN_D1

IN_D0#

IN_D0

IN_CLK#

IN_CLK

DOCK_DDI2_TXN0

DOCK_DDI2_TXP0

DOCK_DDI2_TXN1

DOCK_DDI2_TXP1

DOCK_DDI2_TXN2

DOCK_DDI2_TXP2

DOCK_DDI2_TXN3

DOCK_DDI2_TXP3

R203 2.2K_4

EDP_RCOMP

U38A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL_ULT

REV = 1

SKL_ULT

DDI

DISPLAY SIDEBANDS

3

?

Need apply PN

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

?1 OF 20

INT_EDP_TXN0

C47

INT_EDP_TXP0

C46

INT_EDP_TXN1

D46

INT_EDP_TXP1

C45

A45

B45

A47

B47

INT_EDP_AUXN

E45

INT_EDP_AUXP

F45

B52

G50

F50

DOCK_DDI2_AUXN

E48

DOCK_DDI2_AUXP

F48

G46

F46

PCH_HDMI_HPD

L9

PCH_DOCK_DP_HPD

L7

L6

N9

EDP_HPD

L10

PCH_LVDS_BLON

R12

PCH_DPST_PWM

R11

PCH_LCDVCC_EN

U13

2

INT_EDP_TXN0 {25}

INT_EDP_TXP0 {25}

INT_EDP_TXN1 {25}

INT_EDP_TXP1 {25}

INT_EDP_AUXN {25}

INT_EDP_AUXP {25}

DOCK_DDI2_AUXN {40}

DOCK_DDI2_AUXP {40}

PCH_HDMI_HPD {26}

PCH_DOCK_DP_HPD {40}

EDP_HPD {25}

PCH_LVDS_BLON {25}

PCH_DPST_PWM {25}

PCH_LCDVCC_EN {25}

1

+3V{4,10,11,12,13,14,15,17,18,25,26,27,29,30,31,34,36,37,38,40,41,42,45,49,52,53,54}

+VCCIO{4,6,53,56}

+VCCSTPLL{4,5,6,9,45,53,56}

Reserve EDP_HPD opposites circuit!

+3V

R200

*10K_4

R199

100K_4

+VCCSTPLL

+VCCSTPLL

H_PROCHOT#

PM_THRMTRIP#_R

EDP_HPD

R590 1K_4

R583 1K_4

02

B2A

U38D

EC_PECI{36}

TP34

TP36

R601 *51_4

H_PROCHOT#{36,42,43,45}

PM_THRMTRIP#{36}

B B

H_PROCHOT#

+VCCIO

R596 499/F_4

R762 100/F_4

B2A

R278 49.9/F_4

R277 49.9/F_4

R620 GT3@49.9/F_4

R626 GT3@49.9/F_4

CATERR#

EC_PECI

PROCHOT#

PM_THRMTRIP#_R

TP49

PROC_POPIRCOMP

PCH_OPI_RCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKL_ULT

REV = 1

SKL_ULT

CPU MISC

4 OF 20

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

PDC

?

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

XDP_TCK0

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_TCK1

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_TCK0

TP35

XDP_TMS

XDP_TDO

XDP_TDI

XDP_TCK0

XDP_TCK1

EC_PECI

R576 *51_4

R588 51_4

R581

R602 51_4

R603 *51_4

R792 KBY@330_4

*51_4

+VCCIO

PLACE NEAR CPU

Need apply PN

?

D3A

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SKYLAKE 1/15 eDP/DDI/MISC

SKYLAKE 1/15 eDP/DDI/MISC

SKYLAKE 1/15 eDP/DDI/MISC

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

LV6

LV6

LV6

1A

1A

2 61Friday, March 11, 2016

2 61Friday, March 11, 2016

1

2 61Friday, March 11, 2016

1A

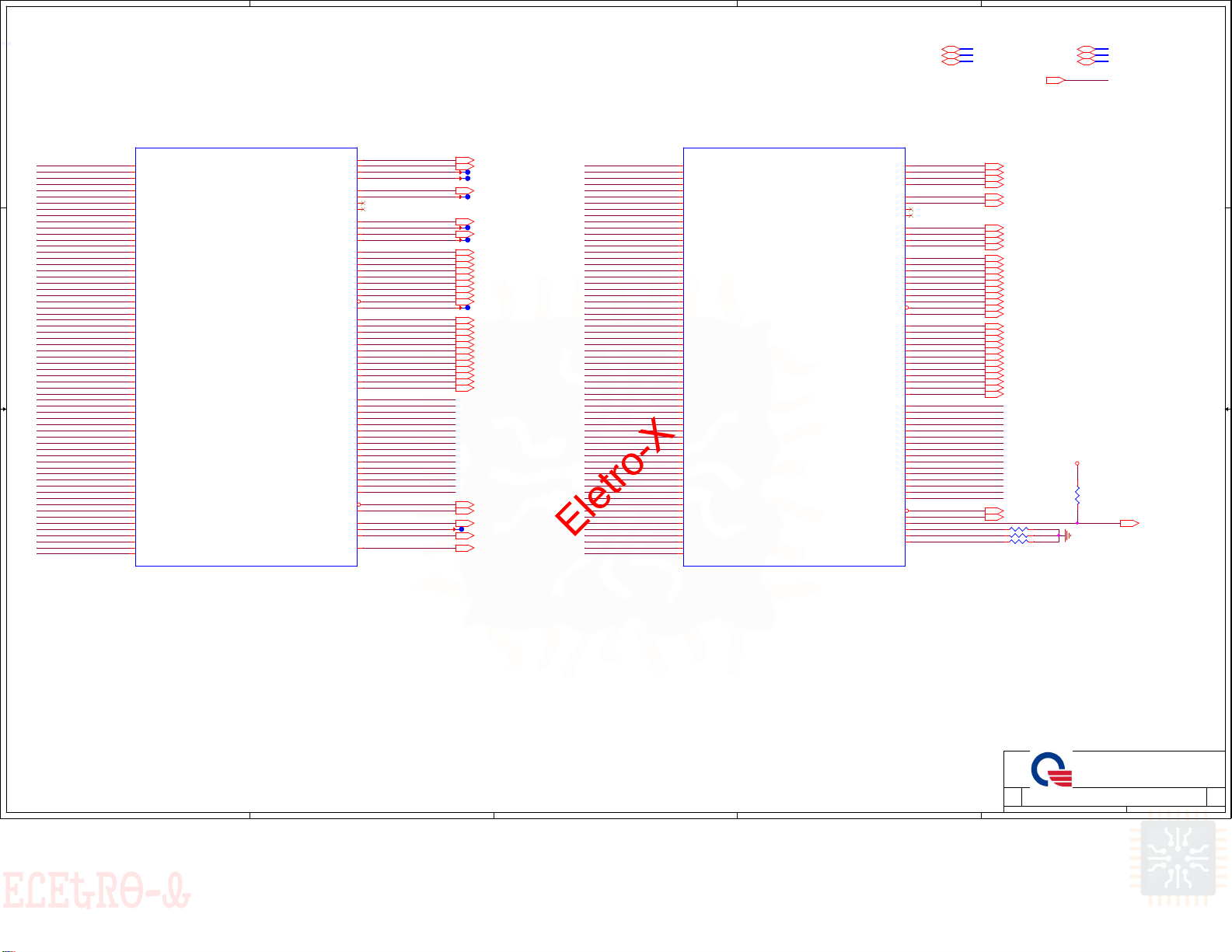

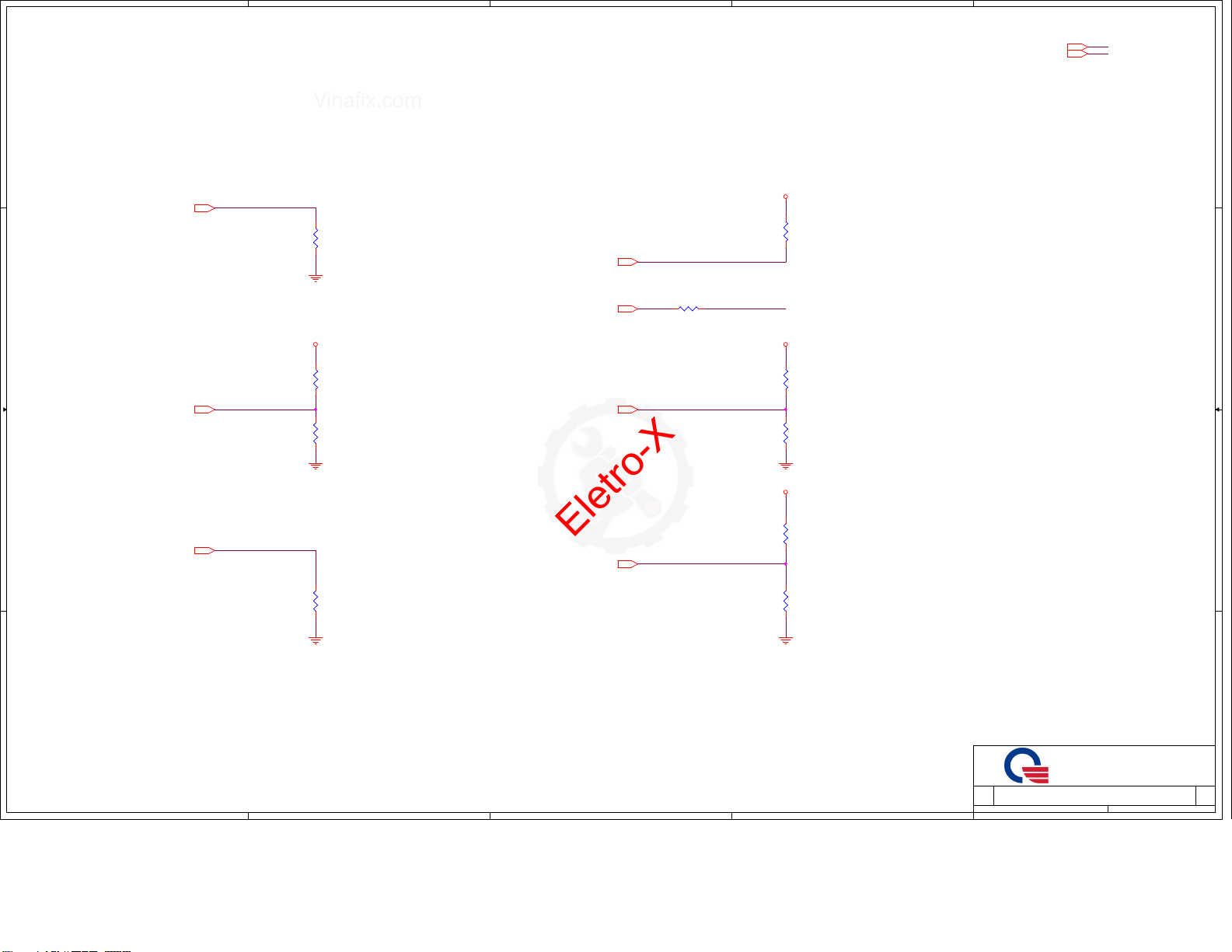

Page 3

5

4

3

2

1

SkyLake ULT Processor (DDR4)

Interleave

D D

?

U38B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

C C

B B

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

SKL_ULT

REV = 1

SKL_ULT

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

NIL-DDR CH A

2 OF 20

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

M_A_DQSN0

AM70

M_A_DQSP0

AM69

M_A_DQSN1

AT69

M_A_DQSP1

AT70

M_B_DQSN0

AH66

M_B_DQSP0

AH65

M_B_DQSN1

AG69

M_B_DQSP1

AG70

M_A_DQSN2

BA64

M_A_DQSP2

AY64

M_A_DQSN3

AY60

M_A_DQSP3

BA60

M_B_DQSN2

AR66

M_B_DQSP2

AR65

M_B_DQSN3

AR61

M_B_DQSP3

AR60

M_A_ALERT#

AW50

M_A_PARITY M_B_ALERT#

AT52

AY67

AY68

BA67

AW67

?

M_A_CLKN0 {16}

M_A_CLKP0 {16}

TP21

TP16

M_A_CKE0 {16}

TP20

M_A_CS#0 {16}

TP18

M_A_ODT0_CPU {16}

TP12

M_A_A5 {16}

M_A_A9 {16}

M_A_A6 {16}

M_A_A8 {16}

M_A_A7 {16}

M_A_BG#0 {16}

M_A_A12 {16}

M_A_A11 {16}

M_A_ACT# {16}

TP52

M_A_A13 {16}

M_A_CAS# {16}

M_A_WE# {16}

M_A_RAS# {16}

M_A_BA#0 {16}

M_A_A2 {16}

M_A_BA#1 {16}

M_A_A10 {16}

M_A_A1 {16}

M_A_A0 {16}

M_A_A3 {16}

M_A_A4 {16}

M_A_ALERT# {16}

M_A_PARITY {16}

SM_VREF_CA {16}

TP55

SM_VREF_DQ1 {17}

DDR_PG_CTRL {17}

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51 M_B_DQSN6

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

U38C

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL_ULT

REV = 1

?

SKL_ULT

Need apply PN

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

NIL-DDR CH B

3 OF 20

PDC

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

M_A_DQSN[7:0]{16}

M_A_DQSP[7:0]{16}

M_A_DQ[63:0]{16}

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

M_A_DQSN4

BA38

M_A_DQSP4

AY38

M_A_DQSN5

AY34

M_A_DQSP5

BA34

M_B_DQSN4

AT38

M_B_DQSP4

AR38

M_B_DQSN5

AT32

M_B_DQSP5

AR32

M_A_DQSN6

BA30

M_A_DQSP6

AY30

M_A_DQSN7

AY26

M_A_DQSP7

BA26

AR25

M_B_DQSP6

AR27

M_B_DQSN7

AR22

M_B_DQSP7

AR21

AN43

M_B_PARITY

AP43

SM_DRAMRST#

AT13

SM_RCOMP_0

AR18

SM_RCOMP_1

AT18

SM_RCOMP_2

AU18

?

M_B_DQSN[7:0]{17}

M_B_DQSP[7:0]{17}

M_B_DQ[63:0]{17}

+1.2V_SUS{6,16,17,50}

M_B_CLKN0 {17}

M_B_CLKN1 {17}

M_B_CLKP0 {17}

M_B_CLKP1 {17}

M_B_CKE0 {17}

M_B_CKE1 {17}

M_B_CS#0 {17}

M_B_CS#1 {17}

M_B_ODT0_CPU {17}

M_B_ODT1_CPU {17}

M_B_A5 {17}

M_B_A9 {17}

M_B_A6 {17}

M_B_A8 {17}

M_B_A7 {17}

M_B_BG#0 {17}

M_B_A12 {17}

M_B_A11 {17}

M_B_ACT# {17}

M_B_BG#1 {17}

M_B_A13 {17}

M_B_CAS# {17}

M_B_WE# {17}

M_B_RAS# {17}

M_B_BA#0 {17}

M_B_A2 {17}

M_B_BA#1 {17}

M_B_A10 {17}

M_B_A1 {17}

M_B_A0 {17}

M_B_A3 {17}

M_B_A4 {17}

M_B_ALERT# {17}

M_B_PARITY {17}

R274 121/F_4

R276 80.6/F_4

R275 100/F_4

+1.2V_SUS

R358

470/F_4

03

DDR4_DRAMRST# {16,17}

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

SKYLAKE 2/15(DDR4 I/F)

SKYLAKE 2/15(DDR4 I/F)

SKYLAKE 2/15(DDR4 I/F)

LV6

LV6

LV6

3 61Friday, March 11, 2016

3 61Friday, March 11, 2016

1

3 61Friday, March 11, 2016

1A

1A

1A

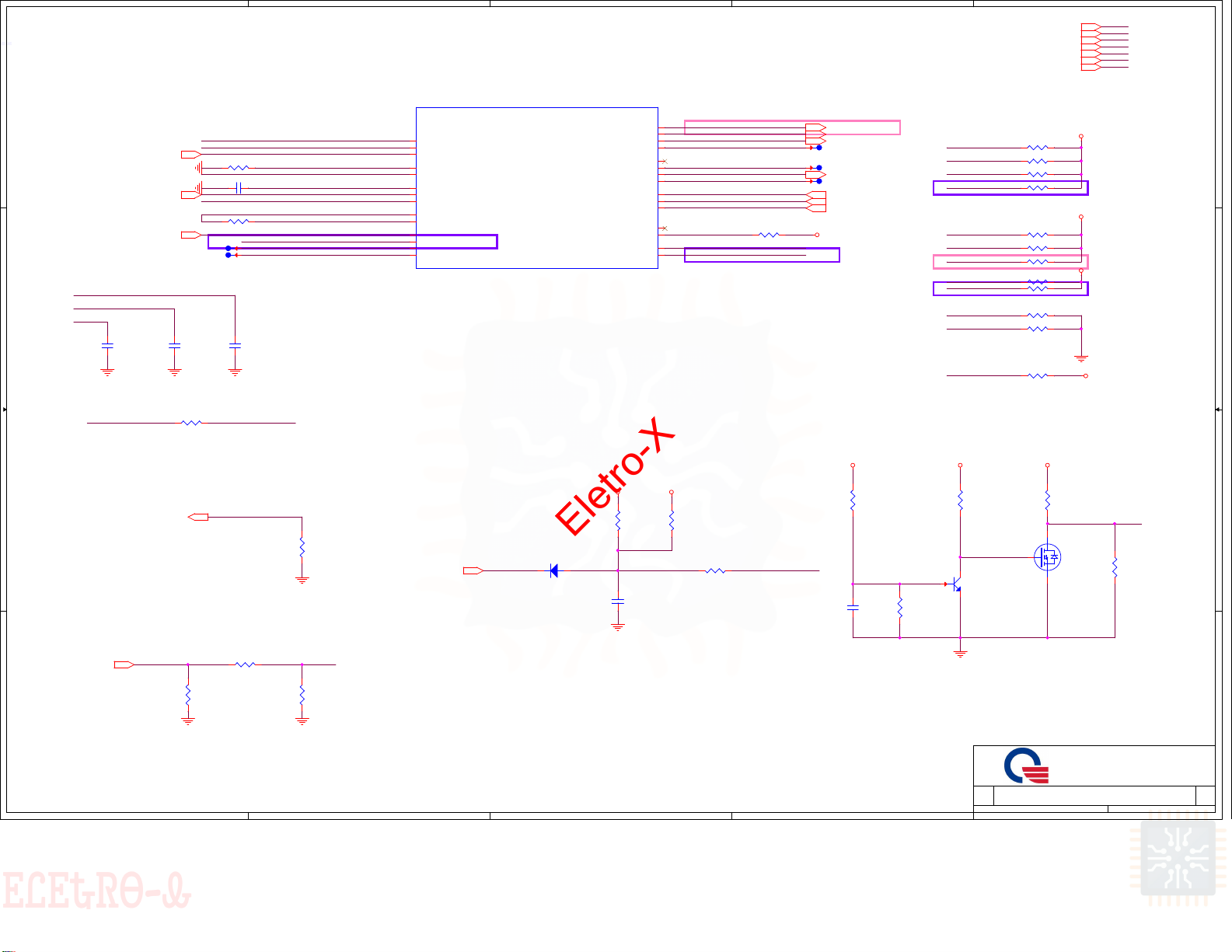

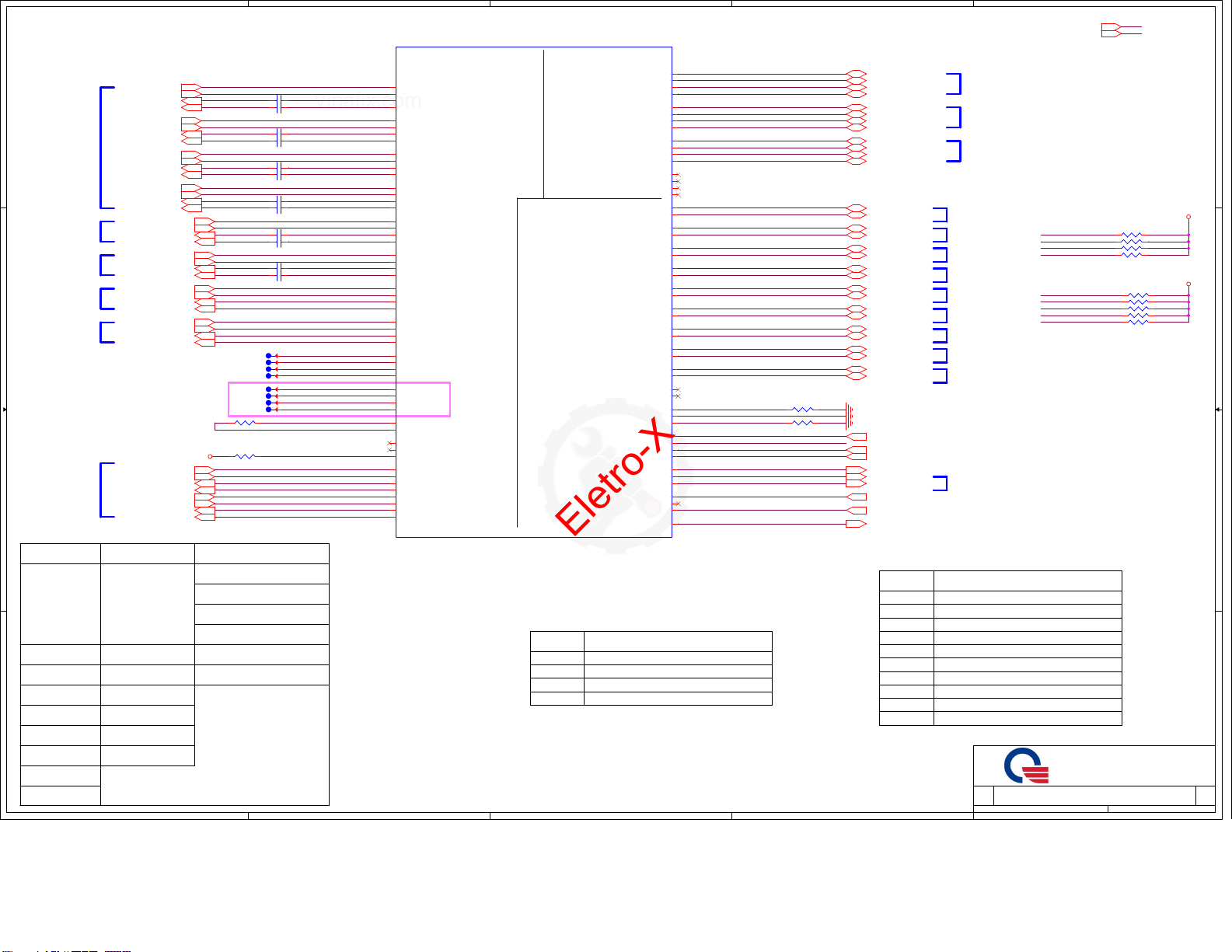

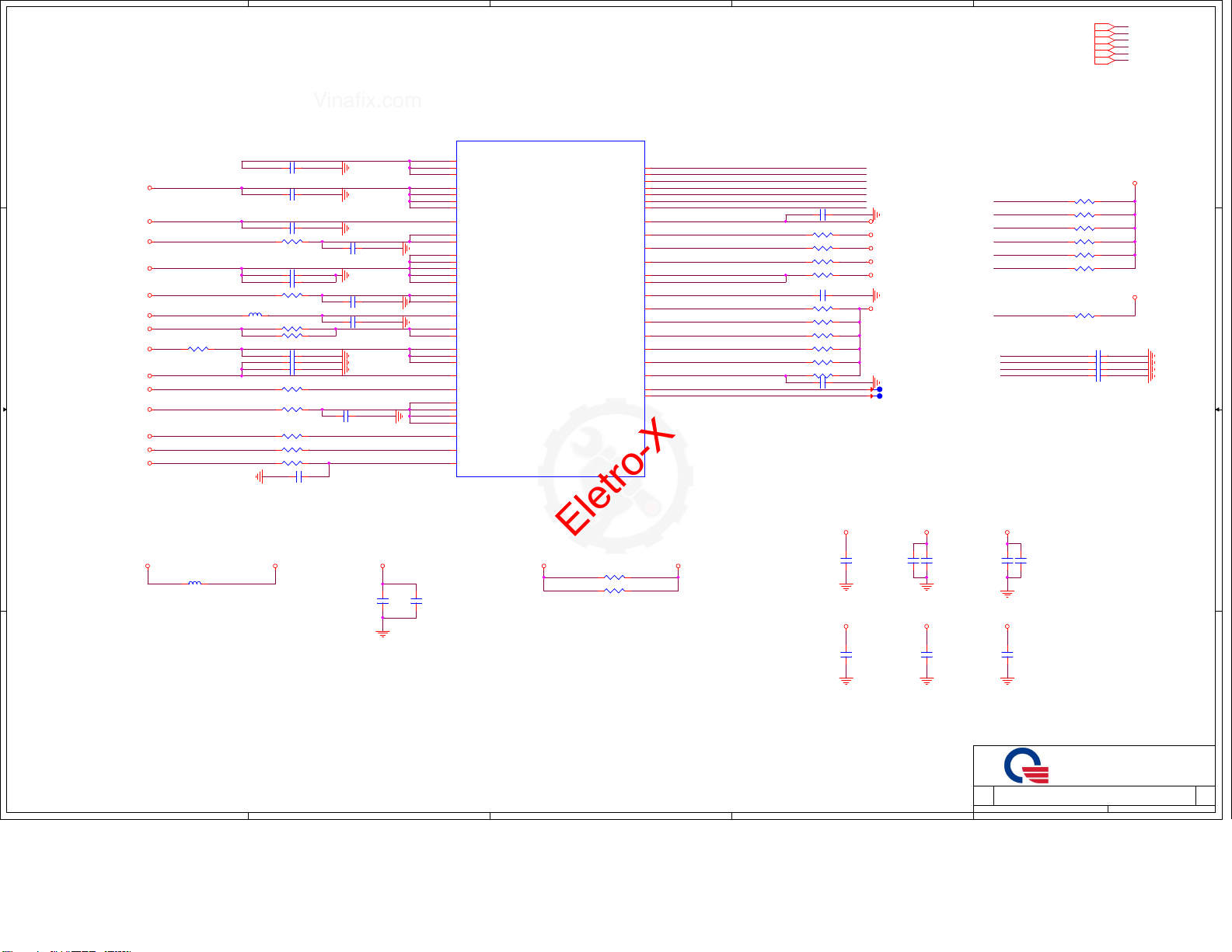

Page 4

5

D D

PLTRST#

SYS_RESET#

RSMRST#{36}

EC_PWROK{29,36,37}

PCIE_WAKE#{19,30,33}

RSMRST#

C C

SYS_RESET#

PLTRST#

EC13

*E@220P/50V_4

R595 10K_4

C276 *0.1U/16V/X7R_4

R295*0_4_S

TP50 R692 10K_4

B2A

TP15

EC9

*E@220P/50V_4

EC38

*E@220P/50V_4

RSMRST#

PROCPWRGD

H_VCCST_PWRGD

SYS_PWROK

EC_PWROK

DSWROK_EC_R

SUSWARN#

SUSACK#

PCIE_WAKE#

GPD2

4

?

U38K

AN10

GPP_B13/PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A13/SUSWARN#/SUSPWRDNACK

AP11

GPP_A15/SUSACK#

BB15

WAKE#

AM15

GPD2/LAN_WAKE#

AW17

GPD11/LANPHYPC

AT15

GPD7/RSVD

SKL_ULT

REV = 1

SKL_ULT

SYSTEM POWER MANAGEMENT

11 OF 20

3

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B11/EXT_PWR_GATE#

GPP_B2/VRALERT#

2

+3V_DEEP_SUS{10,11,14,15,17}

+VCCSTPLL{2,5,6,9,45,53,56}

+3V_RTC_2{13,15}

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

PCH_SLP_S0#

SLP_S5#

SLP_LAN#

DNBSWON#

AC_PRESENT_EC

PM_BATLOW_N_EC

INTRUDER#_R

EXT_PWR_GATE#

PCH_VRALERT#

R287 1M_4

PCH_SLP_S0# {36}

SUSB# {18,36}

SUSC# {36}

TP53

TP51

SLP_WLAN# {33}

TP13

DNBSWON# {36}

AC_PRESENT_EC {36}

PM_BATLOW_N_EC {36}

+3V_RTC_2

C3A

B2A

?

PCH Pull-high/low(CLG)

SUSWARN#

SUSACK#

PM_BATLOW_N_EC

GPD2

B2A

PCIE_WAKE#

AC_PRESENT_EC

DNBSWON#

SYS_RESET#

PCH_VRALERT#

B2A

RSMRST#

DSWROK_EC_R

EXT_PWR_GATE#

R297 10K_4

R293 *10K_4

R302 10K_4

R763 10K_4

R687 10K_4

R780 *10K_4

R196 10K_4

R764 10K_4

R688 10K_4

R288 100K_4

R251 1K_4

+3VS5{10,12,15,26,28,30,32,33,35,36,41,42,44,49,51,53,54,56}

+3V{2,10,11,12,13,14,15,17,18,25,26,27,29,30,31,34,36,37,38,40,41,42,45,49,52,53,54}

+5VS5{34,35,38,39,41,42,44,45,48,50,51,53,54,56}

+VCCIO{2,6,53,56}

+3V_DEEP_SUS

+3VS5

+3V

1

04

C3A

+3VS5

RSMRST#

B B

R285 *0_4_S

PLTRST#{18,28,30,31,33,36,37}

PLTRST#(CLG)

SYS_PWROK{36}

R189

100K_4

A A

System PWR_OK(CLG)

5

DSWROK_EC_R

PLTRST#

R190 *0_4

+VCCIO +3VS5+5VS5

+VCCIO

+VCCSTPLL

R591

1K_4

R437

100K_4

HWPG{36,49,50}

EC_PWROKSYS_PWROK

R192

100K_4

4

HWPG

21

D17 DB2J40600L

H_VCCST_PWRGD_R

C688

*10P/50V_4

3

R582

*1K_4

R597 60.4_4

H_VCCST_PWRGD

R569

15K_4

+1.0V_PWRGD_G1

C665

0.1U/16V/X7R_4

2

R565

100K_4

R559

100K_4

+1.0V_PWRGD_G2

2

Q38

METR3904-G

1 3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

R558

10K_4

3

2

1

SKYLAKE 3/15(PowerManger)

SKYLAKE 3/15(PowerManger)

SKYLAKE 3/15(PowerManger)

HWPG

Q39

2N7002K

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

R557

100K_4

1

LV6

LV6

LV6

1A

1A

4 61Friday, March 11, 2016

4 61Friday, March 11, 2016

4 61Friday, March 11, 2016

1A

Page 5

5

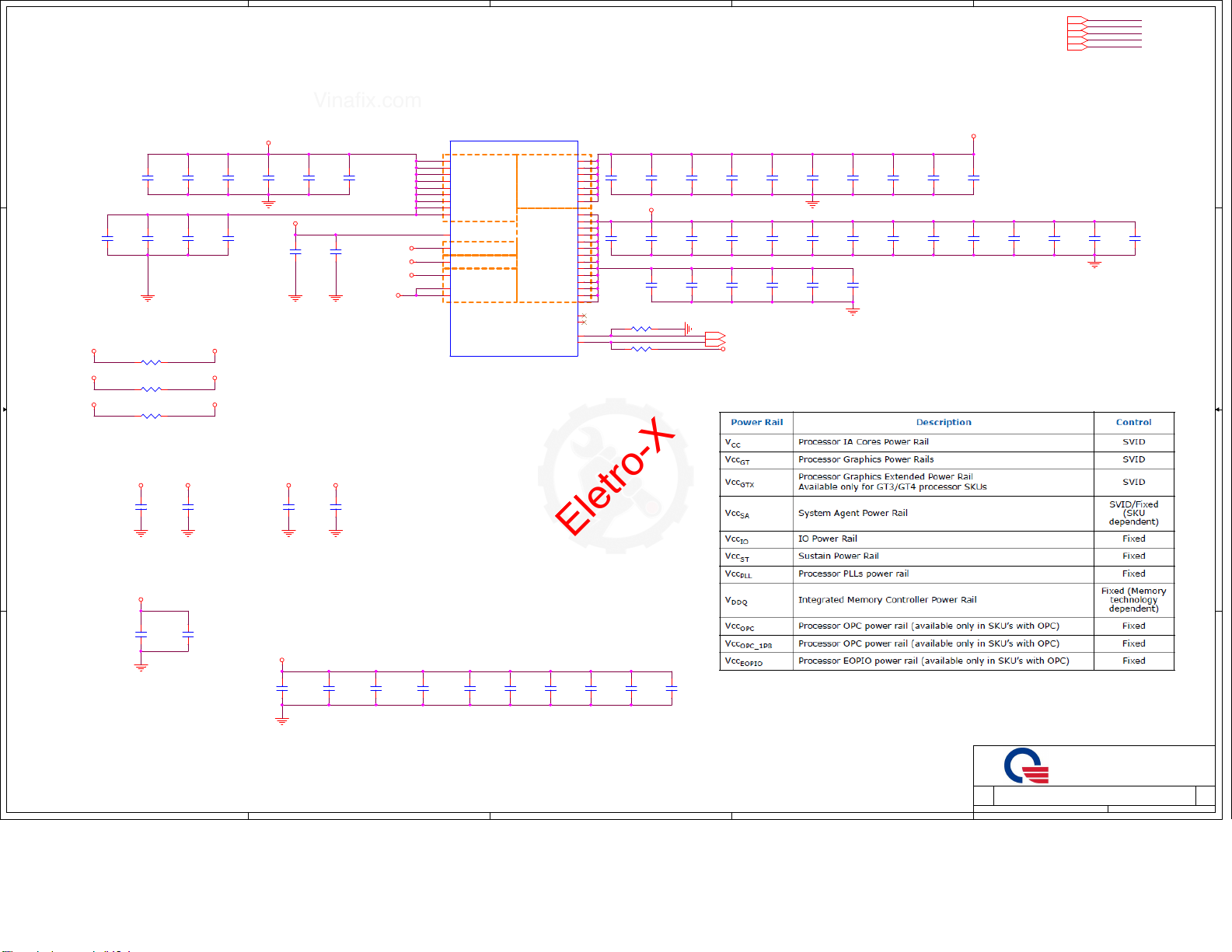

Under CPU

C274

C256

C366

10U/6.3V_4

C333

22U/6.3V/X5R_6

C245

GT3@10U/6.3V_4

C661

C670

C329

22U/6.3V/X5R_6

C353

10U/6.3V_4

C158

22U/6.3V/X5R_6

Close CPU

C660

47U/6.3V_8

C666

10U/6.3V_4

22U/6.3V/X5R_6

47U/6.3V_8

10U/6.3V_4

10U/6.3V_4

10U/6.3V_4

C337

22U/6.3V/X5R_6

C673

47U/6.3V_8

C181

10U/6.3V_4

22U/6.3V/X5R_6

47U/6.3V_8

10U/6.3V_4

D D

+1.8V_DEEP_SUS +1.8V_PRIM

R163 GT3@0_6

C C

B B

C255

GT3@10U/6.3V_4

+VCC_CORE

+VCC_CORE

C317

C365

10U/6.3V_4

C150

22U/6.3V/X5R_6

+VCCOPC

+VCCOPC_SRC{49}

681_AGND{49}

C667

C169

C296

22U/6.3V/X5R_6

C367

10U/6.3V_4

C154

22U/6.3V/X5R_6

C657

47U/6.3V_8

C675

10U/6.3V_4

4

C292

22U/6.3V/X5R_6

C188

10U/6.3V_4

C319

22U/6.3V/X5R_6

+VCCOPC_SRC

681_AGND

+VCCOPC_SRC

681_AGND

C663

47U/6.3V_8

C656

10U/6.3V_4

C325

22U/6.3V/X5R_6

C207

10U/6.3V_4

R244 GT3@100/F_4

R246 GT3@0_4

R239 GT3@0_4

R237 GT3@100/F_4

R247 GT3@0_4

R248 GT3@0_4

C678

47U/6.3V_8

C671

10U/6.3V_4

+VCCOPC

+1.8V_PRIM

+VCCEOPIO

C684

47U/6.3V_8

C677

10U/6.3V_4

C270

22U/6.3V/X5R_6

3

?

SKL_ULT

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

AK32

AB62

AC63

AE63

AE62

AG62

AL63

AJ62

A30

A34

A39

A44

G30

K32

P62

V62

H63

G61

U38L

CPU POWER 1 OF 4

VCC_A30

VCC_A34

33A

VCC_A39

VCC_A44

VCC_AK33

VCC_AK35

VCC_AK37

VCC_AK38

VCC_AK40

VCC_AL33

VCC_AL37

VCC_AL40

VCC_AM32

VCC_AM33

VCC_AM35

VCC_AM37

VCC_AM38

VCC_G30

RSVD_K32

RSVD_AK32

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCC_OPC_1P8_H63

VCC_OPC_1P8_G61

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

SKL_ULT

REV = 1

+VCCEOPIO

+VCCOPC

VCC_SENSE

VSS_SENSE

VIDALERT#

VCCSTG_G20

12 OF 20

C340 GT3@22U/6.3V/X5R_6

C322 GT3@1U/6.3V_4X

C323 GT3@1U/6.3V_4X

C324 GT3@22U/6.3V/X5R_6

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

VIDSCK

VIDSOUT

PDC

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

?

+VCC_CORE +VCC_CORE

C705

1U/6.3V_4X

C253

1U/6.3V_4X

H_CPU_SVIDALRT#

VR_SVID_CLK_R

H_CPU_SVIDDAT

H_CPU_SVIDALRT#

VR_SVID_CLK_R

C235

1U/6.3V_4X

C195

1U/6.3V_4X

C194

1U/6.3V_4X

C208

1U/6.3V_4XC246

2

C344

C229

1U/6.3V_4X

1U/6.3V_4X

C383

C222

1U/6.3V_4X

1U/6.3V_4X

R187 100/F_4

R188 100/F_4

R599 220/F_4

R600 *0_4_S

C368

1U/6.3V_4X

C362

1U/6.3V_4X

+VCCSTPLL

+VCCSTPLL

R587

*54.9/F_4

+VCCSTPLL

R579

56.2/F_4

C689

*0.1U/16V/X7R_4

Under CPU

C219

1U/6.3V_4X

C261

1U/6.3V_4X

C819

1U/6.3V_4X

+VCC_CORE{46}

+VCCSTG{6}

+VCCSTPLL{2,4,6,9,45,53,56}

+VCCOPC{49}

C241

1U/6.3V_4X

+VCC_CORE

VCC_SENSE {45}

VSS_SENSE {45}

+VCCSTG

B2A

SVID ALERT

VR_SVID_ALERT# {45}

SVID CLK

VR_SVID_CLK {45}

1

+VCCSTPLL

05

100- ±1%

pull-up to VCC

near processor.

C682

0.1U/16V/X7R_4

R577

100/F_4

H_CPU_SVIDDAT

A A

5

4

3

2

R578 *0_4_S

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

SVID DATA

VR_SVID_DATA {45}

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

SKYLAKE 4/15 (POWER-1)

SKYLAKE 4/15 (POWER-1)

SKYLAKE 4/15 (POWER-1)

1

LV6

LV6

LV6

1A

1A

5 61Friday, March 11, 2016

5 61Friday, March 11, 2016

5 61Friday, March 11, 2016

1A

Page 6

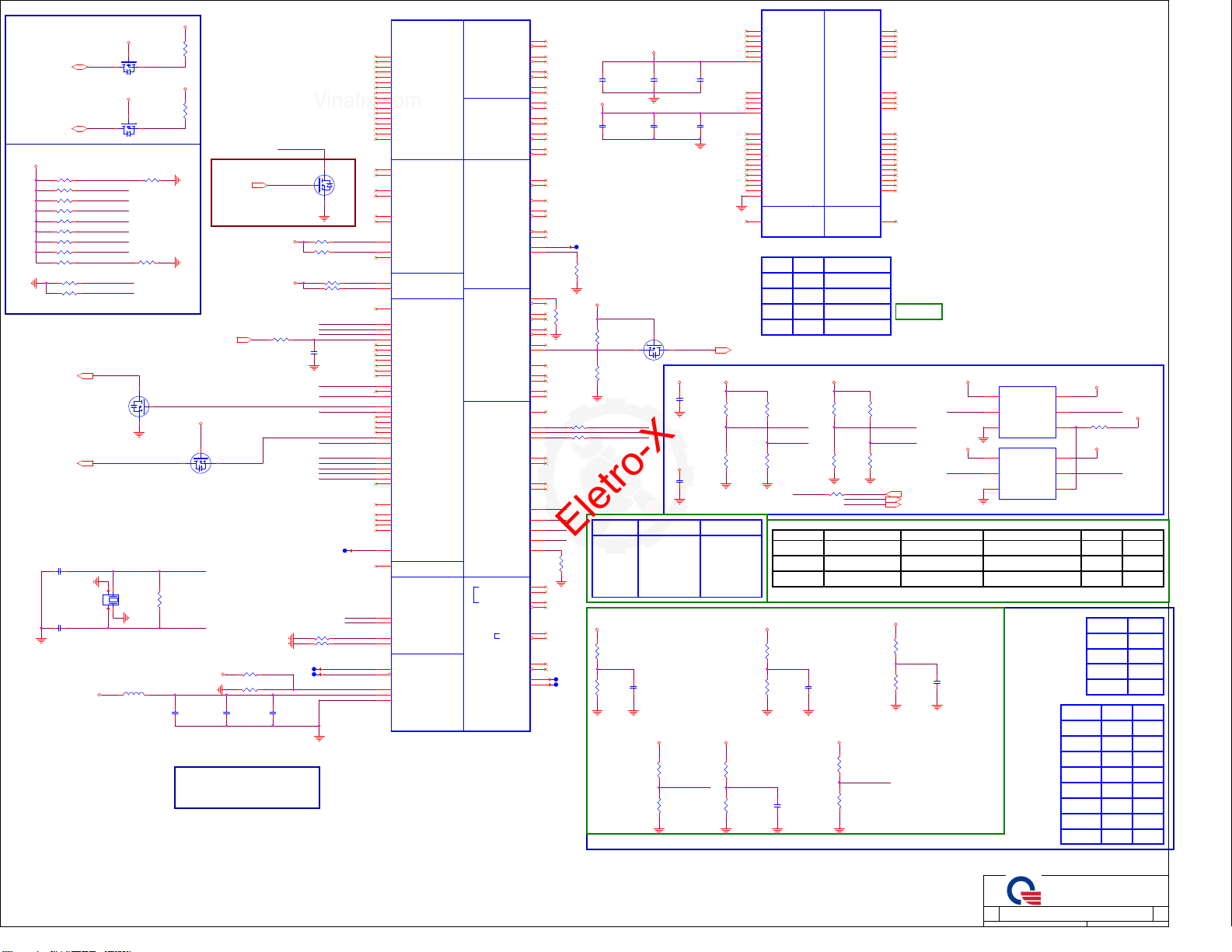

Vinafix.com

5

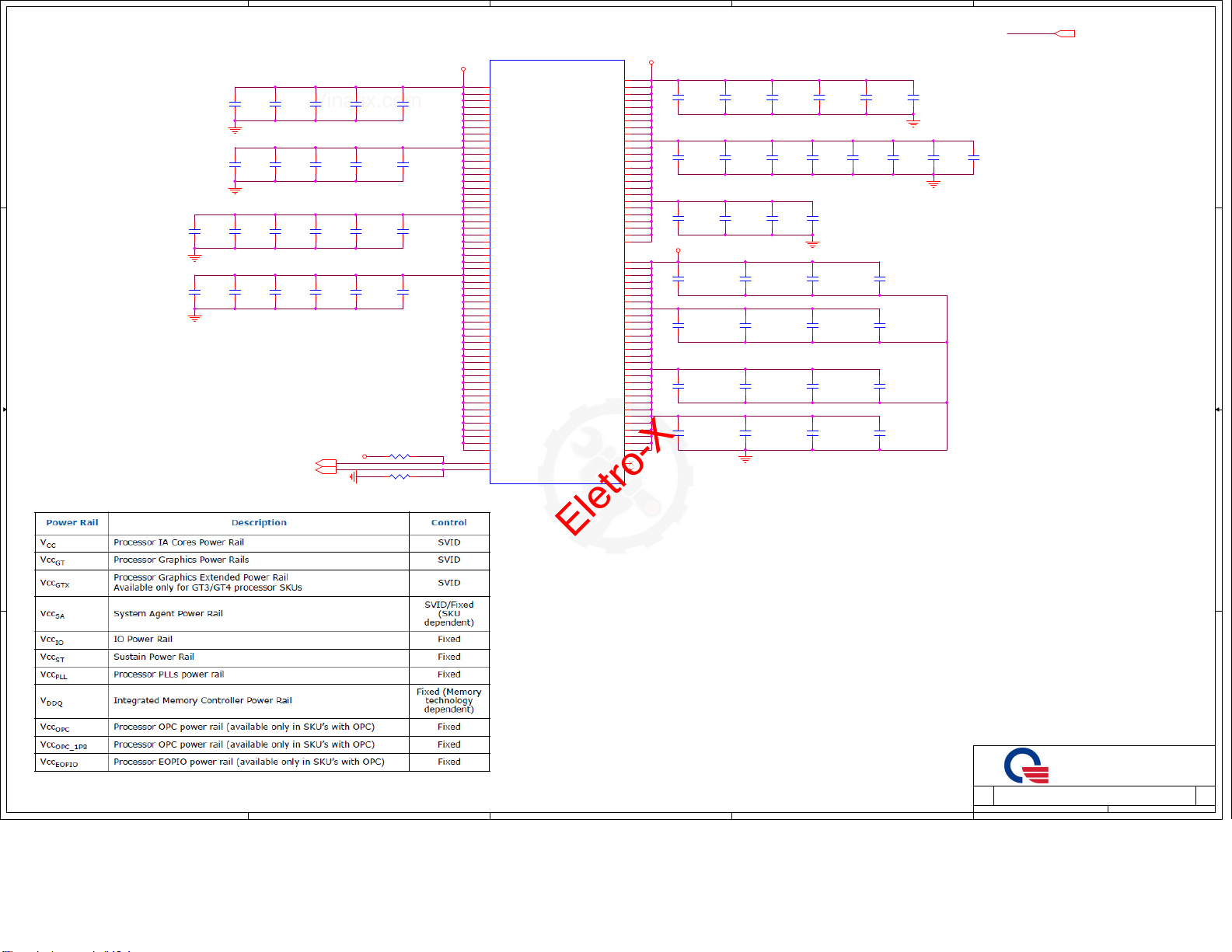

D D

Under CPU

C409

C413

10U/6.3V_4

10U/6.3V_4

Close CPU

C431

C424

10U/6.3V_4

10U/6.3V_4

C C

+VCCIO

C420

10U/6.3V_4

R158 *0_4_S

R280 *0_6_S

R149 *0_6_S

C417

10U/6.3V_4

+VCCSTG

+VCCPLL_OC+1.2V_SUS

+VCCPLL+VCCSTPLL

+1.2V_SUS

C406

1U/6.3V_4X

+1.2V_SUS

*1U/6.3V_4X

C433

1U/6.3V_4X

C412

1U/6.3V_4X

Close CPU Under CPU

C387

10U/6.3V_4

4

C416

1U/6.3V_4X

+VCCSTPLL

+VCCSTG

+VCCPLL_OC

+VCCPLL

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

AL23

A18

A22

K20

K21

SKL_ULT

U38N

CPU POWER 3 OF 4

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

0.12A

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

SKL_ULT

REV = 1

2A

0.04A

0.12A

14 OF 20

?

VCCIO

3.1A

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

4.5A

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

3

+VCCSA

Under CPU

C371

1U/6.3V_4X

C299

1U/6.3V_4X

C312

10U/6.3V_4

C348

1U/6.3V_4X

C668

1U/6.3V_4X

C239

10U/6.3V_4

C350

1U/6.3V_4X

C343

1U/6.3V_4X

C330

10U/6.3V_4

VSSSA_SENSE {45}

VCCSA_SENSE {45}

+VCCSA

C351

10U/6.3V_4

C662

1U/6.3V_4X

C352

10U/6.3V_4

AK28

AK30

AL30

AL42

C349

AM28

1U/6.3V_4X

AM30

AM42

AK23

AK25

G23

G25

G27

C237

G28

1U/6.3V_4X

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

R153 100/F_4

H21

H20

R154 100/F_4

?

C369

10U/6.3V_4

C658

1U/6.3V_4XC407

C659

10U/6.3V_4

2

C382

1U/6.3V_4X

C332

1U/6.3V_4X

C275

10U/6.3V_4

Close CPU

C347

1U/6.3V_4X

Under CPU

C290

10U/6.3V_4

Close CPU

C370

1U/6.3V_4X

C318

10U/6.3V_4

+VCCIO

C346

1U/6.3V_4X

C321

10U/6.3V_4

+VCCIO{2,4,53,56}

+VCCSA{48}

+1.2V_SUS{3,16,17,50}

+VCCSTPLL{2,4,5,9,45,53,56}

+VCCSTG{5}

C238

10U/6.3V_4

C262

10U/6.3V_4

1

C669

10U/6.3V_4

C297

10U/6.3V_4

06

Close CPUUnder CPU

+VCCSTG +VCCPLL_OC +VCCPLL+VCCSTPLL

B B

C203

1U/6.3V_4X

C379

1U/6.3V_4X

C187

1U/6.3V_4X

C293

1U/6.3V_4X

Close A18 Ball

+VCCSTPLL

C186

*1U/6.3V_4X

A A

5

C182

*22U/6.3V/X5R_6

+1.2V_SUS

C432

10U/6.3V/X5R_6X

C428

10U/6.3V/X5R_6X

4

C425

10U/6.3V/X5R_6X

C427

10U/6.3V/X5R_6X

C429

10U/6.3V/X5R_6X

Close to CPU

C430

10U/6.3V/X5R_6X

C386

1U/6.3V_4X

C421

1U/6.3V_4X

3

C408

1U/6.3V_4X

C414

1U/6.3V_4X

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SKYLAKE 5/15 (POWER-2)

SKYLAKE 5/15 (POWER-2)

SKYLAKE 5/15 (POWER-2)

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

LV6

LV6

LV6

1A

1A

6 61Friday, March 11, 2016

6 61Friday, March 11, 2016

1

6 61Friday, March 11, 2016

1A

Page 7

Vinafix.com

5

4

3

2

1

+VCCGT {47}

?

SKL_ULT

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

M62

N63

N64

N66

N67

N69

A48

A53

A58

A62

A66

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

J70

J69

U38M

CPU POWER 2 OF 4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

SKL_ULT

REV = 1

31A

PDC

13 OF 20

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGTX_SENSE

VSSGTX_SENSE

+VCCGT

C729

10U/6.3V_4

C750

10U/6.3V_4

C724

1U/6.3V_4X

C304

1U/6.3V_4X

+VCCGT

C726

10U/6.3V_4

C307

10U/6.3V_4

C752

1U/6.3V_4X

C302

1U/6.3V_4X

C306

C373

1U/6.3V_4X

C374

1U/6.3V_4X

C309

10U/6.3V_4

C372

10U/6.3V_4

C301

1U/6.3V_4X

C378

1U/6.3V_4X

VCCGT_SENSE{45}

VSSGT_SENSE{45}

10U/6.3V_4

C376

10U/6.3V_4

C375

1U/6.3V_4X

C308

1U/6.3V_4X

D D

C C

B B

C377

10U/6.3V_4

C731

10U/6.3V_4

C303

1U/6.3V_4X

C305

1U/6.3V_4X

R634 100/F_4

R642 100/F_4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

+VCCGT

Close CPUUnder CPU

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

?

C758

47U/6.3V_8

C171

22U/6.3V/X5R_6

C338

22U/6.3V/X5R_6

+VCCGT

C743

GT3@22U/6.3V/X5R_6

C744

GT3@22U/6.3V/X5R_6

C277

GT3@10U/6.3V_4

C240

GT3@10U/6.3V_4

C759

47U/6.3V_8

C185

22U/6.3V/X5R_6

C342

22U/6.3V/X5R_6

C180

GT3@22U/6.3V/X5R_6

C209

GT3@22U/6.3V/X5R_6

C278

GT3@10U/6.3V_4

C674

GT3@10U/6.3V_4

C760

47U/6.3V_8

C298

22U/6.3V/X5R_6

C751

22U/6.3V/X5R_6

C761

47U/6.3V_8

C331

C316

22U/6.3V/X5R_6

22U/6.3V/X5R_6

C749

22U/6.3V/X5R_6

C193

GT3@22U/6.3V/X5R_6

C721

GT3@22U/6.3V/X5R_6

C676

GT3@10U/6.3V_4

C260

GT3@10U/6.3V_4

C722

47U/6.3V_8

C345

22U/6.3V/X5R_6

C748

GT3@22U/6.3V/X5R_6

C179

GT3@22U/6.3V/X5R_6

C273

GT3@10U/6.3V_4

C252

GT3@10U/6.3V_4

C762

47U/6.3V_8

C341

22U/6.3V/X5R_6

C227

22U/6.3V/X5R_6

07

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SKYLAKE 6/15 (POWER-3)

SKYLAKE 6/15 (POWER-3)

SKYLAKE 6/15 (POWER-3)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

LV6

LV6

LV6

1A

1A

7 61Friday, March 11, 2016

7 61Friday, March 11, 2016

1

7 61Friday, March 11, 2016

1A

Page 8

Vinafix.com

5

4

3

2

1

08

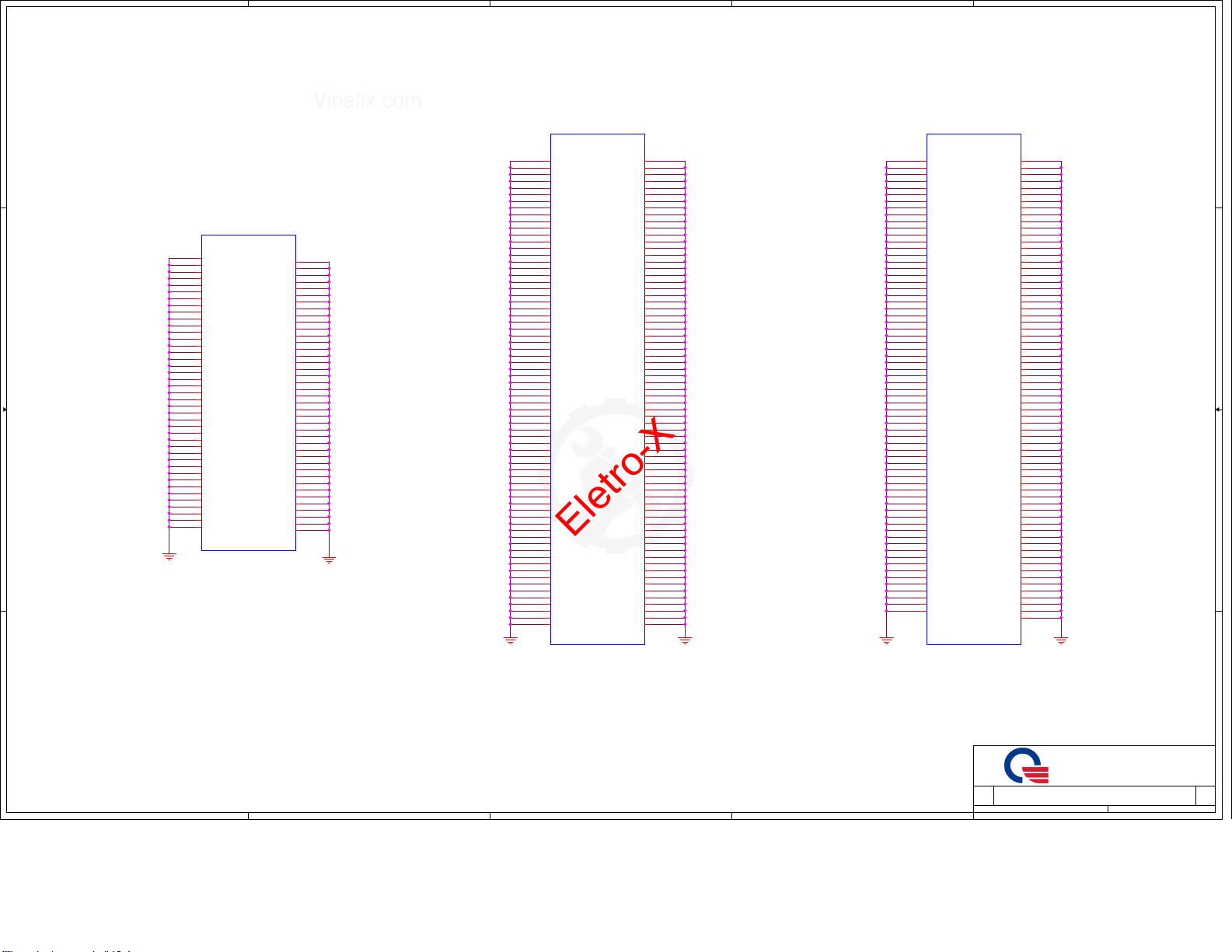

D D

U38R

?

SKL_ULT

GND 3 OF 3

F8

VSS

G10

VSS

G22

VSS

G43

VSS

G45

VSS

G48

VSS

G5

VSS

G52

VSS

C C

B B

G55

VSS

G58

VSS

G6

VSS

G60

VSS

G63

VSS

G66

VSS

H15

VSS

H18

VSS

H71

VSS

J11

VSS

J13

VSS

J25

VSS

J28

VSS

J32

VSS

J35

VSS

J38

VSS

J42

VSS

J8

VSS

K16

VSS

K18

VSS

K22

VSS

K61

VSS

K63

VSS

K64

VSS

K65

VSS

K66

VSS

K67

VSS

K68

VSS

K70

VSS

K71

VSS

L11

VSS

L16

VSS

L17

VSS

18 OF 20

SKL_ULT

REV = 1

L18

VSS

L2

VSS

L20

VSS

L4

VSS

L8

VSS

N10

VSS

N13

VSS

N19

VSS

N21

VSS

N6

VSS

N65

VSS

N68

VSS

P17

VSS

P19

VSS

P20

VSS

P21

VSS

R13

VSS

R6

VSS

T15

VSS

T17

VSS

T18

VSS

T2

VSS

T21

VSS

T4

VSS

U10

VSS

U63

VSS

U64

VSS

U66

VSS

U67

VSS

U69

VSS

U70

VSS

V16

VSS

V17

VSS

V18

VSS

W13

VSS

W6

VSS

W9

VSS

Y17

VSS

Y19

VSS

Y20

VSS

Y21

VSS

?

AA65

AA68

AB15

AB16

AB18

AB21

AD13

AD16

AD19

AD20

AD21

AD62

AE64

AE65

AE66

AE67

AE68

AE69

AF10

AF15

AF17

AF63

AG16

AG17

AG18

AG19

AG20

AG21

AG71

AH13

AH63

AH64

AH67

AJ15

AJ18

AJ20

AK11

AK16

AK18

AK21

AK22

AK27

AK63

AK68

AK69

AL28

AL32

AL35

AL38

AL45

AL48

AL52

AL55

AL58

AL64

U38P

?

SKL_ULT

GND 1 OF 3

A5

VSS

A67

VSS

A70

VSS

AA2

VSS

AA4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF1

VSS

VSS

VSS

VSS

AF2

VSS

AF4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK8

VSS

AL2

VSS

VSS

VSS

VSS

VSS

AL4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

16 OF 20

SKL_ULT

REV = 1

AL65

VSS

AL66

VSS

AM13

VSS

AM21

VSS

AM25

VSS

AM27

VSS

AM43

VSS

AM45

VSS

AM46

VSS

AM55

VSS

AM60

VSS

AM61

VSS

AM68

VSS

AM71

VSS

AM8

VSS

AN20

VSS

AN23

VSS

AN28

VSS

AN30

VSS

AN32

VSS

AN33

VSS

AN35

VSS

AN37

VSS

AN38

VSS

AN40

VSS

AN42

VSS

AN58

VSS

AN63

VSS

AP10

VSS

AP18

VSS

AP20

VSS

AP23

VSS

AP28

VSS

AP32

VSS

AP35

VSS

AP38

VSS

AP42

VSS

AP58

VSS

AP63

VSS

AP68

VSS

AP70

VSS

AR11

VSS

AR15

VSS

AR16

VSS

AR20

VSS

AR23

VSS

AR28

VSS

AR35

VSS

AR42

VSS

AR43

VSS

AR45

VSS

AR46

VSS

AR48

VSS

AR5

VSS

AR50

VSS

AR52

VSS

AR53

VSS

AR55

VSS

AR58

VSS

AR63

VSS

AR8

VSS

AT2

VSS

AT20

VSS

AT23

VSS

AT28

VSS

AT35

VSS

AT4

VSS

AT42

VSS

AT56

VSS

AT58

VSS

?

AT63

AT68

AT71

AU10

AU15

AU20

AU32

AU38

AV68

AV69

AV70

AV71

AW10

AW12

AW14

AW16

AW18

AW21

AW23

AW26

AW28

AW30

AW32

AW34

AW36

AW38

AW41

AW43

AW45

AW47

AW49

AW51

AW53

AW55

AW57

AW6

AW60

AW62

AW64

AW66

AW8

AY66

BA10

BA14

BA18

BA23

BA28

BA32

BA36

BA45

U38Q

?

SKL_ULT

GND 2 OF 3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B10

VSS

B14

VSS

B18

VSS

B22

VSS

B30

VSS

B34

VSS

B39

VSS

B44

VSS

B48

VSS

B53

VSS

B58

VSS

B62

VSS

B66

VSS

B71

VSS

BA1

VSS

VSS

VSS

VSS

BA2

VSS

VSS

VSS

VSS

VSS

F68

VSS

VSS

17 OF 20

SKL_ULT

REV = 1

PDC

BA49

VSS

BA53

VSS

BA57

VSS

BA6

VSS

BA62

VSS

BA66

VSS

BA71

VSS

BB18

VSS

BB26

VSS

BB30

VSS

BB34

VSS

BB38

VSS

BB43

VSS

BB55

VSS

BB6

VSS

BB60

VSS

BB64

VSS

BB67

VSS

BB70

VSS

C1

VSS

C25

VSS

C5

VSS

D10

VSS

D11

VSS

D14

VSS

D18

VSS

D22

VSS

D25

VSS

D26

VSS

D30

VSS

D34

VSS

D39

VSS

D44

VSS

D45

VSS

D47

VSS

D48

VSS

D53

VSS

D58

VSS

D6

VSS

D62

VSS

D66

VSS

D69

VSS

E11

VSS

E15

VSS

E18

VSS

E21

VSS

E46

VSS

E50

VSS

E53

VSS

E56

VSS

E6

VSS

E65

VSS

E71

VSS

F1

VSS

F13

VSS

F2

VSS

F22

VSS

F23

VSS

F27

VSS

F28

VSS

F32

VSS

F33

VSS

F35

VSS

F37

VSS

F38

VSS

F4

VSS

F40

VSS

F42

VSS

BA41

VSS

?

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SKYLAKE 7/15 (GND)

SKYLAKE 7/15 (GND)

SKYLAKE 7/15 (GND)

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

LV6

LV6

LV6

1A

1A

8 61Friday, March 11, 2016

8 61Friday, March 11, 2016

1

8 61Friday, March 11, 2016

1A

Page 9

Vinafix.com

5

D D

R174 49.9/F_4

+1.0V_DEEP_SUS

C C

B B

R195 1K_4

4

CFG3

CFG4

CFG_RCOMP

R173*0_4_S

AL25

AL27

BA70

BA68

E68

B67

D65

D67

E70

C68

D68

C67

F71

G69

F70

G68

H70

G71

H69

G70

E63

F63

E66

F66

E60

E8

AY2

AY1

D1

D3

K46

K45

C71

B70

F60

A52

J71

J68

F65

G65

F61

E61

U38S

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMODE

RSVD_AY2

RSVD_AY1

RSVD_D1

RSVD_D3

RSVD_K46

RSVD_K45

RSVD_AL25

RSVD_AL27

RSVD_C71

RSVD_B70

RSVD_F60

RSVD_A52

RSVD_TP_BA70

RSVD_TP_BA68

RSVD_J71

RSVD_J68

VSS_F65

VSS_G65

RSVD_F61

RSVD_E61

SKL_ULT

REV = 1

SKL_ULT

RESERVED SIGNALS-1

PDC

?

19 OF 20

3

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

RSVD_BB2

RSVD_BA3

RSVD_D5

RSVD_D4

RSVD_B2

RSVD_C2

RSVD_B3

RSVD_A3

RSVD_AW1

RSVD_E1

RSVD_E2

RSVD_BA4

RSVD_BB4

RSVD_A4

RSVD_C4

RSVD_A69

RSVD_B69

RSVD_AY3

RSVD_D71

RSVD_C70

RSVD_C54

RSVD_D54

VSS_AY71

ZVM#

RSVD_TP_AW71

RSVD_TP_AW70

MSM#

PROC_SELECT#

2

+1.0V_DEEP_SUS{13,15,51,53,54,56}

+VCCSTPLL{2,4,5,6,45,53,56}

+1.8V_DEEP_SUS{5,15,42,53,56}

BB68

BB69

AK13

AK12

BB2

BA3

AU5

TP5

AT5

TP6

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

BB5

TP4

A69

B69

AY3

D71

C70

C54

D54

AY4

TP1

BB3

TP2

AY71

R700 *0_4_S

AR56

R238 *GT3@0_4

AW71

AW70

AP56

C64

?

R674 *0_4_S

Connon-U use, SKL-U

un-install.

+1.8V_DEEP_SUS

R211 *0_6

C314

Close to CPU

Placement are required for future platform

compatibility purpose only.

LPM_ZVM_N {49}

R598 *100K_4

+VCCSTPLL

*1U/6.3V_4X

AW69

AW68

AU56

AW48

U12

U11

H11

C7

U38T

RSVD_AW69

RSVD_AW68

RSVD_AU56

RSVD_AW48

RSVD_C7

RSVD_U12

RSVD_U11

RSVD_H11

SKL_ULT

REV = 1

SKL_ULT

SPARE

?

20 OF 20

RSVD_F6

RSVD_E3

RSVD_C11

RSVD_B11

RSVD_A11

RSVD_D12

RSVD_C12

RSVD_F52

1

09

F6

E3

C11

B11

A11

D12

C12

F52

?

Processor Strapping

CFG3

(Physcial Debug Enable)

DFX Privacy

CFG4

(DP Presence Strap)

A A

5

The CFG signals have a default value of '1' if not terminated on the board.

1 0

Disable: Enable: Set DFX Enable in DFX interface MSR

Disable; No physical DP attached to eDP

4

Enable; An ext DP device is connected to eDP

3

CFG3

CFG4

Circuit

R611 *1K_4

R617 1K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SKYLAKE 8/15 (RSV)

SKYLAKE 8/15 (RSV)

SKYLAKE 8/15 (RSV)

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

LV6

LV6

LV6

1A

1A

9 61Friday, March 11, 2016

9 61Friday, March 11, 2016

1

9 61Friday, March 11, 2016

1A

Page 10

Vinafix.com

5

PCH_SPI1_CLK{28}

PCH_SPI1_SO{28}

D D

C C

PCH_SPI1_SI{28}

PCH_SPI_CS2#_TPM{28}

SIO_EXT_SMI#{36}

CL_CLK{33}

CL_DATA{33}

CL_RST#{33}

EC_RCIN#{36}

EC_IRQ_SERIRQ{36}

4

PCH_SPI1_CLK

PCH_SPI1_SO

PCH_SPI1_SI

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CS0#

PCH_SPI_CS2#_TPM

SIO_EXT_SMI#

PCI_SERR#

AW3

AW2

AW13

AY11

AV2

AV3

AU4

AU3

AU2

AU1

M2

M3

J4

V1

V2

M1

G3

G2

G1

U38E

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL_ULT

REV = 1

SKL_ULT

LPC

3

?

SMBUS, SMLINK

GPP_A14/SUS_STAT#/ESPI_RESET#

PDC

5 OF 20

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

2

+3V_DEEP_SUS{4,11,14,15,17}

SMB_PCH_CLK

R7

SMB_PCH_DAT

R8

R10

SMLALERT#

SMB_ME0_CLK

R9

SMB_ME0_DAT

W2

W1

SML0ALERT#

SMB_ME1_CLK

W3

SMB_ME1_DAT

V3

GPP_B23

AM7

AY13

BA13

BB13

AY12

BA12

BA11

CLK_PCI_EC_R

AW9

CLK_PCI_LPC_R

AY9

AW11

CLKRUN#

?

R679 22/F_4

R676 22/F_4

D3A

EC_LPCCLK

DEBUG_LCLKOUT

TP11

SMLALERT# {11}

SML0ALERT# {11}

LPC_LAD0 {33,36}

LPC_LAD1 {33,36}

LPC_LAD2 {33,36}

LPC_LAD3 {33,36}

LPC_LFRAME# {33,36}

EC_LPCCLK {36}

DEBUG_LCLKOUT {33}

CLKRUN# {36}

+3V{2,4,11,12,13,14,15,17,18,25,26,27,29,30,31,34,36,37,38,40,41,42,45,49,52,53,54}

+3VS5{4,12,15,26,28,30,32,33,35,36,41,42,44,49,51,53,54,56}

EMI(near PCH)

DEBUG_LCLKOUT

EC_LPCCLK

1

EC37

*E@18P/50V_4

10

EC36

*E@18P/50V_4

GPIO Pull UP

EC_IRQ_SERIRQ

CLKRUN#

SIO_EXT_SMI#

EC_RCIN#

PCI_SERR#

B B

R714 10K_4

R695 8.2K_4

R625 10K_4

R691 10K_4

R624 10K_4

+3V +3V_DEEP_SUS

SMB_PCH_CLK

SMB_PCH_DAT

SMB_ME1_CLK

SMB_ME1_DAT

SMB_ME0_CLK

SMB_ME0_DAT

R650 2.2K_4

R654 2.2K_4

R646 1K_4

R635 1K_4

R647 1K_4

R649 1K_4

SMBus/Pull-up(CLG)

+3V_DEEP_SUS

MBCLK_THRM{19,36,37,42}

MBDATA_THRM{19,36,37,42}

R648 4.7K_4

+3V

SMB_RUN_DAT{17,27}

A A

SMB_RUN_CLK{17,27}

5

+3V

R656 4.7K_4

Q41

5

2

6

*2N7002DW

Q42

4 3

1

SSM6N48FU

SMB_ME1_CLK

43

SMB_ME1_DAT

1

+3V

5

SMB_PCH_DAT

2

SMB_PCH_CLK

6

4

PCH SPI ROM(CLG)

R684 10K_4

+3VS5

C773 *1U/10V_4

Vender P/N

EON

Socket

3

Size

TP70

TP67

TP68

TP69

TP22

TP23

AKE3DZNKQ00(EN25QH128AHIP)16MB

AKE3DF00Q00 (GD25B128CSIGR)GGD 16MB

DFHS08FS023

PCH_SPI_CS0#_R

PCH_SPI1_CLK_R

PCH_SPI1_SI_R

PCH_SPI1_SO_R

BIOS_WP#

HOLD#

PCH_SPI_CS0# PCH_SPI_CS0#_R

PCH_SPI1_CLK

PCH_SPI1_SO

+3VSPI

PCH_SPI_IO2

R693 33_4

R690 33_4

R699 33_4

R694 33_4

R697 1K_4

R685 33_4

2

PCH_SPI1_CLK_R

PCH_SPI1_SI_RPCH_SPI1_SI

PCH_SPI1_SO_R

C769

22P/50V/NPO_4

PCH_SPI_CS0#_R {36}

PCH_SPI1_CLK_R {36}

PCH_SPI1_SI_R {36}

PCH_SPI1_SO_R {36}

R713 *0_4_S

U46

1

CE#

6

SCK

5

SI

2

SO

3

WP#

W25Q128FVSIQ

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

+3VS5

8

+3VSPI

VDD

7

HOLD#

4

VSS

SKYLAKE 9/15(SPI/LPC/SM)

SKYLAKE 9/15(SPI/LPC/SM)

SKYLAKE 9/15(SPI/LPC/SM)

R698 1K_4

R689 33_4

HOLD#

PCH_SPI_IO3BIOS_WP#

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LV6

LV6

LV6

10 61Friday, March 11, 2016

10 61Friday, March 11, 2016

1

10 61Friday, March 11, 2016

C772

0.1U/16V/X7R_4

1A

1A

1A

Page 11

Vinafix.com

5

4

3

2

+3V_DEEP_SUS{4,10,14,15,17}

1

+3V{2,4,10,12,13,14,15,17,18,25,26,27,29,30,31,34,36,37,38,40,41,42,45,49,52,53,54}

11

D D

Functional Strap Definitions

DESIGN NOTE:

WEAK PULL UP RESISTOR PRESENT ON THIS NET

ACZ_SPKR{14,29}

C C

B B

GSPI1_MOSI{14}

ACZ_SPKR

SMLALERT#

GSPI1_MOSI

R683

*20K/F_4

TOP SWAP OVERRIDE

HIGH - TOP SWAP ENABLE

LOW-DISABLED

HIGH: LPC SELECTED FOR SYSTEM FLASH

WEAK INTERNAL PD

+3V_DEEP_SUS

R657

1K/F_4

R653

*20K_4

No Boot:

The signal has a weak internal pull-down.

0 = Disable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (no confidentiality).

1 = Enable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (with confidentiality). Must be

pulled up to support Intel AMT with TLS and Intel

SBA (Small Business Advantage) with TLS.

ACZ_SDOUT{14}

EN_OVERRIDE{36}

GPP_B18{14}SMLALERT#{10}

SML0ALERT#{10}

R710 1K_4

ACZ_SDOUT

ACZ_SDOUT

GPP_B18

SML0ALERT#

+3V_DEEP_SUS

R702

*4.7K_4

+3V

R291

*4.7K_4

+3V_DEEP_SUS

R290

10K_4

R651

*10K_4

No Boot:

The signal has a weak internal pull-down.

0 = Enable security measures defined in the Flash

Descriptor.

1 = Disable Flash Descriptor Security (override). This

strap should only be asserted high using external

pull-up in manufacturing/debug environments ONLY.

This function is useful when running ITP/XDP.

No Boot:

The signal has a weak internal pull-down.

0 = Disable No Reboot mode.

1 = Enable No Reboot mode

(PCH will disable the TCO

Timer system reboot feature).

This function is useful when running ITP/XDP.

R670

*20K_4

No Boot:

The signal has a weak internal pull-down.

This field determines the destination of accesses to the

BIOS memory range. Also controllable using Boot BIOS

Destination bit (Chipset Configuration Registers: Offset

3410h:Bit 10). This strap is used in conjunction with Boot

BIOS Destination Selection 0 strap.

Bit 10 Boot BIOS Destination

0 SPI

1 LPC

A A

5

4

3

R652

20K_4

No Boot:

The signal has a weak internal pull-down.

0 = LPC Is selected for EC.

1 = eSPI Is selected for EC.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

SKYLAKE 10/15(Strip)

SKYLAKE 10/15(Strip)

SKYLAKE 10/15(Strip)

1

LV6

LV6

LV6

1A

1A

11 61Friday, March 11, 2016

11 61Friday, March 11, 2016

11 61Friday, March 11, 2016

1A

Page 12

Vinafix.com

5

+3V

PEG_RXN0

PEG_RXP0

PEG_TXN0

PEG_TXP0

PEG_RXN1

PEG_RXP1

PEG_TXN1

PEG_TXP1

PEG_RXN2

PEG_RXP2

PEG_TXN2

PEG_TXP2

PEG_RXN3

PEG_RXP3

PEG_TXN3

PEG_TXP3

C3A

R608 100/F_4

R696 10K_4

C694 EV@0.22U/10V_4X

C693 EV@0.22U/10V_4X

C690 EV@0.22U/10V_4X

C698 EV@0.22U/10V_4X

C696 EV@0.22U/10V_4X

C697 EV@0.22U/10V_4X

C685 EV@0.22U/10V_4X

C691 EV@0.22U/10V_4X

C702 0.1U/16V/X7R_4

C703 0.1U/16V/X7R_4

C679 0.1U/16V/X7R_4

C683 0.1U/16V/X7R_4

TP4

TP6

TP40

TP37

TP74

TP77

TP76

TP75

PCIE_TXN5_LAN_C

PCIE_TXP5_LAN_C

PCIE_TXN6_WLAN_C

PCIE_TXP6_WLAN_C

PCIE_RCOMPN

PCIE_RCOMPP

PIRQA#

PEG_RXN0{18}

PEG_RXP0{18}

PEG_TXN0{18}

D D

PEG

LAN

WLAN

C C

ODD

HDD

B B

SSD

PEG_TXP0{18}

PEG_RXN1{18}

PEG_RXP1{18}

PEG_TXN1{18}

PEG_TXP1{18}

PEG_RXN2{18}

PEG_RXP2{18}

PEG_TXN2{18}

PEG_TXP2{18}

PEG_RXN3{18}

PEG_RXP3{18}

PEG_TXN3{18}

PEG_TXP3{18}

PCIE_RXN5_LAN#{30}

PCIE_RXP5_LAN{30}

PCIE_TXN5_LAN#{30}

PCIE_TXP5_LAN{30}

PCIE_RXN6_WLAN#{33}

PCIE_RXP6_WLAN{33}

PCIE_TXN6_WLAN#{33}

PCIE_TXP6_WLAN{33}

SATA_RXN7_ODD#{31}

SATA_RXP7_ODD{31}

SATA_TXN7_ODD#{31}

SATA_TXP7_ODD{31}

SATA_RXN8_HDD#{31}

SATA_RXP8_HDD{31}

SATA_TXN8_HDD#{31}

SATA_TXP8_HDD{31}

PCIE_RXN11_SSD{31}

PCIE_RXP11_SSD{31}

PCIE_TXN11_SSD{31}

PCIE_TXP11_SSD{31}

SATA_RXN_SSD#{31}

SATA_RXP_SSD{31}

SATA_TXN_SSD#{31}

SATA_TXP_SSD{31}

PCI-E Port Mapping Table

PCI-E Port

Function

Port1

Port2

Port3

dGPU

Port4

Port5

Port6

Port7

A A

Port8

Port9

Port10

Port11

Port12

LAN

WLAN

ODD

HDD

Un-used

DOCK

SSD

if Pcie Bus will lane reverse.

if SATA BUS is SATA2.

5

CLK RQ Port

Port0

Port1

Port2

Port3

Port4

Port5

Function

dGPU

LAN

WLAN

DOCK

Un-used

SSD

PEG_TXN0_C

PEG_TXP0_C

PEG_TXN1_C

PEG_TXP1_C

PEG_TXN2_C

PEG_TXP2_C

PEG_TXN3_C

PEG_TXP3_C

4

U38H

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL_ULT

REV = 1

4

PCIE/USB3/SATA

3

?

SKL_ULT

PDC

SSIC / USB3

USB2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

8 OF 20

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2_COMP

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

?

USB3.0 Port Mapping Table

USB3.0 Function

PORT-1

PORT-2

PORT-3

USB3.0_R1

USB3.0_R2

USB3.0_DOCK

PORT-4

3

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_ID

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

B9

J1

J2

J3

H2

H3

G4

H1

USB30_RX1-_R1

USB30_RX1+_R1

USB30_TX1-_R1

USB30_TX1+_R1

USB30_RX2-_R2

USB30_RX2+_R2

USB30_TX2-_R2

USB30_TX2+_R2

USB30_RX3-_DOCK

USB30_RX3+_DOCK

USB30_TX3-_DOCK

USB30_TX3+_DOCK

USBP1-_R1

USBP1+_R1

USBP2-_R2

USBP2+_R2

USBP3-_DOCK

USBP3+_DOCK

USBP4-_L1

USBP4+_L1

USBP5-_L2

USBP5+_L2

USBP6-_FP

USBP6+_FP

USBP7-_Card

USBP7+_Card

USBP8-_BT

USBP8+_BT

USBP9-_CCD

USBP9+_CCD

USB2_COMP

R227 113/F_4

R236 *0_4_S

USB_Normal_OC0#_R

USB_Normal_OC1#

USB_SC_OC2#

USB_Normal_OC3#_L2

WLAN_OFF#

DEVSLP1_HDD

DEVSLP2_SSD

TPM_INT#

SSD_PEDET#

SATA_LED#_R

2

USB30_RX1-_R1 {34}

USB30_RX1+_R1 {34}

USB30_TX1-_R1 {34}

USB30_TX1+_R1 {34}

USB30_RX2-_R2 {34}

USB30_RX2+_R2 {34}

USB30_TX2-_R2 {34}

USB30_TX2+_R2 {34}

USB30_RX3-_DOCK {39}

USB30_RX3+_DOCK {39}

USB30_TX3-_DOCK {39}

USB30_TX3+_DOCK {39}

USBP1-_R1 {34}

USBP1+_R1 {34}

USBP2-_R2 {34}

USBP2+_R2 {34}

USBP3-_DOCK {39}

USBP3+_DOCK {39}

USBP4-_L1 {35}

USBP4+_L1 {35}

USBP5-_L2 {35}

USBP5+_L2 {35}

USBP6-_FP {38}

USBP6+_FP {38}

USBP7-_Card {32}

USBP7+_Card {32}

USBP8-_BT {33}

USBP8+_BT {33}

USBP9-_CCD {25}

USBP9+_CCD {25}

USB_Normal_OC0#_R {34}

USB_SC_OC2# {35}

USB_Normal_OC3#_L2 {35}

WLAN_OFF# {33}

DEVSLP1_HDD {31}

DEVSLP2_SSD {31}

TPM_INT# {28}

SSD_PEDET# {31}

SATA_LED#_R {38}

USB3.0_R1

USB3.0_R2

Onelink+_USB3.0

USB2.0_R1

USB2.0_R2

Onelink+_USB2.0

USB2.0_L1&SC

USB2.0_L2

Figure Printer

Cardreader

BT

CCD

HDD Device Sleep

SSD Device Sleep

USB2.0 Port Mapping Table

USB2.0 Function

PORT-1

PORT-2

PORT-3

PORT-4

PORT-5

PORT-6

PORT-7

PORT-8

PORT-9

PORT-10

2

USB2.0_R1

USB2.0_R2

USB2.0_DOCK

USB2.0_L1_S&C

USB2.0_L2

Figure Printer

Cardreader

BT

CCD

NC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

+3V{2,4,10,11,13,14,15,17,18,25,26,27,29,30,31,34,36,37,38,40,41,42,45,49,52,53,54}

+3VS5{4,10,15,26,28,30,32,33,35,36,41,42,44,49,51,53,54,56}

SATA_LED#_R

DEVSLP1_HDD

DEVSLP2_SSD

SSD_PEDET#

USB_Normal_OC0#_R

USB_Normal_OC1#

USB_SC_OC2#

USB_Normal_OC3#_L2

WLAN_OFF#

SKYLAKE 11/15 (PCIE/USB)

SKYLAKE 11/15 (PCIE/USB)

SKYLAKE 11/15 (PCIE/USB)

R606 10K_4

R618 *10K_4

R614 *10K_4

R180 10K_4

R586 10K_4

R580 10K_4

R594 10K_4

R592 10K_4

R619 10K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LV6

LV6

LV6

1

12 61Friday, March 11, 2016

12 61Friday, March 11, 2016

12 61Friday, March 11, 2016

12

+3V

+3VS5

1A

1A

1A

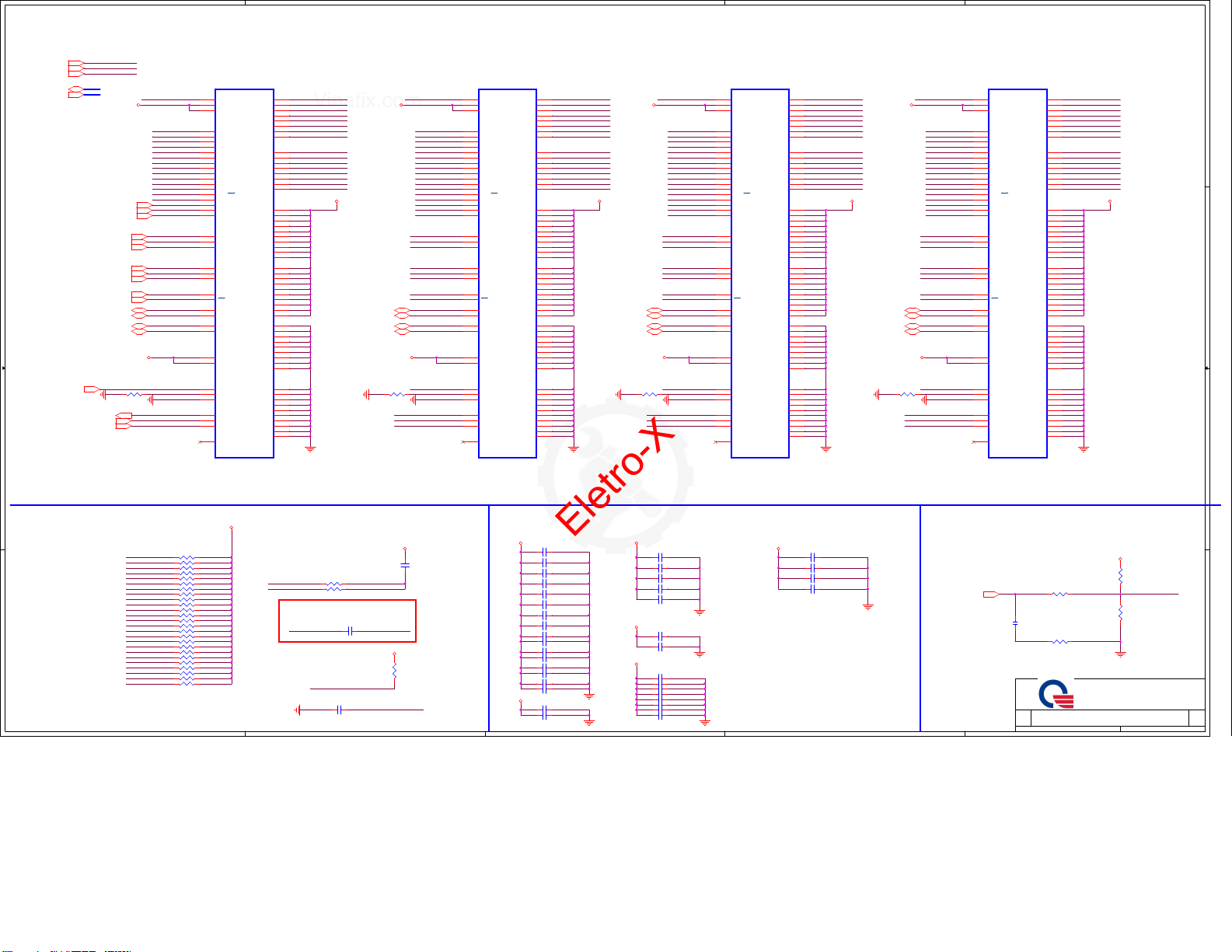

Page 13

Vinafix.com

5

C3A

CLK_PCIE_VGAN{18}

CLK_PCIE_VGAP{18}

PCIE_CLK_VGA_REQ#{19}

CLK_PCIE_LAN#{30}

CLK_PCIE_LAN{30}

PCIE_CLK_LAN_REQ#{30}

CLK_PCIE_WLANN{33}

CLK_PCIE_WLANP{33}

PCIE_CLK_WLAN_REQ#{33}

TP72

TP73

TP38

TP39

CLK_PCIE_SSDN{31}

CLK_PCIE_SSDP{31}

PCIE_CLK_SSD_REQ#{31}

D D

PEG

LAN

WLAN

DOCK

SSD

CLK_REQ/Strap Pin(CLG)

C C

+3V

4

R28910K_4

R71210K_4

R70610K_4

R71510K_4

R70410K_4

R70510K_4

PCIE_CLK_VGA_REQ#

PCIE_CLK_LAN_REQ#

PCIE_CLK_WLAN_REQ#

PCIE_CLK_LAN_REQ#_DOCK

PCIE_CLKREQ4#

R568 *SSD@0_2_S

R570 *SSD@0_2_S

PCIE_CLK_SSD_REQ#

PCIE_CLK_LAN_REQ#_DOCK

PCIE_CLK_WLAN_REQ#

PCIE_CLK_LAN_REQ#

PCIE_CLK_VGA_REQ#

PCIE_CLKREQ4#

PCIE_CLK_SSD_REQ#

U38J

D42

CLKOUT_PCIE _N0

C42

CLKOUT_PCIE _P0

AR10

GPP_B5/SRCCLKREQ 0#

B42

CLKOUT_PCIE _N1

A42

CLKOUT_PCIE _P1

AT7

GPP_B6/SRCCLKREQ 1#

D41

CLKOUT_PCIE _N2

C41

CLKOUT_PCIE _P2

AT8

GPP_B7/SRCCLKREQ 2#

D40

CLKOUT_PCIE _N3

C40

CLKOUT_PCIE _P3

AT10

GPP_B8/SRCCLKREQ 3#

B40

CLKOUT_PCIE _N4

A40

CLKOUT_PCIE _P4

AU8

GPP_B9/SRCCLKREQ 4#

E40

CLKOUT_PCIE _N5

E38

CLKOUT_PCIE _P5

AU7

GPP_B10 /SRCCLKRE Q5#

SKL_ULT

REV = 1

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

U38I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKL_ULT

REV = 1

SKL_ULT

CLOCK SIGNALS

SKL_ULT

?

10 OF 20

?

PDC

9 OF 20

3

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIA SREF

SRTCRST#

TBT

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

?

RTCX1

RTCX2

RTCRST#

2

+3V_RTC_2{4,15}

+3V{2,4,10,11,12,14,15,17,18,25,26,27,29,30,31,34,36,37,38,40,41,42,45,49,52,53,54}

+1.0V_DEEP_SUS{9,15,51,53,54,56}

VSTBY_FSPI{25,29,36,38,39}

F43

E43

PCH_SUSCLK_R

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

?

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTC_X1

RTC_X2

SRTC_RST#

RTC_RST#

CSI2_COMP

EMMC_RCOMP

R242 *SSD@0_4_S

R169 2.7K/F_4

R176 *60.4/F_4

R182 100/F_4

R672 200/F_4

PCH_SUSCLK {31}

+1.0V_DEEP_SUS

Co-lay 60ohm 1% to GND

for Connonlake-U use

1

13

B B

RTC Clock 32.768KHz (RTC)

<RTC>

B2B

C763 15P/50V/NPO_4

Y5

32.768KHz

C755 15P/50V/NPO_4

A A

5

RTC_X1

12

R669

10M_4

RTC_X2

RTC Circuitry (RTC)

+3V_RTC

R441 45.3K_4