Page 1

5

D D

4

3

2

1

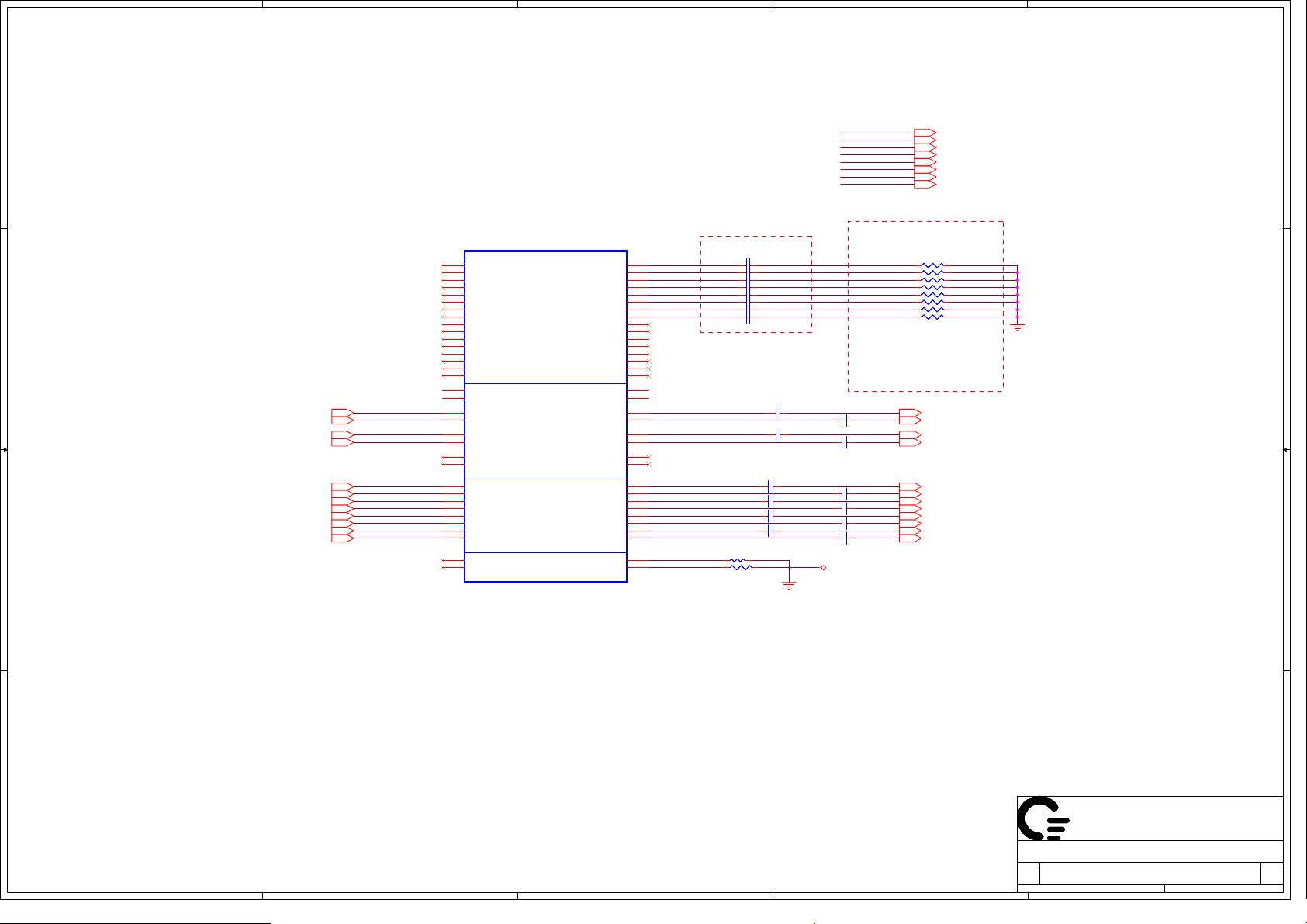

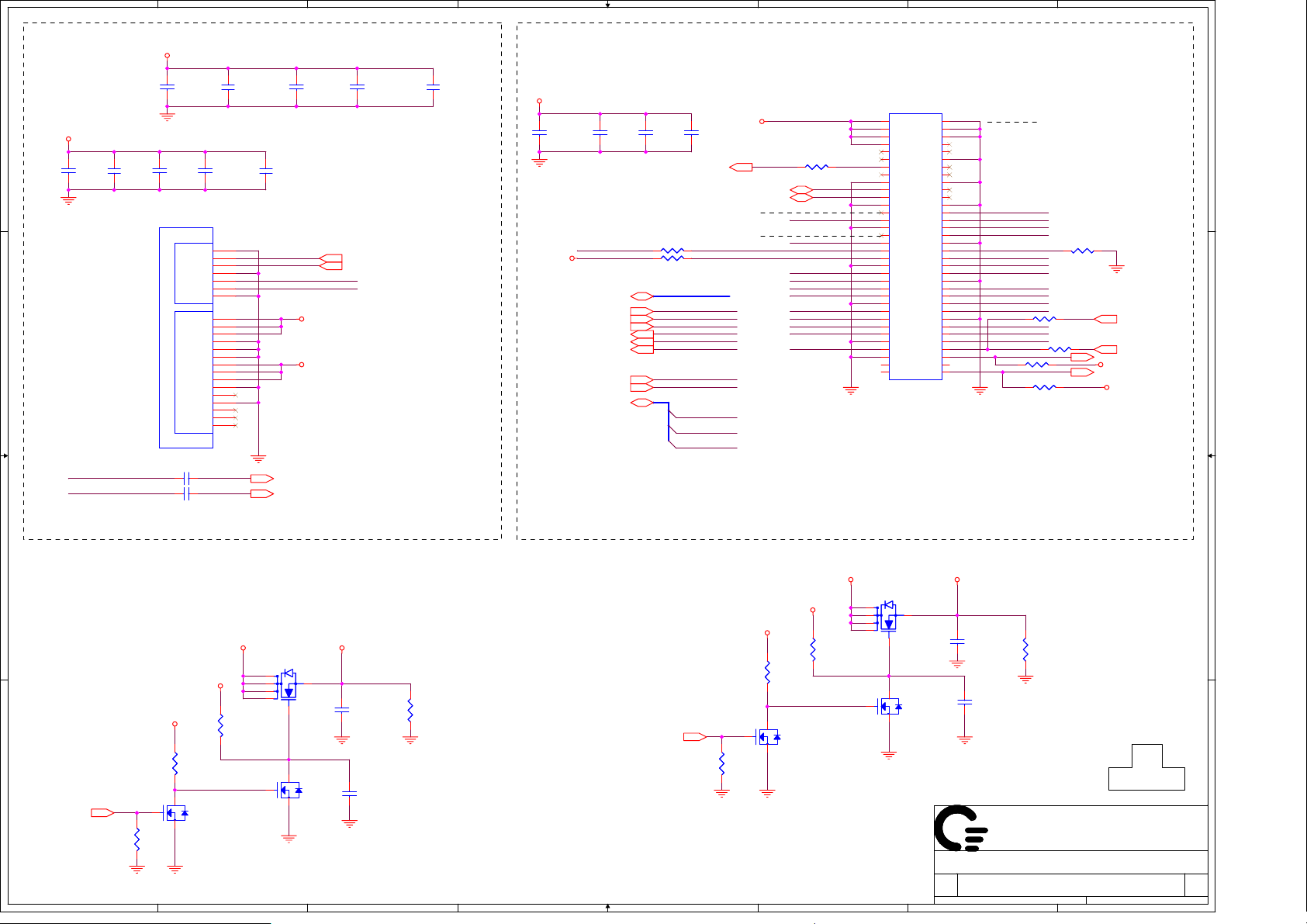

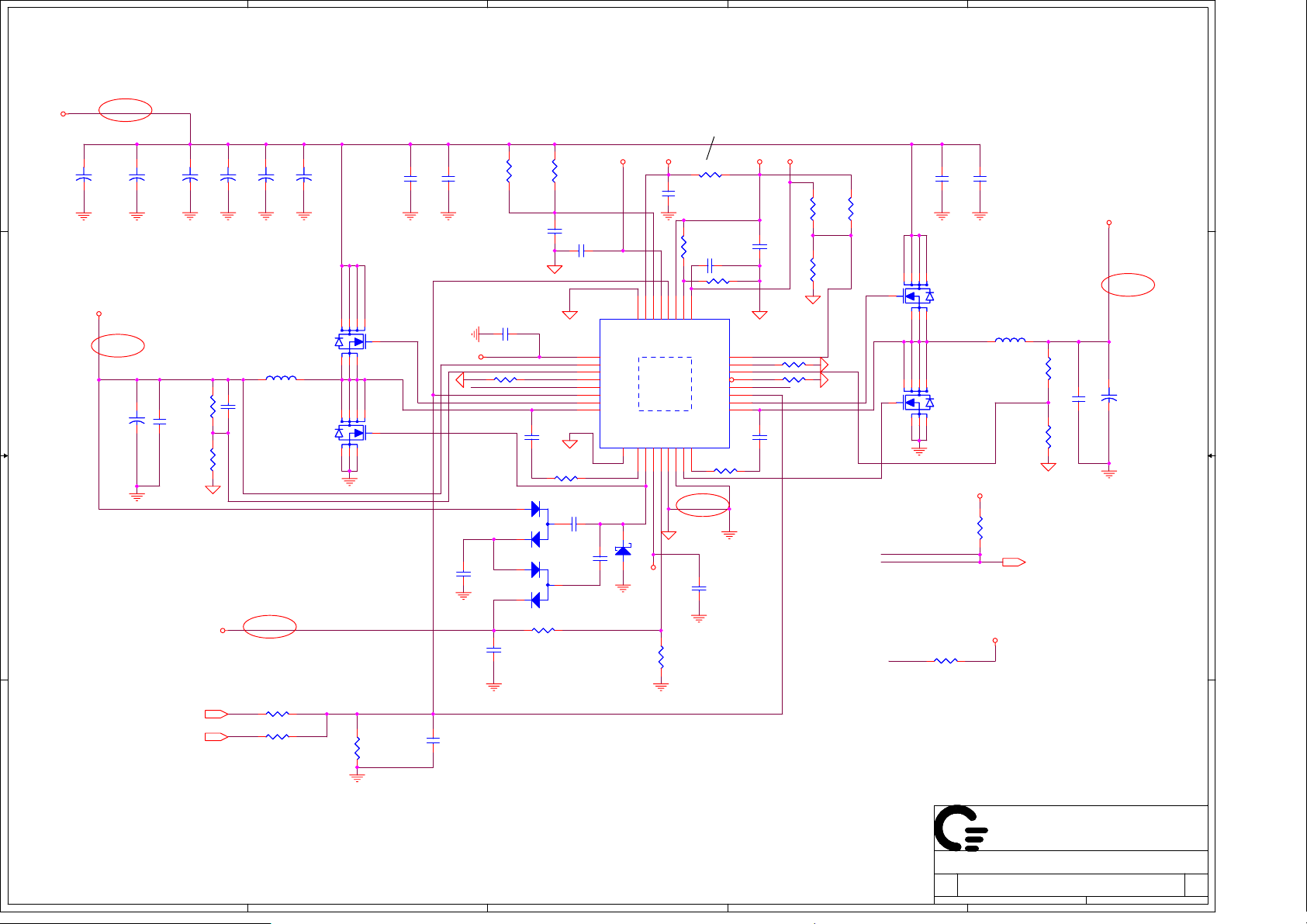

Quanta Project Name: JX6

C C

Dell Project Name: MGD Lite

2007-03-01

REV : D3B

A00/X-Build Stage

B B

A A

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

COMPUTER

COVER PAGE

COVER PAGE

COVER PAGE

MGD 3A

MGD 3A

MGD 3A

1

189Friday, March 02, 2007

189Friday, March 02, 2007

189Friday, March 02, 2007

of

of

of

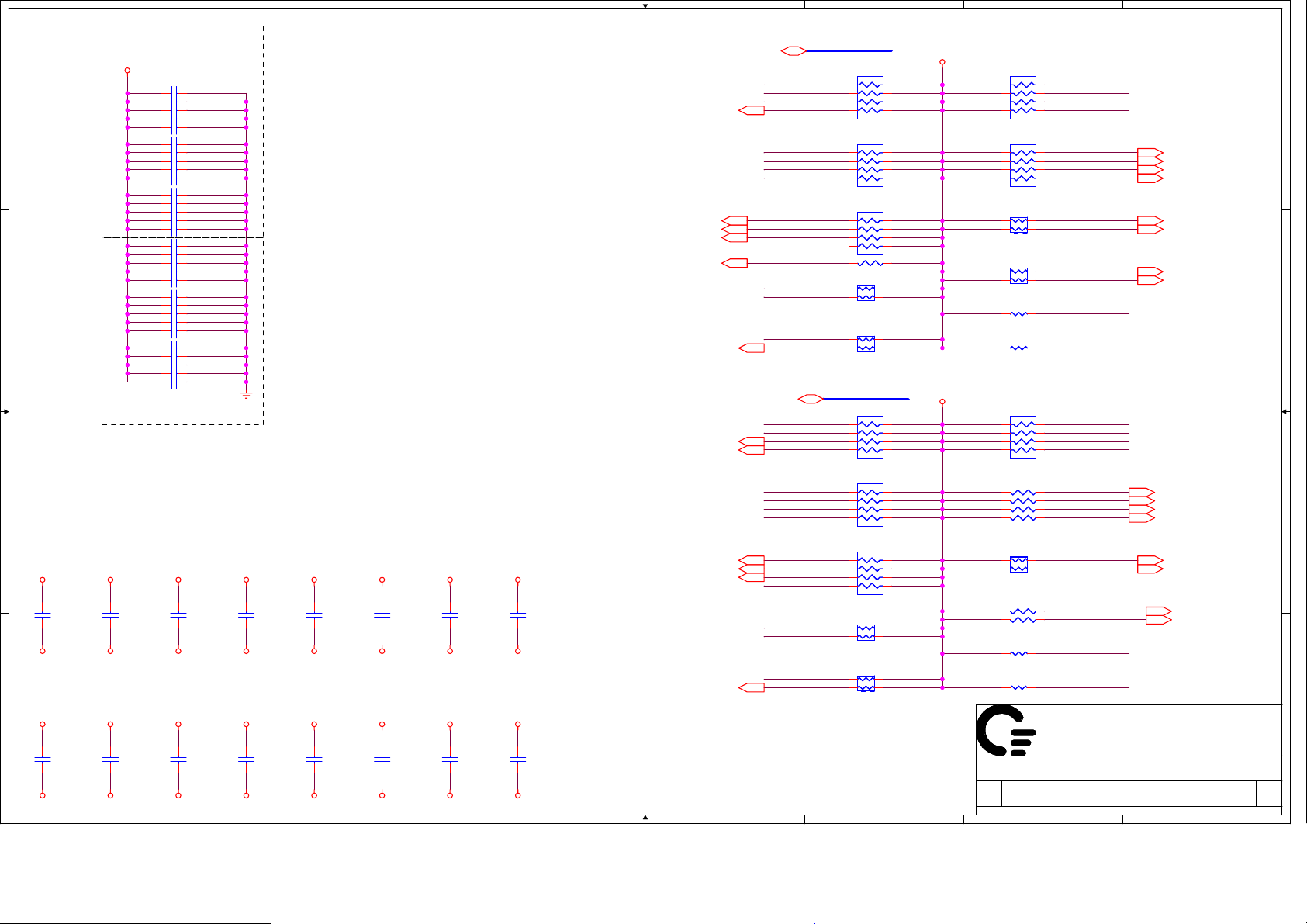

Page 2

1

2

3

4

5

6

7

8

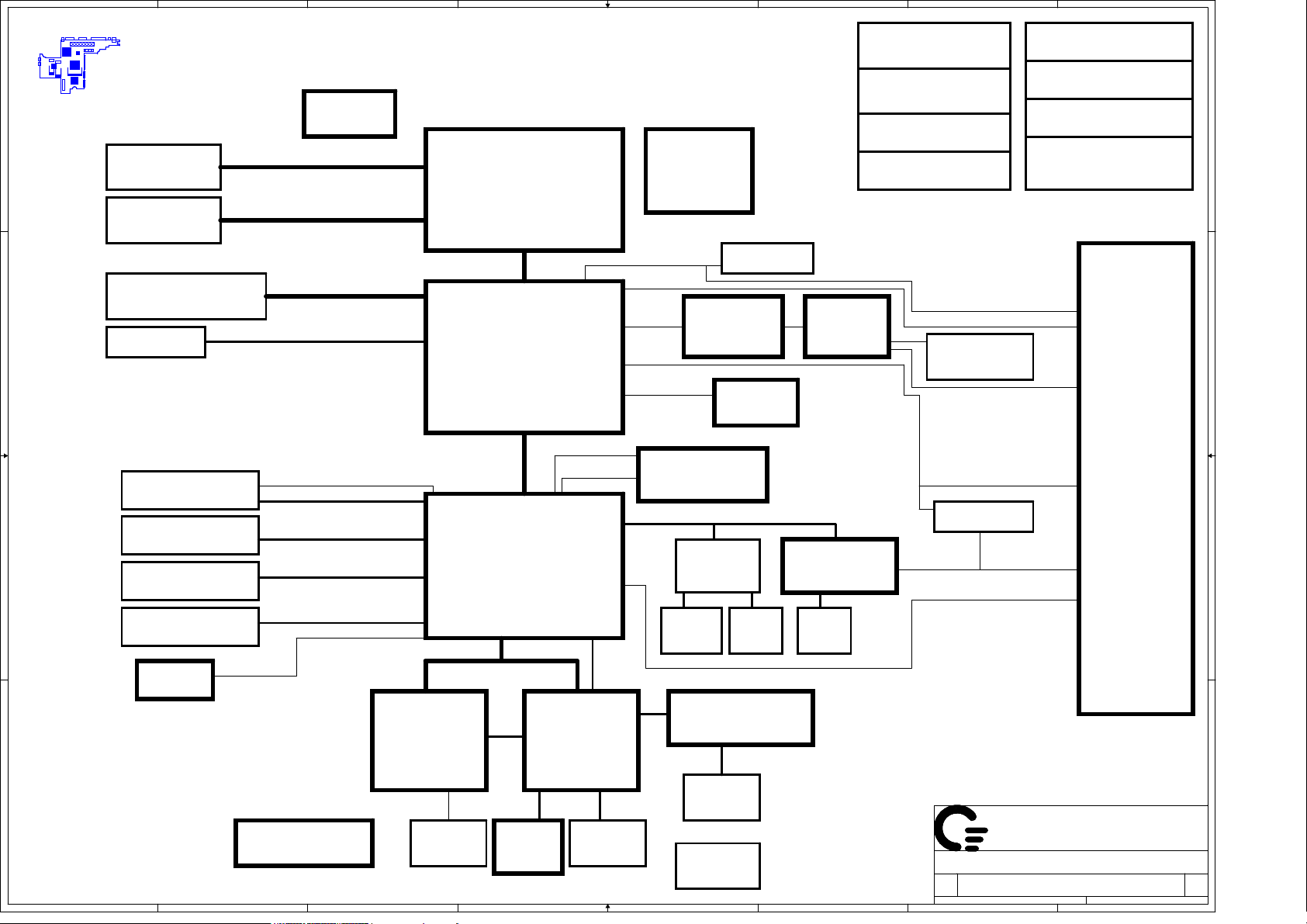

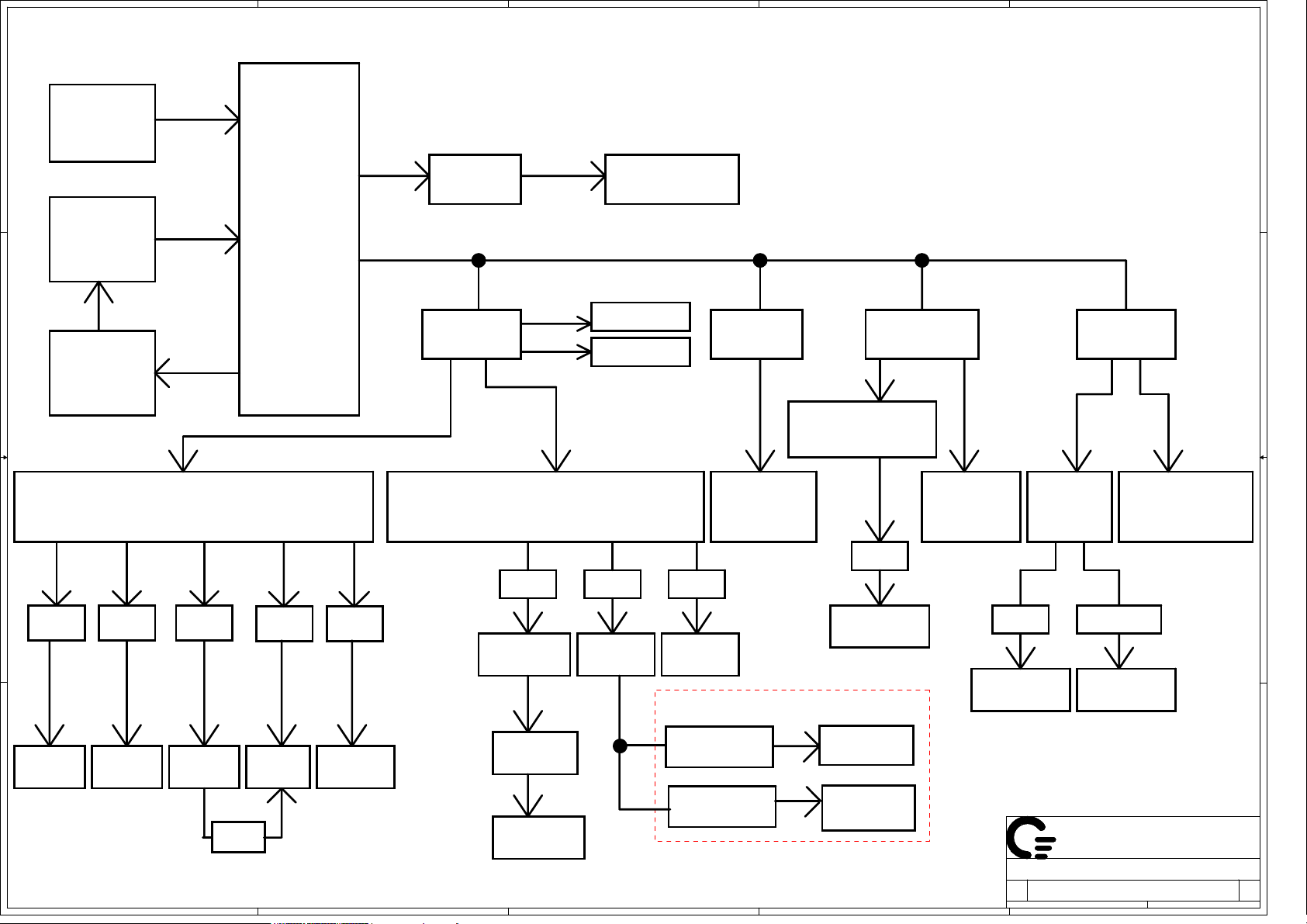

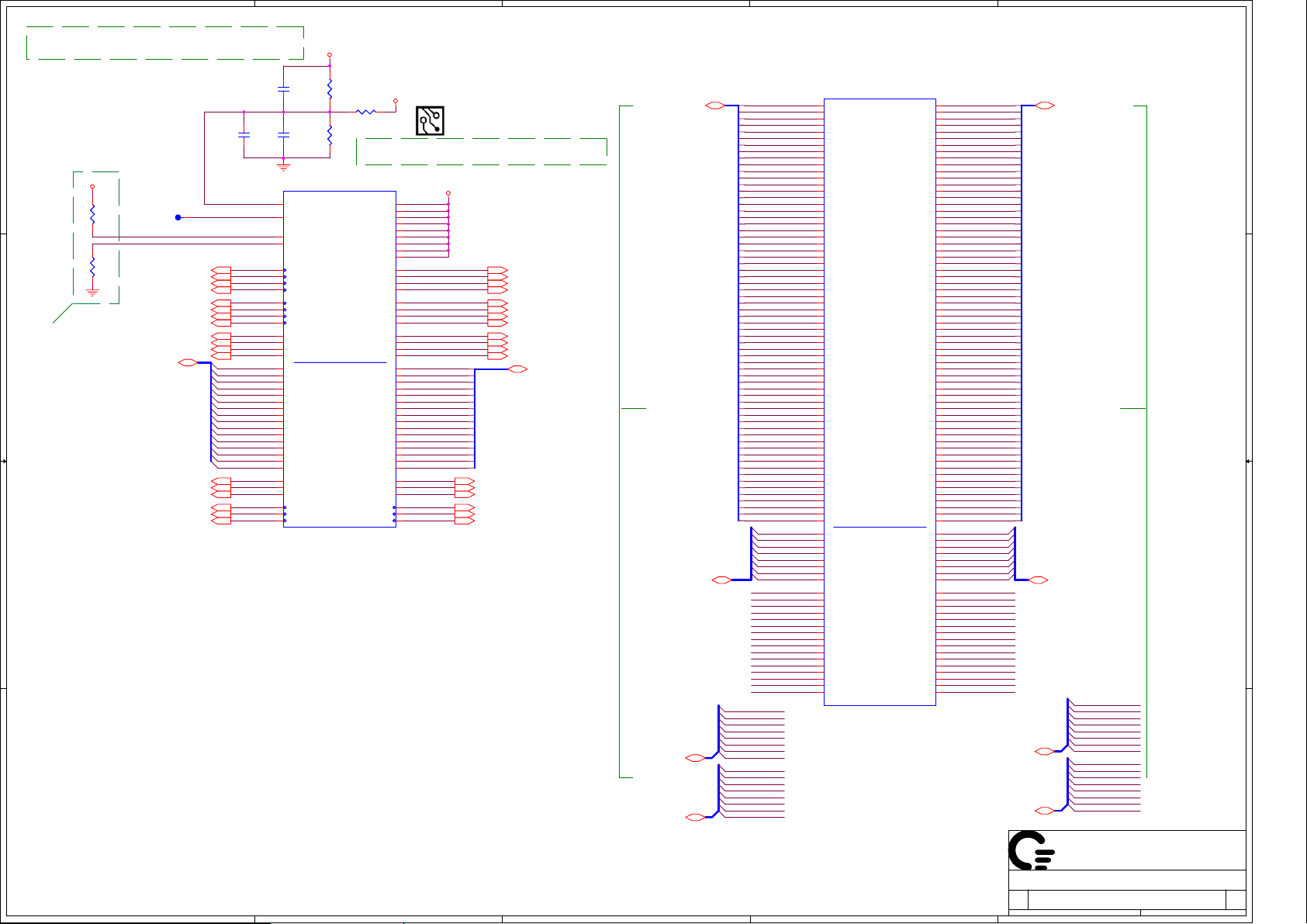

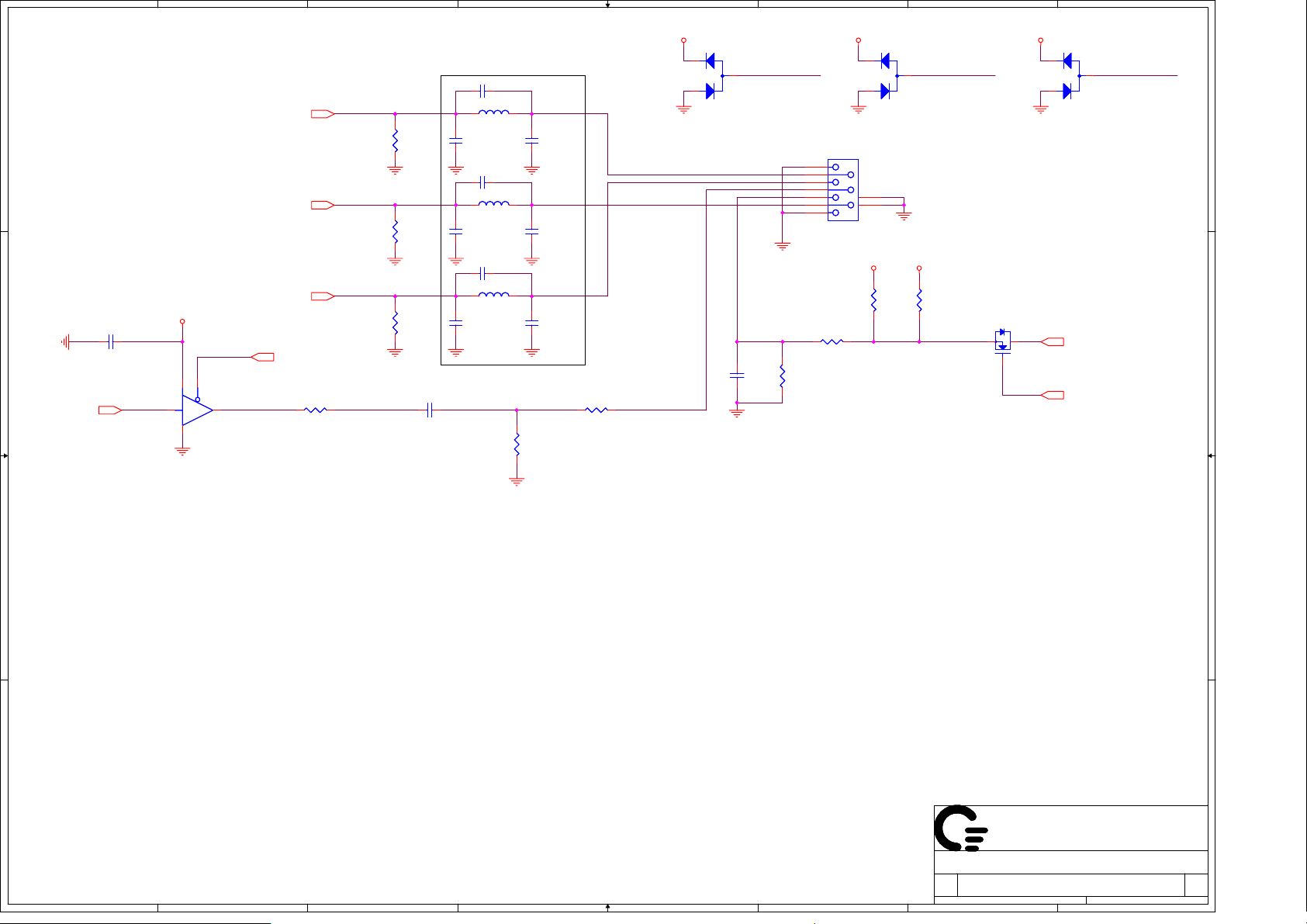

SYSTEM

JX6 MGD-INTEGRATED

RESET CIRCUIT

POWER SW

JX6_PCBJX6_PCB

A A

DDR2-SODIMM1

CH1 DDR II 533/667/800 MHz

PG 17,18

DDR2-SODIMM2

CH2 DDR II 533/667/800 MHz

PG 17,18

DDR2-MEMORY DEVICE

8MX16X4 84-PIN FBGA

PG 16

B B

Panel CONN.

PG 20

CPU HDT

DEBUG PORT

PG 10

533 MHZ DDR II

LVDS

AMD S1

Turion 64 Rev.F Dual-Core/

Sempron Rev.F Single-Core

Dual-Core 35W / Single-Core 25W

(638 S1g1 socket)

PG 8,9,10,11

HT_LINK

RS690

465 FCBGA

PG 12,13,14,15,16

VGA

DVI

PCIE(L2)

TVOUT

PCIE(L1)

CLOCK

ICS951462

PG 7

BCM 5755M

PG 30

MINI-CARD

CRT CONN.

PG 21

WLAN

BATT

CHARGER

AC/BATT

CONNECTOR

E-Switch

PI3L500

+3.3V_LAN

PG 31

PG 43

PG 42

PG 46

PG 51

VGA

DVI

RJ45/Magnetics

PG 31

CPU VR

DC/DC

+3.3V_ALW/+5V_ALW/+15V_ALW

REGULATOR

VCC_NB

REGULATOR

+1.8V_SUS/+1.2V_VCCP

+1.5V_RUN/+0.9V_DDR_VTT

PG 50

PG 47

PG 42

PG 48

PG 35

D-Module

PG 27

SATA - HDD

PG 27

C C

Side External USBX2

USB2.0 (P4)

IDE

SATA

USB2.0 (P0,P1)

SB600

549 BGA

A_LINK

USB2.0 (P6)

PG 33

33MHz PCI

Rear External USBX2

PG 33

USB2.0 (P2,P3)

USB2.0 (P7)

PG 23,24,25,26

LPC

CARDBUS/1394

OZ711EZ1TN

HD-AZALIA

RJ11

for Dock

SPI

PG 32

PG 36

MDC

PG 34

Tip

Ring

PG 34

AUDIO/AMP

STAC9205

PG 28

Audio

Jacks

PG 29

S-Video CONN

PG 22

S/PDIF

USB2.0 (P8)

DOCKING

CONNECTOR

PG 36

Bluetooth

PG 41

D D

FAN & THERMAL

EMC4001

PG 19

1

2

SIO

ECE5018

Expander

USB 2.0 Hub(4)

128 Pins VTQFP

PG 38

Serial Port

PG 33

3

BC

FLASH

SST25VF016B

PG 37

4

EC

MEC5025

128KB Flash

TMKBC

128 Pins VTQFP

PG 39

SPI PS/2

Touchpad/

Stick point

PG 41

BC

Keyboard

Controllor

Keyboard

PG 40

USER

INTERFACE

PG 40

5

ECE1077

PG 37

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

6

Date: Sheet

COMPUTER

System Block Diagram

System Block Diagram

System Block Diagram

MGD 1A

MGD 1A

MGD 1A

7

of

of

of

289Thursday, March 01, 2007

289Thursday, March 01, 2007

289Thursday, March 01, 2007

8

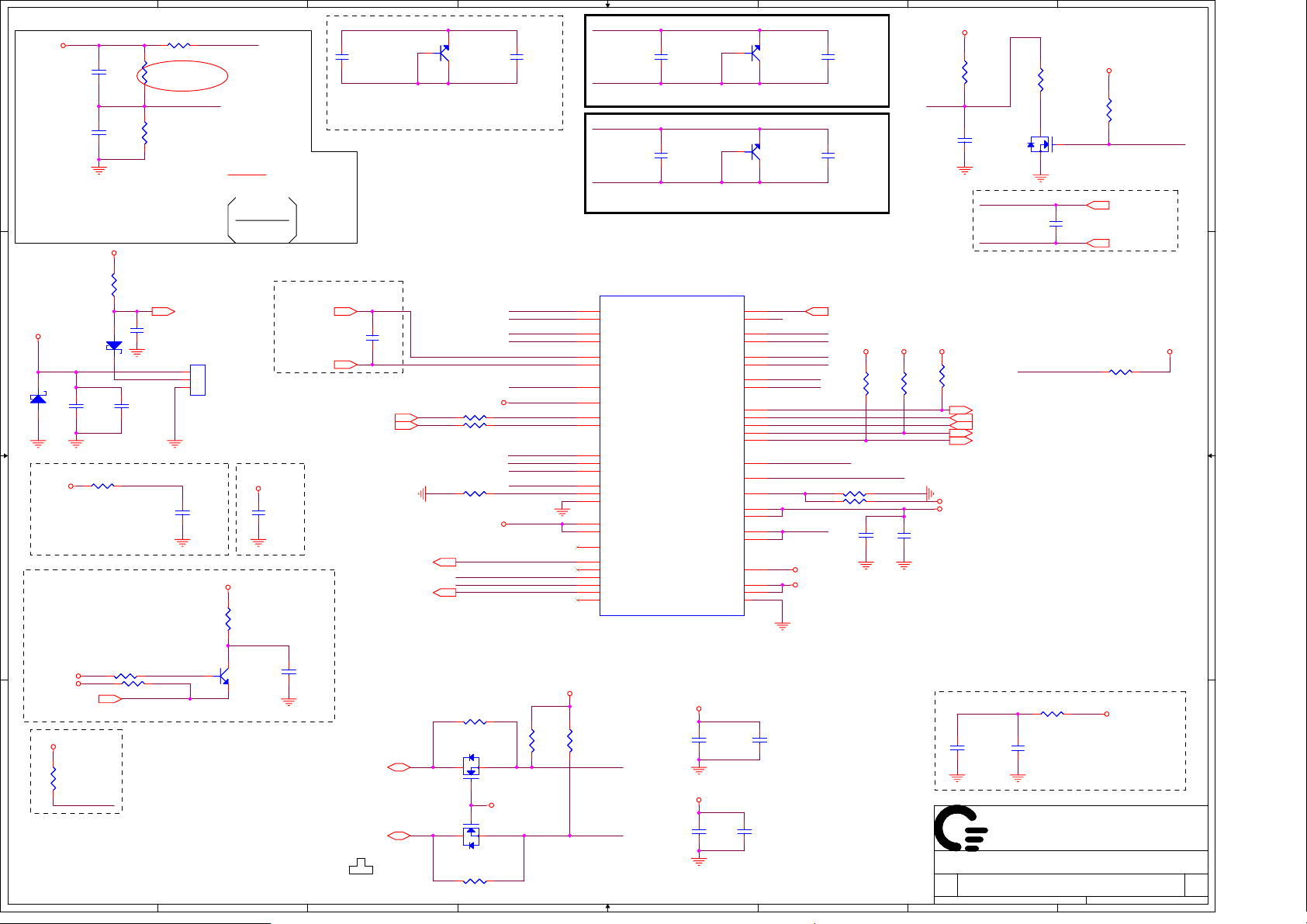

Page 3

1

2

3

4

5

6

7

8

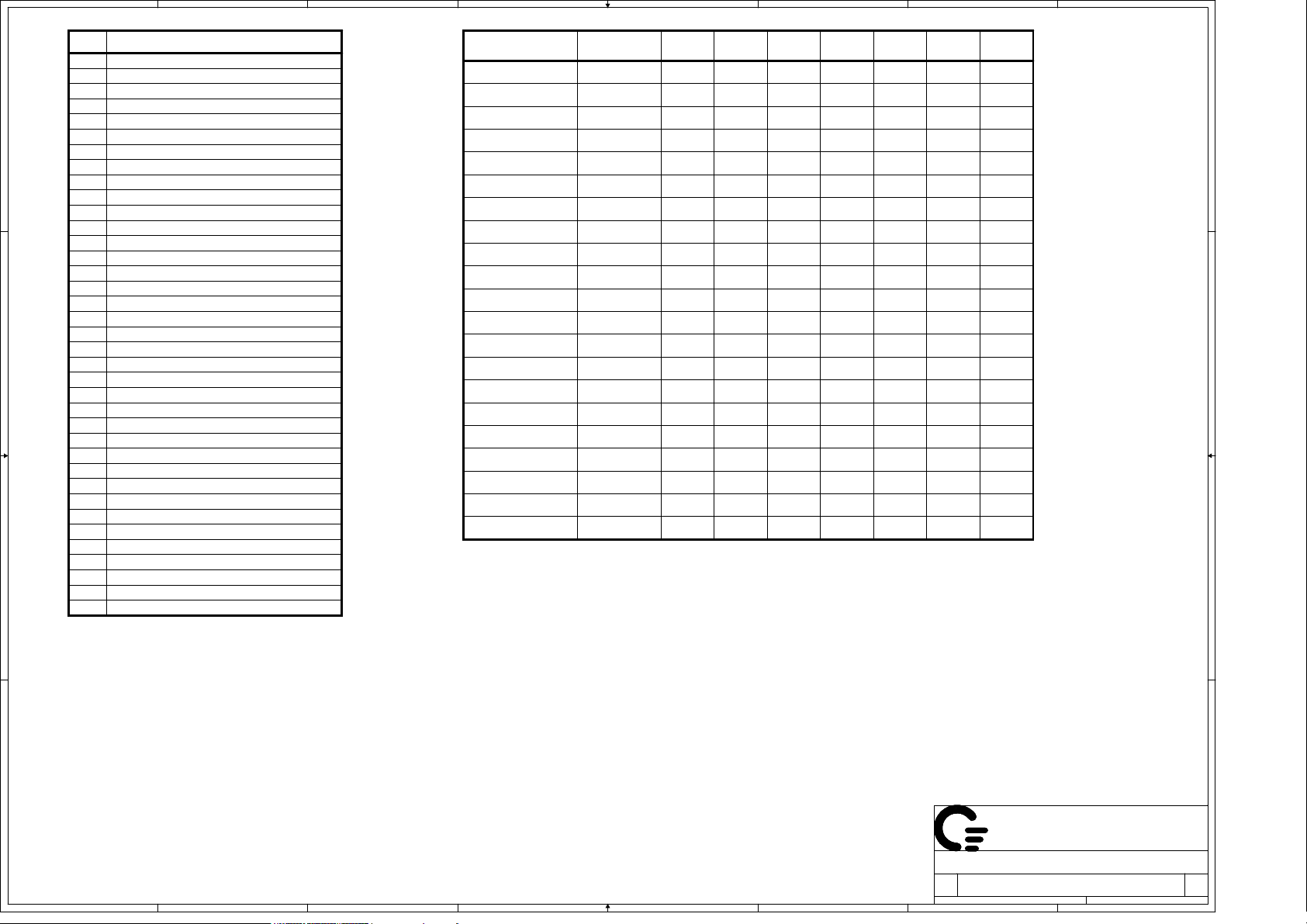

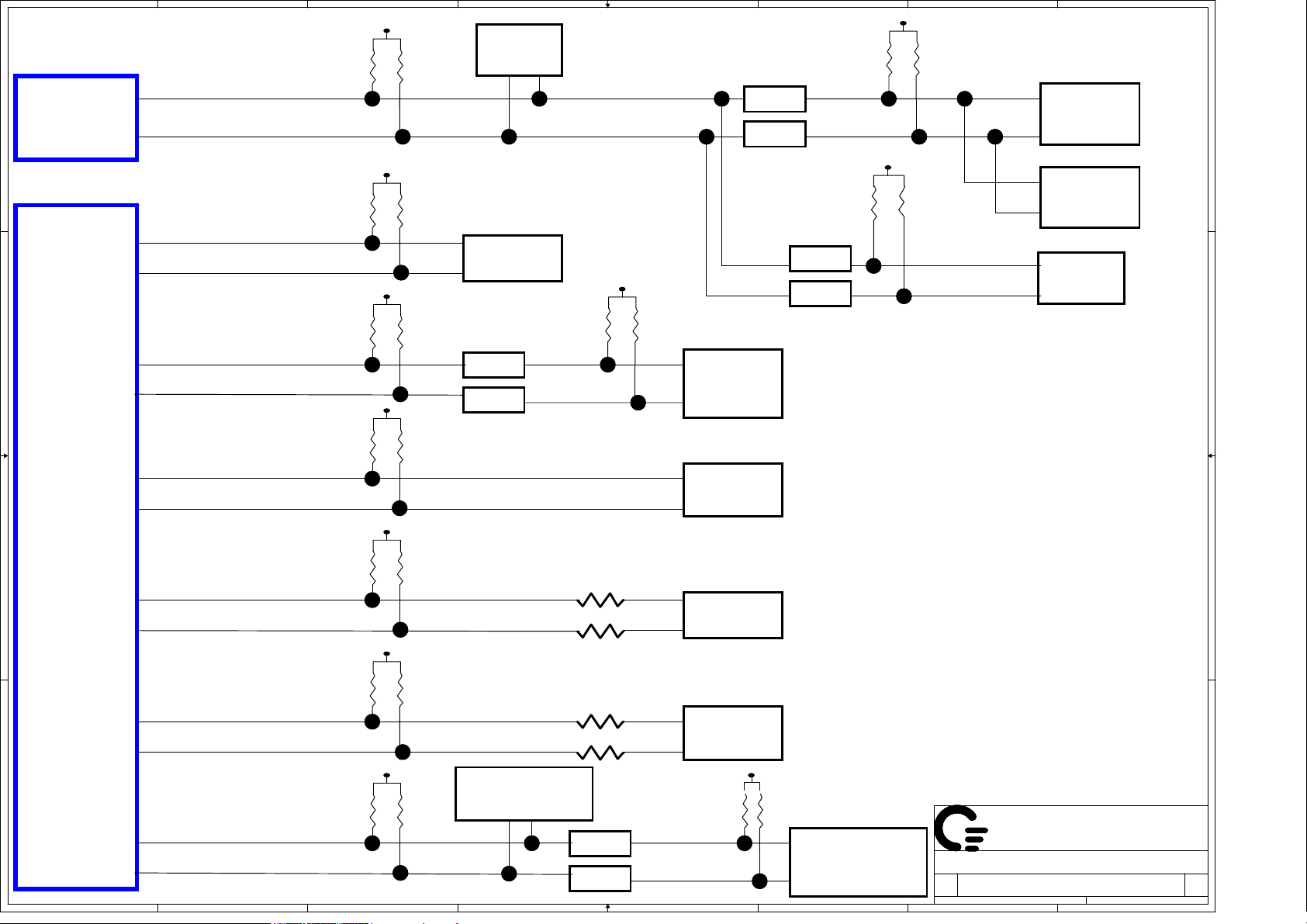

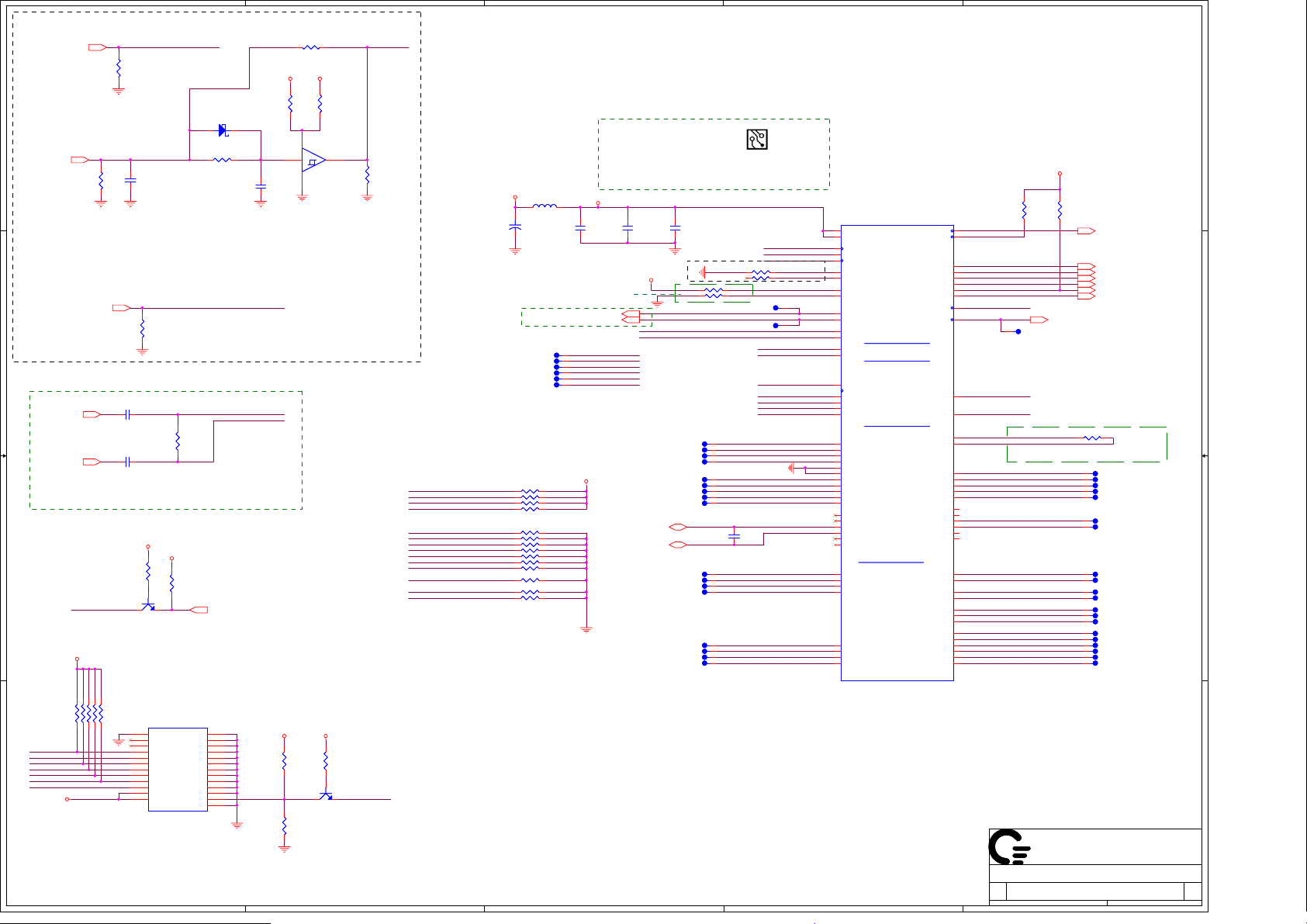

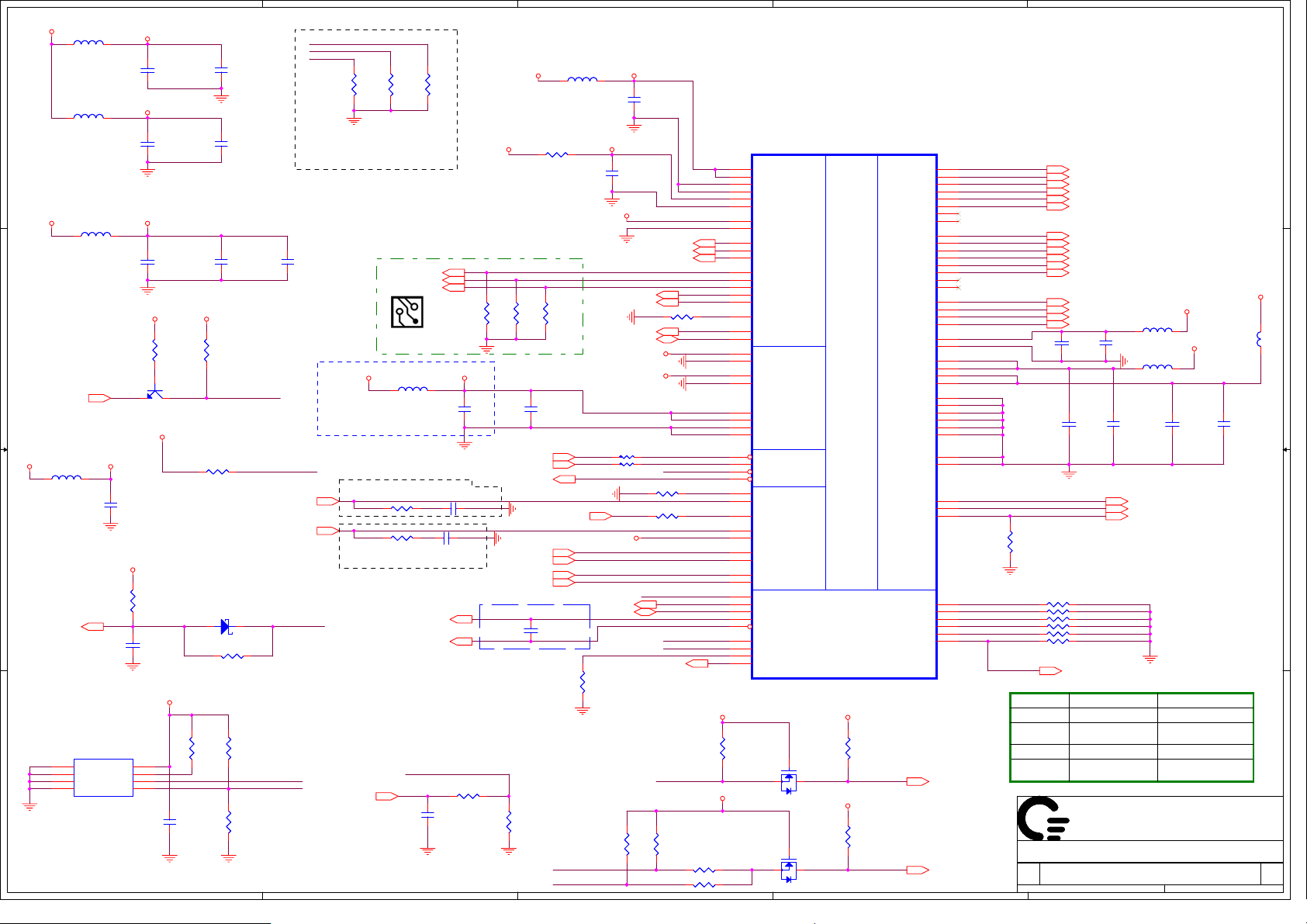

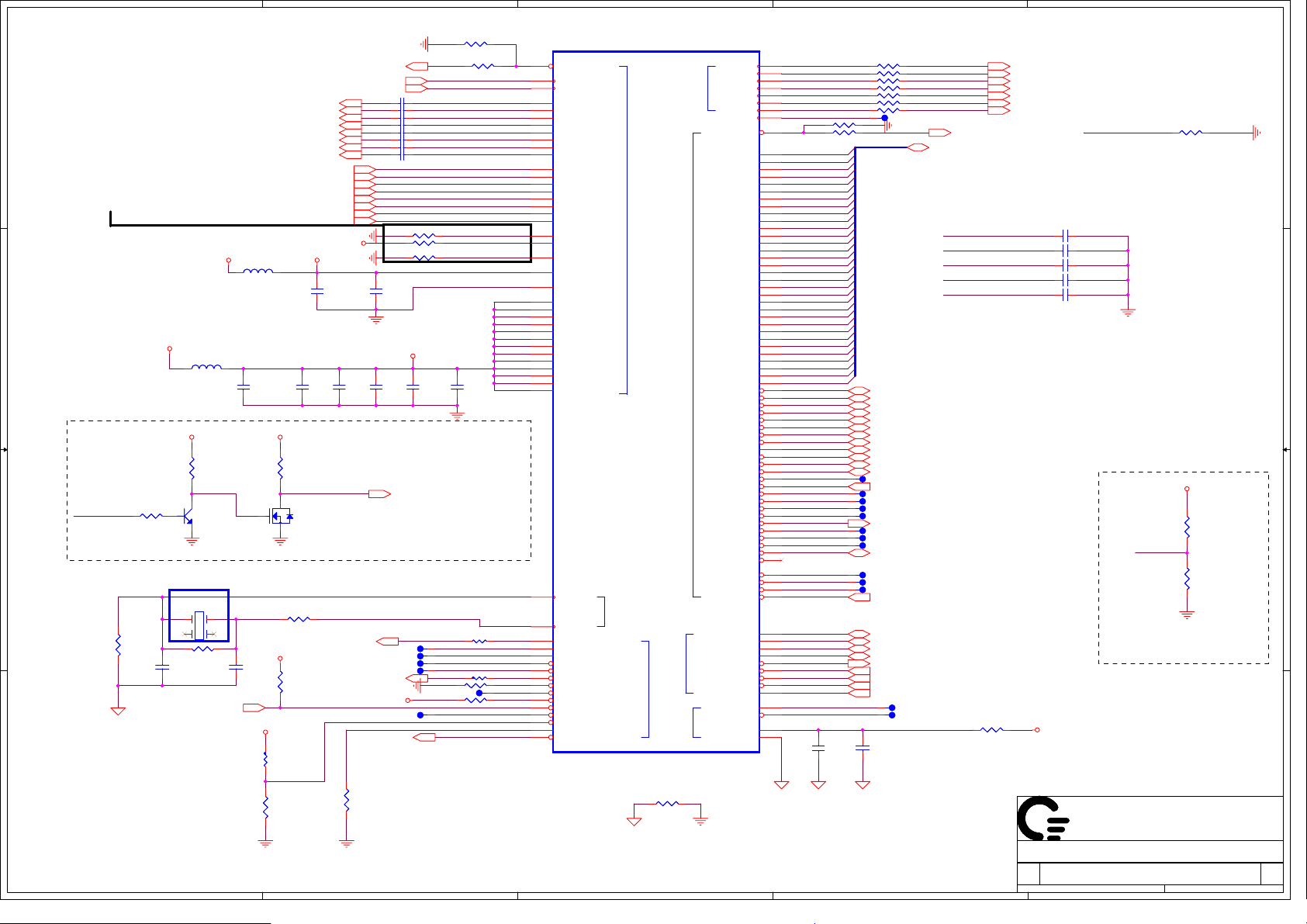

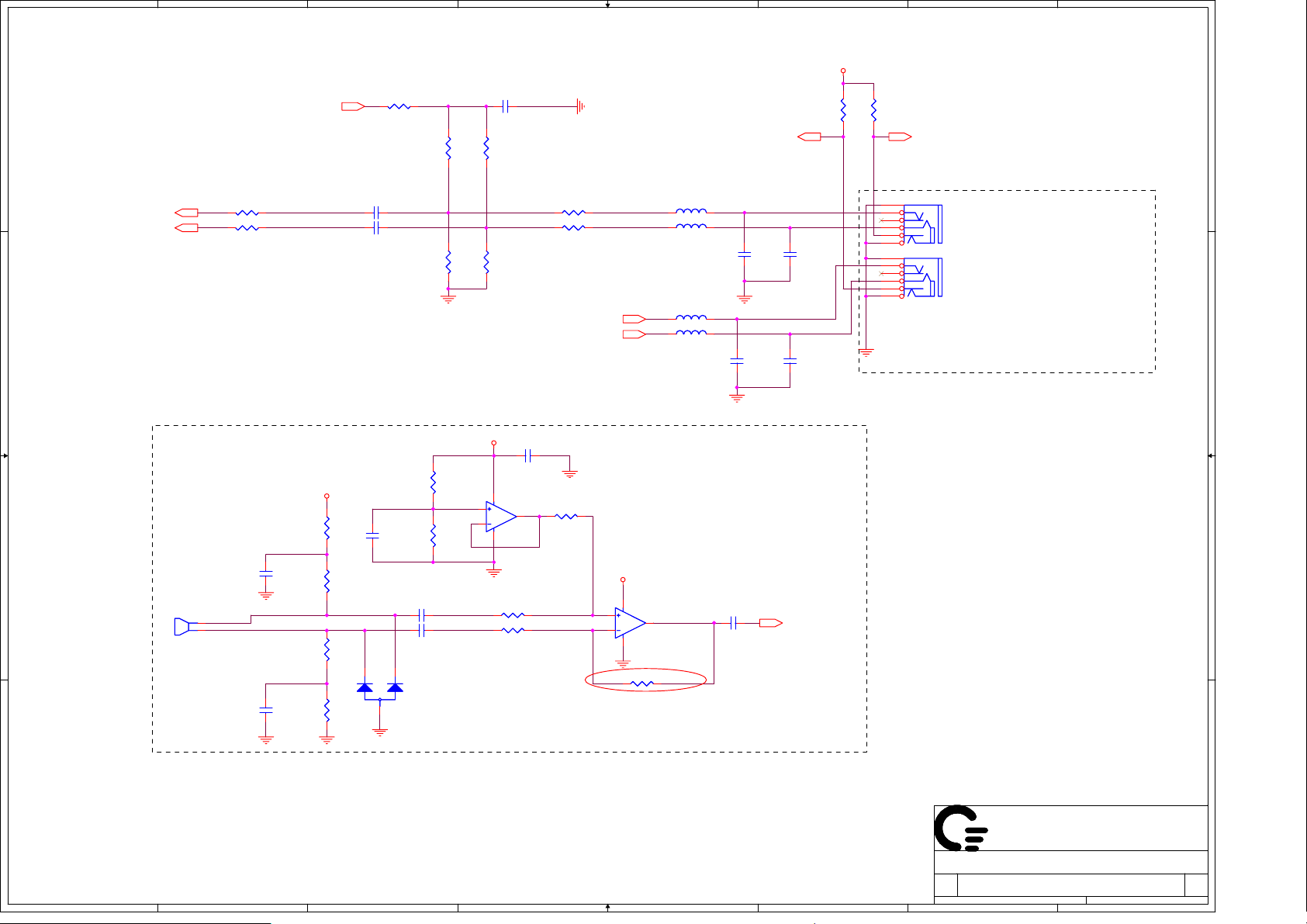

INDEX Power States

Pg# Description

Schematic Block Diagram

1

2

Front Page

3-4

Merom

5-10

Crestline

ICH8M

A A

B B

C C

11-14

DDRII SO-DIMM(200P)

15-16

17

Clock Generator

18-23

VGA

24

LCD Conn. & SSP

25

CRT Conn

26

SATA & IDE Conn

27

PCCARD/Conn & 1394

Express Card & Smart Card

28

29

Mini Card

MDC Conn.

30

31

SIO (MEC5025)

32

SIO (MEC5018)

33

SERIAL PORT & USB

34

Flash ROM, RTC & ECE1077

TP,BT & FIR

35

36

Switch,Keyboard & LED

FAN & Thermal

37

Audio CODEC(STAC9205)/Phone Jack

38-39

LOM (Nineveh)/Switch

40-41

42-43

Docking Conn/Q-Switch

System Reset Circuit

44

Battery Selector & Charger

45-46

47

DDR2_1.8VSUS, 0.9V

48

1.5VSUS,1.05V(VTT)

49

VGA DC/DC,1.25V,1.05V

CPU_MAX8786(3phase)

50

D/D Power

51

52

RUN Power Switch

53

DCIN,Batt

PAD& SCREW

54

55

EMI CAP

SMBUS BLOCK

56

Power Rail S3/M1

+3.3V_ALW

+5V_ALW

+3.3V_LAN

+1.8V_SUS

+0.9V_DDR_VTT

+5V_SUS

+3.3V_SUS

+5V_RUN

+3.3V_RUN

+1.8V_RUN

+1.25V_RUN

+1.5V_RUN

+1.05V_VCCP

VCC_VCRE

+LCDVCC

+5V_MOD

Control

Signal

S0/M0

S3/M1 S4/M1

S3/

M-off

S4/

M-off

S5/

M-off

D D

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

1

2

3

4

5

6

Date: Sheet

COMPUTER

Index, DNI, Power & Ground

Index, DNI, Power & Ground

Index, DNI, Power & Ground

MGD 1A

MGD 1A

MGD 1A

7

of

of

of

389Thursday, March 01, 2007

389Thursday, March 01, 2007

389Thursday, March 01, 2007

8

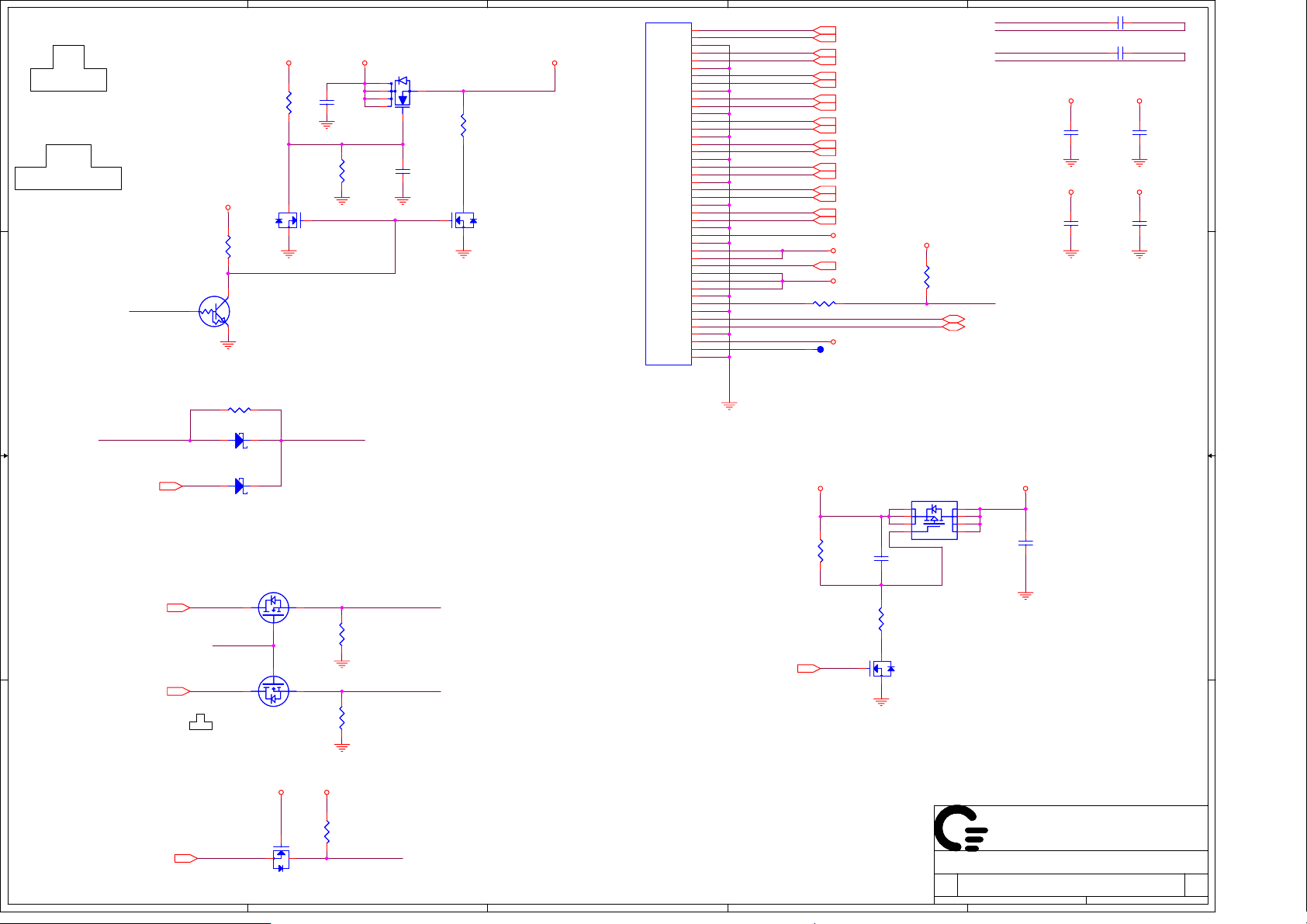

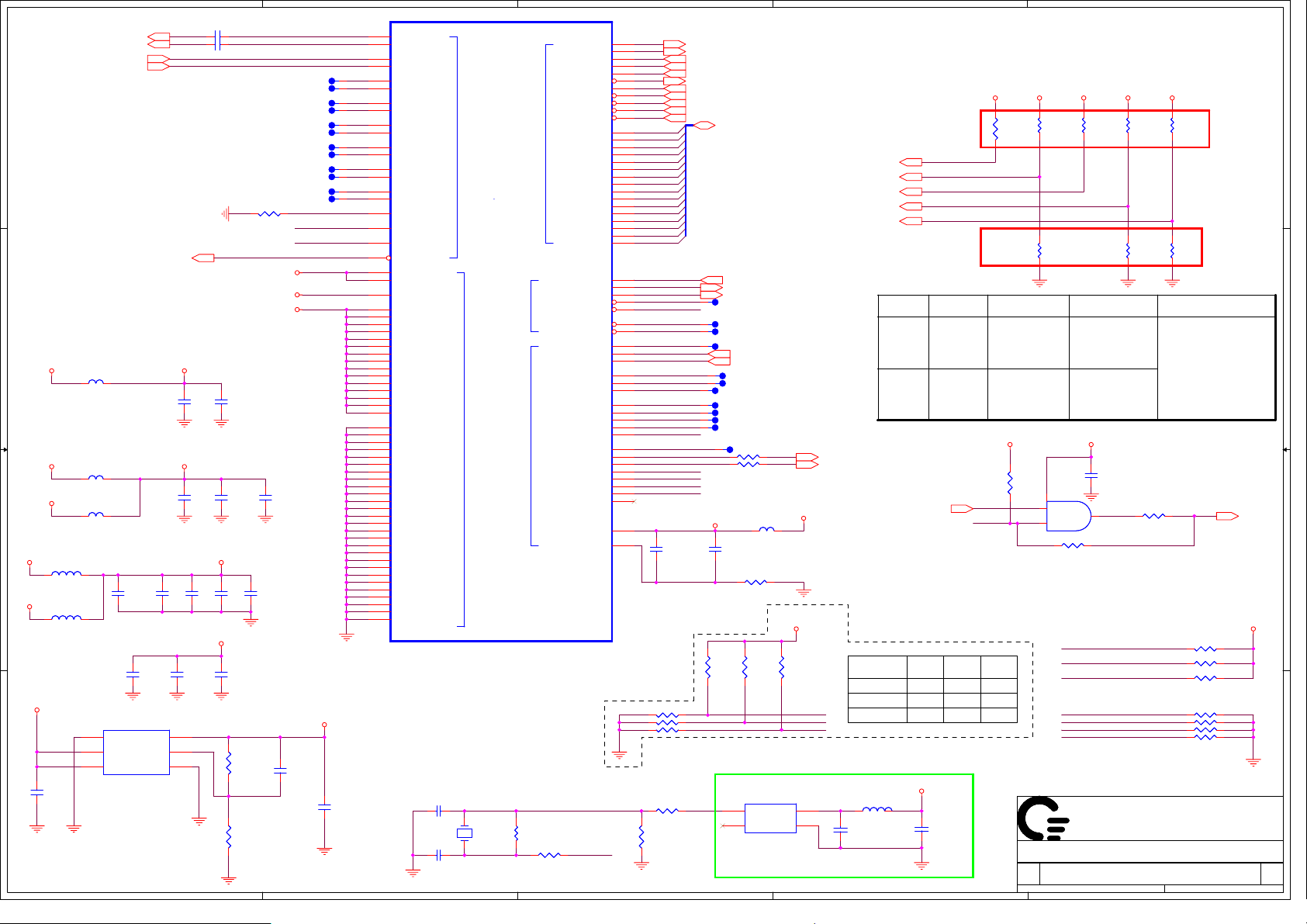

Page 4

5

4

3

2

1

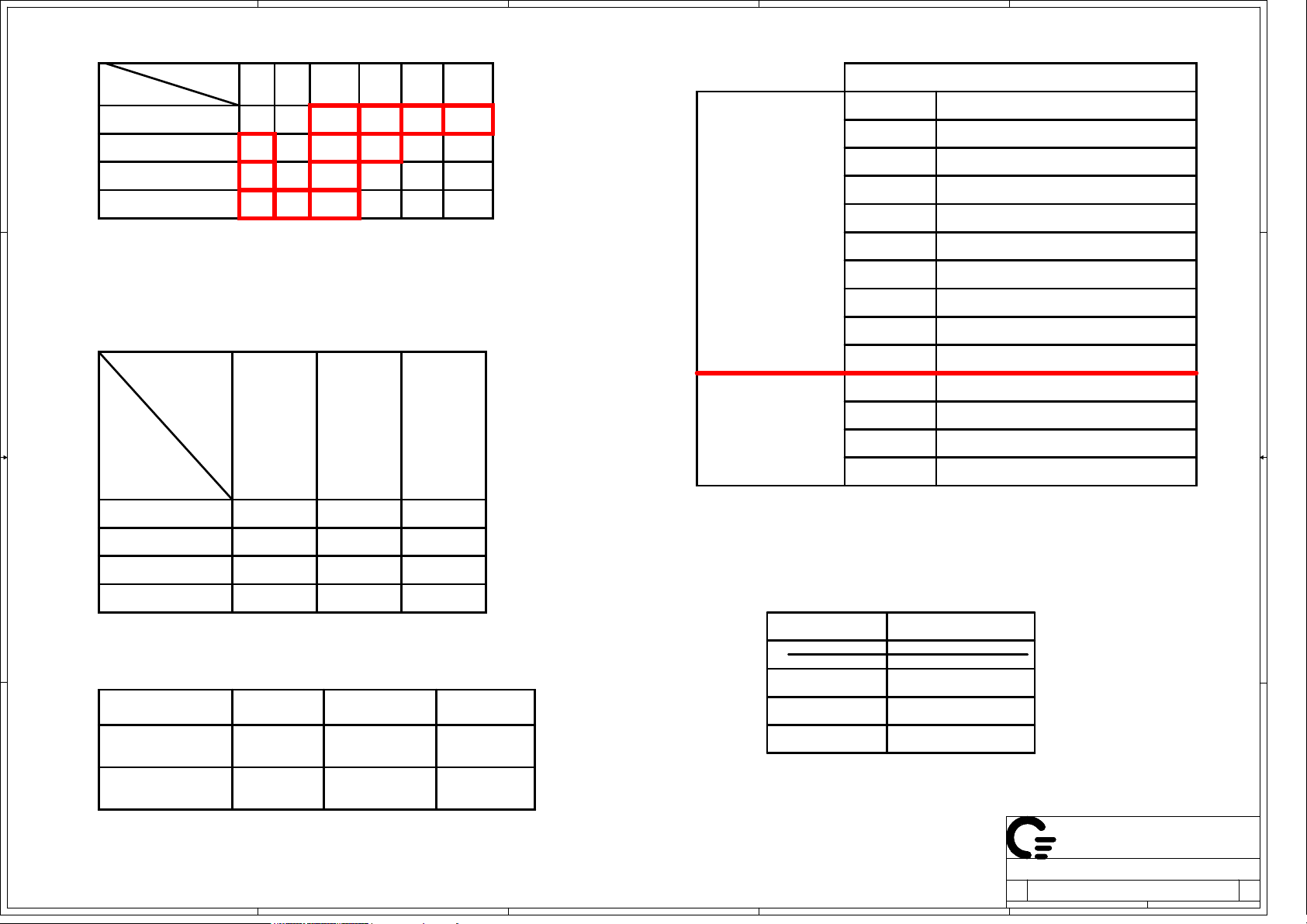

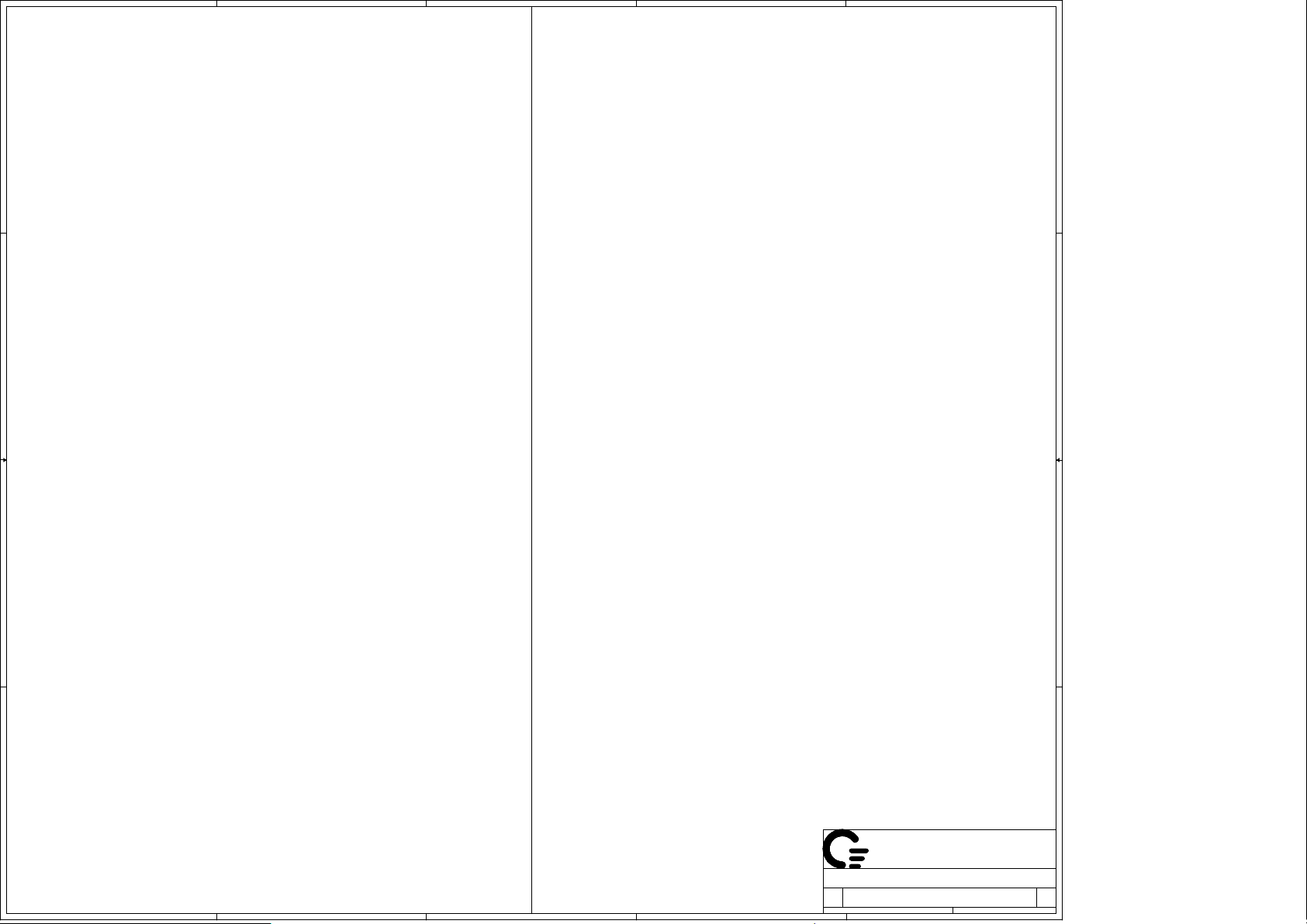

POWER STATES

SLP

State

D D

S0 (Full ON)

S3 (Suspend to RAM)

S4 (Suspend to DISK) ON OFF

S5 (SOFT OFF) ON OFFLOW LOW

Signal

SLP

S5#

HIGH

ALWAYS

PLANE

S3#

HIGH

LOW HIGH ON ON OFF

LOW HIGH

ON

SUS

RUN

PLANE

PLANE

ON ON ON

OFF

OFF

CLOCKS

OFF

OFF

OFF

SB600

USB PORT#

0

1

2

3

4

DESTINATION

Side Pair Top

Side Pair Bottom

Rear Bottom as viewed from the back

Rear Top as viewed from the back

Floppy Disk

5

6

7

C C

B B

PM TABLE

State

S0

S3

S5 S4/AC

S5 S4 on Battery

power

plane

+15V_ALW

+5V_ALW

+3.3V_ALW

+1.2V_ALW_SUS

ON

ON

+5V_SUS

+3.3V_SUS

+1.8V_SUS

+0.9V_DDR_VTT

ON ON

ON

OFF

OFFOFF

+5V_RUN

+3.3V_RUN

+2.5V_RUN

+1.8V_RUN

+1.2V_RUN

+1.5V_RUN

+VCC_CORE

+NB_CORE

OFFON

OFF

OFF

ECE5018

8

9

1

2

3

4

PCI EXPRESS

PCI TABLE

PCI DEVICE IDSEL

REQ#/GNT#

PIRQ

Lane 0

Lane 1

Lane 2

MINI CARD-1 WWAN

MINI CARD-2 WLAN

Cardbus

BT

Dock

NC

NC

NC

NC

DESTINATION

LOM

CardBus

A A

5

AD17 REQ#1/GNT#1

REQ#0/GNT#0

4

IRQ_SERIRQ

IRQD

PIRQADocking AD24

3

Lane 3

2

None

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

COMPUTER

ATHLON64 HT I/F

ATHLON64 HT I/F

ATHLON64 HT I/F

MGD 1A

MGD 1A

MGD 1A

1

of

of

of

489Thursday, March 01, 2007

489Thursday, March 01, 2007

489Thursday, March 01, 2007

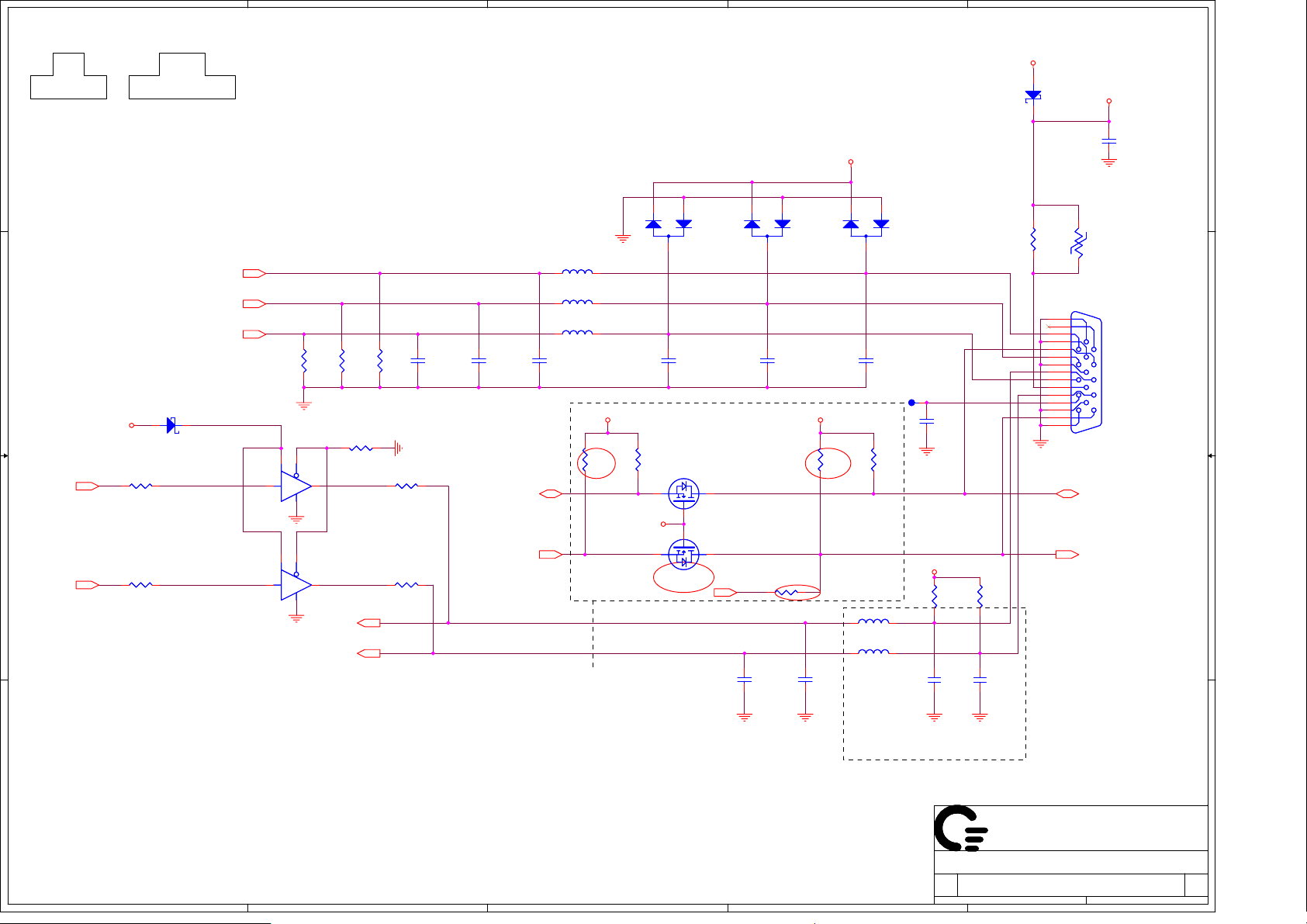

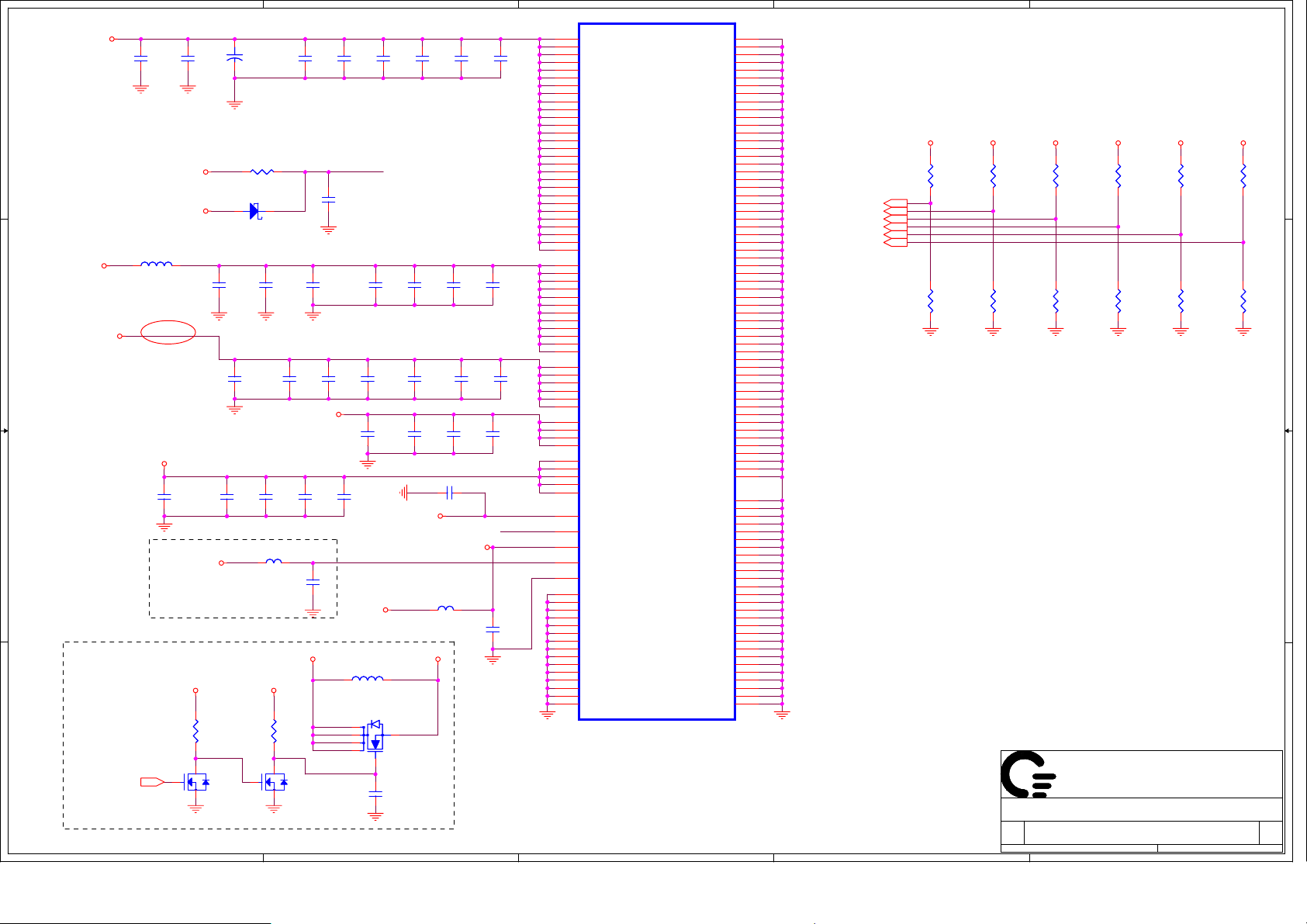

Page 5

5

4

3

2

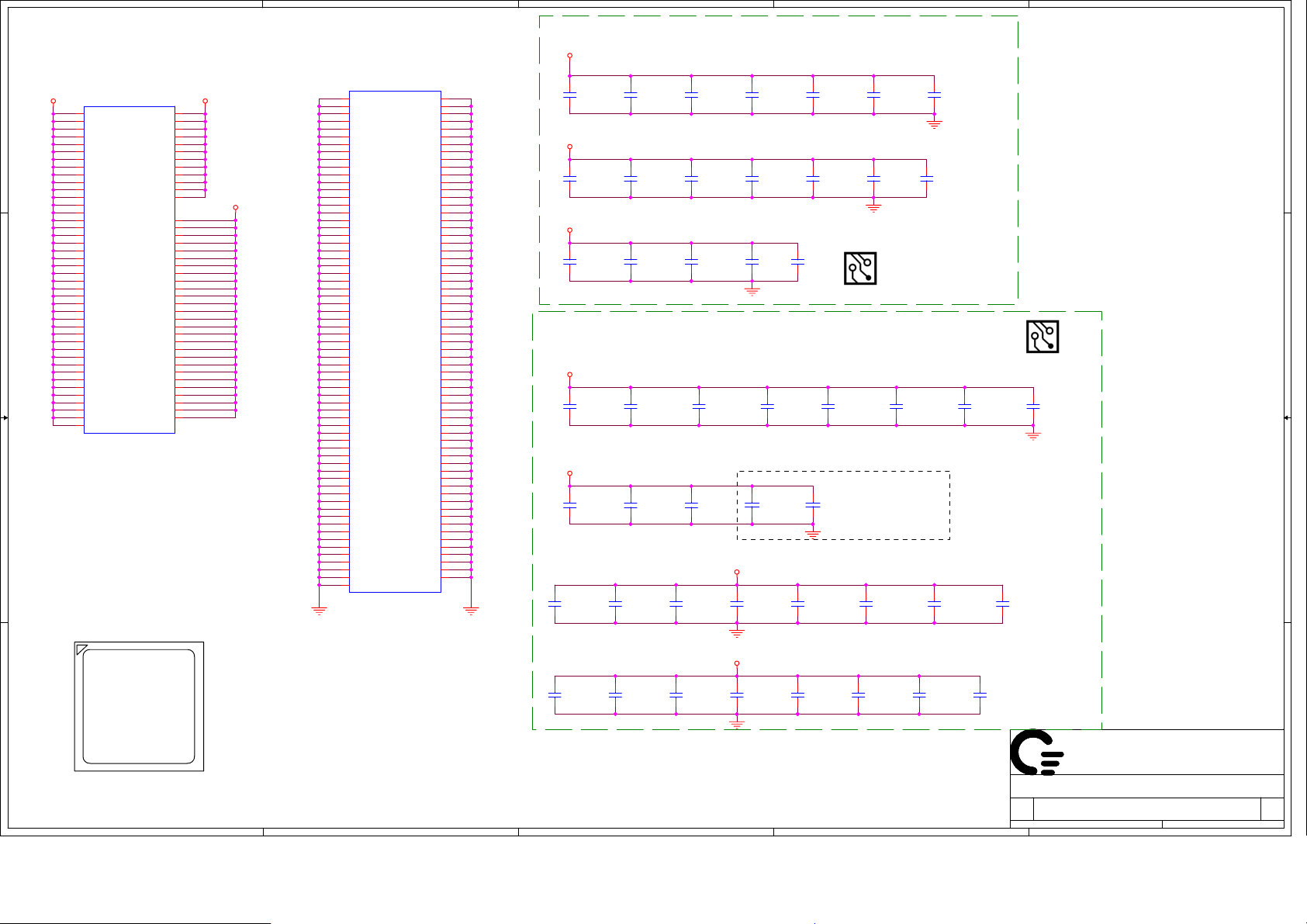

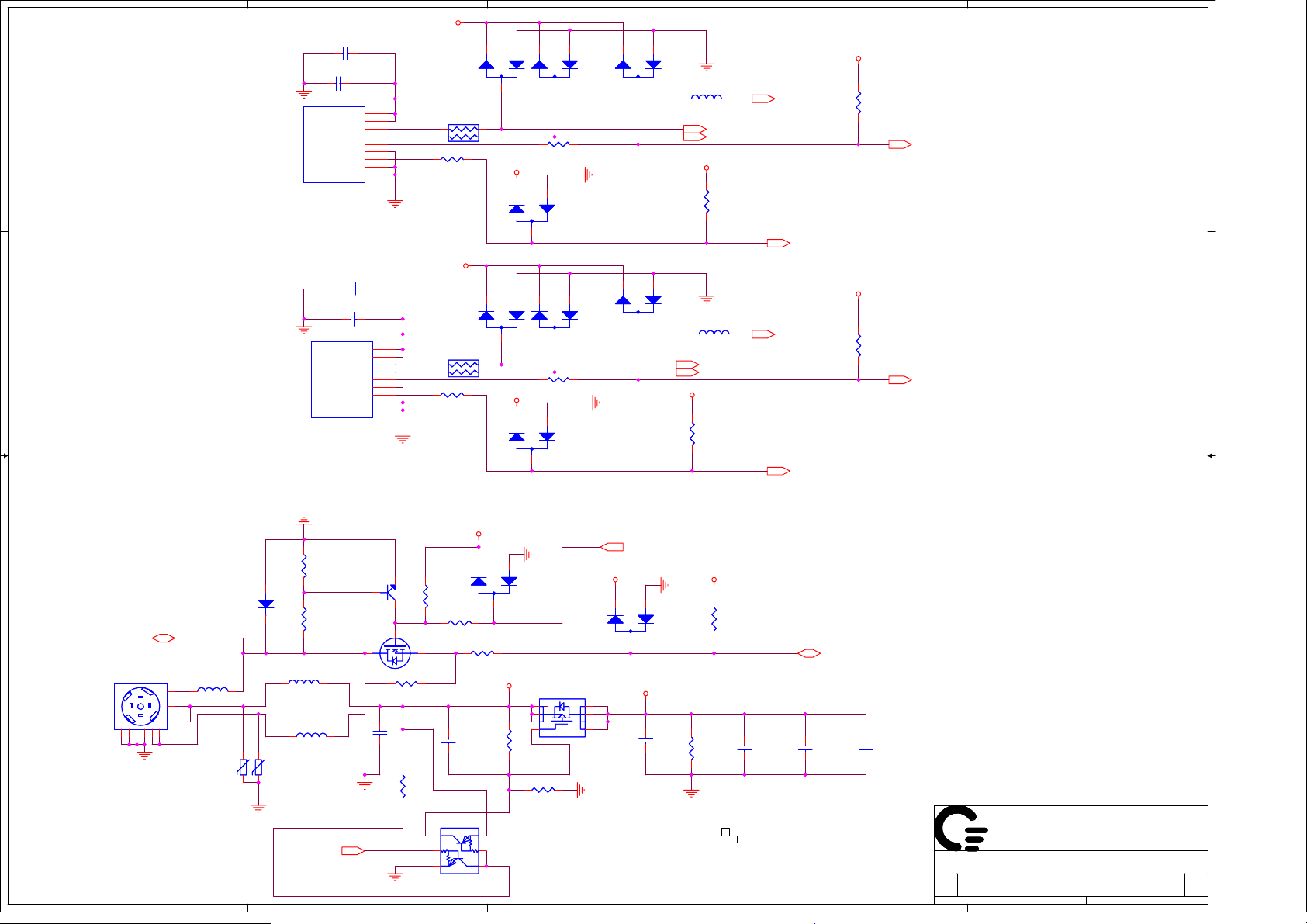

1

D D

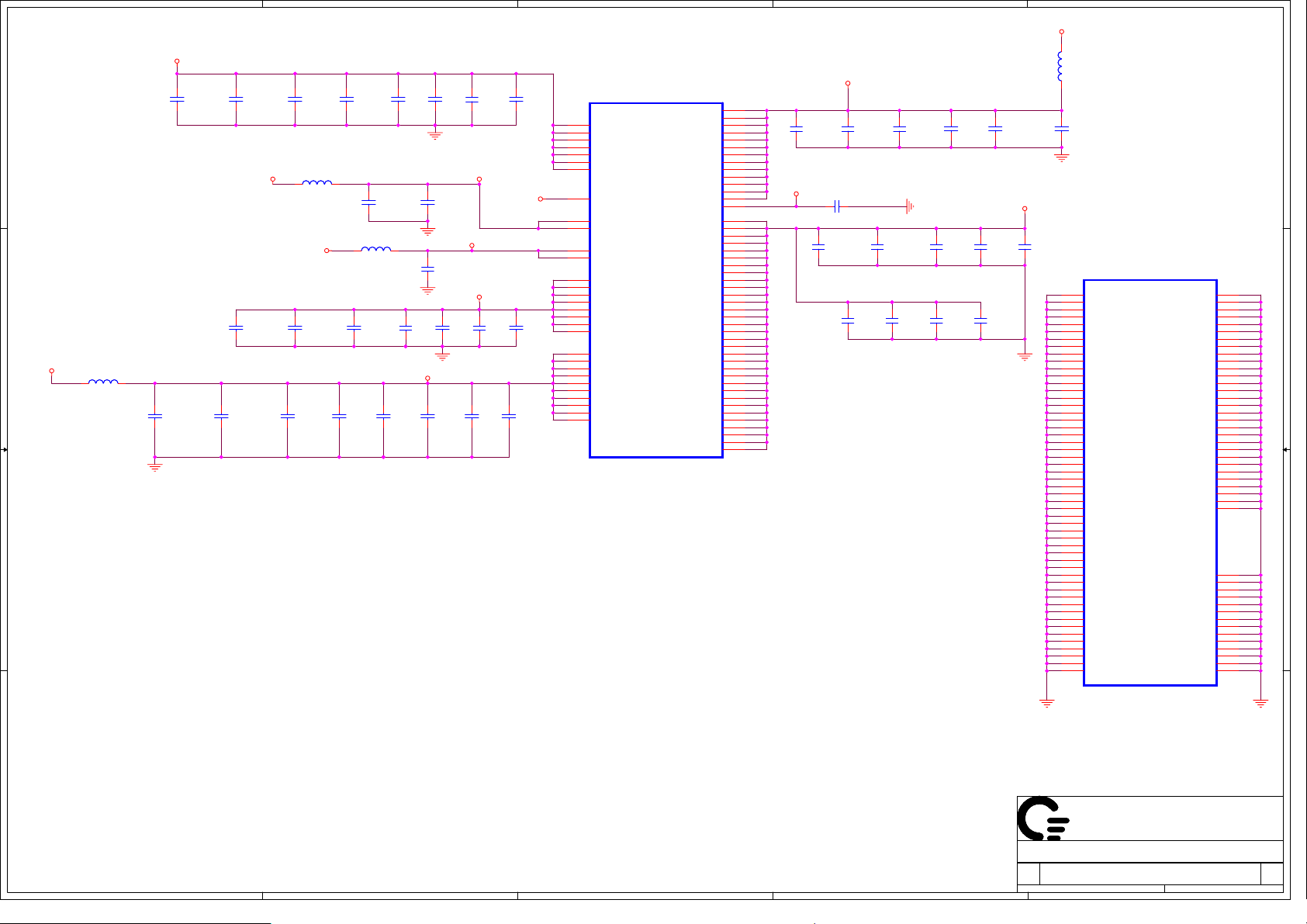

ADAPTER

+PWR_SRC

FDS4435BZ +INV_PWR_SRC

RUN_ON

BATTERY

ALW_ON

C C

ISL6236

+5V_ALW

MAX8731

+5V_ALW2

+15V_ALW

MAX8774 MAX8632

ISL6236

Charger

1.2V_ALW_SUS_ON

ALW_ON

+5V_ALW

B B

FDC655BN

FDC655BN

SI4810

793475

FDC655BN

+3.3V_ALW

Si4336DY

3.3V_RUN_ON

+3.3V_RUN

ALW_ON

FDS6670AS

ENAB_3VLAN

+3.3V_LAN

FDC655BN

SUS_ON

+3VSUS

+1.2V_ALW_SUS

CPU_VCORE_ENABLE

+VCC_CORE

1.2V_RUN_ON

FDS8880

+1.2V_RUN

NB_VCORE_RUN_ON

+NB_CORE

FDC655BN

1.8V_RUN_ON

DDR_ON

+1.8V_SUS

MAX8794

1.5V_RUN_ON

DDR_ON

+0.9V_DDR_VTT

SUS_ON

HDDC_EN#

MODC_EN#

+5V_HDD +5V_MOD +5V_RUN +VDDA

A A

RUN_ON

AUDIO_AVDD_ENABLE

+5V_SUS

EMC4001

REGCTL_PNP12

PBSS5540Z

( Q40 )

REGCTL_PNP25

MBT35200MT1G

( Q39)

L?

(Option)

5

4

+2.5VRUN

3

5755M

+1.2V_LOM

+2.5V_LOM

2

+1.8V_RUN

Title

Title

Title

ATHLON64 HT I/F

ATHLON64 HT I/F

ATHLON64 HT I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MGD 1A

MGD 1A

MGD 1A

Date: Sheet

Date: Sheet

Date: Sheet

+1.5V_RUN

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

1

of

of

of

589Thursday, March 01, 2007

589Thursday, March 01, 2007

589Thursday, March 01, 2007

Page 6

1

C3

A A

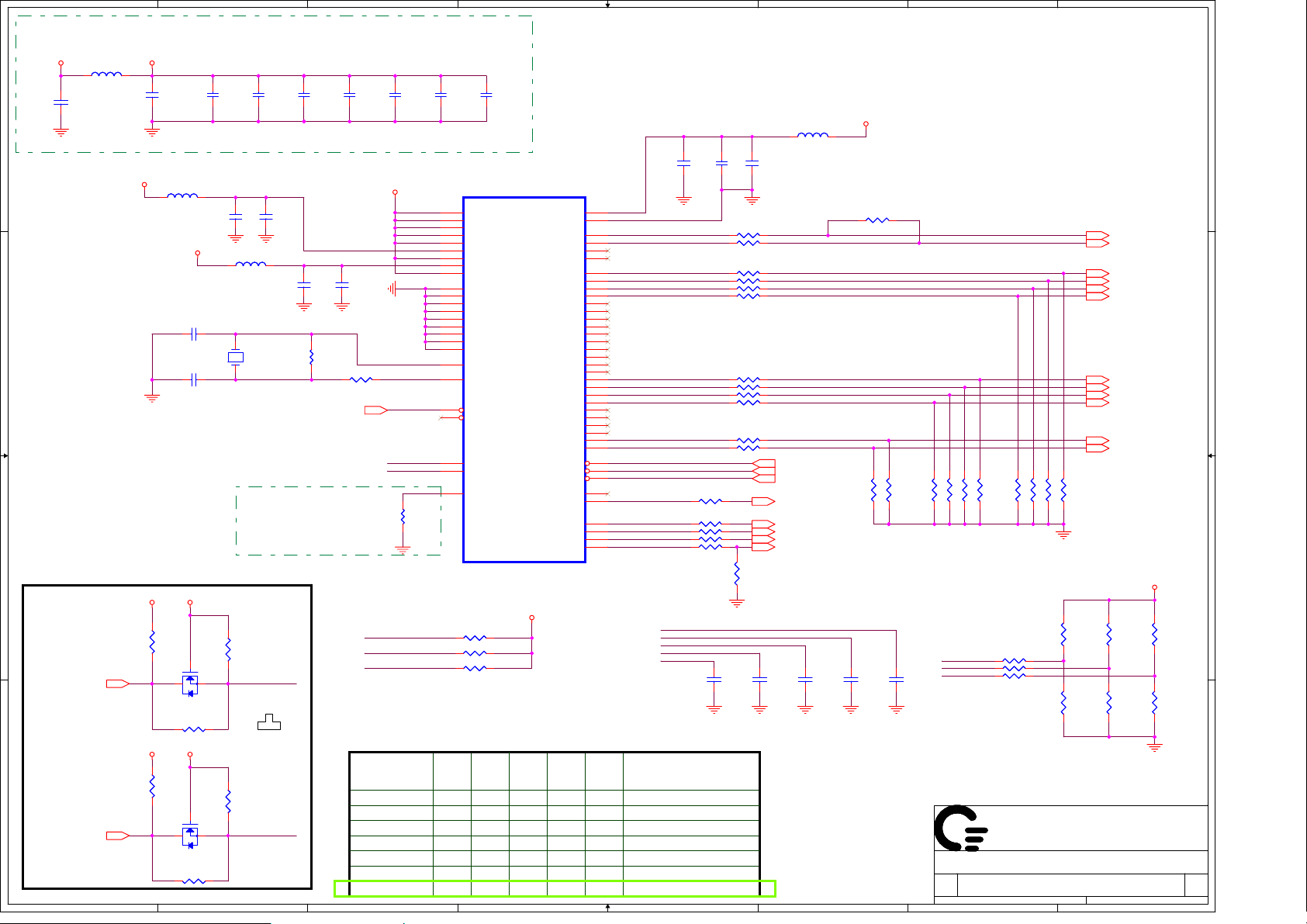

SB600

F3

8

7

B B

13

12

2

3

+3.3V_SUS

2.2K 2.2K

SB_SMBCLK

SB_SMBDATA

+3.3V_ALW

8.2K 8.2K

LCD_SMBCLK

LCD_SMBDAT +3.3V_ALW

+3.3V_ALW

2.2K 2.2K

CKG_SMBCLK

+3.3V_ALWCKG_SMBDAT

+5V_ALW

SMBUS Address [C8]

+3.3V_SUS

6

5

Inverter

2N7002

2N7002

4

5755M

LOM

C8C7

INV

CLK_SCLK

CLK_SDATA

SMBUS Address [58]

+3.3V_RUN

2.2K 2.2K

16

17

5

CLK GEN.

6

2N7002

2N7002

MEM_SCLK

MEM_SDATA

2.2K 2.2K

2N7002

2N7002

SMBUS Address [D2]

+3.3V_RUN

2.2K 2.2K

+3.3V_WLAN

WLAN_SMBCLK

WLAN_SMBDATA

7

197

195

SMBUS Address [A0]

197

195

SMBUS Address [A2]

30

32

SMBUS Address [TBD]

8

DIMM0

DIMM1

WLAN

8.2K 8.2K

SIO

DOCK_SMB_CLK

6

DOCK_SMB_DAT

5

+5V_ALW

39

DOCKING

40

SMBUS Address [C4, 72, 70, 48]

+3.3V_ALW

Macallan IV

C C

10

SBAT_DH_SMBCLK

9

2.2K 2.2K

+3.3V_ALW

100

+3.3V_ALWSBAT_DH_SMBDAT

3

2'nd

4

BATTERY

SMBUS Address [16]

100

2.2K2.2K

112

111

PBAT_SMBCLK

PBAT_SMBDAT

+3.3V_ALW

+3.3V_ALW

D D

100

THERM_SMBCLK

99

1

2

4.7K 4.7K

+3.3V_ALWTHERM_SMBDAT

3

CHARGER

SMBUS Address [12]

910

4

100

100

2N7002

2N7002

3

BATTERY

4

CONN

+3.3V_SUS

2.2K 2.2K

EMC_SMBCLK

EMC_SMBDATA

5

SMBUS Address [16]

12

GUARDIAN

11

SMBUS Address [2F]

6

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

COMPUTER

SMBUS BLOCK

SMBUS BLOCK

SMBUS BLOCK

MGD 1A

MGD 1A

MGD 1A

7

of

of

of

689Thursday, March 01, 2007

689Thursday, March 01, 2007

689Thursday, March 01, 2007

8

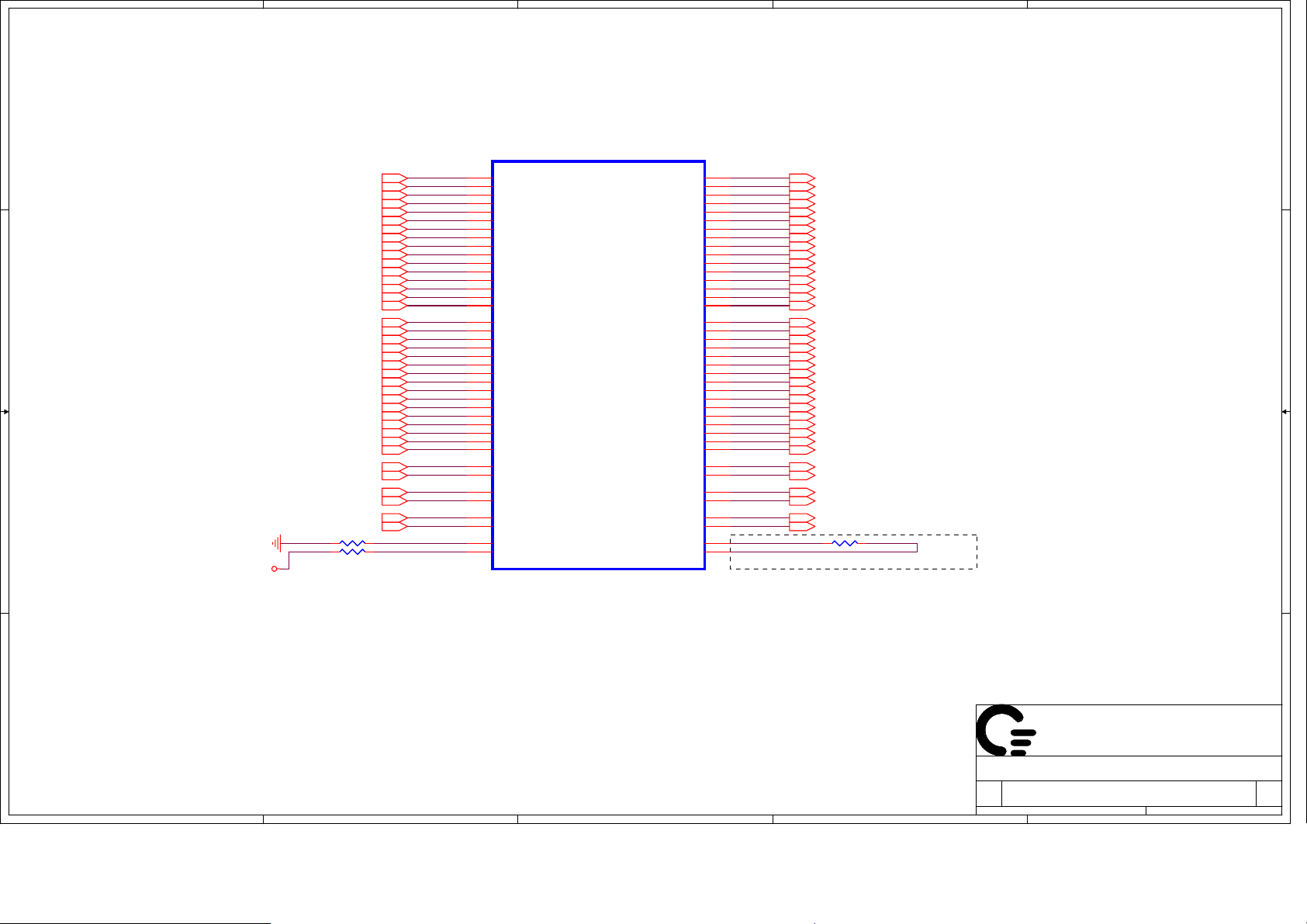

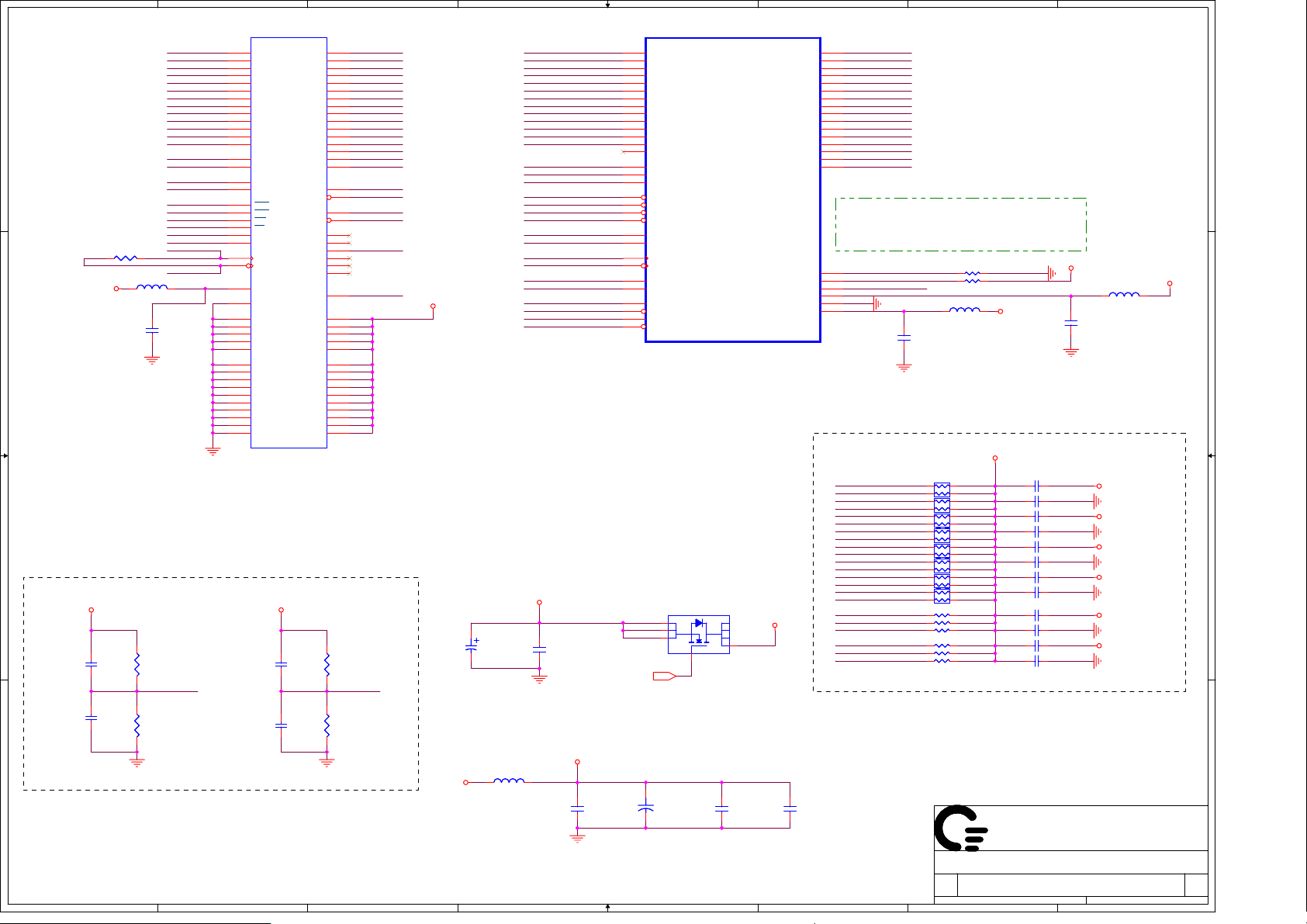

Page 7

1

33 ohm +-25%@100MHz

25m ohm max DC resistance

3A current rating

+3.3V_RUN

L27

L27

1 2

BLM18PG330SN1B

BLM18PG330SN1B

12

C599

C599

10U

10U

10

10

X5R

X5R

A A

EP

EP

0805

0805

%

%

±20

±20

B B

C C

+3.3V_CLK

12

0603

0603

C125

C125

22U_6.3V_0805

22U_6.3V_0805

+3.3V_RUN

L28

L28

1 2

BLM15AG221SN1D

BLM15AG221SN1D

+3.3V_RUN

Parallel Resonance Crystal

C588 33P

C588 33P

C584 33P

C584 33P

+3.3V_ALW

+3.3V_RUN

SMbus address D2

These are for

backdrive issue.

CKG_SMBDAT39

D D

CKG_SMBCLK39

1

R554

R554

2.2K

2.2K

1 2

+3.3V_ALW

R524

R524

2.2K

2.2K

1 2

3 1

2N7002W-7-F

2N7002W-7-F

R555 0_NCR555 0_NC

1 2

+3.3V_RUN

3 1

2N7002W-7-F

2N7002W-7-F

R517 0_NCR517 0_NC

1 2

50

50

NPO

NPO

50

50

NPO

NPO

2

Q65

Q65

2

Q64

Q64

2

+3.3V_CLK(40 mils)

12

12

12

C133

C133

C166

C166

0.1U_10V

0.1U_10V

0.1U_10V

0.1U_10V

12

12

C128

C128

C591

C591

0.047U

0.047U

2.2U

2.2U

16

16

6.3

6.3

%

%

±10

±10

0603

0603

0603

0603

X5R

X5R

X7R

X7R

L67

L67

1 2

BLM15AG221SN1D

BLM15AG221SN1D

21

Y5

Y5

14.318MHZ

14.318MHZ

20PPM

20PPM

20p

20p

XTALOUT_CLK_C XTALOUT_CLK

Place R535 less than

100mils from Clock Gen.

R553

R553

2.2K

2.2K

1 2

CLK_SDATA

GDS

231

2N7002W-7-F

C169

C169

0.1U_10V

0.1U_10V

+3VS_CLK_VDD48

+3VS_CLK_VDDREF

12

12

C585

C585

2.2U

2.2U

6.3

6.3

0603

0603

X5R

X5R

R516

R516

1M_NC

1M_NC

1 2

R520 0R520 0

1 2

CLOCK_ENABLE#39

12

C129

C129

0.1U_10V

0.1U_10V

C586

C586

0.047U

0.047U

16

16

±10

±10

0603

0603

X7R

X7R

%

%

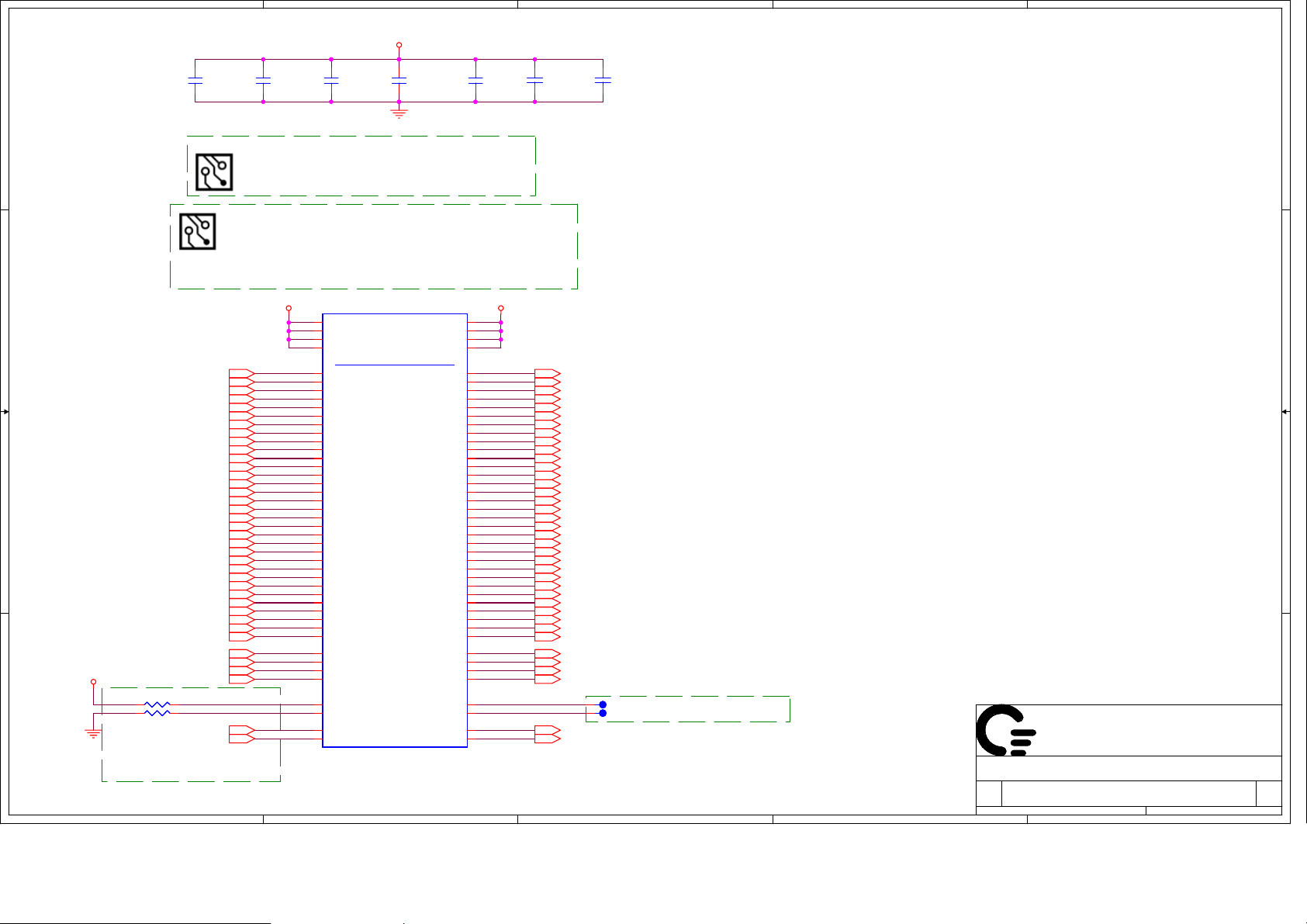

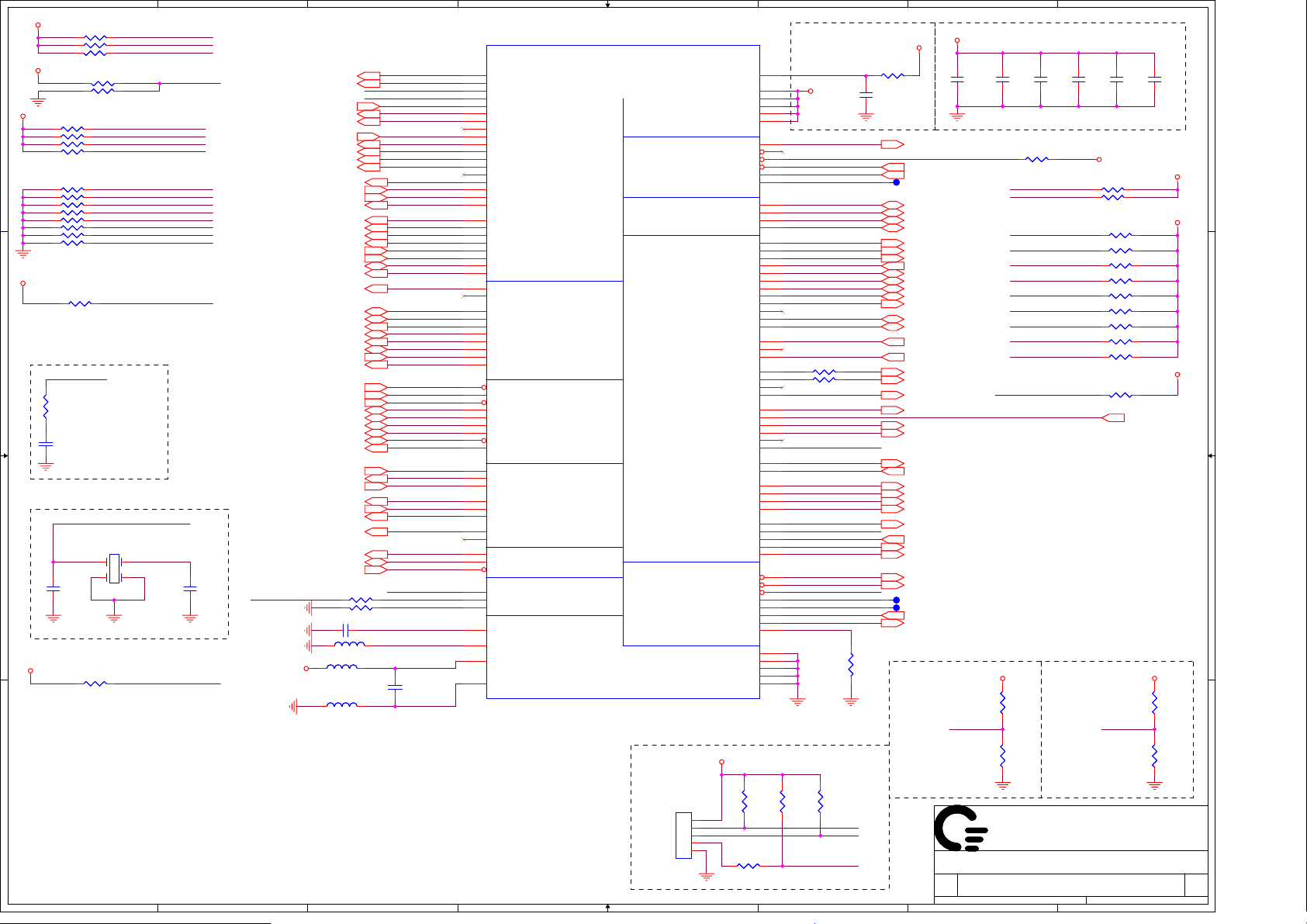

EXT CLK FREQUENCY SELECT TABLE(MHZ)

FS2

R519

1 2

2

R519

2.2K

2.2K

CLK_SCLK

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 1

3

12

C174

C174

0.1U_10V

0.1U_10V

+3.3V_CLK

XTALIN_CLK

CLK_SCLK

CLK_SDATA

CLKIREF

R535

R535

475_F

475_F

1 2

LOM_CLKREQ#

MINI1CLK_REQ#

MINI2CLK_REQ#

FS0

FS1

3

12

C137

C137

0.1U_10V

0.1U_10V

U33

U33

54

VDDCPU

14

VDD_SRC1

23

VDD_SRC2

28

VDD_SRC3

44

VDD_SRC4

5

VDD_48

39

VDD_ATIG

2

VDD_REF

60

VDDHTT

53

GND_CPU

15

GND_SRC1

22

GND_SRC2

29

GND_SRC3

45

GND_SRC4

8

GND_48

38

GND_ATIG

1

GND_REF

58

GNDHTT

3

XIN

4

XOUT

11

RESET_IN#

61

NC

9

SMBCLK

10

SMBDAT

48

IREF

ICS951462

ICS951462

R507 10KR507 10K

1 2

R551 10KR551 10K

1 2

R552 10KR552 10K

1 2

CPU

Hi-Z

X

180.00

220.00

100.00

133.33

200.00

12

C179

C179

0.1U_10V

0.1U_10V

SRCCLK

[2:1]

100.00

100.00

100.00

100.00

100.00

100.00

100.00

4

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

SRCCLKT6

SRCCLKC6

ATIGCLKT0

ATIGCLKC0

ATIGCLKT1

ATIGCLKC1

ATIGCLKT2

ATIGCLKC2

ATIGCLKT3

ATIGCLKC3

SRCCLKT5

SRCCLKC5

SRCCLKT4

SRCCLKC4

SRCCLKT3

SRCCLKC3

SRCCLKT2

SRCCLKC2

SRCCLKT0

SRCCLKC0

SRCCLKT1

SRCCLKC1

SRCCLKT7

SRCCLKC7

CLKREQA#

CLKREQB#

CLKREQC#

48MHz_1

48MHz_0

FS1/REF1

FS0/REF0

FS2/REF2

HTTCLK0

+3.3V_RUN

PCI

HTT

Hi-Z

Hi-Z

X/3 X/6

60.00

30.00

73.12

36.56

66.66

33.33

33.33

66.66

66.66

33.33 48.00

4

VDDA

GNDA

+3.3V_CLK_VDDA

50

49

CPUCLK_R

56

CPUCLK_R#

55

52

51

PCIE_LOM

16

PCIE_LOM#

17

NB_GFX

41

NB_GFX#

40

37

36

35

34

30

31

18

19

20

21

NB_SBLINK

24

NB_SBLINK#

25

PCIE_MINI2

26

PCIE_MINI2#

27

47

46

43

42

PCIE_SB

12

PCIE_SB#

13

LOM_CLKREQ#

57

32

33

7

CLK_SB

6

FS1

63

FS0

64

FS2

62

HTREFCLK

59

COMMENT

USB

Reserved

48.00

Reserved

48.00

Reserved

48.00

48.00

Reserved

Reserved

48.00

48.00

Reserved

Normal ATHLON64 operation

5

12

12

R526 33R526 33

R514 33R514 33

R511 33R511 33

R117 33R117 33

R523 33R523 33

CLK_SB_48M

CLK_SIO_14M

CLK_NB_14M

CLK_SB_14M

CLK_HTREF_66M

5

C602

C602

C172

C172

0.1U

0.1U

0.047U

0.047U

0402

0402

16

16

%

%

10

10

±10

±10

0603

0603

X7R

X7R

R525 47.5_FR525 47.5_F

1 2

R528 47.5_FR528 47.5_F

1 2

R533 33R533 33

R536 33R536 33

R542 33R542 33

R546 33R546 33

R539 33R539 33

R543 33R543 33

R547 33R547 33

R549 33R549 33

R529 33R529 33

R531 33R531 33

12

C589

C589

10P_NC

10P_NC

50V

50V

220 ohm @100MHz

300mA current rating

12

C603

C603

22U

22U

0805

0805

6.3

6.3

LOM_CLKREQ# 30

MINI2CLK_REQ# 35

MINI1CLK_REQ#

R522

R522

49.9_F

49.9_F

1 2

12

C127

C127

10P_NC

10P_NC

50V

50V

6

L66

L66

BLM15AG221SN1D

BLM15AG221SN1D

CLK_SB_48M 24

CLK_SIO_14M 38

CLK_NB_14M 14

CLK_SB_14M 24

CLK_HTREF_66M 14

12

C580

C580

10P_NC

10P_NC

50V

50V

6

+3.3V_RUN

R527 261_FR527 261_F

1 2

R532 49.9_FR532 49.9_F

R530 49.9_FR530 49.9_F

12

12

12

12

C587

C587

C596

C596

10P_NC

10P_NC

10P_NC

10P_NC

50V

50V

50V

50V

7

R537 49.9_FR537 49.9_F

R544 49.9_FR544 49.9_F

R548 49.9_FR548 49.9_F

R540 49.9_FR540 49.9_F

R550 49.9_FR550 49.9_F

12

12

12

12

FS0

FS1

FS2

Title

Title

Title

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MGD 3A

MGD 3A

MGD 3A

Date: Sheet

Date: Sheet

Date: Sheet

12

R518 8.2KR518 8.2K

1 2

R515 8.2KR515 8.2K

1 2

R114 8.2KR114 8.2K

1 2

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

7

R545 49.9_FR545 49.9_F

R541 49.9_FR541 49.9_F

12

R534 49.9_FR534 49.9_F

12

12

R512

R512

2.2K

2.2K

1 2

R513

R513

2.2K_NC

2.2K_NC

1 2

8

CPU_CLK 10

CPU_CLK# 10

CLK_PCIE_LOM 30

CLK_PCIE_LOM# 30

CLK_NB_GFX 14

CLK_NB_GFX# 14

CLK_NB_SBLINK 14

CLK_NB_SBLINK# 14

CLK_PCIE_MINI2 35

CLK_PCIE_MINI2# 35

CLK_PCIE_SB 23

CLK_PCIE_SB# 23

+3.3V_RUN

R510

R510

2.2K

2.2K

1 2

1 2

R509

R509

2.2K_NC

2.2K_NC

1 2

1 2

of

of

of

789Thursday, March 01, 2007

789Thursday, March 01, 2007

789Thursday, March 01, 2007

8

R113

R113

2.2K

2.2K

R116

R116

2.2K_NC

2.2K_NC

Page 8

5

C502

C101

C101

4.7U

4.7U

10

10

0805

0805

1 2

X7R

D D

X7R

C502

4.7U

4.7U

10

10

0805

0805

1 2

X7R

X7R

C501

C501

4.7U

4.7U

10

10

0805

0805

1 2

X7R

X7R

4

+1.2V_RUN

C95

C95

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C512

C512

0.22U

0.22U

10

10

0603

0603

X7R

X7R

12

C93

C93

180P_50V

180P_50V

12

C518

C518

180P_50V

180P_50V

3

2

1

LAYOUT: Place bypass cap on topside of board

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

PROCESSOR HYPERTRANSPORT INTERFACE

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

C C

HT_CADIN1512

HT_CADIN#1512

HT_CADIN1412

HT_CADIN#1412

HT_CADIN1312

HT_CADIN#1312

HT_CADIN1212

HT_CADIN#1212

HT_CADIN1112

HT_CADIN#1112

HT_CADIN1012

HT_CADIN#1012

HT_CADIN912

HT_CADIN#912

HT_CADIN812

HT_CADIN#812

B B

+1.2V_RUN

R472 51R472 51

A A

R473 51R473 51

HT_CADIN712

HT_CADIN#712

HT_CADIN612

HT_CADIN#612

HT_CADIN512

HT_CADIN#512

HT_CADIN412

HT_CADIN#412

HT_CADIN312

HT_CADIN#312

HT_CADIN212

HT_CADIN#212

HT_CADIN112

HT_CADIN#112

HT_CADIN012

HT_CADIN#012

HT_CLKIN112

HT_CLKIN#112

HT_CLKIN012

HT_CLKIN#012

1 2

1 2

HT_CTLIN012

HT_CTLIN#012

Place R472 and R473 less

than 100mils from CPU

5

+1.2V_RUN

U7AU7A

D4

D3

D2

D1

N5

P5

M3

M4

L5

M5

K3

K4

H3

H4

G5

H5

F3

F4

E5

F5

N3

N2

L1

M1

L3

L2

J1

K1

G1

H1

G3

G2

E1

F1

E3

E2

J5

K5

J3

J2

P3

P4

N1

P1

VLDT_A3

VLDT_A2

VLDT_A1

VLDT_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Athlon 64 S1

Processor Socket

4

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

+1.2V_RUN

AE5

AE4

AE3

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

HT_CPU_CTLOUT1HT_CTLIN1

T5

HT_CPU_CTLOUT#1HT_CTLIN#1

R5

R2

R3

HT_CADOUT15 12

HT_CADOUT#15 12

HT_CADOUT14 12

HT_CADOUT#14 12

HT_CADOUT13 12

HT_CADOUT#13 12

HT_CADOUT12 12

HT_CADOUT#12 12

HT_CADOUT11 12

HT_CADOUT#11 12

HT_CADOUT10 12

HT_CADOUT#10 12

HT_CADOUT9 12

HT_CADOUT#9 12

HT_CADOUT8 12

HT_CADOUT#8 12

HT_CADOUT7 12

HT_CADOUT#7 12

HT_CADOUT6 12

HT_CADOUT#6 12

HT_CADOUT5 12

HT_CADOUT#5 12

HT_CADOUT4 12

HT_CADOUT#4 12

HT_CADOUT3 12

HT_CADOUT#3 12

HT_CADOUT2 12

HT_CADOUT#2 12

HT_CADOUT1 12

HT_CADOUT#1 12

HT_CADOUT0 12

HT_CADOUT#0 12

HT_CLKOUT1 12

HT_CLKOUT#1 12

HT_CLKOUT0 12

HT_CLKOUT#0 12

T97T97

T99T99

HT_CTLOUT0 12

HT_CTLOUT#0 12

Place T97 and T99 less

than 100mils from CPU

3

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

COMPUTER

ATHLON64 HT I/F

ATHLON64 HT I/F

ATHLON64 HT I/F

MGD 1A

MGD 1A

MGD 1A

889Thursday, March 01, 2007

889Thursday, March 01, 2007

889Thursday, March 01, 2007

of

of

1

of

Page 9

A

B

C

D

E

Notes for the SODIMM locations:

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

CPU_VTT_SUS_SENSE

should be routed as 10mils

and 10mils spacing from any

4 4

for +0.9V_DDR_VTT

feedback

KEEP TRACE TO RESISTORS LESS

THAN 1.5" FROM CPU PIN

3 3

2 2

1 1

adjacent signals in X, Y, Z

directions.

+1.8V_SUS

R95

R95

39.2

39.2

1%

1%

R100

R100

39.2

39.2

1%

1%

DDR_A_MA[0..15]17,18

DDR_CS3_DIMMA#17,18

DDR_CS2_DIMMA#17,18

DDR_CS1_DIMMA#17,18

DDR_CS0_DIMMA#17,18

DDR_CS3_DIMMB#17,18

DDR_CS2_DIMMB#17,18

DDR_CS1_DIMMB#17,18

DDR_CS0_DIMMB#17,18

DDR_CKE3_DIMMB17,18

DDR_CKE2_DIMMB17,18

DDR_CKE1_DIMMA17,18

DDR_CKE0_DIMMA17,18

CPU_VTT_SUS_SENSE

T113T113

M_ZN

M_ZP

DDR_A_BS217,18

DDR_A_BS117,18

DDR_A_BS017,18

DDR_A_RAS#17,18

DDR_A_CAS#17,18

DDR_A_WE#17,18

+0.9V_CPU_M_VREF_SUS

12

C583

C583

0.1U_10V

0.1U_10V

W17

AE10

AF10

W24

DDR_A_MA15

DDR_A_MA14

DDR_A_MA13

DDR_A_MA12

DDR_A_MA11

DDR_A_MA10

DDR_A_MA9

DDR_A_MA8

DDR_A_MA7

DDR_A_MA6

DDR_A_MA5

DDR_A_MA4

DDR_A_MA3

DDR_A_MA2

DDR_A_MA1

DDR_A_MA0

Y10

V19

J22

V22

T19

Y26

J24

U23

H26

J23

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

K22

R20

T22

T20

U20

U21

12

C581

C581

0.1U_10V

0.1U_10V

12

C582

C582

1000p_50V

1000p_50V

U7B

U7B

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

+1.8V_SUS

R508

R508

1K_F_0603

1K_F_0603

1 2

1 2

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 S1

Processor Socket

+V_DDR_VREF

1 2

R505 0_0603_NCR505 0_0603_NC

R506

R506

1K_F_0603

1K_F_0603

Place Capacitors for +0.9V_CPU_M_VREF_SUS < 1" from the RS690.

+0.9V_CPU_M_VREF_SUS trace length < 6", trace width > 15mils and

20mils spacing from any adjacent signals in X, Y, Z directions.

+0.9V_DDR_VTT

D10

VTT1

C10

VTT2

B10

VTT3

AD10

VTT4

W10

VTT5

AC10

VTT6

AB10

VTT7

AA10

VTT8

A10

VTT9

Y16

MA0_CLK_H2

AA16

MA0_CLK_L2

E16

MA0_CLK_H1

F16

MA0_CLK_L1

AF18

MB0_CLK_H2

AF17

MB0_CLK_L2

A17

MB0_CLK_H1

A18

MB0_CLK_L1

W23

MB0_ODT1

W26

MB0_ODT0

V20

MA0_ODT1

U19

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

DDR_B_MA15

J25

DDR_B_MA14

J26

DDR_B_MA13

W25

DDR_B_MA12

L23

DDR_B_MA11

L25

DDR_B_MA10

U25

DDR_B_MA9

L24

DDR_B_MA8

M26

DDR_B_MA7

L26

DDR_B_MA6

N23

DDR_B_MA5

N24

DDR_B_MA4

N25

DDR_B_MA3

N26

DDR_B_MA2

P24

DDR_B_MA1

P26

DDR_B_MA0

T24

K26

T26

U26

U24

V26

U22

DDR_B_BS2 17,18

DDR_B_BS1 17,18

DDR_B_BS0 17,18

DDR_B_RAS# 17,18

DDR_B_CAS# 17,18

DDR_B_WE# 17,18

M_CLK_DDR1 17

M_CLK_DDR#1 17

M_CLK_DDR0 17

M_CLK_DDR#0 17

M_CLK_DDR3 17

M_CLK_DDR#3 17

M_CLK_DDR2 17

M_CLK_DDR#2 17

M_ODT3 17,18

M_ODT2 17,18

M_ODT1 17,18

M_ODT0 17,18

DDR_B_MA[0..15] 17,18

DIMMA = Far = Bottom

DIMMB = Near = Top

Processor DDR2 Memory Interface

U7C

DDR_B_D[0..63]17

To SODIMM socket B (Near/TOP)

DDR_B_DM[0..7]17 DDR_A_DM[0..7] 17

DDR_B_DQS[0..7]17

DDR_B_DQS#[0..7]17

DDR_B_D63

DDR_B_D62

DDR_B_D61

DDR_B_D60

DDR_B_D59

DDR_B_D58

DDR_B_D57

DDR_B_D56

DDR_B_D55

DDR_B_D54

DDR_B_D53

DDR_B_D52

DDR_B_D51

DDR_B_D50

DDR_B_D49

DDR_B_D48

DDR_B_D47

DDR_B_D46

DDR_B_D45

DDR_B_D44

DDR_B_D43

DDR_B_D42

DDR_B_D41

DDR_B_D40

DDR_B_D39

DDR_B_D38

DDR_B_D37

DDR_B_D36

DDR_B_D35

DDR_B_D34

DDR_B_D33

DDR_B_D32

DDR_B_D31

DDR_B_D30

DDR_B_D29

DDR_B_D28

DDR_B_D27

DDR_B_D26

DDR_B_D25

DDR_B_D24

DDR_B_D23

DDR_B_D22

DDR_B_D21

DDR_B_D20

DDR_B_D19

DDR_B_D18

DDR_B_D17

DDR_B_D16

DDR_B_D15

DDR_B_D14

DDR_B_D13

DDR_B_D12

DDR_B_D11

DDR_B_D10

DDR_B_D9

DDR_B_D8

DDR_B_D7

DDR_B_D6

DDR_B_D5

DDR_B_D4

DDR_B_D3

DDR_B_D2

DDR_B_D1

DDR_B_D0

DDR_B_DQS7

DDR_B_DQS#7

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DM7

DDR_B_DM6

DDR_B_DM5

DDR_B_DM4

DDR_B_DM3

DDR_B_DM2

DDR_B_DM1

DDR_B_DM0

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

AD12

AC16

AE22

AB26

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

Y11

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

E25

A22

B16

A12

F26

E26

A24

A23

D16

C16

C12

B12

U7C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

Athlon 64 S1

Processor Socket

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

DDR: DATA

DDR: DATA

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

DDR_A_D63

DDR_A_D62

DDR_A_D61

DDR_A_D60

DDR_A_D59

DDR_A_D58

DDR_A_D57

DDR_A_D56

DDR_A_D55

DDR_A_D54

DDR_A_D53

DDR_A_D52

DDR_A_D51

DDR_A_D50

DDR_A_D49

DDR_A_D48

DDR_A_D47

DDR_A_D46

DDR_A_D45

DDR_A_D44

DDR_A_D43

DDR_A_D42

DDR_A_D41

DDR_A_D40

DDR_A_D39

DDR_A_D38

DDR_A_D37

DDR_A_D36

DDR_A_D35

DDR_A_D34

DDR_A_D33

DDR_A_D32

DDR_A_D31

DDR_A_D30

DDR_A_D29

DDR_A_D28

DDR_A_D27

DDR_A_D26

DDR_A_D25

DDR_A_D24

DDR_A_D23

DDR_A_D22

DDR_A_D21

DDR_A_D20

DDR_A_D19

DDR_A_D18

DDR_A_D17

DDR_A_D16

DDR_A_D15

DDR_A_D14

DDR_A_D13

DDR_A_D12

DDR_A_D11

DDR_A_D10

DDR_A_D9

DDR_A_D8

DDR_A_D7

DDR_A_D6

DDR_A_D5

DDR_A_D4

DDR_A_D3

DDR_A_D2

DDR_A_D1

DDR_A_D0

DDR_A_DM7

DDR_A_DM6

DDR_A_DM5

DDR_A_DM4

DDR_A_DM3

DDR_A_DM2

DDR_A_DM1

DDR_A_DM0

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS[0..7]17

DDR_A_DQS#[0..7]17

DDR_A_D[0..63] 17

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

To SODIMM socket A (Far/Bottom)

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

COMPUTER

ATHLON64 DDRII MEMORY

ATHLON64 DDRII MEMORY

ATHLON64 DDRII MEMORY

MGD 1A

MGD 1A

MGD 1A

E

989Thursday, March 01, 2007

989Thursday, March 01, 2007

989Thursday, March 01, 2007

of

of

of

Page 10

5

4

3

2

1

SB600 ONLY

CPU_PWRGD23

D D

LDT_STOP#14,23

C C

CPU_CLK7

CPU_CLK#7

B B

R499

R499

680

680

NOTE: R499 and C564 close to

JCPU pin F10

LDT_RST#23

C115 3900P_50VC115 3900P_50V

1 2

C111 3900P_50VC111 3900P_50V

1 2

1.KEEP TRACE TO RESISTOR LESS THAN 600MILS FROM CPU

PIN AND TRACE TO AC CAPS LESS THAN 1250MILS.

2. CPUCLK and CPUCLK# mismatch < 35 mils.

CPU_PROCHOT#

+1.8V_SUS

R85

R85

680

680

12

R485

R485

10K

10K

CPU_PWRGD

D31

D31

SDMK0340L-7-F

SDMK0340L-7-F

R668 20K

R668 20K

C564

C564

0.1U_16V_NC

0.1U_16V_NC

R88

R88

NOTE: Place R88 on the top of the board that is

680

680

iaccessible, and that shorting across this

resistor will toggle the hyper Transport reset

signal.

12

R91

R91

169_F

169_F

+1.8V_SUS

+3.3V_SUS

12

R479

R479

4.7K

4.7K

1 2

2

Q61

Q61

MMBT3904

MMBT3904

13

EC_CPU_PROCHOT# 39

1%

1%

C760

C760

47P

47P

NPO

NPO

50

50

LDT_RST#

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

R498 0_NCR498 0_NC

1 2

+1.8V_SUS+1.8V_RUN

R666

R666

0_NC

0_NC

U35

U35

2 4

NL17SZ17DFT2G

NL17SZ17DFT2G

3 5

R6670R667

0

LDT_STOP_R#LDT_STOP_R#

R669

R669

680_NC

680_NC

L65 ferrite bead with an approximate

impedance of 33 , a maximum DC

resistance of 0.025 ohm , and a current

rating of at least 3000mA.

+2.5V_RUN

12

C130

C130

+

+

100U

100U

6.3

6.3

3528

3528

Polymer

Polymer

±20

If AMD SI is not used, the SID pin can be left unconnected

and SIC should have a 300-Ω (±5%) pulldown to VSS.

Place R78 and R77 < 1.5".

Route CPU_HTREF1/0 with 5mils trace width and 10mils

spacing from other signals in X, Y, Z directions

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

If no use which Net

need pull-up or down

±20

To Power

R90 300_NCR90 300_NC

1 2

R86 300R86 300

1 2

R477 1K_FR477 1K_F

1 2

R497 510 1%R497 510 1%

R491 300R491 300

1 2

R84 300_NCR84 300_NC

1 2

R87 300_NCR87 300_NC

1 2

R92 300_NCR92 300_NC

1 2

R487 300_NCR487 300_NC

1 2

R480 300_NCR480 300_NC

1 2

R481 300_NCR481 300_NC

1 2

R484 510 1%R484 510 1%

R482 300R482 300

1 2

R483 300R483 300

1 2

L65

0603L65

0603

12

BLM18PG330SN1D

BLM18PG330SN1D

%

%

CPU_VDD_RUN_FB_H50

CPU_VDD_RUN_FB_L50

T117T117

T114T114

T31T31

T32T32

T115T115

T111T111

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

This trace should be kept at least 20 mils away from all other signals.

+2.5V_CPU_VDDA_RUN

+2.5V_CPU_VDDA_RUN

12

C526

C526

4.7U

4.7U

10

10

1 2

0805

0805

X7R

X7R

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_CLK

CPU_CLK#

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

+1.8V_SUS

+2.5V_CPU_VDDA_RUN

C525

C525

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C536

C536

3300P

3300P

50

50

%

%

±5

±5

1 2

LF (Lead Free)

LF (Lead Free)

0402

0402

X7R

X7R

The AMD SI feature has errata, and will not be plemented.

+1.2V_RUN

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

H_THERMDC19

H_THERMDA19

R80 300R80 300

R81 0_NCR81 0_NC

R78 44.2_FR78 44.2_F

1 2

R77 44.2_FR77 44.2_F

1 2

CPU_TEST25_H_BYPASSCLK_H

T119T119

CPU_TEST25_L_BYPASSCLK_L

T110T110

CPU_TEST19_PLLTEST0

T118T118

CPU_TEST18_PLLTEST1

T116T116

CPU_TEST17_BP3

T25T25

CPU_TEST16_BP2

T108T108

CPU_TEST15_BP1

T102T102

CPU_TEST14_BP0

T104T104

CPU_TEST12_SCANSHIFTENB

T106T106

1 2

Place C32< 100mils from CPU.

CPU_RSVD_MA0_CLK3_P

T134T134

CPU_RSVD_MA0_CLK3_N

T124T124

CPU_RSVD_MA0_CLK0_P

T129T129

CPU_RSVD_MA0_CLK0_N

T128T128

CPU_RSVD_MB0_CLK3_P

T130T130

CPU_RSVD_MB0_CLK3_N

T131T131

CPU_RSVD_MB0_CLK0_P

T122T122

CPU_RSVD_MB0_CLK0_N

T126T126

1 2

1 2

T103T103

T105T105

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

C531

C531

220P

220P

50V

50V

LDT_RST#

CPU_PWRGD

LDT_STOP_R#

CPU_HTREF1

CPU_HTREF0

H_THERMDC

H_THERMDA

CPU_SIC

CPU_SID

F8

F9

B7

A7

F10

AF4

AF5

P6

R6

F6

E6

W9

Y9

A9

A8

G10

AA9

AC9

AD9

AF9

E9

E8

G9

H10

AA7

C2

D7

E7

F7

C7

AC8

C3

AA6

W7

W8

Y6

AB6

P20

P19

N20

N19

R26

R25

P22

R22

U7D

U7D

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HT_REF1

HT_REF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

MISC

MISC

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

PSI_L

DBREQ_L

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

+1.8V_SUS

R478

R478

R486

R486

300

300

300

300

1 2

H_THERMTRIP#

AF6

CPU_PROCHOT#

AC7

A5

VID5

C6

VID4

A6

VID3

A4

VID2

C5

VID1

B5

VID0

AC6

A3

PSI_L is a Power Status Indicator signal. This signal is asserted when the

processor is in a low powerstate. PSI_L should be connected to the power

supply controller, if the controller supports “skipmode, or diode emulation

mode”. PSI_L is asserted by the processor during the C3 and S1 states.

E10

AE9

TDO

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

1 2

CPU_PRESENT#

T24T24

CPU_DBREQ#

CPU_TDO

CPU_TEST24_SCANCLK1

CPU_TEST23_TSTUPD

CPU_TEST22_SCANSHIFTEN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_MA_RESET#

CPU_MB_RESET#

CPU_RSVD_VIDSTRB1

CPU_RSVD_VIDSTRB0

CPU_RSVD_VDDNB_FB_P

CPU_RSVD_VDDNB_FB_N

CPU_RSVD_CORE_TYPE

CPU_RSVD_15

CPU_RSVD_16

CPU_RSVD_17

CPU_RSVD_18

CPU_RSVD_19

CPU_RSVD_20

H_THERMTRIP# 19

VID5 50

VID4 50

VID3 50

VID2 50

VID1 50

VID0 50

CPU_PSI# 50

R490 80.6_FR490 80.6_F

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

12

T29T29

T109T109

T30T30

T112T112

T27T27

T28T28

T26T26

T120T120

T123T123

T22T22

T23T23

T98T98

T100T100

T101T101

T133T133

T121T121

T132T132

T107T107

T125T125

T127T127

AMD NPT S1 SOCKET

12

12

12

12

12

R98 220_NCR98 220_NC

R101 220_NCR101 220_NC

R492 220_NCR492 220_NC

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

A A

+1.8V_SUS

R494 220_NCR494 220_NC

NOTE:HDT TERMINATION IS REQUIRED FOR REV.Ax SILICON ONLY.

R493 220_NCR493 220_NC

5

HDT CONNECTOR

JHDT1

JHDT1

GND1GND

Resreved13GND

Resreved25GND

DBREQ_L7GND

DBRDY9GND

TCK11GND

TMS13GND

15

TDI

GND

TRST_L17GND

TDO19GND

VDDIO121GND

VDDIO223RESET_L

GND

HDT conn_NC

HDT conn_NC

2

4

6

8

10

12

14

16

18

20

22

24

25

12

12

R64

R64

4.7K

4.7K

R66

R66

100K_NC

100K_NC

+1.8V_RUN+3.3V_RUN

MMBT3904

MMBT3904

12

R67

R67

4.7K

4.7K

2

Q13

Q13

LDT_RST#CPU_RESET#

13

4

3

Processor Socket

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

COMPUTER

ATHLON64 CTRL & DEBUG

ATHLON64 CTRL & DEBUG

ATHLON64 CTRL & DEBUG

MGD 3A

MGD 3A

MGD 3A

1

10 89Thursday, March 01, 2007

10 89Thursday, March 01, 2007

10 89Thursday, March 01, 2007

of

of

of

Page 11

5

4

3

2

1

+VCC_CORE

C539

C539

U7F

+VCC_CORE +VCC_CORE

D D

C C

B B

A1

AC4

AD2

M10

N11

R11

U11

U13

G4

H2

J9

J11

J13

K6

K10

K12

K14

L4

L7

L9

L11

L13

M2

M6

M8

N7

N9

P8

P10

R4

R7

R9

T2

T6

T8

T10

T12

T14

U7

U9

V6

V8

V10

U7E

U7E

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

POWER

POWER

Athlon 64 S1

Processor Socket

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

+1.8V_SUS

A26

AA4

AA11

AA13

AA15

AA17

AA19

AB2

AB7

AB9

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

H21

H23

F11

F13

F15

F17

F19

F21

F23

F25

B4

B6

B8

B9

D6

D8

D9

E4

F2

H7

H9

J4

U7F

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

Athlon 64 S1

Processor Socket

GROUND

GROUND

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

1

22U

22U

6.3

6.3

0805

0805

2

X6S

X6S

+VCC_CORE

C557

C557

1

22U

22U

6.3

6.3

0805

0805

2

X6S

X6S

+1.8V_SUS

C566

C566

1

22U

22U

6.3

6.3

0805

0805

2

X6S

X6S

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.8V_SUS

C186

C186

10U

10U

10

10

1 2

0805

0805

X7R

X7R

+1.8V_SUS

12

C594

C594

0.01U_16V

0.01U_16V

C117

C117

4.7U

4.7U

10

10

1 2

0805

0805

X7R

X7R

BOTTOMSIDE DECOUPLING

C538

1 2

C540

C540

4.7U

4.7U

10

10

0805

0805

X7R

X7R

1

2

1

2

1

2

1 2

12

C529

C529

22U

22U

6.3

6.3

0805

0805

X6S

X6S

C554

C554

22U

22U

6.3

6.3

0805

0805

X6S

X6S

C569

C569

22U

22U

6.3

6.3

0805

0805

X6S

X6S

C184

C184

10U

10U

10

10

0805

0805

X7R

X7R

C568 to be

placed as close

as possible to

the socket

C595

C595

0.01U_16V

0.01U_16V

C538

1

22U

22U

6.3

6.3

0805

0805

2

X6S

X6S

C560

C560

0.22U

0.22U

10

10

0603

0603

C571

C571

0.22U

0.22U

10

10

0603

0603

C187

C187

10U

10U

10

10

1 2

0805

0805

X7R

X7R

12

C568

C568

180P_50V

180P_50V

C552

C552

4.7U

4.7U

10

10

1 2

0805

0805

X7R

X7R

1

2

12

+0.9V_DDR_VTT

C121

C121

4.7U

4.7U

10

10

1 2

0805

0805

X7R

X7R

+0.9V_DDR_VTT

C530

C530

22U

22U

6.3

6.3

0805

0805

X6S

X6S

C528

C528

0.22U

0.22U

10

10

0603

0603

C576

C576

0.22U

0.22U

10

10

0603

0603

1 2

C597

C597

180P_50V

180P_50V

C185

C185

10U

10U

10

10

0805

0805

X7R

X7R

1

2

1

2

12

C567

C567

22U_NC

22U_NC

6.3

6.3

0805

0805

X6S

X6S

12

C565

C565

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C550

C550

22U

22U

6.3

6.3

0805

0805

X6S

X6S

C535

C535

0.01U_16V

0.01U_16V

C601

C601

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C598

C598

180P_50V

180P_50V

C549

C549

1

22U

22U

6.3

6.3

0805

0805

2

X6S

X6S

12

C558

C558

180P_50V

180P_50V

C597,and C598 to be

evenly spaced along the

VDDIO/VSS plane split

C544

C544

0.22U

0.22U

10

10

0603

0603

X7R

X7R

1

2

C543

C543

1

22U_NC

22U_NC

6.3

6.3

0805

0805

2

X6S

X6S

22uF/0805/6.3V/X6S

0.22uF/0603/10V/X7R

0.01uF/0402/16V/X7R

180pF/0402/50V/NPO

C593

C593

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C545

C545

22U

22U

6.3

6.3

0805

0805

X6S

X6S

C600

C600

0.22U

0.22U

10

10

0603

0603

X7R

X7R

22uF/0805/6.3V/X6S

10uF/0805/10V/X7R

4.7uF/0805/10V/X7R

0.22uF/0603/10V/X7R

0.01uF/0402/16V/X7R

1000pF/0402/50V/X7R

180pF/0402/50V/NPO

C551

C551

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C555

C555

0.22U

0.22U

10

10

0603

0603

X7R

X7R

C592

C592

0.22U

0.22U

10

10

0603

0603

X7R

X7R

12

C118

Athlon 64 S1g1

uPGA638

A A

Top View

C118

1000p_50V

1000p_50V

12

C546

C546

1000p_50V

1000p_50V

12

C120

C120

1000p_50V

1000p_50V

12

C556

C556

1000p_50V

1000p_50V

12

C119

C119

180P_50V

180P_50V

12

C553

C553

180P_50V

180P_50V

12

C562

C562

180P_50V

180P_50V

AF1

PROCESSOR POWER AND GROUND

5

4

3

2

12

C122

C122

180P_50V

180P_50V

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

COMPUTER

ATHLON64 PWR & GND

ATHLON64 PWR & GND

ATHLON64 PWR & GND

MGD 1A

MGD 1A

MGD 1A

1

of

of

of

11 89Thursday, March 01, 2007

11 89Thursday, March 01, 2007

11 89Thursday, March 01, 2007

Page 12

5

D D

4

3

2

1

Change Part Number

U5A

U5A

Rev.A12

P21

P22

P18

P19

M22

M21

M18

M19

L18

L19

G22

G21

J20

J21

F21

F22

N24

N25

L25

M24

K25

K24

J23

K23

G25

H24

F25

F24

E23

F23

E24

E25

L21

L22

J24

J25

N23

P23

HT_TXCALP

C25

HT_TXCALN

D24

Place R450 < 100 mils from U5A.C25 and U5A.D24

HT_CADIN15 8

HT_CADIN#15 8

HT_CADIN14 8

HT_CADIN#14 8

HT_CADIN13 8

HT_CADIN#13 8

HT_CADIN12 8

HT_CADIN#12 8

HT_CADIN11 8

HT_CADIN#11 8

HT_CADIN10 8

HT_CADIN#10 8

HT_CADIN9 8

HT_CADIN#9 8

HT_CADIN8 8

HT_CADIN#8 8

HT_CADIN7 8

HT_CADIN#7 8

HT_CADIN6 8

HT_CADIN#6 8

HT_CADIN5 8

HT_CADIN#5 8

HT_CADIN4 8

HT_CADIN#4 8

HT_CADIN3 8

HT_CADIN#3 8

HT_CADIN2 8

HT_CADIN#2 8

HT_CADIN1 8

HT_CADIN#1 8

HT_CADIN0 8

HT_CADIN#0 8

HT_CLKIN1 8

HT_CLKIN#1 8

HT_CLKIN0 8

HT_CLKIN#0 8

HT_CTLIN0 8

HT_CTLIN#0 8

R450 100_FR450 100_F

1 2

check

HT_CADOUT158

HT_CADOUT#158

HT_CADOUT148

HT_CADOUT#148

HT_CADOUT138

HT_CADOUT#138

HT_CADOUT128

HT_CADOUT#128

HT_CADOUT118

HT_CADOUT#118

HT_CADOUT108

HT_CADOUT#108

HT_CADOUT98

HT_CADOUT#98

HT_CADOUT88

C C

B B

+VDDHT_PKG

HT_CADOUT#88

HT_CADOUT78

HT_CADOUT#78

HT_CADOUT68

HT_CADOUT#68

HT_CADOUT58

HT_CADOUT#58

HT_CADOUT48

HT_CADOUT#48

HT_CADOUT38

HT_CADOUT#38

HT_CADOUT28

HT_CADOUT#28

HT_CADOUT18

HT_CADOUT#18

HT_CADOUT08

HT_CADOUT#08

HT_CLKOUT18

HT_CLKOUT#18

HT_CLKOUT08

HT_CLKOUT#08

HT_CTLOUT08

HT_CTLOUT#08

R429 49.9_FR429 49.9_F

1 2

R453 49.9_FR453 49.9_F

1 2

HT_RXCALP

HT_RXCALN

R19

R18

R21

R22

U22

U21

U18

U19

W19

W20

AC21

AB22

AB20

AA20

AA19

Y19

T24

R25

U25

U24

V23

U23

V24

V25

AA25

AA24

AB23

AA23

AB24

AB25

AC24

AC25

W21

W22

Y24

W25

P24

P25

A24

C24

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALP

HT_RXCALN

RS690T

RS690T

PART 1 OF 6

PART 1 OF 6

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCALP

HT_TXCALN

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

RS690T-HT LINK0 I/F

RS690T-HT LINK0 I/F

RS690T-HT LINK0 I/F

MGD 2A

MGD 2A

MGD 2A

12 89Thursday, March 01, 2007

12 89Thursday, March 01, 2007

12 89Thursday, March 01, 2007

of

of

1

of

Page 13

5

4

3

2

1

D D

U5B

U5B

G5

GFX_RX0P

G4

GFX_RX0N

J8

GFX_RX1P

J7

GFX_RX1N

J4

GFX_RX2P

J5

GFX_RX2N

L8

GFX_RX3P

L7

GFX_RX3N

L4

GFX_RX4P

L5

GFX_RX4N

M8

AB7

AB6

AC4

AD4

M7

M4

M5

P8

P7

R7

R8

U4

U5

P4

P5

R4

R5

V9

W9

Y4

Y5

W4

W5

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

NC_1

NC_2

RS690T

RS690T

C C

PCIE_NBRX_WLANTX_P135

WLAN <-----

GIGA LAN <-----

B B

PCIE_NBRX_WLANTX_N135

PCIE_NBRX_LOMTX_P230

PCIE_NBRX_LOMTX_N230

ALINK_NBRX_SBTX_P023

ALINK_NBRX_SBTX_N023

ALINK_NBRX_SBTX_P123

ALINK_NBRX_SBTX_N123

ALINK_NBRX_SBTX_P223

ALINK_NBRX_SBTX_N223

ALINK_NBRX_SBTX_P323

ALINK_NBRX_SBTX_N323

PART 2 OF 6

PART 2 OF 6

PCIE I/F

PCIE I/F

GFX

GFX

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

PCE_PCAL

PCE_NCAL

Rev.A12

DVI_C_TX2+

J1

DVI_C_TX2-

H2

DVI_C_TX1+

K2

DVI_C_TX1-

K1

DVI_C_TX0+

K3

DVI_C_TX0-

L3

DVI_C_CLK+

L1

DVI_C_CLK-

L2

N2

N1

P2

P1

P3

R3

R1

R2

V3

W3

PCIE_NBTX_WLANRX_P1

W1

PCIE_NBTX_WLANRX_N1

W2

PCIE_NBTX_LOMRX_P2

U2

PCIE_NBTX_LOMRX_N2

U1

V2

V1

ALINK_NBTX_SBRX_P0

AC1

ALINK_NBTX_SBRX_N0

AC2

ALINK_NBTX_SBRX_P1

AB1

ALINK_NBTX_SBRX_N1

AB2

ALINK_NBTX_SBRX_P2

AA1

ALINK_NBTX_SBRX_N2

AA2

ALINK_NBTX_SBRX_P3

Y2

ALINK_NBTX_SBRX_N3

Y3

PCE_PCAL

AE4

PCE_NCAL

AE3

Place near RS690T

C72 0.1U_16VC72 0.1U_16V

1 2

C71 0.1U_16VC71 0.1U_16V

1 2

C80 0.1U_16VC80 0.1U_16V

1 2

C75 0.1U_16VC75 0.1U_16V

1 2

C73 0.1U_16VC73 0.1U_16V

1 2

C74 0.1U_16VC74 0.1U_16V

1 2

C81 0.1U_16VC81 0.1U_16V

1 2

C82 0.1U_16VC82 0.1U_16V

1 2

C85 0.1U

C83 0.1U

C94 0.1U

C91 0.1U

C89 0.1U

C87 0.1U

R83 562_FR83 562_F

1 2

R82 2K_FR82 2K_F

1 2

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

DVI_TX2+

DVI_TX2DVI_TX1+

DVI_TX1DVI_TX0+

DVI_TX0DVI_CLK+

DVI_CLK-

10C85 0.1U

10

C86 0.1U

10C83 0.1U

10

C84 0.1U

10C94 0.1U

10

C96 0.1U

10C91 0.1U

10

C92 0.1U

10C89 0.1U

10

C90 0.1U

10C87 0.1U

10

C88 0.1U

+1.2V_VDDA12

DVI_TX2+

DVI_TX2-

DVI_TX1+

DVI_TX1-

DVI_TX0+

DVI_TX0DVI_CLK+

DVI_CLK-

No placement limitation,

minimum stub

R454 750 1%R454 750 1%

R452 750 1%R452 750 1%

R465 750 1%R465 750 1%

R460 750 1%R460 750 1%

R73 750 1%R73 750 1%

R74 750 1%R74 750 1%

R75 750 1%R75 750 1%

R76 750 1%R76 750 1%

Layout Note :750 ohm

resistors

are placed at the same

via as

the series capacitors

10C86 0.1U

10

X7R

X7R

10C84 0.1U

10

X7R

X7R

10C96 0.1U

10

X7R

X7R

10C92 0.1U

10

X7R

X7R

10C90 0.1U

10

X7R

X7R

10C88 0.1U

10

X7R

X7R

DVI_TX2+ 36

DVI_TX2- 36

DVI_TX1+ 36

DVI_TX1- 36

DVI_TX0+ 36

DVI_TX0- 36

DVI_CLK+ 36

DVI_CLK- 36

PCIE_NBTX_C_WLANRX_P1 35

PCIE_NBTX_C_WLANRX_N1 35

PCIE_NBTX_C_LOMRX_P2 30

PCIE_NBTX_C_LOMRX_N2 30

ALINK_NBTX_C_SBRX_P0 23

ALINK_NBTX_C_SBRX_N0 23

ALINK_NBTX_C_SBRX_P1 23

ALINK_NBTX_C_SBRX_N1 23

ALINK_NBTX_C_SBRX_P2 23

ALINK_NBTX_C_SBRX_N2 23

ALINK_NBTX_C_SBRX_P3 23

ALINK_NBTX_C_SBRX_N3 23

----->WLAN

----->GIGA LAN

A A

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

COMPUTER

RS485-PCIE LINK I/F

RS485-PCIE LINK I/F

RS485-PCIE LINK I/F

MGD 3A

MGD 3A

MGD 3A

1

of

of

of

13 89Thursday, March 01, 2007

13 89Thursday, March 01, 2007

13 89Thursday, March 01, 2007

Page 14

5

+1.8V_RUN

L19

L19

BLM15AG221SN1D

BLM15AG221SN1D

L18

D D

L18

BLM15AG221SN1D

BLM15AG221SN1D

+1.8V_AVDDQ

C52

C52

10U_10V_0805_NC

10U_10V_0805_NC

1 2

+1.8V_PLLVDD

C53

C53

10U_10V_0805_NC

10U_10V_0805_NC

1 2

12

C453

C453

2.2U_10V_0603

2.2U_10V_0603

12

C54

C54

2.2U_10V_0603

2.2U_10V_0603

TV_CVBS

TV_Y

TV_C

R435, R451 and R444

should be placed

close to NB

+1.8V_RUN

BLM15AG221SN1D

BLM15AG221SN1D

C C

LDT_STOP#10,23

+1.2V_VDDA12 +1.2V_PLLVDD12

L53

L53

BLM15AG221SN1D

BLM15AG221SN1D

B B

BMREQ#23

U32

U32

1

NC

2

A1

3

A A

A2

4

VSS

AT24C04N-10SU-2.7_NC

AT24C04N-10SU-2.7_NC

NOTE: ACCESS TO STRAP_DATA and I2C_CLK PINS IS MANDATORY.

L22

L22

+1.8V_HTPVDD

1 3

12

C451

C451

2.2U_10V_0603

2.2U_10V_0603

+3.3V_RUN

1 2

1 2

8

VCC

7

WP

6

SCL

5

SDA

5

C66

C66

10U_10V_0805_NC

10U_10V_0805_NC

1 2

+1.8V_RUN

R47

R47

4.7K

4.7K

1 2

2

Q12

Q12

MMBT3904

MMBT3904

+3.3V_RUN

R441

R441

10K_NC

10K_NC

C466

C466

15P_NC

15P_NC

+3.3V_RUN

12

C64

C64

4.7U_6.3V_0603

4.7U_6.3V_0603

+3.3V_RUN

R49

R49

10K

10K

1 2

LDT_STOP#_NB

R71 4.7KR71 4.7K

1 2

D23

D23

SDMK0340L-7-F_NC

SDMK0340L-7-F_NC

R434 0R434 0

12

R458

R458

R457

R457

10K_NC

10K_NC

2K_NC

2K_NC

1 2