Page 1

PRESTIGIO CAVALIERE 142

TECHNICAL SERVICE

MANUAL

Page 2

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Outline of the Prestigio Cavaliere 142

1.1 Introduction

This chapter provides the outline features and operation of the Cavaliere 142 including the BIOS

Setup program and other system options.

The Cavaliere 142 notebook offers the latest in advanced portable computing and multimedia

technology that even outperforms most desktop computers. It incorporates the latest Intel

Pentium-IV PGA Processor or Intel Celeron PGA processor and fully compatibles with an

entire library of PC software based on operating systems such as MS-DOS, Windows 2000 /

XP. It also runs on future versions of Windows. It comes with a built-in keyboard, glide pad

pointing device, sound system, PCMCIA slots, USB (Universal Serial Bus) port, IEEE 1394

port, advanced power management and more new multimedia features.

1.2 Feature Highlights

The Cavaliere 142 includes a variety of innovative features:

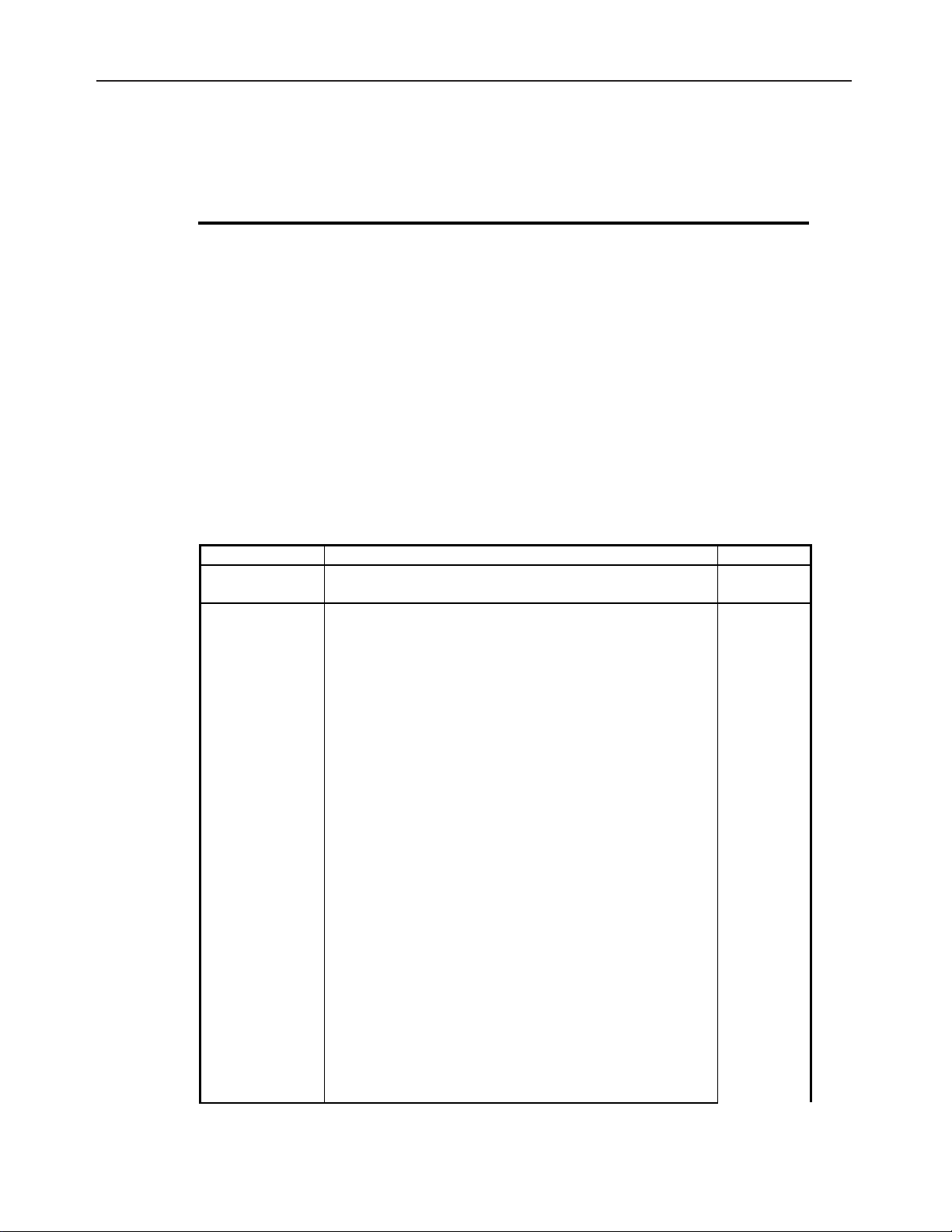

Category Specification Stepping

CPU Intel Pentium – M Processor

: Banias 1.3/1.4/1.5/1.6/1.7 GHZ

Core Logic

Intel Montara-GM (North Bridge) :

CPU(Banias) I/F

VGA Controller

LVDS I/F

DVOB&DVOC IF.

RGB analog I/F

200/266 DDR MEMORY I/F

Hub-Link I/F

Intel ICH4-M (South Bridge) :

Integrated Hub-Link I/F to connect with PCI

Bridge

Dual IDE Master/Slave Controller ,Integrated

DMA Controller

1.1/2.0 Universal Serial Bus Host Controller

Integrated 10/100M Fast Ethernet MAC

Controller

Integrated Audio Controller with AC97 V2.2

Interface

Advanced Power Management(ACPI)

RTC

Integrated PCI to LPC Bridge

Integrated Audio Controller with AC97 Interface

PCI Bus Interface (PCI 2.2 compliant)

GPIO

Advance PIC

1

Page 3

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

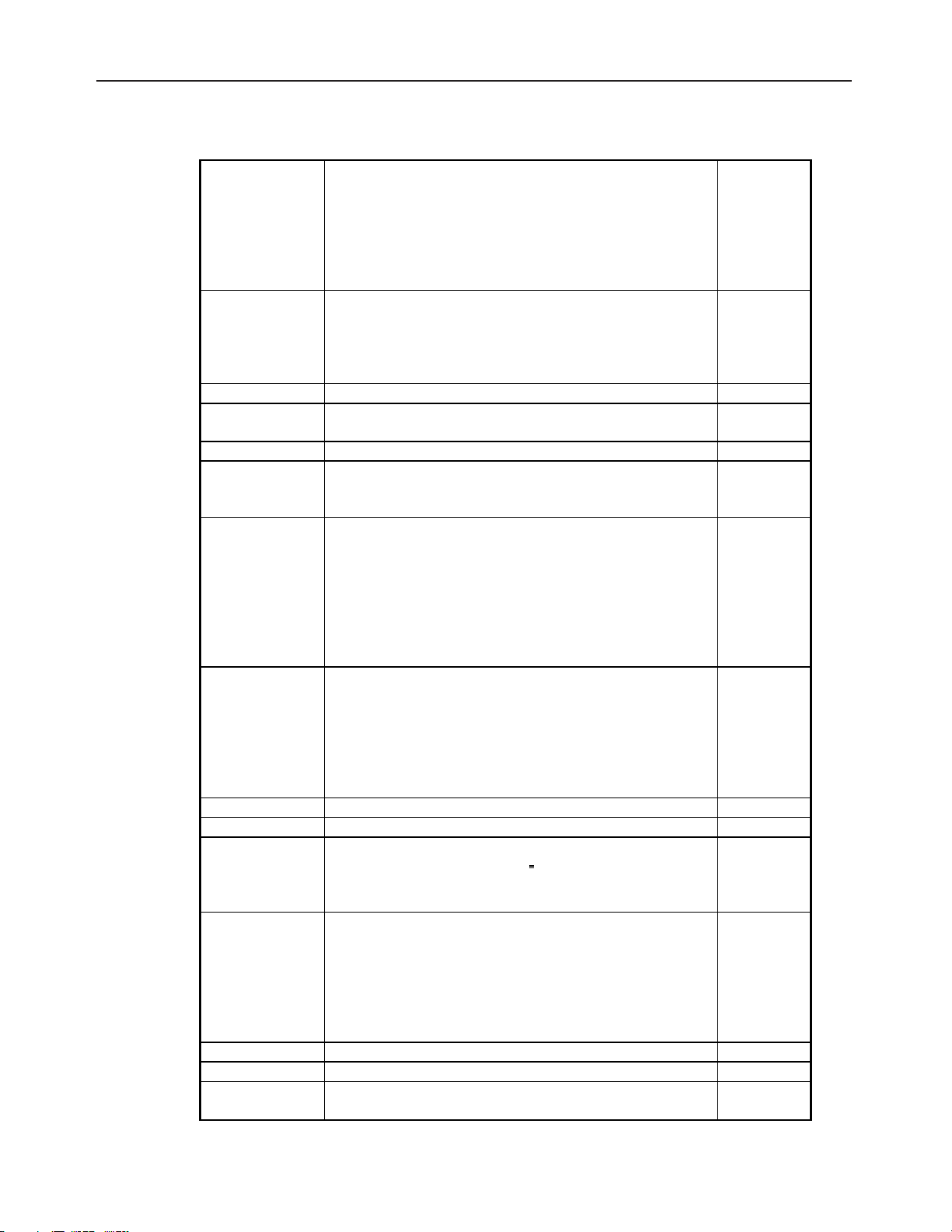

Cache Memory L1 Cache (Pentium Processor internal):

12KB code and 8KB data

8-way cache associativity provides

L2 Cache (Pentium Processor internal):

256KB Advanced Transfer Cache,8 way associativity

8-way set associative, 32-byte line size, 1 line per

sector

System Memory Expansion Memory: 2 SO-DIMM Slot (1.25”)

Size: 128/256/512MB/1G

Type: DDR DRAM, 3.3V

Data Path: 64Bit

Frequency : 266/200MHz

Refer to the Cavaliere 142 Key component list in detail.

BIOS ROM Flash ROM

1st Vendor : SST 49LF004A TSSOP Package 4Mbit LPC

flash ROM

2nd Vendor : <TBD>

4Mbit, 32 pin TSSOP package

PS: PLCC32 Package is just for DEBUG

Super I/O

RTC + NVRAM Integrated in South Bridge (Intel ICH4-M)

K/B Controller

PMU New PMU08

VGA Controller Embedded in Intel Montara-GM

VRAM Share system memory, UMA (using DVMT

TV out encoder None

CardBus

Controller

Sound

None

Real Time Clock with 256 byte extended

CMOS.

IBM AT Clock/Calendar/Alarm (14 Bytes)

Mitsubishi M38859 LPC KBC

Internal K/B, Touch Pad, External K/B or M/S

Supported A20Gate,firmware version 2.14

Mitsubishi M38859FFHP

Embedded Controller

High Performance and high quality 3D

accelerator

Integrated dual DVO bridge

Integrated LVDS Interface

Integrated RGB analog Interface

High performance 2D accelerator

Complete TV-OUT/Digital Flat Panel Solution

configuration)

RICOH R5C551 (PCI Card Bus controller)

PC/Card Bus Type II x1

Build in smart card (none)

AC’97 CODEC

Realtek ALC202

AC’97 Revision 2.2 Compliant

TBD

2

Page 4

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

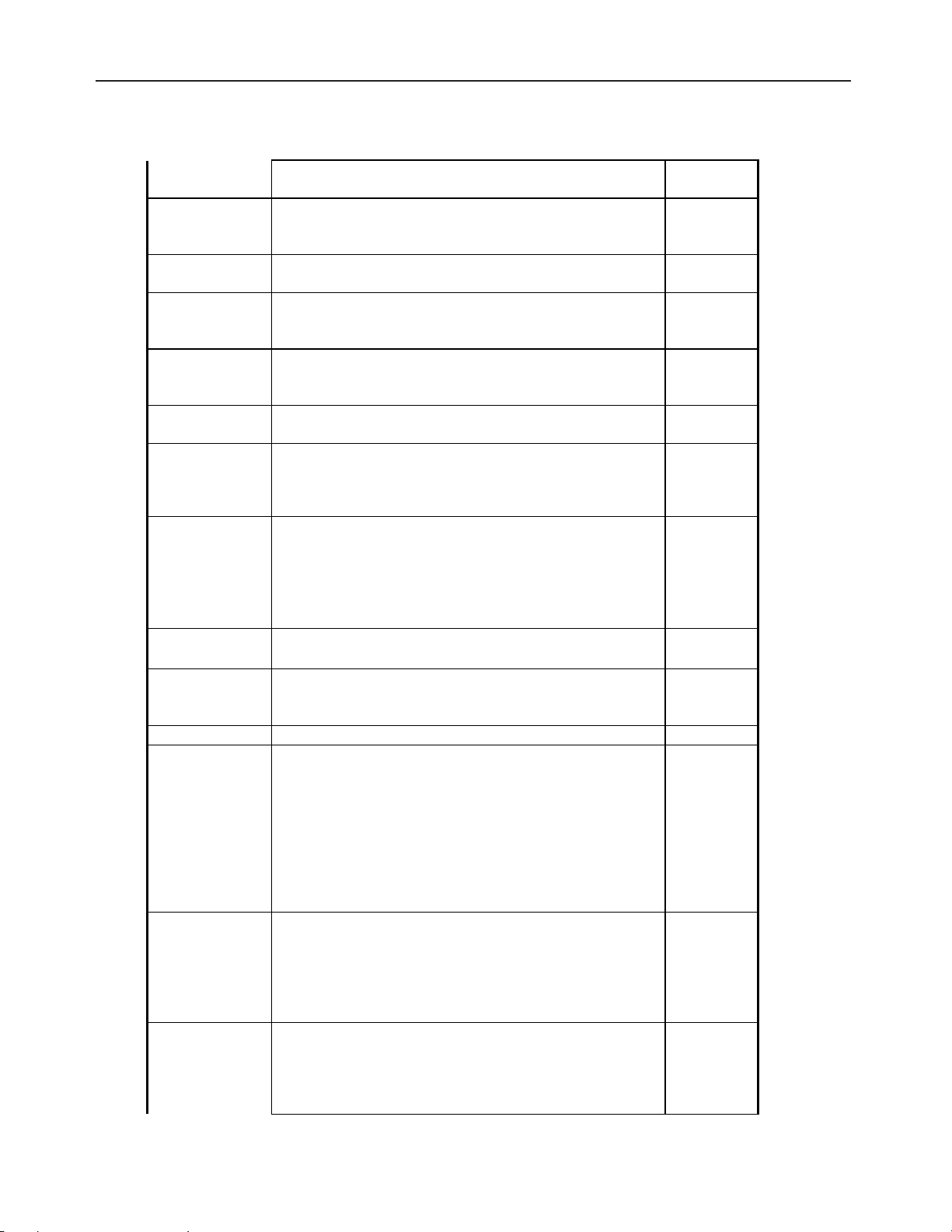

Modem Askey / Actiontec MDC modem

V.90, K56flex, ITU-T V.34, V.32, RJ11 Jack

TIA/EIA 602, V.42

ITU-T V.17, V.29, V.27ter, V.21 Ch2

TIA/EIA 578 Class1 FAX

Wake up on Ring

On board LAN Intel ICH4-M + Intel 82562EZ

Support LAN boot

Support for auto-negotiation (10BASE-T and 100BASETX)

Wake up On LAN

3com Combo

802.11b Support by Intel Calexico Mini-PCI Wireless LAN Card

<Design Ready Only>

1394 RICOH R5C551, support one port

Cellular I/F Support PDC/PIAFS/CdmaOne/Dupa(None) Support by

USB

Intel ICH4-M

IDE Interface

(Intel ICH4-M)

Printer Interface

Serial Interface

External PS/2

Port

(M38859)

Universal Serial

Bus

(Intel ICH4-M)

Infrared

Modem

LAN

Integrated in South Bridge Intel ICH4-M)

USB v.1.1 and Intel Universal HCI v.1.1 compatible

USB v.2.0 and Enhance Universal HCI v.2.0 compatible

Eighteen level (doublewords) data FIFO with full scatter

and gather capability

Root hub and four function ports

Integrated physical layer transceivers with optional overcurrent detection status on USB inputs

Fast IDE, 2 ports:

--Integrated multithreaded I/O link mastering with read

pipelined streaming

--Dual independent IDE channel each with 16 DW FIFO

--Native and compatibility mode

--PIO mode 0,1,2,3,4, and multiword DMA mode 0,1,2

--Ultra DMA 33/66/100

None

None

External Keyboard or PS/2 Mouse

Exclusively connected.

Can use both device by using branch

cable(option)

--Integrated multithreaded IO link mastering

--Dual independent OHCI controllers with root hub

--Support up to 6 USB ports

--Support legacy devices

--Over current detection equipped

--Option to separately configure each port as a wake-up

source

None

56K Data/Fax Modem (v.90)

10/100 Base TX LAN

Lan boot support and WFM 2.0

Cellular I/F

USB Cable

3

Page 5

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

LCD Panel 14.1” XGA

; Refer to the Cavaliere 142 Key component list in detail.

HDD 2.5 inch HDD (Standard)

9.5mm Height

; Refer to the Cavaliere 142 Key component list in detail.

CD-ROM

(Option)

FDD(None)

DVD

(Option)

CD-RW,Combo 9.5mm Height ,24X

Pointing Device Internal Touch Pad

Keyboard Internal Keyboard

Speakers (audio) Two built-in dynamic speakers

Microphone Built-in non-directional Back Electric Condenser

Buzzer Not support

Battery Battery Pack

RTC Battery Ni-MH Battery

DC/DC

Converter

CD-ROM (9.5mm Height)

; Refer to the Cavaliere 142 Key component list in detail.

USB FDD

3 mode Support

; Refer to the Cavaliere 142 Key component list in detail.

DVD

9.5mm Height ,8X

; Refer to the Cavaliere 142 Key component list in detail.

; Refer to the Cavaliere 142 Key component list in detail.

Pad SYNAPTICS : TM41P-351

Refer to the Cavaliere 142 Key component list in detail.

6.5mm Height, 3.0mm Stroke, 19mm Pitch

Vendor: ALLTOP

PAN-international

; Refer to the Cavaliere 142 Key component list in detail.

40 x 20mm, 1W 4Ω

Microphone

Panasonic : WM62PCX

Type: 8 cell Li-ION Battery with EEPROM

Voltage: 14.4V

Cell: 1800mAh Prisamtic

Method: 4P2S

Capacity: 3600mAh/52Wh Panasonic

Vendor: SANYO/ Panasonic

; Refer to the Cavaliere 142 Key component list in

detail.

Model: 3/V 15H

Voltage: 3.6V

Capacity: 15mAh

Vendor: VARTA

Daughter board

5.0 V Max 7.0 A

3.3 V Max 4.5 A

1.5V Max 2A

1.8V Max1A

.

4

Page 6

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

CPU Vcore 1.3V Max 32A

AC Adapter PA-1600-05 : Liteon

Input: AC100 – 240V, 50/60Hz

Output: 19V, 60W Peak 80W

Size: 110mm x 50mm x 29mm (Liteon)

Vendor: Liteon

Color : TBD

; Refer to the Cavaliere 142 Key component list in detail.

Size 310MM X 266MM X 27.3 MM (H)

SUPPORTS KENSINGTON LOCK

Weight AROUND 2.54 KG OR 4.5 LBS WITH 14.1” LCD SYSTEM

WITH HDD, FDD, CD-ROM AND ONE LI-ION BATTERY

PACK

Battery Handling

Category

Battery Charging

Max Change Current:

1.7A-1.75A±150mA

Battery Life

Save to RAM 1st Li-ion 3 Days TBD

Consumption power

Specification

Power On Li-ion 3.5 h

Power Off Li-ion 3.5 h

1st Li-ion 4.5 h TBD

Charge 24 h CMOS Battery

System on

Discharge 3 month

System off

Maximum 75W

Typical 25W TBD

MobileMark 10W Target

Remark

5

Page 7

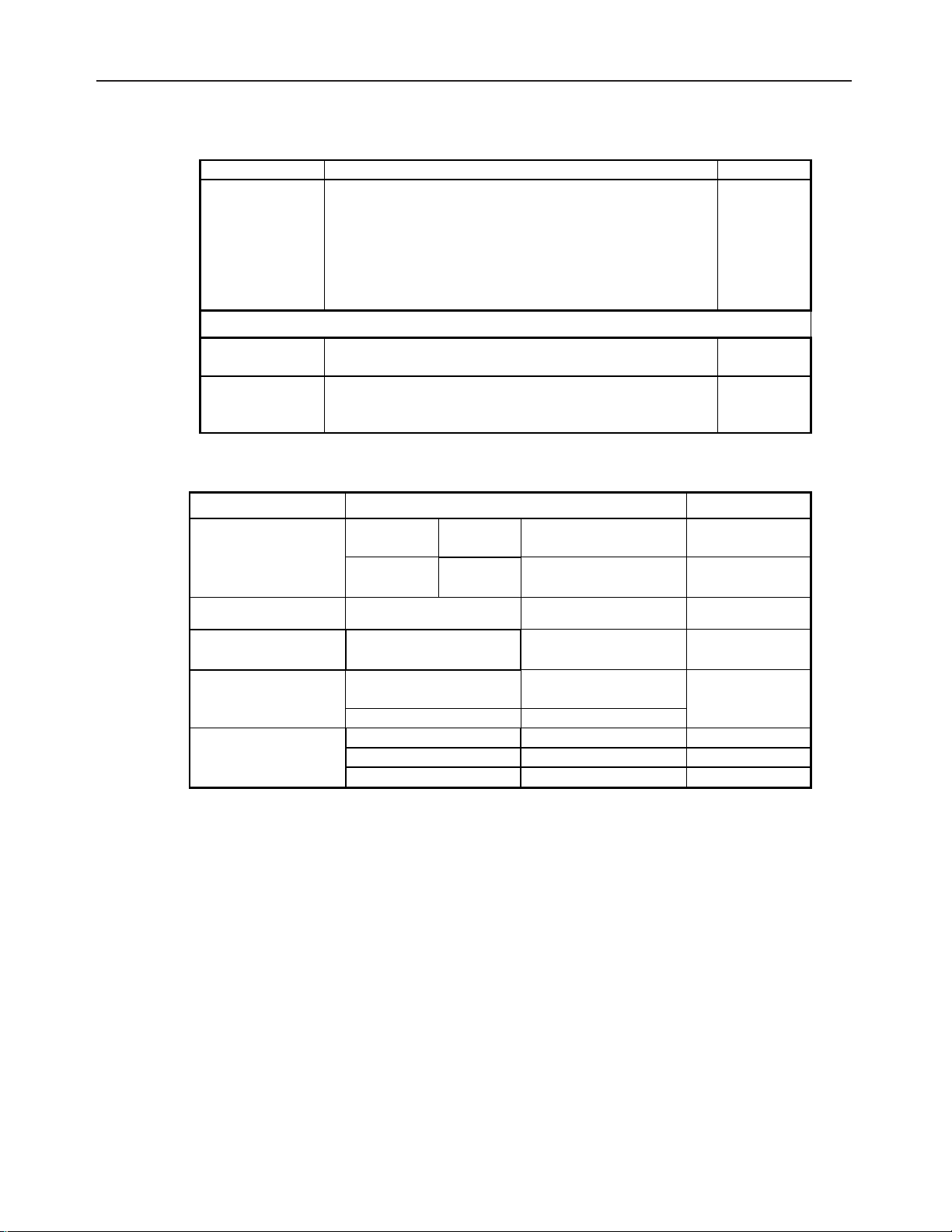

1.3 System Configuration

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

Figure 1-1 System Configuration Diagram

6

Page 8

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

1.4 Quick Tour of the Notebook

Please take a moment to become familiar with the location and purpose of every control, the

LED status panel, connectors and ports, which are illustrated in this section. It is

recommended to first go through the User Guide of the notebook, which is shipped together

with the notebook for information on how to operate its features.

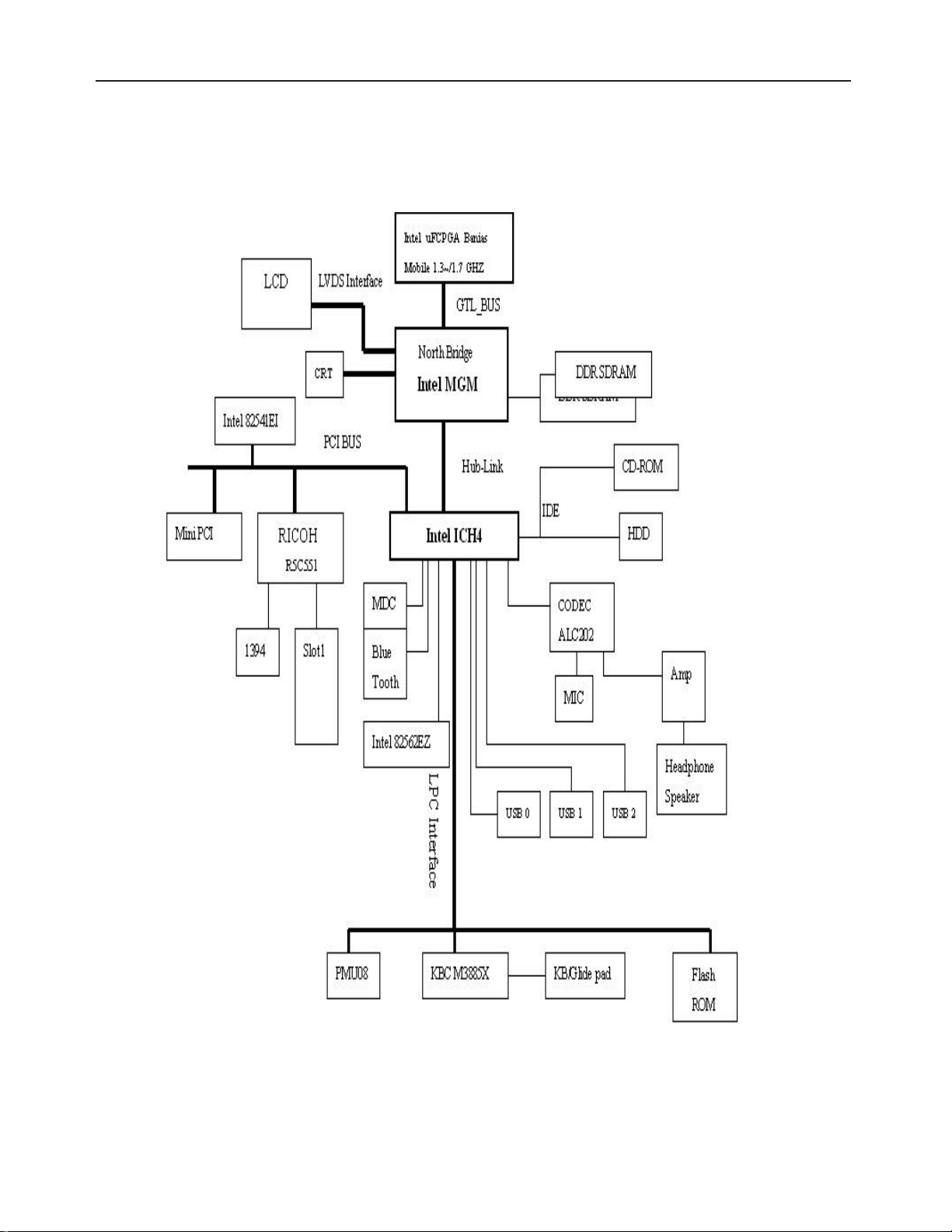

1.4.1 The Inside of the Notebook

To open the LCD cover of the notebook, find the cover latch located at the front center of the

LCD cover. Push the latch to the right to release and tilt the LCD cover up. Inside, you will

see the LCD display panel, keyboard, touch pad, status LED, and power switch.

Figure 1-2 The Inside side of the Notebook

Color LCD Display

Œ

Integrated Microphone

•

’

Power On/Resume

Button

Built-in Stereo Speakers

•

Status LED Indicator

•

➑

Keyboard

Easy Buttons

Ž

Built-in Stereo Speakers

‘

❾

Touchpad Pointing

Device

• Color LCD Display

The notebook computer comes with a color LCD that you can adjust for a

comfortable viewing position. The LCD can be 14.1" TFT color LVDS with

1024x768 XGA (Extended Graphics Array) or 1400x1050 SXGA+ resolution

panels. The features of the Color LCD Display are summarized as follows:

⇓ TFT color LVDS with 14.1" 1024x768 XGA or 14.1" 1400x1050

SXGA+ resolution panels.

⇓ Capable of displaying 16M colors (32-bit true color) on either size

panels.

⇓ LCD display control hot-keys allows you to adjust the brightness of the

LCD.

⇓ Simultaneous display capability for LCD and external desktop computer

monitor.

7

Page 9

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

• Built-in Stereo Speakers

Integrated left and right mini stereo speakers located at the bottom of LCD

panel for sound and audio output for your multimedia presentations or

listening pleasure.

• Easy Buttons

There are two easy buttons used for accessing Internet and e-mail functions

instantly and easily. Description of the easy buttons appears in the latter part

of this section.

• Integrated Microphone

Integrated mono microphone for instant voice recording and simultaneous

voice conversation.

• Status LED Indicator

Keeps you informed of your notebook computer’s current power status and

operating status. Description of the status icons appears in the latter part of

this section.

• Power On/Resume Button

Switches the computer power on and off, or resumes whenever it is in

Suspend mode.

• Keyboard

⇓ Standard QWERTY-key layout and full-sized 82/84 keys keyboard with

Windows system hot-keys, embedded numeric keypad, 7 hot keys,

inverted "T" cursor arrow keys, and separate page screen control keys.

⇓ Wide extra space below the keyboard panel for your wrist or palm to sit-

on comfortably during typing.

• Touchpad Pointing Device

Microsoft and IBM PS/2 mouse compatible with three select buttons as one

Scroll button and two Touchpad click buttons. These three buttons array

below the Glide pad. The middle one is located with the Scroll button that

lets you execute the scroll page function. The two click buttons located at

each side support tapping selection and dragging functions. These buttons

work like a standard computer mouse. Simply move your fingertip over the

Glide Pad to control the position of the cursor. Use the selection buttons

below the Glide Pad to select menu items.

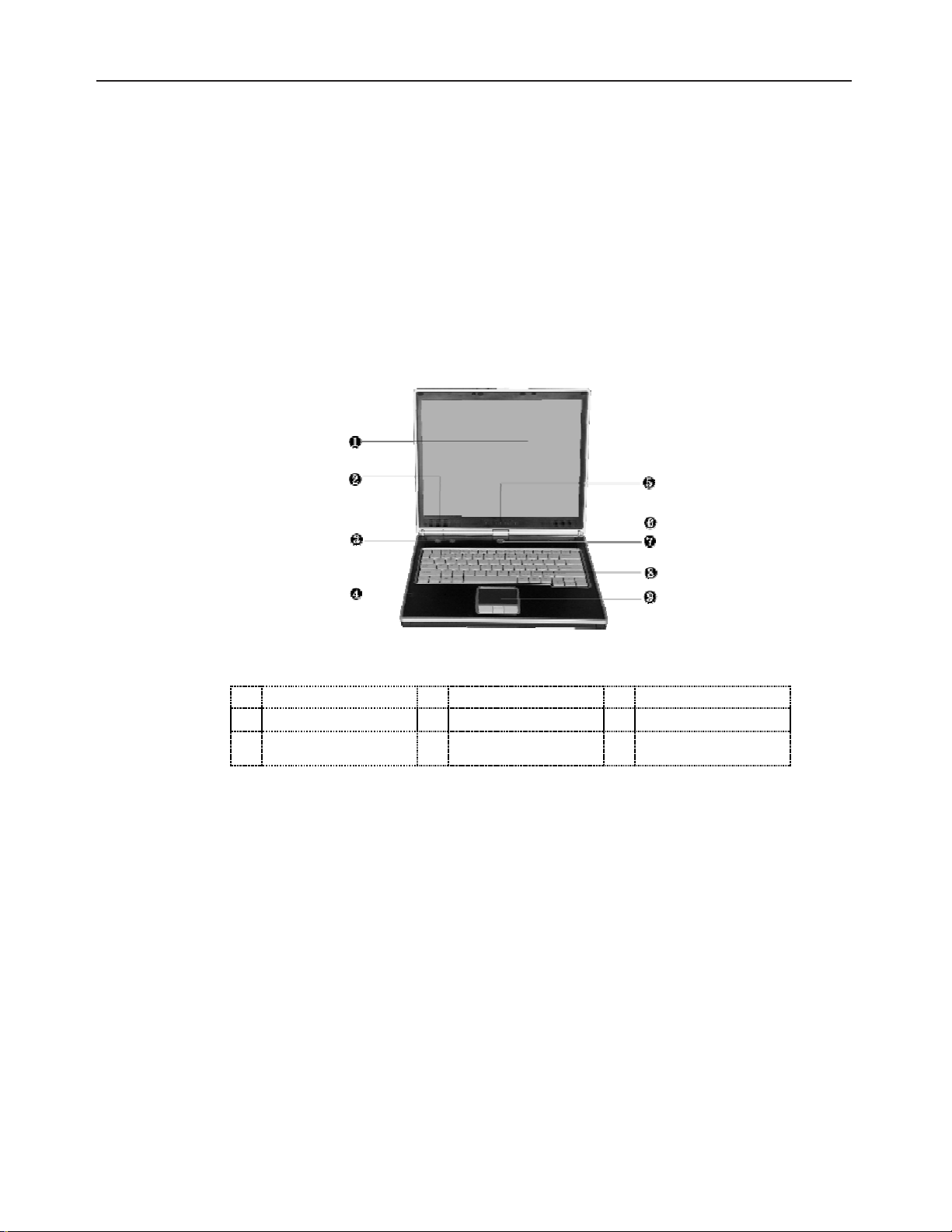

Easy Buttons

There are three easy buttons, two use for accessing Internet and e-mail functions instantly and

easily, the other one lets you define certain functions by yourself. Descriptions of the easy

buttons appear in the latter part of this section.

8

Page 10

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Internet Button

Œ

Figure 1-3 Easy Button

E-Mail Button

•

• Internet Button

This technology is designed specifically for providing a very convenient way

in connecting Internet only by pressing Internet button as shown in the

graphics. For more understanding and interesting, you can refer Section 2.5

to recognize the driver installation procedures in activating Internet button.

• E-mail Button

This is the most convenient way to access the outlook 98/2000/2002... utility

just by pressing this button. You can simplify several procedures in entering

into Outlook 98/2000/2002... environment.

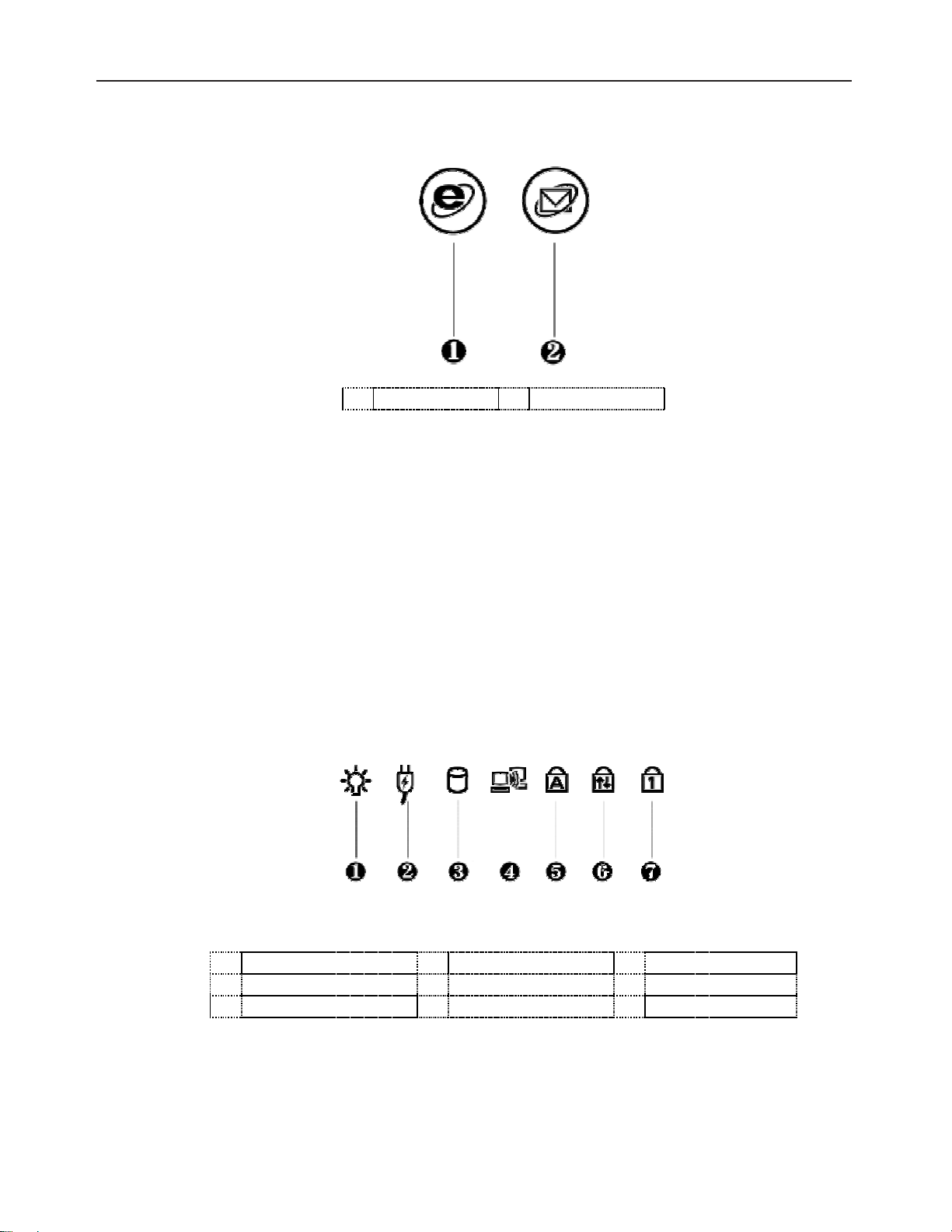

Status LED Indicator

Located just in front of the palmrest assembly, you will find three LEDs for the power and

battery charge status. These LEDs are positioned to be visible even if the LCD cover is closed.

Figure 1-4 Status LED Indicator

Power Indicator

Œ

Wireless LAN Access

•

❼

Num Lock

Battery charging LED

•

Caps Lock

•

Drive Access

Ž

Scroll Lock

‘

• Power Indicator

Lets you know that power to the system is turned on. This LED is positioned

so that you can see the power state whether the LCD panel is opened or

closed.

9

Page 11

⇓ Lights green when the system is powered on

⇓ Lights green blinking when the system is in Suspend to RAM.

• Battery Charging LED

Lights to indicate battery in charging status.

⇓ Lights green to indicate that the battery is in charging.

⇓ Lights off to indicate the battery is fully charged or no battery installed.

• Drive Access

When LED in green light indicates that the system is accessing either the

Hard Disk or Combo drive.

• Wireless LAN access

When LED in green light indicates that the wireless LAN module is installed.

When LED in blinking green light indicates that the system is accessing or

retrieving data by wireless device.

• Caps Lock

When LED in green light indicates that the Caps Lock key on the keyboard is

activated. When activated, all alphabet keys typed in will be in uppercase or

capital letters.

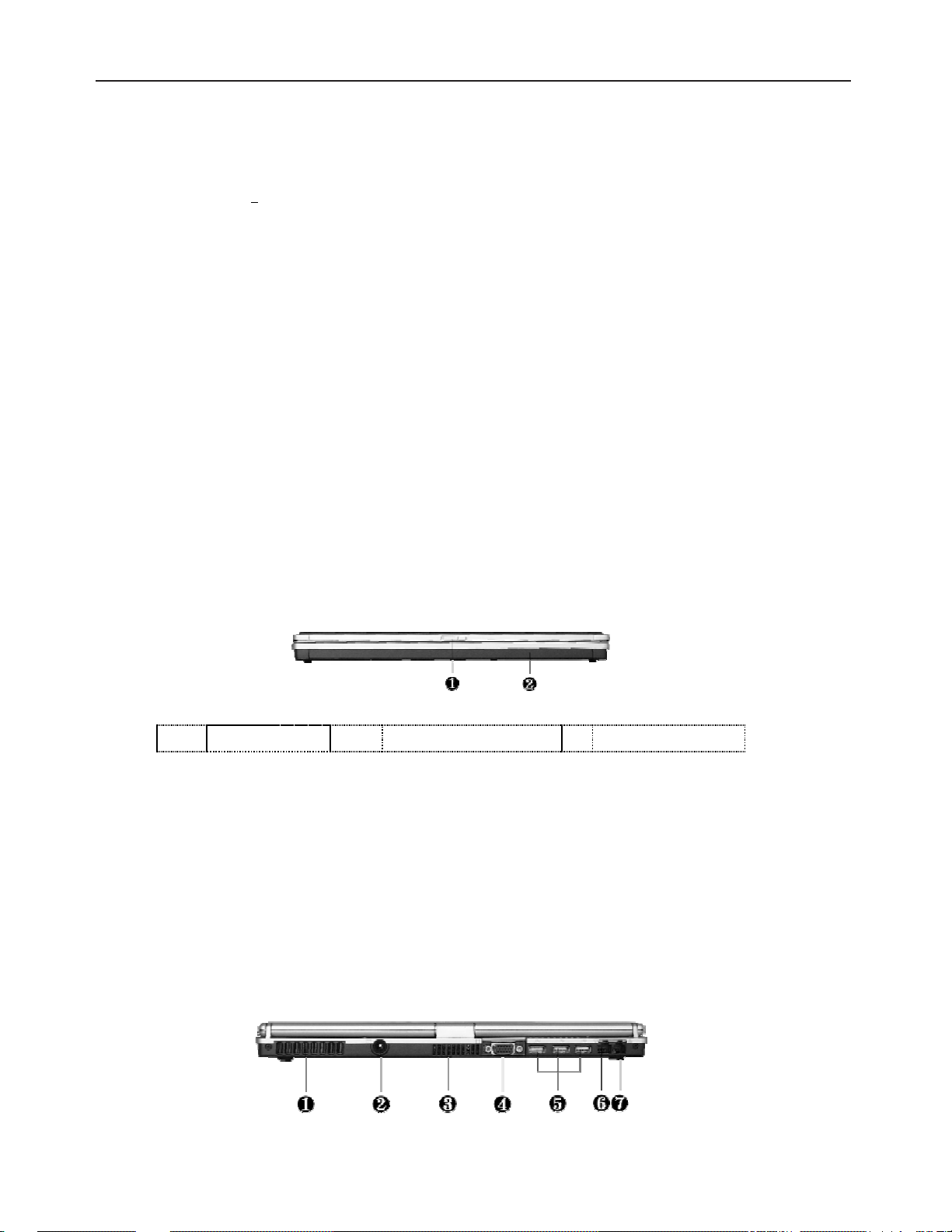

1.4.2 The Front Side of the Notebook

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

Œ

Cover Switch

Figure 1-8 The Front Side of the Notebook

•

Battery

• Cover Switch

The cover (LCD panel) is locked when it is closed. Slide the button right

aside to release the latch for opening the cover of the computer.

• Battery

The battery pack is inserted here.

•

1.4.3 The Rear Side of the Notebook

The rightt side of the notebook computer offers the features shown in the following figure.

10

Page 12

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Air-Outlet Vent

Œ

CRT Port

•

Modem Port

’

Figure 1-9 The Rear side of the Notebook

• Air-Outlet Vent

Emits the heat out of your computer and keeps it within operating

temperature.

• DC Power Port

Lets you connect the AC power adapter in supplying continuous power to

your notebook and recharging the battery.

• Air Inhalant

Inhale the air into your computer to keep it within operating temperature.

• Monitor Port

Lets you attach an external monitor or projector for wider display. You can

run the LCD display and the external monitor simultaneously or switch it to

monitor only using the display hot-key.

AC Power Port

•

USB Port

•

Air-Outlet Vent

Ž

LAN Port

‘

• USB Port

The Universal Serial Bus (USB) port allows you to connect up to 127 USBequipped peripheral devices (for example, printers, scanners and so on) to

your notebook computer.

• LAN Port

An internal 10Base-T/100Base-TX LAN module connects your computer to

other computers/networks through a local area network (LAN).

• Modem Port

A 56K internal fax/data modem is installed. It keeps you connected to the

outside world through networks.

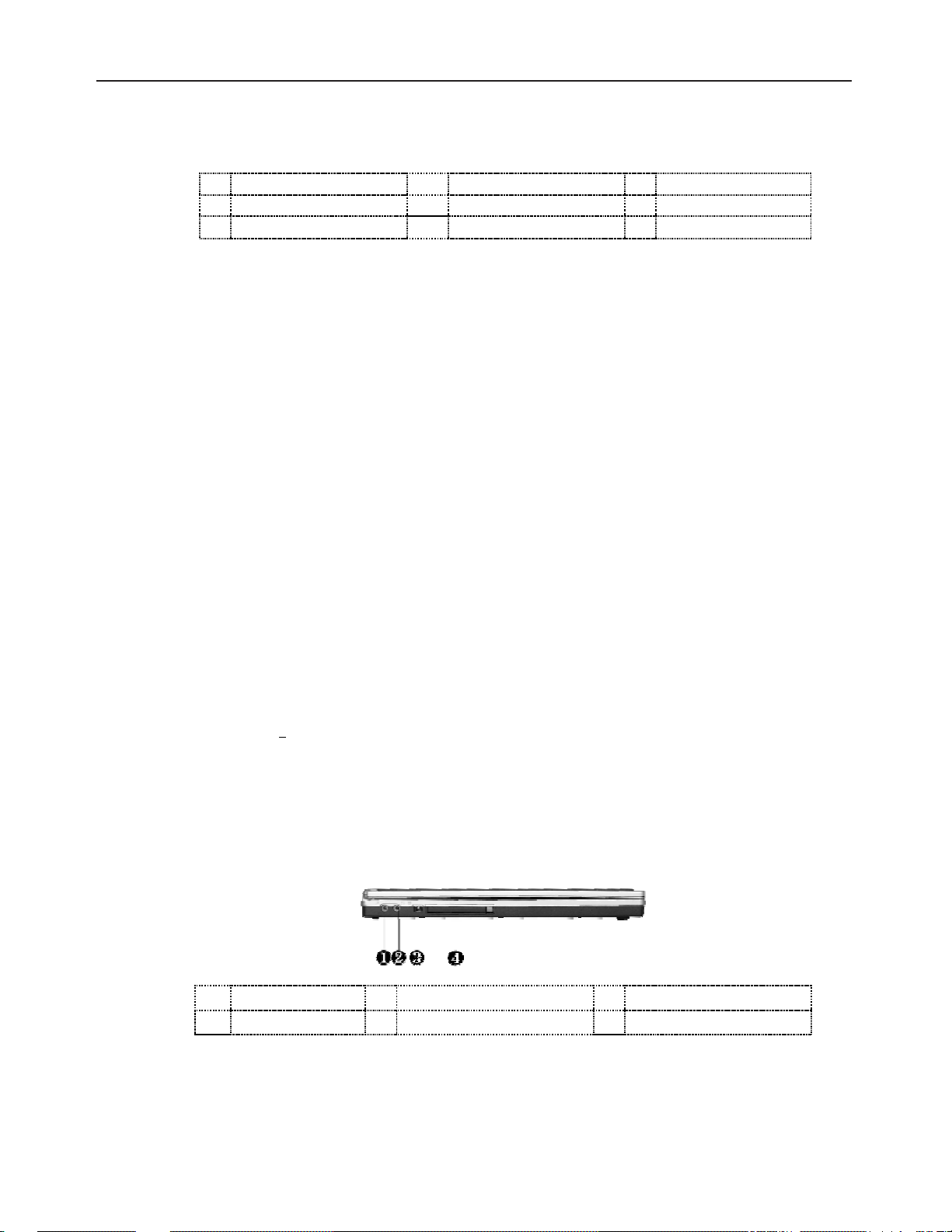

1.4.4 The Left Side of the Notebook

The left side of your notebook computer provides the features shown in the following figure.

To see all the ports located on the left side, you can open the cover first.

Microphone Jack

Œ

PC Card Slot

•

Headphone Jack

•

Figure 1-10 The Left side of the Notebook

Ž

IEEE 1394

11

Page 13

• Microphone Jack

Allows you to connect an external microphone for monophonic sound

recording directly into your notebook computer.

• Headphone Jack

Lets you plug in a stereo headphone, powered speakers, or earphone set with

1/8 inch phono plug for personal listening.

• IEEE 1394

IEEE 1394 port is a high speed I/O port that can transfer high levels of data

in real-time, such as external hard disk, Digital Video Camera.

• PC Card Slot

⇓ Lets you connect various PC cards such as memory card

⇓ Supports both 3V, 5V 32-bit CardBus and 16-bit PC cards.

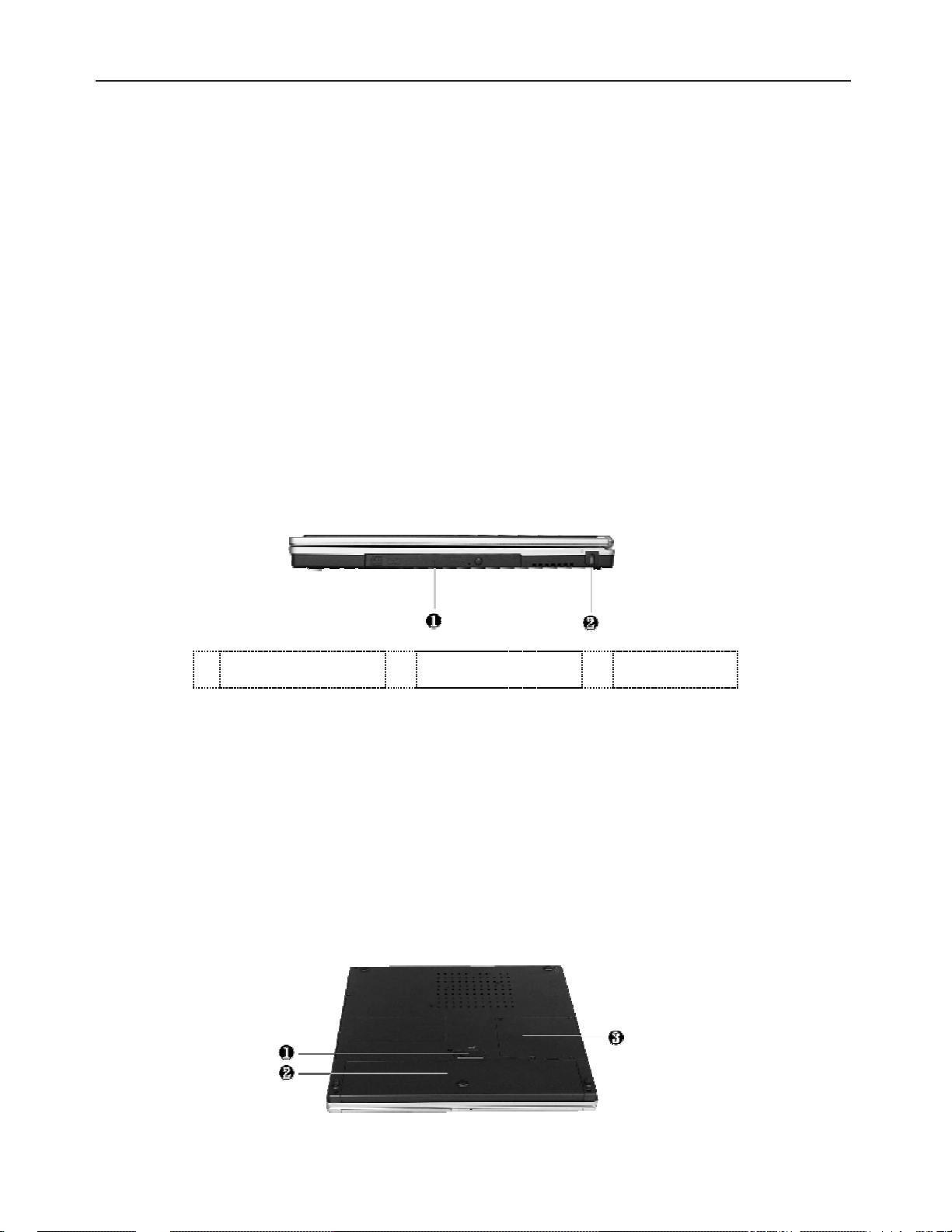

1.4.5 The Right Side of the Notebook

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

CD-ROM, DVD-ROM,

Œ

CD-RW module

Figure 1-11 The Right side of the Notebook

Locking Device

•

Keyhole

• CD-RW/DVD Combo Drive

Allows you to load and start programs from a compact disc (CD) or a digital

video disc (DVD) and play conventional audio CDs. It also can make CD by

using CD-R or CD-RW.

• Locking Device Keyhole

Lets you attach a Kensington security system or a compatible lock to secure

your notebook computer.

1.4.6 The Under Side of the Notebook

12

Page 14

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Battery Release Latch

Œ

•

Battery Bay

Hard Disk Compartment

Ž

Figure 1-12 Under Side of the Notebook

• Battery Release Latch

Push the latch to the left end to remove the battery pack.

• Battery Bay

Equipped with a choice of Lithium-Ion (Li-Ion) battery pack.

• Hard Disk Compartment

Open this cover of this compartment to replace with other Hard Disk Drive.

Please refer to Chapter 7 for how to replace it.

1.5 Notebook Accessories and System Options

It is also important to understand the accessories that come along with the notebook and the

options for fully utilizing the capabilities of the computer. This section describes briefly what

these accessories and options are.

1.5.1 AC Adapter and Power Cord

The AC Adapter supplies external power to your computer and at the same time charges the

internal battery pack. The AC adapter has an auto-switching design that can connect to any

100VAC ~ 240VAC power outlets. Connect the adapter to the AC wall outlet using the power

cord. You just change the power cord if you are going to use your notebook in other countries

with different connector outlets. When you connect the AC adapter, it charges the battery

whether or not the notebook computer is powered on. There is an LED on the AC adapter to

indicate if DC power is already available.

1.5.2 Battery Pack

Aside from the AC adapter, your computer can also be powered through the internal battery

pack. The battery pack uses rechargeable Lithium-Ion (Li-Ion) battery cells that provide long

computing hours when fully charged and power management enabled. You should always

leave the battery inside your computer even when using the AC adapter as it also acts as a

back-up power supply in case power from the AC adapter is cut off. It is also very important

to have the battery pack always charged to prevent battery cell degradation.

1.5.3 Internal Modem Module

The notebook allows you to insert a proprietary internal 56Kbps-modem card to the notebook

found on the underside of the notebook. The internal modem card supports only fax and data

communication and is V.90-compliant. You connect the telephone line to the RJ-11 jack

found on the rear side of the notebook.

1.5.4 Internal Ethernet LAN Module

This notebook comes with an optional 10Base-T/100Base-TX LAN module that supports data

transfer rates at 10Mbps and can be up to 100Mbps.

13

Page 15

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

1.5.5 DVD-ROM Drive

Other than the internal CD-ROM drive, the notebook also provides optional factory built-in

DVD-ROM drive. DVD-ROM drives are also backward compatible with CD-ROM, so you

can also use any audio CDs, video CDs, photo CDs, and CD-R. Using a software MPEG2/DVD program, the notebook can playback any commercial DVD movie titles.

1.6 System BIOS SETUP Program

Your computer is likely to have been properly setup and configured by your dealer prior to

delivery. However, you may find it necessary to use the computer’s BIOS (Basic InputOutput System) Setup program to change system configuration information, such as the

current date and time, or your hard disk drive type. The Setup program can be accessed when

you power on the system and pressing the <F2> function key.

The settings that you specify within the Setup program are recorded in a special area memory

called the CMOS RAM. This memory is backed up by a battery so that is will not be erased

when you turn off or reset the system. Whenever you turn on the computer, the system will

read the settings stored in the CMOS RAM and compare them to the equipment check

conducted during the Power On Self Test (POST). If an error occurs, an error message will be

displayed on the screen, and you will then be prompted to run the Setup Program.

As the POST (Power-On Self Test) executes during the boot up process, the screen will

display the following message:

Press <F2> to Enter SETUP

Press the <F2> key to run the BIOS Setup program. The BIOS Setup program is organized

into five menus which you can select using the ß and à keys. To move from one option to

another, you use the up and down arrow keys while using the <F5> and <F6>, or <+>and <->

keys to change the settings. On the right hand side of the screen are some brief help

descriptions of each item you want to change.

On the BIOS Setup program, you will find the following parts on the screen:

• Item Specific Help

The right side of the screen. This area describes each parameter and its

available settings.

• Menu Bar

The top line of the screen. Each of the five selections displays its own screen.

• Parameters

The left side of the screen. This area lists the parameters and their current

settings.

• Key Status Bar

The bottom part of the screen. These lines display the keys available to move

the cursor, select a particular function and so forth.

To exit the BIOS Setup program, simply press the <Esc> key and select from the Exit menu

whether you want to Save changes and exit; Discard Changes and exit.

14

Page 16

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

1.6.1 Using the Main Menu Setup

PhoenixBIOS Setup Utility

Main Advanced Security Boot Exit

Item Specific Help

System Time: [12 :00 :00] <Tab>, <Shift-Tab>,

System Date: [05/20/2002] or <Enter> selects

Language: [English (US)] field.

Legacy USB Support: [Enabled]

Internal HDD: [20004MB]

4

Internal DVD/CD-ROM Installed

Boot Display Device: [Both]

System Memory: 640 KB

Extended Memory: 114687 KB

CPU Type: Celeron (TM)

CPU Speed: 1066 MHz

BIOS Version: 0.3C-0022-0713

F1 Help

Esc Exit

Select Item -/+ Change Values F9 Setup Defaults

á â

Select Menu Enter Select 4Sub-Menu F10 Save and Exit

ßà

• System Time

Allows you to change the system time using the hour:minute:second format

of the computer.

Enter the current time for reach field and use the <Tab>, <Shift>+<Tab>, or

<Enter> key to move from one field or back to another.

You can also change the system time from your operating system.

• System Date

Allows you to set the system date using the month/date/year format.

Enter the current time for reach field and use the <Tab>, <Shift>+<Tab>, or

<Enter> key to move from one field or back to another.

You can also change the system time from your operating system.

• Language

This field shows the Language version of the BIOS.

• Legacy USB Support

Allow you to select the Enabled or Disabled option for enabled or disabled

the USB port.

15

Page 17

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

• Internal HDD

This field displays various parameters for the hard disk drive. If type [Auto]

is selected, the system automatically sets these parameters. If type [User] is

selected, Cylinders, Heads and Sectors can be edited.

• Internal DVD/CD-ROM

This field is for information only as the BIOS automatically detects the CD-

ROM/DVD-ROM.

• Boot Display Device

Lets you select the display device.

• System Memory

This field reports the amount of base (or conventional) memory found by the

BIOS during Power-On Self-Test (POST).

• Extended Memory

This field reports the amount of extended memory found by the BIOS during

Power-On Self-Test (POST).

• CPU Type

This field reports the CPU type information detected by the BIOS during

Power-On Self-Test (POST).

• CPU Speed

This field reports the CPU speed information detected by the BIOS during

Power-On Self-Test (POST).

• BIOS Version

This field is for information only as the BIOS displays the BIOS version

during the Power-On Self-Test (POST).

16

Page 18

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

1.6.2 Internal HDD Sub-Menu

PhoenixBIOS Setup Utility

Main Advanced Security Boot Exit

Internal HDD: [20004MB] Item Specific Help

Type: [Auto] User = you enter

parameters of hard Multi-Sector Transfers: [16 Sectors] disk drive installed

LBA Mode Control: [Enabled] at the Connection.

Auto = autotypes

32 Bit I/O: [Disabled] Hard-disk drive

Transfer Mode: [FPIO 4/DMA 2] installed here.

SMART Monitoring: Enabled None = no device is

Ultra DMA Mode: [Mode 5] installed here.

CD-ROM = a CD ROM drive is

installed here.

F1 Help

Esc Exit

Use the Type field to select the drive type installed. You can select different drive types as

CD-ROM, User, Auto, or None by pressing <Space> bar. Set this option to Auto so your

computer will automatically detect the drive type during power on. Set this option to None

when your computer is not installed any devices. Press <Esc> to return to the Main Menu.

Select Item -/+ Change Values F9 Setup Defaults

á â

Select Menu Enter Select 4Sub-Menu F10 Save and Exit

ßà

1.6.3 Using the Advanced CMOS Setup

PhoenixBIOS Setup Utility

Main Advanced Security Boot Exit

Item Specific Help

PS/2 Mouse: [Enabled] ‘Disabled’ prevents any

LCD Panel View Expansion: [Enabled] installed PS/2 mouse

from functioning, but

Silent Boot: [Enabled] frees up IRQ12.

Frame Buffer Size: [16 MB] 'Enabled' allows the

operating system to

I/O Device Configuration determine whether to

4

enable or disable the

mouse

F1 Help

Esc Exit

Select Item -/+ Change Values F9 Setup Defaults

á â

Select Menu Enter Select 4Sub-Menu F10 Save and Exit

ßà

17

Page 19

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

• PS/2 Mouse

[Enable] allows the OS to enable or disable the PS/2 mouse when it is

detected. [Disabled] prevents any installed PS/2 mouse from functioning.

• LCD Panel View Expansion

Expands or keeps the original LCD Screen View during the booting

procedure. Expands may get full screen LCD display, however, it degrades

the graphic/text quality.

• Silent Boot

Lets you specify the boot screen as Logo screen, POST screen, or Black

screen by choosing Enabled, Disabled, or Black option, respectively.

• Frame Buffer Size:

Lets you specify the sharing memory size of the Video chip from SDRAM.

The Default sharing size is 16MB. You should carefully specify the value,

since while the set value is too high, the memory size of your software

application will be reduced.

• I/O Device Configuration

Lets you configure input/output device such as Serial Port, Parallel Port, and

Floppy disk controller.

I/O Device Configuration Sub-Menu

Main Advanced Security Boot Exit

Serial port A: [Auto] Configure serial port A

Infrared port: [Enabled] using options:

Mode: [IrDA] [Disabled]

Base I/O address: [2E8 IRQ3] No configuration,

Parallel port: [Auto]

Mode: [EPP] [Enabled]

User configuration

Floppy disk controller: [Disabled]

[Auto]

BIOS or OS chooses

configuration

F1 Help

Esc Exit

á â

ßà

PhoenixBIOS Setup Utility

I/O Device Configuration Item Specific Help

Select Item -/+ Change Values F9 Setup Defaults

Select Menu Enter Select 4Sub-Menu F10 Save and Exit

• Serial port

You can select the Enabled, Disabled, or Auto option for enabled or disabled

the port, or automatically sensed by BIOS or OS. If you select Enable, you

also need to set the parameter of Base I/O address and IRQ.

18

Page 20

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

• Infrared port

You can select the Enabled, Disabled, or Auto option for enabled or disabled

the port, or automatically sensed by BIOS or OS. If you select Enable, you

also need to set the IR mode, Base I/O and IRQ for the IR device.

• Mode

This field is for information only as the BIOS displays the IR device type of

this notebook.

• Parallel port

Allows you to select the Enabled, Disabled, or Auto option for enabled or

disabled this port, or automatically sensed by BIOS or OS. If you select

Enable, you also need to set the parameter of Base I/O address.

• Mode

Allows you to select a parallel mode as Uni-directional, EPP or ECP when

the parallel port is configured.

• Floppy disk controller

This field is for information only as the BIOS displays the floppy disk

controller of this notebook.

19

Page 21

1.6.4 Security Menu Setup

Main Advanced Security Boot Exit

Item Specific Help

Set Supervisor Password [Enter] Supervisor Password

Set User Password [Enter] controls access to the

setup utility.

Password on boot [Disabled]

Fixed disk boot sector [Normal]

Diskette access [Supervisor]

F1 Help

Esc Exit

Select Item -/+ Change Values F9 Setup Defaults

á â

Select Menu Enter Select 4Sub-Menu F10 Save and Exit

ßà

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

PhoenixBIOS Setup Utility

• Set Supervisor Password

Supervisor password gives you the authority in accessing the setup utility.

You also need to enter this password in system booting and resuming from

suspend mode. When you press <Enter> in this field, the Set Supervisor

Password dialog box appears. Enter a new password with up to 8 alpha-

numeric characters, and then re-enter it for confirmation.

• Set User Password

This field is only available when Supervisor Password has set. Enter the user

password when boot the system or resume from suspend mode. But if the

Write Protect is set in the Fixed disk boot sector field, you should enter a

supervisor password to access the fixed disk when boot the system or resume

from suspend mode.

• Password on Boot

If you set this field to Enabled, your computer will always ask for the

password every time you boot your computer.

• Fixed Disk Boot Sector

If you set this field to Write Protect, the write protect boot sector on hard disk

will protect against viruses. In this situation, only the supervisor can access

the Boot Sector of fixed disk.

• Diskette Access

If you set this field to Supervisor, only the supervisor can access to the

diskette drives. If you set to User, both the supervisor and user can access to

the diskette drives.

20

Page 22

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

1.6.5 Using the Boot Setup

This item allows you to set the search drive sequence where the system will try to boot up

first.

PhoenixBIOS Setup Utility

Main Advanced Security Boot Exit

Item Specific Help

Removable Devices Use <á> or <â> to

+Hard Drive select a device, then

CD-ROM Drive press <+> or <-> to move

the device up or down

<Enter> expands or

collapses device.

F1 Help

Esc Exit

To select the boot device, you can use the up or down arrow key, then press <+> to move up

the device in the list or press <-> to move down the device in the list. To exit from this menu,

press <Esc>.

Select Item -/+ Change Values F9 Setup Defaults

á â

Select Menu Enter Select 4Sub-Menu F10 Save and Exit

ßà

1.6.6 How to Exit the Setup Program

There are two choices to escape from the Setup program.

PhoenixBIOS Setup Utility

Main Advanced Security Boot

Item Specific Help

Exit Saving Changes

Exit Discarding Changes

Load Setup Defaults changes to CMOS.

Discard Changes

Save Changes

Battery Refresh

F1 Help

Esc Exit

• Exit Saving Changes

Saves all changes to CMOS while running the BIOS setup program and exit

from the system setup program.

Select Item F5/F6 Change Values F9 Setup Defaults

á â

Select Menu Enter Execute Command F10 Save and Exit

ßà

Exit

Exit System Setup

and save your

21

Page 23

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

• Exit Discarding Changes

Allows you to discard all changes made while running the BIOS setup

program and exit from the system setup program.

• Load Setup Defaults

Lets you load the default values for all setup items.

• Discard Changes

Reverts to previously selected settings.

• Save Changes

Saves Setup data to CMOS.

• Battery Refresh

Conditions the battery so that the battery can be fully charged.

1.6.7 How to Upgrade the BIOS

Your computer uses EPROM Flash BIOS chip that allows you to easily upgrade the BIOS

program. When you update the BIOS, any customized settings you made are lost.

To upgrade the BIOS:

1. Insert the BIOS Update diskette into the diskette drive.

2. Power on the system with the diskette in the diskette drive.

3. On the DOS prompt, type the following command.

A:\>Phlash XXXXXX.ROM (BIOS filename) or

A:\>XXXXXX.BAT (Batch file for BIOS file)

4. Press <Enter> to run this BIOS utility. After the system has been successfully

run this program, a message similar to the following appears:

Flash memory has been successfully programmed, press any key to restart the

system. If the system does not restart, turn it off, then turn on again.

5. Press any key to restart this system.

Contact your dealer for the latest BIOS update file.

22

Page 24

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Installation and Upgrade

2.1 Overview

This chapter provides guidelines on installing the device drivers for the built-in features of the

Cavaliere 142. Most of the driver installation procedures mentioned here are only for and Windows

XP. This chapter also includes procedures on how to upgrade major internal system

components like CPU, memory, hard disk, and feature card modules.

2.2 Notebook Drivers and Utilities

The notebook requires several device drivers that you need to install and setup before you can

fully operate the notebook. These are:

• Intel 855GM VGA Driver – Windows XP

ALC201A Audio Driver – Windows XP

•

• Synatics Touch Pad Driver – Windows XP

Montara-GM Chipset Driver – Windows XP

•

• Easy Button PRO utility – Windows XP

Ambit MDC Modem – Windows XP

•

• Intel 562EZ LAN driver– Windows XP

Intel Wireless LAN driver – Windows XP

•

Audio Volume Status utility

•

Intel Wireless LAN utility

•

i Visit Prestigio website http://www.prestigio.com for the latest

driver updates.

2.2.1 Installing Windows XP from CD / DVD ROM

This section provides Windows XP installation guide from the CD-ROM or DVD-ROM

device.

Installing Windows XP from CD-ROM / DVD-ROM

To install Windows XP directly from your CD-ROM, insert the Windows XP installation CD

into CD-ROM drive with following the instructions on the screen to finish the installation.

You could go to Boot menu of BIOS setup menu to confirm the priority of boot device. Use

arrow key to select "ATAPI CD-ROM Drive", and then use "+" or "-" to move it to the top.

Go to Exit menu and select “Exit Saving Changes”.

2.2.2 Installing the VGA Device Driver

Your notebook computer uses the high-performance Intel 855GM VGA controller, which is

an AGP 4x video local bus, 2D/3D Graphic Engine. Following is the procedure for installing

the VGA Driver for Windows XP :

Installing VGA Driver for Windows XP

1. Click the Start button, then point to Settings, and click Control Panel.

23

Page 25

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

2. Double-click on the System icon, Hardware, and then click on the Device Manager

folder tab.

3. Under the Other Devices line, you will find the Video Controller (VGA compatible),

click Uninstall, OK, and then Scan for Hardware Changes buttons to appear the New

Hardware Found Message Box.

4. In the Found New Hardware Wizard message box which shows searching

Controller (VGA compatible) driver. Click Next to proceed the further step.

5. Select "Search for a suitable driver for my device", and click Next.

6. Tick on "Specify a location box", then, click Next and Browse buttons, and then

navigate to the VGA driver location as "\Drivers\ WinXP\VGA".

7. Click OK and Next to begin searching the driver. Click Next to continue installing the

driver.

1. Click

button to finish installing VGA driver and Click

Finish

to restart the computer.

Yes

Video

2.2.3 Installing the Audio Device Driver

Your notebook computer uses Realtek Audio controller.

Installing Audio Driver for Windows XP

1. Click the Start button, then point to Settings, and click Control Panel.

2. Double-click on the System icon, Hardware and then click on the Device Manager

folder tab.

3. Under the Other Devices line, you will find the Multimedia Audio Controller, click

Uninstall, OK, and then Scan for hardware changes buttons to appear the New

Hardware Found Message Box.

4. In the Found New Hardware Wizard message box which shows searching Multimedia

Audio Controller driver. Click Next to proceed to the next step.

5. Select

6. Tick on "Specify a location box", then click Next and Browse buttons, and navigate to

7. Click OK and Next to begin searching the driver. The Add New Hardware will found

8. Click Yes to continue installing the driver. Click Finish button to finish installing Audio

"Search for a suitable driver for my device"

the Audio driver location as "\Drivers\ WinXP\Audio".

Intel ALC201A Audio.

driver.

, and click

Next

.

2.2.4 Installing Touch Pad Driver

Following is the procedure for installing Synaptics touch pad driver.

Installing Touch Pad Driver for Windows XP

1. Boot Windows from your hard disk and insert the diskette containing touch pad driver.

2. Click the

navigate to the directory as "\Driver\WinXP\Touch Pad\setup.exe", path according to

your Operating System and run "Setup.exe".

3. Execute the setup program and then select the language for this installation. After that, a

Welcome dialog box appears.

4. Click Next continuously three times when the screen appears the Next button.

5. Click OK to restart your system.

button, then click

Start

. In the Run dialog box, click

Run

Browse

button and

2.2.5 Installing Internal Modem Device Driver

Your notebook computer may come with an optional internal modem. The internal modem is

a 56Kps V.90 Ambit MDC modem.

24

Page 26

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Installing Internal Modem for Windows XP

1. Boot Windows from your hard disk and insert the disc containing the Modem driver for

Windows.

2. Click the

and navigate to the directory as "\driver\WinXP\MODEM\setup.exe" where the

modem driver is located.

3. Click OK to process the installation of modem driver. Follow the instruction to finish

the installation.

4. With “Yes, I want to restart my computer now” selected, click Finish to complete the

modem installation.

button and then click

Start

. In the Run dialog box, click

Run

Browse

button

2.2.6 Installing Internal LAN Device Driver

Your notebook computer may come with an optional internal LAN, which uses the Intel

562EZ chip. Please follow the procedures below for installing the LAN driver:

Installing Internal LAN for Windows XP

1. Click the Start button, then point to Settings, and click Control Panel.

2. Double-click on the System icon, Hardware and then click on the Device Manager

folder tab.

3. Under the Other Devices line, you will find the Ethernet Controller, click Uninstall,

OK, then Scan for hardware changes buttons to appear the New Hardware Found

Message Box.

4. In the Found New Hardware Wizard message box which shows searching

Controller driver. Click Next to proceed to the next step.

5. Select "Search for a suitable driver for my device", and click Next.

6. Tick on "Specify a location box". Then, click Next and Browse buttons and navigate to

the LAN driver location as "\Drivers\WinXP\LAN". Click OK and Next to begin

searching the driver.

7. The Add New Hardware will found Intel Fast Ethernet . Click Yes to continue installing

the driver.

Click Finish button to finish installing LAN driver.

Ethernet

2.2.7 Installing EzButton Driver

Following is the procedure for installing Easy Button driver.

Installing Easy Button driver for Windows XP

1. Boot Windows from your hard disk and insert the disc containing the Easy Button driver.

2. Click the Start button, then click Run. In the Run dialog box, click Browse button and

navigate to the directory as "\Drivers\WinXP\Easy Button\Ez Button.exe".

3. Run the execution file for installing the Easy Button driver, and then click

complete the installing procedure.

Finish

after

25

Page 27

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

2.3 System Upgrades

This section provides an easy step in doing system upgrades for your notebook computer.

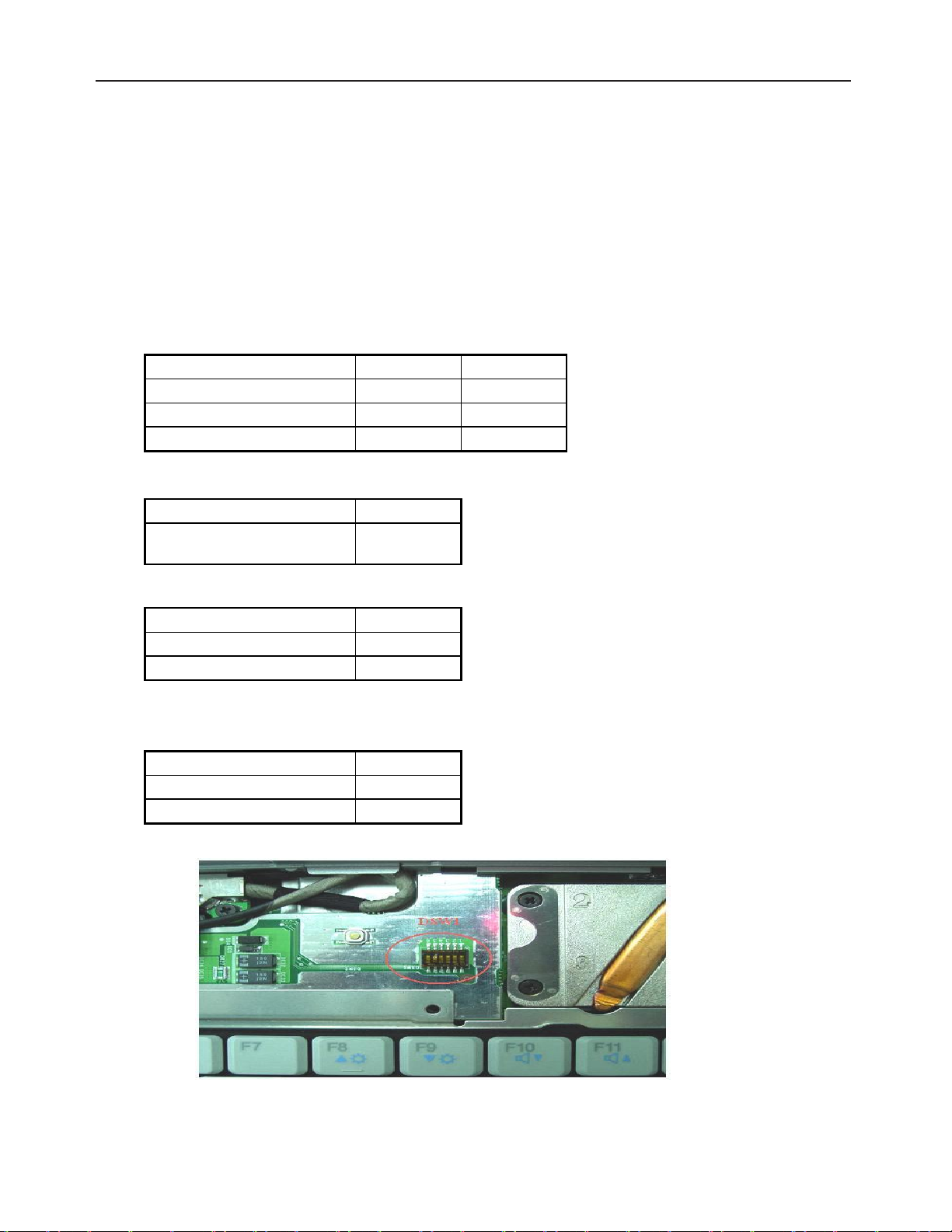

2.3.1 Jumper Settings

This section provides a jumper setting lists of configuring the notebook.

DSW1

Keyboard Type Select

K/B Type Pos #1 POS #2

US KEYBOARD OFF OFF

JP KEYBOARD ON OFF

UK KEYBOARD ON ON

DVDSEL

ODD select Pos #5

KME UJDA745 DVD/CD-RW

Combo

BIOS Crisis

BIOS Crisis Pos#4

Default OFF

BIOS Crisis ON

Password Override ( CMOS / RTC Data ) Jumper Setting

CMOS clear select Pos#6

RTC Battery Normal OFF

Clear (RTC) DATA ON

ON

Figure 2-1 Location of DSW1

26

Page 28

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

2.3.2 CPU Upgrade Procedure

The Cavaliere 142 features Mobile Intel Pentium-M FCPGA Processors. It is located on the upper

right side of the system motherboard.

How to Access the CPU Socket

To install or replace the CPU, follow the steps below:

1. Turn off the system and remove both AC adapter and the battery pack from the notebook

unit.

2. There are four screws on the bottom case and that should be removing as the picture

indicated.

Figure 2-2 Location of screws

3. Remove keyboard cover by gently bending it and sliding it towards in front of you.

Figure 2-3 Remove keyboard Cover

4. Lift the keyboard and tilt it towards the LCD panel.

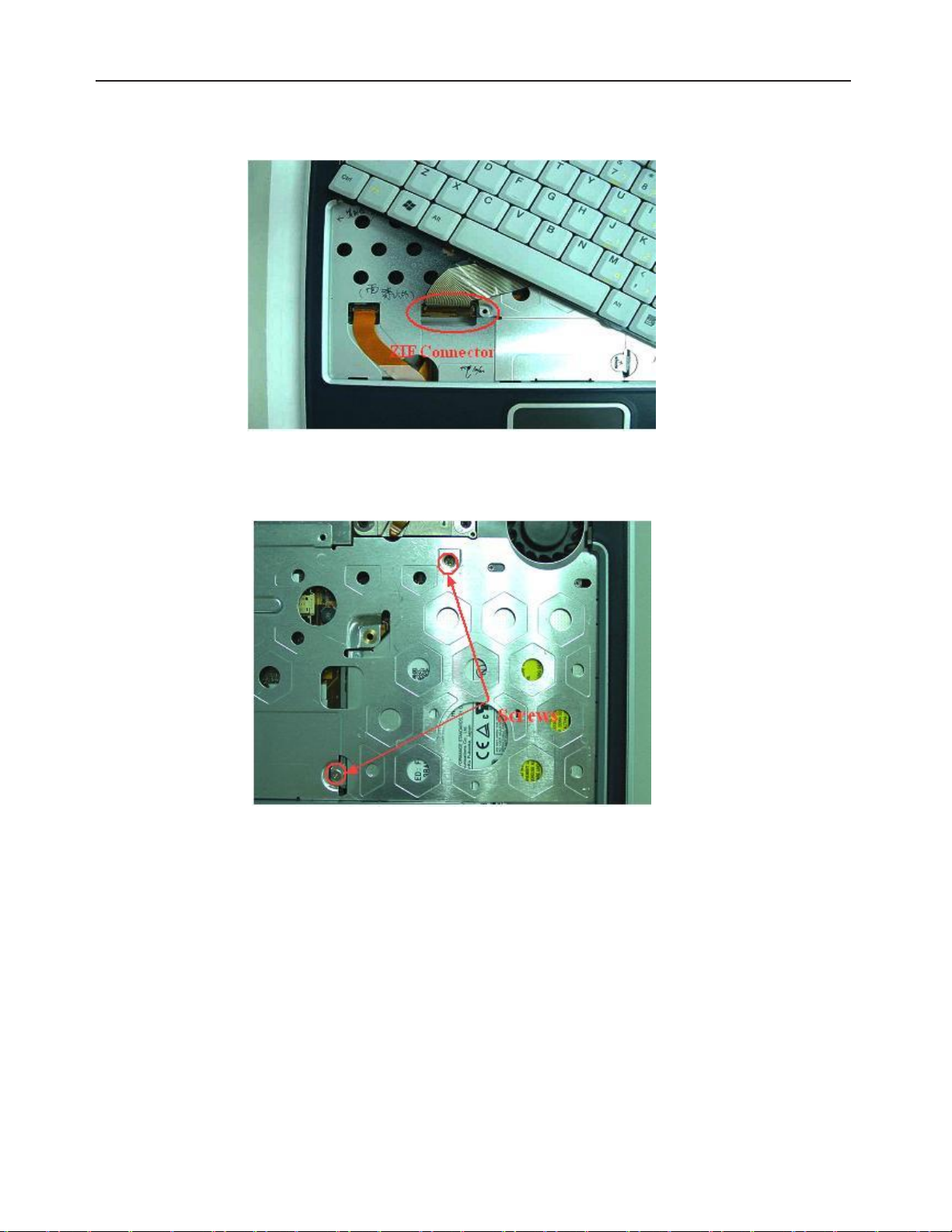

5. Release keyboard cable by sliding the ZIF connector towards up direction.

27

Page 29

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

Figure 2-4 Remove keyboard

6. Release two screws as shown in the picture below, and then remove Middle plate.

Figure 2-5 Remove Middle plate

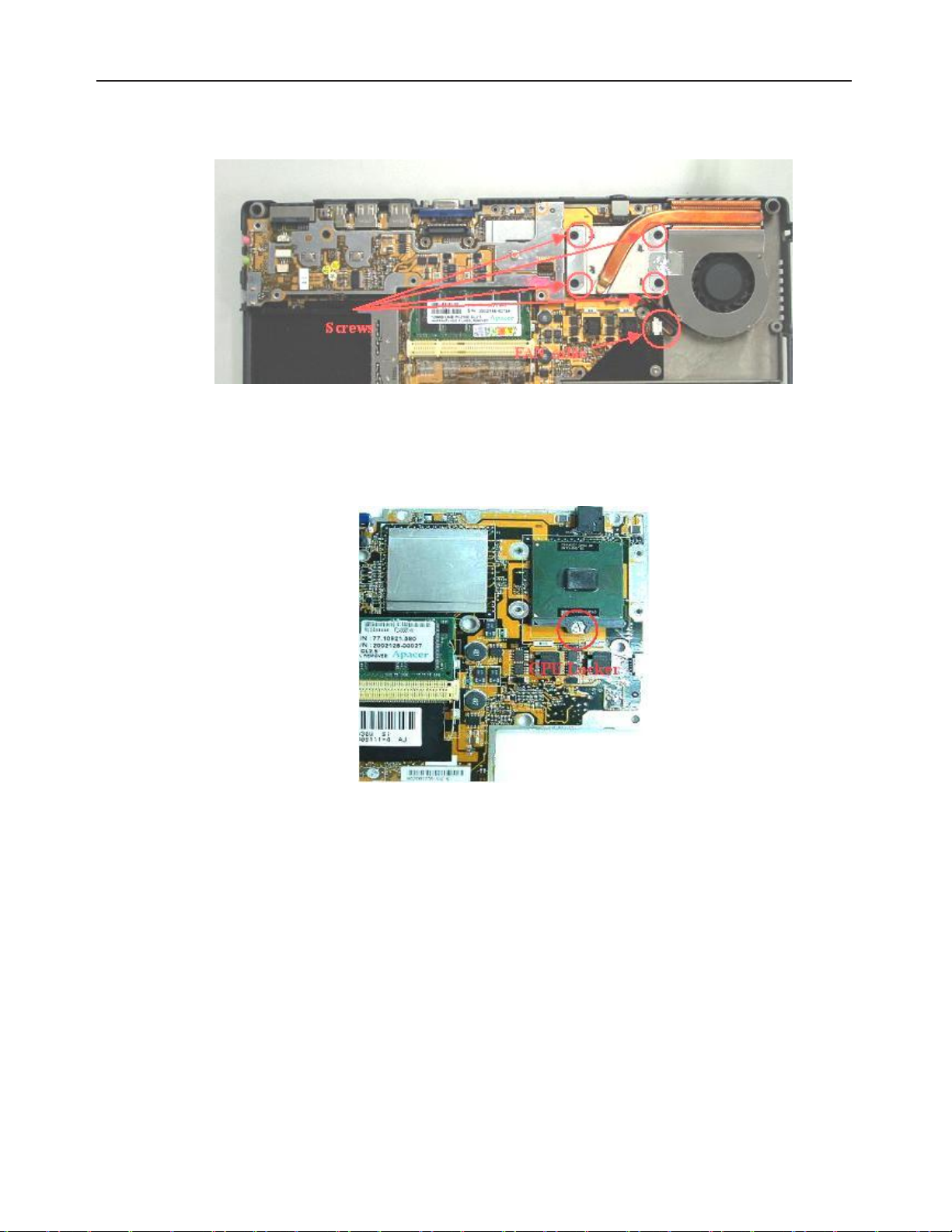

7. Release four screws and one cable as shown in the picture below, and then remove heat

sink plate and Fan.

28

Page 30

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Figure 2-6 Remove heat sink plate and Fan

8. Use a flat screwdriver to unlock CPU.

Figure 2-7 Remove CPU

9. Remove CPU and insert the preferred CPU.

10. Use a flat screwdriver to lock CPU.

11. Place back the heat plate and keyboard cover. Boot on the computer, and then BIOS will

automatically detect the type of the CPU which just be installed.

2.3.3 Memory Upgrade Procedure

The notebook computer offers two memory slot using DDR DIMM at 128MB, 256MB,

512MB and 1024MB DDR-RAM. Two memory slots are found inside the memory

compartment. The memory compartment is located on the underside of your computer inside

the memory compartment. With two memory slots, you can have several combinations up to

2048MB.

29

Page 31

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

Using the Memory Slot inside the Memory Compartment

Follow the steps below on how to upgrade the memory modules:

1. Make sure the system is powered off and that no peripheral devices are attached.

2. Turn the system over and locate the screw on the memory compartment.

3. Remove the K/B cover, K/B and Middle plate.

4. Locate the memory module socket. Align the notch with the notch in the socket connector

and insert the module as follows:

Hold the DIMM at a 60-degree angle and align the DIMM connector with the

−

socket in the system. Push the connector into the socket.

− Press down on the edge of the DIMM until the locking tabs on the sides snap into

place, securing the module.

5. To remove a DIMM, press the locking tabs away from the sides of the module until the

module pops up. Then, remove the DIMM.

6. Reassemble the notebook components as follows.

Put the DIMM door back.

−

− Replace the screw and turn the system over.

2.3.4 Hard Disk Upgrade Procedure

The notebook provides a built-in hard disk for the primary IDE controller. The HDD is an

industry standard 2.5” IDE disk drive and can be upgraded with another standard 2.5” HDD.

1. Make sure the system is powered off and that no peripheral devices are attached.

2. Remove the four screws.

Figure 2-8 Remove HDD module

30

Page 32

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

3. Remove the HDD module from the base unit.

4. Remove four screws of frame HDD bracket plate.

Figure 2-9 Screws Locations of the frame HDD bracket plate

2.3.5 System BIOS Upgrade Procedure

The notebook supports EPROM Flash BIOS that allows you to easily update the system BIOS

using the Phoenix BIOS Flash utility program called “PHLASH.COM”. This program runs

under MS-DOS and requires the system not to load high memory like HIMEM.SYS. It also

needs the “PLATFORM.BIN” file in order to activate.

Follow the steps below on how to update the system BIOS:

1. Prepare a clean bootable diskette without loading the HIMEM.SYS. Copy the files

PHLASH.COM and PLATFORM.BIN into the diskette along with the BIOS ROM file.

Restart the computer and boot from the diskette. At the DOS prompt, type the command

2.

“PHLASH <BIOSfile.ROM>” to activate Flash BIOS programming utility. The

computer will then start to update the system BIOS inside the notebook.

3. After programming is complete, the system will prompt you to press any key to shutdown

the computer. The BIOS version is displayed inside the BIOS Setup Main menu. Press

<F2> after power on to run CMOS Setup program.

BIOS Version : 1.0A-0716-0724

i It is very important not to power off the system whenever the FLASH BIOS

program is running. Otherwise, the system may not be able to power on and you

need to replace the BIOS EPROM chip from another working notebook.

i Always plug in the AC adapter when updating the BIOS.

31

Page 33

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

Software Functional Overview

3.1 Overview

The is an IBM PC/AT compatible Notebook PC, which supports the Intel MicroPGA Pentium M CPU processors family. The following are the major features that Cavaliere

142 supports.

Microsoft PC99 logo and Win XP logo approval.

§

Offer 1024x768 XGA display with 13.3 XGA LCD panel.

§

§ Support ACPI 1.0B (or above).

§ Support PCI 2.1 (or above).

§ Support AGP 2.0.

Support SMBIOS 2.3.

§

Support DDR266/200 SDRAM.

§

Support 100/133 Mhz CPU front side bus.

§

3.2 Summary of the BIOS Specification

The summary of the BIOS specification is as the below description:

Controller Chip Description

Shadow Always enable VGA and System BIOS shadow

Display

Hard Disk

Multi Boot Allow the user to select boot from FDD, HDD and CD-ROM

Plug and Play Support PnP Run Time Service and conflict-free allocation of

Smart Battery Support BIOS interface to pass battery information to the

Keyboard Controller Support Fn hot keys, one Win95 hot keys, built-in Glide Pad.

PCMCIA Compliant with PCMCIA 2.1 specification

§ System auto detects LCD or CRT presence on boot and lid

closed.

§ Support Panning while LCD in a display resolution greater

than supported.

§ Support Microsoft Direct 3D.

§ Support AGP 4x BUS.

§ Enhanced IDE spec.

Support auto IDE detection.

§

§ Support LBA mode for larger capacity HDD.

§ Support Ultra DMA 33/66/100.

§ Support Fast PIO mode 1-4 transfer.

§ Support 32 bit PIO transfer.

§ Support Multi-Sector transfer.

§ Support SMART monitoring.

resource during POST

application via SMBus

32

Page 34

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Power Management

Support (ACPI Mode)

The power management is compliant with ACPI 1.0B

specification and supports the following power state:

§ S0 (Full-On) Mode

§ S3 (STR) Mode

§ S4 (STD) Mode

§ S5 (Soft-Off) Mode

3.3 Subsystem Software Functions

This section provides introduction on the software functions of the notebook subsystems and

BIOS related function.

3.3.1 Key Chipset Summary

Following are the main chipsets used in the notebook:

Controller Chip Vendor Description

Processor

North Bridge

South Bridge

Video Controller

PCMCIA Controller

Audio Chip

Audio Codec

Keyboard Controller

PMU Controller

ROM BIOS

Clock Generator

Temperature Sensor

IEE 1394

LAN

Modem

Intel Mobile Banias

Intel Montara GM

Intel ICH4

Intel Embedded in Montara GM

RICOH R5C551

Intel South Bridge Integrated

Intel ICH4

Misubishi M3885x

NEC PMU08

SST 49LF004A

IMI CY28346

NS MAX6690

RICOH R5C551

Intel ICH4

Intel MDC AC’97

3.3.2 System Memory

The system memory consists of SDRAM memory on 64-bit bus and the module size options

are 128/256/512/1GMB upward. The BIOS will automatically detect the amount of memory

in the system and configure CMOS accordingly during the POST (Power-On Self Test)

process. This must be done in a way that requires no user interaction.

Base SO-DIMM DRAM

slot

Expansion SO-DIMM DRAM

slot

Total Size

(Bank 0&1) (Bank 2&3)

NIL 128MB 128MB

NIL 256MB 256MB

33

Page 35

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

NIL 512MB 512MB

128MB NIL 128MB

128MB 128MB 256MB

128MB 256MB 384MB

128MB 512MB 640MB

256MB NIL 256MB

256MB 128MB 384MB

256MB 256MB 512MB

256MB 512MB 768MB

512MB NIL 512MB

512MB 128MB 640MB

512MB 256MB 768MB

512MB 512MB 1024MB

3.3.3 Video

The Video subsystem used External DDR memory of Video memory. The system will

support the true ZV port, the Microsoft Direct 3D assist, simultaneous display, monitor

sense for auto display on boot and VESA Super VGA function call.

Supported Video Mode

The following is the display modes supported by the SIS Mobility Video control in

LCD only, CRT only, and simultaneous mode. The VGA BIOS will allow mode sets of

resolutions greater than the panel size but only show as much mode display as will fit

on the panel.

Supported standard VGA modes:

The VGA BIOS supports the IBM VGA Standard 7-bit VGA modes numbers.

Mode Pixel Resolution Colors Memory

00h/01h 40*25 16 Text

02h/03h 80*25 16 Text

04h/05h 320*200 4 2-bit Planar

06h 640*200 2 1-bit Planar

07h 80*25 Mono Text

0Dh 320*200 16 4-bit Planar

0Eh 640*200 16 4-bit Planar

0Fh 640*350 Mono 1-bit Planar

10h 640*350 16 4-bit Planar

11h 640*480 2 2-bit Planar

12h 640*480 16 4-bit Planar

13h 320*200 256 8-bit Planar

Note: All Standard VGA Modes are limited to the standard VGA refresh rates.

34

Page 36

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

Supported extended video modes:

CRT device will support all listed VESA mode; and other devices such as PANEL & TV may

be limited to the mode support due to their characteristics.

VESA

Mode

100h 640 x 400 8-bit Packed 70 2MB

101h 640 x 480 8-bit Packed 60, 72, 75, 85 2MB

102h 800 x 600 4-bit Planar 60, 72, 75, 85, 100 2MB

103h 800 x 600 8-bit Packed 60, 72, 75, 85, 100 2MB

104h 1024 x 768 4-bit Planar 43(I), 60, 70, 75, 85, 100 2MB

105h 1024 x 768 8-bit Packed 43(I), 60, 70, 75, 85, 100 2MB

106h 1280 x 1024 4-bit Planar 43(I), 60, 75, 85

107h 1280 x 1024 8-bit Packed 43(I), 60, 75, 85

10Eh 320 x 200 16-bit Packed 70

10Fh 320 x 200 32-bit Unpacked 70

111h 640 x 480 16-bit Packed 60, 72, 75, 85

112h 640 x 480 32-bit Unpacked 60, 72, 75, 85

114h 800 x 600 16-bit Packed 60, 72, 75, 85, 100

115h 800 x 600 32-bit Unpacked 60, 72, 75, 85, 100

117h 1024 x 768 16-bit Packed 43(I), 60, 70, 75, 85, 100

118h 1028 x 768 32-bit Unpacked 43(I), 60, 70, 75, 85, 100

11Ah 1280 x 1024 16-bit Packed 43(I), 60, 75, 85

11Bh 1280 x 1024 32-bit Unpacked 43(I), 60, 75, 85

11Dh 640 x 400 16-bit Packed 70

11Eh 640 x 400 32-bit Packed 70

120h 1600 x 1200 8-bit Packed 48(I), 60, 75, 85

122h 1600 x 1200 16-bit Packed 48(I), 60, 75, 85

124h 1600 x 1200 32-bit Unpacked 48(I), 60, 75, 85

12Ah 640 x 480 24-bit Packed 60, 72, 75, 85

12Bh 800 x 600 24-bit Packed 60, 72, 75, 85, 100

12Ch 1024 x 768 24-bit Packed 43(I), 60, 70, 75, 85, 100

12Dh 1280 x 1024 24-bit Packed 43(I), 60, 75, 85

12Eh 320 x 200 8-bit Packed 70

131h 320 x 200 8-bit Packed 72

133h 320 x 200 16-bit Packed 72

134h 320 x 200 32-bit Packed 72

13Bh* 1400 x 1050 8-bit Packed 60, 75

13Ch* 1400 x 1050 16-bit Packed 60, 75

13Eh* 1400 x 1050 32-bitUnpacked 60, 75

Pixel

Resolution

Memory Model Refresh Rates In (Hz) Minimum

Memory

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

4MB

4MB

8MB

2MB

2MB

2MB

4MB

8MB

2MB

2MB

4MB

4MB

2MB

2MB

2MB

2MB

2MB

4MB

8MB

35

Page 37

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

141h 400 x 300 8-bit Packed 72

143h 400 x 300 16-bit Packed 72

144h 400 x 300 32-bitUnpacked 72

151h 512 x 384 8-bit Packed 70

153h 512 x 384 16-bit Packed 70

154h 512 x 384 32-bitUnpacked 70

171h 720 x 480 8-bit Packed 75

173h 720 x 480 16-bit Packed 75

174h 720 x 480 24-bit Packed 75

175h 720 x 480 32-bitUnpacked 75

176h 720 x 576 8-bit Packed 75

178h 720 x 576 16-bit Packed 75

179h 720 x 576 24-bit Packed 75

17Ah 720 x 576 32-bitUnpacked 75

Note: “*” The modes may not be available. Their availability should be determined by VESA

function calls.

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

2MB

Panel Type Initialization

The VGA BIOS will issue INT 15h function call during POST. This function call

allows the system BIOS to specify the panel type to the VGA BIOS. The system BIOS

should get the panel type from GPIO pins before the VGA chip initialized, and pass

this information to VGA BIOS through INT 15 Function 4E00h.

LCD Panel ID pin Definition:

VT82C686B GPI Pins

GPI

[23]

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

GPI

[17]

GPI

[11]

GPI

[10]

Panel Type

ID0

ID1

ID2

ID3

36

Page 38

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

1 1 0 1

1 1 1 0

1 1 1 1

3.3.4 Enhanced IDE

The system BIOS must be ready to support 4 IDE devises on two controllers. The BIOS

support Ultra DMA33/66/100 and also supports automatic configuration of drives using

both the LBA and CHS large drive remapping method. In addition to supporting

standard drives through an auto-configuration process that does NOT require user

involvement or confirmation. The system should automatically do this at POST time in a

way that is transparent to the user. If a drive is connected to the bus, the drive should be

automatically recognized, configured and available for use under MS-DOS 6.2x.

3.3.5 Audio

The audio subsystem will support the requirements identified by the AC’97 specification.

Both software and hardware will control the volume level for the internal audio subsystem. In

addition to the volume control, the user will be able to mute the sound to completely cut off

the volume using both software and hardware.

3.3.7 PCMCIA

The PCMCIA controller chip of the notebook provides the following features:

• Individually accessed, dual-buffer implementation

Support for 2 separate CardBus slots (one type III or two type II stacked)

•

• Support for 3.3v, 5v and 12v (flash programming) cards

3.3.8 LED Indicator

The table below lists down the functions of the Status LED indicator:

Indicator Function Description

IDE accessing LEDΠThis LED will turn on while accessing the IDE Device.

Battery Charging LED Turn on (Blue) – Battery is under charging mode

Turn off – Battery full charged or no battery

CapsLock LEDΠThis LED will turn on when the function of CapsLock is active.

ScrollLock LEDΠThis LED will turn on when the function of ScrollLock is active.

NumLock LEDΠThis LED will turn on when the function of NumLock is active.

Power Status LED Blue – System is powered on.

Blue Blinking- System is entered suspend mode.

Trun off – Battery Low.

Mail LEDΠThis LED will turn on while Mail was arrived.

i

Π- These LEDs will be turned off during Suspend mode.

37

Page 39

170~177, 1F0~1F7,

220~22F, 300~301,

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

3.3.9 Hot Keys Definition

All Hot keys must be active at all times under all operation systems.

Function Function Handler

Fn + F3 Toggle Display (LCD/CRT/TV/LCD&CRT) BIOS Handler

Fn + F2 RF ON/OFF BIOS Handler

Fn + F6 System Speaker On/Off BIOS Handler

Fn + F8 Brightness Increase Controlled by PMU08

Fn + F9 Brightness Decrease Controlled by PMU08

ScrLock Scroll Lock

Internet

Button

Mail Button Mail Function Key Controlled by Driver

Internet Function Key Controlled by Driver

3.3.10 Plug & Play

The BIOS supports the Plug and Play Specification 1.0A. (Include ESCD)

This section describes the device management. The system board devices and its resources are

as follows:

Device Connect

Type

I/O IRQ DMA Memory

DMA Controller Static 00~0F, 81~8F - DMA5 Interrupt Controller Static 20~21, A0~A1 IRQ2 - System Timer Static 40~43 IRQ0 - RTC Static 70~71 IRQ8 - ISA Bus Static - - - System Speaker Static 61 - - System Board Static - - - E0000~FFFFF

PnP Mother Board Static 80 - - Keyboard Controller Static 60, 64 IRQ1 - PMU08 Controller Static 68, 6C - - Math Coprocessor Static F0~FF IRQ13 - Glide Pad Static - IRQ12 - Video Controller Static 3B0~3BB,

Dual IDE Controller Static

CardBus Controller Dynamic 3E0~3E1 IRQ10 - Audio chip Dynamic

IEEE1394 Dynamic IRQ10

Modem Dynamic 3E8~3EF IRQ10 - LAN Dynamic 1080~10FF IRQ10 - USB Host Controller Dynamic EF80~EF9F IRQ5 - -

Resources

IRQ5 - A0000~BFFFF

3C0~3DF

IRQ14, 15 - -

3F6

IRQ5 DMA3 -

388~38B

,

C0000~CFFFF

38

Page 40

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

3.3.11 PCI Device

The table below summarizes the PCI IDSEL Pin Allocation:

IDSEL Pin PCI Device

Device Number Function

Number

AD23 Device 07 Function 0 RICOH Card Bus

Function 1 RICOH IEEE1394

AD17 Device 01 Function 0 MINI PCI

The table below summarizes the INT Pin Allocation:

INT Pin PCI Device

INTA CardBus/MiniPCI/LAN

INTB Cardbus/MiniPCI

INTC

INTD

The table below summarizes the PCI bus master Allocation:

Device Name

Arbiter Signal Agents

(Master)

REQ00/GNT00

REQ20/GNT20

REQ30/GNT30

REQ10/GNT10 RICOH Card Bus Controller

Function Use

3.3.12 SMBus Devices

The SMBus is a two-wire interface through which the system can communicate

with power-related chips. The BIOS should initialize the SMBus devices during

POST.

ICH4 SMBus Connection Devices

SMBus Device Host/Slave Address BIOS Need to Initialization

SO-DIMM Slave A0h/A2h Memory Auto Sizing (SPD).

CY28346

CLK Generator

Slave D2h Program the desired clock frequency

(Pin23 output 24MHz, Pin22 output

48MHz)

39

Page 41

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

PMU 08 SMBus Connection Devices

SMBus Device Host/Slave Addres

s

A7 ~

A1

PMU08 Master 10h Enable PS01 decode interface

MAX6690 (Thermal

Slave 9Ch Program the desired temperature

sensor)

Battery (1st Battery) Slave A8h No Need

I/O Map

Hex Address Device

000 - 01F 8237-1

020 - 021 8259-1

022

040 - 05F 8254

060 - 064 Keyboard Controller

068 – 06C PMU08 Controller

070 - 07F RTC & NMI Mask

080 - 08F DMA Page Registers

092 System Control Port

0A0 - 0A1 8259-2

0B2 Advanced Power Management Control Port

0B3 Advanced Power Management Status Port

0C0 – 0DF 8237-2

0F0 – 0FF Math Coprocessor

170 - 177 IDE Secondary Command Block

1F0 - 1F7 IDE Primary Command Block

220 - 22F Sound Blaster

279 ISA PnP Address

330 - 333 MIDI

376 IDE Secondary Control Block

388 - 38B FM Synthesizer

3B0 - 3DF Video Controller

3E0 - 3E1 PCMCIA Controller

3F0 - 3F5, 3F7 Floppy Disk Controller

3F6 IDE Primary Control Block

A79 ISA PnP Address

CF8 – CFF PCI BUS configuration Register

ISA DMA Map

DMA Channel Device

DMA 0 Unused

DMA 1 Unused

DMA 2 Floppy Disk

DMA 3 Audio

BIOS Need to Initialization

range

40

Page 42

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

DMA 4 Unused

DMA 5 Unused

DMA 6 Unused

DMA 7 Unused

Memory Map

Address Range Length Description

00000 - 9FFFFh 640 KB System Memory

A0000 – BFFFFh 128 KB Video Memory

C0000 – C9FFFh 40 KB Video ROM

CA000 – DBFFFh 72 KB Unused

DC000 - DFFFFh 16 KB DMI information

E0000 – FFFFFh 128 KB System ROM BIOS

IRQ Map

IRQ# Description

IRQ 0 System Timer

IRQ 1 Keyboard

IRQ 2

IRQ 3

IRQ 4

IRQ 5 Audio/VGA/USB

IRQ 6 Floppy Disk Drive

IRQ 7

IRQ 8 RTC Alarm

IRQ 9 ACPI

IRQ10 LAN / Modem or Combo, (Card Bus), IEEE 1394

IRQ11 Reserved for PCMCIA card

IRQ12 Glide Pad

IRQ13 FPU (FERR)

IRQ14 Hard Disk Drive

IRQ15 CD-ROM or DVD-ROM

3.3.13 GPIO Pin Assignment

The GPI and GPO pins connected to system devices. The BIOS can get device’s

status and control the device via the GPI and GPO pins.

ICH4 GPI pin assignment

GPIO

Number

GPIO0 PanelID0 I Panel ID setting

GPIO1 PanelID1 I Panel ID setting

GPIO2 PanelID2 I Panel ID setting

GPIO3 PanelID3 I Panel ID setting

Signal Name Default I/O Notes

41

Page 43

R5C551 Hardware suspend control

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

GPIO8

GPIO11 LPC_QPME0 1 O 0:LPC_QPME0 Event Enable

GPIO12 EC_SCI0 I 0:PMU SCI Detect

GPIO13 PM_RI0 I 0:PMU GPIO detect

GPIO25 CB_HWSUS

GPIO32 SPDMUX0 1 O SMBus select 1

GPIO33 SPDMUX1 1 0 SMBus select 0

Q_SMI0 I 0:External K/B SMI0

1:Normal operation

1:Normal operation --

1:PMU SCI not Detect

1:PMU GPIO not Detect

1 O

P0

pin

3.3.14 PMU08 GPIO pin assignment

GPIO

number

GPIO B6 PM_SLP_S

GPIO B5 N.C. -- -- No used

Signal

Name

10

Default I/O Notes Remar

1 I Suspend Plane A control for

ICH4

0: POS, STR and STD

suspend state.

1: not suspend state.

k

GPIO B4 N.C. -- -- No used

GPIO B1 N.C. 1 O No used

GPIO B0 N.C. -- -- No use

GPIO A7 N.C -- -- No use

GPIO A6 PCMRI0 1 I PC Card Ring event

0: Ring

1: No Ring

GPIO A0 LID0 1 I LCD Open/Close Status

0: LCD Close

1: LCD Open

GPIO C1 NC -- -- No Use

GPIO B7 PM_RI0 1 O Wake Up event request

0: Wake SMI(SCI)

1: There is no demand.

GPIO B2 N.C. -- - No Use

GPIO B0 N.C. -- -- No Use

GPIO A5 PRSTMSK0 1 O PCI Reset Mask

0: Reset Mask

1: Reset Enable

GPIO A4 PCMUTE0 1 O Mute PC Speaker

GPIO A1 N.C. -- -- No use

42

Page 44

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

GPIO C2 CHGLED Charge Battery indicator :

1 : charging Battery

0 : Stop charging Battery

GPIO C3 N.C. -- -- No Use

GPIO C0 N.C. -- -- No Use

3.4 ACPI

General Requirements

The BIOS must meet the following general Power Management requirements:

Refers to the portion of the firmware that is compatible with the ACPI 1.0b specifications.

Support for Power ON(S0 state), Suspend-to-RAM (S3 state) , Suspend-to-Disk mode (S4

state) and Soft OFF(S5 state).

Global System State Definitions

Global system states (Gx states) apply to the entire system and are visible to the user.

Following is a list of the system states:

G0/S0 - Working:

A computer state where the system dispatches user mode (application) threads and

they execute. In this state, devices (peripherals) are dynamically having their power

state changed. The user will be able to select (through some user interface) various

performance/power characteristics of the system to have the software optimize for

performance or battery life. The system responds to external events in real time. It is

not safe to disassemble the machine in this state.

G1 - Sleeping:

A computer state where the computer consumes a small amount of power, user

mode threads are not being executed, and the system “appears” to be off (from an

end user’s perspective, the display is off, etc.). Latency for returning to the Working

state varies on the wakeup environment selected prior to entry of this state (for

example, should the system answer phone calls, etc.). Work can be resumed without

rebooting the OS because large elements of system context are saved by the

hardware and the rest by system software. It is not safe to disassemble the machine

in this state.

G2/S5 - Soft Off:

A computer state where the computer consumes a minimal amount of power. No

user mode or system mode code is run. This state requires a large latency in order to

return to the Working state. The system’s context will not be preserved by the

hardware. The system must be restarted to return to the Working state. It is not safe

to disassemble the machine.

G3 – Mechanical Off:

A computer state that is entered and left by a mechanical means. It is implied by

the entry of this off state through a mechanical means that the no electrical current is

43

Page 45

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

running through the circuitry and it can be worked on without damaging the

hardware or endangering the service personnel. The OS must be restarted to return to

the Working state. No hardware context is retained. Except for the real time clock,

power consumption is zero.

Sleeping State Definitions

Sleeping states (Sx states) are types of sleeping states within the global sleeping

state, G1. The Sx states are briefly defined below. For a detailed definition of the

system behavior within each Sx state, refer to ACPI specification section 7.5.2. For a

detailed definition of the transitions between each of the Sx states, refer to ACPI

specification section 9.1.

S1 Sleeping State:

The S1 sleeping state is a low wake-up latency sleeping state. In this state, no

system context is lost (CPU or chip set) and hardware maintains all system context.

S3 Sleeping State:

The S3 sleeping state is a low wake-up latency sleeping state where all system

context is lost except system memory. CPU, cache, and chip set context are lost in

this state. Hardware maintains memory context and restores some CPU and L2

configuration context. Control starts from the processor’s reset vector after the wakeup event.

S4 Sleeping State:

The S4 sleeping state is the lowest power, longest wake-up latency sleeping state

supported by ACPI. In order to reduce power to a minimum, it is assumed that the

hardware platform has powered off all devices. Platform context is saved in disk.

S5 Soft Off State:

The S5 state is similar to the S4 state except the OS does not save any context nor

enable any devices to wake the system. The system is in the “SOFT” off state and

requires a complete boot when awakened. Software uses a different state value to

distinguish between the S5 state and the S4 state to allow for initial boot operations

within the BIOS to distinguish whether or not the boot is going to wake from a saved

memory image.

System Power Plane

The system components are grouped as the following parties to let the system to

control the On/Off of power under different power management modes.

44

Page 46

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

3.4.1 System Power Plane

The system components are grouped as the following parties to let the system to control the

On/Off of power under different power management modes.

The power plane is divided as following:

Power Group Power

Controlled Devices

Control Pin

+B Nil IMM, (9V~20V)

+3VA Nil RTC I/F, PMU08

+12V PWRON PCMCIA Card, AC97 Codec

+5V PWRON PCMCIA Slot 5V

+3V PWRON VGA, PCMCIA, PCMCIA Slot 3V, DRAM, Twister(DRAM

I/F), M3885x, MAX3243

+5VS SUSB# FLASH ROM, HDD, CD-ROM, USB, Internal K/B, Glide Pad,

Audio AMP, Fan

+3VS SUSB# ISA I/F Power, Clock Generator & Buffer (W137)

+RTCVCCS Nil RTC

3.4.2 Power Management Mode Transition Flow Chart

From a user-visible level, the system can be thought of as being one of the states in the

following diagram:

G2 (S5) -

Soft Off

ACPI

Boot

(SCI_EN=1)

SLP_TYPx=S5

and

SLP_EN

or

PWRBTN_OR

Wake

Event

G0 (S0) -

Working

S4BIOS_REQ

to

SMI_CMD

OEM S4 BIOS

Handler

SLP_TYPx=S1

SLP_EN

SLP_TYPx=S2

SLP_TYPx=S4

and

and

SLP_EN

SLP_TYPx=S3

and

SLP_EN

and

SLP_EN

SLP_TYPx=S4

and

SLP_EN

S1

Sleeping

S2

Sleeping

G1

S3

Sleeping

S4

Sleeping

45

Page 47

TECHNICAL SERVICE MANUALPrestigio Cavaliere 142

3.4.3 Power States transition event

The following table summarizes the entry events and wake-up events of each power:

The following table summarize the entry events and wake-up events of each power state

Power State Entry Event Wake up Event

S3 OSPM control

Lid Close

Power Button

Sleep Button

Battery Low

Power Button

Ring Wake up

RTC Alarm

LAN Wake Up

Lid open

S4 OSPM control,

Power button

Sleep button

Lid Close

Battery Low

S5 Power Button

Battery Low

OSPM control

x OSPM: OS-directed Power Management

Power Button

RTC Alarm

Power Button

Device Power Control Methodology

Power state of local devices table

This section illustrates the power control status of each key device/component of the

system under each power management mode.

PowerState

Component

CPU Stop

L2 CACHE ON Power Down Power Off Power Off

MontaraGM ON Stop Clock Power Off (except

ICH4 ON ON Power Off (except

DRAM ON Self Refresh Self Refresh Power Off

Clock Synthesizer ON Low Power Power Off Power Off

CDROM ON Power Down Power Off Power Off

HDD ON Power Down Power Off Power Off

FDD ON Power Down Power Off Power Off

KBC ON ON Power Down Power Off

PMU08 ON ON Power Down Power Down

VGA/VRAM ON Power Down Power Down Power Off

PCMCIA ON Power Down Power Down Power Off

AUDIO ON Power Down Power Off Power Off

Audio AMP ON Power Down Power Off Power Off

LCD Backlight ON Power Off Power Off Power Off

Doze Stand By STR STD/SOff

Stop Clock Power Off Power Off

Grant

Power Off

Vcc)

Power Off (except

SUSVcc, RTCVcc )

SUSVcc, RTCVcc)

46

Page 48

TECHNICAL SERVICE MANUAL Prestigio Cavaliere 142

LAN ON Power Down Power Down Power Down

Internal Modem ON Power Down Power Down Power Down

Device Power control Methodology During S3 Mode

This section illustrates the control methodology of each device/component and its details