Page 1

42” Receptor de Plasma Color TV

Modelo: PLA-4200M

Manual de Reparaciones

Page 2

TELEVISOR PDP MANUAL DE REPARACIONES

Contenido

1. Instrucciones de seguridad…………………………….…………….. 2

2. Especificaciones………………………………….………………..… 4

3. Bloque diagrama de procesamiento de señal y sistema….………….. 5

4. Lista de partes……………………………….………………..……… 7

5. Dibujo general de montaje…………….………………….…………. 10

6. Diagrama general de conexión………………………………….…… 11

7. Análisis de fracasos…………………………….…………….……… 15

8. Descripción de Ics y componentes principales….…….........……….. 19

1

Page 3

TELEVISOR PDP MANUAL DE REPARACIONES

Aviso: Este manual de reparaciones es sólo para lectura y

utilización de profesionales. El reparador tiene que

revisar la parte de precauciones de seguridad antes de

empezar a trabajar.

1. Instrucciones de seguridad

PARA EVITAR CUALQUIER PELIGRO POSIBLE, DAÑO GENERAL O FÍSICO, POR FAVOR

CONSIDERE Y OBSERVE TODAS LAS ADVERTENCIAS MENCIONADAS EN ESTE PÁRRAFO.

A. Advertencias

Si no considera las siguientes advertencias antes de realizar reparaciones, puede tener como resultado muerte o

herida grave.

(1) El módulo PDP es controlado por voltaje de unos 350V. Si necesita manejar el módulo durante la operación o

poco después del apagamiento, tiene que tomar precauciones contra choque eléctrico y nunca toque el circuito

propulsor o las partes metálicas del módulo PDP.

Los condensadores en el circuito propulsor quedan temporalmente cargados incluso después del apagamiento.

Después de apagar la potencia, usted tiene que esperar por lo menos un minuto antes de tocar el módulo. Si el

voltaje resto es suficientemente fuerte, puede causar choque eléctrico.

(2) No utilice ningún otro voltaje del suministro de potencia sino el especificado en las especificaciones de este

producto. Si utiliza voltaje no mencionado en las especificaciones, puede provocar incendio o fracaso del

producto.

(3) No maneje o instale el producto en circunstancia no especificada tales como sitio con humedad o lluvia; cerca de

agua- por ejemplo, bañera, lavadero o fregadero; en un sótano mojado; o cerca de piscina; tampoco cerca de

fuego o calentador, por ejemplo, cerca o sobre radiador de calor; o donde está expuesto directamente a luces del

sol; o sitio parecido. Si usted utiliza el módulo PDP en los sitos mencionados arriba, puede tener como resultado

choque eléctrico, incendio o fracaso del producto.

(4) Si objeto ajeno (p. ej: agua, líquido o pedacito metálico o polvo) entra en el módulo PDP, tiene que apagar

inmediatamente el voltaje al módulo. Nunca empuje ningún objeto en el módulo PDP porque puede tocar punto

de voltaje peligroso o hace cortocircuito, lo cual puede provocar incendio o choque eléctrico.

(5) Si humo, olor ofensivo o ruido anormal sale del módulo PDP, tiene que apagar inmediatamente el voltaje al

módulo.

Además, si la pantalla de PDP no visualiza ninguna imagen después de ser encendida o durante la operación,

tiene que apagar inmediatamente el voltaje al módulo. No siga operando el módulo PDP bajo estas condiciones.

(6) No desconecte o conecte el conector del módulo PDP cuando éste esté encendido o poco después del

apagamiento, porque el módulo funciona con voltaje alto y los condensadores en el circuito propulsor siguen

cargados temporalmente incluso después del apagamiento. Si necesita desconectarlo, tieme que esperar por lo

menos un minuto después del apagamiento.

(7) No desconecte o conecte el conector de potencia con mano mojada. El voltaje del producto puede ser

suficientemente fuerte para causar choque eléctrico. fort qu’il peut causer un choc électrique.

2

Page 4

TELEVISOR PDP MANUAL DE REPARACIONES

(8) No dañe o modifique el cable de potencia del módulo PDP.

(9

) Si el cable de potencia o el conector está dañado o desgastado, no lo utilice.

) Si el conector de potencia está cubierto de polvo, lo limpie con un trapo seco antes de encenderlo.

(10

Cautela

Si no considera las siguientes cautelas, puede tener como resultado herida personal o daño al producto.

(1

) No coloque el módulo PDP en sitio inestable, vibrante o inclinado, porque el módulo PDP puede caer y causar

da grave a personas o daño grave al producto mismo.

heri

(2

) Si necesita mover el módulo PDP a otro sitio, tiene que apagarlo, desconectar el cable de interfaz y el de potencia

l módulo y tener cuidado durante el trabajo. Si el cable está dañado, puede causar incendio o choque eléctrico.

de

Además, si el módulo cae, puede causar herida a personas.

) Si quiere tirar o insertar el cable de PDP, tiene que apagar el módulo antes y hacerlo agarrando el conector. Si

(3

agarr

a el cable, el alambre eléctrico en el cable puede exponerse o romperse, lo cual puede causar incendio o

choque

(4

) Si quiere llevar el módulo PDP, tiene que ser con dos trabajadores a fin de evitar accidente inesperado.

) El módulo PDP tiene una placa de vidrio. Si el módulo recibe presión excesiva, por ejemplo: choque, vibración,

(5

dobl

Además, no aprete o golpee la superficie de vidrio.

(6

) Si la placa está rota, no la toque con mano sin protección, porque puede herir su mano.

) No coloque nada sobre la placa de vidrio porque puede rayar o romperla.

(7

) No coloque nada sobre el módulo PDP, porque si el objeto cae, puede herir a personas.

(8

eléctrico.

adura o choque de calor, la placa de vidrio puede romperse, lo cual puede provocar herida a personas.

3

Page 5

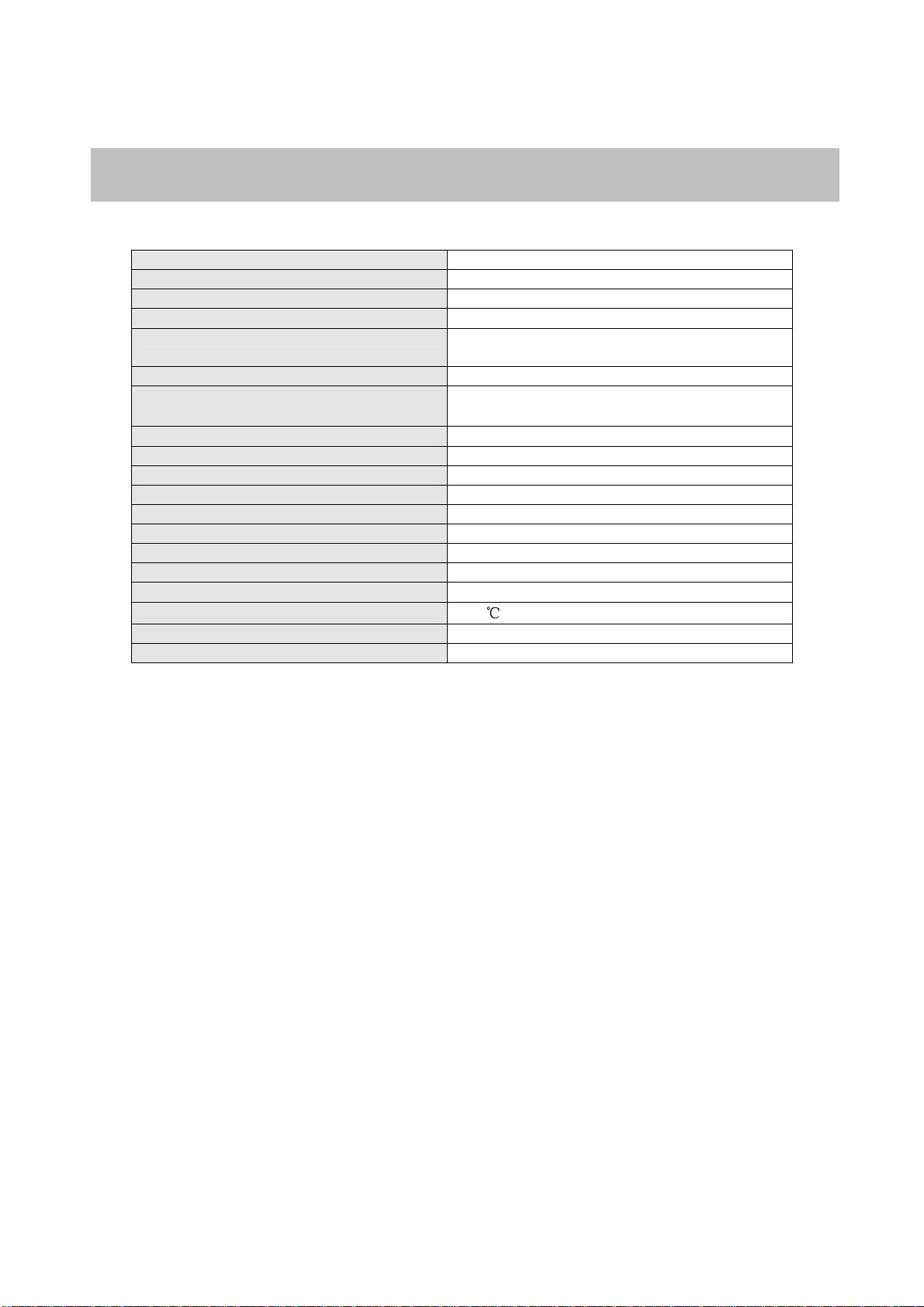

2. Especificaciones

TELEVISOR PDP MANUAL DE REPARACIONES

Modelo

Sistema de teledifusión

Sistema de señal de vídeo

Cantidad de programas almacenados

Gama de canales

Intensidad de señal

Entrada de audio

Salida de altavoz

Ángulo visual (Max)

Resolución

Suministro de potencia

Consumo de energía

Medidas (Ancho*Alto*Fondo)

Tamaño de pantalla

Razón de aspecto

Peso

Temperatura ambiental

Humedad ambiental

Presión atmosférica ambiental

PLA-4200M

NTSC-M

PAL/NTSC/SECAM

125

Aire: Canal 2 a Canal 69,

Cab

le: CATV1 a CATV 125

70dB

Impedancia de entrada>10k

Volgaje de entrada 0.1-0.5 V (rms)

2*5 W

160°

852*480

AC 100V-240V (50Hz/60Hz)

350 W (típico). 3 W (espera)

46.1*29.1*5.2 pulgada

42 pulgadas

16:9

110 1b

0-3

5

20%-70% RH

86-

106 Kpa

4

Page 6

TELEVISOR PDP MANUAL DE REPARACIONES

as

VDS

S

J

5V

V

V

N

V

N

(0,7)

G(0,7)

UV

UV

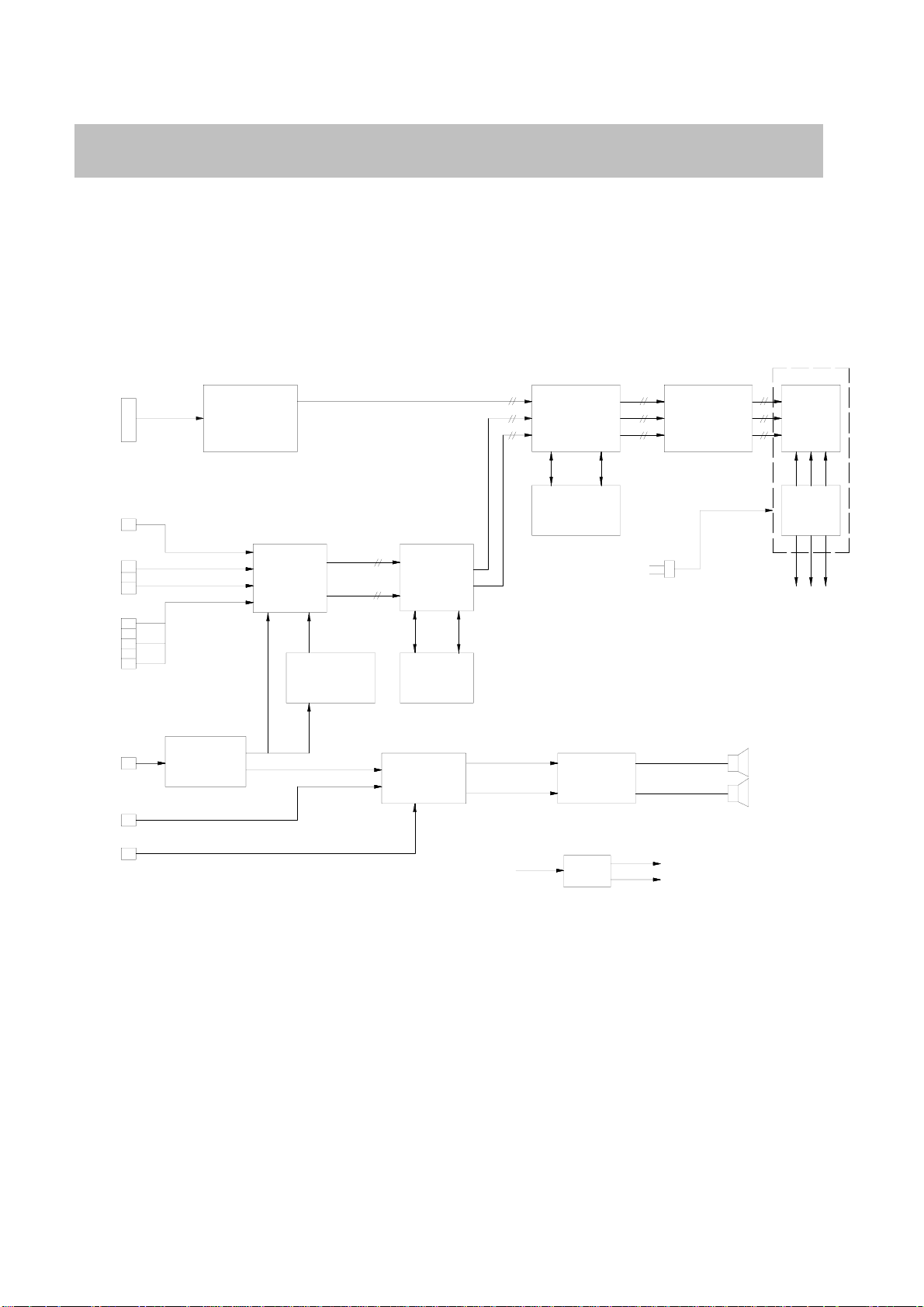

3. Bloque diagrama de procesamiento de señal y sistema

A. Bloque diagrama de procesamiento de señal de imagen

VGA EN

S-VHS IN

1 I

2 I

YCbCr IN

Cable/aire EN

A1 EN

J201

R G B H V

J4

J3

2

Convertidor A/D

TCPN9082DC

27D(T)

Sintoniza

Audio EXT EN

U202

AD9883A

RGB Digital

Y

U301 U302

VPC3230

Descodific

PW1230

De-entrecruza

U1

Memoria

Zilog Z86229

CCDV-chi

VIDEO OUT

intermedia

U303

U3

Proceso MTS

U101 U531

R

PW166B

Escala

THC63LVD823

L

U31

SST39VF800A

h

Fl

Tarjeta AC

+

U4

TDA8944

Amp de audio

Altavoz

Altavoz

AMP

+

+

A2 EN

Audio EXT EN

+12

DC/DC

+

+3..3V

5

Page 7

TELEVISOR PDP MANUAL DE REPARACIONES

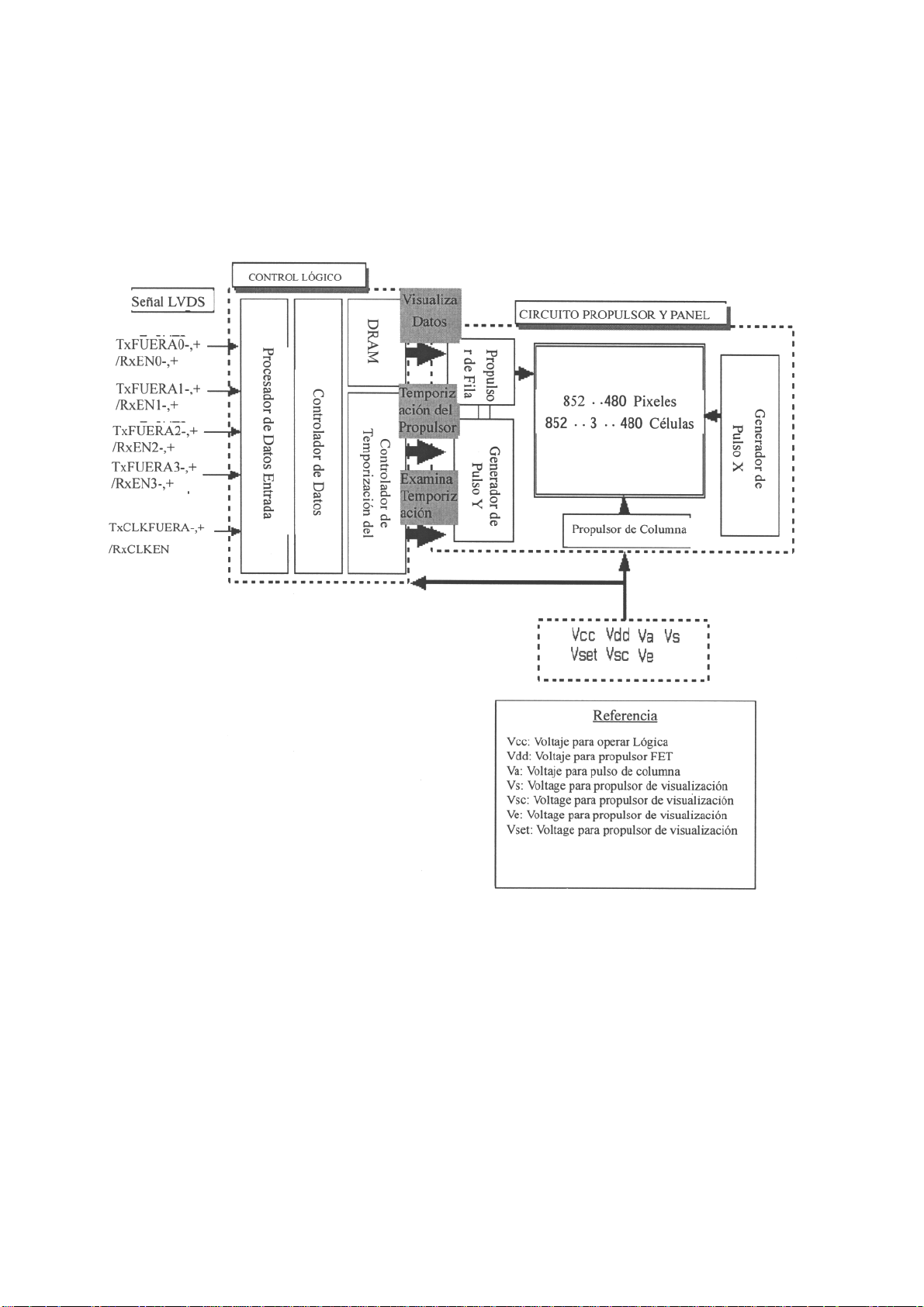

B. BLOQUE DIAGRAMA DE LA PANTALLA VISUALIZACIÓN PDP

6

Page 8

TELEVISOR PDP MANUAL DE REPARACIONES

4. Lista de Partes

Part Number Description Qty.

A904008 Polaroid PLA-4200M Panel De Exhibición De Plasma 1

Incluido in A904008 Polaroid PLA-4200M Cable L=150mm

SPW5.069.166

SPW5.969.003

A920008

SPW8.339.008 Polaroid PLA-4200M Botón De la Alimentación Principal 1

E143221J

E143222J

E14346

E14346

E14423

E14443

E69022

E69022

E69022

E69023

E69042

E69066

E69067

S07018

G33017

F Polaroid PLA-4200M Tornillo Que golpea ligeramente ST3*8F 2

H Polaroid PLA-4200M Tornillo Que golpea ligeramente ST3*8 6

1 Polaroid PLA-4200M Tornillo Que golpea ligeramente ST4*16 16

3 Polaroid PLA-4200M Tornillo Que golpea ligeramente ST4*16 6

1 Polaroid PLA-4200M Tornillo Que golpea ligeramente ST3*10 30

1 Polaroid PLA-4200M Tornillo Que golpea ligeramente ST4*10 3

0 Polaroid PLA-4200M SEMS Tornillo M3*8 16

1 Polaroid PLA-4200M SEMS Tornillo M3*8 (black) 6

3 Polaroid PLA-4200M SEMS Tornillo M3*8 (black) 15

0 Polaroid PLA-4200M SEMS Tornillo M3*10 2

0 Polaroid PLA-4200M SEMS Tornillo M4*8 14

0 Polaroid PLA-4200M SEMS Tornillo M6*16 (black) 10

0 Polaroid PLA-4200M SEMS Tornillo M6*20 (black) 4

3 Polaroid PLA-4200M Interruptor KDC-A04-1 1

0 Polaroid PLA-4200M Mando A distancia 1

Polaroid PLA-4200M YPbPr Tablero De Circuito

Polaroid PLA-4200M Tablero De Circuito Del Mando A distancia

Polaroid PLA-4200M Zinnia PDP Tablero De Circuito De Control

1

1

1

1

7

Page 9

4. Lista de Partes

TELEVISOR PDP MANUAL DE REPARACIONES

Esta página intencionalmente esta en blanco.

8

Page 10

4. Lista de Partes

TELEVISOR PDP MANUAL DE REPARACIONES

Esta página intencionalmente esta en blanco.

9

Page 11

p

(

)

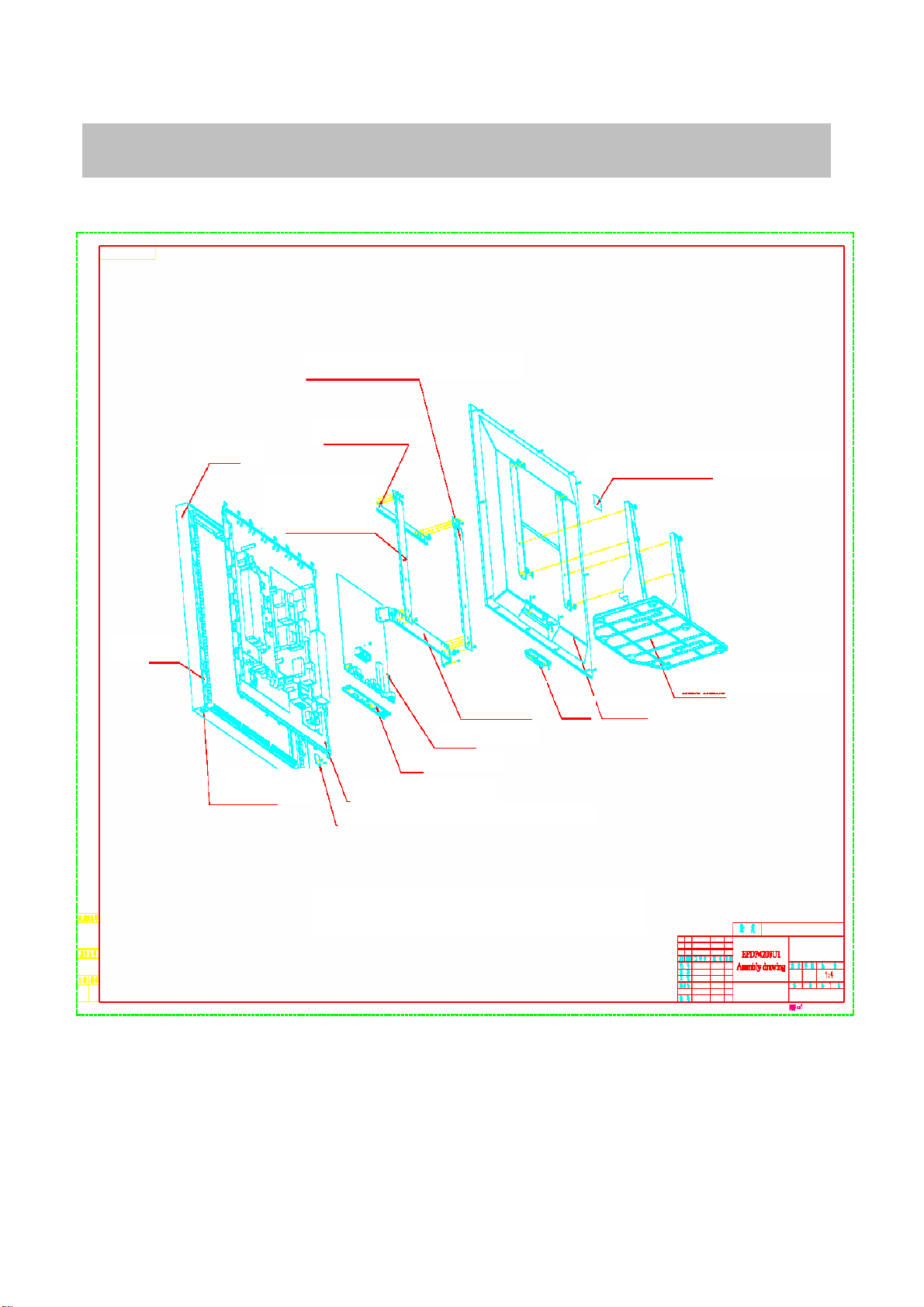

5. Dibujo general de montaje

Soporte de tapa trasera (A)

Soporte de PDP

Caja

Soporte de tapa

trasera (A)

TELEVISOR PDP MANUAL DE REPARACIONES

Placa de nombre en la tapa trasera

Altavoz

Marco de base

Interruptor de

otencia

Soporte de PDP

inferior

Chasis

Placa

Pantalla 42” de PDP

Montaje del control remoto

Marco

Tapa trasera

Dibujo de montaje EPDP4208U1

10

Page 12

TELEVISOR PDP MANUAL DE REPARACIONES

CN

CN6

J

J

J7

J6

CN6

r

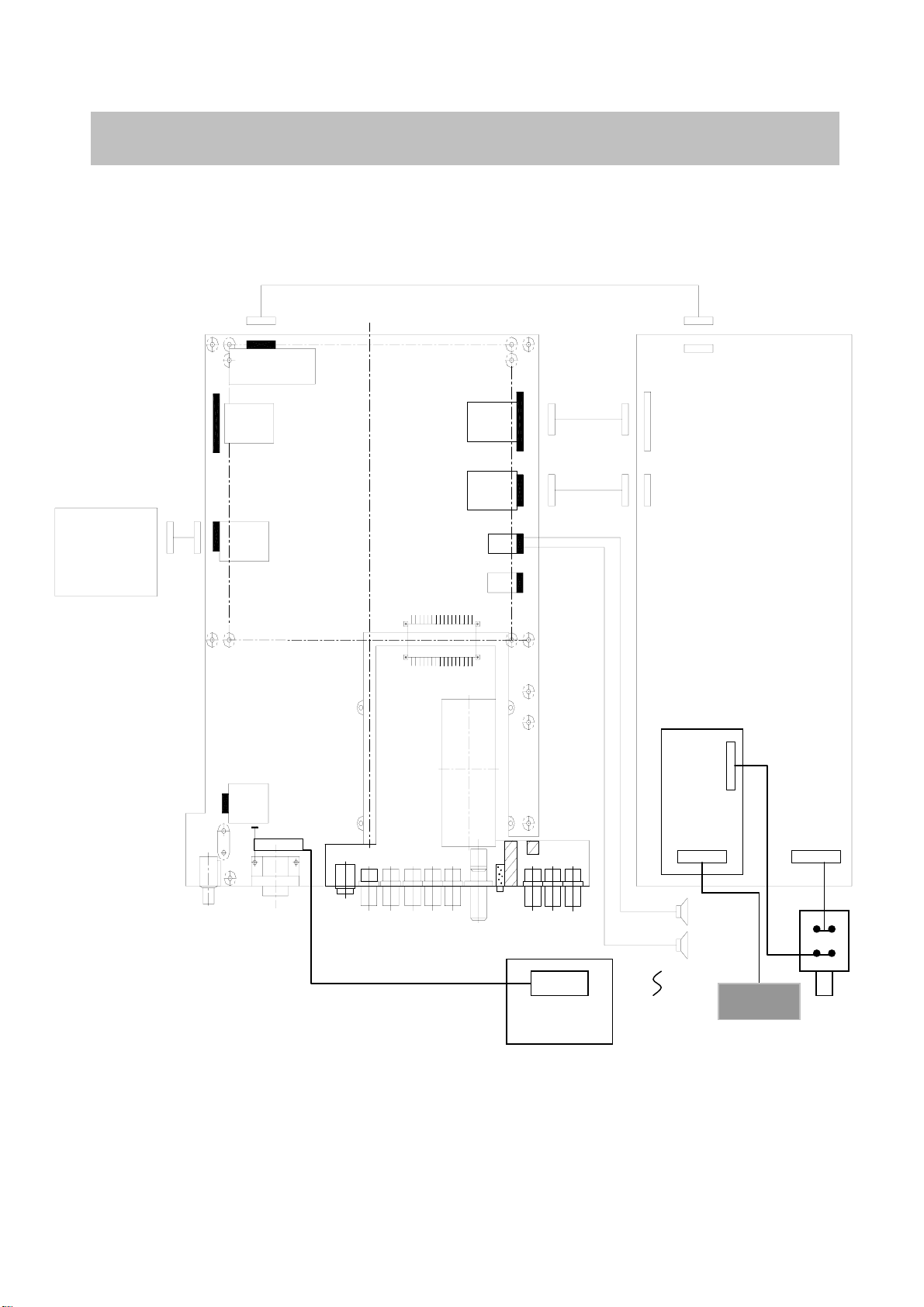

6. Diagrama general de conexión

W2

31

7-

Unidad de

recepción para el

control remoto

SP

W.5.969.003

X1001

W1

6-

15

J5 (LVDS 1/F)

1 31

(TTL 1/F)

Tabla principal

1

(OSD)

15

7

1

Potencia

2

Potencia

13

1

9

1

6

1

W3

4-

W5

6

W4

2-13

1-

9

Conector

CN1

2

CN

LA03

11

CON80

CON8009

Panel visualización de plasma

S42SD-YD

Tabla de

(DV1)

J8

12 1

sintonizador

Tabla filtro de potencia

5-3

CN8702

CN8701

CON8002

Derech

o

Tabla YPbPr

Izquierd

3-12

Enchufe YPbPr

o

9-1

16-1

SPW5.069.166

Speake

Speaker

220V~IN

Toma de corriente

11

Interrupt

5-

3

Page 13

Page 14

TELEVISOR PDP MANUAL DE REPARACIONES

B. Fuente de Voltaje de Potencia Entrada y Asignación de Alfileres

Nombre del Conector : SA JJ11((W44))

A la Tabla de Imagen

Núm del

al

filer

1 5Vsb Vcc5-SB-PDP

2 GND GND

3 GND-D GND

4 B5d1 NC

5 RELÉ PDP-RELÉ

6 TH-DET NC

7 FAN-DET NC

8 GND-A GND

9 GND-A GND

10 NC NC

11 V12A NC

12 V5a Vcc5-PDP

13 NC NC

Fuente de voltaje

Uso

Nombre del conector: AUDIO JJ22((W55))

A la Tabla de Amplificador de Audio

Núm del

filer

al

Fuente de voltaje

Uso

1 V5A Vcc5-PDP

2 GND-A GND

3 12VCC Vcc12-FAN

4 V9A Vcc9-PDP

5 GND-A GND

6 24Vsp Vcc12-AUD-PDP

7 24Vsp Vcc12-AUD-PDP

8 GNDS GND-AUD

9 GNDS GND-AUD

13

Page 15

TELEVISOR PDP MANUAL DE REPARACIONES

Nombre del conector: OSD

(W17)

Núm

del

Uso

alfiler

1 Vcc5

2 KPAD0

3 KPAD1

4 KPAD2

5 KPAD3

6

7

8 Vcc5-SB

9 GND

10

11 IR

12 KPAD4

13 KPAD5

14 KPAD6

15 KPAD7

LED-ROJO

LED-VERDE

POTENCIA-SW

Nombre del conector:

ALTAVOZ (W3)

Núm del

alfiler

1 ALTAVOZ-SW

2 ALTAVOZ-FUERA13 ALTAVOZ-FUERA1+

4 GND

5 ALTAVOZ-FUERA 26 ALTAVOZ-FUERA2+

Uso

14

Page 16

p

7. Análisis de fracasos

TELEVISOR PDP MANUAL DE REPARACIONES

Sin trama

Juzgue si el voltaje y la

frecuencia de entrada

están correctos

Juzgue si el producto

está en el modo

espera por el control

remoto

Verifique si la señal

receptada ahora está

correcta

Entre voltaje y frecuencia

según las especificaciones

Preione el botón

potencia para

encenderlo

Verifique la fuente

externa de señal

Apague el producto y

después de 2 minutos

vuelva a encenderlo

ara verificar si

Abra la tapa trasera, entre

en el modo encendido para

verificar el voltaje

CON8002-220v del PDP

Si ahora funciona

bien, hubo el

fracaso

Reemplace el interruptor de

potencia o el filtro con

funcionamiento malo

15

Page 17

TELEVISOR PDP MANUAL DE REPARACIONES

p

p

Verifique el voltaje

salida

CON8011/CON8009 de

la tabla de

otencia

Verifique y repare el voltaje

de tabla potencia de la

pantalla visualización

Verifique el conector

voltaje entrada J1/J3

de la tabla principal

Verifique los voltajes de

suministro de la tabla

principal: Vcc5-SUB

(IC-U15-4#), Vcc3

(IC-U8-2#)

Verifique o transponga el

hilo de datos señal del

conector

Verifique y transponga el

hilo del conector

Verifique o transponga

U15-1.#IN,

D1,CE21,CE26.U8-2#I

N, C198,CE33.

Verifique y transponga la tabla

principal

Verifique la tabla propulsor de la

antalla visualización de PDP y

los pedazos del IC suave, etc.

Verifique otros circuitos

16

Page 18

TELEVISOR PDP MANUAL DE REPARACIONES

r

Visualiza imagen sin sonido

Enciéndalo para

verificar si hay

ruidos

Cambie la tabla de

sintonizado

Verifique si el volumen

está configurado

correctamente

Lea las instrucciones de

operación y vuelva a

configurar el volumen

Verifique la forma

de onda J7 de la

salidad audio del

altavoz

Verifique y cambie el

altavoz

Verifique el IC U4

para ver si la señal

entrada o salida está

correcta

Verifique y cambie el IC

U4

Verifique el IC U3

para ver si la señal

entrada-60#/salida-27

# 28# está correcta

Verifique y cambie el

IC U3

17

Page 19

TELEVISOR PDP MANUAL DE REPARACIONES

r

verifique si hay salida

audio en el alfiler

CN1/CN2-40# del

conecto

Verifique si hay salida

audio en la tabla de

sintonizador (U5-14#)

Cambie la tabla de sintonizador

o el sintonizador

Verifique y cambie el

conector que no funciona bien

18

Page 20

TELEVISOR PDP MANUAL DE REPARACIONES

8. Descripción de ICs y componentes principales

(1) M52790SP/FP

2

INTERRUPTOR AV con CONTROL BUS I

DESCRIPCIÓN

El M52790 es circuito integrado con semiconductor

interruptor AV con el control bus I

Este IC contiene 2-canales de 4-entrada interruptores de

audio y 2-canales de 4-entrada interruptores de vídeo.

Cada canal puede controlarse independientemente.

Los interruptores de vídeo contienen amplificadores, que

pueden controlarse un aumento de salida 0dB o 6dB.

CARACTERÍSTICAS

z Interruptores de vídeo y sonido estereofónico en un

paquete

z Gama ancha de frecuencia (interruptor de

vídeo).......DC-20MHz

z Separación alta (interruptor de

vídeo)..........diafonía-60dB(tìpico) a 1 MHz

z Dos tipos de paquetes son disponibles:SDIP con un

pitch alambre de 1.778mm (M52790SP); y SSOP con

un pitch alambre de 0.8mm(M52790FP)

APLICACIÓN

Equipo de vídeo

CONDICIÓN DE OPERACIÓN

RECOMENDADA

Voltaje de suministro 4.7V-9.3V

Voltaje de suministro establecido 5V, 9V

Corriente de salida máxima 63mA (a 9V)

2

C.

C

CONFIGURACIÓN DE ALFILERES (VISTA VERTICAL)

VIDEO 2 EN

Lch 2 EN

C 2 EN

Rch 2 EN

Y 2 EN

VIDEO 3 EN

Lch 3 EN

C 3 EN

Rch 3 EN

Y 3 EN

VIDEO 4 EN

Lch 4 EN

C 4 EN

Rch 4 EN

Y 4 EN

Esbozo 36P4E

(Pitch alambre: 1.778mm)

CONFIGURACIÓN DE ALFILERES (VISTA VERTICAL)

VIDEO 2 EN

Lch 2 EN

C 2 EN

Rch 2 EN

Y 2 EN

VIDEO 3 EN

Lch 3 EN

C 3 EN

Rch 3 EN

Y 3 EN

VIDEO 4 EN

Lch 4 EN

C 4 EN

Rch 4 EN

Y 4 EN

VCC

SCL

SDA

VCC

SCL

SDA

SINTONIZADOR EN

Lch T EN

C EN

Rch T EN

Y IN

V 1 FUERA

Lch 1 FUERA

C 1 FUERA

Rch 1 FUERA

Y 1 FUERA

V 2 FUERA

Lch 2 FUERA

C 2 FUERA

Rch 2 FUERA

Y 2 FUERA

PORALIZACIÓN

CHIP SELECCIÓN

GND

SINTONIZADOR EN

Lch T EN

C EN

Rch T EN

Y IN

V 1 FUERA

Lch 1 FUERA

C 1 FUERA

Rch 1 FUERA

Y 1 FUERA

V 2 FUERA

Lch 2 FUERA

C 2 FUERA

Rch 2 FUERA

Y 2 FUERA

PORALIZACIÓN

CHIP SELECCIÓN

GND

Esbozo 36P2R-D

(Pitch alambre: 0.8mm)

19

Page 21

BLOQUE DIAGRAMA

SINTONIZADOR EN

VIDEO 2 EN

VIDEO 3 EN

VIDEO 4 EN

Y 2 EN

Y 3 EN

Y 4 EN

TELEVISOR PDP MANUAL DE REPARACIONES

V 1 FUERA

C EN

Y EN

Y 1 FUERA

Y 2 FUERA

C 2 EN

C 3 EN

C 4 EN

Rch T EN

Rch 2 EN

Rch 3 EN

Rch 4 EN

Lch T EN

Lch 2 EN

Lch 3 EN

Lch 4 EN

PORALIZA

CIÓN

PORALIZA

CIÓN

Control I2C

V 2 FUERA

C 1 FUERA

C 2 FUERA

C 2 FUERA

Rch 1 FUERA

C 2 FUERA

Rch 2 FUERA

Lch 1 FUERA

Lch 2 FUERA

CHIP SELECCIÓN

20

Page 22

TELEVISOR PDP MANUAL DE REPARACIONES

r

(2) MSP3450G

Familia del Procesador Sonido de Multiestándar

Emite Nota: Barras de revisión indican cambios significantes a la edición anterior. La descripción de hardware y

software en este documento es válida para versión B5 de MSP 3450G y las siguientes versiones.

Introducción

La familia MSP 3450G de Procesadores de Sonido de un solo chip de Multiestándar abarca el procesamiento de

sonido de todos estándares mundiales de televisión analógica y los estándares de sonido digital NICAM. El

procesamiento completo del sonido de televisión, empezando con señal-entrada de sonido analógico IF, hasta

AF-fuera analógico procesado es realizado en un solo chip. La ilustración 4 es un bloque diagrama funcional

simplificado del MSP 3450G.

Esta generación nueva de ICs de procesar sonido de televisión ahora incluye versiones para procesar la señal sonido

de televisión de multicanal (Multichannel television sound: MTS) en conformidad con el estándar recomendado por el

Broadcast Television Systems Committee (BTSC). La reducción de ruido DBX o Reducción de Ruido MICRONAS

(MICRONAS Noise Reduction: MNR) se realiza alineación libre.

Otros estándares son el estándar múltiplex FM-FM de Japón (EIA-J) y el estándar de Radiodifusión Estereofónica

FM.

Los ICs actuales tienen que realizar procedimientos ajustes en fin de obtener buena separación estereofónica para

BTSC y EIA-J.

El MSP 3450G tiene el mejor funcionamiento estereofónico sin ningún ajuste.

Todas versiones de MSP 3450G son compatibles con MSP 3450D en alfiler, software y otros. El MSP 34x0G

simplifica más el software controlador. Selección estándar necesita transmisión de un solo I

El MSP 34x0G tiene funciones automáticas incorporadas: el IC es capaz de detectar automáticamente el estándar del

sonido actual (Detección Automática de Estándar). Además, niveles piloto y señales de identificación pueden ser

evaluados internamente con cambio posterior entre mono/estéreo/

bilingüe; no hace falta interacción de I2C (Selección

Automática de Sonido).

Los ICs se producen con tecnología CMOS submicron. El MSP 34x0G es disponible en los siguientes paquetes:

PLCC68, PSDIP64, PSDIP52, PQFP80 y PLQFP64.

Sonido IF1

Sonido IF2

Demodula

dor

Preprocesa

miento

Prescala

Procesamie

nto de

sonido

altavoz-fue

Procesamient

o de sonido

auricular

Selecci

ón

entrada

SCAR

T DSP

Prescala

Selección fuente

Ilustración 4: bloque diagrama funcional simplificado del MSP 3450G

2C sólo.

Altavoz-fuerte

Altavoz de bajos

Auricular

Selección

salida

SCART

21

Page 23

TELEVISOR PDP MANUAL DE REPARACIONES

g

(3) VPC323OD

HOJA DE DATOS PRELIMINARES

Procesador Vídeo de Filtro Peine

Introducción

El VPC 3230D es un extremo-delantero de vídeo de buena calidad y de un solo chip, que es para televisores de 4:3 y

16:9, 50/60-Hz y 100/120 Hz. El puede ser combinado con otros miembros de la familia DIGIT3000 IC (como DDP

331x) y/o puede ser utilizado con otros productos.

El VPC 3230D tiene las siguientes características principales:

– Separador Y/C de filtro peine 4H adaptable de gran rendimiento con cumbre vertical ajustable

– descodificador de color de multi-estándar PAL/NTSC/SECAM incluídos todos subestándares.

–cuatro entradas de CVBS, una de S-VHS, una salida CVBS

– Dos entradas de componente RGB/YC

– Convertidores A/D incorporados de buena calidad y circuitos asociados sujetador y AGC

– procesamiento sincrónico de multi-estándard

–escalamiento horizontal lineal (0.25 ... 4) y escalamiento horizontal no-lineal ‘visión panorámica’

– PAL+ preprocesamiento

– reloj línea-cerrada, datos y sinc, o interfaz de 656-salida

– cumbre, contraste, brillo, saturación de color y matiz para RGB/YC

– mezclador suave de buena calidad controlado por Vacío Rápido

– procesamiento PIP para cuatro tamaños de imagen (1/4,1/9,1/16, o 1/36 de tamaño normal) con resolución de 8-bit

– 15 configuraciones visualización PIP predefinidas y modo experto (completamente programable)

– interfaz control para memoria de campo externo

– interfaz I

2

C-bus

– un cristal 20.25-MHz, pocos componentes externos

– paquete PQFP de 80-alfiler

Arquitectura del Sistema

Ilustración.5 es un bloque diagrama del procesador de vídeo.

rCb, una entrada Vacío Rápido (Fast Blank: FB)

rCb y CVBS/S-VHS

Extremo-d

elantero

Analógico

Extremo-Del

antero

Componente

ico

Analó

Filtro peine

adaptable

Procesamie

Matriz

Contraste

Saturación

Brillo

Matiz

Descodifica

dor de color

Matiz

Saturación

Mezclador

Escalador 2D

Modo de

panorama

Contraste

Brillo

Cumbre

Bus I2C

Gen

Reloj

Ilustración. 5: bloque diagrama del VPC 3230D

Formatead

or de salida

Control de

memoria

LLC Reloj

Generación

Sinc+Reloj

22

Page 24

Configuración de Alfileres

TELEVISOR PDP MANUAL DE REPARACIONES

Ilustración. 6: paquete PDFP de 80-alfiler

23

Page 25

TELEVISOR PDP MANUAL DE REPARACIONES

(4) Z86229

DESCODIFICADOR CCD DE LÍNEA 21 NTSC

CARACTERÍSTICAS

Visulalización en

Aparatos

Velocidad

(MHz)

Cuenta

alfiler/Tips de

Paquete

Gama de

Temperatura

Estándar

Pantalla y

Subtitulación

Cerrada

Extracción de Datos Automática

Clasificación

de Programa

Hora de

Día

Z86229 12 18-PinDIP,SOIC O

z Descodificador de línea 21 autónomo completo

para Servicios Subtitulado-Cerrados y de Datos

Extendidos (Extended Data Services: XDS).

z Preprogramado para Facilitar Conformidad

Completa con Especificaciones EIA-608 para

Servicios de Datos Extendidos.

z Extracción Automática y Salida en Serie de

Paquetes XDS Especiales (Hora de Día, Zona

Horaria Local y Bloqueo de Programa)

z Filtro XDS Programable para un Paquete XDS

Específico

z Solución Rentable para Bloqueo de Violencia

NTSC dentro de Ventanas Imagen-en-Imagen

(Picture-in-Picture: PiP)

DESCRIPCIÓN GENERAL

°C to + 70°C

z Comunicaciones Mínimas y Control en Alto

Facilitan Ejecución Simple de Bloqueo de

Violencia, Subtitulación Cerrada y Características

de Configuración Reloj Auto.

z Programable, Visualización en Pantalla (On-Screen

Display: OSD) para crear OSD de Pantalla

Completa o Subtitulación dentro de Ventanas

Imagen-en-Imagen (Picture-in-Picture: PiP)

z Posición de Visualización Horizontal Programable

de usuario para Centración y Ajustes fáciles de

OSD.

z Datos en Serie I2C y Comunicación de Control

z Apoya 2 Direcciones I2C Seleccionables

SÍ SÍ SÍ

Capaz de procesar datos de Intervalo Vacío Vertical (Vertical Blanking Interval: VBI) de ambos campos del

marco vídeo en datos, el descodificador de línea 21 Z86229 proporciona una solución de múltiples

características para cualquier televisión o aplicación. La naturaleza fuerte del Z86229 ayuda al aparato que se

ajuste al formato de transmisión definido en la Ley de Circuitos de Descodificador de Televisión (Television

Decoder Circuits Act) de 1990, y esté de acuerdo con la Especificación de Asociación de Industria Electrónica

608 (Electronics Industry Association specification) (EIA–608).

La corriente datos de Línea 21 consiste en datos desde varios canales de datos múltiplex juntos. Campo 1

consiste en cuatro canales de datos: Dos Subtítulos y dos Textos. Campo 2 consiste en cinco canales adicionales

de datos: dos Subtítulos, dos Textos y Servicios de Datos Extendidos (XDS). La estructura de datos XDS se

define en EIA–608. El Z86229 puede recuperar y visualizar datos transmitidos en cualquiera de estos nueve

canales.

El Z86229 puede recuperar y sale a un procesador anfitrión por el bus en serie I

2C. El paquete de datos XDS

recuperado se defime más en la especificación EIA–608. Los filtros XDS en-chip en el Z86229 son totalmente

programables, activando recuperación de esos paquetes de datos XDS sólo seleccionados por el usuario. Esta

función permite el aparato que extraiga información necesitada XDS con el sistema adecuado del filtro XDS

para compatibilidad en diversos TVs, VCRs, y cajas Set-Top.

Además el Z86229 es adecuado para controlar el vídeo de línea 21 visualizado en ventana PiP para bloqueo de

violencia, CCD y otros servicios de datos XDS.

24

Page 26

TELEVISOR PDP MANUAL DE REPARACIONES

DESCRIPCIÓN DE ALFILERES

Tabla 1. Identificación de alfileres de Z86229*

Núm Símbolo Función Dirección

I2C SEL

VERDE

AZUL

SEN

HIN

SNS

VÍDEO

CSYNC

LPF

ROJO

CAJA

SDO

SCK

SDA

/DENTRO

V

EN

V

DD

(A)

V

SS

RREF

Ilustración. 2 Configuraciones de alfileres de Z86229

CLASIFICACIÓN MÁXIMA ABSOLUTA*

1 I2C SEL I2C Selección de

Dirección

2 VERDE Salida de Vídeo Salida

3 AZUL Salida de Vídeo Salida

4 SEN Activar en serie Entrada

5 HIN Horizontal En Entrada

6 SMS Selección de Modo en

Serie

7 VÍDEO Vídeo Compuesto Entrada

8 CSYNC Sinc Compuesta Salida

9 LPF Filtro de bucle Salida

10 RREF Referencia de

Resistidor

11 VSS (A) Suministro de

Potencia

(Analógico)

GND

12 VDD Suministro de

Potencia

13 VEN/

DENTRO

Vertical En /

Interrupción fuera

14 SDA Datos en Serie

15 SCK Reloj en Serie Entrada

16 SDO Datos en Serie Fuera Salida

17 CAJA Señal Temporización

OSD

18 ROJO Salida Vídeo Salida

Nota: Configuraciones de alfileres DIP y SOIC son iguales.

Entrada

Entrada

Entrada

Entrada/Salida

Entrada/Salida

Salida

Símbolo Parámetro Valor Unidad

VDD Voltaje de Suminitro DC -0.5 to 6.0 V

VEN Voltaje de Entrada DC -0.5 to V

V

I

I

I

P

T

T

Voltaje de Salida DC -0.5 to V

FUERA

Corriente Entrada DC por Alfiler +10 mA

EN

Corriente Salida DC por Alfiler +20 mA

FUERAN

Corriente de Suminitro DC +30 mA

DD

Disipación de Potencia por Aparato 300 mW

D

Temperatura de Almacenaje -65 to +150

STG

Temperatura alambre, 1 mm de Caso durante 10 segundos 260

L

+0.5 V

DD

+0.5 V

DD

°C

°C

Notas:

Voltajes referidos a VSS(A). Valores superiores a los máximos mencionados arriba pueden causar daño al aparato.

Debe restringir la operación funcional en los límites especificados en las tablas Características DC y AC o la Sección

de Descripción de Alfiler.

25

Page 27

TELEVISOR PDP MANUAL DE REPARACIONES

(5) HY57V641620HG

DRAM

DESCRIPCIÓN

El Hynix HY57V641620HG es un DRAM Sincrónico de 67,108,864-bit CMOS, que conviene para aplicaciones en

Móbil, porque necesita consumo de potencia bajo y gama de temperatura extendida. HY57V641620HG se organiza

como 4 bancos de 1,048,576x16

HY57V641620HG está facilitando operación totalmente sincrónica referida a un borde positivo del reloj. Todas

entradas y salidas están sincronizadas con el borde montar de entrada del reloj. Los ficheros de datos son tramitados

internamente para lograr ancho de banda muy alta. Todos los niveles de voltaje de entrada y salida son compatibles

con LVTTL.

Opciones programables incluyen el largo de tubería (Lea latencia de 2 o 3), el número de ciclos consecutivos de leer y

escribir iniciados por una orden de solo control (largo explosión de 1,2,4,8 de página completa) y la secuencia cuenta

explosión (secuencial o entrecruzada). Una explosión de ciclos de leer o escribir en progreso puede ser terminado por

un comando de terminar explosión o puede ser interrumpido o reemplazado por un comando nuevo explosión de leer

y escribir en cualquier ciclo. (Este diseño tramitado no está restringido por la regla 2N)

CARACTERÍSTICAS

z Suministro de potencia solo 3.3+0.3V

z Todos alfileres del aparato son compatibles con

interfaz LVTTL.

z Estándar JEDEC 400mil 54 alfiler TSOP-II con

0.8mm de pitch alfiler.

z Todas entradas y salidas referidas al borde positivo

del reloj sistema.

z Función máscara de datos por UDQM o LDQM

z Operación de cuatro bancos interna

z Actualización auto y actualización él mismo

z 4096 ciclos actualización/64ms

z Largo Explosión y Tipo Explosión Programables

z -1,2,4,8 o Página Completa para Explosión

z -1,2,4 o 8 para Explosión Entrecruzada

z Latencia CAS Programable; 2,3 Relojes

INFORMACIÓN DE ORDEN

Núm. Parte

HY57V641620HGT-51/551/61/71

HY57V641620HGT-KI

HY57V641620HGT-81

HY57V641620HGT-HI

HY57V641620HGT-PI

HY57V641620HGT-SI

HY57V641620HGLT-51/551/61/71

HY57V641620HGLT-KI

HY57V641620HGLT-81

HY57V641620HGLT-HI

HY57V641620HGLT-PI

HY57V641620HGLT-SI

Nota: VDD (Min) de HY57V641620HG(L)T-51/551/61 es 3.135V

Frecuencia de

Reloj

200/183/166/143MHZ

133

MHZ

133

MHZ

125

MHZ

100

MHZ

100

MHZ

200/183/166/143MHZ

133

MHZ

133

MHZ

125

MHZ

100

MHZ

100

MHZ

Potencia Organización Interfaz Paquete

Normal

4Bancos x

1Mbits x 16

Potencia

Baja

Secuencial

LVT TL

400mil

54alfiler

TSOP II

26

Page 28

TELEVISOR PDP MANUAL DE REPARACIONES

CONFIGURACIÓN DE ALFILERES

DESCRIPCIÓN DE ALFILERES

ALFILER

CLK Reloj

CKE Reloj activa

CS Selección Chip Activa o desactiva todas entradas excepto CLK,CKE y DQM

BA0,BA1 Dirección Banco

A0-A11 Dirección

RAS,CAS,WE

LDQM,UDQM

DQ0-DQ15 Entrada/Salida de Datos Alfiler de entrada/salida de datos múltiplex

VDD/VSS

V

DDQ/VSSQ

NC No hay Conexión

NOMBRE DEL

ALFILER

Estroboscopia de

Dirección Fila,

Estroboscopia de

Dirección Columna,

Escribir Activa

Máscara de

Entrada/Salida de Datos

Suministro de

Potencia/Tierra

Potencia de Salida de

Datos/Tierra

DESCRIPCIÓN

La entrada del reloj sistema. Todas otras entradas están registradas al

SDRAM en el borde creciente de CLK.

Controla la señal interna de reloj, cuando esté desactivado, el SDRAM

estará en uno de los siguientes estados: apagado, suspendido o

actualización él mismo

Selecciona banco de ser activado durante actividad RAS

Selecciona banco de ser leído/escrito durante actividad CAS

Dirección Fila: RA0~RA11, Dirección Columna: CA0~CA7

Bandera Auto-Precarga: A10

RAS, CAS y WE define la operación

Consulte la tabla de función por detalles

Controla altavoces de bajos de salida en el modo leer y datos entrada

de máscaras en el modo escribir.

Suministro de potencia para circuitos internos y altavoces de bajos de

entrada

Suministro de potencia para altavoces de bajos de salida

No hay conexión

27

Page 29

(6) TDA8944J

AMPLIFICADOR DE AUDIO ESTEREOFÓNICO

1. Descripción General

El TDA8944J es un amplificador de potencia audio de doble-canal con una potencia

sali

da de 2 x 7 vatio a una carga 8 ? y a un suministro 12V. El circuito contiene dos

amplificadores de Puente Atada Carga (Bridge Tied Load: BTL) con una etapa de salida

do-NPN y lógica espera/muda. El TDA8944J viene en un paquete de potencia

to

DIL-bent-SI

(print

Una huella PCB tiene cabida de ambos productos de mono y estéreo.

2. Características

L (DBS) de 17-alfiler. El TDA8944J es tabla de circuito-impreso

ed-circuit board: PCB) compatible con todos otros tipos en la familia TDA894x.

TELEVISOR PDP MANUAL DE REPARACIONES

3. Aplicaciones

4. Datos de consulta rápida

Tabla 1: Datos de consulta rápida

Símbolo Parámetro Condiciones Min Tip Max Unidad

V

I

I

Pocos componentes externos

Aumento fijado

Modo espera y mudo

No hay plaf al cambio encendido/apagado

Corriente baja en espera

Rechazo onda de voltaje de suministro alto

Sale cortocircuito protegido a tierra, suministro y a través de la carga

Protegido térmicamente

Tabla de circuito-impreso compatible

Aplicaciones principles realimentación (p.ej. sonido de televisión)

Audio PC

Audio portátil

q

stb

CC

Voltaje de suministro

Corriente de suministro

quie

scente

Corriente de suministro

en

espera

VCC=12 V; RL=

6 12 18 V

- 24 36 mA

- - 10

uA

28

Page 30

5. Información de orden

TELEVISOR PDP MANUAL DE REPARACIONES

Tabla 1: Datos de consulta rápida

Símbolo Parámetro Condiciones Min Tip Max Unidad

P

O

THD

G

V

SVRR

Potencia de salida

Distorsión

tota

armónica

l

Aumento de voltaje

Rechazo de onda de

voltaje

suministro

THD=10%; RL=8Ω;

=12V

V

CC

=1W

P

O

31 32 33 dB

50 65 - dB

6 7 - W

- 0.03 0.1 %

Tabla 2: Información de orden

Número de tipo Paquete

6. Bloque diagrama

TDA8944J

Nombre

Descripción Versión

DBS17P Paquete de potencia plástico DIL-bent-SIL; 17

ala

mbres (largo alambre 12 mm)

SOT243-1

LÓGICA

ESPERA/MU

DA

PROTECCIÓN

DE

RTOCIRCUIT

CO

O Y

TEMPE

RATURA

Ilustración 9. Bloque diagrama

29

Page 31

TELEVISOR PDP MANUAL DE REPARACIONES

r

(7) Procesador de Imagen PW166

Controlador IC de Visualización de Panel Plano XGA/SXGA

General

El Procesador de Imagen PW166/PW166B es un

“sistema-en–un-chip” altamente incorporado que interface

entradas analógicas, digitales y de vídeo en virtualmente

cualquier formato a un sistema de proyección digital o

visualización de multimedia. El PW 166/PW166B es

alfiler-compatible con el PW 164.

Una memoria intermedia de marco SDRAM clavada y

controlador de memoria realizan conversión de velocidad marco.

Imagenes ordenador de VGA a UXGA a casi cualquier velocidad

de actualización pueden ser cambiada a adaptarse a un aparato de

visualización objetivo de frecuencia-fijada con cualquier

resolución hasta SXGA con color completo de 24-bit.

El PW166/PW166B tiene escalamiento avanzado de segunda

generación de imagen que facilita escalamiento de imagen

programable, horizontal y vertical completamente. Temática

permite efectos verticales de temática. Además, escalamiento

no-lineal está apoyado para control de escalamiento preciso, con

fuentes razón de aspecto 16:9 y visualizaciones. Este

escalamiento de buena-calidad—junto con Circuitos de

Optimización Imagen Automática—facilita imagenes claras de

pantalla-completa, centradas en la pantalla, sin ningún ajuste

manual.

El PW166/PW166B también tiene descodificación sincrónica

avanzada de segunda generación, que facilita todo apoyo para una

gran variedad de tipos sincrónicos. Esto incluye entrecruzado,

progresivo, sinc-en-verde, y TMDS DE (Fecha Activada) sólo.

El Procesador Imagen PW166/PW166B apoya datos de vídeo

NTSC o PAL con fuentes de razón de aspecto 4:3, tales como

DVD o HDTV. Escalamiento no-lineal y escalador horizontal y

vertical separado hace que estas entradas estén cambiadas

óptimamente para resolución nativa y razón aspecto del aparato

visualización.

El PW166B utiliza un PLL incorporado para sincronizar la

temporización del interfaz visualización con la de entrada. Esto

sólo requiere un solo cristal externo para generar todos relojes

necesarios para el sistema (PW166B sólo).

Un controlador incorporado OSD facilita OSDs basados en

bit-mapa con 16 colores de una paleta de color 64K. El

controlador OSD apoya funciones transparentes y translucientes.

El PW166B facilita una salida de Modulación de Ancho Pulso

(Pulse Width Modulation:PWM) para luz fondo de coste bajo o

control audio.

Con código de fuente referencia y un microprocesador en-chip,

fabricantes pueden desarrollar productos de muchas

características con tiempo rápido al mercado. Características

programables incluyen el interfaz de usuario, pantalla puesta en

marcha de cliente, todas características de imagen automáticas y

efectos especiales de pantalla.

Relojes

Ordenado

Vídeo

Visualización

Descodifi

cador de

PW166/166B

Bloque diagrama del sistema

Características

z Escalamiento de imagen de segunda generación

z Optimización de imagen automática de segunda generación

z Procesamiento de vídeo

z Imagen-en-imagen (PIP)

z Conversión de velocidad marco

z Escalamiento multi-región, no-lineal

z Matriz de color para ajuste temperatura color mejorado

z En-tabla PLLs para generar MCLK y DCLK (PW166B

sólo)

z Visualización en-pantalla

z Microprocesador en-chip

z Depuración JTAG

z Salida Hardware PWM

Aplicaciones

z monitores de panel plano

z Sistema de Proyección Digital

z visualización de multimedia

Aparato Aplicación Paquete

PW166-10T

PW166B-10T

PW166-10TK

PW166B-10TK

PW166-20T

PW166B-20T

PW166-20TK

PW166B-20TK

Hasta SXGA en,

SVGA/XGA fuera, sin

temática

Hasta SXGA en,

SVGA/XGA fuera,

con temática

Hasta SXGA en,

SVGA fuera, sin

temática

Hasta SXGA en,

SVGA fuera, con

temática

256 PBGA

30

Page 32

TELEVISOR PDP MANUAL DE REPARACIONES

Ilustración 11.Diagrama de alfiler PW166 – Vista Vertical

31

Page 33

TELEVISOR PDP MANUAL DE REPARACIONES

b

b

Descripciones de Alfileres del Procesador de Imagen

Nombre Alfiler(es) Tipo Función

Port Gráficos

Port gráficos pixel reloj entrada. Típicamente propulsado por un Reloj Gport PLL

GCLK H19 ID

externo. El alfiler GCLK puede ser seleccionado como fuente para el GCLK

interno que es utilizado para captura imagen Gport y para el divididor PLL (vea

GCKPOL & GCKPOL)

Port gráficos pixel activa entrada. Utilizado para control de flujo externo cuando

EXTFCE =1. Cuando GPENSOG esté alto, pixel RGB entrada es válido. Utilizar

GPENSOG permite captura de datos no-cercanos. Cuando EXTFCE=0, este es

GPENSOG G20 ID

entrada de port gráficos Sinc-En-Verde (Sync-On-Green, SOG). Propulsado por

circuito desprendedor sinc externo, este alfiler es controlado (estado bit SOGACT)

y puede facilitar información compuesta sinc (depende de bits SOGEN &

COMPEN)

Port gráficos vertical sinc entrada. Indica inicio del siguiente campo o marco de

GVS J17 ID

datos entrada. GVS puede ser activo-alto o activoVPOL y VSOK. GVS no se utiliza cuando se utilice una fuente compuesta digital

sinc (SOGEN=1 o COMPEN=1)

Port gráficos horizontal sinc entrada. Indica inicio de la siguiente línea de datos

entrada. Esta señal es internamente corregida de polaridad y controlada para

GHS G19 ID

contenido sinc compuesto (estado bits HSOK, HPOL, & COMP). GHS puede

facilitar informaciòn sinc horizontal o información sinc compuesta digital (depende

de bit COMPEN). GHS es también utilizado como entrada al circuito retraso fase

reloj que produce la señal GREF.

Port gráficos PLL realimentación/línea avanza entrada. Este alfiler tiene tres

funciones diferentes depende del ajuste registro para EXTFBK y EXTFCE:

its

ajo como determinado por

GFBK

GRE0

GRE1

GRE2

GRE3

GRE4

GRE5

GRE6

GRE7

GGE0

GGE1

GGE2

GGE3

GGE4

GGE5

GGE6

GGE7

EXTFBK EXTFCE

0 X

H17 I/O

1 0

1 1

M20 ID

N19 ID

N18 ID

N17 ID

N20 ID

P20 ID

P19 ID

R20 ID

F18 ID

E19 ID

E20 ID

J18 ID

H20 ID

J19 ID

J20 ID

K19 ID

Port gráficos datos rojo par sub-pixel entrada. Datos de canal rojo para modo solo

pixel o datos pixel rojo par para modo entrada de doble pixel. Datos canal Pr para

entrada YpbPr

Port gráficos datos verde par sub-pixel entrada. Datos de canal verde para modo

solo pixel o datos pixel verde par para modo entrada de doble pixel. Datos canal Y

para entrada YpbPr.

GFBKOUT: una salida desde el divididor PLL interno.

GFBKIN: una entrada al pulso realimentación desde un

divididor PLL externo. En modo captura marcha libre, esta

señal se utiliza para definir la región captura horizontal

(junto con CAPL y CAPW), y avanza el controlador captura

Gport a la siguiente lìnea entrada. El bit LAVPOL es utiliza

para seleccionar la polaridad de GFBKIN.

GLAV: una entrada a avance línea de port gráficos. Utilizado

en modo captura de control flujo externo. Cuando GLAV

haga transición (depende de bit LAVPOL), avanza el

controlador captura Gport a la siguiente lìnea entrada.

Función GFBK

32

Page 34

TELEVISOR PDP MANUAL DE REPARACIONES

Descripciones de Alfileres del Procesador de Imagen (continuado)

Nombre Alfiler(es) Tipo Función

GBE0 D16 ID

GBE1

GBE2 C17 ID

GBE3 B18 ID

GBE4 A19 ID

GBE5 B19 ID

GBE6 A20 ID

GBE7 D18 ID

GRO0 K20 ID

GRO1 L17 ID

GRO2 L18 ID

GRO3 L19 ID

GRO4 L20 ID

GRO5 M18 ID

GRO6 M17 ID

GRO7 M19 ID

GGO0 E17 ID

GGO1 C19 ID

GGO2 B20 ID

GGO3 C20 ID

GGO4 E18 ID

GGO5 F17 ID

GGO6 D19 ID

GGO7 D20 ID

GBO0 B15 ID

GBO1 A16 ID

GBO2 C15 ID

GBO3 D15 ID

GBO4 B16 ID

GBO5 A17 ID

GBO6 C16 ID

GBO7 B17 ID

GREF H18 0

GBLKSPL F19 0

GCOAST F20 0

VCLK D12 ID

VPEN C13 ID

WS A14 ID

VHS B14 ID

VFIELD A15 ID

A18 ID

Port gráficos datos azul par sub-pixel entrada. Datos de canal azul para modo solo pixel o datos

pixel azul par para modo entrada de doble pixel. Datos canal Pb para entrada YpbPr.

Port gráficos datos rojo impar sub-pixel entrada. No utilizado para modo solo pixel, datos pixel

rojo impar para modo entrada de doble pixel.

Port gráficos datos verde impar sub-pixel entrada. No utilizado para modo solo pixel, datos pixel

azul impar para modo entrada de doble pixel.

Port gráficos datos azul impar sub-pixel entrada. No utilizado para modo solo pixel, datos pixel

azul impar para modo entrada de doble pixel.

Port gráficos PLL referencia salida. Versión retrasada de GHS separado sinc interno. Tipicamente

conectado a entrada REF de PLL. Si cambia los bits FASE, cambia la cantidad de retraso entre GHS y

GREF.

Port gráficos negro muestra sujetador pulso salida. Utilizado como parte de un circuito restauración DC

externo para sujetar el nivel negro de datos RGB analógicos Gport a la tierra. Este pulso ocurre después

de Hsync y es programable (BKSPOL, BKSCEN, BKSBEG, & BKSWID)

Port gráficos PLL costa control salida. Utilizado para activar costa PLL (ignora GREF y GFBK )

durante vacío vertical. Utilizado para evitar el PLL de reaccionar a pulsos HS extra o perdidos durante

vacío vertical. Costa activa y duración es programable (PLLCM, PLLCB & PLLCE)

Port vídeo

Port vídeo pixel reloj. Controla captura imagen de port vídeo. Típicamente propulsado por

descodificador vídeo externo.

Por vídeo pixel activa entrada. Utilizado para control flujo externo cuando EXTFCE=1. cuando VPEN

sea alto, datos pixel entrada son válidos. Utilizar VPEN permite captura de datos no-cercanos.

Vídeo vertical sinc indica inicio del siguiente campo o marco de datos desde el descodificador vídeo

externo. VVS puede ser activo-alto o activo-bajo como determinado por VPOL. VVS no se utiliza

cuando una fuente sinc digital compuesta se utilice. (COMPEN)

Vídeo horizontal sinc indica el inicio de la siguiente línea de datos entrada desde el descodificador

vídeo externo. VHS puede ser activo-alto o activo-bajo como determinado por HPOL. Indica sinc

compuesto cuando COMP=1.

indicador de campo impar/par Vídeo. Indica si campo impar o par de entrada entrecruzada está

capturada como lo determinado por FLDINV y FLDSEL. Información del campo también puede ser

derivada desde VVS y VHS, por eso VFIELD no se necesita en algunas aplicaciones

33

Page 35

TELEVISOR PDP MANUAL DE REPARACIONES

Descripciones de Alfileres del Procesador de Imagen (continuado)

Nombre Alfiler(es) Tipo Función

VY0 D8 ID

VY1

VY2 B7 ID

VY3 A7 ID

VY4 B8 ID

VY5 D9 ID

VY6 C9 ID

VY7 A8 ID

VUV0 B9 ID

VUV1 A9 ID

VUV2 B10 ID

VUV3 A10 ID

VUV4 D11 ID

VUV5 A11 ID

VUV6 C12 ID

VUV7 B13 ID

DCKEXT Y13 ID

DCLK W12 O

DVS V13 O

DHS U13 O

DEN Y15 O

DRE0 R19 O

DRE1 T20 O

DRE2 R18 O

DRE3 R17 O

DRE4 T18 O

DRE5 U19 O

DRE6 T17 O

DRE7 V20 O

DGE0 U18 O

DGE1 V19 O

DGE2 W20 O

DGE3 W19 O

DGE4 Y20 O

DGE5 V17 O

DGE6 U16 O

DGE7 W18 O

DBE0 Y19 O

DBE1 Y18 O

DBE2 V16 O

DBE3 U15 O

DBE4 Y16 O

DBE5 V15 O

DBE6 W16 O

DBE7 W15 O

C8 ID

Vídeo Port Y Pixel Datos. Puede operar en tres modos diferentes:

Datos Y en modo YUV 4:2:2;

Datos U en modo YUV 4:4:4;

Datos verdes en modo RGB 24-bit.

Vídeo Port UV Pixel Datos. Puede operar en tres modos diferentes:

Datos UV en modo YUV 4:2:2;

Datos V en modo YUV 4:4:4;

Datos azules en modo RGB 24-bit.

Port visualización

Visualiza reloj entrada. No hace falta cuando use en–chip PLL (PW166B sólo)

Visualiza pixel reloj salida. Activado cuando DCLKEN=1. Polaridad es invertida

cuando DCPOL=1. Marcha a 1/2 velocidad pixel cuando DCK2EN=1.

Visualiza vertical sinc salida. Polaridad y temporización controladas por VSPOL,

VPLSE, y VDLY.

Visualiza horizontal sinc salida. Polaridad y temporización controladas por

HSPOL,HPLSE.

Visualiza pixel activa

Visualiza datos rojo par salida sub-pixel en modo salida de doble pixel.

Visualiza datos rojo sub-pixel salida en modo salida de solo pixel.

Visualiza datos verde par salida sub-pixel en modo salida de doble pixel.

Visualiza datos verde sub-pixel salida en modo salida de solo pixel.

Visualiza datos azul par salida sub-pixel en modo salida de doble pixel.

Visualiza datos azul sub-pixel salida en modo salida de solo pixel.

34

Page 36

TELEVISOR PDP MANUAL DE REPARACIONES

Descripciones de Alfileres del Procesador de Imagen (continuado)

Nombre Alfiler(es) Tipo Función

DRO0 Y12 O

DRO1

DRO2 Y11 O

DRO3 U10 O

DRO4 V10 O

DRO5 W10 O

DRO6 Y10 O

DRO7 W9 O

DGO0 Y9 O

DGO1 W8 O

DGO2 V8 O

DGO3 U8 O

DGO4 Y8 O

DGO5 Y7 O

DGO6 W7 O

DGO7 Y5 O

DBO0 V6 O

DBO1 U6 O

DBO2 W5 O

DBO3 Y4 O

DBO4 V5 O

DBO5 Y3 O

DBO6 V4 O

DBO7 Y2 O

WR M4 O

RD M3 O

ROMOE M1 O

ROMWE L2 O

BHEN N2 O

RAMOE L1 O

RAMWE K2 O

CS0 M2 O

CS1 N1 O

EXTINT E2 ID

NMI D1 ID

W11 O

Visualiza datos rojo impar salida sub-pixel en modo salida de doble pixel.

No se utiliza en modo salida de solo pixel

Visualiza datos verde impar salida sub-pixel en modo salida de doble pixel.

No se utiliza en modo salida de solo pixel

Visualiza datos azul impar salida sub-pixel en modo salida de doble pixel.

No se utiliza en modo salida de solo pixel

Escribir Activa. Bajo indica escritura a RAM externo o otros aparatos.

Leer Activa. Bajo indica lectura a RAM externo o otros aparatos.

ROM Salida Activa. Salida baja activa indica una lectura desde ROM externo.

ROM Escribir Activa. Bajo activo indica una escritura al ROM externo.

Alto-byte activa. Bajo indica byte superior de datos está válido.

RAM Salida Activa. Salida baja activa indica una lectura desde RAM externo.

RAM Escribir Activa. Bajo activo indica una escritura al RAM externo.

Variado Chip Selección 0. Salida baja activa selecciona aparatos externos. Cada

Chip Selección descodifica un bloque 256-byte de espacio dirección de CPU (lugar

de bloque es programable )

Variado Chip Selección 1. Salida baja activa selecciona aparatos externos. Cada

Chip Selección descodifica un bloque 256-byte de espacio dirección de CPU (lugar

de bloque es programable )

Interrupción externa pide 0. Puede ser programado a nivel o borde sensitivo. Este

alfiler se convierte en entrada TDI de CPU cuando el depurador JTAG se active.

Interrupción no-máscara. Una entrada alta provoca una interrupción no-máscara al

microprocesador en-chip.

Interfaz de microprocesador

35

Page 37

TELEVISOR PDP MANUAL DE REPARACIONES

Descripciones de Alfileres del Procesador de Imagen (continuado)

Nombre Alfiler(es) Tipo Función

A0 P1 O

A1

A2 N3 O

A3 N4 O

A4 R1 O

A5 R2 O

A6 T1 O

A7 T2 O

A8 R3 O

A9 U1 O

A10 U2 O

A11 R4 O

A12 T3 O

A13 V1 O

A14 W1 O

A15 V2 O

A16 T4 O

A17 U3 O

A18 Y1 O

A19 W2 O

D0 F4 I/O

D1 F3 I/O

D2 E1 I/O

D3 F2 I/O

D4 F1 I/O

D5 G2 I/O

D6 G1 I/O

D7 H1 I/O

D8 H4 I/O

D9 H3 I/O

D10 H2 I/O

D11 J1 I/O

D12 J2 I/O

D13 J4 I/O

D14 J3 I/O

D15 K1 I/O

PORTA0 C2 I/O

PORTA1 B1 I/O

PORTA2 B2 I/O

PORTA3 A1 I/O

PORTA4 C4 I/O

PORTA5 D5 I/O

PORTA6 B3 I/O

PORTA7 A2 I/O

P2 O

Dirección del microprocesador bus salida bits (19:0)

Microprocesador 16-bit bidireccional datos bus.

Alfileres interfaz periféricos

Propósito general IO port.

PORTA7 puede ser seleccionado como la salida PWM.

36

Page 38

TELEVISOR PDP MANUAL DE REPARACIONES

Descripciones de Alfileres del Procesador de Imagen (continuado)

Nombre Alfiler(es) Tipo Función

PORTB0 A3 I/O

PORTB1

PORTB2 D6 I/O

PORTB3 B4 I/O

PORTB4 A4 I/O

PORTB5 C6 I/O

PORTB6 B5 I/O

PORTB7 A5 I/O

IRRCVR0 E4 IU

IRRCVR1 D2 IU

RXD C1 ID

TXD D3 O

RESET E3 IU

MCKEXT W13 ID

MODE2 B6 IU

MODE1 U5 ID

MODE0 A13 ID

XTALIN P3 ID

XTALOUT P4 O

CPUTMS D13 ID

CPUTCK A6 ID

CPUTDO W3 O

VDD2.5

VDD2.5P V7 P

VDD3.3

C5 I/O

Propósito general I/O Port. Puede operar en tres modos diferentes:

8 bits de GPIO en modo Vport YUV 4:2:2;

Datos vídeo Y en modo Vport YUV 4:4:4;

Datos vídeo rojo en modo Vport 24-bit RGB;

IR receptor entra 0

IR receptor entra 1

Recibe datos al port en serie en-chip

Transmite datos desde el port en serie en-chip

Reajuste maestro. Una entrada alta empieza todas lógicas internas.

Reloj sistema memoria. No se necesita cuando se utilice en-chip PLL (PW166B

sólo).

NOTA: Modo 101 es modo normal de operación para PW166B.

Entrada cristal para PLL o entrada Reloj si OSC se desactiva (PW166B sólo)

Salida cristal (PW166B sólo)

JTAG entrada Prueba Modo Selección. Activo alto para activar port prueba JTAG

para depurador CPU.

JTAG Reloj Prueba para modo depurador de CPU

JTAG Prueba Datos Salida modo depurador de CPU.

B12,C3,

C10,C11,

C14,G3,

G18,K18,

P

Potencia digital 2.5V

L3,P18,

V11,V14,

Y14

Potencia analógica PLL 2.5. conecta a suministro 2.5V por un resistidor 27 ohm.

C7,C18

K3,U20

V9,V12

P

Potencia digital 3.3V

V18,V3,Y6

Y17

Variados

Modo

2 1 0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Port Depurador de Microprocesador

Potencia y Tierra

Descripción de modo JTAG 24-Bit PLL OSC

Reservado

Normal con PLL y OSC

Normal

Modo Dirección 24-bit

Modo de probar alfiler

VG (7:0) Salida

0 X 80 Z

0 X 82 O

0 X 83 1

PLL y OSC (PW166B sólo)

modo Emulación PW364

PLL sólo (PW166B sólo)

- - - -

SÍ NO SÍ SÍ

SÍ NO NO NO

SÍ SÍ SÍ SÍ

- - - -

NO NO SÍ SÍ

NO NO NO NO

NO NO SÍ NO

37

Page 39

TELEVISOR PDP MANUAL DE REPARACIONES

Descripciones de Alfileres del Procesador de Imagen (continuado)

Nombre Alfiler(es) Tipo Función

A12,B11,

D4,D7,

D10,D14,

D17,G4,

G17,K4,

VSS

K17,L4,

P17,T19,

U4,U7,U9,

U11,U12,

U14,U17,

W4,W6,

W14,W17

P

Tierra

38

Loading...

Loading...