Page 1

Colour Television Chassis

VES1.1E

LA

See table of contents on page 3

Published by MB/SC 1363 Quality Printed in the Netherlands Subject to modification EN 3122 785 19393

2013-Mar-29

2013 ©

TP Vision Netherlands B.V.

All rights reserved. Specifications are subject to change without notice. Trademarks are the

property of Koninklijke Philips Electronics N.V. or their respective owners.

TP Vision Netherlands B.V. reserves the right to change pr oducts at any time without being obliged to adjust

earlier supplies accordingly.

PHILIPS and the PHILIPS’ Shield Emblem are used under license from Koninklijke Philips Electronics N.V.

Page 2

EN 2 VES1.1E LA1.

Revision List

1. Revision List

Manual xxxx xxx xxxx.0

• First release.

Manual xxxx xxx xxxx.1

• Added the Service Mode menu

.

Manual xxxx xxx xxxx.2

• Added several new sets to this chassis, see table 2-1

Described

model numbers.

• Added the section Hotel Mode setup menu

.

Manual xxxx xxx xxxx.3

• Added several schematics of the SSB

• Added the schematics of the PSU

.

.

2. Technical Specifications and Connections

Index of this chapter:

Technical specifications

Directions for Use

Notes:

• Figures can deviate due to the different set executions.

• Specifications are indicative (subject to change).

Technical Specifications

For on-line product support please use the links in Table 2-1. Here is

product information available, as well as getting started, user manuals,

frequently asked questions and software & drivers.

Table 2-1 Described model numbers

CTN Styling Published in:

19PFL2908H/12 2900 3122 785 19392

22PFL2807H/12 2800 3122 785 19390

22PFL2908H/12 2900 3122 785 19392

24HFL2808D/12

24PFL2908H/12

26HFL2808D/12 2800 3122 785 19392

26PFL2908H/12

32PFL2807H/12

2800 3122 785 19392

2900 3122 785 19392

2900 3122 785 19392

2800 3122 785 19390

Directions for Use

You can download this information from the following websites:

http://www.philips.com/support

http://www.p4c.philips.com

2013-Mar-29

back to

div. table

Page 3

Contents

1 Introduction ............................................................................................................................................. 6

1.1

1.2 SSB Placement of Blocks .................................................................................................................. 8

2 Tuner (TU3) .............................................................................................................................................. 9

2.1 General description of the Sony RE216 tuner .................................................................................. 9

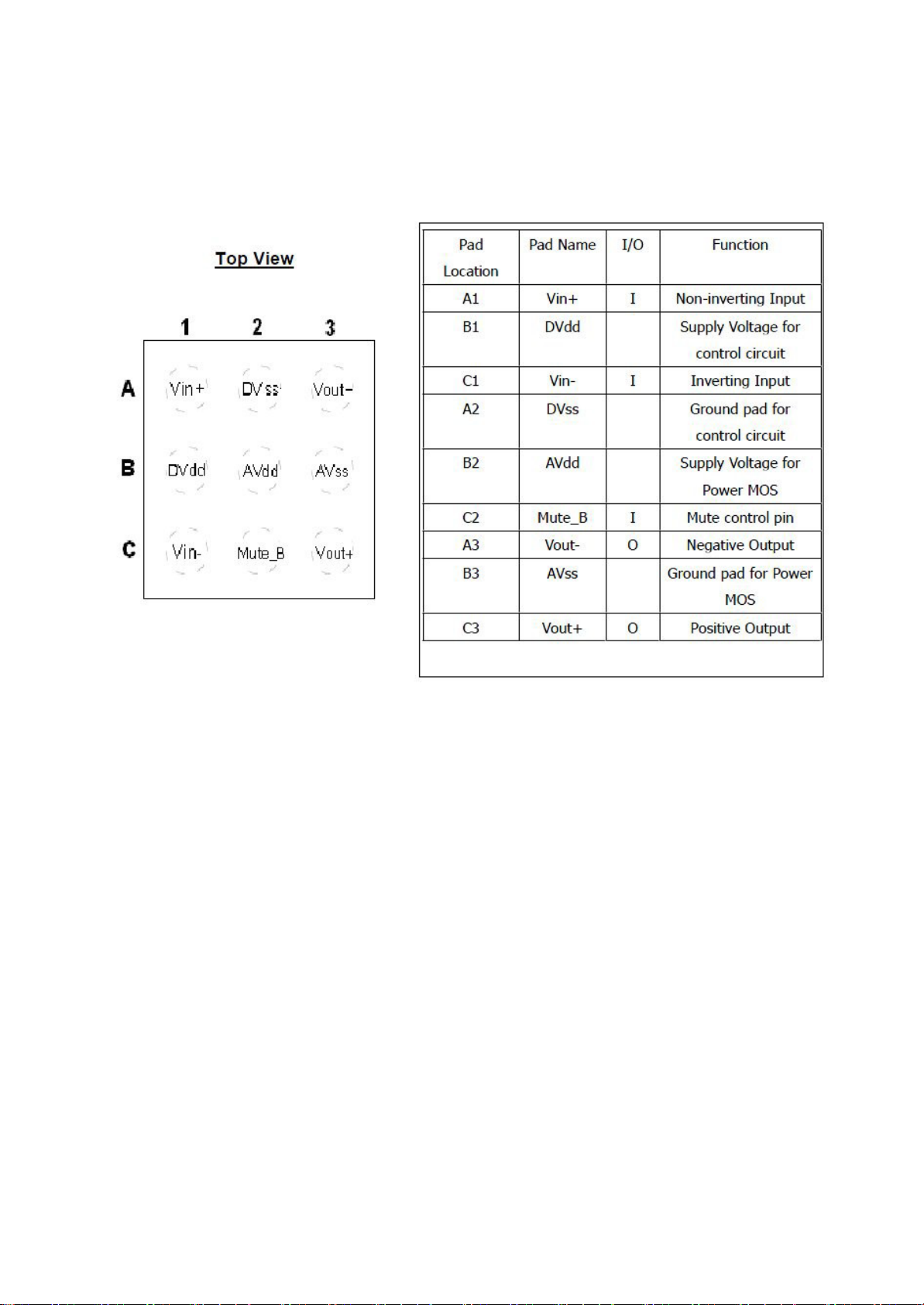

3 Audio amplifier stage with AZAD2102 (U163, U164) ............................................................................. 11

3.1 General description ........................................................................................................................ 11

3.2 Features .......................................................................................................................................... 12

3.3 Absolute

3.4 Pinning ............................................................................................................................................ 15

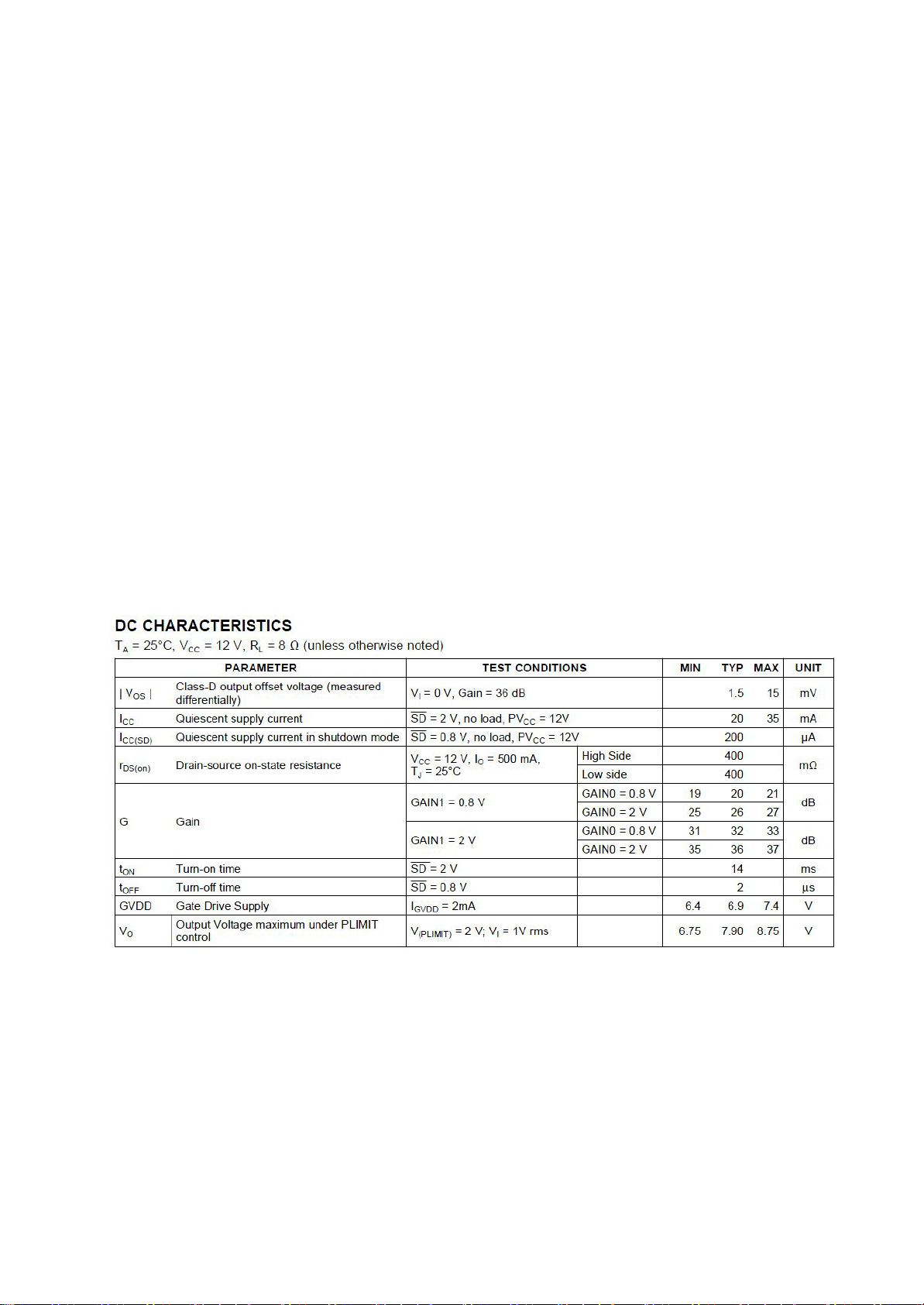

4 Audio amplifier stage with TPA3113 (U168) .......................................................................................... 15

4.1 General Description ....................................................................................................................... 15

4.2 Absolute Ratings ............................................................................................................................. 16

General

3.3.1 Electrical

3.3.2 Operating

4.2.1 Electrical Characteristics ........................................................................................................ 16

Block

Diagram

Ratings

Characteristics

specifications

................................................................................................................... 7

........................................................................................................................... 13

....................................................................................................... 13

....................................................................................................... 14

4.2.2 Operating

4.3

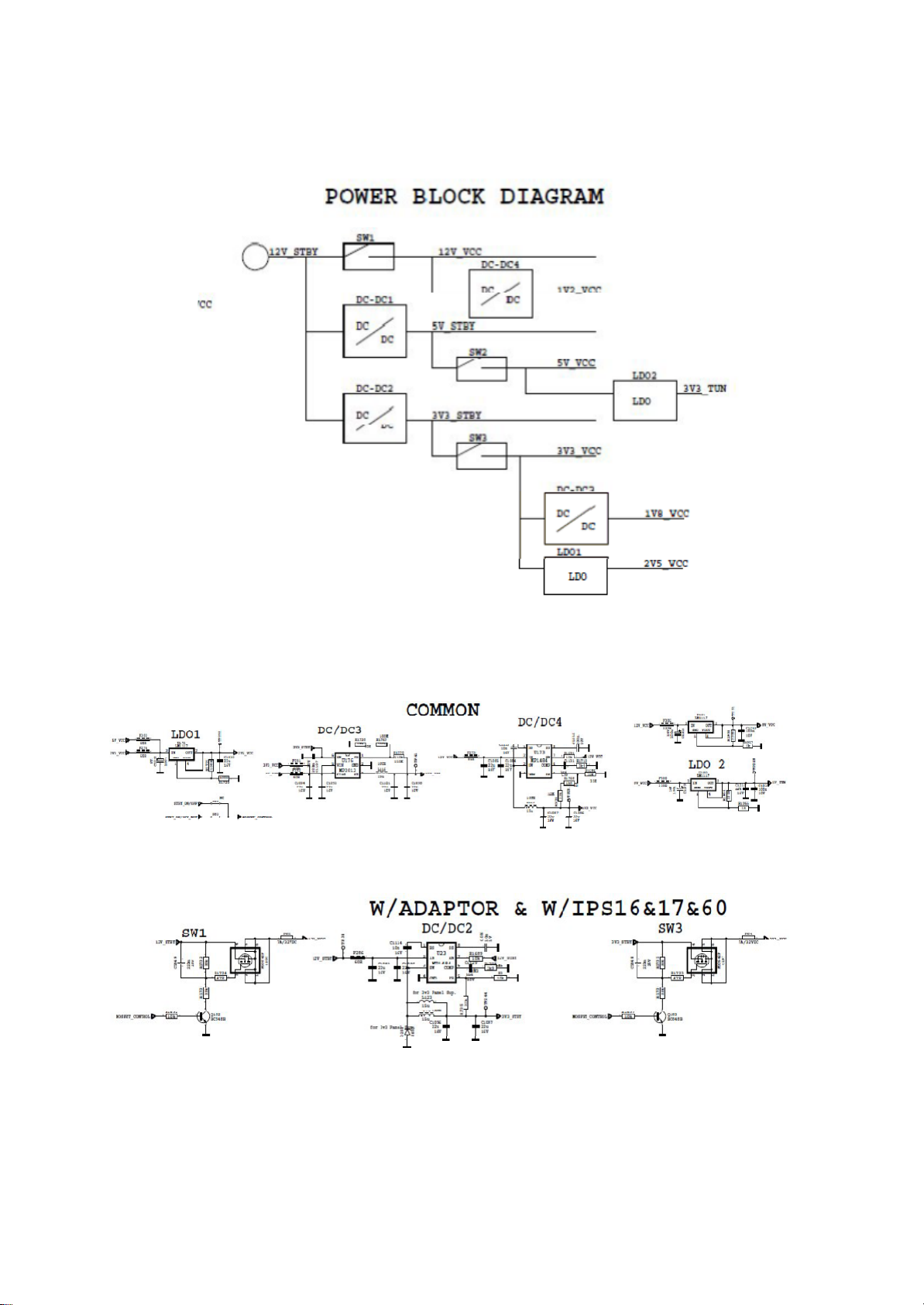

5 Power stage ............................................................................................................................................ 18

5.1 Power management ....................................................................................................................... 21

6 Microcontroller – MSTAR (U5) ............................................................................................................... 23

6.1 Description ..................................................................................................................................... 23

6.2 MSTAR block diagram .................................................................................................................... 27

6.3 Reset circuit .................................................................................................................................... 28

7 CI interface ............................................................................................................................................. 28

8 USB interface .......................................................................................................................................... 29

9 DDR2 SDRAM K4T1G164QF (U155) ....................................................................................................... 30

9.1 Description ..................................................................................................................................... 30

9.2 Features .......................................................................................................................................... 30

Pinning ........................................................................................................................................................ 31

10 Scaler and LVDS sockets ..................................................................................................................... 32

Pinning

........................................................................................................................................... 17

Specifications

...................................................................................................... 17

10.1 LVDS sockets block diagram .......................................................................................................... 32

10.2 Panel supply switch circuit ............................................................................................................. 32

11 SPI flash memory - MX25L1005 (U158) ............................................................................................. 33

11.1 General Description ....................................................................................................................... 33

11.2 Features.......................................................................................................................................... 33

Page 4

11.3 Absolute maximum ratings ............................................................................................................ 34

11.4 Pinning ............................................................................................................................................ 34

12 NAND Flash memory – NAND512XXA2C (U162) ................................................................................ 35

12.1 General Description ....................................................................................................................... 35

12.2 Features .......................................................................................................................................... 35

12.3 Pinning ............................................................................................................................................ 36

13 LNBH23L (U6) ..................................................................................................................................... 37

13.1 Description ..................................................................................................................................... 37

13.2 Features.......................................................................................................................................... 37

13.3 Block diagram ................................................................................................................................. 38

14 Advanced DVB-S/S2 demodulator M88DS3002 (U3) ....................................................................... 38

14.1 Description ..................................................................................................................................... 38

14.2 Features.......................................................................................................................................... 38

14.3 Pin Assignment .............................................................................................................................. 40

15 LM1117 (U175, U180, U181) .............................................................................................................. 41

15.1 General description ........................................................................................................................ 41

15.2 Features .......................................................................................................................................... 41

15.3 Applications .................................................................................................................................... 41

15.4 Absolute maximum ratings ............................................................................................................ 41

15.5 Pinning ............................................................................................................................................ 42

16 MP2012 (U176) .................................................................................................................................. 42

17 General description ............................................................................................................................ 42

17.1 Features .......................................................................................................................................... 42

17.2 Pinning ............................................................................................................................................ 43

18 RTA8283A (U23, U173) ....................................................................................................................... 43

18.1 General description ........................................................................................................................ 43

18.2 Features .......................................................................................................................................... 43

18.3 Pinning ............................................................................................................................................ 45

19 MP1583 (U174) .................................................................................................................................. 46

19.1 General description ........................................................................................................................ 46

19.2 Features .......................................................................................................................................... 46

19.3 Pinning ............................................................................................................................................ 46

20 FDC642 ............................................................................................................................................... 47

20.1 General description ........................................................................................................................ 47

20.2 Features .......................................................................................................................................... 47

20.3 Pinning ............................................................................................................................................ 47

21 FDC604P ............................................................................................................................................. 48

Page 5

21.1 General description ........................................................................................................................ 48

21.2 Features .......................................................................................................................................... 48

21.3 Pinning ............................................................................................................................................ 48

22 Connectors ......................................................................................................................................... 49

22.1 SCART (SC1) .................................................................................................................................... 49

22.2 HDMI (CN707, CN708) ................................................................................................................... 49

22.3

VGA (CN711)

................................................................................................................................. 50

23 Service menu mode ............................................................................................................................ 51

23.1 Main service menu ......................................................................................................................... 51

23.2 Video Settings ................................................................................................................................. 52

23.3 Audio Settings ................................................................................................................................ 52

23.4 Options 1 ........................................................................................................................................ 53

23.5 Options 2 ........................................................................................................................................ 53

23.6 Tuning Settings ............................................................................................................................... 54

23.7 Source Settings ............................................................................................................................... 54

23.8 Diagnostic ....................................................................................................................................... 54

23.9 USB operations ............................................................................................................................... 54

23.10 Profile Operations ...................................................................................................................... 57

23.10.1 Upload profile Data from USB ............................................................................................ 57

23.10.2 PQ Files Operations ............................................................................................................ 57

23.10.3 Upload PQ files from USB ................................................................................................... 57

23.10.4 Ci+ credentials key update ................................................................................................. 57

23.10.5 HDCP keys update .............................................................................................................. 57

23.10.6 Edid update ....................................................................................................................... 58

23.10.7 DDR settings update ........................................................................................................... 58

23.10.8 MAC address update .......................................................................................................... 58

23.11 Hotel Mode setup menu ............................................................................................................ 58

23.11.1 Hotel TV welcome image update (only available in Hotel TVs) ......................................... 58

24 Software update ................................................................................................................................. 59

25 Troubleshooting ................................................................................................................................. 59

25.1 No backlight problem ..................................................................................................................... 59

25.2 CI module problem ......................................................................................................................... 61

25.3 LED blinking problem ..................................................................................................................... 63

25.4 IR problem ...................................................................................................................................... 63

25.5 Keypad touchpad problems ........................................................................................................... 64

25.6 USB problems ................................................................................................................................. 65

25.7 No sound problem.......................................................................................................................... 65

Page 6

25.8 No sound problem at headphone .................................................................................................. 66

25.9 Standby On/Off problem................................................................................................................ 66

25.10 DVD problems ............................................................................................................................ 67

25.11 No signal problem ...................................................................................................................... 67

26 Styling sheet ....................................................................................................................................... 69

27 Schematics .......................................................................................................................................... 70

27.1 SSB .................................................................................................................................................. 70

27.2 PSU ................................................................................................................................................. 79

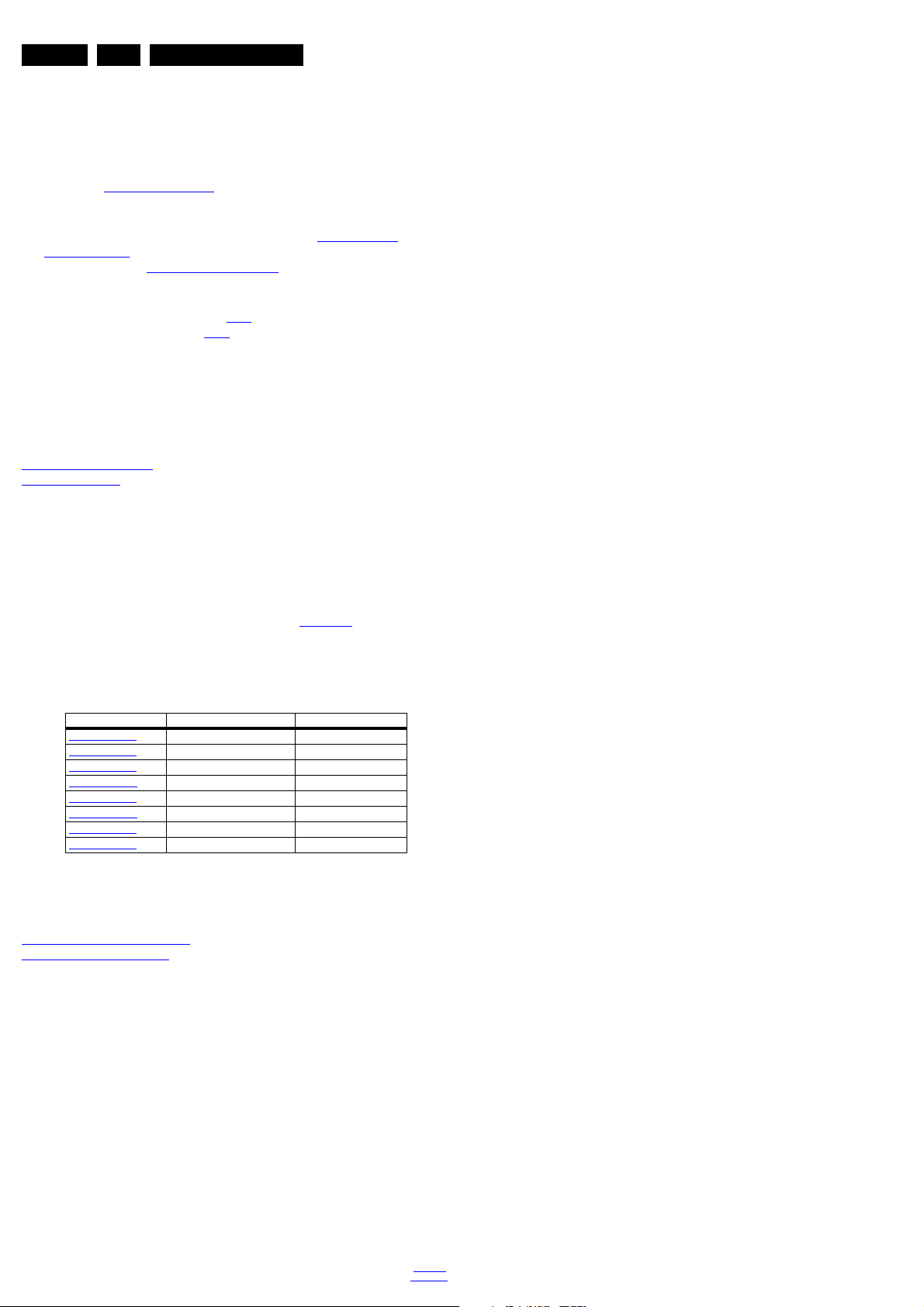

1 Introduction

The SSB is driven by a MStar SOC. This IC is capable of handling Video and audio

processing, Scaling-Display processing, 3D comb filter, OSD and text processing, LVDS

transmitting, channel and MPEG2/4 decoding, integrated DVB-T/C demodulator and

media center functionality.

The TV supports PAL, SECAM, NTSC colour standards and multiple transmission

standards as B/G, D/K, I/I’, and L/L’ including German and NICAM stereo. Also DVB T,

DVB-C are supported internal demodulators of Mstar IC and DVB-S/S2 is supported with

external demodulator.

Sound system output is supplying max. 2 × 2.5 W (less 10% THD at maximum output)

with 4

Ω

speakers or 2 × 6 W for stereo 8 Ω

speakers.

Supported peripherals are:

1 RF input VHF I, VHF III, UHF @ 75 Ω (Common)

1 Side AV (CVBS, R/L_Audio)

1 SCART socket (Common)

1 YPbPr (Optional)

1 PC input (Common)

2 HDMI 1.3 input (1 HDMI input is common, 1 input is optional)

1 S/PDIF output (Optional)

1 Headphone (Optional)

1 Common interface (Common)

1 USB (Common)

1 DVD (Optional)

1 On-board Keypad (Optional)

1 External Keypad (Optional)

1 External TouchPad (Optional)

Page 7

1.1

GPIO

General

Block

Diagram

D3K

••

HDIJI1

!

i

Mstar

VGA

-HPOEre

cr-.

2XIi'H

.O.UDIO AU'

Block Diagram

V1.1

Drawn

By Ulas

03.01.2011

Dere i

Page 8

1.2 SSB Placement of Blocks

Sat

Demod

Tuner(T3

)

External

Keyboard

Touchboard

DVD

Connector

Power Connector

CI Connector

Nand

Flash

(U162)

LVDS

Connectors

USB

Main IC

(U5)

DDR2

RAM

(U155)

YPbPr SAV HP

Satellite Tuner

SPI

Flash

HDMI

Connectors

Adapter DC

Input

VGA

SPDIF

Out

Keypad

SCART

Connec

tor

Speaker

Con.

Led

Con

Inv.

Con

Page 9

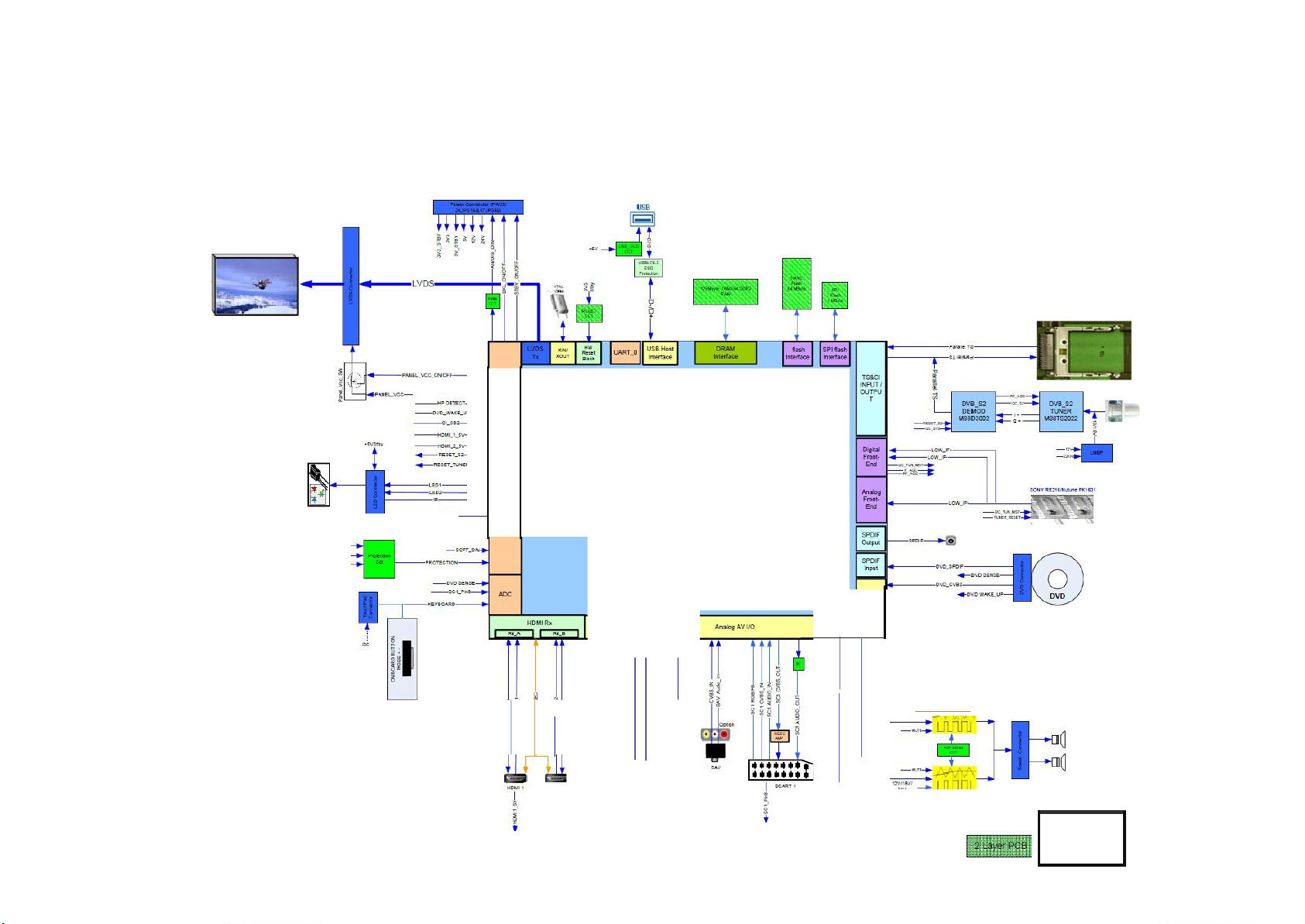

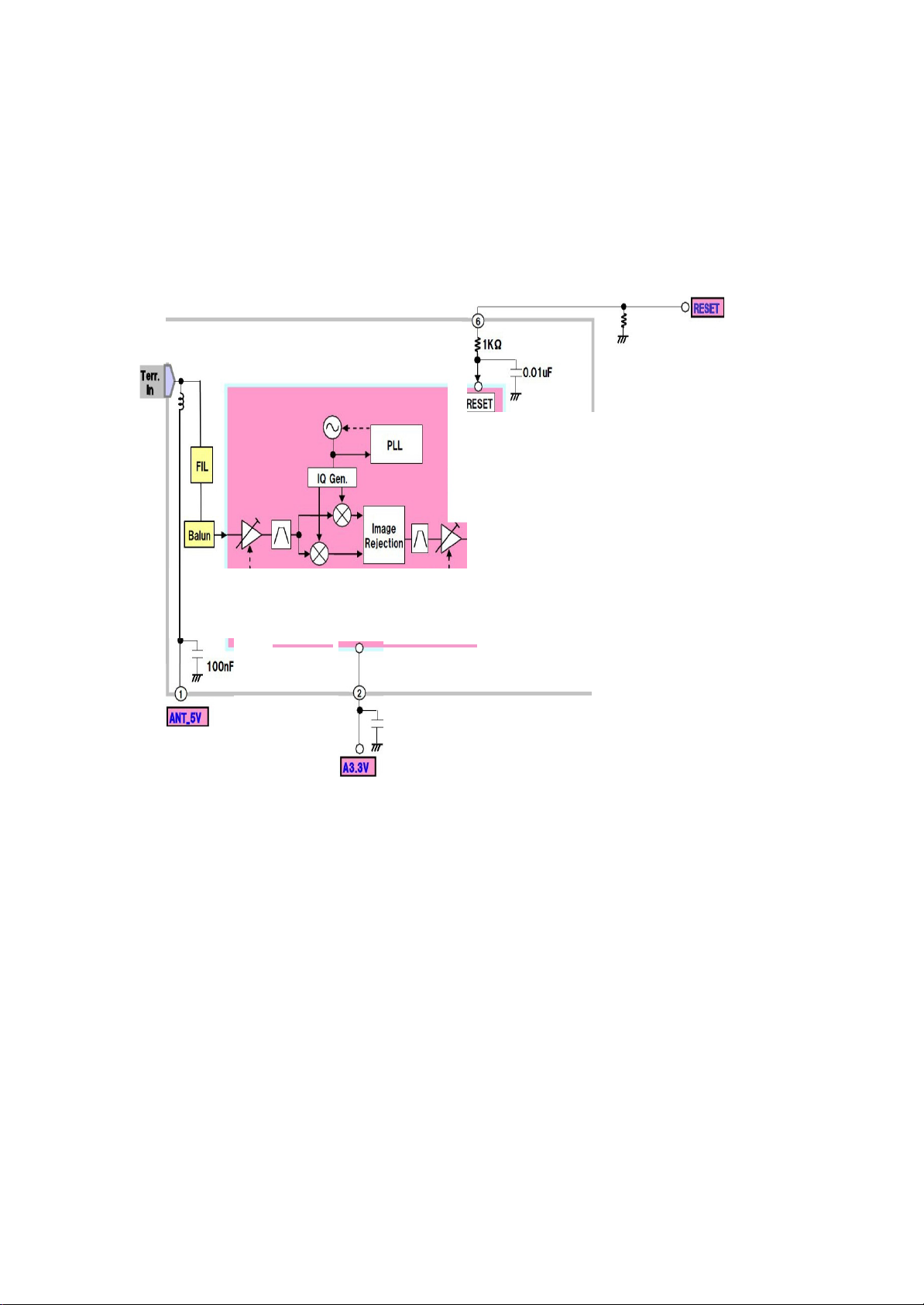

2 Tuner (TU3)

A horizontal mounted and Digital Half-Nim tuner is used in the product, which covers 3

Bands (From 48 MHz to 862 MHz for COFDM, from 45.25 MHz to 863.25 MHz for CCIR

channels). The tuning is available through the digitally controlled I2C bus (PLL).

In the active antenna option, the following circuits are used. ANT_CTRL pin is controlled by

microcontroller. If ANT_CTRL is low, ANT_PWR will be low. If ANT_CTRL is high,

ANT_PWR will be high.

OVER_CUR_DETECT pin is a monitor for short circuit in antenna. OVER_CUR_DETECT

is low, ANT_CTRL will be low, so ANT_PWR will be low. Finally, short circuit protection is

done by circuits and microcontroller.

2.1 General description of the Sony RE216 tuner

The SUT-RE216 is designed for terrestrial TV (digital & analog) and digital cable

reception. It includes a full band tuner and a channel filtering for digital signals. It provides

a low IF output after channel filtering to drive a channel demodulator. Tuning, band

switching and initialization are made via an I

interface. The module is built on a low-loss printed

circuit board carrying all the components in a metal

housing frame with top and rear covers. The single

aerial connector is mounted on one frame side and all

other connections are made via pins at the bottom.

Features:

Full frequency range from 47 to 870 Mhz

• Digital Platform (DVB-T/T2, DVB-C, ISDB-T & ATSC)

Analog platforms (PAL B/G/I/D/K, NTSC M & SECAM L/L’)

Low IF tuner concept

2

C bus

Page 10

./

Programmable channel Filter

./

Fully

I2C

bus

controlled

./

For Hybrid TV

AGC:

applications

I

:

---------------------------------------•

bandwidth

-

----{)-------w.

---

---o

..-----'M'h\--{®f-----....-!-'N\\-OIAocI

1000

1KO

3.3V pull up

-

1uF

Page 11

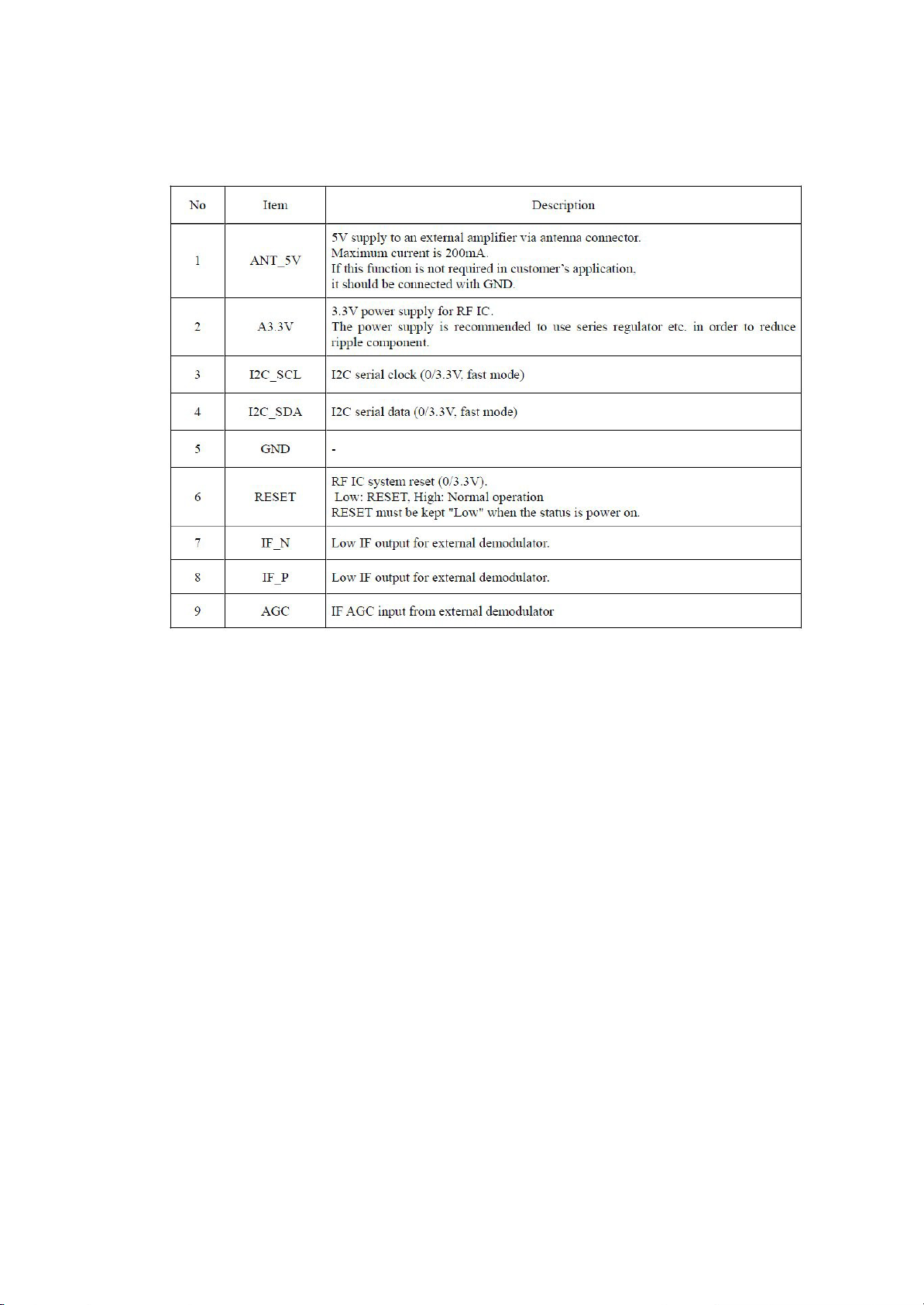

---Pinning Table

and Application Block Diagram of Tuner---

3 Audio amplifier stage with AZAD2102 (U163, U164)

3.1 General description

This chassis uses two 2.5 W Class D Mono Audio Amplifers for from 16" to 24"

TVs.

AZAD2102B

AVdd = DVdd = 5.5 Volt) with high efficiency filter-free class-D audio power amplifier

in a 1613 mm x 1613 mm wafer chip scale package (W CSP). AZAD2102B uses

Current- switch technology to achieve high performance class-d amplifier that

features 0.03% THD, 85% efficiency, –70 dB PSRR, to improve RF-rectification immunity.

AZAD2102B provide a Vibration-Spectrum modulation clock for PWM Output. This

vibration frequency is around 10 kHz shift (+/- 5 kHz of Fpwm).

The advantage of the small size package (WCSP) makes AZAD2102B very suitable for

mobile phone and PDA device application. And the Class-D amplifier structure let

AZAD2102B to have highly efficiency power consumption than Class-AB amplifier.

AZAD2102B can shrink the application board, reduce system cost, and external

components.

ESD level protection I/O embedded in AZAD2102B. For general applications, there is

no need to add extra ESD protection devices (like Varistors) in application systems for

AZAD2102B’s I/O.

is a 2.9 Watts (max. can offer 3.0 Watts @ Load = 3 Ω,THD = 10%,

Page 12

3.2 Features

• CMOS Technology

• High Efficiency 85%

• High PSRR 70 dB at 217 Hz

• Differential OP-amp Input

• AZAD2102B provides Vibration-Spectrum Modulation clock for reduce EMI

• Provide Mute function (set Mute_B to GND will go into Mute status)

• For the input stage AZAD2102B built-in a 10Kohm resistors (Gain

setting = 29.5 dB)

• Maximum Battery Life and Minimum Heat

• Efficiency With an 8 Ω

• 3.5 mA Quiescent Current

• Output Power at 10% THD

• 2.85 Watts at AVdd = DVdd = 5.0 Volt, Rload = 4 Ω

• 1.45 Watts at AVdd = DVdd = 3.6 Volt, Rload = 4Ω

• 0.30 Watts at AVdd = DVdd = 3.0 Volt, Rload = 4Ω

• 1.75 Watts at AVdd = DVdd = 5.5 Volt, Rload = 8Ω

• 0.87 Watts at AVdd = DVdd = 3.6 Volt, Rload = 8Ω

• 0.41 Watts at AVdd = DVdd = 3.0 Volt, Rload = 8Ω

• Eliminate Power on and Power-off “Pop” noise

• A fewer external components

• Optimized PWM output stage eliminates LC output filter

• Internally generate 290 kHz switching frequency to eliminate capacitor and resistor

• Improve PSRR (–70 dB) and wide supply voltage (3.0 V to 5.5 V)

•

Fully differential design reduces RF rectification

• This chip has been built-in a very strong ESD protection.

• System level ESD 4 KV (IEC 61000-4-2 ESD Contact Level)

• Wafer chip scale package (WCSP)

•

TSSOP package with exposed pad

Speaker:

Page 13

.

Operating Votl

age

Vop AVdd-DVdd

to

AVss-DVss

3.0 5

5.5

v

RL=80 f=

217Hz

Common mode

rejectio

n

High level nput

current

Under

Voltage

I

I

3.3 Absolute

Ratings

3.3.1 Electrical

VDD = AVdd = DVdd, VSS = AVss = DVss = Ground

TA =

25˚C, Filter

P

ARAMETER

Output offset vol

Power supply

ra

tio

ra

tio

Low level

current

Input

Operation cur

Characteristics

Bandwidth =

tage

rejection

rent

20 Hz -20 kHz

Symbo

l

vos

PSRR

Cf':lRR

I

IIHII

I

IlLI

lop

VDD = 5.5

VDD = 3.0

VDD

=

3.0 V

i

nput ac grounded with

Ci=2.2uF,Vripple=

= 3.0 V to 5.5 V,Vic =

VDD

0.5 V,Vi c = VDD/2

VDD=

5.5V,Vi=5.8V

VDD=

5.5V,Vi=-0.3V

=

5.5 V,no load

VDD

VDD = 3.6 V,no load

TEST COND TIONS

V,VI=

0 V,AV = 6 V/V

V,VI=

0 V,AV = 6 V/V

V,VI=

0 V,AV = 6 V/V 1.2

to

5.5 V, AV = 2 V/V

200mVpp,

to

0.5 VDD

3.0

VDD/2 to

-0.8 V,

MNI

TYP

4.5

MAX

6.5

UNIT

mV

2.1

4.0

3.0

-68

-65

25

1

3.6

5.0

4.2

VDD = 3.6

dB

dB

uA

uA

mA

Output

switchin

frequency

Vibration-Spectrum

Modulation

Protect

Mute_B

Gain

g

clock Ranqe

ion

pin Impedance

VDD = 3.0 V,no load

F

pwm

Fvs

UVP

RMuB

Gain

VDD = 5.5 V,no load

VDD = 3.6 V,no load

VDD = 3.0 V,no load

VDD = 5.0

Vin+

Mute_B

VDD=5.0V,Ri=5K0+10K

(Av=20V/V)

O

and

V,no load

Vin-

to

Ground

connect

to

GND,no load

2.5

3.5

290

300

315

+/-5 +/-10

18

2.0

270

20

22

2.5

KHz

KHz

v

KQ

V/V

Page 14

VDD = 3.0 V

0.60

No

weighting

45

3.3.2 Operating

TA = 25°C,Gain = 20

Pw

THD+N

PSRR

SNR

Vnoise

CMRR

ZI

ZF

P

ARAMETER TEST COND

Output

power

Total ha

distortion

Supply

rejection ratio

Signal-to-noise r

Output noise

Common

rejecti

Input impedance

Feedback res

rmonic

ripple

on

specifications

V/V,

THO+ N = 10%,

= 4Q

THO + N

RL = 4 Q

THO+ N =

= 8Q

THO + N

RL

VDD

plus

noise

VDD = 3.0 V,PO = 200

VDD

Av=20V/V,Inputs

grounded with

atio

VDD

VDD

kHz, nputs ac-grounded wi

Ci = l.OJJF

VDD = 3.6

level

mode

ratio

istor

TIONS

f = 1

kHz,RL

= 1%, f = 1

10%, f = 1kHz,RL

= 1%, f = 1 kH

= 8 Q

=

5.0 V,PO = 1W,RL = 8 Q,f = 1

=

3.6 V,PO = 0.5 W,RL = 8 Q, f = 1

=

3.6

V,

connect

Ci = l.OJ,JF

=

5 V,PO = 1W,RL = 8 Q

=

3.6 V,f = 20 Hz

V,Vin = 100mVpp f

kHz,

z,

mW,

RL = 8 Q, f = 1

to

to

20

th

= 5.0V

VDD

VDD = 3.6

VDD = 3.0 V

=

5.0 V

VDD

VDD = 3.6

VDD = 5.0

VDD = 3.6 V

VDD = 3.0

VDD

=

5.0 V

VDD = 3.6

VDD = 3.0 V

kHz

kHz

kHz

=

217 H.

F

VRipple

mVpp

A wei

= 217Hz

z,

= 200

ghting

V

V

V

V

V

MIN

TYP MAX

2.85

1

.45

0.77

2.25

1.15

1.75

0.87

0.47

1.39

0.70

0.36

0.15

0.12

0,09

-67

95

dB

120

8

40

-72

10 12

150 180

UNIT

w

w

w

w

%

VDD

dB

J,JVRMS

dB

kQ

kQ

Page 15

3.4 Pinning

4 Audio amplifier stage with TPA3113 (U168)

4.1 General Description

This chassis uses a 6 W Class D Mono Audio Amplifier for from 26” to 32” TVs.

The TPA3113D2 is a 6 W (per channel) efficient, Class-D audio power amplifier for driving

bridged-tied stereo speakers. Advanced EMI Suppression Technology enables the use of

inexpensive ferrite bead filters at the outputs while meeting EMC requirements.

SpeakerGuard™ speaker protection circuitry includes an adjustable power limiter and a

DC detection circuit. The adjustable power limiter allows the user to set a "virtual" voltage

rail lower than the chip supply to limit the amount of current through the speaker. The DC

detect circuit measures the frequency and amplitude of the PWM signal and shuts off the

output stage if the input capacitors are damaged or shorts exist on the inputs.

The TPA3113D2 can drive stereo speakers as low as 4 Ω. The high efficiency of the

TPA3113D2, 87%, eliminates the need for an external heat sink when

playing music.

The outputs are also fully protected against shorts to GND, VCC, and output-to-output.

The short-circuit protection and thermal protection includes an auto-recovery feature.

Page 16

3.2. Features

• 6 W/ch into an 8-Ω Loads at 10% THD+N From a 10-V Supply

• 12-W into a 4-Ω Mono Load at 10% THD+N From a 10-V Supply

• 87% Efficient Class-D Operation Eliminates Need for Heat Sinks

• Wide Supply Voltage Range Allows Operation from 8 V to 26 V

• Filter-Free Operation

• SpeakerGuard™ Speaker Protection Includes Adjustable Power Limiter plus DC

Protection

• Flow Through Pin Out Facilitates Easy Board Layout

• Robust Pin-to-Pin Short Circuit Protection and Thermal Protection with Auto

Recovery Option

• Excellent THD+N / Pop-Free Performance

• Four Selectable, Fixed Gain Settings

• Differential inputs

4.2 Absolute Ratings

4.2.1 Electrical Characteristics

Page 17

65

IJV

·

c

·c

p

4.2.2 Operating

AC

CHARACTERISTICS

TA

= 25•c, Vee =

KsvR

THO+N Total

Vn

SNR Signa-l

fosc

12

V, RL

PARAMETER TEST CONDITIONS

Supply

ripple rejection

harmonic

Output integrated nois

Crosstalk

to-noise ratoi

Oscillator frequency

T

hermal trip

The

point

rmal hysteresis

4.3

NAME

so

FAULT

LI

LINN

GAlNO

GAIN1

AVCC

AGNO

GVOO

PLIMIT

RINN

RINP

NC

PBTL

PVCCR

PVCCR

BSPR

OUTPR

PGNO

OUTNR

BSNR

BSNL

OUTNL

PGNO

OUTPL

BSPL

PVCCL

PVCCL

Pinning

PIN

NP

Specifications

= 8 0

(unless

distortion +noise RL = 8

e

Pin

Number

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

otherwise noted

200 mVpp

Gain

20 Hz to 22 kHz,A-weighted fi

P0 = 1 W,Gain

Maxi

Gain

110/P

I

0

I

I

I

Gani select

I

Gani seel ct most

0

I

I

I

I

p

p

I

Bootstrap 110

0

0

I

Bootstrap 1/0 for right channel,

I

Bootstrap 1/0

0

0

I

Bootstrap 1/0 for left c

p

p

)

ripple

from 20

= 20 dB,Inputs ac-coupled to AGNO

0, f = 1kHz, Po = 3 W (half-p

= 20 dB, f = 1 kHz

mum output at

= 20 dB, A-weighted

Shutdown

enabled).TTL l

Open

compilant to

FAULT pin

be reset by cycling PVCC.

Postiive

Negative audio input for left channeL

Analog supply

Analog signalgrou

High-side

as

Power

powerlimit. Connect di

Negative

Positive

Not connected

ParallelBTL

Power supply for right channel H-bridge. Right c

supply inputs

Power supply for right channel H-bri

channel

Class-0

Power ground for the H-bri

Class-0

Class-0 H-bridge ne

Power

Class-0

Power supply for left

supply

Power supply for left

supply

logic input for audio amp (LOW =

drain output

audio

FET gate drive suppl

supply for PLIMIT function

limti leveladjust

audio input for right ch

audio

power

H-bridge

H-bridge

ground

H-bridge

inputs are

i

nputs

Hz-1kHz,

lter, Gani = 20 dB

THO+N

<

1%, f = 1 kHz

ogic l

evels with

used to display short cir

AVCC.Short circuit

to

SO pin. Otherwise,

input

for left channeL

least sign

ifi

cant bit. TTL

significant bit TTL logic l

nd.

Connect to the thermal pad.

Connect a resistor divi

rectly to

input

for right

channeL Bi

mode switch

are connect internally.

supply inputs

for

right channel, positive

positive output

negative

for left c

for the H-bri

positive output

connect internally.

are connect internally.

are connect internally.

dges.

output for right c

hanne,l n

egative high-side FET.

gative output

dges.

hanne,l positive

channelH-bridge.

channelH-bri

ower)

,

DESCRIPTION

compli

ance to AVCC.

faults can be set

y.Nominalvol

GVOO for no power limit.

anne.l Biased at

negative

cuit

both

short circuit

Biased at

Biased at 3V.

logic levels with complian

evels with

ase

d at

dge. Right

high-side

for right c

for left

hannel.

hannel.

high-side FET.

for left

channel.

channeL

high-side FET.

Right channel and left

dge. Right

MIN

TYP

250

outputs Hi-Z,HIGH = outputs

or de detect fault status.Vot

to auto-recovery

faults

and de

3V.

compliance

tage is 7V. Also

der

from GVOO

3V.

3V.

hanneland left channel

channelandleft

FET.

channel

and left

MAX UNIT

-70

0.06

-80

-100

102

310 350 kHz

150

15

by connecting

detect faults must

ce to AVCC.

to

AVCC.

should be

to

GND to se

channel power

channel power

lag

used

powe

t

dB

%

dBV

dB

dB

e

r

Page 18

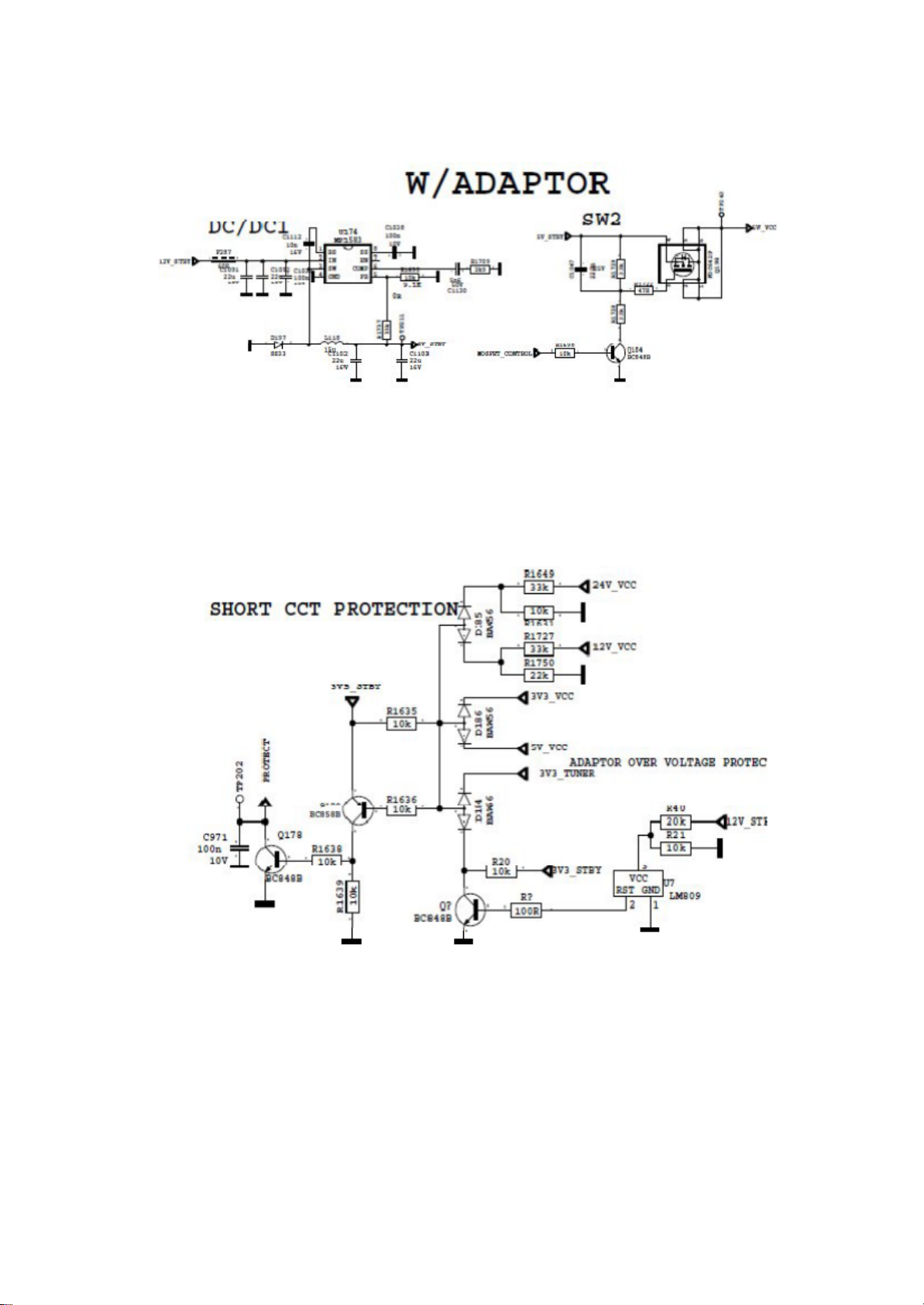

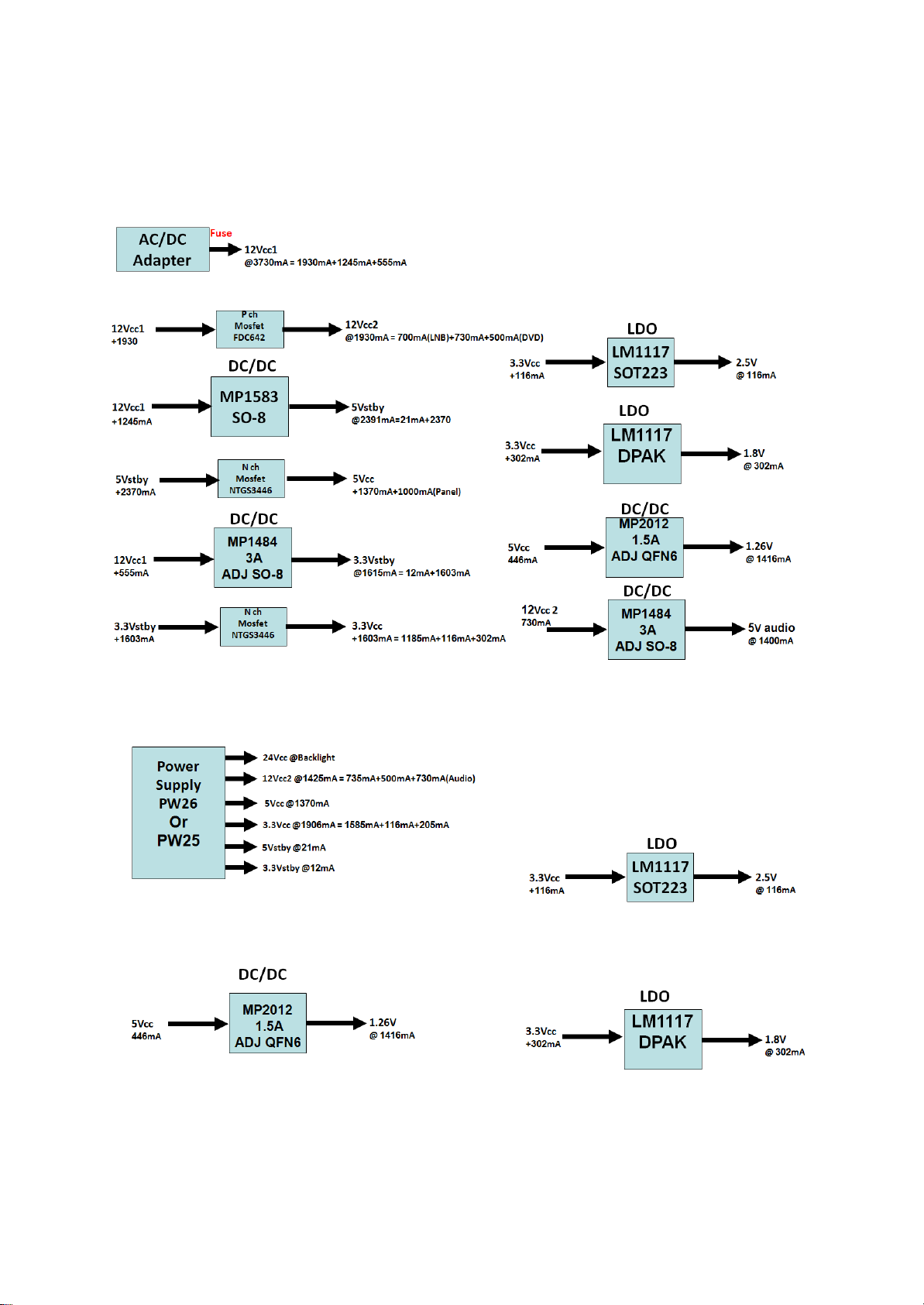

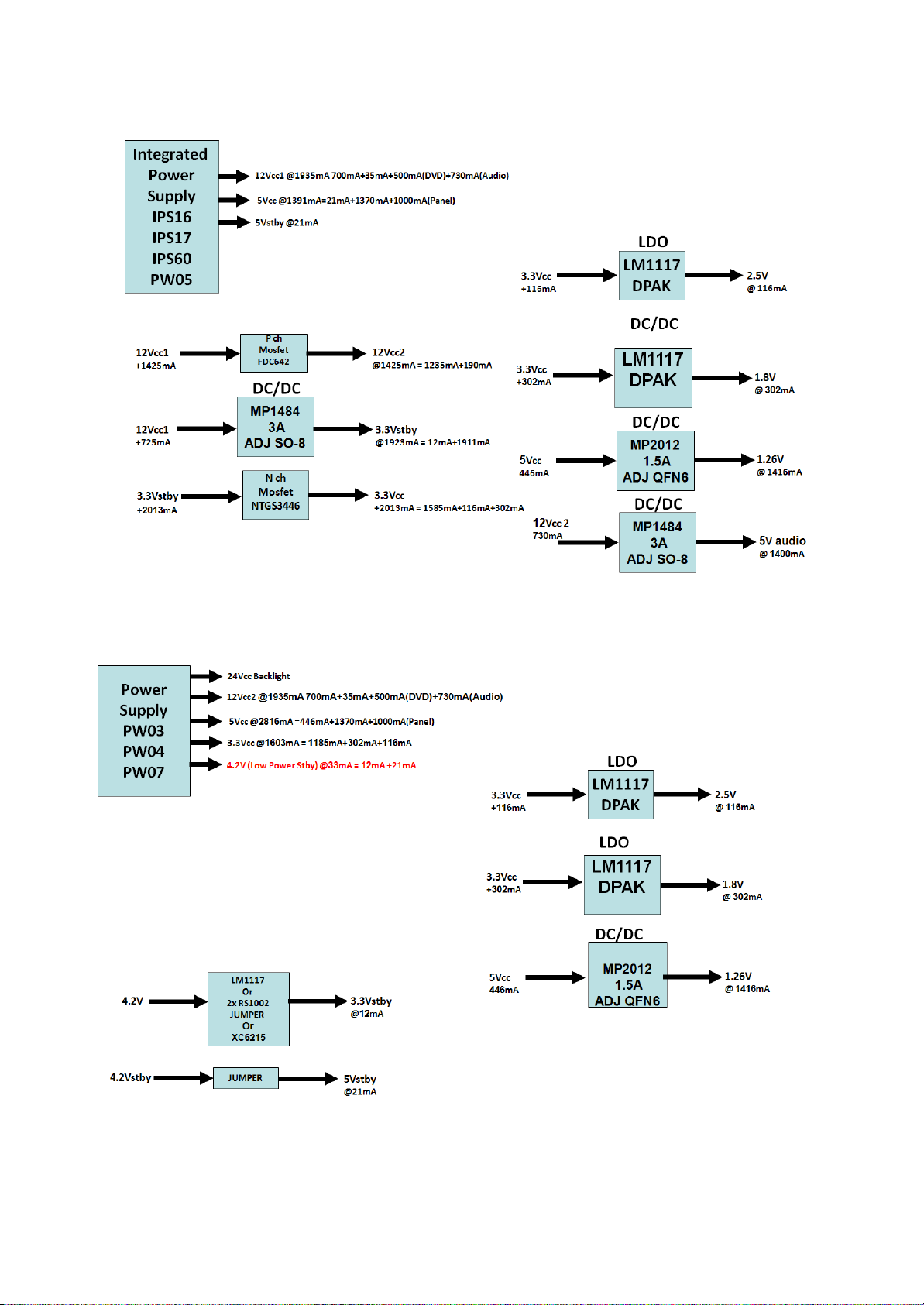

5 Power stage

The DC voltages required at various parts of the chassis and panel are provided by a

main power supply unit. This chassis can operate with the different supplies: IPS60,

IPS16, IPS17, PW26, PW27 as main power supply and also with 12V adaptor.

CN706 is used for IPS60, IPS16 and IPS17 and CN1 is used for PW26 and PW27.

JK9 is used for the adapter option and also CN705 inverter socket or DB32 chassis with

CN706 is used to supply backlight.

The power supplies generate 18V, 12V, 5V, 3,3V and 12V, 5V, stand- by mode DC

voltages. Power stage which is on-chassis generates 5V, 3V3 stand by voltage and 12V,

8V, 5V, 3V3, 2.5V, 1,8V and 1,2V supplies for other different parts of the chassis. Chassis

block diagram is indicated below.

Page 19

The blocks on power block diagram is using dependent to main supply. For PW26 and

PW27 just common blocks are enough for proper operation.

For IPS16, IPS17, IPS60 below blocks must work properly.

For adapter case also below blocks are necessary.

Page 20

Short CCT Protection Circuit

Short circuit protection is necessary for protecting chassis and main IC against damages

when any Vcc supply shorts to ground. Protect pin should be logic high while normal

operation. W hen there is a short circuit protect pin shold be logic low. After any short

detection, SW forces LEDs on LED card to blink.

Page 21

5.1 Power management

--- Power Management with Adaptor---

--- Power Management with PW25/ PW26---

Page 22

--- Power Management with IPS16/IPS17/IPS60/PW05---

--- Power Management with PW03/PW04/PW07---

Page 23

6 Microcontroller – MSTAR (U5)

6.1 Description

MSD9WB9PT-2 (Main IC) (U5)

The MSD9WB9PT-2 is MStar’s most up-to-date system-on-chip solution for flat panel

integrated digital television products. Building on the success of MStar’s preceding SOC

series, the MSD9WB9PT-2 provides most cost-effective solution for DTV application with

creative and attractive features exclusively presented by MStar.

The MSD9WB9PT-2 integrates DTV/multi-media all-purpose AV decoder, DVB-T

demodulator, VIF demodulator, and Sound/Video processor into a single device. This

allows the overall BOM to be reduced significantly making the MSD9WB9PT-2 a very

competitive multi-media DTV solution. For ATV users, the MSD9WB9PT-2 provides multistandard analog TV support with adaptive 3D video decoding and VBI data extraction.

The build-in audio decoder is capable of decoding FM, AM, NICAM, A2, BTSC and EIA-J

sound standards. The MSD9WB9PT-2 supplies all the necessary A/V inputs and outputs

to complete a receiver design including a multi-port HDMI receiver and component video

ADC. All input selection multiplexed for video and audio are integrated, including full

SCART support with CVBS output. The equipped MStar MACE-5 color engine is the

latest masterpiece from

MStar famous color engine series providing excellent video and picture quality in Full-HD

and large-scale displaying system.

To meet the increasingly popular energy legislative requirements without the use of

additional hardware, the MSD9WB9PT-2 has an ultra low power standby mode during

which an embedded MCU can act upon standby events and wake up the system as

required.

The MSD9WB9PT-2 is composed of several modules:

• High Performance Micro-processor

o Ultra high speed/performance 32-bit RISC CPU

o One full duplex UARTs

o Supports USB and ISP programming

o DMA Engine

• Transport Stream De-multiplexer

o Supports parallel and serial TS interface, with or without sync signal

o Supports TS input and output for external CI module

o Maximum TS data rate is 104 Mb/sec for serial or 16 MB/sec for parallel

o 32 general purpose PID filters and section filters for each transport stream

de-multiplexer

o Supports additional audio/video/PCR filters

o Supports TS DMA channel for time-shift

o Supports 3DES/DES and AES encryption/decryption

• MPEG-2 Video Decoder

o ISO/IEC 13818-2 MPEG-2 video MP@HL

o Automatic frame rate conversion

o Supports resolution up to HDTV (1080i, 720p) and SDTV

Page 24

•

MPEG-4

•

Hardware

•

NTSC/PAL/SECAM

•

Multi-Standard TV Sound Processor

•

Audio Interface

Video Decoder

o ISO/IEC 14496-2 MPEG-4 ASP video decoding

o Supports resolutions up to HDTV (1080p@30fps)

o

Supports DivX1 Home Theater & HD profilesOptional

o Supports VC-1Optional, FLV video format decoding

JPEG

o Supports sequential mode, single scan

o

Supports both color and grayscale pictures

o Following the file header scan the hardware decoder fully handles the

decode process

o Supports programmable Region of Interest (ROI)

o Supports formats: 422/411/420/444/422T

o Supports scaling down ratios: 1/2, 1/4, 1/8

o Supports picture rotation

o Supports NTSC-M, NTSC-J, NTSC-4.43, PAL (B,D, G, H, M, N, I, Nc),

and SECAM standards

o Automatic standard detection

o Motion adaptive 3D comb filter

o Five configurable CVBS & Y/C S-video inputs

o

Supports Teletext, Closed Caption (analog CC 608/ analog CC 708/digital

608/digital CC708), V-chip and SCTE

CC

o SIF audio decoding

o Supports BTSC/A2/EIA-J demodulation

o Supports NICAM/FM/AM demodulation

o Supports MTS Mode Mono/Stereo/SAP in BTSC/ EIA-J mode

o Supports Mono/Stereo/Dual in A2/NICAM mode

o Built-in audio sampling rate conversion (SRC)

o Audio processing for loudspeaker channel, including volume, balance,

mute, tone, EQ,virtual stereo/surround and treble/bass controls

o Advanced sound processing options available,for example: SRS1, BBE2,

QSound3, Audyssey4

o Supports digital audio format decoding:

MPEG-1,

Supports Optional Dolby Digital Plus, Dolby mPulse, and MS10

multistream decoder, including Dolby Digital Encoder for

transcoding streams to Dolby Digital 5.1 (DDCO)

Supports MPEG Audio, Dolby Digital, Dolby Digital Plus format AD

(Audio Description)

o Supports PVR and time-shifting

o One SIF audio input interface with minimal external saw filters

o Four L/R audio line-inputs

o Two L/R outputs for main speakers and additional line-outputs

o Supports stereo headphone driver

2

o I

S digital audio input & output

o S/PDIF digital audio output

o HDMI audio channel processing

o Programmable delay for audio/video synchronization

Video

Decoder

MPEG-2 (Layer I/II), MP3, Dolby Digital (AC-3), AAC-LC

Page 25

o

Analog RGB Compliant

Input

Port

o Three analog ports support up to 1080P

o

Supports PC RGB input up to SXGA@75Hz

o Supports HDTV RGB/YPbPr/YCbCr

o Supports Composite Sync and SOG Sync-on-Green

o Automatic color calibration

o

AV-link support

o Analogue RGB Auto-Configuration & Detection

o Auto input signal format and mode detection

o Auto-tuning function including phasing, positioning, offset, gain, and jitter

detection

o Sync Detection for H/V Sync

•

DVI/HDCP/HDMI

Compliant

Input

Port

o Two HDMI/DVI Input ports

o HDMI 1.3 Compliant

o HDCP 1.1 Compliant

o 225 MHz @ 1080P 60 Hz input with 12-bit Deep-color support

o CEC support

o Single link DVI 1.0 compliant

o Robust receiver with excellent long-cable support

• MStar Advanced Color Engine

(MStarACE

-5)

• 10/12-bit internal data processing

• Fully programmable multi-function scaling engine

o

Nonlinear video scaling supports various modes including

o

Supports dynamic scaling for

VC

-1

• High-Quality DTV video processor

o

3D motion video deinterlacer with motion object st

o

Edge-oriented deinterlacer with edge and artifact smoother

o Automatic

3:2/2:2/M:N

pull-down detection and recovery

o 3D multi-purpose noise reduction for DTV or lousy air/cable input

o

MPEG

reduction

o

Arbitrary frame rate

artifact removal including de-blocking and mosquito noise

conversion

• MStar Professional Picture Enhancement:

o

Dynamic brilliant and fresh

o

Dynamic Blue Stretch

o

Intensified contrast and

o

Dynamic Vivid

o

Dynamic sharpened Luma/Chroma

o

Global and local dynamic depth of field perception

o

Accurate and independent color control

o

Supports sRGB and xvYCC color

o

Supports HDMI 1.3 deep color format

Skin

details

color

edges

processing

• Programmable 12-bit RGB gamma CLUT

• Output Interface

o Single/dual link 8/10-bit LVDS output

o Supports panel resolution up to Full-HD (1920x1080) @ 60Hz

o Supports TH/TI format

o Supports dithering options to 6/8-bit output

o Spread spectrum output for EMI suppression

•

CVBS

Video

Encoder

o Supports all NTSC/PAL TV Standard

o Stand-alone scaling engine

o Programmable Hue, Contract, Brightness

o Supports TTX/CC/WSS output

o

CVBS

Video Output

abilizer

Pa

norama

Page 26

o Allows CVBS output of all source inputs

•

2D Graphics

Engine

o Hardware Graphics Engine for responsive

o Interactive applications

o Supports point draw, line draw, rectangle draw/fill, text draw and trapezoid

draw

o BitBlt, stretch BitBlt, trapezoid BitBlt, mirror BitBlt and rotate BitBlt

o Raster Operation (ROP)

o Support Porter-Duff

•

VIF Demodulator

o Compliant with NTSC M/N, PAL B, G/H, I, D/K, SECAM L/L' standards

o Audio/Video dual-path processor

o Stepped-gain PGA with 25 dB tuning range and 1 dB tuning resolution

o

Maximum IF gain of 37 dB

o Programmable TOP to accommodate different tuner gain and SAW filter

insertion loss to optimize noise and linearity performance

o Multi-standard processing with single SAW

o Supports silicon tuner low IF output architecture

•

DVB-T Demodulator

o Digital carrier frequency offset correction: ±500KHz

o Optimised for SFN channels with pre/post-cursive echoes inside/outside

the guard

o Acquisition range ±857kHz includes up to 3x ±1/6 MHz transmitter offset

o Meets Nordig Unified 1.0.3, D-Book 5.0, EICTA E-Book/C-Book test

requirement

o ±400kHz internal carrier offset recovery range

o 6.8 usecs echo cancellation at 7 Msym/s

o Supports IF, low-IF, zero-IF inputs

o

Ultra-fast automatic blind UHF/VHF channel scan (constellations and

symbol rate)

•

Co

nnectivity

o Two USB 2.0 host ports

o USB architecture designed for efficient support of external storage

devices in conjunction with off air broadcasting

•

Miscellaneous

o DRAM interface supporting one 16-bit DDR2 @1066MHz

o Supports PVR

o Supports Common Interface for conditional access support

o Bootable SPI interface with serial flash support

o Parallel interface for external NAND flash support

o Power control module with ultra low power MCU available in standby

mode

o 380-ball LFBGA package

o Operating Voltages: 1.26V (core), 1.8V (DDR2), 2.5V and 3.3V (I/O and

analog)

Page 27

6.2 MSTAR block diagram

Page 28

6.3 Reset circuit

Reset circuit using for initiliazing main Mstar IC. Reset condition is high and nomal

working condition is low for RESET pin.

7 CI interface

CI Interface Power Switch:

It is used for CI module supply, when Module is inserted (it means CI detect is low) This

circuit is opened or closed by CI_POWER_CTRL port of main uController

Page 29

8 USB interface

Main Concept IC has integrated 2 USB 2.0 interface. One of them is used for ethernet

function, the other one is used for USB connectivity for last user. Last user can play video,

picture and audio files. Also digital channels can be record to external storage device by

this interface. All SW files can be updated with interface.

USB circuit has 3 main parts

• Integrated USB 2.0 Host interface of D3K (U5)

• Protection IC (U145)

• Over current protection IC (U8)

Page 30

9 DDR2 SDRAM K4T1G164QF (U155)

9.1 Description

The 1Gb DDR2 SDRAM is organized as a 16Mbit x 8 I/Os x 8 banks, 8Mbit x 16 I/Os x 8

banks device. This synchronous device achieves high speed double-data-rate transfer

rates of up to 1066Mb/sec/pin (DDR2-1066) for general applications. The chip is designed

to comply with the following key DDR2 SDRAM features such as posted CAS with additive

latency, write latency = read latency - 1, Off-Chip Driver (OCD) impedance adjustment and

On Die Termination. All of the control and address inputs are synchronized with a pair of

externally supplied differential clocks. Inputs are latched at the crosspoint of differential

clocks (CK rising and CK falling). All I/Os are synchronized with a pair of bidirectional

strobes (DQS and DQS) in a source synchronous fashion. The address bus is used to

convey row, column, and bank address information in a RAS/CAS multiplexing style. For

example, 1Gb (x8) device receive 14/10/3 addressing. The 1Gb DDR2 device operates

with a single 1.8V ± 0.1V power supply and 1.8V ± 0.1V VDDQ. The 1 Gb DDR2 device is

available in 60 ball FBGA(x8) and 84ball FBGA(x16).

9.2 Features

• JEDEC standard VDD = 1.8V ± 0.1V Power Supply

• VDDQ = 1.8V ± 0.1V

• 533MHz fCK for 1066Mb/sec/pin

• 8 Banks

• Posted CAS

• Programmable CAS Latency: 4, 5, 6, 7

• Programmable Additive Latency: 3, 4, 5. 6

• Write Latency(WL) = Read Latency(RL) -1

• Burst Length: 4 , 8(Interleave/nibble sequential)

• Programmable Sequential / Interleave Burst Mode

• Bi-directional Differential Data-Strobe (Single-ended data-strobe is an optional

feature)

• Off-Chip Driver(OCD) Impedance Adjustment

• On Die Termination

• Special Function Support - PASR(Partial Array Self Refresh) - 50ohm ODT - High

• Temperature Self-Refresh rate enable

• Average Refresh Period 7.8us at lower than TCASE 85°C, 3.9us at 85°C < TCASE <

95°C

• All of products are Lead-free, Halogen-free, and RoHS compliant

Page 31

7

Voo

Vss

VssQ

VoDQ

VooQ

VssQ

Voo

Vss

VssQ

VoDQ

VooQ

VssQ

VooL

VRE

F

Vss

CKE WE

Vss

Voo

VssQ

VoDQ

VssQ

VoDQ

VoDQ

VssQ

VssQ

VoDQ

VssQ

VoDQ

VoDQ

VssQ

VssoL

Voo

RAS CK

OOT

cs

Voo

Vss

F

•••

••

G

Pinning

1

2

OQ14

NC

7 8

3

UOM

UOQS

UOQS

9

DQ15

OQ9

OQ12

NC

DQ6

OQ1

DQ4

BA2

Ball Locations

BAO

A10/AP

A3

A7 A9

A12

DQ11

LDM

OQ3

BA1

(x1

A1

AS

NC

6)

DQ10

L

OQS

OQ2

CAS

A2

A6

A11

NC

1 2 3 4 s 6 8

A

B

••••••++++++

•

Populated ball

+ Ball

Top view

(See the

not

balls throughp

populated

ackage)

c

D •••

E

•••

++++•• ••

H •••+++•· ••

J

K

+

••

•••••+

L

M

+

N •••+++•·

p

R

+•••••+++

D

Q8

OQ13

LDQS

DQO

CK

AO

A4

A8

NC

OQ7

OQ5

•

·••••

+++•· ••

+++•·•

+++•· •+•

•

•+

·

•

•

•

+

9

•

Page 32

10 Scaler and LVDS sockets

10.1 LVDS sockets block diagram

10.2 Panel supply switch circuit

This switch is used to open and close panel supply of TCON. It is controlled by port of

main ucontroller. Also with this circit panel sequency could be adjusted correctly. 3 panel

supplys are connected to this circuit. All of them are optional according to panels.

Page 33

11 SPI flash memory - MX25L1005 (U158)

11.1 General Description

MX25L1005 is a CMOS 1,048,576 bit serial Flash memory, which is configured as

131,072 x 8 internally.The MX25L1005 feature a serial peripheral interface and software

protocol allowing operation on a simple 3-wire bus. The three bus signals are a clock

input (SCLK), a serial data input (SI), and a serial data output (SO). SPI access to the

device is enabled by CS# input. The MX25L1005 provide sequential read operation on

whole chip. After program/erase command is issued, auto program/ erase algorithms

which program/ erase and verify the specified page or sector/block locations will be

executed. Program command is executed on page (256 bytes) basis, and erase

command is executes on chip or sector(4K-bytes) or block(64K-bytes). To provide user

with ease of interface, a status register is included to indicate the status of the chip. The

status read command can be issued to detect completion status of a program or erase

operation via WIP bit. W hen the device is not in operation and CS# is high, it is put in

standby mode and draws less than 10uA DC current. The MX25L1005 utilize MXIC's

proprietary memory cell, which reliably stores memory contents even after 100,000

program and erase cycles.

11.2 Features

• Serial Peripheral Interface (SPI) compatible -- Mode 0 and Mode 3

• 1,048,576 x 1 bit structure

• 32 Equal Sectors with 4K byte each, Any Sector can be erased individually

• 2 Equal Blocks with 64K byte each, Any Block can be erased individually

• Single Power Supply Operation

Page 34

• 2.7 to 3.6 volt for read, erase, and program operations

• Latch-up protected to 100mA from -1V to Vcc +1V

• Low Vcc write inhibit is from 1.5V to 2.5V

11.3 Absolute maximum ratings

RATING VALUE

Ambient Operating

Temperature

0°C to 70°C

Storage Temperature -55°C to 125°C

Applied Input Voltage -0.5v to 4.6v

Applied Output Voltage -0.5v to 4.6v

VCC to Ground Potential -0.5v to 4.6v

11.4 Pinning

8-PIN SOP (150mil)

SYMBOL DESCRIPTION

CS# Chip select

SI Serial Data Input

SO Serial Data Output

SCLK Clock Input

HOLD# Hold, to pause the device without

deselecting the device

VCC +3.3v Power Supply

GND Ground

Page 35

12 NAND Flash memory – NAND512XXA2C (U162)

12.1 General Description

The NAND flash 528-byte/ 264-word page is a family of non-volatile flash memories that

uses the single level cell (SLC) NAND technology. It is referred to as the small page

family.

The NAND512R3A2C, NAND512R4A2C, and NAND512W3A2C have a density of 512

Mbits and operate with either a 1.8 V or 3 V voltage supply. The size of a page is either

528 bytes (512 + 16 spare) or 264 words (256 + 8 spare) depending on whether the

device has a x8 or x16 bus width.

The address lines are multiplexed with the Data Input/Output signals on a multiplexed x8

or x16 input/output bus. This interface reduces the pin count and makes it possible to

migrate to other densities without changing the footprint.

To extend the lifetime of NAND flash devices it is strongly recommended to implement an

error correction code (ECC). The use of ECC correction allows to achieve up to 100,000

program/erase cycles for each block. A write protect pin is available to give a hardware

protection against program and erase operations.

12.2 Features

• High density NAND flash memories

o 512-Mbit memory array

o Cost effective solutions for mass storage applications

• NAND interface

o x8 or x16 bus width

o Multiplexed address/ data

• Supply voltage: 1.8 V, 3 V

• Page size

o x8 device: (512 + 16 spare) bytes

o x16 device: (256 + 8 spare) words

• Block size

o x8 device: (16K + 512 spare) bytes

o x16 device: (8K + 256 spare) words

• Page read/program

o Random access: 12 μs (3 V)/15 μs (1.8 V) (max)

o Sequential access: 30 ns (3 V)/50 ns (1.8 V) (min)

o Page program time: 200 μs (typ)

• Copy back program mode

• Fast block erase: 2 ms (typ)

Page 36

• Status register

• Electronic signature

• Chip Enable ‘don’t care’

• Security features

o OTP area

• Serial number (unique ID) option

• Hardware data protection

o Program/erase locked during power transitions

• Data integrity

o 100,000 program/erase cycles (with ECC)

o 10 years data retention

• RoHS compliant packages

• Development tools

o Error correction code models

o Bad blocks management and wear leveling algorithms

12.3 Pinning

Page 37

13 LNBH23L (U6)

13.1 Description

Intended for analog and digital satellite receivers,the LNBH23L is a monolithic voltage

regulator

and interface IC, assembled in QFN32 5 x 5 specifically designed to provide the 13 / 18 V

power supply and the 22 kHz tone signalling to the LNB down-converter in the antenna

dish or to

the multi-switch box. In this application field, it offers a complete solution with extremely

low

component count, low power dissipation together with simple design and I²C standard

interfacing.

13.2 Features

• Complete interface between LNB and I²C bus

• Built-in DC-DC converter for single 12 V supply operation and high efficiency (typ.

93% @ 0.5 A)

• Selectable output current limit by external resistor

• Compliant with main satellite receivers output voltage specification

• Auxiliary modulation input (EXTM pin) facilitates DiSEqC™ 1.X encoding

• Accurate built-in 22 kHz tone generator suits widely accepted standards

• Low-drop post regulator and high efficiency step-up PWM with integrated power

NMOS allow low power losses

• Overload and over-temperature internal protections with I²C diagnostic bits

• LNB short circuit dynamic protection

• +/- 4 kV ESD tolerant on output power pins

Page 38

13.3 Block diagram

14 Advanced DVB-S/S2 demodulator M88DS3002 (U3)

14.1 Description

The M88DS3002 is an advanced single-chip demodulator for digital satellite television

broadcasting. It is fully compliant with the DVB-S/S2 standard and can support QPSK,

8PSK, 16APSK and 32APSK demodulation schemes. The chip provides a fast, easy-toapply and cost-effective front-end solution for digital satellite receiver. The M88DS3002

accepts baseband differential or single ended I and Q signals from a tuner, then

digitizes, demodulates and decodes the signals, and finally outputs an MPEG transport

stream. The M88DS3002 supports symbol rate from 1 Msps up to 45 Msps, and code

rate from 1/4 to 9/10. Its features cover blind scan, fade detection, timing and carrier

recovery, performance monitoring, co-channel interference cancellation, command

interface, and DiSEqC™ 2.X interface, etc. The device is controlled via a 2-wire serial

bus. The M88DS3002 works properly with 1.25 V and 3.3 V voltage supplies. Typically,

the power consumption is around 390 mW. The chip is available in a 64-pin QFN

package and is RoHS compliant.

14.2 Features

• Multi-standard demodulation

• Compliant with DVB-S/S2 specification

• QPSK, 8PSK, 16APSK and 32APSK demodulation schemes

• Maximum channel bit rate is 130 Mbps

• Maximum symbol rates are: 45 Msps for QPSK and 8PSK; 36 Msps for 16APSK

and 28 Msps for 32APSK

Page 39

• DSP features

• Symbol rate sweeping

• I/Q impairment cancellation

• Automatic spectrum inversion

• Adaptive equalizer for RF reflection removal

• Roll-off factor automatic identification

• Blind scan for programming search

• High performance on-chip micro-controller

• Multi-error monitor

• Accurate SNR estimation

• Multi-lock indicators

• Clipping rate reporter

• DC removal

• Automatic frequency correction (AFC)

• Fast timing loop acquisition

• Robust frame synchronization scheme

• Phase noise indicator

• Fast system recovery from fading or other abnormal conditions

• Co-channel interference cancellation

• Constellation monitor

• Interface

• DVB-S/S2 common, parallel and serial MPEG output interface compliant

• 2-wire serial bus to configure the device

• 2-wire bus repeater for tuner configuration

• DiSEqC™ 2.X compliant interface

• General purpose output (GPO)

• Dedicated reference clocks (13.5MHz / 27MHz) generation

• System

o On-chip 8-bit ADC

o On-chip PLL for master clock from a 27 MHz external clock or quartz

crystal

o Sleep mode supported

Page 40

14.3 Pin

Assignment

---Block Diagram of M88DS3002---

Page 41

15 LM1117 (U175, U180, U181)

15.1 General description

The LM1117 is a series of low dropout voltage regulators with a dropout of 1.2V at 800mA

of load current. It has the same pin-out as National Semiconductor’s industry standard

LM317. The LM1117 is available in an adjustable version, which can set the output

voltage from 1.25V to 13.8V with only two external resistors. In addition, it is also

available in five fixed voltages, 1.8V, 2.5V, 2.85V, 3.3V, and 5V. The LM1117 offers

current limiting and thermal shutdown. Its circuit includes a zener trimmed bandgap

reference to as-sure output voltage accuracy to within ±1%. The LM1117 series is

available in SOT- 223, TO-220, and TO-252 D-PAK packages. A minimum of

tantalum capacitor is required at the output to improve the transient response and

stability.

15.2 Features

• Available in 1.8V, 2.5V, 2.85V, 3.3V, 5V, and Adjustable Versions

• Space Saving SOT-223 Package

• Current Limiting and Thermal Protection

• Output Current 800mA

• Line Regulation 0.2% (Max)

• Load Regulation 0.4% (Max)

• Temperature Range

• LM1117 0°C to 125°C

• LM1117I -40°C to 125°C

10μF

15.3 Applications

• 2.85V Model for SCSI-2 Active Termination

• Post Regulator for Switching DC/DC Converter

• High Efficiency Linear Regulators 15

• 32” TFT TV Service Manual 10/01/2005

• Battery Charger

• Battery Powered Instrumentation

15.4 Absolute maximum ratings

Page 42

15.5 Pinning

16 MP2012 (U176)

17 General description

The MP2012 is a fully integrated, internally compensated 1.2MHz fixed frequency PWM

step-down converter. It is ideal for powering portable equipment that runs from a single

cell Lithium-Ion (Li+) Battery, with an input range from 2.7V to 6V. The MP2012 can

provide up to 1.5A of load current with output voltage as low as 0.8V. It can also operate

at 100% duty cycle for low dropout applications. With peak current mode control and

internal compensation, the MP2012 is stable with ceramic capacitors and small inductors.

Fault condition protection includes cycle-by-cycle current limiting and thermal shutdown.

17.1 Features

• 2.7-6V Input Operation Range

• Output Adjustable from 0.8V to VIN

• 1 μA Max Shutdown Current.

• Up to 95% Efficiency

• 100% Duty Cycle for Low Dropout

• Applications

• 1.2MHz Fixed Switching Frequency

• Stable with Low ESR Output Ceramic

• Capacitors

• Thermal Shutdown

• Cycle-by-Cycle Over Current Protection

• Short Circuit Protection

• Available in 6-pin 3x3mm QFN

Page 43

17.2 Pinning

Pin # Name

Description

1

FB

Feedback input. An external resistor divider from

output voltage.

2

GND,

Pad

Ground pin. Connect exposed pad to ground

3

SW

Switch node to the inductor.

4

PVIN

Input supply pin for power FET.

5

VIN

Input Supply pin for controller. Put small

decoupling ceramic near this pin.

6

EN

Enable input, “High” enables MP2012. EN is

pulled to GND with 1Meg internal resistor.

Exposed

18 RTA8283A (U23, U173)

the output to GND, tapped to the FB pin sets the

plane for proper thermal performance.

18.1 General description

The RT8283A is a high-efficiency, monolithic synchronous step-down DC/DC converter

that can deliver up to 3A output current from a 4.5V to 23V input supply. The RT8283A's

current mode architecture and external compensation allow the transient response to be

optimized over a wide range of loads and output capacitors. Cycle-by-cycle current limit

provides protection against shorted outputs and soft-start eliminates input current surge

during start-up. The RT8283A also provides output under voltage protection and thermal

shutdown protection. The low current (<3μA) shutdown mode provides output

disconnect,

enabling easy power management in batterypowered systems. The RT8283A is available

in a SOP-8 package.

18.2 Features

• ±1.5% High Accuracy Feedback Voltage

• Integrated N-MOSFET Switches

• Current Mode Control

• Fixed Frequency Operation : 340kHz

• Output Adjustable from 0.8V to 20V

• Up to 95% Efficiency

• Thermal Shutdown Protection

Page 44

Page 45

18.3 Pinning

Pin No.

Pin

Name

Description

1

BOOT

greater ceramic capacitor from BOOT to SW pins.

2

large ceramic capacitor.

3

4, 9 (Exposed

Pad)

5

FB

Feedback Input pin is connected to the converter output.

6

COMP

Compensation Node. COMP is used to compensate the

7

EN

Enable Input Pin. Logic high enables the converter; a

automatic startup.

8

SS

Soft-Start Control Input. SS controls the soft-start period.

Bootstrap for high-side gate driver. Connect a 0.1μF or

VIN

SW Phase Node--Connect to external L-C filter..

GND Ground.

Input Supply 4.5V to 23V. Must bypass with a suitably

It is used to set the output of the converter to regulate to

the desired value via an internal res divider. For an

adjustable output, an external res divider is connected to

this pin.

regulation Control loop. Connect a series RC network

from COMP to GND. In some cases, an additional

capacitor from COMP to GND is required.

logic low forces the RT8253A into shutdown mode.

Attach this pin to VIN with a 100kΩ pull up resistor for

Connect a capacitor from SS to GND to set the soft-start

period. A 0.1μF capacitor sets the soft-start period to

13.5ms.

Page 46

19 MP1583 (U174)

Pin

No.

Pin

Name

Description

High-Side Gate Drive Bootstrap Input. BS supplies the drive for the

2

IN

Power Input. Drive IN with a 4.75V to 23V power source.

3

SW

Power Switching Out is the switching node that supplies power to the

output

4

GND

Ground.

5

FB

Feedback Input. FB senses the output voltage and regulates it. Drive

threshold is 1.222V.

6

COMP

Compensation Node is used to compensate the regulation control

loop.

19.1 General description

The MP1583 is a step-down regulator with a built-in internal Power MOSFET. It

achieves

3A of continuous output current over a wide input supply range with excellent load and

line regulation. Current mode operation provides fast transient response and eases

loop stabilization. Fault condition protection includes cycle-by-cycle current limiting and

thermal shutdown. An adjustable soft-start reduces the stress on the input source at startup. The MP1583 requires a minimum number of external components, providing a

compact solution.

19.2 Features

• 3A Output Current

• Programmable Soft-Start

• 100mΩ

Internal

• Stable with Low ESR Output Ceramic Capacitors

• Up to 95% Efficiency

• 20μA Shutdown

• Fixed 385KHz Frequency

• Thermal Shutdown

• Cycle-by-Cycle Over Current Protection

• Wide 4.75V to 23V Operating Input Range

• Output Adjustable from 1.22V to 21V

• Under-Voltage Lockout

Power

Mode

MOSFET Switch

19.3 Pinning

1 BOOT

high-side N-Channel MOSFET switch.

FB with a resistive voltage divider from the output voltage. FB

Page 47

7

EN

Enable/UVLO. A voltage greater than 2.71V enables operation. For

complete low current shutdown the EN pin voltage needs to be at less

reaches 2.71V.

8

SS

Soft-Start Control Input. SS controls the soft-start period.

than 900mV. When the voltage on EN exceeds 1.2V, the internal

regulator will be enabled and the soft-start capacitor will begin to

charge. The MP1583 will start switching after the EN pin voltage

20 FDC642

20.1 General description

This P-Channel 2.5V specified MOSFET is produced using Fairchild’s advanced

PowerTrench® process that has been especially tailored to minimize on-state resistance

and yet maintain low gate charge for superior switching performance.

These devices have been designed to offer exceptional power dissipation in a very small

footprint for applications where the larger packages are impractical.

20.2 Features

• Max rDS(on) = 65 mΩ at VGS = -4.5 V, ID = -4.0 A

• Max rDS(on)

• Fast switching speed

• Low gate charge (11nC typical)

• High performance trench technology for extremely low rDS(on)

• SuperSOTTM-6 package: small footprint (72% smaller than standard

• Termination is Lead-free and RoHS Compliant

20.3 Pinning

=

100 mΩ at VGS = -2.5 V, ID = -3.2 A

SO-8); low profile (1 mm thick)

Page 48

21 FDC604P

21.1 General description

This P-Channel 1.8V specified MOSFET uses Fairchild’s low voltage PowerTrench

process. It has been optimized for battery power management applications.

21.2 Features

• –5.5 A, –20 V. RDS(ON) = 33 mΩ @ VGS = –4.5 V

• RDS(ON) = 43 mΩ @ VGS = –2.5 V

=

• RDS(ON)

• Fast switching speed.

• High performance trench technology for extremely low RDS(ON)(S)

21.3 Pinning

60 mΩ @ VGS = –1.8 V

Page 49

22 Connectors

22.1 SCART (SC1)

22.2 HDMI (CN707, CN708)

Page 50

-

.

22.3

VGA

(CN711)

14.

VERTICAL

15. DOC CLOCK

SYNC

_.

15

.

Page 51

23 Service menu mode

To enter the service menu, press MENU-4-7-2-5 keys consecutively, on the remote control. The top-level

service menu will appear. All submenus can be selected via Up/Down keys and displayed by pressing OK

key. When a submenu is displayed, top-level service menu disappears. Pressing RETURN key, returns to

the one level higher menu. Pressing the MENU key will exit service menu.

Some items are changeable at service menu, the values of which are stored in the NVM when the menu is

closed. Some items are read-only, which can only be changed by Profile Manager and displayed in service

menu for convenience.

23.1 Main service menu

Service menu or a sub-menu is displayed on the screen when the TV is in one of the TV/AV/PC modes. It

shows what the items are set in Profile Manager. It is a read-only screen, not writable.

It shows the following items:

TV Life Time: The number of minutes the set is in the “On” mode.

Standby SW Version: The version number of the Stand-by software.

Mboot Version: The version number of the Mboot software.

PANEL: The LCD panel identification including the software version information.

PQ: Picture quality tool version information.

PROFILE: TV specific option profile

PIX FILES: Not applicable

HW Profile Version: The version number of the hardware profile.

SW Profile Version: The version number of the software profile.

Lan Profile Version: The version number of the Lan profile.

Customer: Philips

Items exist in the main screen of service menu. Also, software version number and DCF id are written in

the header of service menu.

Page 52

The main items in Service Menu:

23.2 Video Settings

RF AGC adjustments for neighbour and image channels exist or don't. Also, ADC Calibration gain

and offset values for RGB separately due to selected sources

23.3 Audio Settings

Surround type and surround mode text items are displayed.

Page 53

23.4 Options 1

Profile options such as AUTO TV off time, Power up mode, EPG type, etc. are displayed in options 1.

23.5 Options 2

Profile options such as APS sorting, Dynamic Menu, Auto zoom mode etc. are displayed in Options 2.

Page 54

23.6 Tuning Settings

Tuner type is displayed.

23.7 Source Settings

Enable and disabled sources are displayed.

When TV is disabled, Items which are connected to Tuner are picked off from menu. (Install and Retune

Menu, Channel List Menu...).

23.8 Diagnostic

The result of various diagnostic tests are displayed here.

23.9 USB operations

USB operations are performed by pressing that button.

See Service Menu Design Idea for Menu structure, look and feel, position, etc…

Page 55

Video Settings

• RF AGC SECAM

Options 2

RF AGC NEIGHBOUR NO IMAGE NO

•

RF AGC NEIGHBOUR NO IMAGE YES

•

RF AGC NEIGHBOUR YES IMAGE NO

•

RF AGC NEIGHBOUR YES IMAGE YES

•

RF AGC

•