Page 1

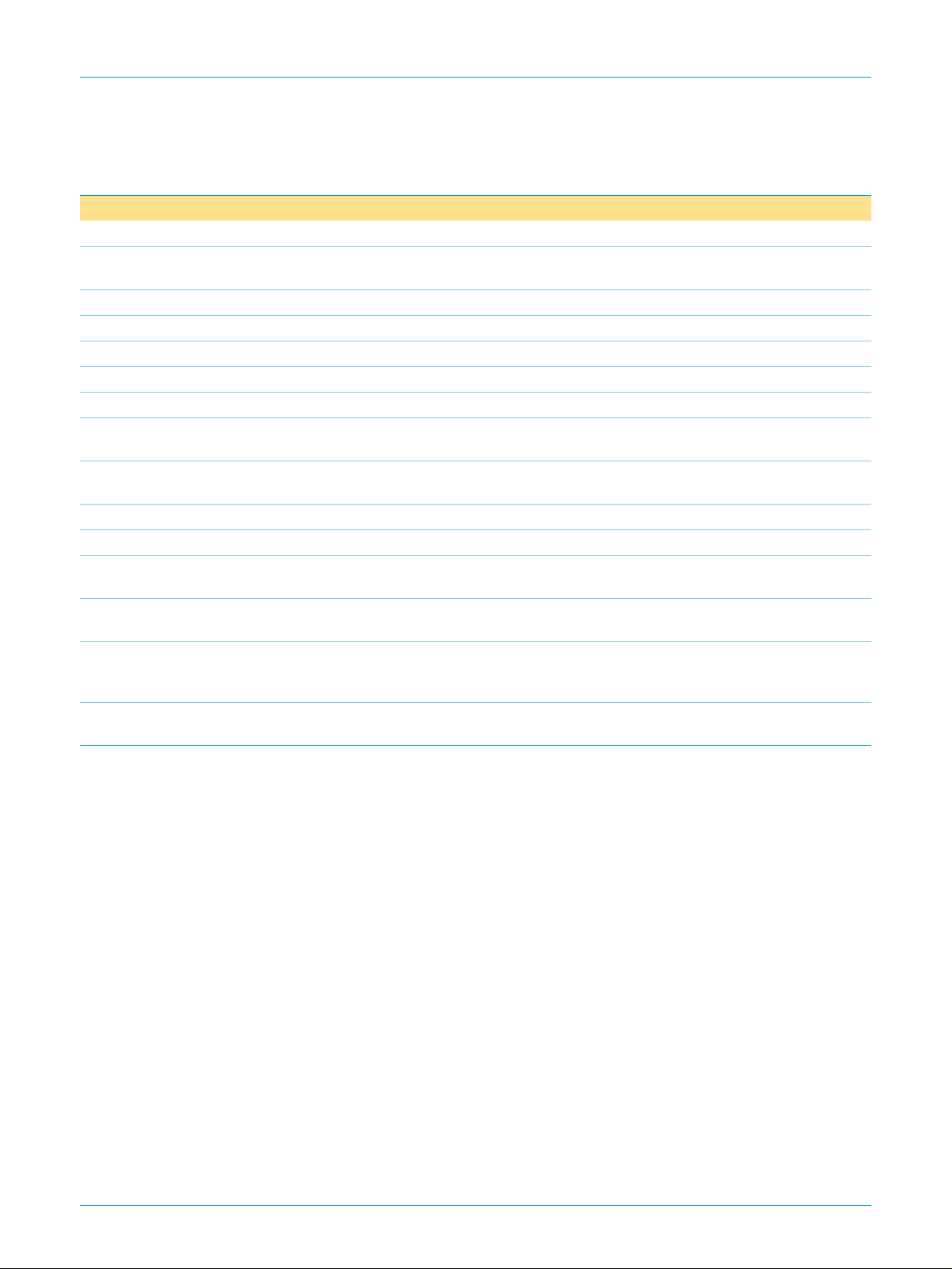

UM10110_1

PNX8550 Programmable Source Decoder

with Integrated Peripherals

Rev. 02 — July 21 2004

Page 2

Philips Semiconductors

Contents

Chapter 1: Functional specification

PNX8550

Programmable Source Decoder with Integrated Peripherals

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. PNX8550 Functional Overview . . . . . . . . . . . . 3

3. PNX8550 Feature Summary . . . . . . . . . . . . . . . 5

4. Compatibility with the PNX8525 . . . . . . . . . . . 6

5. Analog/Digital Standard Definition Video

Improvement Capabilities . . . . . . . . . . . . . . . . . 7

5.1 Temporal-Spatial Improvement Processing . . . . 7

5.2 Temporal Noise Reduction . . . . . . . . . . . . . . . . . . .8

6. HD Decode and Display Capabilities . . . . . . 8

6.1 Dual HD Decode/Display Using 2 PNX8550 . . . . 9

7. Internal Functional Overview . . . . . . . . . . . . . 11

8. Internal Functional Overview . . . . . . . . . . . . . 12

8.1 Overview of Function Partitioning . . . . . . . . . . . .12

9. Integrated Processors . . . . . . . . . . . . . . . . . . . .14

9.1 PR4450 General Purpose Processor . . . . . . . . . 14

9.2 Dual TM3260 VLIW Media Processors . . . . . . .15

9.2.1 Prefetch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

10. Digital Video/Transport Stream Inputs. . . . 17

10.1 Backwards Compatibility . . . . . . . . . . . . . . . . . . . . 17

10.2 New Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

11. MPEG2 Decoding . . . . . . . . . . . . . . . . . . . . . . . . . 19

11.1 MPEG System Processor (MSP). . . . . . . . . . . . . 19

11.2 DVD Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

11.3 Software Processing of MPEG2 Streams . . . . . 21

11.4 VMPG - MPEG2 Decoder and VLD2 . . . . . . . . . 21

12. Image Processing Hardware . . . . . . . . . . . . . 22

12.1 Pixel Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

12.2 Video Input Processor (VIP) . . . . . . . . . . . . . . . . . 23

12.3 Tunnel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

12.4 Quality Temporal Noise Reduction (QTNR)

and Video Measurement . . . . . . . . . . . . . . . . . . . . 24

12.5 Memory Based Scaler (MBS). . . . . . . . . . . . . . . . 25

12.6 2D and DMA Engine . . . . . . . . . . . . . . . . . . . . . . .26

12.7 Quality Video Composition Processor

(QVCP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

12.8 Integrated Digital Video Encoder (DENC) . . . . . 30

12.9 PNX8510/11 Analog Companion Chip . . . . . . . .30

13. Audio Processing and Input/Output. . . . . . 30

13.1 Audio Processing . . . . . . . . . . . . . . . . . . . . . . . . . . 30

13.2 Audio Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . .31

13.3 Audio Compatibility . . . . . . . . . . . . . . . . . . . . . . . . 31

14. Miscellaneous Functions . . . . . . . . . . . . . . . . 31

14.1 Enhanced DMA Controller (EDMA) . . . . . . . . . . 31

14.2 Semaphores. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

14.3 Inter-Processor Communication. . . . . . . . . . . . . 32

15. System Memory. . . . . . . . . . . . . . . . . . . . . . . . . . 32

15.1 System DRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

15.2 System EEPROM, ROM or Flash . . . . . . . . . . . 34

16. Security Provisions . . . . . . . . . . . . . . . . . . . . . . 34

16.1 Power Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

17. Peripheral Interfaces. . . . . . . . . . . . . . . . . . . . . 35

17.1 IDE Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

17.2 MemoryStick and MultiMediaCard . . . . . . . . . . . 36

17.3 GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

17.3.1 Software I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

17.3.2 Timestamping . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

17.3.3 Event Sequence Monitoring and Signal

Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

17.3.4 Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . 38

17.3.5 Timer/Counter Capabilities . . . . . . . . . . . . . . . . . 38

17.3.6 GPIO Pin Reset Value . . . . . . . . . . . . . . . . . . . . . 39

17.3.7 Compatibility with PNX8525 . . . . . . . . . . . . . . . . 39

17.3.8 Remote Control Receiver/Blaster. . . . . . . . . . . . 39

17.4 PCI2.2 and XIO16 Bus Interface Unit . . . . . . . . 40

17.4.1 PCI Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

17.4.2 Simple Peripheral Capabilities (XIO8/16) . . . . . 40

18. Endian Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

19. PNX8550 Boot. . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

20. Boundary Scan . . . . . . . . . . . . . . . . . . . . . . . . . . 43

21. Changes from PNX8550_RevA to

PNX8550_RevB . . . . . . . . . . . . . . . . . . . . . . . . . . 44

21.1 MBS2 Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

21.1.1 Frequency of Operation and Performance . . . . 44

21.2 Vertical Peaking Block (VPK) . . . . . . . . . . . . . . . 44

21.2.1 Frequency of Operation and Performance . . . . 45

21.3 Video Streaming Connections . . . . . . . . . . . . . . 45

21.3.1 Tunnel Interface to QVCP . . . . . . . . . . . . . . . . . . 45

21.3.2 MBS2 Block to QVCP. . . . . . . . . . . . . . . . . . . . . . 45

21.3.3 Vertical Peaking Block to QVCP . . . . . . . . . . . . 45

21.4 Contrast Brightness Control with Soft Clipper

(CBSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Chapter 2: Bus Architecture and System Memory Map

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 Bus Architecture Block Diagram . . . . . . . . . . . . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.3 Low Power Adapter Implementation . . . . . . . . . . . 3

3. DCS Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.1 DCS Controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

4. Standard System Memory Map . . . . . . . . . . . .6

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 i

4.1 Apertures in the Standard System Memory Map 6

4.2 Building the Standard System Memory Map . . . 7

4.3 Rationale for the Standard System Memory

Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

5. Hardware Limitations to Object Visibility . 8

6. Register Descriptions. . . . . . . . . . . . . . . . . . . . . 9

6.1 Aperture Control Registers . . . . . . . . . . . . . . . . . . 9

6.1.1 PCI, TM3260, and MIPS PR4450 . . . . . . . . . . . . 9

6.2 Global 2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . 9

Page 3

Philips Semiconductors

PNX8550

Programmable Source Decoder with Integrated Peripherals

7. Alternate System Memory Map with

External Host CPU. . . . . . . . . . . . . . . . . . . . . . . . 10

7.1 PCI Standard Boot and Memory Map

Assembly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

7.2 Internal MIPS PR4450 and External Host CPU 10

8. Memory Map Perspectives . . . . . . . . . . . . . . . 11

8.1 View from MIPS PR4450 . . . . . . . . . . . . . . . . . . .11

8.1.1 MIPS PR4450 Exception Vector Logic . . . . . . . . 12

Chapter 3: PMAN Hub

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 PNX8550 HUB Block . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.1 PMAN Arbiter (IP_1010) . . . . . . . . . . . . . . . . . . . . . 4

2.2.2 PMAN Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.2.3 DMA Gate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.2.4 Memory Bandwidth Monitor . . . . . . . . . . . . . . . . . . 7

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 8

3.1 Data Flow and Control. . . . . . . . . . . . . . . . . . . . . . . 8

3.1.1 Arbitration Algorithm . . . . . . . . . . . . . . . . . . . . . . . . 8

3.2 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . . 11

Chapter 4: DCS network and security

8.2 View from the TM3260 CPU Cores . . . . . . . . . . 13

8.3 View from PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . 14

8.3.1 PNX8550 as PCI Configuration Manager. . . . . 14

8.3.2 An External Host CPU as PCI Configuration

Manager . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

8.4 View from the MDCS and TDCS Buses . . . . . . 15

8.5 MMIO Base Address Map . . . . . . . . . . . . . . . . . . 16

3.2.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . 11

3.2.2 Reset-Related Issues . . . . . . . . . . . . . . . . . . . . . . 11

3.2.3 Register Programming Guidelines. . . . . . . . . . . 11

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . 12

4.1 PMAN Hub Arbiter Registers . . . . . . . . . . . . . . . 12

4.1.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 12

4.1.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.2 PMAN Security Registers . . . . . . . . . . . . . . . . . . 14

4.2.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 14

4.2.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.3 Memory Bandwidth Monitor Registers . . . . . . . 25

4.3.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 25

4.3.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Protection Mechanisms . . . . . . . . . . . . . . . . . . . 2

2.1 MIPS PR4450 Protection Mechanisms . . . . . . . .2

2.2 TM3260 Protection Mechanisms . . . . . . . . . . . . . .2

3. DCS Target Access Control . . . . . . . . . . . . . . .3

3.1 DCS Controller Block Level Diagram . . . . . . . . . . 3

3.1.1 DCS Initiator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.2 DCS Target . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.3 Programmable Address Map . . . . . . . . . . . . . . . . . 5

3.1.4 Error Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1.5 Selective Blocking of Initiators (System

Security) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1.6 Interrupt Generation. . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1.7 Programmable Timeout. . . . . . . . . . . . . . . . . . . . . . 6

3.1.8 Null Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.1.9 Arbitration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2 DCS Adapters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2.1 Endianness . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.3 DCS Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Chapter 5: Endian mode

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Endian Mode Theory . . . . . . . . . . . . . . . . . . . . . . 1

2.1 Law 1: The “CPU Rule” . . . . . . . . . . . . . . . . . . . . . .2

2.2 Law 2: The “DMA Convention Rule” . . . . . . . . . . .4

3. Endian Mode Architecture Details . . . . . . . . . 4

3.3.1 Deadlock Handling . . . . . . . . . . . . . . . . . . . . . . . . . 8

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . . 8

4.1 MIPS DCS Network Controller Configuration

Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.1.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.1.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4.2 MIPS DCS Network Controller Security

Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.2.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 12

4.2.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.3 TriMedia DCS Network Controller

Configuration Registers . . . . . . . . . . . . . . . . . . . . 14

4.3.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 14

4.3.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.4 TriMedia DCS Network Controller Security

Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 18

4.4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1 Global Endian Mode . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2 Peripheral Control . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.3 Peripheral DMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.4 SIMD Programming Issues . . . . . . . . . . . . . . . . . . 6

3.5 Optional Endian Mode Override . . . . . . . . . . . . . . 7

4. Audio In—Programmer’s View (Example) 7

5. Detailed Example . . . . . . . . . . . . . . . . . . . . . . . . . 8

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 ii

Page 4

Philips Semiconductors

Chapter 6: Pixel formats

PNX8550

Programmable Source Decoder with Integrated Peripherals

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Summary of Native Pixel Formats . . . . . . . . . 2

3. Native Pixel Format Representation. . . . . . . 3

3.1 Indexed Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.2 16-Bit Pixel-Packed Formats . . . . . . . . . . . . . . . . . 4

3.3 32-Bit Pixel-Packed Formats . . . . . . . . . . . . . . . . . 4

3.4 Packed YUV 4:2:2 Formats . . . . . . . . . . . . . . . . . . 5

3.5 Planar YUV 4:2:0 and YUV 4:2:2 Formats . . . . . 6

3.5.1 Planar Variants . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Chapter 7: Boot

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 Boot Block Level Diagram. . . . . . . . . . . . . . . . . . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2.1 MMIO Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2.2 I2C Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

2.2.3 Boot Control/State Machine . . . . . . . . . . . . . . . . . . 4

2.2.4 Internal Script Block . . . . . . . . . . . . . . . . . . . . . . . . . 4

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 5

Chapter 8: Clocks

3.5.2 Semi-Planar 10-Bit YUV 4:2:2 and 4:2:0

Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.5.3 Packed 10-bit YUV 4:2:2 format. . . . . . . . . . . . . 10

4. Universal Converter. . . . . . . . . . . . . . . . . . . . . . 10

5. Alpha Value and Pixel Transparency . . . . 11

6. YUV and RGB Values . . . . . . . . . . . . . . . . . . . . 11

7. Image Storage Format . . . . . . . . . . . . . . . . . . . 11

8. System Endian Mode . . . . . . . . . . . . . . . . . . . . 12

3.1 Boot Mode Configuration. . . . . . . . . . . . . . . . . . . . 5

3.2 Internal vs. External Boot. . . . . . . . . . . . . . . . . . . . 6

3.3 Symbolic Boot Language. . . . . . . . . . . . . . . . . . . . 6

3.4 Internal Boot Scripts . . . . . . . . . . . . . . . . . . . . . . . . 7

3.5 External Boot Scripts . . . . . . . . . . . . . . . . . . . . . . . 8

3.5.1 External I2C Boot EEPROM Types . . . . . . . . . . . 8

3.5.2 External EEPROM Boot Script Binary Format. . 9

3.5.3 Details on I2C Operation . . . . . . . . . . . . . . . . . . . 10

3.5.4 Internal Host Booting Using an External Script 10

3.5.5 External Host Boot . . . . . . . . . . . . . . . . . . . . . . . . 11

3.6 Bootup Sequence . . . . . . . . . . . . . . . . . . . . . . . . . 12

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 Clocks Block Level Diagram. . . . . . . . . . . . . . . . . . 3

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 4

3.0.1 System Level Clocks . . . . . . . . . . . . . . . . . . . . . . . . 4

3.0.2 Sources of the PNX8550 Clocks . . . . . . . . . . . . . .7

3.0.3 DDS Programming . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.0.4 PLL Requirements . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.0.5 Oscillator Pad Requirements . . . . . . . . . . . . . . . . 12

3.0.6 Special Clock Relationships . . . . . . . . . . . . . . . . .12

3.0.7 Clock Control and Selection Logic . . . . . . . . . . . 12

3.0.8 PLL Clock Blocking . . . . . . . . . . . . . . . . . . . . . . . .18

3.0.9 Bypass Clock Sources. . . . . . . . . . . . . . . . . . . . . . 18

3.0.10 Power-Up and Reset Sequence . . . . . . . . . . . . .20

Chapter 9: Reset

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 Reset Block Level Diagram . . . . . . . . . . . . . . . . . . 1

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 2

3.1 Data Flow and Control. . . . . . . . . . . . . . . . . . . . . . . 2

3.0.11 Powerdown. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.0.12 DFT Clock Selection. . . . . . . . . . . . . . . . . . . . . . . 20

3.0.13 DFT Frequency Counter . . . . . . . . . . . . . . . . . . . 22

3.0.14 Clock Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.1 Power Management . . . . . . . . . . . . . . . . . . . . . . . 24

4. Application Notes. . . . . . . . . . . . . . . . . . . . . . . . 24

4.1 Essential Operating Infrastructure During

Powerdown. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.2 Special Modules . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.3 Peripheral Module Powerdown Sequence . . . . 25

4.4 Peripheral Module Wakeup Sequence . . . . . . . 26

4.5 DCS Network Power “Spreading” . . . . . . . . . . . 26

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 27

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.1.1 PERI_RST State Machine. . . . . . . . . . . . . . . . . . . 4

3.1.2 MIPS_RST State Machine. . . . . . . . . . . . . . . . . . . 5

3.1.3 SYS_RST_OUT State Machine . . . . . . . . . . . . . . 6

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . . 7

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 10: Power management

1. Power Management Mechanisms . . . . . . . . . 1 1.1 Clock Management. . . . . . . . . . . . . . . . . . . . . . . . . 1

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 iii

Page 5

Philips Semiconductors

PNX8550

Programmable Source Decoder with Integrated Peripherals

1.1.1 Essential Operating Infrastructure During

Powerdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1.2 Special Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1.3 Peripheral Module Powerdown Sequence. . . . . . 2

1.1.4 Peripheral Module Wakeup Sequence . . . . . . . . . 3

1.2 Special Power Management Mechanisms. . . . . . 3

1.2.1 PR4450 MIPS Processor . . . . . . . . . . . . . . . . . . . . 3

1.2.2 TriMedia 3260 CPUs . . . . . . . . . . . . . . . . . . . . . . . . 4

Chapter 11: Interrupts

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 Interrupts Block Level Diagram . . . . . . . . . . . . . . . 1

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Chapter 12: Global registers

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Global Register Descriptions. . . . . . . . . . . . . . 1

2.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2.1.1 Global 1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Chapter 13: PCI-XIO

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 PCI-XIO Block Level Diagram . . . . . . . . . . . . . . . . 3

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 4

3.1 Data Flow and Control. . . . . . . . . . . . . . . . . . . . . . . 4

3.1.1 NAND-Flash Interface Operation. . . . . . . . . . . . . . 5

3.1.2 Motorola Style Interface . . . . . . . . . . . . . . . . . . . . 10

3.1.3 NOR Flash Interface . . . . . . . . . . . . . . . . . . . . . . . 11

3.1.4 IDE Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.1.5 PCI Interrupt Enable Register . . . . . . . . . . . . . . .17

4. Application Notes . . . . . . . . . . . . . . . . . . . . . . . .17

1.2.3 SDRAM Controller . . . . . . . . . . . . . . . . . . . . . . . . . 4

2. System Powerdown Mode Examples . . . . . 5

2.1 Reduced Power Mode . . . . . . . . . . . . . . . . . . . . . . 5

2.2 Minimal Power Mode . . . . . . . . . . . . . . . . . . . . . . . 6

2.3 Shutdown Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.3.1 Procedure for Shutting Down . . . . . . . . . . . . . . . . 6

2.3.2 Procedure for Power Up . . . . . . . . . . . . . . . . . . . . 7

3. General Operations . . . . . . . . . . . . . . . . . . . . . . . 2

3.1 Data Flow and Control . . . . . . . . . . . . . . . . . . . . . . 2

3.1.1 Register Programming Guidelines. . . . . . . . . . . . 6

4. Application Notes. . . . . . . . . . . . . . . . . . . . . . . . . 6

2.1.2 Global 2 Register Summary . . . . . . . . . . . . . . . . . 2

2.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.1 Global 1 Register Descriptions. . . . . . . . . . . . . . . 3

2.2.2 Global 2 Register Descriptions. . . . . . . . . . . . . . . 7

4.1 DTL MMIO Interface. . . . . . . . . . . . . . . . . . . . . . . 17

4.2 DVP Memory Bus Interface. . . . . . . . . . . . . . . . . 18

4.3 XIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.3.1 Motorola Interface . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.3.2 NAND-Flash Interface . . . . . . . . . . . . . . . . . . . . . 19

4.3.3 NOR Flash Interface. . . . . . . . . . . . . . . . . . . . . . . 19

4.3.4 IDE Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.4 PCI Endian Support . . . . . . . . . . . . . . . . . . . . . . . 20

4.5 General Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.5.1 Known PCI Non-Compliance . . . . . . . . . . . . . . . 21

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 21

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 21

5.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Chapter 14: DDR SDRAM

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 3

2.1 DDR Controller Block Level Diagram . . . . . . . . . . 3

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.3 Input processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.4 Start and Warm Start . . . . . . . . . . . . . . . . . . . . . . . . 5

2.4.1 Start. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.4.2 Warm Start. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.4.3 Observing Start State . . . . . . . . . . . . . . . . . . . . . . . 5

2.4.4 Sequence of Actions . . . . . . . . . . . . . . . . . . . . . . . . 5

2.5 Arbitration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.5.1 First Level Arbitration: Between DMA and

CPUs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.5.2 Second Level Arbitration: Among CPUs . . . . . . . 8

2.5.3 Dynamic Ratios. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 iv

2.5.4 Pre-Emption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.5.5 Back Log Buffer (BLB) . . . . . . . . . . . . . . . . . . . . . 11

2.5.6 PMAN (Hub) versus DDR Controller

Interaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.6 Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.6.1 Memory Regions . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.6.2 Memory Region Mapping Scheme. . . . . . . . . . . 13

2.7 DDR Memory Rank Locations . . . . . . . . . . . . . . 15

2.7.1 Some Examples . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3. General Operations . . . . . . . . . . . . . . . . . . . . . . 16

3.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . 16

3.2 Asynchronous Reset Synchronization. . . . . . . . 16

3.3 Programming via the DTL Port . . . . . . . . . . . . . . 17

3.3.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.4 Power Management . . . . . . . . . . . . . . . . . . . . . . . 17

3.4.1 Halting and Unhalting . . . . . . . . . . . . . . . . . . . . . . 17

Page 6

Philips Semiconductors

PNX8550

Programmable Source Decoder with Integrated Peripherals

3.4.2 Handshaking Protocol . . . . . . . . . . . . . . . . . . . . . . 18

3.4.3 MMIO Directed Halt . . . . . . . . . . . . . . . . . . . . . . . . 18

3.4.4 Auto Halt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.4.5 Observing Halt Mode . . . . . . . . . . . . . . . . . . . . . . . 19

3.4.6 Sequence of Actions . . . . . . . . . . . . . . . . . . . . . . . 20

4. Application Notes . . . . . . . . . . . . . . . . . . . . . . . .20

4.1 Memory Configurations . . . . . . . . . . . . . . . . . . . . .20

4.2 Error Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

4.3 Latency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Chapter 15: CTL12 Tunnel

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 CTL12 Tunnel Block Level Diagram . . . . . . . . . . .2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.1 Transaction Overview . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.2 Bandwidth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

2.2.3 Latency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 5

3.1 Internal Interface Protocol. . . . . . . . . . . . . . . . . . . . 5

3.2 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.3 Register Programming Guidelines . . . . . . . . . . . . 6

3.4 Tunnel Specifics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4.4 Endianness. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.5 Booting the DDR SDRAM Controller . . . . . . . . . 22

4.6 Data Coherency. . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.7 Programming the Internal Arbiter . . . . . . . . . . . . 26

4.8 Compatible DDR Parts List . . . . . . . . . . . . . . . . . 27

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 30

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 31

5.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.4.1 CTL12 Tunnel Overview . . . . . . . . . . . . . . . . . . . . 6

3.4.2 CTL12 Tunnel Transmit and Receive

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.4.3 Multiplexing Overview . . . . . . . . . . . . . . . . . . . . . . 9

3.4.4 CTL12 Tunnel Flow Control . . . . . . . . . . . . . . . . 10

3.4.5 Write Transaction . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.4.6 Read Transaction . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.5 Tunnel Traffic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.5.1 North Bound MTL Traffic . . . . . . . . . . . . . . . . . . . 13

3.5.2 South Bound, DCS Traffic . . . . . . . . . . . . . . . . . . 13

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . 15

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 15

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Chapter 16: Smartcard UART

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 Smartcard UART Module Block Level Diagram . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 4

3.1 Cold and Warm Reset . . . . . . . . . . . . . . . . . . . . . . . 4

3.1.1 Cold Reset Procedure . . . . . . . . . . . . . . . . . . . . . . .4

3.1.2 Warm Reset Procedure . . . . . . . . . . . . . . . . . . . . . . 4

3.2 ISO 7816 UART Functional Description. . . . . . . . 5

Chapter 17: GPIO

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 GPIO Block Level Diagram. . . . . . . . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 2

3.1 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3.1.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . . 2

3.1.2 Events. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.3 GPIO Mode Settings . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.4 Reading and Writing GPIO Data . . . . . . . . . . . . . . 4

3.1.5 Signal Monitoring and Pattern Generation. . . . . . 6

3.1.6 Master Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . .6

3.1.7 Timestamp Units. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2.1 Activation and Deactivation Sequence . . . . . . . . 5

3.2.2 Transmit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2.3 Receive Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.2.4 ISO UART Interrupts . . . . . . . . . . . . . . . . . . . . . . . 9

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . 11

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 11

4.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.2.1 Smartcard UART1 Registers . . . . . . . . . . . . . . . 12

4.2.2 Smartcard UART2 Registers . . . . . . . . . . . . . . . 27

3.1.8 Event Queues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.1.9 IR Wakeup Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.1.10 Timer Counter Unit . . . . . . . . . . . . . . . . . . . . . . . . 18

3.1.11 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1.12 Event Queue Interrupts . . . . . . . . . . . . . . . . . . . . 19

3.1.13 Timestamp Unit Interrupts . . . . . . . . . . . . . . . . . . 20

3.1.14 IR Wakeup and Counter/Timer Unit Interrupts 20

3.1.15 Direct Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4. Applications Notes. . . . . . . . . . . . . . . . . . . . . . . 20

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 21

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 21

5.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 v

Page 7

Philips Semiconductors

Chapter 18: UART

PNX8550

Programmable Source Decoder with Integrated Peripherals

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 UART Block Level Diagram . . . . . . . . . . . . . . . . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.1 Clock Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.2 Register Programming Guidelines . . . . . . . . . . . . 3

Chapter 19: USB

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 3

2.1 USB Block Level Diagram. . . . . . . . . . . . . . . . . . . . 3

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 4

3.1 Components of USB System . . . . . . . . . . . . . . . . . 4

Chapter 20: High Performance I2C Ports (1 & 2)

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 HP IIC Block Level Diagram . . . . . . . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 2

3.1 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . 2

3.1.1 Master Transmit Mode. . . . . . . . . . . . . . . . . . . . . . . 3

3.1.2 Master Receive Mode . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.3 Slave Receive Mode . . . . . . . . . . . . . . . . . . . . . . . . 7

3.1.4 Slave Transmit Mode . . . . . . . . . . . . . . . . . . . . . . . 10

3.2 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . 12

3.2.1 Clocking Constraints . . . . . . . . . . . . . . . . . . . . . . . 12

3.3 Interrupt Processing. . . . . . . . . . . . . . . . . . . . . . . . 14

3.3.1 Interrupts from HS I2C. . . . . . . . . . . . . . . . . . . . . . 14

3.2.1 UART Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.2.2 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.2.3 Transmitter FIFO Function . . . . . . . . . . . . . . . . . . 4

3.2.4 Receiver FIFO Function. . . . . . . . . . . . . . . . . . . . . 4

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . . 4

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . 4

4.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

4.2.1 UART1 Module Registers . . . . . . . . . . . . . . . . . . . 5

4.2.2 UART2 Module Registers . . . . . . . . . . . . . . . . . . . 9

3.1.1 USB Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.2 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . 10

3.2.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . 10

3.2.2 Power Management . . . . . . . . . . . . . . . . . . . . . . . 10

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . 11

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 11

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3.2 Clearing Interrupts . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3.3 Enabling Interrupts . . . . . . . . . . . . . . . . . . . . . . . . 15

3.4 Power Management . . . . . . . . . . . . . . . . . . . . . . . 16

3.5 Register Programming Guidelines. . . . . . . . . . . 16

4. Application Notes. . . . . . . . . . . . . . . . . . . . . . . . 16

4.1 Module and Interrupt Status . . . . . . . . . . . . . . . . 16

4.1.1 Example of a Master Transmitter . . . . . . . . . . . . 16

4.2 Status Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 23

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 23

5.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.2.1 HP I2C1 Module Registers . . . . . . . . . . . . . . . . . 24

5.2.2 HP I2C2 Module Registers . . . . . . . . . . . . . . . . . 28

Chapter 21: Fast I2C Ports (3 & 4)

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2. Functional Description . . . . . . . . . . . . . . . . . . . . 3

2.1 Fast I2C Block Level Diagram . . . . . . . . . . . . . . . . 3

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Data Flow and Control. . . . . . . . . . . . . . . . . . . . . . . 3

3.1.1 Fast I2C Module Arbitration and Control Logic . . 3

3.1.2 Serial Clock Generator . . . . . . . . . . . . . . . . . . . . . . 4

3.1.3 Bit Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.1.4 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.1.5 Status Decoder and Register . . . . . . . . . . . . . . . . .4

3.1.6 Input Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.7 Address Register and Comparator . . . . . . . . . . . . 5

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 vi

3.1.8 Data Shift Register . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.9 Related Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2.1 Master Transmitter Mode. . . . . . . . . . . . . . . . . . . . 6

3.2.2 Master Receiver Mode. . . . . . . . . . . . . . . . . . . . . . 7

3.2.3 Slave Receiver Mode . . . . . . . . . . . . . . . . . . . . . . . 7

3.2.4 Slave Transmitter Mode. . . . . . . . . . . . . . . . . . . . . 8

3.2.5 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . 8

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . . 8

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4.2.1 Fast I2C3 Module Registers . . . . . . . . . . . . . . . . . 9

4.2.2 Fast I2C4 Module Registers . . . . . . . . . . . . . . . . 20

Page 8

Philips Semiconductors

Chapter 22: DV Input Ports

PNX8550

Programmable Source Decoder with Integrated Peripherals

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. DV Input to VIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Chapter 23: DVI Output Ports

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Chapter 24: Audio Input Ports

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 Audio Input Block Level Diagram . . . . . . . . . . . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.1 Chip Level External Interface . . . . . . . . . . . . . . . . . 3

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.1.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.1.2 Reset-Related Issues . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.3 Register Programming Guidelines . . . . . . . . . . . . 6

3.2 Serial Data Framing . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.3 Memory Data Formats. . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 25: Audio Output

3. TS Mode of DV1, DV2 and DV3. . . . . . . . . . . . 1

3.1 Transport Stream Input Signal Descriptions . . . 3

3.2 Digital Video/TS Interface Timing Diagrams . . . 4

3.3.1 Endian Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.4 Memory Buffers and Capture . . . . . . . . . . . . . . . 10

3.5 Data Bus Latency and HBE . . . . . . . . . . . . . . . . 10

3.6 Error Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.7 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.8 Timestamp Events . . . . . . . . . . . . . . . . . . . . . . . . 12

3.9 Diagnostic Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.9.1 Audio In Operation . . . . . . . . . . . . . . . . . . . . . . . . 13

3.10 Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.11 Raw Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . 14

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 14

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 Audio Output Block Level Diagram . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Memory Data Formats. . . . . . . . . . . . . . . . . . . . . . . 3

3.1.1 Endian Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

3.2 Audio Out Data DMA Operation . . . . . . . . . . . . . . 4

3.2.1 TRANS_ENABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.3 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.3.1 Interrupt Latency. . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.4 Timestamp Events . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.5 Serial Data Framing . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.5.1 Serial Frame Limitations . . . . . . . . . . . . . . . . . . . . . 7

3.5.2 WS Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.5.3 I2S Serial Framing Example . . . . . . . . . . . . . . . . . 8

3.6 Codec Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.7 Data Bus Latency and HBE . . . . . . . . . . . . . . . . . 9

3.8 Error Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.9 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . 11

3.9.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . 11

3.9.2 Reset-Related Issues . . . . . . . . . . . . . . . . . . . . . . 13

3.9.3 Power Management . . . . . . . . . . . . . . . . . . . . . . . 14

3.9.4 Register Programming Guidelines. . . . . . . . . . . 14

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . 15

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 15

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Chapter 26: SPDIF Input

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 SPDIF IN Block Level Diagram . . . . . . . . . . . . . . . 1

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2.1 Functional Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Data Flow and Control. . . . . . . . . . . . . . . . . . . . . . . 3

3.1.1 Received Serial Format. . . . . . . . . . . . . . . . . . . . . . 3

3.1.2 Memory Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.3 SPDIF IN Endianness . . . . . . . . . . . . . . . . . . . . . . . 4

3.1.4 Bandwidth and Latency Requirements. . . . . . . . . 5

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 vii

3.2 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2.1 SPDIF IN Clock Domains . . . . . . . . . . . . . . . . . . . 6

3.2.2 SPDIF Receiver Sample Rate Tolerance and

IEC60958 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2.3 SPDIF Receiver Jitter Tolerance . . . . . . . . . . . . . 6

3.2.4 SPDIF IN and the Oversampling Clock. . . . . . . . 7

3.3 Register Programming Guidelines. . . . . . . . . . . . 7

3.3.1 SPDIF IN Register Set . . . . . . . . . . . . . . . . . . . . . . 7

3.3.2 SPDI_STATUS Register Functions . . . . . . . . . . . 8

3.3.3 LOCK and UNLOCK State Behavior . . . . . . . . . . 8

3.3.4 UNLOCK Error Behavior and DMA . . . . . . . . . . . 9

3.3.5 SPDI_CTL and Functions . . . . . . . . . . . . . . . . . . 10

Page 9

Philips Semiconductors

PNX8550

Programmable Source Decoder with Integrated Peripherals

3.3.6 SPDI_CBITSx and Channel Status Bits . . . . . . . 10

3.3.7 SPDI_UBITSx and User Bits . . . . . . . . . . . . . . . . 12

3.3.8 SPDI_BASEx and SPDI_SIZE Registers and

Memory Buffers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3.9 SPDI_SMPMASK and Sample Size Masking . . 12

3.3.10 SPDI_BPTR and the Start of an IEC60958

Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Chapter 27: SPDIF Output

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 SPDIF Out Block Level Diagram . . . . . . . . . . . . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 2

3.1 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.2 Register Programming Guidelines . . . . . . . . . . . . 3

3.2 Data Formatting . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2.1 IEC-60958 Serial Format . . . . . . . . . . . . . . . . . . . .5

Chapter 28: MIPS RISC Core Processor

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 PNX8550 User ManualBlock Level Diagram. . . . 1

2.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3. Instruction Execution Units . . . . . . . . . . . . . . . 2

3.1 Computational Registers. . . . . . . . . . . . . . . . . . . . . 3

3.2 Coprocessor 0 (CP0) Registers . . . . . . . . . . . . . . . 4

4. Instruction Set Overview . . . . . . . . . . . . . . . . . . 5

4.1 MIPS32 Instruction Set . . . . . . . . . . . . . . . . . . . . . . 5

5. Pipeline Execution. . . . . . . . . . . . . . . . . . . . . . . . 11

5.1 Eight-Stage Pipeline . . . . . . . . . . . . . . . . . . . . . . . 11

5.2 Efficient Handling of Pipeline Stalls. . . . . . . . . . . 12

5.2.1 Interlocking for Data Dependency . . . . . . . . . . . .12

5.2.2 Branch-Likely Instructions. . . . . . . . . . . . . . . . . . . 13

3.3.11 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.3.12 Event Timestamping. . . . . . . . . . . . . . . . . . . . . . . 14

4. Application Notes. . . . . . . . . . . . . . . . . . . . . . . . 14

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 15

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 15

5.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.2.2 Transparent Mode. . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.3 Errors and Interrupts. . . . . . . . . . . . . . . . . . . . . . . . 7

3.3.1 DMA Error Conditions . . . . . . . . . . . . . . . . . . . . . . 7

3.3.2 HBE and Databus Latency . . . . . . . . . . . . . . . . . . 8

3.3.3 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.3.4 Timestamp Events . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.4 Endianness. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . . 9

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . 9

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

6. MIPS16 Supports . . . . . . . . . . . . . . . . . . . . . . . . 13

6.1 MIPS16 Instruction Set . . . . . . . . . . . . . . . . . . . . 13

6.1.1 Extend Instruction . . . . . . . . . . . . . . . . . . . . . . . . . 14

6.1.2 PC-Relative Addressing. . . . . . . . . . . . . . . . . . . . 14

6.1.3 SP-Relative Addressing. . . . . . . . . . . . . . . . . . . . 14

6.1.4 Load/Store Offset Shifts. . . . . . . . . . . . . . . . . . . . 14

6.2 Switching Between MIPS16 and 32-Bit Modes 14

6.3 MIPS16 Registers. . . . . . . . . . . . . . . . . . . . . . . . . 15

7. MAD Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

8. Instruction and Data Caches. . . . . . . . . . . . . 15

9. Memory Architecture . . . . . . . . . . . . . . . . . . . . 16

9.1 Memory Protection . . . . . . . . . . . . . . . . . . . . . . . . 16

9.2 Endianness. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

10. Debug Support. . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Chapter 29: TM3260 CPU Core Processor

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 Programmable source decoder with integrated

peripherals CPU Core Block Level Diagram 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 2

3.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3.1.1 DRAM Aperture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.2 MMIO Aperture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.3 Aperture1 (DCS Bus Aperture) . . . . . . . . . . . . . . .5

3.2 Special Event Handling . . . . . . . . . . . . . . . . . . . . . .5

3.2.1 Reset and Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2.2 EXC (Exceptions) . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2.3 INT and NMI (Maskable and Non-Maskable

Interrupts). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 viii

3.3 Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.4 Debug Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.5 System Provisions . . . . . . . . . . . . . . . . . . . . . . . . 10

3.5.1 TM32_CTL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.5.2 TM32_MODID . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.5.3 Endian Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.6 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . 10

3.6.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . 10

3.6.2 Reset-Related Issues . . . . . . . . . . . . . . . . . . . . . . 10

3.6.3 Power Management . . . . . . . . . . . . . . . . . . . . . . . 11

4. Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.1 Global 1 and 2 Registers . . . . . . . . . . . . . . . . . . . 12

4.2 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 13

4.3 TM3260 MMIO Register Descriptions . . . . . . . . 17

Page 10

Philips Semiconductors

Chapter 30: Video Input Processor (VIP)

PNX8550

Programmable Source Decoder with Integrated Peripherals

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 VIP Block Level Diagram . . . . . . . . . . . . . . . . . . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2.1 Chip I/O and Connections. . . . . . . . . . . . . . . . . . . . 4

2.2.2 Data Routing and Video Modes . . . . . . . . . . . . . . . 5

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 6

3.1 VIP Basic Operation. . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1.1 Input Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1.2 Input Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 31: MBS

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 MBS Block Level Diagram . . . . . . . . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Data Flow and Control. . . . . . . . . . . . . . . . . . . . . . . 3

3.1.1 Horizontal Processing Pipeline . . . . . . . . . . . . . . .3

3.1.2 Vertical Processing Pipeline . . . . . . . . . . . . . . . . . 4

3.2 Data Processing in MBS . . . . . . . . . . . . . . . . . . . . . 5

3.3 MBS Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.3.1 Task Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.3.2 Video Source Controls. . . . . . . . . . . . . . . . . . . . . . . 7

3.1.3 Video Data Path . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1.4 Horizontal Video Filters (Sampling, Scaling, Color

Space Conversion) . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1.5 Video Data Write to Memory. . . . . . . . . . . . . . . . 17

3.1.6 Auxiliary Data Path . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1.7 Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . 24

3.2 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.1 Reset-Related Issues . . . . . . . . . . . . . . . . . . . . . 24

4. Register Definitions. . . . . . . . . . . . . . . . . . . . . . 25

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 25

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.3.3 Horizontal Video Filters . . . . . . . . . . . . . . . . . . . . . 9

3.3.4 Vertical Video Filters. . . . . . . . . . . . . . . . . . . . . . . 10

3.3.5 De-Interlacing in MBS . . . . . . . . . . . . . . . . . . . . . 10

3.3.6 Color-Key Processing. . . . . . . . . . . . . . . . . . . . . . 10

3.3.7 Alpha Processing . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.3.8 Video Data Output . . . . . . . . . . . . . . . . . . . . . . . . 11

3.3.9 Address Generation . . . . . . . . . . . . . . . . . . . . . . . 12

3.3.10 Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . 12

3.3.11 Measurement Functions . . . . . . . . . . . . . . . . . . . 13

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . 14

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 14

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Chapter 32: MBS2 (streaming)

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Register Descriptions . . . . . . . . . . . . . . . . . . . . . 1

Chapter 33: QVCP (5L and 2L)

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2. Functional Description . . . . . . . . . . . . . . . . . . . . 3

2.1 QVCP Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.1.1 QVCP Top Level View. . . . . . . . . . . . . . . . . . . . . . . 3

2.1.2 QVCP Block Level Diagram . . . . . . . . . . . . . . . . . . 4

2.1.3 QVCP Data Flow Diagram . . . . . . . . . . . . . . . . . . . 5

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 7

3.1 Layer Resources and Functions . . . . . . . . . . . . . . 7

3.1.1 Memory Access Control (DMA CTRL) . . . . . . . . . 7

3.1.2 Pixel Formatter Unit (PFU) . . . . . . . . . . . . . . . . . . . 8

3.1.3 Chroma Key and Undither (CKEY/UDTH) Unit. . 8

3.1.4 Chroma Up-Sample Filter (CUPS) . . . . . . . . . . .11

3.1.5 Linear Interpolator (LINT) . . . . . . . . . . . . . . . . . . . 11

3.1.6 Video/Graphics Contrast Brightness Matrix

(VCBM). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1.7 Layer and Fetch Control . . . . . . . . . . . . . . . . . . . . 13

3.2 Pool Resources and Functions . . . . . . . . . . . . . . 13

3.2.1 CLUT (Color Look-Up Table) . . . . . . . . . . . . . . . . 13

2.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . 1

2.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.2.2 DCTI (Digital Chroma/Color Transient

Improvement). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.2.3 HSRU (Horizontal Sample Rate Upconverter). 14

3.2.4 HIST (Histogram Modification) Unit . . . . . . . . . . 14

3.2.5 LSHR (Luminance/Luma Sharpening) Unit . . . 14

3.2.6 CFTR (Color Features) Unit . . . . . . . . . . . . . . . . 15

3.2.7 PLAN (Semi Planar DMA) Unit. . . . . . . . . . . . . . 15

3.3 Screen Timing Generator . . . . . . . . . . . . . . . . . . 15

3.4 Mixer Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.4.1 Key Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.4.2 Alpha Blending. . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.5 Output Pipeline Structure. . . . . . . . . . . . . . . . . . . 20

3.5.1 Formatter (FRMT). . . . . . . . . . . . . . . . . . . . . . . . . 21

3.5.2 Chroma Down-Sampler (CDNS) . . . . . . . . . . . . 21

3.5.3 Contrast Brightness and Soft Clip (CBSC). . . . 21

3.5.4 Average Beam Current Limiter (ABCL) or Power

Meter (PM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.5.5 Noise-Shaping (GNSH and ONSH) . . . . . . . . . . 22

3.5.6 Interleaver and Muxes . . . . . . . . . . . . . . . . . . . . . 22

3.5.7 Layer Selection, Dual Stream Support . . . . . . . 22

3.6 Output Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . 23

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 ix

Page 11

Philips Semiconductors

PNX8550

Programmable Source Decoder with Integrated Peripherals

3.6.1 Output Interface Modes. . . . . . . . . . . . . . . . . . . . . 23

3.6.2 Out Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . 25

3.6.3 Auxiliary Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4. Programming and Resource

Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.1 MMIO and Task Based Programming . . . . . . . .26

4.2 Setup Order for the QVCP . . . . . . . . . . . . . . . . . . 28

4.2.1 Shadow Registers . . . . . . . . . . . . . . . . . . . . . . . . .29

4.2.2 Fast Access Registers. . . . . . . . . . . . . . . . . . . . . . 32

4.3 Programming the Layer and Pool Resources . .33

4.3.1 Resource Assignment and Selection . . . . . . . . . 33

4.3.2 Aperture Assignment . . . . . . . . . . . . . . . . . . . . . . .35

4.3.3 Data Flow Selection . . . . . . . . . . . . . . . . . . . . . . . . 36

4.3.4 Pool Resource Assignment Example . . . . . . . . . 37

4.4 Programming the STG. . . . . . . . . . . . . . . . . . . . . . 39

4.4.1 Changing Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.5 Programming QVCP for Different Output

Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Chapter 34: QTNR

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 QTNR Block Level Diagram . . . . . . . . . . . . . . . . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Pixel Fetch Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.1 Summary of Required Functionality . . . . . . . . . . . 3

3.1.2 Design Requirements . . . . . . . . . . . . . . . . . . . . . . .3

3.2 Temporal Noise Reduction . . . . . . . . . . . . . . . . . . .3

3.2.1 Summary of Required Functionality . . . . . . . . . . . 3

3.3 Pixel Store Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

3.3.1 Summary of Required Functionality . . . . . . . . . . . 4

3.3.2 Design Requirements . . . . . . . . . . . . . . . . . . . . . . .4

3.4 Measurement Interface Block. . . . . . . . . . . . . . . . . 4

3.4.1 Summary of Required Functionality . . . . . . . . . . . 4

3.4.2 Design Requirements . . . . . . . . . . . . . . . . . . . . . . .4

3.5 Noise Level Measurement . . . . . . . . . . . . . . . . . . . 4

3.5.1 Summary of Required Functionality . . . . . . . . . . . 4

3.5.2 Design Requirements . . . . . . . . . . . . . . . . . . . . . . .5

3.6 Black Bar Measurement . . . . . . . . . . . . . . . . . . . . . 5

3.6.1 Summary of Required Functionality . . . . . . . . . . . 5

3.6.2 Design Requirements . . . . . . . . . . . . . . . . . . . . . . .5

4.6 Special Features . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.6.1 Signature Analysis . . . . . . . . . . . . . . . . . . . . . . . . 41

4.7 Programming Help . . . . . . . . . . . . . . . . . . . . . . . . 42

4.7.1 LINT Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . 42

4.7.2 HSRU Parameters . . . . . . . . . . . . . . . . . . . . . . . . 42

4.7.3 LSHR Parameters. . . . . . . . . . . . . . . . . . . . . . . . . 43

4.7.4 DCTI Parameters . . . . . . . . . . . . . . . . . . . . . . . . . 44

4.7.5 CFTR Parameters. . . . . . . . . . . . . . . . . . . . . . . . . 44

4.8 Underflow Behavior . . . . . . . . . . . . . . . . . . . . . . . 44

4.8.1 Layer Underflow . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.8.2 Underflow Symptoms . . . . . . . . . . . . . . . . . . . . . . 45

4.8.3 Underflow Recovery . . . . . . . . . . . . . . . . . . . . . . . 45

4.8.4 Underflow Troubleshooting . . . . . . . . . . . . . . . . . 45

4.8.5 Underflow Handling . . . . . . . . . . . . . . . . . . . . . . . 45

4.9 Clock Calculations . . . . . . . . . . . . . . . . . . . . . . . . 46

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 47

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 47

5.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.7 Black Level Measurement. . . . . . . . . . . . . . . . . . . 5

3.7.1 Summary of Required Functionality. . . . . . . . . . . 5

3.7.2 Design Requirements. . . . . . . . . . . . . . . . . . . . . . . 5

3.8 Histogram Measurement . . . . . . . . . . . . . . . . . . . . 5

3.8.1 Summary of Required Functionality. . . . . . . . . . . 5

3.8.2 Design Requirements. . . . . . . . . . . . . . . . . . . . . . . 6

3.9 UV Bandwidth Detection . . . . . . . . . . . . . . . . . . . . 6

3.9.1 Summary of Required Functionality. . . . . . . . . . . 6

3.9.2 Design Requirements. . . . . . . . . . . . . . . . . . . . . . . 6

3.10 Measurement Only Mode . . . . . . . . . . . . . . . . . . . 6

3.10.1 Summary of Required Functionality. . . . . . . . . . . 6

3.10.2 Design Requirements. . . . . . . . . . . . . . . . . . . . . . . 6

3.11 PIO and Task FIFO. . . . . . . . . . . . . . . . . . . . . . . . . 6

3.11.1 Software-Controlled Task Stack. . . . . . . . . . . . . . 6

3.11.2 Summary of Required Functionality. . . . . . . . . . . 6

3.11.3 Design Requirements. . . . . . . . . . . . . . . . . . . . . . . 6

3.12 Video Measurement Unit (VMU) . . . . . . . . . . . . . 7

3.12.1 VMU Functional Description . . . . . . . . . . . . . . . . . 7

3.12.2 VMU Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . . 8

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Chapter 35: Video Encoder (DVI_DENC)

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 DENC Block Level Diagram . . . . . . . . . . . . . . . . . . 1

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Data Flow and Control. . . . . . . . . . . . . . . . . . . . . . . 3

3.1.1 Video Input Modes . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.1.2 Video DAC Control . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.1.3 Signature Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . 4

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 x

3.2 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2.1 PAL/NTSC/SECAM Encoder . . . . . . . . . . . . . . . . 5

3.2.2 Luminance and Chrominance Processing . . . . . 6

3.2.3 Sync Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2.4 Macrovision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2.5 VBI Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2.6 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . 9

3.2.7 Reset-Related Issues . . . . . . . . . . . . . . . . . . . . . . . 9

3.2.8 Interrupt Processing . . . . . . . . . . . . . . . . . . . . . . . . 9

3.2.9 Power Management . . . . . . . . . . . . . . . . . . . . . . . . 9

Page 12

Philips Semiconductors

PNX8550

Programmable Source Decoder with Integrated Peripherals

3.2.10 Register Programming Guidelines . . . . . . . . . . . . 9

3.3 Module-Specific Capabilities . . . . . . . . . . . . . . . . 12

4. Application Notes . . . . . . . . . . . . . . . . . . . . . . . .12

Chapter 36: Vertical Peaking (VPK)

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 Vertical Peaking Block Level Diagram . . . . . . . . . 2

2.2 Vertical Peaking IP Block . . . . . . . . . . . . . . . . . . . . 2

2.3 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 3

3.1 Vertical Peaking Core . . . . . . . . . . . . . . . . . . . . . . . 3

3.2 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.2.1 Clock Speed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.2.2 Y_Out According to Output Mode . . . . . . . . . . . . . 4

3.2.3 Soft Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.2.4 Interrupt Processing. . . . . . . . . . . . . . . . . . . . . . . . . 4

3.2.5 Interrupt Generation. . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2.6 Powerdown Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Chapter 37: 2D Drawing Engine

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 2

2.1 PNX8550 User Manual Block Level Diagram . . . 2

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2.2 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2.3 Color Expand. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.4 Rotator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.5 Source FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.6 Pattern FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.7 Destination FIFO. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.8 Write Datapath . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.9 Source State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.10 Destination State . . . . . . . . . . . . . . . . . . . . . . . . . . .3

2.2.11 Address Stepper . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2.12 Bit BLT Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2.13 Vector Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2.14 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 12

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 12

5.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.2.7 Progressive Output Mode . . . . . . . . . . . . . . . . . . . 6

3.3 Module-Specific Capabilities . . . . . . . . . . . . . . . . . 6

3.3.1 Special Output Modes . . . . . . . . . . . . . . . . . . . . . . 6

3.3.2 Video Input Interface Description . . . . . . . . . . . . . 8

3.3.3 Video Output Interface Description . . . . . . . . . . . 8

4. Application Notes. . . . . . . . . . . . . . . . . . . . . . . . 10

4.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.1.1 Buffering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.1.2 Endianness Conversion. . . . . . . . . . . . . . . . . . . . 10

4.2 Suggested Coefficient Values for Effective

Peaking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5. Register Descriptions. . . . . . . . . . . . . . . . . . . . 10

5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 10

5.2 Register Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2.15 Byte Masking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3. General Operations . . . . . . . . . . . . . . . . . . . . . . . 4

3.1 Data Flow and Control . . . . . . . . . . . . . . . . . . . . . . 4

3.1.1 Raster Operations . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.2 Alpha Blending. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.3 Source Data Location and Type . . . . . . . . . . . . . 6

3.1.4 Patterns. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1.5 Transparency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.1.6 Block Writes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2 Register Programming Guidelines. . . . . . . . . . . . 7

3.2.1 Alpha Blending. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2.2 Mono Expand. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.2.3 Mono BLT Register Setup . . . . . . . . . . . . . . . . . . 10

3.2.4 Solid Fill Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.2.5 Color BLT Setup . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.2.6 PatRam. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4. Register Descriptions. . . . . . . . . . . . . . . . . . . . 13

4.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . 14

4.2 Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Chapter 38: Transport Stream Network (TSIO)

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Functional Description . . . . . . . . . . . . . . . . . . . . 1

2.1 Transport Stream Network Top Level View . . . . . 2

2.2 TSIO Block Level Diagram . . . . . . . . . . . . . . . . . . . 3

2.3 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3. General Operations. . . . . . . . . . . . . . . . . . . . . . . . 4

3.1 TS Input Interface Modes . . . . . . . . . . . . . . . . . . . . 4

3.1.1 Serial Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

UM10110_1 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Rev. 02 — 21 July 2004 xi

3.1.2 TS OUT Interface . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1.3 TS Input Router . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2 Standard Features . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.2.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . 6