Page 1

PNX2000 User Manual

UM10105_1

Audio Video Input Processor

Rev. 1.0 — 28 November 2003

Page 2

Philips Semiconductors

PNX2000

Audio Video Input Processor

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -ii

Page 3

Philips Semiconductors

Table of Contents

Chapter 1: Functional Specification

PNX2000

Audio Video Input Processor

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2 PNX2000 Feature Summary . . . . . . . . . . . . . 1-1

1.2.1 Video Features . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2.1.1 1FH Video . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2.1.2 2FH Video . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2.1.3 VBI Data Capture . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2.1.4 ITU656 output interface . . . . . . . . . . . . . . . . . . . . 1-2

1.2.2 Audio Features . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2.2.1 Demodulator and decoder . . . . . . . . . . . . . . . . . 1-2

Chapter 2: Control Interface

2.1 PNX2000 Control Interface . . . . . . . . . . . . . . 2-1

2.2 I2C Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.2.1 I2C Bus Features . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.2.2 Allocated I2C Address . . . . . . . . . . . . . . . . . . . . . 2-2

2.2.3 I2C Register Access Protocol. . . . . . . . . . . . . . . 2-2

2.2.4 I2C Interface Block . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.3 BCU Module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.3.1 BCU Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.3.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.3.2.1 BCU Interrupt Status Register

(BCU_INT_STATUS). . . . . . . . . . . . . . . . . . . . . . 2-8

2.3.2.2 BCU Interrupt Enable Register

(BCU_INT_ENABLE)

. . . . . . . . . . . . . . . . . . . . . . 2-8

1.2.2.2 Audio Multi Channel Decoder . . . . . . . . . . . . . . . 1-3

1.2.2.3 Volume and tone control . . . . . . . . . . . . . . . . . . . 1-3

1.2.2.4 Reflection and delay . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2.2.5 Psychoacoustic spatial algorithms,

downmix and split . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2.2.6 Interfaces and switching . . . . . . . . . . . . . . . . . . . 1-4

1.3 Functional Description. . . . . . . . . . . . . . . . . . . 1-4

1.4 Overview of Functional Partitioning . . . . . 1-6

2.3.2.3 BCU Interrupt Status Set Command

(BCU_INT_SET) . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.3.2.4 BCU Interrupt Status Clear Command

(BCU_INT_CLEAR)

2.3.2.5 BCU Bus Fault Status Register

(BCU_FAULT_STATUS) . . . . . . . . . . . . . . . . . . 2-10

2.3.2.6 BCU Bus Fault Address Register

(BCU_FAULT_ADDR) . . . . . . . . . . . . . . . . . . . . 2-10

2.3.2.7 BCU Time-Out Register (BCU_TOUT) . . . . . . 2-11

2.3.2.8 BCU Memory Coherency Register

(BCU_SNOOP) . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

. . . . . . . . . . . . . . . . . . . . . . . 2-9

2.4 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Chapter 3: I2D

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2 Functional Capabilities of the Links. . . . . 3-2

3.3 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.4 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.4.1 Transmitter / Receiver Transmission Modes. . 3-6

3.4.2 Data Rate and Timing Output Signals . . . . . . . 3-8

3.5 Configuration Registers. . . . . . . . . . . . . . . . . 3-9

3.5.1 I2D Register Map . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.5.1.1 I2D_RX_CTRL . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.5.1.2 I2D_RX_STATUS. . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.5.1.3 I2D_REC_DEMUX_MODE. . . . . . . . . . . . . . . . 3-11

3.5.1.4 I2D _REC_SYNC_LOST. . . . . . . . . . . . . . . . . . 3-12

3.5.1.5 I2D _PRBS_STAT . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.5.1.6 I2D _PRBS_CTRL . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.5.1.7 I2D _INT_STATUS. . . . . . . . . . . . . . . . . . . . . . . 3-14

Chapter 4: Video Processing (Viddec)

4.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 Data input, Sample Rate Converter

and timing

4.2.1 Short Description . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.3 AGC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4.3.1 Short Description . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4.3.2 AGC Gain Stages . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

3.5.1.8 I2D _INT_ENABLE . . . . . . . . . . . . . . . . . . . . . . . 3-14

3.5.1.9 I2D _INT_CLEAR . . . . . . . . . . . . . . . . . . . . . . . . 3-15

3.5.1.10 I2D _INT_SET . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

3.5.1.11 I2D _MOD_ID . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

3.6 Interrupt Procedure. . . . . . . . . . . . . . . . . . . . 3-16

3.6.1 Interrupt Behaviour . . . . . . . . . . . . . . . . . . . . . . . 3-16

3.6.2 Software Action with Registers. . . . . . . . . . . . . 3-17

3.6.2.1 Start Up. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

3.6.2.2 Normal Operation . . . . . . . . . . . . . . . . . . . . . . . . 3-18

3.6.2.3 Soft_reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

3.6.2.4 Change of Source Selection . . . . . . . . . . . . . . . 3-18

3.6.2.5 Sync lost on a datalink (Out Of Sync) . . . . . . . 3-18

3.6.2.6 Missing data_valid pulses . . . . . . . . . . . . . . . . . 3-19

3.6.2.7 Test mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

4.3.3 AGC Control Circuit . . . . . . . . . . . . . . . . . . . . . . 4-11

4.3.3.1 AGC Control Circuit for CVBS / Yyc path. . . . 4-11

4.3.3.2 AGC Control Circuit for Yyuv / Cyc Path . . . . 4-14

4.3.3.3 AGC Control Circuit for the Sync Path . . . . . . 4-22

4.4 Digital Multi Standard Decoder

(DMSD)

4.4.1 Y processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-23

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -iii

Page 4

Philips Semiconductors

PNX2000

Audio Video Input Processor

4.4.2 Demodulator, Filtering (Combfilter)

and SECAM Decoder

4.4.2.1 Demodulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

4.4.2.2 Filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-29

4.4.2.3 SECAM decoder . . . . . . . . . . . . . . . . . . . . . . . . . 4-32

4.4.3 Color PLL and Delay Line . . . . . . . . . . . . . . . . . 4-33

4.4.3.1 Color PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33

4.4.4 Color System Manager . . . . . . . . . . . . . . . . . . . 4-38

4.4.5 Signal controls, Macrovision and Debug . . . . 4-46

4.4.5.1 Signal Controls . . . . . . . . . . . . . . . . . . . . . . . . . . 4-46

4.4.5.2 Macrovision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-47

4.4.5.3 Debug & Control . . . . . . . . . . . . . . . . . . . . . . . . . 4-49

4.4.6 Sync Processing . . . . . . . . . . . . . . . . . . . . . . . . . 4-50

4.4.6.1 Horizontal Sync Processing 1 Fh

and Measurement/Control

. . . . . . . . . . . . . . . . . . . . 4-27

. . . . . . . . . . . . . . . . 4-52

Chapter 5: Data Capture Unit

5.1 Summary of Functions . . . . . . . . . . . . . . . . . . 5-1

5.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.2.1 Block Description . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.3 Design Specification. . . . . . . . . . . . . . . . . . . . . 5-3

5.4 Data Packet Formats . . . . . . . . . . . . . . . . . . . . 5-3

5.4.1 Status Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.4.2 Euro WST, US WST and NABTS Data . . . . . . 5-4

5.4.3 WSS625 Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.4.4 WSS525 Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.4.5 VPS Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.4.6 Closed Caption . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5.4.7 Moji (Japanese Text) . . . . . . . . . . . . . . . . . . . . . . 5-6

5.4.8 VITC Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5.4.9 Open Data Types . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

4.4.6.2 Vertical Sync Processing 1 Fh . . . . . . . . . . . . . 4-58

4.4.6.3 Horizontal Sync Processing 2 Fh . . . . . . . . . . . 4-63

4.4.6.4 Vertical Sync Processing 2 Fh . . . . . . . . . . . . . 4-69

4.4.6.5 Fast Blanking / External 2 Fh Sync /

Clamp Info

4.4.6.6 YUV Switch + Formatter . . . . . . . . . . . . . . . . . . 4-78

4.4.7 Switching VIDDEC between 1Fh and 2Fh . . . 4-80

4.4.8 Use of interrupt bits. . . . . . . . . . . . . . . . . . . . . . . 4-81

4.4.9 Automatic selection of different

input signal formats. . . . . . . . . . . . . . . . . . . . . . . 4-82

4.4.9.1 CVBS or Y/C Input Selection . . . . . . . . . . . . . . 4-83

4.4.9.2 CVBS + RGB Insert via SCART. . . . . . . . . . . . 4-86

4.4.9.3 CVI Input Selection . . . . . . . . . . . . . . . . . . . . . . . 4-88

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-74

5.5 Packet Processing Capabilities. . . . . . . . . . 5-7

5.5.1 Magazine and Packet Number Decoding . . . . . 5-7

5.5.1.1 Input Data Format . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.5.1.2 Output Data Format . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.5.2 Page Header Decoding . . . . . . . . . . . . . . . . . . . . 5-8

5.5.3 WSS525 CRC Checking . . . . . . . . . . . . . . . . . . . 5-8

5.5.4 Packet Validity Checking. . . . . . . . . . . . . . . . . . . 5-8

5.6 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5.6.1 DCR1: Data Capture Register (Write) . . . . . . . 5-10

5.6.2 DCR2: Data Capture Register 2 (Write) . . . . . 5-11

5.6.3 LCR2..LCR24: Line Control

Registers (Write) . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

5.6.4 DCS: Data Capture Status (Read). . . . . . . . . . 5-13

5.6.5 Interrupt Registers (Read/Write) . . . . . . . . . . . 5-14

5.6.6 MODULE_ID (Read). . . . . . . . . . . . . . . . . . . . . . 5-14

Chapter 6: ITU656

6.1. ITU656 Formatter Overview . . . . . . . . . . . . . 6-1

6.2. ITU656 Formatter Data Interfaces . . . . . . . 6-2

6.3. Control Registers . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.3.1 ITU656 Formatter Registers . . . . . . . . . . . . . . . . 6-3

6.3.2 CONFIG Register . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.3.2.1 MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.3.2.2 Columbus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.3.2.3 VBI_CONTROL. . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.3.2.4 VBI_ONLY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.3.2.5 CVBS_COMPL . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.3.2.6 UV_COMPL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.3.2.7 DITHER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.3.2.8 DC_JUSTIFIED. . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.2.9 CLOCK_INVERT . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.2.10 CLOCK_STUTTER . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.3.2.11 PROGRESSIVE_MODE . . . . . . . . . . . . . . . . . . . 6-8

6.3.2.12 OUTPUT_TEST_MODE . . . . . . . . . . . . . . . . . . . 6-8

6.3.2.13 INPUT_TEST_MODE . . . . . . . . . . . . . . . . . . . . . 6-9

6.3.2.14 DVO_ENABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

6.3.3 Data Identification Register – VBI data. . . . . . . 6-9

6.3.4 Data Identification Register – HBI data . . . . . 6-10

6.3.5 CAPTURE Register . . . . . . . . . . . . . . . . . . . . . 6-10

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -iv

6.3.6 FIFO Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.3.7 VF CONTROL Register . . . . . . . . . . . . . . . . . . . 6-11

6.3.8 VF SYNC Register . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.3.9 FIELD 1 Register. . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.10 FIELD 2 Register. . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.11 VBI 1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.12 VBI 2 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.13 VBI 3 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.14 VBI 4 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.15 PROG HBI Register . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.16 YUV Offset Register . . . . . . . . . . . . . . . . . . . . . . 6-14

6.3.17 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.3.17.1 INT_STATUS Register . . . . . . . . . . . . . . . . . . . 6-14

6.3.17.2 INT_ENABLE Register . . . . . . . . . . . . . . . . . . . 6-15

6.3.17.3 INT_CLEAR Register . . . . . . . . . . . . . . . . . . . . 6-15

6.3.17.4 INT_SET Register . . . . . . . . . . . . . . . . . . . . . . . 6-15

6.3.18 MODULE_ID Register . . . . . . . . . . . . . . . . . . . . 6-15

6.3.19 Debug Control Register . . . . . . . . . . . . . . . . . . 6-15

6.4. Video Line Interface Signal Structure. . . 6-17

6.4.1 PNX2000 (Mode 0) in Columbus Mode . . . . . 6-17

6.4.2 PNX2000 (Mode 1) in Columbus Mode . . . . . 6-18

6.4.3 PNX2000 (Mode 0) in PNX8550 mode . . . . . . 6-18

Page 5

Philips Semiconductors

PNX2000

Audio Video Input Processor

6.4.4 PNX2000 (Mode 1) in PNX8550 mode. . . . . . 6-19

6.4.5 PNX2000 (Mode 2) in PNX8550 mode. . . . . . 6-19

Chapter 7: Audio Processing

7.1 General Description . . . . . . . . . . . . . . . . . . . . . 7-1

7.2 Supported Standards . . . . . . . . . . . . . . . . . . . . 7-2

7.2.1 Analogue 2-carrier Systems . . . . . . . . . . . . . . . . 7-3

7.2.2 2-carrier Systems with NICAM . . . . . . . . . . . . . . 7-3

7.2.3 Satellite Systems . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.2.4 BTSC/SAP, Japan (EIAJ) and FM Radio

Systems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.3.1 Demodulator and Decoder . . . . . . . . . . . . . . . . . 7-4

7.3.2 Audio Multi Channel Decoder. . . . . . . . . . . . . . . 7-5

7.3.3 Volume and Tone Control . . . . . . . . . . . . . . . . . . 7-5

7.3.4 Reflection and Delay . . . . . . . . . . . . . . . . . . . . . . 7-6

7.3.5 Psychoacoustic Spatial Algorithms,

Downmix and Split . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.3.6 Interfaces and Switching . . . . . . . . . . . . . . . . . . . 7-6

7.4 Functional Overview of the

Sound Core

7.5 Sound Core Control Interface . . . . . . . . . . . 7-8

7.6 I2S . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.7 Digital-Analogue Converters . . . . . . . . . . . 7-11

7.8 Demdec DSP. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.8.1 DDEP in Brief . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.8.2 What DDEP Does NOT Do. . . . . . . . . . . . . . . . 7-13

7.8.3 Design Considerations . . . . . . . . . . . . . . . . . . . 7-14

7.8.4 DDEP Basics and Usage . . . . . . . . . . . . . . . . . 7-15

7.8.5 DEMDEC Hardware Blocks and the

Sample Rate Problem . . . . . . . . . . . . . . . . . . . . 7-15

7.8.6 Signal Processing in DSP Software . . . . . . . . 7-16

7.8.7 SRC constraints . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

7.8.8 The DDEP Control Register . . . . . . . . . . . . . . . 7-23

7.8.8.1 Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . 7-23

7.8.8.2 Starting and Restarting . . . . . . . . . . . . . . . . . . . 7-24

7.8.8.3 DDEP Control Variables . . . . . . . . . . . . . . . . . . 7-24

7.8.8.4 Dependencies Between Variables in

the DDEPR

7.8.8.5 Automute Function . . . . . . . . . . . . . . . . . . . . . . . 7-27

7.8.8.6 NICAM Configuration . . . . . . . . . . . . . . . . . . . . . 7-28

7.8.8.7 Amplitude and Noise Threshold Registers. . . 7-30

7.8.8.8 SAP Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . 7-32

7.8.8.9 EIAJ Subcarrier Detection. . . . . . . . . . . . . . . . . 7-32

7.8.9 Other DEMDEC Control Options . . . . . . . . . . . 7-33

7.8.9.1 ADC Channel Control . . . . . . . . . . . . . . . . . . . . 7-36

7.8.10 Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . 7-37

7.8.10.1 DEMDEC Status Register. . . . . . . . . . . . . . . . . 7-37

7.8.10.2 NICAM Status Registers . . . . . . . . . . . . . . . . . . 7-40

7.8.11 Noise Detection. . . . . . . . . . . . . . . . . . . . . . . . . . 7-41

7.8.12 Muting all DEMDEC Outputs . . . . . . . . . . . . . . 7-41

7.8.13 Using DDEP in a Set Design . . . . . . . . . . . . . . 7-42

7.8.13.1 Application Related Constant Settings . . . . . . 7-42

7.8.13.2 Prerequisites and User Interface . . . . . . . . . . . 7-42

7.8.13.3 Auto-tune Process . . . . . . . . . . . . . . . . . . . . . . . 7-44

7.8.13.4 Channel Switch Procedure . . . . . . . . . . . . . . . . 7-44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-27

6.4.6 PNX2000 (Mode 3) in PNX8550 mode . . . . . . 6-19

7.8.14 Details of Operation . . . . . . . . . . . . . . . . . . . . . . 7-45

7.8.14.1 Search Procedures (ASD Mode) . . . . . . . . . . . 7-45

7.8.14.2 Using the SSS Mode . . . . . . . . . . . . . . . . . . . . . 7-52

7.8.14.3 Automatic Signal Switching and Routing . . . . 7-54

7.9 AUDIO-DSP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-59

7.9.1 Functional Overview . . . . . . . . . . . . . . . . . . . . . . 7-59

7.9.2 Loudspeaker Channel Sound Modes . . . . . . . 7-62

7.9.3 Comments about Function Control . . . . . . . . . 7-63

7.9.3.1 Automatic Volume Levelling (AVL) . . . . . . . . . 7-63

7.9.3.2 Virtual Dolby® Surround (VDS). . . . . . . . . . . . . 7-63

7.9.3.3 Virtual Dolby® Digital (VDD) . . . . . . . . . . . . . . . 7-64

7.9.3.4 Noise Sequencer for DPLII . . . . . . . . . . . . . . . . 7-65

7.9.3.5 Dolby® Pro Logic II® Function (DPLII) . . . . . . 7-65

7.9.3.6 Bass / Treble . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-67

7.9.3.7 Loudness . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-69

7.9.3.8 Incredible Stereo (IStereo) . . . . . . . . . . . . . . . . 7-70

7.9.3.9 Incredible Mono (IMono) . . . . . . . . . . . . . . . . . . 7-72

7.9.3.10 Dynamic Ultra Bass (DUB) . . . . . . . . . . . . . . . . 7-73

7.9.3.11 Dynamic Bass Enhancement (DBE) . . . . . . . . 7-75

7.9.3.12 BBE

7.9.3.13 Bass Management . . . . . . . . . . . . . . . . . . . . . . . 7-77

7.9.3.14 Acoustical Compensation . . . . . . . . . . . . . . . . . 7-82

7.9.3.15 Equalizers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-83

7.9.3.16 Volume and Trim. . . . . . . . . . . . . . . . . . . . . . . . . 7-87

7.9.3.17 Beeper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-87

7.9.3.18 Mono Signal for Cancellation in the

7.9.3.19 Audio Monitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-87

7.9.3.20 Digital Output Crossbar . . . . . . . . . . . . . . . . . . . 7-87

7.9.3.21 Clip Management . . . . . . . . . . . . . . . . . . . . . . . . 7-88

7.9.3.22 Power On / Reset Specification . . . . . . . . . . . . 7-89

7.9.4 Audio Feature Specification . . . . . . . . . . . . . . . 7-89

7.9.4.1 Automatic Volume Levelling (AVL) . . . . . . . . . 7-90

7.9.4.2 Dolby® Pro Logic II® (DPLII) . . . . . . . . . . . . . . . 7-91

7.9.4.3 Virtual Dolby® Surround (VDS). . . . . . . . . . . . . 7-92

7.9.4.4 Virtual Dolby® Digital (VDD) . . . . . . . . . . . . . . . 7-93

7.9.4.5 Incredible Stereo (IStereo) . . . . . . . . . . . . . . . . 7-94

7.9.4.6 Incredible Mono (IMono) . . . . . . . . . . . . . . . . . . 7-95

7.9.4.7 Dynamic Ultra Bass (DUB) . . . . . . . . . . . . . . . . 7-96

7.9.4.8 Dynamic Bass Enhancement (DBE) . . . . . . . . 7-97

7.9.4.9 Loudness . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-98

7.9.4.10 BBE

7.9.4.11 Bass and Treble . . . . . . . . . . . . . . . . . . . . . . . . 7-100

7.9.4.12 Bass Management . . . . . . . . . . . . . . . . . . . . . . 7-101

7.9.4.13 Delay Line Unit . . . . . . . . . . . . . . . . . . . . . . . . . 7-102

7.9.4.14 Pseudo Hall / Matrix . . . . . . . . . . . . . . . . . . . . . 7-103

7.9.4.15 Master Volume & Trim . . . . . . . . . . . . . . . . . . . 7-104

7.9.4.16 Volume and Balance for Auxiliary

7.9.4.17 Level Adjust . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-106

7.9.4.18 Main Equalizer . . . . . . . . . . . . . . . . . . . . . . . . . . 7-107

7.9.4.19 Central Equalizer. . . . . . . . . . . . . . . . . . . . . . . . 7-108

7.9.4.20 Soft Mute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-109

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-76

®

Voice Control IC . . . . . . . . . . . . . . . . . . . . . . . . . 7-87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-99

®

Channels

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-105

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -v

Page 6

Philips Semiconductors

PNX2000

Audio Video Input Processor

7.9.4.21 Digital Input Crossbar . . . . . . . . . . . . . . . . . . . 7-110

7.9.4.22 Digital Output Crossbar . . . . . . . . . . . . . . . . . . 7-111

7.9.4.23 Audio Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . 7-112

Chapter 8: CGU

8.1 Clock Generation Unit (CGU) . . . . . . . . . . . . 8-1

8.2 PNX2000 Clock Requirements. . . . . . . . . . . 8-1

8.3 Crystal Oscillator Specification . . . . . . . . . 8-3

8.4 Phase Locked Loops . . . . . . . . . . . . . . . . . . . . 8-4

8.4.1 Power Saving Mode . . . . . . . . . . . . . . . . . . . . . . . 8-6

8.5 ITU Output Clock Generation. . . . . . . . . . . . 8-7

8.6 I2S Word Select (WS) Clock

Generation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.7 Clock Selection for 1fh and 2fh

Video Modes

. . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

Chapter 9: Standards, Modes and Settings

9.1 Video Standards . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.2 Data Capture Standards . . . . . . . . . . . . . . . . . 9-2

9.3 Audio Standards. . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.4 Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.5 ITU656 Formatter Settings. . . . . . . . . . . . . . . 9-5

9.6 Viddec Settings. . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

7.9.4.24 Beeper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-113

7.9.4.25 Noise Generator . . . . . . . . . . . . . . . . . . . . . . . . 7-114

8.8 Clock Configuration and Status

Registers

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

8.9 Power-on and Reset . . . . . . . . . . . . . . . . . . . . 8-14

8.9.1 Reset Selection . . . . . . . . . . . . . . . . . . . . . . . . . . 8-14

8.9.2 Reset Operation and Power Management . . . 8-15

8.9.2.1 Power on/External Hard Reset . . . . . . . . . . . . 8-15

8.9.2.2 Soft Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-15

8.10 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-16

8.10.1 Top-Level Interrupt Status and

Control Registers . . . . . . . . . . . . . . . . . . . . . . . . 8-16

8.11 Miscellaneous Registers. . . . . . . . . . . . . . . . 8-17

9.7 DCU Register Settings . . . . . . . . . . . . . . . . . . . 9-8

9.8 I2D Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

9.9 GTU Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

9.10 BCU Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-10

9.11 MPIF Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-10

Chapter 10: Device Initialization

10.1 Power-up Sequence (after Power-on

Reset)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

Chapter 11: Application Example

11.1 Application Example

(Single PNX2000)

. . . . . . . . . . . . . . . . . . . . . . . 11-1

Chapter 12: PCB Layout Guidelines

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.2 Power Supplies and Grounding . . . . . . . 12-1

12.2.1 PNX2000 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.2.2 PNX3000 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-2

Chapter 13: Support Tools

13.1 Universal Register Debugger. . . . . . . . . . . 13-1

List of Figures

Chapter 1: Functional Specification

10.2 Full-power to Standby Sequence . . . . . . . 10-1

10.3 Standby to Full-power Sequence . . . . . . . 10-2

12.3 Signal Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

12.3.1 Data-Link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

12.3.2 SAW Filters and IF Leads . . . . . . . . . . . . . . . . . 12-5

12.3.3 DACs Reference Voltages. . . . . . . . . . . . . . . . . 12-6

Figure 1: PNX2000 Block Diagram . . . . . . . . . . . . . . . 1-5

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -vi

Page 7

Philips Semiconductors

Chapter 2: Control Interface

PNX2000

Audio Video Input Processor

Figure 1: Control Interface. . . . . . . . . . . . . . . . . . . . . . . 2-1

Figure 2: Single Write. . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Figure 3: Single Read. . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Chapter 3: I2D

Figure 1: Overview - I2D Transmitter/Receiver . . . . . 3-2

Figure 2: Overview - Datalink Modes, Transmitter

Side PNX3000 . . . . . . . . . . . . . . . . . . . . . . . . 3-3

Figure 3: Simplified Transmitter Side PNX3000 . . . . 3-4

Figure 4: Simplified Receiver Side PNX2000. . . . . . . 3-6

Chapter 4: Video Processing (Viddec)

Figure 1: Block Diagram VIDeo DECoder . . . . . . . . . 4-2

Figure 2: Input and Sample Rate Conversion . . . . . . 4-3

Figure 3: Selection Input Data Streams for

VIDDEC in I2D . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Figure 4: AGC Block Diagram. . . . . . . . . . . . . . . . . . . . 4-5

Figure 5: AGC Gain Stages. . . . . . . . . . . . . . . . . . . . . . 4-6

Figure 6: Input Format vs. Output Format of AGC . . 4-7

Figure 7: AGC Universal Programmable

Gain Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Figure 8: AGC Control Circuit CVBS/Yyc and

Yyuv/Cyc . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Figure 9: Levels Before and After the AGC in

the Yyuv Path . . . . . . . . . . . . . . . . . . . . . . . . 4-16

Figure 10: Levels Before and After the AGC in

the Sync Path

Figure 11: AGC Control Circuit Sync . . . . . . . . . . . . . . 4-21

Figure 12: Levels Before and After Sync AGC. . . . . . 4-23

Figure 13: Block Diagram Digital Multi Standard

Decoder (DMSD)

Figure 14: Y Processing. . . . . . . . . . . . . . . . . . . . . . . . . 4-25

Figure 15: Demodulator and Filtering . . . . . . . . . . . . . 4-28

Figure 16: Demodulator . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

. . . . . . . . . . . . . . . . . . . . . . . . 4-18

. . . . . . . . . . . . . . . . . . . . . 4-24

Figure 4: Burst Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Figure 5: Burst Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Figure 5: Mode 0a Transmission. . . . . . . . . . . . . . . . . . 3-8

Figure 6: Mode 0b Transmission (Default) . . . . . . . . . 3-8

Figure 7: Mode 1 Transmission (2fh on Main

Channel, on sub is 1fh) . . . . . . . . . . . . . . . . . 3-9

Figure 8: Read Write and Control Flow . . . . . . . . . . . . 3-9

Figure 17: Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-29

Figure 18: SECAM Detector. . . . . . . . . . . . . . . . . . . . . . 4-32

Figure 19: Color PLL and Delay Line . . . . . . . . . . . . . . 4-33

Figure 20: Color PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33

Figure 21: Delay Line . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-37

Figure 22: Color System Manager . . . . . . . . . . . . . . . . 4-38

Figure 23: Color Decoder Output Control . . . . . . . . . . 4-46

Figure 24: Macrovision Detection . . . . . . . . . . . . . . . . . 4-47

Figure 25: Debug & Control . . . . . . . . . . . . . . . . . . . . . . 4-49

Figure 26: Sync Processing . . . . . . . . . . . . . . . . . . . . . . 4-50

Figure 27: Horizontal Sync Processing 1 Fh. . . . . . . . 4-52

Figure 28: Vertical Sync Processing 1 Fh . . . . . . . . . . 4-58

Figure 29: Horizontal Sync Processing 2 Fh. . . . . . . . 4-63

Figure 30: Vertical Sync Processing 2Fh. . . . . . . . . . . 4-69

Figure 31: Fast blanking, External 2 Fh

Composite Sync Input and Clamp Info

Figure 32: YUV Switch and Formatter . . . . . . . . . . . . . 4-78

Figure 33: Block Diagram CVBS / YC Selection . . . . 4-83

Figure 34: Block diagram full SCART input

(CVBS + RGB + Fast Blanking)

Figure 35: Block diagram CVI input selection . . . . . . . 4-88

. . . 4-74

. . . . . . . . . 4-86

Chapter 5: Data Capture Unit

Figure 1: Block Diagram of the Data Capture Unit . . 5-2

Chapter 6: ITU656

Figure 1: Formatter Block Diagram . . . . . . . . . . . . . . . 6-1

Figure 2: Insertion of HBI Data in ITU

Data Stream . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

Figure 3: Shifting of Bits in Pure Text Mode. . . . . . . . 6-5

Figure 4: Generation of Bytes in Nibble Mode. . . . . . 6-6

Figure 5: Dithering of 9 Bit Video Data to 8 Bits . . . . 6-7

Figure 6: ITU Output Data Stream

(CONFIG(10) = 0) . . . . . . . . . . . . . . . . . . . . . 6-7

Figure 7: ITU Output Data Stream

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -vii

Figure 8: ITU Output Data Stream

Figure 9: Colour Bar Test Pattern . . . . . . . . . . . . . . . . . 6-8

Figure 10: Mono Bar Test Pattern. . . . . . . . . . . . . . . . . . 6-9

Figure 11: Insertion of VBI Data in ITU

Figure 12: Insertion of HBI Data in ITU

(CONFIG(10) = 1) . . . . . . . . . . . . . . . . . . . . . . 6-8

(CONFIG(11) = 1) . . . . . . . . . . . . . . . . . . . . . . 6-8

Data Stream. . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

Data Stream

. . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

Page 8

Philips Semiconductors

Chapter 7: Audio Processing

PNX2000

Audio Video Input Processor

Figure 1: Sound Functions . . . . . . . . . . . . . . . . . . . . . . 7-7

Figure 2: Philips I2S Format . . . . . . . . . . . . . . . . . . . . 7-10

Figure 3: Sony I2S Format . . . . . . . . . . . . . . . . . . . . . 7-10

Figure 4: Japanese Format . . . . . . . . . . . . . . . . . . . . . 7-11

Figure 5: Control Flow . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

Figure 6: DEMDEC structure . . . . . . . . . . . . . . . . . . . 7-16

Figure 7: Signal Processing Modules and

SRC in DEMDEC DSP (Simplified). . . . . . 7-18

Figure 8: Switching and Matrixing in

Post-processing Block. . . . . . . . . . . . . . . . . 7-19

Figure 9: Spectra of TV HF Signals . . . . . . . . . . . . . . 7-47

Figure 10: B/G Search Procedure . . . . . . . . . . . . . . . . 7-49

Figure 11: D/K search procedure . . . . . . . . . . . . . . . . . 7-50

Figure 12: Search Procedure for M Standards . . . . . 7-52

Figure 13: Audio Backend Operation of PNX2000 . . 7-61

Figure 14: Virtual Dolby® Surround Left and

Right Output Signal

. . . . . . . . . . . . . . . . . . . 7-64

Figure 15: Virtual Dolby® Digital Left and Right

Output Signal . . . . . . . . . . . . . . . . . . . . . . . . 7-65

Figure 16: Dolby® Pro Logic II® Function . . . . . . . . . . 7-67

Figure 17: Bass / Treble Function with Equal

Settings and Steps of 5dB . . . . . . . . . . . . . 7-68

Figure 18: Treble Function within Steps of 2dB.

The Bass Control is Set to Flat

. . . . . . . . . 7-68

Figure 19: Bass Function within Steps of 2dB.

The Treble Control is Set to Flat . . . . . . . . 7-69

Figure 20: Loudness Curves for a MASTVOL

Range of 0 - -30dB (Step Width 1dB)

. . . . 7-70

Figure 21: Block Diagram of the IStereo (RIS)

Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-71

Figure 22: Left/Right Output Signal of IStereo

Module (conditions 1 and 2) . . . . . . . . . . . . 7-71

Figure 23: Block Diagram of IMono Module . . . . . . . . 7-72

Figure 24: Block Diagram of the IMONO

Decorrelator Module

. . . . . . . . . . . . . . . . . . 7-72

Figure 25: Left and Right Output Signal of the

IMono Module

. . . . . . . . . . . . . . . . . . . . . . . . 7-73

Figure 26: Block Diagram of the DUB Function . . . . . 7-74

Figure 27: Download Procedure for DUB and

DBE Coefficients

. . . . . . . . . . . . . . . . . . . . . 7-74

Figure 28: DUB Spectrum Plot . . . . . . . . . . . . . . . . . . . 7-75

Figure 29: Block Diagram of the Dynamic Bass

Enhancement (DBE)

. . . . . . . . . . . . . . . . . . 7-76

Figure 30: DBE Response Curves for two

different Input Levels . . . . . . . . . . . . . . . . . . 7-76

Figure 31: Response Curve - Contour +9dB

@ 100Hz and Process +12dB @ 10kHz

. 7-77

Figure 32: Overview of the PNX2000 Bass

Redirection

. . . . . . . . . . . . . . . . . . . . . . . . . . 7-79

Figure 33: PNX2000 Bass Redirection in

Configuration 1

. . . . . . . . . . . . . . . . . . . . . . . 7-80

Figure 34: PNX2000 Bass Redirection in

Configuration 2 . . . . . . . . . . . . . . . . . . . . . . . 7-80

Figure 35: PNX2000 Bass Redirection in

Configuration 3 . . . . . . . . . . . . . . . . . . . . . . . 7-81

Figure 36: PNX2000 Bass Redirection in

Configuration 4 (car application)

. . . . . . . . 7-82

Figure 37: PNX2000 Bass Redirection

switched off . . . . . . . . . . . . . . . . . . . . . . . . . . 7-82

Figure 38: Block Diagram Acoustical

Compensation Filter . . . . . . . . . . . . . . . . . . . 7-83

Figure 39: Download Procedure - Equalizer

Coefficients after Power On Reset

. . . . . . 7-84

Figure 40: Graphic Equalizer: 100Hz and 8kHz

Band (2dB Steps) and Envelope for

Max./Min. Gain . . . . . . . . . . . . . . . . . . . . . . . 7-85

Figure 41: Graphic Equalizer: 300Hz Band

(2dB Steps)

. . . . . . . . . . . . . . . . . . . . . . . . . . 7-85

Figure 42: Graphic Equalizer: 1kHz Band

(2dB Steps) . . . . . . . . . . . . . . . . . . . . . . . . . . 7-86

Figure 43: Graphic Equalizer: 3kHz Band

(2dB Steps) . . . . . . . . . . . . . . . . . . . . . . . . . . 7-86

Figure 44: Clip Management . . . . . . . . . . . . . . . . . . . . . 7-89

Figure 45: AVL (Automatic Volume Levelling) . . . . . . 7-90

Figure 46: DPLII (Dolby® Pro Logic II®). . . . . . . . . . . . 7-91

Figure 47: VDS (Virtual Dolby® Surround) . . . . . . . . . 7-92

Figure 48: VDD (Virtual Dolby® Digital) . . . . . . . . . . . . 7-93

Figure 49: IStereo (Incredible Stereo) . . . . . . . . . . . . . 7-94

Figure 50: IMono (Incredible Mono) . . . . . . . . . . . . . . . 7-95

Figure 51: DUB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-96

Figure 52: DBE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-97

Figure 53: Loudness . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-98

Figure 54: BBE

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-99

®

Figure 55: Bass & Treble . . . . . . . . . . . . . . . . . . . . . . . 7-100

Figure 56: Bass Management . . . . . . . . . . . . . . . . . . . 7-101

Figure 57: Delay Line Unit . . . . . . . . . . . . . . . . . . . . . . 7-102

Figure 58: Pseudo Hall / Matrix . . . . . . . . . . . . . . . . . . 7-103

Figure 59: Master Volume & Trim . . . . . . . . . . . . . . . . 7-104

Figure 60: Volume and Balance for Auxiliary

Channels

. . . . . . . . . . . . . . . . . . . . . . . . . . . 7-105

Figure 61: Level Adjust . . . . . . . . . . . . . . . . . . . . . . . . . 7-106

Figure 62: Main Equalizer. . . . . . . . . . . . . . . . . . . . . . . 7-107

Figure 63: Center Equalizer . . . . . . . . . . . . . . . . . . . . . 7-108

Figure 64: Soft Mute . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-109

Figure 65: Digital Input Crossbar. . . . . . . . . . . . . . . . . 7-110

Figure 66: Digital Output Crossbar . . . . . . . . . . . . . . . 7-111

Figure 67: Audio Monitor . . . . . . . . . . . . . . . . . . . . . . . 7-112

Figure 68: Beeper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-113

Figure 69: Noise Generator . . . . . . . . . . . . . . . . . . . . . 7-114

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -viii

Page 9

Philips Semiconductors

Chapter 8: CGU

PNX2000

Audio Video Input Processor

Figure 1: Application Diagram: (a) Slave/Test Mode,

(b) Oscillation Mode. . . . . . . . . . . . . . . . . . . . 8-3

Figure 2: Simplified Schematic of PLL . . . . . . . . . . . . 8-4

Chapter 9: Standards, Modes and Settings

Chapter 10: Device Initialization

Chapter 11: Application Example

Figure 1: Typical TV Application Architecture . . . . . 11-2

Chapter 12: PCB Layout Guidelines

Figure 1: Example of PCB Structure . . . . . . . . . . . . . 12-4

Figure 2: Suggested Data Link Routing . . . . . . . . . . 12-5

Figure 3: Track Length . . . . . . . . . . . . . . . . . . . . . . . . . 12-5

Chapter 13: Support Tools

Figure 1: AMB - CE5109 . . . . . . . . . . . . . . . . . . . . . . . 13-2

Figure 3: Block Diagram - PNX2000 CGU . . . . . . . . . 8-6

Figure 4: Schematic of ITU Output Clock

Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

Figure 4: Ground Shields . . . . . . . . . . . . . . . . . . . . . . . 12-6

Figure 5: PNX2000 DAC Connections. . . . . . . . . . . . 12-7

List of Tables

Chapter 1: Functional Specification

Table 1: Major Functions . . . . . . . . . . . . . . . . . . . . . . . 1-6 Table 2: Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Chapter 2: Control Interface

Table 1: BCU Register Map . . . . . . . . . . . . . . . . . . . . . 2-7

Table 2: BCU_INT_STATUS register. . . . . . . . . . . . . 2-8

Table 3: BCU_INT_ENABLE register. . . . . . . . . . . . . 2-8

Table 4: BCU_INT_SET command. . . . . . . . . . . . . . . 2-9

Table 5: BCU_INT_CLEAR command. . . . . . . . . . . . 2-9

Chapter 3: I2D

Table 1: Content of Data Links . . . . . . . . . . . . . . . . . . 3-7

Table 2: Data Rate Output Signals. . . . . . . . . . . . . . . 3-9

Table 3: I2D Register Summary . . . . . . . . . . . . . . . . 3-10

Table 4: I2D_RX_CTRL . . . . . . . . . . . . . . . . . . . . . . . 3-10

Table 5: I2D_RX_STATUS . . . . . . . . . . . . . . . . . . . . 3-11

Table 6: I2D _REC_DEMUX_MODE . . . . . . . . . . . . 3-11

Table 7: Demultiplexer Output with Mask

Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Table 6: BCU_FAULT_STATUS Register . . . . . . . . 2-10

Table 7: BCU_FAULT_ADDR Register . . . . . . . . . . 2-10

Table 8: BCU_TOUT Register . . . . . . . . . . . . . . . . . . 2-11

Table 9: BCU_SNOOP Register . . . . . . . . . . . . . . . . 2-11

Table 10: Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Table 8: I2D_REC_SYNC_LOST . . . . . . . . . . . . . . . 3-12

Table 9: I2D_PRBS_STAT . . . . . . . . . . . . . . . . . . . . . 3-13

Table 10: I2D_PRBS_CTRL . . . . . . . . . . . . . . . . . . . . . 3-13

Table 11: I2D _INT_STATUS . . . . . . . . . . . . . . . . . . . . 3-14

Table 12: I2D _INT_ENABLE . . . . . . . . . . . . . . . . . . . . 3-14

Table 13: I2D_INT_CLEAR. . . . . . . . . . . . . . . . . . . . . . 3-15

Table 14: I2D _INT_SET . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Table 15: I2D _MOD_ID Block information . . . . . . . . 3-16

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -ix

Page 10

Philips Semiconductors

Chapter 4: Video Processing (Viddec)

PNX2000

Audio Video Input Processor

Table 1: Bit Description - AGC Gain Stages -

Address 0X7FF9xxx . . . . . . . . . . . . . . . . . . . 4-7

Table 2: Bit Description - AGC Gain Control -

Address 0X7FF9xxx . . . . . . . . . . . . . . . . . . 4-12

Table 3: Bit Description - AGC Control Circuit

for Yyuv / Cyc Path - Address 0X7FF9xxx

Table 4: AGC Yyuv / Cyc for YPrPb Signals. . . . . . 4-17

Table 5: AGC Yyuv / Cyc for RGB Signals with

Sync on CVBS . . . . . . . . . . . . . . . . . . . . . . . 4-19

Table 6: AGC Yyuv / Cyc for Cyc Signals . . . . . . . . 4-21

Table 7: Bit Description - AGC Control Circuit

for the Sync Path - Address 0X7FF9xxx . 4-22

Table 8: Bit Description - Y Processing -

Address 0X7FF9xxx

Table 9: Bit Description - Demodulator -

Address 0X7FF9xxx . . . . . . . . . . . . . . . . . . 4-28

Table 10: Bit Description - Filters - Address

0X7FF9xxx . . . . . . . . . . . . . . . . . . . . . . . . . . 4-30

Table 11: DMSD_COL_DEC Control/Status -

Address 0X7FF9xxx

Table 12: Range - dmsd_heuc . . . . . . . . . . . . . . . . . . 4-35

Table 13: Bit Description - Delay Line -

Address 0X7FF9xxx . . . . . . . . . . . . . . . . . . 4-38

Table 14: Bit Description, Color System Manager -

Control Bits - Address 0X7FF9xxx

Table 15: Auto Mode - Settings. . . . . . . . . . . . . . . . . . 4-42

Table 16: Full Search Loop . . . . . . . . . . . . . . . . . . . . . 4-43

Table 17: Short Search Loop. . . . . . . . . . . . . . . . . . . . 4-43

Table 18: Bit Descrition - Status Bits -

. . . . . . . . . . . . . . . . . . 4-26

. . . . . . . . . . . . . . . . . . 4-34

4-15

. . . . . . 4-40

Address 0X7FF9xxx

Table 19: Bit Description - Signal Control -

Address 0X7FF9xxx . . . . . . . . . . . . . . . . . . . 4-46

Table 20: Bit Description - Macrovision

Detection - Address 0X7FF9xxx . . . . . . . . 4-48

Table 21: Bit Description - Debug and Control -

Address 0X7FF9xxx

Table 22: Bit Description - Horizontal Sync -

Address 0X7FF9xxx . . . . . . . . . . . . . . . . . . . 4-53

Table 23: Status Bit Descrition - Vertical Sync -

Address 0X7 FF9xxx . . . . . . . . . . . . . . . . . . 4-59

Table 24: Control Bit Description - Vertical

Sync - Address 0X7FF9xxx

Table 25: Bit Description - Horiz. Sync -

Address 0X7FF9xxx . . . . . . . . . . . . . . . . . . . 4-64

Table 26: Bit Description - Measurement /

Control - Address 0X7FF9xxx . . . . . . . . . . 4-67

Table 27: Status Bit Description - Vert.Sync.

2Fh - Address OX7FF9xxx

Table 28: Control Bit Description - Vert.Sync.

2Fh - Address OX7FF9xxx . . . . . . . . . . . . . 4-71

Table 29: Setting of Bits . . . . . . . . . . . . . . . . . . . . . . . . 4-73

Table 30: Bit Description - Fast Blanking -

Address OX7FF9xxx . . . . . . . . . . . . . . . . . . 4-75

Table 31: Bit Description - YUV Switch -

Address 0X7FF9xxx . . . . . . . . . . . . . . . . . . . 4-79

Table 32: 1Fh/2Fh Switching - Address

OX7FF7xxx . . . . . . . . . . . . . . . . . . . . . . . . . . 4-80

Table 33: Interrupt Bits . . . . . . . . . . . . . . . . . . . . . . . . . 4-81

. . . . . . . . . . . . . . . . . . . 4-44

. . . . . . . . . . . . . . . . . . . 4-49

. . . . . . . . . . . . 4-60

. . . . . . . . . . . . . 4-70

Chapter 5: Data Capture Unit

Table 1: VBI Mode Text - Line Numbers . . . . . . . . . . 5-3

Table 2: Data Packet Structure . . . . . . . . . . . . . . . . . . 5-3

Table 3: Status Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Table 4: Status Bytes Bit Definitions . . . . . . . . . . . . . 5-4

Table 5: Assembly of WSS625 Data into

Data Packet

Table 6: WSS625 Biphase Decoding. . . . . . . . . . . . . 5-4

Table 7: WSS525 Data in Data Capture Memory . . 5-5

Table 8: Assembly of VPS Data into Data Packet . . 5-5

Table 9: VPS Biphase Decoding. . . . . . . . . . . . . . . . . 5-5

Table 10: VITC Data Packet Contents. . . . . . . . . . . . . 5-6

Table 11: Page Header Byte Sequence . . . . . . . . . . . 5-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Table 12: Register Address Map and

Reset Values . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Table 13: DCR1: Data Capture Register (Write). . . . 5-10

Table 14: Effect of DCR Register. . . . . . . . . . . . . . . . . 5-10

Table 15: DCR2: Data Capture Register 2 (Write) . . 5-11

Table 16: Effect of DCR2 Register . . . . . . . . . . . . . . . 5-11

Table 17: Structure of LCR Registers . . . . . . . . . . . . . 5-11

Table 18: Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Table 19: DCS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Table 20: DCS Register Bit Definition . . . . . . . . . . . . . 5-13

Table 21: Interrupt Register Bit Assignments . . . . . . 5-14

Table 22: Module-ID Register Contents . . . . . . . . . . . 5-14

Chapter 6: ITU656

Table 1: ITU656 Formatter Register Summary . . . . 6-3

Table 2: CONFIG Register . . . . . . . . . . . . . . . . . . . . . . 6-3

Table 3: Supported Video Standards . . . . . . . . . . . . . 6-4

Table 4: Data Identification Register – VBI data . . . 6-9

Table 5: Data Identification Register – HBI data . . 6-10

Table 6: CAPTURE Register . . . . . . . . . . . . . . . . . . . 6-10

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -x

Table 7: FIFO Register . . . . . . . . . . . . . . . . . . . . . . . . 6-11

Table 8: VF Control Register . . . . . . . . . . . . . . . . . . . 6-11

Table 9: VF Sync Register . . . . . . . . . . . . . . . . . . . . . 6-11

Table 10: Field 1 Register . . . . . . . . . . . . . . . . . . . . . . . 6-12

Table 11: Field 2 Register . . . . . . . . . . . . . . . . . . . . . . . 6-12

Table 12: VBI 1 Register . . . . . . . . . . . . . . . . . . . . . . . . 6-12

Page 11

Philips Semiconductors

PNX2000

Audio Video Input Processor

Table 13: VBI 2 Register. . . . . . . . . . . . . . . . . . . . . . . . 6-13

Table 14: VBI 3 Register. . . . . . . . . . . . . . . . . . . . . . . . 6-13

Table 15: VBI 4 Register. . . . . . . . . . . . . . . . . . . . . . . . 6-13

Table 16: PROG HBI Register . . . . . . . . . . . . . . . . . . . 6-13

Table 17: YUV Offset Register . . . . . . . . . . . . . . . . . . 6-14

Table 18: INT_STATUS Register . . . . . . . . . . . . . . . . 6-14

Table 19: INT_ENABLE Register . . . . . . . . . . . . . . . . 6-15

Table 20: INT_CLEAR Register . . . . . . . . . . . . . . . . . 6-15

Table 21: INT_SET Register . . . . . . . . . . . . . . . . . . . . 6-15

Chapter 7: Audio Processing

Table 1: Frequency Modulation . . . . . . . . . . . . . . . . . . 7-3

Table 2: Identification for A2 Systems . . . . . . . . . . . . 7-3

Table 3: NICAM Standards . . . . . . . . . . . . . . . . . . . . . 7-3

Table 4: FM Satellite Sound. . . . . . . . . . . . . . . . . . . . . 7-4

Table 5: Frequency Modulation . . . . . . . . . . . . . . . . . . 7-4

Table 6: Identification for BTSC/SAP, Japan

(EIAJ) and FM Radio Systems . . . . . . . . . . 7-4

Table 7: Output Signal Restriction Depending

on SRCPREF

Table 8: Active Output Signals Depending

on Standard and SRCPREF Selection. . . 7-21

Table 9: Active SRC Channels per Configuration . 7-22

Table 10: SRCPREF Selection Depending on

Desired Sources

Table 11: Contents of DDEP Control Register

(DDEPR)2 (DD22) . . . . . . . . . . . . . . . . . . . . 7-25

Table 12: Standard detection control bits in

ASD mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-26

Table 13: Static standard selection codes in

SSS mode

Table 14: NICAM Configuration Register

(NICAM_CFG_REG, DD21)

Table 15: Magnitude Detection Register

(MAGDET_THR_REG, DD17)

Table 16: Noise Automute Control Register, FMA2/

SAP (NMUTE_FMA2_SAP_REG, DD18

Table 17: SAP Detection by magnitude and

noise detection

Table 18: Control Variables for EIAJ Subcarrier

Detection

. . . . . . . . . . . . . . . . . . . . . . . . 7-20

. . . . . . . . . . . . . . . . . . . . . . 7-22

. . . . . . . . . . . . . . . . . . . . . . . . . . . 7-26

. . . . . . . . . . . . 7-29

. . . . . . . . . . 7-30

. 7-32

. . . . . . . . . . . . . . . . . . . . . . . 7-32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-33

Table 22: MODULE_ID Register . . . . . . . . . . . . . . . . . 6-15

Table 23: DEBUG Register . . . . . . . . . . . . . . . . . . . . . . 6-16

Table 24: DEBUG Signals. . . . . . . . . . . . . . . . . . . . . . . 6-16

Table 25: PNX2000 (Mode 0) in Columbus Mode . . 6-17

Table 26: PNX2000 (Mode 1) in Columbus Mode . . 6-18

Table 27: PNX2000 (Mode 0) in PNX8550 Mode . . . 6-18

Table 28: PNX2000 (Mode 1) in PNX8550 Mode . . . 6-19

Table 29: PNX2000 (Mode 2) in PNX8550 Mode . . . 6-19

Table 30: PNX2000 (Mode 3 - Default) in

PNX8550 Mode

. . . . . . . . . . . . . . . . . . . . . . . 6-19

Table 19: DDEP_OPTIONS1_REG Register . . . . . . 7-33

Table 20: SRC Configuration - up to sIx Channels. . 7-34

Table 21: DD_OPTIONS2_REG Register . . . . . . . . . 7-35

Table 22: ADC Channel Control Register

(DEM_ADC_SEL_REG, DD24) . . . . . . . . . 7-36

Table 23: DEMDEC Status Register

(INF_MAIN_STATUS_REG, DD01)

. . . . . 7-38

Table 24: Generalized Stereo / Dual Flags . . . . . . . . 7-39

Table 25: Deriving the Stereo / Dual Information

in Case of Forced Mono . . . . . . . . . . . . . . . 7-40

Table 26: NICAM Status Register

(INF_NICAM_STATUS_REG, DD02) . . . . 7-40

Table 27: Noise Detector Status Register

(INF_NOISELEVEL_REG, DD08

. . . . . . . . 7-41

Table 28: Noise Levels for Muting per Standard. . . . 7-42

Table 29: Areas and ASD Settings . . . . . . . . . . . . . . . 7-44

Table 30: Deciding for a Standard Group. . . . . . . . . . 7-49

Table 31: DEMDEC Output Signals (not

Considering SRC Restriction). . . . . . . . . . . 7-54

Table 32: Overmodulation Adaptation Status

Register (INF_OVMADAPT_REG,

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-56

DD28)

Table 33: Register Map Overview of DEMDEC

DSP (High Latency Registers)

. . . . . . . . . . 7-58

Table 34: Loudspeaker Channel Sound Modes . . . . 7-62

Table 35: Sound Modes . . . . . . . . . . . . . . . . . . . . . . . . 7-62

Table 36: DUB - Coefficient . . . . . . . . . . . . . . . . . . . . 7-115

Table 37: DBE - Coefficient . . . . . . . . . . . . . . . . . . . . 7-115

Table 38: DBE - Coefficients for Maximum Boost .7-116

Table 39: Acoustical Compensation – Coefficient .7-117

Chapter 8: CGU

Table 1: GTU Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

Table 2: Control Subsystem Clock . . . . . . . . . . . . . . . 8-1

Table 3: Video Subsystem Clock . . . . . . . . . . . . . . . . 8-2

Table 4: Sound Subsystem Clock. . . . . . . . . . . . . . . . 8-3

Table 5: Primary Clock Settings . . . . . . . . . . . . . . . . . 8-4

Table 6: Clocks Derived from Crystal. . . . . . . . . . . . . 8-4

Table 7: PLL Control Signals . . . . . . . . . . . . . . . . . . . . 8-5

Table 8: Summary of PLLs. . . . . . . . . . . . . . . . . . . . . . 8-5

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -xi

Table 9: WS Clock Generation Modes . . . . . . . . . . . . 8-7

Table 10: GP_WSSLAVEPLLCONTROL. . . . . . . . . . . 8-8

Table 13: GP_WSPLLCONTROL . . . . . . . . . . . . . . . . . 8-9

Table 11: GP_WSPLLMASTERSEL . . . . . . . . . . . . . . . 8-9

Table 12: GP_WSPLLSLAVESEL . . . . . . . . . . . . . . . . . 8-9

Table 15: GP_WS_FSCOUNTER . . . . . . . . . . . . . . . . 8-10

Table 16: GP_WS_SAMPLERATE . . . . . . . . . . . . . . . 8-10

Table 14: GP_WSPLLSTATUS . . . . . . . . . . . . . . . . . . 8-10

Page 12

Philips Semiconductors

PNX2000

Audio Video Input Processor

Table 17: Clock Selection . . . . . . . . . . . . . . . . . . . . . . . 8-11

Table 18: GP_CLKEN . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

Table 19: GP_CLKSEL . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

Table 20: GP_DISTRICONTROL . . . . . . . . . . . . . . . . 8-12

Table 21: GP_TURBOPLLSEL . . . . . . . . . . . . . . . . . . 8-12

Table 22: GP_TURBOPLLCONTROL . . . . . . . . . . . . 8-12

Table 23: GP_TURBOPLLSTATUS . . . . . . . . . . . . . . 8-13

Table 24: GP_SYSPLLSEL . . . . . . . . . . . . . . . . . . . . . 8-13

Table 25: GP_SYSPLLCONTROL . . . . . . . . . . . . . . . 8-13

Chapter 9: Standards, Modes and Settings

Table 1: PAL Standard . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

Table 2: SECAM Standards. . . . . . . . . . . . . . . . . . . . . 9-1

Table 3: NTSC Standards . . . . . . . . . . . . . . . . . . . . . . 9-1

Table 4: ATSC Standards . . . . . . . . . . . . . . . . . . . . . . 9-1

Table 5: NI Standards . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

Table 6: Component Video Standards . . . . . . . . . . . . 9-2

Table 7: Data Capture Standards . . . . . . . . . . . . . . . . 9-2

Table 8: Audio Standards . . . . . . . . . . . . . . . . . . . . . . . 9-3

Table 9: Display Modes . . . . . . . . . . . . . . . . . . . . . . . . 9-4

Table 10: ITU656 Formatter Settings . . . . . . . . . . . . . . 9-5

Table 11: Different Settings when Interfacing

to Columbus . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

Table 12: Different Settings when using External

Syncs in Display Mode 1152i/50Hz . . . . . . 9-5

Table 13: Viddec Settings. . . . . . . . . . . . . . . . . . . . . . . . 9-6

Table 18: Negative Syncs Settings. . . . . . . . . . . . . . . . 9-7

Table 14: Different Settings when Decoding

SECAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-7

Table 15: Different Settings when Decoding YC . . . . 9-7

Table 26: GP_SYSPLLSTATUS . . . . . . . . . . . . . . . . . 8-14

Table 27: Internal POR Mode (select=1,

reset_n=0)

Table 28: External POR (select=0) . . . . . . . . . . . . . . . 8-14

Table 29: POR Bypass Mode (select=reset_n) . . . . . 8-14

Table 30: Soft Reset Control Bits. . . . . . . . . . . . . . . . . 8-15

Table 31: GP_IRQ_STAT. . . . . . . . . . . . . . . . . . . . . . . 8-16

Table 32: GP_IRQ_ENAB . . . . . . . . . . . . . . . . . . . . . . . 8-17

Table 33: GP_IRQ_CLR . . . . . . . . . . . . . . . . . . . . . . . . 8-17

Table 34: GP_IRQ_SET . . . . . . . . . . . . . . . . . . . . . . . . 8-17

Table 16: Additional Settings when

Interfacing to Columbus. . . . . . . . . . . . . . . . . 9-7

Table 17: Additional/Different Settings using

External HV Syncs

Table 19: DCU Register Settings. . . . . . . . . . . . . . . . . . 9-8

Table 20: Different Settings when Interfacing

to Columbus. . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

Table 21: I2D Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

Table 22: I2D Settings (YC) . . . . . . . . . . . . . . . . . . . . . . 9-8

Table 23: Crystal Divider Settings . . . . . . . . . . . . . . . . . 9-9

Table 24: SYSPLL and TURBOPLL Divider

Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

Table 25: WSPLL Divider Settings - Auto

Master Mode

Table 26: WSPLL Divider Settings - Master Mode . . . 9-9

Table 27: Clock Settings for 1fh/2fh video modes . . 9-10

Table 28: Enables/Resets . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 29: BCU Settings . . . . . . . . . . . . . . . . . . . . . . . . . 9-10

Table 30: Recommended MPIF to AVIP Video

Settings

. . . . . . . . . . . . . . . . . . . . . . . . . . . 8-14

. . . . . . . . . . . . . . . . . . . . . 9-7

. . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-10

Chapter 10: Device Initialization

Chapter 11: Application Example

Chapter 12: PCB Layout Guidelines

Table 1: PNX2000 3V3 Power Supplies . . . . . . . . . 12-1

Table 2: PNX2000 1V8 Power Supplies . . . . . . . . . 12-1

Table 3: PNX2000 Ground References . . . . . . . . . . 12-2

Table 4: Non-connected Pins . . . . . . . . . . . . . . . . . . 12-2

Table 5: PNX3000 8V / 5V Supplies . . . . . . . . . . . . . 12-2

Table 6: PNX3000 5V Supplies . . . . . . . . . . . . . . . . . 12-2

Table 7: PNX3000 Ground References . . . . . . . . . . 12-2

Chapter 13: Support Tools

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 -xii

Page 13

Chapter 1: Functional Specification

PNX2000 User Manual

Rev. 1.0 — 28 November 2003

1.1 Introduction

The PNX2000 is a companion IC device for the Nexperia DVP SOC PNX8550, to be

used in combination with the PNX3000.

It is aimed at mid and high-end analogue and hybrid TV sets, focusing on input

decoding of a single stream of analogue audio and a single stream of analogue video

signals. In addition, the PNX2000 is used for decoding and the presentation of all

audio output streams in the system.

1.2 PNX2000 Feature Summary

1.2.1 Video Features

• Automatic Gain Control (AGC) to correct amplitude errors at input source.

• Synchronization identification (used for channel search).

• Sync processing for 1FH and 2FH video input source.

• Standard detection of PAL, NTSC or SECAM and various 1FH/2FH component

video input sources.

1.2.1.1 1FH Video

• Color decoding (ITU-601) for PAL, NTSC or SECAM input sources.

• 2D comb filter.

• Supports component video sources with sync on CVBS or green.

• Fastblank insertion of RGB signals onto CVBS input.

1.2.1.2 2FH Video

• Supports various progressive and interlaced component video sources.

• Synchronization of video sources with sync on Y or external H/V inputs.

1.2.1.3 VBI Data Capture

• Decodes 525 line standards – WST, WSS, VPS, CC, VITC.

Page 14

Philips Semiconductors

1.2.1.4 ITU656 output interface

1.2.2 Audio Features

1.2.2.1 Demodulator and decoder

PNX2000

Functional Specification

• Decodes 625 line standards – WST, WSS, CC, VITC.

• Video and VBI formatted into an ITU-style output data stream, compliant to ITU-

656/1364 (exception being the use of a data valid signal).

• Interfaces to PNX8550 IC.

• Supports CVBS/C mode to interface to external picture improvement devices.

• Demodulator and Decoder Easy Programming (DDEP)

• Auto standard detection (ASD)

• Static Standard Selection (SSS)

• DQPSK demodulation for different standards, simultaneously with 1-channel FM

demodulation

• NICAM decoding (B/G, I, D/K and L standard)

• Two-carrier multistandard FM demodulation (B/G, D/K and M standard)

• Decoding for three analogue multi-channel systems (A2, A2+ and A2*) and

satellite sound

• Adaptive de-emphasis for satellite FM

• Optional AM demodulation for system L, simultaneously with NICAM

• Identification A2 systems (B/G, D/K and M standard) with different identification

time constants

• FM pilot carrier present detector

• Monitor selection for FM/AM DC values and signals, with peak and quasi peak

detection option

• BTSC MPX decoder

• SAP decoder

• dbx noise reduction

• Japan (EIAJ) decoder

• FM radio decoder

• Soft-mute for DEMDEC outputs DEC, MONO and SAP

• FM overmodulation adaptation option to avoid clipping and distortion

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 1-2

Page 15

Philips Semiconductors

1.2.2.2 Audio Multi Channel Decoder

PNX2000

Functional Specification

• Sample rate conversion (SRC) for up to three demodulated terrestrial audio

signals. It is possible to process SCART signals together with demodulated

terrestrial signals.

• Dolby

®

Pro Logic® II Surround (DPL2) — Registered Trademark of Dolby®

Laboratories

• Six channel processing for Main Left and Main Right, Subwoofer, Center,

Surround Left and Surround Right

1.2.2.3 Volume and tone control

• Automatic Volume Level (AVL) control

• Smooth volume control

• Master volume control and Balance

• Soft-mute

• Loudness

• Bass, Treble

• Dynamic Bass Enhancement (DBE)

• Dynamic Ultra Bass (DUBII)

• Non processed subwoofer

• 5 band equalizer

• Acoustical compensation

• Programmable beeper

• Noise generator for loudspeaker level trimming

1.2.2.4 Reflection and delay

• Dolby

®

Pro Logic® Delay

• Pseudo hall/matrix function

1.2.2.5 Psychoacoustic spatial algorithms, downmix and split

• Incredible Mono

• Incredible Stereo

• Virtual Dolby

• Virtual Dolby

• Bass Redirection according to Dolby

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

®

Surround (VDS 522,523)

®

Digital (VDD 522,523)

®

specifications

Rev. 1.0 — 28 November 2003 1-3

Page 16

Philips Semiconductors

1.2.2.6 Interfaces and switching

PNX2000

Functional Specification

• Digital audio input interface (stereo I

• Digital audio output interface (stereo I

• Digital crossbar switch for all digital signal sources and destinations

• Output crossbar for exchange of channel processing functionality

• Voice recognition output interface (stereo I

• Audio monitor for level detection

• 8 audio DACs for six channel loudspeaker outputs and stereo headphones output

• 4 audio DACs for stereo SCART output and stereo LINE output.

• Serial data link interface for interfacing with the analogue multi-purpose interface

IC PNX3000.

1.3 Functional Description

The following figure shows a block diagram of the PNX2000 device.

2

S input interface)

2

S output interface)

2

S output interface)

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 1-4

Page 17

Philips Semiconductors

p

N

PNX2000

Functional Specification

DLINK1 DLINK2 DLINK3

Audio data SIF or L/R

I2C

Bus

INT

13.5/27

MHz

Xtal

6x I2S

Inputs

6x I2S

Output s

I2C

GTU

Clocks

Sound

SDACS

X4 X6 X2

I2D

PI-Bus

Video data CVBS, Y/C, YUV

54MHz clock 27/54 Msam

VIDDEC

DCU

ITU-656

ITU-656

1fh/2f h

10-bit dat a

les/sec

HSYNC

HSYNC/VSY

PNX3000

interf ace

(2 stereo/4

mono)

BCU

Figure 1: PNX2000 Block Diagram

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 1-5

Page 18

Philips Semiconductors

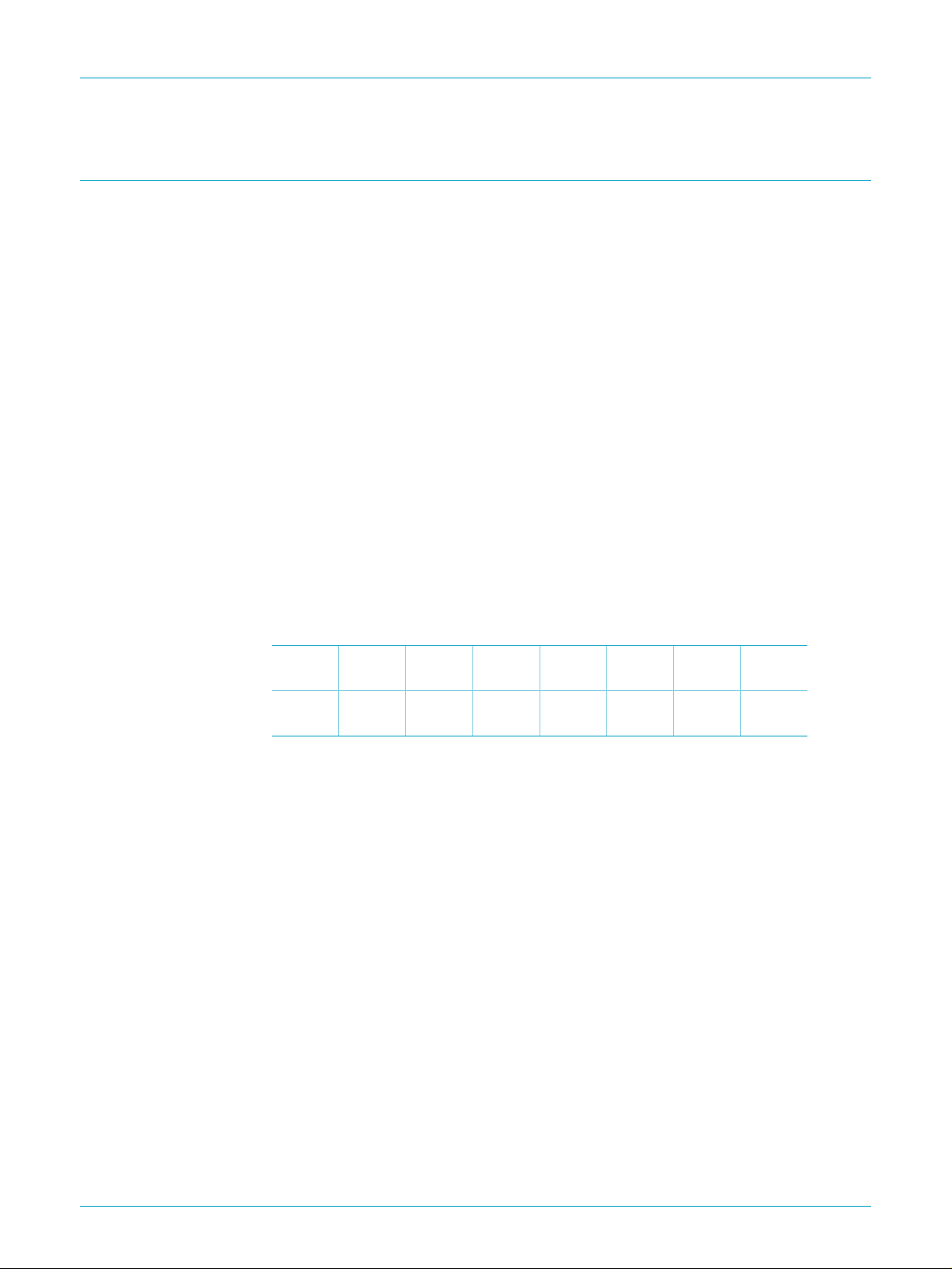

1.4 Overview of Functional Partitioning

The following table illustrates how the major functions are mapped to hardware

blocks.

Table 1: Major Functions

Function Block Description

High speed data-link I2D Receives data in 3 streams from PNX3000

Video Decoder Processor VIDDEC Decodes and processes CVBS, YUV or Y/C in YUV

2

Serial Interface I

Global Task Unit GTU Generates all the internal clocks, Reset and Power

TV Sound Decoder DEMDEC

Audio Processor AUDIO

Data Capture Unit DCU Acquires VBI data (Teletext, CC, VPS) and formats

Formatter Unit ITU-656 Formats YUV, VBI data and CVBS data in ITU-656

Bus Control Unit BCU Bus arbitration among all the internal blocks

C To access all the internal registers

DSP

DSP

PNX2000

Functional Specification

stream

management

Demodulation, decoding of terrestrial TV audio

standards

Processing analogue and digital audio sources

in a stream

Table 2: Interfaces

Interface Description

2

I

C The PNX2000 IC is controlled using an I2C bus. It performs like an I2C-bus to PI-

bus bridge, i.e. translates I

commands.

I2D Receives data in three streams from PNX3000.

2

I

S Serial digital audio interface (6 stereo inputs and 6 stereo outputs) for connection

to other devices that support the I

sound from a multi-channel digital audio decoder, provide additional ADCs and

DACs, or loop audio signals through an external processor or delay line.

ITU656 Mainly intended to transfer output data stream externally to the PNX8550 but the

output data stream could also be readable by other ITU 656 input devices that

implement data valid signalling

DACS Digital-analogue converters used to generate analogue outputs from Sound Core

2

C-slave received commands to PI-bus master

2

S standard. Can be used to receive decoded

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 1-6

Page 19

Chapter 2: Control Interface

r

V

A

PNX2000 User Manual

Rev. 1.0 — 28 November 2003

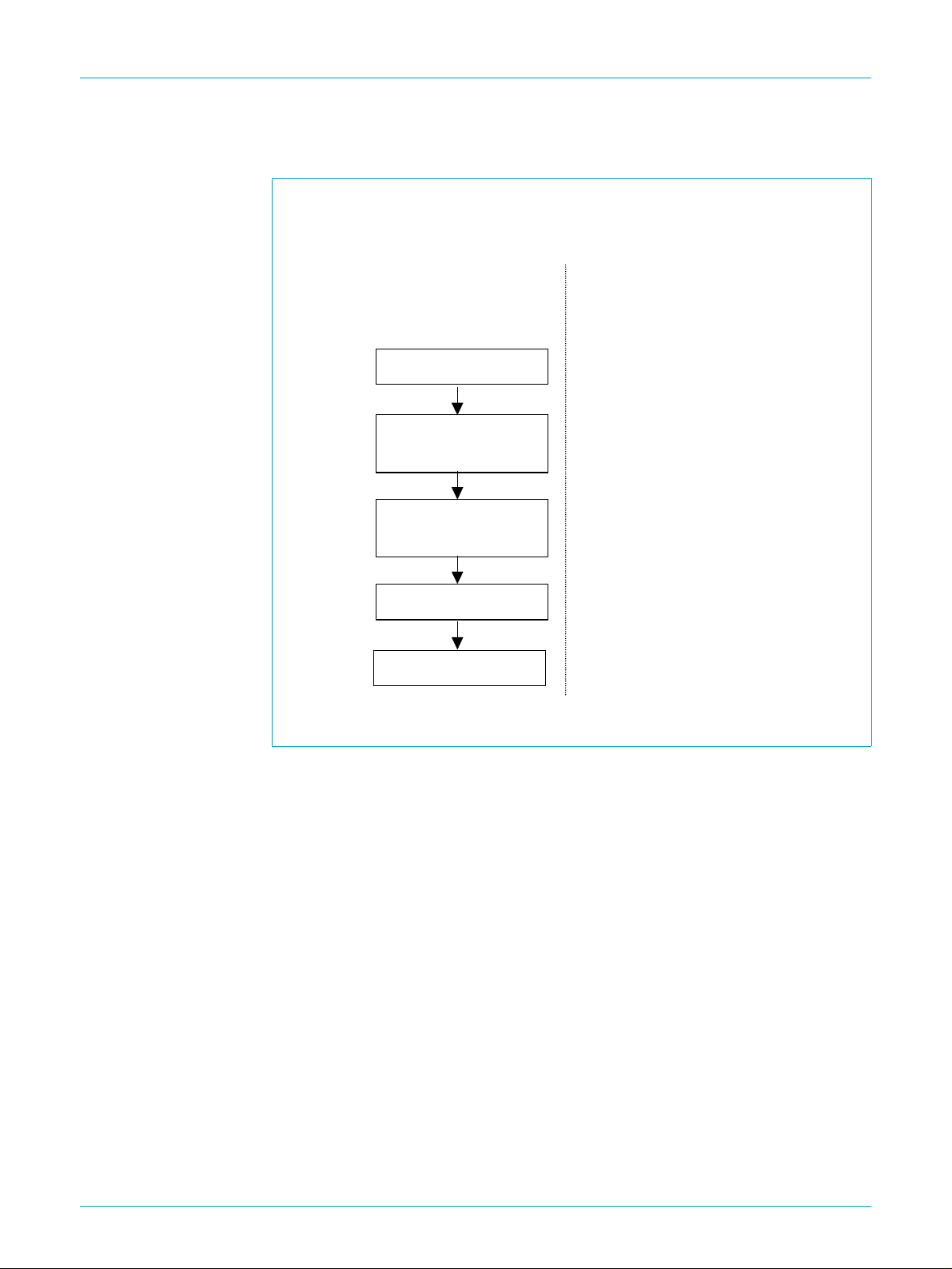

2.1 PNX2000 Control Interface

The PNX2000 device is controlled via an I2C interface. Internally, an I2C-to-PI Bus

bridge converts I

2

C accesses into read and write transactions on the internal PI-Bus.

This PI-Bus provides access to the control and status registers for all the modules in

the PNX2000 design. The operation of the internal PI bus is controlled by the BCU

block.

BCU

ITU656

Registers

I2D

Registers

I2C-Bus

I2C/PI Bus

Bridge

2

C Slave

I

PI Bus

Maste

PI Bus

I2S

Registers

IDDEC

Registers

GTU

Registers

DEMDEC

Registers

udio DSP

Registers

DCU

Registers

PI Bus

Figure 1: Control Interface

Page 20

Philips Semiconductors

2.2 I2C Bus Interface

2.2.1 I2C Bus Features

The I2C module has the following features:

PNX2000

Control Interface

• 7-bit I

• LSB of I

2

C slave address.

2

C address selectable from external pin, to allow two PNX2000 devices

to coexist on a shared I

• Auto increment addressing to allow sequential (burst) register accesses with no

address transmission overhead.

• PI Bus data width 32 bits.

• PI bus address width 32 bits.

2

• I

C data transmitted in big endian format (MSB transmitted first).

• Up to 400 kHz I2C bus speed.

2.2.2 Allocated I2C Address

2

The 7-bit I

A6 A5 A4 A3 A2 A1 A0 RW

100010XX

C address of the PNX2000 device is:

2

C bus.

Bit A0 can be selected via the external pin I2CADR. This pin defaults to pull-down (A0

= 0) if left unconnected.

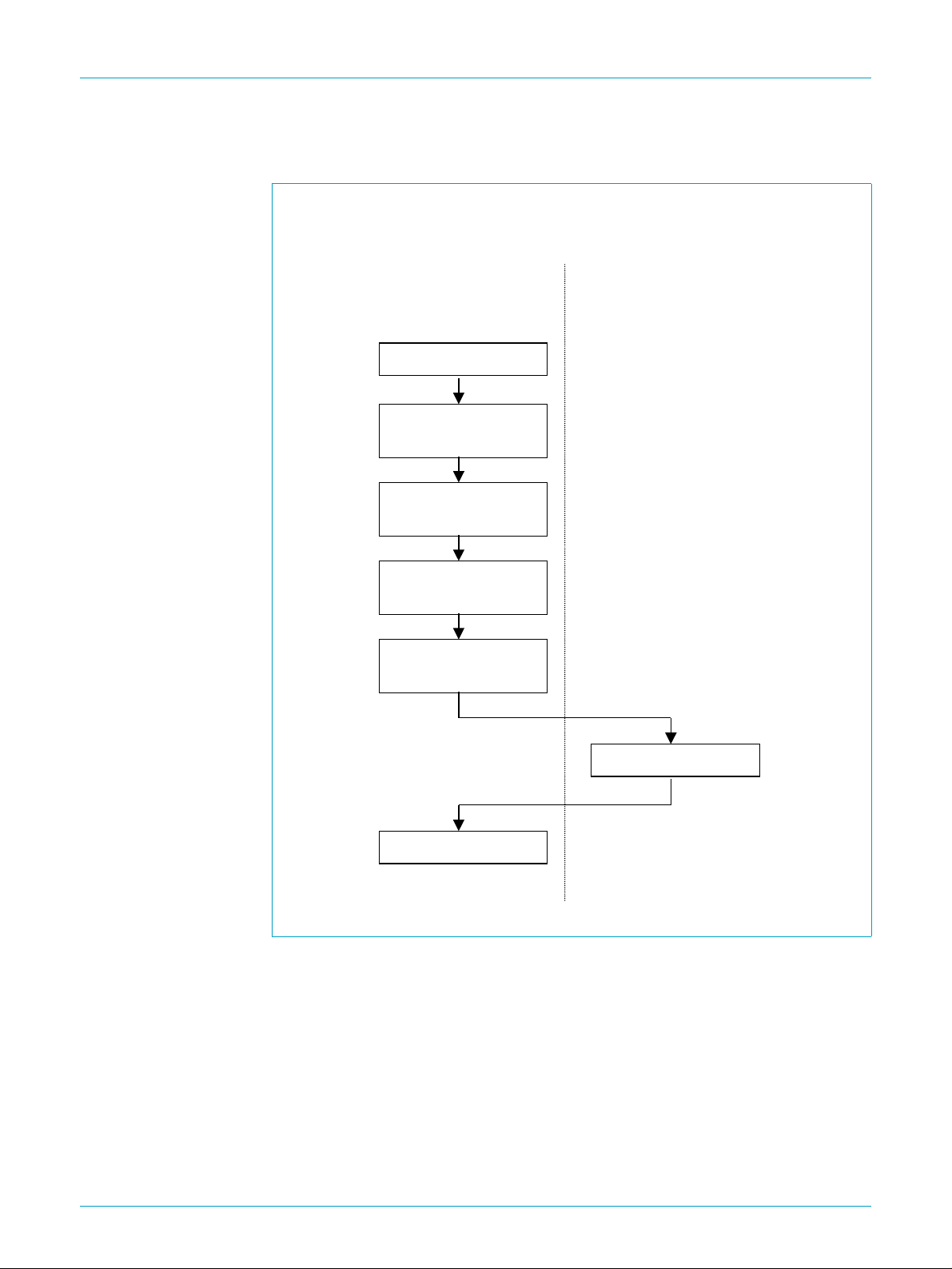

2.2.3 I2C Register Access Protocol

The following diagrams illustrate the procedure used to access register locations over

2

the I

C bus.

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 2-2

Page 21

Philips Semiconductors

PNX2000

Control Interface

Single Write

I2C Master

I2C Start Condition

Device Address

(r/w = 0)

4 bytes subaddress

(= PI bus address)

4 bytes data

I2C Stop Condition

I2C Slave (PNX2000)

Figure 2: Single Write

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 2-3

Page 22

Philips Semiconductors

PNX2000

Control Interface

Single Read

I2C Master

I2C Start Condition

Device Address

(r/w = 0)

4 bytes subaddress

(= PI bus address)

I2C Repeat - Start

Condition

Device Address

(r/w = 1)

I2C Slave (PNX2000)

4 bytes data

I2C Stop Condition

Figure 3: Single Read

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 2-4

Page 23

Philips Semiconductors

PNX2000

Control Interface

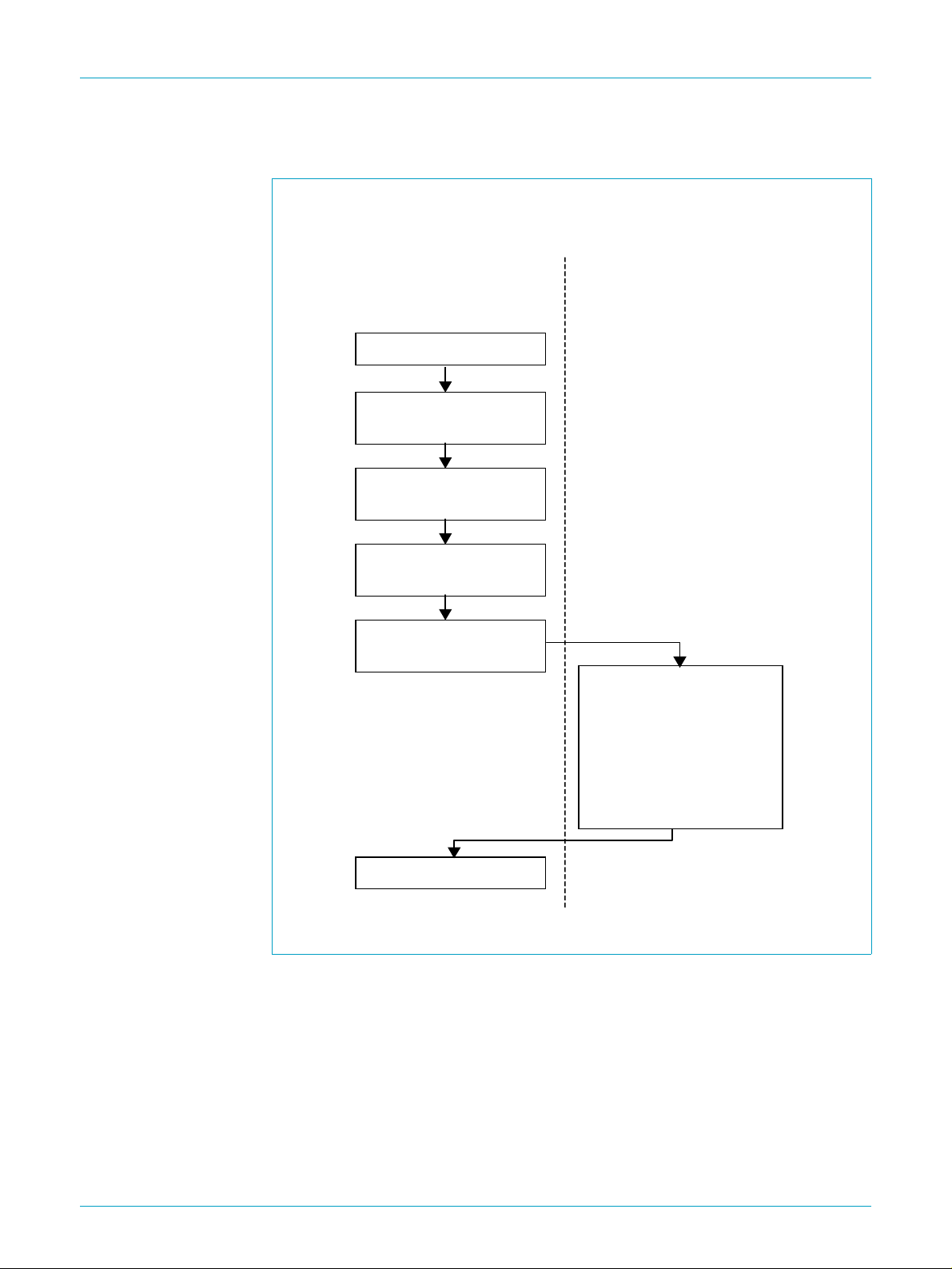

Burst Write

I2C Master

I2C Start Condition

Device Address

(r/w = 0)

4 bytes subaddress

(= PI bus address)

4 bytes data

4 bytes data

…(as many 4 - byte

words as desired)

I2C Slave (PNX2000)

PNX2000 will

internally increment

the PI - Bus address

for each data word

I2C Stop Condition

Figure 4: Burst Write

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 2-5

Page 24

Philips Semiconductors

Burst Read

PNX2000

Control Interface

I2C Master

I2C Start Condition

Device Address

(r/w = 0)

4 bytes subaddress

(= PI bus address)

Repeat - Start

Condition

Device Address

(r/w = 1)

I2C Slave (PNX2000)

4 bytes data

4 bytes data

…(as

many 4 - byte data

words as desired).

The PNX2000 will

internally increment

the PI - Bus address

for each data word.

I2C Stop Condition

Figure 5: Burst Read

2.2.4 I2C Interface Block

The I2C interface module contains no software-accessible status or configuration

registers.

If the internal PI-Bus locks up, the I

holding the SCL signal low. The only way to break the lockup is to reset the entire

PNX2000 device. In order to avoid this condition, the BCU timeout register should be

configured by software early in the PNX2000 initialization process.

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 2-6

2

C interface will lock the external I2C bus by

Page 25

Philips Semiconductors

The PNX2000 I2C module will not respond to a ‘general call’ on the I2C-bus, i.e. when

a slave address of 0000000 is sent by a master. In case of any illegal address,

transmission of the data that follows is not acknowledged, and the transmission is

aborted.

The I

400 kbits/s in accordance with the I

2.3 BCU Module

2.3.1 BCU Features

The BCU module performs the following functions:

PNX2000

Control Interface

2

C-bus slave devices are capable of operating at a maximum speed of

• Address space mapping and slave selection

• Bus error notification and logging

• Bus timeout monitoring, with software programmable timeout threshold

2

C fast-mode specification.

• Interrupt generation on bus error and timeout

2.3.2 Registers

The BCU contains eight software accessible registers which are listed in

the following table. Note that the base address of the BCU is 0x07fe8000.

The “reset” values given in the tables in the following subsections correspond to the

state of a variable after PI-Bus reset.

Table 1: BCU Register Map

Register Name

BCU_INT_STATUS 0x00 BCU interrupt status

BCU_INT_SET 0x04 BCU interrupt status set

BCU_INT_CLEAR 0x08 BCU interrupt status clear

BCU_FAULT_STATUS 0x0C BCU bus fault status

BCU_FAULT_ADDRESS 0x10 BCU bus fault address

BCU_INT_ENABLE 0x14 BCU interrupt enable

BCU_TOUT 0x18 BCU time-out control

BCU_SNOOP 0x1C BCU memory coherency control

Offset from BCU

Slave address

Description

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.

Rev. 1.0 — 28 November 2003 2-7

Page 26

Philips Semiconductors

2.3.2.1 BCU Interrupt Status Register (BCU_INT_STATUS)

This register contains the BCU interrupt status variables. It is read-only. The register

also controls the bus fault logging process.

Table 2: BCU_INT_STATUS register

Bits Variable Reset R/W

31:2 RSD - -

1 BCU_TO 0 R

0 BCU_BE 0 R

RSD Reserved bits, will produce zero on a read action and ignored on write

BCU_TO Time-out error:

PNX2000

Control Interface

action

0: no time-out error has occurred. Fault logging enabled if BCU_BE=0

and BCU_TO=0.

1: time-out error has occurred. Fault logging stopped. Registers

BCU_FAULT_STATUS and BCU_FAULT_ADDRESS contain valid

information. Depending on the state of the BCU_INT_EN flag in the

BCU_INT_ENABLE register, an interrupt request may be generated.

BCU_BE Bus error:

0: no bus error has occurred. Fault logging enabled if BCU_TO=0 and

BCU_BE=0.

1: bus error has occurred. Fault logging stopped. Registers

BCU_FAULT_STATUS and BCU_FAULT_ADDRESS contain valid

information. Depending on the state of the BCU_INT_EN flag in the

BCU_INT_ENABLE register, an interrupt request may be generated.

2.3.2.2 BCU Interrupt Enable Register (BCU_INT_ENABLE)

This register contains a variable to enable/disable BCU interrupt request generation.

It is read/writable. Note that this register does not have two enable bits (i.e.

corresponding to the two status bits in the BCU_INT_STATUS, BCU_INT_SET, and

BCU_INT_CLEAR registers). One enable bit controls the generation of both bus error

and timeout interrupts.

Table 3: BCU_INT_ENABLE register

Bits Variable Reset R/W

31: 1 RSD - R

0 BCU_INT_EN 0 R/W

RSD Reserved bits, produce zero on read action and ignored on

write.

BCU_INT_EN BCU Interrupt Enable

0: disable BCU interrupt request.

UM10105_1 © Koninklijke Philips Electronics N.V. 2003. All rights reserved.