Philips TSA5060ATS, TSA5060AT Datasheet

INTEGRATED CIRCUITS

DATA SH EET

TSA5060A

1.3 GHz I

2

C-bus controlled low

phase noise frequency synthesizer

Product specification

Supersedes data of 2000 Sep 19

File under Integrated Circuits, IC02

2000 Oct 24

Philips Semiconductors Product specification

1.3 GHz I2C-bus controlled low phase

noise frequency synthesizer

FEATURES

• Complete 1.3 GHz single chip system

• Optimized for low phase noise

• Selectable divide-by-two prescaler

• Operationupto1.3 GHzwithoutdivide-by-twoprescaler

• Selectable reference divider ratio

• Compatible with UK-DTT (Digital Terrestrial Television)

offset requirements

• Selectable crystal or comparison frequency output

• Four selectable charge pump currents

• Four selectable I2C-bus addresses

• Standard and fast mode I2C-bus

• I2C-bus compatible with 3.3 and 5 V microcontrollers

• 5-level Analog-to-Digital Converter (ADC)

• Low power consumption

• Three I/O ports and one output port.

APPLICATIONS

• Digital terrestrial and cable tuning systems

• Hybrid (digital and analog) terrestrial and cable tuning

systems

• Digital set-top boxes.

GENERAL DESCRIPTION

The TSA5060A is a single chipPLL frequency synthesizer

designed for terrestrial and cable tuning systems up to

1.3 GHz.

TSA5060A

The comparison frequency is obtained from an on-chip

crystal oscillator that can also be driven from an external

source. Either the crystal frequency or the comparison

frequency can be switched to the XT/COMP output pin to

drive the reference input of another synthesizer or the

clock input of a digital demodulation IC.

Bothdividedand comparison frequencies are compared in

the fast phase detector which drives the charge pump.

The loop amplifier is also on-chip, however an external

NPN transistor to drive directly the 33 V tuning voltage.

Controldataisenteredvia the I2C-bus;fiveserialbytesare

required to address the device, select the main divider

ratio, the reference divider ratio, program the four output

ports,set the charge pump current,select the prescaler by

two, select the signal to switch to the XT/COMP output pin

and select a specific test mode. Three of the four output

ports can also be used as input ports and a 5-level ADC is

provided. Digital information concerning the input ports

andtheADC can be read out oftheTSA5060Aon the SDA

line (one status byte) during a READ operation. A flag is

set when the loop is ‘in-lock’ and is read during a READ

operation, as well as the Power-on reset flag. The device

has four programmable addresses, programmed by

applying a specific voltage at pin AS, enabling the use of

multiple synthesizers in the same system.

TheRF preamplifierdrivesthe17-bitmaindividerenabling

astep size equal tothe comparison frequency, foran input

frequency up to 1.3 GHz covering the complete terrestrial

frequency range. A fixed divide-by-two additional

prescaler can be inserted between the preamplifier and

the main divider. In this case, the step size is twice the

comparison frequency.

2000 Oct 24 2

Philips Semiconductors Product specification

1.3 GHz I2C-bus controlled low phase

TSA5060A

noise frequency synthesizer

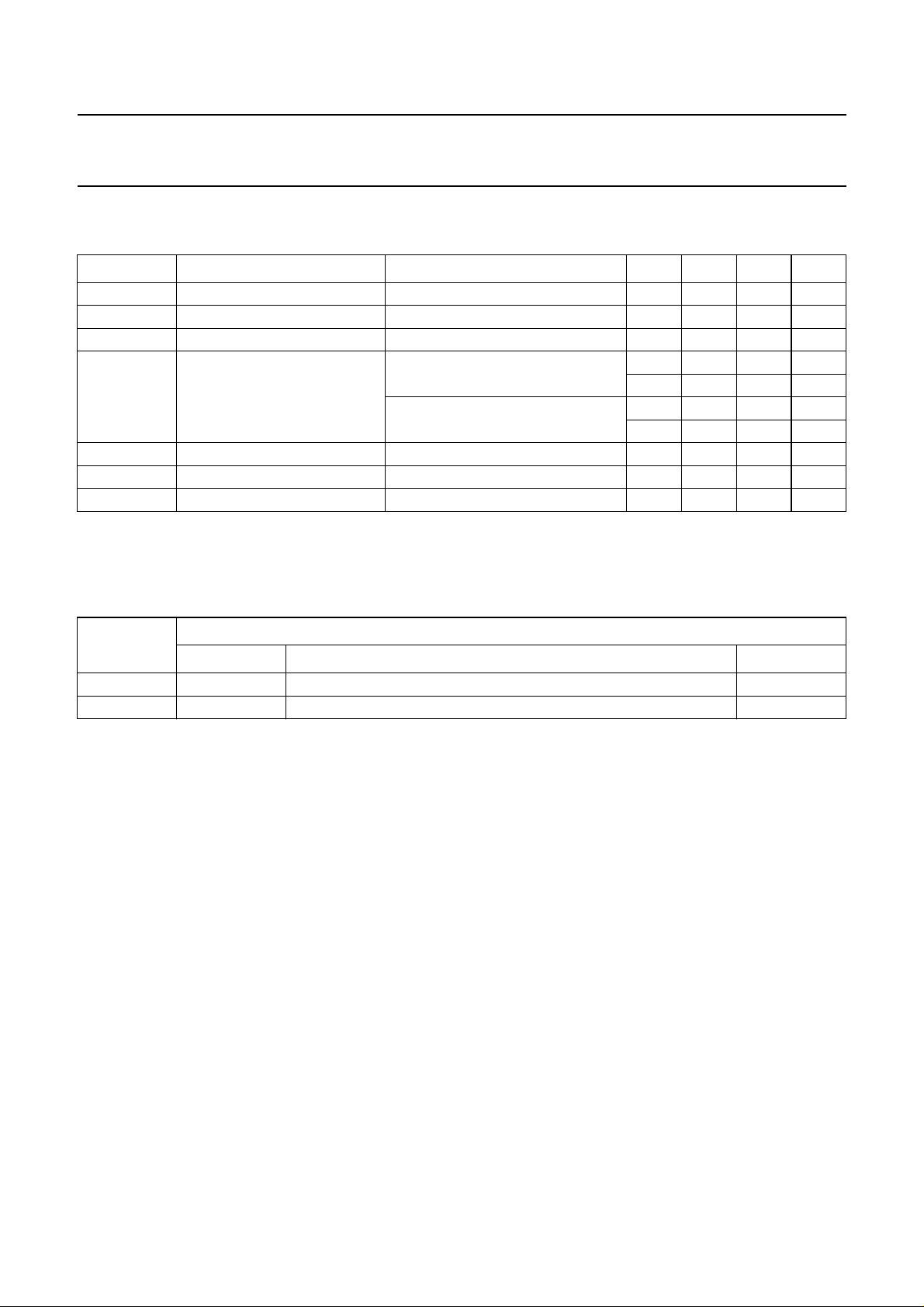

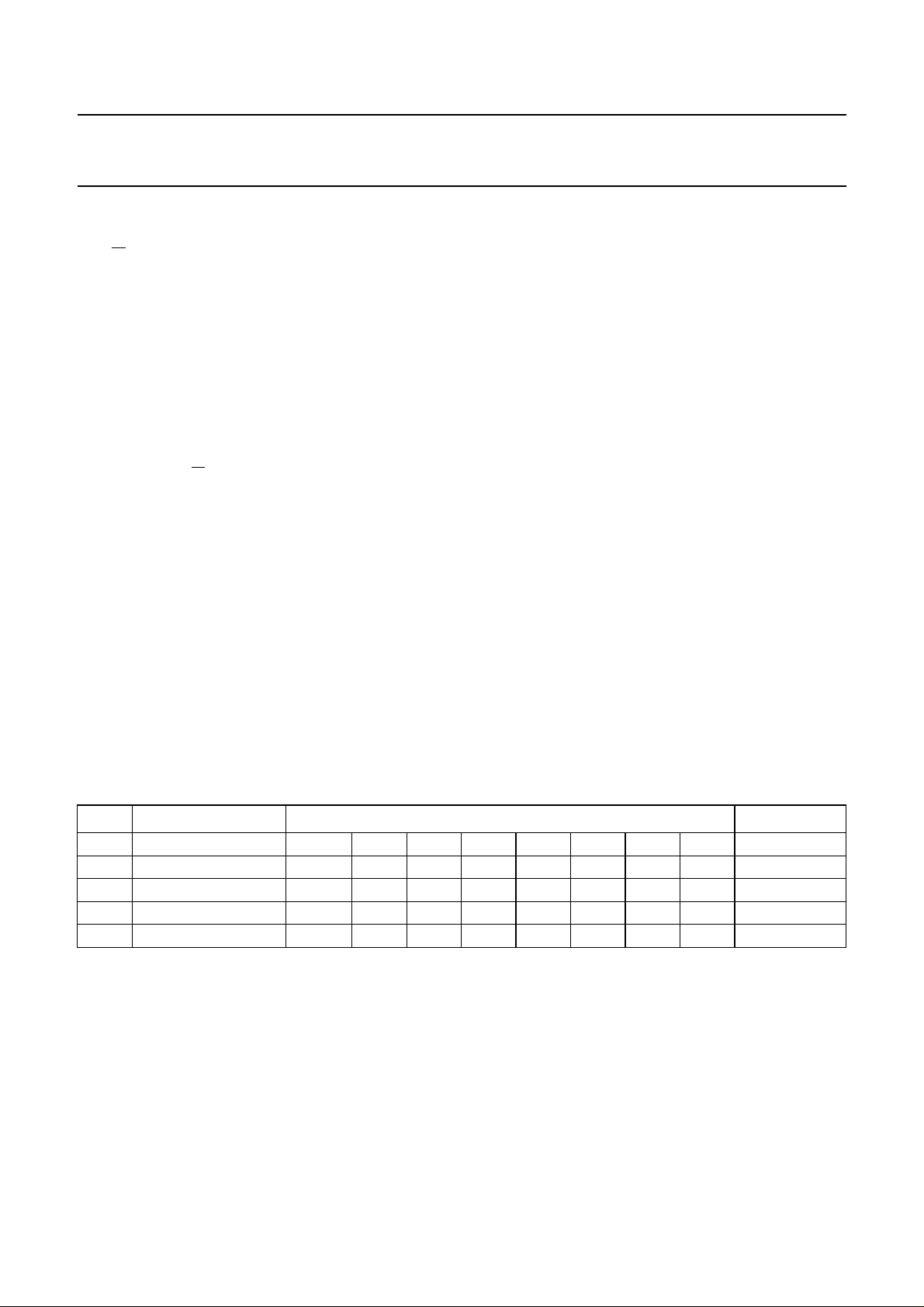

QUICK REFERENCE DATA

VCC= 4.5 to 5.5 V; T

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC

I

CC

f

i(RF)

V

i(RF)(rms)

f

xtal

T

amb

T

stg

supply voltage 4.5 5.0 5.5 V

supply current T

RF input frequency 64 − 1300 MHz

RF input voltage (RMS value) f

crystal frequency 4 − 16 MHz

ambient temperature −20 − +85 °C

storage temperature −40 − +150 °C

Note

1. Asymmetrical drive on pin RFA or RFB; see Fig.3.

= −20 to +85 °C; unless otherwise specified.

amb

=25°C 303745mA

amb

from 64 to 150 MHz; note 1 12.6 − 300 mV

i(RF)

from 150 to 1300 MHz; note 1 7.1 − 300 mV

f

i(RF)

−25 − +2.5 dBm

−30 − +2.5 dBm

ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

TSA5060AT SO16 plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

TSA5060ATS SSOP16 plastic shrink small outline package; 16 leads; body width 4.4 mm SOT369-1

2000 Oct 24 3

Philips Semiconductors Product specification

1.3 GHz I2C-bus controlled low phase

noise frequency synthesizer

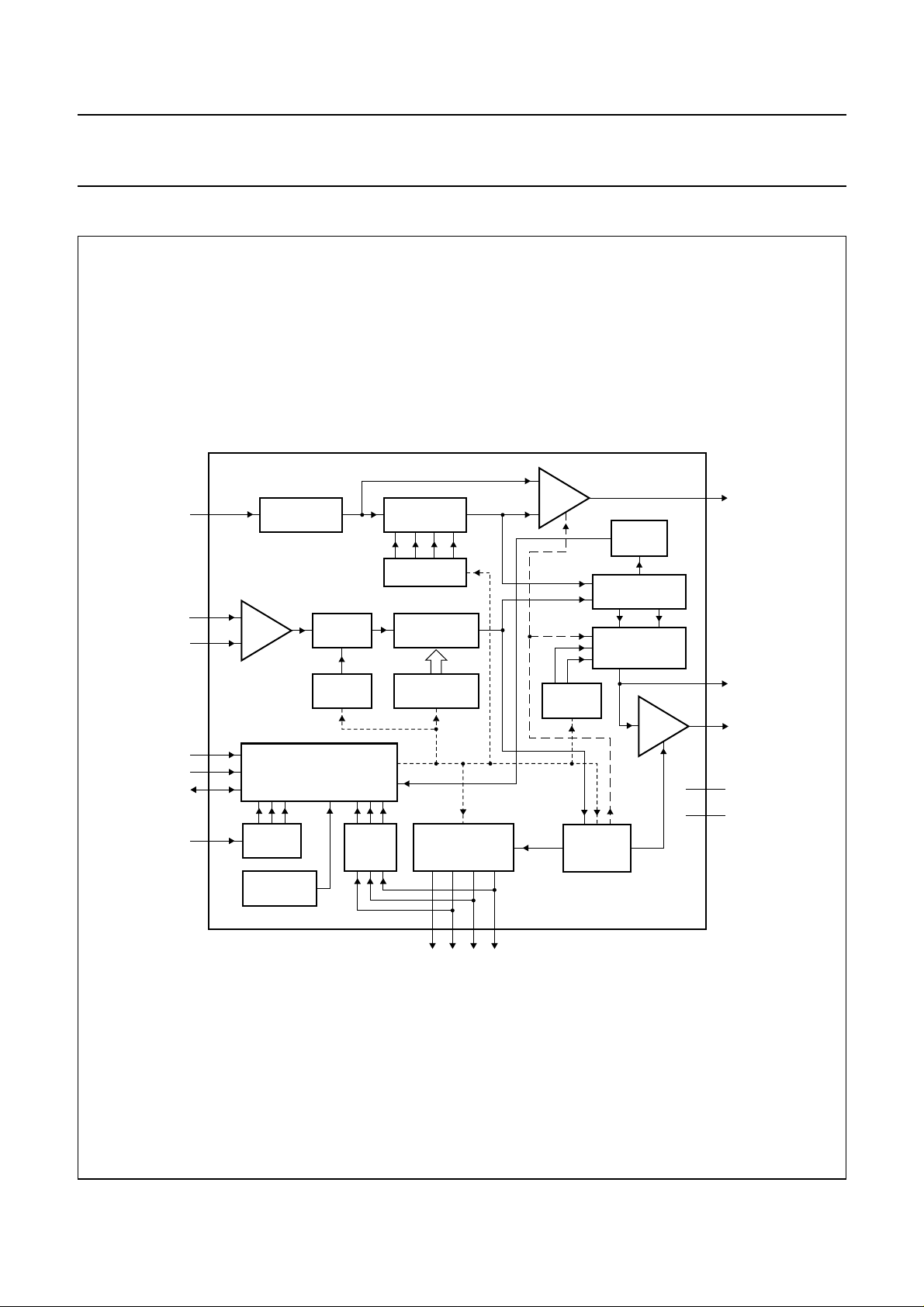

BLOCK DIAGRAM

handbook, full pagewidth

XTAL

RFA

RFB

2

13

14

OSCILLATOR

PRE

AMP

XTAL

DIVIDER

1/2

REFERENCE

DIVIDER

4-BIT LATCH

DIVIDER

17-BIT

LOCK

DETECT

DIGITAL PHASE

COMPARATOR

CHARGE PUMP

TSA5060A

3

XT/COMP

AS

SCL

SDA

ADC

4

6

5

11

TRANSCEIVER

3-BIT

ADC

POWER-ON

RESET

1-BIT

LATCH

I2C-BUS

3-BIT

INPUT

PORTS

17-BIT LATCH

DIVIDE RATIO

4-BIT LATCH

AND

OUTPUT PORTS

P3 P2 P1 P0

1

2-BIT

LATCH

AMP

MODE

CONTROL

LOGIC

CP

16

DRIVE

12

V

CC

15

GND

TSA5060A

10987

FCE717

Fig.1 Block diagram.

2000 Oct 24 4

Philips Semiconductors Product specification

1.3 GHz I2C-bus controlled low phase

noise frequency synthesizer

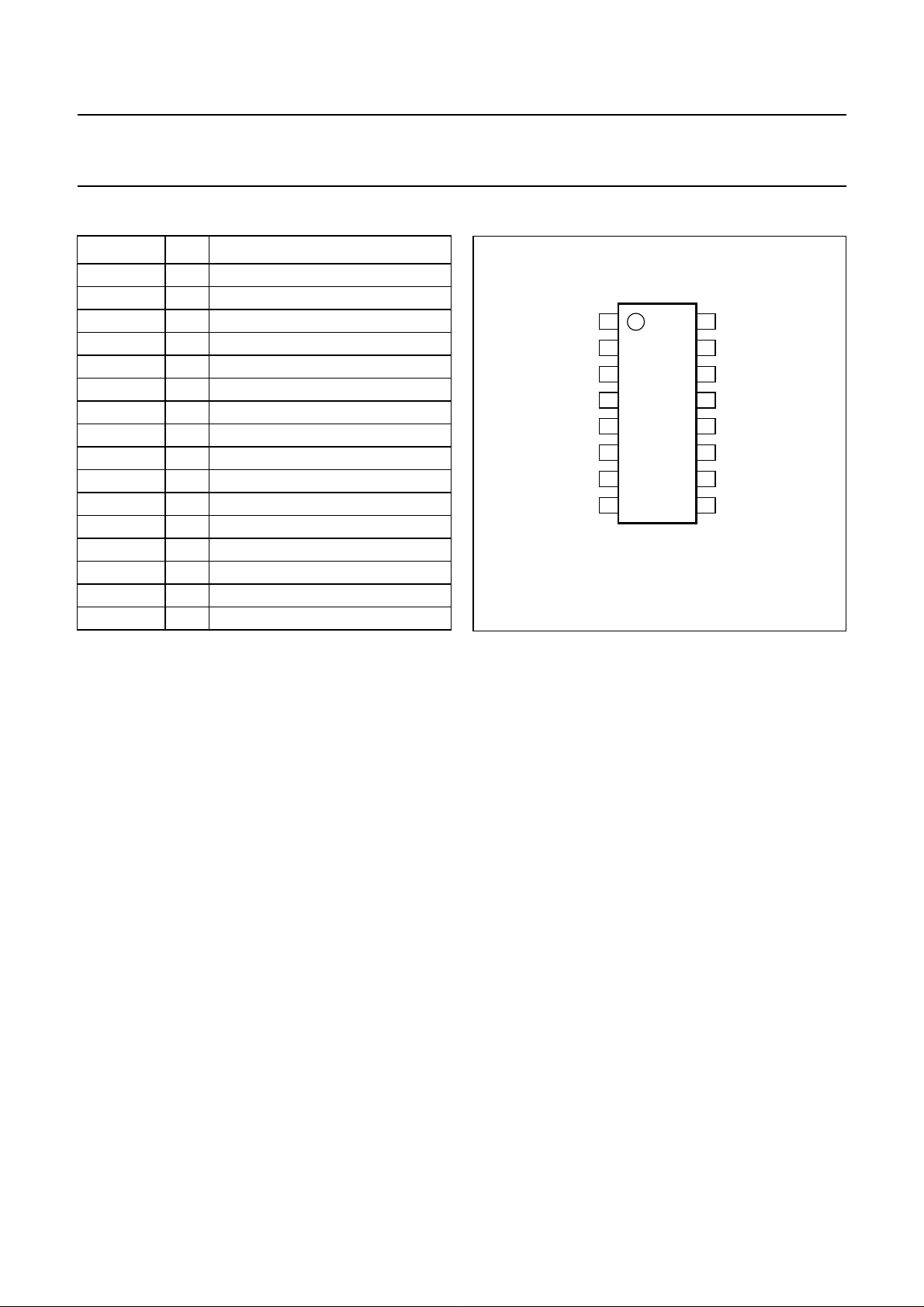

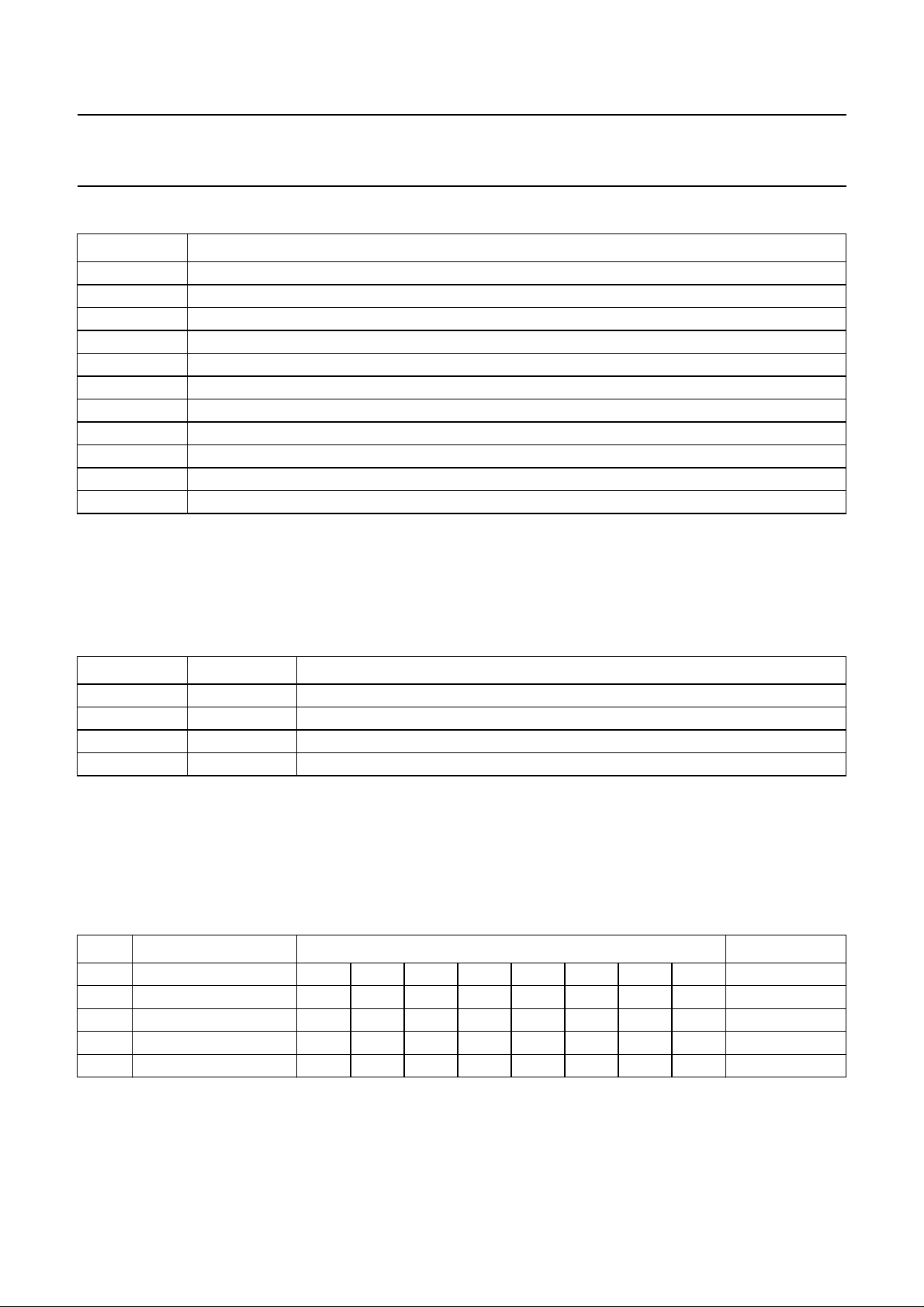

PINNING

SYMBOL PIN DESCRIPTION

CP 1 charge pump output

XTAL 2 crystal oscillator input

XT/COMP 3 f

AS 4 I

SDA 5 I

SCL 6 I

P3 7 general purpose output Port 3

P2 8 general purpose input/output Port 2

P1 9 general purpose input/output Port 1

P0 10 general purpose input/output Port 0

ADC 11 analog-to-digital converter input

V

CC

12 supply voltage

RFA 13 RF signal input A

RFB 14 RF signal input B

GND 15 ground

DRIVE 16 external NPN drive output

or f

xtal

2

C-bus address selection input

2

C-bus serial data input/output

2

C-bus serial clock input

signal output

comp

handbook, halfpage

XT/COMP

CP

1

XTAL

2

3

4

AS

TSA5060A

5

SDA

6

SCL

7

P3

8

P2

FCE718

Fig.2 Pin configuration.

TSA5060A

16

DRIVE

15

GND

14

RFB

13

RFA

12

V

CC

11

ADC

10

P0

9

P1

FUNCTIONAL DESCRIPTION

The TSA5060A contains all the necessary elements

except a reference source, a loop filter and an external

NPN transistor to control a varicap tuned local oscillator

forming a phase locked loop frequency synthesized

source. The IC is designed in a high speed process with a

fast phase detector to allow a high comparison frequency

to reach a low phase noise level on the oscillator.

The block diagram is shown in Fig.1. The RF signal is

applied at pins RFA and RFB. The input preamplifier

provides a good sensitivity. The output of the preamplifier

is fed to the 17-bit programmable divider either through a

divide-by-two prescaler or directly. Because ofthe internal

high speed process, the RF divider is working at a

frequency up to 1.3 GHz, without the need for the

divide-by-two prescaler to be used.

The output of the 17-bit programmable divider f

DIV

is fed

into the phase comparator, where it is compared in both

phaseandfrequency with the comparison frequency f

comp

This frequency is derived from the signal present at

pin XTAL, f

, divided down in the reference divider. It is

xtal

possible either to connecta quartz crystalto pin XTAL and

then using the on-chip crystal oscillator, or to feed this pin

with a reference signal from an external source.

The reference divider can have a dividing ratio selected

from 16 different values between 2 and 320, including the

ratio 24 to cope with the offset requirement of the UK-DTT

system, see Table 8.

The output of the phase comparator drives the

charge pump and the loop amplifier section. This amplifier

requires the use of an external NPN transistor. Pin CP is

the output of the charge pump, and pin DRIVE is

connected to the base of the external transistor. This

transistor has its emitter grounded and the collector drives

the tuning voltage to the varicap diode of the Voltage

Controlled Oscillator (VCO). The loop filter has to be

connected between pin CP and the collector of the

external NPN transistor (see Fig.4).

It is also possible to drive another PLL synthesizer, or the

clock input of a digital demodulation IC, from

pin XT/COMP. It is possible to select by software either

f

, the crystal oscillator frequency or f

xtal

, the frequency

comp

present after the reference divider. It is also possible to

switch off this output, in case it is not used.

.

For test and alignment purposes, it is possible to release

the drive output to be able to apply an external voltage on

it, to select one of the three charge pump test modes, and

to monitor half the f

at Port P0. See Table 10 for all

DIV

possible modes.

Four open-collector output portsare provided on the IC for

general purpose; three of these can also be used as input

ports. A 3-bit ADC is also available.

2000 Oct 24 5

Philips Semiconductors Product specification

1.3 GHz I2C-bus controlled low phase

noise frequency synthesizer

The TSA5060A is controlled via the two-wire I2C-bus.

For programming, there is one 7-bit module address and

bit R/W for selecting READ or WRITE mode.

To be able to have more than one synthesizer in an

I2C-bussystem,oneoffourpossible addresses is selected

depending on the voltage applied at pin AS (see Table 3).

The TSA5060A fulfils the fast mode I2C-bus, according to

the Philips I2C-bus specification. The I2C-bus interface is

designed in such a way that pins SCL and SDA can be

connected either to 5 or 3.3 V pulled-up I2C-bus lines,

allowing the PLL synthesizer to be connected directly to

the bus lines of a 3.3 V microcontroller.

WRITE mode: R/W=0

After the address transmission (first byte), data bytes can

be sent to the device (see Table 1). Four data bytes are

needed to fully program the TSA5060A. The bus

transceiver has an auto-increment facility that permits

programming of the TSA5060A within one single

transmission (address + 4 data bytes).

TSA5060A

To allow a smooth frequency sweep for fine tuning, and

while the data of the dividing ratio of the main divider is in

data bytes 2, 3 and 4, it is necessary to change the

frequency to send the data bytes 2 to 5 in a repeated

sending, or to finish an incomplete transmission by a

STOP condition. Repeated sending of data bytes 2 and 3

without ending the transmission does not change the

dividing ratio. To illustrate, the following data sequences

will change the dividing ratio:

• Bytes 2, 3, 4 and 5

• Bytes 4, 5, 2 and 3

• Bytes 2, 3, 4 and STOP

• Bytes 4, 5, 2 and STOP

• Bytes 2, 3 and STOP

• Bytes 2 and STOP

• Bytes 4 and STOP.

The TSA5060A can also be partly programmed on the

condition that the first data byte following the address is

byte 2 or 4. The meaning of the bits in the data bytes is

given in Table 1. The first bit of the first databyte indicates

whether byte 2 (first bit is logic 0) or byte 4 (first bit is

logic 1) will follow.Until an I2C-bus STOP conditionis sent

by the controller, additional data bytes can be entered

without the need to re-address the device.

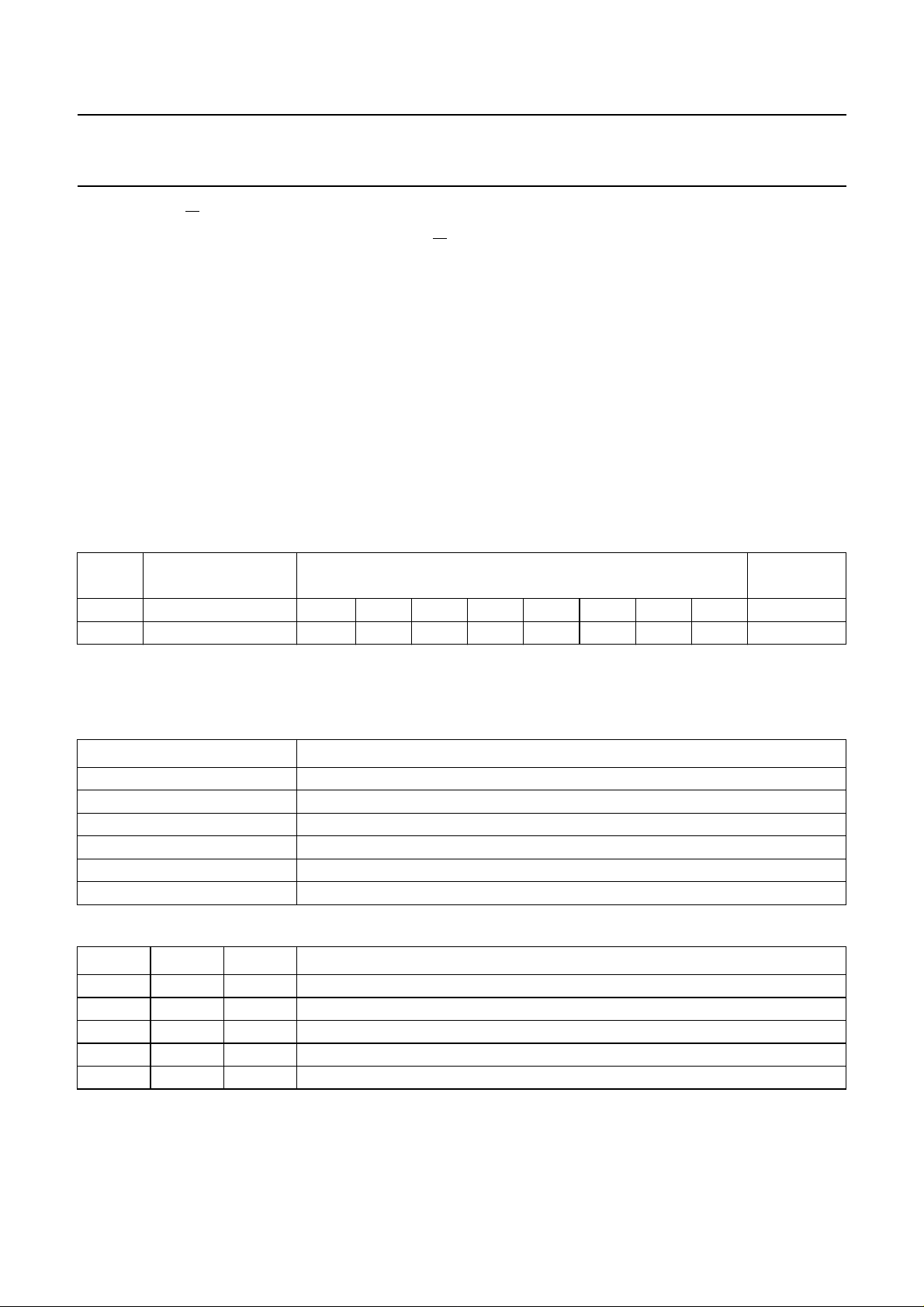

Table 1 Write data format

BYTE DESCRIPTION MSB

1 address 1 1 0 0 0 MA1 MA0 0 A

2 programmable divider 0 N14 N13 N12 N11 N10 N9 N8 A

3 programmable divider N7 N6 N5 N4 N3 N2 N1 N0 A

4 control data 1 N16 N15 PE R3 R2 R1 R0 A

5 control data C1 C0 XCE XCS P3 P2/T2 P1/T1 P0/T0 A

Note

1. MSB is transmitted first.

(1)

LSB CONTROL BIT

2000 Oct 24 6

Philips Semiconductors Product specification

1.3 GHz I2C-bus controlled low phase

TSA5060A

noise frequency synthesizer

Table 2 Explanation of Table 1

BIT DESCRIPTION

MA1 and MA0 programmable address bits; see Table 3

A acknowledge bit

N16 to N0 programmable main divider ratio control bits; N = N16 × 2

PE prescaler enable (prescaler by 2 is active when bit PE = 1)

R3 to R0 programmable reference divider ratio control bits; see Table 8

C1 and C0 charge pump current select bits; see Table 9

XCE XT/COMP enable; XT/COMP output active when bit XCE = 1; see Table 10

XCS XT/COMP select; signal select when bit XCE = 1, test mode enable when bit XCE = 0; see Table 10

T2, T1 and T0 test mode select when bit XCE = 0 and bit XCS = 1; see Table 10

P3, P2 and P1 Port P3, P2 and P1 output states

P0 Port P0 output state, except in test mode; see Table 10

Address selection

The module address contains the programmable address bits MA1 and MA0, which offer the possibility of having

up to 4 synthesizers in one system. The relationship between MA1 and MA0 and the input voltage at pin AS is given in

Table 3.

16

+ N15 × 215+ ... + N1 × 21+N0

Table 3 Address selection

MA1 MA0 VOLTAGE APPLIED TO PIN AS

0 0 0 to 0.1V

CC

0 1 open-circuit

1 0 0.4V

1 1 0.9V

to 0.6VCC; note 1

CC

to V

CC

CC

Note

1. This address is selected by connecting a 15 kΩ resistor between pin AS and pin V

CC

.

Status at Power-On Reset (POR)

At power-on or whenthe supply voltage drops below approximately 2.75 V internalregisters are set according to Table 4.

Table 4 Status at Power-on reset; note 1

BYTE DESCRIPTION MSB LSB CONTROL BIT

1 address 11000MA1MA00 A

2 programmable divider 0 XXXXXXX A

3 programmable divider XXXXXXXX A

4 control data 1 XXXXXXX A

5 control data 0001X

(2)

(2)

1

(2)

X

(2)

X

A

Notes

1. X = don’t care.

2. At Power-on reset, all output ports are in high-impedance state.

2000 Oct 24 7

Philips Semiconductors Product specification

1.3 GHz I2C-bus controlled low phase

TSA5060A

noise frequency synthesizer

READ mode: R/W=1

Data can be read out of the TSA5060A by setting bit R/W

to logic 1 (see Table 5). After the slave address has been

recognized, the TSA5060A generates an acknowledge

pulse and the first data byte(status word) is transferred on

the SDA line. Data is valid on the SDA line during a

HIGH-level of the SCL clock signal.

Asecond data byte canbe read out of theTSA5060A if the

microcontroller generates an acknowledge bit on the

SDA line.End oftransmissionwilloccur if no acknowledge

bit from the controller occurs.The TSA5060A will then

release the data line to allow the microcontroller to

generate a STOP condition. When ports P0 to P2 are

used as inputs, they must be programmed in their

high-impedance state.

Table 5 Read data format

BYTE DESCRIPTION MSB

(1)

1 address 1 1000MA1MA01 A

2 status byte POR FL I2 I1 I0 A2 A1 A0 −

The POR flag is set to logic 1 when VCC drops below

approximately 2.75 V and at power-on.

It is reset to logic 0 when an end of data is detected by the

TSA5060A (end of a READ sequence).

Control of the loop is made possible with the in-lock flag

which indicates if the loop is phase-locked (bit FL = 1).

The bits I2, I1 and I0 represent the status of the I/O ports

P2, P1 and P0 respectively. A logic 0 indicates a

LOW-level and a logic 1 indicates a HIGH-level.

A built-in 5-level ADC is available at pin ADC. This

converter can be used to feed AFC information to the

microcontroller through the I2C-bus. The relationship

between bits A2, A1, A0 and the input voltage at pin ADC

is given in Table 7.

LSB

CONTROL

BIT

Note

1. MSB is transmitted first.

Table 6 Explanation of Table 5

BIT DESCRIPTION

A acknowledge bit

MA1 and MA0 programmable address bits; see Table 3

POR Power-on reset flag (bit POR = 1 at power-on)

FL in-lock flag (bit FL = 1 when the loop is phase-locked)

I2, I1 and I0 digital information for I/O ports P2, P1 and P0 respectively

A2, A1 and A0 digital outputs of the 5-level ADC; see Table 7

Table 7 ADC levels

A2 A1 A0 VOLTAGE APPLIED TO PIN ADC

1 0 0 0.6VCCto V

0 1 1 0.45VCCto 0.6V

0 1 0 0.3VCCto 0.45V

0 0 1 0.15VCCto 0.3V

0 0 0 0 to 0.15V

CC

CC

CC

CC

CC

Note

1. Accuracy is ±0.03 V

CC

.

(1)

2000 Oct 24 8

Loading...

Loading...