Philips TEA1205AT Datasheet

INTEGRATED CIRCUITS

DATA SH EET

TEA1205AT

High efficiency DC/DC converter

Preliminary specification

File under Integrated Circuits, IC03

1998 Mar 24

Philips Semiconductors Preliminary specification

High efficiency DC/DC converter TEA1205AT

FEATURES

• Fully integrated DC/DC converter circuit

• Up conversion in 2 different modes

• High efficiency over wide load range

• Synchronizes to external high frequency clock

• Output power up to 3.6 W (typ.) continuous, 8 W in GSM

burst mode

• Low quiescent power consumption

• True current limit for Li-ion battery compatibility

• Shut-down function

• 8-pin SO package.

APPLICATIONS

• Cellular and cordless phones PDAs and others

• Supply voltage source for low-voltage chip sets

• Portable computers

• Battery backup supplies

• Cameras.

GENERAL DESCRIPTION

The TEA1205AT (see Fig.1) is a fully integrated DC/DC

converter circuit using the minimum amount of external

components. It is intended to be used to supply electronic

circuits with supply voltages of 3.3 or 5.5 V from

2, 3 or 4 NiCd cell batteries or one Li-ion battery at an

output power level up to 3.6 W (typ.) continuously, or 8 W

in GSM TDMA (1 : 8) burst mode. The switching frequency

of the converter can be synchronized to an external

high-frequency clock. Efficient, compact and dynamic

power conversion is achieved using a novel, digitally

controlled Pulse Width and Frequency Modulation

(PWFM) like control concept, integrated low R

power switches with low parasitic capacitances and

synchronous rectification.

dsON

CMOS

ORDERING INFORMATION

TYPE NUMBER

NAME DESCRIPTION VERSION

TEA1205AT SO8 plastic small outline package; 8 leads; body width 3.9 mm SOT96-1

PACKAGE

1998 Mar 24 2

Philips Semiconductors Preliminary specification

High efficiency DC/DC converter TEA1205AT

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

O

V

start

Efficiency; see Figs 6 and 7

η efficiency

Current levels

I

q

I

SHDWN

I

limN

I

lx

Power MOSFETS

R

dsON(N)

R

dsON(P)

Timing

f

sw

t

res

f

sync

output voltage VSEL = LOW 5.23 5.55 5.85 V

VSEL = HIGH 3.13 3.34 3.54 V

start-up voltage 1.6 2.0 2.2 V

up from 2.4 to 3.3 V 1 mA < I

up from 3.6 to 5.5 V 1 mA < I

<1.0A 809095%

L

<1.0A 839094%

L

quiescent current at pin 3 50 60 70 µA

shut-down current − 210µA

NFET current limit note 1 0.9 I

limIlim

1.1 I

lim

A

max. continuous current at pin 5 −−1.0 A

pin-to-pin resistance NFET 0.08 0.12 0.20 Ω

pin-to-pin resistance PFET 0.10 0.16 0.25 Ω

switching frequency 150 200 240 kHz

response time from standby to P

max

− 25 −µs

synchronisation input frequency − 13 − MHz

Note

1. The NFET current limit is set by an external 1% accurate resistor R

The typical maximum instantaneous current is defined as: I

lim

connected between pin 7 and pin 6 (ground).

lim

= 890 V/ R

so the use of R

lim

= 315 Ω will lead to a

lim

typical maximum current value of 2.83 A. The average inductor current during current limit also depends on

inductance value and resistive losses in all components in the power path. In normal application and when using

R

= 315 Ω, the average inductor current will be limited to 2.3 A typical.

lim

1998 Mar 24 3

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1998 Mar 24 4

handbook, full pagewidth

BLOCK DIAGRAM

High efficiency DC/DC converter TEA1205AT

Philips Semiconductors Preliminary specification

5

LX

I/V

CONVERTER

N-type

POWER

FET

GND

sense

FET

ILIM

P-type POWER FET

CONTROL LOGIC

I

IimN

TEMPERATURE

PROTECTION

20 MHz

OSCILLATOR

16278

VSEL SYNC

MODE GEARBOX

START-UP

CIRCUIT

AND

ROM

DIGITAL CONTROLLER

SHDWN

TIME

COUNTER

TEA1205AT

BANDGAP

REFERENCE

3

OUT

4

SENSE

MGM696

Fig.1 Block diagram.

Philips Semiconductors Preliminary specification

High efficiency DC/DC converter TEA1205AT

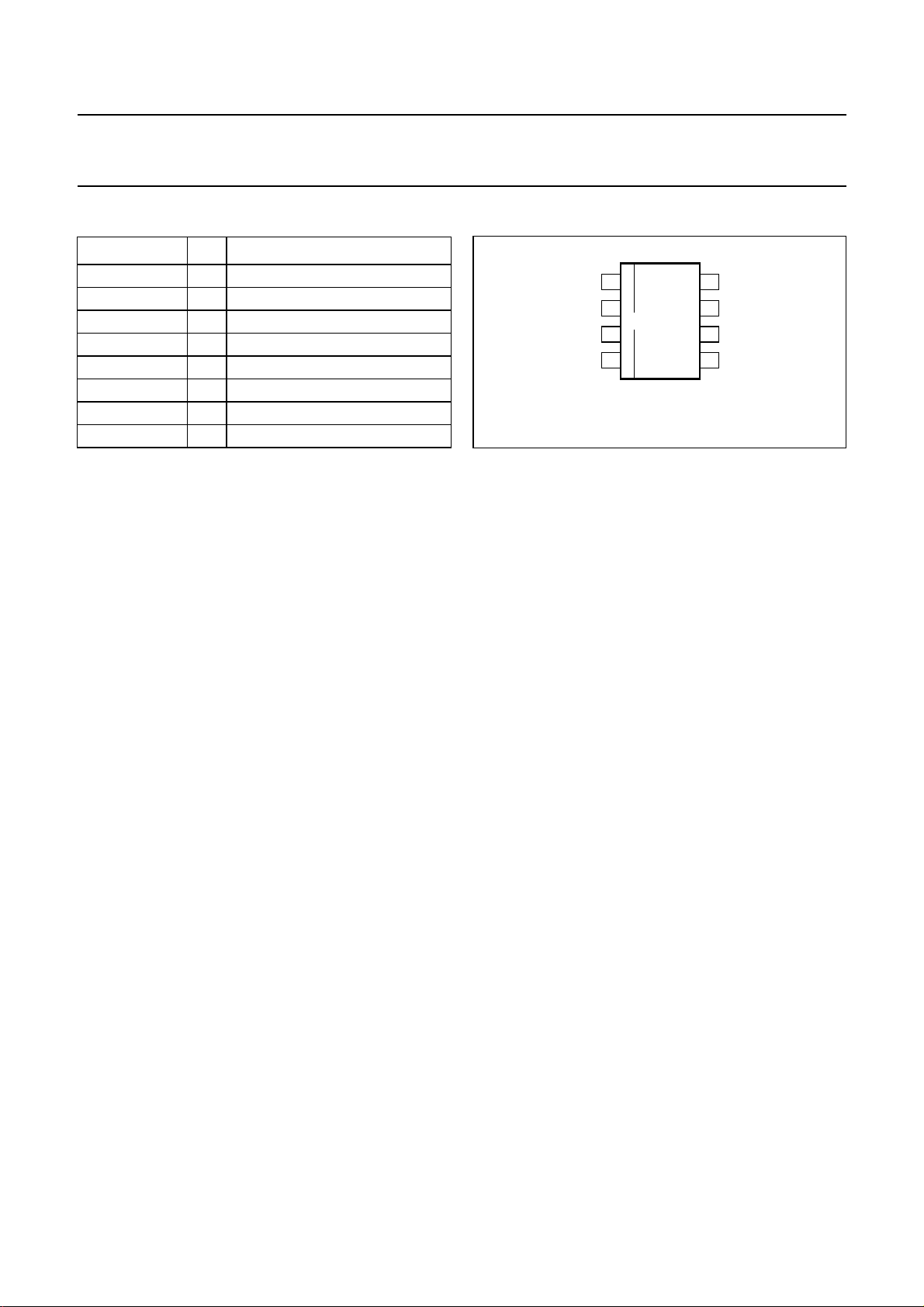

PINNING

SYMBOL PIN DESCRIPTION

VSEL 1 output voltage selection input

SYNC 2 synchronisation clock input

OUT 3 output voltage output

SENSE 4 output voltage sense input

LX 5 inductor connection

GND 6 ground

ILIM 7 current limit resistor connection

SHDWN 8 shut-down input

handbook, halfpage

1

VSEL SHDWN

2

SYNC ILIM

OUT GND

SENSE LX

TEA1205AT

3

4

8

7

6

5

MGM697

Fig.2 Pin configuration.

FUNCTIONAL DESCRIPTION

Control mechanism

The TEA1205AT DC/DC converter is able to operate in

discontinuous or continuous conduction operation.

All switching actions are completely determined by a

digital control circuit which uses the output voltage level as

its control input. This novel digital approach enables the

use of a new pulse width and frequency modulation

scheme, which ensures optimum power efficiency over the

complete range of operation of the converter. The scheme

works as follows. At low output power, a very small current

pulse is generated in the inductor, and the pulse rate

varies with a varying load. When the output voltage drops

below a specific limit, which indicates that the converter’s

current capability is not sufficient, the digital controller

switches to the next state of operation. The peak current in

the inductor is made higher, and the pulse rate can again

vary with a varying load. A third operation state is available

for again higher currents.

When high output power is requested, the device starts

operating in continuous conduction mode. This results in

minimum AC currents in the circuit components and hence

optimum efficiency, cost, and EMC. In this mode, the

output voltage is allowed to vary between two predefined

voltage levels. As long as the output voltage stays within

this so-called window, switching continues in a fixed

pattern. When the output voltage reaches one of the

window borders, the digital controller immediately reacts

by adjusting the pulse width and inserting a current step in

such a way that the output voltage stays within the window

with higher or lower current capability. This approach

enables very fast reaction to load variations. Figure 3

shows the various coil current waveforms for low and high

current capability in each power conversion mode.

Figure 4 shows the converter’s response to a sudden load

increase. The upper trace shows the output voltage.

The ripple on top of the DC level is a result of the current

in the output capacitor, which changes in sign twice per

cycle, times the capacitor’s internal Equivalent Series

Resistance (ESR). After each ramp-down of the inductor

current, i.e. when the ESR effect increases the output

voltage, the converter determines what to do in the next

cycle. As soon as more load current is taken from the

output the output voltage starts to decay. When the output

voltage becomes lower than the low limit of the window,

a corrective action is taken by a ramp-up of the inductor

current during a much longer time. As a result, the DC

current level is increased and normal continuous

conduction mode can continue. The output voltage

(including ESR effect) is again within the predefined

window.

Figure 5 depicts the spread of the output voltage window.

The absolute value is most dependent on spread, while the

actual window size is not affected. For one specific device,

the output voltage will not vary more than 4%.

Start-up

A possible deadlock situation in boost configuration can

occur after a sequence of disconnecting and reconnecting

the input voltage source. If, after disconnection of the input

source, the output voltage falls below 2.0 V, the device

may not restart properly after reconnection of the input

source, and may take continuous current from the input.

An external circuit to prevent the deadlock situation is

shown in Chapter “Application information”.

Shut-down

When the shut-down pin is made HIGH, the converter

disables both switches and power consumption is reduced

to a few µA.

1998 Mar 24 5

Loading...

Loading...